3

0

Cont

i

t(T

150_C

)

a

I

A

C

/

查询SI5435DC供应商

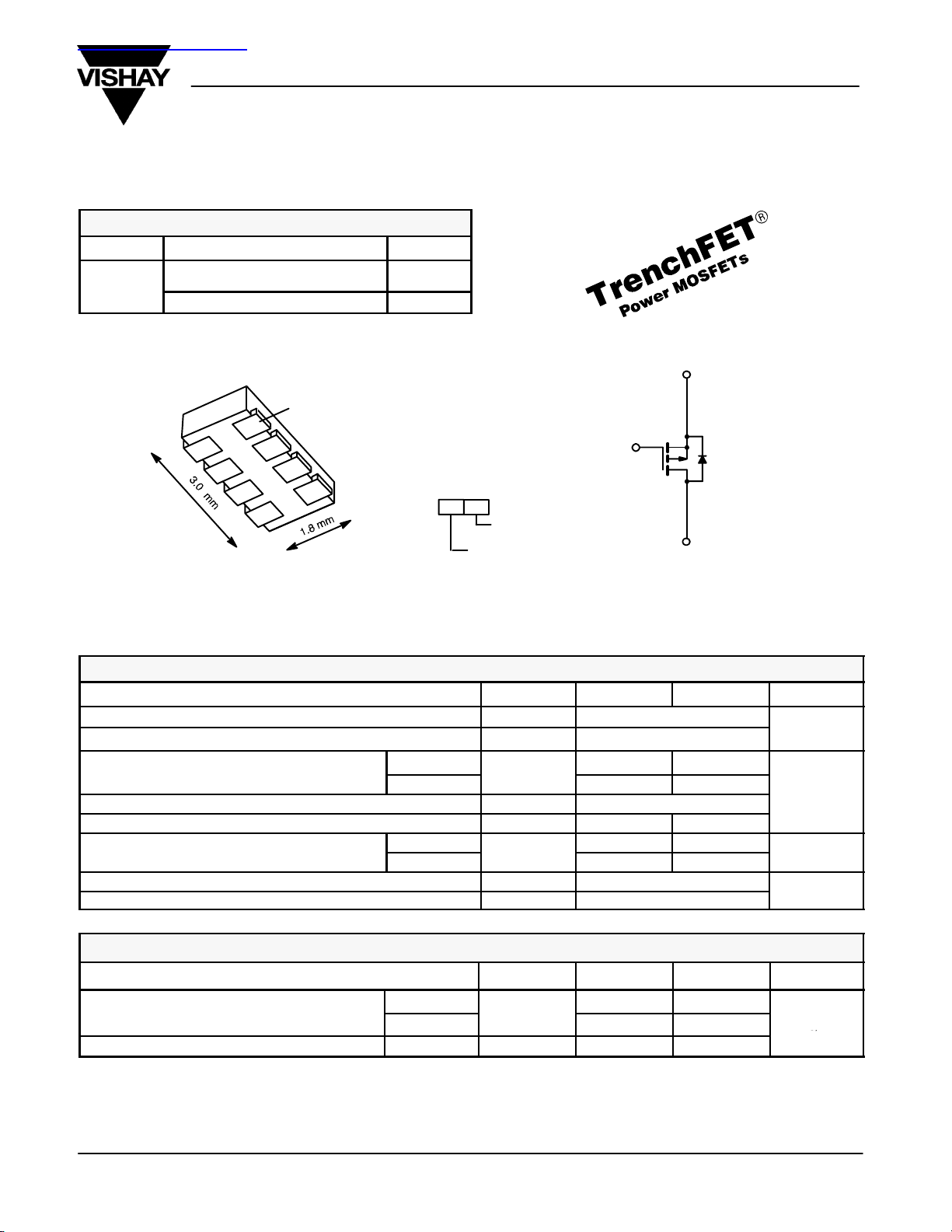

PRODUCT SUMMARY

VDS(V) r

--

--

0.050 @ VGS=--10V

0.080 @ VGS=--4.5 V -- 4 . 0

P-Channel 30-V (D-S) MOSFET

(Ω) ID(A)

DS(on)

-- 5 . 6

Si5435DC

Vishay Siliconix

1206-8 ChipFETt

D

D

D

D

D

S

Bottom View

1

G

D

G

Marking Code

BE XX

Part # Code

Lot Traceability

and Date Code

P-Channel MOSFET

S

D

Ordering Information: Si5435DC-T1

ABSOLUTE MAXIMUM RATINGS (TA=25_C UNLESS OTHERWISE NOTED)

Parameter Symbol 5 secs Steady State Unit

Drain-Source Voltage V

Gate-Source Voltage V

a

=

nuousDrainCurren

Pulsed Drain Current I

Continuous Source Current

Maximum Power Dissipation

Operating Junction and Storage Temperature Range TJ,T

Soldering Recommendations (Peak Temperature)

_

=

J

a

a

b, c

TA=25_C

TA=85_C

TA=25_C

TA=85_C

DM

I

P

DS

GS

D

S

D

stg

-- 5 . 6

-- 4 . 0 -- 2 . 9

-- 2 . 1 -- 1 . 1

2.5 1.3

1.3 0.7

-- 3 0

20

-- 3 0

-- 55 to 150

260

-- 4 . 1

_

_C

V

W

THERMAL RESISTANCE RATINGS

Parameter Symbol Typical Maximum Unit

Maximum Junction-to-Ambient

Maximum Junction-to-Foot (Drain) Steady State R

Notes

a. Surface Mounted on 1” x 1” FR4 Board.

b. See Reliability Manual for profile. The ChipFET is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation

process in manufacturing. A solder fillet at the exposed c opper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection.

c. Rework Conditions: manual soldering with a soldering iron is not recommended for leadless components.

Document Number: 71144

S-21251—Rev. B, 05-Aug-02

a

t ≤ 5sec

Steady State

R

thJA

thJF

40 50

80 95

15 20

_C/W

www.vishay.com

2-1

Si5435DC

A

V

V

D

D

=--15

V,RL=15

Ω

Vishay Siliconix

SPECIFICATIONS (TJ=25_C UNLESS OTHERWISE NOTED)

Parameter Symbol Test Condition Min Typ Max Unit

Static

Gate Threshold Voltage V

Gate-Body Leakage I

Zero Gate Voltage Drain Current I

On-State Drain Current

Drain-Source On-State Resistance

Forward Transconductance

Diode Forward Voltage

Dynamic

Total Gate Charge Q

Gate-Source Charge Q

Gate-Drain Charge Q

Turn-On Delay Time t

Rise Time t

Turn-Off Delay Time t

Fall Time t

Source-Drain Reverse Recovery Time t

Notes

a. Pulse test; pulse width ≤ 300 ms, duty cycle ≤ 2%.

b. Guaranteed by design, not subject to production testing.

b

a

a

a

a

GS(th)

GSS

DSS

I

D(on)

r

DS(on)

g

V

d(on)

d(off)

fs

SD

gs

gd

r

f

rr

VDS=VGS,ID= --250 mA -- 1 V

VDS=0V,VGS= 20 V 100 nA

VDS=--24V,VGS=0V -- 1

VDS=--24V,VGS=0V,TJ=85_C -- 5

VDS-- 5 V, VGS=--10V -- 3 0 A

VGS=--10V, ID=--4.1A 0.042 0.050

VGS=--4.5V,ID=--3.1A 0.070 0.080

VDS=--15V,ID=--4.1A

IS=--1.1A,VGS=0V -- 0 . 8 -- 1 . 2 V

g

VDS=--15V, VGS=--10V,ID=--4.1A 3.6 nC

ID≅ -- 1 A , V

=--15V,R

GEN

IF= --1.1 A, di/dt = 100 A/ms 30 60

=15Ω

=--10V,RG=6Ω

8 S

16 24

3.1

11 20

5 10

40 80

20 40

m

Ω

ns

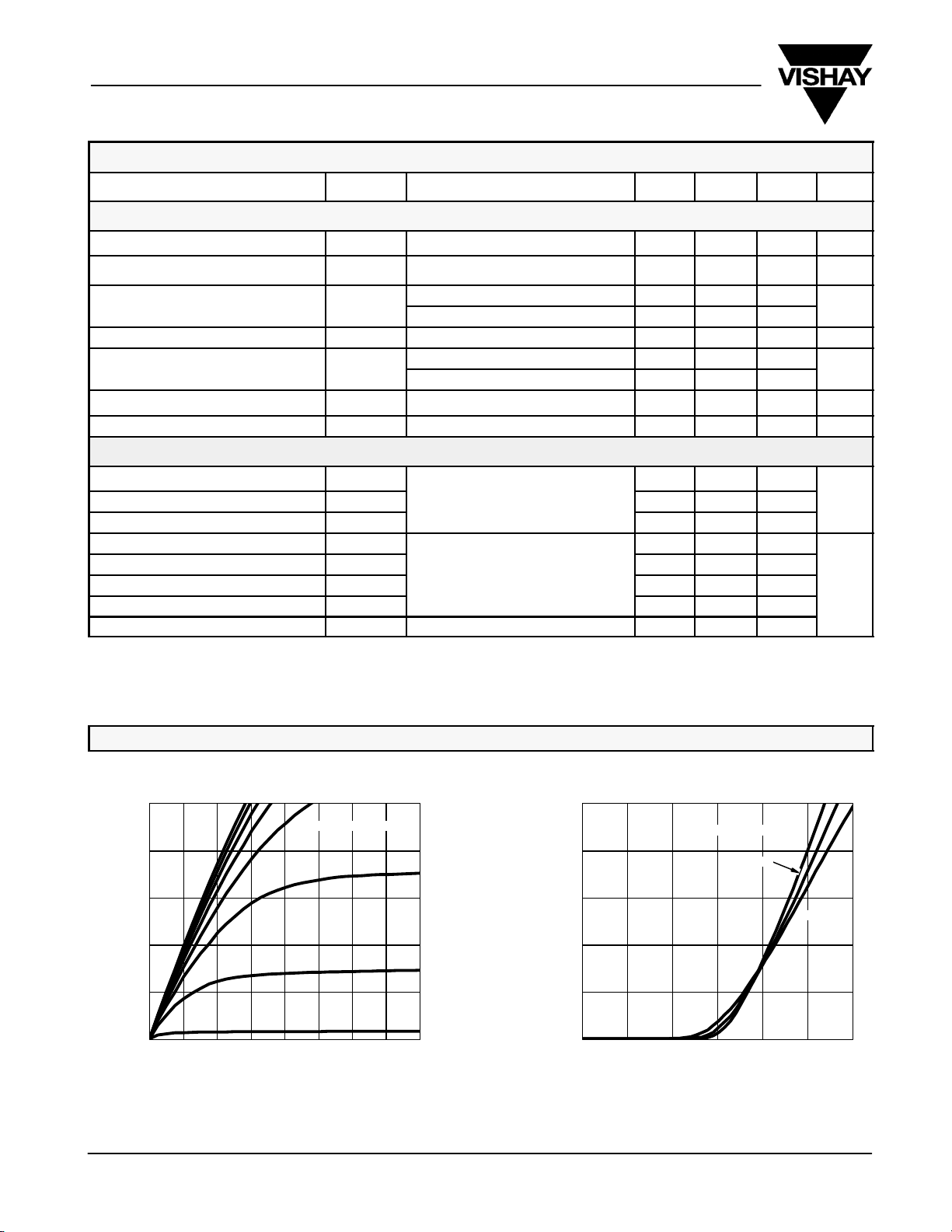

TYPICAL CHARACTERISTICS (25_C UNLESS NOTED)

30

24

18

12

-- Drain Current (A)I

D

6

0

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

www.vishay.com

2-2

Output Characteristics Transfer Characteristics

VGS=10thru6V

5V

4V

3V

VDS-- Drain-to-Source Voltage (V)

30

TC=--55_C

24

18

12

-- Drain Current (A)I

D

6

0

0123456

VGS-- Gate-to-Source Voltage (V)

25_C

Document Number: 71144

S-21251—Rev. B, 05-Aug-02

125_C

TYPICAL CHARACTERISTICS (25_C UNLESS NOTED)

Si5435DC

Vishay Siliconix

On-Resistance vs. Drain Current

0.16

Ω )

0.12

VGS=10V

0.08

-- On-Resistance (r

DS(on)

0.04

0.00

0 6 12 18 24 30

I

-- Drain Current (A)

D

VGS=4.5V

1200

900

600

C -- Capacitance (pF)

300

0

0 6 12 18 24 30

Gate Charge

10

8

6

VDS=15V

I

=4.1A

D

1.6

Ω)

1.4

1.2

C

iss

C

rss

On-Resistance vs. Junction Temperature

VGS=10V

I

=4.1A

D

Capacitance

C

oss

VDS-- Drain-to-Source Voltage (V)

4

-- Gate-to-Source Voltage (V)

GS

2

V

0

0 4 8 12 16

Qg-- Total Gate Charge (nC)

Source-Drain Diode Forward Voltage On-Resistance vs. Gate-to-Source Voltage

30

TJ= 150_C

10

-- Source Current (A)I

S

1

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

VSD-- Source-to-Drain Voltage (V) VGS-- Gate-to-Source Voltage (V)

TJ=25_C

(Normalized)

-- On-Resistance (r

1.0

DS(on)

0.8

0.6

-- 50 -- 25 0 25 50 75 100 125 150

TJ-- Junction Temperature (_C)

0.16

Ω )

0.12

ID=4.1A

0.08

-- On-Resistance (r

0.04

DS(on)

0.00

0246810

Document Number: 71144

S-21251—Rev. B, 05-Aug-02

www.vishay.com

2-3

Si5435DC

Vishay Siliconix

TYPICAL CHARACTERISTICS (25_C UNLESS NOTED)

Threshold Voltage

0.8

0.6

ID= 250 mA

0.4

0.2

Variance (V)V

GS(th)

0.0

-- 0 . 2

-- 0 . 4

-- 50 -- 25 0 25 50 75 100 125 150

TJ-- T emperature (_C)

Normalized Thermal Transient Impedance, Junction-to-Ambient

2

1

Duty Cycle = 0.5

0.2

0.1

0.1

0.01

0.05

0.02

Single Pulse

-- 4

10

-- 3

10

Thermal Impedance

Normalized Effective Transient

Single Pulse Power

50

40

30

Power (W)

20

10

0

-- 3

10

-- 2

10

-- 1

1 10 60010

10

Square Wave Pulse Duration (sec)

-- 1

-- 2

Time (sec)

Notes:

P

DM

t

1. Duty Cycle, D =

2. Per Unit Base = R

3. TJM-- TA=PDMZ

4. Surface Mounted

1 100 6001010

1

t

2

t

1

t

2

=80_C/W

thJA

(t)

thJA

100

2

1

0.1

Thermal Impedance

Normalized Effective Transient

0.01

www.vishay.com

2-4

Duty Cycle = 0.5

0.2

0.1

0.05

0.02

-- 4

10

Single Pulse

Normalized Thermal Transient Impedance, Junction-to-Foot

-- 3

10

-- 2

10

-- 1

Square Wave Pulse Duration (sec)

11010

Document Number: 71144

S-21251—Rev. B, 05-Aug-02

Loading...

Loading...