VIS VG26V17400EJ-6, VG26V17400EJ-5, VG26S17400EJ-5, VG26S17400EJ-6 Datasheet

Document : 1G5-0142 Rev.1 Page 1

VIS

VG26(V)(S)17400E

4,194,304 x 4 - Bit

CMOS Dynamic RAM

Description

The device is CMOS Dynamic RAM organized as 4,194,304 words x 4 bits. It is fabricated

with an advanced submicron CMOS technology and designed to operate from a single 5V only

or 3.3V only power supply. Low voltage operation is more suitable to be used on battery

backup, portable electronic application. A new refresh feature called “ self-refresh “ is supported

and very slow CBR cycles are being performed. It is packaged in JEDEC standard 26/24 - pin

plastic SOJ or TSOP (II).

Features

• Single 5V (%) or 3.3V (%) only power supply

• High speed t

RAC

access time : 50/60 ns

• Low power dissipation

- Active mode : 5V version 605/550 mW (Max.)

3.3V version 396/360 mW (Max.)

- Standby mode : 5V version 1.375 mW (Max.)

3.3V version 0.54 mW (Max.)

• Fast Page Mode access

• I/O level : TTL compatible (Vcc = 5V)

LVTTL compatible (Vcc = 3.3V)

• 2048 refresh cycles in 32 ms (Std) or 128ms (S - version)

• 4 refresh mode :

- RAS only refresh

- CAS-before-RAS refresh

- Hidden refresh

- Self - refresh (S - version)

10

±

10±

Document : 1G5-0142 Rev.1 Page 2

VIS

VG26(V)(S)17400E

4,194,304 x 4 - Bit

CMOS Dynamic RAM

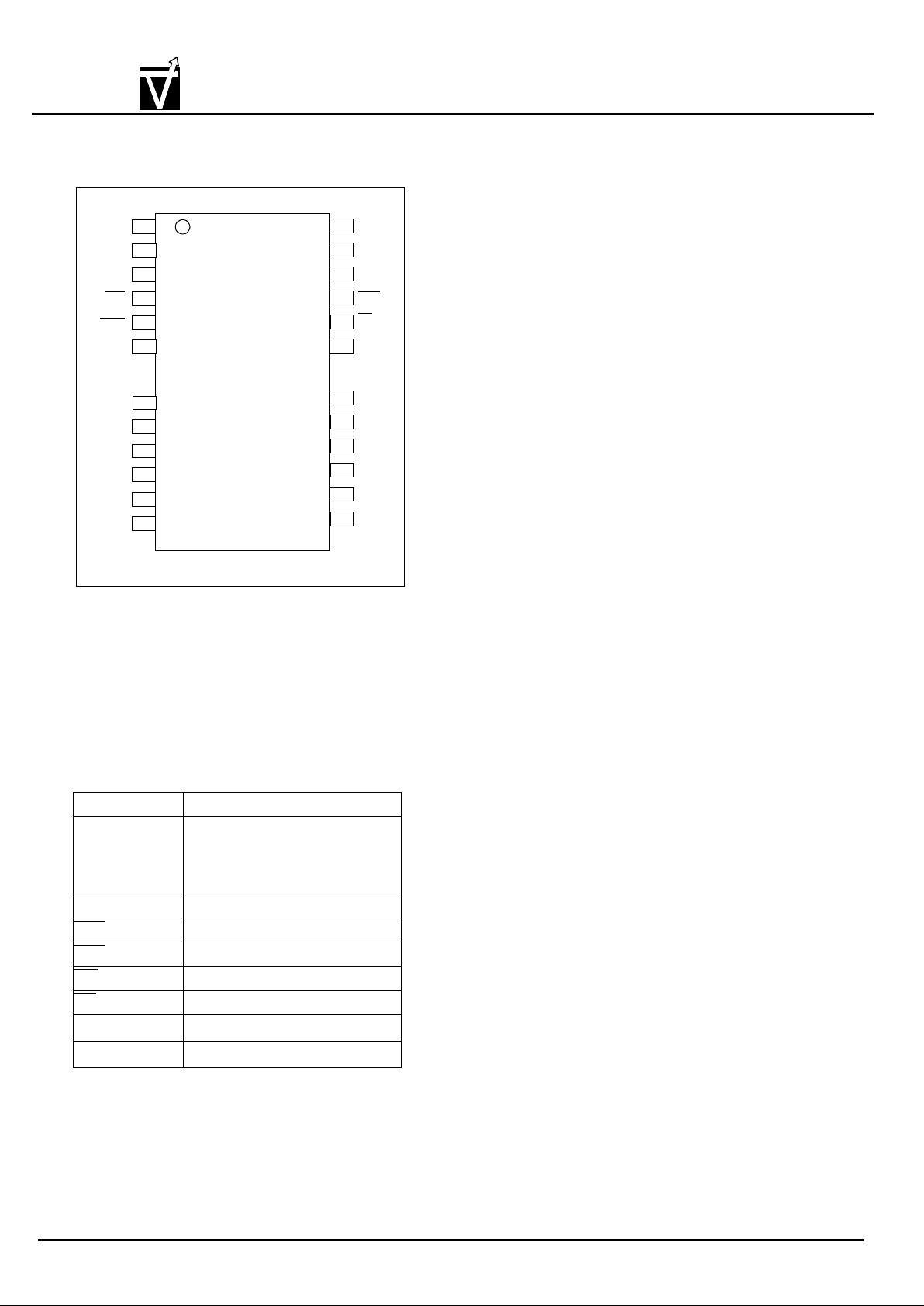

Pin Description

Pin Name Function

A0 - A10 Address inputs

- Row address A0 - A10

- Column address A0 - A10

- Refresh address A0 - A10

DQ1 ~ DQ4 Data - in/data - out

RAS Row address strobe

CAS Column address strobe

WE Write enable

OE Output enable

V

cc

Power (+ 5V or + 3.3V)

V

ss

Ground

VG26(V) (S)17400EJ

DQ1

WE

V

SS

DQ4

A

2

A

3

V

CC

A

0

A

1

A

10

V

CC

A

8

A

7

A

6

A

5

A

4

V

SS

1

2

3

4

5

6

CAS

OE

A

9

26

25

24

23

22

21

8

9

10

11

12

13

19

18

17

16

15

14

RAS

DQ3

NC

DQ2

Pin configuration

26/24 - PIN 300mil Plastic SOJ

Document : 1G5-0142 Rev.1 Page 3

VIS

VG26(V)(S)17400E

4,194,304 x 4 - Bit

CMOS Dynamic RAM

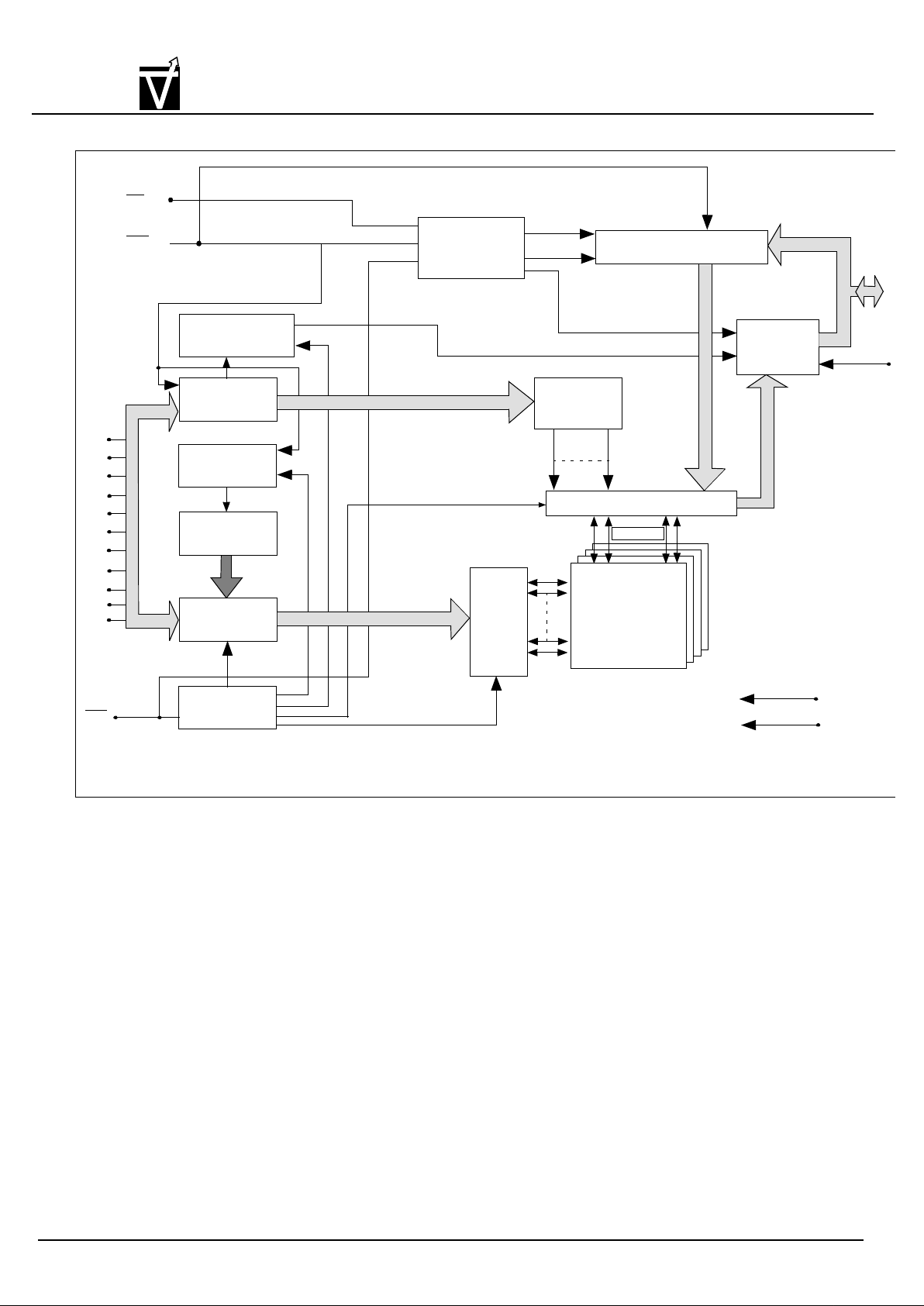

WE

GENERATOR

COLUMN-

ADDRESS

BUFFERS (11)

REFRESH

CONTROLLER

REFRESH

COUNTER

BUFFERS (11)

ADDRESS

ROW

NO. 1 CLOCK

GENERATOR

A0

RAS

A1

A2

A3

A4

A5

A6

A7

A8

CONTROL

LOGIC

DATA - IN BUFFER

DATA - OUT

BUFFER

DQ1

DQ4

COLUMN

DECODER

2048

SENSE AMPLIFIERS

I/O GATING

2048 x 4

2048 x 2048 x 4

MEMORY

ARRAY

2048

ROW

DECODER

Vcc

Vss

Block Diagram

CAS

A9

A10

NO. 2 CLOCK

Document : 1G5-0142 Rev.1 Page 4

VIS

VG26(V)(S)17400E

4,194,304 x 4 - Bit

CMOS Dynamic RAM

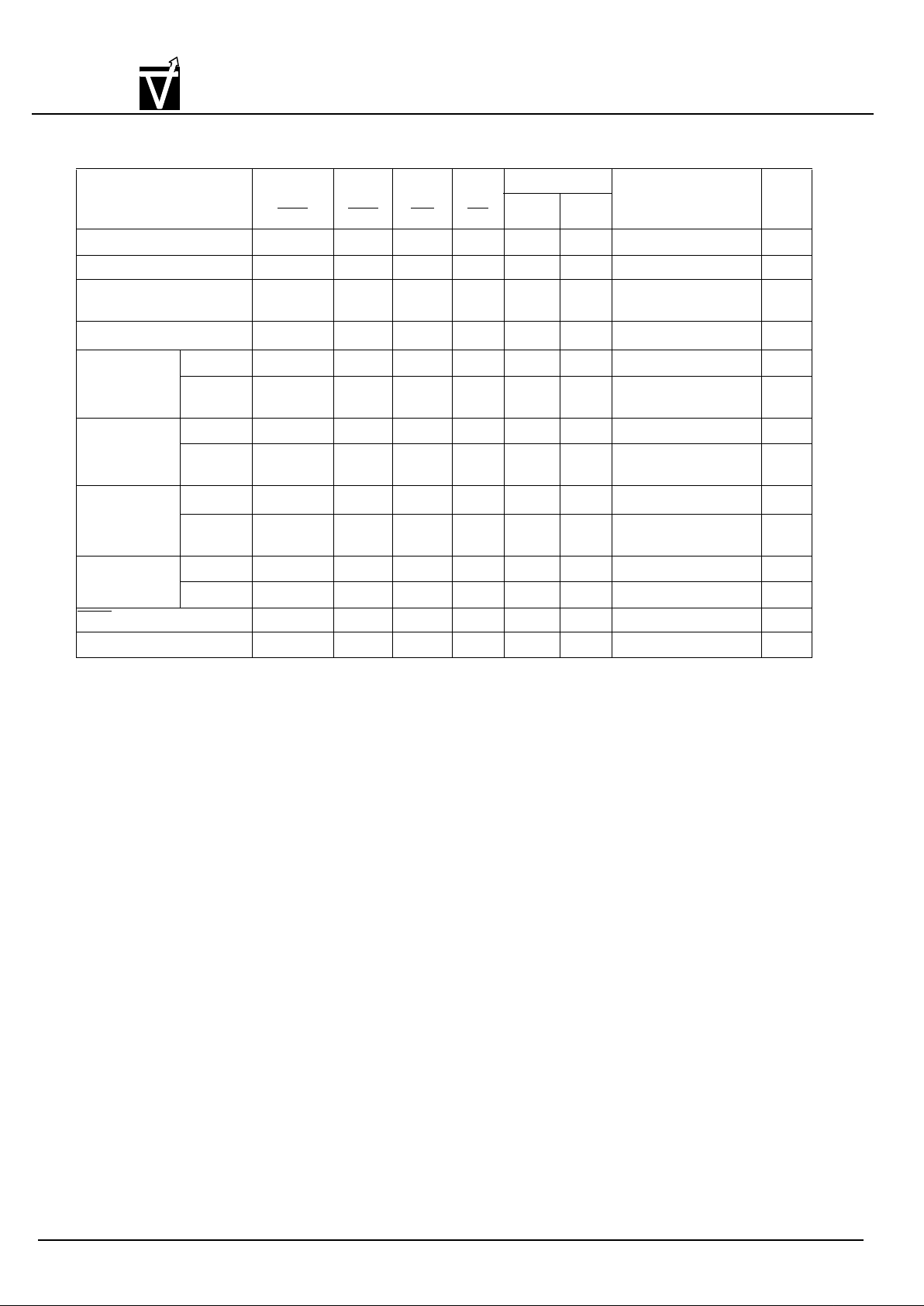

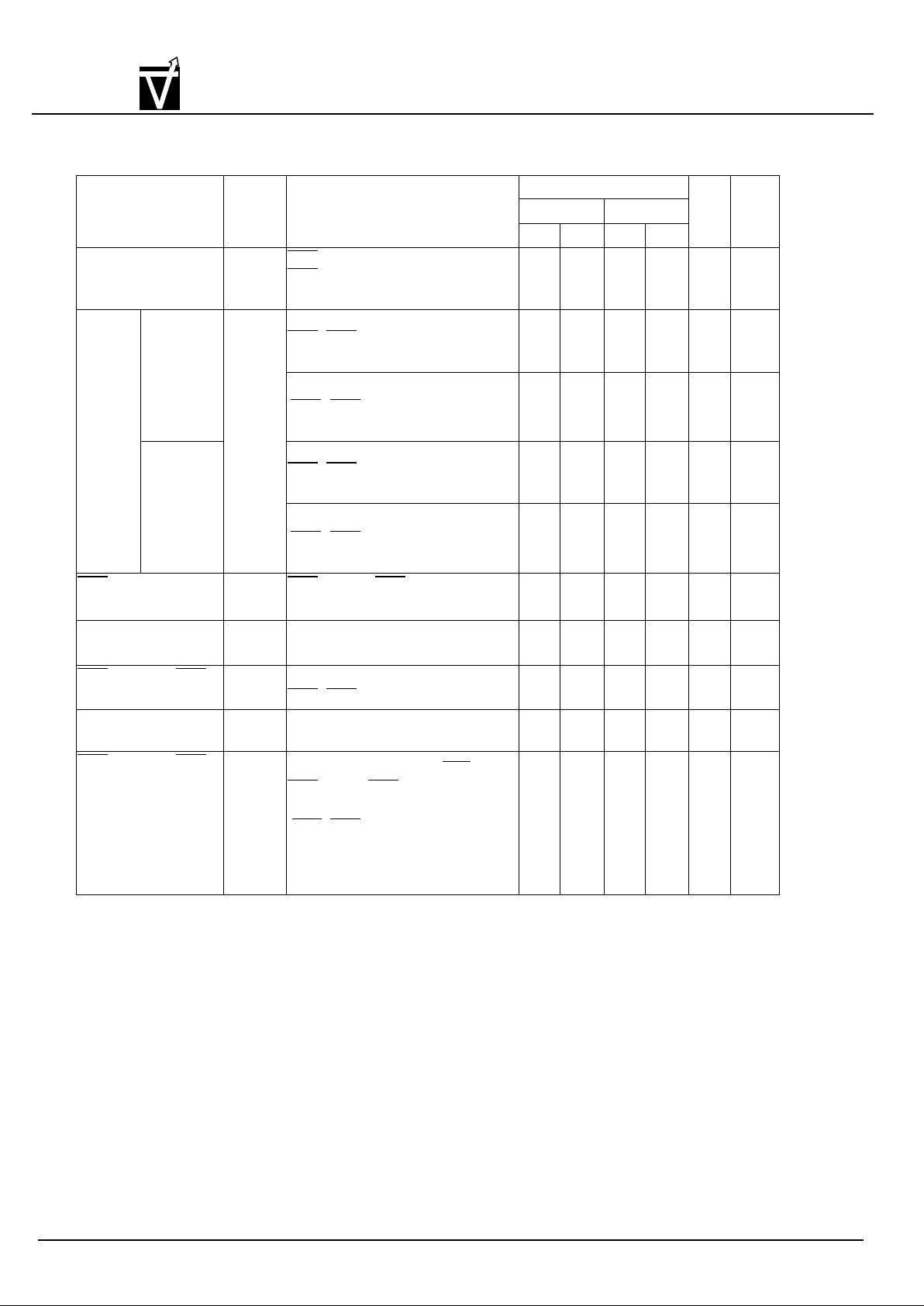

Truth Table

Notes : 1. EARLY WRITE only.

FUNCTION RAS CAS WE OE

ADDRESSES

DQ

S

Notes

ROW COL

STANDBY H X X X X High - Z

READ L L H L ROW COL Data - Out

WRITE : (EARLY

WRITE)

L L L X ROW COL Data - In

READ WRITE L L ROW COL Data - Out, Data - In

PAGE -

MODE READ

1st Cycle L H L ROW COL Data - Out

2st

Cycle

L H L n/a COL Data - Out

PAGE -

MODE WRITE

1st Cycle L L X ROW COL Data - In

2st

Cycle

L L X n/a COL Data - In

PAGE - MODE

READ - WRITE

1st Cycle L ROW COL Data - Out, Data - In

2st

Cycle

L n/a COL Data - Out, Data - In

HIDDEN

REFRESH

READ L H L ROW COL Data - Out

WRITE L L X ROW COL Data - In 1

RAS - ONLY REFRESH L H X X ROW n/a High - Z

CBR REFRESH L H X X X High - Z

HX

→

HL

→

LH→

HL→

HL→

HL→

HL→

HL

→

HL

→

LH

→

HL

→

HL

→

LH

→

LHL→→

LHL→→

HL

→

Document : 1G5-0142 Rev.1 Page 5

VIS

VG26(V)(S)17400E

4,194,304 x 4 - Bit

CMOS Dynamic RAM

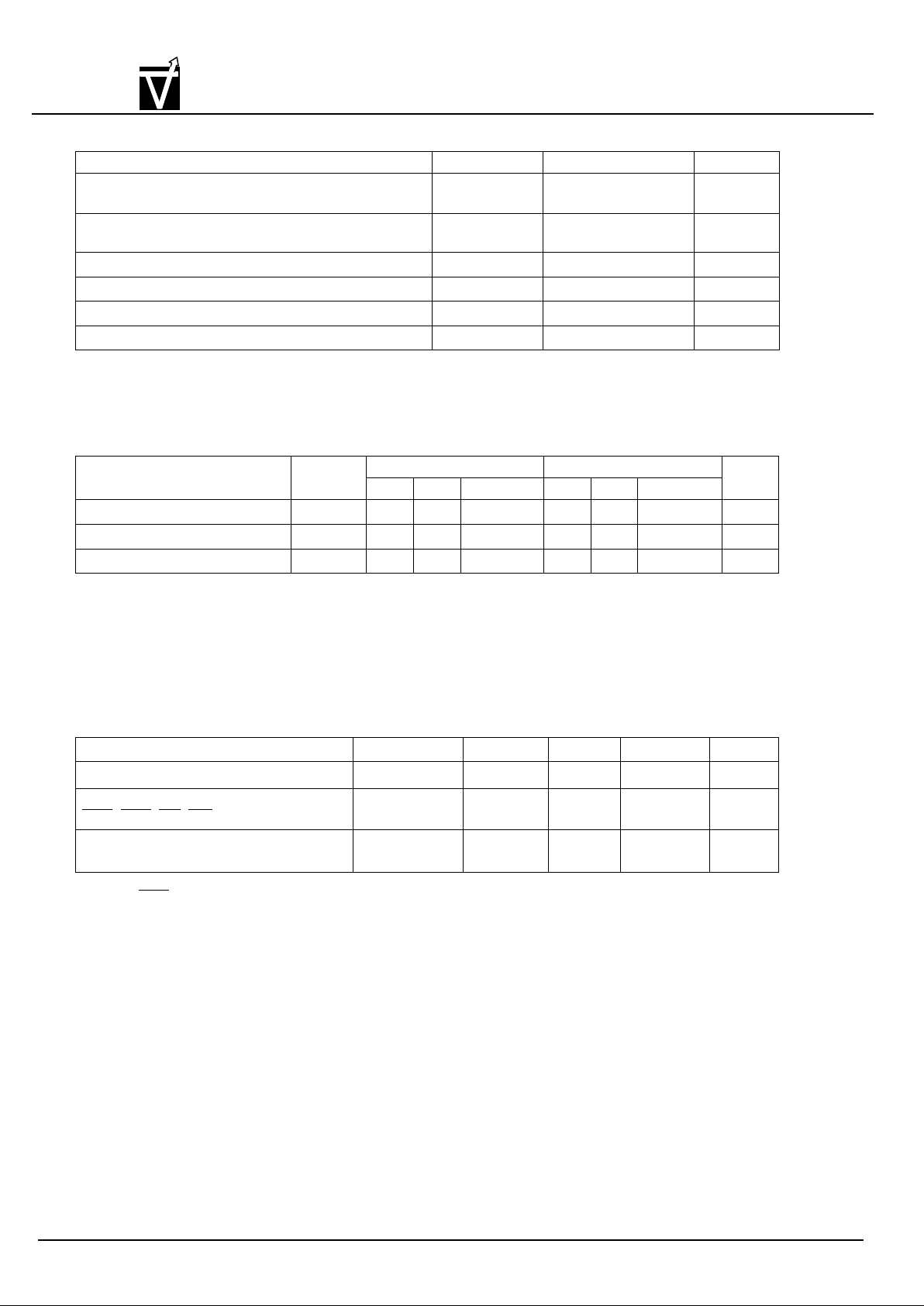

Absolute Maximum Rating

Recommended DC Operating Conditions

Capacitance

Ta = 25°C, V

CC

= % or %, f = 1MHz

Note : 1. Capacitance measured with effective capacitance measuring method.

2. CAS = VIH to disable Dout.

Parameter Symbol Value Unit

Voltage on any pin relative to Vss 5V

3.3V

V

T

-1.0 to + 7.0

-0.5 to + 4.6

V

Supply voltage relative to Vss 5V

3.3V

V

cc

-1.0 to + 7.0

-0.5 to + 4.6

V

Short circuit output current I

OUT

50 mA

Power dissipation P

D

1.0 W

Operating temperature T

OPT

0 to + 70 °C

Storage temperature T

STG

-55 to + 125 °C

Parameter/Condition Symbol 5 Volt Version 3.3 Volt Version Unit

Min Typ Max Min Typ Max

Supply Voltage V

cc

4.5 5.0 5.5 3.0 3.3 3.6 V

Input High Voltage, all inputs V

IH

2.4 - V

CC

+ 1.0 2.0 - V

CC

+ 0.3 V

Input Low Voltage, all inputs V

IL

-1.0 - 0.8 -0.3 - 0.8 V

Parameter Symbol Typ Max Unit Note

Input capacitance (Address) C

l1

- 5 pF 1

Input capacitance

(RAS, CAS, OE, WE)

C

l2

- 7 pF 1

Output capacitance

(Data - in, Data - out)

C

I/O

- 7 pF 1,2

±

3.3V10

±

Document : 1G5-0142 Rev.1 Page 6

VIS

VG26(V)(S)17400E

4,194,304 x 4 - Bit

CMOS Dynamic RAM

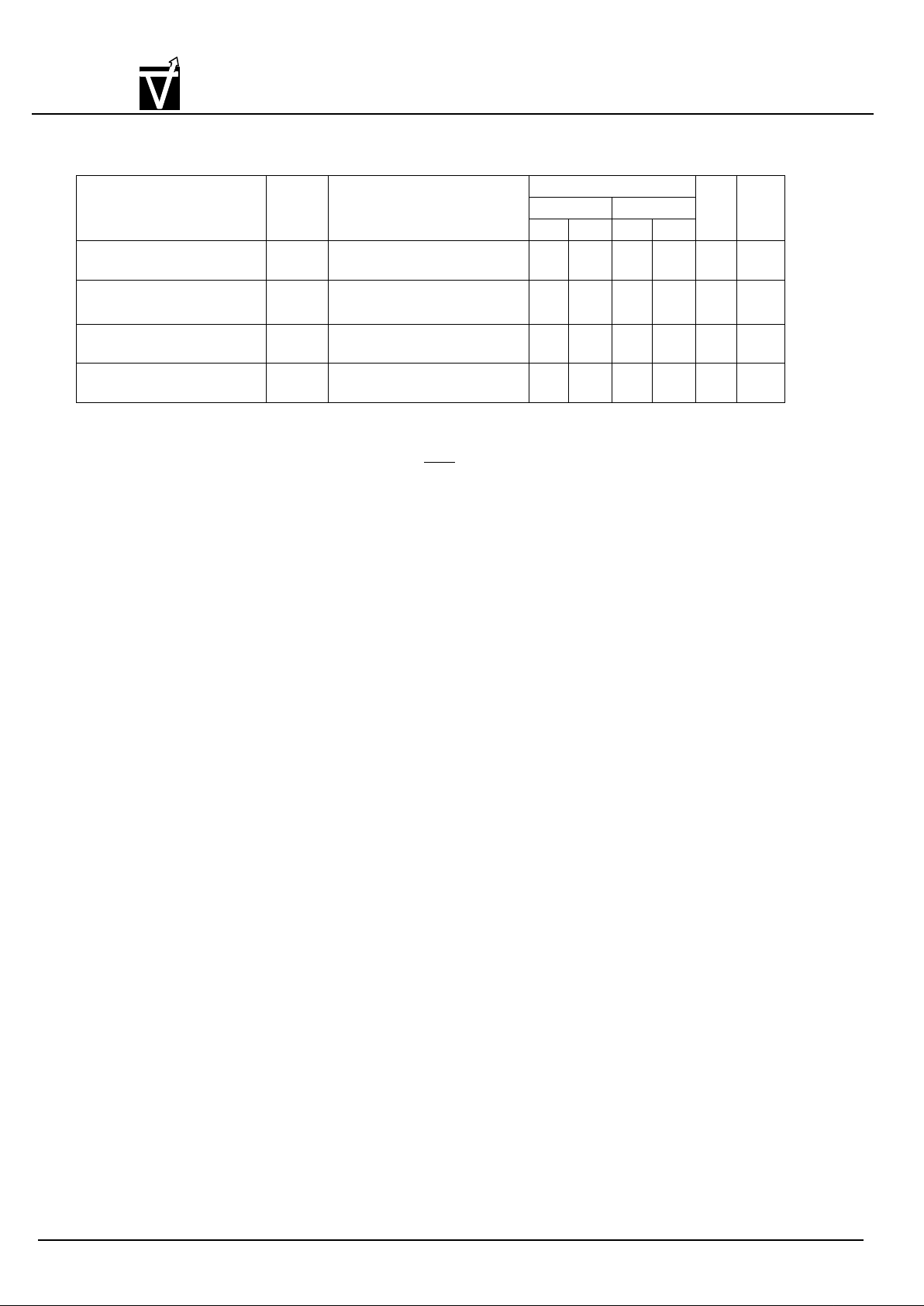

DC Characteristics; 5 - Volt verion

(Ta= 0 to 70°C, VCC = + 5V10%, V

ss

= 0V)

Parameter Symbol Test Conditions

VG26 (V) (S) 17400E

Unit Notes

-5 -6

Min Max Min Max

Operating

current I

CC1

RAS cycling

CAS cycling

tRC = min.

- 110 - 100 mA 1, 2

Standby

Current

Low

power

S - version

I

CC2

TTL interface

RAS, CAS = V

IH

Dout = high - Z

- 2 - 2

mA

CMOS interface

- 0.2V

Dout = high - Z

- 0.25 - 0.25

mA

Standard

power

version

TTL interface

RAS, CAS = V

IH

Dout = high - Z

- 2 - 2

mA

CMOS interface

- 0.2V

Dout = high - Z

- 1 - 1

mA

RAS - only

refresh current

I

CC3

RAS cycling, CAS = V

IH

t

RC

= min.

- 110 - 100

mA

1, 2

Fast page mode

current

I

CC4

t

PC

= min.

- 80 - 70

mA

1,3

CAS - before - RAS

refresh current

I

CC5tRC

= min.

RAS, CAS cycling

- 110 - 100

mA

1, 2

Self - refresh currant

(S - Version)

I

CC8

- 350 - 350

CAS - before - RAS

long refresh

current (S - Version)

I

CC9

Standby : VCC CAS before RAS refresh :

2048 cycles/128ms

RAS, RAS :

VCC - (Max)

Dout = high - Z,

- 500 - 500

±

RASCAS,V

CC

≥

RASCAS,V

CC

≥

t

RASS

100µS≥µA

0.2V

RAS

≤

0VVIL0.2V

≤≤

0.2VV

IHVIH

≤≤

t

RAS

300ns

≤

µA

Document : 1G5-0142 Rev.1 Page 7

VIS

VG26(V)(S)17400E

4,194,304 x 4 - Bit

CMOS Dynamic RAM

DC Characteristics ; 5 - Volt Version (cont.)

(Ta = 0 to 70°C, V

CC

= + 5V10%, V

ss

= 0V)

Notes :

1. lCC is specified as an average current. It depends on output loading condition and cycle rate when

the device is selected. lCC max is specified at the output open condition.

2. Address can be changed once or less while RAS = VIL.

3. For l

CC4

, address can be changed once or less within one Fast page mode cycle time.

Parameter Symbol Test Conditions

VG26 (V) (S) 17400E

Unit Notes

-5 -6

Min Max Min Max

lnput leakage

current

I

LI

+ 0.5V

-5 5 -5 5

Output leakage

current

I

LO

+ 0.5V

Dout = Disable

-5 5 -5 5

Output high

voltage

V

OH lOH

= -5mA 2.4 - 2.4 - V

Output low

voltage

V

OL lOL

= + 4.2mA - 0.4 - 0.4 V

±

0VVinV

CC

≤≤

µA

0VVoutV

CC

≤≤

µA

Document : 1G5-0142 Rev.1 Page 8

VIS

VG26(V)(S)17400E

4,194,304 x 4 - Bit

CMOS Dynamic RAM

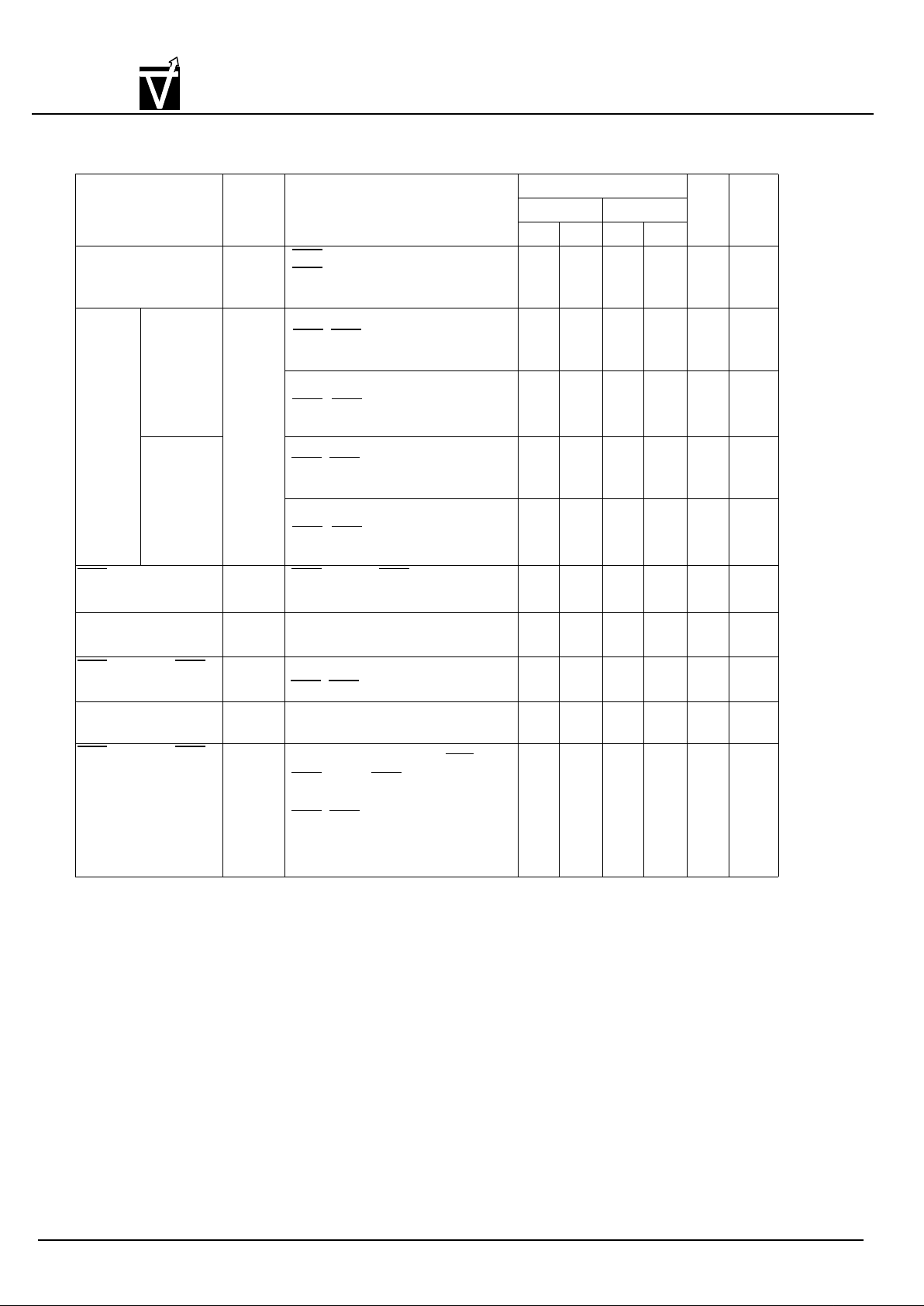

DC Characteristics ; 3.3 - Volt Verion

(Ta = 0 to 70°C, V

CC

= + 3.3V 10%, V

ss

= 0V)

Parameter Symbol Test Conditions

VG26 (V) (S) 17400E

Unit Notes

-5 -6

Min Max Min Max

Operating

current I

CC1

RAS cycling

CAS cycling

tRC = min.

- 110 - 100 mA 1, 2

Standby

Current

Low

power

S - version

I

CC2

LVTTL interface

RAS, CAS = V

IH

Dout = high - Z

- 0.5 - 0.5

mA

CMOS interface

- 0.2V

Dout = high - Z

- 0.25 - 0.25

mA

Standard

power

version

LVTTL interface

RAS, CAS = V

IH

Dout = high - Z

- 2 - 2

mA

CMOS interface

- 0.2V

Dout = high - Z

- 0.5 - 0.5

mA

RAS - only

refresh current

I

CC3

RAS cycling, CAS = V

IH

t

RC

= min.

- 110 - 100

mA

1, 2

Fast page mode

current

I

CC4

t

PC

= min.

- 80 - 70

mA

1,3

CAS - before - RAS

refresh current

I

CC5 tRC

= min.

RAS, CAS cycling

- 110 - 100

mA

1, 2

Self - refresh currant

(S - Version)

I

CC8

- 250 - 250

CAS - before - RAS

long refresh

current (S - Version)

I

CC9

Standby : VCC CAS before RAS refresh :

2048 cycles/128ms

RAS, RAS :

VCC - (Max)

Dout = high - Z,

- 300 - 300

±

RASCAS,V

CC

≥

RASCAS,V

CC

≥

t

RASS

100µS≥µA

0.2V

RAS

≤

0VV

IL

0.2V

≤≤

0.2VV

IHVIH

≤≤

t

RAS

300ns

≤

µA

Loading...

Loading...