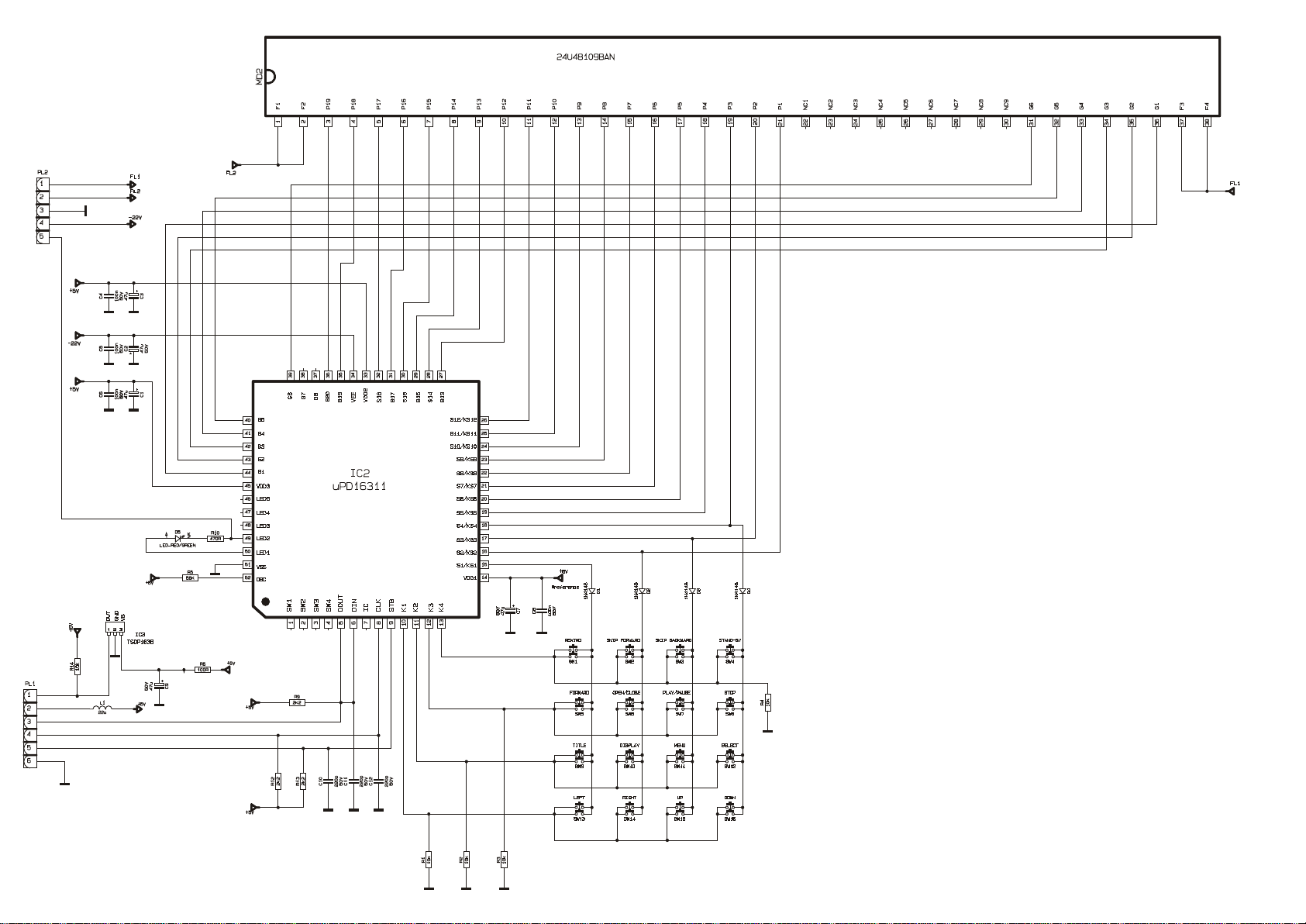

Vestel DVD 2100 Schematic

DVD BACK PANEL BOARD

DVD-FRONT PANEL

DVD SMPS 002

#BPRESET

SPDIF

PCMCLK

SCLK

LRCLK

SDATA0

SDATA1

SDATA2

BPPIO0

BPPIO1

BPPIO2

BPPIO3

SCL

SDA

STANDBY voltages still carry power durin g Standby Mode

VCC-STANDBY

J11

10

11

12

13

14

15

16

17

18

19

20

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

FFC20

4

2

3

1

#BPRESET

SPDIF

SPDIF_IN

PCMCLK

SCLK

LRCLK

SDATA0

SDATA1

SDATA2

BPPIO0

BPPIO1

BPPIO2 LUMA_OUT

BPPIO3

SCL

SDA

R145

75R

C145

47pF

Reserv ed for SPDIF input

RED

GREEN

BLUE

CHROMA

LUMA

CVBS

VCC-PCM

U13

MCLK

SCLK

LRCLK

SDATA

CS4334

7

AOUTL

VA

AOUTR

AGND

6

VIDFILTR

{Value}

C90

10uF

16V

C92

10uF

16V

RED

GREEN

BLUE

CHROMA

LUMA

CVBS

R60

100K

1%

R62

100K

1%

GREEN_OUT

CHROMA_OUT

R59

562R

1%

R61

562R

1%

GREEN

BLUE

CHROMA

LUMA

CVBS

8

5

VCC3-STANDBY

RED_OUT

BLUE_OUT

LUMA_OUT

CVBS_OUT

+12V +5V

RED_OUTRED

GREEN_OUT

BLUE_OUT

CHROMA_OUT

CVBS_OUT

C91

1500pF

C93

1500pF

-12V

10

11

12

13

14

15

16

17

18

19

20

1

2

3

4

5

6

7

8

9

J12

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

FFC20

JP11

1

2

3

4

5

6

HEADER 6

CVBS

LEFT

RIGHT

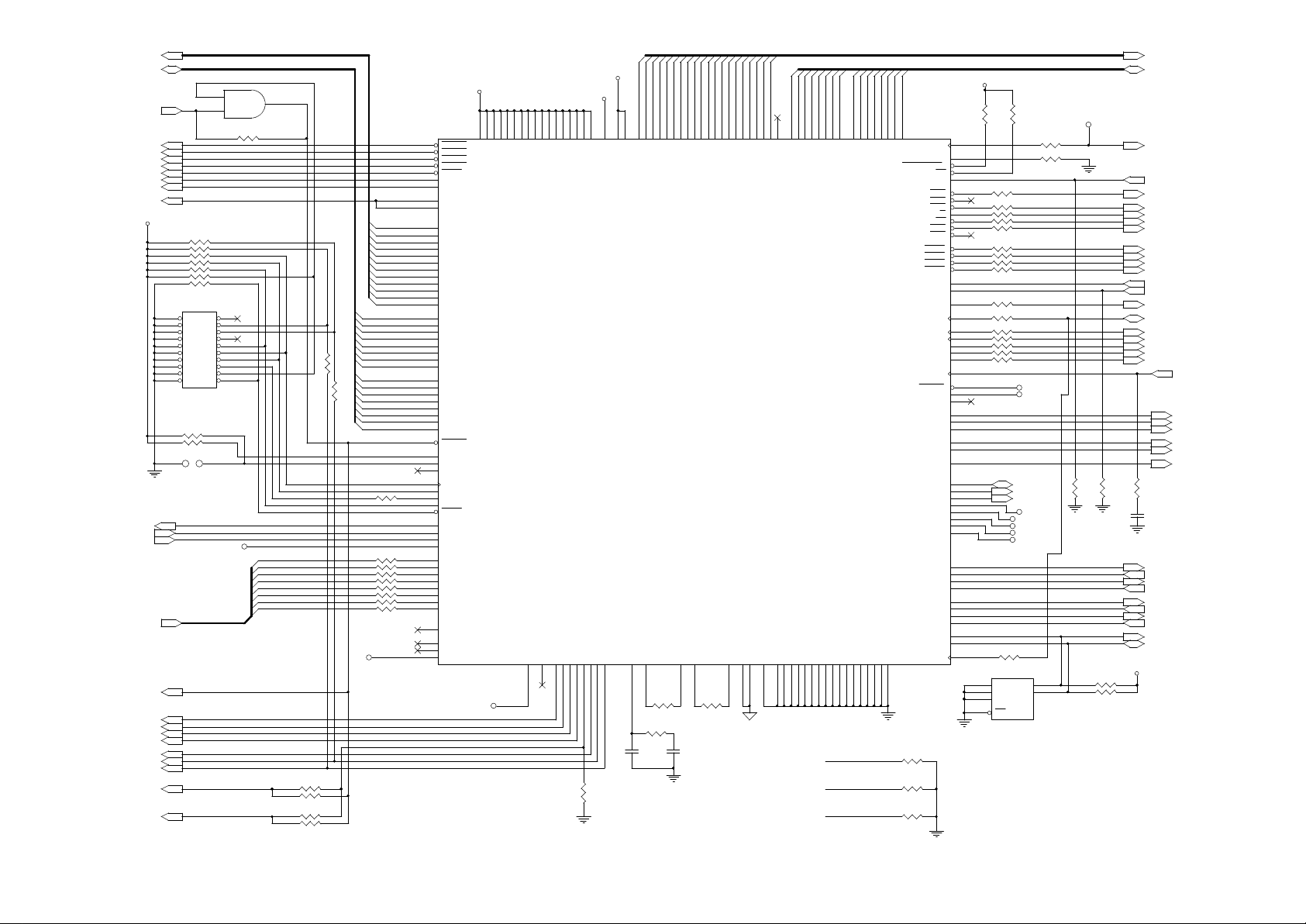

STI5505 - Back Panel Connectors

MA[0..11]

MD[0..15]

#POWERON_RESET

#SDCS0

#SDCS1

#SDRAS

#SDCAS

#SDWE

DQML

DQMU

SDCLK

PARA_REQ

PARA_SYNC

PARA_STR

PARA_DATA[0..7]

#RESET

BPPIO0

BPPIO1

BPPIO2

BPPIO3

SR0

FS0

FS1

#FERESET

#BPRESET

VCC3

R22 10K

R23 10K

PARA_DATA[0..7]

MA[0..11]

MD[0..15]

R12 10K

R13 10K

R14 10K

R15 10K

R16 10K

R17 10K

R18 10K

J3

12

34

56

78

910

1112

1314

1516

1718

1920

HEADER20

Shrouded

JP3

JUMPER

#RESET

BPPIO0

BPPIO1

BPPIO2

BPPIO3

SR0

FS0

FS1

#FERESET

#BPRESET

#JTAG_RESET

U3

1

2

LMOS TC4S81F

R9 NS

TRIGIN

TRIGOUT

TP15

4

TDO

PARA_DATA0

PARA_DATA1

PARA_DATA2

PARA_DATA3

PARA_DATA4

PARA_DATA5

PARA_DATA6

PARA_DATA7

R43 0R0

R44 NS

R49 0R0

R50 NS

R20 10K

R21 10K

R27 56R

PARA_REQ

PARA_SYNC

PARA_STR

PARA_DVALID

R28 220R

R29 220R

R30 220R

R31 220R

R32 220R

R33 220R

R34 220R

R35 220R

TP16

#SDCS0

#SDCS1

#SDRAS

#SDCAS

#SDWE

DQML

DQMU

SDCLK

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

#RESET

TCK

TDI

TMS

#TRST

VCC3

U1

84

SDCS0

85

SDCS1

88

SDRAS

VDD31VDD3

SDCAS

SDWE

DQML

DQMU

MEMCLKOUT

MEMCLKIN

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

RESET

PWM0/OSLINK_SEL

PWM1/BOOTFROMROM

PWM2

TCK

TDI

TDO

TMS

TRST

PARA_REQ/PIO0_3

PARA_SYNC/PIO0_0

PARA_STR/PIO0_4

PARA_DVALID

PARA_DATA0/PIO0_5

PARA_DATA1/PIO0_7

PARA_DATA2/B_DATA

PARA_DATA3/B_BCLK

PARA_DATA4/B_FLAG

PARA_DATA5/B_SYNC

PARA_DATA6/SDAV_CLK

PARA_DATA7/SDAV_DATA

SDAV_VALID

NRSS_CLK/B_WCLK

NRSS_IN/B_V4

NRSS_OUT

105

104

100

101

106

107

108

109

112

113

114

115

188

186

189

187

190

89

90

91

76

78

79

80

81

69

70

71

72

73

74

82

83

92

93

94

97

98

99

29

26

27

28

16

15

17

33

20

22

36

37

38

39

30

31

32

40

42

41

STi5505

#SOFT_RESET

18

34

VDD3

VDD3

TP11

67

75

VDD3

VDD3

86

VDD3

95

102

VDD3

PIO2_0

3

110

130

119

VDD3

VDD3

PIO1_4

199

139

VDD3

VDD3

PIO3_0

201

VCC3-PCM

149

171

159

VDD3

VDD3

PIO3_1

PIO3_2

202

203

204

VCC3-DENC

184

208

48

VDD3

VDD3

VDD3

PIO3_3

PIO3_4

PIO3_5

PIO3_6

2

205

206

207

R45

10K

53

VDDA3

VDDA3_PCM

PIO3_7

ADR1

161

60

VDDA3

VREF_PCM

49

ADR2

162

ADR1

ADR2

V_REF DAC RGB

58

18K7

R42

C87

330pF

ADR4

ADR3

163

164

ADR3

R40

10K

ADR5

165

ADR4

ADR5

ADR6

166

ADR7

167

ADR6

59

1%

ADR9

ADR8

168

169

ADR7

ADR8

I_REF DAC RGB

65

11K5

C88

.0033uF

ADR13

ADR15

ADR16

ADR14

ADR10

ADR11

ADR12

170

173

174

175

176

177

178

ADR9

ADR10

ADR11

ADR12

ADR13

ADR14

ADR15

V_REF DAC YC

I_REF DAC YC

54

66

R41

1%

ADR17

ADR18

179

180

ADR16

ADR17

VSSA

VSSA

61

ADR19

ADR20

181

182

183

ADR18

ADR19

ADR20

ADR21

VSS

VSSA_PCM

4

19

50

DATA0

DATA1

141

142

DATA0

VSS

VSS

68

35

DATA2

DATA3

143

144

DATA1

DATA2

VSS

VSS

87

77

DATA4

DATA5

DATA6

DATA7

145

146

147

148

DATA3

DATA4

DATA5

DATA6

VSS

VSS

VSS

VSS

96

103

120

111

PARA_DVALID

PARA_DATA6

PARA_DATA7

DATA8

DATA9

DATA10

DATA11

151

152

153

154

DATA7

DATA8

DATA9

DATA10

PIO0_6/PCM_OUT2

VSS

VSS

VSS

VSS

VSS

150

140

131

172

160

DATA12

DATA13

DATA14

DATA15

155

156

157

158

PPCCLK

DMAXFER

PPC_MODE

DATA11

DATA12

DATA13

DATA14

DATA15

READY

SPDIF

PCM_CLK

LRCLK

PCM_OUT0

PCM_OUT1

PIXCLK _27Mhz

HSYNC

ODD/EVEN

OSD_ACTIVE

R_OUT

G_OUT

B_OUT

Y_OUT

C_OUT

CVBS_OUT

YUV0/PIO4_0

YUV1/PIO4_1

YUV2/PIO4_2

YUV3/PIO4_3

YUV4/PIO4_4

YUV5/PIO4_5

YUV6/PIO4_6

YUV7/PIO1_3

PIO2_3

PIO2_4

PIO1_5/TXD1

PIO1_6/RXD1

PIO2_5

PIO2_7

PIO1_7/TXD3

PIO4_7/RXD3

PIO1_2/SCL

PIO1_0/SDA

AUXCLK

VSS

VSS

VSS

185

200

R147

10K

R148

10K

R149

10K

CE1

CE2

CE3

R/W

BE0

BE1

RAS0

RAS1

CAS0

CAS1

IRQ0

IRQ1

SCLK

CS

OE

VCC3

R7

10K

137

134

138

135

136

#READY

124

R127 33R

125

126

R128 33R

133

R129 33R

123

R130 33R

121

R131 33R

122

127

R132 33R

128

R133 33R

129

R134 33R

132

R135 33R

23

IR

25

INT

47

R202 33R

45

R19 33R

43

R203 33R

46

R204 33R

44

R205 33R

24

R206 33R

21

R207 33R

118

PIXCLK

51

52

117

57

RED

56

GREEN

55

BLUE

62

LUMA

63

CHROMA

64

CVBS

191

192

193

194

195

196

197

198

5

OPEN

6

#SENSE

11

CLOSE

12

#PUSH

7

RTS

8

CTS

13

TXD

14

RXD

10

SCL

9

SDA

R168 NS

116

1

2

3

7

I2C Address: 0xA0 (Write), 0xA1(Read)Default configuration

R8

10K

R10 33R

R11 10K

TP13

TP14

FP_DATA

FP_CLK

FP_STB

TP17

TP7

TP8

TP9

TP10

U2

A0

SCL

A1

SDA

A2

WC

I2C-EEPROM

256x8

SPDIF

AUDCLK

SCLK

LRCLK

SDATA0

SDATA1

SDATA2

6

5

ADR[1..20]

DATA[0..15]

TP1

#CE1

#CE3

R/W

#OE

#BE0

#RAS0

#RAS1

#CAS0

#CAS1

R24

10K

R38 4K7

R39 4K7

R25

10K

VCC

ADR[1..20]

DATA[0..15]

PPCCLK

#READY

#CE1

#CE3

R/W

#OE

#WE

#RAS0

#RAS1

#CAS0

#CAS1

IR

INT

SPDIF

AUDCLK

SCLK

LRCLK

SDATA0

SDATA1

SDATA2

R26

75R

C86

47pF

OPEN

#SENSE

CLOSE

#PUSH

RTS

CTS

TXD

RXD

SCL

SDA

PIXCLK

RED

GREEN

BLUE

LUMA

CHROMA

CVBS

STI5505 - Core Logic

Loading...

Loading...