Vestel АК18 Service Manual

CONTENTS

Contents ................................................................................................................................................................................... 1

Safety Precautions ................................................................................................................................................................... 2

TV Set switched off .................................................................................................................................................................. 2

Measurements .......................................................................................................................................................................... 2

PERI-TV SOCKET ................................................................................................................................................................... 2

SCART 1 ................................................................................................................................................................................... 2

SCART 2 ................................................................................................................................................................................... 2

INTRODUCTION ...................................................................................................................................................................... 2

SMALL SIGNAL PART WITH TDA884X .................................................................................................................................. 2-3

TUNER...................................................................................................................................................................................... 4

VIDEO SWITCH TEA6415C .................................................................................................................................................... 4

AM DEMODULATOR TDA9830 ............................................................................................................................................... 4-5

DIGITAL TV SOUND PROCESSOR TDA9875 ....................................................................................................................... 5

SOUND OUTPUT STAGE TDA2614/TDA2615/TDA2616Q .................................................................................................... 5

VERTICAL OUTPUT STAGE WITH TDA8351/TDA8356 ........................................................................................................ 6

VIDEO OUTPUT AMPLIFIER TDA6107Q ............................................................................................................................... 6

SINGLE/MULTISTANDARD VIF/SIF-PLL and FM-PLL/AM DEMODULATOR TDA9818 ....................................................... 6

COMB FILTER SAA4961 ......................................................................................................................................................... 6

POWER SUPPLY (SMPS) ....................................................................................................................................................... 6

MICROCONTROLLER SDA525X ............................................................................................................................................ 6

SERIAL ACCESS CMOS 8K (1024*8) EEPROM ST24C08 ................................................................................................... 6

CLASS AB STEREO HEADPHONE DRIVER TDA1308 ......................................................................................................... 7

SAW FILTERS .......................................................................................................................................................................... 7

IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM ....................................................................................................... 7

TDA8840/TDA8842/TDA8844 ........................................................................................................................................... 7-8

UV1315/UV1316/UV1336 .................................................................................................................................................. 9-10

TEA6415C .......................................................................................................................................................................... 10

TDA9830 ............................................................................................................................................................................ 10

TDA2614/TDA2615/TDA2616Q......................................................................................................................................... 11-12

TDA8351/TDA8356 ............................................................................................................................................................ 12

TDA6107Q ......................................................................................................................................................................... 13

SAA4961 ............................................................................................................................................................................ 13-14

MC44604 ............................................................................................................................................................................ 14-15

SDA525X ............................................................................................................................................................................ 16-17

TDA9875 ............................................................................................................................................................................ 17-18

TDA9818 ............................................................................................................................................................................ 18

ST24C08 ............................................................................................................................................................................ 18

TDA1308 ............................................................................................................................................................................ 18

G1965M .............................................................................................................................................................................. 18

TDA9855 ............................................................................................................................................................................ 19

AK19 CHASSIS MANUAL ADJUSTMENT PROCEDURE ...................................................................................................... 20

For Adjust Settings ............................................................................................................................................................. 20

WHITE BALANCE ADJUSTMENT .................................................................................................................................... 20

AGC ADJUSTMENT .......................................................................................................................................................... 20

IF-PLL NEGATIVE ADJUSTMENT .................................................................................................................................... 20

IF-PLL POSITIVE ADJUSTMENT ..................................................................................................................................... 20

LUMINANCE DELAY ADJUSTMENT ................................................................................................................................ 20

VERTICAL ZOOM ADJUSTMENT .................................................................................................................................... 20

VERTICAL SCROLL ADJUSTMENT ................................................................................................................................. 20

4 : 3 HORIZONTAL SHIFT ADJUSTMENT ................................................................................................................... 20

4 : 3 VERTICAL SLOPE ADJUSTMENT ....................................................................................................................... 20

4 : 3 VERTICAL AMPLITUDE ADJUSTMENT .............................................................................................................. 21

4 : 3 S-CORRECTION ADJUSTMENT .......................................................................................................................... 21

4 : 3 VERTICAL SHIFT ADJUSTMENT......................................................................................................................... 21

4 : 3 EW WIDTH ADJUSTMENT ................................................................................................................................... 21

4 : 3 EW PARABOLA WIDTH ADJUSTMENT .............................................................................................................. 21

4 : 3 EW CORNER PARABOLA ADJUSTMENT ........................................................................................................................ 21

4 : 3 EW TRAPEZIUM ADJUSTMENT ........................................................................................................................................ 21

16 : 9 HORIZONTAL SHIFT ADJUSTMENT ................................................................................................................................. 21

16 : 9 VERTICAL SLOPE ADJUSTMENT ..................................................................................................................................... 21

16 : 9 VERTICAL AMPLITUDE ADJUSTMENT ........................................................................................................................... 21

16 : 9 S-CORRECTION ADJUSTMENT ......................................................................................................................................... 21

16 : 9 VERTICAL SHIFT ADJUSTMENT ....................................................................................................................................... 21

16 : 9 EW WIDTH ADJUSTMENT .................................................................................................................................................. 21

16 : 9 EW PARABOLA WIDTH ADJUSTMENT ........................................................................................................................... 21

16 : 9 EW CORNER PARABOLA ADJUSTMENT ....................................................................................................................... 22

16 : 9 EW TRAPEZIUM ADJUSTMENT ....................................................................................................................................... 22

For Option Settings ..................................................................................................................................................................................... 22

OPTION 00 .......................................................................................................................................................................................... 22

OPTION 01 .......................................................................................................................................................................................... 23

OPTION 02 .......................................................................................................................................................................................... 23

OPTION 03 .......................................................................................................................................................................................... 23-24

OPTION 04 .......................................................................................................................................................................................... 24

OPTION 05 .......................................................................................................................................................................................... 24

OPTION 06 .......................................................................................................................................................................................... 24

OPTION 07 .......................................................................................................................................................................................... 24-25

OPTION 08 .......................................................................................................................................................................................... 25

OPTION 09 .......................................................................................................................................................................................... 25

OPTION 10 .......................................................................................................................................................................................... 25

GENERAL BLOCK DIAGRAM OF CHASSIS AK19 .............................................................................................................................. 26

ELECTRONIC COMPONENT PART LIST ............................................................................................................................................... 27-28

1

DO NOT CHANGE ANY MODULE UNLESS THE SET IS SWITCH OFF

The mains supply side of the switch mode power supply transformer is live.

Use an isolating transformer.

The receivers fulfill completely the safety requirements.

Safety precautions:

Servicing of this TV should only be carried out by a qualified person.

- Components marked with the warning symbol on the circuit diagram are critical for safety and must only be replaced

with an identical component.

- Power resistor and fusable resistors must be mounted in an identical manner to the original component.

- When servicing this TV, check that the EHT does not exceed 26kV.

TV Set switched off:

Make short-circuit between HV-CRT clip and CRT ground layer.

Short C804 (150mF) before changing IC802 or other components in primary side of SMPS.

Measurements:

Voltage readings and oscilloscope traces are measured under following conditions.

Antenna signal 60dB from colourbar generator. (100% white, 75% colour saturation)

Brightness, contrast, colour set for a normal picture.

Mains supply, 220VAC, 50Hz.

PERI-TV SOCKET

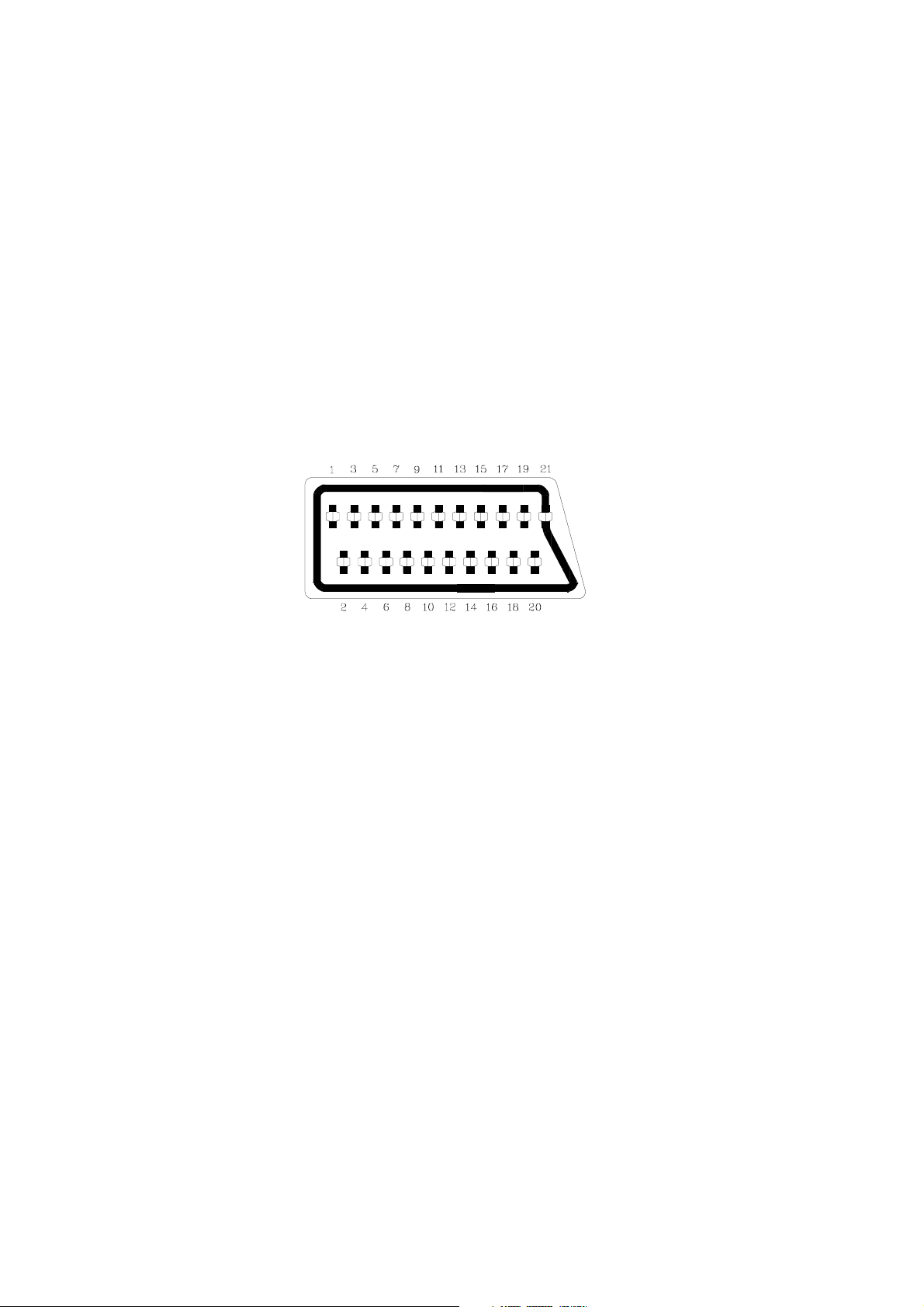

SCART 1 (SC050) SCART 2 (SC051)

1 Audio right output 0.5Vrms / 1K 1 Audio right output 0.5Vrms / 1K

2 Audio right input 0.5Vrms / 10K 2 Audio right input 0.5Vrms / 10K

3 Audio left output 0.5Vrms / 1K 3 Audio left output 0.5Vrms / 1K

4 Ground AF 4 Ground AF

5 Ground Blue 5 Ground Blue

6 Audio left input 0.5Vrms / 10K 6 Audio left input 0.5Vrms / 10K

7 Blue input 0.7Vpp / 75ohm 7 Blue input 0.7Vpp / 75ohm

8 AV switching input 0-12VDC /10K 8 AV switching input 0-12VDC /10K

9 Ground Green 9 Ground Green

10 - 10 11 Green input 0.7Vpp / 75ohm 11 12 - 12 13 Ground Red 13 Ground Red

14 Ground Blanking 14 Ground Blanking

15 Red input 0.7Vpp / 75ohm 15 16 Blanking input 0-0.4VDC, 1-3VDC / 75ohm 16 17 Ground CVS output 17 Ground CVS output

18 Ground CVS input 18 Ground CVS input

19 CVS output 1Vpp / 75ohm 19 CVS output 1Vpp / 75ohm

20 CVS input 1Vpp / 75ohm 20 CVS input 1Vpp / 75ohm

21 Ground 21 Ground

INTRODUCTION

Ak18 is a 100Hz double scan color television capable of driving 28 4:3/16:9 and 33 4:3 picture tubes.

The chassis is capable of operation both in PAL, SECAM, NTSC playback color standards and multiple transmission

standards as B/G, D/K, I/I+, and L/L´. Sound system output is supplying 12W (10%Thd) for left, right and center outputs

of 8ohm speakers and 7W for 2 surround outputs of two 8ohm speakers. TV has Megatext or Tvtext teletext system.

The chassis is equipped with 1 full EuroScart, 2 other Scarts for AV input/output, front-AV/back-AV, headphone output,

SVHS input, VGA input, two external speaker output, one center speaker and two surround speaker outputs.

2

IF PART

TDA4470/TDA4472

The TDA44XX is an integrated bipolar circuit for multistandard video/sound IF (VIF/SIF) signal processing in TV/VCR

and multimedia applications. The circuit processes all TV video IF signals with negative modulation (e.g., B/Gstandard),

positive modulation (e.g., L standard) and the AM, FM/NICAM sound IF signals. Active carrier generation by FPLL

(frequency phase-locked loop) is the principle for true synchronous demodulation. VCO circuit is operating on picture

carrier frequency, The VCO frequency is switchable for L´-mode. AFC without external reference circuit is alignmentfree

and polarity of The AFC curve is switchable.

VIF-AGC for negative modulated signals operates on peak sync detection principle and for positive modulation on peak

white/black level detection principle. Tuner AGC is adjustable with determining take over point. It has alignment-free

quasi parallel sound (QPS) mixer for FM/NICAM sound IF signals.

Intercarrier output sound is gain controlled (necessary for digital sound processing). AM- demodulator is completely

alignment-free with gain controlled AF output. Operation of the AM demodulator and QPS mixer (for NICAM-L stereo

sound is parallel.TDA4472 is used for negative modulation and TDA4470 is used for both negative and positive

modulation.

100Hz FEATURE BOX

SDA9205/SDA9257/SDA9254/SDA9220/SDA9280

The SDA9205 is a single IC containing three separate 8-bit analog to digital converters for video (YUV) applications.

It provides 30-Mhz sampling rates at 8 bits. Different digital output multiplex formats are selectable on chip via several

control inputs. The SDA9257 is the clock sync generator. It is I2C controlled. It has PLL locked-in behaviour is locked to

TV mode. It clamps CVBS inputs and provides all horizontal and vertical sync signals and clocks for PAMUX, analog

circuit decoder, the A/D converters, PSDN and Feature-box. SDA9220 is a memory sync controller which is responsible

for driving the picture memory devices and generating sync signals. Together with the other devices of feature-box it

enhances picture quality and offers special operating modes. It is set via I2C bus. The memory controller produces

driving signals for the memory devices and the clock generator consists essentially of a PLL which generates the

internal and exported system clocks from input clock LL3 or LL1.5 and synchronises them with the horizontal blanking

signal.

SDA9280 is the display processor is an integrated triple 9-bit D/A converter which performs digital enhancements and

manipulations of digital video component signals. It has 8-bit amplitude resolution for each input component with input

sample frequency up to 30Mhz. DCTI (Digital color transient improvement), luminance peaking, 16:9 compatibility,

delay for luminance and chrominance signals, zoom facility are tasks which are performed by this IC. The SDA9254 is

a dynamic sequential access memory for 100Hz TV applications. It is a triple port dynamic sequential-access memory

for high-data-rate video applications It is organised for the storage of planes of at TV field (NTSC, PAL, SECAM, MAC)

in standard quality.

COMB FILTER

SAA4961

The SAA4961 is a single chip PAL/NTSC comb filter with internal delay lines, filters, clock control, synchronisation and

signal switches. The comb filter function is realised in a switched-capacitor technic, so it has time discrete but

amplitude continuos processing. The Y/CVBS input is first clamped and then fed to the delay-line and comb filter

section via low pass pre-filter. This signal is also fed to the sync separator, where horizontal and vertical reference

pulses are created. Bypass mode for secam mode can be forced by a control pin (BYP).

FSC is the sub-carrier input which is connected to the color decoder.

POWER SUPPLY (SMPS)

TDA4605

The Dc voltages required at various parts of the chassis are provided by an SMPS transformer controlled by the

IC TDA4605 which is designed for driving, controlling, and protecting switching transistor of SMPS. Two optocouplers

are used to control the regulation of line voltage and stand-by power consumption. Line voltage value is supplied by an

oprtocoupler (CQY80NG) to the control input of SMPS IC on the primary side and regulation is controlled by variable

resistor on secondary side of the stage. An ON/OFF signal comes from microcontroller and drives an optocoupler

(MOC3023) to connect and disconnect the 220V AC line. A second transformer which is driven directly from mains

AC input generates the necessary 5V DC stand-by voltage. Transformer produces 148/150V DC for FBT input, +/-16V

DC for audio output 8.5V, 16V, 22V and 33V for the other parts of the chassis. The serial circuit and primary winding of

the flyback transformer are connected in series to the input voltage. During the switch on period of the transistor,

energy is stored in the transformer. During the switch off period energy is fed to the load via secondary winding.

By varying switch-on time of the power transistor, It controls each portion of energy transferred to the second side such

that the output voltage remains nearly independent of load variations. The required control information is taken from the

input voltage during the switch on period and from a regulation winding during the switch off period. A new cycle will

start if the transformer has transferred the stored energy completely into the load. The power supply is operating in the

burst mode at typical 20 to 40Khz.

3

TUNER

UV1316

The UV1316 tuner belongs to the UV1300 family of tuners, which are designed to meet a wide range of applications.

It is a combined VHF, UHF tuner suitable for CCIR systems B/G, H, L, L´, I and I´, D/K. The low IF output impedance

has been designed for direct drive of a wide variety of SAW filters with sufficient suppression of triple transient.

The tuning is available through built-in digitally controlled I2C bus (PLL).

Channel coverage of UV1316:

BAND

Low Band E2 to C 48.25 to 82.25 (1) S01 to S08 69.25 to 154.25

Mid Band E5 to E12 175.25 to 224.25 S09 to S38 161.25 to 439.25

High Band E21 to E69 471.25 to 855.25 (2) S39 to S41 447.25 to 463.25

(1). Enough margin is available to tune down to 45.25 MHz.

(2). Enough margin is available to tune up to 863.25 MHz.

OFF-AIR CHANNELS CABLE CHANNELS

CHANNELS FREQUENCY CHANNELS FREQUENCY

RANGE (MHz) RANGE (MHz)

Noise Typical Max. Gain Min. Typical Max.

Low band : 5dB 9dB All channels : 38dB 44dB 52dB

Mid band : 5dB 9dB Gain Taper (of-air channels) : - - 8dB

High band : 6dB 9dB

Channel Coverage UV1336:

BAND CHANNELS FREQUENCY

RANGE (MHz)

Low Band 2 to D 55.25 to 139.25

Mid Band E to PP 145.25 to 391.25

High Band QQ to 69 397.25 to 801.25

Noise is typically 6dB for all channels. Gain is minimum 38dB and maximum 50dB for all channels.

Channel Coverage of UV1315:

BAND

Low Band E2 to C 48.25 to 82.25 (1) S01 to S10 69.25 to 168.25

Mid Band E5 to E12 175.25 to 224.25 S11 to S39 231.25 to 447.25

High Band E21 to E69 471.25 to 855.25 (2) S40 to S41 455.25 to 463.25

(1). Enough margin is available to tune down to 45.25 MHz.

(2). Enough margin is available to tune up to 863.25 MHz.

Noise Typ. Max. Gain Min. Typ. Max.

Low band : 6dB 9dB All Channels 38dB 44dB 50dB

Mid band : 6dB 10dB Gain Taper - - 8dB

High band : 6dB 11dB (off-air channels)

OFF-AIR CHANNELS CABLE CHANNELS

CHANNELS FREQUENCY CHANNELS FREQUENCY

RANGE (MHz) RANGE (MHz)

DIGITAL DEFLACTION PART

SDA9362

The SDA9362is a highly integrated deflection controller for TV receivers with doubled line and doubled field frequencies.

It controls among others an horizontal driver circuit for a flyback line output stage, a DC coupled vertical sawtooth output

stage and an East-West raster correction circuit. All adjustable outputs are I2C bus controlled. Inputs are doubled

HSYNC and doubled VSYNC signals coming from sync switching IC which takes its inputs from TDA9143 IC and VGA

sync input. It has also horizontal and vertical EHT-compensation input against beam current run away. The protection

circuit watches an EHT reference and the sawtooth of the vertical output stage. H-output stage is switched off if the EHT

succeeds a defined threshold or if the V-deflection fails. H- and V-blanking time is adjusted via I2C bus.

4

DIGITAL TV SOUND PROCESSING

MSP3410D

The MSP3410D is a I2C controlled single-chip multistandard sound processors for applications in analog and digital TV

sets. The full TV sound processing, starting with analog sound IF signal-in, down to processed analog AF-out is

performed in a single-chip covering all European TV-standards. It is designed to simultaneously perform digital

demodulation and decoding of NICAM-coded TV stereo sound, as well as demodulation of FM or AM-mono TV sound.

Alternatively, two carrier FM systems according to the German or Korean terrestrial specs of the satellite specs can be

processed within the IC.

It has two selectable analog sound IF inputs: TV and SAT-IF sources. There is AGC for analog inputs:0.14-3Vpp.

All demodulation and filtering is performed on chip and is individually programmable. All digital NICAM standards (B/G,

I and L) are realised. FM-demodulation of all satellite and terrestrial standards are possible. Only one crystal clock

(18.432Mhz) is necessary. External capacitors at each crystal pin to ground are required. They are necessary for tuning

the open-loop frequency of the internal PLL and for stabilising the frequency in closed-loop operation. The higher the

capacitors, the lower the clock frequency results. The nominal free running frequency should match the center of the

tolerance range between 18.433 and 18.431Mhz as closely as possible. By means of standardised I2S interface,

additional feature processors (TMS37600, Dolby Prologic digital audio signal processor for this chassis) can be

connected to the IC. I2S bus interface consists of five pins: I2S_DA_IN1 and I2S_DA_IN2; For input, Four channels

(two channels per line) per sampling cycle 32Khz. I2DA_OUT; For output, two channels per sampling rate of 32Khz.

I2S_CL; For timing of the transmission of I2S serial data, 1.024Mhz. I2S_WS; The word strobe line defining the left and

right sample.

DOLBY PRO LOGIC DASP (Digital audio signal processing IC)

TMS37600

The TMS37600 IC is a digital audio signal processor used when Dolby Pro Logic option is available.

It gets digitised sound from the audio processor IC MSP3410D for both 4 channels via I2S_DA_OUT pin and

processes these information to give two outputs for MSP3410D: I2S_DA_IN1 (for right and left channels) and

I2S_DA_IN2 (for center and surround channels). Synchronisation is obtained by 2 I2S busses: I2S_CL; For timing of

the transmission of I2S serial data, 1.024Mhz and I2S_WS; The word strobe line defining the left and right sample at

32Khz. The IC is also I2C bus controlled to select the sound feature (stereo, ^D-phonic and Dolby Pro Logic).

It operates with a external DRAM in order to download some data which processes sound for sound features and

sound modes. It has an external clock generator cycling at 27.576Mhz.

AUDIO AND VIDEO INPUT AND OUTPUT SOURCE SWITCHING

TEA6415/TEA6420

Video switching is performed by TEA6415 and audio switching is performed by TEA6420. Inputs for audio switch are:

Three Scart left and right audio signals, front-AV audio for left and right channels. Outputs for audio switch are:

Three Scart left and right audio signals, one left and right audio signal output for Scart_1 Left and Right input of

MSP3410D. The audio switch IC is I2C bus controlled and gain of each input-output matrices are 0dB. Inputs for video

switch are: front-end CVBS, three Scart video signals, and front-AV video signal and Y input from SVHS source.

Outputs of video switch are three Scart video signals, one video output for PIP-video input and one output for switched

Y or CVBS input of the comb filter. The video switch IC is also I2C bus controlled and gain of each input-output

matrices are 0dB.

HEADPHONE OUTPUT

TDA1308

The TDA1308 is an integrated class AB stereo headphone driver. It gets its input from Scart2 left and right audio

outputs of MSP3410D and has gain adjusting feedback from output to input signal.

VIDEO OUTPUT AMPLIFIER STAGE

TDA611Q

The TDA6111Q is a video output amplifier with 16Mhz bandwidth. It has a high slew rate. Automatic black-current

stabilisation is possible by black-current measurement output. It has two cathode outputs: one for DC currents and one

for transient currents. A feedback output is separated from the cathode outputs. An internal protection exists against

positive appearing cathode-ray-tube flashover discharges with ESD protection.

5

VERTICAL OUTPUT STAGE

TDA8351

The TDA8351 vertical deflection circuit can be used in 1100 deflection systems with field frequency from 50 up to

120Hz. With its bridge configuration the deflection output can be DC coupled with few external components.

Only a single supply voltage for the scan and a second supply for the flyback are needed. The drive voltage is amplified

by an amplifier and fed to two amplifiers, one is inverting and the other is a non inverting amplifier.

The outputs are connected to the series connection of the vertical deflection coil and feedback resistor Rsense.

The voltage across Rsense is fed via pin9 to correction amplifier, to obtain a deflection current which is proportional to

the drive voltage. The supply voltage for the TDA8351 is 15V DC at pin 3. The supply voltage generator has a separate

supply voltage of 45V DC at pin 6.

SAW FILTERS

K9453 : Two channel switchable sound IF saw filter of BG, DK, I, L systems for input channel 2 and of L´ system for

input channel 1.

K3953 : Two channel switchable video IF saw filter of BG, DK, I, L systems for input channel 2 and of L´system for

input channel 1.

J3950 : Video IF saw filter for I system

YUV VIDEO AND SYNC PROCESSOR

TDA9143

The TDA9143 is an I2c bus controlled, alignment-free PAL/NTSC/SECAM decoder and sync processor.

It has been designed for use with baseband chrominance delay lines, and has a combined subcarrier frequency/comb

filter enable signal for communication with a PAL/NTSC comb filter. The IC can process both CVBS input signals and

Y/C input signals. The input signal is available on an output pin, in the event of a Y/C signal, it is added into a CVBS

signal. The sync processor provides a two-level sandcastel, a horizontal pulse (CLP or HA pulse, bus selectable) and a

vertical (VA) pulse. When HA pulse is selected a line locked clock (LLC) signal is available at the output port pin.

A fast switch can select either the internal Y signal with the UV input signals, or YUV signals made of the RGB input

signals. The RGB input signals can be clamped with either the internal or an external clamping signal. IC has inputs Y

C or CVBS from comb filter board. RGB signals coming from Scart1 are also injected into the IC. UV signal input and

output are also ready for chromaninance delay line. One CVBS output is for teletext operation and it enters

The Megatext IC or Tvtext controller. Outcoming YUV signals enter the feature box for double scan 100Hz digital video

processing. Horizontal and vertical sync pulses are added and they enter the feature box for production of double scan

vertical and horizontal sync pulses and synchronisation signal LL1_5X.

RGB OUTPUT AND BLACK-CURRENT STABILISATION

TDA4780

The TDA4780 is I2C bus controlled post video signal processor with a baseband signal interface and two sets of

analog RGB inputs. Doubled frequency color difference signals YUV coming from feature box are matrixed with the

luminance signal to obtain the RGB signals driving the RGB output stage (TDA6111Q). Three analog input sets are

available, one luminance/color-difference input signals and two sets of RGB and fast-blanking signals. One input set is

used for RGB+fb signal coming from Megatext IC (for OSD and teletext) and the other set is used for RGB+fb signals

coming from full Scart1. Different RGB matrices can be selected via I2Cbus, either PAL/SECAM matrix or the NTSC

matrix. Saturation, contrast, and brightness controls are individually adjusted via I2C bus (for the luminance/color

difference and RGB inputs). All adjustments can be synchronised with the vertical blanking interval. It expands lower

signal levels, while higher signal levels are compressed to enlarge the contrast ratio and thus expands the portrayal in

the direction of black. Adaptive black level control acts on the luminance signal, the darkest level of the active picture is

detected and controlled to the internal reference black level. The automatic cut-off control measures the cut-off currents

of the CRT using artificial black level signals provided on the outputs during three successive lines, the provided

artificial black level equals the clamping level of the RGB or Y input signals. A luminance signal for scan velocity

modulation of a line deflection can be provided if required.

6

AUDIO OUTPUT

TDA7264

The TDA7264 is a 25W+25W stereo sound amplifier with mute/stand-by facility. STPA control signal coming from

microcontroller (when it is at high level) activates the mute function. IC is muted when mute port is at low level.

Two stereo audio signals coming from audio module is injected to the inputs of the IC and a power of 12Wrms (10%) is

obtained. An external pop-noise circuitry pulls AF inputs of the IC in order to eliminate pop noise when TV is turned on or off

via mains supply connection.

SERIAL ACCESS 32K EEPROM

24LC32A

The IC s 32Kbit electrically erasable programmable memory. The memory is compatible with the I2C standard, two

wire serial interface which uses a bi-directional data bus and serial clock.

MEGATEXT TELETEXT AND OSD GENERATOR

SDA5273

The SDA5273 is a single-chip IC for teletext, VPS, PDC, telecaption and OSD generator. Its input is analog CVBS with

on-chip clamping circuit. It has analog RGB+fb output which enters into the RGB processor (TDA4780). It is I2C bus

controlled or 3-wire USART-interface is selected. IC has two independent clock systems for acquisition and display.

Its main functions are the decoding and display of teletext information coming from analog sources and the generation

of OSD which can provide the TV with status information or menu (user interface) assistance. The Megatext is a real

single chip solution which combines data slicer, teletext processor, VPS-decoder, page/pixel memory and display

controller. The memory is extended by external DRAM to increase the teletext capacity up to 512 pages. The Megatext

IC delivers analog RGB-output signals with a maximum amplitude of 2V peal to peak. The contrast/brightness of the

RGB output signal can be controlled by software in linear steps without decreasing the amplitude resolution.

IC is controlled by an external controller (SDA30264) via M3L-Bus (USART, 2+1 wires). M3L-Bus increases the

maximum data rate up to 1Mbits/sec and is thus 10 times faster than the I2C bus in standard mode.

MICROTEXT CONTROLLER (with TVTEXT option)

SDA5253

The device is TVTEXT tuning and control system and designed for a low cost TV-SET. The system offers an on

screen display /OSD) and IR remote control of all functions. Display of program number, channel number, TV standard,

analog values, sleep timer, parental control, mute and user interface are done by OSD. There is dual color single LED

for IR active, and stand-by indication. There is 3 lines for external selection, 2 lines for TV standard selection, one

stand-by line, 2 lines for PIP mode, Vga line and sound output mute line. System configuration is also controlled by the

IC with service mode facility.

MICROTEXT CONTROLLER (with Megatext option)

SDA30C264

The SDA30C264 is the microcontroller used with Megatext option. Its architecture and instruction set are based upon

that of the 8051 microcomputer. Like the 8051 it has many features which increase programming ease; extended

internal data memory-space , variable manipulation in internal data memory, free stack location in data RAM, 4 register

banks, special function registers, memory mapped I/O, individually addressable bits and a Boolean processor which

gives the programmer the ability to improve the power of the software development. The IC communicates with the

EPROM and produce the following input or output control signals; Agc_con, Pal_secam,Pip_mod_sw,On_off (stand-by)

Pip_sel, Sdat and SclT (M3L bus) for Megatext IC, Scx_in_av (pin 8 information from 3 Scarts), AFC, Vga_fb, STPA

(to mute audio output IC), IICENx.

PORT EXPANDER

PCF8574

The PCF8574 is an I2C bus controlled IC for standard selection control lines for the IF IC (TDA447X).

The IC has inputs for standard and L´ control from the microcontroller and outputs for IF IC.

7

VGA SYNC POLARITY CONVERTER

74HC86

The 74HC86 is an exor logic IC. Its inputs are Vga horizontal and vertical sync signals of positive or negative polarity.

Whatever their polarity, they are converted to higher polarity and IC has always positive polarity Vga horizontal and

vertical sync signals

SOURCE SWITCH BETWEEN TV AND VGA SYNC SIGNALS

HEF4053B

The HEF4053B is a switch IC used to select sync signals entering feature box to provide correct sync signal between

VGA and normal TV sync signals. Selection of sync couple is controlled by VGA_fb control signal coming from

microcontroller.

CHROMINANCE DELAY LINE

TDA4665

The TDA4665 is a chrominance delay line. Its inputs are U-V signals and sandcastel signal coming from video

processor (TDA9143). Output is the 1H delayed U-V signals entering into video processor.

DRAM

HYB514400BJ

The HYB514400BJ is the new generation dynamic RAM organised as 1M by 4-bit. it utilises CMOS silicon gate

process as well as advances circuit techniques to provide wide operation margins, both internally and for the system

user. This DRAM is used with Megatext IC to store teletext pages and with Dolby IC to download related coefficients of

the ROM for different sound features.

EPROM

ST27C2001

The ST27C2001 is 2097 152-bit, ultra-violet erasable, electrically programmable read-only memory. This device is

fabricated using power-saving CMOS technology for high speed and simple interface with MOS and bipolar circuits.

All inputs (including program data inputs) can be driven by series 74TTL circuits without the use of external pull-up

resistors. Each output can drive one series 74 TTL circuit without external resistors. Software for user interface and

control of hardware circuitry are stored in this eprom IC.

IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM

n TDA4470/TDA4472

n SDA9205/SDA9257/SDA9254/SDA9220/SDA9280

n SAA4961

n TDA4605

n TUNER (UV1315,UV1316,UV1336)

n SDA9362

n MSP3410D

n TMS37600

n TEA6415 / TEA6420

n TDA1308

n TDA611Q

n TDA8351

n TDA9143

n TDA4780

n TDA7264

n SDA5273

n SDA5253

n SDA30C264

n TDA4665

n HYB514400BJ

n ST27C2001

8

TDA4470 / TDA4472 :

The TDA4470 is an integrated bipolar circuit for multistandard video / sound IF (VIF / SIF) signal prosessing in TV / VCR

and Multimedia applications. The circuit processes all TV video IF signals with negative modulation (e.g. L standard) and

the AM, FM / NICAM sound IF signals.

Features:

n 5V supply voltage; low power consumption

n Active carrier generation by FPLL principle (frequency-phase-locked-loop) for true synchronous demodulation

n Very linear video demodulation, good pulse response and excellent intermodulation figures

n VCO circuit is operating on picture carrier frequency, the VCO frequency is switchable for the Lmode

n Alignment-free AFC without external reference circuit, polarity of the AFC curve is switchable

n VIF-AGC for negative modulated signals (peak sync detection) and for positive modulation

(peak white/black level detector)

n TunerAGC with adjustable take over point

n Alignment-free quasi parallel sound (QPS) mixer for FM/NICAM sound IF sihnals

n Intercarrier output signal is gain controlled (necessary for digital sound processing)

n Complete alignament-free AM demodulator with gain controlled AF output

n Separate SIF-AGC with average detection

n Two independent SIF inputs

n Parallel operation of the AM demodulator and QPS mixer (for NICAM-L stereo sound)

n Package and relevant pinning is compatible with the single standard version TDA 4472; simplifies the desihn of an

universal IF module

PINNING PIN VALUE

1. Input sensitivity, RMS value : 80mVrms

2. Input sensitivity, RMS value : 80mVrms

3. SIF Input selector switch : 2.0 V

4. Ground

5. IF gain control range : 65dB

6. Input sensitivity, RMS value : 80mVrms

7. Input sensitivity, RMS value : 80mVrms

8. IF gain control range : 65dB

9. Ground

10. Aveilable tuner-AGC current : 2mA

11. Aveilable tuner-AGC current : Min : 0.3V Max : 13.5V

12. Video output : Min : 1.8V Max : 2.2V

13. Standard switch : Min : 0V Max : 0.8V

14. Lswitch : Min : 0V Max : 3.0V

15. IF gain control range : 65dB

16. Ground

17. Internal reference voltage :

18. FPLL and VCO : Min : 1mA Max : 4mA

19. AFC switch : Min : 0V Max : 0.8V

20. FPLL and VCO : Min : 1mA Max : 4mA

21. FPLL and VCO : Min : 1mA Max : 4mA

22. AFC output : 0.7 mA/kHz

23. DC supplay : Min : 4.5V Max : 9.0V

24. DC output voltage : 2V

25. AF output-AM : 2.2V

26. FPLL and VCO : Min : 1mA Max : 4mA

27. Input sensitivity, RMS value : 80mVrms

28. Input sensitivity, RMS value : 80mVrms

9

Loading...

Loading...