UEi RACKtangle DNR-12-1G-02, HalfRACK DNR-6-1G, RACKtangle DNR-12-1G, RACKtangle DNR-12-1G-00, RACKtangle DNR-12-1G-01 User Manual

...Page 1

DNR-12-1G Series RACKtangle

and

DNR-6-1G Series HalfRACK

Data Acquisition Systems

—

User Manual

October 2018

PN Man-DNR-X-1G

© Copyright 1998-2018 United Electronic Industries, Inc. All rights reserved.

Page 2

Information furnished in this manual is believed to be accurate and reliable. However , no responsibility

is assumed for its use, or for any infringement of patents or other rights of third parties that may result

from its use.

All product names listed are trademarks or trade names of their respective companies.

See the UEI website for complete terms and conditions of sale:

http://www.ueidaq.com/cms/terms-and-conditions/

Contacting United Electronic Industries

Mailing Address:

27 Renmar Avenue

Walpole, MA 02081

U.S.A.

For a list of our distributors and partners in the US and around the world, please contact a memb er of our

support team:

Support:

Telephone: (508) 921-4600

Fax: (508) 668-2350

Also see the FAQs and online “Live Help” feature on our web site.

Internet Support:

Support: support@ueidaq.com

Website: www.ueidaq.com

FTP site: ftp://ftp.ueidaq.com

Product Disclaimer:

WARNING!

DO NOT USE PRODUCTS SOLD BY UNITED ELECTRONIC INDUSTRIES, INC. AS CRITICAL

COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

Products sold by United Electronic Industries, Inc. are not authorized for use as critical components in

life support devices or systems. A critical component is any component of a life support device or

system whose failure to perform can be reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness. Any attempt to purchase any United Electronic

Industries, Inc. product for that purpose is null and void and United Electronic Industries Inc. accepts

no liability whatsoever in contract, tort, or otherwise whether or not resulting from our or our

employees' negligence or failure to detect an improper purchase.

Specifications in this document are subject to change without notice. Check with UEI for

current status.

Page 3

DNR-X-1G Series RACKtangle and HalfRACK Systems i

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Table of Contents

Table of Contents

Chapter 1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Organization of This Manual. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Product Versions Described in This Manual. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Chapter 2 The DNR-12-1G Series RACKtangle System . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.1 PowerDNR DNR-12-1G System Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2 DNR-12-1G Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.3 DNR-12-1G Key Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.4 DNR-12-1G RACKtangle Enclosure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.4.1 DNR-12-1G Enclosure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.4.2 DNR-12-1G Enclosure Common Components . . . . . . . . . . . . . . . . . . . . . . . . 8

2.4.3 DNR-12-1G Cooling Air Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.5 DNR-12 Power, NIC/CPU, and I/O Boards LEDs & Controls . . . . . . . . . . . . . . . . . . 14

2.6 DNR-POWER-DC Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.7 DNR-CPU/NIC Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.7.1 Device Architecture of DNR Core Module . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.8 DNR-Buffer Module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.9 DNR I/O Boards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.10 DNR-12-1G DC Power Thresholds. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Chapter 3 The DNR-6-1G Series HalfRACK System . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.1 PowerDNR DNR-6-1G System Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.2 DNR-6-1G Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.3 DNR-6-1G Key Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.4 DNR-6-1G HalfRACK Enclosure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.4.1 DNR-6-1G Enclosure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.4.2 DNR-6-1G Enclosure Common Components . . . . . . . . . . . . . . . . . . . . . . . . 30

3.4.3 DNR-6-1G Cooling Air Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.5 DNR-6 Power, NIC/CPU, and I/O Boards LEDs & Controls . . . . . . . . . . . . . . . . . . . 33

3.6 DNR-6-1G DNR-POWER-DC Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.7 DNR-6-1G DNR-CPU/NIC Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.8 DNR-6-1G DNR-IO-Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.9 DNR-6-1G DC Power Thresholds. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Chapter 4 Installation and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4.1 Initial Installation Guide. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4.1.1 Inspect Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.1.2 Install Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2 Initial Boot-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

4.3 IP Address Overview & Update Procedures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Page 4

DNR-X-1G Series RACKtangle and HalfRACK Systems ii

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Table of Contents

4.3.1 When Should You Change the IP Address? . . . . . . . . . . . . . . . . . . . . . . . . . 41

4.3.2 How to Change the Primary IP Address (NIC1). . . . . . . . . . . . . . . . . . . . . . . 42

4.3.3 How to Change the Secondary (Diagnostic) IP Address (NIC2). . . . . . . . . . 43

4.4 Network Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4.4.1 Example of Configuring Network Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.5 Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

4.6 Updating Firmware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.6.1 Determining Currently Installed Firmware Version . . . . . . . . . . . . . . . . . . . . 51

4.6.2 Updating Firmware via PowerDNA Explorer . . . . . . . . . . . . . . . . . . . . . . . . . 52

4.6.3 Updating Firmware via Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.7 Mounting and Field Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4.7.1 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

4.7.2 Pinout Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.7.3 Network Wiring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.8 Wiring I/O Boards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.9 Repairing (and Upgrading) a DNR System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.10 Configuring a NIC Port for Diagnostic Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.11 Disabling Writes to Flash/EEPROM (NVRAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.11.1 Disabling NVRAM Writes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.11.2 Re-enabling NVRAM Writes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Chapter 5 PowerDNA Explorer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5.1 Getting Started with PowerDNA Explorer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5.1.1 Connecting PowerDNA Explorer to Your System . . . . . . . . . . . . . . . . . . . . . 70

5.2 Overview of the Main Window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.2.1 Menu Bar . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.2.2 Toolbar. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.2.3 Device Tree . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.2.4 Settings Panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.3 Exploring I/O Boards with PowerDNA Explorer . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3.1 Digital Input/Output Board Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3.2 Analog Output Board Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

5.3.3 Analog Input Board Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.3.4 Counter/Timer Board Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Chapter 6 Programming CPU Board-specific Functions . . . . . . . . . . . . . . . . . . . . . . . . 91

6.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

6.2 Memory Map Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

6.3 Startup Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

6.4 Setting and Reading CPU Core Parameters via Serial Port. . . . . . . . . . . . . . . . . . . 93

6.4.1 Help Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

6.4.2 Show System Parameters Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

6.4.3 Set and Store Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.4.4 Reset DNR-X-1G Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.4.5 Password Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

6.4.6 Display Table of Installed Boards & Logic Version Command. . . . . . . . . . . 100

6.4.7 Display Power Diagnostics Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Page 5

DNR-X-1G Series RACKtangle and HalfRACK Systems iii

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Table of Contents

6.4.8 Memory Test/Memory Clear Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

6.4.9 Monitor CPU and Pbuf Usage Command . . . . . . . . . . . . . . . . . . . . . . . . . . 103

6.4.10 Clock and Watchdog Access Command . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Appendix A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Network Interface Card Configuration

Appendix B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Field Replacement of Fuses on DNA and DNR Boards

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Page 6

DNR-X-1G Series RACKtangle and HalfRACK Systems iv

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

List of Figures

List of Figures

Chapter 1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Chapter 2 The DNR-12-1G Series RACKtangle System . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2-1 Typical DNR-12-1G RACKtangle System......................................................................4

2-2 DNR-12-1G Technical Specifications....... .....................................................................6

2-3 DNR-12-1G PowerDNR Product Features....................................................................7

2-4 Typical PowerDNR DNR-12 Enclosure (Exploded View)..............................................8

2-5 Typical PowerDNR DNR-12 Board Placement..............................................................9

2-6 Optional DNR-IO-Filler Panel for Empty Slots.............................................................11

2-7 DNR-BRACKET Reversible Mounting Bracket............................................................11

2-8 DNR Board Ejection/Insertion Lever Operation...........................................................12

2-9 DNR-12 Air Flow..........................................................................................................13

2-10 DNR-12-1G System Front Panel Arrangement............ ... ... ... ... .... ... ... ... .... ... ... ............14

2-11 DC Power Module LEDs..............................................................................................15

2-12 DNR-CPU-1000/-XX Module LEDs.............................................................................15

2-13 Typical I/O Module LEDs.............................................................................................16

2-14 DNR-POWER-DC Module...........................................................................................18

2-15 Functional Block Diagram of DNR-POWER-DC Module.............................................19

2-16 Functional Block Diagram of DNR-12 Enclosure.........................................................20

2-17 DNR-X-1G Series Core Module (CPU/NIC) ................................................................21

2-18 FreeScale PowerPC CPU/NIC Controller Architecture................................................22

Chapter 3 The DNR-6-1G Series HalfRACK System . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3-1 Typical DNR-6-1G HalfRACK System.........................................................................25

3-2 DNR-6-1G Technical Specifications............................................................................27

3-3 DNR-6-1G HalfRACK Product Features......................................................................28

3-4 Typical HalfRACK DNR-6 Enclosure (Exploded View)....... ... ... ...................................29

3-5 Typical PowerDNR DNR-6 Board Placement..............................................................30

3-6 DNR-6 Air Flow............................................................................................................32

3-7 DNR-6-1G System Front Panel Arrangement.............................................................33

Chapter 4 Installation and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4-1 Typical MTTTY Screen after DNR-X-1G Boot-up........................................................40

4-2 System Configuration Using show Command.............................................................41

4-3 Using PowerDNA Explorer to Change IP Address......................................................42

4-4 Single DNR-X-1G Direct-Connected to Host without LAN Switch...............................44

4-5 Single Network for Operation and Diagnostics Using DNR Racks and LAN Switch ...44

4-6 Separate Networks for Operation and Diagnostics: Two Racks & Two Switches.......45

4-7 Typical Configuration for a Single DNR-X-1G with a LAN Switch ... ... ... ......................48

4-8 Displaying the Version of Your Firmware....................................................................51

4-9 Update Firmware Menu Item.......................................................................................52

4-10 Password Dialog Box ..................................................................................................53

4-11 Firmware Update Progress Dialog Box.......................................................................53

4-12 Firmware Update via Serial Port..................................................................................55

4-13 Physical Dimensions of DNR-12 Enclosure.................................................................56

4-14 Physical Dimensions of DNR-6 Enclosure...................................................................57

4-15 DNR-X-1G Pinout Diagrams........................................................................................58

4-16 System Configuration with LAN Switch.......................................................................58

4-17 DNR-X-1G NIC/CPU Core Module and Carrier...........................................................66

4-18 NVRAM Protection Jumper .........................................................................................67

Page 7

DNR-X-1G Series RACKtangle and HalfRACK Systems v

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

List of Figures

Chapter 5 PowerDNA Explorer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5-1 PowerDNA Explorer ....................................................................................................69

5-2 Address Ranges to be Scanned..................................................................................70

5-3 Typical Screen for Analog Input Board........................................................................71

5-4 PowerDNA Explorer Main Window..............................................................................72

5-5 PowerDNA Explorer Timeout Preferences..................................................................72

5-6 Address Ranges Dialog Box........................................................................................73

5-7 Edit Address Ranges Dialog Box ................................................................................73

5-8 After a Network >>Scan Network................................................................................74

5-9 Password Dialog Box for “Store Config” and “Store All Configs”.................................75

5-10 Password Dialog Box for “Update Firmware . . .”........................................................75

5-11 Example of a Hardware Report...................................................................................76

5-12 Example of a Wiring Diagram Display.........................................................................77

5-13 PowerDNA Explorer Toolbar Buttons (Config Level)...................................................78

5-14 PowerDNA Explorer Toolbar Buttons (Board Level)....................................................78

5-15 Example of the Device Tree........................................................................................79

5-16 Example of IOM Settings Panel for HalfRACK DNR-6-1G..........................................80

5-17 Example of I/O Device Settings ..................................................................................81

5-18 Screen from Network >> Start Reading Input Data.....................................................82

5-19 Example DIO-403 Inputs.............................................................................................83

5-20 Example DIO-403 Outputs ..........................................................................................84

5-21 Example of DIO-403 Configuration..............................................................................85

5-22 Example AO-308 Board...............................................................................................86

5-23 Example AI-207 Board ................................................................................................87

5-24 Example CT-601 Module.............................................................................................88

5-25 Example Quadrature Controls.....................................................................................88

5-26 Example Bin Counter Controls....................................................................................89

5-27 Example Pulse Width Modulation (PWM) Controls.....................................................89

5-28 Example Pulse Period Controls...................................................................................89

5-29 Example Frequency Controls......................................................................................89

5-30 Example of Started Counter........................................................................................90

Chapter 6 Programming CPU Board-specific Functions . . . . . . . . . . . . . . . . . . . . . . . . 91

6-1 TCP/IP Properties........................................................................................................98

B-1 Location of Fuse for Base Boards Equipped with a Fuse..........................................109

B-2 Location of Fuses for DNR-POWER-DC Board ................. ... ... .... ... ... ... .... ................110

B-3 Location of Fuses for DNR-POWER-1GB Board.......................................................110

Page 8

DNR-X-1G Series RACKtangle and HalfRACK Systems vi

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

List of Figures

List of Tables

Chapter 1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1-1 Summary of DNR-X-1G/DNR-X-1G-XX Product Versions...........................................3

Chapter 2 The DNR-12-1G Series RACKtangle System . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2-1 Components in PowerDNR DNR-12 Enclosure............................................................9

2-2 Components in PowerDNR Core Module (DNR-CPU-1000 Series)...........................22

Chapter 3 The DNR-6-1G Series HalfRACK System . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3-1 Components in PowerDNR DNR-6 Enclosure............................................................30

Chapter 4 Installation and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4-1 Port States..................................................................................................................60

4-2 List of Functions and Associated Boards ...................................................................64

Chapter 5 PowerDNA Explorer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5-1 Fields and Descriptions for IOM Settings Panel................................... .... ... ...............80

5-2 Fields and Descriptions for I/O Device Settings Panel................................ ... ... ... .... ..81

Chapter 6 Programming CPU Board-specific Functions . . . . . . . . . . . . . . . . . . . . . . . . 91

6-1 Memory Map for DNR-X-1G CPU (DNR-CPU-1000) .................................................91

6-2 Memory Map for DNR-X-1G-02 CPU (DNR-CPU-1000-02).......................................92

6-3 Memory Map for DNR-X-1G-03 CPU (DNR-CPU-1000-03).......................................92

6-4 Set Parameters...........................................................................................................97

B-1 DNA/DNR Replacement Fuses .. ... .... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... ....................109

Page 9

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 1 Introduction

This document describes the features, performance specifications, and

operating functions of the DNR-12-1G Series RACKtangle

Series HalfRACK

RACKtangle and HalfRACK versions are identical except for the size of the

enclosure and the number of IO boards that can be installed. Both are designed

for use with a Gigabit Ethernet 1000 Base-T communication network.

This chapter provides the following information about the DNR-X-1G systems:

• Organization of This Manual (Section 1.1)

• Product Versions Described in This Manual (Section 1.2)

data acquisition systems.

DNR-X-1G Series RACKtangle and HalfRACK Systems

Chapter 1 1

Introduction

and the DNR-6-1 G

1.1 Organization of This Manual

This DNR-X-1G User Manual is organized as follows:

• Chapter 1 – Introduction

This chapter describes the organi zation of the document and the

conventions used throughout the manual.

• Chapter 2 – DNR-12-1G Series RACKtangle

This chapter provides an overview of a DNR-12-1G system, features,

accessories, and a list of all items you need for initial operation.

• Chapter 3 – DNR-6-1G Series HalfRACK

This chapter provides an overview of a DNR-6-1G system, features, and

accessories. It is essentially the same as the DNR-12-1G system except

for enclosure size and number and arrangement of I/O boards.

• Chapter 4 – Installation and Configuration

This chapter summarizes the recommended procedures for installing,

configuring, starting up, and troubleshooting a DNR-X-1G system.

• Chapter 5 – PowerDNA Explorer

This chapter provides a general description of the menus and screens of

UEI’s GUI-based communication application, PowerDNA Explorer,

when used with a DNR-X-1G system.

• Chapter 6 – Programming CPU Board-specific Functions

This chapter describes tools and facilities used for programming boardspecific functions.

System

System

• Appendix A – Configuring Additional Ethernet Cards

This appendix describes procedures for installing and configuring

Ethernet cards for use with Windows operating systems.

• Appendix B – Field Replacement of Fuses

This appendix describes procedures for replacing fuses in the field.

• Index

This is an alphabetical listing of topics covered in the manual, identified

by page number.

Page 10

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 1 2

Introduction

Manual Conventions

To help you get the most out of this manual and our products, please note that

we use the following conventions:

Tips are designed to highlight quick ways to get the job done, or reveal

good ideas you might not discover on your own.

NOTE: Notes alert you to important information.

CAUTION! advises you of precautions to take to avoid injury, data loss, and

damage to your boards or a system crash.

T ext formatted in bold typeface g enerally represents text that shou ld be entered

verbatim. For instance, it can represent a filenames, as in the following example:

“You can instruct users how to run setup using setup.exe executable.”

Bold typeface will also represent button names, as in “Click Scan Network.”

Text formatted in fixed typeface generally represents commands,

source code, or other text that should be entered verbatim into the source code,

initialization, or other file or at a command prompt.

Before you begin:

Before plugging any I/O connector into the chassis or board(s), be sure to

remove power from all field wiring. Failure to do so may cause severe

damage to the equipment.

No HOT SWAP

Always turn POWER OFF before performing maintenance on a UEI system.

Failure to observe this warning may result in damage to the equipment and

possible injury to personnel.

Usage of Terms

Throughout this manual, the term “Cube” refers to either a PowerDNA Cube

product or to a PowerDNA RACKtangle

applicable.

Additionally throughout this manual, the following conventions apply:

• “DNR-X-1G” refers to both DNR-12-1G and DNR-6-1G types of

systems. The DNR-12-1G can accept up to 12 I/O boards and the

DNR-6-1G can accept up to 6 I/O boards. The two models are identical

in all other respects.

rack mounted system, whichever is

• Unless otherwise noted, “DNR-X-1G” applies to all versions of the

RACKtangle and HalfRACK systems: DNR-X-1G (-00/-01),

DNR-X-1G-02, and DNR-X-1G-03. Differences between product

versions are noted on the following page.

Note that the -02 product version is a fully compatible upgrade of the

-00/-01 version.

Page 11

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 1 3

Introduction

1.2 Product Versions Described in This Manual

This user manual provides documentation for the DNR-X-1G series data

acquisition systems: DNR-X-1G, DNR-X-1G-02, and DNR-X-1G-03 product

versions.

Each product version is available in a DNR-12-1G RACKtangle chassis or a

DNR-6-1G HalfRACK chassis.

T able 1-1 below provides a summary of features for each prod uct version. Refer

to the following chapters in this manual for detailed descriptions.

NOTE: Unless otherwise noted, DNR-X-1G refers collectively to the

DNR-X-1G(-00/-01), DNR-X-1G-02, and DNR-X-1G-03 series of

products.

Table 1-1 Summary of DNR-X-1G/DNR-X -1G-XX Product Versions

Item Summary of Features

DNR-X-1G

(DNR-X-1G-00 /

DNR-X-1G-01)

• 10/100/1000Base-T Ethernet interface

• Freescale MPC8347 CPU

• 1PPS synchronization support

• 128 MB RAM

• 32 MB flash memory

2

2

1

DNR-X-1G-02 • 10/100/1000Base-T Ethernet interface

• Freescale MPC8347 CPU

• 1PPS/IEEE-1588 synchronization support

• Optional solid-state hard drives

3

1

• 256 MB RAM2

• 32 MB flash memory

2

DNR-X-1G-03 • 10/100/1000Base-T Ethernet interface

• Freescale MPC8347E CPU, (encryption-ready / IPSec support

pending)

• 1PPS/IEEE-1588 synchronization support

• Optional solid-state hard drives

• 256 MB RAM

• 128 MB flash memory

2

2

3

1

1.1PPS and IEEE-1588 synchronization support is described in the PowerDNx 1PPS Sync Interface Manual.

2.RAM and flash memory are not user-accessible for PowerDNA applications (hosted deployment). Portions

of RAM and flash are available for UEIPAC-based systems (stand-alone deployment). See UEIPAC documentation for more information.

3.On UEIPAC-based systems (stand-alone deployment), solid state d rives are used for data and/or root file

system storage.See UEIPAC documentation for more information.

Page 12

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

The DNR-12-1G Series RACKtangle System

Chapter 2 4

Chapter 2 The DNR-12-1G Series RACKtangle System

This chapter provides the following information about the DNR-12-1G Series

RACKtangle

• PowerDNR DNR-12-1G System Overview (Section 2.1)

• DNR-12-1G Specifications (Section 2.2)

• DNR-12-1G Key Features (Section 2.3)

• DNR-12-1G RACKtangle Enclosure (Section 2.4)

• DNR-12 Power, NIC/CPU, and I/O Boards LEDs & Controls

• DNR-POWER-DC Module (Section 2.6)

• DNR-CPU/NIC Module (Section 2.7)

• DNR-Buffer Module (Section 2.8)

• DNR I/O Boards (Section 2.9)

• DNR-12-1G DC Power Thresholds (Section 2.10)

NOTE: For a list of product versions available for the DNR-12-1G Series

system:

(Section 2.5)

RACKtangle systems, refer to Section 1.2 on page 3.

2.1 PowerDNR DNR-12-1G System Overview

UEI PowerDNR DNR-12-1G RACKtangle systems are rack-mounted versions

of the PowerDNA Cube Ethernet-based data acquisition systems.

The DNR-12-1G houses a PowerDNA data acquisition system in a rack

enclosure with cabling, installation hardware, LEDs, and a power switc h

accessible from the front of the rack chassis. Multiple DNR-12-1G systems may

be mounted in a single rack. All standard DNA- Cube I/O boards are also

available in DNR- RACK versions for use in DNR-12-1G systems.

Figure 2-1. Typical DNR-12-1G RACKtangle System

Page 13

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 2 5

The DNR-12-1G Series RACKtangle System

A standard DNR-12-1G rack system consists of the following:

• One or more DNR-12 rack mounted enclosure(s)

• DNR-POWER-DC Power Module (one for each enclosure)

• DNR-CPU-1000 or DNR-CPU-1000-XX Module

(Freescale MPC8347 or MPC8347E CPU and 1-GB Ethernet

1000 Base-T Network Interface Module — one for each enclosure)

• DNR-BUFFER Board Module (one for each enclosure)

• Optional DNR-IO-FILLER panels (one for each unused I/O slot)

Note: These slot covers are optional and not included in the price of the

rack

• DNA-PSU-180 180-Watt, 120/230 VAC to +24 VDC External Power

Supply (one for each enclosure) with cable and Molex connector for

plug-in to the DNR-POWER-DC Module front panel

T o configure a complete data acquisition system, insert up to 12 DNR I/O boards

into each PowerDNR rack enclosure. I/O boards may be specified in any

combination of UEI’s I/O boards.

All standard PowerDNA accessories are also available for use in a PowerDNR

rack-mount system.

NOTE: For detailed descriptions of all I/O boards and accessories available for

DNR-X-1G systems, refer to www.ueidaq.com.

UEI stand-alone systems (UEIPAC, UEISIM, UEIModbus, and UEIOPCUA

deployments) are also available for use with DNR-12-1G RACK systems:

• UEIPAC 1200R - Programmable Automation Controller

• UEISIM 1200R - Simulink / Simulink Coder Target

• UEIModbus 1200R - Modbus TCP-based Controller

• UEIOPCUA 1200R - OPC-UA Server, accessed by any OPC-UA client

Page 14

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Standard Interfaces

To Host Computer Two independent 1000Base-T Gigabit Ethernet

ports (100/10Base-T compatible)

Distance from host 100 meters, max

Other Interfaces One USB 2.0 controller port, One USB 2.0 slave

port.

Cong/General RS-232, 9-pin “D”

Sync Custom cable to sync multiple racks

I/O Slots Available

DNR-12-1G 12 slots

Data transfer and communications rates

Ethernet data

transfer rate

20 megabytes per second

Analog data

transfer rate

up to 6 megasample per sec (16-bit samples)

DMAP I/O mode update 1000 I/O channels

(analog and/or digital)

in less than 1 millisecond, guaranteed

Processor

CPU Freescale 8347, 400 MHz, 32-bit

Memory 128 MB (not including on-board Flash)

Status LEDs Power supplies within spec, One second system

heart-beat, Attention, Read/Write, Power, Communications Active

Environmental

Temp (operating) Tested to -40 °C to 70 °C

Temp (storage) -40 °C to 85 °C

Humidity 0 to 95%, non-condensing

Vibration

(IEC 60068-2-64) 10–500 Hz, 3 g (rms), Broad-band random

(IEC 60068-2-6) 10–500 Hz, 3 g, Sinusoidal

Shock

(IEC 60068-2-27)

50 g, 3 ms half sine, 18 shocks at 6 orientations;

50 g, 11 ms half sine, 18 shocks at 6 orientations

MTBF 130,000 hours

Physical Dimensions

DNR-12 series 5.25” x 6.2” x 17.5” (3U in a 19” rack)

Power Requirements

Voltage 9 - 36 VDC (AC adaptor included)

Fuse Internal 10 A

Power Dissipation 13 W at 24 VDC (not including I/O boards)

Power Monitoring

I/O board power All internal power supplies monitored to ±1% ac-

curacy. All PS voltages may be read by host. LED

annunciators indicate out of range

Input current Monitored by host, LED indicates overcurrent

Chapter 2 6

The DNR-12-1G Series RACKtangle System

2.2 DNR-12-1G

Specifi-

Figure 2-2 lists the technical specifications of the DNR-12-1G PowerDNR

system.

cations

Figure 2-2. DNR-12-1G Technical Specifications

Page 15

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Easy to Configure and Deploy

Over 30 different I/O boards available

Over 5 quadrillion possible configurations

Gigabit Ethernet based (100/10Base-T compatible)

Bracket kit for mounting to wall or in 19” racks

Industrial quality rubber feet for solid table-top mounting

Passive backplane ensures extremely low MTTR

Standard “Off-the-shelf” products and delivery

True Real-time Performance

1 msec updates guaranteed with 1000 I/O

Up to 6 million samples per second

Use QNX, RTX, 7Y8PSLT

Flexible Connectivity

1000Base-T with Cat-5 cable

Supports WIFI / GSM / Cell networks

Built-in USB 2.0 slave and controller ports

Compact Size:

5.25” x 6.2” x 17.5”

300 analog inputs per rack

384 analog outputs per rack

576 digital I/O bits per rack

96 counter/quadrature channels per rack

144 ARINC-429 channels per rack

48 RS-232/422/485 ports per rack

Low Power:

Less than 13 watts per typical rack (not including I/O)

AC, 9-36 VDC or battery powered

Standalone Modes

Upgradeable to UEI1"$ 1200R

Upgradeable to UEI4*. 1200R

Upgradeable to UEIModbus 1200R

Rugged and Industrial:

Solid Aluminum construction

130,000 hour MTBF

Operation tested from -40°C to +70°C

Vibration tested to 3 g, (operating)

Shock tested to 50 g (operating)

All I/O isolated from rack and host PC

Outstanding Software Support

Windows, Linux, RT Linux, Windows RT, RTX VXworks and

QNX operating systems

VB, VB .NET, C, C#, C++

MATLAB, LabVIEW, OPC, ActiveX support

Chapter 2 7

The DNR-12-1G Series RACKtangle System

2.3 DNR-12-1G

The following table is a list of key features of a DNR-12-1G PowerDNR system.

Key Features

Figure 2-3. DNR-12-1G PowerDNR Product Features

Page 16

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Backplane

Mounting

Brackets (2)

(Reversible for

rack or surface

mounting)

Grounding

Fingers

Add rubber feet (4)

for tabletop mounting

Note: Top/Rear Cover Not Shown

The DNR-12-1G Series RACKtangle System

Chapter 2 8

2.4 DNR-12-1G RACKtangle Enclosure

2.4.1 DNR-12-1G

Enclosure

This section describes the DNR-12-1G chassis and provides an overview of

common components included in every DNR-12-1G system.

The DNR-12 enclosure is a rigid mechanical structure with complete EMI

shielding (see Figure 2-4 below). Unused slots can be filled with filler panels

(filler panel diagram shown in Figure 2-6).

The DC/DC power module provides output voltages of 24, 3.3, 2.5, 1.5, and 1.2

VDC for the logic/CPU and 8 VDC to power the four cooling fans .

2.4.2 DNR-12-1G

Figure 2-4. Typical PowerDNR DNR-12 Enclosure (Exploded View)

NOTE: Note that the rightmost module (I/O board slot 12) is 2-slots wide (to

accommodate future designs and/or custom modules).

Also note that the DNR-12 enclosure has reversible mounting flanges

designed for rack or surface mounting. Rubber feet are supplied for

desktop or tabletop mounting.

Refer to Section 4.7 on page 56 for more information about mounting

options and field connections.

Each DNR-12-1G chassis contains a power board (DNR-POWER-DC) with

Enclosure

Common

Components

status indicators and an external ON/OFF switch. Each DNR-12-1G chassis

also contains a CPU board with a dedicated GigE CPU and two Network

Interface Control (NIC) ports, one for controlling up to 12 I/O boards mounted in

the enclosure and another for diagnostics functions. Front-loading slots allow

I/O boards to be quickly and easily installed and removed, as needed.

Page 17

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

DNR-POWER-DC DNR-CPU-1000/-XX DNR-BUFFER

up to 12 PowerDNR I/O Boards

Chapter 2 9

The DNR-12-1G Series RACKtangle System

Up to 12 DNR I/O boards can be installed in the chassis; DNR I/O boards are

functionally identical to the corresponding DNA boards for the Power DNA Cube.

The only differences between RACK and Cube I/O boards are the mounting

hardware. The DNA version I/O boards are designed to stack in a Cube chassis.

The DNR version I/O boards are designed to plug into the backplane of a RACK

chassis.

Figure 2-5. Typical PowerDNR DNR-12 Board Placement

Table 2-1 Components in PowerDNR DNR-12 Enclosure

Item / Part No. Description

DNR-POWER-DC One isolated DC/DC Power Module/Power Monitor with status indicators, a local

on/off switch, and 4-pin Molex Power-In connector. (Refer to Section 2.6 for

detailed information)

DNR-CPU-1000,

DNR-CPU-1000-02,

DNR-CPU-1000-03

DNR-BUFFER One for buf fering address/con trol/clock lines (not currently addr essable). (Refer to

PowerDNR I/O

Boards

DNR-BP-12 One backplane with two temperature sensors (see Figure 2-4 for diagram)

DNR-IO-FILLER Blank filler panels for all unused slots (see Figure 2-6. Note that this item is

One dual-slot CPU/NIC module with status indicators, two Ethernet connectors

(Main and Diagnostic Ports), sync connector , reset pushbutton, SD card slot, USB

controller/slave ports (reserved), and a DB-9 connector for a serial port.

(Refer to Section 2.7 for detailed information)

Section 2.8 for detailed information)

Up to 12 front pull-out I/O boards (DNR boards are functionally identical to

PowerDNA Cube I/O boards but designed for installation in a DNR rack

enclosure). (Refer to Section 2.9 for detailed information)

optional / not included in price of rack)

Fans Four 8-volt cooling fans mounted on the rear of the enclosure (see Figure 2-9 for

air flow diagram)

All UEI modules are available in both PowerDNA and Power DNR package

designs.

Page 18

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 2 10

The DNR-12-1G Series RACKtangle System

2.4.2.1 Physical

Addressing of

DNR-12-1G

Components

A feature of th e DNR-X-1G design is that the address of a module is determined

by the position of the module within the enclosure, numbered from left to right. A

typical module address is:

0xA00nxxxx

where A00 is the BASE address

n is the module position number starting from 0 at the left

xxxx is the address of the module

With this addressing method, the address of a given I/O board (module)

automatically changes if you move it from one position to another within the

enclosure.

The slots or module positions are numbered as follows (left to right):

Physical Position Position Number Module Description

10xC POWER-DC

2 0x0 I/O Board 1

3 0x1 I/O Board 2

4 0x2 I/O Board 3

5 0x3 I/O Board 4

6 0x4 I/O Board 5

7 0x5 I/O Board 6

80xD

0xE

POWER-1GB

CPU/NIC

9 N/A BUFFER

10 0x6 I/O Board 7

11 0x7 I/O Board 8

12 0x8 I/O Board 9

13 0x9 I/O Board 10

14 0xA I/O Board 11

15 0xB I/O Board 12

Page 19

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Grounding

Fingers

Turn bracket upside down

to use as surface or flange

mounted device

Chapter 2 11

The DNR-12-1G Series RACKtangle System

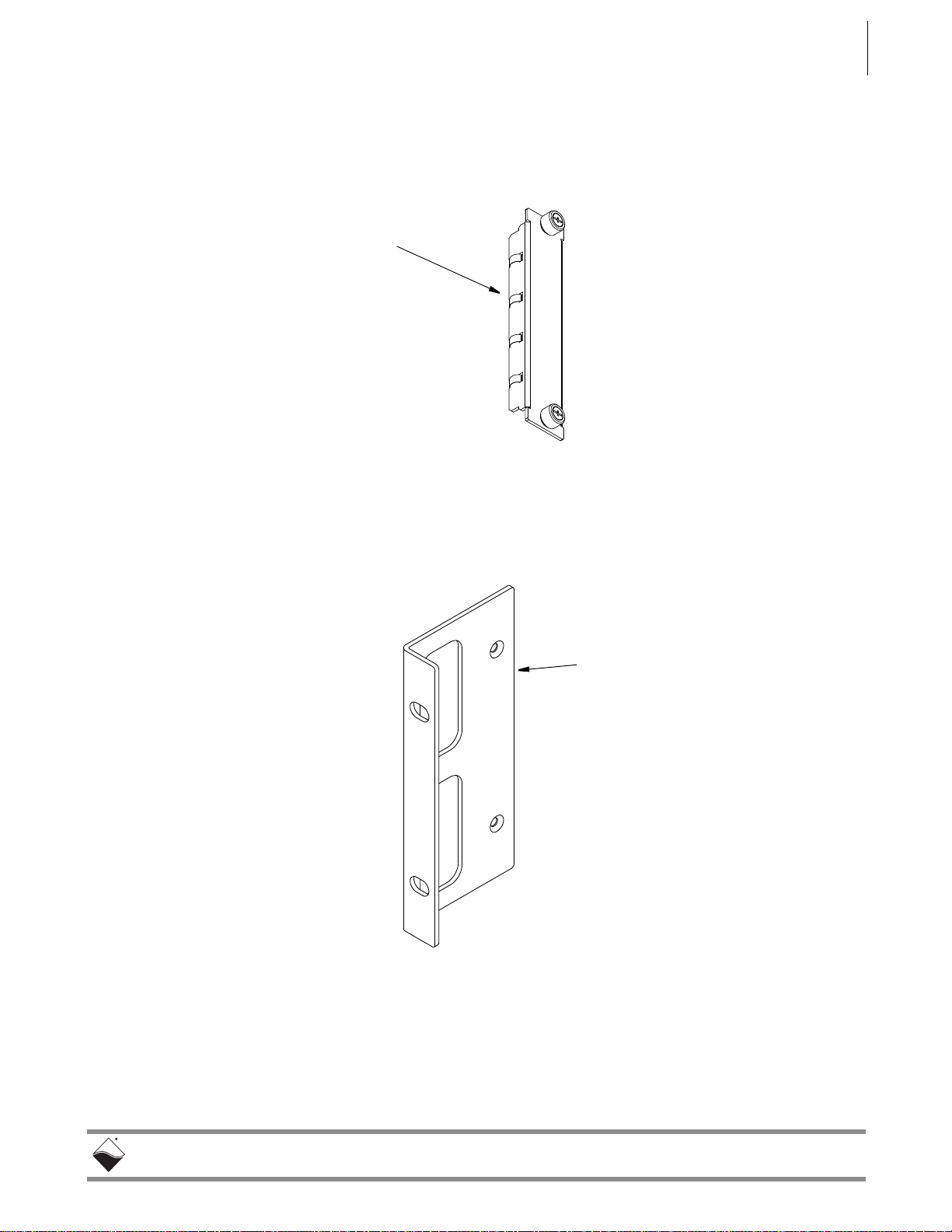

2.4.2.2 DNR-IOFILLER, DNRBRACKET, &

DNR- I/O

Board

Drawings

The following section provides drawings for the DNR-IO-FILLER,

DNR-BRACKET, and DNR- I/O board extraction lever as found in DNR-X-1G

systems.

Figure 2-6. Optional DNR-IO-Filler Panel for Empty Slots

Figure 2-7. DNR-BRACKET Reversible Mounting Bracket

Page 20

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Lift Lever

to eject

board from

backplane

connector

Press lever

down to

insert board

into

backplane

connector

DNR Backplane Connector

Chapter 2 12

The DNR-12-1G Series RACKtangle System

Figure 2-8. DNR Board Ejection/Insertion Lever Operation

Page 21

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 2 13

The DNR-12-1G Series RACKtangle System

2.4.3 DNR-12-1G

Cooling Air

Flow

As shown below in Figure 2-9, cooling air is drawn into the rear of the enclosur e

via four fans, routed forward over the electronic circuit boards, up to the top of

the enclosure, and then out the top rear of the enclosure. The system is

designed to maintain positive pressure cooling within the enclosure at all times.

Figure 2-9. DNR-12 Air Flow

Two sensors mounted on the backplane over the Power Module and over the

CPU board continuously monitor internal temperatures, turning fans on if the

internal temperature exceeds 45°C, off if it falls below 45°C, and shutting down

power if a high limit is exceeded.

Page 22

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

SD Card

USB B

USB A

NIC 1

NIC 2

Sync/Reset

RS-232

3.3

24

COM

USRR/W

PG

POWER

Module 1

Module 2

Module 3

Module 4

Module 5

Module 6

CPU/NIC

Buffer

Module 7

Module 8

Module 9

Module 10

Module 11

Module 12

Module

(dual width)

DNR-POWER-DC

Typical

I/O Board

Serial Port

Connector

Status

LEDs

NIC1 Port

NIC2 Port

Temp1 Sensor (on backplane)Temp0 Sensor (on backplane)

Status

LEDs

DB

Connector

V

in

1.5V

User

Overtemp

24V

3.3V

I

in

I/O

Attention

24V

3.3V

(7-12)

(1-6)

Power

Conn.

PowerDNR

PowerDNR

Fan

Switch

0n/off

Power

DB-9

ATT Indicates error when red

R/W Flashes when bus is active

COM Flashes when SD Card is read/written

PG Indicates presence of valid power input

LEDs

DC/DC Module

(Single Slot Model)

USB 2.0

USB 2.0

Controller

DNR-CPU-1000/-XX

CPU/NIC Module

PowerDNR

Slave Port

Port

Sync Conn/

RESET

SD Card

Slot

Chapter 2 14

The DNR-12-1G Series RACKtangle System

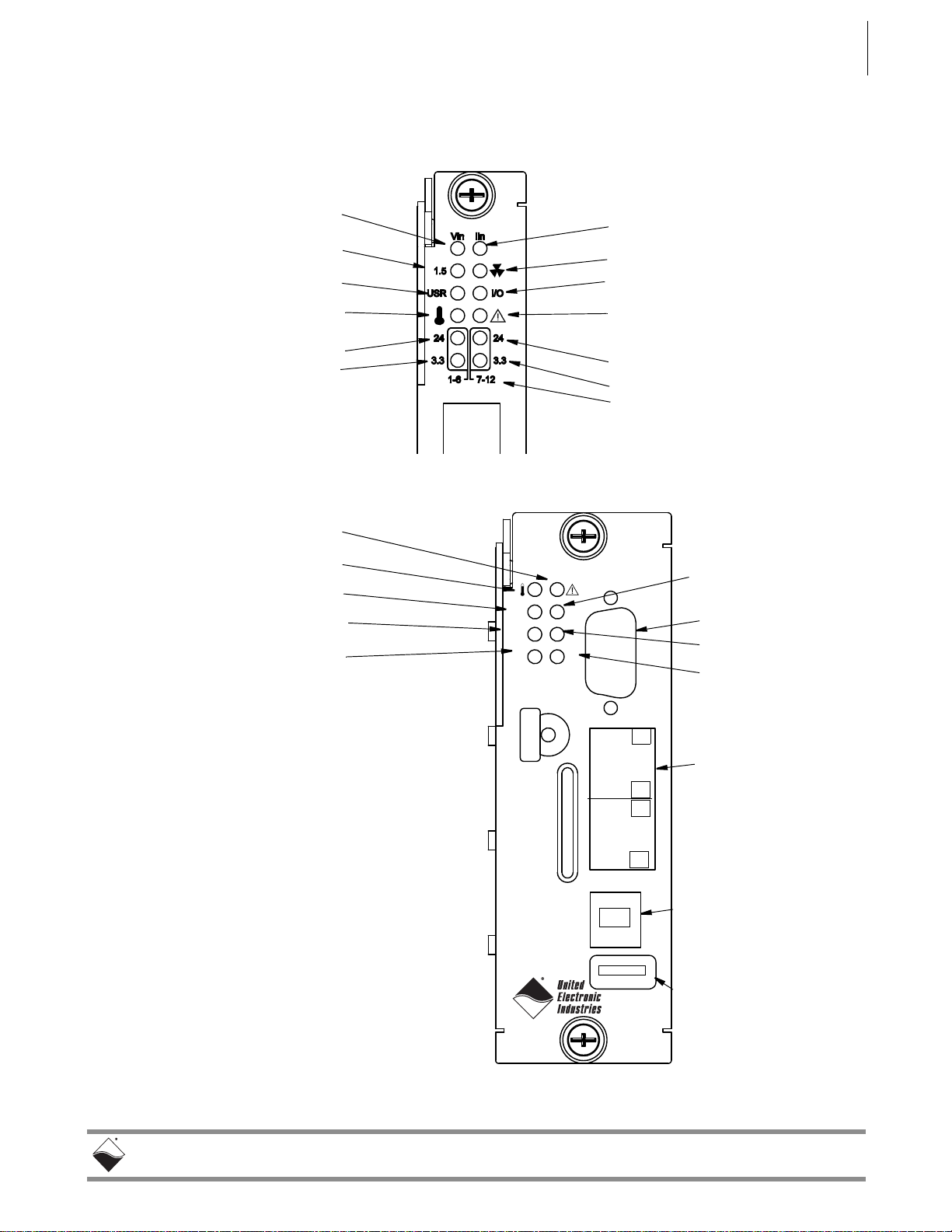

2.5 DNR-12

Power, NIC/

CPU, and I/O

Boards LEDs

& Controls

DNR-12-1G LED indicators are illustrated in Figure 2-10.

The power , CPU, and I/O board LEDs are individu ally described in Figure 2-11,

Figure 2-12, and Figure 2-13 respectively.

Figure 2-10. DNR-12-1G System Front Panel Arrangement

Page 23

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Input Voltage OK/Error

1.5VDC OK/Error

User Controlled/Off (default)

LED ON/Off means:

Input Current OK/High

Fans On/Off

I/O Circuit OK (flashes 1/sec))

LED ON/OFF means:

24VDC OK/Error -- Modules 7-12

3.3VDC OK/Error -- Modules 7-12

24VDC OK/Error -- Modules 1-6

3.3VDC OK/Error -- Modules 1-6

When flashing, module needs

Temp High/OK

Module Groups

attention

SD Card

USB B

USB A

NIC 1

NIC 2

Sync/Reset

RS-232

3.3

24

COM

USRR/W

PG

When Flashing,

Read/Write Activity

Serial Comm. Activity

Power Good

Module Needs Attention

Note: On a UEIPAC CPU/NIC module,

the LEDs are user-programmable.

Temp High/OK

USB 2.0 Controller Port

Type A Connector

USB 2.0 Slave Port

Type B Connector

(reserved for future use)

(reserved for future use)

Ethernet Ports

NIC1 (Main),

Serial Port

User Controlled/Off

3.3VDC OK/Error

24VDC OK/Error

NIC2 (Secondary)

The DNR-12-1G Series RACKtangle System

Figure 2-11. DC Power Module LEDs

Chapter 2 15

Figure 2-12. DNR-CPU-1000/-XX Module LEDs

Page 24

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Ready (Power ON)

Status

The DNR-12-1G Series RACKtangle System

Figure 2-13. Typical I/O Module LEDs

Chapter 2 16

Page 25

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 2 17

The DNR-12-1G Series RACKtangle System

2.6 DNR-POWER-

DC Module

The DNR-POWER-DC Module is a dedicated DC/DC source and control

module available only for use with a PowerDNR rack enclosure. It is always

mounted in the leftmost slot of the DNR chassis and is recognized on the

PowerDNR bus with an ID of 0x020 at address 0xA00C0000.

The non-isolated side (NIS) logic complies with full common logic interface (CLI)

implementation. The key features of the DNR-POWER Module are:

• Input power — 9-36 VDC 80W maximum, protected by resettable fuses

and EMI chokes

• Power supply on/off switch (with guard)

• Output power sources (all with greater than 90% efficiency)

24V, 1A (24W)

3.3V, 5A (16.5W, including the 2.5V derived voltage)

2.5V, 3A (derived from 3.3V source)

1.5V, 5A, (7.5W, including the 1.2V derived voltage)

8V, 0.5A (4W for fans)

• DC/DC for 24V , 3.3V , and 1.5V are synchron ized from the single spreadspectrum clock source in the CPU/NIC Module for lower EMI noise level

• Fan control (Forced ON) and status ON/OFF

• Monitoring and LED indicators (1% accuracy, 0.25Hz update rate)

for:

– All output voltages

– Input current for the 9-36VDC for the DNR Enclosure

– All voltages from the NIC Module (24V, 3.3V, 2.5V)

– Temperature of the DNR backplane (2 sensors)

• Onboard FPGA logic chip is CYCLONE EP1C3/C6T144

• TI MSP4300 microcontroller used for logic reprogramming

• Input-Output connector is a 128-pin component that provides 9-36VDC

for all modules from an external power source

Page 26

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Ejection Lever

On/Off Switch

Power

Connector

Indicating LEDs

Grounding

Fingers

(hidden)

Chapter 2 18

The DNR-12-1G Series RACKtangle System

Figure 2-14. DNR-POWER-DC Module

Page 27

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

3.3V DC/DC

3.3V DC/DC

3.3V DC/DC

2.5V LDO

1.5V DC/DC

1.2V LDO

24V DC/DC

FAN3-4 CONTROL

8V FAN DC/DC

24-bit ADC (LTC2498) 13 sources: +2.5V, +2.5VNIC, 3.3V, +3.3VNIC,

+24Vm +24VNIC, +VIN, +1.5V, +1.2V, +8V FAN, I

in

,

TEMP1 (TCPOS), TEMP2 (TCNEG). Voltage sources use 1:23.1

dividers on the front end, except for the Vin, which uses a 1:45.3

divider.

Standard NIC-logic plus:

Access to ADC data readings

Fan 1-2 and 3-4 ON/OFF control

Fan ON/OFF status

12 LEDs ON/OFF control

LED block – 12 status LEDs

Input Current

Monitor

+2.5V NIC

DNR Bus Connector

+3.3V NIC

+24V NIC

TEMP1

TEMP2

FAN1-2 CONTROL

Input Voltage Source

9-36 VDC @ 80 W max.

1.2V

1.5V

24V

3.3V

2.5V

24V

8V

Vin

Chapter 2 19

The DNR-12-1G Series RACKtangle System

A functional block diagram of the DNR-POWER-DC Module is shown in

Figure 2-15 below.

Figure 2-15. Functional Block Diagram of DNR-POWER-DC Module

As shown in Figure 2-15, the DNR-POWER-DC Module operates as follows:

A 9-36 VDC voltage input (Vin) from an external source is connected to the

board through a replaceable slow-blow fuse. The board monitors the input

current and passes Vin to the DNR bus as Vout.

Vout also is connected to DC/DC converters that produce 24 VDC, 3.3 VDC and

1.5 VDC output voltages, which are also placed on the DNR bus. Both 3.3 and

1.5 VDC voltages are connected to low dropout regulator s that, in turn, generate

the 2.5 VDC and 1.2 VDC output voltages on the bus. The 24 VDC source is fed

to a low dropout regulator that produces 8 VDC to drive the cooling fans (through

fan controller chips).

Page 28

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

CPU/NIC

PULLUPS

SLOTS

6...B

SLOTS

0..5, C

PWR

ADDR/CTRL

CLOCKS

TEMP1

TEMP0

2.5V

3.3V, 24V

1.2V AND 1.5V

2.5V,3.3V

ADDR/CTRL

CLOCKS

6

6

DNR-BUFFER/

CLOCK DIST.

DATA BUS

DNR-POWER-DC

PULLUPS

I/O

I/O

Chapter 2 20

The DNR-12-1G Series RACKtangle System

The input current and all output voltages, including the +2.5, +3.3, and +24 VDC

from the NIC module, plus signals from the two temperature sensors mounted

within the enclosure, are input to a 24-bit delta-sigma A/D converter. Except for

Vin, the voltage sources use 1:23.1 divide rs on the front end. Vin uses a 1:45.3

divider.

Figure 2-16 shows the interaction of modules within a DNR-12 enclosure when

the DNR-BUFFER module is used.

Figure 2-16. Functional Block Diagram of DNR-12 Enclosure

As shown above, the I/O slots are divided into two groups: 0 to 5 and 6 to 0xB.

0xC for the DC Power Module is included with the 0 to 5 group. The DNRBUFFER board is located at the center of the enclosure, which is also at the

center point of the ADDR/CTRL bus. The DNR-CPU-1000 module is also

located at the center of the enclosure and the center of the data b us to minimize

bus delays. The CPU addresses I/O Boards and transmits clock ticks through

the Buffer Board, which controls the Addr/Ctrl and clock lines to the modules.

Temperature sensors monitor temperatures within the enclosure above the

DNR-POWER-DC module and the DNR-CPU module.

Page 29

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Front Panel Isometric of Carrier

(holds two circuit boards – CPU and NIC)

SD Card

USB B

USB A

NIC 1

NIC 2

Sync/Reset

RS-232

3.3

24

COM

USRR/W

PG

DB-9 Connector

for serial port

Diagnostic

Port - NIC2

Primary Ethernet

Port - NIC1

USB A

USB B

Chapter 2 21

The DNR-12-1G Series RACKtangle System

2.7 DNR-CPU/NIC Module

The DNR-CPU/NIC Core Module (DNR-CPU-1000, DNR-CPU-1000-02, or

DNR-CPU-1000-03) occupies two slots of a DNR-X-1G RACKtangle

enclosure.

The DNR-CPU/NIC Core module consists of a Freescale (formerly Motorola)

MPC8347 or MPC8347E 32-bit 400 MHz CPU and per ipheral devices (USB 2.0,

RS-232, NIC, SD, etc) for use with a Gigabit Ethernet communication network

and an internal 66 MHz 32-bit common logic interface bus. The NICs are cop per

(1000BaseT) interfaces. The module has an RS-232 port used for co nfiguration

and also two USB 2.0 ports (controller and slave) for general purpose use (not

implemented yet). LEDs on the front panel of each module indicate the current

operating status of the device.

Figure 2-17. DNR-X-1G Series Core Module (CPU/NIC)

Page 30

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

MAC

MAC

PPC 8347

DC/DC

9-36V DC Input

Power Out

Power In

SD Card RS-232

32-bit 66-MHz bus

RJ-45

RJ-45

PHY

PHY

RTC

DDR2

FLASH

MII

1000-BASE-T

MII

FPGA

USB 2.0

USB 2.0

,(((QHWZRUNV\QFKURQL]DWLRQVXSSRUWRQDQG&38YHUVLRQV

Chapter 2 22

The DNR-12-1G Series RACKtangle System

2.7.1 Device

Architecture

of DNR Core

Module

Figure 2-17 shows the architecture of the DNR-CPU-1000 Series Core

Modules:

Figure 2-18. FreeScale PowerPC CPU/NIC Controller Architecture

The core of the system is a Freescale PowerPC MPC834 7 or MPC8347E 32-bit

400 MHz processor, which controls the following components:

Table 2-2 Components in PowerDNR Core Module (DNR-CPU-1000 Series)

Item Description

NIC1:

Primary Network

Interface MII Port

NIC2:

Diagnostic Network

Interface MII Port

RS-232 Port The RS-232 port provides a serial communication link between the DNR-X-1G

USB 2.0 Dual Port

(Controller and Slave)

32 MB or 128 MB

Flash Memory

1

The NIC1 port provides communication between the DNR system and the

primary LAN network.

The NIC2 port provides access to the DNR system for monitoring system health

during operation, using a separate diagnostic port. This port may also be

assigned as the primary Ethernet port if NIC1 is not available for use.

system and a standard RS-232 terminal.

The USB A and B ports are not supported on DNR-X-1G (hosted) systems

(only supported on UEIPAC, UEISIM, UEIModbus, and UEIOPC-UA

deployments).

DNR-X-1G (-00/-01) systems provide 32 MB of flash memory (DNR-CPU-

1000).

DNR-X-1G-02 systems provide 32 MB of flash memory (DNR-CPU-1000-02).

DNR-X-1G-03 systems provide 128 MB of flash memory (DNR-CPU-1000-03).

Page 31

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

The DNR-12-1G Series RACKtangle System

Table 2-2 Components in PowerDNR Core Module (DNR-CPU-1000 Series)

Item Description

Chapter 2 23

128 MB or 256 MB

of SDRAM

SYNC Port

1

2

IEEE-1588

Synchronization

Support

SD Card

2

1

DNR-X-1G (-00/-01) systems provide 128 MB of RAM (DNR-CPU-1000).

DNR-X-1G-02 systems provide 256 MB of RAM (DNR-CPU-1000-02).

DNR-X-1G-03 systems provide 256 MB of RAM (DNR-CPU-1000-03).

A high-speed system-to-system synchronization connector permits triggers or

clocks to be shared among multiple systems. Two systems may be connected

together directly and larger groups m ay use the SYNC in terface to shar e timing

signals among many racks and systems.

The trigger and clock inputs will accept signals from standard digital logic that is

powered in the range of 3.3 V to 5 V. The inputs also have internal pull-up

resistors to an internal 5 V supply , making the inputs also compatible with a lowside drive open-collector output. The Sync and trigger outputs have 5 V logic

levels. The sync connector’s ground and 5 V power connections are provided

by its own isolated DC-DC converter.

DNR-X-1G-02 and DNR-X-1G-03 systems implement IEEE-1588

synchronization in hardware. (DNR-CPU-1000-02 and DNR-CPU-1000-03)

A slot for inserting a Secure Digital card.

SD cards are not supported on DNR-X-1G systems.

(SD cards are only supported on UEIPAC, UEISIM, UEIModbus, and UEIOPCUA deployments, uses EXT3 as filesystem for the system partition and

optionally FAT32 for one or more data partitions on the UEIPAC-based standalone systems only).

1

Solid state hard drive

Optional solid state hard drive (only supported on UEIPAC, UEISIM,

UEIModbus, and UEIOPC-UA deployments).

LEDs The operating conditions indicated by the front panel LEDs are described in

Figure 2-11 on page 15 through with Figure 2-13 on page 16.

Watchdog T imer With

Real-time Clock

The DNR-X-1G system includes a watchdog timer with battery backed-up realtime clock.

(Battery Backed)

1.The SD card, SSDs, RAM and flash memory are not user-accessible for PowerDNA applications (hosted

deployment). Portions of RAM and flash are available for UEIPAC-based systems (stand-alone deployment).

See UEIPAC documentation for more information.

2.1PPS and IEEE-1588 synchronization support is described in the PowerDNx 1PPS Sync Interface Manual.

Not all components are available for control from the CPU. The CPU can

program flash memory, set the LEDs, set up the watchdog timer, set the realtime clock and use 256 bytes of backed-up memory in th e watchdog timer chi p.

All functions are available at the firmware level only (described in iom.c/iom.h).

Page 32

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 2 24

The DNR-12-1G Series RACKtangle System

2.8 DNR-Buffer Module

The DNR-BUFFER Module provides buffering between the CPU and I/O board

address/control/clock lines, which functions as described in Figure 2-16.

Although the module may not always be required, it is included to provide an

extra margin of safety against loss of data.

2.9 DNR I/O Boards

All standard cube-based PowerDNA I/O boards are also available as rackbased PowerDNR boards. A typical PowerDNR board is functionally identical to

its corresponding PowerDNA version. The only difference between them is the

physical mounting arrangement. PowerDNR modules are designe d for insertion

into the DNR-6 or DNR-12 enclosure; PowerDNA modules can be inserted only

into a PowerDNA Cube.

Refer to the datasheets and user manuals for detailed electrical specifications,

board descriptions, and user instructions for I/O boards. These documents are

available on the UEI website at www.ueidaq.com.

2.10 DNR-12-1G

DC Power

Table 2-1 lists the DC power threshold specifications for DNR-12-1G 12-slot

RACKtangle systems.

Thresholds

Table 2-1 DC Power Thresholds for DNR-X-1G RACKtangle and HalfRACK systems

Logic power

supply

Analog power

supply

Fan power

supply

On-board

DC/DCs that

use input

power

Backplane

Power Rail

Voltages

+3.3V, +2.5V,

+1.5V, +1.2V

+24V 8.5 - 7.8 Analog power supply is

+12V 8.5 - 8.4

+VIn 7.8-8.8 - 7.5-8.5 Varies with board type.

Turn-on

Voltage, V

1

7.5 7.2

(When Vin is

below 7.2V , a

voltage reset

puts all

boards into

reset mode.)

Reset

Voltage, V

Turn-off

Voltage, V

2

7.0 Supplies power to all CPUs

and FPGAs. DNR can communicate with Ethernet

when CPU is functional

used as a regulated source

for on-board DC/DCs on

most boards

Notes

1. Turn-on, V: The value of Vin at which the corresponding DC/DCs are turned on.

2. Turn-off, V: The value of Vin at which the corresponding DC/DCs are turned off.

NOTE: A DNR-12- 1G CPU/NIC core module consumes only 70mW whe n Vin is

below 7V.

Page 33

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

The DNR-6-1G Series HalfRACK System

Chapter 3 25

Chapter 3 The DNR-6-1G Series HalfRACKSystem

This chapter provides the following information about the DNR-6-1G Series

HalfRACK

NOTE: For the list of product versions available for the DNR-6-1G Series

system:

• PowerDNR DNR-6-1G System Overv iew (Section 3.1)

• DNR-6-1G Specifications (Section 3.2)

• DNR-6-1G Key Features (Section 3.3)

• DNR-6-1G HalfRACK Enclosure (Section 3.4)

• DNR-6 Power, NIC/CPU, and I/O Boards LEDs & Controls (Section 3.5)

• DNR-6-1G DNR-POWER-DC Module (Section 3.6)

• DNR-6-1G DNR-CPU/NIC Module (Section 3.7)

• DNR-6-1G DNR-IO-Modules (Section 3.8)

• DNR-6-1G DC Power Thresholds (Section 3.9)

HalfRACK systems, refer to Section 1.2 on page 3.

3.1 PowerDNR DNR-6-1G System Overview

UEI DNR-6-1G HalfRACK systems are identical to the DNR-12-1G systems

except for the size of the enclosure and the number and ord er of I/O boards that

can be accepted. All standard DNA- Cube I/O boards are available in

DNR- RACK versions for use in DNR-6-1G systems.

Figure 3-1. Typical DNR-6-1G HalfRACK System

Page 34

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Chapter 3 26

The DNR-6-1G Series HalfRACK System

A standard DNR-6-1G rack system consists of the following modules:

• One or more DNR-6 rack mounted enclosure(s)

• DNR-POWER-DC Power Module (one for each enclosure)

• DNR-CPU-1000 or DNR-CPU-1000-XX Module

(Freescale MPC8347 or MPC8347E CPU and 1-GB Ethernet

1000 Base-T Network Interface Module — one for each enclosure)

• Optional DNR-IO-FILLER panels (one for each unused I/O slot)

Note: These slot covers are optional and not included in the price of the

rack.

• DNR-PSU-100 100-Watt, 120/230 VAC to +24 VDC External Power

Supply (one for each enclosure) with cable and Molex connector for

plug-in to the DNR-POWER-DC Module front panel.

To configure a complete data acquisition system, insert up to 6 DNR I/O boards

into each PowerDNR rack enclosure. I/O boards may be specified in any

combination of UEI’s I/O boards.

All standard PowerDNA accessories are also available for use in a PowerDNR

rack-mount system.

NOTE: For detailed descriptions of all I/O boards and accessories available for

DNR-X-1G systems, refer to www.ueidaq.com.

UEI stand-alone systems (UEIPAC, UEISIM, UEIModbus, and UEIOPCUA

deployments) are also available for use with DNR-6-1G RACK systems:

• UEIPAC 600R - Programmable Automation Controller

• UEISIM 600R - Simulink / Simulink Coder Target

• UEIModbus 600R - Modbus TCP-based Controller

• UEIOPCUA 600R - OPC-UA Serv er, accessed by any OPC-UA client

Page 35

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Standard Interfaces

To Host Computer Two independent 1000Base-T Gigabit Ethernet

ports (100/10Base-T compatible)

Distance from host 100 meters, max

Cong/General RS-232, 9-pin “D”

Sync Custom cable to sync multiple racks

I/O Slots Available

DNR-6-1G 6 slots

Data transfer and communications rates

Ethernet data

transfer rate

20 megabytes per second

Analog data

transfer rate

up to 6 megasample per sec (16-bit samples)

DMAP I/O mode update 1000 I/O channels (analog and/or digital)

in less than 1 millisecond, guaranteed

Processor

CPU Freescale 8347, 400 MHz, 32-bit

Memory 128 MB (not including on-board Flash)

Status LEDs Power supplies within spec, One second system

heart-beat, Attention, Read/Write, Power, Communications Active

Environmental

Temp (operating) Tested to -40 °C to 70 °C

Temp (storage) -40 °C to 85 °C

Humidity 0 to 95%, non-condensing

Vibration

(IEC 60068-2-64) 10–500 Hz, 3 g (rms), Broad-band random

(IEC 60068-2-6) 10–500 Hz, 3 g, Sinusoidal

Shock

(IEC 60068-2-27)

50 g, 3 ms half sine, 18 shocks at 6 orientations;

50 g, 11 ms half sine, 18 shocks at 6 orientations

MTBF 130,000 hours

Physical Dimensions

DNR-6 series 5.25” x 6.2” x 10.5” (3U in a 19” rack)

Power Requirements

Voltage 9 - 36 VDC (AC adaptor included)

Fuse Internal 10 A

Power Dissipation 13 W at 24 VDC (not including I/O boards)

Power Monitoring

I/O board power All internal power supplies monitored to ±1% ac-

curacy. All PS voltages may be read by host. LED

annunciators indicate out of range

Input current Monitored by host, LED indicates overcurrent

Input voltage Monitored by host, LED indicates out of range

Chapter 3 27

The DNR-6-1G Series HalfRACK System

3.2 DNR-6-1G

The technical specifications of the DNR-6-1G system are listed below.

Specifications

Figure 3-2. DNR-6-1G Technical Specifications

Page 36

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Easy to Configure and Deploy

Over 30 different I/O boards available

Over 5 quadrillion possible configurations

Gigabit Ethernet based (100/10Base-T compatible)

Bracket kit for mounting to wall or in 19” racks

Industrial quality rubber feet for solid table-top mounting

Passive backplane ensures high MTBF and Low MTTR

Standard “Off-the-shelf” products and delivery

True Real-time Performance

1 msec updates guaranteed with 1000 I/O

Up to 6 million samples per second

Use QNX, RTX, 7Y8PSLT

Flexible Connectivity

1000Base-T with Cat-5 cable

Supports WIFI / GSM / Cell networks

Compact Size:

5.25” x 6.2” x 10.5”

150 analog inputs per rack

192 analog outputs per rack

288 digital I/O bits per rack

48 counter/quadrature channels per rack

72 ARINC-429 channels per rack

24 RS-232/422/485 ports per rack

Low Power:

Less than 13 watts per typical rack (not including I/O)

AC, 9-36 VDC or battery powered.

Standalone Modes

Upgradeable to UEI1"$ 600R

Upgradeable to UEI4*. 600R

Upgradeable to UEIModbus 600R

Rugged and Industrial:

Solid Aluminum construction

130,000 hour MTBF

Operation tested from -40°C to +70°C

Vibration tested to 3 g, (operating)

Shock tested to 50 g (operating)

All I/O isolated from rack and host PC.

Outstanding Software Support

Windows, Linux, RT Linux, Windows RT, RTX VXworks and

QNX operating systems

VB, VB .NET, C, C#, C++

MATLAB, LabVIEW, OPC, Active X

Chapter 3 28

The DNR-6-1G Series HalfRACK System

3.3 DNR-6-1G

The following table is a list of the key features of a DNR-6-1G system.

Key Features

Figure 3-3. DNR-6-1G HalfRACK Product Features

Page 37

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

Backplane

Rubber feet (4)

for tabletop mounting

Guides for Power,

CPU, and I/O

modules

Cooling Fans

Carrying

Handle

with 2 temp.

sensors

Chapter 3 29

The DNR-6-1G Series HalfRACK System

3.4 DNR-6-1G HalfRACK Enclosure

3.4.1 DNR-6-1G

Enclosure

This section describes the DNR-6-1G chassis and provides an overview of

common components included in every DNR-6-1G system.

The enclosure is a rigid mechanical structure with complete EMI shielding. A

convenient carrying handle is also provided for portability. Unused slots can be

filled with blank filler panels. The DC/DC power module provides output voltages

of 24, 3.3, 2.5, 1.5, and 1.2 VDC for the logic/CPU and 8 VDC to power the three

cooling fans.

Figure 3-4. Typical HalfRACK DNR-6 Enclosure (Exploded View)

NOTE: Note that the rightmost module (I/O board 6) is 2-slots wide (to

accommodate future designs and/or custom boards).

Also note, rubber feet are supplied for desktop or tabletop mounting. If

rack mounting is desired, UEI recommends using a shelf for mounting in

a 19 inch enclosure. Refer to Section 4.7 on page 56 for more

information about mounting and field connections.

Page 38

DNR-X-1G Series RACKtangle and HalfRACK Systems

October 2018 www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

DNR-POWER-DC DNR-CPU-1000/-XX DNR-IO-FILLER

up to 6 I/O Boards

Chapter 3 30

The DNR-6-1G Series HalfRACK System

3.4.2 DNR-6-1G

Enclosure

Common

Components

Each DNR-6-1G chassis contains a power board (DNR-POWER-DC) with

status indicators and an external ON/OFF switch , an d a CPU bo ar d with a

dedicated GigE CPU and two Network Interface Control (NIC) ports, one for

controlling up to 6 I/O boards mounted in the enclosure and another for

diagnostics functions. Front-loading slots allow I/O boards to be quickly and

easily installed and removed, if needed.

Up to 6 DNR I/O boards can be installed in the chassis; DNR I/O boards are

functionally identical to the corresponding Cube-based DNA boards. The only

differences between RACK and Cube I/O boards are the mounting hardware.

The DNA version I/O boards are designed to stack in a Cube chassis. T he DNR

version I/O boards are designed to plug into the backplane of a RACK chassis.

Figure 3-5 Typical PowerDNR DNR-6 Board Placement

Table 3-1 Components in PowerDNR DNR-6 Enclosure