Transcend TS8GCFX500, TS16GCFX500, TS2GCFX500, TS4GCFX500 DATASHEET

T

S

2

G

~

1

6

G

C

F

X

5

0

0

T

S

2

G

~

1

6

G

C

F

X

5

T

S

2

G

~

1

6

G

C

F

X

5

0

0

0

0

CFast Card

Description

Transcend CFast cards are designed to satisfy high

performance requirements using a SATA 3Gb/s

interface. As a removable device, it is easier to plug and

remove in space-limited applications; such as

thin-clients or industrial PCs. Complaint with CFast 1.0

standard, CFast is your best choice as an embedded

SATA storage solution."

.

Placement

Features

• RoHS compliant

• CFast Specification Version 1.0 Compliant

• Power Supply: 3.3V±5%

• Operating Temperature: 0

• Storage Temperature: -40

• Humidity (Non condensation): 0% to 95%

• Built-in 8-bit/512Byte ECC (Error Correction Code)

functionality ensures highly reliable of data transfer.

• Global wear-leveling algorithm eliminate excessive write

operation and extends product life.

• Suppot StaticDataRefresh & EarlyRetirement

technology to monitor error bit level and react before

data is corrupted.

• Support S.M.A.R.T (Self-defined)

• Support Security Command

• Fully compatible with devices and OS that support the

SATA 3Gb/s standard

o

C to 70oC

o

C to 85oC

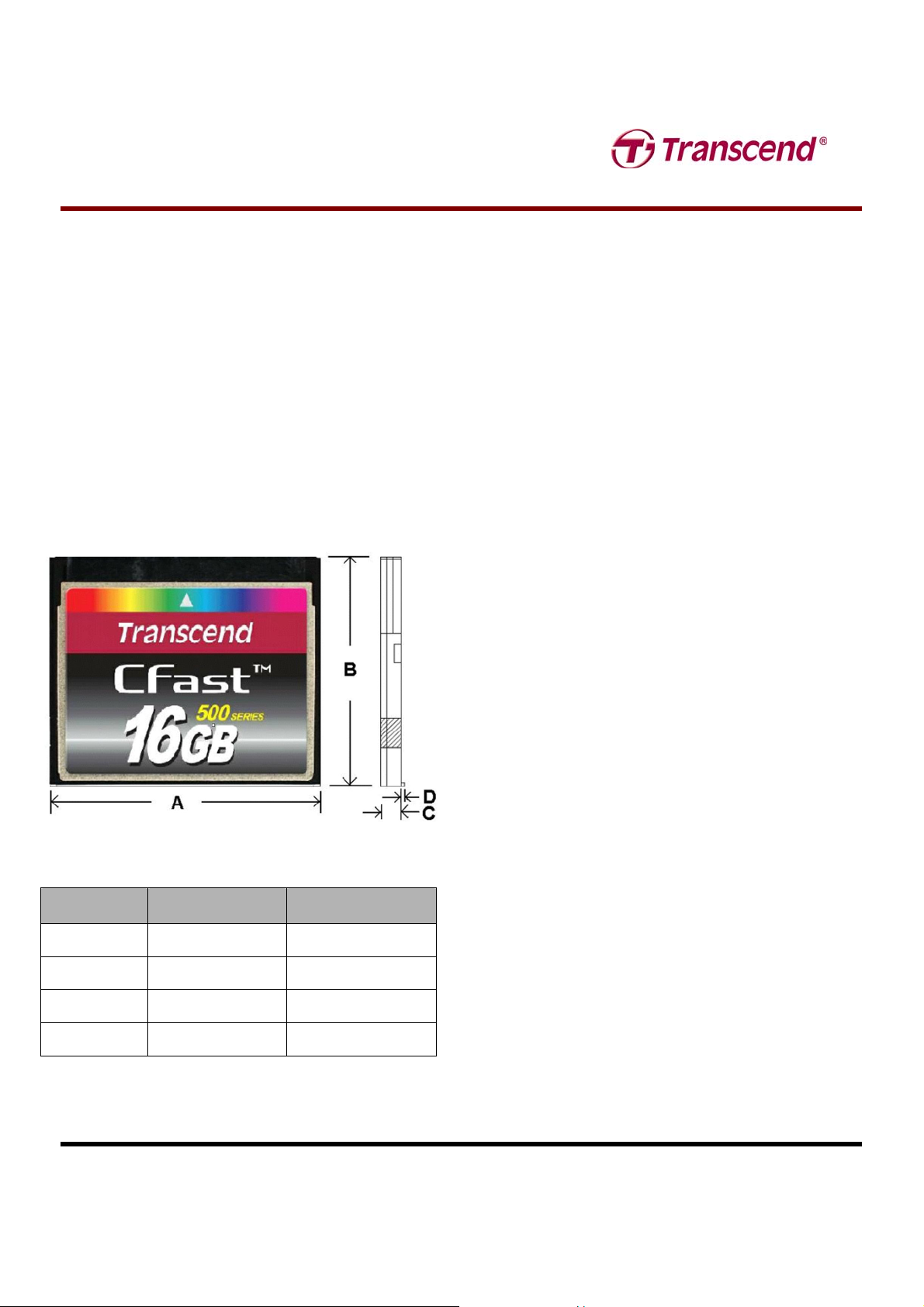

Dimensions

Side Millimeters Inches

A 42.8 1.685

B 36.4 1.433

C 3.3 0.13

D 0.6 0.02

Transcend Information Inc.

• Non-volatile SLC Flash Memory for outstanding data

retention

• Durability of Connector: 10,000 times

1

V0.5

T

S

2

G

~

1

6

T

S

2

G

T

S

2

Specifications

Physical Specification

Form Factor

Storage Capacities

Dimensions (mm)

Input Voltage

Weight

Connector

Environmental Specifications

G

~

~

1

1

6

6

G

G

G

C

C

C

Length

Width

Height

F

F

F

X

X

X

5

0

0

5

5

0

0

0

0

CFast

2GB~16 GB

42.8 ± 0.1

36.4 ± 0.15

3.3 ± 0.1

3.3V ± 5%

TBD

CFAST connector

CFast Card

Operating Temperature

Storage Temperature

Humidity

Regulations

Compliance

Performance

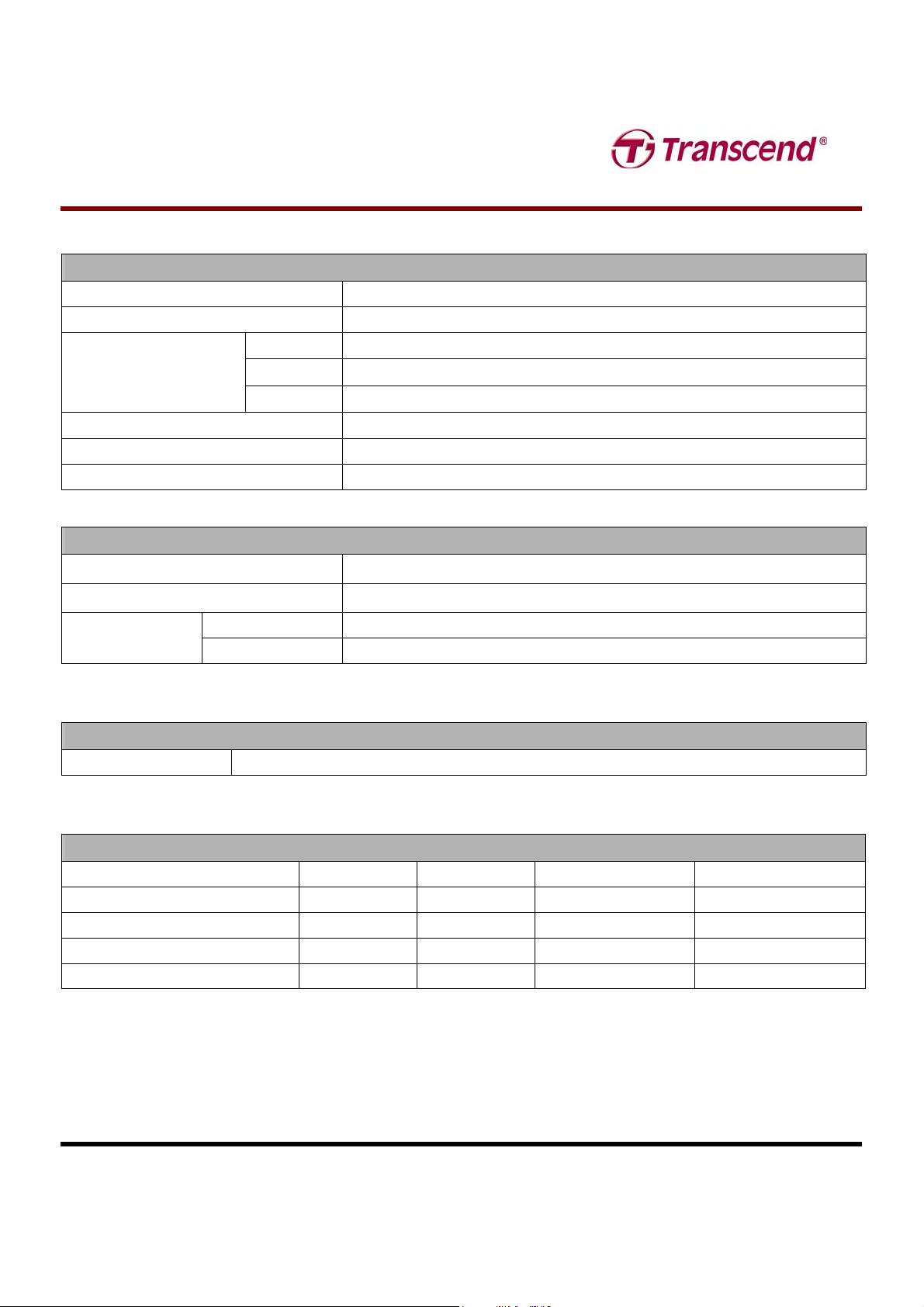

Model P/N Read Write Random Read Random Write

TS2GCFX500 56 MB/s 27MB/s 50 MB/s 8 MB/s

TS4GCFX500 56 MB/s 49MB/s 50 MB/s 12 MB/s

TS8GCFX500 102 MB/s 88MB/s 83MB/s 17 MB/s

TS16GCFX500 108 MB/s 91MB/s 89 MB/s 18 MB/s

Note: 25 ℃, test on ASUS P4S800-MX, 1GB RAM, Windows® XP Version 2002 SP2, benchmark utility HDBENCH

(version 3.4006), copied file 1GB.

Operating

Non-Operating

CE, FCC and BSMI

0 to 70

- 40

0% to 95% (Non-condensing)

0% to 95% (Non-condensing)

℃

℃ to 85 ℃

Transcend Information Inc.

2

V0.5

T

S

2

G

~

1

6

G

C

F

X

5

0

0

T

S

2

G

~

1

6

G

C

F

X

5

T

S

2

G

~

1

6

G

C

F

Actual Capacity

Model P/N User Max. LBA Cylinder Head Sector

TS2GCFX500 3,865,680 3,835 16 63

TS4GCFX500 7,732,368/ 7,671 16 63

TS8GCFX500 15,465,344 15,343 16 63

TS16GCFX500 30,932,992 16,383 15 63

Power Requirements

Input Voltage

Mode Max. (mA)

Write

Power Consumption

Read

Idle

(peak)

X

(peak)

(peak)

5

0

0

0

0

CFast Card

3.3V ± 5%

352

371

141

SHOCK & Vibration Test

Condition Standard

Mechanical Shock Test

Vibration Test

1500G, 0.5ms, 3 axis IEC 60068-2-27

20G (Peak-to-Peak)

20Hz to 2000Hz (Frequency)

IEC 60068-2-6

Transcend Information Inc.

3

V0.5

T

S

2

G

~

1

6

G

C

F

X

5

0

0

T

S

2

G

~

1

6

G

C

F

X

5

T

S

2

G

~

1

6

G

C

F

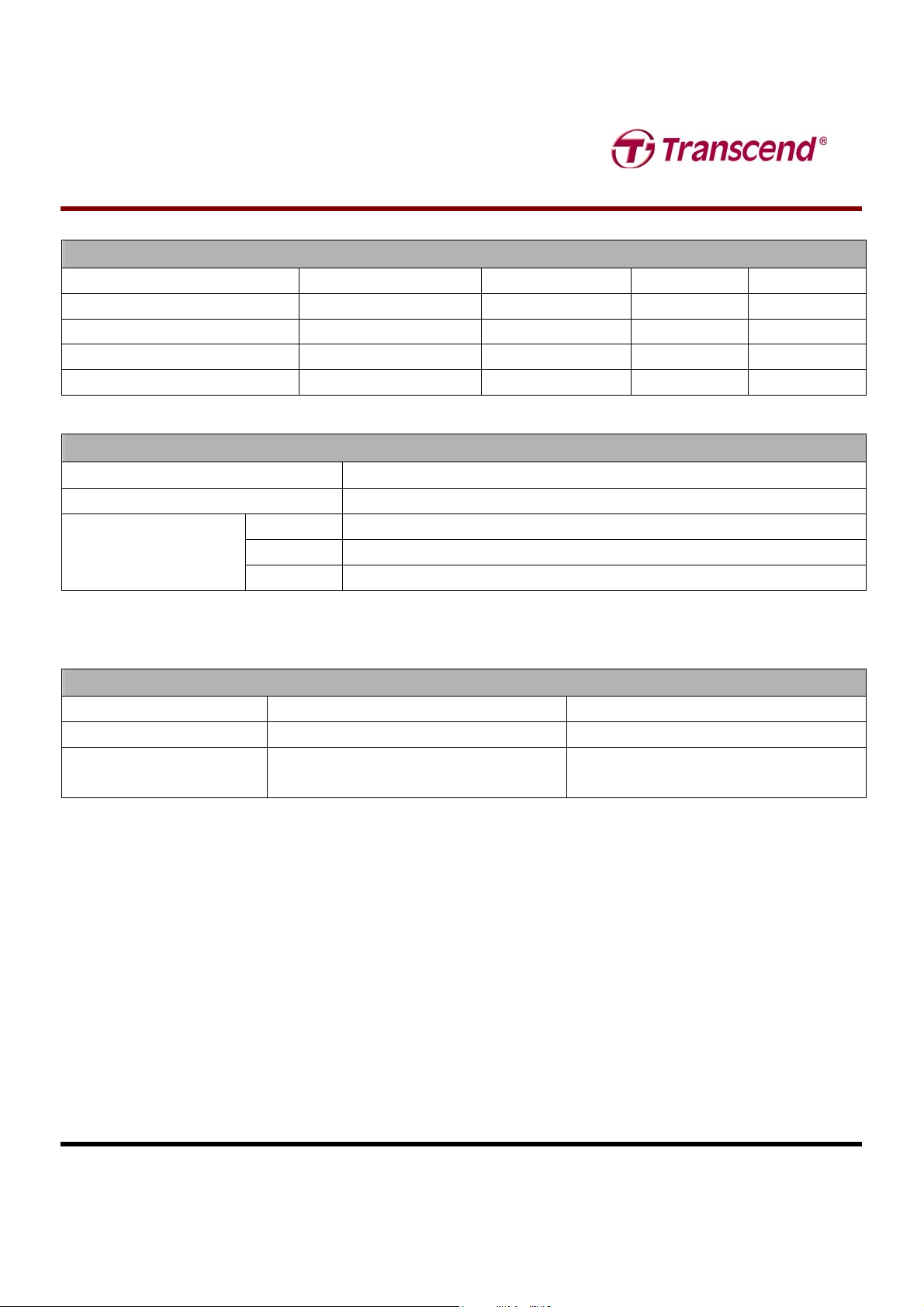

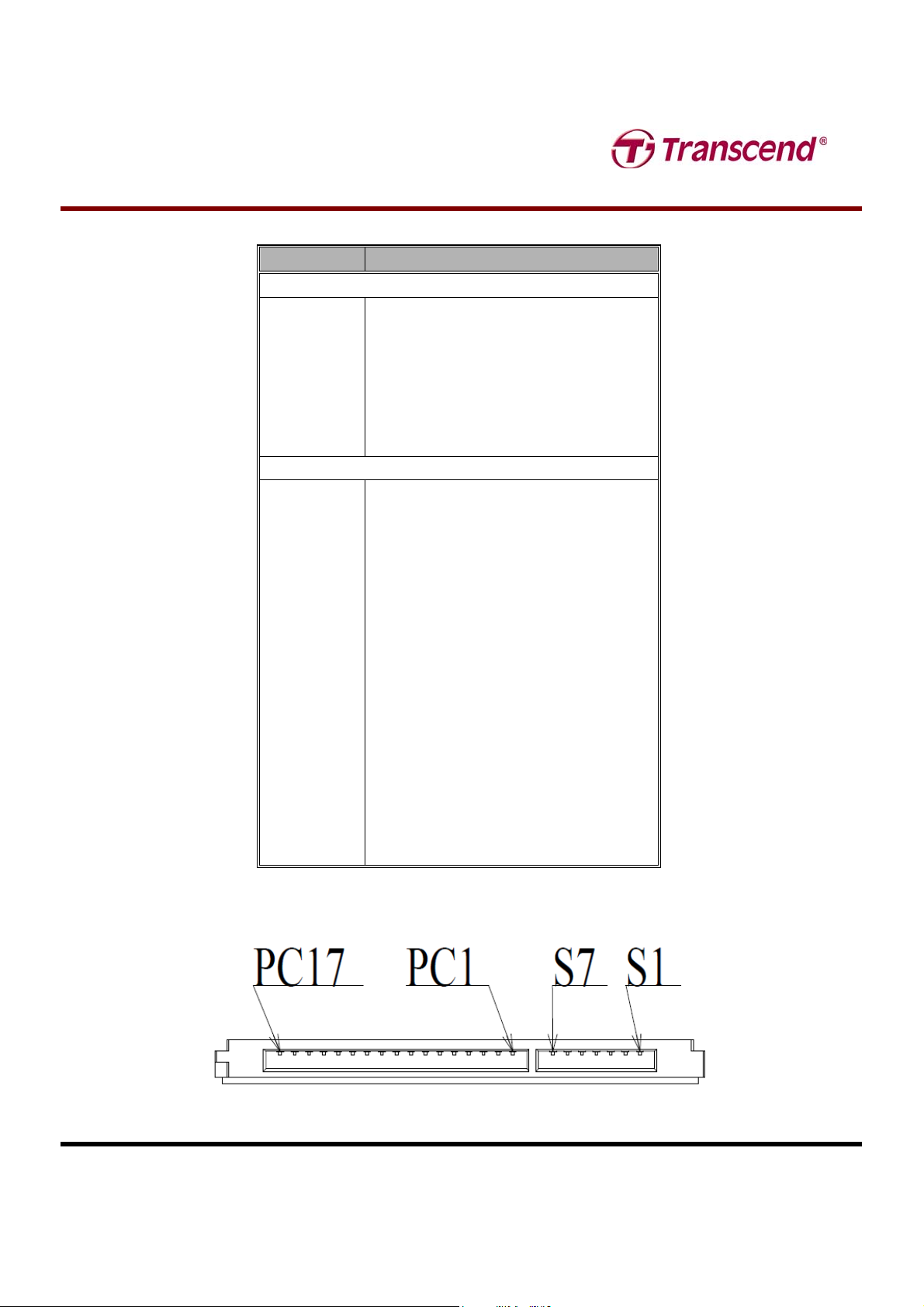

Package Dimensions

Below figure illustrates the Transcend CFastTM. All dimensions are in mm.

X

5

0

0

0

0

CFast Card

Transcend Information Inc.

4

V0.5

T

S

2

G

T

S

2

T

S

Pin Assignments

2

G

G

~

~

~

1

1

1

6

6

6

G

G

G

C

F

X

5

0

0

C

F

X

5

C

F

Pin No. Pin Name

PC1 CDI

PC2 GND

PC3 NC

PC4 NC

PC5 NC

PC6 NC

PC7 GND

PC8 NC

PC9 NC

PC10 NC

PC11 NC

PC12 NC

PC13 3.3V

PC14 3.3V

PC15 GND

PC16 GND

PC17 CDO

0

X

5

0

S1 GND

S2 A+

S3 AS4 GND

S5 BS6 B+

S7 GND

0

0

7-pin Signal Segment

17-pin Power Segment

CFast Card

Pin Layout

Transcend Information Inc.

5

V0.5

T

S

2

G

T

S

2

T

S

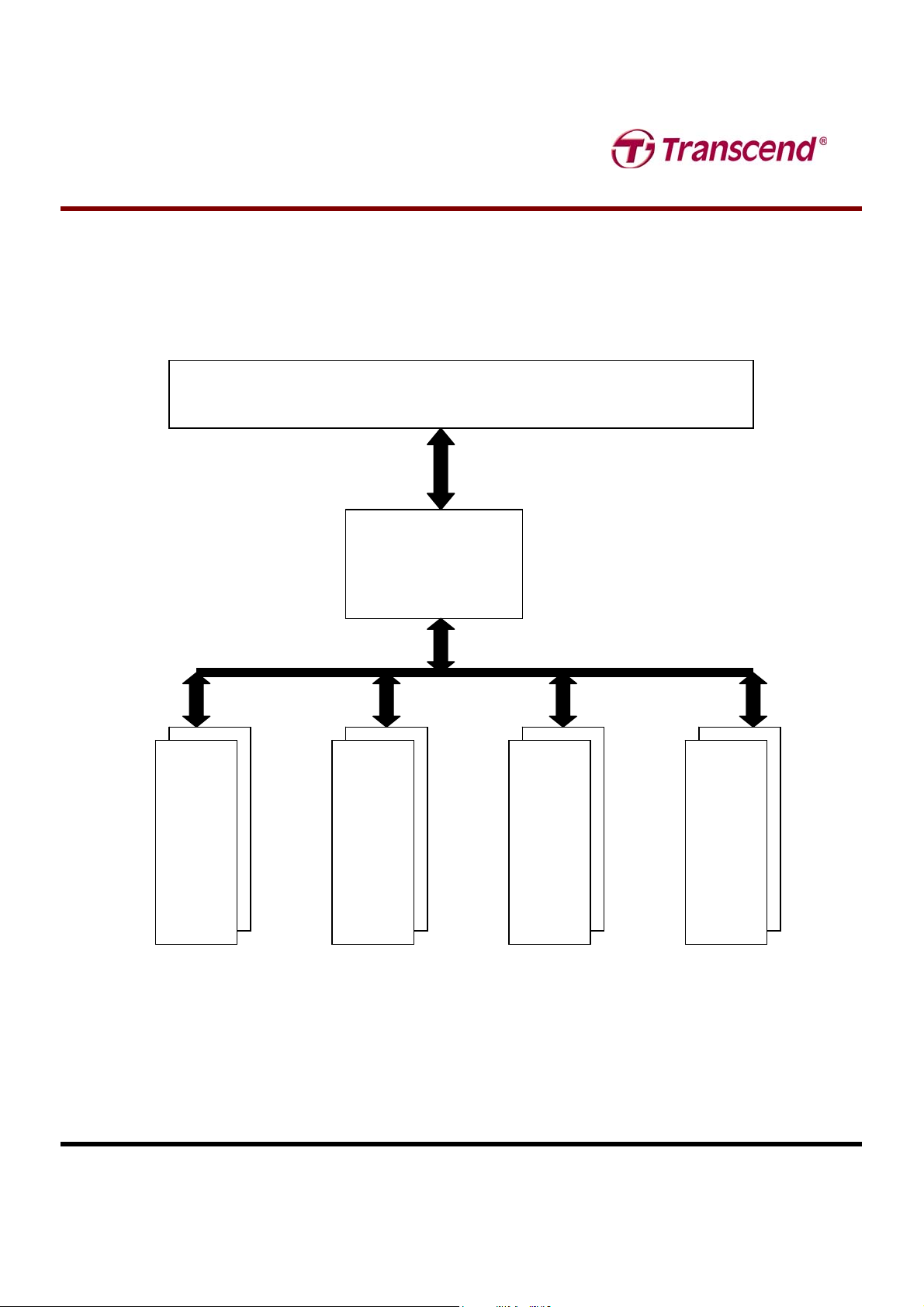

Block Diagram

2

G

G

~

~

~

1

1

1

6

6

6

G

G

G

C

C

C

F

F

F

X

X

X

5

0

0

5

5

0

0

0

0

CFASTTM Interface

SATA SSD CTL

CFast Card

Flash

Transcend Information Inc.

Flash

Flash

6

Flash

V0.5

T

S

2

G

~

1

6

G

C

F

X

5

0

0

T

S

2

G

~

1

6

G

C

F

X

5

T

S

2

G

~

1

6

G

C

F

Reliability

Wear-Leveling algorithm

The controller supports static/dynamic wear leveling. When the host writes data, the controller will find and use the block

with the lowest erase count among the free blocks. This is known as dynamic wear leveling. When the free blocks' erase

count is higher than a threshold value plus data blocks', it will activate the static wear leveling, replacing the not so

frequently used user blocks with the high erase count free blocks.

ECC algorithm

Using 8bit BCH Error Correction Code with ea ch channel, the controller can co rrect 8 random bits per 512 b yte data

sector for SLC NAND flash. The hardware executes parity generation and error detection/correction features.

StaticDataRefresh Technology

Normally, ECC engine corrections are taken plac e without affecting the host normal opera tio ns . As time pa ss e s by, the

number of error bits accumulated in the read transaction exceeds the correcting capability of the ECC engine, resu lting

in corrupted data being sent to the host. To prevent this, the controller monitors the error bit levels at each read

X

5

0

0

0

0

CFast Card

operation; when it reaches the preset threshold value, the controller automatically performs data refresh to “restore” the

correct charge levels in the cell. This implementation practically restores the data to its orig inal, error-free state, and

hence, lengthening the life of the data.

EarlyRetirement Technology

The StaticDataRefresh feature functions well when the cells in a block are still healthy. As the block ages over time, it

cannot reliably store charge anymore, EarlyRetirement enters the scene. EarlyRetirement works by moving the static

data to another block (a health block) before the previously used block becomes completely incapable of holding

charges for data. When the charge loss error level exceeds another threshold value (higher from that for

StaticDataRefresh), the controller automatically moves its data to anothe r block. In addition, the original block is then

marked as a bad block, which prevents its further use, and thus the block enters the state of “EarlyRetirement.”

Note that, through this proc ess, the incorr ect data are detected and effectively correc ted by the ECC eng ine, thus the

data in the new block is stored error-free.

Transcend Information Inc.

7

V0.5

T

S

2

G

~

1

6

G

C

F

X

5

0

0

T

S

2

G

~

1

6

G

C

F

X

5

T

S

2

G

~

1

6

G

C

F

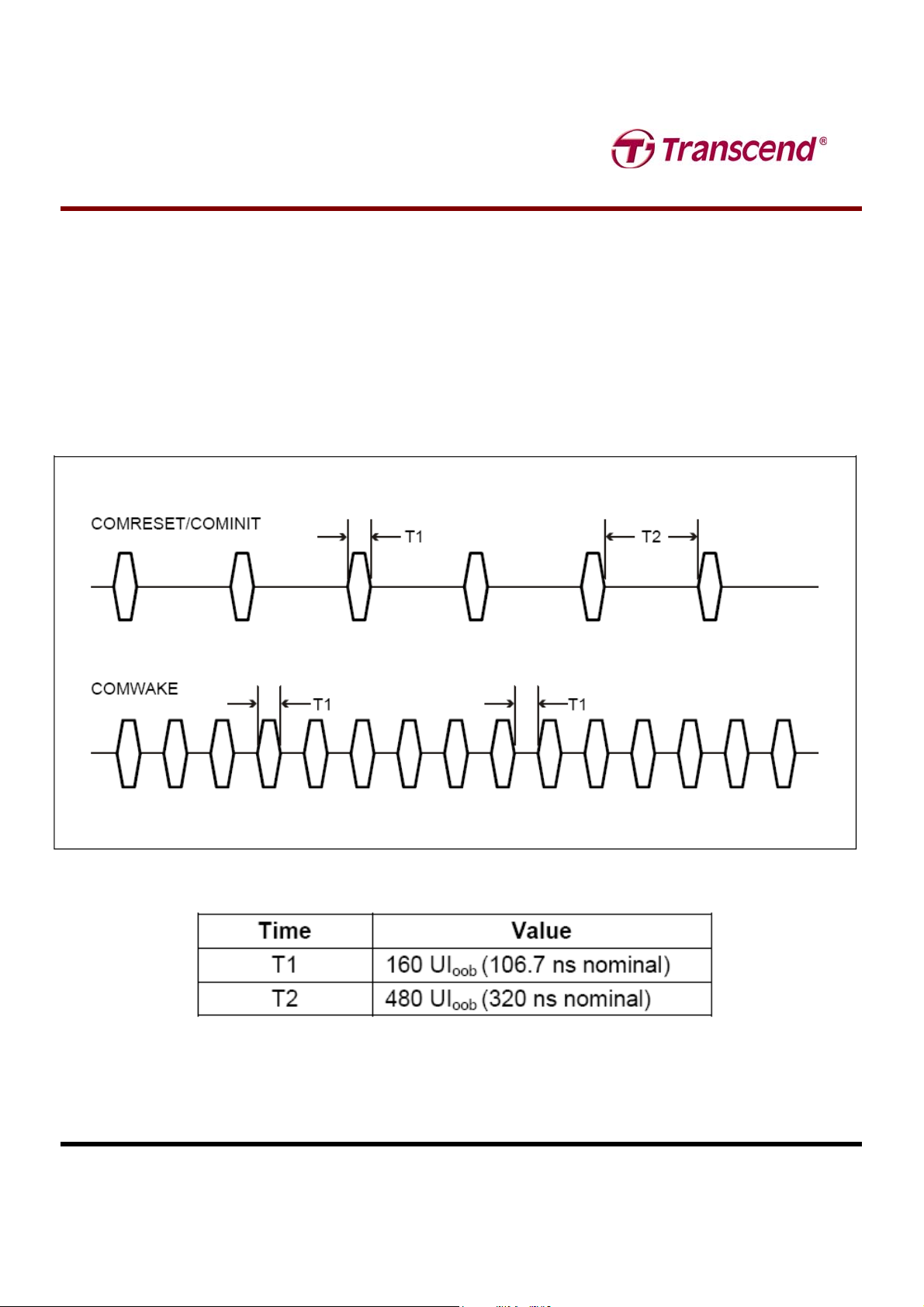

CFastTM Interface

Out of bank signaling

There shall be three Out Of Band (OOB) signals used/dete cted by the Phy: COMR ESET, COMINIT, and CO MWAKE.

COMINIT, COMRESET and COMWAKE OOB signaling shall be achieved by transmission of either a burst of four Gen1

P primitives or a burst composed of four Gen1 Dwords with each Dword composed of four D24.3 characters, each

ALIGN

X

5

0

0

0

0

CFast Card

burst having a duration of 160 UI

as depicted in Figure 4 and Table 2.

OOB. Each burst is followed by idle periods (at common-mode levels), having durations

Transcend Information Inc.

Figure 4 : OOB signals

Table 2 : OOB signal times

8

V0.5

Loading...

Loading...