Toshiba TXZ Reference Manual

1 / 107

© 2017-2021

TXZ/TXZ+ Family

Advanced Vector Engine Plus

32-bit RISC Microcontroller

TXZ/TXZ+ Family

Reference Manual

Advanced Vector Engine Plus

(A-VE+-B)

Revision 3.1

2021-02

Toshiba Electronic Devices & Storage Corporation

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

2 / 107

Advanced Vector Engine Plus

Contents

Preface ................................................................................................................................................................. 7

Related document ..................................................................................................................................................... 7

Conventions .............................................................................................................................................................. 8

Terms and Abbreviation .......................................................................................................................................... 10

1. Outlines ....................................................................................................................................................... 11

2. Configuration ............................................................................................................................................... 12

2.1. Configuration of the VE .................................................................................................................................... 12

2.2. Interaction between the VE, PMD, and ADC ................................................................................................... 14

3. Description of Operations ........................................................................................................................... 15

3.1. Clock Supply .................................................................................................................................................... 15

3.2. Schedule Management .................................................................................................................................... 15

3.2.1. Schedule Control ........................................................................................................................................................ 17

3.2.2. Start Control ............................................................................................................................................................... 19

3.2.3. Interrupt Control .......................................................................................................................................................... 20

3.3. Description of Tasks ........................................................................................................................................ 21

3.3.1. Current Control (Task 5) ............................................................................................................................................. 23

3.3.2. SIN/COS calculation (Task 6) ..................................................................................................................................... 29

3.3.3. Output Voltage Transformation (Coordinate Axis Transformation/Phase Transformation) ......................................... 31

3.3.3.1. Output coordinate axis transformation (Task 7) ............................................................................................................. 31

3.3.3.2. Output phase transformation 1 (Space vector transformation) (Task 8) ........................................................................ 32

3.3.3.3. Output phase transformation 2 (Inverse Clarke transformation) (Task 11) .................................................................... 34

3.3.4. Output Control ............................................................................................................................................................ 36

3.3.4.1. Output control 1 (Task 0) ............................................................................................................................................... 36

3.3.4.2. Output control 2 (Task 9) ............................................................................................................................................... 42

3.3.5. Trigger Generation (Task 1) ....................................................................................................................................... 47

3.3.6. Input Process.............................................................................................................................................................. 49

3.3.6.1. Input process 1 (Task 2) ................................................................................................................................................ 49

3.3.6.2. Input process 2 (Task 10) .............................................................................................................................................. 52

3.3.7. Input Current Transformation (Phase Transformation/Coordinate Axis Transformation) ............................................ 56

3.3.7.1. Input phase transformation (Task 3) .............................................................................................................................. 56

3.3.7.2. Input coordinate axis transformation (Task 4)................................................................................................................ 57

3.3.8. Other Tasks ................................................................................................................................................................ 58

3.3.8.1. ATAN2 (Arctangent function 2) (Task 12) ...................................................................................................................... 58

3.3.8.2. SQRT (Square root function) (Task 13) ......................................................................................................................... 59

4. Registers ..................................................................................................................................................... 60

4.1. List of Registers ............................................................................................................................................... 60

4.2. Details of VE Control Registers ....................................................................................................................... 63

4.2.1. [VExEN] (VE Operation Enable/Disable Register) ...................................................................................................... 63

4.2.2. [VExCPURUNTRG] (CPU Start Trigger Selection Register) ...................................................................................... 63

4.2.3. [VExTASKAPP] (Task Selection Register) ................................................................................................................. 64

4.2.4. [VExACTSCH] (Operation Schedule Selection Register) ........................................................................................... 65

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

3 / 107

Advanced Vector Engine Plus

4.2.5. [VExREPTIME] (Operation Schedule Repeat Number Selection Register) ................................................................ 65

4.2.6. [VExTRGMODE] (Start Trigger Mode Setting Register) ............................................................................................. 65

4.2.7. [VExERRINTEN] (Error Interrupt Enable/Disable Setting Register) ............................................................................ 66

4.2.8. [VExCOMPEND] (VE Forcible Termination Register) ................................................................................................. 66

4.2.9. [VExERRDET] (Error Detection Register) .................................................................................................................. 66

4.2.10. [VExSCHTASKRUN] (Schedule Operation Status/Ongoing Task Number Register) ............................................... 67

4.2.11. [VExTMPREG0] (Temporary Registers 0) ................................................................................................................ 67

4.3. Details of Dedicated Registers ........................................................................................................................ 68

4.3.1. [VExMCTLF] (Status Register) ................................................................................................................................... 68

4.3.2. [VExMODE] (Task Control Mode Register) ................................................................................................................ 69

4.3.3. [VExFMODE] (Flow Control Register) ........................................................................................................................ 71

4.3.4. [VExTPWM] (PWM Period Rate setting Register) ...................................................................................................... 72

4.3.5. [VExOMEGA] (Rotational Speed setting Register) ..................................................................................................... 72

4.3.6. [VExTHETA] (Motor Phase setting Register) .............................................................................................................. 73

4.3.7. d-axis/q-axis Current Reference setting Registers ..................................................................................................... 73

4.3.7.1. [VExIDREF] (d-axis Current Reference setting Register) .............................................................................................. 73

4.3.7.2. [VExIQREF] (q-axis Current Reference setting Register) .............................................................................................. 73

4.3.8. d-axis/q-axis Voltage setting Registers ....................................................................................................................... 74

4.3.8.1. [VExVD] (d-axis Voltage setting Register) ..................................................................................................................... 74

4.3.8.2. [VExVQ] (q-axis Voltage setting Register) ..................................................................................................................... 74

4.3.8.3. [VExVDQ] (Voltage Scalar Register) ............................................................................................................................. 74

4.3.8.4. [VExVSLIM] (Voltage Scalar Limitation Register) .......................................................................................................... 75

4.3.9. Coefficient Registers for PI control ............................................................................................................................. 76

4.3.9.1. [VExCIDKI] (d-axis Current Integral Coefficient setting Register for PI control) ............................................................. 76

4.3.9.2. [VExCIDKP] (d-axis Current Proportional Coefficient setting Register for PI control) .................................................... 76

4.3.9.3. [VExCIDKG] (d-axis Coefficient Range setting Register for PI control) .......................................................................... 76

4.3.9.4. [VExCIQKI] (q-axis Current Integral Coefficient setting Register for PI control) ............................................................. 77

4.3.9.5. [VExCIQKP] (q-axis Current Proportional Coefficient setting Register for PI control) .................................................... 77

4.3.9.6. [VExCIQKG] (q-axis Coefficient Range setting Register for PI control) ......................................................................... 77

4.3.9.7. [VExVDIH] (d-axis Voltage Integral component Store Register for PI control (Upper)) .................................................. 78

4.3.9.8. [VExVDILH] (d-axis Voltage Integral component Store Register for PI control (Lower)) ................................................ 78

4.3.9.9. [VExVQIH] (q-axis Voltage Integral component Store Register for PI control (Upper)) .................................................. 78

4.3.9.10. [VExVQILH] (q-axis Voltage Integral component Store Register for PI control (Lower)) .............................................. 78

4.3.10. [VExPIOLIM] (Output Limitation Register for PI control) ........................................................................................... 78

4.3.11. [VExFPWMCHG] (PWM Switching Speed setting Register) .................................................................................... 79

4.3.12. [VExPWMOFS] (PWM Shift 2 Offset Register) ......................................................................................................... 79

4.3.13. SIN/COS Registers ................................................................................................................................................... 80

4.3.13.1. [VExCOS] (Cosine value Register of θ) ....................................................................................................................... 80

4.3.13.2. [VExSIN] (Sine value Register of θ)............................................................................................................................. 80

4.3.13.3. [VExCOSM] (Previous Cosine value Register) ............................................................................................................ 80

4.3.13.4. [VExSINM] (Previous Sine value Register) .................................................................................................................. 80

4.3.14. Sector Information Registers .................................................................................................................................... 81

4.3.14.1. [VExSECTOR] (Sector Information Register) .............................................................................................................. 81

4.3.14.2. [VExSECTORM] (Previous Sector Information Register) ............................................................................................ 81

4.3.15. 3-phase Current Registers ....................................................................................................................................... 82

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

4 / 107

Advanced Vector Engine Plus

4.3.15.1. [VExIAO] (a-phase Zero-Current Register) .................................................................................................................. 82

4.3.15.2. [VExIBO] (b-phase Zero-Current Register) .................................................................................................................. 82

4.3.15.3. [VExICO] (c-phase Zero-Current Register) .................................................................................................................. 82

4.3.15.4. [VExIAADC] (ADC Conversion Result Register for a-phase Current) .......................................................................... 83

4.3.15.5. [VExIBADC] (ADC Conversion Result Register for b-phase Current) .......................................................................... 83

4.3.15.6. [VExICADC] (ADC Conversion Result Register for c-phase Current) .......................................................................... 83

4.3.15.7. [VExIA] (a-phase Current Register) ............................................................................................................................. 83

4.3.15.8. [VExIB] (b-phase Current Register) ............................................................................................................................. 84

4.3.15.9. [VExIC] (c-phase Current Register) ............................................................................................................................. 84

4.3.16. DC Supply Voltage Registers ................................................................................................................................... 85

4.3.16.1. [VExVDC] (DC Supply Voltage Register) .................................................................................................................... 85

4.3.16.2. [VExVDCL] (DC2 Supply Voltage Register)................................................................................................................. 85

4.3.17. d-axis/q-axis Current Registers ................................................................................................................................ 86

4.3.17.1. [VExID] (d-axis Current Register) ................................................................................................................................ 86

4.3.17.2. [VExIQ] (q-axis Current Register) ................................................................................................................................ 86

4.3.18. [VExTADC] (ADC Conversion Time setting Register) .............................................................................................. 87

4.3.19. 3-phase PWM Duty Registers .................................................................................................................................. 88

4.3.19.1. [VExCMPU] (U-phase PWM Duty Register) ................................................................................................................ 88

4.3.19.2. [VExCMPV] (V-phase PWM Duty Register)................................................................................................................. 88

4.3.19.3. [VExCMPW] (W-phase PWM Duty Register) ............................................................................................................... 88

4.3.19.4. [VExMINPLS] (Minimum Pulse Width setting Register) ............................................................................................... 89

4.3.20. PWM Output Limitation Registers ............................................................................................................................. 90

4.3.20.1. [VExPWMMAX] (PWM Upper-Limit setting Register) .................................................................................................. 90

4.3.20.2. [VExPWMMIN] (PWM Lower-Limit setting Register) ................................................................................................... 90

4.3.21. [VExOUTCR] (PMD Output Control Register) .......................................................................................................... 91

4.3.22. Trigger Generation Registers ................................................................................................................................... 93

4.3.22.1. [VExTRGCRC] (Synchronous Trigger Correction setting Register) ............................................................................. 93

4.3.22.2. [VExTRGCMP0] (PMD Trigger 0 Timing setting Register) .......................................................................................... 93

4.3.22.3. [VExTRGCMP1] (PMD Trigger 1 Timing setting Register) .......................................................................................... 93

4.3.22.4. [VExTRGSEL] (Synchronous Trigger Selection setting Register) ................................................................................ 94

4.3.23. [VExEMGRS] (EMG release Register) ..................................................................................................................... 94

4.3.24. [VExDELTA] (Current Declination Angle Register) ................................................................................................... 94

4.3.25. Motor Constant Registers ......................................................................................................................................... 95

4.3.25.1. [VExCPHI] (Motor Interlinkage Magnetic Flux Register) .............................................................................................. 95

4.3.25.2. [VExCLD] (Motor d-axis Inductance Register) ............................................................................................................. 95

4.3.25.3. [VExCLQ] (Motor q-axis Inductance Register) ............................................................................................................. 95

4.3.25.4. [VExCR] (Motor Resistance Register) ......................................................................................................................... 95

4.3.25.5. [VExCPHIG] (Motor Magnetic Flux Range setting Register) ........................................................................................ 96

4.3.25.6. [VExCLG] (Motor Inductance Range setting Register) ................................................................................................ 96

4.3.25.7. [VExCRG] (Motor Resistance Range setting Register) ................................................................................................ 96

4.3.26. [VExVDE] (d-axis Voltage Register for Non-interference Control) ............................................................................ 97

4.3.27. [VExVQE] (q-axis Voltage Register for Non-interference Control) ............................................................................ 97

4.3.28. [VExDTC] (Dead Time Compensation Register) ...................................................................................................... 97

4.3.29. [VExHYS] (Hysteresis Width Register for Current Polarity Determination) ............................................................... 97

4.3.30. [VExHYS2] (Hysteresis Width Register 2 for Current Polarity Determination) .......................................................... 98

4.3.31. [VExDTCS] (Dead Time Compensation Control/Status Register) ............................................................................ 98

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

5 / 107

Advanced Vector Engine Plus

4.3.32. [VExTHTCLP] (Clipped Phase value setting Register) ............................................................................................. 99

4.3.33. 2-phase Voltage Registers ....................................................................................................................................... 99

4.3.33.1. [VExVALPHA] (α-phase Voltage Register) .................................................................................................................. 99

4.3.33.2. [VExVBETA] (β-phase Voltage Register) .................................................................................................................... 99

4.3.34. 3-phase Voltage Duty Registers ............................................................................................................................. 100

4.3.34.1. [VExVDUTYA] (a-phase Voltage Duty Register) ....................................................................................................... 100

4.3.34.2. [VExVDUTYB] (b-phase Voltage Duty Register) ....................................................................................................... 100

4.3.34.3. [VExVDUTYC] (c-phase Voltage Duty Register) ....................................................................................................... 100

4.3.35. 2-phase Current Registers ..................................................................................................................................... 101

4.3.35.1. [VExIALPHA] (α-phase Current Register) .................................................................................................................. 101

4.3.35.2. [VExIBETA] (β-phase Current Register) .................................................................................................................... 101

4.3.36. [VExVDELTA] (Voltage Declination Angle Register) .............................................................................................. 101

4.3.37. [VExVDCRC] (d-axis Voltage Correction Register) ................................................................................................ 101

4.3.38. [VExVQCRC] (q-axis Voltage Correction Register) ................................................................................................ 102

5. Precautions ............................................................................................................................................... 103

6. Revision History ........................................................................................................................................ 104

RESTRICTIONS ON PRODUCT USE ............................................................................................................. 107

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

6 / 107

Advanced Vector Engine Plus

List of Figures

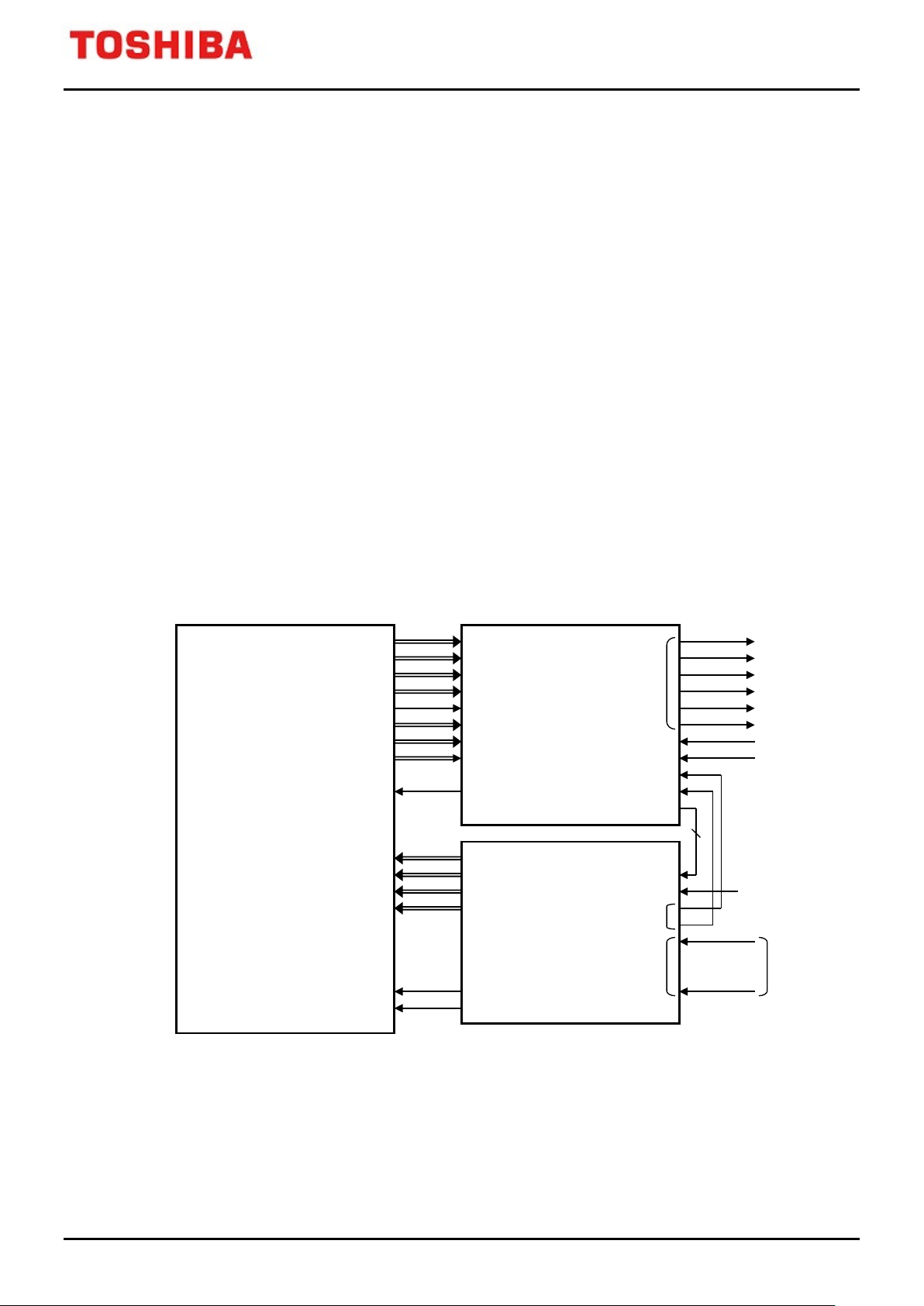

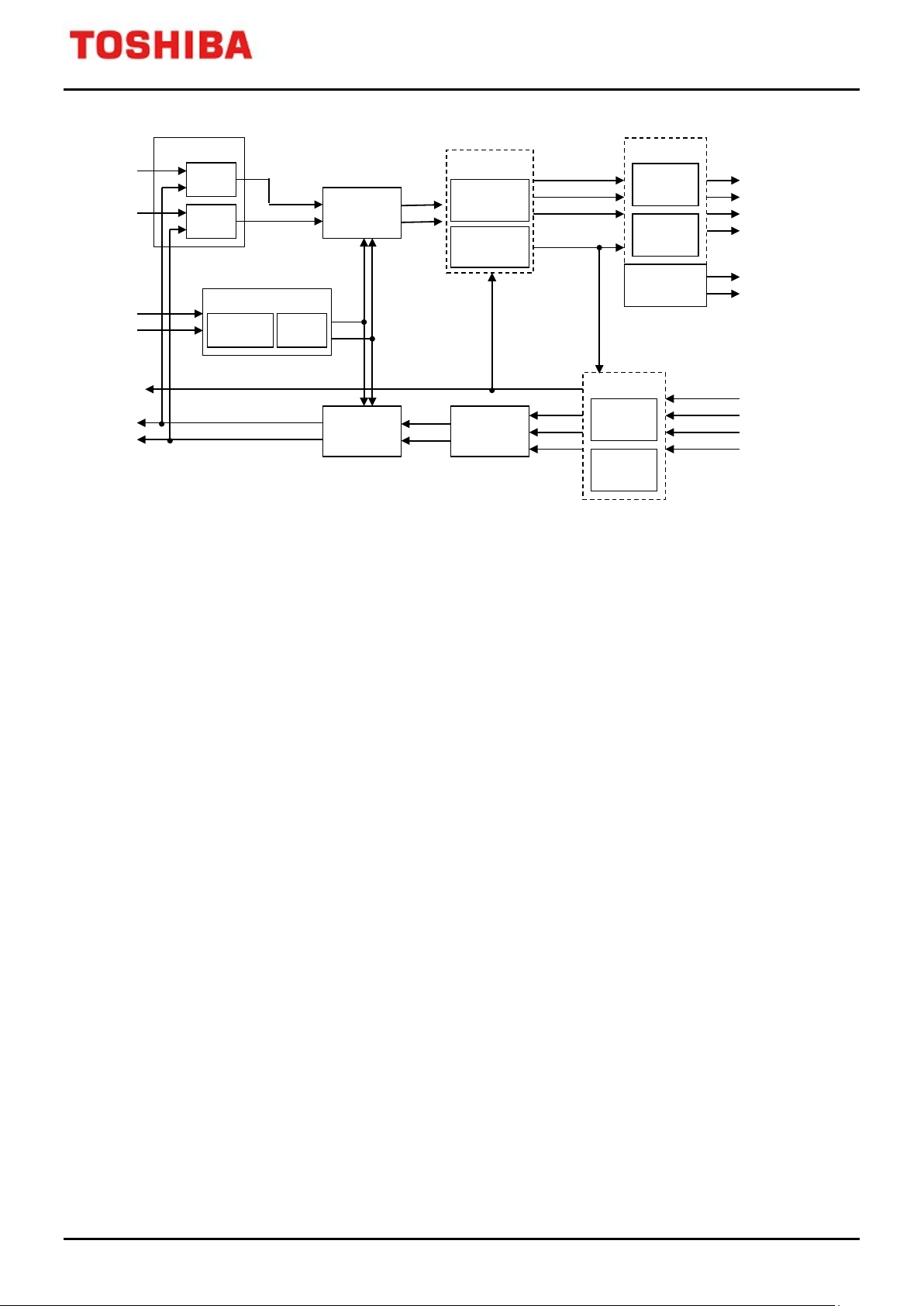

Figure 2.1 Block diagram of VE ............................................................................................................... 12

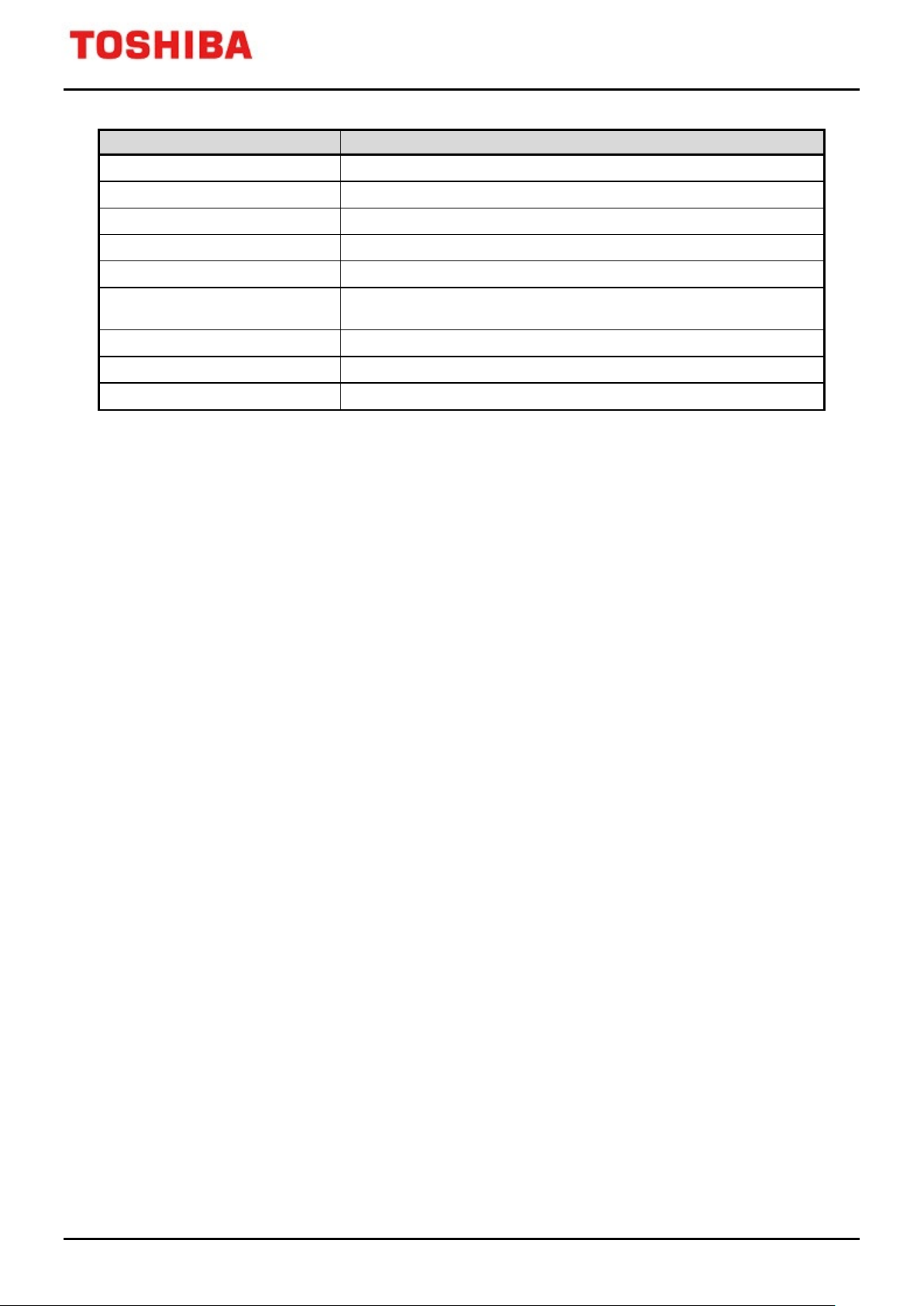

Figure 2.2 Connection diagram of VE and peripherals ............................................................................ 14

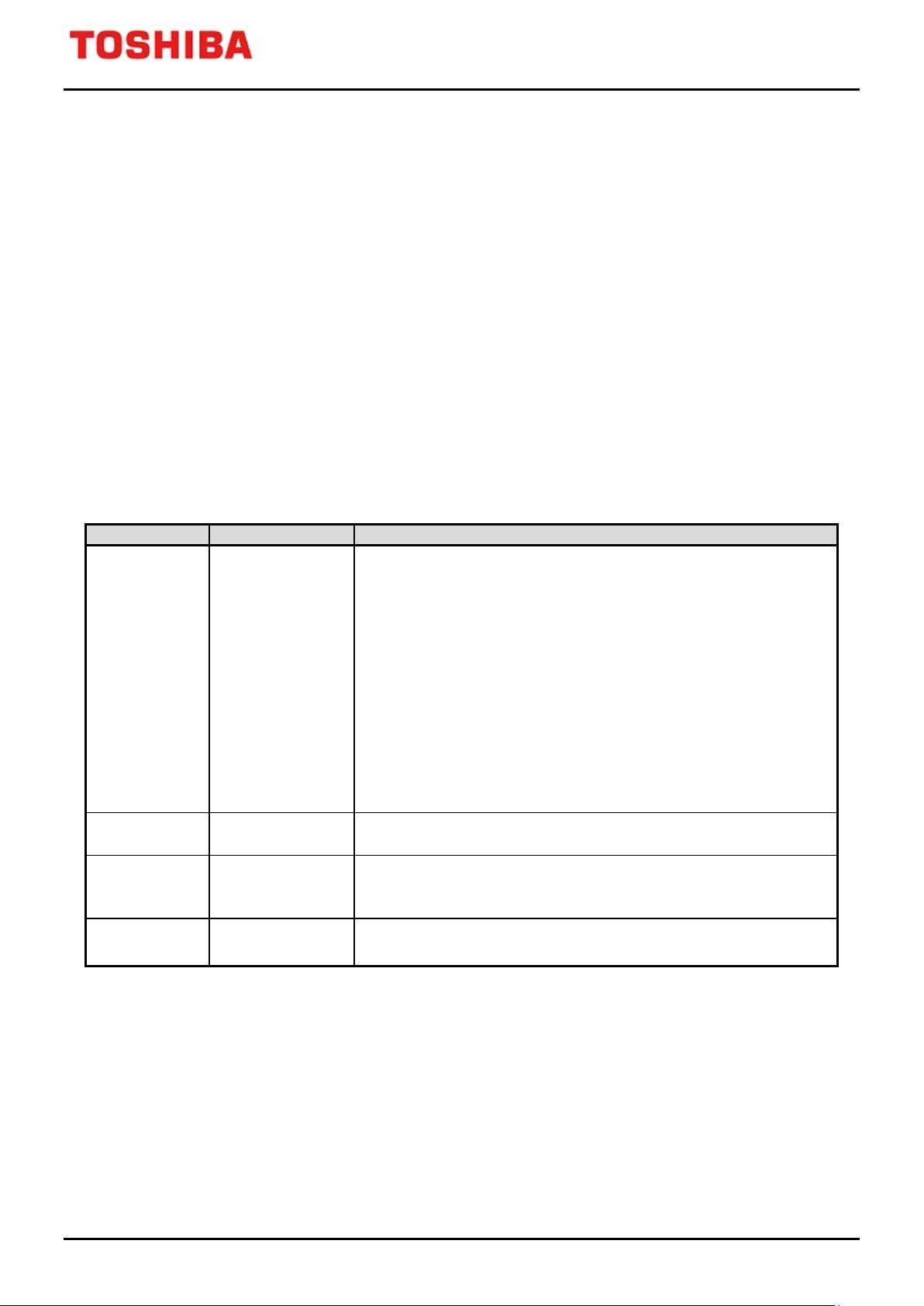

Figure 3.1 Example of Motor Control Operation Status Flowchart .......................................................... 15

Figure 3.2 Operation schedule flowchart ................................................................................................. 18

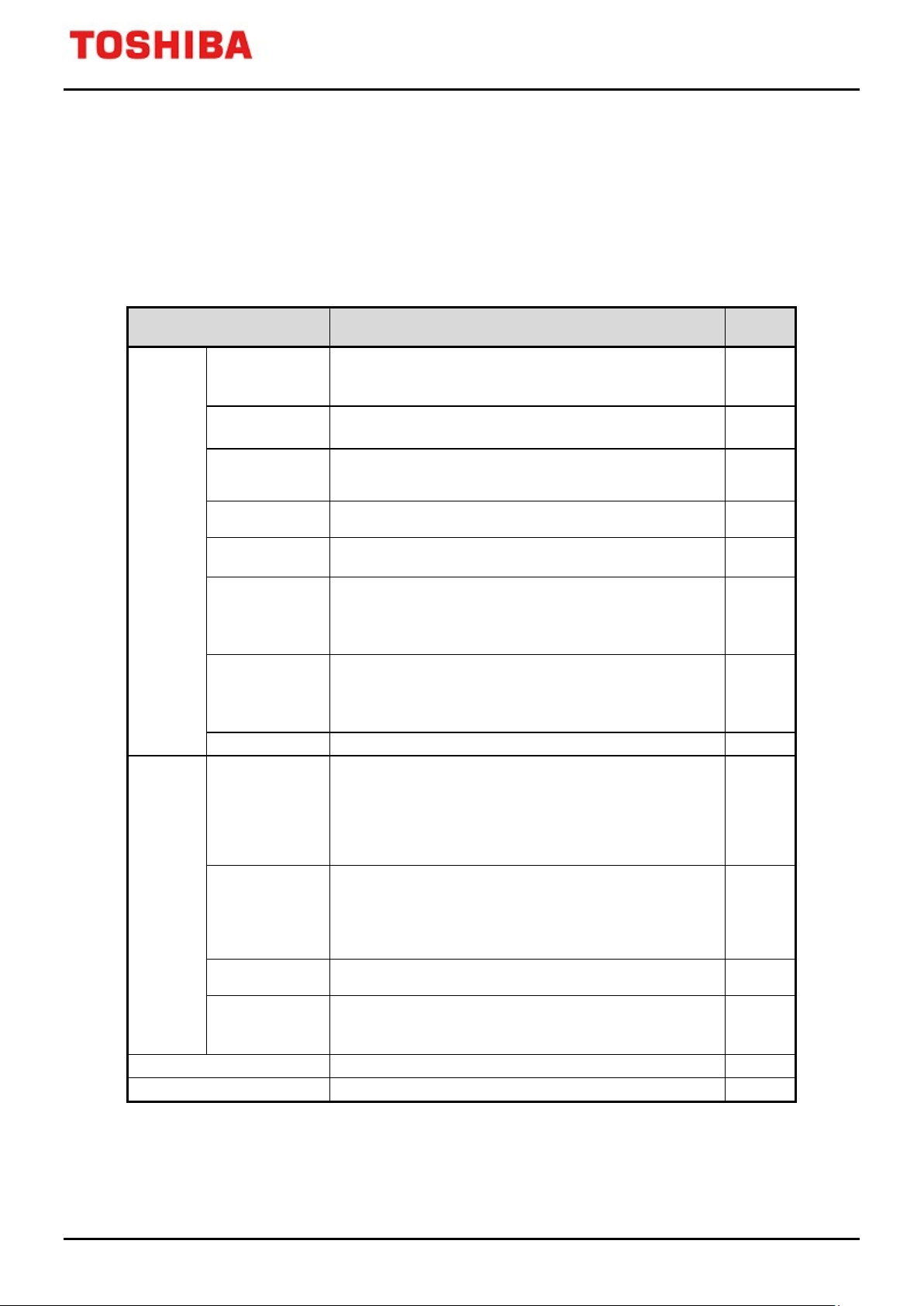

Figure 3.3 Relationship diagram of tasks ................................................................................................. 22

Figure 4.1 [VExVDC]/[VExVDCL] store register ...................................................................................... 70

Figure 4.2 ADC conversion time .............................................................................................................. 87

List of Tables

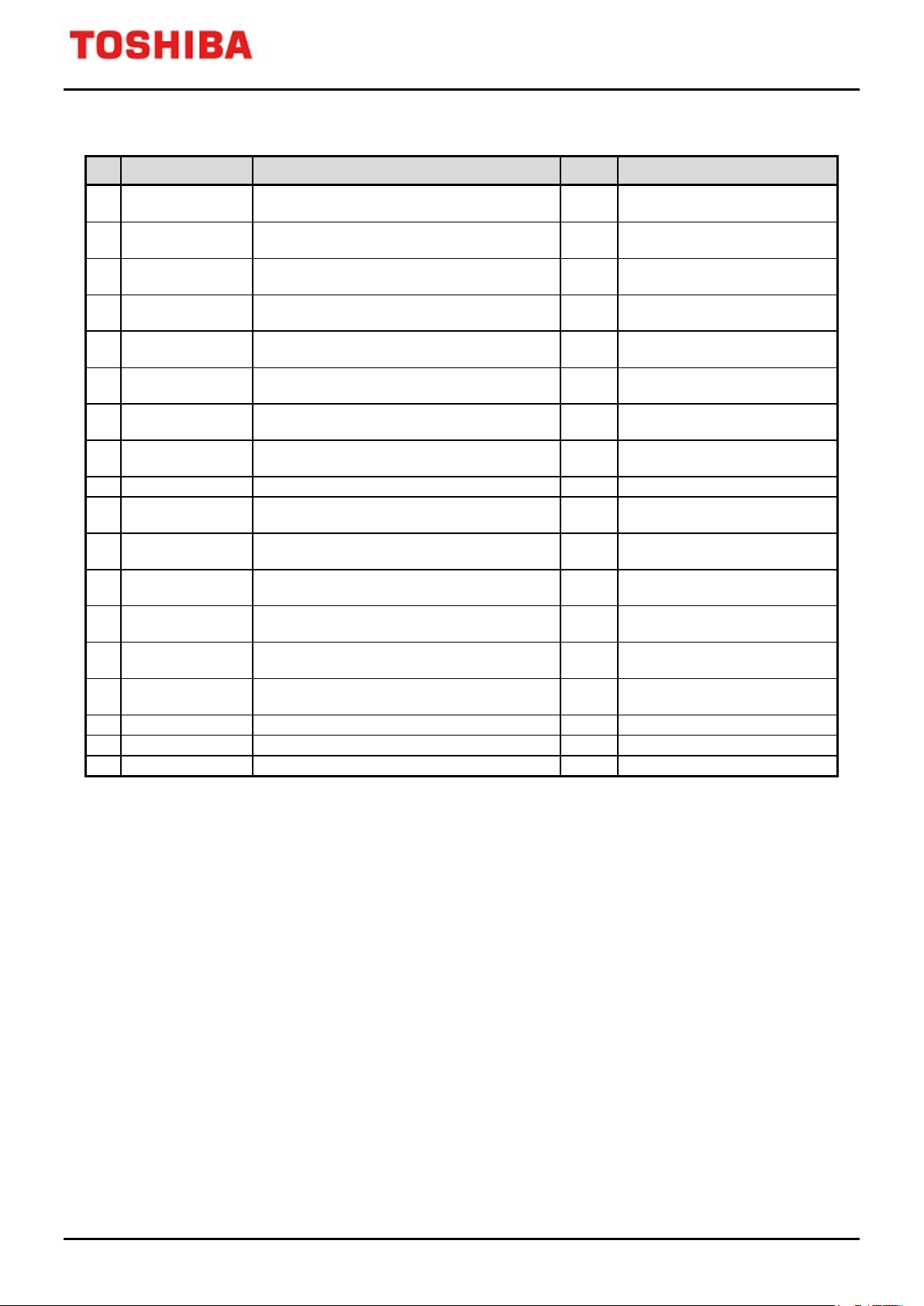

Table 2.1 List of signals ........................................................................................................................... 13

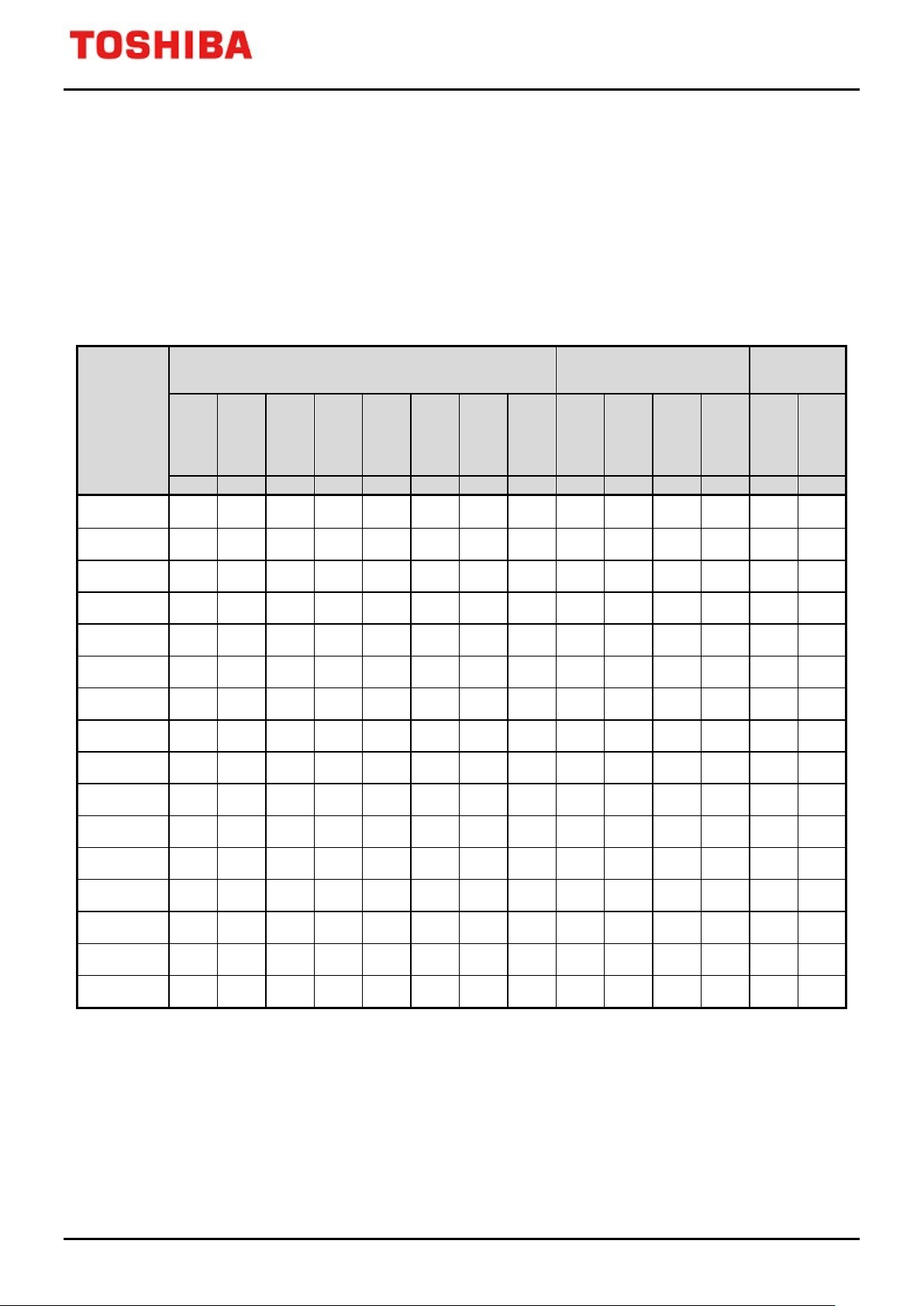

Table 3.1 Execution task in each schedule.............................................................................................. 17

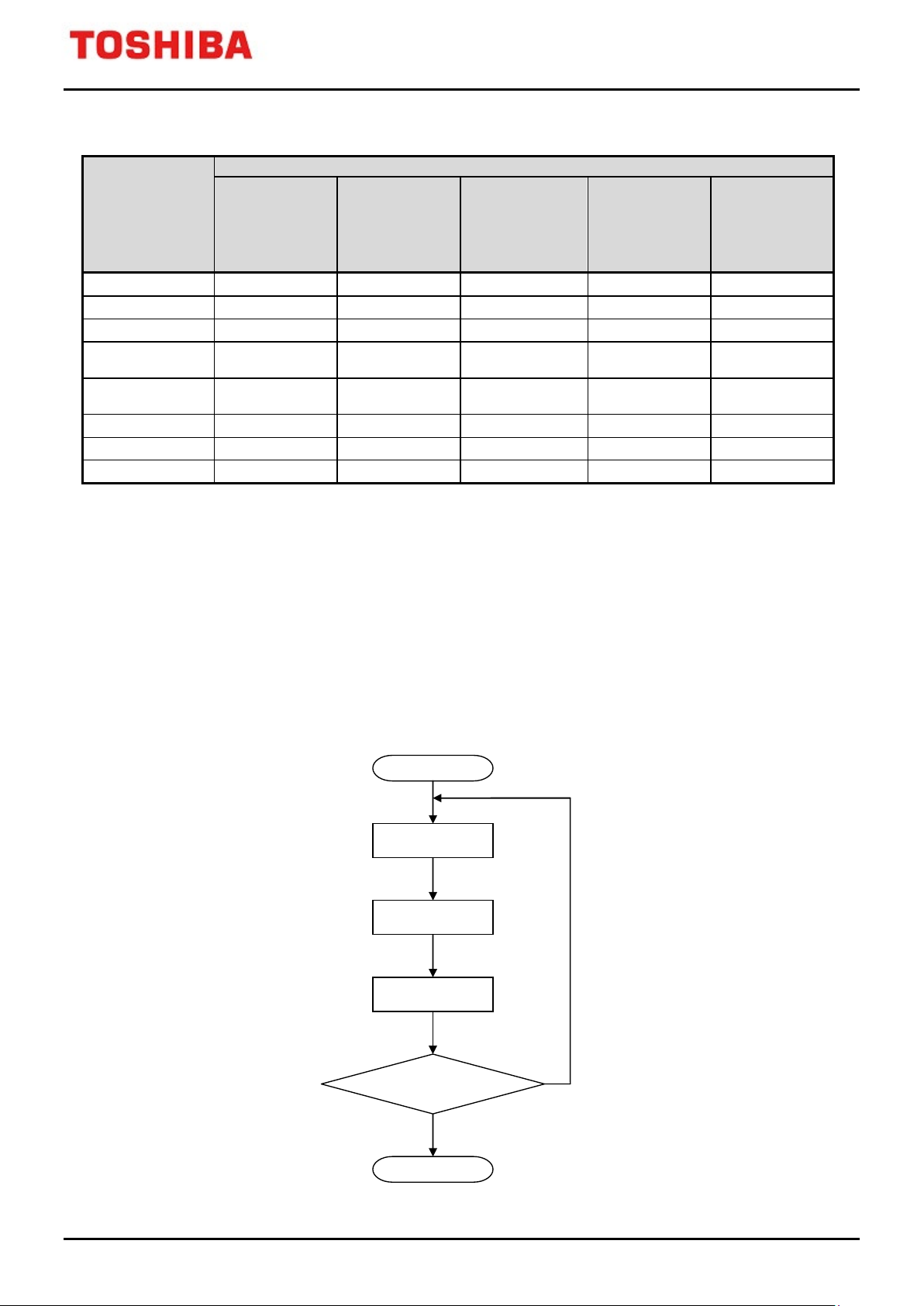

Table 3.2 Example of setting for typical operation flow ........................................................................... 18

Table 3.3 Schedule-related tasks ............................................................................................................ 19

Table 3.4 List of tasks .............................................................................................................................. 21

Table 4.1 <UPWM>, <UOC[1:0]> PMD setting: Output control of U-phase(UOx, XOx) ......................... 92

Table 4.2 <VPWM>, <VOC[1:0]> PMD setting: Output control of V-phase(VOx, YOx) .......................... 92

Table 4.3 <WPWM>, <WOC[1:0]> PMD setting: Output control of W-phase(WOx, ZOx) ...................... 92

Table 6.1 Revision history ...................................................................................................................... 104

2021-02-24

Rev. 3.1

7 / 107

Preface

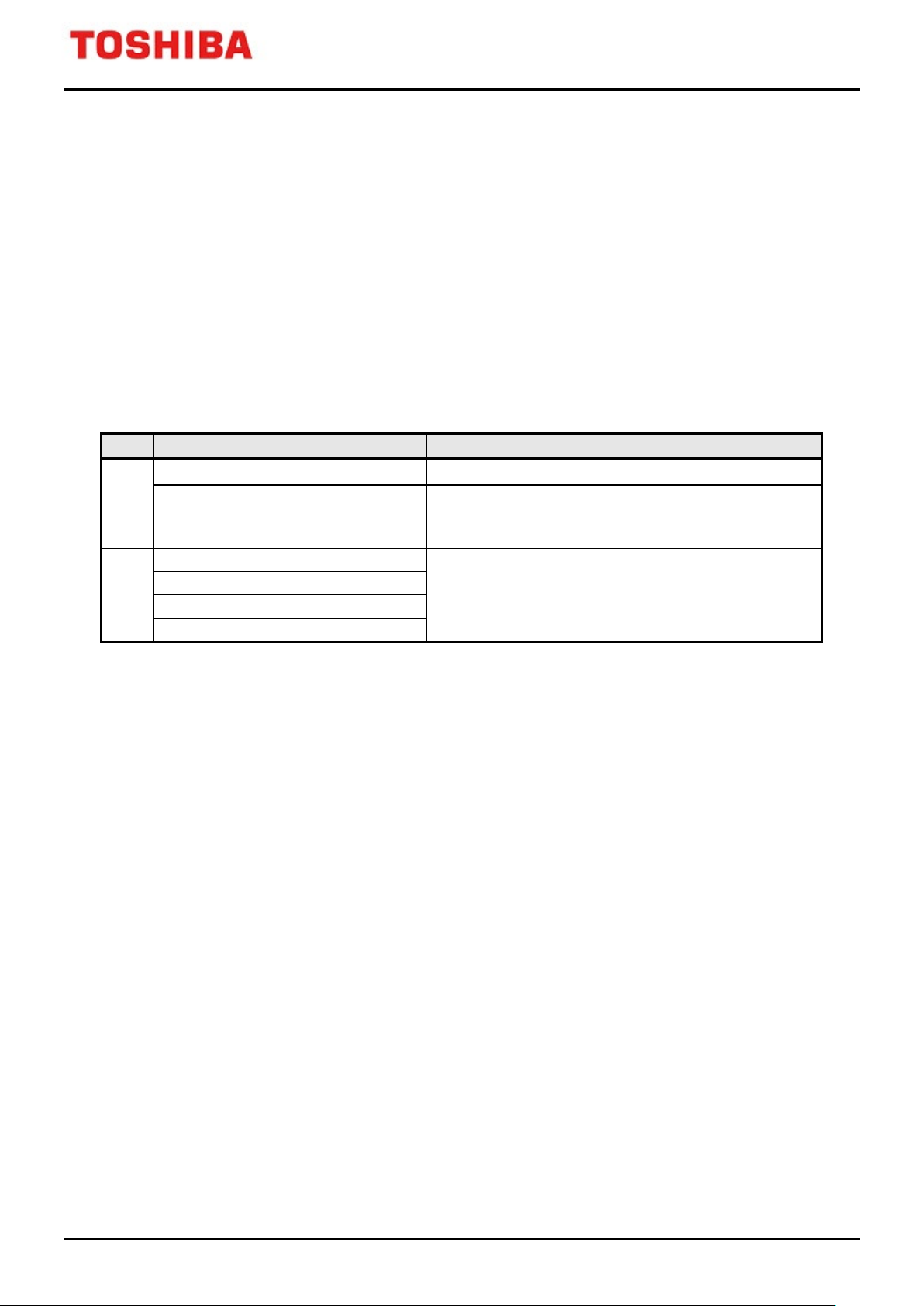

Related document

Document name

Advanced Programmable Motor Control Circuit

12-bit Analog to Digital Converter

Exception

Clock Control and Operation Mode

Product Information

TXZ/TXZ+ Family

Advanced Vector Engine Plus

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

8 / 107

Advanced Vector Engine Plus

Conventions

● Numeric formats follow the rules as shown below:

Hexadecimal: 0xABC

Decimal: 123 or 0d123 – Only when it needs to be explicitly shown that they are decimal numbers.

Binary: 0b111 – It is possible to omit the "0b" when the number of bit can be distinctly understood from a

sentence.

● "_N" is added to the end of signal names to indicate low active signals.

● It is called "assert" that a signal moves to its active level, "deassert" to its inactive level.

● When two or more signal names are referred, they are described like as [m: n].

Example: S[3: 0] shows four signal names S3, S2, S1 and S0 together.

● The characters surrounded by [ ] defines the register.

Example: [ABCD]

● "n" substitutes suffix number of two or more same kind of registers, fields, and bit names.

Example: [XYZ1], [XYZ2], [XYZ3] [XYZn]

● "x" substitutes suffix number or character of units and channels in the Register List.

In case of unit, "x" means A, B, and C ...

Example: [ADACR0], [ADBCR0], [ADCCR0] [ADxCR0]

In case of channel, "x" means 0, 1, and 2 ...

Example: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA] [T32AxRUNA]

● The bit range of a register is written like as [m: n].

Example: Bit[3: 0] expresses the range of bit 3 to 0.

● The configuration value of a register is expressed by either the hexadecimal number or the binary number.

Example: [ABCD]<EFG> = 0x01 (hexadecimal), [XYZn]<VW> = 1 (binary)

● Word and Byte represent the following bit length.

Byte: 8 bits

Half word: 16 bits

Word: 32 bits

Double word: 64 bits

● Properties of each bit in a register are expressed as follows:

R: Read only

W: Write only

R/W: Read and Write are possible

● Unless otherwise specified, register access supports only word access.

● The register defined as reserved must not be rewritten. Moreover, do not use the read value.

● The value read from the bit having default value of "—" is unknown.

● When a register containing both of writable bits and read-only bits is written, read-only bits should be written

with their default value, in the cases that default is "—", follow the definition of each register.

● Reserved bits of the Write-only register should be written with their default value.

In the cases that default is "—", follow the definition of each register.

● Do not use read-modified-write processing to the register of a definition which is different by writing and

read out.

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

9 / 107

Advanced Vector Engine Plus

All other company names, product names, and service names mentioned herein may be trademarks of their

respective companies.

2021-02-24

Rev. 3.1

10 / 107

Terms and Abbreviation

Some of abbreviations used in this document are as follows:

ADC Analog to Digital Converter

A-PMD Advanced Programmable Motor Control Circuit

A-VE+ Advanced Vector Engine Plus

PMD Programmable Motor Control Circuit

VE Vector Engine

TXZ/TXZ+ Family

Advanced Vector Engine Plus

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

11 / 107

Function

Classification

Calculate with fixed point number.

Interface task for PMD(Note1) and ADC(Note2)

d axis PI control, q axis PI control.

- Output limit by voltage scalar value

SIN/COS

Calculate sine and cosine values at phase θ

- Phase interpolation and phase clipping possible

- Coordinate transformation(Inverse park transformation)

Clarke transformation)

Convert 3-phase voltage to PWM output setting of PMD(Note1) (2 types)

- Compensation control of dead time

Trigger generation

task

Calculate AD conversion sampling timing set value of PMD from 3-phase

duty.

Read the ADC(Note2) conversion results and convert it to fixed point

- Current polarity determination (hysteresis/reverse hysteresis)

- Phase transformation (Clarke transformation)

- Axis transformation (park transformation)

- Arctangent (ATAN) calculation task

- Square root calculation task

Execute tasks sequentially

- 15 types of schedule

- Command start

process task by the ADC conversion end interrupt

Schedule end

interrupt

Interrupt that occurs when PWM interrupt is input from PMD(Note1) during

output schedule execution

Task end interrupt

Interrupt that occurs when the specified task completion.

Outputs a signal at task transition timing during schedule operation.

It can be monitored by PMD's(Note1) debug output function.

Advanced Vector Engine Plus

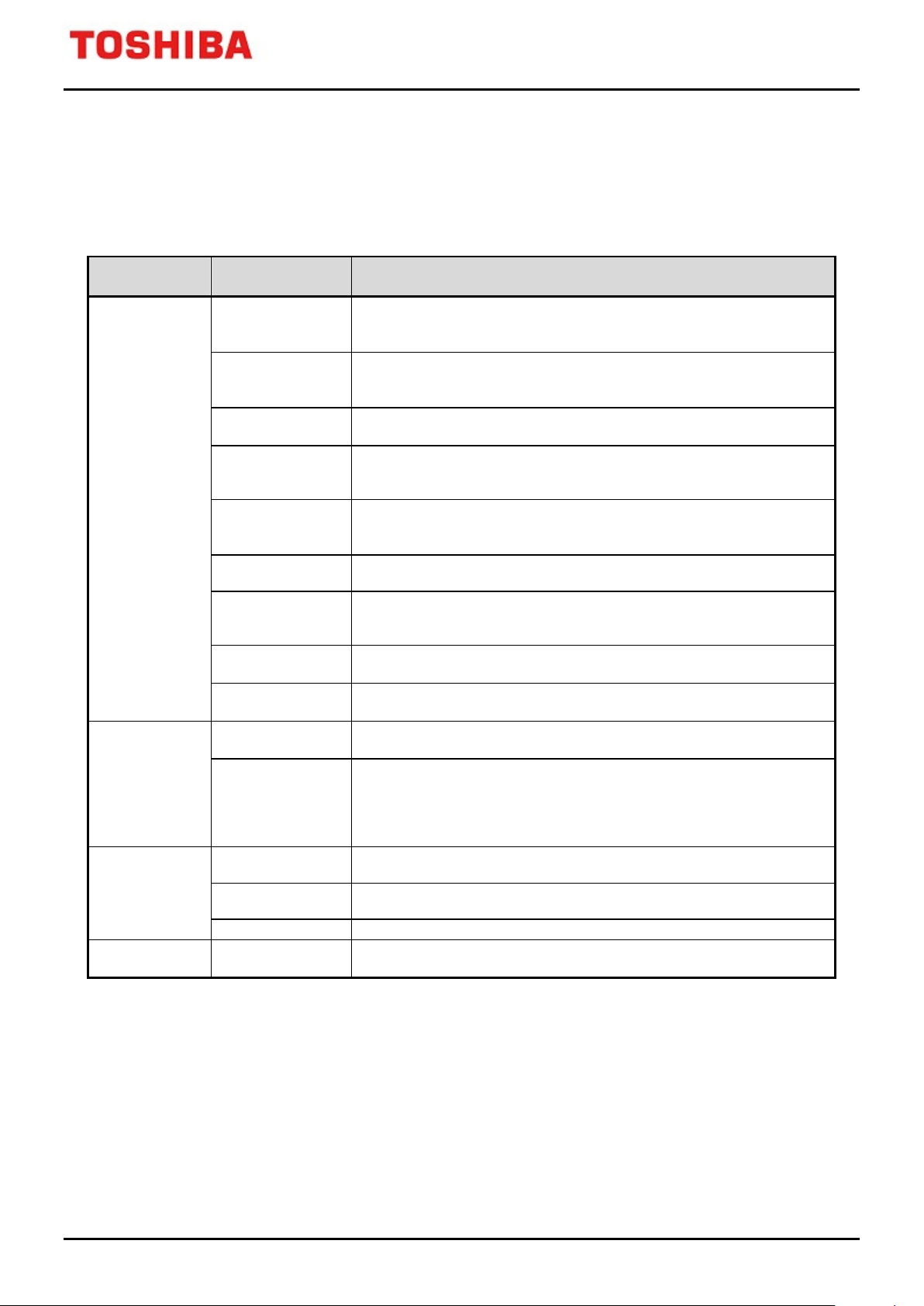

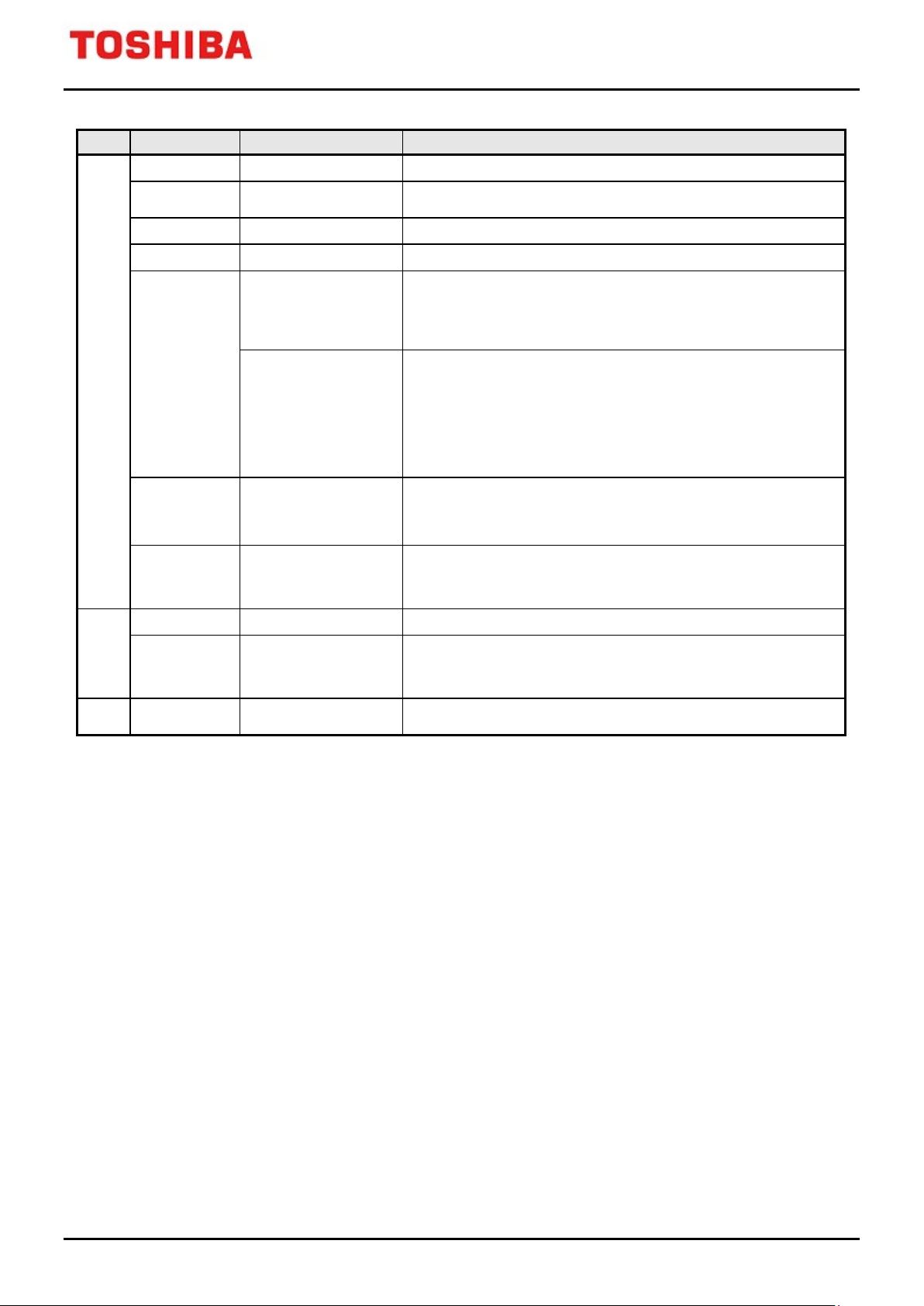

1. Outlines

The advanced vector engine plus (hereafter referred to as VE) can support vector control of 1 channel motor in 1

unit. The following is a list of functions.

Function Operation

Calculation

function

Basic function

Current control task

calculation task

Output voltage

transformation task

Output control task

Input process task

Input current

transformation task

Individual function

Scheduling control

Computation task for vector control

- Non-interference control

- Phase transformation: 2 types(Space vector transformation, Inverse

- Output limit possibility

number (2 types).

Schedule

manager

Interrupt control

Other function

Start control

Error interrupt

Output for

debugging

- Repeat start

- Start input schedule by end of AD conversion.

Start from the standby state after the output schedule ends from the input

Interrupt that occurs at the completion of schedule

Note1: For details of the PMD, refer to the reference manual "Advanced Programmable Motor Control

Circuit".

Note2: For details of the ADC, refer to the reference manual "12-bit Analog to Digital Converter".

2021-02-24

Rev. 3.1

12 / 107

Ta sk s

Current Control

Output voltage

transformation

Output control

Trigger generation

Input process

Input current

transformation

Scheduler

Schedule 0

Schedule

management

Start co

ntrol

Schedule

control

Interrupt control

Registers

Computation

Unit

INTPWMx

INTVCNx

Decoder

Error detection

ADC

INTADxPDA

INTADxPDB

INTVCTx

VExDBGO

Schedule 1

Schedule 15

PMD

ADxREG0 to 3

VExCMPU to W

VExTRGCMP0,1

VExTRGSEL

VExEMGRS

VExOUTCR

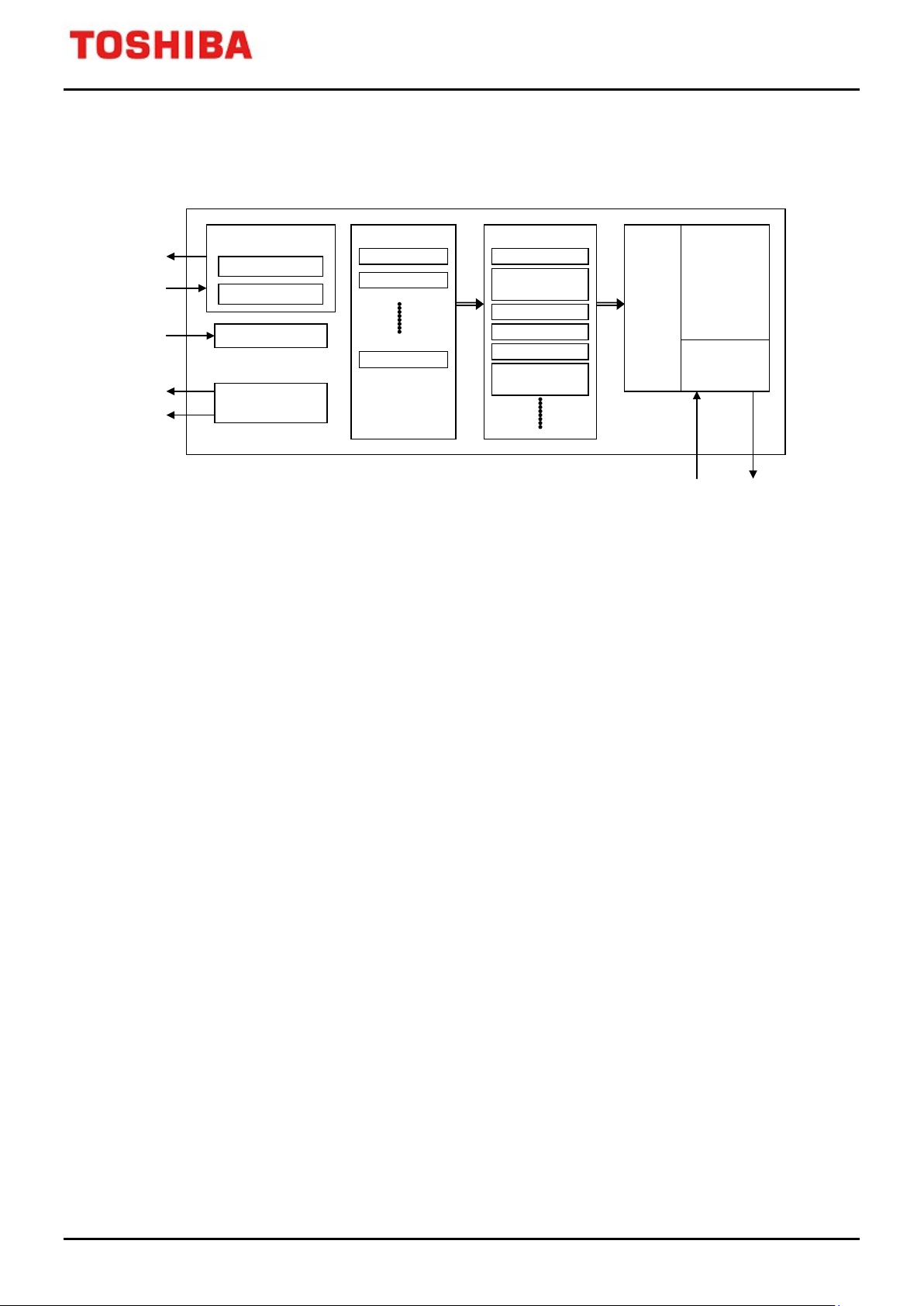

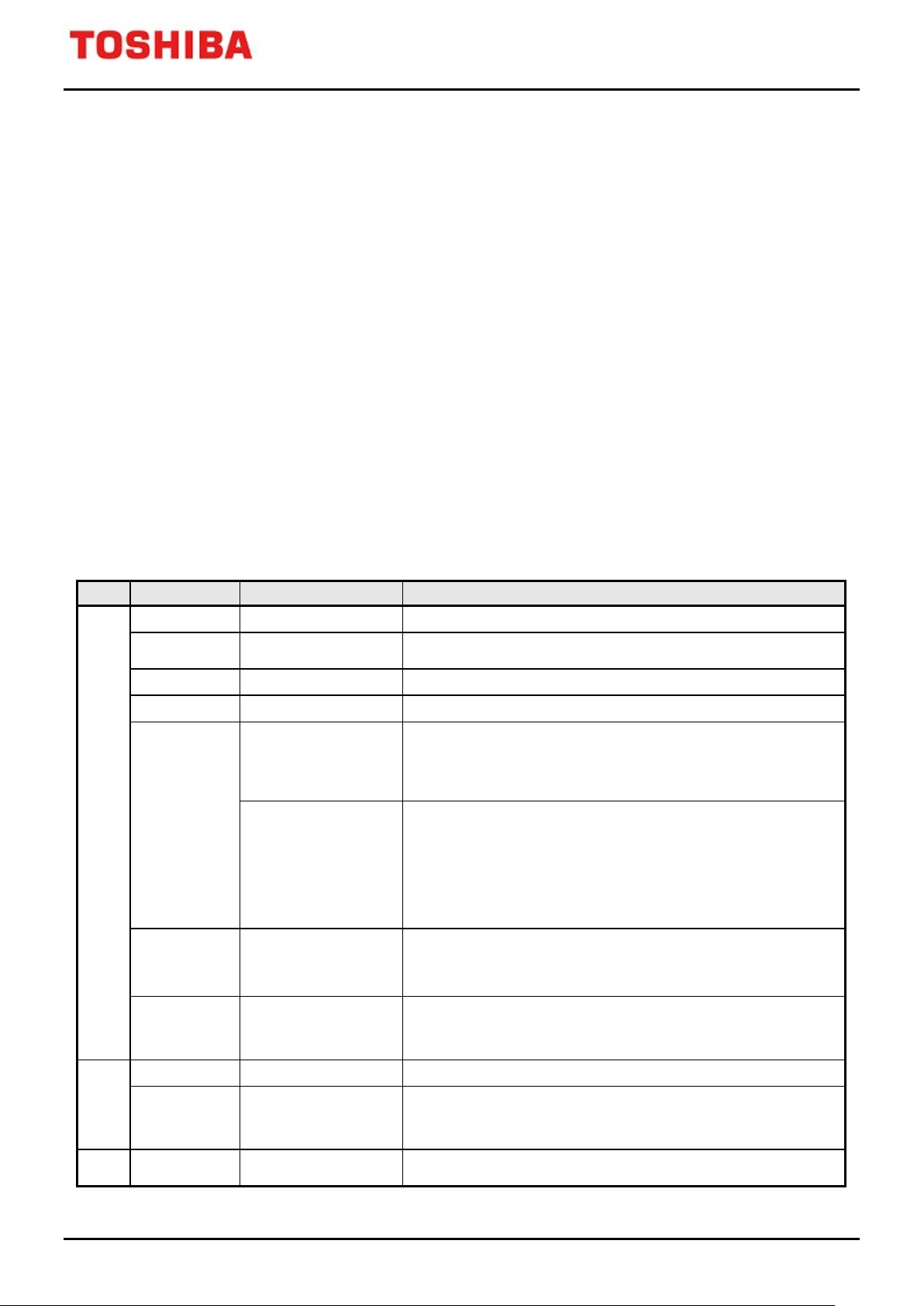

2. Configuration

2.1. Configuration of the VE

TXZ/TXZ+ Family

Advanced Vector Engine Plus

Figure 2.1 Block diagram of VE

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

13 / 107

U-phase PWM duty

([VExCMPU] register output to PMD)

V-phase PWM duty

([VExCMPV] register output to PMD)

W-phase PWM duty

([VExCMPW] register output to PMD)

Trigger compare 0

([VExTRGCMP0] register output to PMD)

([VExTRGCMP1] register output to PMD)

Synchronous trigger output selection

([VExTRGSEL] register output to PMD)

Conduction control / output control

([VExOUTCR] register output to PMD)

EMG release

[VExEMGRS]

9

INTPW Mx

PWM interrupt (from PMD)

Input

Product Information

ADC conversion result 0

(Current 1 data from ADC)

ADC conversion result 1

(Current 2 data from ADC)

ADC conversion result 2

(Current 3 data from ADC)

ADC conversion result 3

(DC voltage data from ADC)

ADC conversion end interrupt A

(Trigger from ADC)

ADC conversion end interrupt B

(Trigger from ADC)

16

INTVCNx

Schedule end interrupt

Output

Exception, Product Information

17

INTVCTx

Task end interrupt

Output

Exception, Product Information

18

VExDBGO

Task transition signal (debug output)

Output

Product Information

Advanced Vector Engine Plus

Table 2.1 List of signals

No Signal name Signal name I/O Related Reference manual

1 VExCMPU

2 VExCMPV

3 VExCMPW

4 VExTRGCMP0

5 VExTRGCMP1

6 VExTRGSEL

7 VExOUTCR

8 VExEMGRS

10 ADxREG0

11 ADxREG1

12 ADxREG2

13 ADxREG3

Trigger compare 1

(

register output to PMD)

Output Product Information

Output Product Information

Output Product Information

Output Product Information

Output Product Information

Output Product Information

Output Product Information

Output Product Information

Input Product Information

Input Product Information

Input Product Information

Input Product Information

14 INTADxPDA

15 INTADxPDB

Input Product Information

Input Product Information

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

14 / 107

VE ch0

PMD ch0

ADC unit A

Trigger output

Port

UO0

VO0

WO0

XO0

YO0

ZO0

・

・

・

Port

AINAx

ADAREG0

ADAREG1

ADAREG2

ADAREG3

VE0CMPU

VE0CMPV

VE0

CMPW

VE0OUTCR

VE0EMGRS

VE0TRGCMP0

VE0TRGCMP1

VE0TRGSEL

INTPW M0

INTPW M0

PMD0CMPU

PMD0CMPV

PMD0CMPW

PMD0OUTCR

PMD0EMGRS

PMD0TRGCMP0

PMD0TRGCMP1

PMD0TRGSEL

PWM output

Protect signal

(Internal)

EMG0

OVV0

Protect signal

(External)

General purpose trigger

PMD trigger 0 to 5

Monitor function output

from timer

Analog input

INTADAPDA

INTADAPDA

INTADAPDB

INTADAPDB

Current 1 input

Current 2 input

Current 3 input

DC voltage input

ADAREG0

ADAREG1

ADAREG2

ADAREG3

Advanced Vector Engine Plus

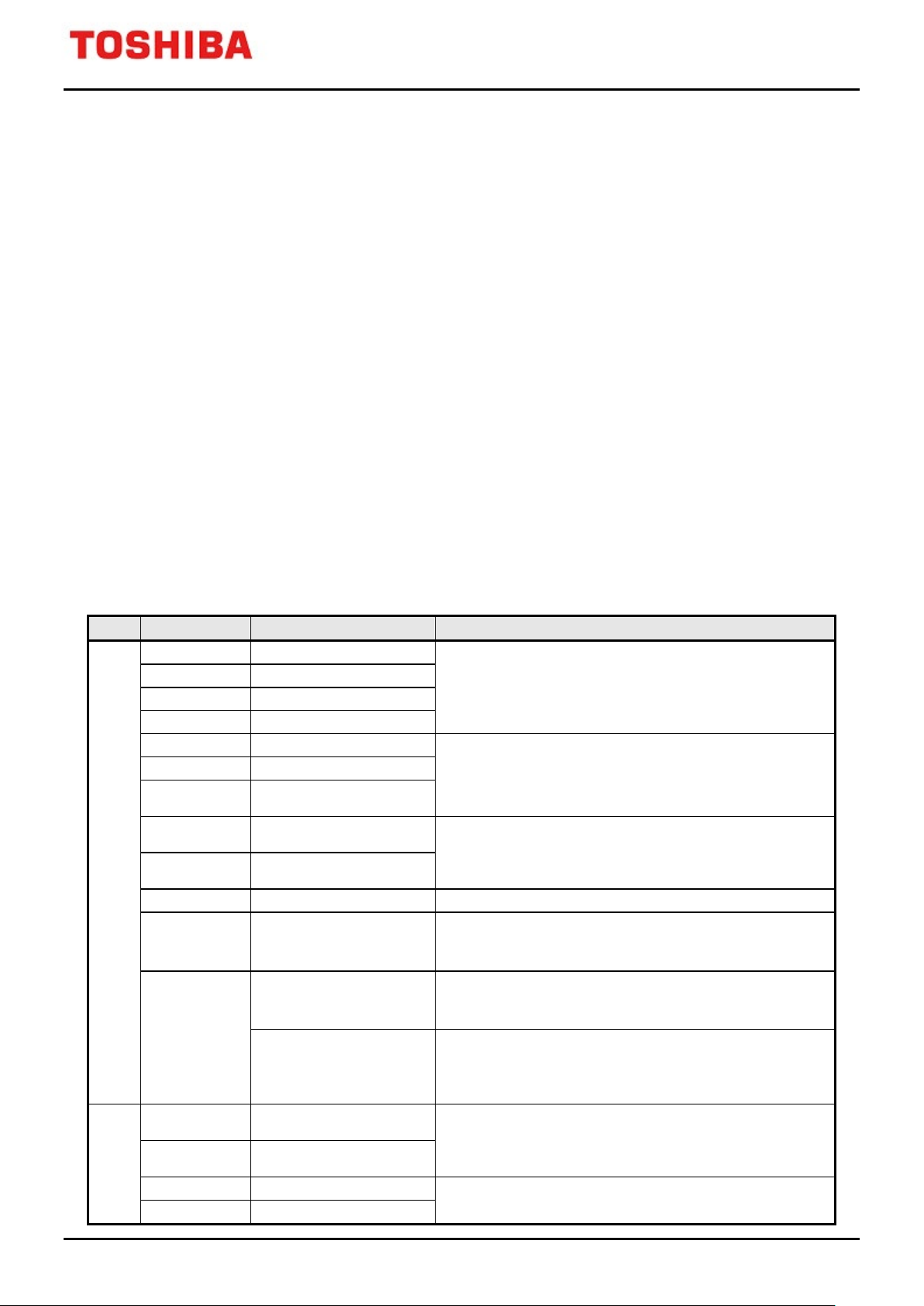

2.2. Interaction between the VE, PMD, and ADC

As shown in Figure 2.2, the VE allows to swap data between the PMD and ADC directly.

When the [PMDxCMPU], [PMDxCMPV], [PMDxCMPW], [PMDxMDOUT], [PMDxTRGCMP0],

[PMDxTRGCMP1] and [PMDxTRGSEL] registers of the PMD is set to the VE mode with the

[PMDxMODESEL] register, these registers are switched to [VExCMPU], [VExCMPV], [VExCMPW],

[VExOUTCR], [VExTRGCMP0], [VExTRGCMP1] and [VExTRGSEL] of the VE registers(Note). In this case,

these VE registers cannot be controlled via the corresponding registers of the PMD by the CPU. These registers

can be written by the VE. There are no read/write restrictions for other PMD registers.

The VE can read the value of the conversion result storage registers ([ADxREG0], [ADxREG1], [ADxREG2],

[ADxREG3]) of the ADC in the input process task. When reading the conversion result, phase information set in

the conversion program for each synchronous trigger from the PMD is also read from the ADC.

Note: Even if PMD register is switched to VE register, double buffer / triple buffer function of PMD is

valid. Refer to "Advanced Programmable Motor Control Circuit" in the reference manual for details

of buffer function.

When executing double buffers / triple buffers with PMD, while executing the task of operating

these registers with VE (output control 1 task/output control 2 task/trigger generation task, refer to

"3.3 Description of Tasks".) Even if the double buffer / triple buffer execution stage update timing is

reached, the execution stage is not updated.

Figure 2.2 Connection diagram of VE and peripherals

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

15 / 107

RESET

Initial input

Stop

Positioning

Forced

commutation

Speed control by

current feedback

Brake

Initial setting

EMG release

:

Executed by the VE

:

Software control

Change

[VExACTSCH]

Enable VE

Change

[VExMODE]

Change [VExACTSCH

]

Change [VExMODE

]

Change [VExACTSCH]

Change [VExMODE]

Change [VExACTSCH]

Change [VExMODE]

Change [VExACTSCH]

Change [VExMODE]

Change

[VEx

ACTSCH]

Change[VExMODE]

Advanced Vector Engine Plus

3. Description of Operations

3.1. Clock Supply

When you use VE, please set an applicable clock enable bit to "1" (clock supply) in Clock supply and stop register

A for fsys ([CGFSYSENA], [CGFSYSMENA]), Clock supply and stop register B for fsys ([CGFSYSENB],

[CGFSYSMENB]), and Clock supply and stop register for fc ([CGFCEN]).

An applicable register and the bit position vary according to a product. Therefore, the register may not exist with

the product. Please refer to "Clock Control and Operation Mode" of the reference manual for the details.

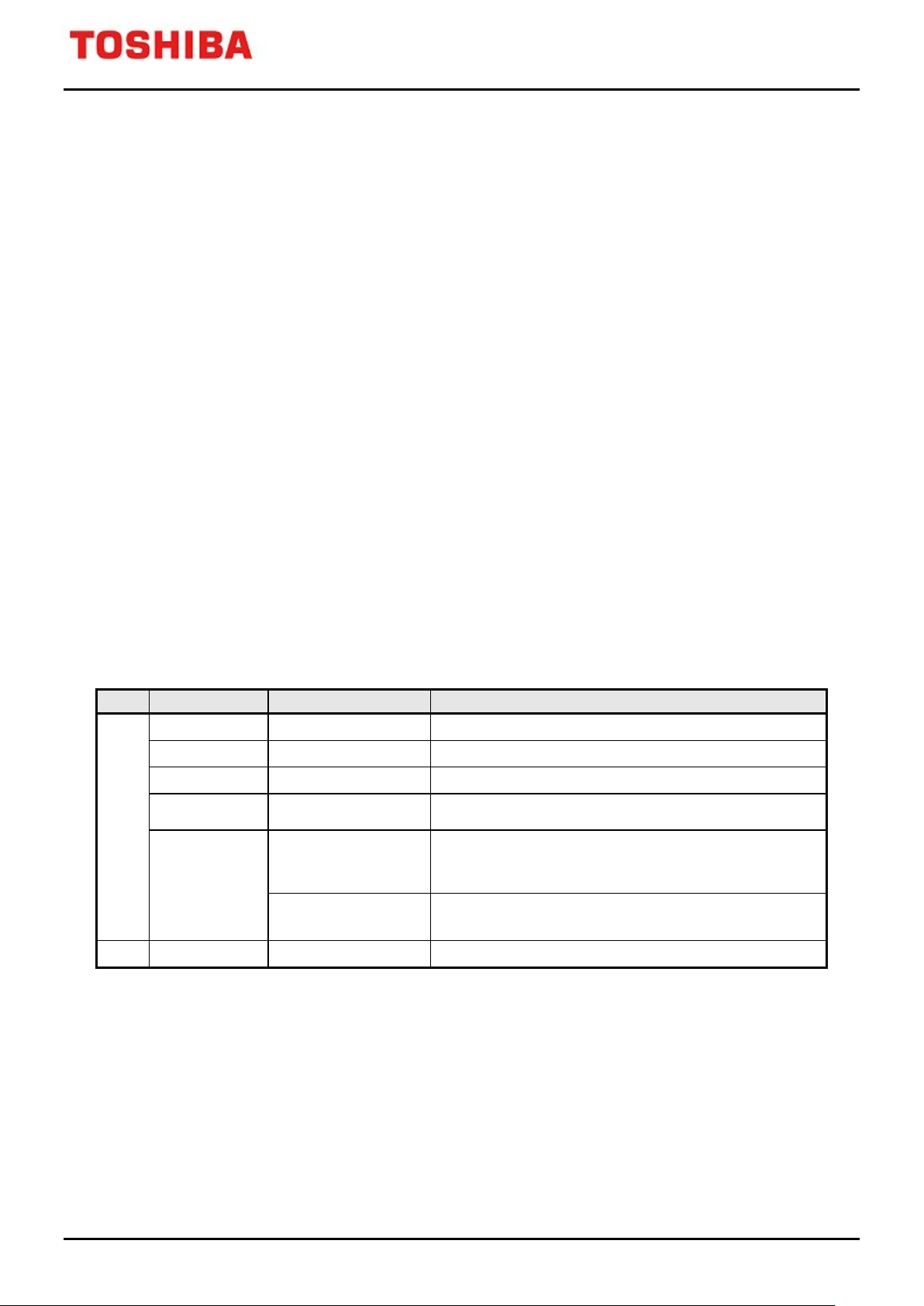

3.2. Schedule Management

Figure 3.1 shows a flowchart of motor control. The VE changes operation status according to the schedule setting

([VExACTSCH]) and mode setting ([VExMODE]).

Figure 3.1 Example of Motor Control Operation Status Flowchart

2021-02-24

Rev. 3.1

Advanced Vector Engine Plus

16 / 107

Item

Function

RESET Resets the MCU.

Initial setting Specifies the initial setting by software.

Stop Stops the motor.

Initial input Samples and stores zero-current data when the motor is at stop.

Positioning Controls the motor initial position.

TXZ/TXZ+ Family

Forced commutation

Speed control by current feedback Control motor rotation speed by current feedback.

Brake Deceleration control

EMG release Release the EMG protection state.

Rotates the motor. The motor is rotated without current feedback control at

a specified speed in a motor activation period.

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

17 / 107

Provided by

execution

SIN/COS

Output

formation

for

for

mation

Input

formation

Task 5

Task 6

Task 7

Task 8

Task 11

Task 0

Task 9

Task 1

Task 2

Task 10

Task 3

Task 4

Task 12

Task 13

0:Individual

task execution

(Note 1)

(Note 1)

(Note 1)

(Note 1)

(Note 1)

(Note 1)

(Note 1)

(Note 1)

(Note 1)

(Note 1)

10: Schedule 10

11: Schedule 11

12: Schedule 12

13: Schedule 13

14: Schedule 14

Advanced Vector Engine Plus

3.2.1. Schedule Control

An operation schedule is selected with the [VExACTSCH] register.

The schedule is comprised of the output schedule handling output process tasks and the input schedule handling

input process tasks. Table 3.1 shows the relationship between the schedules and operation tasks.

A task operation is specified with the dedicated register according to the motor control method.

Table 3.1 Execution task in each schedule

Output schedule

execution tasks

Input schedule

execution tasks

only individual

Schedule

Selection

[VExACTSCH]

<VACT>

1: Schedule 1

Current

control

calcula-

coordi-

tion

(Note 1)

nate

axis

trans-

Output

phase

trans-

mation

1

Output

phase

trans-

mation

2

-

Output

control

1

Output

control

2

-

Trigger

genera-

tion

(Note 1)

Input

process

1

Input

process

2

-

Input

phase

trans-

for

coordi-

nate

axis

trans-

ATAN2

calcula-

tion

(Note 1) (Note 1)

- -

Square

root

calcula-

tion

2: Schedule 2 - - - - -

3: Schedule 3 - - - - -

4: Schedule 4 -

-

-

-

- -

5: Schedule 5 - - - - - -

6: Schedule 6 - - - - - -

7: Schedule 7 -

-

-

-

- -

8: Schedule 8 - - - - -

9: Schedule 9 - - - - - - - - - - -

15:Schedule 15 - - - - - - - - - -

-

- - - - - - - -

- - - - - - - - -

- - - - - - - - -

-

- - - - - - - -

- - - - - - - - - -

Note 1: Only the tasks that are specified with [VExTASKAPP] are executed.

Note 2: : Execution task, -: Non execution task

2021-02-24

Rev. 3.1

18 / 107

Setting

Phase

<PVIEN>

Forced

commutation

Current feedback

speed control

×

Start command

Execute

output schedule

Execute

input schedule

Wait for

start trigger

Schedule end

Yes

No

Start trigger

Repeated specified

number of times?

TXZ/TXZ+ Family

Advanced Vector Engine Plus

Table 3.2 Example of setting for typical operation flow

Motor control

flow

Stop 9 0

Initial input 9 0

Positioning 1 5 0 01 0

Brake 4 6 0 01 0

EMG release 9 0

Short circuit brake 4 6

Schedule

setting

[VExACTSCH]

<VACT>

1 5 1 01 0

1 5 1 01 0

Task selection

[VExTASKAPP]

<VTASK>

interpolation

enable

[VExMODE]

×

×

×

Output control

operation

[VExMODE]

<OCRMD>

00 0

00 1

11 0

10 0

Zero-current

detection

[VExMODE]

<ZIEN>

×: don’t care

An output schedule starts operation with the command ([VExCPURUNTRG]). When all output-related tasks are

completed, the VE enters standby state and waits for a start trigger ([VExTRGMODE] setting).

An input schedule starts operation by a start trigger. When all input-related tasks are completed, the VE generates

an interrupt to the CPU and enters halt state. However, if the number of repeating of the schedule

([VExREPTIME]) is set to "2" or more, the output schedules continue execution. An interrupt does not occur

until the schedules have been executed for the specified number of times.

Note: Repeat setting is not available in Schedule 10 to Schedule 15. (The schedule ends once even if the

condition is [VExREPTIME] ≥ 2.)

Figure 3.2 Operation schedule flowchart

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

19 / 107

Register name

Function

Advanced Vector Engine Plus

3.2.2. Start Control

Before the schedule is started, set the VE to enable ([VExEN]<VEEN> = 1), and then set the operation schedule

selection register ([VExACTSCH]), task selection register ([VExTASKAPP]) and operation schedule repeat

specify register ([VExREPTIME]). After that, the schedule can be executed as follows:

A schedule of the VE is comprised of output schedules and input schedules. Typically, the VE enters wait state

after an output schedule is complete. At this time, if a startup trigger occurs, an input schedule is executed.

The output schedule and the input schedule are started on different conditions below:

● Start conditions for the output schedule

‒ Starting by the command. A task ([VExTASKAPP]) is specified with [VExCPURUNTRG].

‒ Repeat setting. Starting after the input schedules have been executed for the number of times

([VExREPTIME] ≥ 1).

● Start conditions for the input schedule

‒ Starting an input process task that is started from wait state by a trigger (specified with

[VExTRGMODE]). In this case, the VE is in wait state after the output schedule is complete.

‒ Starting by the command. A task ([VExTASKAPP]) is specified with [VExCPURUNTRG].

[VExACTSCH]

[VExTASKAPP]

[VExREPTIME]

[VExTRGMODE]

Operation

schedule selection

Starting

task designation

The number of

repeating of

the schedule

Start trigger mode

selection

Table 3.3 Schedule-related tasks

0x0: Only the task specified with [VExTASKAPP] is executed.

0x1: Schedule 1 is executed.

0x2: Schedule 2 is executed.

0x3: Schedule 3 is executed.

0x4: Schedule 4 is executed.

0x5: Schedule 5 is executed.

0x6: Schedule 6 is executed.

0x7: Schedule 7 is executed.

0x8: Schedule 8 is executed.

0x9: Schedule 9 is executed.

0xA: Schedule 10 is executed.

0xB: Schedule 11 is executed.

0xC: Schedule 12 is executed.

0xD: Schedule 13 is executed.

0xE: Schedule 14 is executed.

0xF: Schedule 15 is executed.

Specifies the task number that can be executed among the selected

operation schedule.

Sets the number from "1" to "15".

Note: When one-time execution is specified, set "1".If "0" is set, the

schedule is not executed.

Selects the input schedule trigger.

Sets INTADxPDA or INTADxPDB.

2021-02-24

Rev. 3.1

Advanced Vector Engine Plus

20 / 107

3.2.3. Interrupt Control

The VE has a schedule end interrupt (INTVCNx) that occurs at the completion of the schedule, and a task

completion interrupt (INTVCTx) that occurs at the completion of specified task.

● Schedule end interrupt

(1) Specifies the schedule with the operation schedule selection register ([VExACTSCH]). Sets the

command ([VExCPURUNTRG] = 1).

(2) When the schedules have been executed for the specified times ([VExREPTIME]), an INTVCNx

interrupt occurs.

(3) If the error detection interrupt control is enabled ([VExERRINTEN]<VERREN> = 1), a PWM

interrupt of the PMD circuit occurs while output schedule is being executed. Then an INTVCNx

interrupt occurs and an error flag ([VExERRDET]<VERRD>) is set to "1".

● Task end interrupt

(1) Specifies a task triggered of a task end interrupt ([VExTASKAPP]<VITASK>). Sets task end interrupt

control to enable ([VExERRINTEN]<INTTEN> = 1).

(2) Starts the schedule by the command ([VExCPURUNTRG] = 1). Sets a INTVCTx interrupt to occur at

the completion of the task specified with <VITASK>

TXZ/TXZ+ Family

2021-02-24

Rev. 3.1

Advanced Vector Engine Plus

21 / 107

Task

number

Output coordinate

transformation

Output phase

transformation 1

Input phase

transformation

3.3. Description of Tasks

This subsection describes the outline of each task operation in the schedule.

Table 3.4 shows the task numbers that are used to specify the execution task and the start task.

Table 3.4 List of tasks

Task Task function

PI control for d-axis/q-axis (PI control output limit enable)

Current control

SIN/COS

calculation

Non-interference control for d-axis and q-axis, voltage scalar

limitation

Sine/cosine calculation

Phase interpolation (with clipping function)

TXZ/TXZ+ Family

5

6

Output

schedule

Input

schedule

axis

Output phase

transformation 2

Output control 1

Output control 2

Trigger generation

Input process 1

Input process 2

Inverse Park transformation

Transforms from 2-phase to 3-phase [SVM] 8

Transforms from 2-phase to 3-phase [Inverse Clarke

transformation]

Converts the data to PMD setting format. Switches PWM Shift

1.

Limits the PWM output.

Sets the dead time compensation control.

Converts the data to PMD setting format. Switches PWM Shift

2.

Limits the PWM output.

Sets the dead time compensation control.

Generates the synchronous trigger timing for ADC.

Corresponds to sensor, 3-shunt and 1-shunt current

detection.1-shunt is corresponded in the case of PWM Shift

prohibited or PWM Shift 1.

Captures the result of AD conversion and converts them into

fixed-point format.

Specifies the hysteresis width to determine the current polarity.

Corresponds to sensor, 3-shunt and 1-shunt current

detection.1-shunt is corresponded in the case of PWM Shift 2.

Captures the result of AD conversion and converts them into

fixed-point format.

Specifies the hysteresis width to determine the current polarity.

11

10

7

0

9

1

2

Transforms from 3-phase to 2-phase.

Input coordinate

axis

transformation

ATAN2 calculation Calculates the arctangent. 12

SQRT calculation Calculates the square root. 13

Performs Park transformation

Calculates the declination angle of the current vector or the

induced voltage vector on the d-q coordinate.

3

4

2021-02-24

Rev. 3.1

22 / 107

Input process

Output control

Phase

transformation

Current control

SIN/COS

calculation

Phase

interpolation

PI

control

PI

control

Cordinate axis

transformation

[I-Park]

Phase

transformation 1

[SVM]

Output

control 1

sin,cos

VD

VQ

Valpha

Vbeta

DUTYA

DUTYB

DUTYC

SECTOR

θ

ω

Trigger

generation

Phase

transformation

[Clark]

Input

process1

Ialpha

Ibeta

VDC,VDCL

ID

IQ

PWM output

setting (PMD)

Synchronous

trigger t setting

(PMD)

Current/Voltage

detection value

(ADC)

SIN

COS

IDREF

ID

IQ

IQREF

VDC

IA

IB

IC

Phase

transformation 2

[I-Clark]

Output

control 2

Input

process2

VDC

Cordinate axis

transformation

[Park]

TXZ/TXZ+ Family

Advanced Vector Engine Plus

Figure 3.3 Relationship diagram of tasks

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

23 / 107

Advanced Vector Engine Plus

3.3.1. Current Control (Task 5)

The current control task is comprised of a PI control unit for d-axis current and a PI control unit for q-axis current,

and calculates the d-axis and q-axis voltages respectively.

The expansion control enables the non-interference control and the voltage scalar limitation that controls d-axis

and q-axis together.

a. d-axis current PI control

<Equation>

[PI control]

Δid = [VExIDREF] - [VExID] ; Calculates between the current reference value

and the current feedback

kpg = ([VExCIDKG]<CIDKPG> setting) ; Range of proportional coefficient

kig = ([VExCIDKG]<CIDKIG> setting) ; Range of Integral coefficient

limit = [VExPIOLIM]

if (kpg ≥ 2) n = kpg ; Selected range is more than twice

Save Range of proportional coefficient

limit = limit / kpg ; Limit correction

kig = kig / kpg ; Range correction of integral

kpg = 1 ; Range correction of proportional

else n = 1

cidkp = [VExCIDKP] × kpg ; Proportional coefficient

cidki = [VExCIDKI] × kig ; Integral coefficient

vdi0 = cidki × Δid + VDI ; Calculates the integral components.

vd0 = cidkp × Δid + vdi0 ; Calculates the voltage by adding the

proportional components.

[PI control output limitation]

if (vd0 > limit) ; The upper-limit value

vd = limit

[VExMCTLF]<PIDOVF> = 1

else if (vd0 < -limit) ; The lower-limit value

vd = -limit

[VExMCTLF]<PIDOVF> = 1

else

[VExVD] = vd × n ; Save more than a double proportional range

to be compensated.

[Anti-windup]

Δvd = vd - vd0 ; Calculates the difference between the d-axis

voltage and the limit.

VDI = vdi0 + Δvd × ([VExMODE]<AWUMD> setting) ; Reflects the above difference

to the integral component.

vd = vd0

2021-02-24

Rev. 3.1

24 / 107

Register name

Function

Detail

d-axis current reference

value

Integral component

of d-axis voltage

TXZ/TXZ+ Family

Advanced Vector Engine Plus

Input

[VExID]

[VExIDREF]

[VExCIDKP]

[VExCIDKI]

[VExCIDKG]

[VExPIOLIM]

[VExMODE]

d-axis current

Proportional coefficient

Integral coefficient

[3:0] Sets a range of

d-axis PI control integral

coefficient

[11:8] Sets a range of

d-axis PI control

proportional coefficient

PI control output

limitation

[9:8] Anti-windup ratio

setting when output is

limited.

32-bit fixed-point data (31 fractional bits)

16-bit fixed-point data(15 fractional bits)

16-bit data

16-bit data

<CIDKIG> Range of Integral coefficient

0000: 1 / 1 0001: 1 / 2

0011: 1 / 2

0101 to 1111: Reserved

<CIDKPG> Range of proportional coefficient

0000: 1 / 1 0001: 1 / 2

0011: 1 / 2

0101 to 1000: Reserved

1001: 2 1010: 2

1100: 2

1101 to 1111: Reserved

16-bit fixed-point data (15 fractional bits)

Valid range: 0x0000 to 0x7FFF

Output limitation is disabled when [VExPIOLIM] = 0x0000.

<AWUMD>

00: Disabled 01: 1 / 4 10: 1 / 2

11: 1 / 1

12

12

4

0100: 1 / 2

0100: 1 / 2

4

16

4

16

2

0010: 1 / 2

0010: 1 / 2

1011: 2

8

8

3

Output

Internal

Note: The VDI is comprised of 64 bits. The upper is used for the [VExVDIH] register and the lower is used for

b. q-axis current PI control

<Equation>

[PI control]

Δiq = [VExIQREF] - [VExIQ] ; Calculates between the current reference value

and the current feedback

kpg = ([VExCIQKG]<CIQKPG> setting) ; Range of proportional coefficient

kig = ([VExCIQKG]<CIQKIG> setting) ; Range of Integral coefficient

limit = [VExPIOLIM]

if (kpg ≥ 2) n = kpg ; Selected range is more than twice,

Save Range of proportional coefficient

limit = limit / kpg ; Limit correction

kig = kig / kpg ; Range correction of integral

kpg = 1 ; Range correction of proportional

else n = 1

ciqkp = [VExCIQKP] × kpg ; Proportional coefficient

ciqki = [VExCIQKI] × kig ; Integral coefficient

vqi0 = ciqki × Δiq + VQI ; Calculates the integral components.

[VExVD]

[VExMCTLF]

VDI

d-axis voltage

[8] Flag for d-axis output

limitation on PI control

the [VExVDILH] register

32-bit fixed-point data (31 fractional bits)

<PIDOVF>

0: |d-axis output on PI control | ≤ [VExPIOLIM]

1: |d-axis output on PI control | > [VExPIOLIM]

64-bit fixed-point data (63 fractional bits)

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

25 / 107

Register name

Function

Detail

q-axis current reference

value

Integral component

of q-axis voltage

Advanced Vector Engine Plus

vq0 = ciqkp × Δiq + vqi0 ; Calculates the voltage by adding the

proportional components.

[PI control output limitation]

if (vq0 > limit) ; The upper-limit value

vq = limit

[VExMCTLF]<PIQOVF> = 1

else if (vq0 < -limit) ; The lower-limit value

vq = -limit

[VExMCTLF]<PIQOVF> = 1

else vq = vq0

[VExVQ] = vq × n ; Save more than a doubled proportional range

to be compensated.

[Anti-windup]

Δvq = vq - vq0 ; Calculates the difference between the q-axis

voltage and the limit.

VQI = vqi0 + Δvq × ([VExMODE]<AWUMD> setting) ; Reflects the above difference to the

integral component.

Input

[VExIQ]

[VExIQREF]

[VExCIQKP]

[VExCIQKI]

[VExCIQKG]

[VExPIOLIM]

[VExMODE]

q-axis current

Proportional coefficient

Integral coefficient 16-bit data

[3:0] Sets a range of

q-axis PI control integral

coefficient

[11:8] Sets a range of

q-axis PI control

proportional coefficient

PI control output

limitation

[9:8] Anti-windup ratio

setting when output is

limited.

32-bit fixed-point data (31 fractional bits)

16-bit fixed-point data(15 fractional bits)

16-bit data

<CIQKIG> Range of Integral coefficient

0000: 1 / 1 0001: 1 / 2

0011: 1 / 2

0101 to 1111: Reserved

<CIQKPG> Range of proportional coefficient

0000: 1 / 1 0001: 1 / 2

0011: 1 / 212 0100: 1 / 216

0101 to 1000: Reserved

1001: 2 1010: 2

1100: 24

1101 to 1111: Reserved

16-bit fixed-point data (15 fractional bits)

Valid range: 0x0000 to 0x7FFF

Output limitation is disabled when [VExPIOLIM] = 0x0000.

<AWUMD>

00: Disabled 01: 1 / 4 10: 1 / 2

11: 1

12

4

0100: 1 / 216

4

2

1011: 2

0010: 1 / 2

0010: 1 / 2

3

8

8

Output

Internal

Note: The VQI is comprised of 64 bits. The upper is used for the [VExVQIH] register and the lower is used for

[VExVQ]

[VExMCTLF]

VQI

q-axis voltage

[9] Flag for q-axis output

limitation on PI control

32-bit fixed-point data (31 fractional bits)

<PIQOVF>

0: |q-axis output on PI control | ≤ [VExPIOLIM]

1: |q-axis output on PI control | > [VExPIOLIM]

64-bit fixed-point data (63 fractional bits)

the [VExVQILH] register

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

26 / 107

Register name

Function

Detail

[VExVD]

d-axis voltage

[VExID]

d-axis current

[VExIQ]

[VExCLD]

[VExCLQ]

Motor Interlinkage magnetic

flux

Motor Inductance range

setting

Motor Interlinkage magnetic

flux range setting

[VExIDREF], [VExIQREF]

1: Expansion control is enabled.

Non-interference correction

voltage for d-axis

Non-interference correction

voltage for q-axis

[VExVD]

[VExVQ]

Advanced Vector Engine Plus

c. Non-interference control

The result of PI control is corrected using the results of the interference to d-axis and q-axis based on motor

voltage equation.

<Equation>

if ([VExMODE]<T5ECEN> = 1) ; Expansion control is enabled

ld = [VExCLD] × ([VExCLG] setting) ; d-axis inductance

lq = [VExCLQ] × ([VExCLG] setting) ; q-axis inductance

phi = [VExCPHI] × ([VExCPHIG] setting) ; Interlinkage magnetic flux

id = [VExID] ; Feedback current

iq = [VExIQ]

if ([VExFMODE]<IDQSEL> = 1) id = [VExIDREF] ; Inputs a command value

iq = [VExIQREF]

[VExVDE] = - [VExOMEGA] × iq × lq ; Calculates the interference to d-axis

[VExVQE] = [VExOMEGA] × id × ld + [VExOMEGA] × phi ; Calculates the interference to q-axis

if ([VExMODE]<NICEN> = 1) ; Non-interference control is enabled

[VExVD] = [VExVD] + [VExVDE]

[VExVQ] = [VExVQ] + [VExVQE]

Input

Output

[VExVQ]

[VExCPHI]

[VExCLG]

[VExCPHIG]

[VExOMEGA]

[VExFMODE]

[VExMODE]

[VExVDE]

[VExVQE]

q-axis voltage

q-axis current

Motor d-axis inductance

Motor q-axis inductance

Rotational speed 16-bit fixed-point data (15 fractional bits)

[4] Selects Non-interference

control input

[11] Non-interference control

enable

[10] Expansion control

enable

d-axis voltage

q-axis voltage

32-bit fixed-point data (31 fractional bits)

16-bit fixed-point data (11 fractional bits)

000: 1 / 1 001: 1 / 24 010: 1 / 28

011: 1 / 2

101 to 111: Reserved

<IDQSEL>

0: Use [VExID], [VExIQ]

1: Use

<NICEN>

0: Non-interference control is disabled.

1: Non-interference control is enabled.

<T5ECEN>

0: Expansion control is disabled.

(Non-interference control is disabled.)

16-bit fixed-point data (15 fractional bits)

32-bit fixed-point data (31 fractional bits)

12

100: 1 / 216

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

27 / 107

Advanced Vector Engine Plus

d. Voltage scalar limitation

The voltage scalar limitation controls d-axis voltage and q-axis voltage, so as to be lower the composite value (the

2

square root of VD

+ VQ2) that is comprised of d-axis voltage and q-axis voltage than the limit value.

<Equation>

if ([VExMODE]<T5ECEN> = 1) ; Expansion control is enabled.

[VDQ calculation]

if (([VExVD]

2

+ [VExVQ]2)> [VExVSLIM]2) ; Confirm the excess

if ([VExFMODE]<VSLIMMD> = 00) ; Voltage scalar limitation is disabled

[VExVDQ] = SQRT([VExVD]

2

+ [VExVQ]2)

else if ([VExFMODE]<VSLIMMD> = 01) ; Scalar limitation on the d-axis direction

2

[VExVDQ] = SQRT([VExVSLIM]

+ [VExVQ]2)

else if ([VExFMODE]<VSLIMMD> = 10) ; Scalar limitation on the q-axis direction

[VExVDQ] = SQRT([VExVSLIM]

2

+ [VExVD]2)

else if ([VExFMODE]<VSLIMMD> = 11) ; dq proportional scalar limitation

[VExVDQ] = SQRT([VExVD]

else [VExVDQ] = SQRT([VExVD]

2

+ [VExVQ]2)

2

+ [VExVQ]2) ; Calculation of voltage scalar value

Note: SQRT is the square root calculation

[Calculation for the declination angle]

x = |[VExVQ]|

y = |[VExVD]|

[VExVDELTA] = ATAN(x, y)

Note: ATAN is arctangent calculation

[Limitation calculation for each axis]

if ([VExFMODE]<VSLIMMD> = 00) ; Voltage scalar limitation is disabled

vdlim = [VExVSLIM]

vqlim = [VExVSLIM]

else if ([VExFMODE]<VSLIMMD> = 01) ; Scalar limitation on the d-axis direction

vdlim = [VExVDQ]

vqlim = [VExVSLIM]

else if ([VExFMODE]<VSLIMMD> = 10) ; Scalar limitation on the q-axis direction

vdlim = [VExVSLIM]

vqlim = [VExVDQ]

else if ([VExFMODE]<VSLIMMD> = 11) ; dq proportional scalar limitation

vdlim = [VExVSLIM] × SIN([VExVDELTA])

vqlim = [VExVSLIM] × COS([VExVDELTA])

[Limitation process]

if ([VExVD] > vdlim)

[VExVD] = vdlim ; Process for the upper-limit of d-axis

[VExMCTLF]<VSOVF> = 1

else if ([VExVD] < -vdlim)

[VExVD] = -vdlim ; Process for the lower-limit of d-axis

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

28 / 107

Register name

Function

Detail

The value of d-axis

voltage correction

The value of q-axis

voltage correction

The value of voltage

axis direction limitation.

[10] Indicates the

scalar limitation.

Advanced Vector Engine Plus

[VExMCTLF]<VSOVF> = 1

if ([VExVQ] > vqlim)

[VExVQ] = vqlim ; Process for the upper-limit of q-axis

[VExMCTLF]<VSOVF> = 1

else if ([VExVQ] < -vqlim)

[VExVQ] = -vqlim ; Process for the lower-limit of q-axis

[VExMCTLF]<VSOVF> = 1

[Correction process]

[VExVD] = [VExVD] + [VExVDCRC] ; d-axis correction

[VExVQ] = [VExVQ] + [VExVQCRC] ; q-axis correction

Input

[VExVD]

[VExVQ]

[VExVSLIM]

[VExVDCRC]

[VExVQCRC]

[VExMODE]

[VExFMODE]

[VExVDQ]

d-axis voltage

q-axis voltage

The limit value of

voltage scalar

[10] Expansion control

enable

[11:10] Limitation mode

setting

scalar or the value of

32-bit fixed-point data (31 fractional bits)

16-bit fixed-point data (15 fractional bits)

0x0000 to 0x7FFF

Limitation is disabled when [VExVSLIM] = 0x0000

16-bit fixed-point data (15 fractional bits)

<T5ECEN>

0: Expansion control is disabled.(Scalar limitation is

disabled.)

1: Expansion control is enabled.

<VSLIMMD>

00: Scalar limitation is disabled.

(Limitation in each axis is enabled.)

01: Scalar limitation is enabled.

(Limitation on the d-axis direction.)

10: Scalar limitation is enabled.

(Limitation on the q-axis direction.)

11: Scalar limitation is enabled.

(dq proportional limitation.)

16-bit fixed-point data (15 fractional bits)

Output

[VExVDELTA]

[VExVD]

[VExVQ]

[VExMCTLF]

The voltage declination

angle

d-axis voltage

q-axis voltage

excess flag for voltage

16-bit data

0x0000 to 0x4000 (0-degree to 90-degree)

32-bit fixed-point data (31 fractional bits)

<VSOVF>

0:non excess 1:excess

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

29 / 107

Register name

Function

Detail

The value of clipped

phase

Advanced Vector Engine Plus

3.3.2. SIN/COS calculation (Task 6)

The SIN/COS calculation task executes phase interpolation calculation and SIN/COS calculation.

Phase interpolation calculates the rotation speed by integrating with the PWM period. It is executed only when

phase interpolation is enabled ([VExMODE]<PVIEN> = 1).

a. Phase interpolation

<Equation>

theta0 = [VExOMEGA] × [VExTPWM] + [VExTHETA] ; Calculates the value of

phase interpolation

theta0 = theta0 & 0x0000FFFF

if ([VExMODE]<CLPEN> = 1) ; Enables the clipping

if ([VExOMEGA] ≥ 0) ; On positive rotation

if ([VExTHETA] ≤ [VExTHTCLP] ≤ theta0) theta0 = [VExTHTCLP]

else if (theta0 ≤ [VExTHETA] ≤ [VExTHTCLP]) theta0 = [VExTHTCLP]

else if ([VExTHTCLP] ≤ theta0 ≤ [VExTHETA]) theta0 = [VExTHTCLP]

else if ([VExOMEGA] < 0) ; On inverse rotation

if (theta0 ≤ [VExTHTCLP] ≤ [VExTHETA]) theta0 = [VExTHTCLP]

else if ([VExTHTCLP] ≤ [VExTHETA] ≤ theta0) theta0 = [VExTHTCLP]

else if ([VExTHETA] ≤ theta0 ≤ [VExTHTCLP]) theta0 = [VExTHTCLP]

if ([VExMODE]<PVIEN> = 1) [VExTHETA] = theta0 ; Updates the [VExTHETA] value when

phase interpolation is enabled

Input

Output

[VExTHETA]

[VExOMEGA]

[VExTPWM]

[VExTHTCLP]

[VExMODE]

[VExTHETA]

Phase θ 16-bit fixed-point data (0.0 to 1.0, 16 fractional bits)

Rotational speed

PWM period rate

[0] Phase interpolation

enable

[7] Phase clipping

control

Phase θ

16-bit fixed-point data (-1.0 to 1.0, 15 fractional bits)

16-bit data

16-bit fixed-point data (0.0 to 1.0, 16 fractional bits)

<PVIEN>

0: Phase interpolation is disabled

1: Phase interpolation is enabled

<CLPEN>

0: Clipping is disabled 1: Clipping is enabled

16-bit fixed-point data (0.0 to 1.0, 16 fractional bits)

2021-02-24

Rev. 3.1

TXZ/TXZ+ Family

30 / 107

Register name

Function

Detail

Advanced Vector Engine Plus

b. SIN/COS calculation

<Equation>

[VExSINM] = [VExSIN] ; Stores the previous value (for input process)

[VExCOSM] = [VExCOS]

[VExSIN] = SIN ([VExTHETA]) ; Calculates the SIN and COS values

[VExCOS] = SIN ([VExTHETA] + 1 / 4)

if ([VExFMODE]<MREGDIS> = 1) ; Confirms that the previous value is not maintained

[VExSINM] = [VExSIN]

[VExCOSM] = [VExCOS]

Note: SIN: Sine calculation

Input

Output

[VExTHETA]

[VExFMODE]

[VExSIN]

[VExCOS]

[VExSINM]

[VExCOSM]

Phase θ

[9] Selects to store the

previous value of SIN

and COS

The sine value of θ

The cosine value of θ

Previous sine value

Previous cosine value

16-bit fixed-point data (0.0 to 1.0, 16 fractional bits)

<MREGDIS>

0: Previous value is maintained.

1: Previous value is not maintained.

16-bit fixed-point data (-1.0 to 1.0, 15 fractional bits)

2021-02-24

Rev. 3.1

Loading...

Loading...