東芝インテリジェントパワーデバイス シリコンモノリシック集積回路

TPD7101F

2ch ハイサイド nch パワーMOS FET ゲートドライバ

TPD7101F は 2ch のハイサイドスイッチ用 nch パワーMOS FET ゲートド

ライバです。パワーMOS FET のドライバおよび保護、診断機能を内蔵してお

り、大電流アプリケーションのハイサイドスイッチを容易に構成することがで

きます。

特 長

z 大電流チャージポンプにより、高速スイッチングが可能です。

z パワーMOS FET の保護、診断機能を内蔵しています。

保護機能 : 過電圧 (内部素子保護)、過電流保護、VDD電源低下検出

* 過電圧は内部制限。診断およびシャットダウンはしません。

診断機能 : 過電流

z 過大電流検出レベルが外付け抵抗により設定可能です。

z SSOP–24 パッケージ (300mil) で、梱包形態はエンボステーピングです。

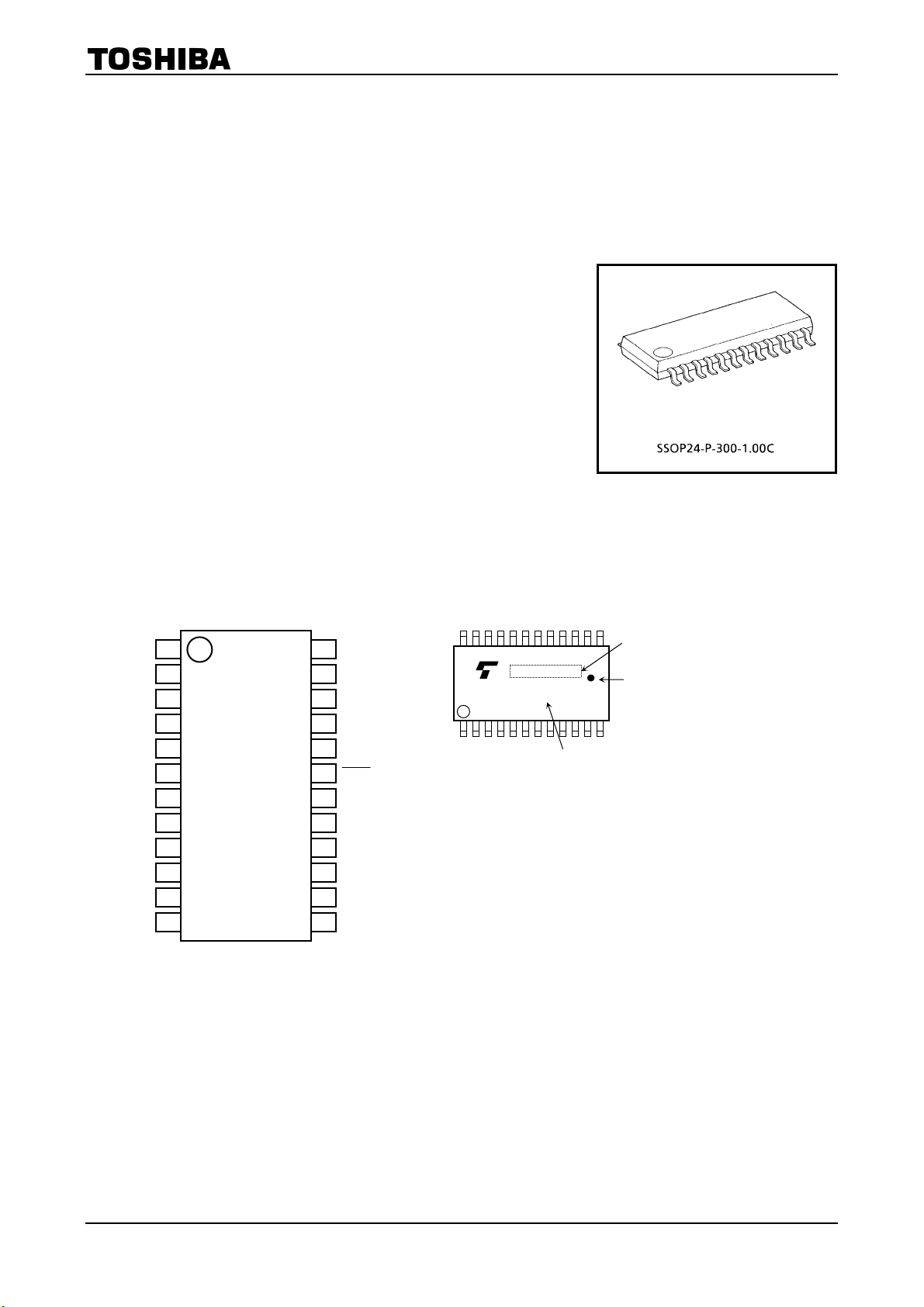

ピン接続 現品表示

質量: 0.29g (標準)

TPD7101F

CP2-

1

CP1-

CP1+

CP2+

V

Vsense1

V

Vsense2

この製品は MOS 構造ですので取り扱いの際には静電気にご注意ください。

2

3

4

5

CPV

6

N.C

7

GS1

8

9

GS2

10

11

GND

12 13

GND

24

23

22

21

20

19

18

17

16

15

14

V

DD1

V

DD2

Rref

RISref1

RISref2

ENB

DIAG1-2

DIAG1-1

DIAG2-2

DIAG2-1

IN1

IN2

TPD7101F

製品名 (または略号)

ロット No.

外装鉛フリー

識別マーク

( なし: 鉛含有

あり: 鉛フリー)

2006-10-31 1

ブロック図

f

f

TPD7101F

DIAG1-1

DIAG1-2

IN1

Rre

Rre

17

18

14

22

DD1

V

CP1+

24 3 2 4 1 5

5V 電源BGR チャージポンプ

入力ロジック

100kΩ

BGR

Iset

5V

マスク回路

Iset

CP1-

CP2+

OSC

ラッチ回路

CP2-

CPV+

28V

レベルシフト回路

+B

V

DD2

23

V

GS1

7

5V

Iset

V

8

RIS

21

SENSE1

ref1

RIS

ref1

負荷

ENB

DIAG2-1

DIAG2-2

IN2

19

15

16

13

100kΩ

V

GS2

9

入力ロジック

100kΩ

マスク回路

Iset

ラッチ回路

レベルシフト回路

5V

Iset

10

20

V

SENSE2

RIS

ref2

RIS

ref2

負荷

11 12

GND GND

2006-10-31 2

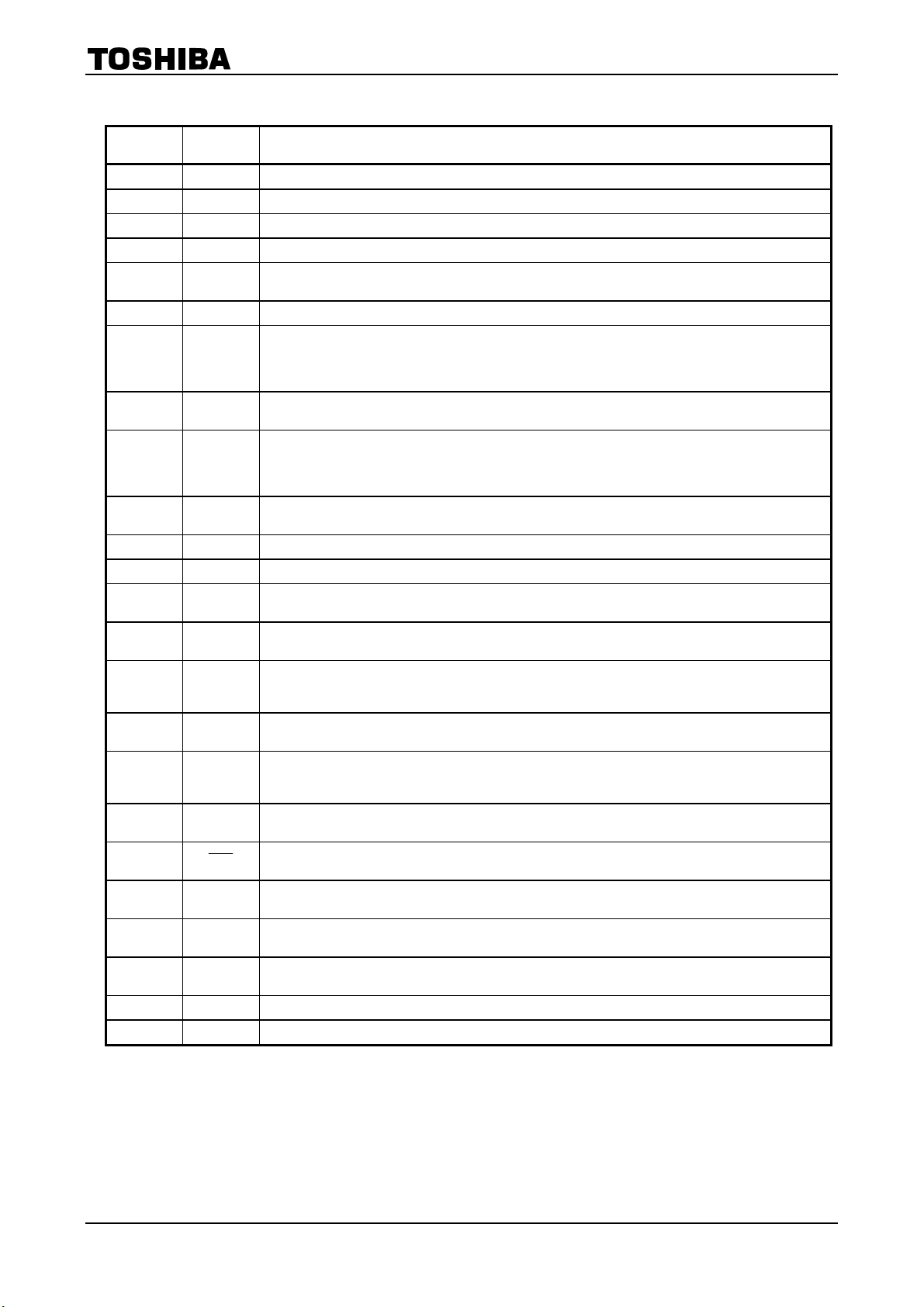

端子説明

端子番号 記号 端子の説明

1 CP2- チャージポンプ用コンデンサ 2 段目の負極側接続端子。

2 CP1- チャージポンプ用コンデンサ 1 段目の負極側接続端子。

3 CP1+ チャージポンプ用コンデンサ 1 段目の正極側接続端子。

4 CP2+ チャージポンプ用コンデンサ 2 段目の正極側接続端子。

5 CPV+

6 N.C. ―

7 V

8 V

9 V

10 V

11 GND 接地端子。内部で 12 ピンと接続されています。

12 GND 接地端子。内部で 11 ピンと接続されています。

13 IN2

14 IN1

15 DIAG2–1

16 DIAG2–2

17 DIAG1–1

18 DIAG1–2

19 ENB

20 RlSref2

21 RlSref1

22 Rref

23 V

24 V

GS1

sense1

GS2

sense2

DD2

DD1

チャージポンプ用コンデンサ 3 段目の正極側接続端子。

の約 3 倍の電圧が発生しますが、電圧クランプ回路により約 28V で制限されます。

V

DD

ch1 の外付けパワーMOS FET のゲートドライブ端子。外付けパワーMOS FET をコントロールする端

子です。

外付けパワーMOS FET に過電流が流れた際には、シャットダウンしてラッチ状態となり、パワーMOS

FET を保護します。ラッチの解除は入力を “L” レベルとした場合に行います。

ch1 の外付けパワーMOS FET のモニタ端子。V

します。

ch2 の外付けパワーMOS FET のゲートドライブ端子。外付けパワーMOS FET をコントロールする端

子です。

外付けパワーMOS FET に過電流が流れた際には、シャットダウンしてラッチ状態となり、パワーMOS

FET を保護します。ラッチの解除は入力を “L” レベルとした場合に行います。

ch2 の外付けパワーMOS FET のモニタ端子。V

します。

ch2 の入力端子。(正論理) プルダウン抵抗 (100kΩ標準) が接続されており、端子がオープン状態に

なっても出力が誤ってオンすることはありません。

ch1 の入力端子。(正論理) プルダウン抵抗 (100kΩ標準) が接続されており、端子がオープン状態に

なっても出力が誤ってオンすることはありません。

ch2 の診断出力端子。nch オープンドレイン端子です。過電流異常状態を検出すると、出力が “L” レ

ベルとなります。また過電流を検出した場合には、次の入力の立ち上がりエッジまでその状態をラッ

チします。

ch2 の診断出力端子。nch オープンドレイン端子です。V

ベルと比較することにより、外付けパワーMOS FET のオン/オフ状態を出力します。

ch1 の診断出力端子。nch オープンドレイン端子です。過電流異常状態を検出すると、出力が “L” レ

ベルとなります。また過電流を検出した場合には、次の入力の立ち上がりエッジまでその状態をラッ

チします。

ch1 の診断出力端子。nch オープンドレイン端子です。V

ベルと比較することにより、外付けパワーMOS FET のオン/オフ状態を出力します。

インヒビット端子。(負論理) この端子が “H” となると、入力信号にかかわらずに、すべての出力をオ

フできます。プルアップ抵抗

ch2

の過電流検出レベル設定端子。Rref 端子に接続された抵抗で決定した定電流と RlSref2 端子の外付

け抵抗で決定される電圧を過電流検出の基準電圧とします。

ch1

の過電流検出レベル設定端子。Rref 端子に接続された抵抗で決定した定電流と RlSref1 端子の外付

け抵抗で決定される電圧を過電流検出の基準電圧とします。

過電流検出回路に使用する定電流値を決定するための抵抗接続端子。

62k

Ω (推奨) を GND 間に接続してください。

外付けパワーMOS FET のドレイン電圧検出端子。

電源端子。過電圧が印加されると電圧を制限し、内部素子を保護します。

(100kΩ標準) が接続されています。

TPD7101F

端子との差電圧と基準電圧を比較し過電流を検出

DD2

端子との差電圧と基準電圧を比較し過電流を検出

DD2

DD2

DD2

と V

と V

端子間の電圧を過電流設定レ

sense2

端子間の電圧を過電流設定レ

sense1

2006-10-31 3

TPD7101F

絶対最大定格

電源電圧 V

入力電圧 V

診断出力電流 I

許容損失 P

動作温度 T

保存温度 T

(Ta = 25°C)

項目 記号 定格 単位

30 V

DD

-0.5~6 V

IN

2 mA

DIAG

0.8 W

D

-40~110 °C

opr

-55~150 °C

stg

注: 本製品の使用条件 (使用温度/電流/電圧等) が絶対最大定格/動作範囲以内での使用においても、高負荷 (高温お

よび大電流/高電圧印加、多大な温度変化等) で連続して使用される場合は、信頼性が著しく低下するおそれが

あります。

弊社半導体信頼性ハンドブック (取り扱い上のご注意とお願いおよびディレーティングの考え方と方法) およ

び個別信頼性情報 (信頼性試験レポート、推定故障率等) をご確認の上、適切な信頼性設計をお願いします。

電気的特性

動作電源電圧 V

消費電流I

入力電圧

入力電流

出力電圧

出力電流

過大電流検出抵抗設定範囲 RlSref RlSref ― 10 20 40 kΩ

定電流源設定端子電圧 VRref Rref Rref = 62kΩ 1.17 1.30 1.43 V

過電流検出電圧

診断出力電流 I

診断出力電圧 V

電源低下検出電圧 V

電源低下検出解除電圧 V

低電圧保護V

スイッチングタイム

特に指定のない場合、

(

項目 記号 端子 測定条件 最小 標準 最大 単位

DD

V

IN (1)

V

IN (2)

I

IN (1)

I

IN (2)

I

I

VOH V

VOL V

IOH

IOL

V

DS (ON) (1)

V

DS (ON) (2)

V

DS (ON) (3)

DH

DDUV1

DDUV1

DDUV2

tON ― 2 5

t

OFF

VDD = 8~18V、Tj = -40~110°C)

V

DD

V

V

V

)1(ENB

)2(ENB

Rref = 62kΩ, RlSref = 10kΩ 0.16 0.20 0.24

Rref = 62kΩ, RlSref = 20kΩ 0.32 0.40 0.48

V

DL

― 6.3 6.7 7.3

-

― 6.6 7.2 7.8

+

― 8 ― 18 V

DD

= 12V, VIN = 0V,

V

DD

DD

IN1, IN2

IN1, IN2

ENB

V

GS1

V

GS2

V

DD2

V

sense1

V

sense2

DIAG1

DIAG2

V

DD

V

GS1

V

GS2

CP = 0.01

DD

VDD = 12V, VGS = “L” ― ― 1.5

DD

VDD = 12V, VIN = 0V -1 ― 1

V

DD

VDD = 12V, 0V

DD

DD

V

DD

CP = 0.01

V

DD

CP = 0.01

Rref = 62k

DD

VDD = 12V, IDL = 1mA ― ― 0.6 V

V

DD

μF

= 12V, VGS = “H” 3.5 ― ―

= 12V, VIN = 5V ― ― 200

= 12V, 5V

= 12V, VIN = 5V ―

= 12V, VIN = 0V ― ― 0.4

= 12V, VIN = 5V,

= 12V, VIN = 0V,

= 12V, V

= 12V, C = 3000pF

V = -45 ― ―

ENB

V = -250 ― ―

ENB

μF

μF

Ω, RlSref = 40kΩ 0.64 0.80 0.96

= 5V ― ― 10 μA

DIAG

― ― ― 4.5

― ― 10 mA

V

*

sense

+15

― 0.1 ―

― 0.1 ―

― 2 5

V

sense

+19

*

V

μA

V

A

V

V

μs

* : Vsense は Vsense 端子電圧

過電流検出抵抗 (RlSref) の計算式

RlSref = Rref×R

DS (ON)×ID

/VRref = Rref×V

DS (ON)

/VRref

ただし、 Rref : Rref 端子に接続される外付け抵抗 (定電流設定用)

R

V

: 外付け MOS FET のオン抵抗 ID : 外付け MOS FET のドレイン電流

DS (ON)

: 外付け MOS FET のオン電圧 VRref : Rref 端子電圧

DS (ON)

2006-10-31 4

真理値表

IN ENB VGS DIAG*–1 DIAG*–2 モード

L H L H H

H H L H H

L L L H H

H L H H (注 1) L

L L L H H

H L H H (注 1) L

L L L L (注 1/注 2) H

H L L L (注 1) H

L L L H H

H L H H H

L L L H H

H L L H H

L L L H L

H L H H L

TPD7101F

正常時

過電圧時

過電流時

電源低下検出

低電圧保護

パワーMOS FET

ショート時

注 1: 過電流はパワーMOS FET のドレイン・ソース間電圧を検出しているため、入力を “H” としてパワーMOS

FET がオンするまでの間はドレイン・ソース間電圧が高く、一時的に過電流を誤検出することがあります。

このため、誤検出しないようマスク回路で 15μs (標準) の期間 DIAG 機能は動作しません。

このマスク時間は内蔵コンデンサと Rref で決定される定電流により決まります (15μs は Rref が 62kΩの場

合です)。

注 2: 過電流を検出した後は、次の入力の立ち上がりエッジまで、DIAG はラッチされます。

タイミングチャート

入力信号

過電圧検出

過大電流検出

V

電源低下検出

DD

V

低電圧検出

DD

パワーMOS FET

ショート

出力信号

(V

出力電圧)

GS

DIAG*-1

IN

ENB

信号

DIAG*-2

信号

2006-10-31 5

応用回路例 1 パワーMOS FETのドレイン・ソース間をモニタ

f

f

TPD7101F

5V

V

CC

IN

17

DIAG1

24 23

V

DD1

CPU

IN

OUT

18

14

DIAG2

TPD7101F

IN

OUT

19

ENB

GND

Rref

22

Rref

GND GND

11 12

応用回路例 2 シャント抵抗間電圧をモニタ

5V

V

CPU

GND

CC

IN

IN

OUT

OUT

Rref

17

18

14

19

22

DIAG1

DIAG2

IN

ENB

Rref

24 23

V

DD1

TPD7101F

GND GND

11 12

防湿梱包に関する注意事項

V

DD2

V

GS

7

V

sense

8

RISre

21

RISref

過電流を高精度で検出する場合

(

+B

nch

負荷

+B

パワーMOSFET

V

DD2

V

GS

7

シャント抵抗

Rshunt

パワーMOSFET

nch

V

sense

8

RISre

21

RISref

負荷

)

防湿梱包開封後は 30°C・RH60%以下の環境で 48 時間以内に実装していただくようお願いします。エンボステーピ

ングのためべーキング処理ができませんので、かならず防湿梱包開封後の許容範囲内にてご使用ください。

テーピングの標準梱包数量は、2000 個/リール (EL1) です。

2006-10-31 6

外形図

TPD7101F

2006-10-31 7

TPD7101F

当社半導体製品取り扱い上のお願い

• 当社は品質,信頼性の向上に努めておりますが,一般に半導体製品は誤作動したり故障することがあります。当

社半導体製品をご使用いただく場合は,半導体製品の誤作動や故障により,生命・身体・財産が侵害されること

のないように,購入者側の責任において,機器の安全設計を行うことをお願いします。

なお,設計に際しては,最新の製品仕様をご確認の上,製品保証範囲内でご使用いただくと共に,考慮されるべ

き注意事項や条件について「東芝半導体製品の取り扱い上のご注意とお願い」,「半導体信頼性ハンドブック」な

どでご確認ください。

• 本資料に掲載されている製品は,一般的電子機器(コンピュータ,パーソナル機器,事務機器,計測機器,産業

用ロボット,家電機器など)に使用されることを意図しています。特別に高い品質・信頼性が要求され,その故

障や誤作動が直接人命を脅かしたり人体に危害を及ぼす恐れのある機器(原子力制御機器,航空宇宙機器,輸送

機器,交通信号機器,燃焼制御,医療機器,各種安全装置など)にこれらの製品を使用すること(以下“特定用

途”という)は意図もされていませんし,また保証もされていません。本資料に掲載されている製品を当該特定用

途に使用することは,お客様の責任でなされることとなります。

• 本資料に掲載されている製品を,国内外の法令,規則及び命令により製造,使用,販売を禁止されている応用製

品に使用することはできません。

• 本資料に掲載してある技術情報は,製品の代表的動作・応用を説明するためのもので,その使用に際して当社及

び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

• 本資料に掲載されている製品の RoHS 適合性など、詳細につきましては製品個別に必ず弊社営業窓口までお問合

せください。本資料に掲載されている製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令な

どの法令を十分調査の上、かかる法令に適合するようご使用ください。お客様が適用される法令を遵守しないこ

とにより生じた損害に関して、当社は一切の責任を負いかねます。

20070701-JA

• 本資料の掲載内容は,技術の進歩などにより予告なしに変更されることがあります。

2006-10-31 8

Loading...

Loading...