查询TMP19A64F20AXBG供应商

32 bit TX System RISC

TX19A Family

TMP19A64F20AXBG

Rev1.1 2007.March.16

Contents

TMP19A64F20AXBG

1. ・Overview and Features

2. ・Pin Layout and Pin Functions

3. ・Flash Memory Operation

4. ・Electrical Characteristics

TMP19A64F20AXBG

TMP19A64(rev1.1)-1

32-bit RISC Microprocessor - TX19 Family

TMP19A64F20AXBG

1. Overview and Features

TMP19A64F20AXBG

The TX19 family is a high-performance 32-bit RISC processor series that TOSHIBA originally developed by

integrating the MIPS16

TM

ASE (Application Specific Extension), which is an extended instruction set of high code

efficiency.

TMP19A64 is a 32-bit RISC microprocessor with a TX19A processor core and various peripheral functions

integrated into one package. It can operate at low volt age wi t h low po wer consumption.

Features of TMP19A64 are as follows:

(1) TX19A processor core

1) Improved code efficiency and operating performance have been realized through the use of two ISA

(Instruction Set Architecture) modes - 16- and 32-bit ISA modes.

• The 16-bit ISA mode instructions are compatible with the MIPS16

code efficiency at the object level.

• The 32-bit ISA mode instructions are compatible with the TX39 instructions of superior operating

performance at the object level.

2) Both high performance and low power consumption have been achieved.

z High performance

RESTRICTIONS ON PRODUCT USE

TM

ASE instructions of superior

070122EBP

• The information contained herein is subject to change without notice. 021023_D

• TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in

general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility

of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire

system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life,

bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in

the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the

“Handling Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc. 021023_A

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal

equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products

are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a

malfunction or failure of which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include

atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments,

combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products

listed in this document shall be made at the customer’s own risk. 021023_B

• The products described in this document shall not be used or embedded to any downstream pro ducts of which manufacture,

use and/or sale are prohibited under any applicable laws and regulations. 060106_Q

• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed

by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is

granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties. 070122_C

• The products described in this document are subject to foreign exchange and foreign trade control laws. 060925_E

• For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled

Quality and Reliability Assurance/Handling Precautions. 030619_S

TMP19A64(rev1.0)1-1

TMP19A64F20AXBG

• Almost all instructions can be executed with one clock.

• High performance is possible via a three-operand operation instruction.

• 5-stage pipeline

• Built-in high-speed memory

• DSP function: A 32-bit multiplication and accumulation operation can be executed with one clock.

z Low power consumption

• Optimized design using a low power consumption library

• Standby function that stops the operation of the processor core

3) High-speed interrupt response suitable for real-time control

• Independency of the entry address

• Automatic generation of factor-specific vector addresses

• Automatic update of interrupt mask levels

(2) On Chip program memory and data memory

Product name On chip ROM On chip RAM

TMP19A64F20AXBG 2 Mbytes (Flash) 64 Kbytes

TMP19A64C1DXBG 1.5 Mbytes 56 Kbytes

• ROM correction function: 1 word × 8 blocks, 8 words × 4 blocks

• Backup RAM: 512 bytes

(3) External memory expansion

• 16-Mbyte off-chip address for code and date

• External data bus:

Separate bus/multiplexed bus : Dynamic bus sizing for 8- and 16-bit widths ports.

• Chip select/wait controller : 6 channels

(4) DMA controller : 8 channels

• Data to be transferred to internal memory, internal I/O, external memory, and external I/O

(5) 16-bit timer : 11 channels

• 16-bit interval timer mode

• 16-bit event counter mode

• 16-bit PPG output

• Event capture function

• 2-phase pulse input counter function (1 channel assign ed to perform this function):

Multiplication-by-4 mode

(6) 32-bit timer

• 32-bit input capture register : 4 channels

• 32-bit compare register : 10 channels

• 32-bit time base timer : 1 channel

(7) Clock timer : 1 channel

(8) General-purpose serial interface: 7 channels

• Either UART mode or synchronous mode can be selected.

(9) Serial bus interface : 1 channel

• Either I

2

C bus mode or clock synchronous mode can be selected

TMP19A64(rev1.0)1-2

TMP19A64F20AXBG

(10) 10-bit A/D converter with (S/H) : 24 channels

• Conversion speed: 54 clocks (7.85 μs@54 MHz)

• Start by an internal timer trigger

• Fixed channel/scan mode

• Single/repeat mode

• High-priority conversion mode

• Timer monitor function

(11) Watchdog timer : 1 channel

(12) Interrupt source

• CPU: 2 factors.............software interrupt instruction

• Internal: 50 factors.......The order of precedence can be set over 7 levels

(except the watchdog timer interrupt).

• External: 20 factors......The order of precedence can be set over 7 levels

(except the NMI interrupt).

Because 8 factors are associated with KWUP, the number of interrupt

factors is one.

(13) 209 pins Input/output ports

(14) Standby mode

• 4 standby modes (IDLE, SLEEP, STOP and BACKUP)

(15) Clock generator

• On-chip PLL (multiplication by 4)

• Clock gear function: The hi g h -speed clock can be divided into 8/8, 7/8, 6/8, 5/8, 4/ 8, 2/8 or 1/8.

• Sub-clock: SLOW, SLEEP and BACKUP modes (32.768 kHz)

(16) Endian: Bi-endian (big-endian/little-endian)

(17) Maximum operating frequency

• 54 MHz (PLL multiplication)

(18) Operating voltage range

Core: 1.35 V to 1.65 V

I/O: 1.65 V to 3.3 V

ADC: 2.7 V to 3.3 V

Backup block : 2.3 V to 3.3 V (under normal operating conditions)

: 1.8 V to 3.3 V (in BACKUP mode)

(19) Package

• P-FBGA281 (13 mm × 13 mm, 0.65 mm pitch)

TMP19A64(rev1.0)1-3

(

(

(

(

(

TMP19A64F20AXBG

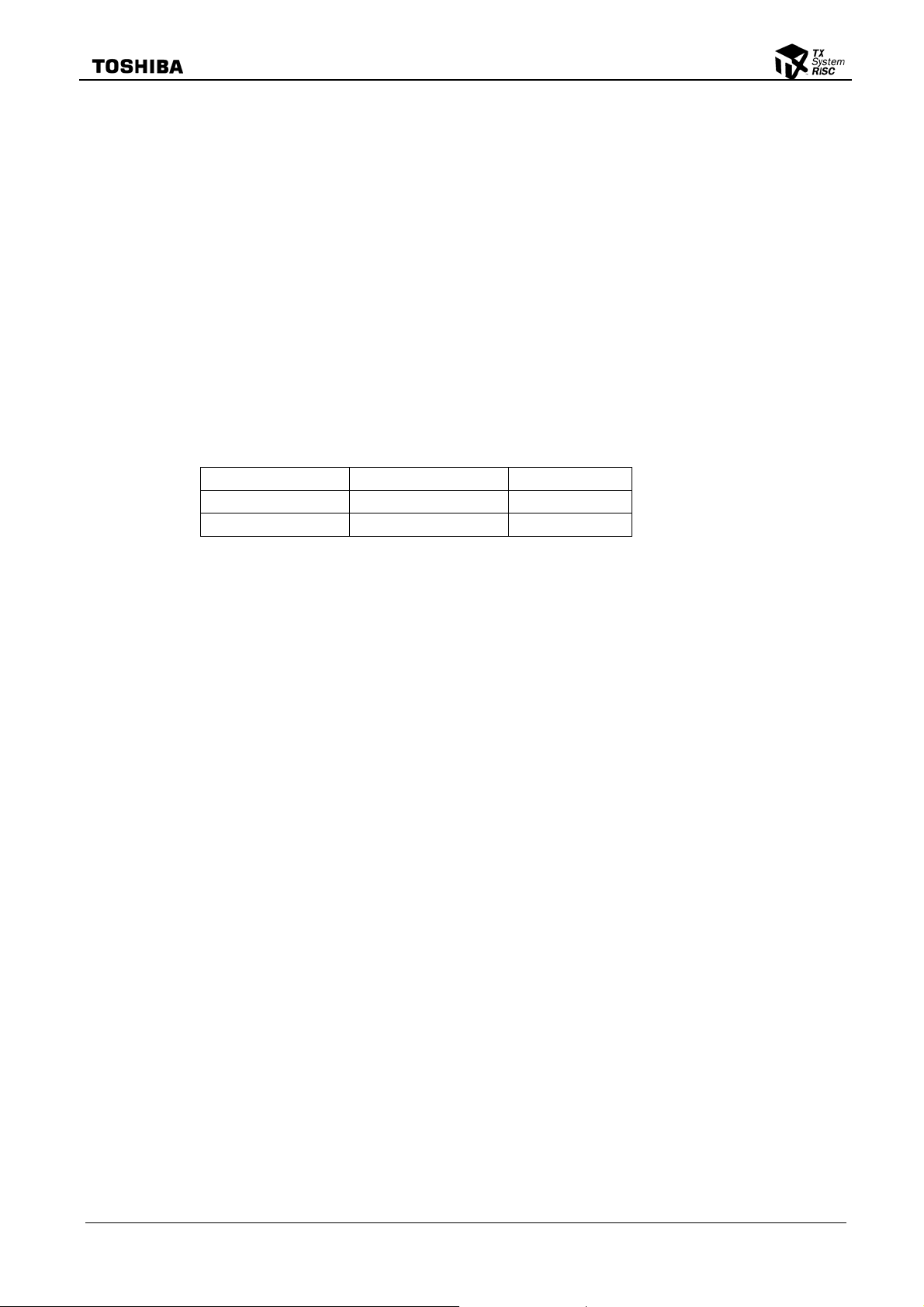

TX19 Processor Core

TX19A CPU

MAC

EJTAG

2-Mbyte

Flash

64-Kbyte

RAM

DMAC

8ch)

INTC EBIF

ROM correction

CG

Backup block

Clock timer (1ch)

Backup RAM

(512 bytes)

I/O bus I/F

PORT0

to

PORT6

(also function as

external bus I/F)

16-bit TMRB

0 to A

11ch)

32-bit TMRC

TBT (1ch)

32-bit TMRC

Input Capture

0 to 3

4ch)

32-bit TMRC

Compare

0 to 9

10ch)

10-bit ADC (24ch)

SIO/UART

0 to 6 (7ch)

I2C/SIO

1ch)

PORT7

to

PORT9

(also function to

receive ADC inputs)

PORTA

to

PORTK, PORTO

(also function as

functional pins)

PORTL t o PORT N

PORTP to PORTQ

(General-purpose ports)

KWUP

0 to 7 (8ch)

WDT

Fig. 1-1 TMP19A64F20AXBG Block Diagram

TMP19A64(rev1.0)1-4

A1 A2 A3 A4A5 A6 A7A8A9A10A11A12A13A

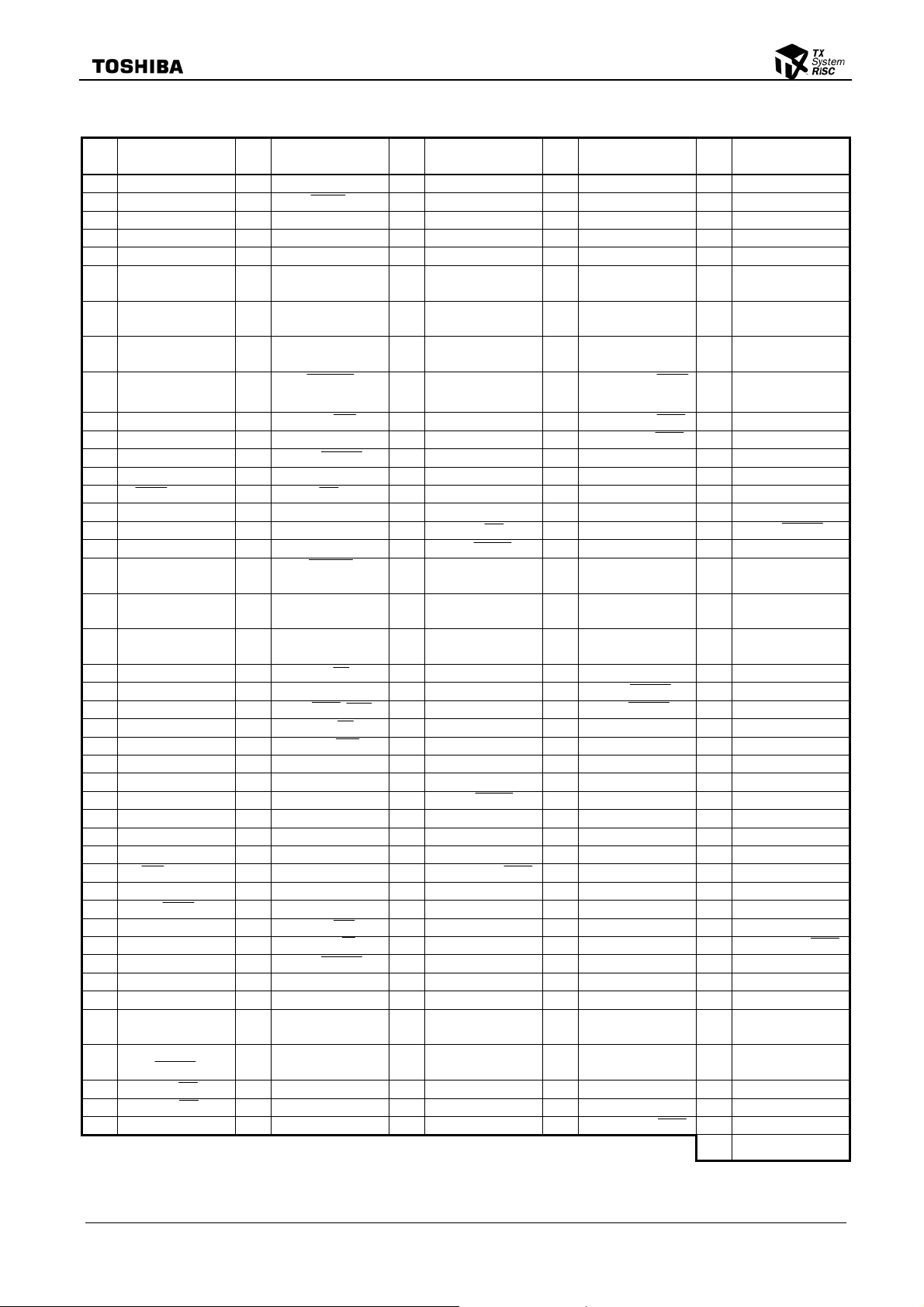

2. Pin Layout and Pin Functions

2.1 Pin Layout

Fig. 2.1.1 shows the pin layout of TMP19A64.

Fig. 2.1.1 Pin Layout Diagram (P-FBGA281)

B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17 B18

C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17 C18

C1

D1

D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 D16 D17 D18

E2 E3 E4 E5 E6 E7 E8 E9 E10 E11 E12 E13 E14 E15 E16 E17 E18

E1

F1

F2 F3 F4 F5 F7 F8 F9 F10 F11 F12 F14 F15 F16 F17 F18

G2 G3 G4 G5 G6 G13 G14 G15 G16 G17 G18

G1

H1

H2 H3 H4 H5 H6 H13 H14 H15 H16 H17 H18

J1

J2 J3 J4 J5 J6 J13 J14 J15 J16 J17 J18

K1 K2 K3 K4 K5 K6 K13 K14 K15 K16 K17 K18

L1

L2 L3 L4 L5 L6 L13 L14 L15 L16 L17 L18

M1 M2 M3 M4 M5 M6 M13 M14 M15 M16 M17 M18

N2 N3 N4 N5 N7 N8 N9 N10 N11 N12 N14 N15 N16 N17 N18

N1

P2 P3 P4 P5 P6 P7 P8 P9 P10 P11 P12 P13 P14 P15 P16 P17 P18

P1

R1

R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R14 R15 R16 R17 R18

T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17 T18

T1

U2 U3 U4 U5 U6 U7 U8 U9 U10 U11 U12 U13 U14 U15 U16 U17 U18

U1

V3 V4 V5 V6 V7 V8 V9 V10 V11 V12 V13 V14 V15 V16 V17

V2

TMP19A64F20AXBG

14 A15 A16 A17

Table 2.1.2 shows the pin numbers and names of TMP19A64.

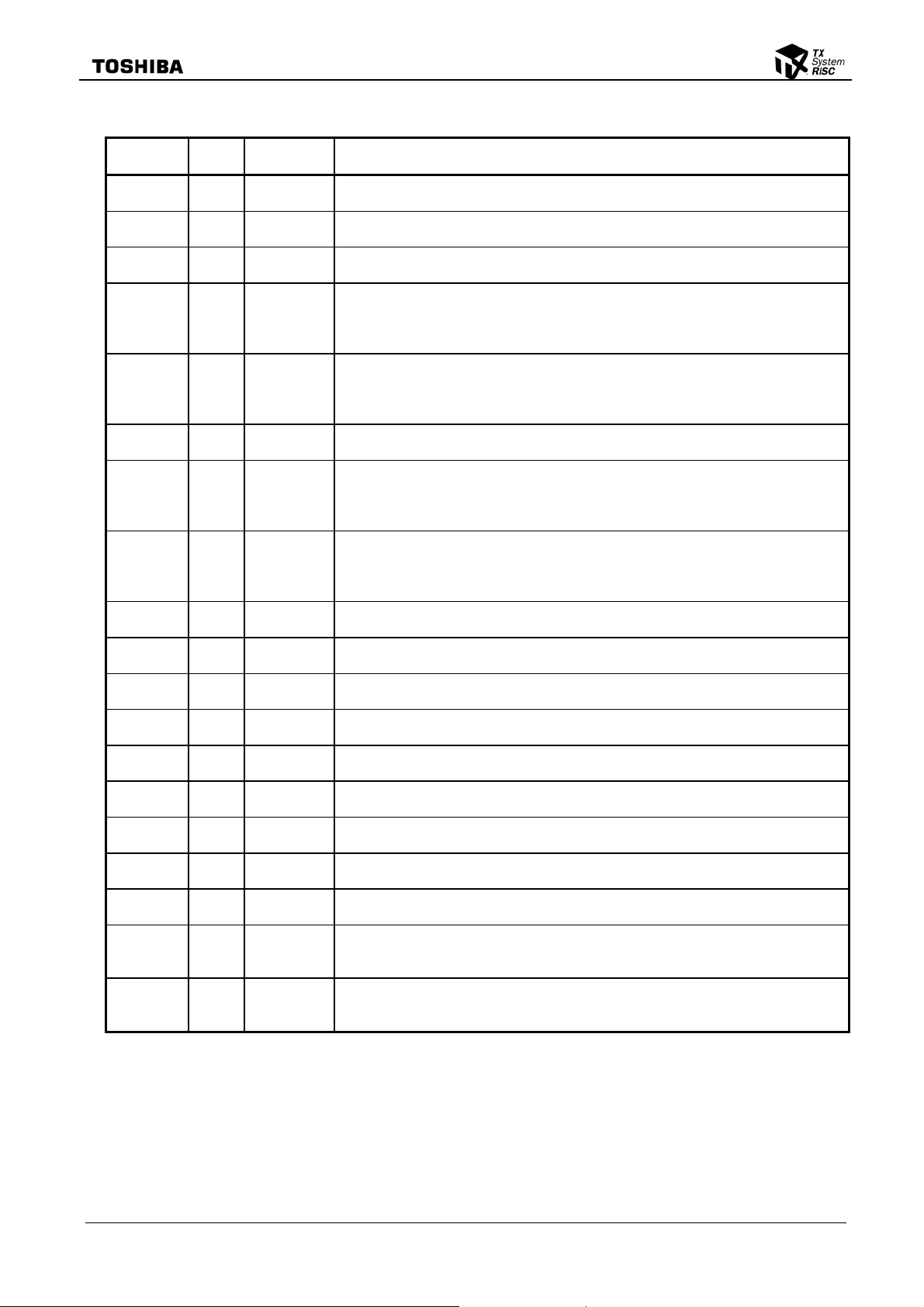

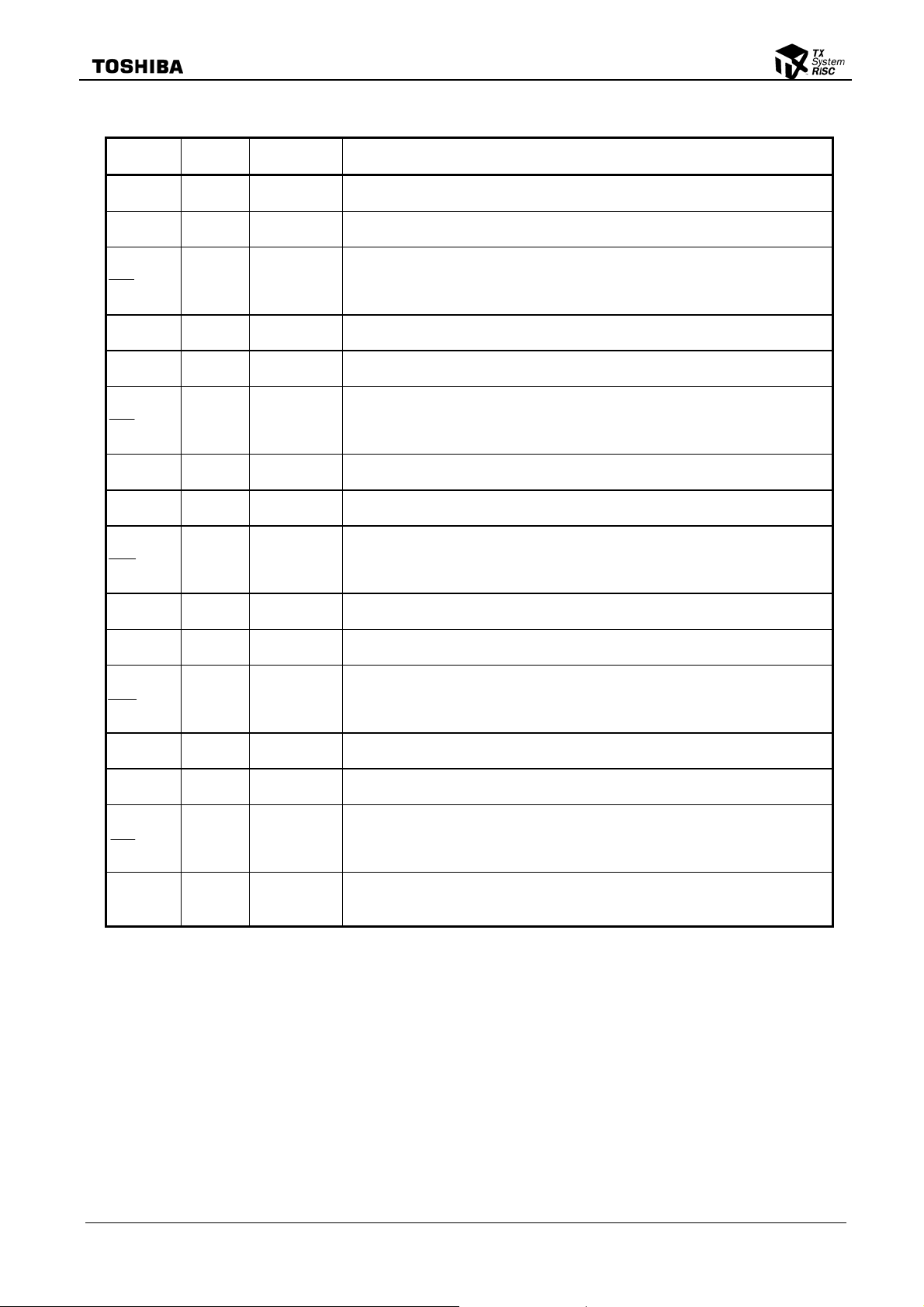

Table 2.1.2 Pin Numbers and Names (1 of 2)

Pin

No.

A1 N.C. A13 PN2 B8 P75/AN5 C2 PCST3 (EJTAG) C14 PM7

A2 VREFL A14 PN0 B9 PL0 C3 P92/AN18 C15 PM3

A3 P90/AN16 A15 PM5 B10 PL3 C4 P95/AN21 C16 PK3/KEY3

A4 P93/AN19 A16 PM1 B11 PO5/TXD6 C5 P82/AN10 C17 CVCC15

A5 P80/AN8 A17 X2 B12 PO1/INT1 C6 P85/AN13 C18 XT2

A6 P83/AN11 B1 AVCC31 B13 PN3 C7 P72/AN2 D1 TDO (EJTAG)

A7 P70/AN0 B2 VREFH B14 PN1 C8 AVSS D2 PCST2 (EJTAG)

A8 P74/AN4 B3 P91/AN17 B15 PM4 C9 PL1 D3 DINT (EJTAG)

A9 PO7/SCLK6/CTS6 B4 P94/AN20 B16 PM0 C10 PL4 D4 DVCC15

A10 PL2 B5 P81/AN9 B17 CVSS/BVSS C11 PO4/INT4 D5 P96/AN22

A11 PO6/RXD6 B6 P84/AN12 B18 X1 C12 PN6 D6 P86/AN14

A12 PO0/INT0 B7 P71/AN1 C1 PCST0 (EJTAG) C13 PN4 D7 P73/AN3

Pin name

Pin

No.

Pin name

Pin

No.

Pin name

Pin

No.

Pin name

Pin

No.

Pin name

TMP19A64(rev1.1)2-1

TMP19A64F20AXBG

Table 2.1.1 Pin Numbers and Names (2 of 2)

Pin

No.

D8 DVCC15 F18 P46/SCOUT K14 PI1/INT1 N18 P14/D12/AD12/A12 T8 PD4/TXD4

D9 DVSS G1 RESET K15 PI3/INT3 P1 PE4 T9 PC0/TXD0

D10 PL5 G2 TDI (EJTAG) K16 PI4/INT4 P2 PA2/TB0OUT T10 PC3/TXD1

D11 PO3/INT3 G3 FVCC15 K17 DVCC30 P3 PA3/TB1IN0/INT7 T11 PH4/TCOUT8

D12 PN7 G4 DVSS K18 PI2/INT2 P4 PA4/TB1IN1/INT8 T12 PH6

D13 PN5 G5 TOVR/TSTA

D14 PM2 G6 BW0 L2 PQ1/TPD1/TPC1

D15 DVCC34 G13 PK7/KEY7 L3 PQ2/TPD2/TPC2

D16 PK2/KEY2 G14 BRESET L4 PQ3/TPD3/TPC3

D17 PK4/KEY4 G15 P41/CS1 L5 PE6/INTA P9 PC2/SCLK0/CTS0 T17 P00/D0/AD0

D18 XT1 G16 P37/ALE L6 PE7/INTB P10 PC5/SCLK1/CTS1 T18 P01/D1/AD1

E1 DCLK (EJTAG) G17 P35/BUSAK L13 P13/D11/AD11/A11 P11 P52/A2 U1 PB4/TB8OUT

E2 PCST1 (EJTAG) G18 FVCC15 L14 P17/D15/AD15/A15 P12 P62/A10 U2 PB3/TB7OUT

E3 TRST (EJTAG) H1 NMI L15 FVCC15 P13 P65/A13 U3 PB7/TBAIN1

E4 PCST4 (EJTAG) H2 DVCC31 L16 PI0/INT0 P14 P26/A22/A6/A22 U4 PF1/SI/SCL

E5 ENDIAN H3 PP7/TPD7 (EJTAG) L17 P45/CS5 P15 P02/D2/AD2 U5 PF5/DREQ3

E6 P97/AN23 H4 BW1 L18 PJ3/DACK3 P16 P10/D8/AD8/A8 U6 PG1/TC1IN

E7 P87/AN15 H5 PLLOFF M1 PQ0/TPD0/TPC0

E8 P76/AN6 H6 TCK (EJTAG) M2 PQ7/TPD7/TPC7

E9 P77/AN7 H13 TEST1 M3 PQ4/TPD4/TPC4

E10 PL6 H14 P31/WR M4 PE3 R2 PA1/TB0IN1/INT6 U10 PH1/TCOUT5

E11 PL7 H15 P32/HWR M5 PA7/TB3OUT R3 PF3/DREQ2 U11 PH5/TCOUT9

E12 PM6 H16 P33/WAIT/RDY M6 DVCC32 R4 PF4/DACK2 U12 P50/A0

E13 PK6/KEY6 H17 P30/RD M13 P06/D6/AD6 R5 PF7/TBTIN U13 P55/A5

E14 PK5/KEY5 H18 P40/CS0 M14 P07/D7/AD7 R6 PG7/TCOUT3 U14 DVCC33

E15 BVCC J1 PP2/TPD2 (EJTAG) M15 DVSS R7 PG4/TCOUT0 U15 P64/A12

E16 PK1/KEY1 J2 PP3/TPD3 (EJTAG) M16 PJ0/DREQ2 R8 PD5/RXD4 U16 P20/A16/A0/A16

E17 PK0/KEY0 J3 PP4/TPD4 (EJTAG) M17 PJ2/DREQ3 R9 PC1/RXD0 U17 P24/A20/A4/A20

E18 DVCC15 J4 PP5/TPD5 (EJTAG) M18 PJ1/DACK2 R10 PC4/RXD1 U18 FVCC3

F1 DVSS J5 PP6/TPD6 (EJTAG) N1 PE5 R11 PH3/TCOUT7 V2 PB5/TB9OUT

F2 TMS (EJTAG) J6 FVCC15 N2 PE0/TXD5 R12 P51/A1 V3 PG0/TC0IN

F3 EJE (EJTAG) J13 DVSS N3 PE2/SCLK5/CTS5 R13 P57/A7 V4 PF0/SO/SDA

F4 BUSMD J14 P47 N4 PE1/RXD5 R14 P66/A14 V5 PG3/TC3IN

F5 BOOT J15 N.C. N5 PA6/TB2OUT R15 P25/A21/A5/A21 V6 PG6/TCOUT2

F7 AVSS J16 P44/CS4 N7 DVSS R16 P03/D3/AD3 V7 PD1/TXD3

F8 AVSS J17 P36/ R/W N8 PD7/INT9 R17 P04/D4/AD4 V8 PD0/SCLK2/CTS2

F9 AVCC32 J18 P34/BUSRQ N9 DVCC15 R18 P05/D5/AD5 V9 PC6/TXD2

F10 DVCC34 K1 PP0/TPD0 (EJTAG) N10 DVSS T1 PB0/TB4OUT V10 PH2/TCOUT6

F11 PO2/INT2 K2 PP1/TPD1 (EJTAG) N11 P56/A6 T2 PB1/TB5OUT V11 PH0/TCOUT4

F12 DVSS K3 PQ5/TPD5/TPC5

F14

F15 P42/CS2 K5 DVSS N15 P15/D13/AD13/A13 T5 PF6/DACK3 V14 P60/A8

F16 P43/CS3 K6 DVSS N16 TEST3 T6 PG5/TCOUT1 V15 P63/A11

F17 DVCC33 K13 TEST2 N17 P16/D14/AD14/A14 T7 PD3/SCLK3/CTS3 V16 P67/A15

Pin name

BUPMD

V17 P22/A18/A2/A18

Pin

No.

K4 PQ6/TPD6/TPC6

Pin name

(EJTAG)

(EJTAG)

(EJTAG)

Pin

No.

L1 FVCC3 P5 PA5/TB1OUT T13 P53/A3

N12 DVSS T3 PB2/TB6OUT V12 PH7

N14 P27/A23/A7/A23 T4 PF2/SCK V13 P54/A4

Pin name

(EJTAG)

(EJTAG)

(EJTAG)

(EJTAG)

(EJTAG)

(EJTAG)

Pin

No.

P6 PB6/TBAIN0 T14 P61/A9

P7 PG2/TC2IN T15 P21/A17/A1/A17

P8 PD6/SCLK4/CTS4 T16 P23/A19/A3/A19

P17 P12/D10/AD10/A10 U7 PD2/RXD3

P18 P11/D9/AD9/A9 U8 DVCC32

R1 PA0/TB0IN0/INT5 U9 PC7/RXD2

Pin name

Pin

No.

Pin name

TMP19A64(rev1.1)2-2

2.2 Pin Names and Functions

Table 2.2.1 shows the names and functions of input/output pins.

Table 2.2.1 Pin Names and Functions (1 of 6)

Pin name

P00-P07

D0-D7

AD0-AD7

P10-P17

D8-D15

AD8-AD15

A8-A15

P20-P27

A16-A23

A0-A7

A16-A23

P30

RD

P31

WR

P32

HWR

P33

WAIT

RDY

P34

BUSRQ

P35

BUSAK

P36

R/W

P37

ALE

P40

CS0

P41

CS1

P42

CS2

P43

CS3

P44

CS4

P45

CS5

P46

SCOUT

P47 1 Input/output Port 47: Input/output port

P50-P57

A0-A7

P60-P67

A8-A15

Number

of pins

8 Input/output

8 Input/output

8 Input/output

1 Output

1 Output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

8 Input/output

8 Input/output

Input or

output

Input/output

Input/output

Input/output

Input/output

Output

Output

Output

Output

Output

Output

Output

Input

Input

Input

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Port 0: Input/output port that allows input/output to be set in units of bits

Data (lower): Data buses 0 to 7 (separate bus mode)

Address data (lower): Address data buses 0 to 7 (multiplexed bus mode)

Port 1: Input/output port that allows input/output to be set in units of bits

Data (upper): Data buses 8 to 15 (separate bus mode)

Address data (upper): Address data buses 8 to 15 (multiplexed bus mode)

Address: Address buses 8 to 15 (multiplexed bus mode)

Port 2: Input/output port that allows input/output to be set in units of bits

Address: Address buses 16 to 23 (separate bus mode)

Address: Address buses 0 to 7 (multiplexed bus mode)

Address: Address buses 16 to 23 (multiplexed bus mode)

Port 30: Port used exclusively for output

Read: Strobe signal for reading external memory

Port 31: Port used exclusively for output

Write: Strobe signal for writing data of D0 to D7 pins

Port 32: Input/output port (with pull-up)

Write upper-pin data: Strobe signal for writing data of D8 to D15 pins

Port 33: Input/output port (with pull-up)

Wait: Pin for requesting CPU to put a bus in a wait state

Ready: Pin for notifying CPU that a bus is ready

Port 34: Input/output port (with pull-up)

Bus request: Signal requesting CPU to allow an external master to take the bus control authority

Port 35: Input/output port (with pull-up)

Bus acknowledge: Signal notifying that CPU has released the bus control authority in response

to BUSRQ

Port 36: Input/output port (with pull-up)

Read/write: "1" shows a read cycle or a dummy cycle. "0" shows a write cycle.

Port 37: Input/output port

Address latch enable (address latch is enabled only if access to external memory is taking place)

Port 40: Input/output port (with pull-up)

Chip select 0: "0" is output if the address is in a designated address area.

Port 41: Input/output port (with pull-up)

Chip select 1: "0" is output if the address is in a designated address area.

Port 42: Input/output port (with pull-up)

Chip select 2: "0" is output if the address is in a designated address area.

Port 43: Input/output port (with pull-up)

Chip select 3: "0" is output if the address is in a designated address area.

Port 44: Input/output port (with pull-up)

Chip select 4: "0" is output if the address is in a designated address area.

Port 45: Input/output port (with pull-up)

Chip select 5: "0" is output if the address is in a designated address area.

Port 46: Input/output port

System clock output: Selectable between high- and low-speed clock outputs, as in the case of

CPU

Port 5: Input/output port that allows input/output to be set in units of bits

Address: Address buses 0 to 7 (separate bus mode)

Port 6: Input/output port that allows input/output to be set in units of bits

Address: Address buses 8 to 15 (separate bus mode)

TMP19A64F20AXBG

Function

TMP19A64(rev1.1)2-3

Pin name

P70-P77

AN0-AN7

P80-P87

AN8-AN15

P90-P97

AN16-AN23

PA0

TB0IN0

INT5

PA1

TB0IN1

INT6

PA2

TB0OUT

PA3

TB1IN0

INT7

PA4

TB1IN1

INT8

PA5

TB1OUT

PA6

TB2OUT

PA7

TB3OUT

PB0

TB4OUT

PB1

TB5OUT

PB2

TB6OUT

PB3

TB7OUT

PB4

TB8OUT

PB5

TB9OUT

PB6

TBAIN0

PB7

TBAIN1

Number

of pins

8 Input

8 Input

8 Input

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

Input or

output

Input

Input

Input

Input

Input

Input

Input

Output

Input

Input

Input

Input

Output

Output

Output

Output

Output

Output

Output

Output

Output

Input

Input

TMP19A64F20AXBG

Table 2.2.1 Pin Names and Functions (2 of 6)

Function

Port 7: Port used exclusively for input

Analog input: Input from A/D converter

Port 8: Port used exclusively for input

Analog input: Input from A/D converter

Port 9: Port used exclusively for input

Analog input: Input from A/D converter

Port A0: Input/output port

16-bit timer 0 input 0: For inputting the count/capture trigger of a 16-bit timer 0

Interrupt request pin 5: Selectable between "H" level, "L" level, rising edge, and falling edge

Input pin with Schmitt trigger

Port A1: Input/output port

16-bit timer 0 input 1: For inputting the count/capture trigger of a 16-bit timer 0

Interrupt request pin 6: Selectable "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port A2: Input/output port

16-bit timer 0 output: 16-bit timer 0 output pin

Port A3: Input/output port

16-bit timer 1 input 0: For inputting the count/capture trigger of a 16-bit timer 1

Interrupt request pin 7: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port A4: Input/output port

16-bit timer 1 input 1: For inputting the count/capture trigger of a 16-bit timer 1

Interrupt request pin 8: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port A5: Input/output port

16-bit timer 1 output: 16-bit timer 1 output pin

Port A6: Input/output port

16-bit timer 2 output: 16-bit timer 2 output pin

Port A7: Input/output port

16-bit timer 3 output: 16-bit timer 3 output pin

Port B0: Input/output port

16-bit timer 4 output: 16-bit timer 4 output pin

Port B1: Input/output port

16-bit timer 5 output: 16-bit timer 5 output pin

Port B2: Input/output port

16-bit timer 6 output: 16-bit timer 6 output pin

Port B3: Input/output port

16-bit timer 7 output: 16-bit timer 7 output pin

Port B4: Input/output port

16-bit timer 8 output: 16-bit timer 8 output pin

Port B5: Input/output port

16-bit timer 9 output: 16-bit timer 9 output pin

Port B6: Input/output port

16-bit timer A input 0: for inputting the count/capture trigger of a 16-bit timer A

2-phase pulse counter input 0

Port B7: Input/output port

16-bit timer A input 1: For inputting the count/capture trigger of a 16-bit timer A

2-phase pulse counter input 1

TMP19A64(rev1.1)2-4

Pin name

PC0

TXD0

PC1

RXD0

PC2

SCLK0

CTS0

PC3

TXD1

PC4

RXD1

PC5

SCLK1

CTS1

PC6

TXD2

PC7

RXD2

PD0

SCLK2

CTS2

PD1

TXD3

PD2

RXD3

PD3

SCLK3

CTS3

PD4

TXD4

PD5

RXD4

PD6

SCLK4

CTS4

PD7

INT9

Number

of pins

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

Input or

output

Output

Input

Input/output

Input

Output

Input

Input/output

Input

Output

Input

Input/output

Input

Output

Input

Input/output

Input

Output

Input

Input/output

Input

Input

TMP19A64F20AXBG

Table 2.2.1 Pin Names and Functions (3 of 6)

Function

Port C0: Input/output port

Sending serial data 0: Open drain output pin depending on the program used

Port C1: Input/output port

Receiving serial data 0

Port C2: Input/output port

Serial clock input/output 0

Ready to send serial data 0 (Clear To Send): Open drain output pin depending on the program

used

Port C3: Input/output port

Sending serial data 1: Open drain output pin depending on the program used

Port C4: Input/output port

Receiving serial data 1

Port C5: Input/output port

Serial clock input/output 1

Ready to send serial data 1 (Clear To Send): Open drain output pin depending on the program

used

Port C6: Input/output port

Sending serial data 2: Open drain output pin depending on the program used

Port C7: Input/output port

Receiving serial data 2

Port D0: Input/output port

Serial clock input/output 2

Ready to send serial data 2 (Clear To Send): Open drain output pin depending on the program

used

Port D1: Input/output port

Sending serial data 3: Open drain output pin depending on the program used

Port D2: Input/output port

Receiving serial data 3

Port D3: Input/output port

Serial clock input/output 3

Ready to send serial data 3 (Clear To Send): Open drain output pin depending on the program

used

Port D4: Input/output port

Sending serial data 4: Open drain output pin depending on the program used

Port D5: Input/output port

Receiving serial data 4

Port D6: Input/output port

Serial clock input/output 4

Ready to send serial data 4 (Clear To Send): Open drain output pin depending on the program

used

Port D7: Input/output port

Interrupt request pin 9: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

TMP19A64(rev1.1)2-5

TMP19A64F20AXBG

Table 2.2.1 Pin Names and Functions (4 of 6)

Pin name

PE0

TXD5

PE1

RXD5

PE2

SCLK5

CTS5

PE3-PE5 3 Input/output Ports E3 to E5: Input/output ports that allow input/output to be set in units of bits

PE6

INTA

PE7

INTB

PF0

SO

SDA

PF1

SI

SCL

PF2

SCK

PF3

DREQ2

PF4

DACK2

PF5

DREQ3

PF6

DACK3

PF7

TBTIN

PG0-PG3

TC0IN-TC3IN

PG4-PG7

TCOU0-TCOUT3

PH0-PH5

TCOU4-TCOUT9

PH6-PH7 2 Input/output Ports H6 to H7: Input/output ports that allow input/output to be set in units of bits

PI0

INT0

PI1

INT1

PI2

INT2

Number

of pins

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

1 Input/output

4 Input/output

4 Input/output

6 Input/output

1 Input/output

1 Input/output

1

Input or

output

Output

Input

Input/output

Input

Input

Input

Output

Input/output

Input

Input/output

Input/output

Input

Output

Input

Output

Input

Input

Output

Output

Input

Input

Input/output

Input

Function

Port E0: Input/output port

Sending serial data 5: Open drain output pin depending on the program used

Port E1: Input/output port

Receiving serial data 5

Port E2: Input/output port

Serial clock input/output 5

Ready to send serial data 5 (Clear To Send): Open drain output pin depending on the program

used

Port E6: Input/output port

Interrupt request pin A: Selectable between "H" level, "L" level, rising edge, and falling edge

Input pin with Schmitt trigger

Port E7: Input/output port

Interrupt request pin B: Selectable between "H" level, "L" level, rising edge, and falling edge

Input pin with Schmitt trigger

Port F0: Input/output port

Pin for sending data if the serial bus interface operates in the SIO mode

Pin for sending and receiving data if the serial bus interface operates in the I

Open drain output pin depending on the program used.

Input with Schmitt trigger

Port F1: Input/output port

Pin for receiving data if the serial bus interface operates in the SIO mode

Pin for inputting and outputting a clock if the serial bus interface operates in the I

Open drain output pin depending on the program used

Input with Schmitt trigger

Port F2: Input/output port

Pin for inputting and outputting a clock if the serial bus interface operates in the SIO mode

Port F3: Input/output port

DMA request signal 2: For inputting the request to transfer data by DMA from an external I/O

device to DMAC2

Port F4: Input/output port

DMA acknowledge signal 2: Signal showing that DREQ2 has acknowledged a DMA transfer

request

Port F5: Input/output port

DMA request signal 3: For inputting the request to transfer data by DMA from an external I/O

device to DMAC3

Port F6: Input/output port

DMA acknowledge signal 3: Signal showing that DREQ3 has acknowledged a DMA transfer

request

Port F7: Input/output port

32-bit time base timer input: For inputting the count for 32-bit time base timer

Ports G0 to G3: Input/output ports that allow input/output to be set in units of bits

For inputting the capture trigger for 32-bit timer

Ports G4 to G7: Input/output ports that allow input/output to be set in units of bits

Outputting 32-bit timer if the result of a comparison is a match

Ports H0 to H5: Input/output ports that allow input/output to be set in units of bits

Outputting 32-bit timber if the result of a comparison is a match

Port I0: Input/output port

Interrupt request pin 0: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port I1: Input/output port

Interrupt request pin 1: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port I2: Input/output port

Interrupt request pin 2: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

2

C mode

2

C mode

TMP19A64(rev1.1)2-6

TMP19A64F20AXBG

Table 2.2.1 Pin Names and Functions (5 of 6)

Pin name

PI3

INT3

PI4

INT4

PJ0

DREQ2

PJ1

DACK2

PJ2

DREQ3

PJ3

DACK3

PK0-PK7

KEY0-KEY7

PL0-PL7 8 Input/output Port L: Input/output port that allows input/output to be set in units of bits

PM0-PM7 8 Input/output Port M: Input/output port that allows input/output to be set in units of bits

PN0-PN7 8 Input/output Port N: Input/output port that allows input/output to be set in units of bits

PO0

INT0

PO1

INT1

PO2

INT2

PO3

INT3

PO4

INT4

PO5

TXD6

PO6

RXD6

PO7

SCLK6

CTS6

PP0-PP7

TPD0-TPD7

PQ0-PQ7

TPC0-TPC7

TPD0-TPD7

Number

of pins

Input or output Function

1 Input/output

Input

1 Input/output

Input

1 Input/output

Input

1 Input/output

Output

1 Input/output

Input

1 Input/output

Output

8 Input/output

Input

1 Input/output

Input

1 Input/output

Input

1 Input/output

Input

1 Input/output

Input

1 Input/output

Input

1 Input/output

Output

1 Input/output

Input

1 Input/output

Input/output

Input

8 Input/output

Output

8 Input/output

Output

Output

Port I3: Input/output port

Interrupt request pin 3: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port I4: Input/output port

Interrupt request pin 4: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port J0: Input/output port

DMA request signal 2: For inputting the request to transfer data by DMA from an external I/O

device to DMAC2

Port J1: Input/output port

DMA acknowledge signal 2: Signal showing that DREQ2 has acknowledged a DMA transfer

request

Port J2: Input/output port

DMA request signal 3: For inputting the request to transfer data by DMA from an external I/O

device to DMAC3

Port J3: Input/output port

DMA acknowledge signal 3: Signal showing that DREQ3 has acknowledged a DMA transfer

request

Port K: Input/output port that allows input/output to be set in units of bits

KEY on wake up input 0 to 7 (with pull-up)

With Schmitt trigger

Port O0: Input/output port

Interrupt request pin 0: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port O1: Input/output port

Interrupt request pin 1: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port O2: Input/output port

Interrupt request pin 2: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port O3: Input/output port

Interrupt request pin 3: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port O4: Input/output port

Interrupt request pin 4: Selectable between "H" level, "L" level, rising edge and falling edge

Input pin with Schmitt trigger

Port O5: Input/output port

Sending serial data 6: Open drain output pin depending on the program used

Port O6: Input/output port

Receiving serial data 6

Port O7: Input/output port

Serial clock input/output 6

Ready to send serial data 6 (Clear To Send): Open drain output pin depending on the program

used

Port P: Input/output port that allows input/output to be set in units of bits

Outputting trace data from the data access address: Signal for DSU-ICE

Port P: Input/output port that allows input/output to be set in units of bits

Outputting trace data from the program counter: Signal for DSU-ICE

Outputting trace data from the data access address: Signal for DSU-ICE

TMP19A64(rev1.1)2-7

TMP19A64F20AXBG

Table 2.2.1 Pin Names and Functions (6 of 6)

Pin name

DCLK 1 Output Debug clock: Signal for DSU-ICE

EJE 1 Input EJTAG enable: Signal for DSU-ICE (input with Schmitt trigger and built-in noise filter)

PCST4-0 5 Output PC trace status: Signal for DSU-ICE

DINT 1 Input Debug interrupt: Signal for DSU-ICE

TOVR/TSTA 1 Output Outputting the status of PD data overflow status: Signal for DSU-ICE

TCK 1 Input Test clock input: Signal for testing JTAG (input with Schmitt trigger and pull-up)

TMS 1 Input Test mode select input: Signal for testing JTAG (input with Schmitt trigger and pull-up)

TDI 1 Input Test data input: Signal for testing JTAG (input with Schmitt trigger and pull-up)

TDO 1 Output Test data output: Signal for testing JTAG

TRST 1 Input Test reset input: Signal for testing JTAG (input with Schmitt trigger and pull-down)

NMI 1 Input Nonmaskable interrupt request pin: Pin for requesting an interrupt at the falling edge

PLLOFF 1 Input Fix this pin to the "H (DVCC15) level."(Input with Schmitt trigger)

RESET 1 Input Reset: Initializing LSI (with pull-up)

X1/X2 2 Input/output Pin for connecting to a high-speed oscillator

XT1/XT2 2 Input/output Pin for connecting to a low-speed oscillator

BUPMD 1 Input Backup mode trigger pin: This pin must be set to "L level" in backup mode.

BRESET 1 Input Backup module reset: Initializing the backup module (with pull-up)

BUSMD 1 Input Pin for setting an external bus mode: This pin functions as a multiplexed bus by sampling the

ENDIAN 1 Input Pin for setting endian: This pin is used to set a mode. It performs a big-endian operation by

BOOT 1 Input Pin for setting a single boot mode: This pin goes into single boot mode by sampling "L" upon

BW0-1 2 Input

VREFH 1 Input Pin (H) for supplying the A/D converter with a reference power supply

VREFL 1 Input Pin (L) for supplying the A/D converter with a reference power supply

AVCC31-32 2

AVSS 3

TEST1-3 3 Input TEST pin: To be fixed to GND.

CVCC15 1

CVSS/BVSS 1

DVCC15 4

BVCC 1

DVCC30-34 8

DVSS 11

FVCC15 4

FVCC3 2

Number

of pins

Input or output Function

(input with Schmitt trigger, pull-up and built-in noise filter)

Input with Schmitt trigger and built-in noise filter

Input with Schmitt trigger and built-in noise filter

Input with Schmitt trigger

"H (DVCC15) level" upon the rising of a reset signal. It also functions as a separate bus by

sampling "L" upon the rising of a reset signal. When performing a reset operation, pull it up or

down according to a bus mode to be used.

sampling the "H (DVCC15) level" upon the rising of a reset signal, and performs a littleendian operation by sampling "L" upon the rising of a reset signal. When performing a reset

operation, pull it up or down according to the type of endian to be used.

the rising of a reset signal. It is used to overwrite internal flash memory. By sampling "H

(DVCC15) level" upon the rising of a reset signal, it performs a normal operation. This pin

should be pulled up under normal operating conditions. Pull it up when resetting.

Fix these pins to BW0="H (DVCC15)" and BW1="H (DVCC15)," respectively.

(Input with Schmitt trigger)

Connect this pin to AVCC31 if the A/D converter is not used.

Connect this pin to AVSS if the A/D converter is not used.

−

−

−

−

−

−

−

−

−

−

Pin for supplying the A/D converter with a power supply. Connect it to a power supply even if

the A/D converter is not used.

A/D converter GND pin (0 V). Connect this pin to GND even if the A/D converter is not used.

Pin for supplying oscillators with power: 1.5 V power supply

GND pin (0 V) for oscillators and backup modules

Power supply pin: 1.5 V power supply

Pin exclusively for supplying backup modules with power: 3 V power supply

Power supply pin: 3 V power supply

GND pin (0 V)

Power supply pin: 1.5 V power supply

Power supply pin: 3 V power supply

TMP19A64(rev1.1)2-8

TMP19A64F20AXBG

Note 1: For BUSMD, ENDIAN and BOOT pins, the state designated for each pin ("H" or "L"

level) must be maintained during one system clock before and after the rising of a

reset signal. The reset pin must always be in a stable state at both "L" and "H" levels.

Note 2: For DREQ2, DACK2, DREQ3 and DACK3, it is necessary to go to the port function

register and to select one port from two groups of ports, PF3 to PF6 and PJ0 to PJ3.

Two ports cannot be operated simultaneously to use the same function.

Likewise, for pins INT0 through INT4, one port must be selected from ports PI0 to PI4

and ports PO0 to PO4.

Table 2.2.2 shows the pin names and power supply pins.

Table 2.2.2 Pin names and power supply pins

Power

Pin name

P0 DVCC33 PCST4 to 0 DVCC31

P1 DVCC33 DCLK DVCC31

P2 DVCC33 EJE DVCC31

P3 DVCC33 TRST DVCC31

P4 DVCC33 TDI DVCC31

P5 DVCC33 TDO DVCC31

P6 DVCC33 TMS DVCC31

P7 AVCC32 TCK DVCC31

P8 AVCC32 DINT DVCC31

P9 AVCC31 TOV DVCC31

PA DVCC32 BUSMD DVCC15

PB DVCC32 BOOT DVCC15

PC DVCC32 ENDIAN DVCC15

PD DVCC32 NMI DVCC15

PE DVCC32 BRESET BVCC

PF DVCC32 BUPMD BVCC

PG DVCC32 X1, X2 CVCC15

PH DVCC32 XT1, XT2 BVCC

PI DVCC30 BW0 and 1 DVCC15

PJ DVCC33 PLLOFF DVCC15

PK DVCC34 RESET DVCC15

PL DVCC34

PM DVCC34

PN DVCC34

PO DVCC34

PP DVCC31

PQ DVCC31

z 2.7 V ≤ AVCC32 ≤ A VCC31

supply pin

Pin name

Power

supply pin

TMP19A64(rev1.1)2-9

TMP19A64F20AXBG

Table 2.2.3 shows the pin numbers and power supply pins.

Table 2.2.3 Pin numbers and power supply pins

Power

supply pin

DVCC15 D4, D8, E18, N9 1.35 V to 1.65 V

CVCC15 C17 1.35 V to 1.65 V

DVCC30 K17 1.65 V to 3.3 V

DVCC31 H2 1.65 V to 3.3 V

DVCC32 M6, U8 1.65 V to 3.3 V

DVCC33 F17, U14 1.65 V to 3.3 V

DVCC34 D15, F10 1.65 V to 3.3 V

AVCC31 B1 2.7 V to 3.3 V

AVCC32 F9 2.7 V to 3.3 V

FVCC15 G3, G18, J6, L15 1.35 V to 1.65 V

FVCC3 L1, U18 2.7 V to 3.3 V

BVCC E15 2.3 V to 3.3 V

Pin number Voltage range

(under normal operating conditions)

1.8 V to 3.3 V (in BACKUP mode)

TMP19A64(rev1.1)2-10

3. Flash Memory Operation

This section describes the hardware configuration and operation of the flash memory. The feature of this device

is that the internal ROM of TMP19A64C1DXBG is replaced by an internal flash memory. Other configurations

and functions of the device remain the same as with TMP19A64C1DXBG. Please refer to the

TMP19A64C1DXBG data sheet for functions not described in this section.

3.1 Flash Memory

3.1.1 Features

1) Memory capacity

The TMP19A64F20AXBG device contains two 8M bits (1MB) of flash memory capacity. The

memory area consists of 4 independent memory blocks (128 kB × 16) to enable independent write

access to each block. When the CPU is to access the internal flash memory, 32-bit data bus width

is used.

2) Write/erase

Write unit: 1 page (128 words) × 4k

Erase unit: Selectable from 128 KB, 512 KB, and 1 MB

Protection unit: Selectable in 512 KB blocks

Protection erasure unit: Selectable in 1 MB blocks

3) Write/erase time

Write time: 8 sec/2 chip (Typ) 2 msec/128 word (Typ.)

Erase time: 1.6 sec /2 chip (Typ) 100 msec/128 Kbyte (Typ.)

Protection bit erase time: 100 msec/2 bit (Typ)

(Note) The above values are theoretical values not including data transfer time.

The write time per chip depends on the write method to be used by the user.

4) Programming method

Two modes are available, i.e., the onboard programming mode to allow programming on the

user's board and the writer mode to program the device using an EPROM writer.

TMP19A64F20AXBG

Onboard programming mode 1) User boot mode

•

2) Single boot mode

The rewriting method to use serial data transfer

(Toshiba's unique method) can be supported.

Writer mode

•

Use of a general purpose EPROM writer is supported.

5) Rewriting method

The flash memory included in this device is generally compliant with the applicable JEDEC

standards except for some specific functions. Therefore, if the user is currently using an external

flash memory device, it is easy to implement the functions into this device. Furthermore, the user

is not required to build his/her own programs to realize complicated write and erase functions

because such functions are automatically performed using the circuits already built-in the flash

memory chip.

This device is also implemented with a read-security function to inhibit reading flash memory

data from any external writer device. On the other hand, rewrite protection is available only

through command-based software programming; any hardware setting method to apply +12VDC

is not supported. The above described security function is automatically enabled when all the four

area are configured for protection. When the user removes protection, the internal data is

automatically erased before the protection is actually removed.

The user's original rewriting method can be supported.

TMP19A64(rev1.1)-3-1

JEDEC compliant functions Modified, added, or deleted functions

• Automatic programming

• Automatic chip erase

• Automatic block erase

• Data polling/toggle bit

3.1.2 Block Diagram

TMP19A64F20AXBG

<Modified> Block protect (only software protection is supported)

<Deleted> Erase resume - suspend function

Automatic multiple block erase (supported to the chip

level)

Internal address bus

Internal data bus

Internal control bus

ROM controller

Control Address Data

Control

circuit

(includes

automatic

sequence

control)

Command

register

Column decoder/sense amplifier

Flash memory cell

1MB 1MB

Row decoder

Erase block decoder

Fig. 3.1.2.1 Block Diagram of the Flash Memory Section

Data latchAddress latch

Flash Memory

Row decoder

TMP19A64(rev1.1)-3-2

TMP19A64F20AXBG

3.2 Operation Mode

This device has four operation modes including the mode not to use the internal flash memory.

Table 3.2.1.1 Operation Modes

Operation mode Operation details

Single chip mode

Normal mode

User boot mode The user can uniquely configure the system to switch between these two modes.

Single boot mode

Writer mode

Among the flash memory operation modes listed in the above table, the user boot mode, single boot mode, and

writer mode are programmable modes. These two modes, the User Boot mode and the Single Boot mode, are

referred to as "Onboard Programming" modes where onboard rewriting of internal flash memory can be made

on the user's card.

After reset is cleared, it starts up from the internal flash memory.

In this operation mode, two different modes, i.e., the mode to execute user application programs

and the mode to rewrite the flash memory onboard the user’s card, are defined. The former is

referred to as "normal mode" and the latter "user boot mode."

For example, the user can freely design the system such that the normal mode is selected when the

port "00" is set to "1" and the user boot mode is selected when it is set to "0."

The user should prepare a routine as part of the application program to make the decision on the

selection of the modes.

After reset is cleared, it starts up from the internal Boot ROM (Mask ROM). In the Boot ROM, an

algorithm to enable flash memory rewriting on the user’s set through the serial port of this device

is programmed. By connecting to an external host computer through the serial port, the internal

flash memory can be programmed by transferring data in accordance with predefined protocols.

This mode allows use of a general purpose EPROM writer to rewrite the internal flash memory.

Please use a special program adaptor and an EPROM writer that are recommended for use.

TMP19A64(rev1.1)-3-3

TMP19A64F20AXBG

g

Either the single chip, single boot, or writer operation mode can be selected by externally setting the levels of

the BW0, BW1, and

BOOT input pins while the device is in the reset state.

Except for the case of the writer mode, the CPU starts operation in the selected operation mode when the reset

condition is removed after the pin levels are set. The writer mode is used with

RESET set to "0". Be sure not to

change the levels during operation once the mode is selected. The mode setting method and the mode transition

diagram are shown below:

Table 3.2.1.2 Operation Mode Setting

Operation mode

(1) Single chip mode

(2) Single boot mode

(3) Writer mode *1 *1 *1 *1

RESET

0 → 1

0 → 1

Input pin

BW0 BW1

1 1 1

1 1 0

BOOT

*1: Don't care (No explanation is given in this section regarding condition settings.)

Writer mode

(3)

Reset mode

Single chip mode

Normal mode

Boot mode

User

(1)

/

RESET = 0

Single

Boot mode

(2)

RESET = 0

/

The number in the parentheses indicate the mode number in the above table to

show the input pin setting to be made for the corresponding state transition.

User to set the

switch method

Onboard

ramming mode

Pro

Fig. 3.2.1.3 Mode Transitio n Diagram

3.2.1 Reset Operation

To reset the device, ensure that the power supply voltage is within the operating voltage range, that the

internal oscillator has been stabilized, and that the

RESET

12 system clocks (1.8 μs with 54 MHz operation; the "1/8" clock gear mode is applied after reset).

(Note 1) Regarding power-on reset of devices with internal flash memory;

For devices with internal flash memory, it is necessary to apply "0" to the

upon power on for a minimum duration of 60 microseconds regardless of the operating

frequency.

During this period, each protection bit, to be described later, is locked in the state it is

written regardless of the state it ought to be. The original values of protection bits can be

checked by reading the register FLCS <BLPRO 3:0> after the power on reset operation is

normally terminated.

(Note 2) While flash programming is in progress, at least 0.5 microseconds of reset period is

required regardless of the system clock frequency.

TMP19A64(rev1.1)-3-4

input is held at "0" for a minimum duration of

RESET inputs

TMP19A64F20AXBG

3.2.2 DSU (EJTAG) - PROBE Interface

This interface is used when the DSU probe is used in debugging. This is the dedicated interface for

connection to the DSU probe. Please refer to the operation manual for the DSU probe you are going to use

for details of debugging procedures to use the DSU probe. Here, the function to enable/disable the DSU

probe in the DSU (EJTAG) mode is described.

1) Security function

This device allows use of an on-board DSU probe for debugging. To facilitate this, the device is

implemented with a security measure to prevent easy reading of the internal flash memory by a third

party other than the authorized user. By enabling the security function, it becomes impossible to read

the internal flash memory from a DSU probe. Use this function together with the security function of

the internal flash memory itself as described later.

2) DSU probe enable/disable function

This device allows use of on-board DSU probes for debugging operations. To facilitate this, the device

is implemented with the "DSU probe inhibit" function (hereafter referred to as the "DSU inhibit"

function) to prevent easy reading of the internal flash memory by a third party other than the

authorized user. By enabling the DSU inhibit function, use of any DSU probe becomes impossible.

3) DSU enable (Enables use of DSU probes for debugging)

In order to prevent the DSU inhibit function from being accidentally removed by system runaway, etc.,

the method to cancel the inhibit function requires a double action operation so it is necessary to set

DSU security mode register DSUSEC1<DSUOFF> to "0" and also write the security code

"0x0000_00C5" to the DSU security control register DSUSEC2 to cancel the function. Then,

debugging to use a DSU probe is allowed. While power to the device is still applied, setting

DSUSEC1<DSUOFF> to "1" and writing "0x0000_00C5" to the DSUSEC2 register will enable the

security function again.

Table 3.2.2.1 DSU Security Mode Register

7 6 5 4 3 2 1 0

DSUSEC1 Bit Symbol DSUOFF

(0xFFFF_E510) Read/Write R R/W

After power

Function Always reads "0." 1: DSU disable

15 14 13 12 11 10 9 8

Bit Symbol

Read/Write R

After power

Function Always reads "0."

23 22 21 20 19 18 17 16

Bit Symbol

Read/Write R

After power

Function

31 30 29 28 27 26 25 24

Bit Symbol

Read/Write R

After power

Function Always reads "0."

on reset

on reset

on reset

on reset

0 1

0: DSU available

0

0

0

(Note) This register can be initialized only by a power on reset. Normal reset inputs cannot reset

the register.

(Note) This register must be 32-bit accessed.

TMP19A64(rev1.1)-3-5

TMP19A64F20AXBG

Table 3.2.2.2 DSU Security Control Register

7 6 5 4 3 2 1 0

DSUSEC2 Bit Symbol

(0xFFFF_E514) Read/Write W

After reset 0

Function Write "0x0000_00C5."

15 14 13 12 11 10 9 8

Bit Symbol

Read/Write W

After reset 0

Function Write "0x0000_00C5."

23 22 21 20 19 18 17 16

Bit Symbol

Read/Write W

After reset 0

Function Write "0x0000_00C5."

31 30 29 28 27 26 25 24

Bit Symbol

Read/Write W

After reset 0

Function Write "0x0000_00C5."

DSECODE07 DSECODE06 DSECODE05 DSECODE04 DSECODE03 DSECODE02 DSECODE01 DSECODE00

DSECODE15 DSECODE14 DSECODE13 DSECODE12 DSECODE11 DSECODE10 DSECODE09 DSECODE08

DSECODE23 DSECODE22 DSECODE21 DSECODE20 DSECODE19 DSECODE18 DSECODE17 DSECODE16

DSECODE31 DSECODE30 DSECODE29 DSECODE28 DSECODE27 DSECODE26 DSECODE25 DSECODE24

(Note) This register must be 32-bit accessed.

4) Example use by the user

An example to use a DSU probe together with this function is shown as follows:

Power ON

External ports

Data, etc.

DSU availability decision program

Protection bit

set to 1111

Y

(to be prepared by the user)

N

[DSU-Probe available]

N

DSU inhibit cleared?

[DSU-Probe disabled]

DSU remains unavailable

Clear ROM security

(only for internal ROM/flash)

Clear DSU inhibit function by writing

to DSUSEC1 and DSUSEC2

[DSU-Probe available]

DSU can be used until power

is turned off.

Y

Fig. 3.2.2.3 Example Use of DSU Inhibit Function

TMP19A64(rev1.1)-3-6

TMP19A64F20AXBG

3.3 On-board Programming of Flash Memory (Rewrite/Erase)

In on-board programming, the CPU is to execute software commands for rewriting or erasing the flash memory.

The rewrite/erase control program should be prepared by the user beforehand. Because the flash memory

content cannot be read while it is being written or erased, it is necessary to run the rewrite/erase program from

the internal RAM or from an external memory device after shifting to the user boot mode. In this section, flash

memory addresses are represented in virtual addresses unless otherwise noted.

3.4 Flash Memory

Except for some functions, writing and erasing flash memory data are in accordance with the standard JEDEC

commands. In writing or erasing, use the SW command of the CPU to enter commands to the flash memory.

Once the command is entered, the actual write or erase operation is automatically performed internally.

Table 3.4.1.1 Flash Memory Functions

Major functions Description

Automatic page program Writes data automatically (in 128 word blocks).

Automatic chip erase Automatically erases the flash memory area one chip at a time (1 MB at a time).

Automatic block erase Erases a selected block automatically (128 kB at a time).

Write protect

Security function

Note that addressing of operation commands is different from the case of standard commands due to the specific

interface arrangements with the CPU as detailed operation of the user boot mode and RAM transfer mode is

described later. Also note that the flash memory is written in 32-bit blocks. So, 32-bit (word) data transfer

commands must be used in writing the flash memory.

The write or erase function can be individually inhibited for each area (of 512 kB). When all

areas are set for protection, the security function is automatically enabled.

A security function is implemented to inhibit reading from the flash memory when the

device is in the writer mode. By setting protection to all the four areas, the security function

is enabled. In order to disable the security function, it is necessary to cancel write protection

when the entire flash memory is automatically erased.

TMP19A64(rev1.1)-3-7

TMP19A64F20AXBG

(1) Block configuration

0xBFDF_FFFF Block 7 128 kB

Protection area 3 Block 6 128 kB

Block 5 128 kB

Chip 1 Block 4 128 kB

Block 3 128 kB

Protection area 2 Block 2 128 kB

Block 1 128 kB

0xBFD0_0000 Block 0 128 kB

0xBFCF_FFFF Block 7 128 kB

Protection area 1 Block 6 128 kB

Block 5 128 kB

Chip 0 Block 4 128 kB

Block 3 128 kB

Protection area 0 Block 2 128 kB

Block 1 128 kB

0xBFC0_0000 Block 0 128 kB

128 words

| x 256

128 words

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

⏐

128 words

| x 256

128 words

Fig. 3.4.1.2 Block Configuration of Flash Memory

TMP19A64(rev1.1)-3-8

TMP19A64F20AXBG

(2) Basic operation

Generally speaking, this flash memory device has the following two operation modes:

• The mode to read memory data (Read mode)

• The mode to automatically erase or rewrite memory data (Automatic operation)

Transition to the automatic mode is made by executing a command sequence while it is in the memory

read mode. In the automatic operation mode, flash memory data cannot be read and any commands

stored in the flash memory cannot be executed. During automatic operation, be sure not to cause any

exceptions other than debug exceptions and reset while a DSU probe is connected. Any interrupt or

exception generation cannot set the device to the read mode except when a hardware reset is generated.

1) Read

When data is to be read, the flash memory must be set to the read mode. The flash memory will

be set to the read mode immediately after power is applied, when CPU reset is removed, or when

an automatic operation is normally terminated. In order to return to the read mode from other

modes or after an automatic operation has been abnormally terminated, either the Read/reset

command (a software command to be described later) or a hardware reset is used. The device

must also be in the read mode when any command written on the flash memory is to be executed.

• Read/reset command and Read command (software reset)

When an automatic operation is abnormally terminated, the flash memory cannot return to the

read mode by itself (When FLCS<RDY/BSY> = 0, data read from the flash memory is

undefined.) In this case, the Read/reset command can be used to return the flash memory to

the read mode. Also, when a command that has not been completely written has to be

canceled, the Read/reset command must be used to return to the read mode. The Read

command is used to return to the read mode after executing the SW command to write the

data "0x0000_00F0" to two arbitrary addresses 0x001x_xxxx and 0x000x_xxxx of the flash

memory.

• With the Read/reset command, the device is returned to the read mode after completing the

third bus write cycle.

2) Command write

This flash memory uses the command control method. Commands are executed by executing a

command sequence to the flash memory. The flash memory executes automatic operation

commands according to the address and data combinations applied (refer to Command Sequence).

If it is desired to cancel a command write operation already in progress or when any incorrect

command sequence has been entered, the Read/reset command is to be executed. Then, the flash

memory will terminate the command execution and return to the read mode.

Also, when issuing a command, the address [20:19] must be fixed to either "1" or "0" in order to

enable a decision to select either chip 0 or 1.

While commands are generally comprised of several bus cycles, the operation to apply the SW

command to the flash memory is called "bus write cycle." The bus write cycles are to be in a

specific sequential order and the flash memory will perform an automatic operation when the

sequence of the bus write cycle data and address of a command write operation is in accordance

with a predefined specific sequence. If any bus write cycle does not follow a predefined

command write sequence, the flash memory will terminate the command execution and return to

the read mode. The address [31:21] in each bus write cycle should be the virtual address [31:21]

of command execution. It will be explained later for the address bits [20:8].

TMP19A64(rev1.1)-3-9

TMP19A64F20AXBG

(Note 1) Command sequences are executed from outside the flash memory area.

(Note 2) The interval between bus write cycles for this device must be 15 system clock cycles or

longer. The command sequencer in the flash memory device requires a certain time period to

recognize a bus write cycle. If more than one bus write cycles are executed within this time

period, normal operation cannot be expected. For adjusting the applicable bus write cycle

interval using a software timer to be operated at the operating frequency, use the section 10)

"ID-Read" to check for the appropriateness.

(Note 3) Between the bus write cycles, never use any load command (such as LW, LH, or LB) to the

flash memory or perform a DMA transmission by specifying the flash area as the source

address. Also, don't execute a Jump command to the flash memory. While a command

sequence is being executed, don't generate any interrupt such as maskable interrupts (except

debug exceptions when a DSU probe is connected).

If such an operation is made, it can result in an unexpected read access to the flash memory

and the command sequencer may not be able to correctly recognize the command. While it

could cause an abnormal termination of the command sequence, it is also possible that the

written command is incorrectly recognized.

(Note 4) The SYNC command must be executed immediately after the SW command for each bus

write cycle.

(Note 5) For the command sequencer to recognize a command, the device must be in the read mode

prior to executing the command. Be sure to check before the first bus write cycle that the

FLCS[0] RDY/BSY bit is set to "1." It is recommended to subsequently execute a Read

command.

(Note 6) Upon issuing a command, if any address or data is incorrectly written, be sure to perform a

system reset operation or issue a reset command (for Chip 0 and Chip 1) to return to the read

mode again.

3) Reset

Hardware reset

The flash memory has a reset input as the memory block and it is connected to the CPU reset

signal. Therefore, when the RESET input pin of this device is set to V

or when the CPU is reset

IL

due to any overflow of the watch dog timer, the flash memory will return to the read mode

terminating any automatic operation that may be in progress. The CPU reset is also used in

returning to the read mode when an automatic operation is abnormally terminated or when any

mode set by a command is to be canceled. It should also be noted that applying a hardware reset

during an automatic operation can result in incorrect rewriting of data. In such a case, be sure to

perform the rewriting again.

Refer to Section 3.1 "Reset Operation" for CPU reset operations. After a given reset input, the

CPU will read the reset vector data from the flash memory and starts operation after the reset is

removed.

4) Automatic Page Programming

Writing to a flash memory device is to make "1" data cells to "0" data cells. Any "0" data cell

cannot be changed to a "1" data cell. For making "0" data cells to "1" data cells, it is necessary to

perform an erase operation.

The automatic page programming function of this device writes data in 128 word blocks. A 128

word block is defined by a same [31:9] address and it starts from the address [8:0] = 0 and ends at

the address [8:0] = 0x1FF. This programming unit is hereafter referred to as a "page."

TMP19A64(rev1.1)-3-10

TMP19A64F20AXBG

Writing to data cells is automatically performed by an internal sequencer and no external control

by the CPU is required. The state of automatic page programming (whether it is in writing

operation or not) can be checked by the FLCS <RDY/BSY> register.

Also, any new command sequence is not accepted while it is in the automatic page programming

mode. If it is desired to interrupt the automatic page programming, use the hardware reset

function. If the operation is stopped by a hardware reset operation, it is necessary to once erase

the page and then perform the automatic page programming again because writing to the page has

not been normally terminated.

The automatic page programming operation is allowed only once for a page already erased. No

programming can be performed twice or more times irrespective of the data cell value whether it

is "1" or "0." Note that rewriting to a page that has been once written requires execution of the

automatic block erase or automatic chip erase command before executing the automatic page

programming command again. Note that an attempt to rewrite a page two or more times without

erasing the content can cause damages to the device.

No automatic verify operation is performed internally to the device. So, be sure to read the data

programmed to confirm that it has been correctly written.

The automatic page programming operation starts when the fourth bus write cycle of the

command cycle is completed. On and after the fifth bus write cycle, data will be written

sequentially starting from the next address of the address specified in the fourth bus write cycle

(in the fourth bus write cycle, the page top address will be command written) (32 bits of data is

input at a time). Be sure to use the SW command in writing commands on and after the fourth bus

cycle. In this, any SW command shall not be placed across word boundary. On and after the fifth

bus write cycle, data is command written to the same page area. Even if it is desired to write the

page only partially, it is required to perform the automatic page programming for the entire page.

In this case, the address input for the fourth bus write cycle shall be set to the top address of the

page. Be sure to perform command write operation with the input data set to "1" for the data cells

not to be set to "0." For example, if the top address of a page is not to be written, set the input data

of the fourth bus write cycle to 0xFFFFFFFF to command write the data.

Once the fourth bus cycle is executed, it is in the automatic programming operation. This

condition can be checked by monitoring the register bit FLCS <RDY/BSY>. Any new command

sequence is not accepted while it is in automatic page programming mode. If it is desired to stop

operation, use the hardware reset function. Be careful in doing so because data cannot be written

normally if the operation is interrupted. When a single page has been command written normally

terminating the automatic page writing process, the FLCS <RDY/BSY> bit is set to "1" and it

returns to the read mode.

When multiple pages are to be written, it is necessary to execute the page programming

command for each page because the number of pages to be written by a single execution of the

automatic page program command is limited to only one page. It is not allowed for automatic

page programming to process input data across pages.

Data cannot be written to a protected block. When automatic programming is finished, it

automatically returns to the read mode. This condition can be checked by monitoring FLCS

<RDY/BSY>. If automatic programming has failed, the flash memory is locked in the mode and

will not return to the read mode. For returning to the read mode, it is necessary to use the reset

command or hardware reset to reset the flash memory or the device. In this case, while writing to

the address has failed, it is recommended not to use the device or not to use the block that

includes the failed address.

Note: Software reset becomes ineffective in bus write cycles on and after the

fourth bus write cycle of the automatic page programming command.

TMP19A64(rev1.1)-3-11

TMP19A64F20AXBG

5) Automatic chip erase (1MB at a time)

The automatic chip erase operation starts when the sixth bus write cycle of the command cycle is

completed.

This condition can be checked by monitoring FLCS <RDY/BSY>. While no automatic verify

operation is performed internally to the device, be sure to read the data to confirm that data has

been correctly erased. Any new command sequence is not accepted while it is in an automatic

chip erase operation. If it is desired to stop operation, use the hardware reset function. If the

operation is forced to stop, it is necessary to perform the automatic chip erase operation again

because the data erasing operation has not been normally terminated.

Also, any protected blocks cannot be erased. If all the blocks are protected, the automatic chip

erase operation will not be performed and it returns to the read mode after completing the sixth

bus read cycle of the command sequence. When an automatic chip erase operation is normally

terminated, it automatically returns to the read mode. If an automatic chip erase operation has

failed, the flash memory is locked in the mode and will not return to the read mode.

For returning to the read mode, it is necessary to use the reset command or hardware reset to reset

the flash memory or the device. In this case, the failed block cannot be detected. It is

recommended not to use the device anymore or to identify the failed block by using the block

erase function for not to use the identified block anymore.

6) Automatic block erase (128 kB at a time)

The automatic block erase operation starts when the sixth bus write cycle of the command cycle

is completed.

This status of the automatic block erase operation can be checked by monitoring FLCS

<RDY/BSY>. While no automatic verify operation is performed internally to the device, be sure

to read the data to confirm that data has been correctly erased. Any new command sequence is not

accepted while it is in an automatic block erase operation. If it is desired to stop operation, use the

hardware reset function. In this case, it is necessary to perform the automatic block erase

operation again because the data erasing operation has not been normally terminated.

Note that any block in the protected area is not erased. It returns to the read mode upon

completing the last bus cycle of the command sequence. If an automatic block erase operation has

failed, the flash memory is locked in the mode and will not return to the read mode. In this case,

use the reset command or hardware reset to reset the flash memory or the device.

Note: Commands can be accepted only by Chip 0. Even if automatic protection bit

programming or erasure is commanded to Chip 1, it will not result in any

setting or clearing of the protection.

7) Automatic programming of protection bits (for each 512 kB block)

This device is implemented with four protection bits. The protection bits can be individually set in

the automatic programming. The applicable protection bit is specified in the seventh bus write

cycle. By automatically programming the protection bits, write and/or erase functions can be

inhibited individually for each protection area. The protection status of each area can be checked

by FLCS <PROTECT3:0> to be described later. Any new command sequence is not accepted

while automatic programming is in progress to program the protection bits. If it is desired to stop

the programming operation, use the hardware reset function. In this case, it is necessary to

perform the programming operation again because the protection bits may not have been correctly

programmed. If all the protection bits have been programmed, the flash memory cannot be read

TMP19A64(rev1.1)-3-12

TMP19A64F20AXBG

from any area outside the flash memory such as the internal RAM. In this condition, the FLCS

<PROTECT3:0> register is set to "0xF" (secure state). After this, no command writing can be

performed.

Note: Commands can be accepted only by Chip 0. Even if automatic protection bit

programming or erasure is commanded to Chip 1, it will not result in any

setting or clearing of the protection.

Note: Software reset is ineffective in the seventh bus write cycle of the automatic

protection bit programming command. The FLCS <RDY/BSY> bit turns to "0"

after entering the seventh bus write cycle.

8) Automatic erasing of protection bits

Different results will be obtained when the automatic protection bit erase command is executed

depending on the status of the protection bits. It depends on the status of FLCS<PROTECT3:0>

before the command execution whether it is set to "0 x F" or to any other values. Be sure to check

the value of FLCS<PROTECT3:0> before executing the automatic protection bit erase command.

• When FLCS<PROTECT3:0> is set to "0 x F" (all the protection bits are programmed):

When the automatic protection bit erase command is command written, the flash memory is

automatically initialized within the device. When the seventh bus write cycle is completed, the

entire area of the flash memory data cells is erased and then all the protection bits are erased. This

operation can be checked by monitoring FLCS <RDY/BSY>. If the automatic operation to erase

protection bits is normally terminated, FLCS<PROTECT3:0> will be set to "0x0." While no

automatic verify operation is performed internally to the device, be sure to read the data to

confirm that it has been correctly erased. For returning to the read mode while the automatic

operation after the seventh bus cycle is in progress, it is necessary to use the hardware reset to

reset the flash memory or the device. If this is done, it is necessary to check the status of

protection bits by FLCS<PROTECT3:0> after retuning to the read mode and perform either the

automatic protection bit erase, automatic chip erase, or automatic block erase operation, as

appropriate.

• When FLCS<PROTECT3:0>is other than "0 x F" (not all the protection bits are programmed):

The protection condition can be canceled by the automatic protection bit erase operation. With

this device, protection bits can be erased handling two bits at a time. The target bits are specified

in the seventh bus write cycle and when the command is completed, the device is in a condition

the two bits are erased. The protection status of each block can be checked by

FLCS<PROTECT3:0> to be described later. This status of the programming operation for

automatic protection bits can be checked by monitoring FLCS <RDY/BSY>. When the automatic

operation to erase protection bits is normally terminated, the two protection bits of

FLCS<PROTECT3:0> selected for erasure are set to "0."

In any case, any new command sequence is not accepted while it is in an automatic operation to

erase option bits. If it is desired to stop the operation, use the hardware reset function. When the

automatic operation to erase option bits is normally terminated, it returns to the read mode.

TMP19A64(rev1.1)-3-13

TMP19A64F20AXBG

9) Flash control/ status register

This resister is used to monitor the status of the flash memory and to indicate the block protection

status.

Table 3.4.1.3 Flash Control Register

7 6 5 4 3 2 1 0

FLCS Bit Symbol PROTECT3 PROTECT2 PROTECT1 PROTECT0 ROMTYPE PRGB RDY/BSY

(0xFFFF_E520) Read/Write R R R R/W R

After power

Function Protection area setting (for each 512 kB)

15 14 13 12 11 10 9 8

After power

Function

23 22 21 20 19 18 17 16

After power

Function

31 30 29 28 27 26 25 24

After power

Function

on reset