32bit TX System RISC

TX19 family

TMP1942CYUE

TMP1942CZUE/XBG

Rev1.0 March 29, 2007

32-Bit RISC Microprocessor TX19 Family

1. Outline and Features

The TX19 is a family of high-performance 32-bit microprocessors that offers the speed of a 32-bit RISC

solution with the added advantage of a significantly reduce code size of a 16-bit architecture. The instruction set

of the TX19 includes as a subset the 32-bit instructions of the TX39, which is based

architecture. Additionally, the TX19 supports the MIPS16

improved code density.

The TMP1942 is built on a TX19 core processor and a selection of intelligent peripherals. The TMP1942 is

suitable for low-voltage, low-power applications.

Features of the TMP1942 include the following:

TMP1942CYUE/CZUE/CZXBG

TM

Application-Specific Extensions (ASE) for

TX1942CY/CZ

on the MIPS R3000ATM

RESTRICTIONS ON PRODUCT USE

• The information contained herein is subject to change without notice.

• TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making

a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA

products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set

forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions

set forth in the “Handling Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc.

021023_A

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer,

personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These

TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality

and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury (“Unintended Usage”).

Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation

instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices,

etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer’s own risk.

• The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws an d regulations.

• The information contained herein is presented only as a guide for the applications of our products. No responsibility is

assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use.

No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

070122_C

• The products described in this document are subject to foreign exchange and foreign trade control laws.

• For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter

entitled Quality and Reliability Assurance/Handling Precautions.

021023_D

060106_Q

030619_S

070122EBP

021023_B

060925_E

TMP1942CY/CZ-1

TX1942CY/CZ

(1) TX19 core processor

1) Two instruction set architecture (ISA) modes: 16-bit ISA for code density and 32-bit ISA for speed

• The 16-bit ISA is object-code compatible with the code-efficient MIPS16

TM

ASE.

• The 32-bit ISA is object-code compatible with the high-performance TX39 family.

2) Combines high performance with low power consumption.

- High performance

• Single clock cycle execution for most instructions

• 3-operand computational instructions for high instruction throughput

• 5-stage pipeline

• On-chip high-speed memory

• DSP function: Executes 32-bit x 32-bit multiplier operations

with a 64-bit accumulation in a single

clock cycle.

- Low power consumption

• Optimized design using a low-power cell library

• Programmable standby modes in which processor clocks are stopped

3) Fast interrupt response suitable for real-time control

• Distinct starting locations for each interrupt service routine

• Automatically generated vectors for each interrupt

source

• Automatic updates of the interrupt mask level

(2) Internal RAM: FDUE/FDXBG: 20KB,CYUE/CZUE/CZXBG: 16 KB

Internal ROM: FDUE/FDXBG: 512KB,CYUE/CZXBG: 384KB,CYUE: 256 KB

ROM correction function (8 words x 4 blocks)

(For FDUE/FDXBG, only registers are available; data is not replaced.)

(3) External memory expansion

• 16-Mbyte off-chip address space for code and

data

• External bus interface with dynamic bus sizing for 8-bit and 16-bit data ports

(4) 4-channel DMA controller

• Interrupt- or software-triggered

(5) 6 channel 8-bit PWM timer

(12 channel 8-bit interval timer, 6 channel 16-bit interval timer, 6 channel 8-bit PPG output)

(6) 14 channel 16-bit timer

(2 channels support 2-phase

input pulse counter mode.)

(7) 1 channel real-time counter (RTC)

(8) 5 channel general-purpose serial interface

(Supports both UART and synchronous transfer modes)

(9) 1 channel serial bus interface

Either I

2

C bus mode or clock-synchronous mode can be selected.

(10) 16 channel 10-bit A/D converter (with internal sample/hold)

Conversion time: 2 µs (throughput), 4 to 5 µs (latency)

(11) 3 channel 10-bit D/A converter

(12) Watchdog timer

(13) 4 channel chip select/wait controller

TMP1942CY/CZ-2

TX1942CY/CZ

(14) Interrupt sources

• 4 CPU interrupts: software interrupt instruction

• 45 internal interrupts: 7 priority levels, with the exception of the watchdog timer interrupt

• 29 external interrupts: 7 priority levels, with the exception of the NMI interrupt

The external sources include 14 KWUP sources, which are all assigned to a

single interrupt vector,

INTE), which are all assigned to a single interrupt vector with an identification

flag. Thus, the actual number of external interrupt sources is 13.

(15) 108 pin input/output ports

(16) Three standby function

• IDLE, SLEEP, and STOP

(17) Dual clocks

• RTC clock: Low-speed

(18) Clock generator

• On-chip PLL (x4)

• Clock gear: Divides the operating speed of the CPU by 1/2, 1/4 or 1/8

clock (32.768 kHz)

and 4 extended interrupts (INTB, INTC, INTD, and

(19) Operating voltage range: 2.7 to 3.6 V

PC and PF are 2.7 to 3.6 V or 4.5 to 5.25 V for 5 V-enabled ports.

(20) Operating frequency

•

32 MHz (Vcc ≥ 3.0 V)

• 28 MHz (Vcc ≥ 2.7 V)

(21) Package

• 144-pin QFP (16 x 16 x 1.4 (t) mm, 0.4-mm pitch): FDUE/CZUE/CYUE

• 177-pin CSP (13 x 13 x 1.4 (t) mm, 0.8-mm pitch): FDXBG/CZXBG

Note: TMP1942FDXBG (Package: 177-pin CSP) is under development.

TMP1942CY/CZ-3

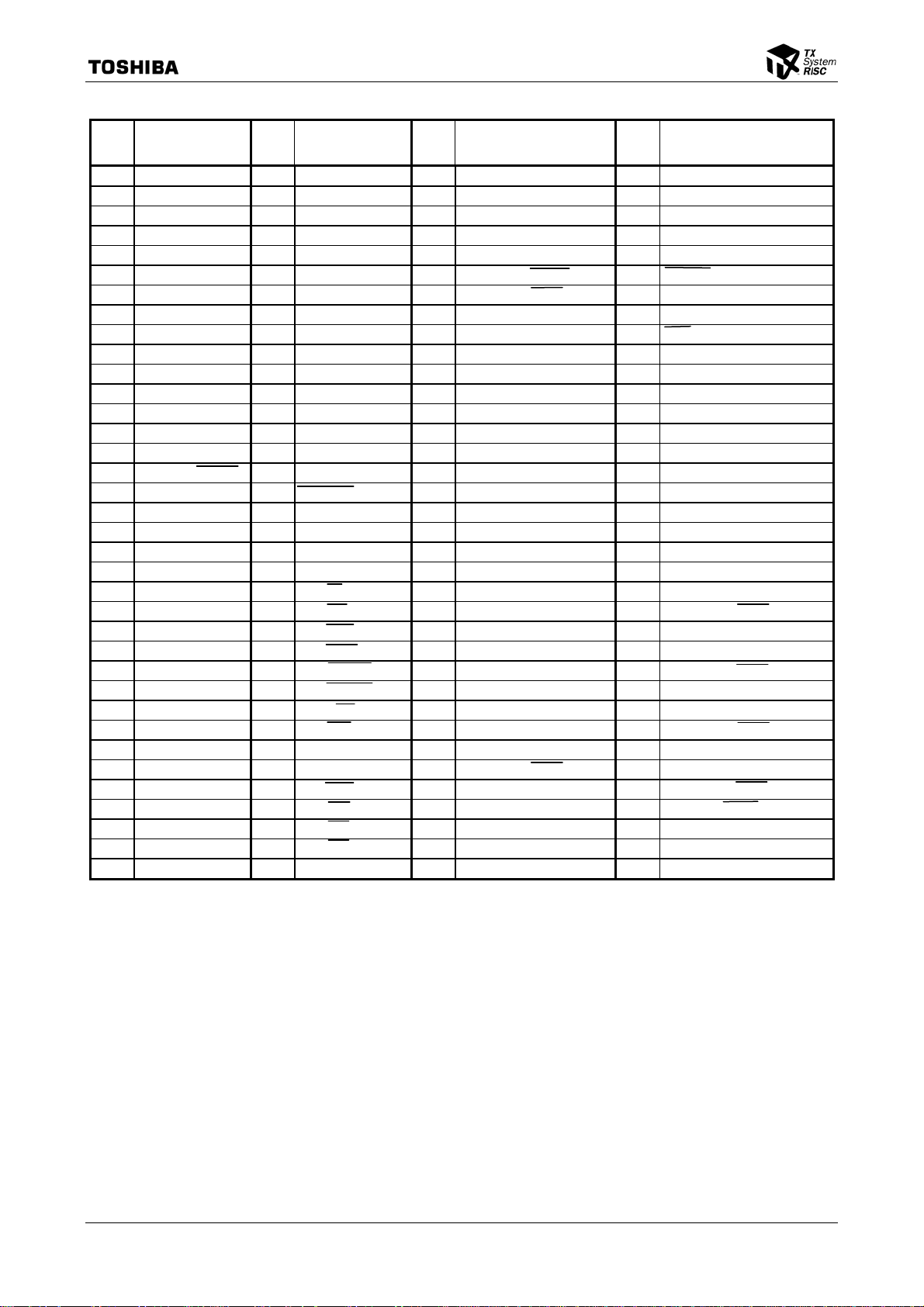

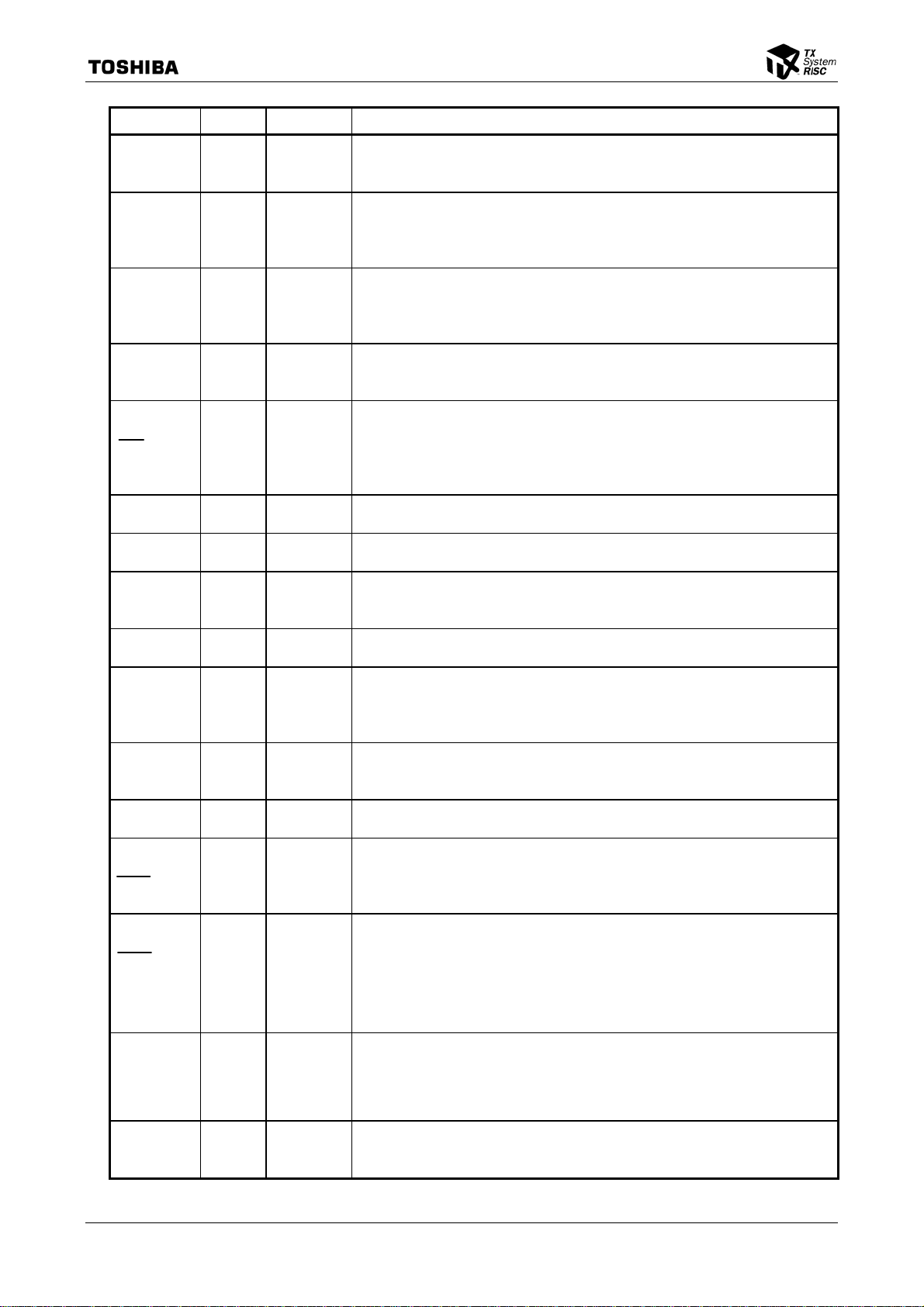

A

A

A

)

)

)

INT1∼2 (PE6∼7)

INT3∼4 (PA0∼1)

INT5∼6 (PA3∼4)

INT8∼A (PC0∼2)

AN0∼7 (P50∼57)

AN8∼15 (P60∼67)

DAVCC/DAVSS

SCLK0/CTS0 (PD2)

SCLK1/CTS1 (PD5)

SCLK3/CTS3 (PE2)

SCLK4/CTS4 (PE5)

TB4IN1 (PB5), TB0IN0∼1 (PA0∼1)

TB7IN0∼1 (P95∼96), TB1IN0∼1 (PA3∼4)

TB8IN0∼1 (PC6∼7), TB2IN0∼1 (PB0∼1)

TB9IN0∼1 (PD0∼1), TB3IN0∼1 (PB3∼4)

TBAIN0∼1 (PD5∼6), TB4IN0 (PB2)

TB0OUT (PA2), TB4OUT (P92)

TB1OUT (PA5), TB5OUT (P93)

TB2OUT (PB2), TB6OUT (P94)

TB3OUT (PB5), TB7OUT (P97)

TA1OUT (PA 6), TA7OUT (PC5)

TA3OUT (PB6), TA9 OUT (PC7)

TA5OUT (PC3), TABOUT (PD5)

TA0IN (PA7), TA6IN (PC1

TA2IN (PB7), TA8IN (PC2

TA4IN (PC0), TAAIN (PC4

SCLK5/CTS5 (PF2)

NMI

INT0 (PF6)

INT7 (PB7)

ADTRG (P57)

AVCC/AVSS

VREFH/VREFL

DAOUT0∼3

DAREFH

TXD0 (PD0)

RXD0 (PD1)

TXD1 (PD3)

RXD1 (PD4)

TXD3 (PE0)

RXD3 (PE1)

SCK (PF3)

SO/SDA (PF4)

SI/SCL (PF5)

TXD4 (PE3)

RXD4 (PE4)

TXD5 (PF0)

RXD5 (PF1)

256 KBROM

(*)

DMAC (4ch)

INTC

10-bit

ADC (16ch)

10-bit

DAC (3ch)

SIO0

SIO1

SIO3

SERIAL

BUS I/F

SIO4

SIO5

16-bit TMR0-D

(14ch)

8-bit TMR0/1

∼ A/B

(12ch)

TX19 Proccessor Core

TX19 CPU

MAC DSU

16 KBRAM

ROM correction

G-Bus

I/O Bus I/F

Counter (RTC)

CG

EBIF

PORT0

PORT1

PORT2

PORT3

PORT4

WDT

Real-Time

INTBCDE

KWUP

JTAG

TX1942CY/CZ

(*) MROM for the mask ROM

version.

CZUE/XBG:384KB

X1

X2

XT1 (PD6)

XT2 (PD7)

SCOUT (P44)

PLLOFF*

RESET*

BW0/1

INTLV (PE7)

D0∼7 (P00∼P07)

D8/A8∼AD15/A15 (P10∼P17)

0/A16∼A7/A23 (P20∼P27)

RD (P30)

WR (P31)

HWR (P32)

WAIT (P33)

BUSRD (P34)

BUSAK* (P35)

R/W (P36)

P37

CS0∼CS3 (P40∼P43)

INTB∼C (PB0∼1)

INTD∼E (PB3∼4)

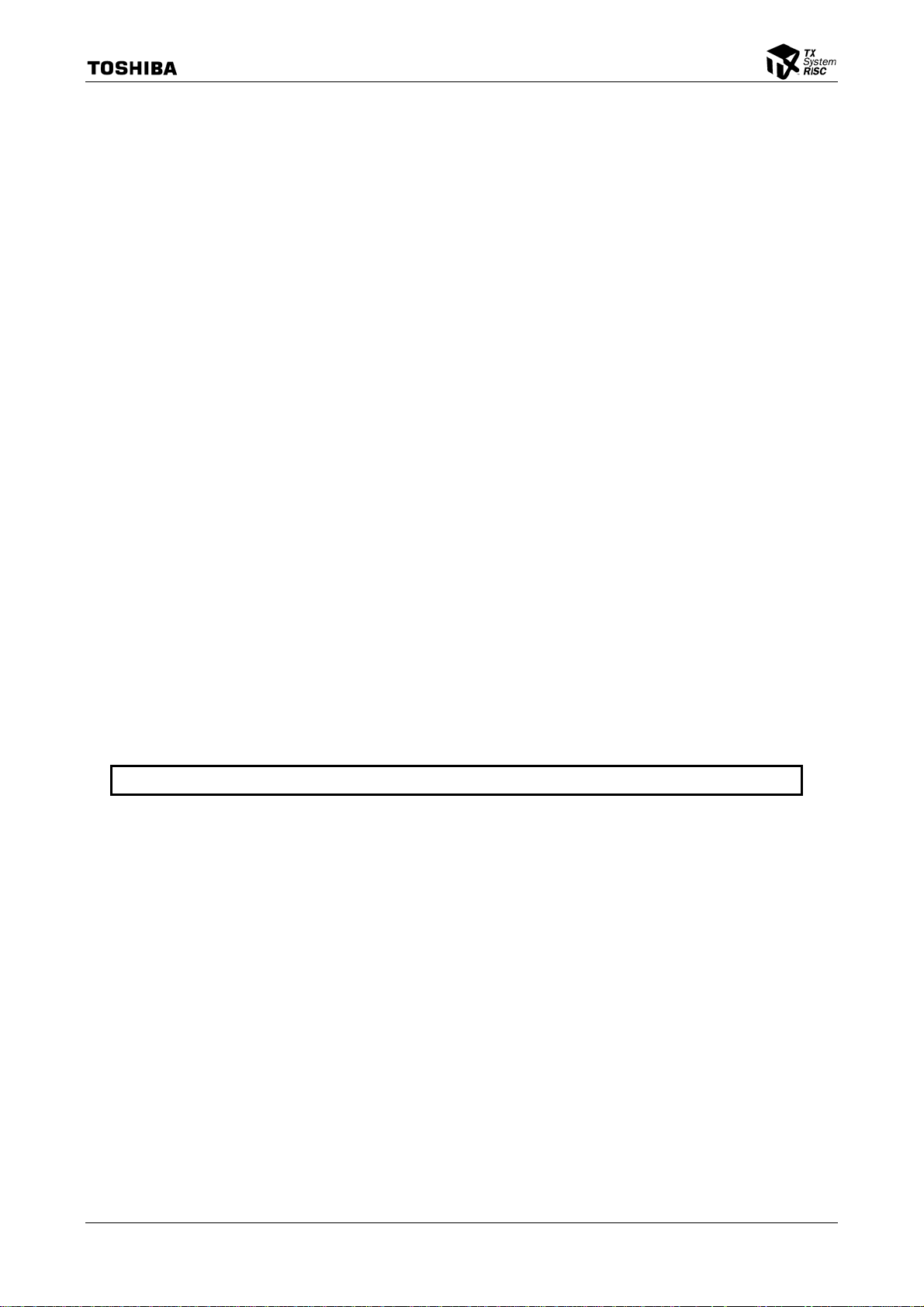

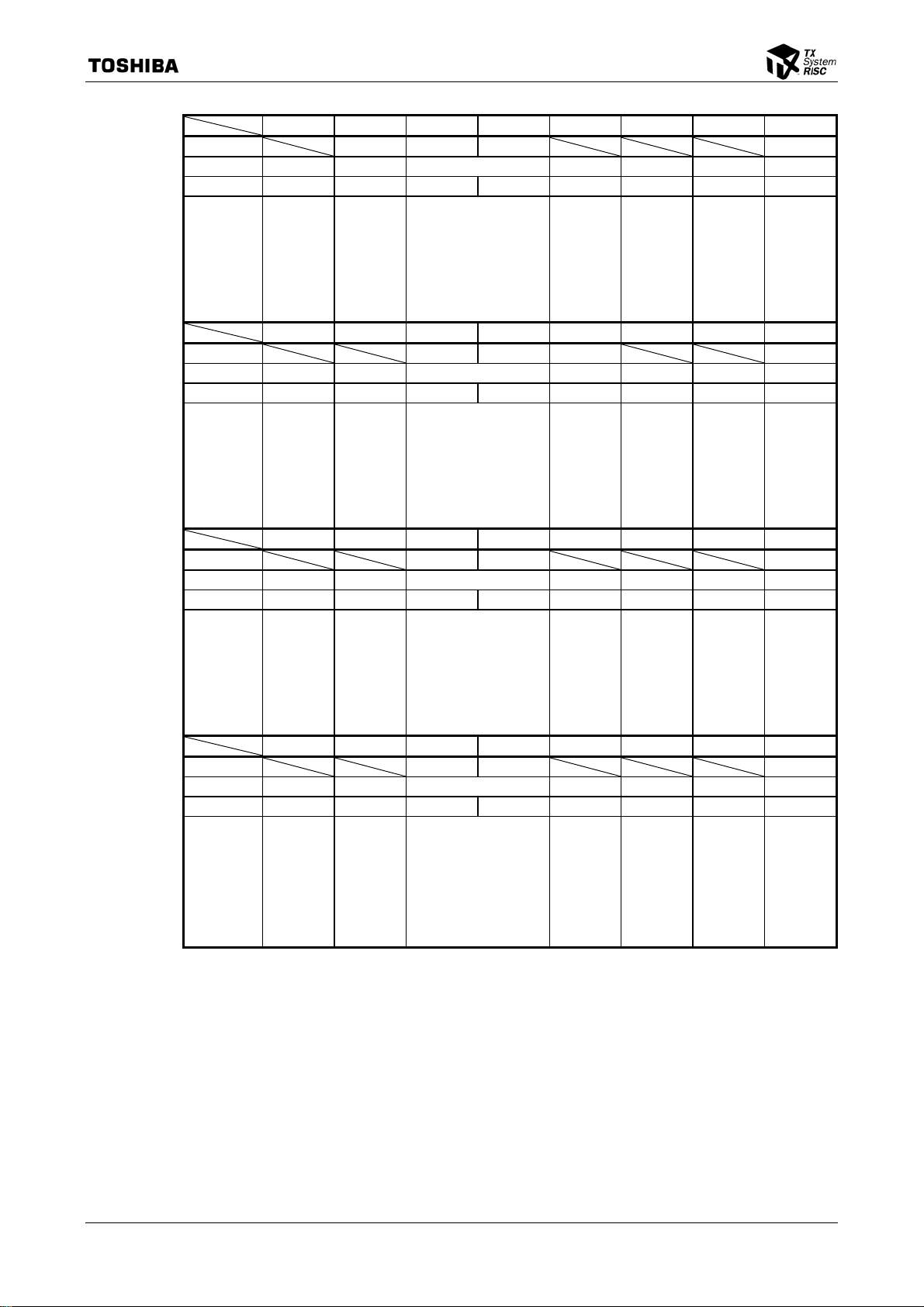

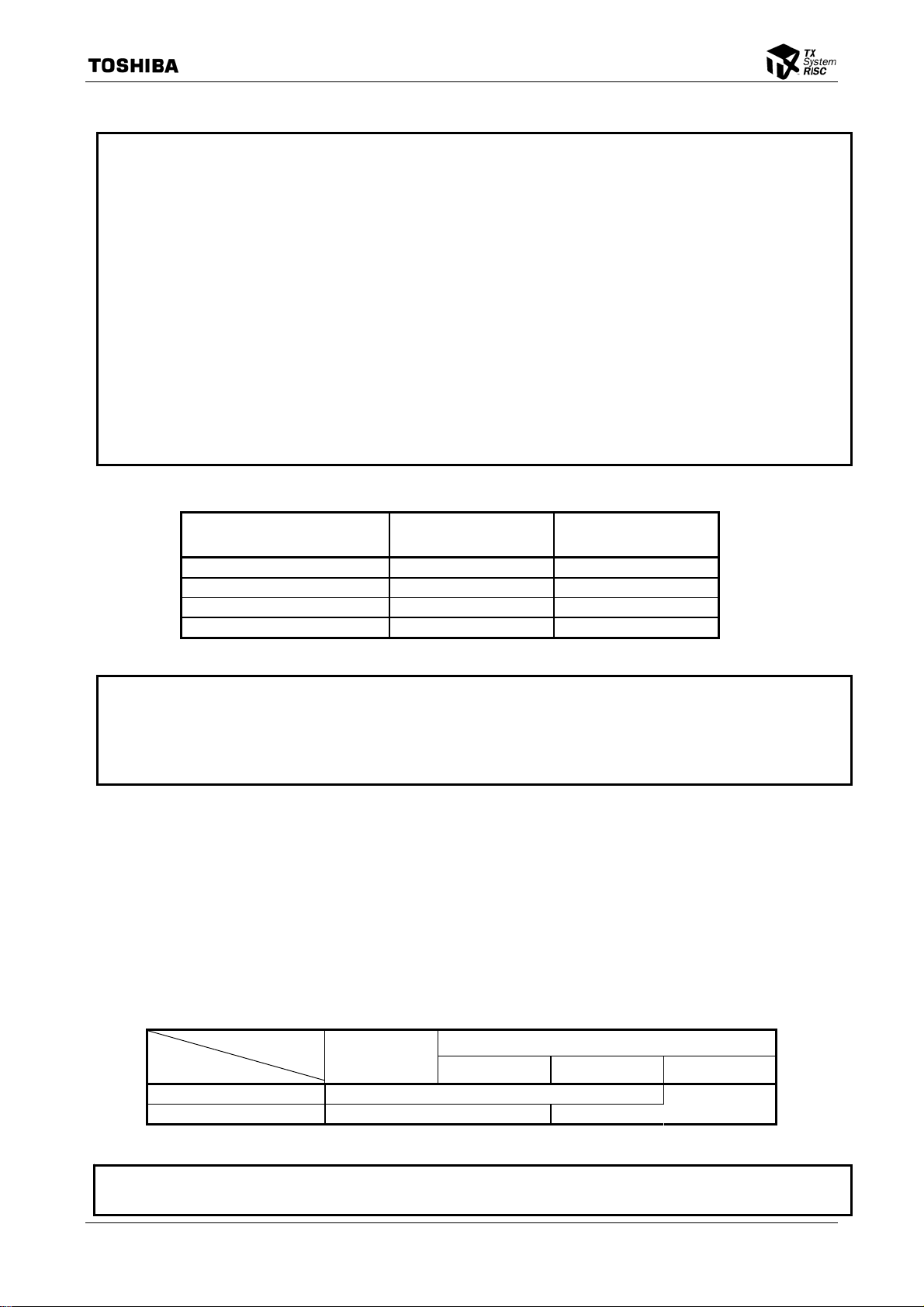

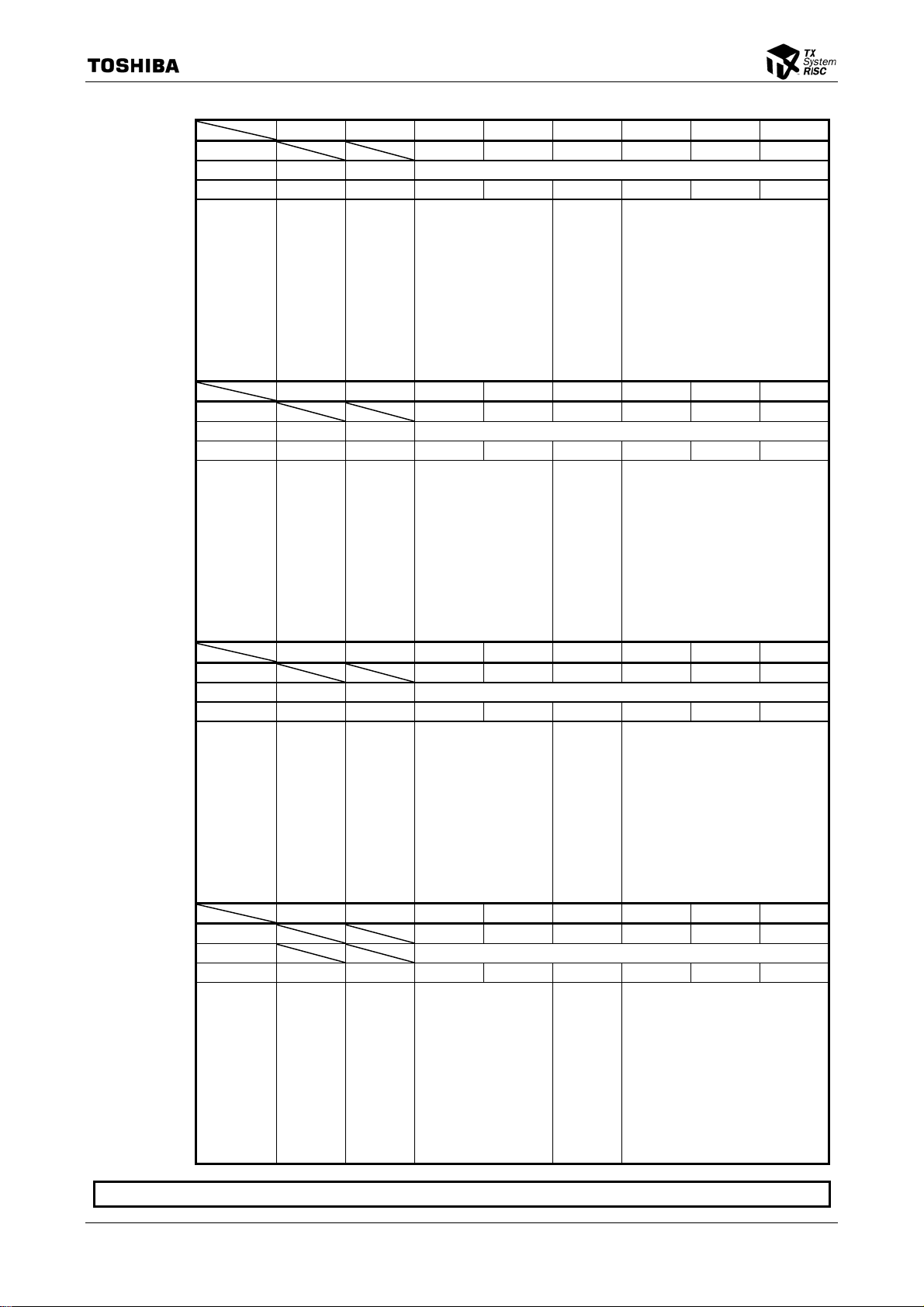

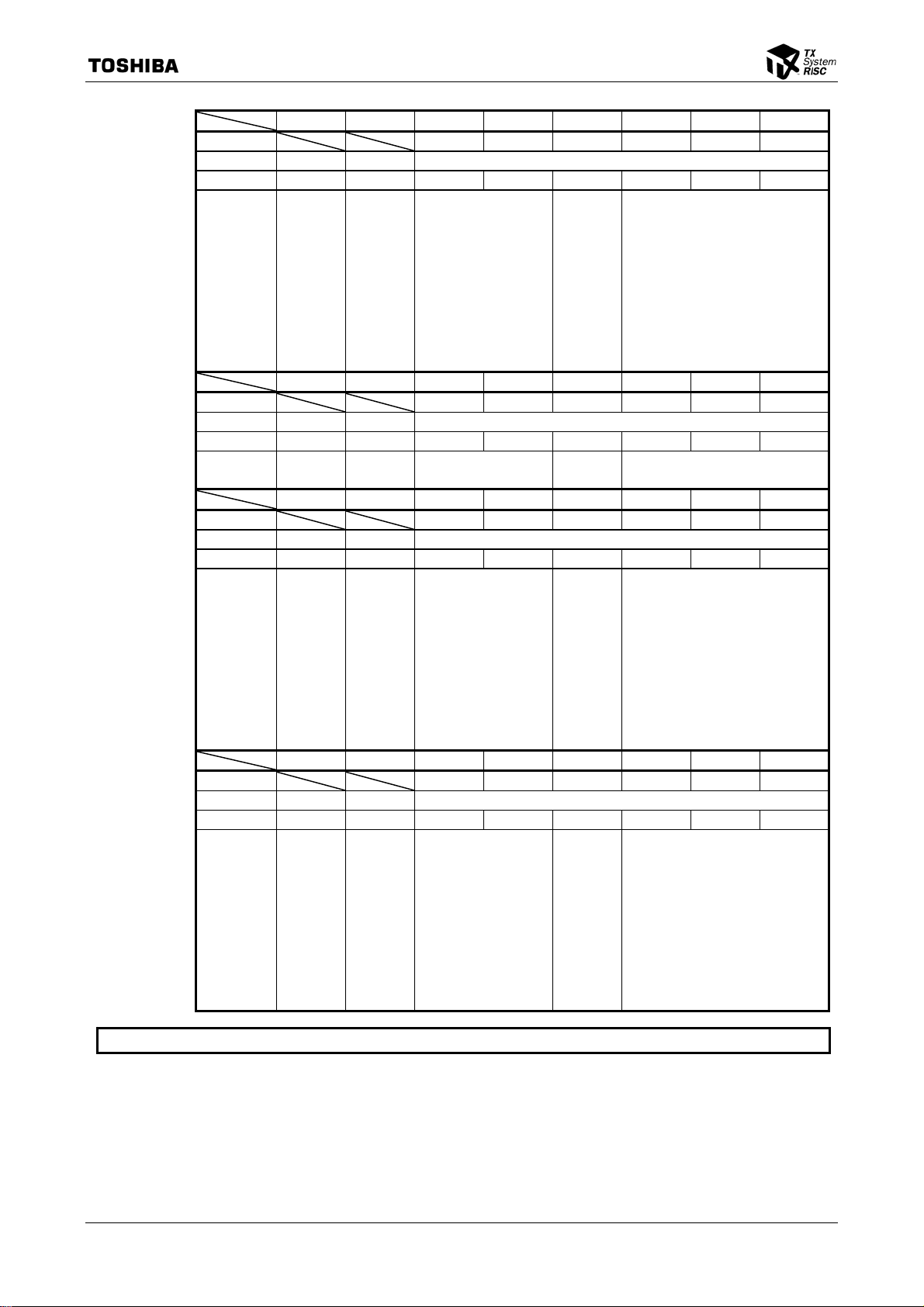

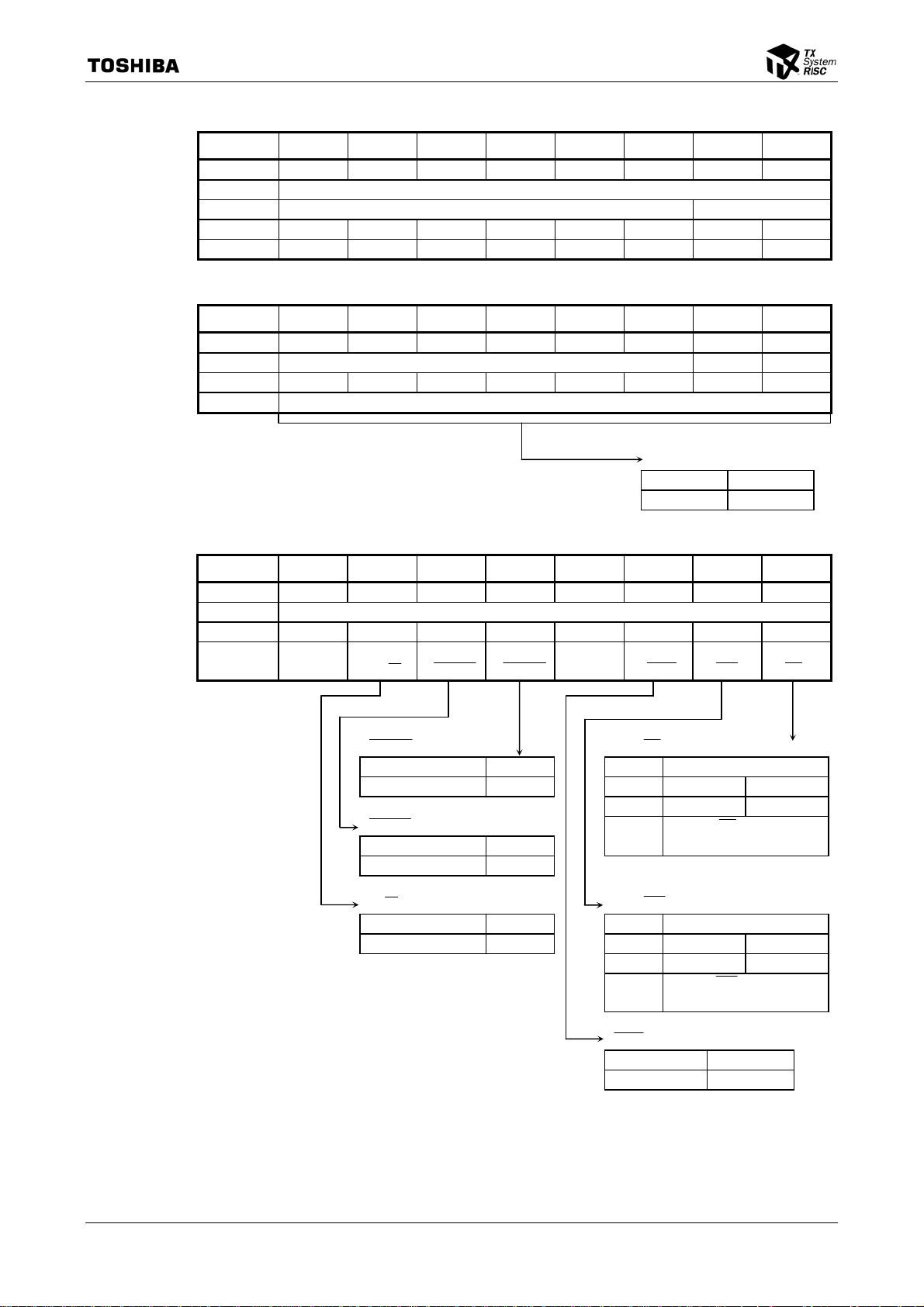

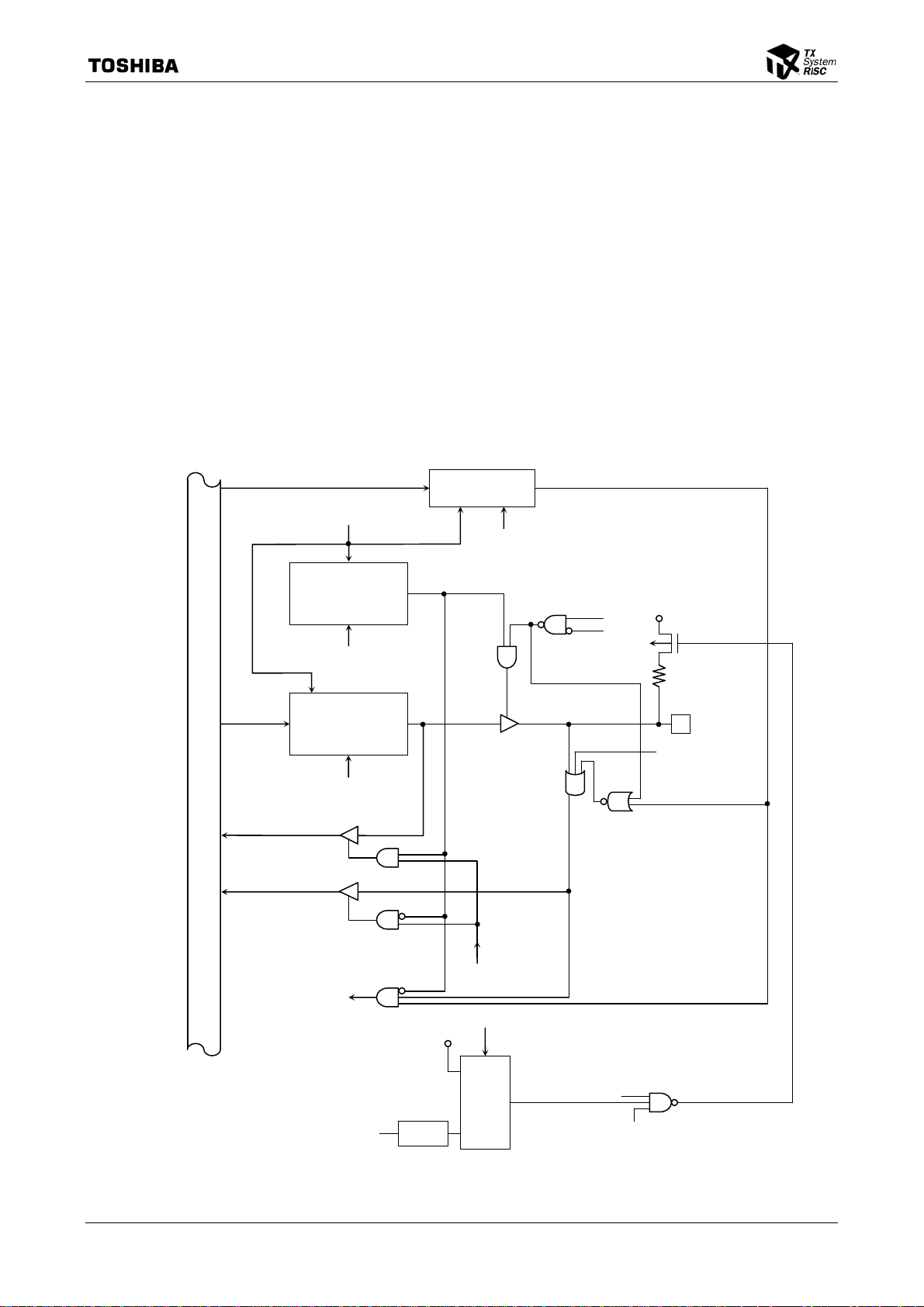

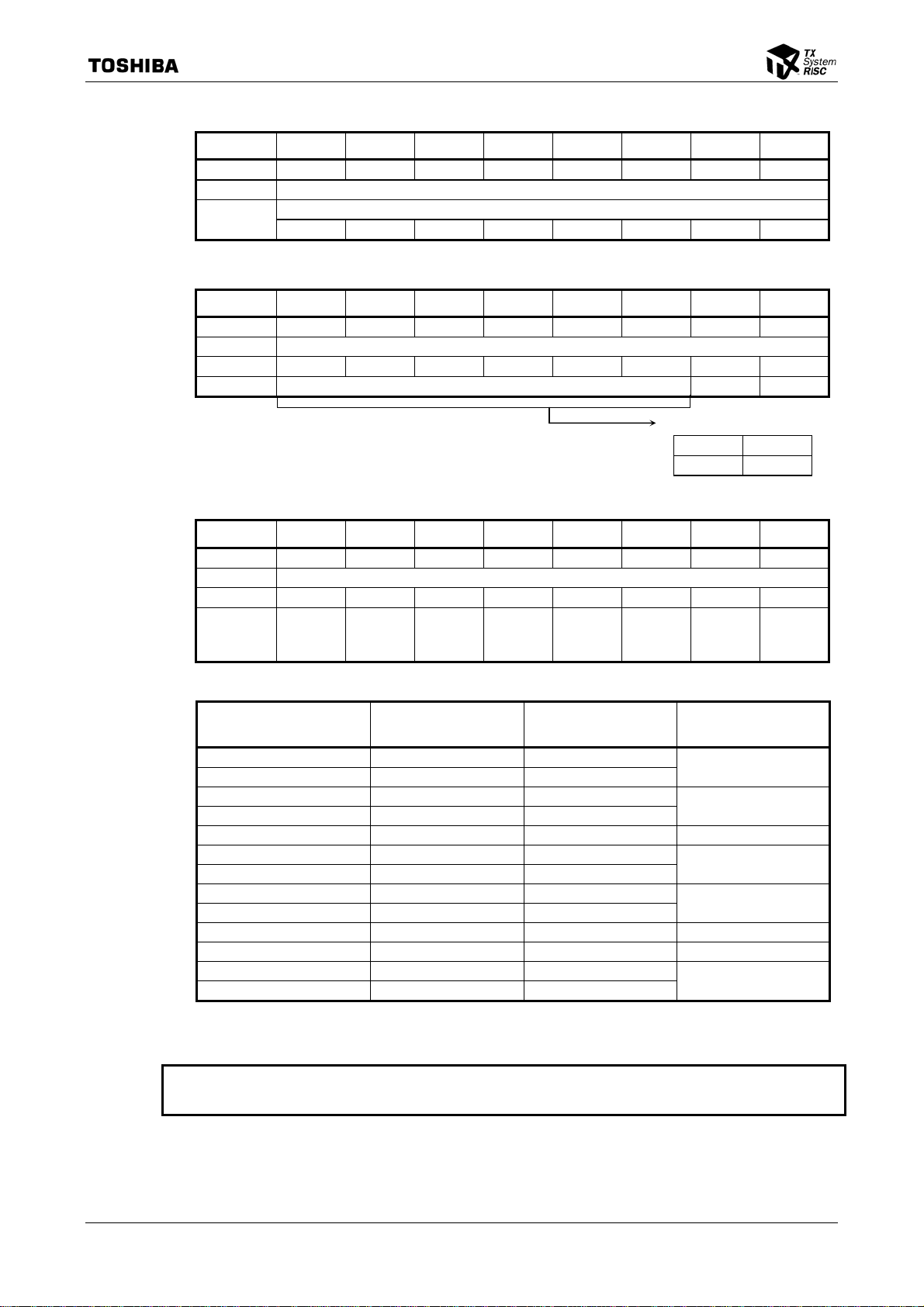

Figure 1.1 TMP1942 Block Diagram

TMP1942CY/CZ-4

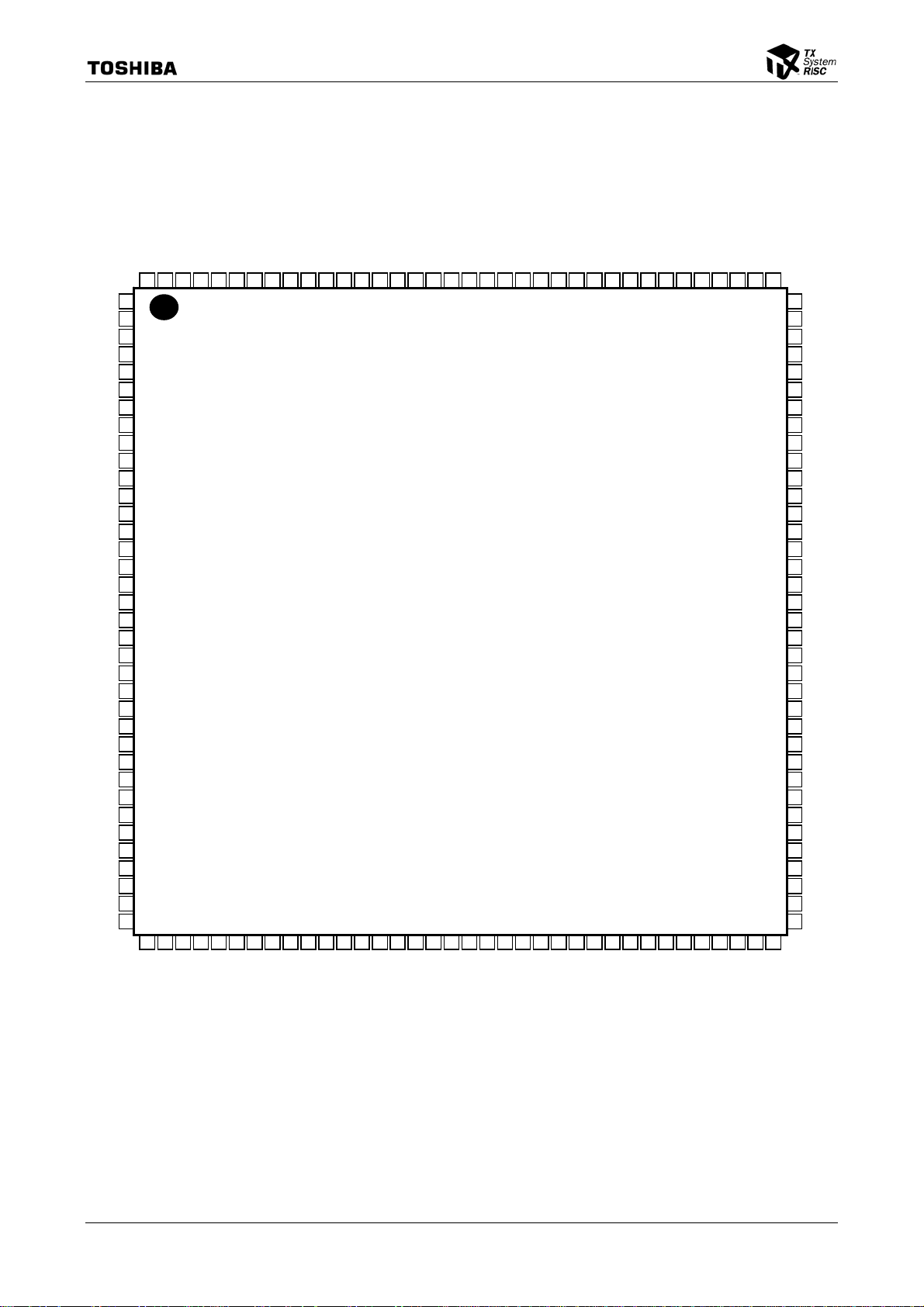

2. Signal Descriptions

This section contains pin assignments for the TMP1942 as well as brief descriptions of the functions of the

TMP1942 input and output pins.

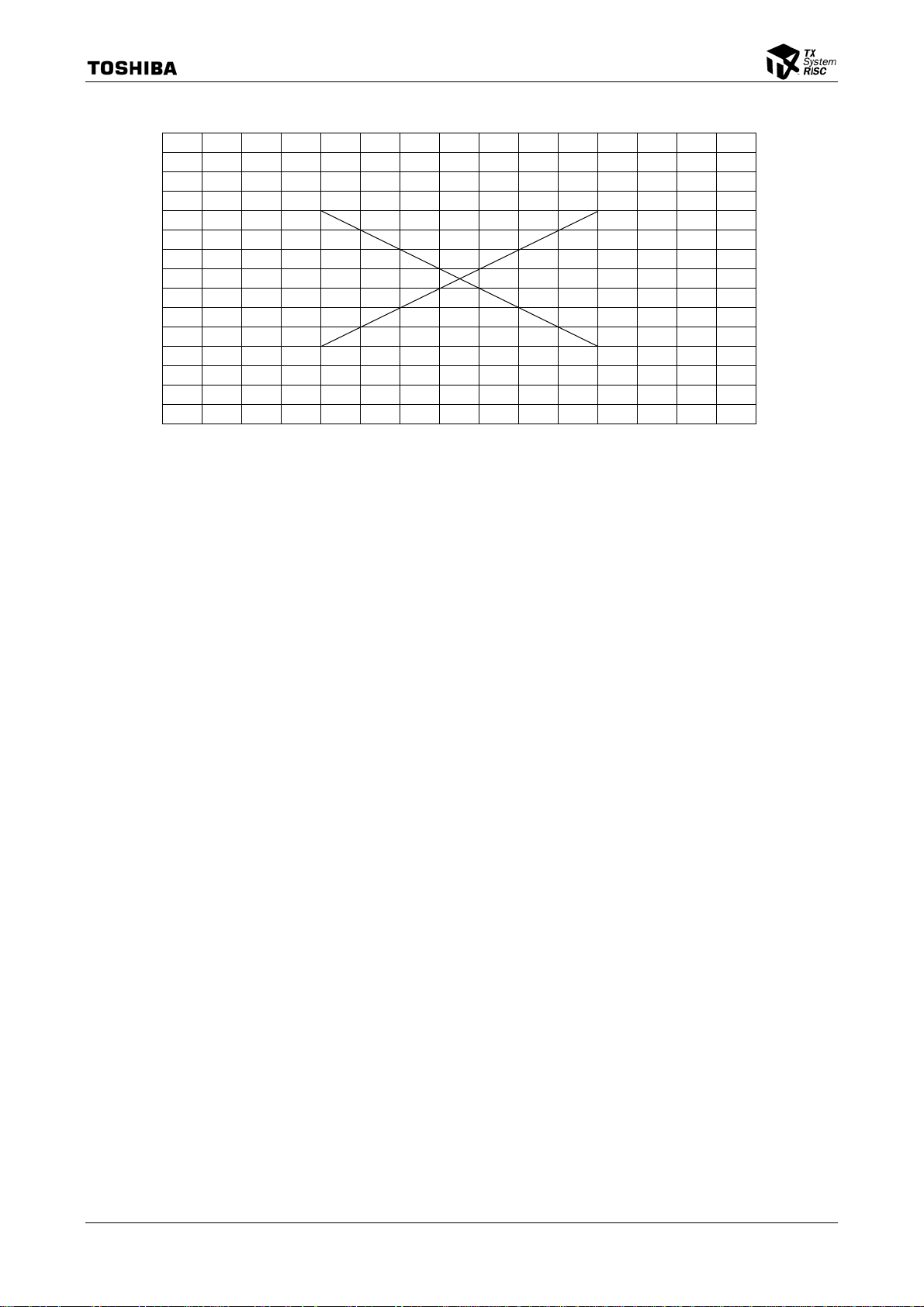

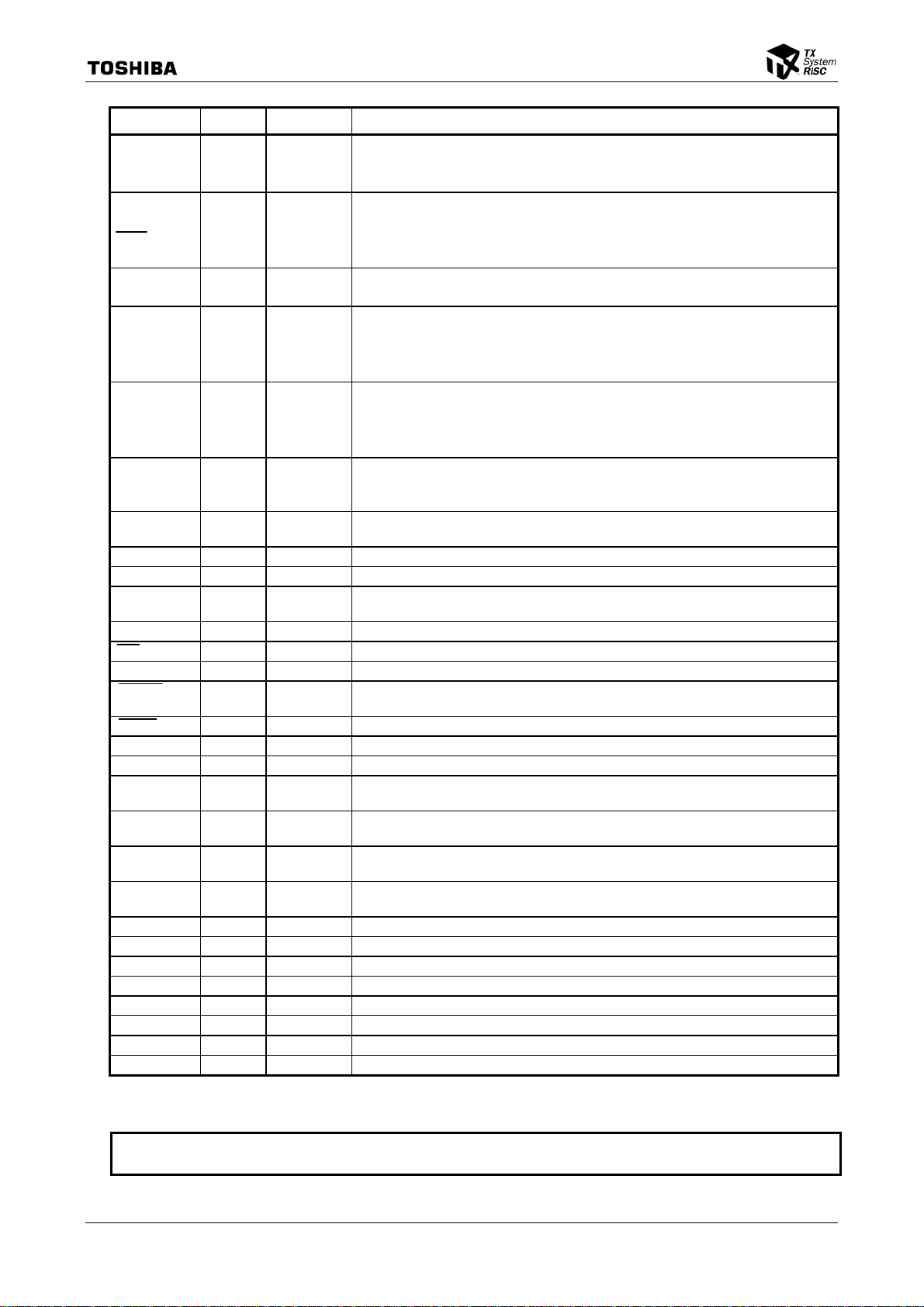

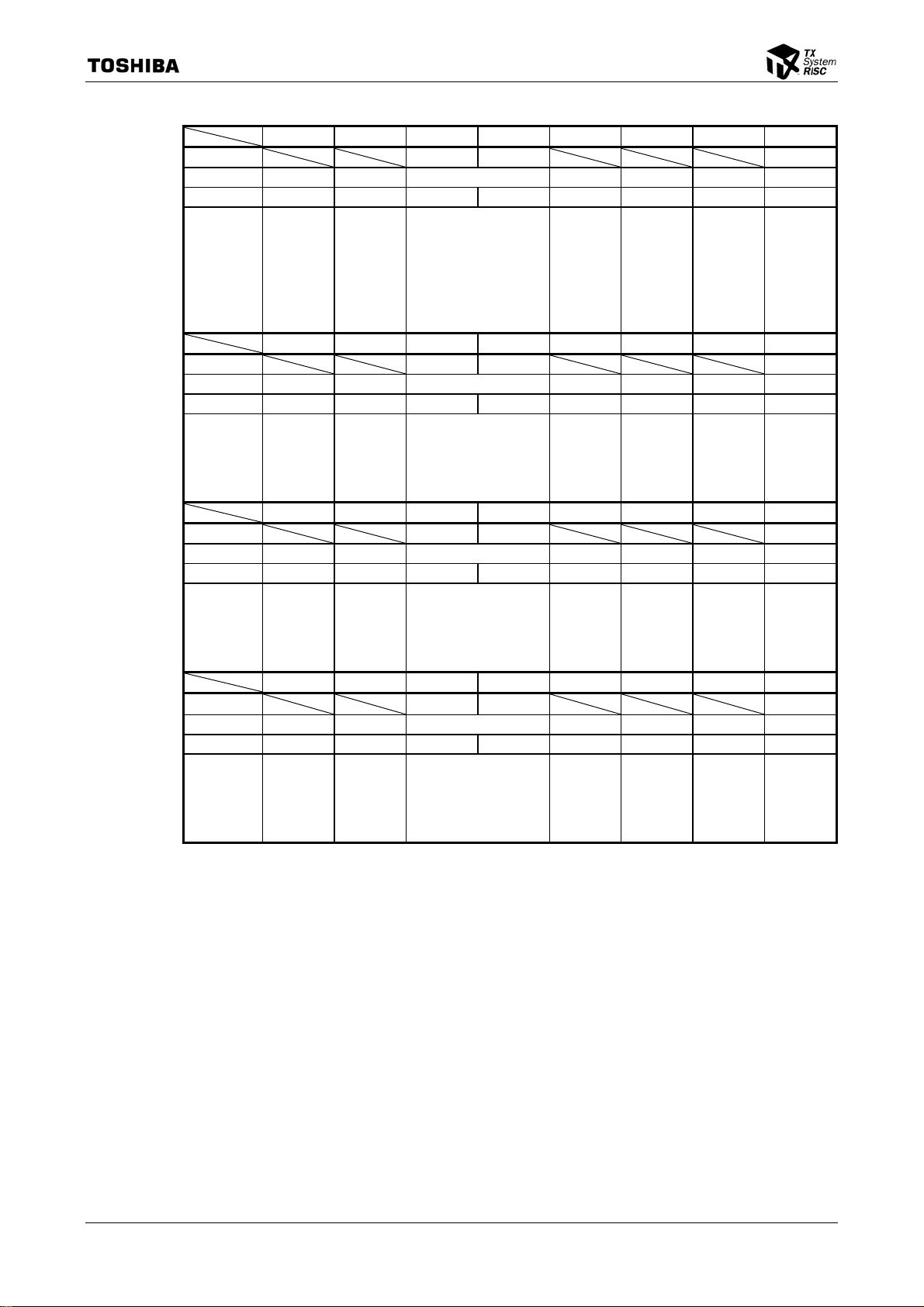

2.1 Pin Assignment

Table 2.1.1 shows TMP1942 pin assignment.

144 143 142 141 139 138 137 136 135 134 133 132 131 130 129 128 127 126 125 124 123 122 121 120 119 118 117 116 115 114 113 112 111 110 109140

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37 38 39 40 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 7241

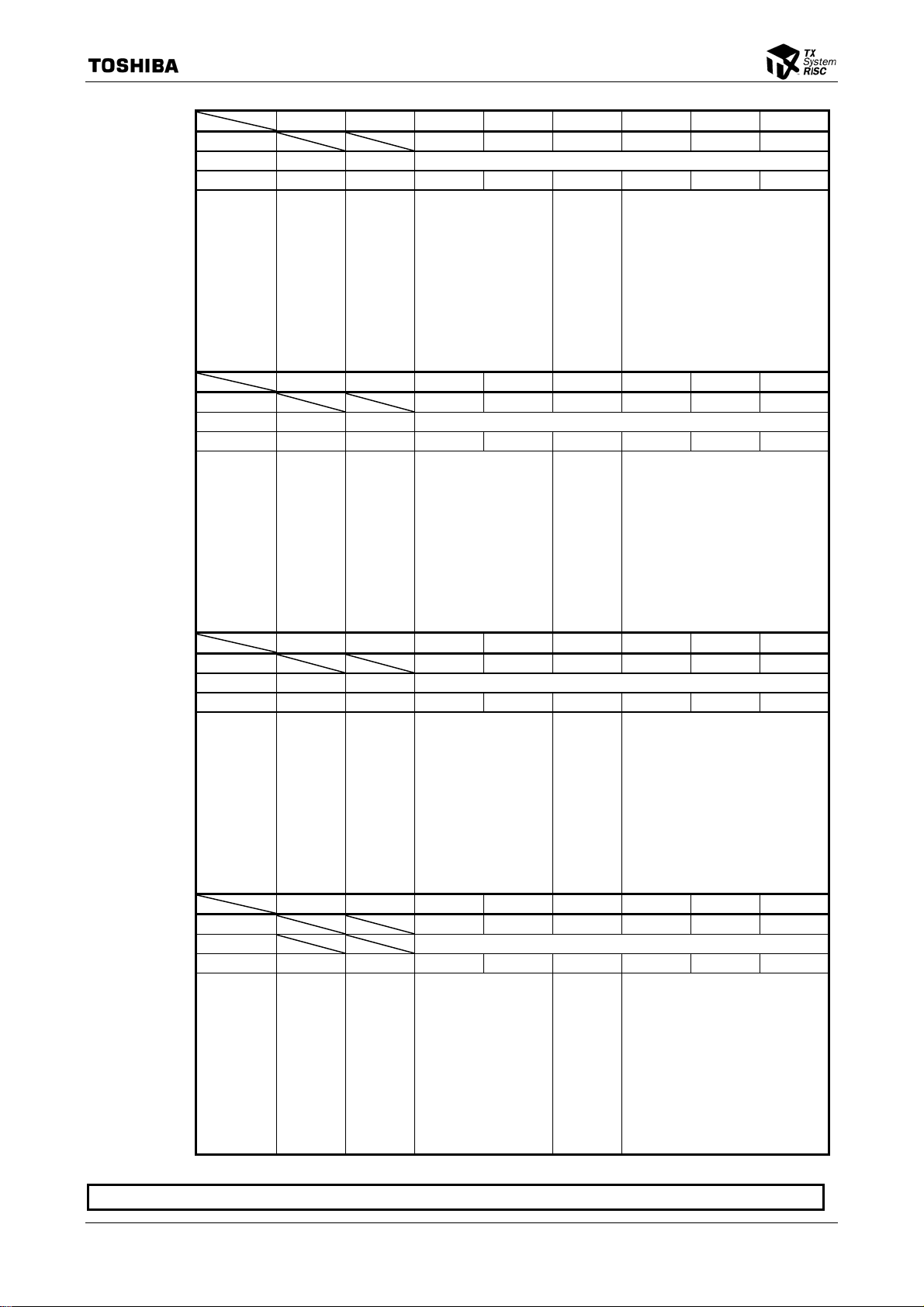

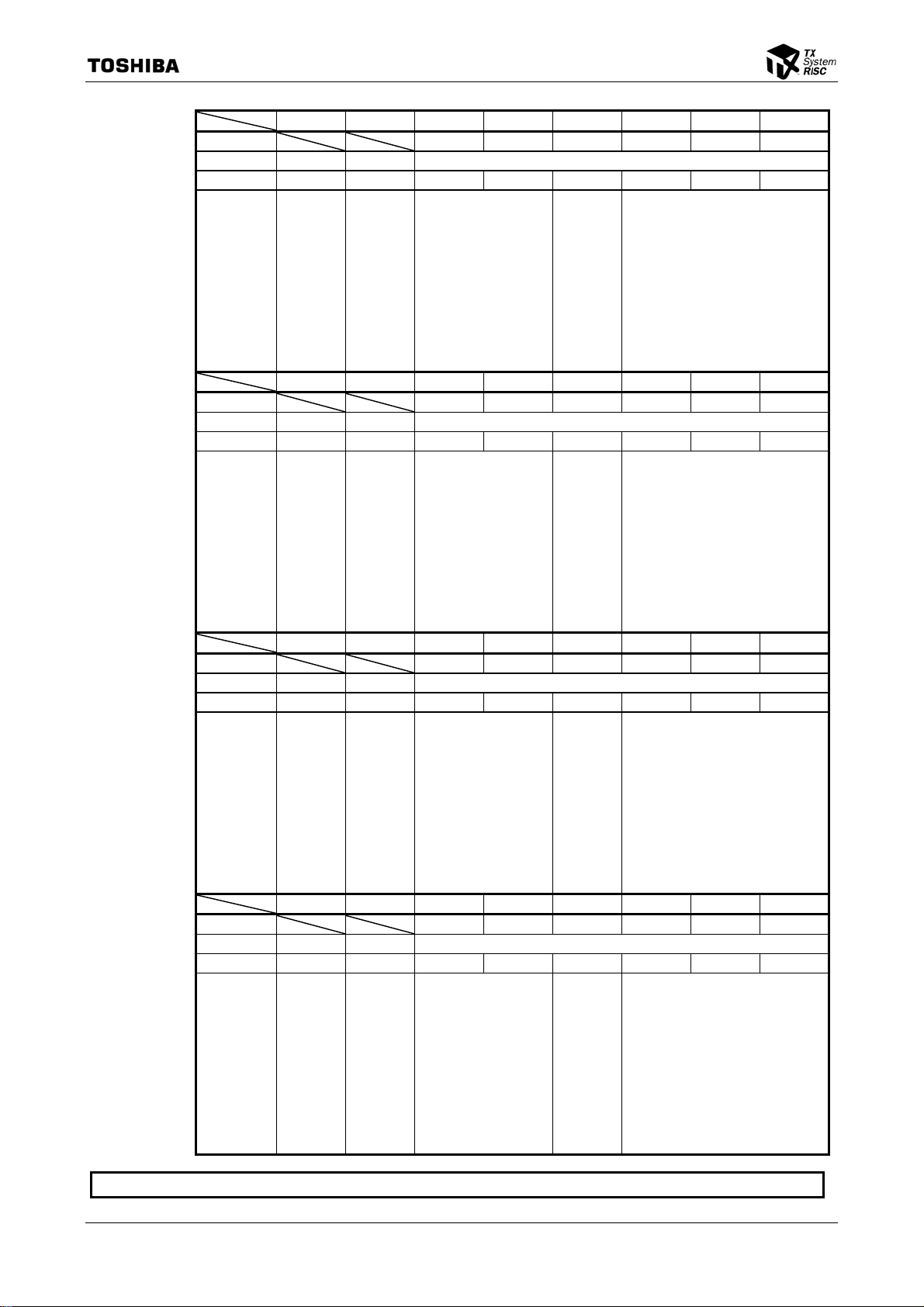

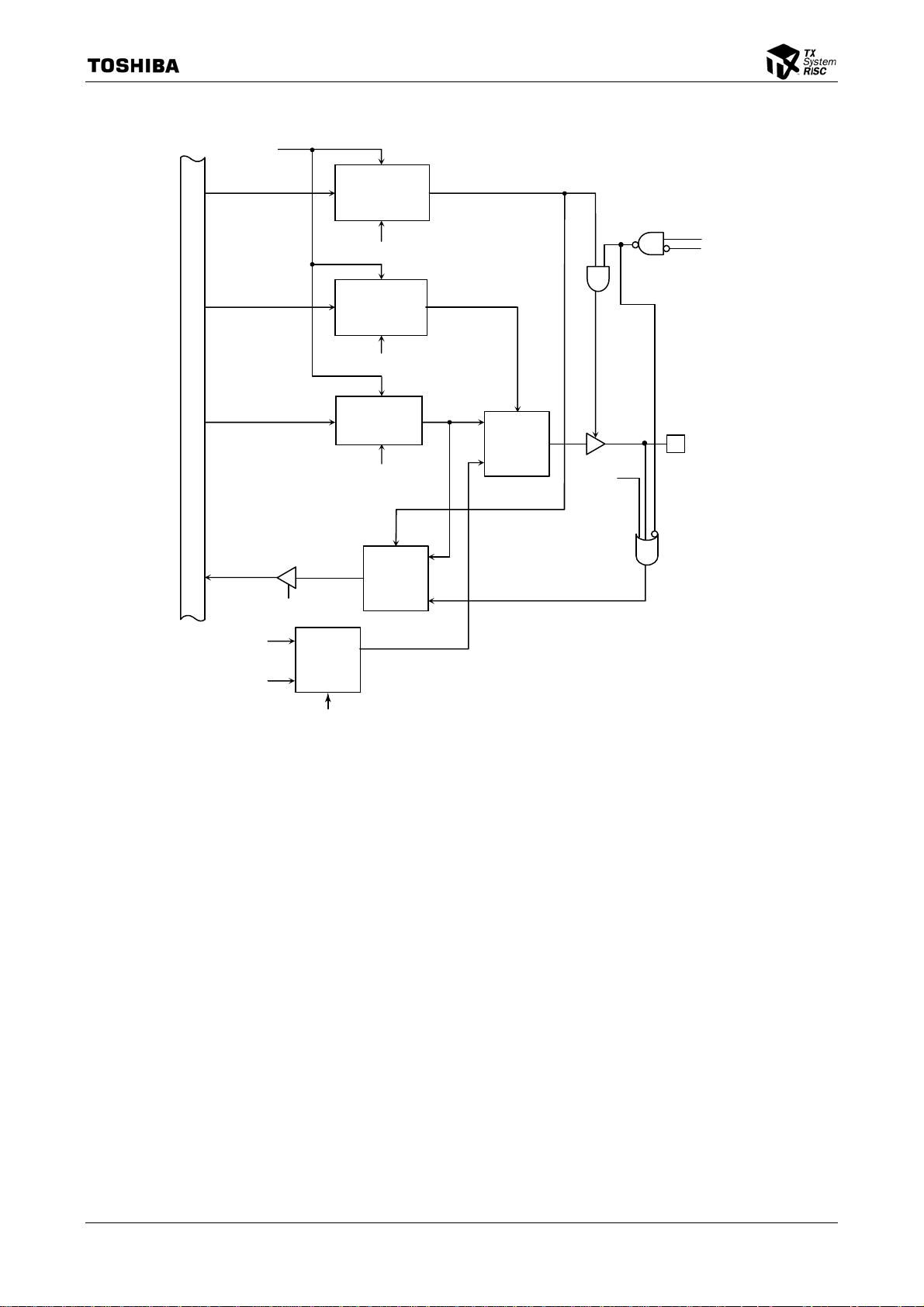

Figure 2.1.1 144-Pin LQFP Pin Assignment

TX1942CY/CZ

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

TMP1942CY/CZ-5

TX1942CY/CZ

Table 2.1.1 Pin Assignment (144-pin LQFP)

Pin

No.

1 VREFH 37 P11/AD9/A9 73 P90/KEY8/DCLK 109 CVCC

2 VREFL 38 P12/AD10/A10 74 P91/KEY9/PCST2 110 X2

3 P50/AN0 39 P13/AD11/A11 75 P92/TB4OUT/PCST1 111 CVSS

4 P51/AN1 40 P14/AD12/A12 76 P93/TB5OUT/PCST0 112 X1

5 P52/AN2 41 P15/AD13/A13 77 P94/TB6OUT/SDSA0/TPC 113 TEST1

6 P53/AN3 42 P16/AD14/A14 78 P95/TB7IN0/DBGE 114 RESET

7 DAVCC 43 P17/AD15/A15 79 P96/TB7IN1/DINT 115 PD6/XT1

8 DAVSS 44 P20/A0/A16 80 P97/TB7OUT/DRESET 116 PD7/XT2

9 DAREH 45 P21/A1/A17 81 DVCC3 117 NMI

10 DAOUT0 46 P22/A2/A18 82 PA0/TB0IN0/INT3 118 BW0

11 DAOUT1 47 P23/A3/A19 83 PA1/TB0IN1/INT4 119 PB0/TB2IN0/INTB

12 DAOUT2 48 P24/A4/A20 84 PA2/TB0OUT 120 PB1/TB2IN1/INTC

13 P54/AN4 49 P25/A5/A21 85 PA3/TB1IN0/INT5 121 PB2/TB2OUT/TB4IN0

14 P55/AN5 50 P26/A6/A22 86 PA4/TB1IN1/INT6 122 PB3/TB3IN0/INTD

15 P56/AN6 51 P27/A7/A23 87 PA5/TB1OUT 123 PB4/TB3IN1/INTE

16 P57/AN7/ADTRG 52 TEST0 88 PA6/TA1OUT 124 PB5/TB3OUT/TB4IN1

17 P60/AN8/KEY0 53 PLLOFF 89 PA7/TA0IN/KEYA 125 PB6/TA3OUT

18 DVSS 54 DVSS 90 DVSS 126 DVSS

19 P61/AN9/KEY1 55 ALE 91 RSTPUP 127 DVCC3

20 P62/AN10/KEY2 56 DVCC3 92 PC0/TA4IN/INT8 128 PB7/TA2IN/INT7/KEYB

21 P63/AN11/KEY3 57 BW1 93 PC1/TA6IN/INT9 129 PD0/TXD0/TB9IN0

22 P64/AN12/KEY4 58 P30/RD 94 PC2/TA8IN/INTA 130 PD1/RXD0/TB9IN1

23 P65/AN13/KEY5 59 P31/WR 95 PC3/TA5OUT 131 PD2/SCLK0/CTS0

24 P66/AN14/KEY6 60 P32/HWR 96 PC4/TAAIN 132 PD3/TXD1/TBAIN0

25 P67/AN15/KEY7 61 P33/WAIT 97 PC5/TA7OUT 133 PD4/RXD1/TBAIN1

26 DVCC3 62 P34/BUSRQ 98 PC6/TB8IN0/KEYC 134 PD5/SCLK1/CTS1/TABOUT

27 P00/AD0 63 P35/BUSAK 99 PC7/TB8IN1/TA9OUT 135 PE0/TXD3

28 P01/AD1 64 P36/R/W 100 DVCC52 136 PE1/RXD3

29 P02/AD2 65 P37/DSU 101 PF0/TXD5 137 PE2/SCLK3/CTS3

30 P03/AD3 66 DVSS 102 PF1/RXD5/KEYD 138 PE3/TXD4

31 P04/AD4 67 DVCC3 103 PF2/SCLK5/CTS5 139 PE4/RXD4

32 P05/AD5 68 P40/CS0 104 PF3/SCK 140 PE5/SCLK4/CTS4

33 P06/AD6 69 P41/CS1 105 PF4/SO/SDA 141 PE6/INT1/BOOT

34 P07/AD7 70 P42/CS2 106 PF5/SI/SCL 142 PE7/INT2/INTLV

35 DVSS 71 P43/CS3 107 PF6/INT0 143 AVCC

36 P10/AD8/A8 72 P44/SCOUT 108 DVCC51 144 AVSS

Pin Name

Pin

No.

Pin Name

Pin

No.

Pin Name

Pin

No.

Pin Name

TMP1942CY/CZ-6

TX1942CY/CZ

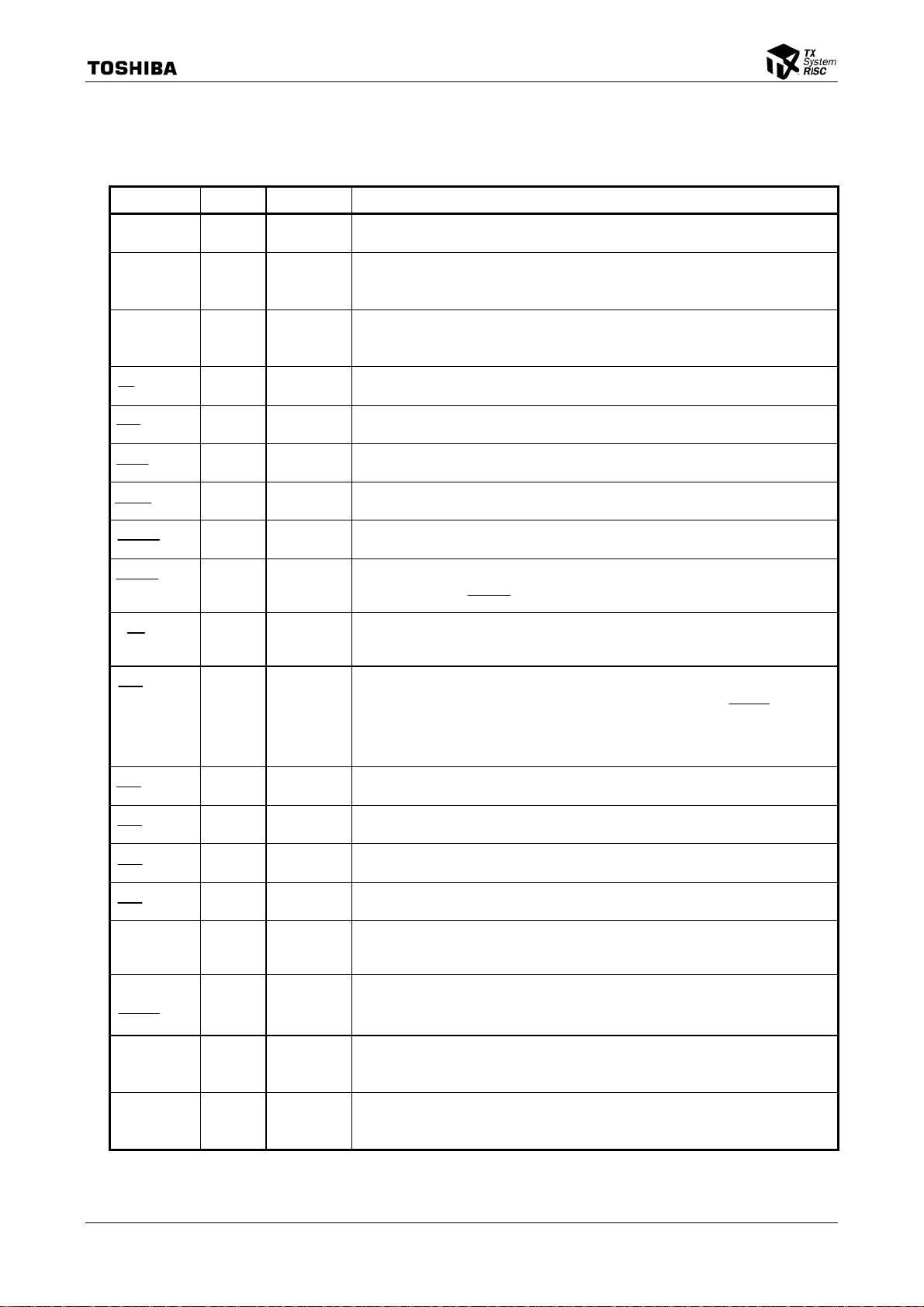

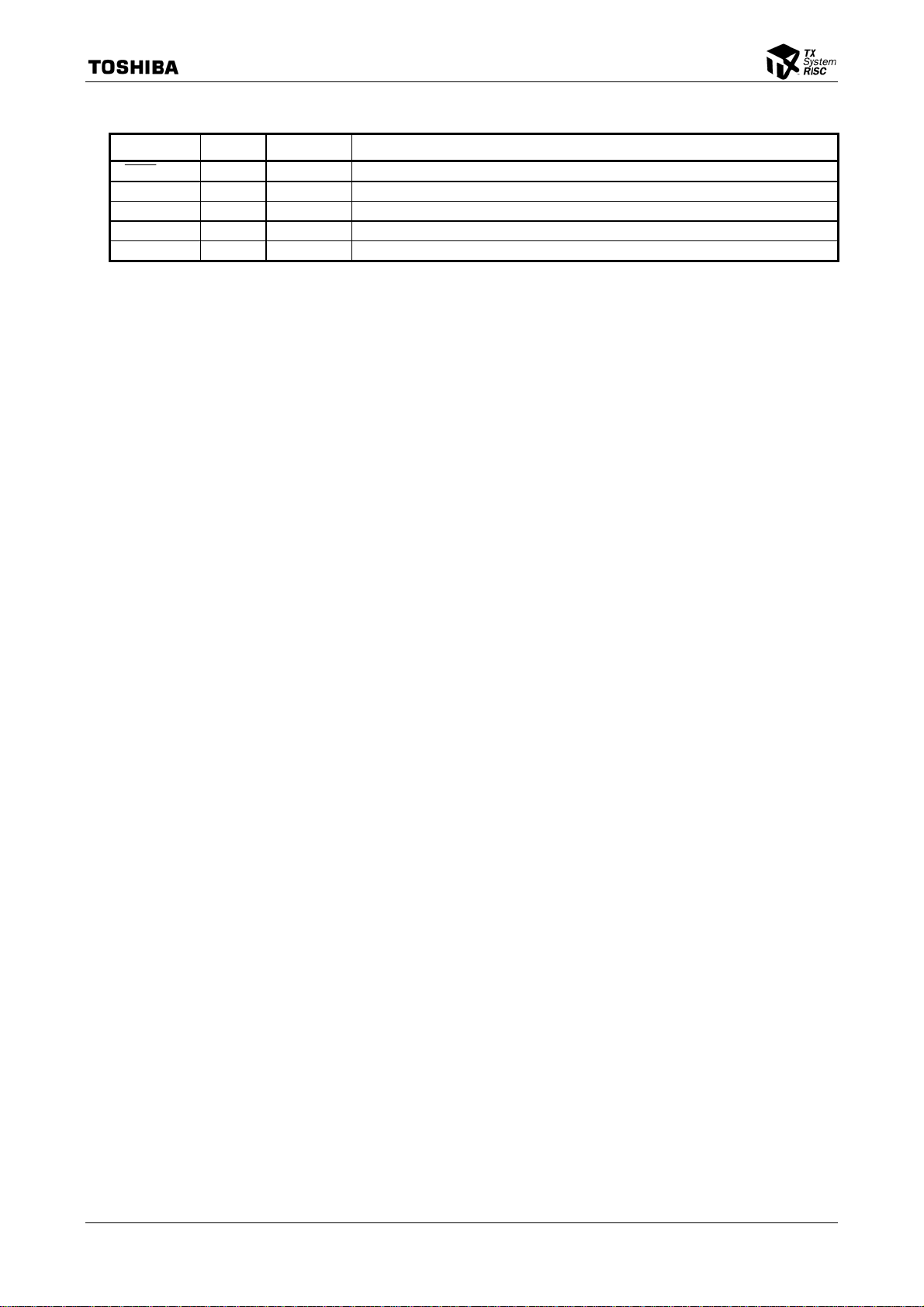

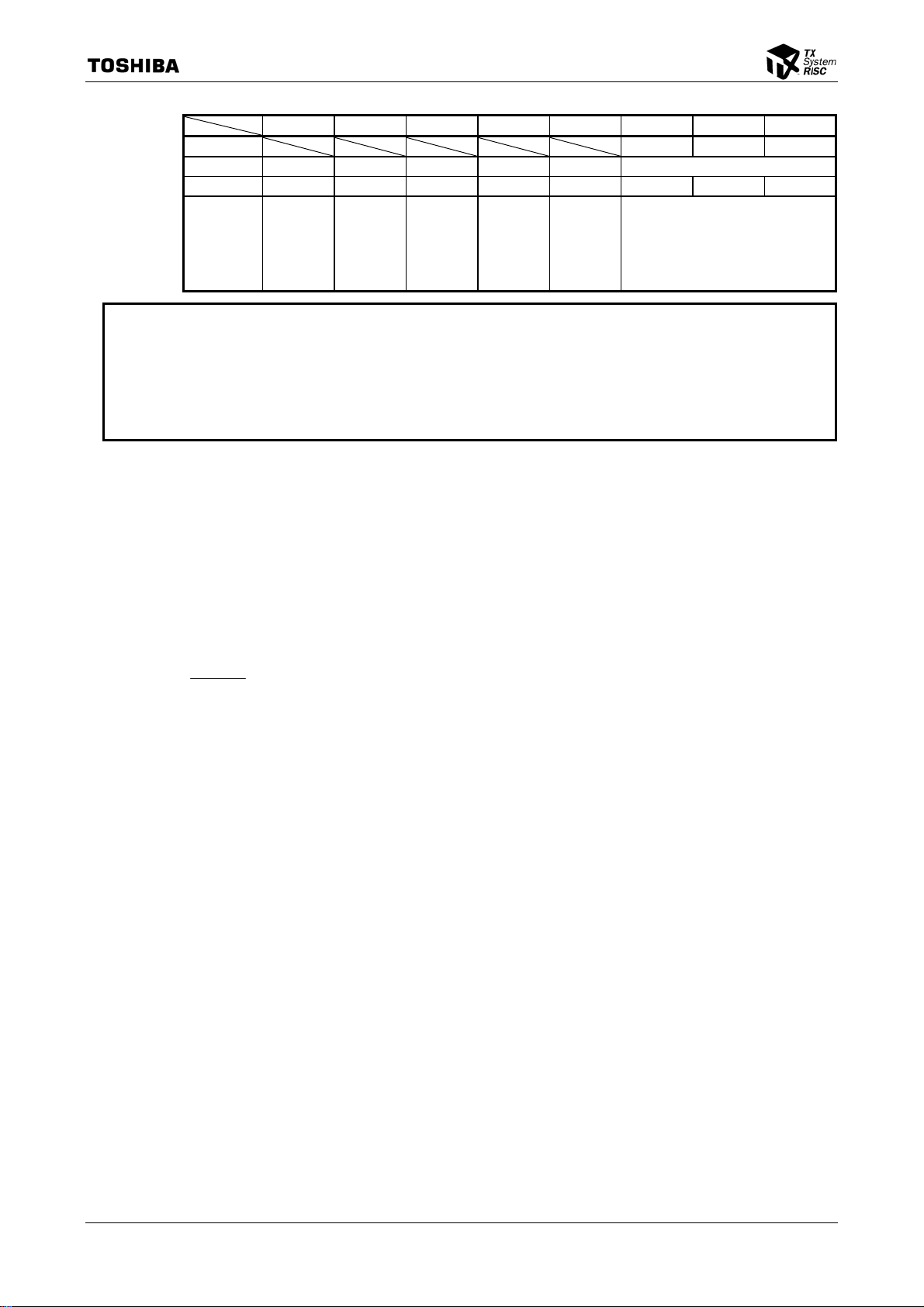

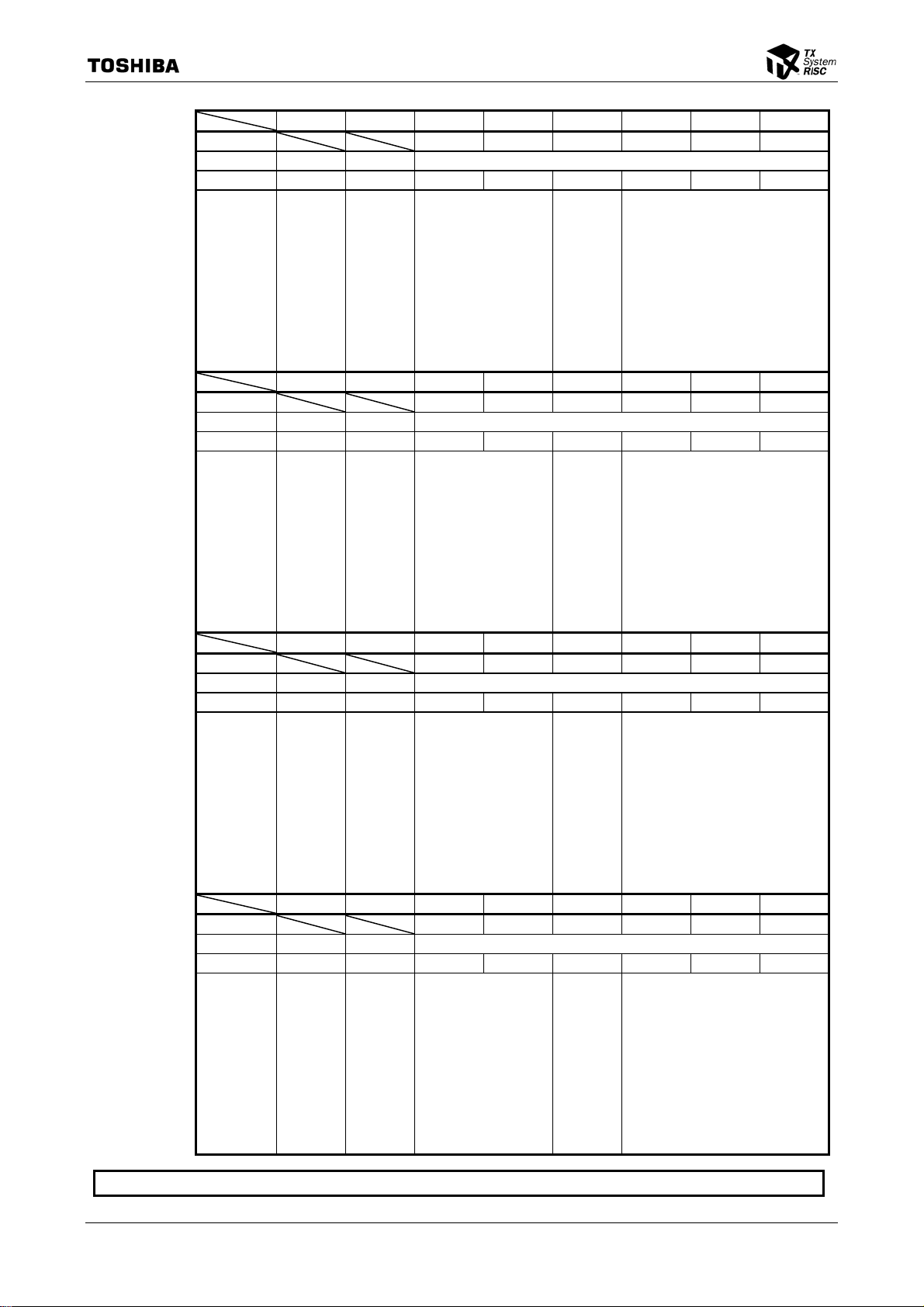

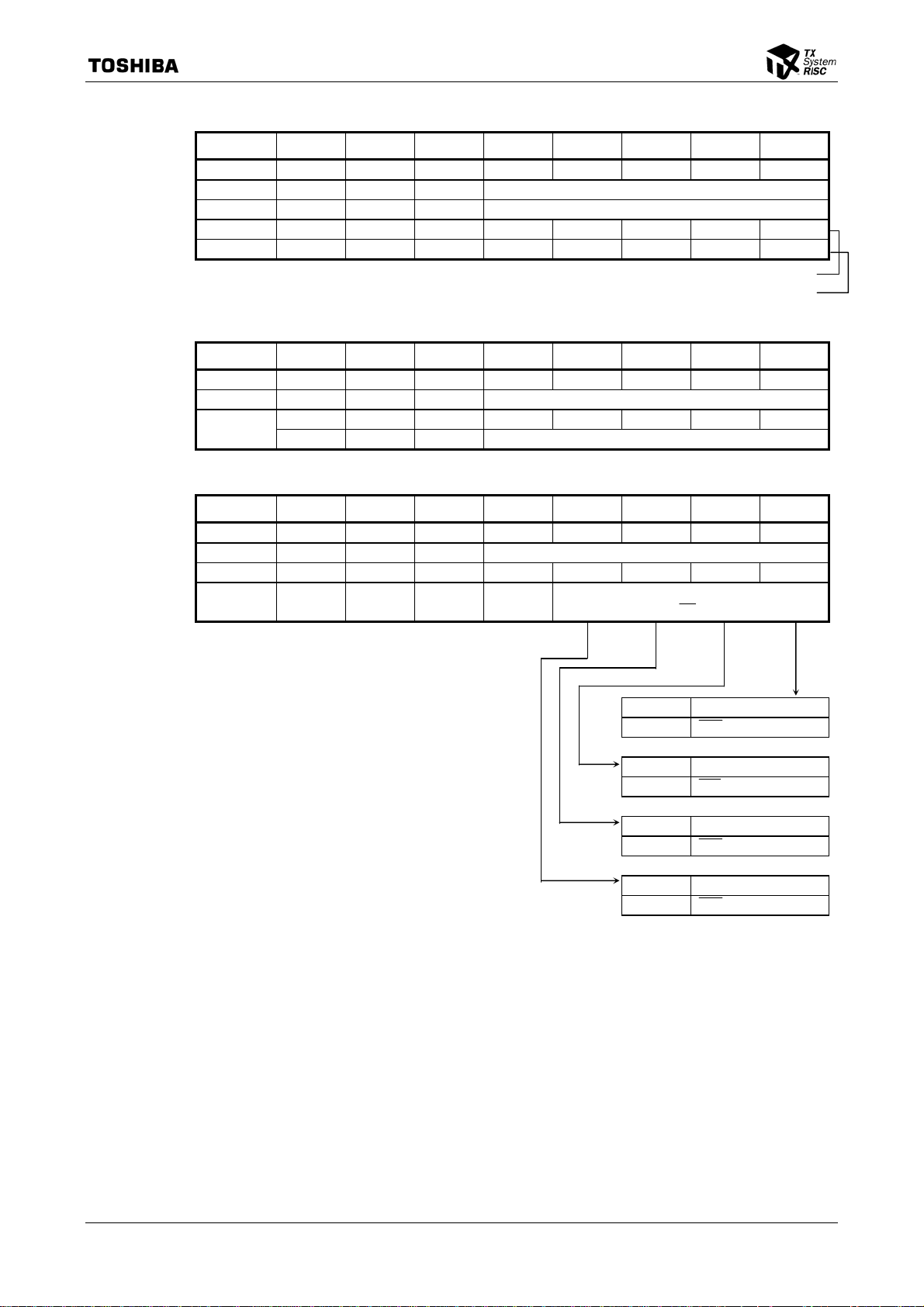

Figure 2.1.2 shows pin assignment for the 177-pin model of the TMP1942.

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15

B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15

D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15

E1 E2 E3 E4 E12 E13 E14 E15

F1 F2 F3 F4 F12 F13 F14 F15

G1 G2 G3 G4 G12 G13 G14 G15

H1 H2 H3 H4 H12 H13 H14 H15

J1 J2 J3 J4 J12 J13 J14 J15

K1 K2 K3 K4 K12 K13 K14 K15

L1 L2 L3 L4 L12 L13 L14 L15

M1 M2 M3 M4 M5 M6 M7 M8 M9 M10 M11 M12 M13 M14 M15

N1 N2 N3 N4 N5 N6 N7 N8 N9 N10 N11 N12 N13 N14 N15

P1 P2 P3 P4 P5 P6 P7 P8 P9 P10 P11 P12 P13 P14 P15

R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R14 R15

Figure 2.1.2 177-Pin CSP Pin Assignment

TMP1942CY/CZ-7

TX1942CY/CZ

Table 2.1.2 Pin Assignment (177-pin CSP)

Pin

No.

A1 VREFL D1 P50/AN0 H13 NC N4 P16/AD14/A14

A2 AVSS D2 DAVSS H14 NC N5 P21/A1/A17

A3 AVCC D3 P52/AN2 H15 DVSS N6 P25/A5/A21

A4 PE7/INT2/INTLV D4 P51/AN1 J1 P67/AN15/KEY7 N7 DVSS

A5 PE3/TXD4 D5 PE0/TXD3 J2 P65/AN13/KEY5 N8 TEST0

A6 TCK (JTAG) D6 PD3/TXD1/TBAIN0 J3 P66/AN14/KEY6 N9 P30/RD

A7 PD2/SCLK0/CTS0 D7 PB7/TA2IN/INT7/KEYB J4 P64/AN12/KEY4 N10 P32/HWR

A8 PB5/TB3OUT/TB4IN1 D8 DVSS J12 PA6/TA1OUT N11 P37

A9 PB1/TB2IN1/INTC D9 PB2/TB2OUT/TB4IN0 J13 PA7/TA0IN/KEYA N12 DVSS

A10 PD7/TX2 D10 NMI J14 NC N13 P41/CS1

A11 PD6/TX1 D11 NC J15 PA5/TB1OUT N14 P91/KEY9

A12 X1 D12 NC K1 P01/AD1 N15 NC

A13 X2 D13 PF1/RXD5/KEYD K2 DVCC3 P1 NC

A14 CVCC D14 PF3/SCK K3 NC P2 P10/AD8/A8

A15 NC D15 PF6/INT0 K4 NC P3 P12/AD10/A10

B1 NC E1 DAVCC K12 PA2/TB0OUT P4 P20/A0/A16

B2 NC E2 DAOUT0 K13 PA3/TB1IN0/INT5 P5 P22/A2/A18

B3 PE6/INT1 E3 DAREFH K14 PA4/TB1IN1/INT6 P6 P26/A6/A22

B4 PE4/RXD4 E4 P53/AN3 K15 PA1/TB0IN1/INT4 P7 TDO (JTAG)

B5 TRST (JTAG) E5 NC (Bonding not applied) L1 P04/AD4 P8 ALE

B6 PD5/SCLK1/CTS1/TABOUT E12 PC6/TB8IN0/KEYC L2 P02/AD2 P9 BW1

B7 PD0/TXD0/TB9IN0 E13 DVCC52 L3 TMS (JTAG) P10 P33/WAIT

B8 DVCC3 E14 PF0/TXD5 L4 P00/AD0 P11 TDI (JTAG)

B9 PB4/TB3IN1/INTE E15 PF2/SCLK5/CTS5 L12 P97/TB7OUT P12 P40/CS0

B10 PB0/TB2IN0/INTB F1 DAOUT1 L13 DVCC3 P13 P42/CS2

B11 NC F2 P55/AN5 L14 PA0/TB0IN0/INT3 P14 P44/SCOUT

B12 RESET F3 P54/AN4 L15 P96/TB7IN1 P15 NC

B13 CVSS F4 DAOUT2 M1 P07/AD7 R1 P11/AD9/A9

B14 DVCC51 F12 PC2/TA8IN/INTA M2 P05/AD5 R2 NC

B15 NC F13 PC4/TAAIN M3 P03/AD3 R3 NC

C1 VREFH F14 PC5/TA7OUT M4 P14/AD12/A12 R4 P13/AD11/A11

C2 NC F15 PC7/TB8IN1/TA9OUT M5 P15/AD13/A13 R5 P17/AD15/A15

C3 PE5/SCLK4/CTS4 G1 P56/AN6 M6 P24/A4/A20 R6 P23/A3/A19

C4 PE2/SCLK3/CTS3 G2 P61/AN9/KEY1 M7 PLLOFF R7 P27/A7/A23

C5 PE1/RXD3 G3 NC M8 NC R8 NC

C6 PD4/RXD1/TBAIN1 G4 P60/AN8/KEY0 M9 DVCC3 R9 P31/WR

C7 PD1/RXD0/TB9IN1 G12 PC0/TA4IN/INT8 M10 P34/BUSRQ R10 P35/BUSAK

C8 PB6/TA3OUT G13 PC1/TA6IN/INT9 M11 P36/R/W R11 DVCC3

C9 PB3/TB3IN0/INTD G14 NC M12 P93/TB5OUT R12 NC

C10 BW0 G15 PC3/TA5OUT M13 P94/TB6OUT R13 P43/CS3

C11 NC H1 DVSS M14 P95/TB7IN0 R14 NC

C12 TEST1 H2 P63/AN11/KEY3 M15 P92/TB4OUT R15 P90/KEY8

C13 PF4/SO/SDA H3 P57/AN7/ADTRG N1 NC

C14 PF5/SI/SCL H4 P62/AN10/KEY2 N2 DVSS

C15 NC H12 RSTPUP N3 P06/AD6

Pin Name

Pin

No.

Pin Name

Pin

No.

Pin Name

Pin

No.

Pin Name

TMP1942CY/CZ-8

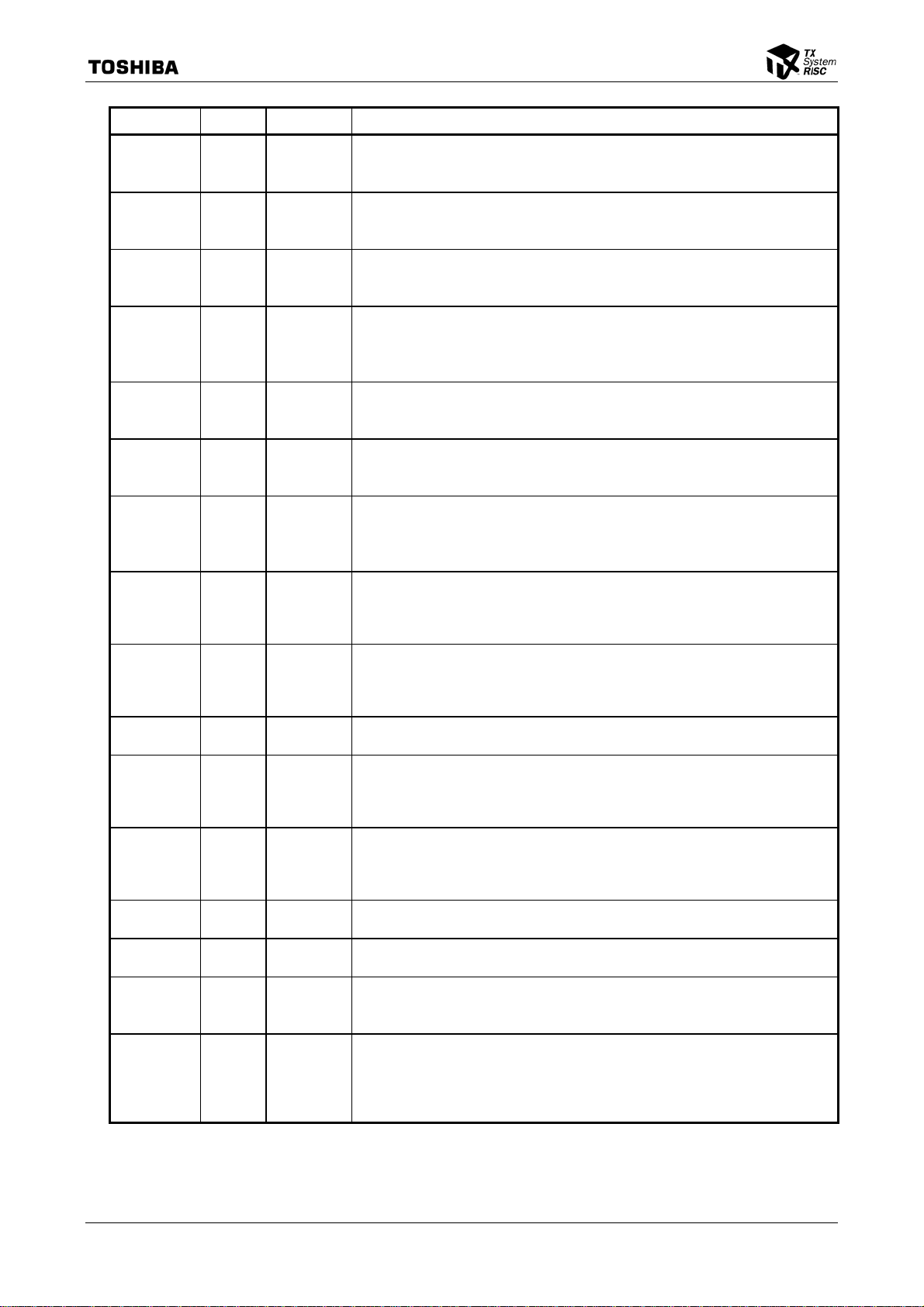

2.2 Pin Usage Information

Table 2.2.1 lists the names and functions of the TMP1942’s input/output pins.

Table 2.2.1 Pin Names and Functions

Pin Name # of Pins Type Function

P00~P07

AD0~AD7

P10~P17

AD8~AD15

A8~A15

P20~P27

A0~A7

A16~A23

P30

RD

P31

WR

P32

HWR

P33

WAIT

P34

BUSRQ

P35

BUSAK

P36

R/W

P37

DSU

P40

CS0

P41

CS1

P42

CS2

P43

CS3

P44

SCOUT

P50~P57

AN0~AN7

ADTRG

P60~P67

AN8~AN15

KEY0-KEY7

P90

DSU (DCLK)

KEY8

8 Input/output

Input/output

8 Input/output

Input/output

Output

8 Input/output

Output

Output

1 Output

Output

1 Output

Output

1 Input/output

Output

1 Input/output

Input

1 Input/output

Input

1 Input/output

Output

1 Input/output

Output

1 Input/output

Input

1 Input/output

Output

1 Input/output

Output

1 Input/output

Output

1 Input/output

Output

1 Input/output

Output

8 Input

Input

Input

1 Input/output

Input

Output

1 Input/output

Output

Input

Port 0: Individually programmable as input or output

Address (Lower): Bits 0-7 of the address/data bus

Port 1: Individually programmable as input or output

Address/Data (Upper): Bits 8-15 of the address/data bus

Address: Bits 8-15 of the address bus

Port 2: Individually programmable as input or output

Address: Bits 0-7 of the address bus

Address: Bits 16-23 of the address bus

Port 30: Output-only

Read Strobe: Asserted during a read operation from an external memory device

Port 31: Output-only

Write Strobe: Asserted during a write operation on D0-D7

Port 32: Programmable as input or output (with internal pull-up resister)

Higher Write Strobe: Asserted during a write operation on D8-D15

Port 33: Programmable as input or output (with internal pull-up resister)

Wait: Causes the CPU to suspend external bus activity

Port 34: Programmable as input or output (with internal pull-up resister)

Bus Request: Asserted by an external bus master to request bus mastership

Port 35: Programmable as input or output (with internal pull-up resister)

Bus Acknowledge: Indicates that the CPU has relinquished the bus in response to

Port 36: Programmable as input or output (with internal pull-up resister)

Read/Write: Indicates the direction of data transfer on the bus: 1 = read or dummy

Port 37: Programmable as input or output (with internal pull-up resister)

This pin is used to select the operating mode during reset. The TMP1940CYAF enters

NORMAL mode when this pin is sampled high at the rising edge of

should not be pulled down to a logic 0 during a reset sequence. The TMP1940FDBF,

which has an on-chip flash, uses this pin as an interface to the DSU tool. For details,

refer to Part 4, TMP1940FDBF.

Port 40: Programmable as input or output (with internal pull-up resister)

Chip Select 0: Asserted low to enable external devices at programmed addresses

Port 41: Programmable as input or output (with internal pull-up resister)

Chip Select 1: Asserted low to enable external devices at programmed addresses

Port 42: Programmable as input or output (with internal pull-up resister)

Chip Select 2: Asserted low to enable external devices at programmed addresses

Port 43: Programmable as input or output (with internal pull-up resister)

Chip Select 3: Asserted low to enable external devices at programmed addresses

Port 44: Programmable as input or output

System Clock Output: Drives out a clock signal at the same frequency as the CPU

Port 5: Input-only

Analog input: Input to the A/D converter

External start request for the A/D converter (multiplexed with P57)

Port 6: Input-only

Analog input: Input to the A/D converter

Key on wake-up input (with internal pull-up resister) (dynamic pull-up selectable)

Port 90: Programmable as input or output

DSU pin

Key on wake-up input (with internal pull-up resister) (dynamic pull-up selectable)

BUSRQ

cycle, 0 = write cycle

.

clock (high-speed or low-speed)

TX1942CY/CZ

RESET

. This pin

TMP1942CY/CZ-9

Pin Name # of Pins Type Function

P91

DSU (PCST2)

KEY9

P92

DSU (PCST1)

TB40UT

P93

DSU (PCST0)

TB5OUT

P94

DSU

(SDSA0/TPC)

TB6OUT

P95

DSU (DBGE*)

TB7IN0

P96

DSU (DINT*)

TB7IN1

P97

DSU

(DRESET)

TB7OUT

PA0

TB0IN0

INT3

PA1

TB0IN1

INT4

PA2

TB0OUT

PA3

TB1IN0

INT5

PA4

TB1IN1

INT6

PA5

TB1OUT

PA6

TA1OUT

PA7

TA0IN

KEYA

PB0

TB2IN0

INTB

1 Input/output

Output

Input

1 Input/output

Output

Output

1 Input/output

Output

Output

1 Input/output

Output

Output

1 Input/output

Input

1 Input/output

Input

1 Input/output

Input

Output

1 Input/output

Input

Input

1 Input/output

Input

Input

1 Input/output

Output

1 Input/output

Input

Input

1 Input/output

Input

Input

1 Input/output

Output

1 Input/output

Output

1 Input/output

Input

Input

1 Input/output

Input

Input

Port 91: Programmable as input or output

DSU pin

Key on wake-up input (with internal pull-up resister) (dynamic pull-up selectable)

Port 92: Programmable as input or output

DSU pin

16-Bit Timer 4 Output: Output from 16-bit Timer 4

Port 93: Programmable as input or output

DSU pin

16-Bit Timer 5 Output: Output from 16-bit Timer 5

Port 94: Programmable as input or output

DSU pin

16-Bit Timer 6 Output: Output from 16-bit Timer 6

Port 95: Programmable as input or output

DSU pin

16-Bit Timer 7 Input 0: Count/capture trigger input to 16-bit Timer 7

Port 96: Programmable as input or output

DSU pin

16-Bit Timer 7 Input 1: Capture trigger input to 16-bit Timer 7

Port 97: Programmable as input or output

DSU pin

16-Bit Timer 7 Output: Output from 16-bit Timer 7

Port A0: Programmable as input or output

16-Bit Timer 0 Input 0: Count/capture trigger input to 16-bit Timer 0

Interrupt Request 3: Programmable to be high-level, low-level, rising-edge or

Port A1: Programmable as input or output

16-Bit Timer 0 Input 1: Capture trigger input to 16-bit Timer 0

Interrupt Request 4: Programmable to be high-level, low-level, rising-edge or

Port A2: Programmable as input or output

16-Bit Timer 0 Output: Output from 16-bit Timer 0

Port A3: Programmable as input or output

16-Bit Timer 1 Input 0: Count/capture trigger input to 16-bit Timer 1

Interrupt Request 5: Programmable to be high-level, low-level, rising-edge or

Port A4: Programmable as input or output

16-Bit Timer 1 Input 1: Capture trigger input to 16-bit Timer 1

Interrupt Request 6: Programmable to be high-level, low-level, rising-edge or

Port A5: Programmable as input or output

16-Bit Timer 1 Output: Output from 16-bit Timer 1

Port A6: Programmable as input or output

8-Bit Timer 0/1 Output: Output from 8-bit Timer 0 or 1

Port A7: Programmable as input or output

8-Bit Timer 0 Input: Input to 8-bit Timer 0

Key on wake-up input (with internal pull-up resister) (dynamic pull-up selectable)

Port B0: Programmable as input or output

16-Bit Timer 2 Input 0: Count/capture trigger input/2-phase input pulse counter input to

Interrupt Request B: Programmable to be high-level, low-level, rising-edge or

falling-edge sensitive

falling-edge sensitive

falling-edge sensitive

falling-edge sensitive

16-bit Timer 2

falling-edge sensitive

TX1942CY/CZ

TMP1942CY/CZ-10

Pin Name # of Pins Type Function

PB1

TB2IN1

INTC

PB2

TB2OUT

TB4IN0

PB3

TB3IN0

INTD

PB4

TB3IN1

INTE

PB5

TB3OUT

TB4IN1

PB6

TA3OUT

PB7

TA2IN

INT7

KEYB

PC0

TA4IN

INT8

PC1

TA6IN

INT9

PC2

TA8IN

INTA

PC3

TA5OUT

PC4

TAAIN

PC5

TA7OUT

PC6

TB8IN0

KEYC

PC7

TB8IN1

TA9OUT

PD0

TXD0

TB9IN0

1 Input/output

Input

Input

1 Input/output

Output

Input

1 Input/output

Input

Input

1 Input/output

Input

Input

1 Input/output

Output

Input

1 Input/output

Output

1 Input/output

Input

Input

Input

1 Input/output

Input

Input

1 Input/output

Input

Input

1 Input/output

Input

Input

1 Input/output

Output

1 Input/output

Input

1 Input/output

Output

1 Input/output

Input

Input

1 Input/output

Input

Output

1 Input/output

Output

Input

Port B1: Programmable as input or output

16-Bit Timer 2 Input 1: Capture trigger input/2-phase input pulse counter input to 16-bit

Interrupt Request C: Programmable to be high-level, low-level, rising-edge or

Port B2: Programmable as input or output

16-Bit Timer 2 Output: Output from 16-bit Timer 2

16-Bit Timer 4 Input 0: Count/capture trigger input to 16-bit Timer 4

Port B3: Programmable as input or output

16-Bit Timer 3 Input 0: Count/capture trigger input/2-phase input pulse counter input to

Interrupt Request D: Programmable to be high-level, low-level, rising-edge or

Port B4: Programmable as input or output

16-Bit Timer 3 Input 1: Capture trigger input/2-phase input pulse counter input to 16-bit

Interrupt Request E: Programmable to be high-level, low-level, rising-edge or

Port B5: Programmable as input or output

16-Bit Timer 3 Output: Output from 16-bit Timer 3

16-Bit Timer 4 Input 1: Capture trigger input to 16-bit Timer 4

Port B6: Programmable as input or output

8-Bit Timer 2/3 Output: Output from 8-bit Timer 2 or 3

Port B7: Programmable as input or output

8-Bit Timer 2 Input: Input to 8-bit Timer 2

Interrupt Request 7: Programmable to be high-level, low-level, rising-edge or

Key on wake-up input (with internal pull-up resister) (dynamic pull-up selectable)

Port C0: Programmable as input or output

8-Bit Timer 4 Input: Input to 8-bit Timer 4

Interrupt Request 8: Programmable to be high-level, low-level, rising-edge or

Port C1: Programmable as input or output

8-Bit Timer 6 Input: Input to 8-bit Timer 6

Interrupt Request 9: Programmable to be high-level, low-level, rising-edge or

Port C2: Programmable as input or output

8-Bit Timer 8 Input: Input to 8-bit Timer 8

Interrupt Request A: Programmable to be high-level, low-level, rising-edge or

Port C3: Programmable as input or output

8-Bit Timer 4/5 Output: Output from 8-bit Timer 4 or 5

Port C4: Programmable as input or output

8-Bit Timer A Input: Input to 8-bit Timer A

Port C5: Programmable as input or output

8-Bit Timer 6/7 Output: Output from 8-bit Timer 6 or 7

Port C6: Programmable as input or output

16-Bit Timer 8 Input 0: Count/capture trigger input to 16-bit Timer 8

Key on wake-up input (with internal pull-up resister) (dynamic pull-up selectable)

Port C7: Programmable as input or output

16-Bit Timer 8 Input 1: Capture trigger input to 16-bit Timer 8

8-Bit Timer 8/9 Output: Output from 8-bit Timer 8 or 9

Port D0: Programmable as input or output

Serial Transmit Data 0

Programmable as an open-drain output

16-Bit Timer 9 Input 0: Count/capture trigger input to 16-bit Timer 9

Timer 2

falling-edge sensitive

16-bit Timer 3

falling-edge sensitive

Timer 3

falling-edge sensitive

falling-edge sensitive

falling-edge sensitive

falling-edge sensitive

falling-edge sensitive

TX1942CY/CZ

TMP1942CY/CZ-11

Pin Name # of Pins Type Function

PD1

RXD0

TB9IN1

PD2

SCLK0

CTS0*

PD3

TXD1

TBAIN0

PD4

RXD1

TBAIN1

PD5

SCLK1

CTS1

TABOUT

PD6

XT1

PD7

XT2

PE0

TXD3

PE1

RXD3

PE2

CTS3*

PE3

TXD4

PE4

RXD4

PE5

SCLK4

CTS4

PE6

INT1

BOOT

PE7

INT2

INTLV

PF0

TXD5

1 Input/output

Input

Input

1 Input/output

Input/output

Input

1 Input/output

Output

Input

1 Input/output

Input

Input

1 Input/output

Input/output

Input

Output

1 Input/output

Input

1 Input/output

Output

1 Input/output

Output

1 Input/output

Input

1 Input/output

Input/output

Input

1 Input/output

Output

1 Input/output

Input

1 Input/output

Input/output

Input

1 Input/output

Input

1 Input/output

Input

1 Input/output

Output

Port D1: Programmable as input or output

Serial Receive Data 0

16-Bit Timer 9 Input 1: Capture trigger input to 16-bit Timer 9

Port D2: Programmable as input or output

Serial Clock Input/Output 0

Serial Clear-to-Send 0

Programmable as an open-drain output

Port D3: Programmable as input or output

Serial Transmit Data 1

Programmable as an open-drain output

16-Bit Timer A Input 0: Count/capture trigger input to 16-bit Timer A

Port D4: Programmable as input or output

Serial Receive Data 1

16-Bit Timer A Input 1: Capture trigger input to 16-bit Timer A

Port D5: Programmable as input or output

Serial Clock Input/Output 1

Serial Clear-to-Send 1

Programmable as an open-drain output

8-Bit Timer A/B Output: Output from 8-bit Timer A or B

Port D6: Programmable as input or open-drain output

Connection pin for a low-speed crystal

Port D7: Programmable as input or open-drain output

Connection pin for a low-speed crystal

Port E0: Programmable as input or output

Serial Transmit Data 3

Programmable as an open-drain output

Port E1: Programmable as input or output

Serial Receive Data 3

Port E2: Programmable as input or output

Serial Clock Input/Output 3

Serial Clear-to-Send 3

Programmable as an open-drain output

Port E3: Programmable as input or output

Serial Transmit Data 4

Programmable as an open-drain output

Port E4: Programmable as input or output

Serial Receive Data 4

Port E5: Programmable as input or output

Serial Clock Input/Output 4

Serial Clear-to-Send 4

Programmable as an open-drain output

Port E6: Programmable as input or output

Interrupt request 1: Individually programmable to be high-level, low-level,

Single-boot mode setting pin: Used when rewriting built-in flash memory (low active).

Port E7: Programmable as input or output

Interrupt request 2: Individually programmable to be high-level, low-level,

Interleave mode setting pin: This pin should be pulled up when using interleave mode.

Port F0: Programmable as input or output

Serial Transmit Data 5

Programmable as an open-drain output

rising-edge or falling-edge sensitive.

During normal operation, this pin should be pulled up.

This pin should always be pulled up for the mask ROM

version.

rising-edge or falling-edge sensitive.

Otherwise, it should be pulled down.

TX1942CY/CZ

TMP1942CY/CZ-12

TX1942CY/CZ

Pin Name # of Pins Type Function

PF1

RXD5

KEYD

PF2

SCLK5

CTS5

PF3

SCK

PF4

SO

SDA

PF5

SI

SCL

PF6

INT0

ALE 1 Output Address Latch Enable

TEST0 1 Input Test pin

TEST1 1 Input Test pin

RSTPUP 1 Input When this pin is driven high (upon reset), pull-up for ports 3 and 4 is enabled. When this

DAOUT0-2 3 Output D/A converter output

NMI 1 Input Non-maskable Interrupt Request: Causes an NMI interrupt on the falling edge

BW0~1 2 Input Set both AM0 and AM1 to 1.

PLLOFF 1 Input This pin should be tied to logic 1 when the frequency multiplied clock from the PLL is

RESET 1 Input Reset (with internal pull-up resister): Initializes the whole TMP1940CYAF

VREFH 1 Input Input pin for high reference voltage for the A/D converter.

VREFL 1 Input Input pin for low reference voltage for the A/D converter.

AVCC 1 ⎯ Power supply pin for the A/D converter. This pin should always be connected to power

AVSS 1 ⎯ Ground pin for the A/D converter. This pin should always be connected to ground even

DAVCC 1 ⎯ Power supply pin for the D/A converter. This pin should always be connected to power

DAVSS 1 ⎯ Ground pin for the D/A converter. This pin should always be connected to ground even

DAREFH 1 ⎯ Reference voltage input pin for the D/A converter

X1/X2 2 Input/output Resonator connecting pin

CVCC 1 ⎯ Power supply pin for the oscillator

CVSS 1 ⎯ Ground pin for the oscillator (0 V)

DVCC3 4 ⎯ Power supply pins

DVCC51 1 ⎯ Power supply pin (port F)

DVCC52 1 ⎯ Power supply pin (port C)

DVSS 5 ⎯ Ground pins (0 V)

Port C becomes a 5 V port when a 5 V power supply is connected to DVCC52.

Port F becomes a 5 V port when a 5 V power supply is connected to DVCC51.

1 Input/output

Input

Input

1 Input/output

Input/output

Input

1 Input/output

Input/output

1 Input/output

Output

Input/output

1 Input/output

Input

Input/output

Input/output

Input

Port F1: Programmable as input or output

Serial Receive Data 5

Key on wake-up input (with internal pull-up resister) (dynamic pull-up selectable)

Port F2: Programmable as input or output

Serial Clock Input/Output 5

Serial Clear-to-Send 5

Programmable as an open-drain output

Port F3: Programmable as input or output

Clock input/output pin when the serial bus interface is in SIO mode

Port F4: Programmable as input or output

Data transmission pin when the serial bus interface is in SIO mode

Data transmission/reception pin when the serial bus interface is in I

Programmable as an open-drain output

Port F5: Programmable as input or output

Data reception pin when the serial bus interface is in SIO mode

Clock input/output pin when the serial bus interface is in I

Programmable as an open-drain output

Port F6: Programmable as input or output

Interrupt request 0: Individually programmable to be high-level, low-level, rising-edge or

(This signal is driven out only when external memory is accessed)

pin is driven low, pull-up is disabled.

used; otherwise, it should be tied to logic 0.

supply even when the A/D converter is not used.

when the A/D converter is not used.

supply even when the D/A converter is not used.

when the D/A converter is not used.

falling-edge sensitive.

2

C mode

2

C mode

Note: When the DSU is enabled, port 9 functions as the processor probe interfacing signal

regardless of the setting of the port 9 control register (P9CR).

TMP1942CY/CZ-13

The following table lists the JT AG specific pins added to the CSP package:

Pin Name # of Pins Type Function

TRST 1 Input JTAG reset pin (with internal pull-up resistor)

TCK 1 Input JTAG clock pin (with internal pull-up resistor)

TDI 1 Input JTAG data input pin (with internal pull-up resistor)

TDO 1 Output JTAG data outpu t pin

TMS 1 Input JTAG mode switching input pin (with internal pull-up resistor)

TX1942CY/CZ

TMP1942CY/CZ-14

3. Functional Description

This section describes the functions and basic operation of each indivi dual circuit bloc k i n the TMP1942 se ries

devices.

3.1 Processor Core

The TX1942 contains a high-performance 32-bit processor core (the TX19 pro cessor core). For details of

the operation of the processor core, refer to “TX19 Family Architecture”.

Functions unique to the TMP1942, which are not explained in “TX19 Family Architecture”, are described

below.

Recommended power-on sequence:

In powering up this device, it is recommended that the DVCC3 be turned on first.

At power-on, the pull-up resistors and input & output buffers pull-down resistors attached to

the I/O ports of the 5V supply domain may rail become unstable or a through current may pass

through the port until the DVCC3 has stabilized, when an injection order is not kept.

TMP1942CY/CZ

3.1.1 Reset Operation

To reset the TMP1942,

power supply voltage is within the rated operating range and the internal high-frequency oscillator is

oscillating stably. (With the device operating at 32 MHz, this period is equal to 3 μs if the PLL is being

used and 6 μs if the PLL is not being used.) After a reset the PLL-multiplied clock is specified by the

setting of the

To reset the TMP1942,

supply voltage and the internal high-frequency oscillator have stabilized. This time is typically 3 μs at 32

MHz when the on-chip PLL is utilized, and 6μs otherwise. After a reset, either the PLL-multiplied clock

or an external clock is selected, depending on the logi c state of the

clock is geared down to 1/8 for internal operation.

The following occurs as a result of a reset:

• The System control coprocessor (CP0) registers within the TX19 core processor are initialized.

• The Reset exception is taken. Program control is transferred to the exception handler at a

RESET

PLLOFF pin and the clock gear is initialized to 1/8 mode.

RESET

For details, refer to the Architecture manual.

predefined address. This predefined location is called an exception vector, which directly

indicates the start of the actual exception handler routine. The Reset exception is always

vectored to virtual address 0xBFC0_0000 (which is the same as f or t he N onmaskable Interrupt

exception).

must be input Low (at 0) for at least 12 system clock cycles while the

must be asserted for at least 12 system clock periods after the power

PLLOFF

pin. By default, the selected

• All on-chip I/O peripheral registers are initialized.

• All port pins, including those multiplexed with on-chip peripheral functions, are configured as

either general-purpose inputs or general-purpose outputs.

TMP1942CY/CZ-15

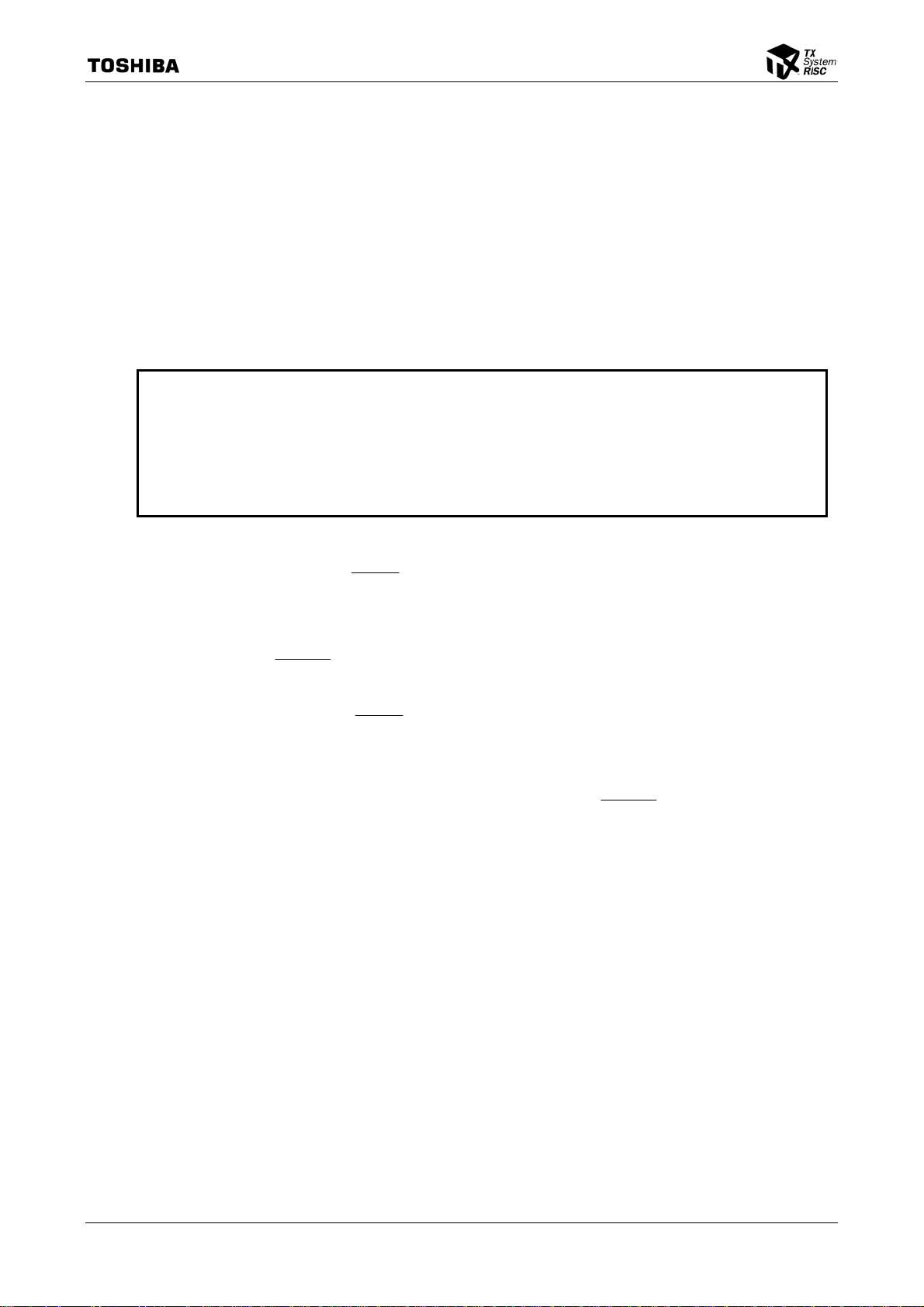

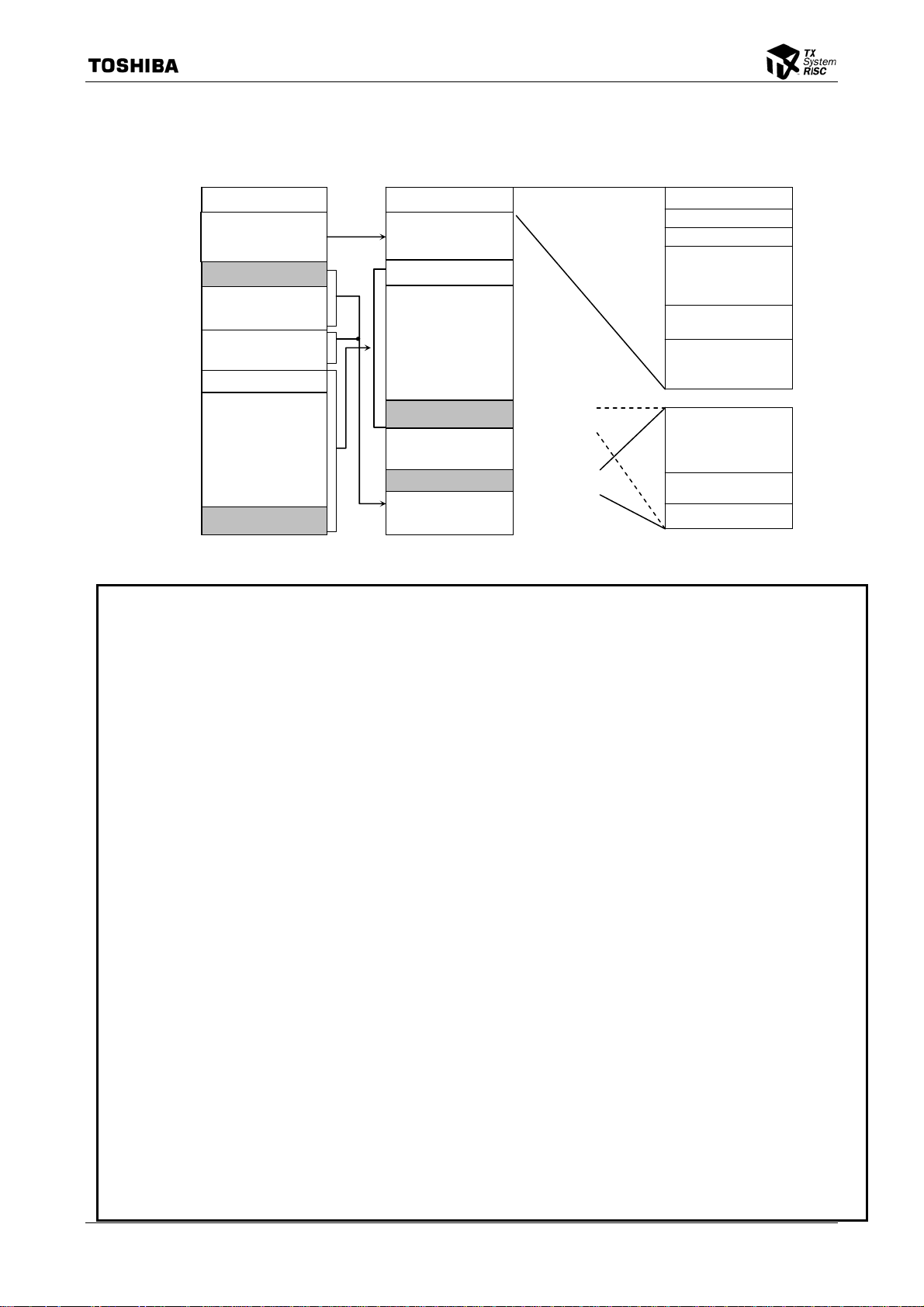

3.2 Memory Map

Figure 3.2.1 shows a memory map of the TMP1942.

0xFFFF_FFFF

0xFF00_0000

0xC000_0000

0xBFC0_0000

0xA000_0000

0x8000_0000

0x0007_FFFF

0x0000_0000

Virtual address

16 Mbytes reserved

16 Mbytes reserved

Kseg2

(cacheable)

Kseg1

(uncacheable)

Kseg0

(cacheable)

Kuseg

(cacheable)

Physical address

16 Mbytes reserved

Kseg2

(1 Gbyte)

16 Mbytes reserved

Kuseg

(2Gbyte)

Internal ROM area

reflected

Cannot be accessed

Internal ROM

512 Mbytes

0x4003_FFFF

0x4000_0000

0x1FC3_FFFF

0x1FC0_0000

TMP1942CY/CZ

Internal I/O

(Reserved)

Internal RAM (16KB)

(Reserved)

Reserved for

debugging (2 MB)

(Reserved)

User program area

Maskable interrupt

area

Exception vector area

0xFFFF_E000

0xFFFF_AFFF

0xFFFF_7000

0xFF3F_FFFF

0xFF20_0000

0xFF00_0000

0x1FC3_FFFF

0x1FC0_0400

0x1FC0_0000

Figure 3.2.1 Memory Map

Note 1: The internal ROM is mapped into the memory space from 0x1FC0_0000 to 0x1FC3_FFFF (for a 256-KB ROM) or

0x1FC0_0000 to 0x1FC5_FFFF (for a 384-KB ROM). The internal RAM is mapped into the memory space from

0xFFFF_8000 to 0xFFFF_BFFF (for a 16-KB RAM).

Note 2: The memory space from 0xFFFF_4000 to 0xFFFF_BFFF is a reserved RAM area. Any area other than those shown above,

where physical memory is located, should not be accessed.

Note 3: The internal memory data is stored in contiguous physical address locations starting at 0x1FC0_0000.

If exception vector addresses are placed in internal ROM, the system control coprocessor (CP0) Status register's BEV bit

must be set to 1 (the default). (This is because exception vector addresses are dispersed if BEV = 0.) If memory is added

externally, the BEV bit can be set to 0.

However, since a virtual address space of 0x0000_0000 ±32 KB is easier to access for reasons of code efficiency, this area

is reflected in the contiguous physical address space from 0x4000_0000 upwards (as indicated by the shaded area) which

corresponds to a virtual address space starting at 0x0000_0000 and which is equal in size to the internal memory. Hence,

accessing this area is equivalent to accessing the internal memory.

Example: Using 32-bit ISA

• Access to the 0x0000_0000 ±32 KB area

ADDIU r2, r0, 7 ; r 2 ← (0x0000_0007)

SW r2, Io (_t) (r0) ; 0x0000_xxxx ← (r2)

↑

Can be accessed using a single instruction.

• Access to areas other than 0x0000_0000 ±32 KB

LUI r3, hi (_f) ; ← Upper address is set to r3.

ADDIU r2, r0, 8 ; r2 ← (0x0000_0008)

SW r2, Io (_f) (r3) ; Memory is accessed after lower address has been set.

Note 4: The TX1942 supports access to only 16 Mbytes of physical space as external address space. A 16-Mbyte physical address

space can be placed in any chip-select area within the CPU's 3.5 Gbytes of physical address space.

However, when access to the internal memory, internal I/O space or a reserved area is performed, the external address

space cannot be accessed simultaneously, since the other t ypes of access have priority.

Note 5: Do not place an instruction in the last four words of the physical area.

• The relevant area of the internal ROM is 0x1FC3_FFF0 to 0x1FC3_FFFF (for a 256-KB ROM) or 0x1FC5_FFF0 to

0x1FC5_FFFF (for a 384-KB ROM).

• If ROM is added externally, this restriction applies to the last four words of the installed memory

(system-dependent).

TMP1942CY/CZ-16

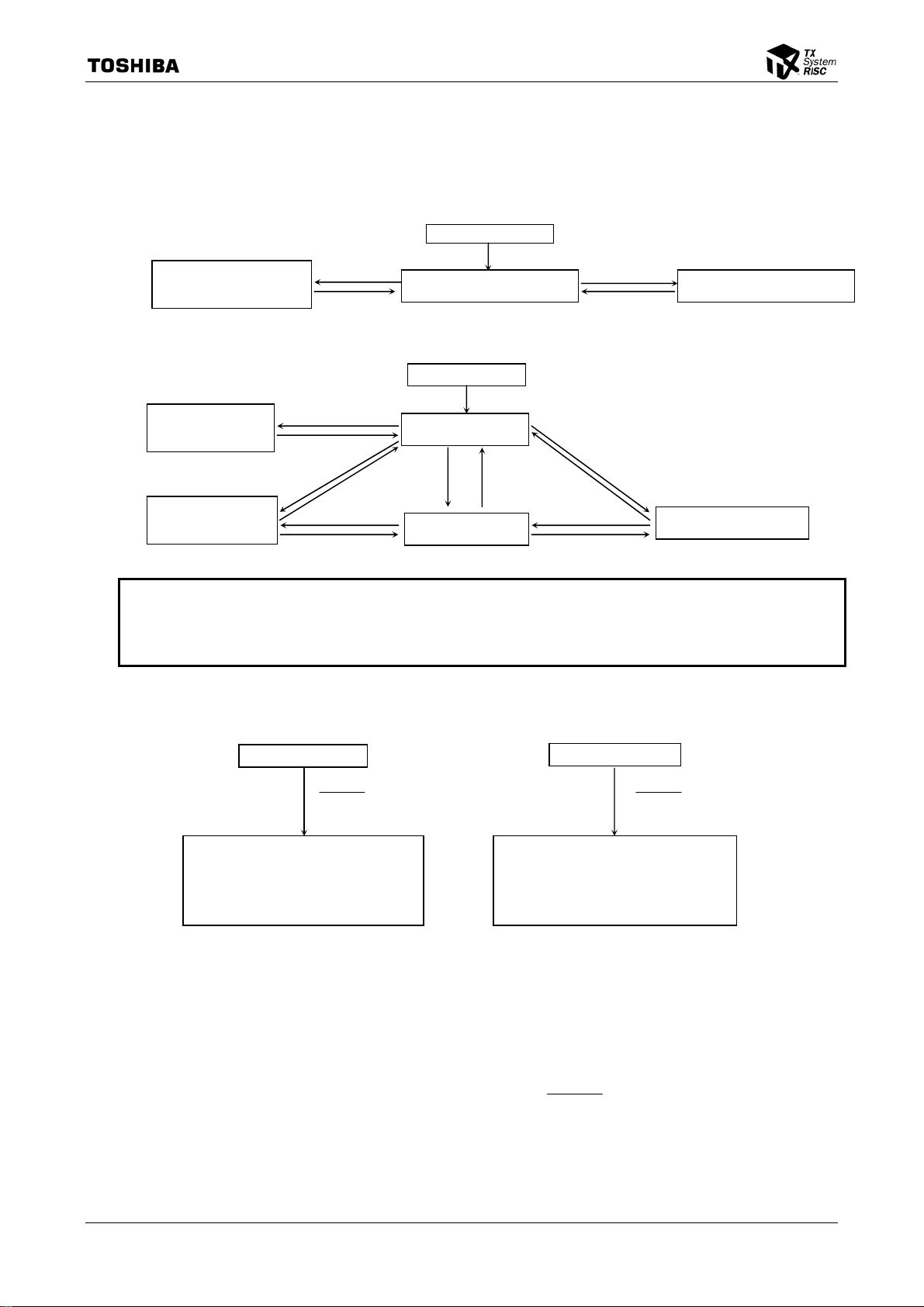

3.3 Clock/Standby Control

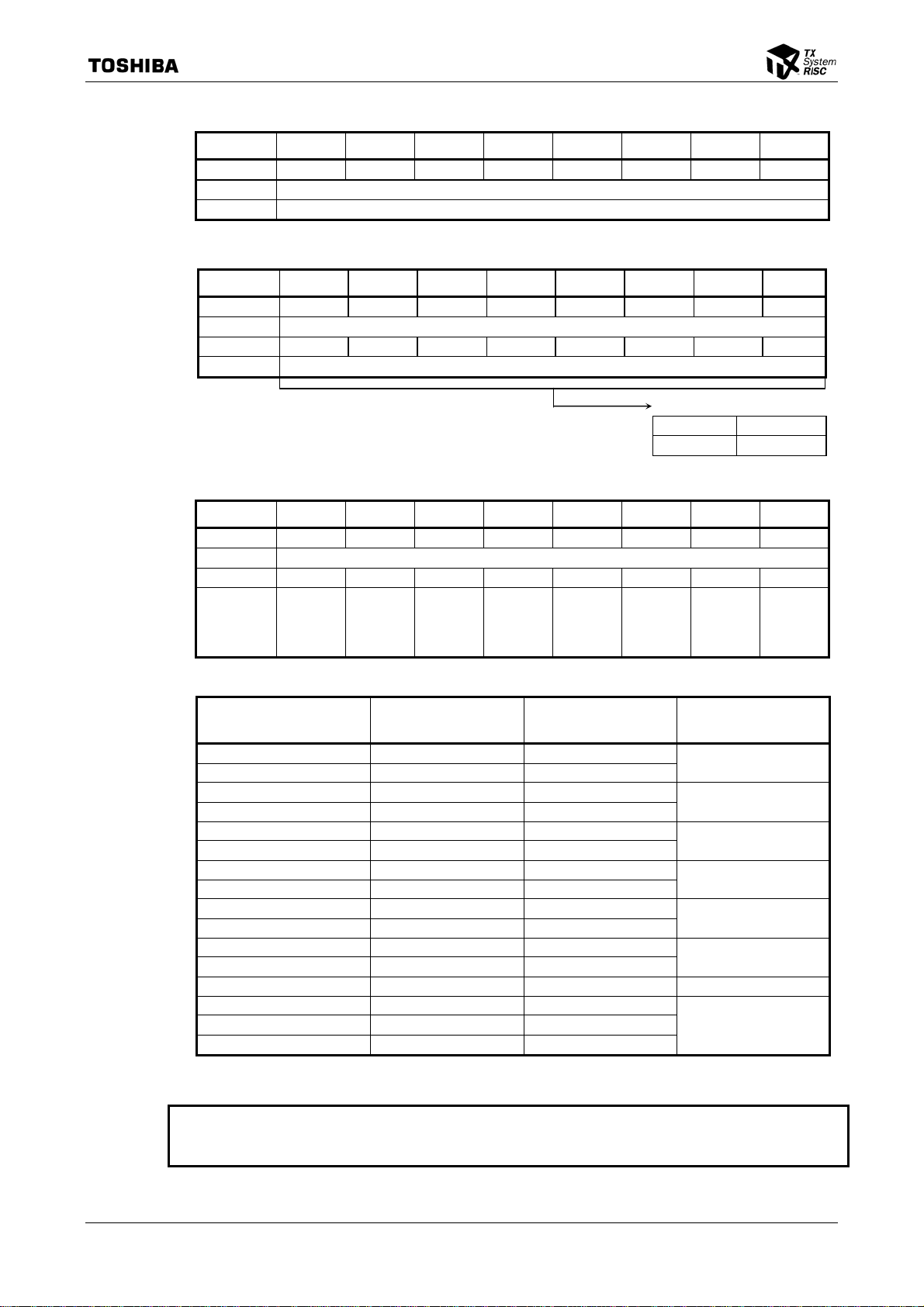

There are essentially two modes of clock operation: single-clock mode (which uses only the X1 and X2

pins) and dual-clock mode (which uses the X1 and X2 pins as well as the XT1 and XT2 pins).

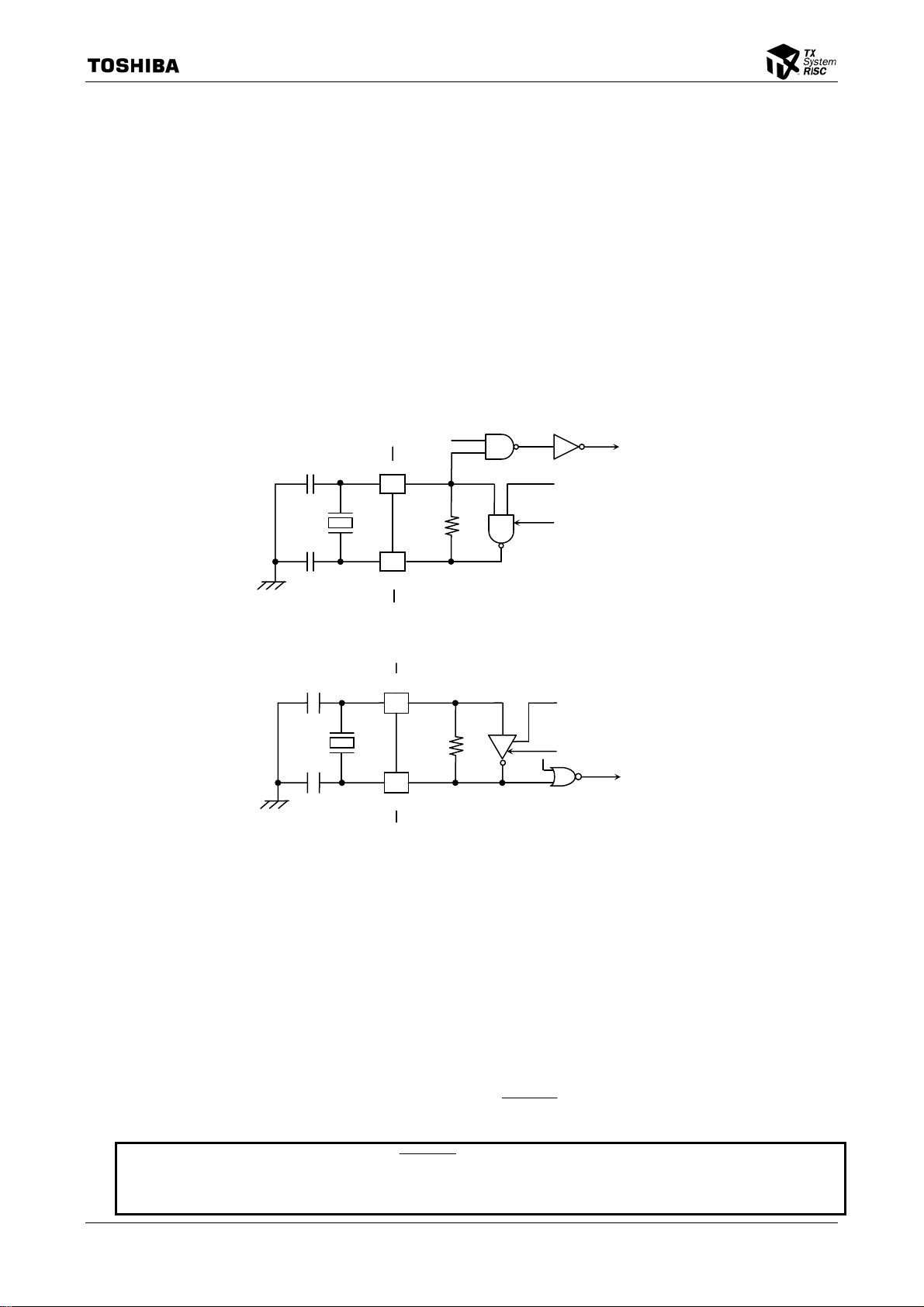

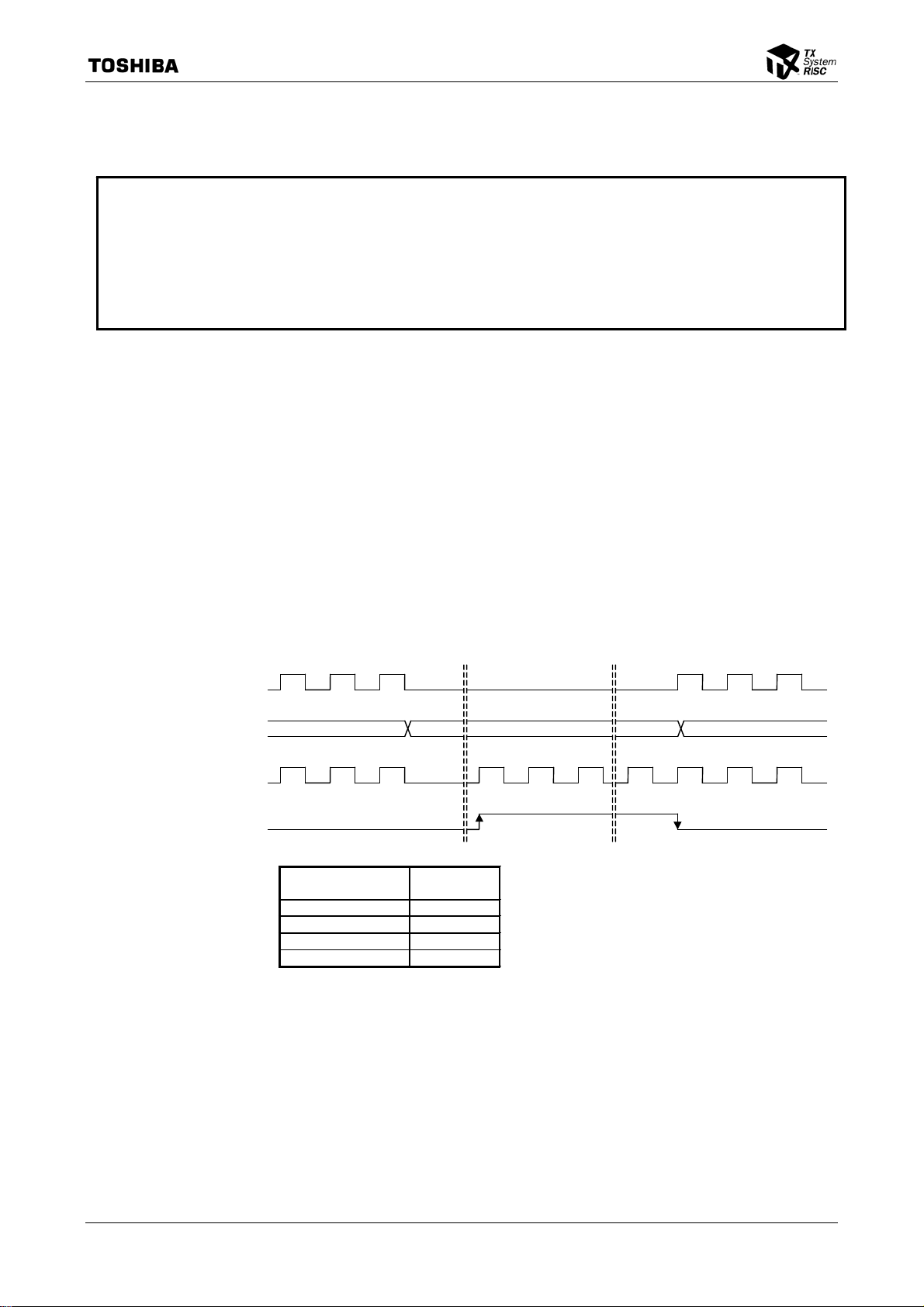

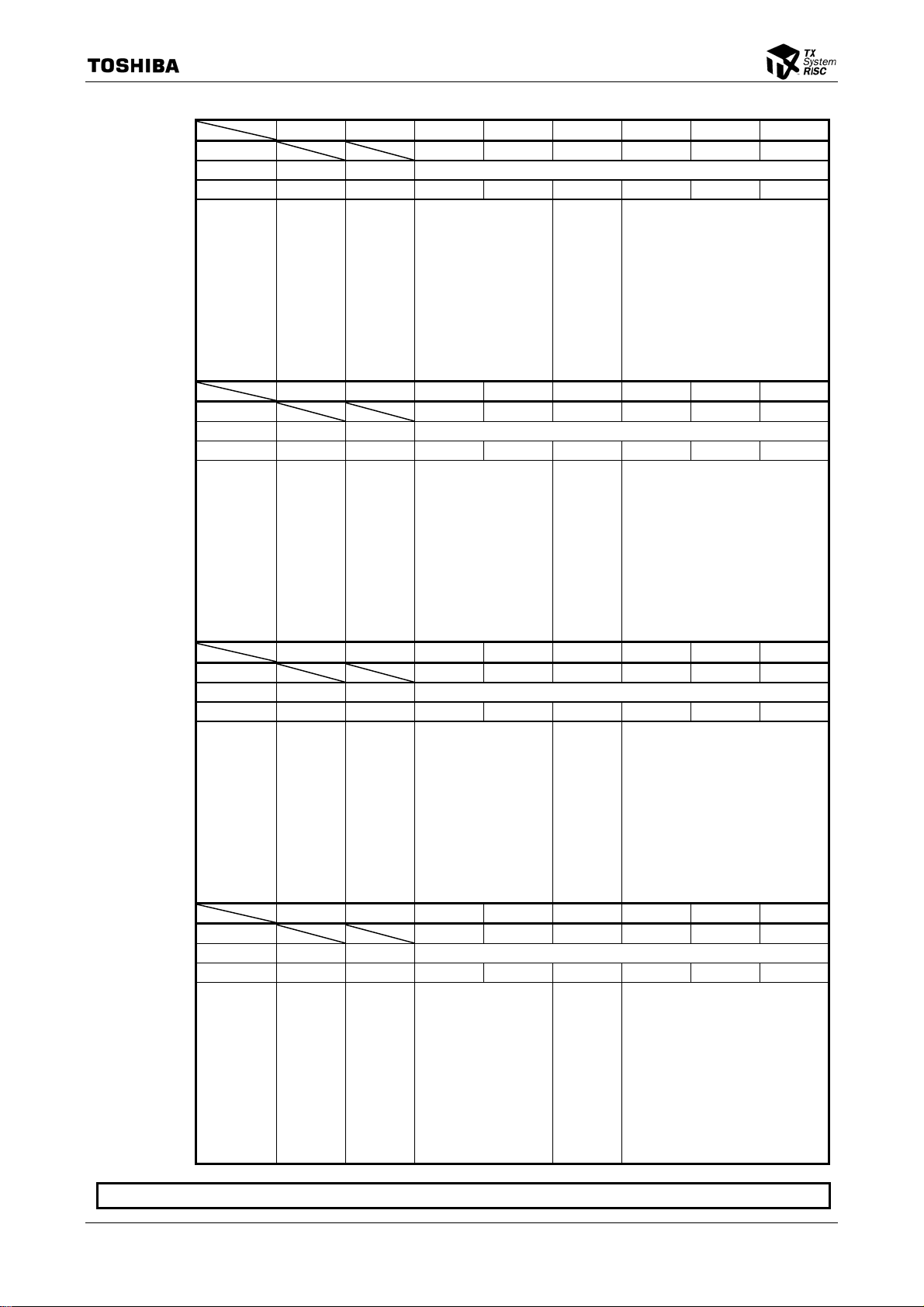

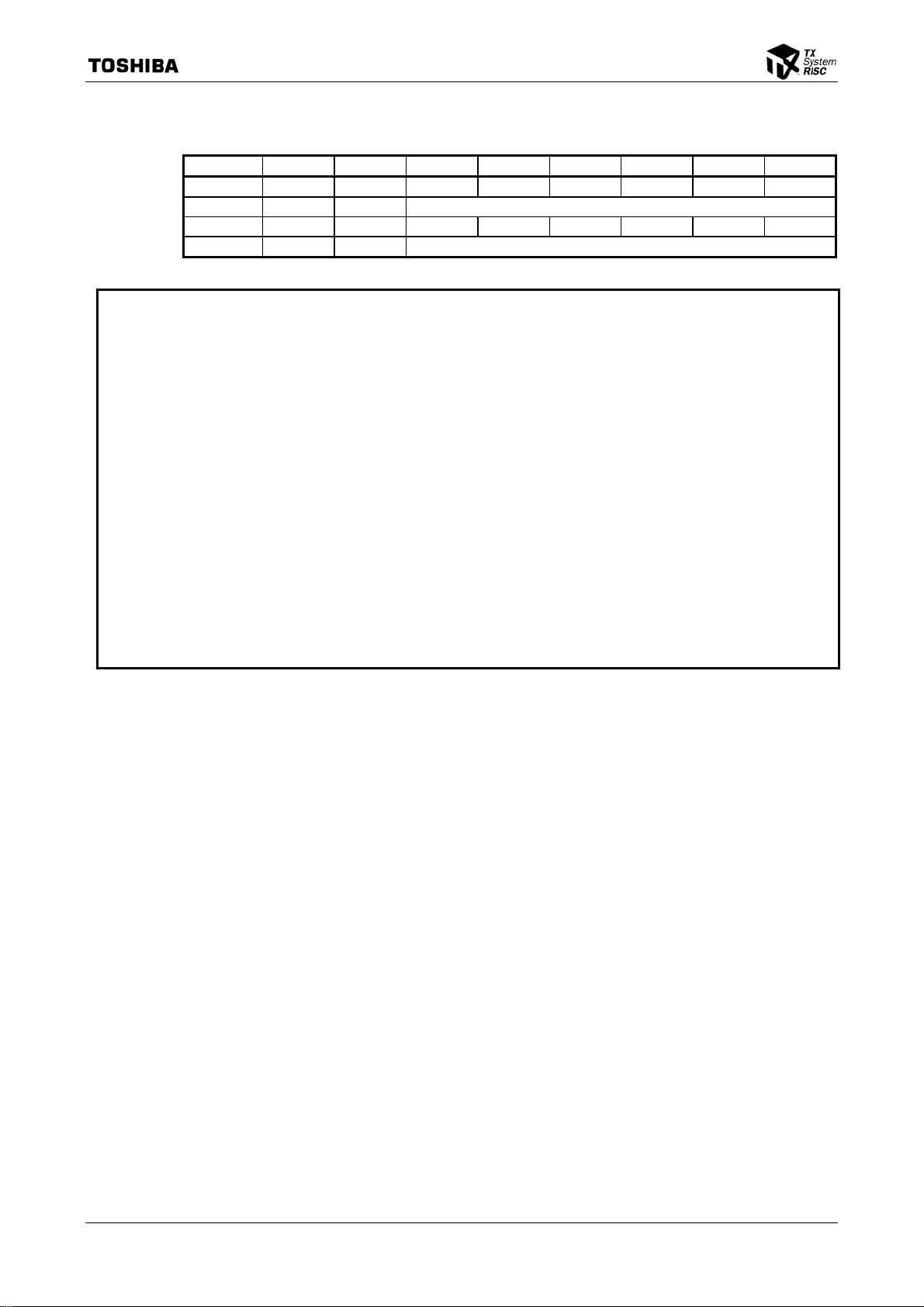

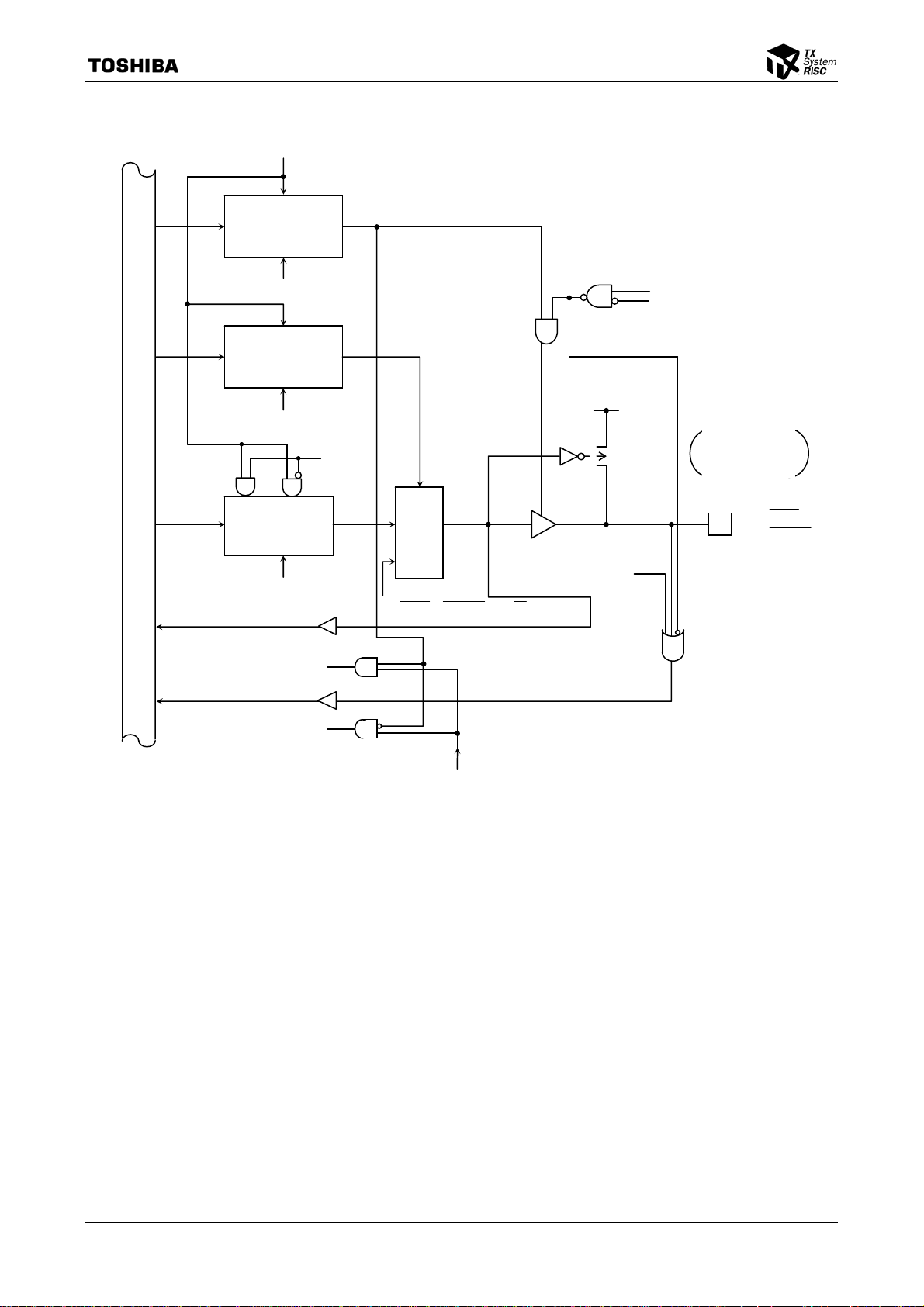

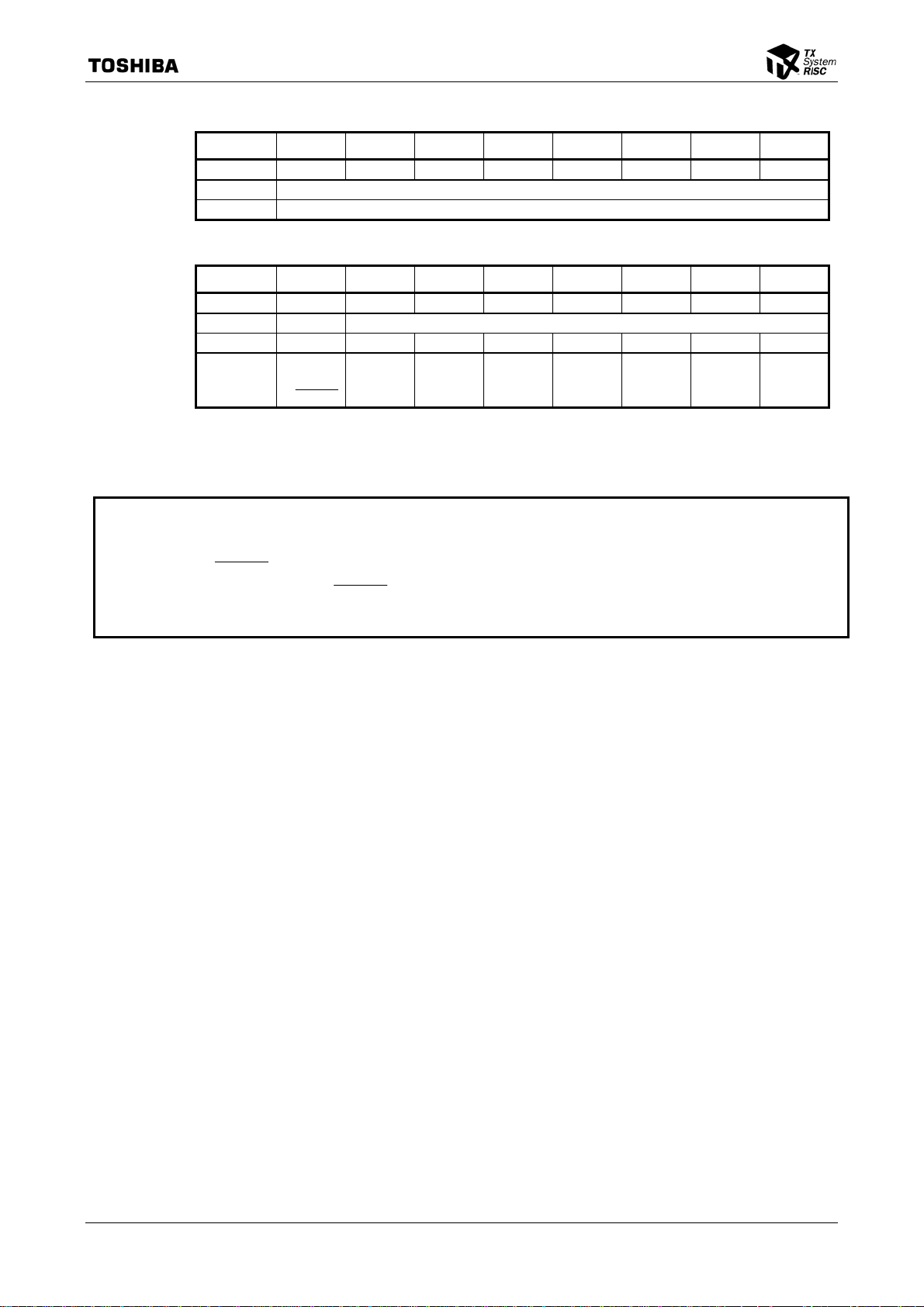

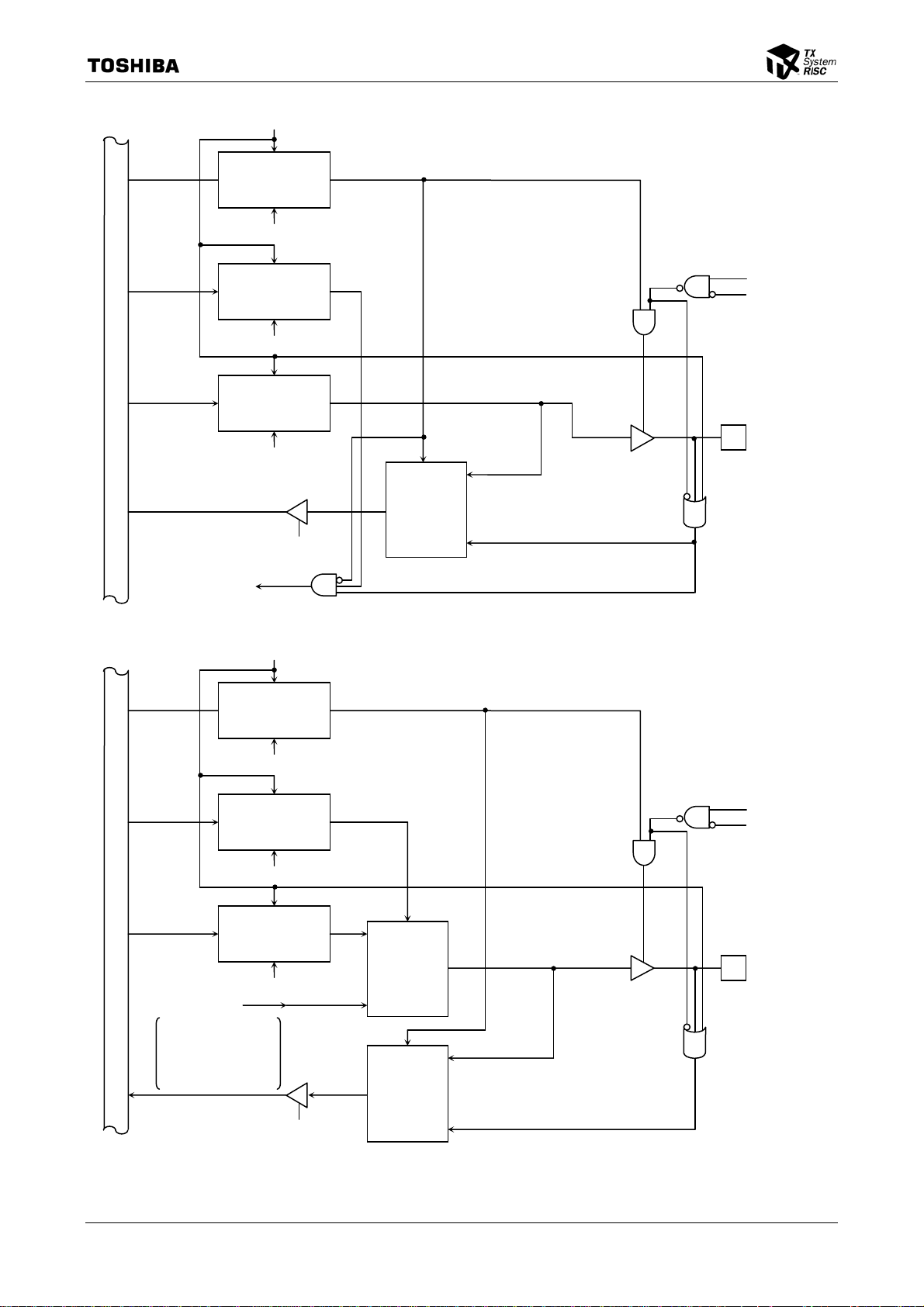

Figure 3.3.1 shows the state transition dia

(I/O select operation)

SLEEP mode (fc only)

IDLE mode

(CPU halted)

(I/O select operation)

IDLE mode

(CPU halted)

(only real-time clock

timer operating)

Instruction

Instruction

gram for each operation mode.

Reset

Reset terminated

Instruction

Interrupt

NORMAL mode

(fc/gear value)

(a) State transition in single-clock mode

Reset

Reset terminated

NORMAL mode

Interrupt

Interrupt

Instruction

Interrupt

(fc/gear value)

Instruction

SLOW mode

(fs)

Interrupt

Instruction

Interrupt

TMP1942CY/CZ

Instruction

Interrupt

Instruction

STOP mode

(all circuits turned off)

STOP mode

(all circuits turned off)

Note 1: Before transition to SLOW/SLEEP mode can occur, the low-speed oscillator (fs) must be oscillating stably.

Note 2: When SLEEP mode is terminated, the device returns to the state in which it was placed before entering SLEEP mode.

Note 3: The state to which the device returns when STOP mode is terminated can be specified using system control register

SYSCR0.

(b) State transition in dual-clock mode

Figure 3.3.1 State Transition Diagrams for Different Modes

Reset

Reset terminated

PLLOFF pin (High)

PLL clock used

NORMAL mode

fc = fpll = fosc × 4

fsys = fc/8

∴fsys = fosc/2

fperiph = fsys

Reset

Reset terminated

PLLOFF pin (Low)

PLL not used

NORMAL mode

fc = fosc/2

fsys = fc/8

∴fsys = fosc/16

fperiph = fsys

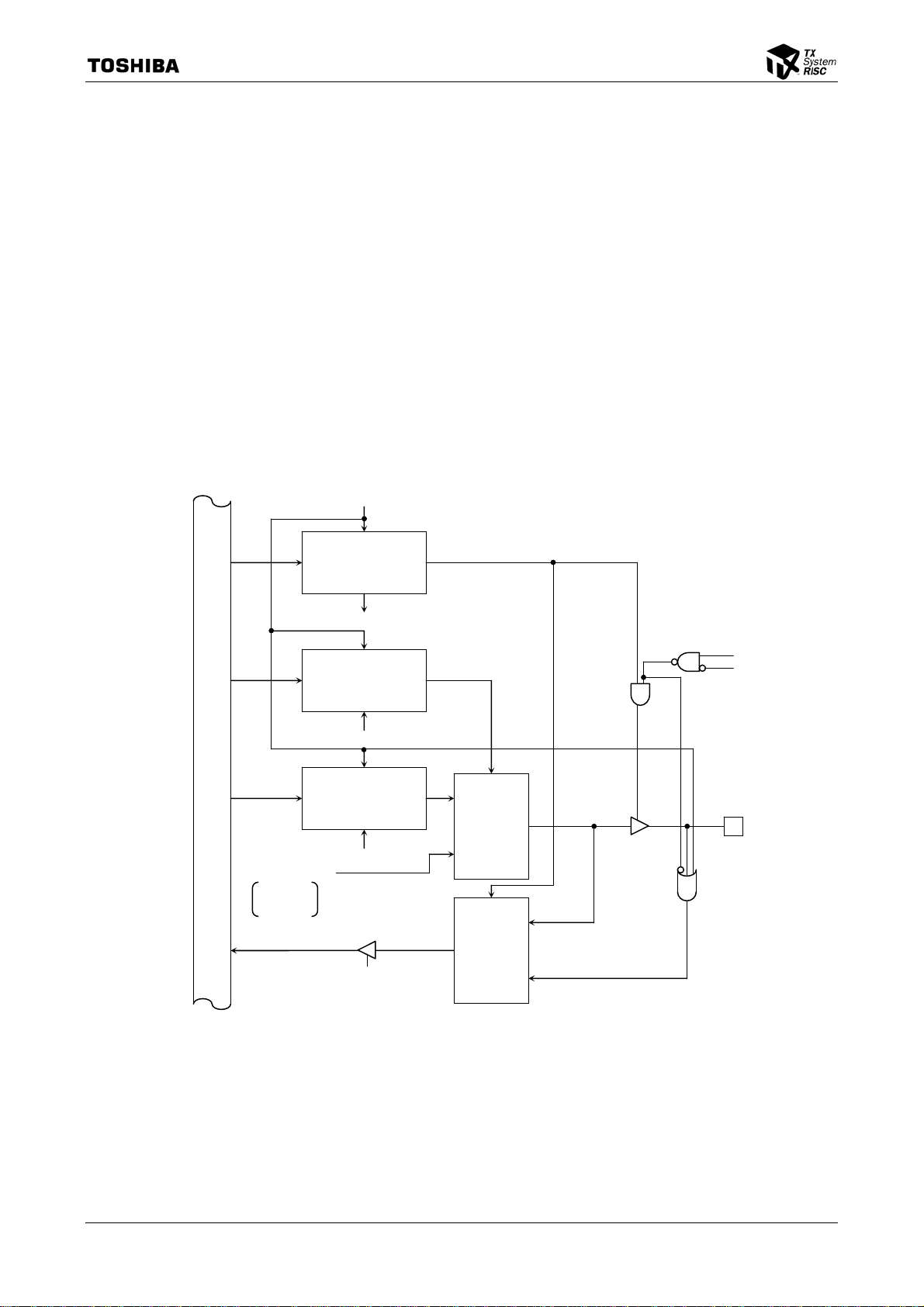

A. When a clock generated by the PLL is used

B. When the PLL is not used

Figure 3.3.32 Default States When the PLL is Used and Those When the PLL is Not Used

fosc: Clock frequency input via X1 and X2 pins

fs: Clock frequency input via XT1 and XT2 pins

fpll: Clock frequency multiplied (x4) by PLL

fc: Clock frequency selected by setting of

PLLOFF pin

fgear: Clock frequency selected by SYSCR1<GEAR1:GEAR0>

System clock fsys: Clock frequency selected by SYSCR1<SYSCK>

fperiph: Input clock for peripheral I/O prescaler

TMP1942CY/CZ-17

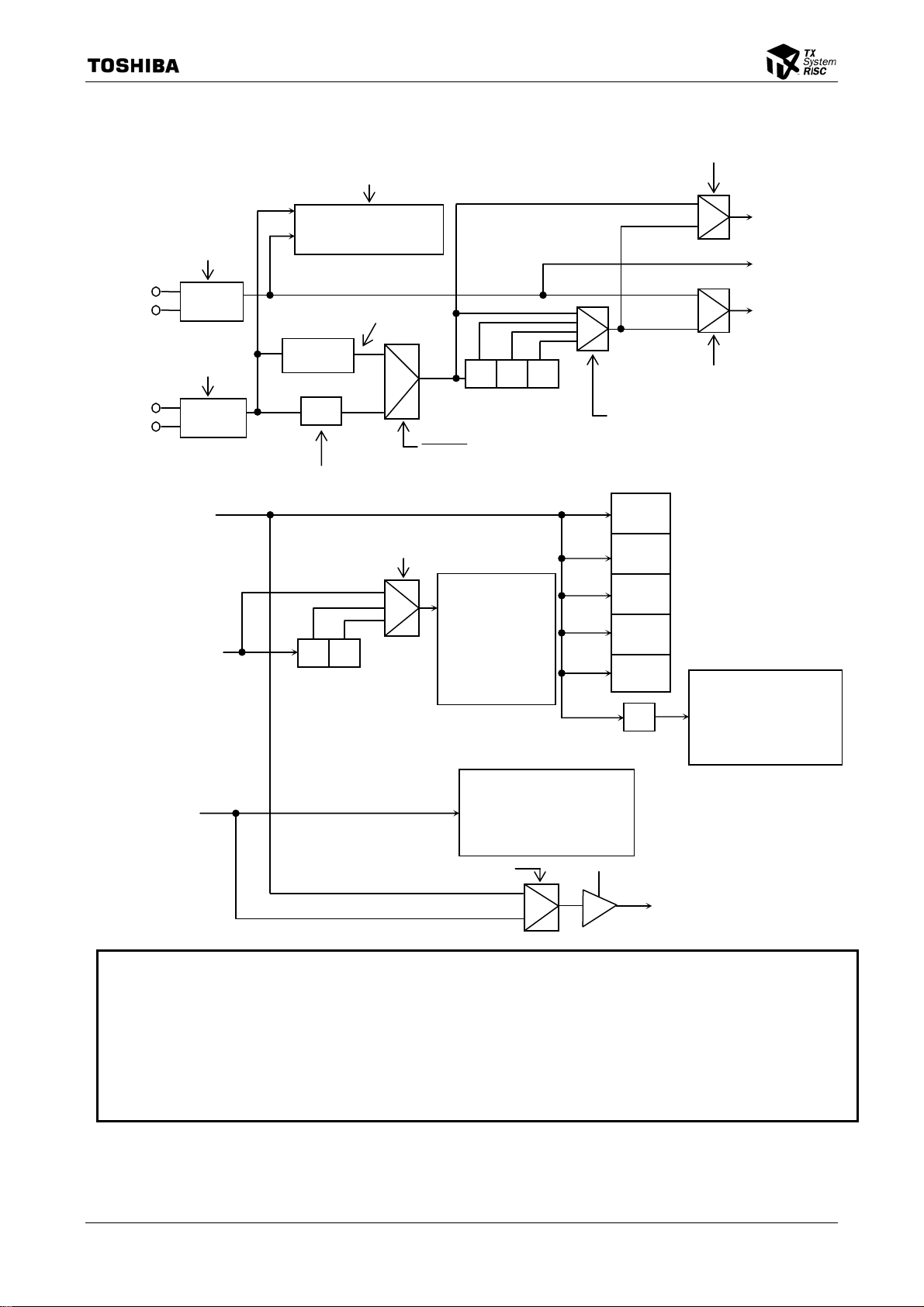

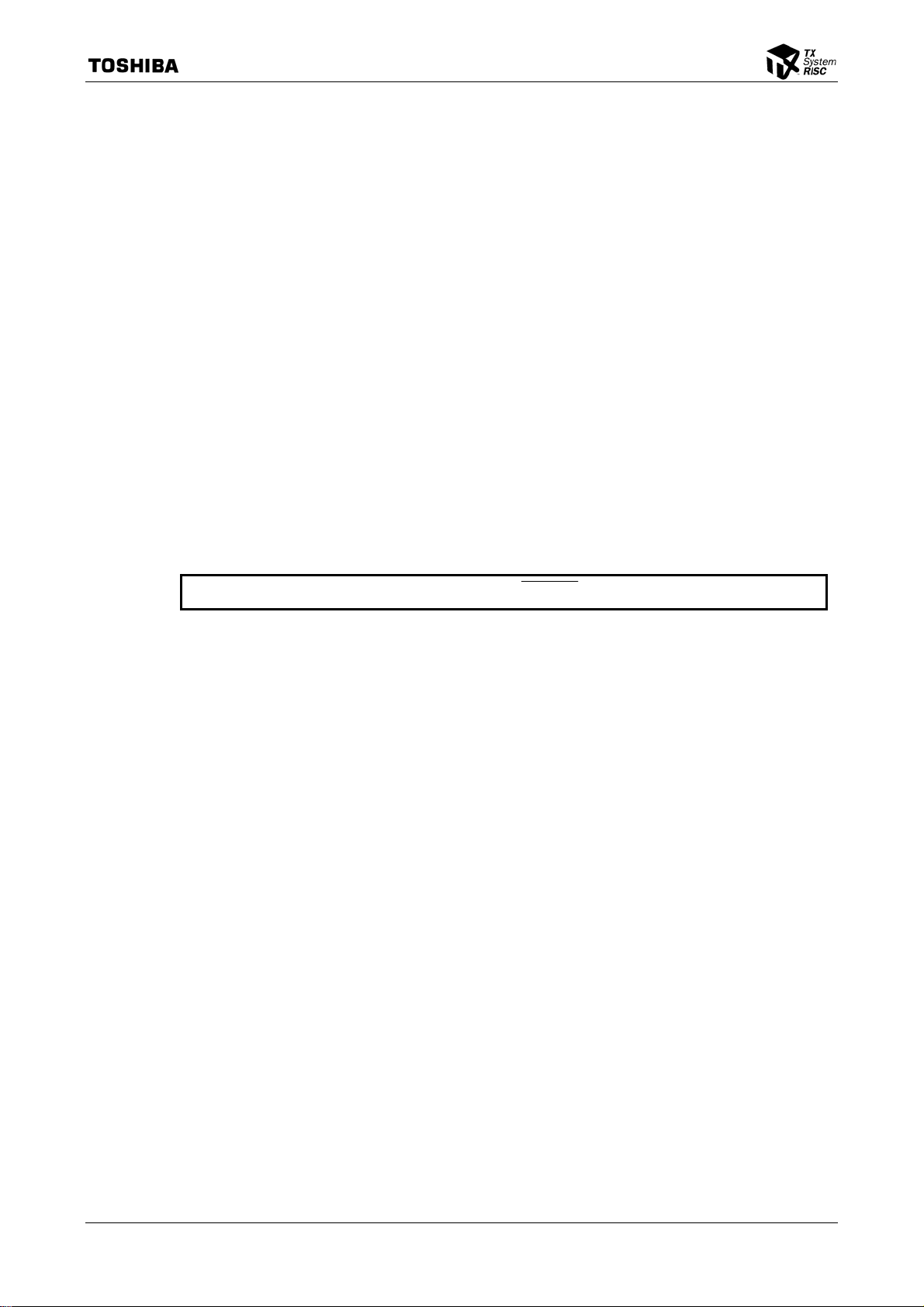

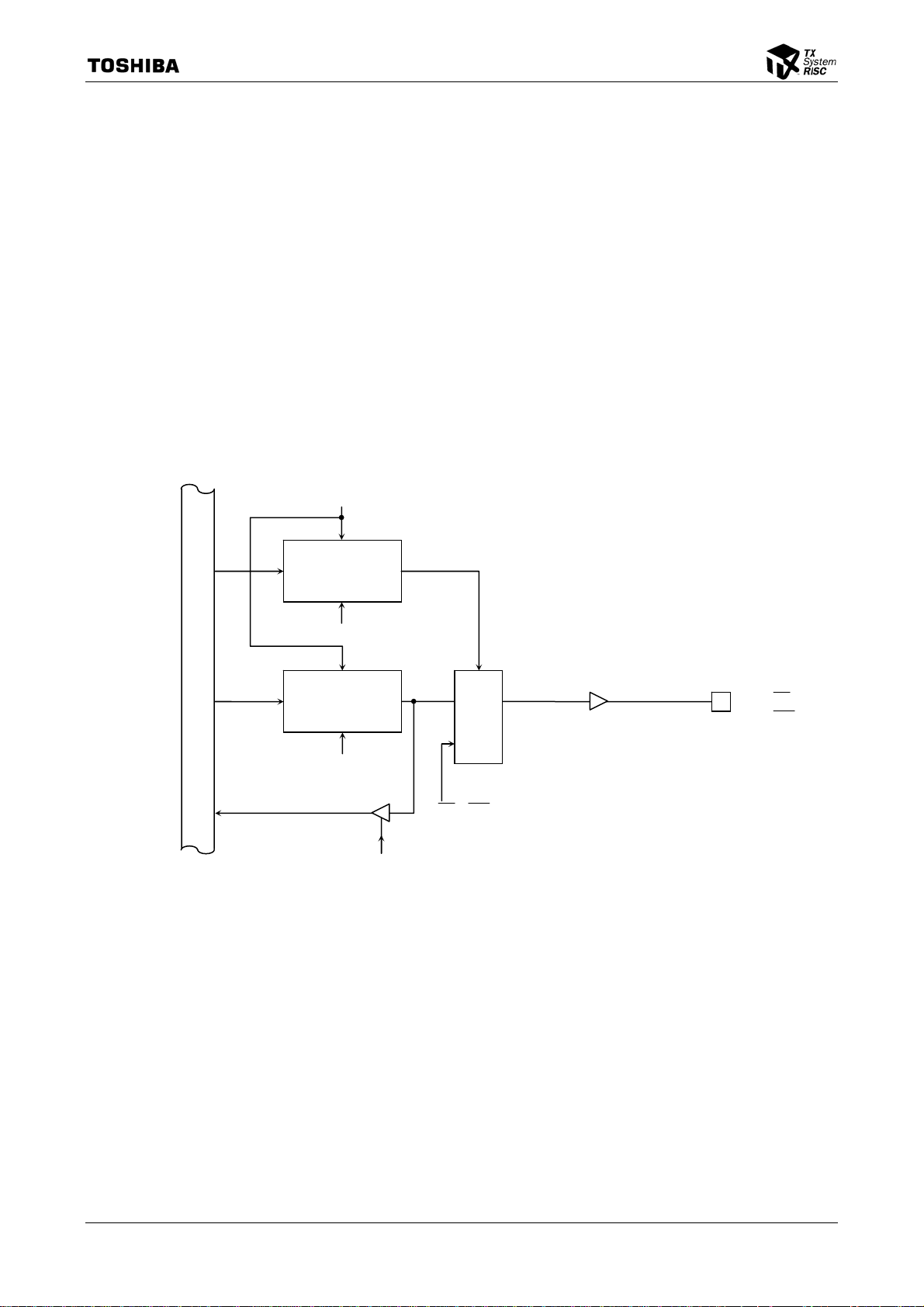

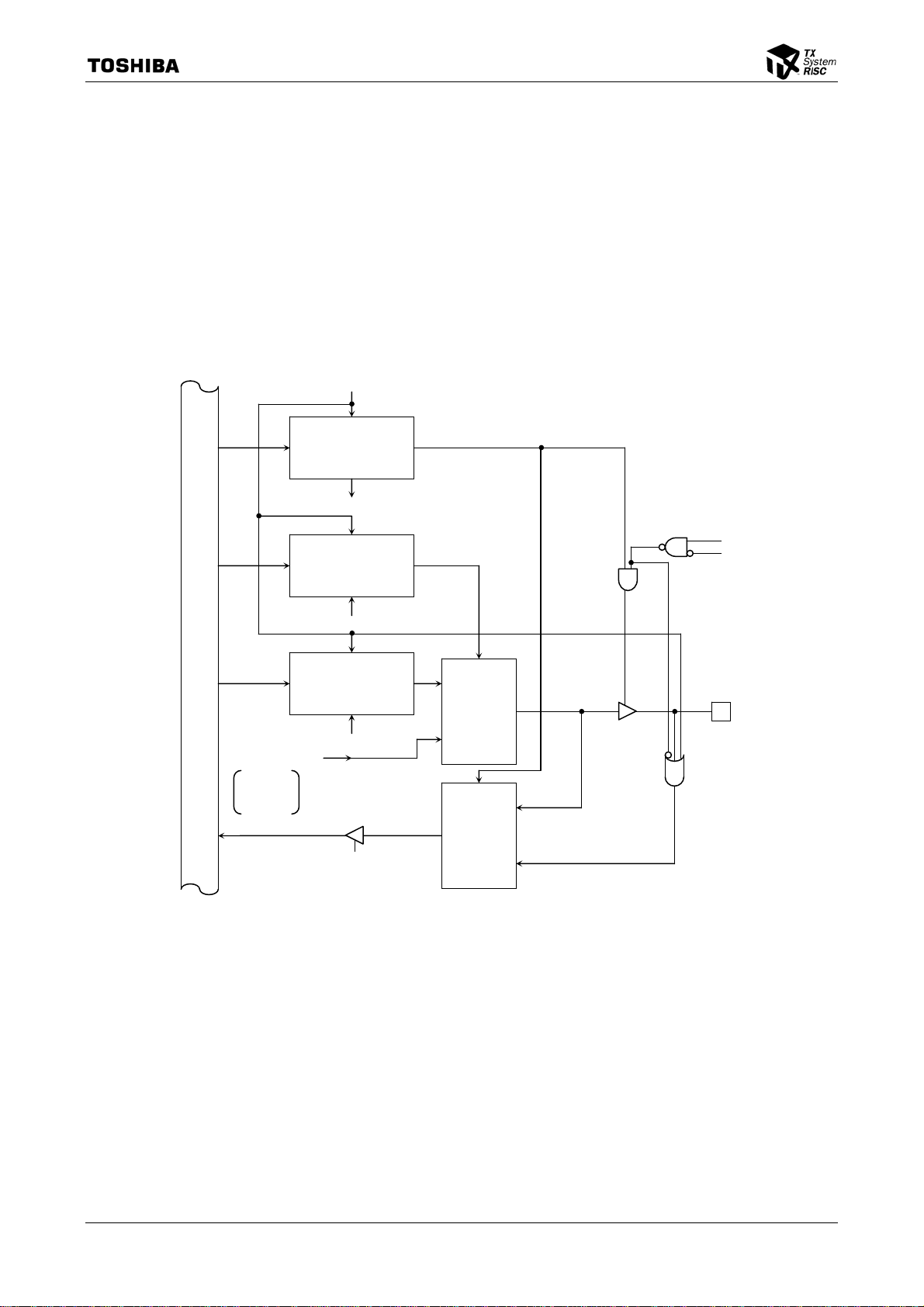

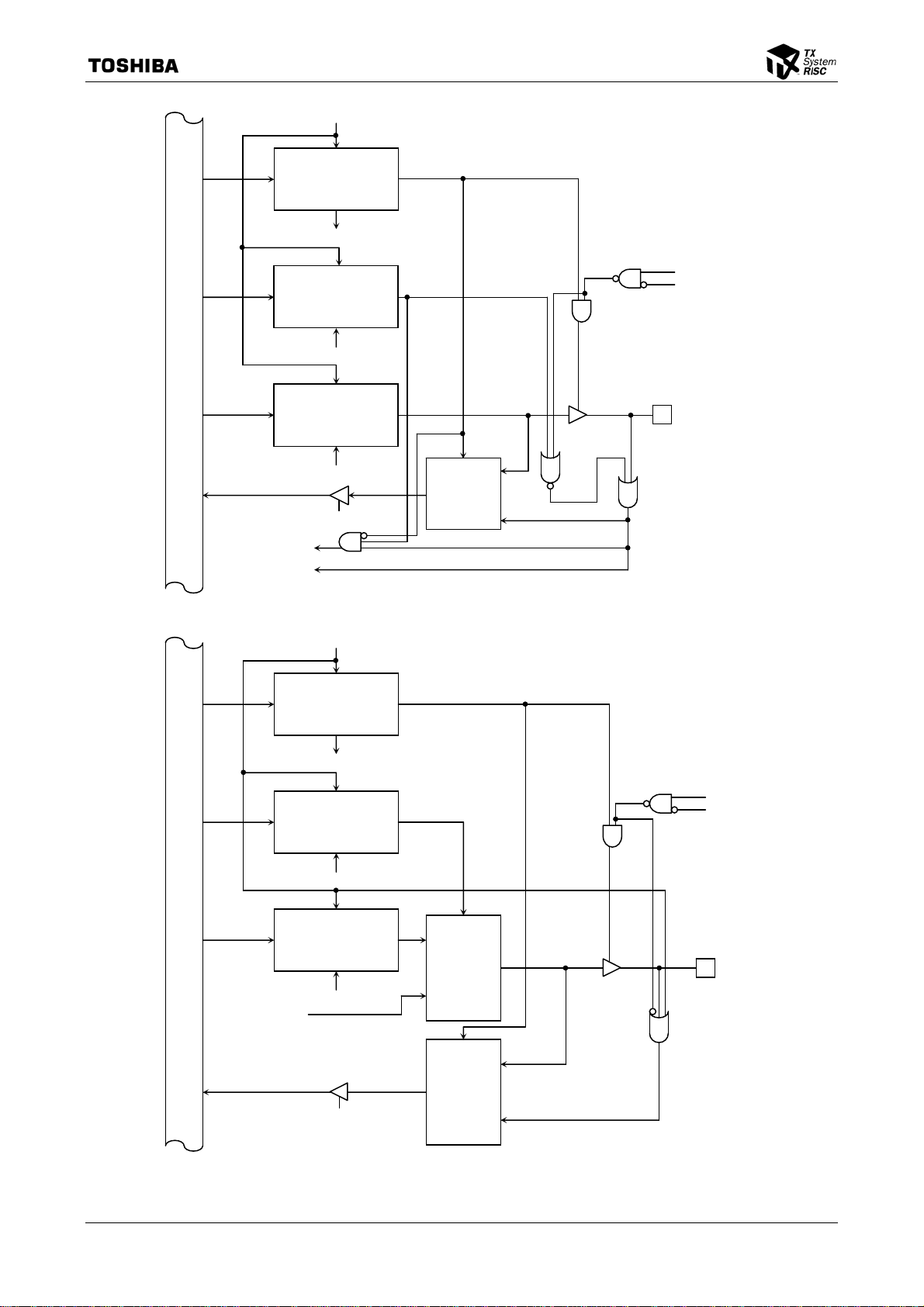

3.3.1 Block Diagram of Clock Circuits

1. Main system clock

• A crystal can be connected between X1 and X2, or X1 can be externally driven with a clock.

•

PLLOFF The on-chip PLL can be enabled or disabled (bypassed) during reset by using the

PLLOFF pin. When the PLL is enabled, the input clock frequency is multiplied by four.

• The clock gear can be programmed t o divide the clock by 2, 4 or 8. (The default is 1/8 on reset.)

• Input clock frequency

Input Frequency Range fmax fmin

PLLON

(for both resonator and external input)

Resonator 16~20 (MHz) 20 MHz 1 MHz

PLLOFF

*1. SYSCR1<DFOSC> must be 0. The default is 0.

2. Sub-system clock

• Generated using a 32.768-kHz resonator (external input also accepted).

• SLOW mode: The CPU runs at low speed.

External input

TMP1942CY/CZ

5~8 (MHz) 32 MHz 2.5 MHz

16~20 (MHz) 20 MHz 1 MHz

20

∼32 (MHz) 16 MHz

*1

1.25 MHz

• SLEEP mode: Only the timer for real-time clock, 2-phase pulse inp ut counter, and dynamic

pull-up operate.

TMP1942CY/CZ-18

3. Block di ag ram

SYSCR0

<XTEN>

XT1

XT2

Low-speed

oscillator

SYSCR0

<XEN>

X1

X2

High-speed

oscillator

fsys

fperiph

fs

SYSCR0<WUEF>

SYSCR2<WUPT1 : 0>

SYSCR3<LUPTM>

Warm-up timer

Lock-up (PLL) timer

fs

Fpll

PLL

÷2

fosc

SYSCR1 <DFOSC>

÷2 ÷4

= fosch × 4

Selector

SYSCR0

<PRCK1:0>

SYSCR3 <SCOSEL>

fc

÷2 ÷4 ÷8

PLLOFF (default pin setting)

Peripheral I/O

(prescaler input)

TMRA/B, SIO

SBI, ADC

Timer for real-time clock

2-phase pulse input counter

KWUP

TMP1942CY/CZ

SYSCR1 <FPSEL>

fgear

SYSCR1 <SYSCK>

SYSCR1 <GEAR1:0>

Divide by 8 after reset

CPU

ROM

RAM

DMAC

INTC

Peripheral I/O

÷2

ADC,DA,TMRA/B,

SIO,SBI,PIO, WDT, RTC

SCOUT

fperiph

(to peripheral I/O)

fs

fsys

Note 1: When using the clock gear to reduce the system clock frequency, make sure that φTn of the

prescaler output for each peripheral I/O block satisfies the following relationship:

φTn<fsys/2

To this end, set the clock-related registe rs so that φTn is slower than fsys/2.

When selecting a low-speed system clock (fs), only the timer for real-time clock, 2 -phase pulse input

counter, and dynamic pull-up can operate.

Figure 3.3.3 Block Diagram of Dual-Clock and Standby Functions

TMP1942CY/CZ-19

TMP1942CY/CZ

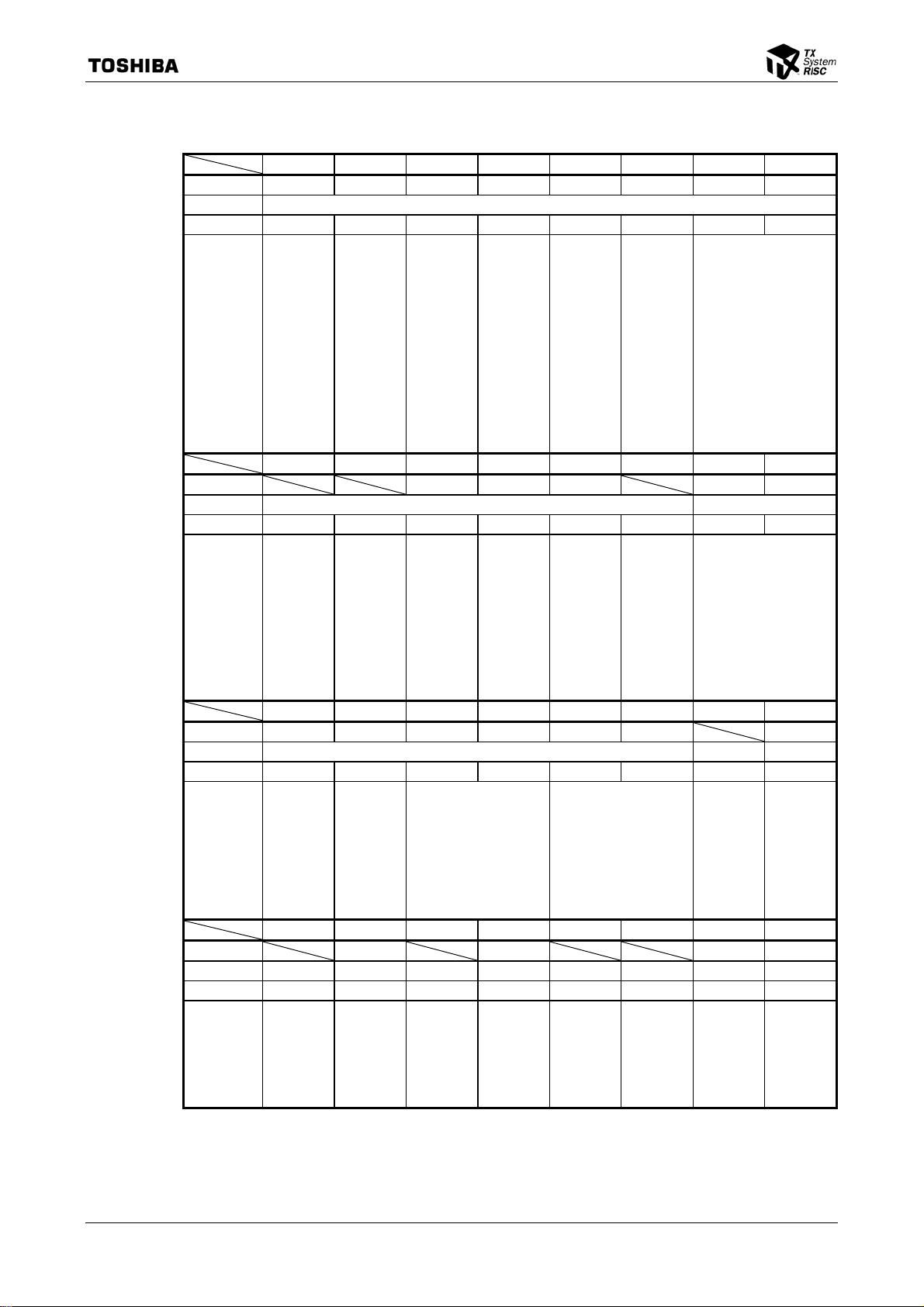

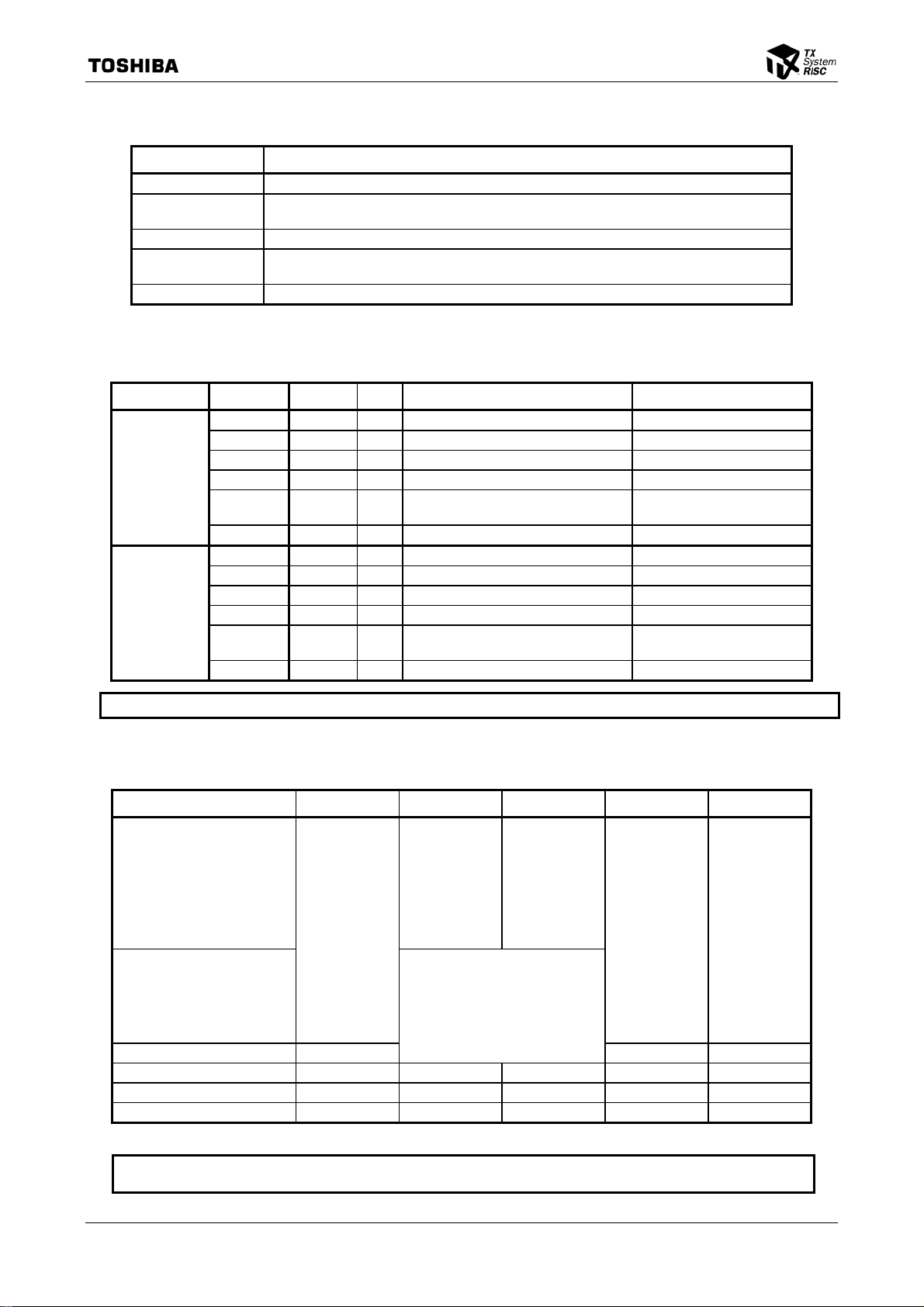

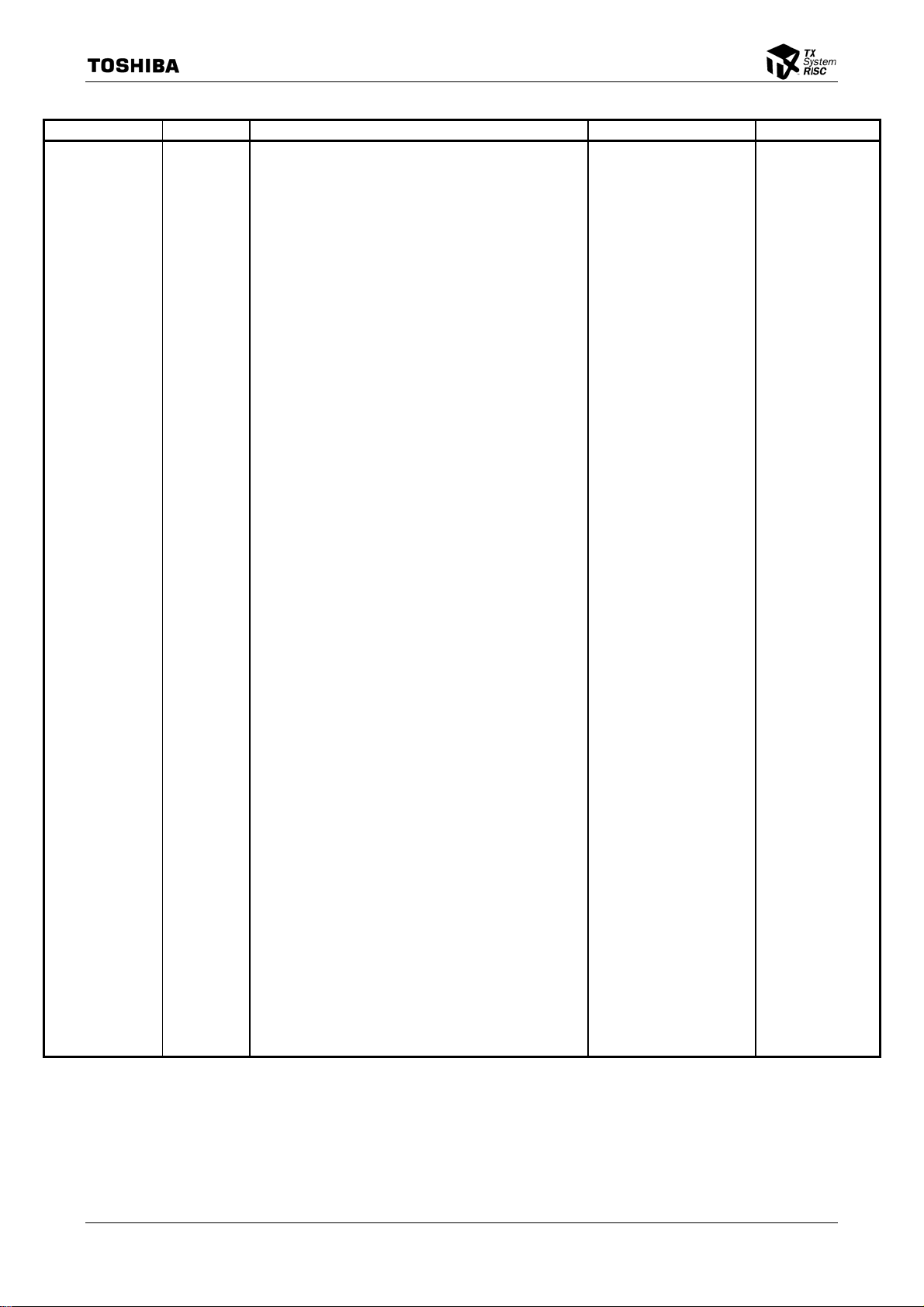

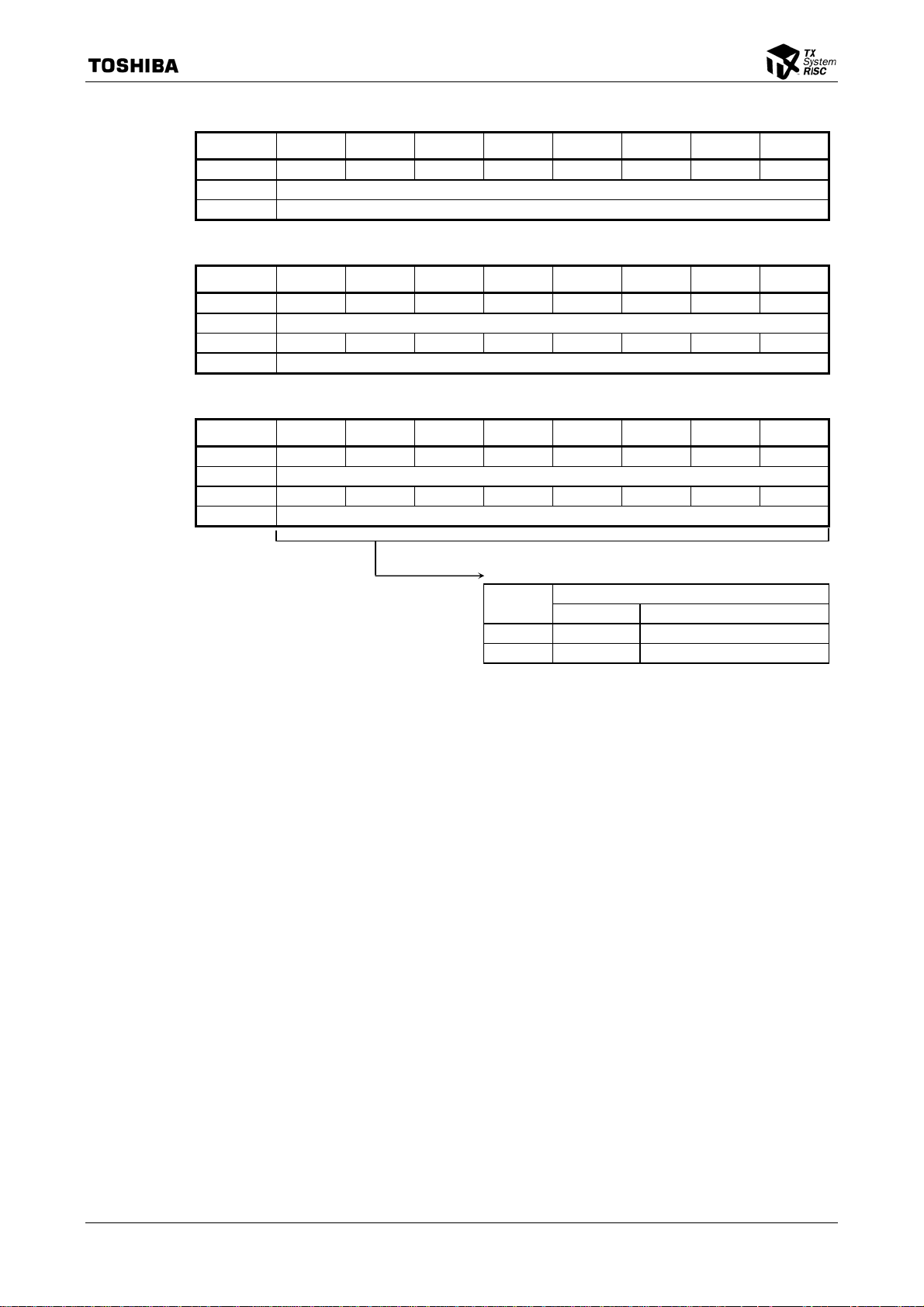

3.3.2 Clock Generator (CG) Registers

(1) Clock-related registers

SYSCR0 Bit Symbol XEN XTEN RXEN RXTEN RSYSCK WUEF PRCK1 PRCK0

(0xFFFF_EE00) Read/Write R/W

After reset 1 0 1 0 0 0 0 0

Function High-speed

SYSCR1 Bit Symbol SYSCK FPSEL DFOSC GEAR1 GEAR0

(0xFFFF_EE01) Read/Write R/W R/W

After reset - - 0 0 0 - 1 1

Function System

SYSCR2 Bit Symbol DRVOSCH DRVOSCL WUPT1 WUPT0 STBY1 STBY0 DRVE

(0xFFFF_EE02) Read/Write R/W - R/W

After reset 0 0 1 0 1 1 - 0

Function High-speed

SYSCR3 Bit Symbol SCOSEL ALESEL LUPFG LUPTM

(0xFFFF_EE03) Read/Write - R/W - R/W - - R R/W

After reset - 0 - 1 - - 0 0

Function SCOUT

7 6 5 4 3 2 1 0

oscillator

0: Turned off

1: Oscillating

Low-speed

oscillator

0: Turned off

1: Oscillating

High-speed

oscillator

after exit

from STOP

mode

0: Turned off

1: Oscillating

Low-speed

oscillator

after exit

from STOP

mode

0: Turned off

1: Oscillating

Clock

selection

after exit

from STOP

mode

0: High speed

1: Low speed

Oscillator

warm-up

timer (WUP)

control

Write 0:

Don't care

Write 1:

WUP start

Read 0:

WUP finished

Read 1:

WUP

operating

Prescaler clock selection

00: fperiph/4

01: fperiph/2

10: fperiph

11: (reserved)

15 14 13 12 11 10 9 8

clock

selection

0: High speed

(fc)

1: Low speed

(fs)

fperiph

selection

0: fgear

1: fc

High-speed

oscillator

frequency

division

selection

0: Divide by 2

1: Divide by 1

High-speed clock (fc)

gear selection

00: fc

01: fc/2

10: fc/4

11: fc/8

23 22 21 20 19 18 17 16

Standby mode selection

00: Reserved

01: STOP mode

10: SLEEP mode

11: IDLE mode

1: Pins are

also

driven in

STOP

mode.

oscillator

driving

capability

control

0: Normal

1: Weak

Low-speed

oscillator

driving

capability

control

0: Normal

1: Weak

Oscillator warm-up time

selection

2

/input frequency

00: 2

8

/input frequency

01: 2

10: 214/input frequency

11: 216/input frequency

31 30 29 28 27 26 25 24

output

selection

0: fs

1: fsys

ALE output

Lock-up flag

width

selection

0: fsys × 0.5

1: fsys × 1.5

0: LUP

finished

1: LUP in

operation

Lock-up time

selection

16

0: 2

/input

frequency

12

/input

1: 2

frequency

TMP1942CY/CZ-20

TMP1942CY/CZ

Note 1: Standby mode selection depends on the settings of the Doze and Halt bits in the CP0's internal

Config register. If the Halt bit = 1, the device will enter the mode selected by STBY[1:0].

If the Doze bit = 1, the device will always enter IDLE mode.

Note 2: When the PLL is not used, set the LUPTM bit in the SYSCR3 register to 1 (i.e., select 2

frequency).

Note3: The WURT1-WUPT0 bitys in the SYSCR2 must be not be changed during the oscillator warm-up

event ( e.g. SLEEP-NORMAL-SLEEP)

Note 4: Do as follows to change the operating mode immediately after the device has warmed up from the

clock stop state (e.g., from SLEEP mode to NORMAL mode to SLEEP mode).

• Warming up by hardware

(1) Moving from STOP or SLEEP mode to NORMAL mode

1) When the PLL is used

Before moving to the next operating mode, ensure that the lock-up bit, LUPFG, in the SYSCR3

register has been cleared to zero and wait for five or more instructions to complete (including the

instruction to check the LUPFG flag).

2) When the PLL is not used

• When the oscillator warm-up time (SYSCR2<WUPT1:0>) is programmed as “01” (i.e., 2

Before moving to the next operating mode, ensure that the lock-up bit, LUPFG, in the SYSCR3 register has

been cleared to zero and wait for five or more instructions to complete.

• When the oscillator warm-up time (SYSCR2<WUPT1:0>) is programmed as “10” (214/input frequency) or

“11” (216/input frequency). Before moving to the next operating mode, wait for five or more instructions to

complete.

8

/input frequency).

12

/input

(2) Moving from STOP or SLEEP mode to SLOW mode

It is possible to move to SLOW mode immediately after the device has warmed up from STOP or SLEEP

mode.

• Warming up by software

(1) Moving from SLOW mode to NORMAL mode

1) When the PLL is used

It is possible to move to NORMAL mode immediately after the device has warmed up. However, to

move to another mode after that, ensure that the lock-up bit, LUPFG , in the SYSCR3 register has been

cleared to zero and wait for five or more instructions to complete (including the instruction to check the

LUPFG flag).

2) When the PLL is not used

• When the oscillator warm-up time (SYSCR2<WUPT1:0>) is programmed as “01” (i.e., 2

It is possible to move to NORMAL mode immediately after the d evice has warmed up . However, to move to

another mode after that, ensure that the lock-up bit, LUPFG, in the SYSCR3 register has been cleare d to zero

and wait for five or more instructions to complete.

8

/input frequency).

• When the oscillator warm-up time (SYSCR2<WUPT1:0>) is programmed as “10” (214/input

frequency) or “11” (2

16

/input frequency). It is possible to move to NORMAL mode immediately

after the device has warmed up. However, to move to another mode after that, wait for five or

more instructions to complete.

(2) Moving from NORMAL mode to SLOW mode

Before moving to SLOW mode, ensure that the warm-up end flag (i.e., the WUEF bit in the SYSCR0

register) is cleared and wait for five or more instructions to complete.

TMP1942CY/CZ-21

TMP1942CY/CZ

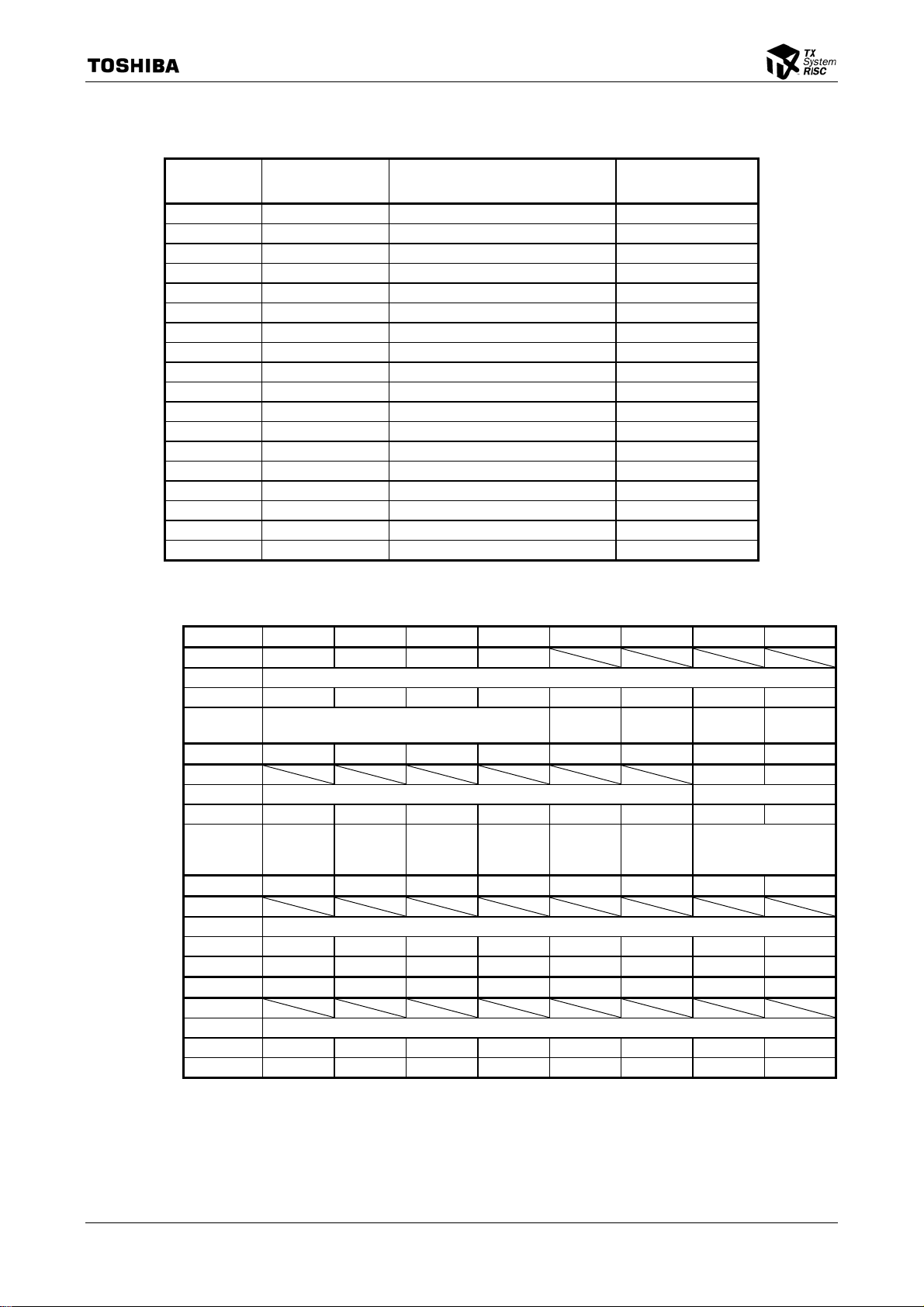

(2) Standby (STOP/SLEEP mode) termination interrupts

IMCGA0

(0xFFFF_EE10) Read/Write ⎯ ⎯ R/W ⎯ ⎯ ⎯ R/W

After reset ⎯ ⎯ 1 0 ⎯ ⎯ ⎯ 0

Function Active state setting for

Bit Symbol

Read/Write ⎯ ⎯ R/W ⎯ ⎯ ⎯ R/W

After reset ⎯ ⎯ 1 0 ⎯ ⎯ ⎯ 0

Function Active state setting for

Bit Symbol EMCG21 EMCG20

Read/Write ⎯ ⎯ R/W ⎯ ⎯ ⎯ R/W

After reset ⎯ ⎯ 1 0 ⎯ ⎯ ⎯ 0

Function Active state setting for

Bit Symbol EMCG31 EMCG30 INT3EN

Read/Write ⎯ ⎯ R/W ⎯ ⎯ ⎯ R/W

After reset ⎯ ⎯ 1 0 ⎯ ⎯ ⎯ 0

Bit Symbol EMCG01 EMCG00 INT0EN

Function Active state setting for

7 6 5 4 3 2 1 0

INT0

INT0 standby termination

request

00: Low level

01: High level

10: Falling edge

11: Rising edge

request

input

0: Disable

1: Enable

15 14 13 12 11 10 9 8

EMCG11 EMCG10 DFOSC INT1EN

INT1 standby termination

request

00: Low level

01: High level

10: Falling edge

11: Rising edge

INT1

request

input

0: Disable

1: Enable

23 22 21 20 19 18 17 16

INT2

INT2 standby termination

request

00: Low level

01: High level

10: Falling edge

11: Rising edge

INT2EN

request

input

0: Disable

1: Enable

31 30 29 28 27 26 25 24

INT3 standby termination

request

00: Low level

01: High level

10: Falling edge

11: Rising edge

INT3

request

input

0: Disable

1: Enable

TMP1942CY/CZ-22

TMP1942CY/CZ

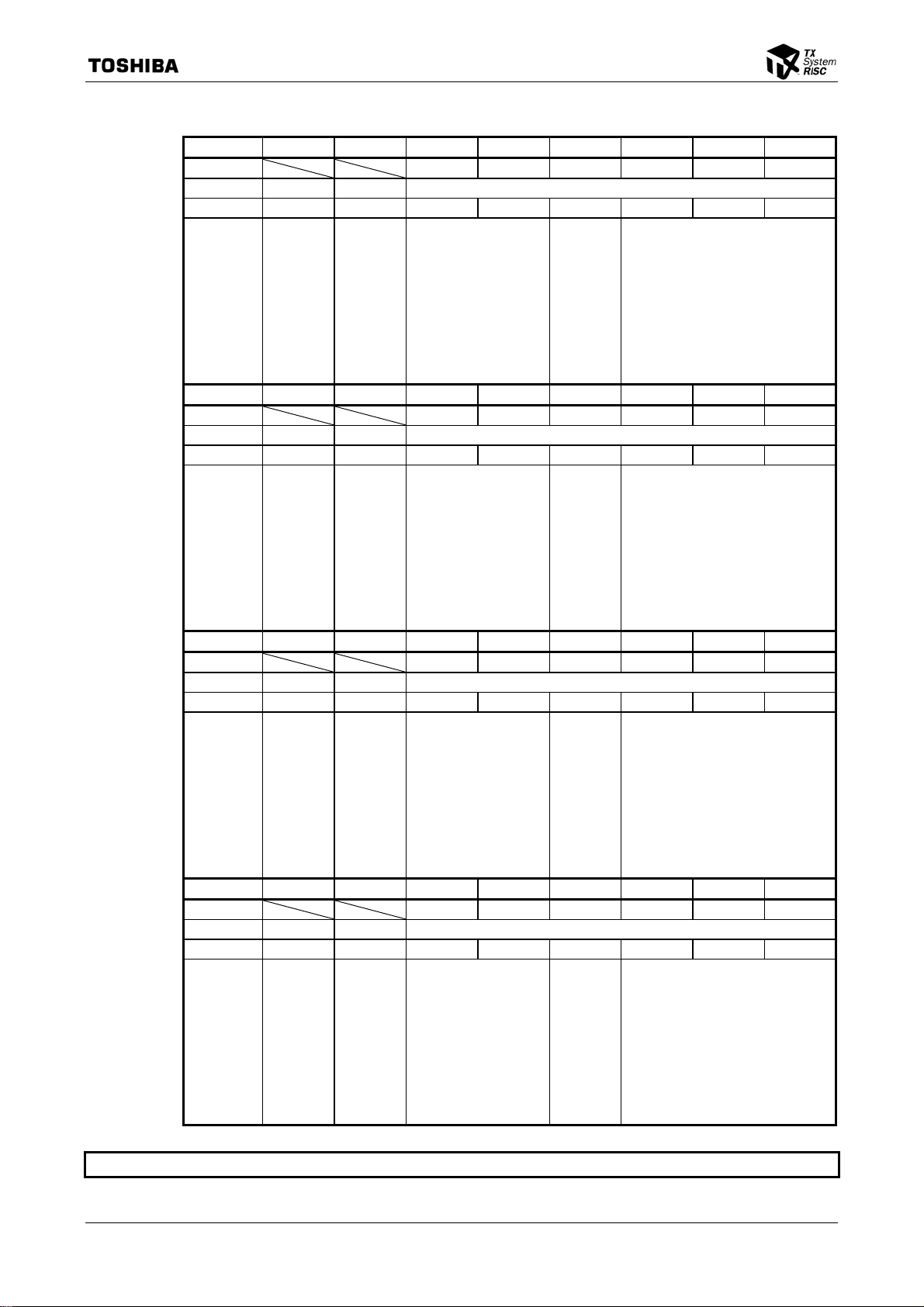

IMCGB0

(0xFFFF_EE14) Read/Write ⎯ ⎯ R/W ⎯ ⎯ ⎯ R/W

After reset

Function

Bit Symbol EMCG51 EMCG50 KWUPEN

Read/Write ⎯ ⎯ R/W ⎯ ⎯ ⎯ R/W

After reset ⎯ ⎯ 1 0 ⎯ ⎯ ⎯ 0

Function These bits should always

Bit Symbol

Read/Write ⎯ ⎯ R/W ⎯ ⎯ ⎯ R/W

After reset ⎯ ⎯ 1 0 ⎯ ⎯ ⎯ 0

Function These bits should always

Bit Symbol EMCG71 EMCG70

Read/Write ⎯ ⎯

After reset

Function

Bit Symbol

7 6 5 4 3 2 1 0

EMCG41 EMCG40 INT4EN

⎯ ⎯ 1 0 ⎯ ⎯ ⎯ 0

Active state setting for

INT4 standby termination

request

00: Low level

01: High level

10: Falling edge

11: Rising edge

INT4

request

input

0: Disable

1: Enable

15 14 13 12 11 10 9 8

be set to 01.

KWUP

request

input

0: Disable

1: Enable

23 22 21 20 19 18 17 16

EMCG61 EMCG60

INTBCDE

be set to 01.

INTBCDEEN

request

input

0: Disable

1: Enable

31 30 29 28 27 26 25 24

INTRTCEN

R/W

0

request

input

0: Disable

1: Enable

⎯ ⎯

R/W

1 0

These bits should always

be set to 11.

⎯ ⎯ ⎯

⎯ ⎯ ⎯

INTRTCEN

TMP1942CY/CZ-23

Note 1: When enabling an interrupt source as a means of terminating a standby mode, always set the active

state for the corresponding interrupt request.

Note 2: When using an interrupt, always perform the following steps in order:

(1) Enable the input for the interrupt if the corresponding pin is also used for a ge neral-purpose

port or any other purpose.

(2) Set the active state for the interrupt during initialization.

(3) Clear the interrupt request.

(4) Enable the interrupt.

Note 3: The TMP1942 has eight interrupt sources (INT0~INT4, INTRTC, INTB/INTC/INTD/INTE, and

KWUP0-KWUPD) which can be used as a means of terminating a standby mode. For INT0 to INT4,

use the CG block to specify whether they are used to terminate a st andby mode and to spe cify their

active edge or level. For INTB/INTC/INTD/INTE and KWUP0-KWUPD, use the CG block to specify

whether they are used to terminate a standby mode and use INTBCDEST and KWUPSTn,

respectively , to specify their active edge or level. Set the active stat e for the corresponding interrupt

source to High in the INTC block.

Example: Enable the INT0 interrupt

IMCGA0<EMCG01:00> = “10” CG block

IMCGA0<INT0EN> = “1” (Input is enabled on the falling edge.)

IMC0L<EIM11:10> = “01” INTC block

IMC0L<IL12:10> = “101” (A High-level interrupt is active and the interrupt level is 5.)

All interrupt sources other than those which are used to terminate S TOP/SLEEP mode are set in the

INTC circuit block.

TMP1942CY/CZ

Note 4: Among the above eight interrupt sources used to request the termination of a standby mode, INT0

to INT4 do not require settings in the CG block if they are used as normal interrupts. They still,

however, require level or edge spe cification in the INTC. If INTB/INTC/INTD/INTE and

KWUP0-KWUPD are used as normal interrupts, specify the active level or edge using

INTBCDEST/KWUPSTn and specify the High level in the INTC. Settings in the CG are not required.

INTRTC always requires settings in both the CG and INTC even if it is used as a normal interrupt.

All interrupt sources other than those which are used to terminate a standby mod e are set in the

INTC circuit block.

TMP1942CY/CZ-24

TMP1942CY/CZ

(3) Interrupt request clear register

EICRCG

(0xFFFF_EE20) Read/Write ⎯ ⎯ ⎯ ⎯ ⎯ W

After reset

Function

Bit Symbol

7 6 5 4 3 2 1 0

ICRCG2 ICRCG1 ICRCG0

⎯ ⎯

Clear interrupt request

1 0

⎯ ⎯ ⎯ ⎯

000: INT0 100: INT4

001: INT1 101:KWUP

010: INT2 110: INTB/C/D/E

011: INT3 111: INTRTC

Note : To clear any of the eight interrupt sources which are used for terminating a standby mode:

(1) For KWUP, use KWUPCLR.

(2) For extended interrupts INTB/INTC/INTD/INTE, use INTFLG.

(3) For INT0 to INT4 and INTRTC, perform the clea ring operation twice, first in the CG block and

then in the INTC block.

(4) For all other interrupt sources, use the INTC block.

3.3.3 System clock control unit

When reset, the device enters single-clock mode with the result that XEN = 1, XTEN = 0 and

GEAR1:0 = 11 ; the system clock fsys is set to fc/8 (= fc × 1/8). (Since the PLL multiplies the original

oscillation frequency by 4, fc equals to fosc × 4, where fosc is the original oscillation frequency.) For

example, if the X1 and X2 pins are connected to an 8-MHz resonator, a reset will set fsys to 4 MHz (= 8

MHz × 4 × 1/8).

To disable the system from using a PLL-multiplied clock as the system clock by default, drive the

PLLOFF pin Low. In this case, too, the system clock fsys will be set to fc/8 (= fc × 1/8) by a reset.

However, since SYSCR1<DFOSC> is initialized to 0 by a reset (so that fc = fosc × 1/2), if the X1 and X2

pins are connected to a 25-MHz reso nator , fsys will be 1.25 MHz. Also, if the device is clocked by an

external oscillator and no internal resonator is connected, fc = fosc can be selected by setting

SYSCR1<DFOCS> to 1 after a reset, so that the system clock frequency fsys is twice the frequency

obtained with an internal resonator.

(1) Oscillation settling time (switchover between NORMAL and SLOW modes)

If a resonator is connected to the resonator-con nect i n g pi ns , the device uses the built-in warm-up

timer to check whether resonator oscillation has settled. The warm-up time can be set to suit the

characteristics of the resonator using SYSCR2<WUPT1:WUPT0>. The value of SYSCR0<WUEF>

must be checked in software (using instructions) to determine the start and completion of the

warm-up

time.

Table 3.3.1 shows warm-up

times for mode switching.

TMP1942CY/CZ-25

TMP1942CY/CZ

Note 1: Warm-up is unnecessary when the clock generator uses an oscillator so that it s oscillation is stable.

Note 2: Since the warm-up timer is clocked by an oscillating clock, it will not be exact if the oscillation

frequency fluctuates. The warm-up time should, therefore, be considered to be an approximate

value.

Note 3: Before starting the warm-up timer, first confirm that the PLL lock-up flag <LUPF G> is 0.

Note 4: The following precautions must be observed when a low-speed oscillator is being used:

When a low-speed oscillator is connected to ports PD6 and PD7, the corresponding re gister must

be set as shown below in order to reduce the device's power consumption.

(When using a resonator)

Set PDCR<PD6C, PD7C> to 11 and PD<PD6, PD7> to 00.

(When using an external clock)

Set PDCR<PD6C, PD7C> to 11 and PD<PD6, PD7> to 10.

Table 3.3.1 Warm-Up Ti me

Warm-Up T ime Selection

SYSCR2<WUPT1:0>

(22/oscillation frequency) 0.5 [μs] 122 [μs]

(28/oscillation frequency) 32 [μs] 7.8 [ms]

(214/oscillation frequency) 2.048 [ms] 500 [ms]

(216/oscillation frequency) 8.192 [ms] 2000 [ms]

High-Speed Clo ck

(fosc)

Low-Speed Clock (fs)

The values calculated

are for when

fosc = 8 MHz

and fs = 32.768 kHz.

Note: When returning from STOP/SLEEP mode to NORMA L or SLOW mode, set the wa rm-up time to 122

μs or greater beforehand.

Example: If the device will return from SLEEP mode to SLOW mode, set SYSCR2<WUPT1:0> to 00,

that is, a warm-up time of 122 μs, before entering SLEEP mode.

(2) Outputting the system clock from a pin

The system clock fsys or fs can be output from the P44/SCOUT pin to an external device. The

P44/SCOUT pin can be set to function as the SCOUT pin by setting the re gisters which rel ate to port

4 as follows: P4CR<P44C> = 1 and P4FC<P44F> = 1. Use SYSCR3<SCOSEL> to select which

clock will be output from this pin.

T able 3. 3.2 shows t he pin stat e for eac h standby m ode when the P44/SC

OUT pin is set t o functio n

as SCOUT.

Table 3.3.2 SCOUT Output State for Each Standby Mode

Mode

SCOUT Selection

<SCOSEL> = “0” Outputs fs clock.

<SCOSEL> = “1” Outputs fsys clock.

NORMAL,

SLOW

IDLE SLEEP STOP

Standby Mode

Fixed to 0 or 1

Note: This function does not guarantee a particular phase difference (AC timing ) betwee n the internal cl ock

and the system clock output from SCOUT.

TMP1942CY/CZ-26

TMP1942CY/CZ

(3) Reducing the driving capability of oscillators

If a resonator is connected to the resonator-connecting pins of an oscillator, this function can

suppress oscillation noise output from the oscillator, while reducing power consumption by the

oscillator.

Setting SYSCR2<DRVOSCH> to 1 causes the driving capability o f the high-speed oscillator to

degrade (Weak). Similarly, setting SYSCR2<DRVOSCL> to 1 causes the driving capability of th e

low-speed oscillator to degrade (Weak).

Because both bits are initialized to 0 upon a system reset, both oscillators start oscillating with

their normal driving capability (Normal) when the power is turned on. The oscillators must be placed

in the Normal state (<DRVOSCL> or <DRVOSCH> = 0) when they start oscillating in any other

cases, such as when STOP/SLEEP mode is terminated.

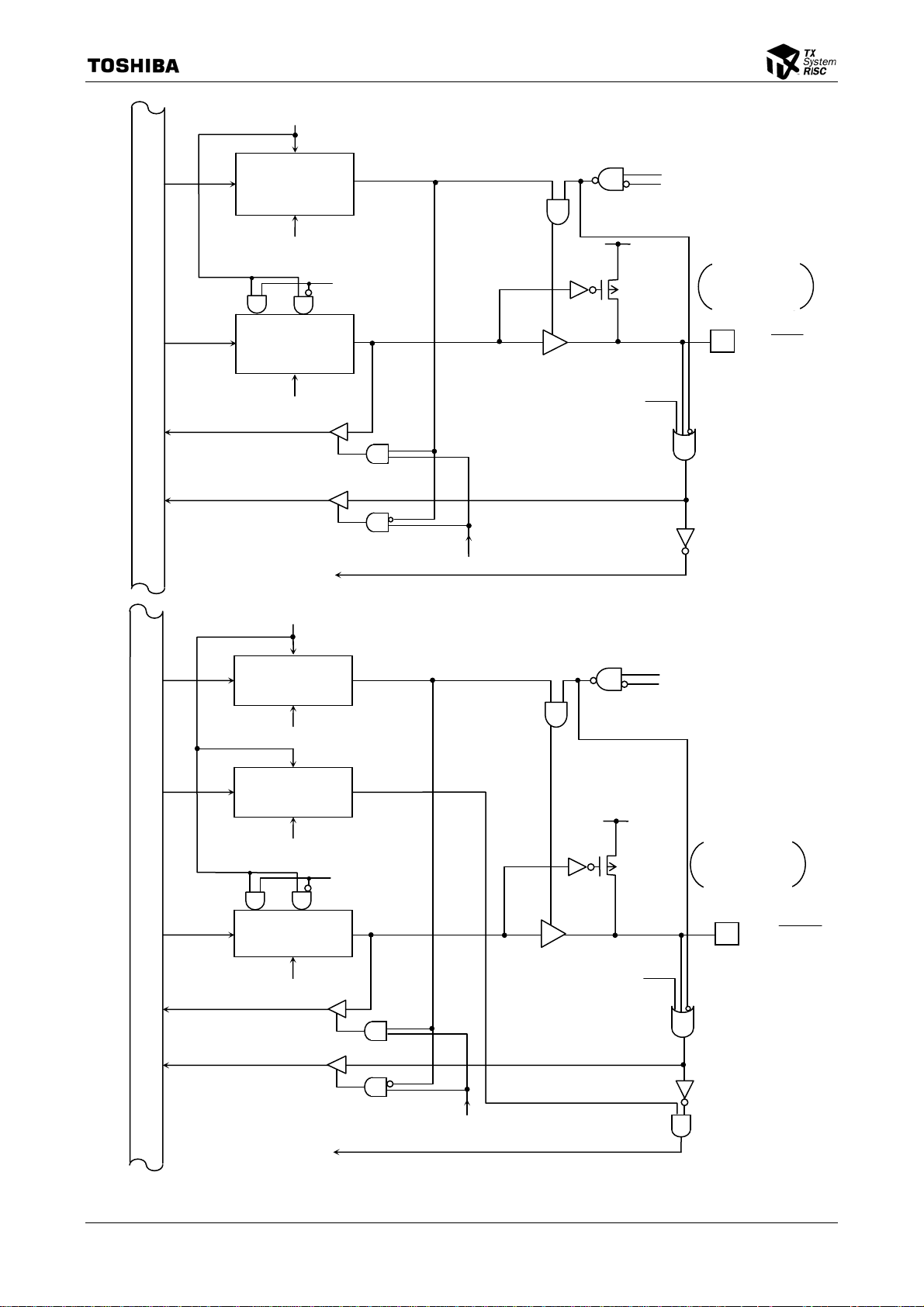

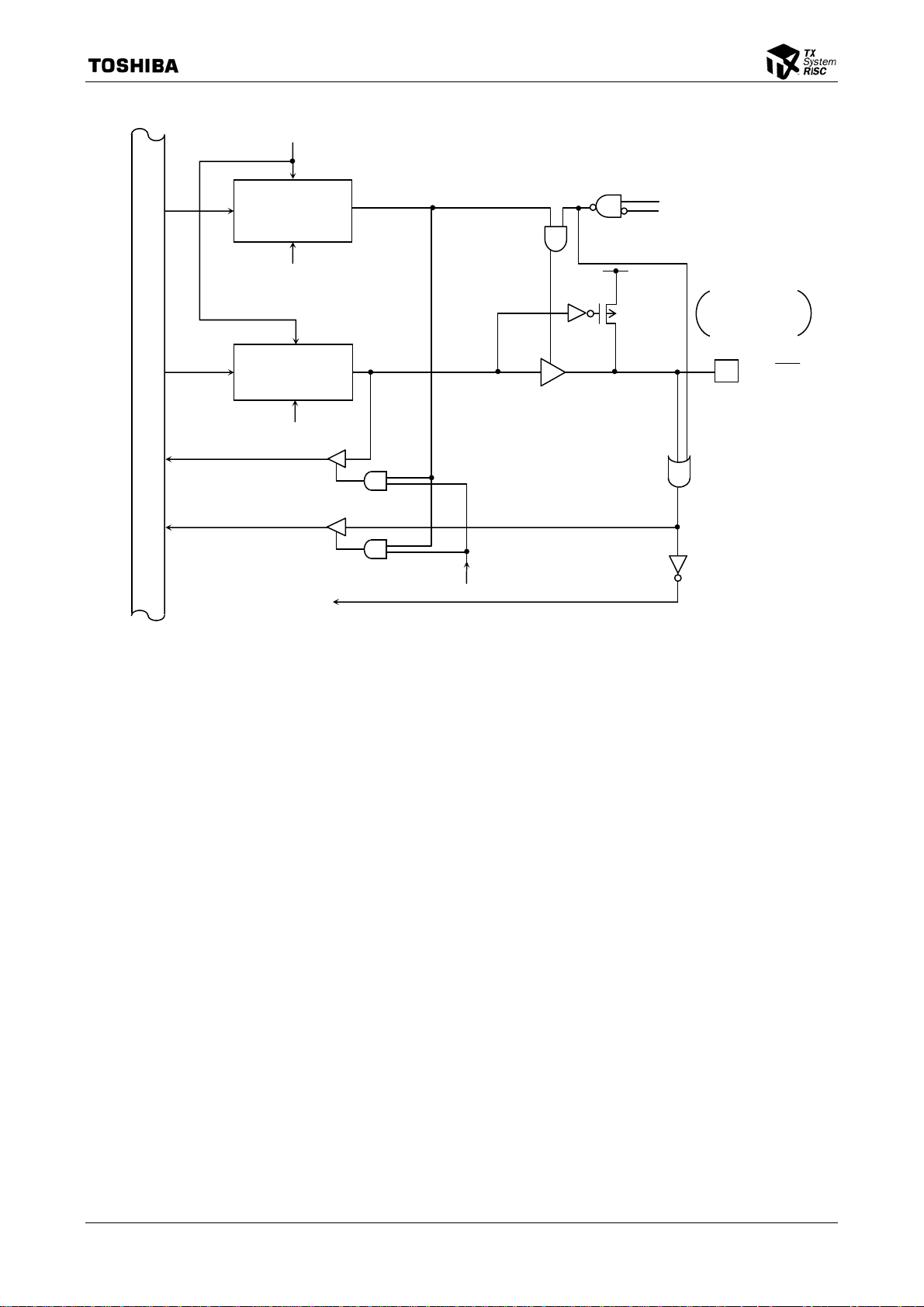

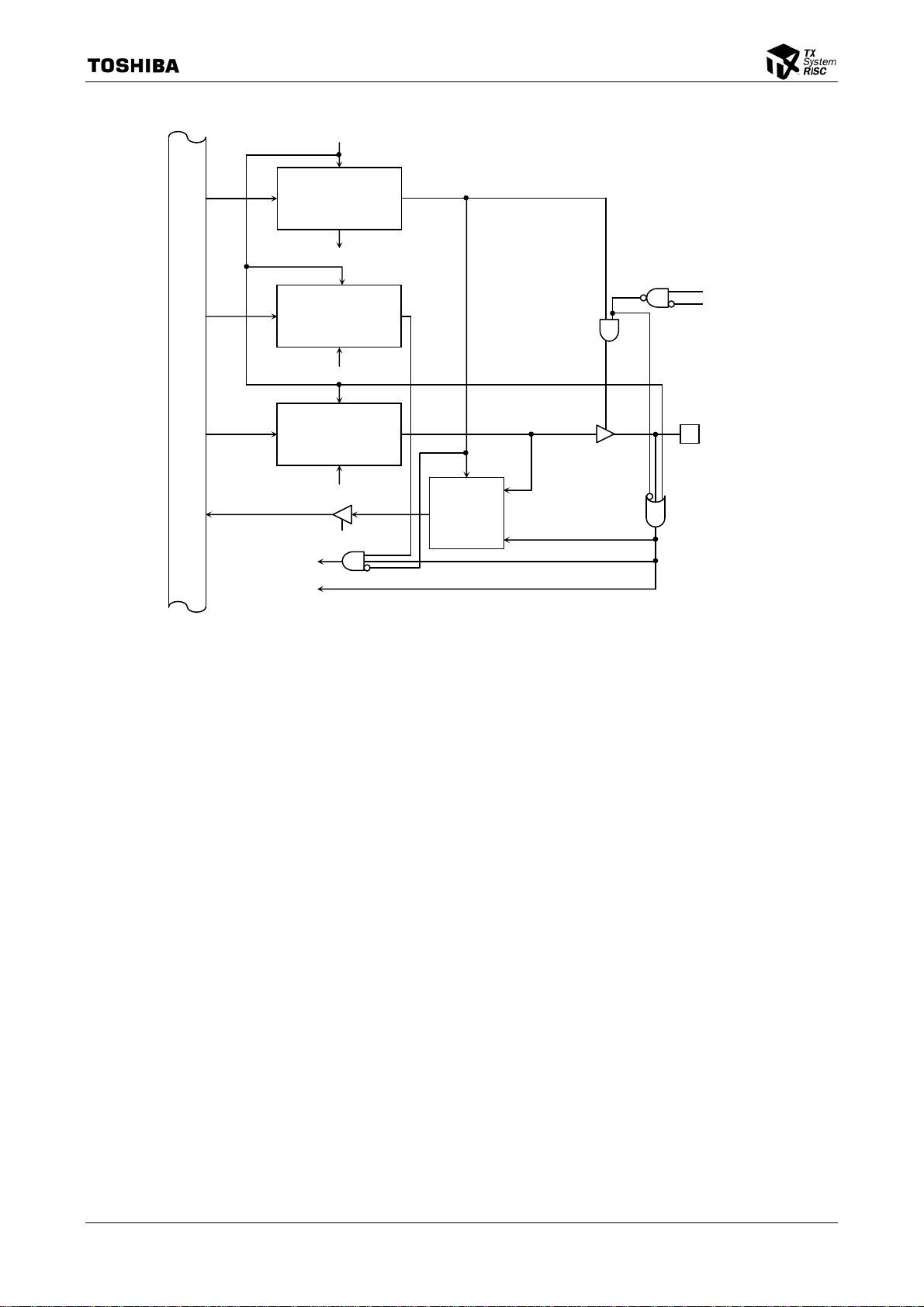

1) Reducing the driving capability of the high-speed oscillator

C1

X1 pin

Resonator

C2

Oscillation enable

SYSCR2<DRVOSCH>

f

OSC

X2 pin

2) Reducing the driving capability of the low-speed oscillator

C1

Resonator

C2

XT1 pin

XT2 pin

Oscillation enable

SYSCR2<DRVOSCL>

f

S

3.3.4 Prescaler clock control unit

The internal I/O blocks (TMRA01 to TMRAAB, TMRB0 to TMRBD, SIO0 to SIO5, SBI, and ADC)

each incorporate a prescaler for dividing the clock frequency. The clock φT0 fed into these prescalers is

derived from the clock fperiph. fperiph is either fgear or fc (as specified by the value of

SYSCR1<FPSEL>) divided by either 4 or 2, or not divided (as specified by the value of

SYSCR0<PRCK1:PRCK0>. By default, fperiph is set to fgear and φT0 to fperiph/4.

3.3.5 Clock multiplication circuit (PLL)

This circuit multiplies the high-speed oscillator outpu t clock, fosc, by 4 and outputs the result as the

clock fpll. This enables the oscillator to yield a fast internal clock with a low oscillator frequency . The

PLL is halted by a reset. To use the PLL, hold the

Note: If a reset is terminated while the

clock chosen will be the original oscillating clock (i.e., it will not be multiplied by 4).

PLLOFF pin High when terminating a reset.

PLLOFF pin is held Low, the PLL will not work and the internal

TMP1942CY/CZ-27

Since the PLL is configured as an analog circuit, it requires a certain settling time (a lock-up time) after

it has been activated, as does the oscillator.

The same timer is used for both warm-up and lock-up. The lock-up time must be set using

SYSCR3<LUPTM> so that it satisfies the following relationship:

Lock-up time ≥ warm-up time

By default, the lock-up time is 2

The lock-up timer is initiated as the high-speed oscillator starts warm-up, and the lock-up flag

SYSCR3<LUPTM> remains 1 until the PLL is locked in phase and cleared to 0 upon the completion of

lock-up.

If, for example, the PLL gets out of lock in a standby mode and control which depends on the software' s

execution speed, such as real-time processing, is to be performed, the software must check the lock-up

flag after operation has started (i.e., after warm-up has been completed) to ensure that the clock has

settled, before it starts processing.

On the other hand, various hardware settings and static processing, such as register and memory

initialization, can be executed before the lock-up flag has been cleared.

Note: The LUPFG bit is undefined when the

Precautions to be observed when switching clock gear:

Clock gear switchover is performed by writing a value to SYSCR1<GEAR1:GEAR0>. The clock gear

is not switched immediately after the write: a execution time equal to several clock cycles is required.

Therefore, one or more instructions following the clock gear switchover instruction may be executed

using the old clock gear value. If these instructions need to be executed using the new clock gear value,

insert a dummy instruction (which executes a write cycle only) after the clock gear switchover

instruction.

When using a clock gear, ma ke sure that the prescaler output φTn in eac h peripheral I/O bl ock satisfies

the following relationship:

φTn < fsys/2

16

/input frequency.

PLLOFF pin is Low (the PLL is not used).

TMP1942CY/CZ

For this purpose set the clock-related registers so that φTn is slower than fsys/2.

3.3.6 Standby control unit

If the Halt bit in the TX19 processor core's Config register is set in NORMAL mode, the device enters

one of the standby modes - IDLE, SLEEP or STOP - as determined by the contents of

SYSCR2<STBY1:STBY0>. If the Config register's Doze bit is set, the device enters IDLE mode

regardless of the setting of SYSCR2<STBY1:STBY0>.

Features of the IDLE, SLEEP and STOP modes are described below.

1) IDLE: In this mode, only the CPU stops.

In the register corresponding to each module there is an IDLE mode run/stop setup bit for

internal I/O. This allows each m odule t o be s et i ndepe ndent ly to run or st op whil e the devi ce is

in IDLE mode. Table 3.3.3 lists the IDLE setup registers available for each internal I/O

m

odule.

TMP1942CY/CZ-28

TMP1942CY/CZ

Table 3.3.3 IDLE Mode Internal I/O Setup Registers

Internal I/O IDLE Mode Setup Register

TMRA01 TA01RUN<I2TA01>

TMRA23 TA23RUN<I2TA23>

TMRA45 TA45RUN<I2TA45>

TMRA67 TA67RUN<I2TA67>

TMRA89 TA89RUN<I2TA89>

TMRAAB TAABRUN<I2TAAB>

TMRB0 TB0RUN<I2TB0>

TMRB1 TB1RUN<I2TB1>

TMRB2 TB2RUN<I2TB2>

TMRB3 TB3RUN<I2TB3>

TMRB4 TB4RUN<I2TB4>

TMRB5 TB5RUN<I2TB5>

TMRB6 TB6RUN<I2TB6>

TMRB7 TB7RUN<I2TB7>

TMRB8 TB8RUN<I2TB8>

TMRB9 TB9RUN<I2TB9>

TMRBA TBARUN<I2TBA>

TMRBB TBBRUN<I2TBB>

TMRBC TBCRUN<I2TBC>

TMRBD TBDRUN<I2TBD>

SIO0 SC0MOD1<I2S0>

SIO1 SC1MOD1<I2S1>

SIO3 SC3MOD1<I2S3>

SIO4 SC3MOD1<I2S4>

SIO5 SC4MOD1<I2S5>

SBI SBI0BR1<I2SBI0>

A/D converter ADMOD1<I2AD>

WDT WDMOD<I2WDT>

Note 1: In Halt mode (entered when the Halt bit in the Config Register is set), the TX19 processor

core stops processor operation while maintaining the pipeline status. Since it does not

respond to requests for control of the bus from interna l DMA, it retains control of the bus.

Note 2: In Doze mode (entered when the Doze bit in the Config Register is set), the TX19 processor

core stops processor operation while maintaining the pipeline status. In this mode, it can

respond to requests for control of the bus from devices extern al to the processor core.

2) SLEEP: Only the internal low-speed oscillator, timer for real-time clock, 2-phase pulse input counter,

and KWUP (dynamic pull-up) operate.

3) STOP: The CPU runs with the low-spee d clock. The INTC, timer for real-time clock, WDT, 2-phase

pulse input counter, KWUP (dynamic pull-up), PIO, and EBIF can operate. Operation of other

peripheral functions is not guaranteed.

4) SLOW: All of the internal circuits stop.

TMP1942CY/CZ-29

TMP1942CY/CZ

(1) Operating status in each mode

Table 3.3.4 Operating Status in Each Mode

Operation Mode Operating Status

NORMAL The TX19 processor core and peripheral I/O both operate at the maximum frequency.

IDLE (Halt) The TX19 processor core, INTC, timer for real-time clock, WDT, 2-phase pulse input counter,

KWUP (dynamic pull-up), PIO, and EBIF operate with the low-speed clock.

IDLE (Doze) Processor operation stops and peripheral I/O operates as specified.

SLEEP Processor operation stops. Only the internal low-speed oscillator, timer for real-time clock,

STOP Processor and peripheral I/O operation stops completely.

2-phase pulse input counter, and KWUP (dynamic pull-up) operate (fs).

(2) CG operation in each mode

Table 3.3.5 CG Status in Each Operating Mode

Clock Source Mode Oscillator PLL Clock Supply to Peripheral I/O Clock Supply to the CPU

Resonator

External input

NORMAL ○ ○ ○ ○

SLOW ○ × Partially supplied (Note) ○

IDLE (Halt) ○ ○ Selectable ×

IDLE (Doze) ○ ○ Selectable ×

SLEEP fs only × Timer for real-time clock, 2-phase pulse

input counter, and dynamic pull-up

STOP

NORMAL × ○ ○ ○

SLOW × × Partially supplied(Note) ○

IDLE (Halt) × ○ Selectable ×

IDLE (Doze) × ○ Selectable ×

SLEEP × × Timer for real-time clock, 2-phase pulse

STOP

× × × ×

input counter, and dynamic pull-up

× × × ×

×

×

Note: This includes the INTC, EBIF (external bus interface), I/O ports, WDT, and timer for real-time clock.

(3) Operation of circuit blocks in each mode (○: Operating, ×: Idle)

Table 3.3.6 Circuit Block Operating Status in Each Mode

Circuit Block Clock Source IDLE (Doze) IDLE (Halt) SLEEP STOP

TX19 processor core

DMAC

INTC

EBIF

External bus right

PIO

DA

ADC

SIO

I2C

Timer counter

WDT

2-phase pulse input counter

Dynamic pull-up

Timer for real-time clock

CG

×

○

○

○

○

fsys

Fsys/fs

Fs ○ ○ ○

fs ○ ○ ○

⎯ ○ ○ ○ ×

○

○

Can be selected to run or stop for

each module independently.

×

×

○

○

○

×

○

×

×

×

×

×

×

× (*1)

×

×

×

×

×

(fs only)

×

×

×

×

×

×

× (*1)

×

×

×

×

×

×

×

×

*1: DAC output is controlled with the OP bit for each channel.

TMP1942CY/CZ-30

TMP1942CY/CZ

(4) Terminating a standby mode

The device can be freed from a standby mode by an interrupt request or a reset. The combination

of the interrupt mask register <CMask15:13> setting and the current standby mode determines

which interrupt source will be used to terminate the standby mode. The interrupt mask register is part

of the Status register in the TX19 processor core's system control coprocessor (CP0). Details are

given in Table 3.3.7.

• T

ermination by an interrupt request

The operation performed when t he device is released from a standby mode by an interr upt request

varies according to the interrupt enable status. If the interrupt level which was set before the device

entered the standby mode is greater than or equal to the value in the interrupt mask register, the

processor services the requested interrupt after exiting the standby mode and then begins executing

instructions starting with the one following the instruction to enter the standby mode (i.e., the

instruction which specified the appropriate Config register bit). If the interrupt request level is less

than the value in the interrupt mask register, the processor immediately begins executing instruct ions

starting with the one following the instruction to enter the standby mode (i.e., the instruction which

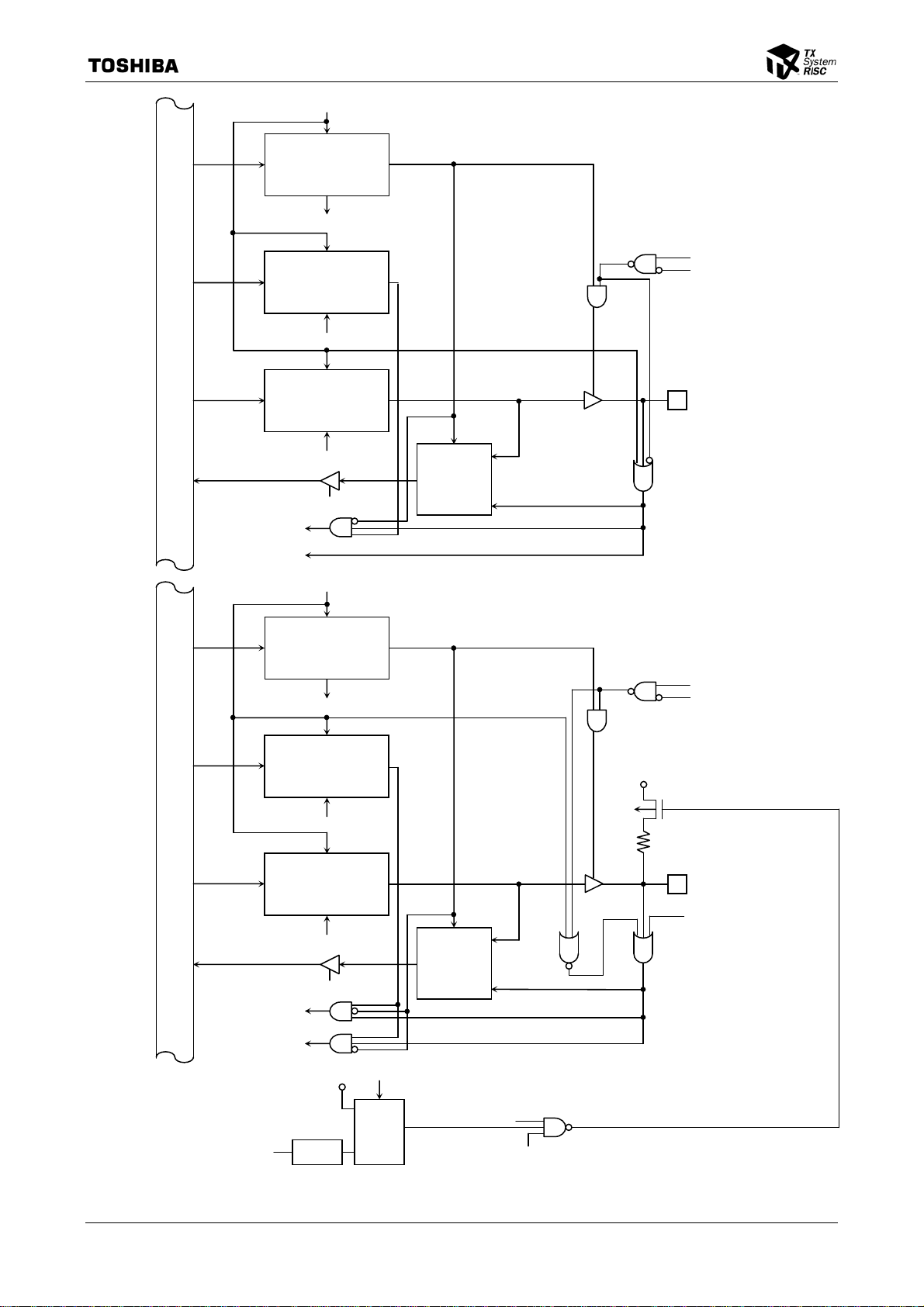

specified the appropriate Config register bit) without servicing the requested interrupt. (The interrupt