東芝 CMOS デジタル集積回路 シリコン モノリシック

TC94A39FAG,TC94A39FB

コントローラ内蔵 1 チップ CD プロセッサ (CD-DX)

TC94A39FAG/FB は、4 ビットマイクロコントローラを内蔵した

デジタルサーボ対応の 1 チップ CD プロセッサです。

コントローラは、LCD ドライバ、4 チャネル 6 ビット AD コンバー

タ、1 系統・2 チャネルの 2 線式・3 線式および UART 対応シリアルイ

ンタフェース、ブザー、20 ビット汎用カウンタ機能、割り込み機能、

8 ビットタイマカウンタを備えています。また、CPU は、4 種類

(16.9344 MHz/75 kHz/32.768 kHz の水晶発振器、CR 発振器) の動

作クロックが選択でき、CD プロセッサとのインタフェースが容易で

す。

CD プロセッサは、CD システムにおける同期分離保護と内挿、

EFM 復調、エラー訂正と補正、サーボ用デジタルイコライザおよび

サーボコントロール回路を内蔵しています。さらに、1 ビット DA コ

ンバータを内蔵し、デジタルサーボ用ヘッドアンプ TA2157F/FN と

の組み合わせで、完全無調整でかつ非常にシンプルに CD プレーヤ

システムを構成できます。

このため、カー用・ラジオカセット用の CD システムに適していま

す。

特

特 長長長長

特特

TC94A39FAG

TC94A39FB

TC94A39FAG/FB

· CMOS 構造 LCD ドライバ・4 ビットマイクロコントローラ内蔵の

1 チップ CD プロセッサ

· 動作電源電圧 CD 動作時: V

CD オフ時: VDD = 1.8~3.6 V (CPUのみ動作時)

· 消費電流 CD 動作時: IDD = 30 mA (標準)

CD オフ時: I

CD オフ時: IDD = 50 µA (CD スタンバイモード時、75 kHz 水晶発振動作、CPU 動作)

· 動作温度範囲 Ta = −40~85°C

· 外囲器 LQFP/QFP-64 (0.5/0.65 mm ピッチ、1.4 mm 厚)

2

PROM TC94AE29FAG/FB

· E

= 3.0~3.6 V (標準 3.3 V)

DD

= 1.5 mA (CD スタンバイモード時、水晶 16.9344 MHz 動作、CPU 動作)

DD

質量

LQFP64-P-1010-0.50 : 0.32 g (標準)

QFP64-P-1212-0.65 : 0.45 g (標準)

1

2003-01-14

TC94A39FAG/FB

4 ビットマイクロコントローラ部

ビットマイクロコントローラ部

ビットマイクロコントローラ部ビットマイクロコントローラ部

· プログラムメモリ (ROM) : 16 ビット ´ 8 k ステップ

· データメモリ (RAM) : 4 ビット ´ 512 ワード

· 命令実行時間 : 1.42 ms, 40 ms, 91.6 ms, Tosc ´ 3 (すべて一語命令)

· 水晶発振周波数 : 16.9344 MHz, 75 kHz, 32.768 kHz, CR 発振周波数

· スタックレベル : 16 レべル

· AD コンバータ : 6 ビット、4 チャネル

· LCD ドライバ : 1/4 デューティ・1/2 バイアス方式または 1/3 バイアス方式、最大 64 セグメント

· I/O ポート : CMOS I/O ポート: 最大 26 本,

Nch オープンドレイン I/O ポート: 最大 3 本 (5.5 V 耐圧)

· タイマカウンタ : 8 ビット (タイマモード、パルス幅検出・測定機能)

· 汎用カウンタ : 20 ビット, 入力アンプ内蔵, 0.1~20 MHz, Vin = 0.2 Vpp 最小

· シリアルインタフェース : 1 系統・2 チャネルの 3 線式と 2 線式および UART に対応

· ブザー : 0.75, 1, 1.5, 3 kHz (4 種類)、連続・単発・10 Hz 断続・10 Hz 断続 1 Hz 間隔の 4 モード

· 割り込み : 外部 1、内部 3 (CD サブシンク同期、シリアルインタフェース、8 ビットタイマ)

· バックアップモード : 4 種類のバックアップモード

CD スタンバイ (CD プロセッサ停止)、クロックストップ (発振停止)、

ハードウエイト (水晶発振のみ動作)、ソフトウエイト (CPU 間欠動作)

· リセット機能 : パワーオンリセット回路、電源検出回路内蔵 (検出電圧 = 1.5 V 標準)

CD プロセッサ部

プロセッサ部

プロセッサ部プロセッサ部

· 同期パターン検出、同期信号保護および内挿動作が確実です。

· EFM 復調回路、サブコード復調回路を内蔵しています。

· CIRC 訂正理論式を用い、高訂正能力を持っています。C1 訂正: 2 重、C2 訂正: 4 重

· ジッタ吸収能力は±6 フレームです。

· 16 KB RAM を内蔵しています。

· デジタルアウト回路を内蔵しています。

· L/R 独立デジタルアッテネート回路を内蔵しています。

· オーディオ出力はバイリンガルに対応しています。

· オーディオ出力は 32f

· サブコード Q データはリードタイミングフリーです。また、オーディオデータとの同期出力も可能です。

· データスライス回路、アナログ PLL (無調整 VCO 採用) 回路を内蔵しています。

· フォーカスサーボ、トラッキングサーボにおけるループゲイン、オフセット、バランスの自動調整が可能です。

· RF ゲイン自動調整回路を内蔵しています。

· 位相補償用デジタルイコライザを内蔵しています。

· デジタルイコライザ用係数 RAM を内蔵しており、各種ピックアップへの対応が可能です。

· フォーカス、トラッキングサーボコントロール回路を内蔵しています。

· サーチコントロールは、あらゆるモードに対応し高速かつ安定したサーチを実現できます。

· レンズキック、フィードキックは速度制御方式を採用しています。

· ディスクモータの CLV サーボ用 AFC 回路および APC 回路を内蔵しています。

· ディフェクト、ショック対策回路を内蔵しています。

· 8 倍オーバサンプリング・デジタルフィルタと 1 ビット DA コンバータを内蔵しています。

· 1 ビット DA コンバータ用アナログフィルタを内蔵しています。

· 0 データ検出出力回路を内蔵しています。

· 2 倍速動作に対応しています。

, 48fs, 64fs切り替え可能です。

s

注: CD プロセッサのサブコード Q データおよびオーディオデータの出力などはコントローラ専用端子と兼用して

います。プログラムにより 1 端子ごとに機能端子の切り替えが可能です。

2

2003-01-14

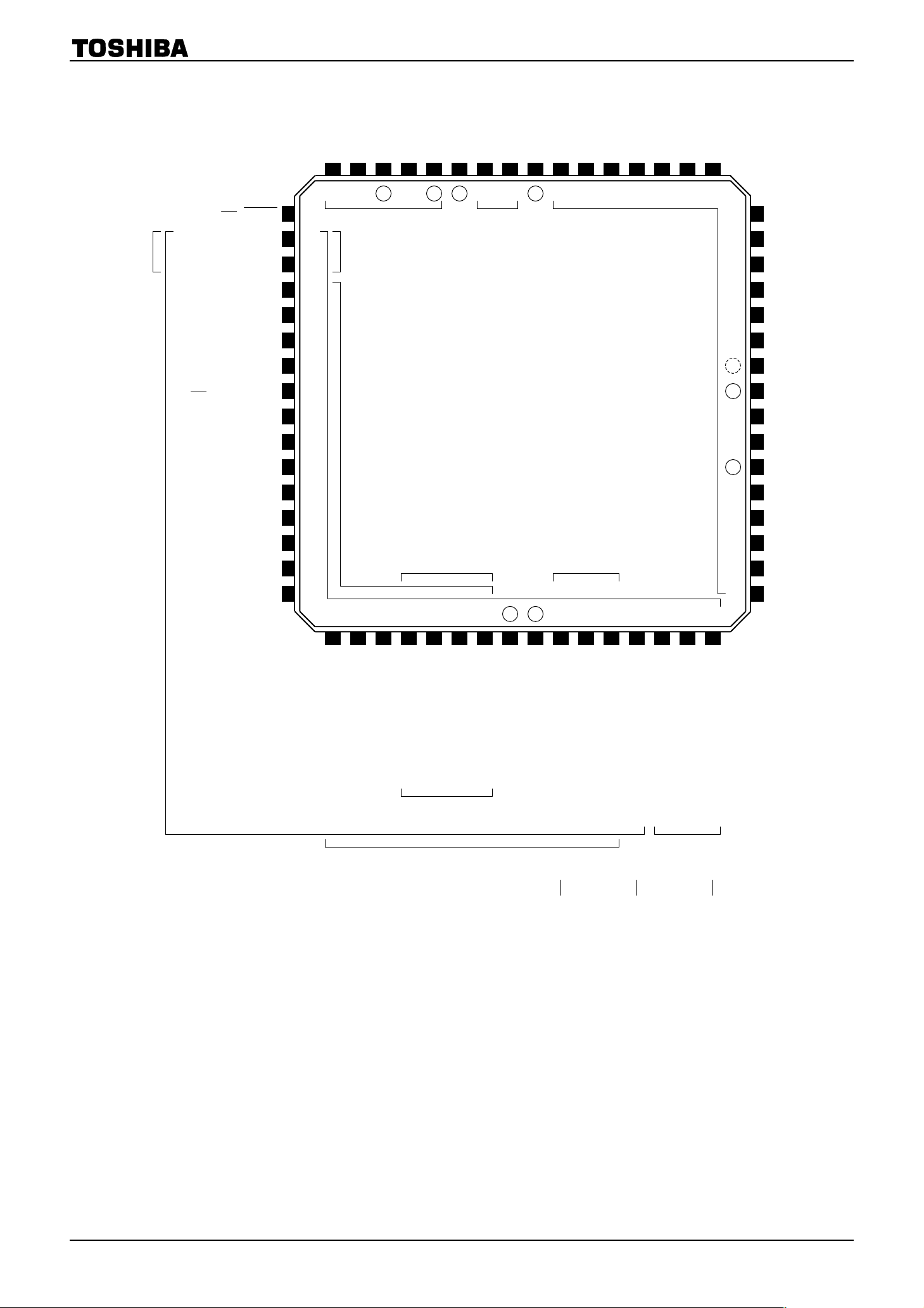

端子接続図

A

A

端子接続図

端子接続図端子接続図

リセット入力

P8-0/MXI/OSC (BRK1)

P8-1/MXO (BRK2)

RESET

RO

DD

DV

SS

XI

CV

16.9344 MHz

発振回路

SS

DVR

LO

DV

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

49

50

51

1 bit DAC

75/32.768 kHz/CR

発振回路

DD

XO

CV

DMO

FMO

SEL

TEBC

RFGC

TC94A39FAG/FB

TRO

FOO

32

31

30

TEZI

TEI

SBAD

P2-0/COM1

プルアップ/プルダウン設定可能

P2-1/COM2

P2-2/COM3

P2-3/COM4

TEST/P3-0/S1

P3-1/S2

テストモード入力

P3-2/S3

P3-3/S4

P4-0/S5

P4-1/S6

P4-2/S7

P4-3/S8

P5-0/S9

52

53

54

55

56

57

58

59

60

61

62

63

64

LCD ドライバ (4 ´ 16 = 64セグメント最大)

AD コンバータ

1 2 4 7 10 11 12 13 14 15 16356

LQFP/QFP-64

(0.5/0.65 mmピッチ)

TOP-VIEW

シリアルインタフェース 1

コントローラ専用端子

8 9

29

28

27

26

25

24

23

22

21

CD プロセッサ専用コントロール入出力端子

20

19

18

17

FEI

RFRP

RFZI

V

REF

V

DD

RFI

SLCO

V

SS

VCOF

LPFO

LPFN

TMAX

PDO

SS

DD

MV

MV

P5-1/S10/BCK (BRK3)

P5-2/S11/LRCK (BRK4)

P5-3/S12/AOUT (BRK5)

P6-1/S14/ADin2/IPF (BRK7)

P6-0/S13/ADin1/DOUT (BRK6)

プルアップ/プルダウン設定可能

CMOS I/O ポート (最大 26 本)

CD 機能兼用端子

P6-3/S16/ADin4/CLCK (BRK9)

P6-2/S15/ADin3/SBOK (BRK8)

P1-1/SDIO1/TX1/SFSY (BRK11)

P1-0/SCK1/RX1/CTin/DATA (BRK10)

P1-3/BUZR (BRK13)

P1-2/SI1/SBS Y ( BRK12)

シリアルインタフェース 2

P7-0/SCK2/RX2 (BRK14)

P7-1/SDIO2/TX2 (BRK15)

Nch オープンドレイン

I/O (3本, 5.5 V 耐圧)

P7-2/INTR/SI2 (BRK16)

注: BRK1~BRK16 は、バックアップ状態の解除がポート単位で設定可能。

注: 56 ピンの TEST 端子は、リセット中プルダウンされ、テストモード入力とな

ります。このため、リセット中は “L” レベルを入力または、オープン状態に

設定してください。

周波数カウンタ入力

ブザー出力

割り込み入力

2003-01-14 3

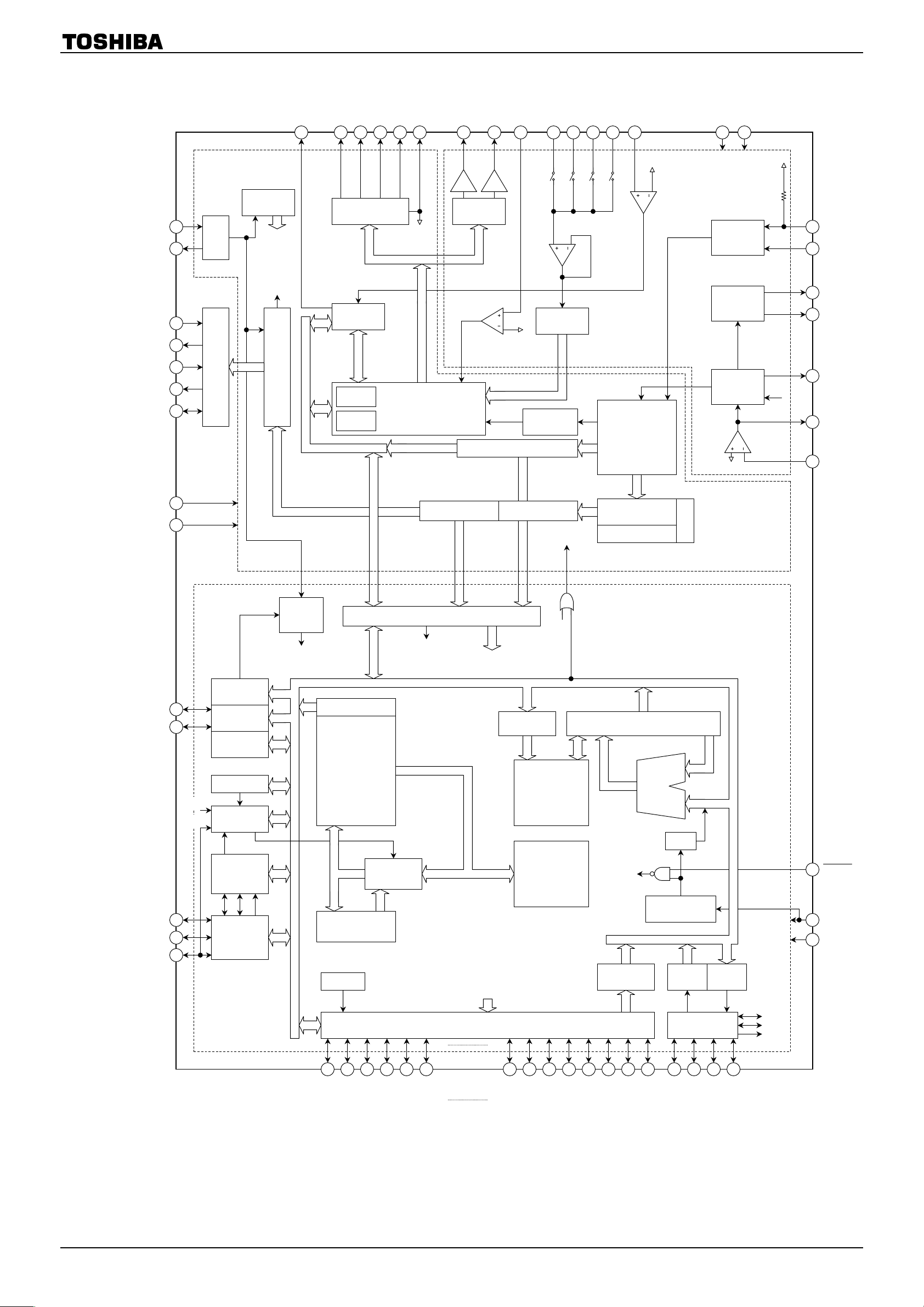

ブロック図

ブロック図

ブロック図ブロック図

TC94A39FAG/FB

FMO

SEL

DMO

TEBC

RFGC

REF

V

TRO

FOO

TEZI

TEI

FEI

SBAD

RFZI

RFRP

V

REF

DD

AV

SS

AV

V

REF

DV

DV

DVR

CV

CV

XO

DD

RO

SS

LO

DD

SS

Clock gene.

XI

X’tal

OSC

LPF

CD clock

ZDET

1 bit DAC

PWM

SERVO

control

ROM

RAM

V

REF

Digital equalizer

Automatic adjustment

circuit

DA

V

REF

Sub code decoder

Digital out Audio out

servo

AD

CLV

CD Reset

Synchronous

guarantee EFM

decode

16 k SRAM

Correction circuit

Data

slicer

PLL

TMAX

VCO

V

REF

V

REF

Address

RFI

SLCO

TMAX

PDO

VCOF

LPFO

LPFN

P8-0/MX1/OSC (BRK1)

P8-1/MXO (BRK2)

P7-0/SCK2/RX2 (BRK14)

P7-1/SDIO2/TX2 (BRK15)

P7-2/INTR/SI2 (BRK16)

SBSY

INTR

CR

OSC

X’tal

OSC

Port8

Timer

Interrupt

cont.

Serial

interface

(SIO)

Port7

MPX

CPU clock

Data Reg (16 bit)

Mask ROM

(16 ´ 8192 Step)

Program

Counter

Stack Reg.

(16Level)

Bias

Micon interface

Reset

SBSY

BCK, LRCK, AOUT, DOUT

IPF, SBOK, CLCK, DATA, SF SY

G-Reg. R/W Buf.

RAM

(4 ´ 512 word)

Instruction

Decoder

BCK, LRCK, AOUT, DOUT, IPF, SB OK,

CLCK, DATA, SFSY , SBSY

Reset

AD

conv.

ALU

F/F

Power on Reset

20 bit

counter

BUZR

RESET

MV

DD

MV

SS

LCD Driver/IO Port2, 3, 4, 5, 6 Port1

P3-1/S2

P2-0/COM1

P2-1/COM2

P2-2/COM3

P2-3/COM4

TEST/P3-0/S1

P5-0/S9

P5-1/S10/BCK (BRK3)

P5-2/S11/LRCK (BRK4)

P5-3/S12/AOUT (BRK5)

P6-1/S14/ADin2/IPF (BRK7)

P6-0/S13/ADin1/DOUT (BRK6)

P6-3/S16/ADin4/CLCK (BRK9)

P6-2/S15/ADin3/SBOK (BRK8)

P1-0/SCK1/RX1/CTin/DATA (BRK10)

P1-2/SI1/SBSY (BRK12)

P1-1/SDIO1/TX1/SFSY (BRK11)

SIO

P1-3/BUZR (BRK13)

2003-01-14 4

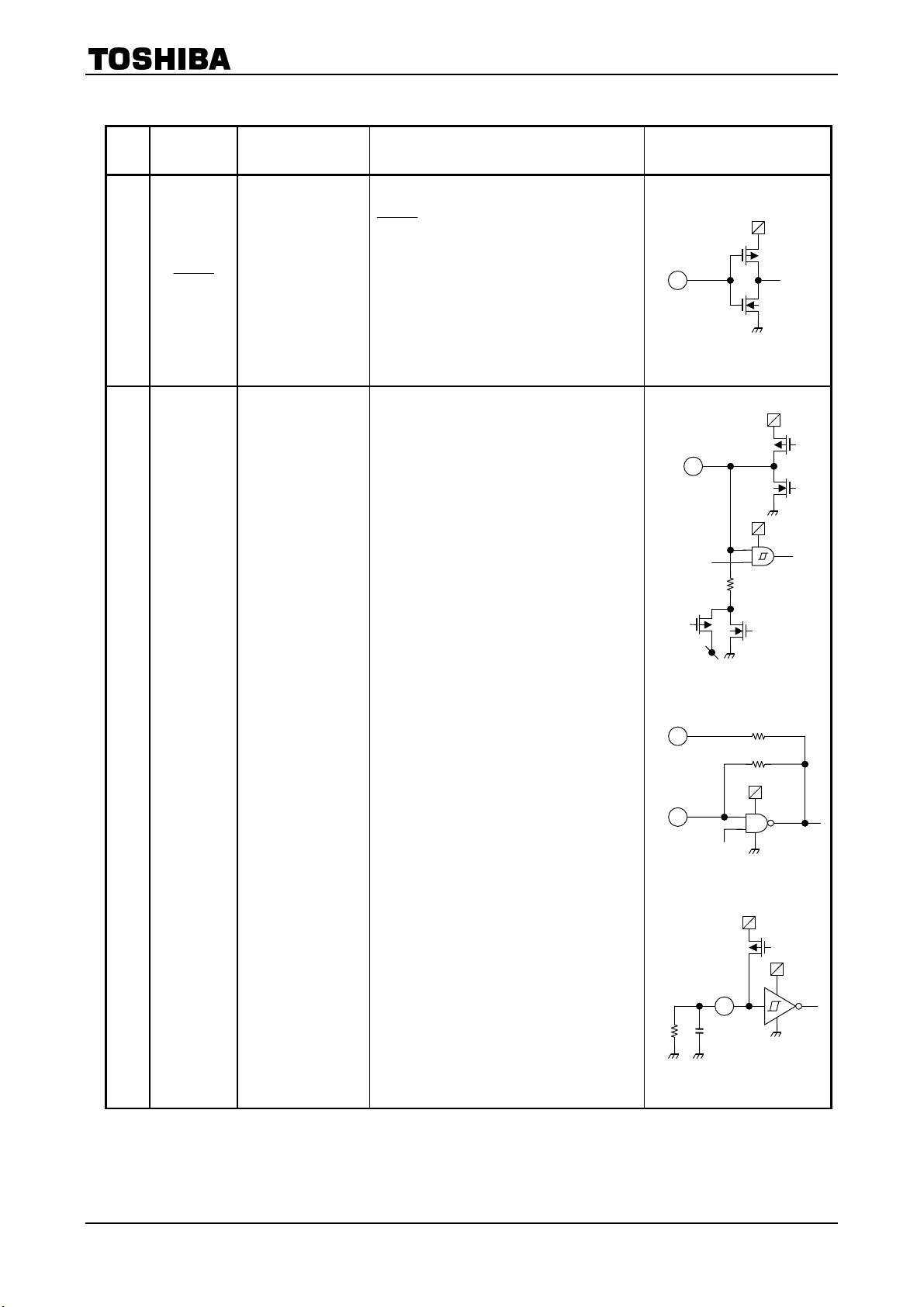

端子説明

端子説明

端子説明端子説明

TC94A39FAG/FB

端子

番号

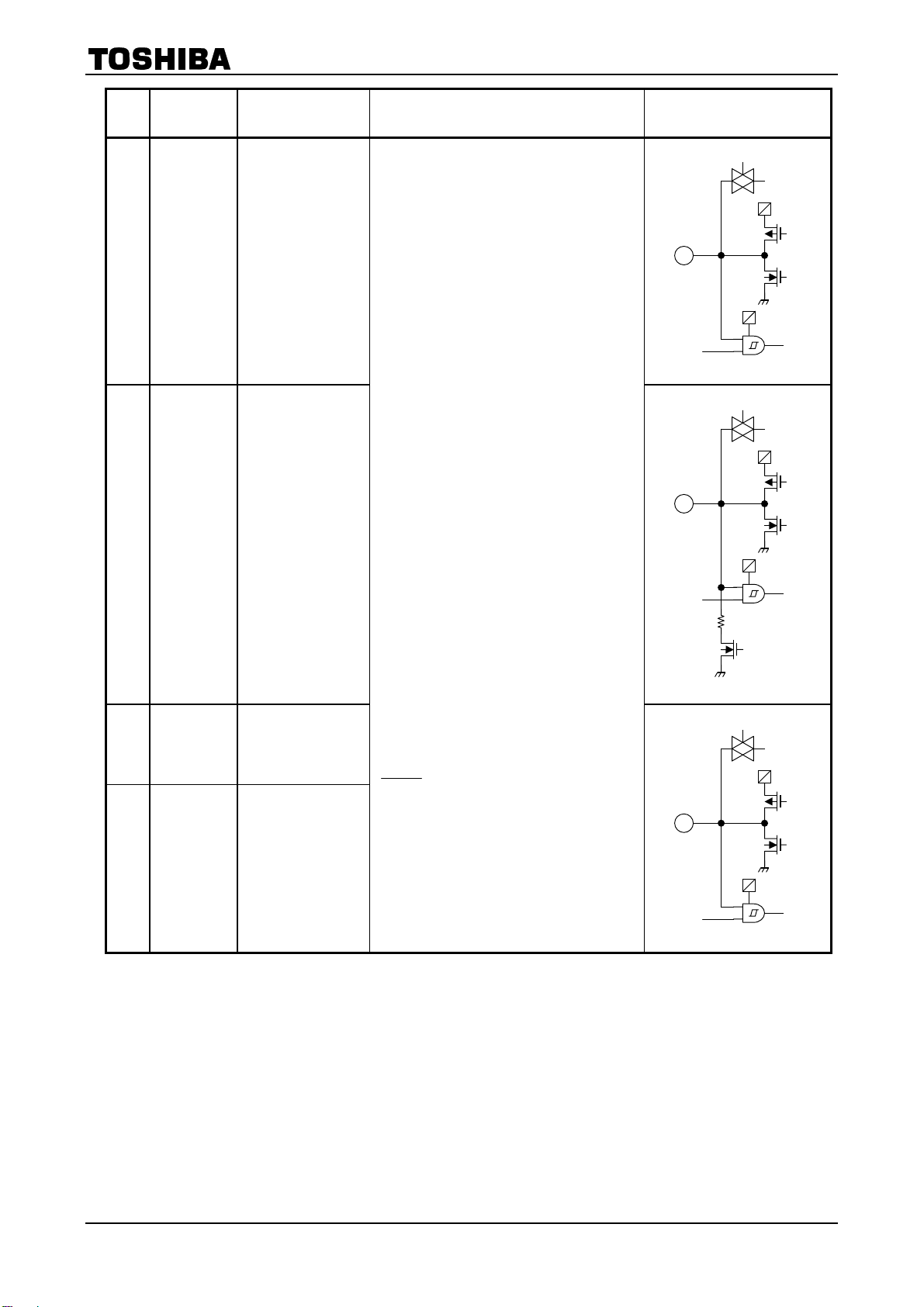

49 RESET リセット入力

50

51

記 号 端 子 名 機 能 ・ 動 作 説 明 備 考

P8-0

/MXI

/OSC

(BRK1)

P8-1

/MXO

(BRK2)

I/O ポート 8-0

/水晶発振器

/CR 発振器

I/O ポート 8-1

/水晶発振器

デバイスのシステムリセット信号入力端子で

す。

RESET が “L” レベルの間リセットがかかり、

“H” レベルになると 16.9344 MHz 水晶発振器

(XI, XO) が動作し、この水晶発振クロックを計

算し、約 50 ms のスタンバイ時間経過後にコン

トローラのプログラムは 0 番地からスタートし

ます。このとき、CD 部はスタンバイ状態となり

ます。

通常は MV

されるとシステムリセットがかかりますので

(パワーオンリセット)、この端子は “H” レベル

に固定して使用します。

2 ビット CMOS I/O ポートです。

1 ビットごとに入力/出力の設定ができます。

I/O ポートの入力を設定したとき、1端子ごとに

入力をプルアップまたはプルダウン状態に設定

することができます。さらに、クロックストッ

プモードおよびウエイトモードのバックアップ

解除許可に設定すると、その入力の変化でバッ

クアップ解除を行うことができます。

これらの端子は、プログラムにより 75 kHz また

は 32.768 kHz 専用水晶発振器に、P8-0端子は

CR 発振器としても使用できます。これらのク

ロックは、コントローラ動作および周辺機器の

クロックに使用されます。システムリセット後

は、コントローラ動作および周辺機器のクロッ

クは 16.9344MHz 水晶発振器 (XI, XO) のク

ロックが選択され、プログラムにより、発振器

設定・コントローラクロックへ切り替えます。発

振器設定時、CKSTP 命令実行中は発振を停止し

ます。

(注) CR 発振器設定時、P8-1 端子は I/O ポート

として使用できます。

(注) バックアップ解除設定は、2 端子が同時に設

定されます。

(注) 水晶発振子は起動特性の良いものを使用し

てください。

(注) システムリセット後は I/O ポートの入力状

態に設定されます。

(注) コントローラクロックへの切り替えは、発

振器設定し、動作が安定した後に行ってく

ださい。

に 0 V ® 1.8 V 以上の電圧が供給

DD

入力命令

R

IN1

MV

DD

(I/O ポート設定時)

MXO

MXI

(水晶発振器設定時)

OSC

MV

MV

R

R

SS

SS

out2

fXT2

MV

MV

MV

MV

MV

DD

SS

DD

MV

DD

DD

MV

DD

DD

R

C

(P8-0 CR 発振器設定時)

5

2003-01-14

MV

SS

TC94A39FAG/FB

端子

番号

52

53

54

55

56

57

58

59

60

61

62

63

記 号 端 子 名 機 能 ・ 動 作 説 明 備 考

24ビット CMOS I/Oポートと 3ビットの N チャ

ネルオープンドレイン I/O ポートです。

1 ビットごとに入力/出力の設定ができます。I/O

P2-0/COM1

P2-1/COM2

P2-2/COM3

P2-3/COM4

TEST

/P3-0/S1

P3-1/S2

P3-2/S3

P3-3/S4

P4-0/S5

P4-1/S6

P4-2/S7

P4-3/S8

I/O ポート 2

/LCD コモン出力

テスト入力

/I/O ポート 3-0

/LCD セグメント出力

I/O ポート 3

/LCD セグメント出力

I/O ポート 4

/LCD セグメント出力

ポートの入力を設定したとき、P6-0~P6-3 端子

は 1 端子ごとに入力をプルアップまたはプルダ

ウン状態に設定することができます。また、P5-1

(BRK3)~P7-2 (BRK16) 端子は I/O ポートの入力

状態およびバックアップ解除許可状態 (ポート

単位で設定) に設定するとその入力の変化でク

ロックストップモードおよびウエイトモードの

バックアップ状態を解除することができます。

さらに、P7-0~P7-2端子は、Nチャネルオープ

ンドレイン構造の I/O ポートで、5.5 V までの印

加が可能です。

I/O ポート 2~6 は、プログラムにより LCD ドラ

イバ出力端子に切り替えることができます。

COM1~COM4 端子が LCD パネルへのコモン信

号出力、S1~S16端子がセグメント信号出力で

す。COM1~COM4 と S1~S16 とのマトリクスで

最大 64 セグメントの表示ができます。

LCDoff ビットに “0” を設定すると、これら

COM1~COM3 および S1~S4 の 8 本の端子はす

べて LCD 出力端子となります。S5~S16 は 1 端

子ごとに I/O ポートとセグメント出力に切り替

えることができます。

駆動方式は 1/4 デューティ・1/2 バイアス方式

(フレーム周波数 62.5 Hz) と 1/4 デューティ・1/3

バイアス方式 (フレーム周波数 125 Hz) の 2 種

類が選択できます。

1/2 バイアス方式設定時は、コモン出力は MV

1/2MV

力は MV

また、1/3 バイアス方式設定時には、コモン出力

およびセグメント出力は、MV

2/3MV

システムリセットおよびクロックストップ実行

解除後は非選択波形 (バイアス電圧) が出力さ

れ、DISP OFF ビットに “0” をセット後コモン

信号が出力されます。

TEST/P3-0/S1 端子は、システムリセット中

(

ド入力となります。このため、リセット中、こ

の端子はオープンまたは “L” レベルを入力して

ください。

P5-1~P6-3, P1-0~P1-2 端子は、1 端子ごとに CD

プロセッサ専用端子に切り替えることができま

す。CD プロセッサ機能は次のとおりです。

, GNDの三値レベルが、セグメント出

DD

, GNDの二値レベルが出力されます。

DD

, GNDの四値レベルで出力されます。

DD

RESET

= “L”) はプルダウンされ、テストモー

(次ページにつづく)

, 1/3MVDD,

DD

DD

入力命令

入力命令

,

入力命令

R

IN2

LCD 電圧

MV

LCD 電圧

MV

リセット信号

MVSS

LCD 電圧

MV

MV

DD

MV

DD

MV

DD

DD

DD

DD

6

2003-01-14

TC94A39FAG/FB

A

端子

番号

64 P5-0/S9

1

2

3

4

5

6

7

記 号 端 子 名 機 能 ・ 動 作 説 明 備 考

P5-1/S10

/BCK

(BRK3)

P5-2/S11

/LRCK

(BRK4)

P5-3/S12

/AOUT

(BRK5)

P6-0/S13

/ADin1

/DOUT

(BRK6)

P6-1/S14

/ADin2

/IPF

(BRK7)

P6-2/S15

/ADin3

/SBOK

(BRK8)

P6-3/S16

/ADin4

/CLCK

(BRK9)

I/O ポート 5-0

/LCD セグメント出力

I/O ポート 5

/LCD セグメント出力

/CD プロセッサ機能

I/O ポート 6

/LCD セグメント出力

/CD プロセッサ機能

●BCK: ビットクロック出力端子です。

1倍速時: 32 f

●LRCK: LR チャネルクロック出力端子です。L

1倍速時: 44.1 kHz

●AOUT: オーディオデータ出力端子です。

●DOUT: デジタルアウト出力端子です。2 倍速

●IPF: 補正フラグ出力端子です。AOUT出力

●SBOK: サブコード Qデータの CRCC判定結果

●CLCK: サブコード P~W データ読み取り用ク

●DATA: サブコード P~W データ出力端子です。

●SFSY: 再生系フレームシンク信号出力端子で

●SBSY: サブコードブロックシンク出力端子で

(注) CD プロセッサ部の動作が不定状態で割込

P6-0~P6-3端子は内蔵 6 ビット 4 チャネル AD

コンバータアナログ入力を兼用しています。

内蔵の AD コンバータは、逐次比較方式で変換時

間は 16.9344 MHz 水晶クロック使用時は 242

ms、75 kHz 水晶使用時は 7 命令サイクル (280

ms)です。プログラムにより必要な端子を 1 ビッ

ト単位で AD アナログ入力に設定できます。基準

電圧には内部電源 (MV

また、P6-0~P6-3端子は I/O ポートの入力を設定

したとき、1 端子ごとに入力をプルアップまたは

プルダウン状態に設定することができます。

32/48/64 f

可能です。

チャネルの時 “L”、R チャネルのとき

“H” が出力されます。出力極性は CD

コマンドにより反転可能です。

MSB/LSBファーストはCDコマンドに

より選択可能です。

まで出力可能です。(CP-1201 準拠)

が C2 訂正出力において訂正不能シン

ボルのとき “H” が出力されます。

(別称 “C2PO”)

出力端子です。判定結果 OK のとき、

“H” が出力されます。

ロック入出力端子です。入出力極性は

CD コマンドにより選択可能です。

す。

す。サブコードシンクが検出されたと

き、S1 の位置で “H” が出力されます。

コントローラ側で CD 割込みが許可さ

れ、SBSY 信号の立ち下がりで割込み

が発生し、プログラムは 2 番地にジャ

ンプします。

み許可をしないでください。

を CD コマンドにより選択

s

= 1.4112 MHz

s

) を使用します。

DD

(次ページにつづく)

入力命令

入力命令

解除許可

入力命令

解除許可

DD

LCD 電圧

MV

DD

MV

DD

LCD 電圧

MV

DD

MV

DD

D 入力

LCD 電圧

MV

DD

MV

DD

R

IN1

MVSS MV

7

2003-01-14

TC94A39FAG/FB

端子

番号

10

11

12

13

14

15

16

記 号 端 子 名 機 能 ・ 動 作 説 明 備 考

P1-0 端子は汎用カウンタ入力を兼用していま

す。入力周波数は、0.1~20 MHzで入力アンプを

内蔵し、C 結合小振幅で動作します。汎用カウ

ンタは 20 ビットのカウンタで 1、4、16、64 ms

(75 kHz 水晶使用時) のゲート時間を選択でき、

20 ビットのデータをそのままメモリに取り込む

ことができます。さらに、マニュアルモードを

使用して命令によるゲートのオン/オフが可能で

す。

P1-0~P1-2端子および P7-0~P7-2端子はシリア

ルインタフェース回路 (SIO) の入力/出力端子

を兼用しています。

SIO は 2 線式と 3 線式および UART に対応した

シリアルインタフェースです。シリアルインタ

フェース回路は 1 系統で、CMOS 構造の I/O 入

出力端子 (SCK1/RX1, SDIO1/TX1, SI1) と N

チャネルオープンドレイン構造 (5.5 V までの印

加が可能) の I/O 入出力端子 (SCK2/RX2,

SDIO2/TX2, SI2) を選択することができます。

シリアルインタフェース回路は、クロックエッ

ジ選択、シリアルクロック入出力選択、クロッ

ク周波数選択機能などを備えているため、さま

ざまな LSI のコントロールおよびコントローラ

間の通信が容易にできます。また、SIO の割り

込みを許可すると、シリアル動作の終了後割り

込みが発生し、プログラムは 4 番地にジャンプ

します。

P1-3 端子はブザー出力を兼用しています。

ブザー出力は、0.75, 1, 1.5, 3 kHz (75 kHz ク

ロック使用時) の周波数 4 種類が選択でき、その

周波数を連続・単発・10 Hz断続・10 Hz 断続 1 Hz

間隔の 4 モードで出力させることができます。

P7-2 端子は外部割り込み入力を兼用していま

す。割り込み機能が許可され、この入力に

1.65~4.96 ms 以上 (75 kHz クロック使用時

13.3~40 ms) のパルスが入力されると割り込み

が発生し、プログラムは 1 番地にジャンプしま

す。入力割り込みは入力の論理および立ち上が

り/立ち下がりエッジが選択できます。また、こ

の入力は内部 8 ビットタイマカウンタのクロッ

クゲート信号入力として使用でき、入力パルス

幅の測定・検出が可能です。

(注) バックアップ解除設定は、ポート単位で許

可・禁止が設定されます。

(注) システムリセット後は I/O ポートの入力状

態に設定されます。

(注) 水晶 32.768 kHz または CR 発振器使用時、

汎用カウンタはタイマとして使用します。

入力命令

解除許可

(I/O ポート設定時)

CTin

(P1-0 汎用カウンタ入力時)

入力命令

解除許可

P1-0/SCK1

/RX1

/CTin

/DATA

(BRK10)

P1-1/SDIO1

/TX1

/SFSY

(BRK11)

P1-2/SI1

/SBSY

(BRK12)

P1-3/BUZR

(BRK13)

P7-0/SCK2

/RX2

(BRK14)

P7-1/SDIO2

/TX2

(BRK15)

P7-2/INTR

/SI2

(BRK16)

I/O ポート 1-0

/シリアルクロック

入出力 1

/シリアル受信

データ 1

/カウンタクロック

入力

/CD プロセッサ機能

I/O ポート 1-1

/シリアルデータ

入出力 1

/シリアル送信

データ 1

/CD プロセッサ機能

I/O ポート 1-2

/シリアルデータ

入力 1

/CD プロセッサ機能

I/O ポート 1-3

/ブザー出力

I/O ポート 7-0

/シリアルクロック

入出力 2

/シリアル受信

データ 2

I/O ポート 7-1

/シリアルデータ

入出力 2

/シリアル送信

データ 2

I/O ポート 7-1

/割り込み入力

/シリアルデータ

入力 2

MV

DD

MV

SS

MV

DD

R

fIN

MV

DD

MV

SS

MV

SS

MV

DD

8

2003-01-14

TC94A39FAG/FB

A

A

端子

番号

記 号 端 子 名 機 能 ・ 動 作 説 明 備 考

8 MVDD

9 MVSS

17 PDO

コントローラ部

電源供給端子

コントローラ部の電源供給端子です。

通常、V

CPU のみ動作時 (75 kHz/32.768 kHz 発振器使

用時) には、V

です。

= 3.0~3.6 V の電圧を供給します。

DD

= 1.8~3.6 V の範囲で動作可能

DD

バックアップ状態 (CKSTP 命令実行時) では低

消費電流 (10 mA以下) となり、電源電圧を 1.0 V

まで下げることができます。

この端子に 0 V ® 1.8 V 以上の電圧がかかると

デバイスにはシステムリセットがかかり、プロ

グラムは 0 番地からスタートします。(パワーオ

ンリセット)

(注) パワーオンリセット動作のために、デバイ

スの電源電圧の立ち上がり時間は 1~50 ms

の間でご使用ください。

(注) バックアップ電流は、CV

のトータル電流値です。

/MVDD/DV

DD

DD

EFM 信号と PLCK 信号との位相誤差信号を出力

する端子です。

4 値出力: AV

/ハイインピーダンス

DD

/V

/AVSS

REF

R

out4

MV

DD

MV

SS

AV

DD

V

SS

TMAX検出結果出力端子です。

18 TMAX

19 LPFN

20 LPFO

CD プロセッサ

制御入出力

所定周期より長い・・・“H” レベル (AV

所定周期より短い・・・“L” レベル (AV

所定周期内・・・ハイインピーダンス

PLL 系のローパスフィルタ用アンプの反転入力

端子です。

PLL 系のローパスフィルタ用アンプの出力端子

です。

21 VCOF VCO フィルタ端子です。

22 AVSS

アナログ系のグラウンド端子です。 ¾

DD

SS

V

REF

AV

DD

)

)

V

SS

AV

DD

V

REF

LPFN

LPFO

V

REF

VCO

VCOF

9

2003-01-14

TC94A39FAG/FB

端子

番号

23 SLCO

24 RFI

記 号 端 子 名 機 能 ・ 動 作 説 明 備 考

データスライスレベル生成用 DAC 出力端子で

す。

RF 信号入力端子です。Zin1 は CD コマンドによ

り選択が可能です。

アナログ系の電源供給端子です。通常、V

25 AVDD

3.0~3.6 V の電圧を供給します。CD スタンバイ

時にはこの電源はオフ状態にしてください。

アナログ基準電源端子です。通常、AV

26 V

REF

(V

= 3.3 V 時、V

DD

します。

= 1.65 V) の電圧を供給

REF

27 RFZI RFRP信号ゼロクロス用入力端子です。

CD プロセッサ

28 RFRP RF リップル信号入力端子です。

制御入出力

29 FEI フォーカスエラー信号入力端子です。

DD

=

DD

の 1/2

RFI

SLCO

RFZI

V

REF

RFRP

FEI

Z

in1

V

REF

AV

DD

DAC

¾

¾

AV

DD

Z

in2

1 kW typ. 32 kW typ.

AV

DD

30 SBAD サブビーム加算信号入力端子です。

31 TEI

トラッキングエラー入力端子です。トラッキン

グサーボオン時に取り込まれます。

32 TEZI トラッキングエラー・ゼロクロス入力端子です。

33 FOO フォーカスイコライザ出力端子です。

34 TRO

トラッキングイコライザ出力端子です。

SBAD

TEI

TEZI

V

Z

in2

REF

1 kW typ. 32 kW typ.

AVDD

R

out3

AV

AV

AV

DD

DD

~

SS

10

2003-01-14

TC94A39FAG/FB

端子

番号

記 号 端 子 名 機 能 ・ 動 作 説 明 備 考

35 RFGC

36 TEBC

37 SEL

38 FMO

CD プロセッサ

制御入出力

RF振幅調整制御信号出力端子です。3値の PWM

信号を出力します。(PWM キャリア = 88.2 kHz)

トラッキングバランス制御信号出力端子です。3

値の PWM 信号を出力します。

(PWM キャリア = 88.2 kHz)

APC 回路オン/オフ信号出力端子です。

レーザオン時、ハイインピーダンスとなります。

フィードイコライザ出力端子です。3 値の PWM

信号を出力します。

(PWM キャリア = 88.2 kHz)

AV

DD

R

out3

V

REF

AV

DD

AV

DD

R

out3

39 DMO

40 CVDD

43 CVSS

41 XO

42 XI

電源供給端子

水晶発振器端子

ディスクイコライザ出力端子です。3 値の PWM

信号を出力します。

(PWM キャリア = 88.2 kHz)

CD プロセッサ部のロジックおよび、16.9344

MHz 専用水晶発振器の電源供給端子です。通常、

・MVSS端子と共通に接続します。CD スタ

MV

DD

ンバイ時には低消費電流となります。

CD プロセッサ専用水晶発振器の入出力端子で

す。16.9344 MHz を接続します。このクロック

は CD プロセッサおよびコントローラのシステ

ムクロックとして使用します。システムリセッ

ト後、コントローラ側のシステムクロックには

このクロックが供給され CPU が起動します。

プログラムにより水晶発振器を停止させること

ができます。通常、コントローラ用クロックに

75/32.768 kHz または CR 発振器を選択したと

き、CD プロセッサのオフ時にはプログラムによ

りこの発振器を停止させます。

(注) コントローラシステムクロックをコント

ローラ用クロックから CD 用水晶発振へ切

り替える場合、CD 用水晶発振器が十分安定

した状態で切り替えてください。

XO

XI

V

REF

CV

DD

CV

SS

R

out1

R

fXT1

CV

DD

CV

SS

11

2003-01-14

TC94A39FAG/FB

R

端子

番号

44 DVDD

45 RO Rチャネルデータ正転出力端子です。

46 DVSS DA コンバータ用グラウンド端子です。

47 LO Lチャネルデータ正転出力端子です。

48 DVR

記 号 端 子 名 機 能 ・ 動 作 説 明 備 考

DA コンバータ用電源端子です。CD スタンバイ

時には低消費電流となります。

オーディオ DAC 出力

リファレンス電圧端子です。

DV

RO/LO

DVSS

DVDD

DV

DD

V

SS

12

2003-01-14

最大定格

最大定格

最大定格最大定格

(Ta ==== 25°C, CVDD ==== DVDD ==== AVDD ==== MVDD)

項目 記号 定格 単位

TC94A39FAG/FB

電源電圧 V

CVDD端子 V

入力電圧

許容損失

動作温度 T

保存温度 T

注 1: V

; 41, 42 端子

IN1

V

; 17~39 端子 (ただし、電源印加端子は除く)

IN2

V

; 45, 47, 48 端子

IN3

V

; 1~13, 49~64 端子 (ただし、電源印加端子は除く)

IN4

V

; 14, 15, 16 端子

IN5

AVDD端子 V

DVDD端子 V

(注 1)

MVDD端子 V

V

TC94A39FAG 400

TC94A39FB

DD

-0.3~CVDD + 0.3

IN1

-0.3~AVDD + 0.3

IN2

-0.3~DVDD + 0.3

IN3

-0.3~MVDD + 0.3

IN4

-0.3~6.0

IN5

PD

-40~85 °C

opr

stg

-0.3~4.0 V

V

mW

500

-65~150 °C

13

2003-01-14

電気的特性

>

電気的特性

電気的特性電気的特性

(特に指定がない場合

特に指定がない場合, Ta ==== 25°C, CVDD ==== MVDD ==== DVDD ==== AVDD ==== 3.3 V, V

特に指定がない場合特に指定がない場合

TC94A39FAG/FB

==== 1.65 V)

REF

項目 記号

V

DD1

動作電源電圧範囲

メモリ保持電圧範囲 MVHD ¾ 水晶発振停止 (CKSTP 命令実行時) (注 4) 1.0 ~ 3.6 V

動作電源電流

(注 2)

メモリ保持電流 MIHD ¾

発振周波数

発振周波数誤差 Df

水晶発振開始時間 tst ¾

水晶発振器アンプ帰還抵抗

水晶発振器出力抵抗

減電圧検出電圧 V

減電圧検出回路動作電流 IDD-VD ¾

V

DD2

V

DD3

I

DD1

I

DD2

I

DD3

I

DD4

I

DD5

f

MXT

fXT (XI-XO) (注 4) ¾ 16.9344 ¾

f

OSC

OSC

R

fXT1

R

fXT2

R

out1

R

out2

DET

測定

回路

CPU 動作 (MXI = 75 kHz 水晶接続時) ¾ 50 100 mA

CPU 動作 (OSC = 0.5 MHz 発振時) ¾ 2.0 ¾ mA

(MXI-MXO) 水晶設定時

¾ (OS C) CR 発振器設定時 ¾ ¾ 15 %

(XI-XO) 0.5 1.0 2.0

(XO) 0.25 0.5 1.0

¾ 1.4 1.5 1.6 V

CPU, CD 動作時,

ただし,

MV

DD

¾

CPU 動作時 (CD スタンバイ, 16.9344 MHz

水晶発振器/CR 発振器使用時)

CPU のみ動作時 (CD スタンバイ,

75 kHz/32.768 kHz 水晶使用時) (注 5)

CPU, CD 動作

(XI = 16.9344 MHz水晶使用時)

CPU のみ動作

(XI = 16.9344 MHz水晶使用時)

¾

スタンバイモード

(水晶のみ発振, MXI = 75 kHz)

(CV

DD

(CKSTP 命令実行時)

¾

(OSC) CR 発振器設定時 0.01 ~ 0.75

(MXI-MXO)

水晶発振 f

¾

(MXI-MXO) ¾ 16 ¾

¾

(MXO) 50 100 200

(MV

DD

測定条件 最小 標準 最大 単位

= CV

/MVDD/AVDD/DVDD) 水晶発振停止

) 減電圧回路許可時

DVDD = AV

DD

= 75 kHz/32.768 kHz

mxt

DD

(注 4)

(注 4)

(注 3) (注 5) 30 ~ 100 kHz

3.0 ~ 3.6

3.0 ~ 3.6

1.8 ~ 3.6

¾ 30 50

¾ 1.5 ¾

¾ 40 80 mA

¾ 0.1 10 mA

¾ ¾ 1.0 s

¾ 100 ¾ mA

V

mA

MHz

MW

kW

注 2: 動作電源電流は、CVDD/MVDD/DVDD/AVDD電源端子のトータル電流値です。

注 3: 接続する水晶発振子に合わせて定数など設計・検討願います。

注 4: この項目は、CVDD = MVDD = DVDD = AVDD = 3.0~3.6 V、Ta = -40~85°C にて保証。

注 5: この項目は、CVDD = MVDD = DVDD = AVDD = 1.8~3.6 V、Ta = -30~75°C にて保証。

汎用カウンタ

汎用カウンタ

汎用カウンタ汎用カウンタ

項目 記号

周波数範囲 fCT ¾ VIN = 0.2 V

入力振幅範囲 VCT ¾ (注 4) 0.2 ¾ 2.0 V

動作電源電流I

入力アンプ帰還抵抗 R

(CTin)

測定

回路

¾ 汎用カウンタ動作電流, fin = 20 MHz ¾ 0.7 ¾ mA

DD-CT

¾ (CTin) 200 350 1000 kW

fIN

測定条件 最小 標準 最大 単位

(注 4) 0.1 ¾ 20 MHz

P-P

注 4: この項目は、CVDD = MVDD = DVDD = AVDD = 3.0~3.6 V、Ta = -40~85°C にて保証。

14

2003-01-14

P-P

LCD コモン出力

コモン出力/セグメント出力

コモン出力コモン出力

セグメント出力

セグメント出力セグメント出力

(COM1~COM4, S1~S16)

TC94A39FAG/FB

項目 記号

出力電流

バイアス電圧

LCD 動作電源電流 IDD-LCD ¾ LCD ドライバ動作電流 ¾ 50 ¾ mA

“H”レベル I

“L”レベル I

1/2 レベル V

1/3 レベル V

2/3 レベル V

OH1

OL1

BS2

BS1

BS3

測定

回路

V

¾

¾

1.47 1.67 1.87

= 2.9 V (LCD 出力時) ¾ -300 ¾

OH

VOL = 0.4 V (LCD 出力時) ¾ 450 ¾

無負荷

(コモン出力, 1/2バイアス方式設定時)

無負荷 (LCD 出力, 1/3 バイアス方式設定時)

測定条件 最小 標準 最大 単位

2.3 2.5 2.7

3.13 3.33 3.53

I/O ポート

ポート

ポートポート

出力電流

入力リーク電流 ILI ¾

入力電圧

入力プルアップダウン抵抗

(P1-0~P6-3, P8-0, P8-1, P7-0~P7-3)

項目 記号

“H”レベル I

“L”レベル

“H”レベル VIH ¾

“L”レベル V

OH2

I

OL2

I

OL3

R

R

測定

回路

V

¾

V

¾

IL

IN1

IN2

¾

OH

OL

VOL = 0.4 V (P7-0~P7-3) 5 15 ¾

VIH = 3.3 V,

V

IL

V

IH

(P6-0~P6-3, P8-0, P8-1)

プルダウン, プルアップ設定時

(P3-0) テスト入力プルダウン時 ¾ 10 ¾

測定条件 最小 標準 最大 単位

= 2.9 V (P1-0~P6-3 , P8 - 0 , P8-1) -1.0 -2.0 ¾

= 0.4 V (P1-0~P6-3, P8-0, P8-1) 1.0 2.0 ¾

= 0 V (P1-0~P6-3, P8-0, P8-1)

= 5.5 V, VIL = 0 V (P7-0~P7-3) ¾ ¾ ±1.0

¾ 0 ~

¾ ¾ ±1.0

´

V

DD

0.8

25 50 120

~ MV

MV

´ 0.2

DD

DD

AD コンバータ

コンバータ (ADin1~ADin4)

コンバータコンバータ

mA

V

mA

mA

V

kW

項目 記号

アナログ入力電圧範囲 VAD ¾ ADin1~ADin4 0 ~ MV

分解能V

変換総合誤差 ¾ ¾

アナログ入力リーク電流 ILI ¾ VIH = 3.3 V, VIL = 0 V (ADin1~ADin4) ¾ ¾ ±1.0 mA

RES

測定

回路

¾ ¾ ¾ 6 ¾ bit

MVDD = 1.8~3.6 V, Ta = -30~75°C (注 6) ¾ ¾ ±2.0

MV

DD

測定条件 最小 標準 最大 単位

DD

= 2.0~3.6 V, Ta = -40~85°C (注 6) ¾ ¾ ±1.0

注 6: この項目は、CVDD = DVDD = AVDD = 3.0~3.6 V にて保証。

PDO, TMAX, RFGC, TEBC, FMO, DMO, TRO, FOO, SEL 出力

項目 記号

出力電流

出力抵抗

V

出力オン抵抗 Ron ¾ (RFGC, TEBC, FMO, DMO, PDO) ¾ ¾ 500 W

REF

“H”レベル I

“L”レベル I

OH6

R

R

OL4

out3

out4

測定

回路

V

¾

(RFGC, TEBC, FMO, DMO, TRO, FOO) ¾ 3.0 ¾

¾

= 2.9 V (SEL, TMAX) -2.0 ¾ ¾

OH

VOL = 0.4 V (SEL, TMAX) 2.0 ¾ ¾

(PDO) ¾ 5.0 ¾

測定条件 最小 標準 最大 単位

出力

出力出力

V

LSB

mA

kW

15

2003-01-14

伝達遅延時間

伝達遅延時間

伝達遅延時間伝達遅延時間

TC94A39FAG/FB

(BCK, LRCK, AOUT, DOUT, IPF, SBOK, CLCK, DATA, SFSY, SBSY)

項目 記号

伝達遅延時間

“H”レベル t

“L”レベル t

pLH

pHL

測定

回路

¾ ¾ 10 ¾

¾

測定条件 最小 標準 最大 単位

¾ ¾ 10 ¾

CD プロセッサ

プロセッサ AD 変換部

プロセッサプロセッサ

項目 記号

分解能¾ ¾ (FEI, TEI, RFRP, SBAD) ¾ 8 ¾ bit

サンプリング周波数 ¾ ¾

変換入力レンジ ¾ ¾ AVDD = 3.3 V (FEI, TEI, RFRP, SB AD)

変換部

変換部変換部

(FEI, TEI, RFRP, SBAD)

測定

回路

(FEI, TEI, RFRP) ¾ 176.4 ¾

(SBAD) ¾ 88.2 ¾

測定条件 最小 標準 最大 単位

0.15 ´

AV

DD

¾

0.85 ´

AV

DD

CD プロセッサ

プロセッサ DA変換部

プロセッサプロセッサ

項目 記号

ビット数¾ ¾ (FOO, TRO) ¾ 5 ¾ bit

サンプリング周波数 ¾ ¾ (FOO, TRO) ¾ 2.8 ¾ MHz

変換出力レンジ ¾ ¾ AVDD = 3.3 V (FOO, TRO) AVSS ¾ AV

変換部

変換部変換部

(フォーカストラッキング系

フォーカストラッキング系)

フォーカストラッキング系フォーカストラッキング系

測定

回路

測定条件 最小 標準 最大 単位

DD

CD プロセッサ

プロセッサ PLL/VCO 部部部部

プロセッサプロセッサ

ns

kHz

V

V

項目 記号

入出力信号レンジ ¾ ¾ (LPFN, LPFO) AVSS ¾ AV

周波数特性 ¾ ¾ (LPFN-LPFO) -3dB ポイント (Gain = 1) ¾ 8 ¾ MHz

発振センタ周波数 ¾ ¾ LPFO = V

周波数可変レンジ ¾ ¾

測定

回路

[VCOGSL] bit = “L” -30 ¾ +30

[VCOGSL] bit = “H” -40 ¾ +40

測定条件 最小 標準 最大 単位

¾ 34 ¾ MHz

REF

DD

CD プロセッサ

プロセッサ コンパレータ

プロセッサプロセッサ

項目 記号

入力レンジ ¾ ¾ (TEZI, RFZI) AVSS ¾ AV

ヒステリシス電圧 ¾ ¾ (TEZI, RFZI) V

入力抵抗Z

コンパレータ

コンパレータコンパレータ

¾ (TEZI, RFZI) ¾ 10 ¾ kW

in2

(TEZI, RFZI)

測定

回路

測定条件 最小 標準 最大 単位

基準 -50 ¾ +50 mV

REF

DD

CD プロセッサ

プロセッサ デー

プロセッサプロセッサ

項目 記号

入力振幅¾ ¾ (RFI) V

入力抵抗Z

DAC 分解能 ¾ ¾ (SLCO) R-2R DAC ¾ 6 ¾ bit

DAC 出力変換レンジ ¾ ¾ (SLCO) R-2R DAC

DAC 出力インピーダンス ¾ ¾ (SLCO) R-2R DAC ¾ 2.5 ¾ kW

データスライス回路

タスライス回路

デーデー

タスライス回路タスライス回路

測定

回路

¾ (RFI) CD コマンドにより抵抗設定

in1

(RFI/SLCO)

測定条件 最小 標準 最大 単位

基準 0.6 1.2 2.0 V

REF

¾ 20 ¾

¾ 10 ¾

0.75 ´

V

REF

¾

1.25 ´

V

REF

V

%

V

P-P

kW

V

16

2003-01-14

1 ビット

ビット DA コンバータ

ビットビット

コンバータ

コンバータコンバータ

TC94A39FAG/FB

項目 記号

雑音歪率THD + N ¾ 1 kHz 正弦波、フルスケール入力 ¾ -85 -77 dB

S/N 比

ダイナミックレンジ DR ¾ 1 kHz 正弦波、-60dB 入力換算 83 90 ¾ dB

クロストーク CT ¾ 1 kHz 正弦波、フルスケール入力 ¾ -90 -83 dB

アナログ出力レベル DACout ¾ 1 kHz 正弦波、フルスケール入力 790 825 860 mVrms

S/N (1) 内部ゼロ検出: OFF 85 91 ¾

S/N (2)

測定

回路

¾

内部ゼロ検出: ON 95 100 ¾

測定条件 最小 標準 最大 単位

dB

17

2003-01-14

外形図

外形図

外形図外形図

TC94A39FAG/FB

質量: 0.32 g (標準)

18

2003-01-14

外形図

外形図

外形図外形図

TC94A39FAG/FB

質量: 0.45 g (標準)

19

2003-01-14

TC94A39FAG/FB

当社半導体製品取り扱い上のお願い

当社半導体製品取り扱い上のお願い

当社半導体製品取り扱い上のお願い当社半導体製品取り扱い上のお願い

· 当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり故障することがあります。当

社半導体製品をご使用いただく場合は、半導体製品の誤作動や故障により、生命・身体・財産が侵害されることの

ないように、購入者側の責任において、機器の安全設計を行うことをお願いします。

なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用いただくと共に、考慮されるべ

き注意事項や条件について「東芝半導体製品の取り扱い上のご注意とお願い」、「半導体信頼性ハンドブック」など

でご確認ください。

· 本資料に掲載されている製品は、一般的電子機器 (コンピュータ、パーソナル機器、事務機器、計測機器、産業用

ロボット、家電機器など) に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や

誤作動が直接人命を脅かしたり人体に危害を及ぼす恐れのある機器 (原子力制御機器、航空宇宙機器、輸送機器、

交通信号機器、燃焼制御、医療機器、各種安全装置など) にこれらの製品を使用すること (以下 “特定用途” とい

う) は意図もされていませんし、また保証もされていません。本資料に掲載されている製品を当該特定用途に使用

することは、お客様の責任でなされることとなります。

· 本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されている

ものです。

· 本資料に掲載されている技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社お

よび第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

· 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

000629TBA

20

2003-01-14

Loading...

Loading...