TOSHIBA TC74VHC153F, TC74VHC153FT, TC74VHC153FK Technical data

TC74VHC153F/FT/FK

東芝CMOSデジタル集積回路 シリコン モノリシック

TC74VHC153F,TC74VHC153FT,TC74VHC153FK

Dual 4-Channel Multiplexer

TC74VHC153 は、シリコンゲート CMOS 技術を用いた超高速

CMOS 4 チャネルマルチプレクサです。CMOS の特長である低い消

費電力で、高速ショットキ TTL に匹敵する高速動作を実現できます。

また、新規に採用した Q&Q バッファにより、スイッチング時に発生

する各種ノイズも大幅に低減しました。

入力は、2 本のアドレス A、B、4 本のチャネル入力 C

びストローブ入力 G より構成され、アドレス入力により選択された

チャネルの信号が出力 Y に現れます。

1 パッケージ内の 2 回路のマルチプレクサは、共通のアドレス入力

により制御されます。

ストローブ入力は、データ出力の禁止に使用します。すなわち、

入力が “H” のとき、出力は無条件に “L” になります。

すべての入力端子には、プラス側 (入力から V

向になる) のダイオードが入らない、新開発の入力保護回路を採用し

ました。これにより、電源電圧が加わらない状態で入力に 5.5 V の電

圧が与えられるケースも許容されます。この入力パワーダウンプロ

テクション方式により、2 電源間インタフェース、5 V から 3 V 系へ

のレベル変換、バッテリーバックアップ回路などへの幅広い応用が

可能となります。

特 長

に向かって順方

CC

0~C3

、およ

G

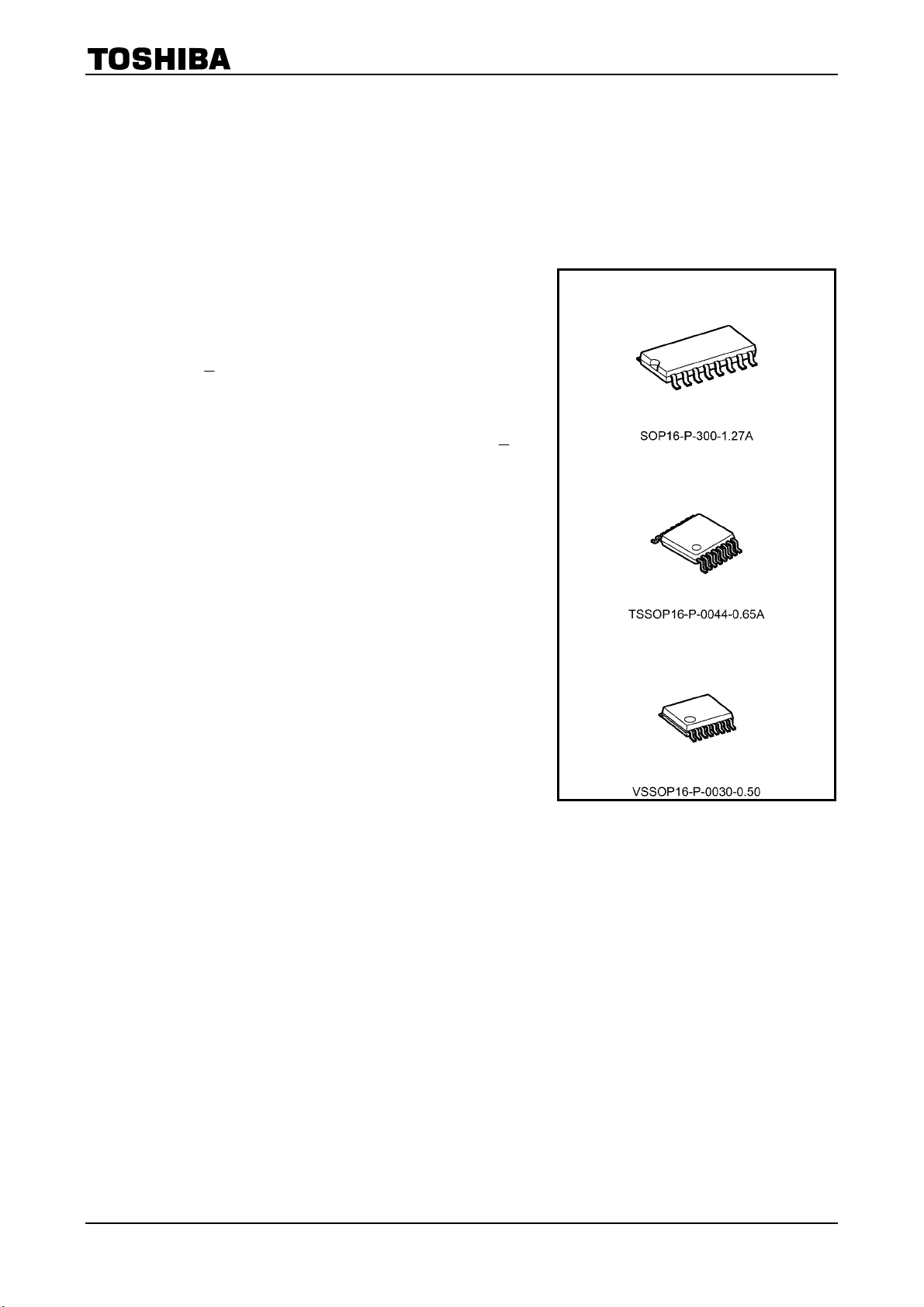

TC74VHC153F

TC74VHC153FT

TC74VHC153FK

• 高速動作 : tpd = 5.0 ns (標準) (VCC = 5 V)

• 低消費電流 : I

• 高雑音余裕度 : V

• 全入力とも、パワーダウンプロテクション機能あり

• バランスのとれた遅延時間 : t

• 広い動作電圧範囲 : V

• 74ALS153 と同一ピン接続、同一ファンクション

= 4 μA (最大) (Ta = 25°C)

CC

= V

NIH

∼

−

pLH

(opr) = 2~5.5 V

CC

= 28% VCC (最小)

NIL

t

pHL

質量

SOP16-P-300-1.27A : 0.18 g (標準)

TSSOP16-P-0044-0.65A : 0.06 g (標準)

VSSOP16-P-0030-0.50 : 0.02 g (標準)

1

2007-10-02

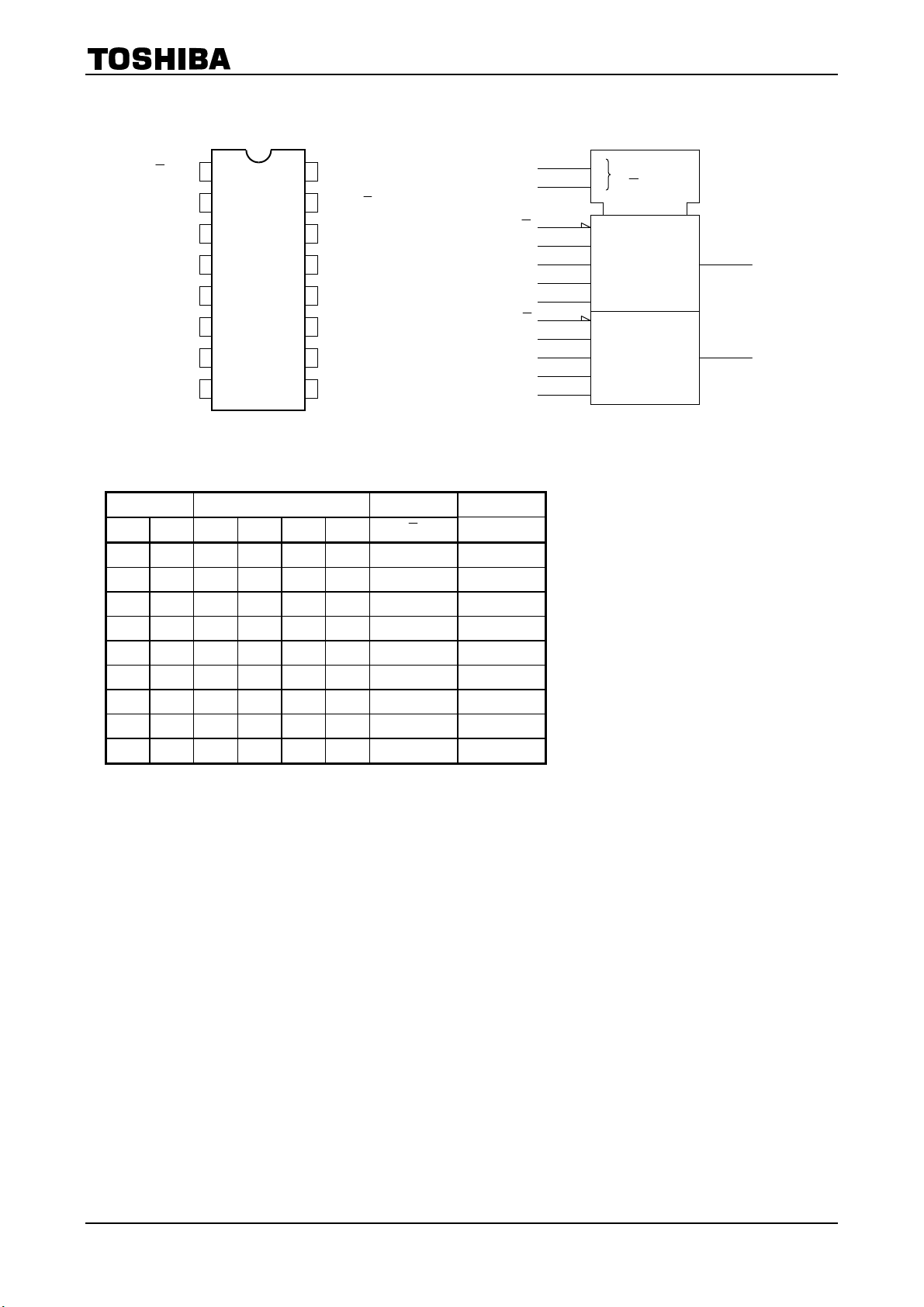

ピン接続図 論理図

A

1

G1

B

2

1C3

3

1C2

4

1C1

5

1C0

6

1Y

7

GND

8 2Y 9

(top view)

15

14

13

12

11

10

VCC 16

G2

2C3

2C2

2C1

2C0

A

B

G1

1C0

1C1

1C2

1C3

G2

2C0

2C1

2C2

2C3

真理値表

Select Inputs Data Inputs Strobe Output

B A C0 C1 C2 C3 G Y

X X X X X X H L

L L L X X X L L

L L H X X X L H

L H X L X X L L

L H X H X X L H

H L X X L X L L

H L X X H X L H

H H X X X L L L

H H X X X H L H

(14)

(2)

(1)

(6)

(5)

(4)

(3)

(15)

(10)

(11)

(12)

(13)

TC74VHC153F/FT/FK

0

0

G

1

3

MUX

EN

0

1

2

3

(7)

(9)

1Y

2Y

X: Don’t care

2

2007-10-02

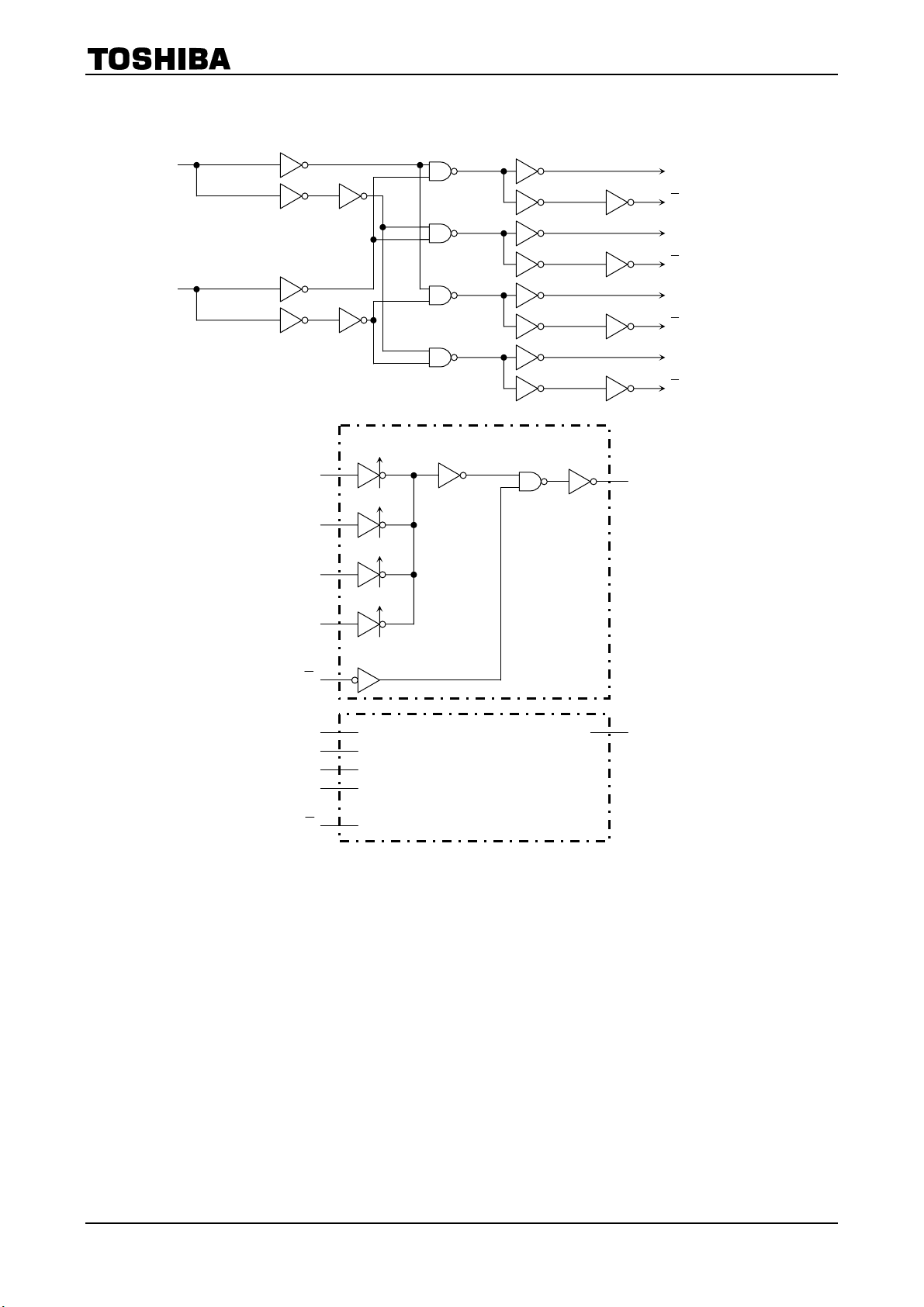

システム図

A

B

TC74VHC153F/FT/FK

14

S0

0S

S1

1S

2

S2

2S

S3

3S

1C0

1C1

1C2

1C3

G1

2C0

2C1

2C2

2C3

G2

6

5

4

3

1

10

11

12

13

15

S0

S1

S2

S3

Same as above block

7

1Y

9

2Y

3

2007-10-02

Loading...

Loading...