TOSHIBA TC74VHC00F, TC74VHC00FT, TC74VHC00FK Technical data

TC74VHC00F/FT/FK

東芝CMOSデジタル集積回路 シリコン モノリシック

TC74VHC00F,TC74VHC00FT,TC74VHC00FK

Quad 2-Input NAND Gate

TC74VHC00 は、シリコンゲート CMOS 技術を用いた超高速

CMOS 2 入力 NAND ゲートです。CMOS の特長である低い消費電

力で、高速ショットキ TTL に匹敵する高速動作を実現できます。ま

た、新規に採用した Q&Q バッファにより、スイッチング時に発生す

る各種ノイズも大幅に低減しました。

内部回路はバッファ付きの 3 段構成であり、高い雑音余裕度と安

定な出力が得られます。

すべての入力端子には、プラス側 (入力から V

向になる) のダイオードが入らない、新開発の入力保護回路を採用し

ました。これにより、電源電圧が加わらない状態で入力に 5.5 V の電

圧が与えられるケースも許容されます。この入力パワーダウンプロ

テクション方式により、2 電源間インタフェース、5 V から 3 V 系へ

のレベル変換、バッテリーバックアップ回路などへの幅広い応用が

可能となります。

特 長

に向かって順方

CC

TC74VHC00F

TC74VHC00FT

• 高速動作 : tpd = 3.7 ns (標準) (VCC = 5 V)

• 低消費電流 : I

• 高雑音余裕度 : V

• 全入力とも、パワーダウンプロテクション機能あり

• バランスのとれた遅延時間 : t

• 広い動作電圧範囲 : V

• 低ノイズ特性 : V

• 74ALS00 と同一ピン接続、同一ファンクション

= 2 μA (最大) (Ta = 25°C)

CC

= V

NIH

∼

−

pLH

CC (opr)

= 0.8 V (最大)

OLP

= 28% VCC (最小)

NIL

t

pHL

= 2~5.5 V

TC74VHC00FK

質量

SOP14-P-300-1.27A : 0.18 g (標準)

TSSOP14-P-0044-0.65A : 0.06 g (標準)

VSSOP14-P-0030-0.50 : 0.02 g (標準)

1

2007-10-01

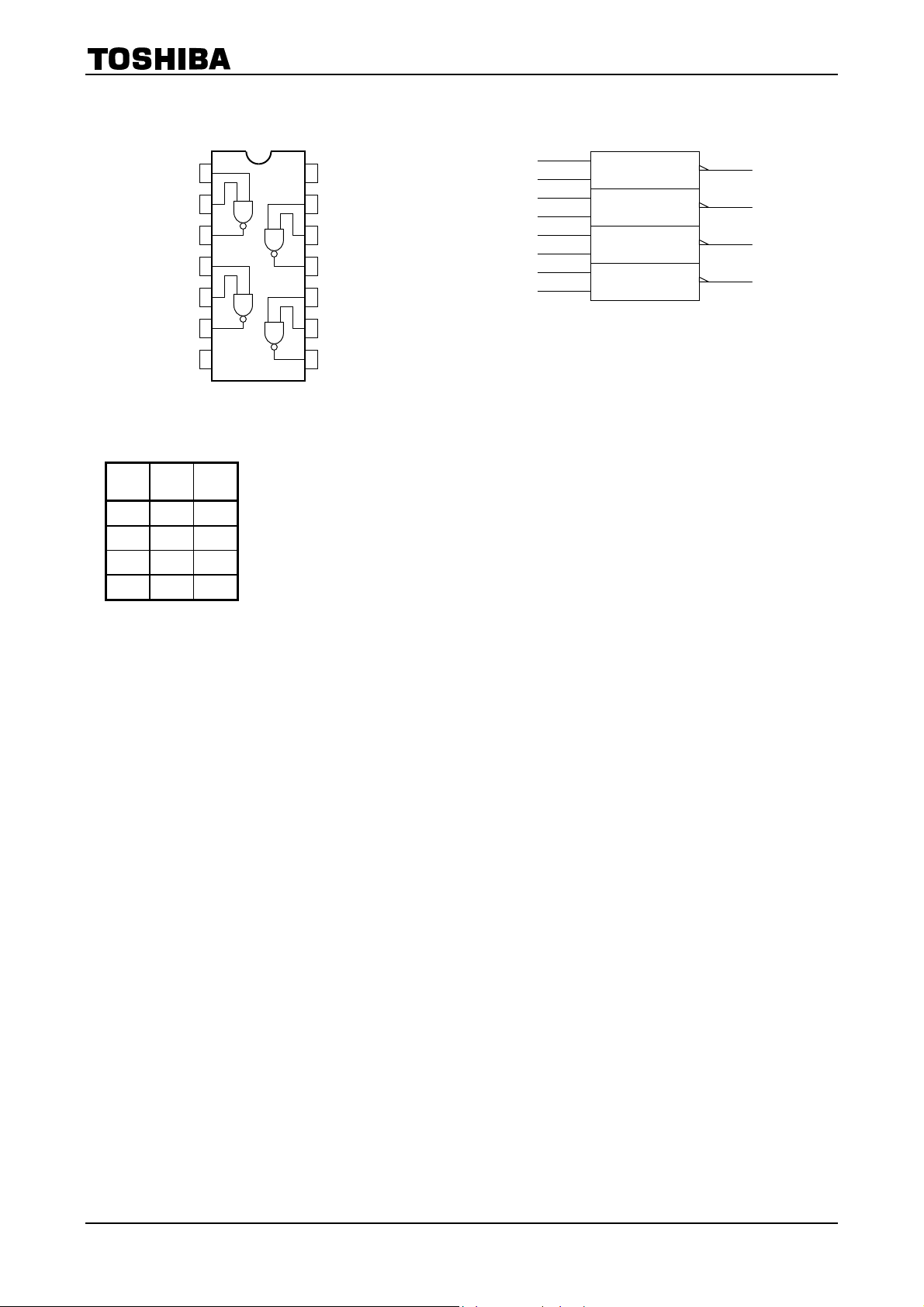

ピン接続図 論理図

1A

1B

1Y

2A

2B

1

2

3

4

5

14

13

12

11

10

VCC

4B

4A

4Y

3B

1A

1B

2A

2B

3A

3B

4A

4B

(1)

(2)

(4)

(5)

(9)

(10)

(12)

(13)

TC74VHC00F/FT/FK

&

(3)

(6)

(8)

(11)

1Y

2Y

3Y

4Y

2Y

GND

真理値表

A B Y

L L H

L H H

H L H

H H L

3A

6

7

(top view)

9

3Y

8

2

2007-10-01

TC74VHC00F/FT/FK

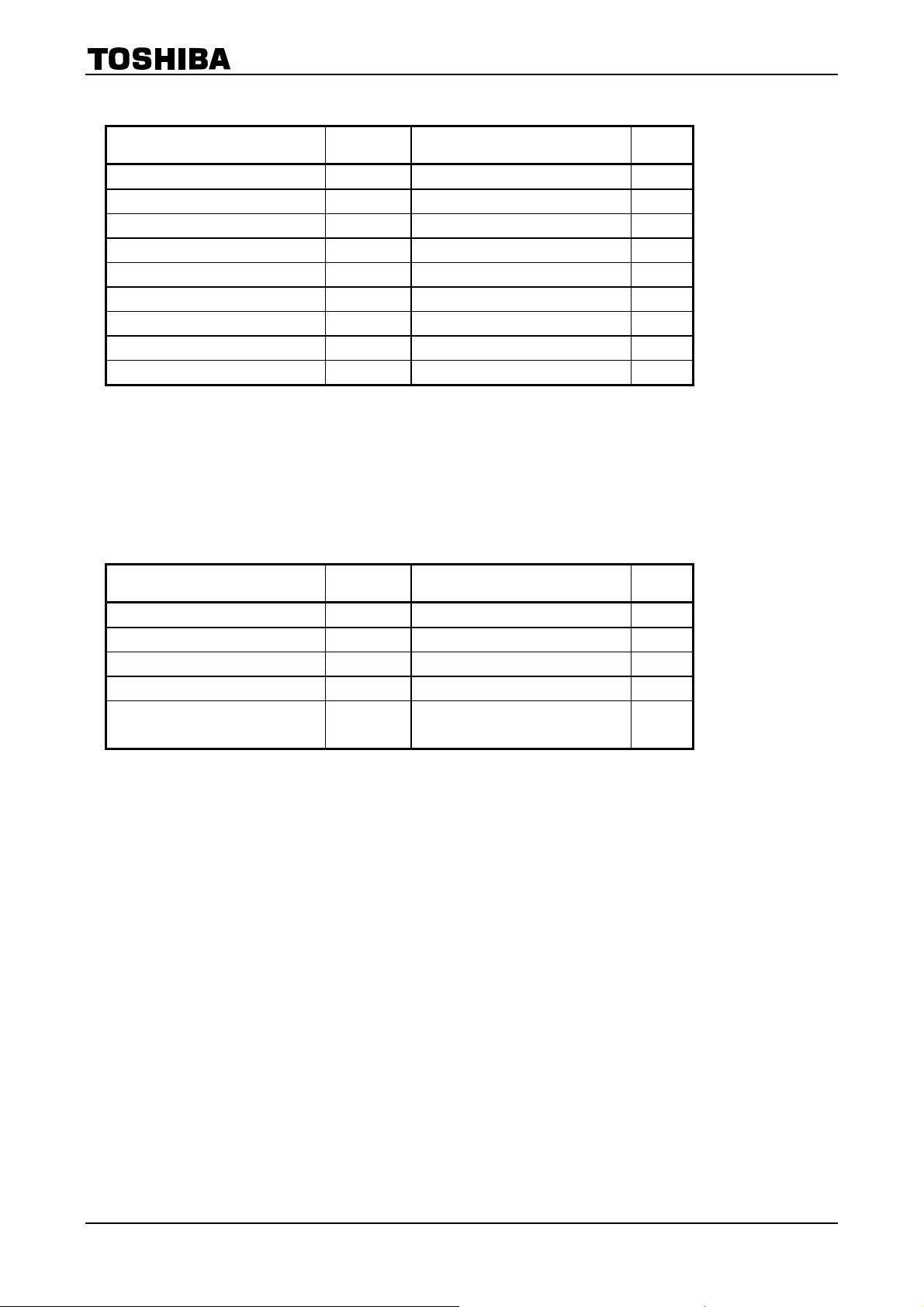

絶対最大定格 (注)

項目 記号 定格 単位

電源電圧 VCC −0.5~7.0 V

入力電圧 VIN −0.5~7.0 V

出力電圧 V

入力保護ダイオード電流 IIK −20 mA

出力寄生ダイオード電流 IOK ±20 mA

出力電流 I

電源/GND 電流 ICC ±50 mA

許容損失 PD 180 mW

保存温度 T

注: 絶対最大定格は、瞬時たりとも超えてはならない値であり、1 つの項目も超えてはなりません。

本製品の使用条件 (使用温度/電流/電圧等) が絶対最大定格/動作範囲以内での使用においても、高負荷 (高温

および大電流/高電圧印加、多大な温度変化等) で連続して使用される場合は、信頼性が著しく低下するおそれ

があります。

弊社半導体信頼性ハンドブック (取り扱い上のご注意とお願いおよびディレーティングの考え方と方法) およ

び個別信頼性情報 (信頼性試験レポート、推定故障率等) をご確認の上、適切な信頼性設計をお願いします。

動作範囲 (注)

−0.5~VCC + 0.5 V

OUT

±25 mA

OUT

−65~150 °C

stg

項目 記号 定格 単位

電源電圧 V

入力電圧 V

出力電圧 V

動作温度 T

入力上昇、下降時間 dt/dv

CC

IN

OUT

opr

注: 動作範囲は動作を保証するための条件です。

使用していない入力は VCC、もしくは GND に接続してください。

0~100 (V

0~20 (V

2.0~5.5 V

0~5.5

0~V

CC

−40~85 °C

= 3.3 ± 0.3 V)

CC

= 5 ± 0.5 V)

CC

V

V

ns/V

3

2007-10-01

Loading...

Loading...