TC74HC40105AP/AF

東芝CMOSデジタル集積回路 シリコン モノリシック

TC74HC40105AP,TC74HC40105AF

4 Bit × 16 Word FIFO Register

TC74HC40105A は、シリコンゲート CMOS 技術を用いた高速

CMOS 4 ビット × 16 ワード ファーストイン·ファーストアウト

(FIFO) レジスタです。CMOS の特長である低い消費電力で、高速動

作を実現できます。

レジスタは 4 ビット × 16 ワードの構成で、シフトインクロック

(SI) の立ち上がり、シフトアウトクロック (

り 4 ビット単位でデータの書き込み、読み出しが行えます。

DIR が “H” のとき書き込みが可能となり、DOR が “H” のとき読

み出しが可能です。また、この DIR、DOR を用いて簡単にカスケード

接続を行うことができます。

MR 端子を “H” にすることにより、DIR は “H” レベルに、DOR は

“L” レベルにセットされます。このときレジスタの内部データは変

化しませんが無効になり、すべてのレジスタは空き状態となります。

データ出力 (Qn) はスリーステート構造を持っており、

“H” にすると Qn はハイインピーダンス状態になります。

すべての入力には静電破壊の防止のために、ダイオードが付加さ

れています。

SO ) の立ち下がりによ

OE 端子を

特 長

• 高速動作 : f

• 低消費電流 : I

• 高雑音余裕度 : V

• 高ファンアウト : LSTTL 10 個を直接駆動可能

(for DIR, DOR)

LSTTL 15 個を直接駆動可能

(for Q0~Q3)

• 対称出力インピーダンス : |I

(for DIR, DOR)

|I

(for Q0~Q3)

• バランスのとれた遅延時間 : t

• 広い動作電圧範囲 : V

= 25 MHz (標準) (VCC = 5 V)

max

= 4 μA (最大) (Ta = 25°C)

CC

= V

NIH

| = IOL = 4 mA (最小)

OH

| = IOL = 6 mA (最小)

OH

∼

−

pLH

(opr) = 2~6 V

CC

= 28% VCC (最小)

NIL

t

pHL

TC74HC40105AP

TC74HC40105AF

質量

DIP16-P-300-2.54A : 1.00 g (標準)

SOP16-P-300-1.27A : 0.18 g (標準)

1

2007-10-01

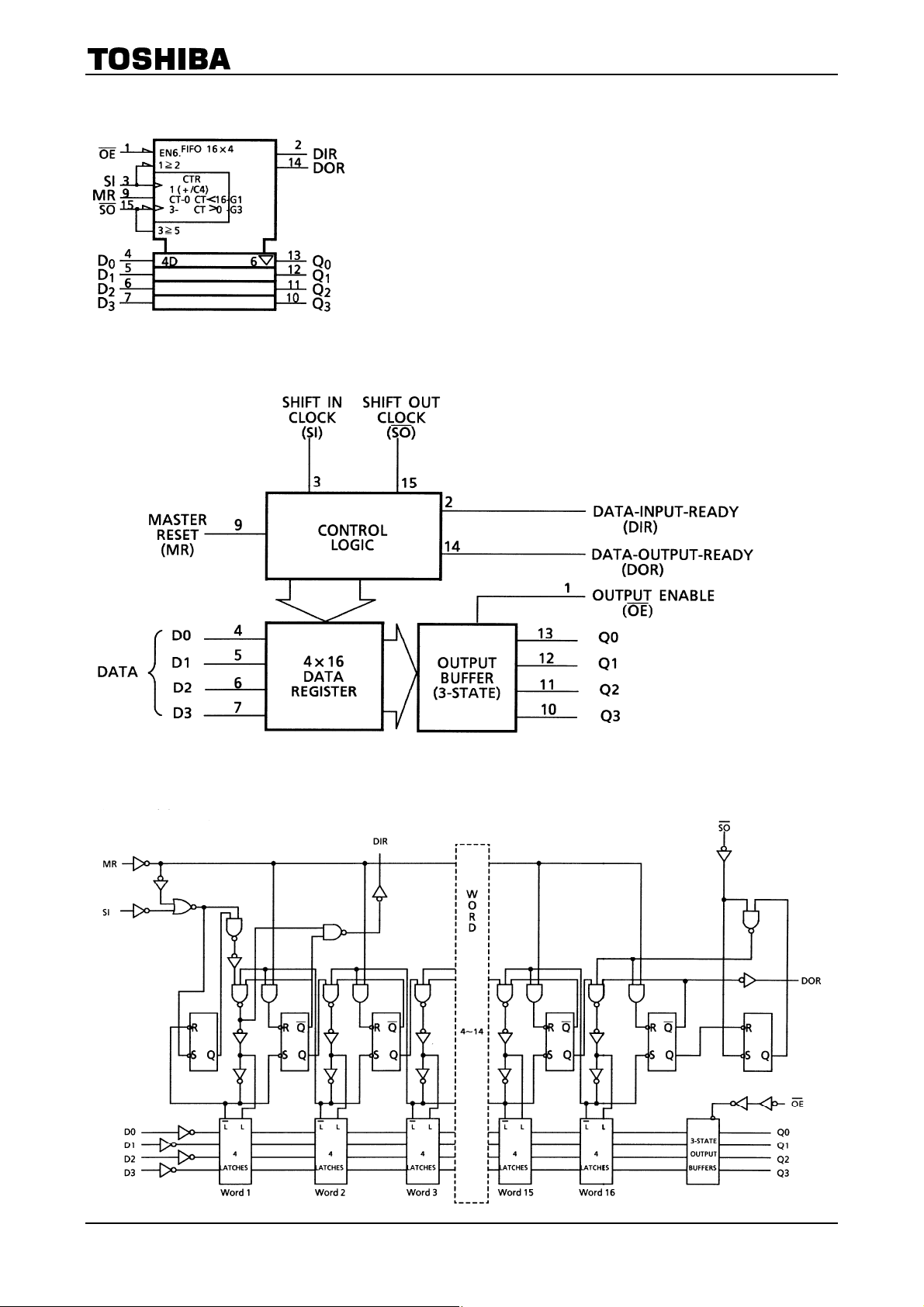

ピン接続図

TC74HC40105AP/AF

2

2007-10-01

論理図

ブロック図

TC74HC40105AP/AF

システム図

3

2007-10-01

タイミング図

TC74HC40105AP/AF

Z: High impedance

動作説明

(1) データ入力

(2) データ出力

(3) マスタリセット

(4) カスケード接続

データは、DIR 出力が “H” のときに SI 入力の立ち上がりで書き込むことができます。このデータは、

ワード・16 から 4 bit 単位でラッチされますが、ワード・1 を通るときに DIR は一瞬 “L” になります。内部

のすべてのワードにデータが入ると DIR は “L” に固定され、SI入力に立ち上がりパルスを与えても受け付

けられず、ラッチされたデータは変化しません。

最初のデータが入力されワード・16 にデータがラッチされると、DOR が “H” に固定されます。ラッチさ

れたデータは DOR が “H” のときに

タが出力されると DOR は一瞬 “L” になりますが、次のデータがある場合は、すぐこのワードにシフトして

くるので、また “H” になります。内部のすべてのワードのデータが出力されると DOR は “L” に固定され、

SO 入力の立ち下がりパルスを受け付けなくなります。

OE を “H” にすると出力はハイインピーダンス状態となります。

MR を “H” にすると内部のコントロール・ロジック部が初期化されます。DIR は “H” になり、DOR は

“L” になります。レジスタ部には変化ありませんが、ラッチされているデータは無効になります。リセット

状態を解除し、次に一番目のデータを書き込むことによりレジスタの内部データはそのデータに書きかえ

られます。

また、SI を “H” にしておき MR にパルスを入力すると、データ入力に与えられたデータが出力にそのま

まあらわれます。

DOR 出力を次段の SI 入力に接続し、

FIFO レジスタとすることができます。

ビットを拡張する場合には、ワード・1 となる DIR 出力のアンドを DIR とし、最終ワードとなる DOR 出

力のアンドを DOR とします。

ワードの拡張、ビットの拡張、いずれの場合にも、電源が立ち上がった後に MR 入力を “H” にして、マス

タリセットをかける必要があります。

SO 入力の立ち下がりで読み出すことができます。ワード・16 のデー

SO 入力に次段からの DIR 出力を接続することにより、n × 16 の

4

2007-10-01

TC74HC40105AP/AF

絶対最大定格 (注 1)

項目 記号 定格 単位

電源電圧 VCC −0.5~7 V

入力電圧 VIN −0.5~VCC + 0.5 V

出力電圧 V

入力保護ダイオード電流 IIK ±20 mA

出力寄生ダイオード電流 IOK ±20 mA

出力電流

電源/GND 電流 ICC ±75 mA

許容損失 PD 500 (DIP) (注 2)/180 (SOP) mW

保存温度 T

(DIR, DOR)

(Q0~Q3)

注 1: 絶対最大定格は、瞬時たりとも超えてはならない値であり、1 つの項目も超えてはなりません。

本製品の使用条件 (使用温度/電流/電圧等) が絶対最大定格/動作範囲以内での使用においても、高負荷 (高温お

よび大電流/高電圧印加、多大な温度変化等) で連続して使用される場合は、信頼性が著しく低下するおそれが

あります。

弊社半導体信頼性ハンドブック (取り扱い上のご注意とお願いおよびディレーティングの考え方と方法) およ

び個別信頼性情報 (信頼性試験レポート、推定故障率等) をご確認の上、適切な信頼性設計をお願いします。

−0.5~VCC + 0.5 V

OUT

I

OUT

−65~150 °C

stg

±25

±35

mA

注 2: Ta = −40~65°C まで、500 mW。Ta = 65~85°C の範囲では−10 mW/°C で、300 mW までディレーティングして

ください。

動作範囲 (注)

項目 記号 定格 単位

電源電圧 VCC 2~6 V

入力電圧 VIN 0~VCC V

出力電圧 V

動作温度 T

入力上昇、下降時間 tr, tf

注: 動作範囲は動作を保証するための条件です。

使用していない入力は VCC、もしくは GND に接続してください。

0~VCC V

OUT

−40~85 °C

opr

0~1000 (V

0~500 (V

0~400 (V

= 2.0 V)

CC

= 4.5 V)

CC

= 6.0 V)

CC

ns

5

2007-10-01

電気的特性

特性

DC

TC74HC40105AP/AF

項目 記号

“H” レベル VIH ⎯

入力電圧

“L” レベル V

“H” レベル VOH

出力電圧

“L” レベル V

スリーステート

オフリーク電流

入力電流 IIN VIN = VCC or GND 6.0 ⎯ ⎯ ±0.1 ⎯ ±1.0 μA

静的消費電流 ICC VIN = VCC or GND 6.0 ⎯ ⎯ 4.0 ⎯ 40.0 μA

⎯

IL

VIN

= V

VIN

= V

OL

V

V

IN

OUT

I

OZ

測定条件 Ta = 25°C Ta = −40~85°C

V

CC

最小 標準 最大 最小 最大

(V)

2.0

1.50

4.5

3.15

6.0

4.20

2.0

⎯

4.5

⎯

6.0

⎯

2.0

1.9

4.5

4.4

6.0

5.9

4.5

4.18

6.0

5.68

4.5

4.18

6.0

5.68

2.0

⎯

4.5

⎯

6.0

⎯

4.5

6.0⎯ ⎯

4.5

6.0⎯ ⎯

6.0 ⎯ ⎯ ±0.5 ⎯ ±5.0 μA

⎯

⎯

⎯

⎯

⎯

⎯

2.0

4.5

6.0

4.31

5.80⎯ ⎯

4.31

5.80⎯ ⎯

0.0

0.0

0.0

0.17

0.18

0.17

0.18

⎯

⎯

⎯

0.50

1.35

1.80

⎯

⎯

⎯

0.1

0.1

0.1

0.26

0.26 ⎯ ⎯

0.26

0.26 ⎯ ⎯

or VIL

IH

(DIR

DOR)

(Q0~Q3)

or VIL

IH

(DIR

DOR)

(Q0~Q3)

= VIH or VIL

= VCC or GND

I

OH

I

OH

I

OH

I

OH

I

OH

I

OL

I

OL

I

OL

I

OL

I

OL

= 20 μA

= 4 mA

= 5.2 mA

= 6 mA

= 7.8 mA

= −20 μA

= −4 mA

= −5.2 mA

= −6 mA

= −7.8 mA

1.50

3.15

4.20

⎯

⎯

⎯

1.9

4.4

5.9

4.13

5.63 ⎯ ⎯

4.13

5.63 ⎯ ⎯

⎯

⎯

⎯

⎯

⎯

⎯

0.50

1.35

1.80

⎯

⎯

⎯

0.1

0.1

0.1

0.33

0.33

0.33

0.33

単位

V

V

6

2007-10-01

TC74HC40105AP/AF

タイミング推奨動作条件

項目 記号

最小パルス幅

(SI)

最小パルス幅

SO )

(

最小パルス幅

(MR)

最小セットアップ時間

(DATA-SI)

最小ホールド時間

(DATA-SI)

最小リムーバル時間

(MR-SI)

クロック周波数 f ⎯

(input: tr = tf = 6 ns)

t

W (L)

t

W (H)

t

W (L)

t

W (H)

t

W (L)

t

W (H)

t

⎯

s

t

⎯

h

t

⎯

rem

特性

AC

(CL = 15 pF, VCC = 5 V, Ta = 25°C)

測定条件 Ta = 25°C

V

⎯

⎯

⎯

(V) 標準 Limit Limit

CC

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

Ta =

−40

95

19

16

95

19

16

95

19

16

0

0

0

125

25

21

65

13

11

2.4

12

13

単位

ns

ns

ns

ns

ns

ns

MHz

~85°C

75

15

13

75

15

13

75

15

13

0

0

0

100

20

17

50

10

9

3

15

18

項目 記号 測定条件 最小 標準 最大 単位

出力上昇、下降時間

(DIR, DOR)

伝搬遅延時間

(

SO , MR-DOR)

伝搬遅延時間

(

SO -DIR)

伝搬遅延時間

(SI-DOR)

伝搬遅延時間

(SI-DIR)

伝搬遅延時間

(MR-DIR)

t

TLH

t

THL

t

pHL

t

pLH

t

pLH

t

pHL

t

pLH

t

pHL

⎯ ⎯ 4 8 ns

⎯ ⎯ 22 39 ns

⎯ ⎯ 242 365 ns

⎯ ⎯ 187 300 ns

⎯ ⎯ 22 35 ns

⎯ ⎯ 25 39 ns

7

2007-10-01

AC

特性

(input: tr = tf = 6 ns)

TC74HC40105AP/AF

項目 記号

出力上昇、下降時間

(Q0~Q3)

出力上昇、下降時間

(DIR, DOR)

伝搬遅延時間

(

SO , MR-DOR)

伝搬遅延時間

(

SO -DIR)

伝搬遅延時間

(SI-DOR)

伝搬遅延時間

(SI-DIR)

(

SO -Qn)

(SI-Qn)

伝搬遅延時間

(MR-DIR)

出力イネーブル時間

出力ディセーブル

時間

測定条件 Ta = 25°C Ta = −40~85°C

t

TLH

t

THL

t

TLH

t

THL

t

pHL

⎯ 50

t

pLH

t

pLH

t

⎯ 50

pHL

t

pLH

t

pHL

t

pLH

t

pHL

t

pLH

t

pHL

t

pZL

t

pZH

t

pLZ

t

pHZ

RL = 1 kΩ

R

L

⎯ 50

⎯ 50

⎯ 50

⎯ 50

⎯

⎯

⎯ 50

= 1 kΩ 50

CL

(pF)

50

150

50

150

50

150

VCC

最小 標準 最大 最小 最大

(V)

⎯

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

21

24

84

28

24

798

266

226

624

208

177

78

26

22

156

52

44

171

57

48

612

204

173

627

209

178

87

29

25

45

15

13

60

20

17

32

16

14

60

7

12

6

10

75

8

15

7

13

225

45

38

2000

400

340

1650

330

280

200

40

34

400

80

68

440

88

75

1500

300

255

1540

308

262

225

45

38

125

25

21

165

33

28

125

25

21

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

単位

75

15

13

95

19

16

280

56

48

2500

500

425

2060

412

350

250

50

43

500

100

85 伝搬遅延時間

550

110

94

1875

375

319伝搬遅延時間

1925

385

327

280

56

48

155

31

26

205

41

35

155

31

26

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

8

2007-10-01

AC

特性

(input: tr = tf = 6 ns) (cont’d)

TC74HC40105AP/AF

項目 記号

最大クロック周波数 f

出力パルス幅

(DIR)

出力パルス幅

(DOR)

入力容量 C

出力容量 C

等価内部容量 C

max

t

w (H)

t

w (L)

t

w (H)

t

w (L)

⎯ ⎯ 5 10 ⎯ 10 pF

IN

⎯ ⎯ 10 ⎯ ⎯ ⎯ pF

OUT

(注) ⎯ 300 ⎯ ⎯ ⎯ pF

PD

測定条件 Ta = 25°C Ta = −40~85°C

CL

⎯

⎯ 50

⎯ 50

(pF)

50

150

VCC

最小 標準 最大 最小 最大

(V)

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

3

15

18

2.6

13

15

⎯

⎯

⎯

⎯

⎯

⎯

注: CPDは、無負荷時の動作消費電流より計算した IC 内部の等価容量です。

7

22

26

6

20

24

95

25

21

95

25

21

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

単位

2.4

12

14

10

12

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

MHz

⎯

2

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

ns

ns

無負荷時の平均動作消費電流は、次式により求められます。

ICC (opr) = CPD・VCC・fIN + ICC

9

2007-10-01

外形図

TC74HC40105AP/AF

質量: 1.00 g (標準)

10

2007-10-01

外形図

TC74HC40105AP/AF

質量: 0.18 g (標準)

11

2007-10-01

TC74HC40105AP/AF

製品取り扱い上のお願い

• 本資料に掲載されているハードウェア、ソフトウェアおよびシステム(以下、本製品という)に関する情

報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

• 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を

得て本資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

• 当社は品質、信頼性の向上に努めていますが、半導体製品は一般に誤作動または故障する場合があります。

本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないよう

に、お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うこ

とをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、デー

タシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の

取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品デー

タ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する

場合は、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

当社は、適用可否に対する責任は負いません。

• 本製品は、一般的電子機器(コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家

電機器など)または本資料に個別に記載されている用途に使用されることが意図されています。本製品は、

特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な

財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下“特定用途”とい

う)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、

航空・宇宙機器、医療機器、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各

種安全関連機器、昇降機器、電力機器、金融関連機器などが含まれます。本資料に個別に記載されている

場合を除き、本製品を特定用途に使用しないでください。

• 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

• 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用すること

はできません。

• 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して

当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

• 別途書面による契約がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の

保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の

非侵害保証を含むがこれに限らない。)をせず、また当社は、本製品および技術情報に関する一切の損害(間

接損害、結果的損害、特別損害、付随的損害、逸失利益、機会損失、休業損、データ喪失等を含むがこれ

に限らない。)につき一切の責任を負いません。

• 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あ

るいはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、

「米国輸出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行っ

てください。

• 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず弊社営業窓口までお問合せください。本

製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分

調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じ

た損害に関して、当社は一切の責任を負いかねます。

12

2007-10-01

Loading...

Loading...