TOSHIBA TC74ACT74P, TC74ACT74F Technical data

TC74ACT74P/F/FT

東芝CMOSデジタル集積回路 シリコン モノリシック

TC74ACT74P,TC74ACT74F,TC74ACT74FT

Dual D-Type Flip Flop with Preset and Clear

TC74ACT74 は、2 層メタル、シリコンゲート CMOS 技術を用い

た超高速 CMOS D タイプ フリップフロップです。CMOS の特長で

ある低い消費電力で、高速ショットキ TTL に匹敵する高速動作を実

現できます。

入力は TTL レベルですので、TTL レベルのバスに直結可能です。

D 入力に与えられた信号は、クロックの立ち上がりで Q 出力に伝

えられます。クリア、プリセット入力は、クロックに非同期に出力

の状態を決定します。これらの入力は “L” レベルで有効です。

また、すべての入力には静電破壊から素子を保護するために、ダ

イオードが付加されています。

特 長

TC74ACT74P

TC74ACT74F

• 高速動作 : f

• 低消費電流 : I

• TTL レベル入力 : V

• 高出力電流 : |IOH| = IOL = 24 mA (最小)

• バランスのとれた遅延時間 : t

• 74F74 と同一ピン接続、同一ファンクション

= 180 MHz (標準) (VCC = 5

max

V)

= 4 μA (最大) (Ta = 25°C)

CC

= 0.8 V (最大)

IL

V

= 2.0 V (最小)

IH

∼

t

−

pLH

pHL

TC74ACT74FT

質量

DIP14-P-300-2.54 : 0.96 g (標準)

SOP14-P-300-1.27A : 0.18 g (標準)

TSSOP14-P-0044-0.65A : 0.06 g (標準)

1

2007-10-01

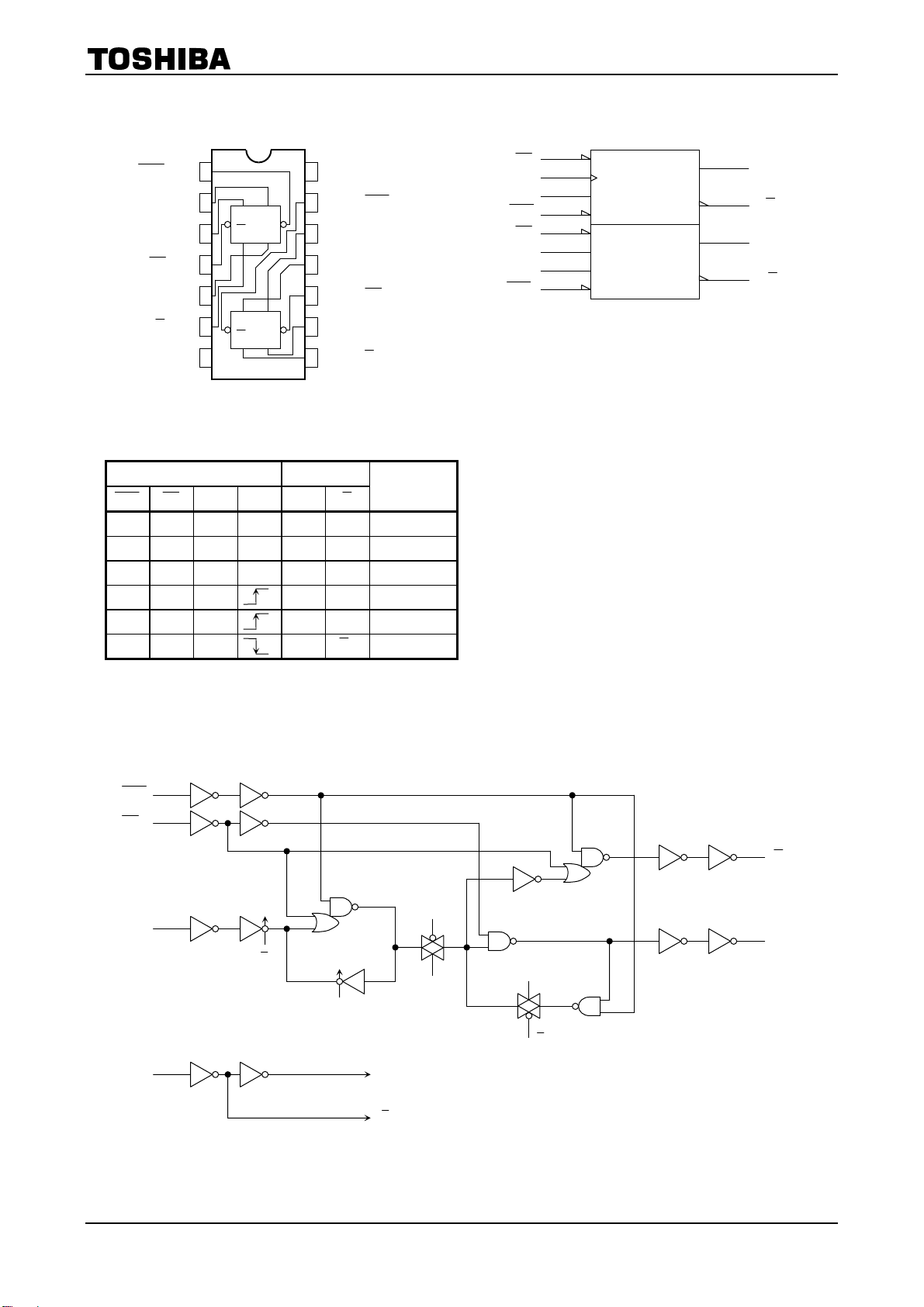

ピン接続図 論理図

CLR1

1CK

PR1

GND

1D

1Q

Q1

14

13

12

11

10

9

8

V

CC

CLR2

2D

2CK

PR2

2Q

Q2

1

2

CK

3

4

5

6

7

Q DQ

CK

D

Q

Q

(top view)

PR1

1CK

1D

CLR1

PR2

2CK

2D

CLR2

真理値表

(4)

(3)

(2)

(1)

(10)

(11)

(12)

(13)

S

1D

R

TC74ACT74P/F/FT

(5)

C

1

(6)

(9)

(8)

1Q

Q1

2Q

Q2

Inputs Outputs

CLR PR D CK Q Q

L H X X L H Clear

H L X X H L Preset

L L X X H H ―

H H L L H ―

H H H H L ―

H H X Qn nQ No Change

X: Don’t care

システム図

1/13

CLR

4/10

PR

2/12

D

ϕ

Function

6/8

Q

5/9

Q

φ

φ

ϕ

3/11

CK

φ

ϕ

2

2007-10-01

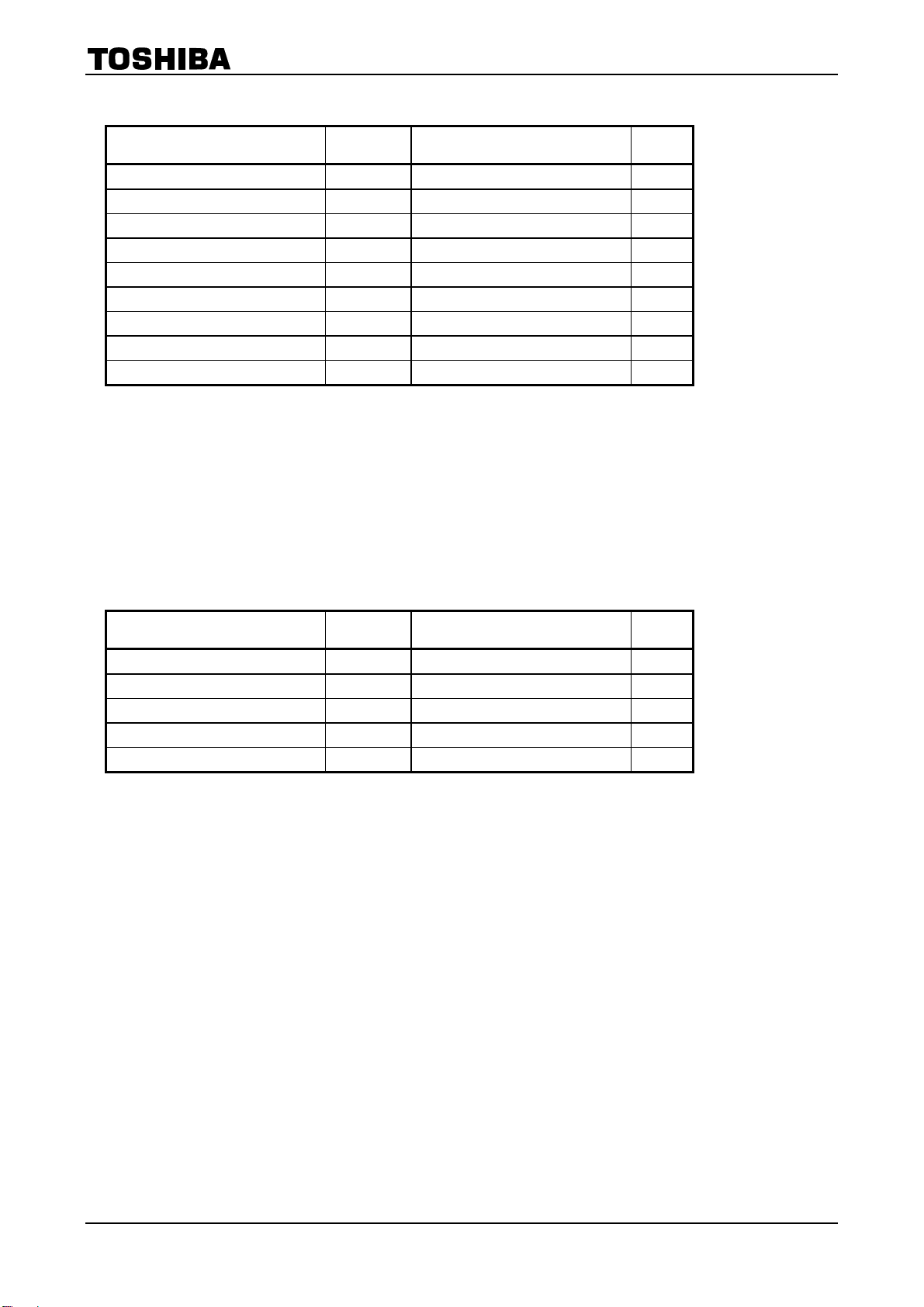

絶対最大定格 (注 1)

項目 記号 定格 単位

TC74ACT74P/F/FT

電源電圧 V

入力電圧 V

出力電圧 V

入力保護ダイオード電流 I

出力寄生ダイオード電流 I

出力電流 I

電源/GND 電流 I

許容損失 P

保存温度 T

−0.5~7.0 V

CC

−0.5~VCC + 0.5 V

IN

−0.5~VCC + 0.5 V

OUT

±20 mA

IK

±50 mA

OK

±50 mA

OUT

±100 mA

CC

500 (DIP) (注 2)/180 (SOP/TSSOP) mW

D

−65~150 °C

stg

注 1: 絶対最大定格は、瞬時たりとも超えてはならない値であり、1 つの項目も超えてはなりません。

本製品の使用条件 (使用温度/電流/電圧等) が絶対最大定格/動作範囲以内での使用においても、高負荷 (高温

および大電流/高電圧印加、多大な温度変化等) で連続して使用される場合は、信頼性が著しく低下するおそれ

があります。

弊社半導体信頼性ハンドブック (取り扱い上のご注意とお願いおよびディレーティングの考え方と方法) およ

び個別信頼性情報 (信頼性試験レポート、推定故障率等) をご確認の上、適切な信頼性設計をお願いします。

注 2: Ta = −40~65°C まで、500 mW。Ta = 65~85°C の範囲では−10 mW/°C で、300 mW までディレーティングし

てください。

動作範囲 (注)

項目 記号 定格 単位

電源電圧 V

入力電圧 V

出力電圧 V

動作温度 T

入力上昇、下降時間 dt/dV 0~10 (V

CC

IN

OUT

opr

注: 動作範囲は動作を保証するための条件です。

使用していない入力は VCC、もしくは GND に接続してください。

4.5~5.5 V

0~V

CC

0~V

CC

−40~85 °C

= 5 ± 0.5 V) ns/V

CC

V

V

3

2007-10-01

Loading...

Loading...