TB6549FG/PG/HQ

東芝Bi-CMOS集積回路 シリコン モノリシック

TB6549FG, TB6549PG, TB6549HQ

DC モータ用フルブリッジドライバ IC

TB6549FG/PG/HQ は、出力トランジスタに MOS 構造を採用した DC

モータ駆動用フルブリッジドライバ IC です。

低 ON 抵抗の MOS プロセス、および PWM 駆動方式の採用により高熱効

率駆動が可能です。

また、IN1、IN2 の 2 つの入力信号により、正転/逆転/ショートブレーキ/ス

トップの 4 モードを選択できます。

特 長

• 電源電圧 : 30 V (max)

• 出力電流 : 3.5 A (max) (FG/PG タイプ)

4.5 A(max.) (HQ タイプ)

• 低 ON 抵抗 : 1.0 Ω (上下和/typ.)

• PWM 制御可能

• スタンバイ機能

• 正転/逆転/ショートブレーキ/ストップ機能

• 過電流保護機能内蔵

• 熱遮断回路内蔵

• パッケージ : HSOP20/DIP16/HZIP25

はんだ付け性については、以下の条件で確認しています。

(1) お客様の使用されるはんだ槽 (Sn-37Pb 半田槽) の場合

はんだ温度 230℃、浸漬時間 5 秒間 1 回、R タイプ フラックス使用

(2) お客様の使用されるはんだ槽 (Sn-3.0Ag-0.5Cu 半田槽) の場合

はんだ温度 245℃、浸漬時間 5 秒間 1 回、R タイプ フラックス使用

TB6549FG

TB6549PG

TB6549HQ

質量

HSOP20-P-450-1.00 : 0.79 g (標準)

DIP16-P-300-2.54A : 1.11 g (標準)

HZIP25-P-1.00F : 7.7 g (標準)

注: 本製品は、MOS 構造の素子を搭載しており静電気に対し非常にデリケートであるため、お取り扱いに際しては、アー

スバンドや導電マットの使用、イオナイザーなどによる静電気除去および、温湿度管理などの静電対策に十分ご配慮

願います。

1

2010-07-13

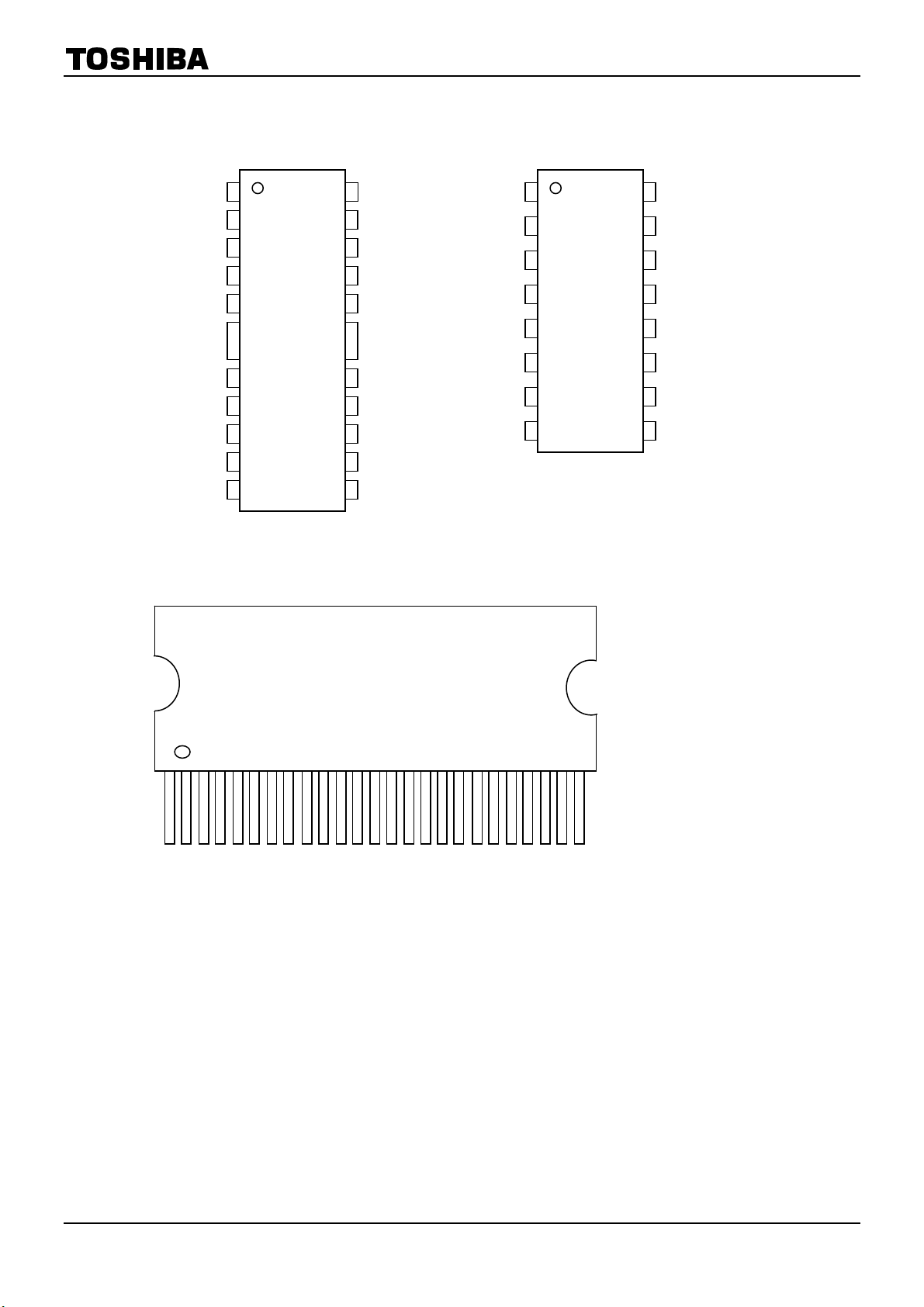

ピン接続図

(

)

HSOP20-P-450-1.00

TB6549FG/PG/HQ

DIP16-P-300-2.54A

NC

CcpA

CcpB

CcpC

NC

S-GND

Fin

NC

IN1

IN2

NC

OUT1

V

CC

NC

V

reg

SB

NC

S-GND

(Fin)

NC

PWM

NC

OUT2

P-GND

CcpA

CcpB

CcpC

S-GND

S-GND

IN1

IN2

OUT1

V

CC

V

reg

SB

S-GND

S-GND

PWM

OUT2

P-GND

HZIP25-P-1.00F

C

c

c

c

p

p

p

C

A

B

-

C

G

N

D

C

NCNC N

S

NC N

C

C

O

I

N

1

N

I

N

2

P

U

T

1

O

C

-

U

G

T

2

N

D

N

P

N

W

C

M

S

N

C

-

C

G

N

D

S

N

N

C

V

V

B

C

r

c

c

e

g

2

2010-07-13

TB6549FG/PG/HQ

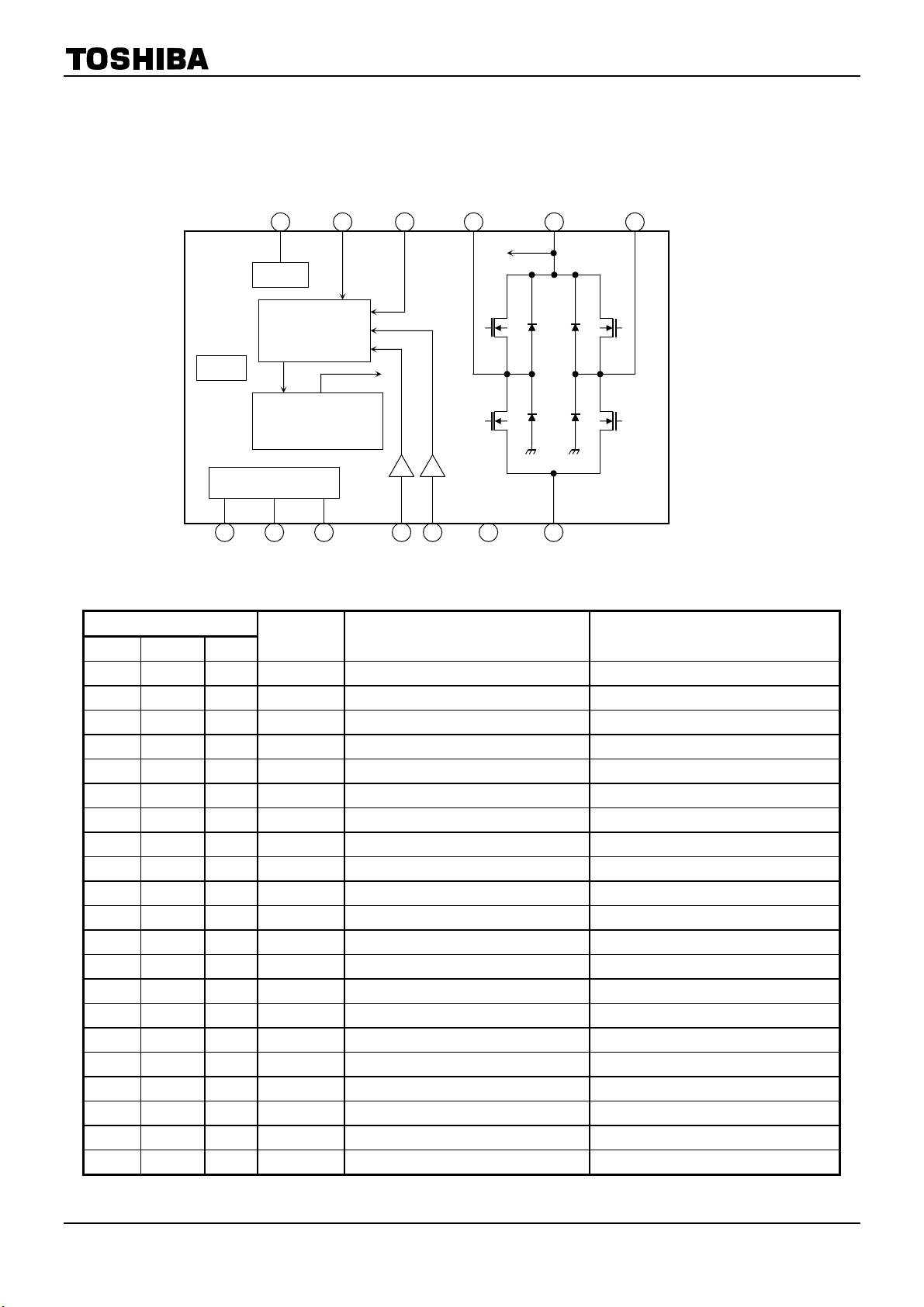

ブロック図

ブロック図内の機能ブロック/回路/定数などは、機能を説明するため、一部省略・簡略化している場合があります。

V

reg

5V

制御ロジック

OSC

過電流検出回路

TSD

チャージポンプ回路

CcpA CcpB CcpC

PWM

IN1

IN2

S-GND

CC

P-GND

OUT1OUT2SB V

端子説明

端子番号

FG PG HQ

1 ⎯ ⎯ (NC) ノンコネクション ⎯

2 1 1 CcpA チャージポンプ用コンデンサ接続端子 A チャージポンプ用コンデンサを接続

3 2 2 CcpB チャージポンプ用コンデンサ接続端子 B チャージポンプ用コンデンサを接続

4 3 3 CcpC チャージポンプ用コンデンサ接続端子 C チャージポンプ用コンデンサを接続

5 ⎯

6 ⎯

7 6 10 IN1 制御信号入力 1 0/5 V 信号を入力

8 7 11 IN2 制御信号入力 2 0/5 V 信号を入力

9 ⎯ ⎯ (NC) ノンコネクション ⎯

10 8 12 OUT1 出力端子 1 モータコイル端子へ接続

11 9 14 P-GND 出力部 GND ⎯

12 10 15 OUT2 出力端子 2 モータコイル端子へ接続

13 ⎯ ⎯ (NC) ノンコネクション ⎯

14 11 16 PWM PWM 制御信号入力端子 0/5 V の PWM 信号を入力

15 ⎯

16 ⎯

17 14 23 SB スタンバイ端子 H: スタート、L: スタンバイ

18 15 24 V

19 ⎯ ⎯ (NC) ノンコネクション ⎯

20 16 25 VCC 電源電圧印加端子 V

FIN 4,5,12,13 6,20 S-GND 接地端子 ⎯

⎯

⎯

⎯

⎯

名称 端子説明 備考

(NC) ノンコネクション ⎯

(NC) ノンコネクション ⎯

(NC) ノンコネクション ⎯

(NC) ノンコネクション ⎯

5V 出力端子 対 S-GND にコンデンサを接続

reg

= 10~27 V

CC (ope)

*) (HQ type) 4, 5, 7, 8, 9, 13, 17, 18, 19, 21, 22pin ;ノンコネクション

3

2010-07-13

TB6549FG/PG/HQ

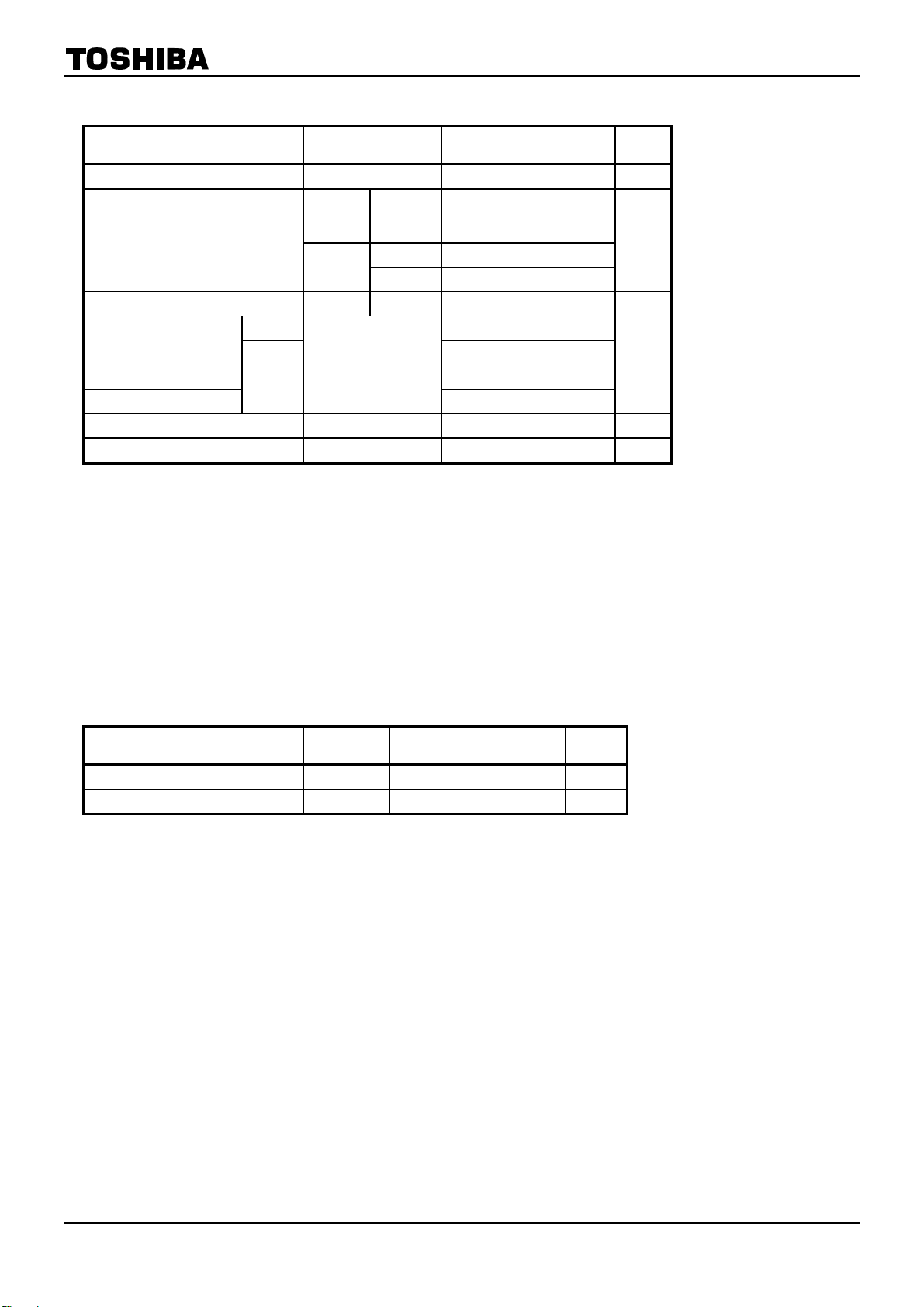

絶対最大定格

電源電圧 V

入力電圧 Vin −0.3~5.5 V

許容損失

動作温度 T

保存温度 T

(Ta = 25°C)

項目 記号 定格 単位

出力電流

CC

IO (パルス)

I

(DC)

O

FG 2.5 (注 3)

PG 2.7 (注 4)

HQ

FG, PG 3.5 (注 1)

HQ 4.5 (注 2 )

FG, PG 2.0

HQ 3.5

P

D

opr

stg

30 V

3.2 (注 5)

40 (注 6)

−20~85 °C

−55~150 °C

A

W

注 1: 絶対最大定格であり、瞬時でも超えないこと

注 2: t = 100 ms

注 3: 基板実装時 115 mm × 75 mm × 1.6 mm 銅箔面積 30%

注 4: 基板実装時 50 mm × 50 mm × 1.6 mm 銅箔面積 50%ガラスエポキシ版面基板

注 5: 単体

注 6: 無限大放熱板

動作範囲

電源電圧 V

PWM 周波数 f

(Ta = 25°C)

項目 記号 定格 単位

CC

100 kHz

CLK

10~27 V

4

2010-07-13

TB6549FG/PG/HQ

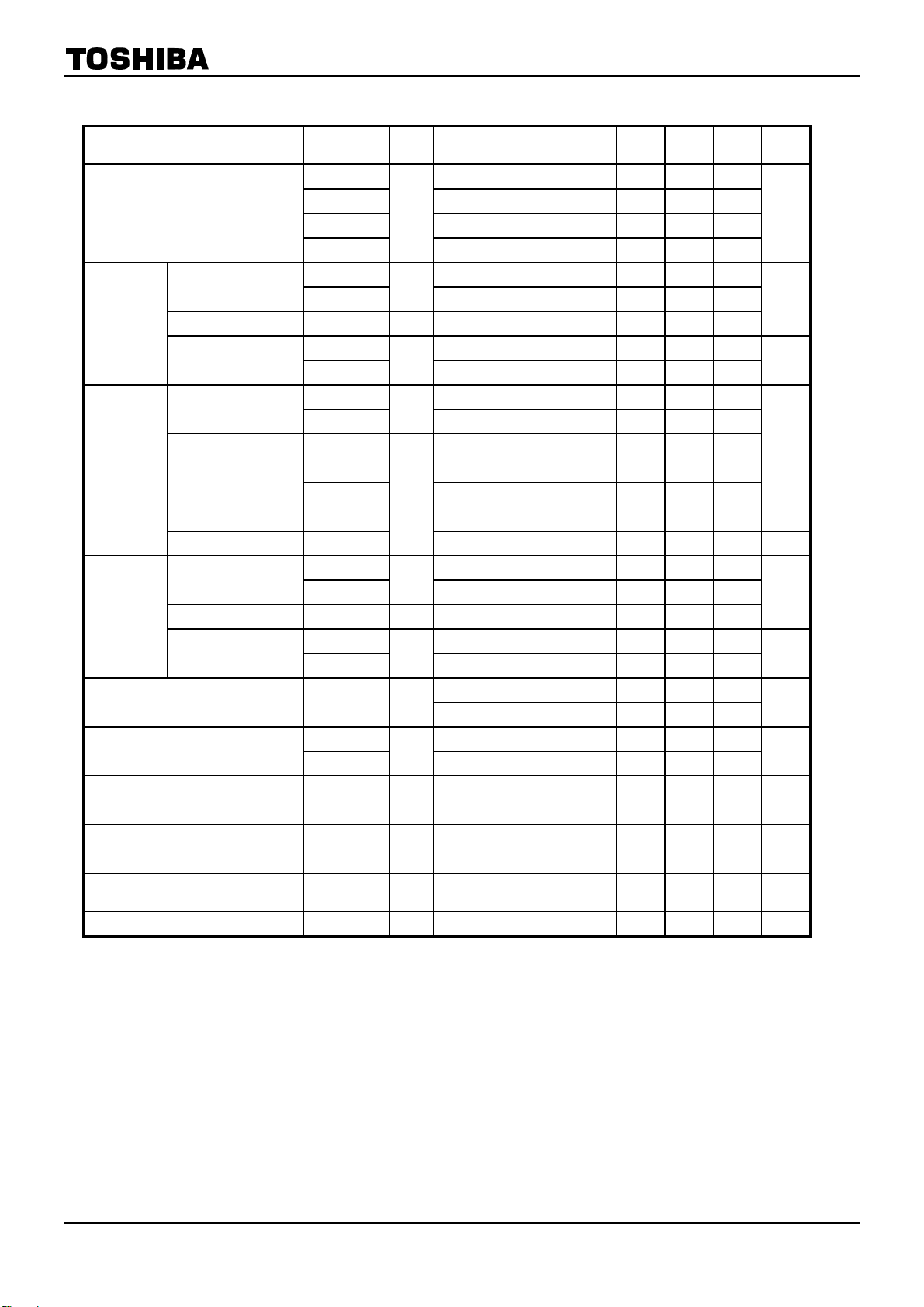

電気的特性

(VCC = 24 V, Ta = 25°C)

項目 記号

電源電流

入力電圧

制御回路

ヒステリシス電圧 V

入力電流

入力電圧

ヒステリシス電圧 V

PWM

入力回路

入力電流

PWM 周波数 f

最小クロックパルス幅 t

入力電圧

スタンバイ

回路

ヒステリシス電圧 V

入力電流

出力オン抵抗 R

出力リーク電流

ダイオード順方向電圧

内部定電圧 V

過電流検出オフセット時間 I

チャージポンプ

立ち上がり時間

測定

回路

I

CC1

I

正転/逆転モード ⎯ 6 10

CC2

I

ショートブレーキモード ⎯ 4 8

CC3

I

CC4

V

2 ⎯ 5.5

INH

V

INL

IN (HYS)

I

V

INH

I

INL

V

PWMH

V

PWML

PWM (HYS)

I

PWMH

I

PWML

PWM

w (PWM)

V

INSH

V

INSL

IN (HYS)

I

INSH

I

INSL

on (U + L)

I

V

L (U)

I

L (L)

V

F (U)

V

F (L)

4 無負荷 4.5

reg

SD (OFF)

7

t

ONG

1

2

⎯ (設計目標値) ⎯ 0.2 ⎯

1

2 ⎯ 5.5

3

⎯ (設計目標値) ⎯ 0.2 ⎯

V

3

Duty: 50 % ⎯ ⎯ 100 kHz

3

2 ⎯ 5.5

2

⎯ (設計目標値) 0.2 ⎯

V

1

4

5

I

6

⎯ (設計目標値) ⎯

測定条件 最小 標準 最大 単位

ストップモード ⎯ 4 8

スタンバイモード ⎯ 1 2

0 ⎯ 0.8

= 5 V ⎯ 50 75

IN

VIN = 0 V ⎯ ⎯ 5

⎯ ⎯ 0.8

= 5 V ⎯ 50 75

PWM

V

= 0 V ⎯ ⎯ 5

PWM

2 ⎯ ⎯ μs

⎯ ⎯ 0.8

= 5 V ⎯ 50 75

IN

VIN = 0 V ⎯ ⎯ 5

IO = 0.2 A ⎯ 1.0 1.75

= 1.5 A ⎯ 1.0 1.75

I

O

= 30 V (注 1) ⎯ ⎯ 150

CC

VCC = 30 V ⎯

= 1.5 A ⎯ 1.3 1.7

O

⎯

IO = 1.5 A ⎯ 1.3 1.7

5

50

C1 = 0.22 μF, C2 = 0.01 μF

(注 2)

⎯ 1 3 ms

10

5.5 V

⎯ μs

熱遮断回路動作温度 TSD ⎯ (設計目標値) ⎯ 160 ⎯ °C

mA

V

μA

V

μA

V

μA

Ω

μA

V

注 1: 内部回路電流含む

注 2: C1: CcpA – GND 間コンデンサ、C2: CcpB – CcpC 間コンデンサ

5

2010-07-13

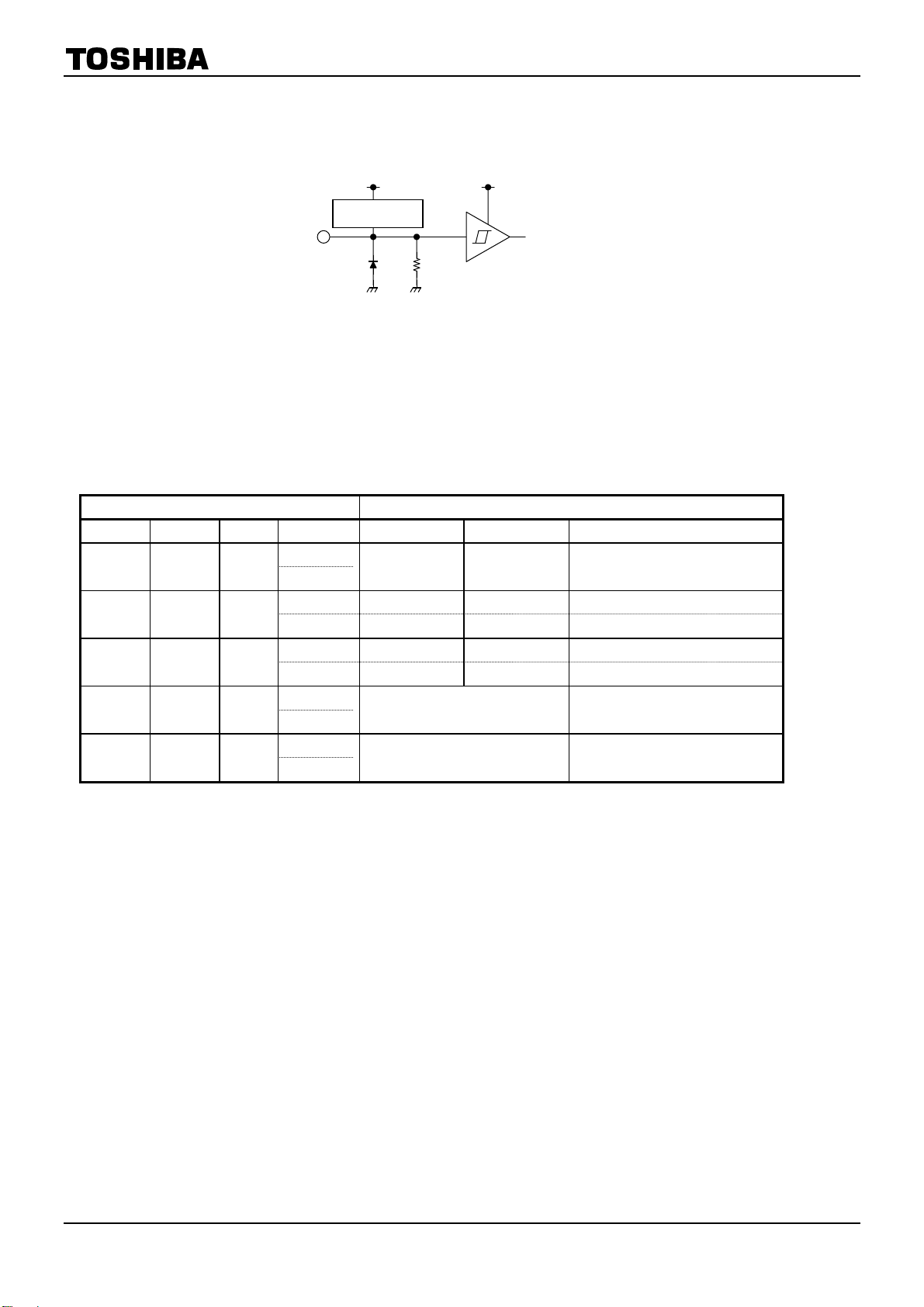

各部説明

サージ

保護回路

TB6549FG/PG/HQ

1.

制御入力

/PWM

入力回路

V

IN1

(IN2, PWM)

reg

100 kΩ

V

reg

• 入力信号は以下であり、CMOS、TTL レベルでの入力が可能です。

なお、入力信号は、0.2 V (typ.) のヒステリシスを持っています。

V

V

: 2~5.5 V

INH

: GND~0.8 V

INL

• PWM 入力周波数は、100 kHz 以下としてください。

入出力ファンクション

入力 出力

IN1 IN2 SB PWM OUT1 OUT2 モード

H H H

L H H

H L H

L L H

H/L H/L L

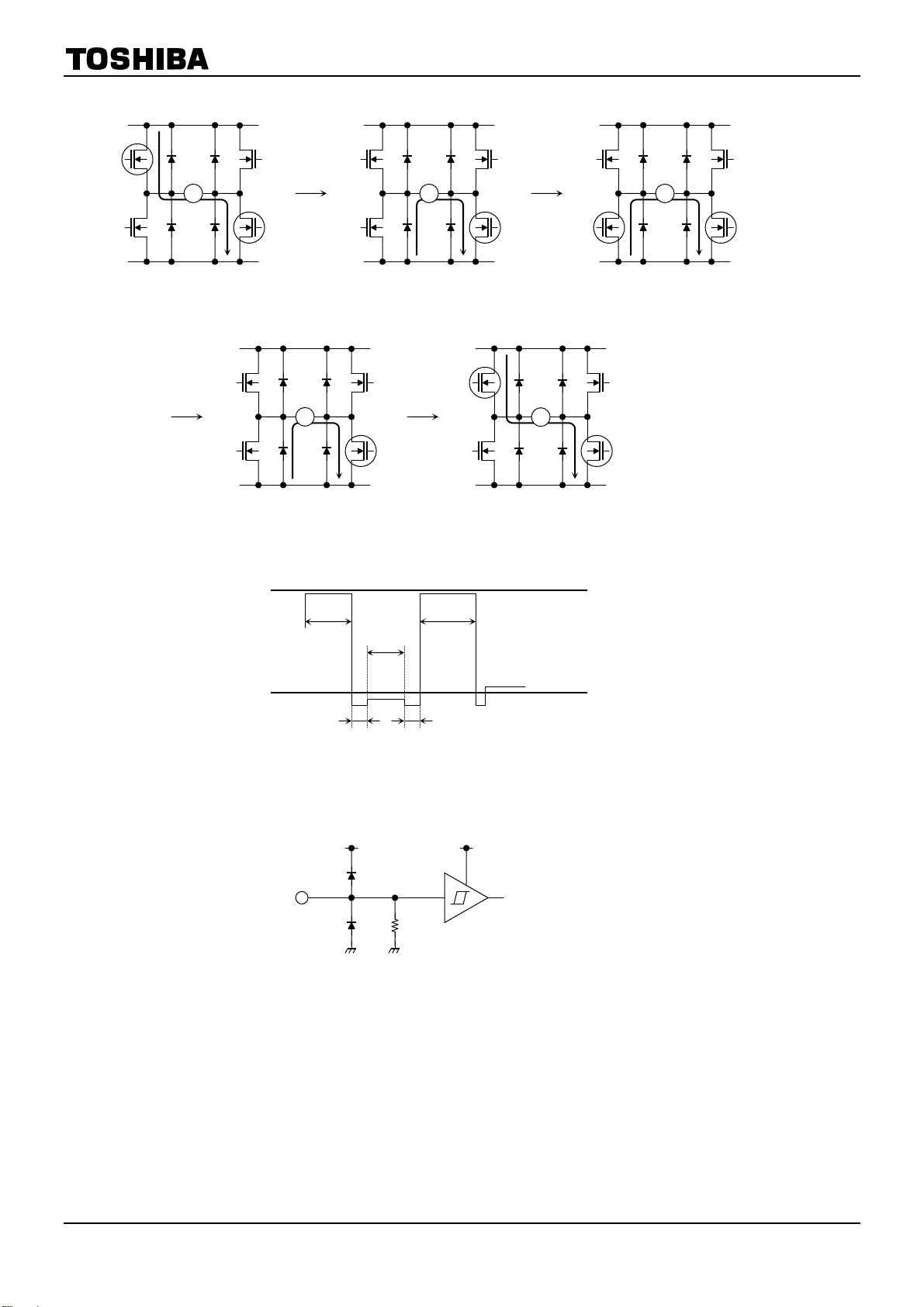

• PWM 制御機能

PWM 端子に 0/5 V の PWM 信号を入力することにより速度制御が可能です。

PWM 制御時は、通常動作とショートブレーキの繰り返しとなります。

出力回路での上下パワートランジスタの同時 ON による貫通電流を防止するために上下のパワートランジスタの

ON ↔ OFF が切り替わるタイミングにおいて 300 ns (設計目標値) のデットタイムを IC 内部にて生成しています。

このため、外部入力により OFF タイムを挿入することなく、同期整流方式による PWM 制御が可能です。

なお、CW ↔ CCW、CW (CCW) ↔ ショートブレーキ時にも、内部にて生成されるデットタイムにより OFF タイ

ムの挿入は不要です。

H

L

H

L

H

L

H

L

H

L

L L ショートブレーキ

L

L

H

L

OFF

(ハイインピーダンス)

OFF

(ハイインピーダンス)

H

L

L

L

正転/逆転

ショートブレーキ

逆転/正転

ショートブレーキ

ストップ

スタンバイ

6

2010-07-13

TB6549FG/PG/HQ

OUT1

M

PWM ON

t1

VCC

GND

OUT1

PWM OFF → ON

t4 = 300 ns (typ.)

M

OUT1

PWM ON → OFF

t2 = 300ns (typ.)

V

CC

GND

V

CC

M

GND

OUT1

PWM ON

OUT1

V

M

GND

t5

M

PWM OFF

t3

CC

VCC

GND

出力電圧波形

(OUT1)

t1

t3

t2

t5

t4

*: PWM 制御機能を使用しない場合には、PWM 端子は H レベルとしてください。

スタンバイ回路

2.

VDD V

SB

100 kΩ

DD

• スタンバイ状態では、スタンバイ回路、内部 5 V 回路以外のすべての回路をオフにします。

• 入力電圧範囲は以下であり、CMOS、TTL レベルでの入力が可能です。

なお、入力信号は 0.2 V (typ.) のヒステリシスをもっています。

V

V

: 2~V

INSH

: GND~0.8 V

INSL

reg

V

• スタンバイ端子に PWM などの信号を入力し、出力を制御することは避けてください。出力が不定となり、IC を破

壊することがあります。 (SB 端子入力信号の切り替わりでチャージポンプ回路も ON/OFF するため、その周期が

早いと、チャージポンプ回路の立ち上がりが追従しなくなります。→ 推奨 ; 50 ms 以上) スタンバイ状態 ⇒ 動作

モードに切り替える場合、あらかじめ IN1、IN2 は “L” レベル (Stop モード) とし、チャージポンプ回路が安定し

た状態 (VcpA が約 V

+ 5 V となった状態) にて、IN1、IN2 を切り替えてください。

CC

V

CC

GND

7

2010-07-13

TB6549FG/PG/HQ

内部定電圧

3.

• 制御回路バイアス用に 5 V 電源を内蔵しています。

• V

reg

さい。

• 電源監視機能を内蔵しており、3.0 V (設計目標値) 以下となった場合、出力を OFF します。0.3 V (設計目標値) の

ヒステリシスをもっており、復帰は 3.3 V (設計目標値) となります。

チャージポンプ回路

4.

(5 V)

端子には、発振防止用にコンデンサを対 S-GND へ接続してください。それ以外の負荷は、接続しないでくだ

回路

V

CC

V

CC

V

reg

VCC

CcpA

CcpB

CcpC

• 出力上側パワートランジスタのゲート駆動用にチャージポンプ回路を持っています。外付けにコンデンサを接続す

ることにより、V

V

立上がり後の VCC + 5 V (typ.) までの昇圧時間は約 2 ms です。

CC

(CcpA = 0.22 μF, CcpB-CcpC 間: 0.01μF 接続時)

• 外付けコンデンサの適正値は、V

(CcpB-CcpC 間コンデンサ値は、モータ駆動時、CcpA 端子電圧が V

ります。(V

<外付けコンデンサ>

10 V~20 V 0.01 μF~0.047 μF 0.22 μF

20 V~27 V 0.01 μF 0.22 μF

• 基準発振は、内部コンデンサにより行なっております。

CC

VCC CcpB − CcpC 間 CcpA − GND 間

+ 5 V (typ.) の電圧が発生します。

CC

により変わりますので、下記を参考にして値を決定してください。

CC

+ 5V (typ.) で安定していることが目安とな

CC

を下げていった時、CcpA 端子電圧が下がり始める場合には、値を見直してください。)

8

2010-07-13

出力回路

f

5.

V

CC

OUT1

(OUT2)

P-GND

• 本 IC は、出力部に上下ともに Nch MOS トランジスタを採用しています。

• 出力 R

は、1 Ω (上下和/typ.) であり、低 Ronタイプとなっております。

on

• 出力トランジスタのスイッチング特性は以下となります。

PWM 入力

t

pLH

t

pHL

TB6549FG/PG/HQ

<標準値>

<実測波形>

PWM 入力

出力電圧

(OUT1, OUT2)

10%

項目 値 単位

t

350

pLH

t

800

pHL

tr 60

t

100

f

ns

t

pLH

(350 ns)

90%

50%

t

r

90%

50%

10%

t

f

t

pLH

(800 ns)

出力電圧

t

r

(60 ns)

t

(100 ns)

注: OUT1,OUT2: オープン時

9

2010-07-13

TB6549FG/PG/HQ

6. V

• VCCは、出力回路、チャージポンプ回路、内部 5 V 回路に電圧を供給します。

• 動作電圧範囲は、次の通りです。

• 電源投入時の出力誤動作を防止するために、電源監視機能を設けていますが、投入時は IN1、IN2、SB を “L” レベ

7. GND部

• 本 IC は、制御部用として S-GND、出力部用として P-GND を、それぞれ分けて設けております。

電源監視回路

8.

• V

• 0.3 V (設計目標値) の電圧ヒステリシスを持っており、本回路動作後、V

熱遮断

9.

熱遮断回路を内蔵しており、ジャンクション温度 (Tj) が 160°C (typ.) を超えると、出力を OFF します。

復帰は自動復帰で、20°C の温度ヒステリシスを持っています。

T

ΔT

過電流検出

10.

出力パワートランジスタに流れる電流の検出機能を内蔵しており設定は 5 A (typ.) となっています。

4 つの出力パワートランジスタに流れる電流を個別に検出し、1 つでも設定を超えると、すべての出力を OFF します。

本回路には、タイマが内蔵されており、過電流検出後、50 μs (typ.) の OFF 時間を経て、自動復帰します。過電流が継

続した場合、この動作を繰り返します。なお、ヒゲパルス電流などによる動作を防止するために、10 μs (typ.) の不感

帯を設けています。

電源部

CC

V

ルとすることを推奨します。

S-GND と P-GND は、IC のできるだけ近くでかならずショートしてください。

CC(opr.)

= 10~27 V

が 3.0 V (設計目標値) 以下となった場合、出力を OFF します。(このとき、VCC = 4.6 V (typ.))

reg

が 3.3 V (設計目標値) を超えたとき、

reg

出力は復帰します。

(TSD)

回路

= 160°C (設計目標値)

SD

= 20°C (設計目標値)

SD

I

LIM

回路

(ISD)

出力電流

0

50 μs

(typ.)

10 μs

(typ.)

不感帯

リミッタ値は、設計目標値を 5 A (typ.) としていますが、IC 間でのばらつき温度特性により以下分布をもっていますの

で、モータのトルク設計の場合には、十分ご考慮ください。

*: 下記ばらつきより、起動時の出力電流のピーク値は、3A 以下に抑えてください。

検出電流: 約 3.5~6.5 A

50 μs

(typ.)

10 μs

(typ.)

10

2010-07-13

測定回路

TB6549FG/PG/HQ

1. I

CC1、ICC2、ICC3、ICC4、IINH、IINL、IINSH、IINSL

V

reg

P-GNDS-GND

5V

5V/0V

5V/0V

5V/0V

I

A

I

IN

A

I

IN

A

INS

CcpC CcpB CcpA

PWM

IN1

IN2

SB

TB6549

TB6549F/P

• I

• I

• I

• I

• I

• I

• I

• I

2. V

: IN1 = 0 V、IN2 = 0 V、SB = 5 V

CC1

: IN1 = 5 V、IN2 = 5 V、SB = 5 V あるいは IN1 = 0 V、IN2 = 5 V、SB = 5 V

CC2

: IN1 = 5 V、IN2 = 5 V、SB = 5 V

CC3

: IN1 = 5 V/0 V、IN2 = 5 V/0 V、SB = 0 V

CC4

: IN1 = 5 V、および IN2 = 5 V

INH

: IN2 = 0 V、および IN2 = 0 V

INL

: SB = 5 V

INSH

: SB = 0 V

INSL

INH、VINL、VINSH、VINSL

A

I

CC

V

CC

OUT1

OUT2

24V

24V

V

CC

OUT1

OUT2

V

V

5V

PWM

IN1 2V/0.8V

IN2 0.8V/2V

SB 2V/0.8V

CcpC CcpB CcpA

TB6549

TB6549F/P

V

reg

P-GNDS-GND

• V

INH、VINSH

• V

INL

: IN1 = 0.8 V、IN2 = SB = 2 V 時の OUT1 = L、OUT2 = H を確認。IN1 = SB = 2 V、IN2 = 0.8 V 時

: IN1 = IN2 = SB = 2 V 時、OUT1 = OUT2 = L を確認。

の OUT1 = OUT2 = L を確認。

• V

: IN1 = IN2 = 2 V 時、SB = 0.8 V 時の出力ハイインピーダンスを確認。

INSL

11

2010-07-13

TB6549FG/PG/HQ

3. V

PWMH、VPWML、IPWMH、IPWML、fPWM

5V/0V

2V/0.8V

100kHz

5V

A

I

PWM

PWM

IN1

CcpCCcpB CcpA

TB6549F/P

IN2 0V

SB 5V

• V

• V

• tw

4. R

on (U + L)、Vreg

PWMH、VPWML、fPWM

PWMH、VPWML

: PWM に 2 V/0.8 V、100 kHz、duty: 20 % (2 μs) 矩形波を入力し、OUT1 を確認。

(PWM)

: PWM = 5 V 時、および PWM = 0 V 時

: PWM に 2 V/0.8 V、100 kHz、duty: 50 %矩形波を入力し、OUT1 を確認。

TB6549

P-GNDS-GND

、tw

V

reg

(PWM)

V

CC

OUT1

OUT2

24V

V

V

24V

→

I

O

V

I

↓

V

O

5V

5V/0V

PWM

IN1

IN2 0V/5V

SB 5V

CcpC CcpB CcpA

TB6549

TB6549F/P

V

reg

P-GNDS-GND

V

V

CC

OUT1

OUT2

• R

on (U + L)

: IO = 0.2 A の上下の Vdsを測定し、その和を抵抗に換算。IO = 1.5 A も同様。OUT1、OUT2 について

測定。

• V

: V

reg

端子電圧。

reg

12

2010-07-13

TB6549FG/PG/HQ

5. I

6. V

L(U)、IL(L)

5V

0V

F(U)、VF(L)

30V

A

I

L(L)

V

CC

OUT1

OUT2

A

I

L(U)

V

→

F(U)

V

24V

I

O

V

V

CC

PWM

IN1

IN2 0V

SB 5V

CcpC CcpB CcpA

TB6549

TB6549F/P

CcpC CcpB CcpA

V

reg

P-GNDS-GND

V

reg

5V

0V

PWM

IN1

IN2 0V

SB 5V

TB6549

TB6549F/P

P-GNDS-GND

OUT1

OUT2

I

↓

V

V

O

F(L)

• V

F(U)、VF(L)

: IO = 1.5 A 時。

13

2010-07-13

TB6549FG/PG/HQ

7. t

ONG

24V

V

V

reg

P-GNDS-GND

V

CC

OUT1

OUT2

5V

PWM

IN1 0V

IN2 0V

SB 0V → 5V

CcpCCcpB CcpA

TB6549F/P

TB6549

• t

: SB = 0 V → 5 V 時、CcpA 電圧が約 29 V (24 V + 5 V) で安定するまでの時間を測定。

ONG

14

2010-07-13

特性グラフ

TB6549FG/PG/HQ

3.0

(1)

P

D

2.4

(w)

1.8

D

(2)

1.2

許容損失 P

0.6

- Ta (TB6549PG)

(1) 基板実装時

(50 mm × 50 mm × 1.6 mm

Cu 50%

ガラスエポキシ片面基板)

(2) 単体

P

– Ta (TB6549FG)

D

熱抵抗

R

= 13°C/W

6

(W)

4

D

(注)

2

許容損失 P

放熱板なし

th (j-c)

R

= 130°C/W

th (j-a)

注:50 mm × 50 mm × 1 mm

Fe 放熱板付き

無限大放熱板

0

0

240 40 80 120 160 200

周囲温度 Ta (°C)

0

0 50 100 150 200

周囲温度 Ta (°C)

80

P

– Ta(TB6549HQ)

D

60

① 無限大放熱板

Rθj-c = 1°C/W

② HEAT SINK (RθHS = 3.5°C/W)

Rθj-c + RθHS = 4.5°C/W

③ 単体

Rθj-a = 39°C/W

(W)

D

40

①

②

許容損失 P

20

③

0

25 0

50 125

75

100

150

周囲温度 Ta (°C)

外付け部品

記号 用途 推奨値 備考

C1 チャージポンプ用 0.22 μF ⎯

C2 チャージポンプ用

C3 V

発振防止用 0.1 μF~1.0 μF ⎯

reg

0.01 μF VCC = 24 V (注)

0.033 μF V

= 12 V (注)

CC

C4 電源ノイズ吸収用 0.1 μF~1.0 μF ⎯

C5 電源ノイズ吸収用 50 μF~100 μF ⎯

注: VCCにより適正値が変わります。各部説明の 4.チャージポンプ回路を参照ください。

15

2010-07-13

応用回路例

5 V

V

DD

GND

マイコン

PWM

PORT1

PORT2

PORT3

14/11/16

7/6/10

8/7/11

17/14/23

C

PWM

IN1

IN2

SB

注 5)

1

TB6549FG/PG/HQ

2

4/3/3

注 4)

C

3

18/15/24

V

reg

C

2/1/1

3/2/2

CcpA CcpB CcpC

TB6549

S-GND

FIN/4,5,12,13,6, 20

TB6549FG: ①⑤⑥⑨⑬⑮⑯⑲ピンはノンコネクション

TB6549HQ: ④⑤⑦⑧⑨⑬⑰⑱⑲ (21)(22)ピンはノンコネクション

注 6)

注 3)

P-GND

11/9/14

20/16/25

V

CC

OUT1

OUT2

注 1)

ヒューズ

C

4

10/8/12

12/10/15

TB6549FG/TB6549PG/TB6549HQ

C5

24V

M

注 2)

注 1: 電源用コンデンサは、V

-PGND 間に、できるだけICの近くに接続してください。

CC

注 2: ノイズ軽減の為にモータ端子間にコンデンサを接続する場合には、チャージ電流制限のため抵抗を接続してください。

また、PWM 制御の場合にはスイッチング損失が増えますので、できるだけコンデンサは接続しないでください。

注 3: S-GND と P-GND は、IC のできるだけ近くでショートしてください。

注 4: コンデンサ C3 は S-GND へ接続してください。

注 5: コンデンサ C1、C2 は、できるだけ IC の近くに接続してください。また、C1 は S-GND の近くに接続してください。

注 6: P タイプの④、⑤、⑫、⑬ pin は、チップのベットとつながっていますので、これらのラウンドエリアを広くとること

により、放熱効果が上がります。

使用上の注意

・ 出力間ショート出力の天絡、地絡、隣接ピンショート時に IC の破壊の恐れがありますので、VCC,GND ラインの設計は十

分注意してください。

・ ICは正しく実装してください。誤った実装 (逆差しなど) をした場合、IC が破壊することがあります。

16

2010-07-13

外形図

TB6549FG/PG/HQ

質量: 0.79 g (標準)

17

2010-07-13

外形図

TB6549FG/PG/HQ

質量: 1.11 g (標準)

18

2010-07-13

外形図

TB6549FG/PG/HQ

19

2010-07-13

記載内容の留意点

ブロック図

1.

ブロック図内の機能ブロック/回路/定数などは、機能を説明するため、一部省略・簡略化している場合があります。

2. 等価回路

等価回路は、回路を説明するため、一部省略・簡略化している場合があります。

3. タイミングチャート

タイミングチャートは機能・動作を説明するため、単純化している場合があります。

4. 応用回路例

応用回路例は、参考例であり、量産設計に際しては、十分な評価を行ってください。

また、工業所有権の使用の許諾を行うものではありません。

5. 測定回路図

測定回路内の部品は、特性確認のために使用しているものであり、応用機器の誤動作や故障が発生しないことを保証す

るものではありません。

使用上のご注意およびお願い事項

TB6549FG/PG/HQ

使用上の注意事項

(1) 絶対最大定格は複数の定格の、どの一つの値も瞬時たりとも超えてはならない規格です。

複数の定格のいずれに対しても超えることができません。

絶対最大定格を超えると破壊、損傷および劣化の原因となり、破裂・燃焼による傷害を負うことがあります。

(2) 過電流の発生や IC の故障の場合に大電流が流れ続けないように、適切な電源ヒューズを使用してください。IC

は絶対最大定格を超えた使い方、誤った配線、および配線や負荷から誘起される異常パルスノイズなどが原因で

破壊することがあり、この結果、IC に大電流が流れ続けることで、発煙・発火に至ることがあります。破壊にお

ける大電流の流出入を想定し、影響を最小限にするため、ヒューズの容量や溶断時間、挿入回路位置などの適切

な設定が必要となります。

(3) モータの駆動など、コイルのような誘導性負荷がある場合、ON 時の突入電流や OFF 時の逆起電力による負極性

の電流に起因するデバイスの誤動作あるいは破壊を防止するための保護回路を接続してください。IC が破壊した

場合、傷害を負ったり発煙・発火に至ることがあります。

保護機能が内蔵されている IC には、安定した電源を使用してください。電源が不安定な場合、保護機能が動作せ

ず、IC が破壊することがあります。IC の破壊により、傷害を負ったり発煙・発火に至ることがあります。

(4) デバイスの逆差し、差し違い、または電源のプラスとマイナスの逆接続はしないでください。電流や消費電力が

絶対最大定格を超え、破壊、損傷および劣化の原因になるだけでなく、破裂・燃焼により傷害を負うことがあり

ます。なお、逆差しおよび差し違いのままで通電したデバイスは使用しないでください。

20

2010-07-13

TB6549FG/PG/HQ

使用上の留意点

(1) 過電流保護回路

(2) 熱遮断回路

(3) 放熱設計

(4) 逆起電力

過電流制限回路 (通常: カレントリミッタ回路) はどのような場合でも IC を保護するわけではありません。動作後

は、速やかに過電流状態を解除するようお願いします。

絶対最大定格を超えた場合など、ご使用方法や状況により、過電流制限回路が正常に動作しなかったり、動作する

前に IC が破壊したりすることがあります。また、動作後、長時間過電流が流れ続けた場合、ご使用方法や状況に

よっては、IC が発熱などにより破壊することがあります。

熱遮断回路 (通常: サーマルシャットダウン回路) は、どのような場合でも IC を保護するわけではありません。動

作後は、速やかに発熱状態を解除するようお願いします。

絶対最大定格を超えて使用した場合など、ご使用法や状況により、熱遮断回路が正常に動作しなかったり、動作す

る前に IC が破壊したりすることがあります。

パワーアンプ、レギュレータ、ドライバなどの、大電流が流出入する IC の使用に際しては、適切な放熱を行い、

規定接合温度 (Tj) 以下になるように設計してください。これらの IC は通常使用時においても、自己発熱をしま

す。IC 放熱設計が不十分な場合、IC の寿命の低下・特性劣化・破壊が発生することがあります。

また、IC の発熱に伴い、周辺に使用されている部品への影響も考慮して設計してください。

モータを逆転やストップ、急減速を行った場合に、モータの逆起電力の影響でモータからモータ側電源へ電流が流

れ込みますので、電源の Sink 能力が小さい場合、IC のモータ側電源端子、出力端子が定格以上に上昇する恐れが

あります。

逆起電力によりモータ側電源端子、出力端子が定格電圧を超えないように設計してください。

21

2010-07-13

TB6549FG/PG/HQ

製品取り扱い上のお願い

• 本資料に掲載されているハードウェア、ソフトウェアおよびシステム(以下、本製品という)に関する情報等、

本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

• 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本

資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

• 当社は品質、信頼性の向上に努めていますが、半導体製品は一般に誤作動または故障する場合があります。本製

品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様

の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うことをお願いします。

なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーショ

ンノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご

確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、

プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全

体で十分に評価し、お客様の責任において適用可否を判断してください。

• 本製品は、一般的電子機器(コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電機器

など)または本資料に個別に記載されている用途に使用されることが意図されています。本製品は、特別に高い

品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起

こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下“特定用途”という)に使用されることは

意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器、車

載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、電力機器、

金融関連機器などが含まれます。本資料に個別に記載されている場合を除き、本製品を特定用途に使用しないで

ください。

• 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

• 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはでき

ません。

• 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及

び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

• 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関し

て、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確

性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

• 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいは

その他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国輸出

管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

• 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず弊社営業窓口までお問合せください。本製品の

ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、

かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、

当社は一切の責任を負いかねます。

22

2010-07-13

Loading...

Loading...