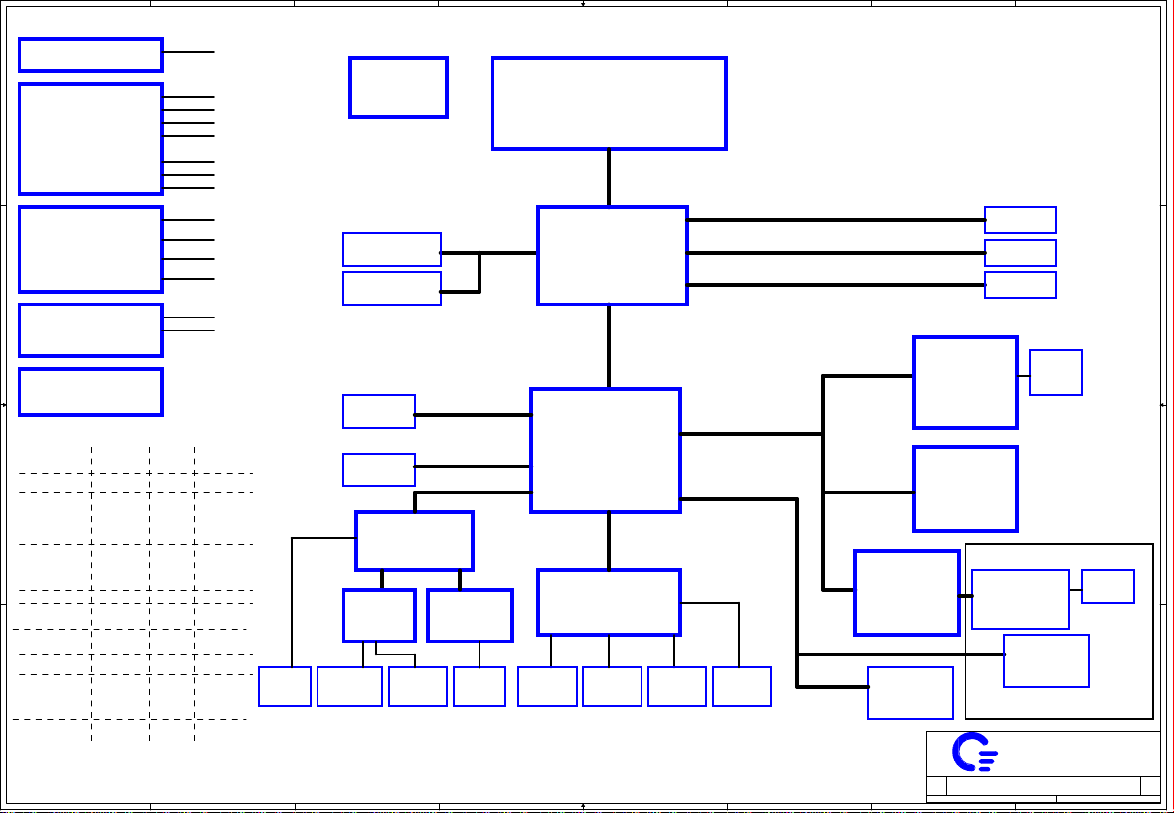

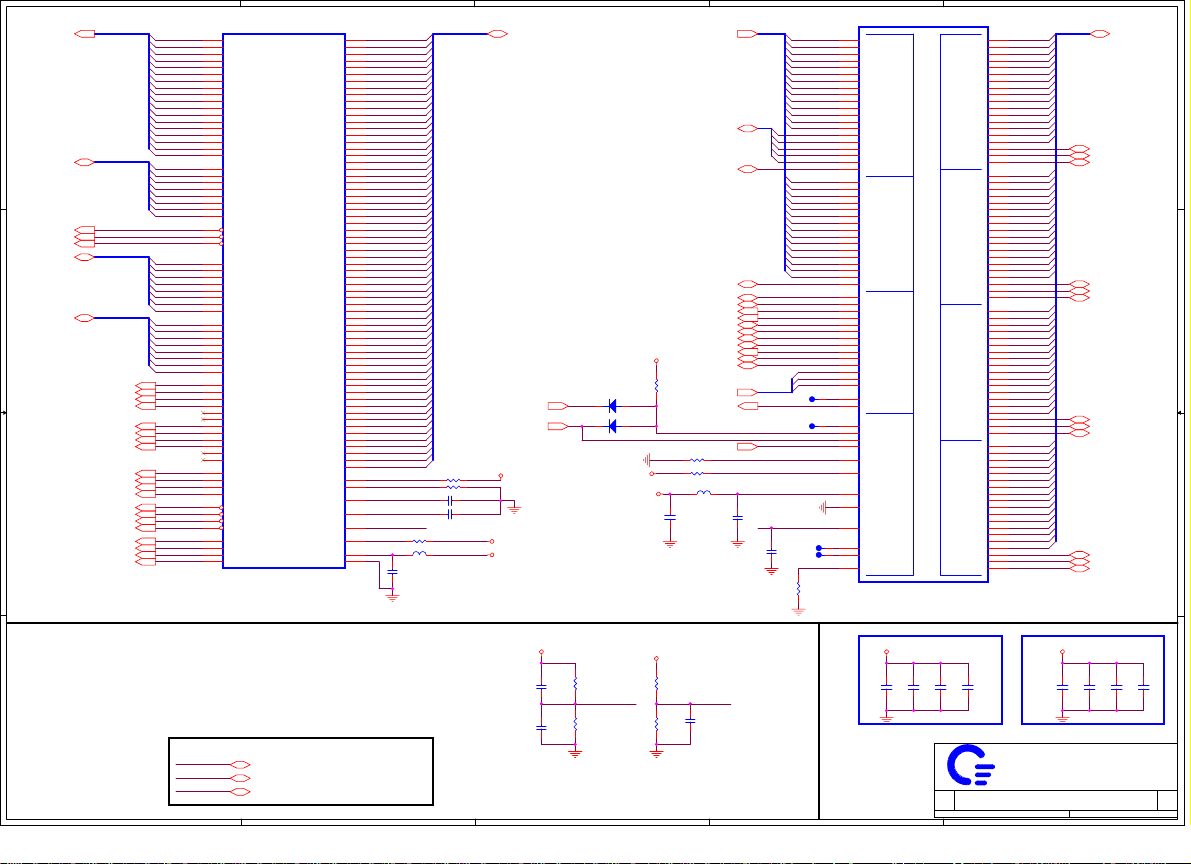

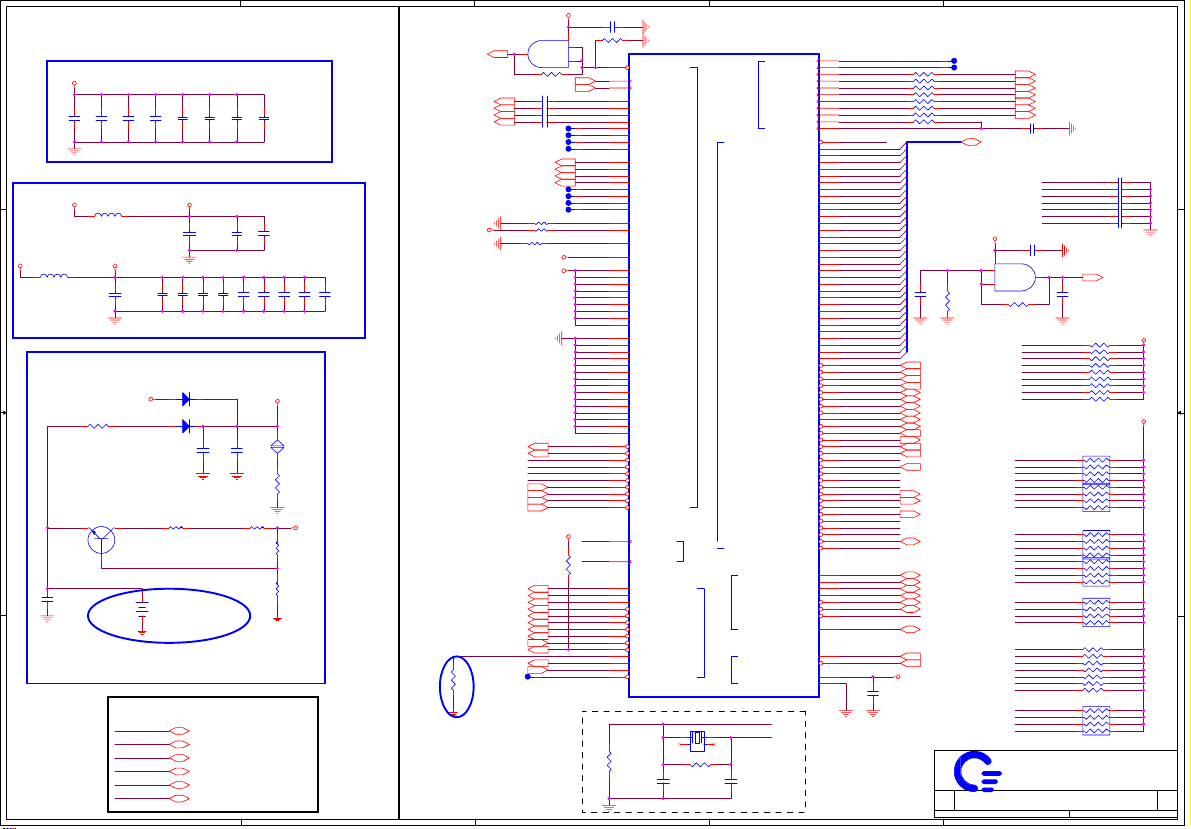

Toshiba Satellite Pro L100 Schematics

1

2

3

4

5

6

7

8

BH2

INTEL Mobile_479 CPU

RC420MB/RC420MD

VTT

+1.2V

+1.8V

+1.8VSUS

+3V

VTT

ATi SB450C

+1.8V

+1.8VUSB_PHY

+1.8V_S5

+3V

+3VSUS

+3V_S5

Page: 9, 10, 11, 12

+5V

KBC

NS

PC97551

Touchpad

4

Keyboard

Page:2, 3

HOST BUS 400MHZ

NB

ATI

Page: 5, 6 , 7, 8

2X PCIE

SB

LPC 33MHZ

Page: 21

Page: 22Page: 22

FLASH

Page: 21

5

RGB

LVDS

S-VIDEO

PCI BUS 33MHZ

USB 2.0

FAN

Page: 22

CRT

Page: 15

LVDS

Page: 15

TV-OUT

Page: 15

TI PCMCIA

PCI1510A

AD17

REQ3# / GNT3#

INTE#

Page: 17

MINI-PCI

Wireless LAN

AD20

REQ1# / GNT1#

INTG# , INTH#

Page: 22

REALTEK

RTL8100CL

AD18

REQ0# / GNT0#

INTF#

Page: 14

SYSTEM

USB PORT *2

USB2,3

Page: 20

Size Document Number Rev

BLOCK DIAGRAM

6

Date: Sheet of

7

TYPE II

SLOT

Page: 17

DAUGHTER BOARD

BOTHHAND

TRANSFORMER

NS0013

Page: 14

SYSTEM

USB PORT *2

USB 0,1

Page: 20

PROJECT : BH2

Quanta Computer Inc.

RJ45

Page: 14

129Thursday, December 22, 2005

8

1A

CPU CORE

+3VPCU

A A

+3V_S5/+3VSUS

+3V

+5VSUS/+5V

+12V

+1.8VSUS/+1.8V

+1.2V

SMDDR_VTERM

B B

+1.8V_S5

VTT

BATTERY CHARGER

Power State Table

Power

Name

VCC_CORE

+3VPCU

C C

+3V_S5

+3VSUS

+3V

+12V

+1.2V

VTT

SMDDR_VTERM MAINON

+1.8V_S5

+1.8VSUS

D D

+1.8V

1

Control

Signal

VRON

N/A

S5_ON

SUSON

MAINON

MAINON

MAINON

MAINON

S5_ON

SUSON

MAINON

Page:26

Page:24

Page:27

Page:23

Page:25

VCC_CORE

+3VPCU

+3V_S5

+3VSUS

+3V

+5VSUS

+5V

+12V

+1.8VSUS

+1.8V

+1.2V

SMDDR_VTERM

+1.8V_S5

VTT

Power

State

S0

ALWAYS

S0-S5

S0-S3

S0

S0

S0

S0

S0

S0-S5

S0-S3

S0

Power

Source

VIN

VIN

+3VPCU

+3VPCU

+3VPCU

VIN

+1.8VSUS

+1.8VSUS

+3VPCU

VIN

+1.8VSUS

2

MIC IN

Page: 18

CLOCK GEN

ICS951413CGLFT

+3V

DDR-II SODIMM1

DDR-II SODIMM2

SATA HDD

IDE-ODD

20468-51

MAX9750

SPEAKER

Page: 19

Page:4

Page: 13

Page: 13

Page: 16

Page: 16

AUDIO CODEC

CONEXANT

Page: 18

AMP

Page: 19

CONEXANT

LINE OUT

Page: 19

3

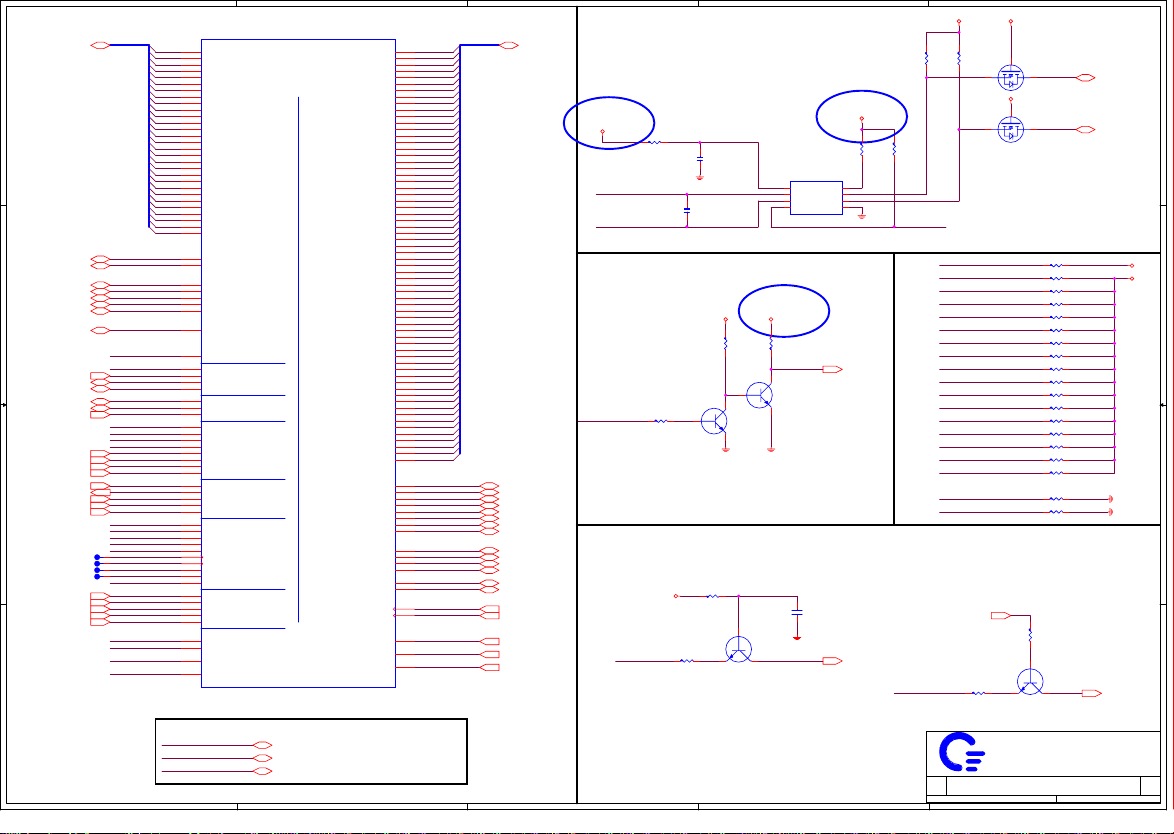

CELERON-M/PENTIUM-M

VTT

VCC_CORE

DDR-II

SATA

ATA 66/100

AC97

MODEM

20493-51

Page: 18

RJ11

Page: 14

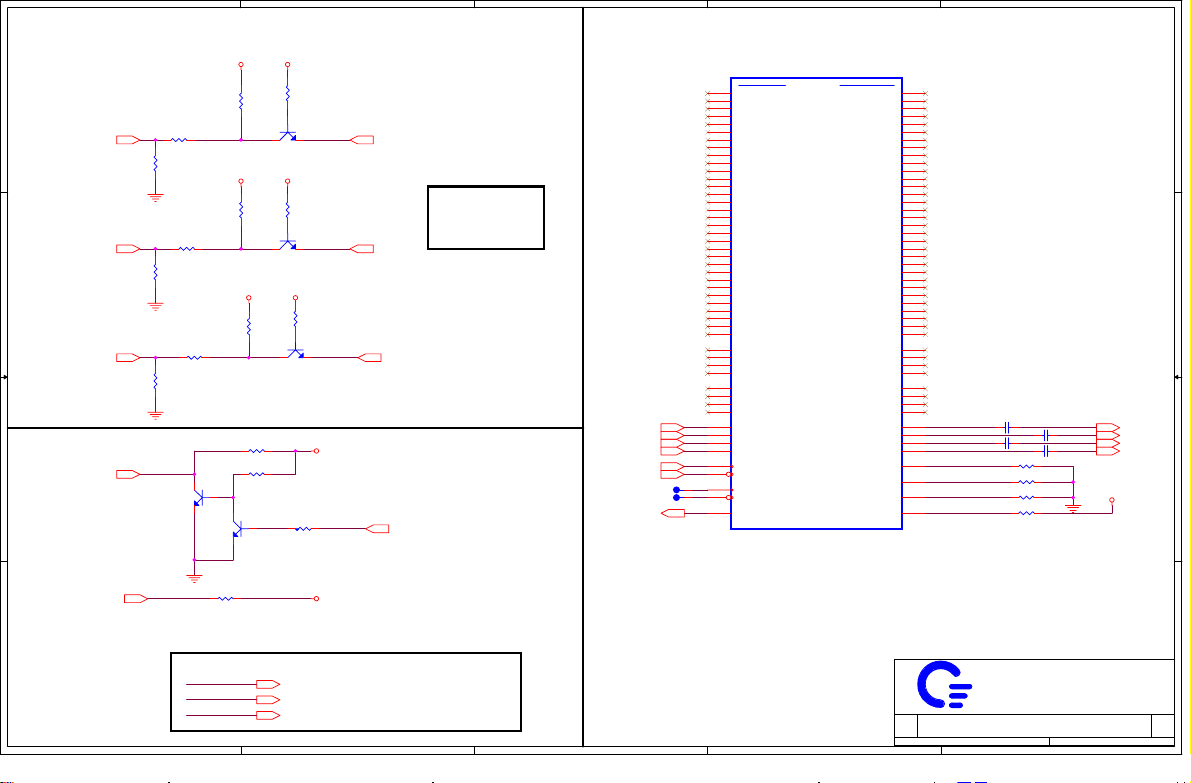

A

HA#[3..31][5]

4 4

HADSTB0#[5]

HADSTB1#[5]

HREQ#0[5]

HREQ#1[5]

HREQ#2[5]

3 3

2 2

1 1

HREQ#3[5]

HREQ#4[5]

ADS#[5]

H_IERR#

HBREQ0#

BPRI#[5]

BNR#[5]

HLOCK#[5]

HIT#[5]

HITM#[5]

DEFER#[5]

BPM0#

BPM1#

BPM2#

BPM3#

HTRDY#[5]

RS#0[5]

RS#1[5]

RS#2[5]

A20M#[9]

FERR#[9]

IGNNE#[9]

CPUPWRGD[9]

STPCLK#[9]

CPUSLP#[9]

CPUPWRGD

SMI#[9]

TCK

TDO

TDI

TMS

TRST#

HCLK_ITP

T46

HCLK_ITP#

T47

PREQ#

T49

PRDY#

T50

DBR#

INTR[9]

NMI[9]

CPUSLP#

DPSLP#

DPSLP#[9]

THERMDA

THERMDC

THERMTRIP#

CPU_PROCHOT#

CPU

A

U20A

HA#3

P4

A3#

HA#4

U4

A4#

HA#5

V3

A5#

HA#6

R3

A6#

HA#7

V2

A7#

HA#8

W1

A8#

HA#9

T4

A9#

HA#10

W2

A10#

HA#11

Y4

A11#

HA#12

Y1

A12#

HA#13

U1

A13#

HA#14

AA3

A14#

HA#15

Y3

A15#

HA#16

AA2

A16#

HA#17

AF4

A17#

HA#18

AC4

A18#

HA#19

AC7

A19#

HA#20

AC3

A20#

HA#21

AD3

A21#

HA#22

AE4

A22#

HA#23

AD2

A23#

HA#24

AB4

A24#

HA#25

AC6

A25#

HA#26

AD5

A26#

HA#27

AE2

A27#

HA#28

AD6

A28#

HA#29

AF3

A29#

HA#30

AE1

A30#

HA#31

AF1

A31#

U3

ADSTB0#

AE5

ADSTB1#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

N2

ADS#

A4

IERR#

N4

BREQ0#

J3

BPRI#

L1

BNR#

J2

LOCK#

K3

HIT#

K4

HITM#

L4

DEFER#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

M3

TRDY#

H1

RS0#

K1

RS1#

L2

RS2#

C2

A20M#

D3

FERR#

A3

IGNNE#

E4

PWRGOOD

B4

SMI#

A13

TCK

A12

TDO

C12

TDI

C11

TMS

B13

TRST#

A16

ITP_CLK0

A15

ITP_CLK1

B10

PREQ#

A10

PRDY#

A7

DBR#

D1

LINT0

D4

LINT1

C6

STPCLK#

A6

SLP#

B7

DPSLP#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

B17

PROCHOT#

Banias_Processor_RVS

POWER CHECK

Banias

1 OF 3

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

VCC_CORE [3,23,24]

+3V [4,6,7,8,9,10,11,12,13,15,16,17,18,20,21,22,23,24,27]

VTT [3,4,5,6,8,9,11,24,27]

DATA

PHASE

SIGNALS

B

HD#[0..63]HA#[3..31]

HD#0

A19

D0#

HD#1

A25

D1#

HD#2

A22

D2#

HD#3

B21

D3#

HD#4

A24

D4#

HD#5

B26

D5#

HD#6

A21

D6#

HD#7

B20

D7#

HD#8

C20

D8#

HD#9

B24

D9#

HD#10

D24

D10#

HD#11

E24

D11#

HD#12

C26

D12#

HD#13

B23

D13#

HD#14

E23

D14#

HD#15

C25

D15#

HD#16

H23

D16#

HD#17

G25

D17#

HD#18

L23

D18#

HD#19

M26

D19#

HD#20

H24

D20#

HD#21

F25

D21#

HD#22

G24

D22#

HD#23

J23

D23#

HD#24

M23

D24#

HD#25

J25

D25#

HD#26

L26

D26#

HD#27

N24

D27#

HD#28

M25

D28#

HD#29

H26

D29#

HD#30

N25

D30#

HD#31

K25

D31#

HD#32

Y26

D32#

HD#33

AA24

D33#

HD#34

T25

D34#

HD#35

U23

D35#

HD#36

V23

D36#

HD#37

R24

D37#

HD#38

R26

D38#

HD#39

R23

D39#

HD#40

AA23

D40#

HD#41

U26

D41#

HD#42

V24

D42#

HD#43

U25

D43#

HD#44

V26

D44#

HD#45

Y23

D45#

HD#46

AA26

D46#

HD#47

Y25

D47#

HD#48

AB25

D48#

HD#49

AC23

D49#

HD#50

AB24

D50#

HD#51

AC20

D51#

HD#52

AC22

D52#

HD#53

AC25

D53#

HD#54

AD23

D54#

HD#55

AE22

D55#

HD#56

AF23

D56#

HD#57

AD24

D57#

HD#58

AF20

D58#

HD#59

AE21

D59#

HD#60

AD21

D60#

HD#61

AF25

D61#

HD#62

AF22

D62#

HD#63

AF26

D63#

C23

DSTBN0#

C22

DSTBP0#

K24

DSTBN1#

L24

DSTBP1#

W25

DSTBN2#

W24

DSTBP2#

AE24

DSTBN3#

AE25

DSTBP3#

D25

DBI0#

J26

DBI1#

T24

DBI2#

AD20

DBI3#

M2

DBSY#

H2

DRDY#

B14

BCLK1

B15

BCLK0

B5

INIT#

CPURST#

B11

RESET#

C19

DPWR#

B

HD#[0..63] [5]

HDSTBN0# [5]

HDSTBP0# [5]

HDSTBN1# [5]

HDSTBP1# [5]

HDSTBN2# [5]

HDSTBP2# [5]

HDSTBN3# [5]

HDSTBP3# [5]

HDBI0# [5]

HDBI1# [5]

HDBI2# [5]

HDBI3# [5]

DBSY# [5]

DRDY# [5]

HCLK_CPU# [4]

HCLK_CPU [4]

CPUINIT# [9]

CPURST# [5]

DPWR# [5]

C

H/W MONITOR

+3V_S5

R287 47_6

THERMDC

10 mil trace /

10 mil space

THERMDA

CPU_PROCHOT#

R292 *330_4

VCC_CORE

THERMTRIP#

C

C438

2200P_4

2

R47 1K_4

R33 33/F_4

15 MIL

3V_THM

C439

.1U_4

+3V +3V_S5

R293

*1K_6

Q28

*MMBT3904

1 3

1 3

Q6 MMBT3904

D

+3V_S5

R38

SMDATA

SMCLK

D

-ALT

10K_4

6

KBSMDAT

7

KBSMCLK

8

5

PROCHOT# [10]

1999_SHT# [2 4]

U18

1

VCC

3

DXN

2

DXP

-OVT4GND

ADM1032AR

R291

330_4

PROCHOT#

Q10

2

*MMBT3904

1 3

C441

*10U/6.3V_8

2

+3V

R37

R286

10K_4

10K_4

R288

10K_4

THER_OVT#

DBR#

CPUPWRGD

TDI

TMS

TDO

CPURST#

H_IERR#

HBREQ0#

THERMTRIP#

CPU_PROCHOT#

FERR#

DPSLP#

CPUSLP#

BPM0#

BPM1#

BPM2#

BPM3#

TCK

TRST#

PWROK[6,10,21]

THER_OVT#

R32 0_6

Size Document Number Rev

CPU ( HOST BUS )-1

Date: Sheet of

E

+3V

2

MBDATA

3

1

Q5 CH2507S

+3V

10mil

2

MBCLK

3

1

Q27 CH2507S

10mil

R322 150_4

R335 330_4

R310 150_4

R328 39/F_4

R312 *54.9/F_4

R314 220_4

R334 56_4

R19 220_4

R289 56_4

R290 56_4

R338 56_4

R325 220_4

R332 220_4

R320 54.9/F_4

R321 54.9/F_4

R317 54.9/F_4

R315 54.9/F_4

R309 27.4/F_4

R307 680_4

R40

330_4

2

1 3

Q7 MMBS3904

PROJECT : BH2

Quanta Computer Inc.

E

MBDATA [21,2 6]

MBCLK [21, 26]

1999_SHT# [2 4]

229Thursday, December 22, 2005

+3V

VTT

1A

A

R20 27.4/F_4

R17 27.4/F_4

R21 54.9/F_4

R16 54.9/F_4

4 4

VCC_CORE

C58

1000P_4

VTT

3 3

C59

.1U_4

C49

1000P_4

C55

10U/6.3V_8

C33

.1U_4

C28

1000P_4

decouple CAP

C43

10U/6.3V_8

C35

C41

.01U_4

.1U_4

C27

C48

1000P_4

1000P_4

decouple CAP

VTT

C472

150U/6.3V_7343

VTT

C44

C57

.01U_4

.01U_4

COMP0

COMP2

18 MIL

COMP0 ~ 4 max length 500 MIL

COMP1 GTLREF0

COMP3

PLACE one 10U & one 0.01U for each VCCA pin

C40

10U/6.3V_8

10U/6.3V/X5R(CC0805) *30

C24

C454

2 2

10U/6.3V_8

C451

10U/6.3V_8

C38

10U/6.3V_8

1 1

10U/6.3V_8

C23

10U/6.3V_8

C51

10U/6.3V_8

10U/6.3V_8

C30

10U/6.3V_8

C456

10U/6.3V_8

C31

C39

10U/6.3V_8

C458

10U/6.3V_8

C444

10U/6.3V_8

C45

10U/6.3V_8

C452

10U/6.3V_8

C455

10U/6.3V_8

POWER CHECK

CPU

A

C459

C25

10U/6.3V_8

10U/6.3V_8

C47

C53

10U/6.3V_8

10U/6.3V_8

C445

C37

10U/6.3V_8

10U/6.3V_8

VTT [2,4,5,6,8,9,11,24,27]

VCC_CORE [2,23,24]

+1.8V [5,7,8,9,11,24,25]

C56

10U/6.3V_8

C54

.01U_4

C46

10U/6.3V_8

C460

10U/6.3V_8

C446

10U/6.3V_8

B

C21

10U/6.3V_8

CPU_VCCA

C34

C60

.01U_4

.01U_4

decouple CAP

C52

10U/6.3V_8

C457

10U/6.3V_8

C447

10U/6.3V_8

B

CPU_VCCA

C61

10U/6.3V_8

C22

.01U_4

decouple CAP

VCC_CORE

C29

10U/6.3V_8

VCC_CORE

C453

10U/6.3V_8

VCC_CORE

C448

10U/6.3V_8

R15 1K/F_6

VTT

A0 : STUFF

A1 : NC

R24 0_8

+1.8V

at least 40 M IL shape

1.5V FOR DOTHAN ONLY

REMOVE +1.5V

C

R14

2K/F_6

CPU_VCCA

C

COMP0

COMP1

COMP2

COMP3

0.5" max

5 MIL

R330

*1K_4

VCC_CORE

TEST1

TEST2

R25

*1K_4

U20B

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

AD26

GTLREF0

E26

GTLREF1

G1

GTLREF2

AC1

GTLREF3

C5

TEST1

F23

TEST2

AC26

VCCA3

N1

VCCA2

B1

VCCA1

F26

VCCA0

D6

VCC00

D8

VCC01

D18

VCC02

D20

VCC03

D22

VCC04

E5

VCC05

E7

VCC06

E9

VCC07

E17

VCC08

E19

VCC09

E21

VCC10

F6

VCC11

F8

VCC12

F18

VCC13

F20

VCC14

F22

VCC15

G5

VCC16

G21

VCC17

H6

VCC18

H22

VCC19

J5

VCC20

J21

VCC21

K22

VCC22

U5

VCC23

V6

VCC24

V22

VCC25

W5

VCC26

W21

VCC27

Y6

VCC28

Y22

VCC29

AA5

VCC30

AA7

VCC31

AA9

VCC32

AA11

VCC33

AA13

VCC34

AA15

VCC35

AA17

VCC36

AA19

VCC37

AA21

VCC38

AB6

VCC39

AB8

VCC40

AB10

VCC41

AB12

VCC42

AB14

VCC43

AB16

VCC44

AB18

VCC45

AB20

VCC46

AB22

VCC47

AC9

VCC48

AC11

VCC49

AC13

VCC50

AC15

VCC51

AC17

VCC52

AC19

VCC53

AD8

VCC54

AD10

VCC55

AD12

VCC56

AD14

VCC57

AD16

VCC58

AD18

VCC59

AE9

VCC60

AE11

VCC61

AE13

VCC62

AE15

VCC63

AE17

VCC64

AE19

VCC65

AF8

VCC66

AF10

VCC67

AF12

VCC68

AF14

VCC69

AF16

VCC70

AF18

VCC71

Banias_Processor_RVS

Banias

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

D

U20C

A2

VSS

A5

VSS

A8

VSS

A11

VSS

A14

VSS

A17

VSS

A20

VSS

A23

VSS

A26

VSS

B3

VSS

B6

VSS

B9

VSS

B12

VSS

B16

VSS

B19

VSS

B22

VSS

B25

VSS

C1

VSS

C4

VSS

C7

VSS

C10

VSS

C13

VSS

C15

VSS

C18

VSS

C21

VSS

C24

VSS

D2

VSS

D5

VSS

D7

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E10

VSS

E12

VSS

E14

VSS

E16

VSS

E18

VSS

E20

VSS

E22

VSS

E25

VSS

F1

VSS

F4

VSS

F5

VSS

F7

VSS

F9

VSS

F11

VSS

F13

VSS

F15

VSS

F17

VSS

F19

VSS

F21

VSS

F24

VSS

G2

VSS

G6

VSS

G22

VSS

G23

VSS

G26

VSS

H3

VSS

H5

VSS

H21

VSS

H25

VSS

J1

VSS

J4

VSS

J6

VSS

J22

VSS

J24

VSS

K2

VSS

K5

VSS

K21

VSS

K23

VSS

K26

VSS

L3

VSS

L6

VSS

L22

VSS

L25

VSS

M1

VSS

M4

VSS

M5

VSS

M21

VSS

M24

VSS

N3

VSS

N6

VSS

N22

VSS

N23

VSS

N26

VSS

P2

VSS

P5

VSS

P21

VSS

P24

VSS

R1

VSS

R4

VSS

HBSEL1[4]

HBSEL0[4]

D

VTT

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

VCCP11

L5

VCCP12

L21

VCCP13

M6

VCCP14

M22

VCCP15

N5

VCCP16

N21

VCCP17

P6

VCCP18

P22

VCCP19

R5

VCCP20

R21

VCCP21

T6

VCCP22

T22

VCCP23

U21

VCCP24

P23

VCCP25

W4

VCCP26

CPU_VID0[23]

CPU_VID1[23]

CPU_VID2[23]

CPU_VID3[23]

CPU_VID4[23]

CPU_VID5[23]

T52

T53

T54

T51

T56

T55

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

Z0501

AE7

VCCSENSE

Z0502

AF6

VSSSENSE

Z0503

B2

NC0

Z0504

AF7

NC1

C14

NC2

Z0506

C3

NC3

C16

TEST3

E1

PSI

R6

VSS

R22

VSS

R25

VSS

T3

VSS

T5

VSS

T21

VSS

T23

VSS

T26

VSS

U2

VSS

U6

VSS

U22

VSS

U24

VSS

V1

VSS

V4

VSS

V5

VSS

V21

VSS

V25

VSS

W3

VSS

W6

VSS

W22

VSS

Banias_Processor_RVS

Size Document Number Rev

CPU ( POWER )-2

Date: Sheet of

E

W23

VSS

W26

VSS

Y2

VSS

Y5

VSS

Y21

VSS

Y24

Banias

3 OF 3

POWER, GROUND AND NC

VID

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA8

VSS

AA10

VSS

AA12

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA20

VSS

AA22

VSS

AA25

VSS

AB3

VSS

AB5

VSS

AB7

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

AB23

VSS

AB26

VSS

AC2

VSS

AC5

VSS

AC8

VSS

AC10

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AC24

VSS

AD1

VSS

AD4

VSS

AD7

VSS

AD9

VSS

AD11

VSS

AD13

VSS

AD15

VSS

AD17

VSS

AD19

VSS

AD22

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF21

VSS

AF24

VSS

PROJECT : BH2

Quanta Computer Inc.

329Thursday, December 22, 2005

E

1A

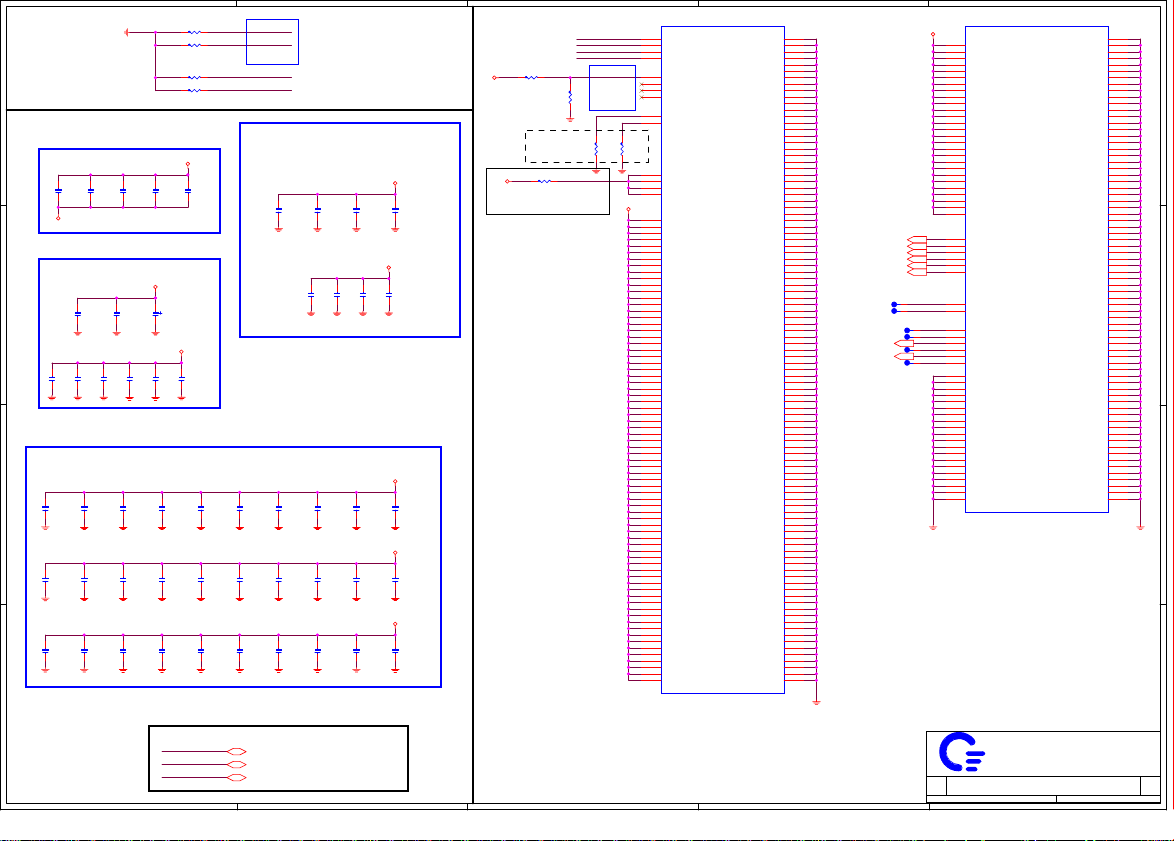

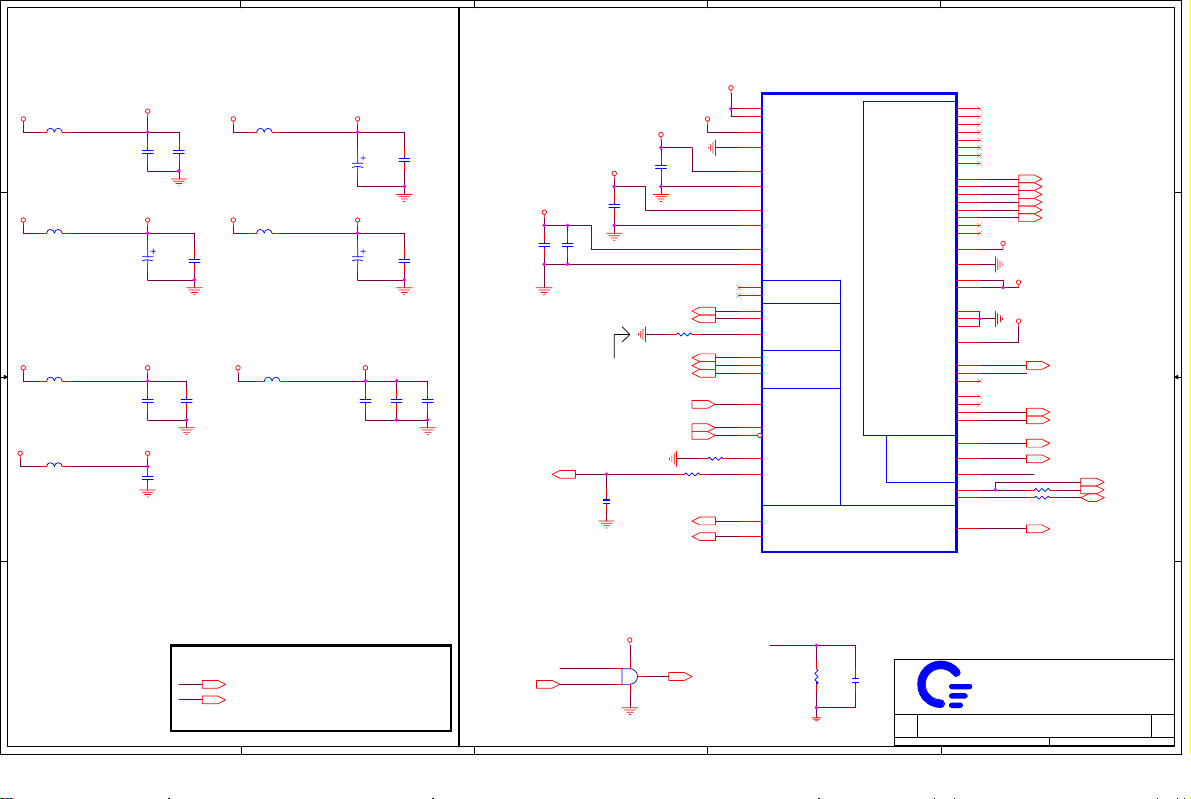

5

4

3

2

1

+3V CLK_VDD

L22 SBK160808T-301Y-S

D D

+3V

L24 SBK160808T-301Y-S

C C

CLK_VDDA

C313

C312

.1U_4

22U/16V_1206

B B

HBSEL1[3]

HBSEL0[3]

A A

C228

22U/16V_1206

CLK_VDD_USB

C221

10U/6.3V_8

L28 SBK160808T-301Y-S

R146

*0_6

R130 0_6

R138 0_6

R131

1k_6

C271

C311

.1U_4

10U/6.3V_8

PUT DECOUPLING CAPS CLOSE TO U300

POWER PIN

decouple CAP

C247

.1U_4

+3V

decouple CAP

VTT

R145

1K_6

BSEL1

BSEL0

R162

*0_6

HBSEL1 HBSEL0

0 0

0 1

POWER CHECK

CLK

5

decouple CAP

C283

C293

.1U_4

.1U_4

BSEL1 [6]

BSEL0 [6]

133 MHz

100 MHz

+3V [2,6,7,8,9,10,11,12,13,15,16,17,18,20,21,22,23,24,27]

VTT [2,3,5,6,8,9,11,24,27]

C287

.1U_4

C267

.1U_4

4

ALINK_RST#[5,9,16,20]

STP_CPU#[9,23]

CLK_VDD_USB

33P_4C242

12

Y4

14.318MHz

33P_4C241

Parallel Resonance Crystal

SCLK[10,13]

SDATA[10,13]

Ioh = 5 * Iref

(2.32mA)

Voh = 0.71V @ 60 ohm

CLK_EN#

EXT_CPU_STP#

CLK_EN#[23]

3

+3V

R126

Reserved

*4.7K_6

32

Q13

1

*CH2507S

VDDA

VSSA

CPUT0

CPUC0

CPUT1

CPUC1

CPUT2

CPUC2

SRCT0

SRCC0

SRCST0

SRCSC0

SRCST1

SRCSC1

SRCT1

SRCC1

SRCT2

SRCC2

SRCT3

SRCC3

SRCT4

SRCC4

SRCT5

SRCC5

CLKREQ0

CLKREQ1

PCIF0/CK410#

USB_48

REF1/FSB

REF0/FSA

REF2

EXT_CPU_STP#

39

38

47

46

CPUCLK_R

43

CPUCLK#_R

42

NBCLK_R

41

NBCLK#_R

40

ALINKCLK_R

34

ALINKCLK#_R

33

30

29

27

28

SBSRCCLK_R

24

SBSRCCLK#_R

25

22

23

18

19

16

17

12

13

10

11

R156 10K_6

50

USBCLK_R

4

9

FSC

53

54

52

OSC14M_R

R127 0_6

CLK_VDD CLK_VDDA

U10

45

VDDCPU

35

VDD_SRC

32

VDD_SRC1

21

VDD_SRC2

14

VDD_SRC3

3

VDD_48

51

VDD_PCI

56

VDD_REF

44

VSS_CPU

36

VSS_SRC

31

VSS_SRC1

26

VSS_SRC2

20

VSS_SRC3

15

VSS_SRC4

5

VSS_48

49

VSS_PCI

55

VSS_REF

1

XIN

2

XOUT

6

VTTPWRGD#/PD

48

CPU_STP#

7

SCLK

8

SDATA

37

IREF

R190

475/F_6

ICS951413CGLFT

CY28RS400 and ICS951411

are fully pin compatible and

can be interchanged without

any hardware modification.

CK410 FREQUENCY SELECT TABLE(MHZ)

CPU

FSA

FSB

FSC

BSEL0

0

0

0

0

1

1

1

1

BSEL1

0

0

1

1

0

0

1

1

MHz

266.66

0

133.33

1

200.00

0

166.66

1

333.33

0

100.00

1

400.00

0

Rsvd

1

2

1- PLACE ALL THE SERIES TERMINATION

RESISTORS AS CLOSE AS CLK GEN AS

POSSIBLE

2- ROUTE ALL CPUCLK/#, NBCLK/# AND

ITPCLK/# AS DIFFERENT PAIR RULE

R164 33_4

R172 33_4

R175 33_4

R182 33_4

R194 33_4

R199 33_4

R192 33_4

R196 33_4

R157 33_6

FSC

FSB

FSA

R161 4.7K_4

R151 4.7K_4

R142 4.7K_4

R139 22_4

R153 33_4

BSEL0

BSEL1

C256

*10P_4

Size Document Number Rev

EXTERNAL CLKGEN

Date: Sheet of

R163 49.9/F_4

R171 49.9/F_4

R174 49.9/F_4

R183 49.9/F_4

R193 49.9/F_4

R198 49.9/F_4

R191 49.9/F_4

R195 49.9/F_4

CLK_VDD

C265

*10P_4

SB_OSCIN [7,10]

OSC14M [7 ]

C212

*10P_4

PROJECT : BH2

Quanta Computer Inc.

NBCLK# [7]

NBCLK [7]

HCLK_CPU# [2]

HCLK_CPU [2]

ALINKCLK [6]

ALINKCLK# [6]

SBSRCCLK [9]

SBSRCCLK# [9]

USBCLK [10]

429Thursday, De cember 22, 2005

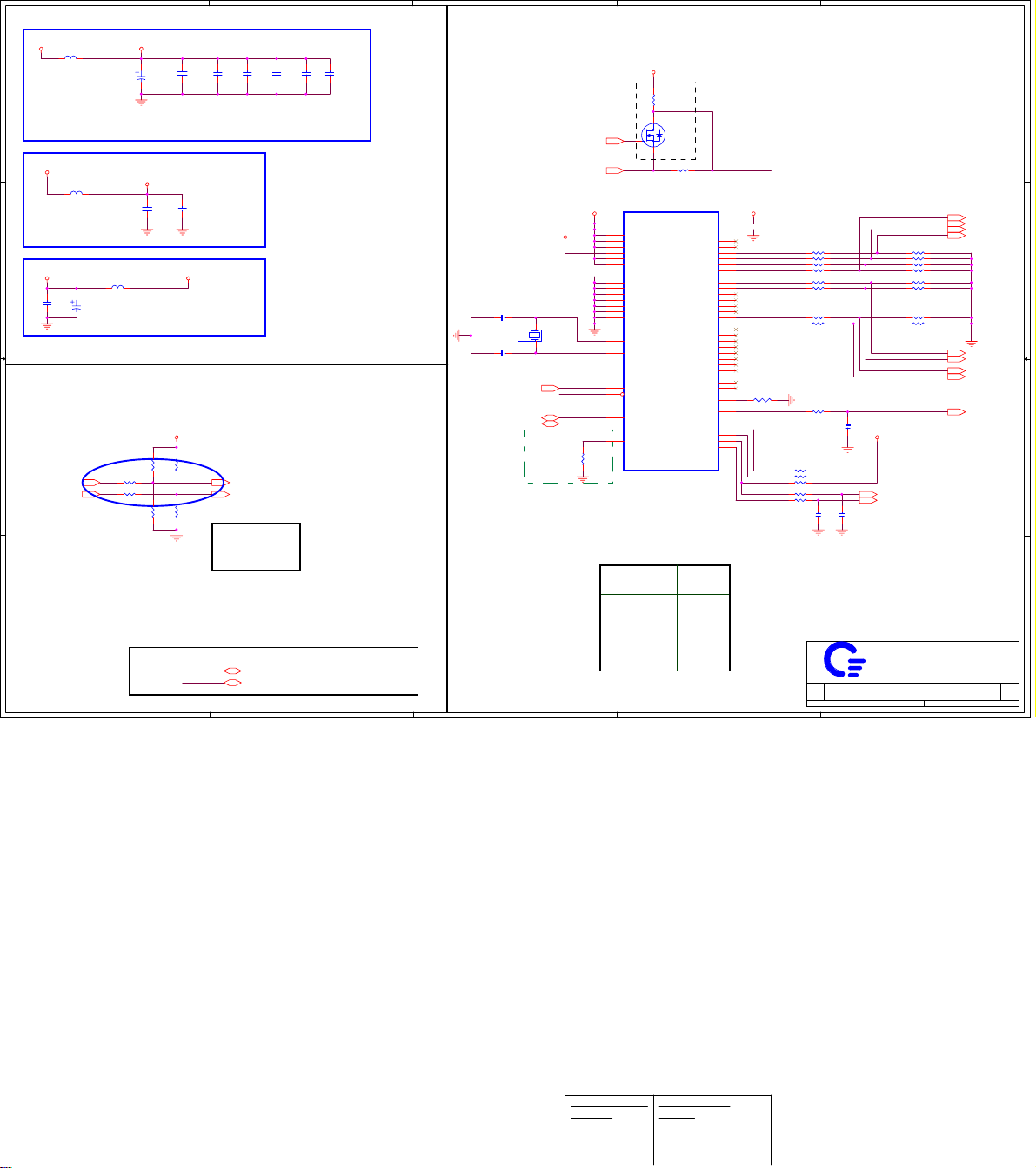

1

1A

REFERENCE

DESIGN

THESE SCHEMATICS ARE

SUBJECT TO MODIFICATION

AND DESIGN IMPROVEMENTS.

PLEASE CONTACT ATI FIELD

APPLICATION ENGINEERS

RESTRICTION

NOTICE

THESE SCHEMATICS CONTAIN

INFORMATION WHICH IS PROPRIETARY

TO AND IS THE PROPERTY OF ATI, AND

MAY NOT BE USED, REPRODUCED OR

DISCLOSED IN ANY MANNER WITHOUT

PERMISSION

5

M_DM[7..0]

M_DQS[7..0]

M_DQS#[7..0]

M_CLKOUT0#[13]

M_CLKOUT0[13]

M_CLKOUT1#[13]

M_CLKOUT1[13]

M_CLKOUT3#[13]

M_CLKOUT3[13]

M_CLKOUT4#[13]

M_CLKOUT4[13]

MA[17..0]

M_CKE0[13]

M_CKE1[13]

M_CKE2[13]

M_CKE3[13]

M_CS#0[13]

M_CS#1[13]

M_CS#2[13]

M_CS#3[13]

M_ODT0[13]

M_ODT1[13]

M_ODT2[13]

M_ODT3[13]

MA[17..0][13]

D D

M_DM[7..0][13]

M_RAS#[13]

M_CAS#[13]

M_WE#[13]

M_DQS[7..0][13]

C C

M_DQS#[7..0][13]

B B

U17C

MA0

AK27

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MA15

MA16

MA17

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_DQS0

M_DQS1

M_DQS2

M_DQS3

M_DQS4

M_DQS5

M_DQS6

M_DQS7

M_DQS#0

M_DQS#1

M_DQS#2

M_DQS#3

M_DQS#4

M_DQS#5

M_DQS#6

M_DQS#7

MEM_A0

AJ27

MEM_A1

AH26

MEM_A2

AJ26

MEM_A3

AH25

MEM_A4

AJ25

MEM_A5

AH24

MEM_A6

AH23

MEM_A7

AJ24

MEM_A8

AJ23

MEM_A9

AH27

MEM_A10

AH22

MEM_A11

AJ22

MEM_A12

AF28

MEM_A13

AJ21

MEM_A14

AG27

MEM_A15

AJ28

MEM_A16

AH21

MEM_A17

AJ17

MEM_DM0

AG15

MEM_DM1

AE20

MEM_DM2

AF25

MEM_DM3

Y27

MEM_DM4

AB28

MEM_DM5

R26

MEM_DM6

R28

MEM_DM7

AJ29

MEMB_RAS#

AG28

MEMB_CAS#

AH30

MEMB_WE#

AJ18

MEM_DQS0P

AE14

MEM_DQS1P

AF22

MEM_DQS2P

AE25

MEM_DQS3P

W27

MEM_DQS4P

AB29

MEM_DQS5P

P25

MEM_DQS6P

R29

MEM_DQS7P

AH17

MEM_DQS0N

AF15

MEM_DQS1N

AE22

MEM_DQS2N

AF26

MEM_DQS3N

W26

MEM_DQS4N

AB30

MEM_DQS5N

R25

MEM_DQS6N

R30

MEM_DQS7N

AC26

MEM_CK0N

AC25

MEM_CK0P

AF16

MEM_CK1N

AE16

MEM_CK1P

V29

MEM_CK2N

V30

MEM_CK2P

AC24

MEM_CK3N

AC23

MEM_CK3P

AG17

MEM_CK4N

AF17

MEM_CK4P

W29

MEM_CK5N

W28

MEM_CK5P

AH20

MEM_CKE0

AJ20

MEM_CKE1

AE24

MEM_CKE2

AE21

MEM_CKE3

AH29

MEM_CS0#

AG29

MEM_CS1#

AH28

MEM_CS2#

AF29

MEM_CS3#

AG30

MEM_ODT0

AE28

MEM_ODT1

AC30

MEM_RSRV2

Y30

MEM_RSRV3

RC420MB

MPVSS need to connect to GND plane

immediately through

a dedicated VIA

PART 3 OF 6

MEM_B I/F

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_COMPN

MEM_COMPP

MEM_CAP2

MEM_CAP1

MEM_VREF

MEM_VMODE

MPVDD

MPVSS

4

AJ16

AH16

AJ19

AH19

AH15

AK16

AH18

AK19

AF13

AF14

AE19

AF19

AE13

AG13

AF18

AE17

AF20

AF21

AG23

AF24

AG19

AG20

AG22

AF23

AD25

AG25

AE27

AD27

AE23

AD24

AE26

AD26

AA25

Y26

W24

U25

AA26

Y25

V26

W25

AC28

AC29

AA29

Y29

AD30

AD29

AA30

Y28

U27

T27

N26

M27

U26

T26

P27

P26

U29

T29

P29

N29

U28

T28

P28

N27

AE29

AJ15

N30

AJ14

AB27

AD28

AB26

AA27

MDQ0

MDQ1

MDQ2

MDQ3

MDQ4

MDQ5

MDQ6

MDQ7

MDQ8

MDQ9

MDQ10

MDQ11

MDQ12

MDQ13

MDQ14

MDQ15

MDQ16

MDQ17

MDQ18

MDQ19

MDQ20

MDQ21

MDQ22

MDQ23

MDQ24

MDQ25

MDQ26

MDQ27

MDQ28

MDQ29

MDQ30

MDQ31

MDQ32

MDQ33

MDQ34

MDQ35

MDQ36

MDQ37

MDQ38

MDQ39

MDQ40

MDQ41

MDQ42

MDQ43

MDQ44

MDQ45

MDQ46

MDQ47

MDQ48

MDQ49

MDQ50

MDQ51

MDQ52

MDQ53

MDQ54

MDQ55

MDQ56

MDQ57

MDQ58

MDQ59

MDQ60

MDQ61

MDQ62

MDQ63

MEM_COMPN

MEM_COMPP

MEM_VREF

R141 1K_6

L19 SBK160808T-301Y-S

C173

1U_6

MDQ[63..0]

R149 61. 9/F_6

R285 61. 9/F_6

C440 .47U_6

C436 .47U_6

+1.8VSUS

+1.8VSUS

+1.8V

MDQ[63..0] [13]

SUS_STAT#[10]

ALINK_RST#[4,9,16,20]

3

D9 SW1010C

D10 SW1010C

21

21

+1.8VSUS

R185

27K_6

VTT

+1.8V

HA#[3..31][2]

HREQ#[0..4][2]

HADSTB0#[2]

HADSTB1#[2]

ADS#[2]

BNR#[2]

BPRI#[2]

DEFER#[2]

DRDY#[2]

DBSY#[2]

DPWR#[2]

HLOCK#[2]

HTRDY#[2]

HITM#[2]

HIT#[2]

RS#[2..0][2]

CPURST#[2]

NB_PWRGD[7,21]

R89 49.9/F_4

R97 24.9/F_6

L13 SBK160808T-301Y-S

C428

4.7U/10V_8

C81

1U_6

CPU_COMP_P

CPU_COMP_N

Place close to NB

NB_GTLREF

C82

220P_6

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

T9

T5

CPVDD

T17

T19

R269

1.8K_6

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

RS#0

RS#1

RS#2

2

G28

H26

G27

G30

G29

G26

H28

J28

H25

K28

H29

J29

K24

K25

F29

G25

F26

F28

E29

H27

M28

K29

K30

J26

L28

L29

M30

K27

M29

K26

N28

L26

N25

L25

N24

L27

F25

F24

E23

E25

G24

F23

G22

E27

F22

E24

D26

E26

G23

D23

D25

C11

E11

AH14

B11

D11

H21

H20

H22

AH13

AJ13

A3

E3

C4

U17A

RC420MB

PART 1 OF 6

CPU_A3#

CPU_A4#

CPU_A5#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A15#

CPU_A16#

CPU_REQ0#

CPU_REQ1#

CPU_REQ2#

CPU_REQ3#

CPU_REQ4#

CPU_ADSTB0#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPU_ADSTB1#

CPU_ADS#

CPU_BNR#

CPU_BPRI#

CPU_DEFER#

CPU_DRDY#

CPU_DBSY#

CPU_DPWR#

CPU_LOCK#

CPU_TRDY#

CPU_HITM#

CPU_HIT#

CPU_RS0#

CPU_RS1#

CPU_RS2#

RESERVED0

CPU_CPURST#

RESERVED1

SUS_STAT#

SYSRESET#

POWERGOOD

CPU_COMP_P

CPU_COMP_N

CPVDD

CPVSS

CPU_VREF

THERMALDIODE_P

THERMALDIODE_N

TESTMODE

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_DSTB0N#

CPU_DSTB0P#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

ADDR. GROUP 1 ADDR. GROUP 0CONTROLMISC.

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_DSTB1N#

CPU_DSTB1P#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_DSTB2N#

CPU_DSTB2P#

CPU_D48#

AGTL+ I/F

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

CPU_DSTB3N#

CPU_DSTB3P#

CPVSS need to connect to GND plane

immediately through

a dedicated VIA

1

HD#[0..63]

HD#0

E28

HD#1

D28

HD#2

D29

HD#3

C29

HD#4

D30

HD#5

C30

HD#6

B29

HD#7

C28

HD#8

C26

HD#9

B25

HD#10

B27

HD#11

C25

HD#12

A27

HD#13

C24

HD#14

A24

HD#15

B26

C27

A28

B28

HD#16

C19

HD#17

C23

HD#18

C20

HD#19

C22

HD#20

B22

HD#21

B23

HD#22HA#22

C21

HD#23

B24

HD#24

E21

HD#25

B21

HD#26

B20

HD#27

G19

HD#28

F21

HD#29

B19

HD#30

E20

HD#31

D21

A21

D22

E22

HD#32

C18

HD#33

F19

HD#34

E19

HD#35

A18

HD#36

D19

HD#37

B18

HD#38

C17

HD#39

B17

HD#40

E17

HD#41

B16

HD#42

C15

HD#43

A15

HD#44

B15

HD#45

F16

HD#46

G18

HD#47

F18

C16

D18

E18

HD#48

E16

HD#49

D16

HD#50

C14

HD#51

B14

HD#52

E15

HD#53

D15

HD#54

C13

HD#55

E14

HD#56

F13

HD#57

B13

HD#58

A12

HD#59

C12

HD#60

E12

HD#61

D13

HD#62

D12

HD#63

B12

E13

F15

G15

HD#[0..63] [2]

HDBI0# [2]

HDSTBN0# [2]

HDSTBP0# [2]

HDBI1# [2]

HDSTBN1# [2]

HDSTBP1# [2]

HDBI2# [2]

HDSTBN2# [2]

HDSTBP2# [2]

HDBI3# [2]

HDSTBN3# [2]

HDSTBP3# [2]

+1.8VSUS

R137

C200

.1U_6

1K/F_6

A A

POWER CHECK

CLG

5

VTT [2,3,4,6,8,9,11,24,27]

+1.8VSUS [8,13,24,25,27]

+1.8V [3,7,8,9,11,24,25]

4

C185

.1U_6

R133

1K/F_6

VTT

Place close to NB,

R81

Use 10/10

width/space

49.9/F_4

MEM_VREF NB_GTLREF

3

R62

100/F_6

C83

1U_6

+1.8VSUS

decouple CAP decouple CAP

C203

C210

C167

C182

.1U_4

.1U_4

.1U_4

.1U_4

Size Document Number Rev

RC400MB-AGTL+ I/F

2

Date: Sheet of

+1.8V

C94

C421

C419

.1U_4

.1U_4

.1U_4

PROJECT : BH2

Quanta Computer Inc.

529Thursday, D e c ember 22, 2005

1

C91

.1U_4

1A

5

4

3

2

1

NB strapping

D D

BMREQ#[9]

C C

VSYNC[7,15] BSEL0 [4]

B B

SCL_STRAP[7]

STRP_DATA[7]

R263 4.7K_6

R262

*4.7K_6

R83 *4.7K_6

R82

4.7K_6

R114 4.7K_6

R109

*4.7K_6

Q9

MMBT3904

R93 4.7K_6

1 3

MMBT3904

2

Q8

+3V

R264

*4.7K_6

Q25 MMBT3904

+3V

R88

*4.7K_6

Q11 *MMBT3904

+3V

R118

4.7K_6

Q24 *MMBT3904

R87 *4.7K_6

R39 4.7K_6

2

1 3

VTT

R266

4.7K_6

2

13

VTT

R101

*4.7K_6

2

13

VTT

R265

*4.7K_6

2

13

+3V

R29 1K_6

+3V

BSEL0 [4]

BSEL1 [4]HSYNC[7,15]

DAC_SCL: CPU VCC

DEFAULT:0

0: MOBILE CPU

1: DESKTOP CPU

PWROK [2,10,21]

STRP_DATA:Debug strap

DEFAULT:1

0: MEMORY CHANNEL STRAPING

1: E2PROM STRAPING

BSEL1 BSEL0

0 0

133 MHz

0 1

100 MHz

BMREQ#&HSYNC&VSYNC: FSB CLK SPEED

DEFAULT: 101

101: 100 MHZ RC420MB

001: 133 MHZ RC420MD

U17B

J5

J4

K4

L4

L6

L5

M5

M4

N4

P4

P6

P5

R5

R4

T4

T3

U6

U5

V5

V4

W4

W3

Y6

Y5

AA5

AA4

AB4

AB3

AC6

AC5

AD5

AD4

AF8

AG8

AG6

AG7

AK7

AJ7

AG4

AH4

AG9

A_RX0N[9]

A_RX1P[9]

A_RX1N[9]

ALINKCLK[4]

ALINKCLK#[4]

BMREQ#[9]

AG10

AE9

AF10

K2

L2

T10

T11

M2

M1

H2

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_CLKP

SB_CLKN

GFX_CLKP

GFX_CLKN

BMREQ#

PART 2 OF 6

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

PCE_TXSET

PCE_ISET

PCE_PCAL

PCE_NCAL

N1

N2

P2

R2

R1

T1

T2

U2

V2

V1

W1

W2

Y2

AA2

AA1

AB1

AB2

AC2

AD2

AD1

AE1

AE2

AF2

AG2

AG1

AH1

AH2

AJ2

AJ3

AJ4

AK4

AJ5

AJ8

AJ9

AE6

AF6

AJ6

AK6

AE4

AF4

AJ10

AJ11

AK9

AK10

AK13

AJ12

AH12

AG12

A_TX0P_C

A_TX0N_C

A_TX1P_C

A_TX1N_C

PCE_TXSET

PCE_ISET

PCE_PCAL

PCE_NCAL

C418 .1U_4

C412 .1U_4

R284 8.25K_6

R283 10K_6

R273 150/F_6

R184 82.5/_6

C420 .1U_4

C415 .1U_4

+1.2V

A_TX0P [9]A_RX0P[9]

A_TX0N [9]

A_TX1P [9]

A_TX1N [9]

RC420MB

A A

CLG

5

POWER CHECK

+1.2V [8,24,27]

+3V [2,4,7 , 8 , 9 , 10,11,12,13,15,16,17,18,20,21,22,23,24, 27]

VTT [2,3,4,5, 8 , 9,11, 24,27]

4

3

2

Size Docum en t N u m be r Re v

RC400MB-PCIE LINK I/F

Date: Sheet

PROJECT : BH2

Quanta Computer Inc.

of

629Thursday, D e cember 22, 2005

1

1A

5

4

3

2

1

decouple CAP

NB_VDDR

FOR VDDR3 ,S0 max:100mA

D D

+3V AVDD_NB+3V

L15 S BK 160808T-301Y-S

C C

L11 S BK 160808T-301Y-S

+1.8V

L32 SBK160808T-301Y-S

B B

FOR CPVDD,MPVDD,AVDDQ,PLLVDD,AVDDDI,LPVDD,LVDDR18A,LVDDR18D

,S0 total max:300mA

NB_VDDR

C112

C141

1U_6

.1U_6

AVDDQ+1.8V PLVDD+1.8V

C416

10U/6.3V_8

PUT AVDD_NB, AVDDQ,NB_VDDR,

PLVDD,NB_LPVDD,NB_LVDDR18D,NB_LVDDR18A DECOUPLING

CAPS ON THE BOTTOM SIDE, CLOSE TO BALLS

NB_LPVDD+1.8V

C111

C70

.1U_6

1U_6

NB_LVDDR18D

C75

1U_6

FOR AVDD ,S0 max:250mA

L12 SB K160808T-301Y-S

L14 SB K160808T-301Y-SL33 S BK 160808T-301Y-S

C413

1U_6

+1.8V

L36 SBK160808T-301Y-S

C74

10U/6.3V_8

C119

10U/6.3V_8

NB_LVDDR18A

C437

.1U_6

C434

.1U_6

C87

.1U_6

C124

1U_6

RSET resistor need 10mils

trace with at least 10mils

spacing.

Also need to connect GND

C435

at AVSSQ HF cap.

1U_6

AVDD_NB

+1.8V

C86

AVDDQ

.1U_6

C106

.1U_4

C109

*22P_4

C409

.1U_6

VSYNC[6,15]

HSYNC[6,15]

R91 715/F_6

VGA_RED[15]

VGA_GRN[15]

VGA_BLU[15]

OSC14M[4]

NBCLK[4]

NBCLK#[4]

R105 *22_4

PHL_CLK[15]

PHL_DATA[15]

R99 10K_6

PLVDD

C125

.1U_6

SB_OSCIN[4,10]

G5

G4

C9

C10

D8

C8

B8

B9

H10

H9

J2

H3

B3

C3

B10

F10

E10

D10

G1

J1

K1

G2

F1

D2

C1

U17D

VDDR3_1

VDDR3_2

AVDD

AVSSN

AVDDDI

AVSSDI

AVDDQ

AVSSQ

PLLVDD

PLLVSS

TMDS_HPD

DDC_DATA

DACVSYNC

DACHSYNC

RSET

RED

GREEN

BLUE

OSCIN

CPU_CLKP

CPU_CLKN

TVCLKIN

OSCOUT

I2C_CLK

I2C_DATA

RC420MB

PART 4 OF 6

CRT

CLK. GEN.

B4

TXOUT_U0N

A4

TXOUT_U0P

B5

TXOUT_U1N

C6

TXOUT_U1P

B6

TXOUT_U2N

A6

TXOUT_U2P

B7

TXOUT_U3N

A7

TXOUT_U3P

E5

TXOUT_L0N

F5

TXOUT_L0P

D5

TXOUT_L1N

C5

TXOUT_L1P

E6

TXOUT_L2N

D6

TXOUT_L2P

E7

TXOUT_L3N

E8

TXOUT_L3P

LPVDD

LPVSS

LVDDR18A_1

LVDDR18A_2

LVSSR_1

LVSSR_2

LVSSR_3

LVDDR18D

LVDS_DIGON

LVDS_BLON

LVDS_BLEN

TXCLK_UP

TXCLK_UN

TXCLK_LP

TXCLK_LN

DACSCL

SVID

DACSDA

STRP_DATA

NB_LPVDD

J8

J7

H8

H7

G9

G8

G7

C7

E2

LVDS_BLON

G3

F2

F8

F7

F6

G6

D9

C

F9

Y

COMP

E9

COMP

B2

C2

DAC_SCL is totem-pole output

D1

TXLOUT0- [1 5]

TXLOUT0+ [15]

TXLOUT1- [1 5]

TXLOUT1+ [15]

TXLOUT2- [1 5]

TXLOUT2+ [15]

NB_LVDDR18A

NB_LVDDR18D

R61 0_6

R60 0_6

LCD_POWER_ON [15]

TXLCLKOUT+ [ 15]

TXLCLKOUT- [ 15]

TV_C/R [15]

TV_Y/G [15]

SCL_STRAP [6]

DDCCLK [15]

DDCDAT [15]

STRP_DATA [6]

+3V

A A

POWER CHECK

+3V [2,4, 6 , 8, 9,10,11,12,13,15,16,17,18, 20,21, 22,23, 24,27]

+1.8V [3,5 , 8 , 9,11,24,25]

NB_PWRGD[5,21]

LVDS_BLON

U5

53

1

4

2

SN74LVC1G08DCKR

BLON [15]

CLG

5

4

3

COMP

R113

75/F_4

C95

100P_4

Size Docum en t N u m be r Re v

RC400MB-VIDEO & CLKGEN

2

Date: Sheet

PROJECT : BH2

Quanta Computer Inc.

of

729Thursday, D e cember 22, 2005

1

1A

5

4

3

2

1

+1.2V

FOR VDD_CORE S0 max:5A

C308

+

C183

C147

.1U_4

1U_6

C146

.1U_4

C181

1U_6

C163

.1U_4

470U/2.5V_7343

D D

+1.2V

C148

.1U_4

C171

1U_6

C164

.1U_4

decouple CAP

C158

C202

1U_6

1U_6

C162

C177

.1U_4

.1U_4

C209

C207

C144

1U_6

1U_6

1U_6

C176

.1U_4

Power sequence requirement

D13 SW1010C

2 1

+3V

+1.8V

C C

FOR VDD_18 ,S0 max:300mA

D11 SW1010C

2 1

L25 TI201209G121

21

C129

1U_6

D12

SW1010C

VDD18

C197

1U_6

C552

C205

C126

+

1U_6

1U_6

*100U/6.3V-3528

decouple CAP

C179

1U_6

decouple CAP

C263

C262

C201

1U_6

1U_6

1U_6

VDDA18

FOR VDDA_18 ,S0 max:600mA

L16 TI201209G121

+1.8V

B B

C213

1U_6

VTT

FOR VDD_CPU ,S0 max:3.5A

C73

22U/16V_1206

VTT

C97

C107

.1U_4

.1U_4

+1.8VSUS

FOR VDD_MEM ,S0 max:7A

C309

100U/10V_7343

+1.8VSUS

+1.2V

C307

470U/2.5V_7343

+1.2V

C152

1U_6

C310

*100U/10V_7343

C227

C277

C276

.1U_4

.1U_4

.1U_4

FOR VDDA_12 ,S0 max:2.5A

C286

+

+

150U/4V_3528

C172

C170

1U_6

1U_6

+1.2V

C80

C79

C78

1U_6

1U_6

1U_6

C121

C122

C77

1U_6

1U_6

1U_6

decouple CAP

C105

C143

.1U_4

.1U_4

C113

.1U_4

C161

.1U_4

decouple CAP

C243

C208

1U_6

1U_6

C204

C192

C224

.1U_4

.1U_4

.1U_4

decouple CAP

C137

C128

.1U_4

.1U_4

C195

C217

C191

1U_6

1U_6

1U_6

C282

C230

C248

1U_6

1U_6

1U_6

VDD18

VDDA18

+1.2V

C229

C159

C180

1U_6

1U_6

1U_6

U16

M13

M15

M17

R16

V15

N12

T15

N14

N16

N18

M19

R12

P13

P15

P17

P19

U12

T13

U14

T17

U18

T19

V13

R14

V17

R18

V19

W12

W14

W16

W18

J9

AB22

AB9

J22

Y8

U8

AB8

Y7

U7

AE11

AC9

AD10

AC10

AG11

AF11

H5

H4

P8

P7

L7

L8

J6

AC7

AB7

U17E

VDD_CORE#M12

VDD_CORE#M13

VDD_CORE#M14

VDD_CORE#M17

VDD_CORE#M18

VDD_CORE#M19

VDD_CORE#N12

VDD_CORE#N13

VDD_CORE#N14

VDD_CORE#N17

VDD_CORE#N18

VDD_CORE#N19

VDD_CORE#P12

VDD_CORE#P13

VDD_CORE#P14

VDD_CORE#P17

VDD_CORE#P19

VDD_CORE#U12

VDD_CORE#U13

VDD_CORE#U14

VDD_CORE#U17

VDD_CORE#U18

VDD_CORE#U19

VDD_CORE#V13

VDD_CORE#V14

VDD_CORE#V17

VDD_CORE#V18

VDD_CORE#V19

VDD_CORE#W12

VDD_CORE#W14

VDD_CORE#W17

VDD_CORE#W18

VDD_18

VDD_18#AF26

VDD_18#AF9

VDD_18#J26

VDDA_18#U8

VDDA_18#AD8

VDDA_18#W6

VDDA_18#AA8

VDDA_18#AA7

VDDA_18#AE7

VDDA_18#AD7

VDDA_18#AC8

VDDA_18#AC7

VDDA_18#AG6

VDDA_18#AF6

VDDA_12#K6

VDDA_12#K4

VDDA_12#F6

VDDA_12#F5

VDDA_12#B3

VDDA_12#A3

VDDA_12#B4

VDDA_12#M8

VDDA_12#W5

RC420MB

PART 5 OF 6

CORE POWER

POWER

PCIE IF

PCIE POWER

VDD_MEM#AB30

VDD_MEM#AJ21

VDD_MEM#AK21

VDD_MEM#AC13

VDD_MEM#AC14

VDD_MEM#AC15

VDD_MEM#AC18

VDD_MEM#AC21

VDD_MEM#AD10

VDD_MEM#AD13

VDD_MEM#AD15

VDD_MEM#AD18

VDD_MEM#AD21

VDD_MEM#AE15

VDD_MEM#AE18

VDD_MEM#AE21

VDD_MEM#AG27

VDD_MEM#AJ30

VDD_MEM#AK18

VDD_MEM#AK24

VDD_MEM#AK9

VDD_MEM#W23

VDD_CPU#H17

VDD_CPU#H19

VDD_CPU#K23

VDD_CPU#L23

VDD_CPU#L24

VDD_CPU#M23

VDD_CPU#M24

VDD_CPU#T23

VDD_CPU#U23

VDD_CPU#U24

VDD_CPU#V23

MEM POWER

VDD_CPU#V24

VDD_CPU#G16

VDD_CPU#G15

VDD_CPU#F22

VDD_CPU#F19

VDD_CPU#F16

VDD_CPU#F15

VDD_CPU#E15

VDD_CPU#A16

VDD_CPU#H16

VDD_CPU#H15

VDD_CPU#G22

VDD_CPU#G21

CPU IF POWER

VDD_CPU#G19

VDDA_12#N8

VDDA_12#C3

VDDA_12#R7

VDDA_12#R8

VDDA_12#U7

VDDA_12#B2

VDDA_12#K8

VDDA_12#L7

VDDA_12#L8

+1.8VSUS

Y24

AC21

AD21

AC13

AD23

AC16

AD19

AD22

V23

AD13

AD16

AC19

AB24

AK24

T24

AK28

AB23

Y23

AK21

T23

V24

AC22

VTT

H11

H13

G20

L23

L24

P23

N23

H17

G17

H14

F17

G14

A10

H16

H23

H12

F12

G12

F11

P24

H19

G11

H24

G16

G13

+1.2V

AC8

K6

M8

T8

T7

M7

W8

W7

AD9

AB5

AB6

AA8

AA7

AD7

AD8

AF7

AE8

AG5

AH5

AH3

AH8

AH7

AH6

AD3

AC3

AA3

AF5

AF3

AF9

AH9

AH10

AC20

A29

W30

W23

AA28

AJ30

AC12

AC15

AD12

AD15

AD18

AC17

AE30

AD14

AC11

AF12

AF27

AC18

AG14

AG18

AG21

AK25

V27

AJ1

AD20

AK12

AK15

AK18

AK2

AH11

AC27

W5

W6

V8

V7

R8

N8

R7

N7

T6

T5

N6

N5

K5

Y3

V3

U3

R3

P3

M3

L3

J23

K8

F4

J3

U17F

VSSA#U5

VSSA#U6

VSSA#Y5

VSSA#Y6

VSSA#P8

VSSA#P7

VSSA#U8

VSSA#U7

VSSA#Y7

VSSA#Y8

VSSA#L8

VSSA#K7

VSSA#AD7

VSSA#A2

VSSA#AF5

VSSA#AC6

VSSA#AC5

VSSA#P6

VSSA#P5

VSSA#L6

VSSA#L5

VSSA#H6

VSSA#H5

VSSA#P4

VSSA#AE3

VSSA#AD3

VSSA#AC3

VSSA#AA3

VSSA#Y3

VSSA#V3

VSSA#U3

VSSA#R3

VSSA#P3

VSSA#M3

VSSA#L3

VSSA#J3

VSSA#H3

VSSA#F3

VSSA#N3

VSSA#AG3

VSSA#AE9

VSSA#AH7

VSS#A15

VSS#A24

VSS#A29

VSS#AA23

VSS#AA24

VSS#AA30

VSS#AB27

VSS#AC12

VSS#AC16

VSS#AC8

VSS#AD12

VSS#AD16

VSS#AD19

VSS#AD23

VSS#AD30

VSS#AD8

VSS#AD9

VSS#AE12

VSS#AE27

VSS#AC19

VSS#AG12

VSS#AF7

VSS#AG18

VSS#AG21

VSS#AG9

VSS#AH28

VSS#AJ1

VSS#AK10

VSS#AK13

VSS#AK16

VSS#AK19

VSS#AK2

VSS#AH11

VSS#AJ11

VSS#AK25

RC420MB

PART 6 OF 6

GND

VSS#M15

VSS#G14

VSS#G18

VSS#G27

VSS#G3

VSS#H13

VSS#H14

VSS#H18

VSS#H23

VSS#H4

VSS#J23

VSS#J24

VSS#J30

VSS#K27

VSS#V30

VSS#U19

VSS#M16

VSS#AD11

VSS#M30

VSS#N15

VSS#N16

VSS#N23

VSS#N27

VSS#G5

VSS#P15

VSS#P16

VSS#P23

VSS#P24

VSS#R12

VSS#R13

VSS#R14

VSS#R15

VSS#R16

VSS#R17

VSS#R18

VSS#R19

VSS#R23

VSS#R24

VSS#R30

VSS#T12

VSS#T13

VSS#T14

VSS#T15

VSS#T16

VSS#T17

VSS#T18

VSS#T19

VSS#T27

VSS#U15

VSS#U16

VSS#V15

VSS#V16

VSS#W16

VSS#W27

VSS#V12

VSS#W13

VSS#V14

VSS#W15

VSS#Y23

VSS#Y24

VSS#C19

VSS#C17

VSS#AH26

VSS#AH25

VSS#AG25

VSS#F30

VSS#F25

VSS#D27

VSS#D25

VSS#D23

VSS#D20

VSS#D17

VSS#C3

VSS#C28

VSS#B30

VSS#B1

VSS#AK29

VSS#AK22

M14

AC14

AG16

A22

A2

D27

AG26

H18

A16

A9

AD17

J24

R27

D24

T30

U19

M16

AD11

H15

N15

N19

D3

A25

F3

R15

P16

G10

M24

M12

R13

P12

P14

U13

R17

V18

R19

R23

R24

J30

T12

N13

T14

P18

T16

U17

T18

W19

J27

U15

N17

M18

V16

W17

M26

V12

W13

V14

W15

U23

U24

A13

V28

AG24

AA24

AA23

F30

K23

D20

A19

D17

D14

F27

D4

M23

B30

B1

AK29

AK22

A A

CLG

5

POWER CHECK

+1.8VSUS [5,13,24,25,27]

+1.2V [6,24,27]

VTT [2,3,4,5,6,9,11,24,27]

+1.8V [3,5,7,9,11,24,25]

+3V [2,4,6,7,9,10,11,12,13,15,16,17,18,20,21,22,23,24,27]

4

Size Document Number Rev

3

2

Date: Sheet of

PROJECT : BH2

Quanta Computer Inc.

RC400MB-POWER

829Thursday, D e c ember 22, 2005

1

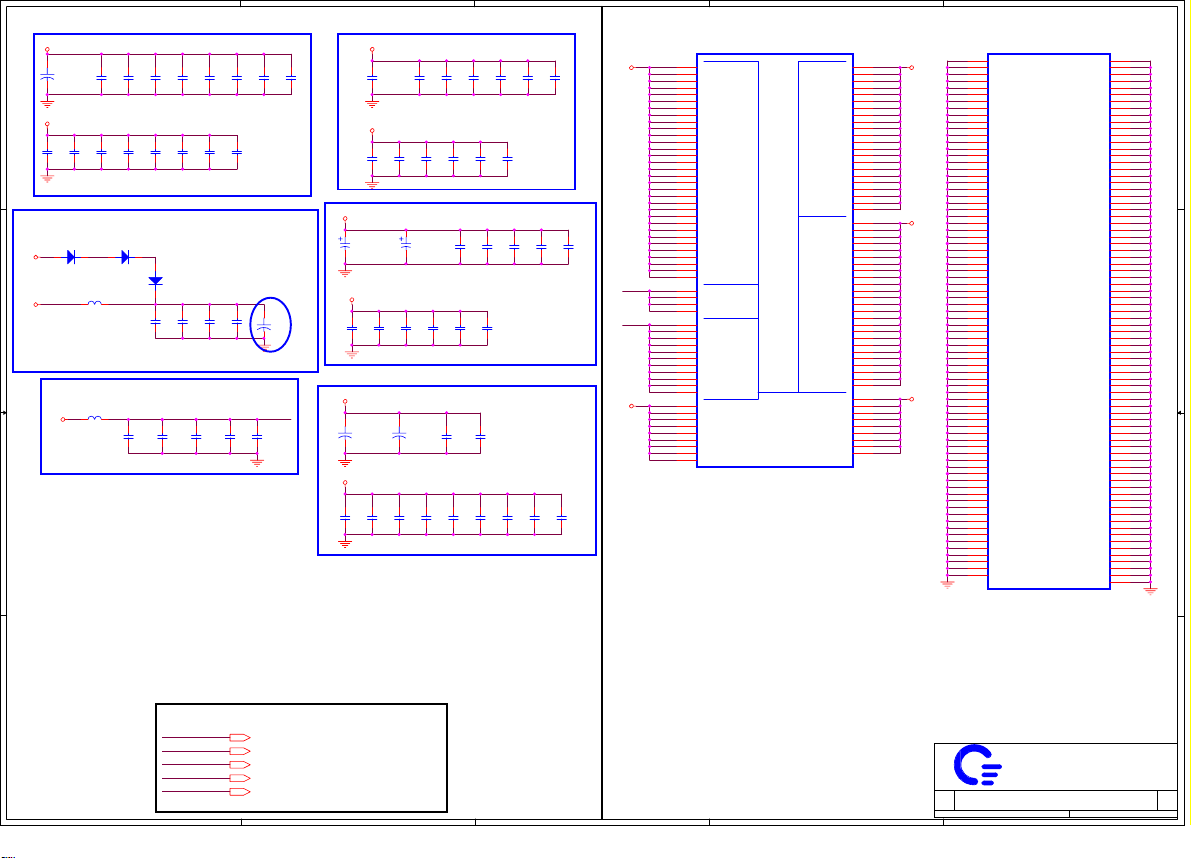

1A

5

C235

C232

1U_6

1U_6

C461

22U/16V_1206

C240

C238

1U_6

1U_6

D7 RB751

D6 RB751

C68

1U_6

VCCRTC [21]

+3VPCU [15,21,22,24,25]

+1.8V [3,5,7,8,11,24,25]

VTT [2,3,4,5,6,8,11,24,27]

+3V_S5 [2,1 0,11,12, 21,24]

+5VSUS [20,24,25,27]

decouple CAP

C236

C233

1U_6

1U_6

C462

C281

1U_6

.1U_4

C239

C255

C254

1U_6

.1U_4

.1U_4

VCCRTC

C69

.1U_4

R31 1.5K_6

decouple CAP

C252

.1U_4

JP8

Clear PAD

1 2

R354

100/F_6

R30

4.7K/F_6

R36

15K/F_6

+3V

D D

+1.8V

L27 TI201209G121

S0 max:183mA

C C

RTC

C244

C279

C280

.1U_4

.1U_4

.1U_4

PCIE Power

+1.8V

L39 SBK160808T-301Y-S

S0 max:126mA

PCIE_VDDR

C296

22U/16V_1206

+3VPCU

RTC_N02

R26 1K_4

C85

.1U_4

C237

1U_6

PCIE_PVDD

2 1

2 1

Change for FMEA.6/28

B B

A A

C62

.1U_4

Q4 MMBT3904

1 3

2

POWER CHECK

RTC_N01 RTC_N043VRTC

RTC_N03

R27 1.5K_6

12

CN3

BATCON

CLG

5

C268

.1U_4

+5VSUS

C253

.1U_4

4

U8 *7SH08

A_RX0P[6]

A_RX0N[6]

A_RX1P[6]

A_RX1N[6]

R188 150/F_4

R187 150/F_4

R343 4.12K/F_4

STP_CPU#[4,23]

DPSLP#[2]

INTE#[17]

INTF#[14]

INTG#[20]

INTH#[20]

CPUPWRGD[2]

INTR[2]

NMI[2]

CPUINIT#[2]

SMI#[2]

CPUSLP#[2]

IGNNE#[2]

A20M#[2]

FERR#[2]

STPCLK#[2]

DPRSLPVR[23]

BMREQ#[6]

T16

4

R115 0_6

C466 .1U_4

C464 .1U_4

C470 .1U_4

C469 .1U_4

A_TX0P[6]

A_TX0N[6]

A_TX1P[6]

A_TX1N[6]

PCIE_PVDD

PCIE_VDDR

ALINK_RST#[4,5,16,20]

PCIE_VDDR

PCMCIA

LAN

MINI

MINI

R410

*10K_4

4

3

+3V_S5

C100 *.1U_4

5

R110 8.2K_4

2

U21A

1

AH8

A_RST#

A_RX0P_C

A_RX1P_C

PCIE_CALRP

PCIE_CALRN

STP_CPU#

DPSLP#

INTA#

INTB#

INTC#

INTD#

INTE#

INTF#

INTG#

INTH#

VTT

R347

*1K_4

A_RX0N_C

A_RX1N_C

PCIE_CALI

32K_X1

32K_X2

3

L27

PCIE_RCLKP

M27

PCIE_RCLKN

M30

PCIE_TX0P

N30

PCIE_TX0N

K30

PCIE_TX1P

L30

PCIE_TX1N

H30

PCIE_TX2P

J30

PCIE_TX2N

F30

PCIE_TX3P

G30

PCIE_TX3N

M29

PCIE_RX0P

N29

PCIE_RX0N

M28

PCIE_RX1P

N28

PCIE_RX1N

J29

PCIE_RX2P

K29

PCIE_RX2N

J28

PCIE_RX3P

K28

PCIE_RX3N

G27

PCIE_CALRP

H27

PCIE_CALRN

G28

PCIE_CALI

R30

PCIE_PVDD

F26

PCIE_VDDR_1

R29

PCIE_VDDR_2

G26

PCIE_VDDR_3

P26

PCIE_VDDR_4

K26

PCIE_VDDR_5

L26

PCIE_VDDR_6

P28

PCIE_VDDR_7

N26

PCIE_VDDR_8

P27

PCIE_VDDR_9

H28

PCIE_VSS_1

F29

PCIE_VSS_2

H29

PCIE_VSS_3

H26

PCIE_VSS_4

F27

PCIE_VSS_5

G29

PCIE_VSS_6

L29

PCIE_VSS_7

J26

PCIE_VSS_8

L28

PCIE_VSS_9

J27

PCIE_VSS_10

N27

PCIE_VSS_11

M26

PCIE_VSS_12

K27

PCIE_VSS_13

P29

PCIE_VSS_14

P30

PCIE_VSS_15

AJ8

CPU_STP#/DPSLP_3V#

AK7

DPSLP_OD#/GPIO37

AG5

INTA#

AH5

INTB#

AJ5

INTC#

AH6

INTD#

AJ6

INTE#/GPIO33

AK6

INTF#/GPIO34

AG7

INTG#/GPIO35

AH7

INTH#/GPIO36

B2

X1

B1

X2

C29

CPU_PG/LDT_PG

A28

INTR/LINT0

C28

NMI/LINT1

B29

INIT#

D29

SMI#

E4

SLP#/LDT_STP#

B30

IGNNE#

F28

A20M#

E28

FERR#

E29

STPCLK#/ALLOW_LDTSTP

D25

SSMUXSEL/GPIO0

E27

DPRSLPVR

D27

BMREQ#

D28

LDT_RST#

SB450C

R85

20M_4 C76

SBSRCCLK[4]

SBSRCCLK#[4]

T62

T58

T60

T59

T61

T18

T57

T14

PCI EXPRESS INTERFACE

Y2 32.768KHZ

2 3

R86 20M_4

18P_4

SB450C SB

Part 1 of 4

PCI INTERFACE

REQ4#/PLL_BP33/PDMA_REQ1#

GNT3#/PLL_BP66/PDMA_GNT0#

GNT4#/PLL_BP50/PDMA_GNT1#

LPC

CPU XTAL

RTC_IRQ#/ACPWR_STRAP

RTC

32K_X1

32K_X2

41

C89

18P_4

PCI CLKS

DEVSEL#/ROMA0

REQ3#/PDMA_REQ0#

ATi Recommend

Vendor: NSK

Part Number: NXG 32.768KAE12FUD 16 PPM.

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

PCICLK7

PCICLK8

PCICLK9

PCICLK_FB

PCIRST#

AD0/ROMA18

AD1/ROMA17

AD2/ROMA16

AD3/ROMA15

AD4/ROMA14

AD5/ROMA13

AD6/ROMA12

AD7/ROMA11

AD8/ROMA9

AD9/ROMA8

AD10/ROMA7

AD11/ROMA6

AD12/ROMA5

AD13/ROMA4

AD14/ROMA3

AD15/ROMA2

AD16/ROMD0

AD17/ROMD1

AD18/ROMD2

AD19/ROMD3

AD20/ROMD4

AD21/ROMD5

AD22/ROMD6

AD23/ROMD7

CBE0#/ROMA10

CBE1#/ROMA1

CBE2#/ROMWE#

CBE3#

FRAME#

IRDY#

TRDY#/ROMOE#

PAR/ROMA19

STOP#

PERR#

SERR#

REQ0#

REQ1#

REQ2#

REQ5#/GPIO13

REQ6#/GPIO31

GNT0#

GNT1#

GNT2#

GNT5#/GPIO14

GNT6#/GPIO32

CLKRUN#

LOCK#

LFRAME#

LDRQ0#

LDRQ1#

SERIRQ

RTCCLK

RTC_GND

2

L4

L3

PCI_MINI

PCI_591

PCI_PCM

PCI_SIO

PCI_CLK6

PCI_LAN

PCI_CLK8

PCICLK9

PCI_CLK9_FB

PCIRST#_C

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE0#

C/BE1#

C/BE2#

C/BE3#

FRAME#

DEVSEL#

IRDY#

TRDY#

PAR

STOP#

PERR#

SERR#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

REQ5#

REQ6#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

GNT5#

GNT6#

CLKRUN#

PCI_LOCK#

LAD0

LAD1

LAD2

LAD3

LFRAME#

LDRQ#0

LDRQ#1

SERIRQ

R73 33_4

R341 33_4

R342 33_4

R72 33_4

R333 22_4

R331 33_4

R69 22_4

R329 22_4

C88

4.7U/6.3V_6

L2

L1

M4

M3

M2

M1

N4

N3

N2

AJ7

W3

Y2

W4

Y3

V1

Y4

V2

W2

AA4

V4

AA3

U1

AA2

U2

AA1

U3

T4

AC1

R2

AD4

R3

AD3

R4

AD2

P2

AD24

AE3

AD25

P3

AD26

AE2

AD27

P4

AD28

AF2

AD29

N1

AD30

AF1

AD31

V3

AB4

AC2

AE4

T3

AC4

AC3

T2

U4

T1

AB2

AB3

AF4

AF3

AG2

AG3

AH1

AH2

AH3

AJ2

AK2

AJ3

AK3

AG4

AH4

AJ4

AG1

AB1

AG25

LAD0

AH25

LAD1

AJ25

LAD2

AH24

LAD3

AG24

AH26

AG26

AK27

C2

F3

A2

VBAT

A1

2

T7

T6

PCLK_MINI

PCLK_591

PCLK_PCM

PCLK_SIO

PCICLK6

PCLK_LAN

PCICLK8

AD[0..31]

C136

*82P_4

CBE0# [14,17,20]

CBE1# [14,17,20]

CBE2# [14,17,20]

CBE3# [14,17,20]

FRAME# [14,17,20]

DEVSEL# [14,17,20 ]

IRDY# [14,1 7,20]

TRDY# [14,17,20]

PAR [14,17,20]

STOP# [14,1 7,20]

PERR# [14,17,20]

SERR# [14,17,20]

REQ0# [14]

REQ1# [20]

REQ3# [17]

GNT0# [14 ]

GNT1# [20 ]

GNT3# [17 ]

CLKRUN# [14,17,20,21]

LAD0/FWH0 [20,21]

LAD1/FWH1 [20,21]

LAD2/FWH2 [20,21]

LAD3/FWH3 [20,21]

LFRAME#/FWH4 [20,21]

LDRQ#0 [20]

SERIRQ [17,20,21]

RTC_CLK [12]

AUTO_ON# [12]

VCCRTC

AD[0..31] [12,14,17,20]

+3V

5

PCIRST#_C

2

1

R295

R294 0_6

8.2K_4

LAN

MINI

PCMCIA

LAN

MINI

PCMCIA

Size Document Number Rev

Custom

SB450C PCIE/PCI/CPU/LPC I/F

Date: Sheet of

1

PCLK_MINI [12,20]

PCLK_591 [12,21]

PCLK_PCM [12,17]

PCLK_SIO [12,20]

PCICLK6 [12]

PCLK_LAN [12,14]

PCICLK8 [12]

C463 *100P-4

Reserved For EMI

PCLK_MINI

C471 *33P_4

PCLK_591

C473 *33P_4

PCLK_PCM

C474 *33P_4

PCLK_SIO

C72 *33P_4

PCICLK6

C467 *33P_4

PCLK_LAN

C465 *33P_4

PCICLK8

C71 *33P_4

C443 *.1U_4

U19

*7SH08

PCIRST#

4

PCI_LOCK#

INTA#

INTB#

INTC#

INTD#

INTE#

INTF#

INTG#

INTH#

FRAME#

STOP#

TRDY#

PAR

REQ0#

REQ2#

REQ1#

REQ3#

GNT0#

GNT1#

GNT2#

GNT3#

SERR#

PERR#

DEVSEL#

IRDY#

GNT6#

GNT5#

REQ6#

CLKRUN#

GNT4#

REQ4#

LAD3

LAD2

LAD1

LAD0

REQ5#

SERIRQ

LDRQ#0

LDRQ#1

LFRAME#

PCIRST# [14,17,20,21]

C442

*82P_4

R319 8.2K_4

R302 8.2K_4

R301 8.2K_4

R300 8.2K_4

R297 8.2K_4

R299 8.2K_4

R298 8.2K_4

R116 8.2K_4

R296 8.2K_4

RN8 8.2KX4_4

2

4

6

2

4

6

RN6 8.2KX4_4

RN4 8.2KX4_4

2

4

6

2

4

6

RN7 8.2KX4_4

2

4

6

RN2 8.2KX4_4

R104 8.2K_4

R306 8.2K_4

R305 100K_4

R303 100K_4

R304 100K_4

R148 100K_4

R308 8.2K_4

RN5 8.2KX4_4

2

4

6

PROJECT : BH2

Quanta Computer Inc.

929Thursday, D e c ember 22, 2005

1

+3V

+3V

1

3

5

78

1

3

5

78

1

3

5

78

1

3

5

78

1

3

5

78

1

3

5

78

1A

Loading...

Loading...