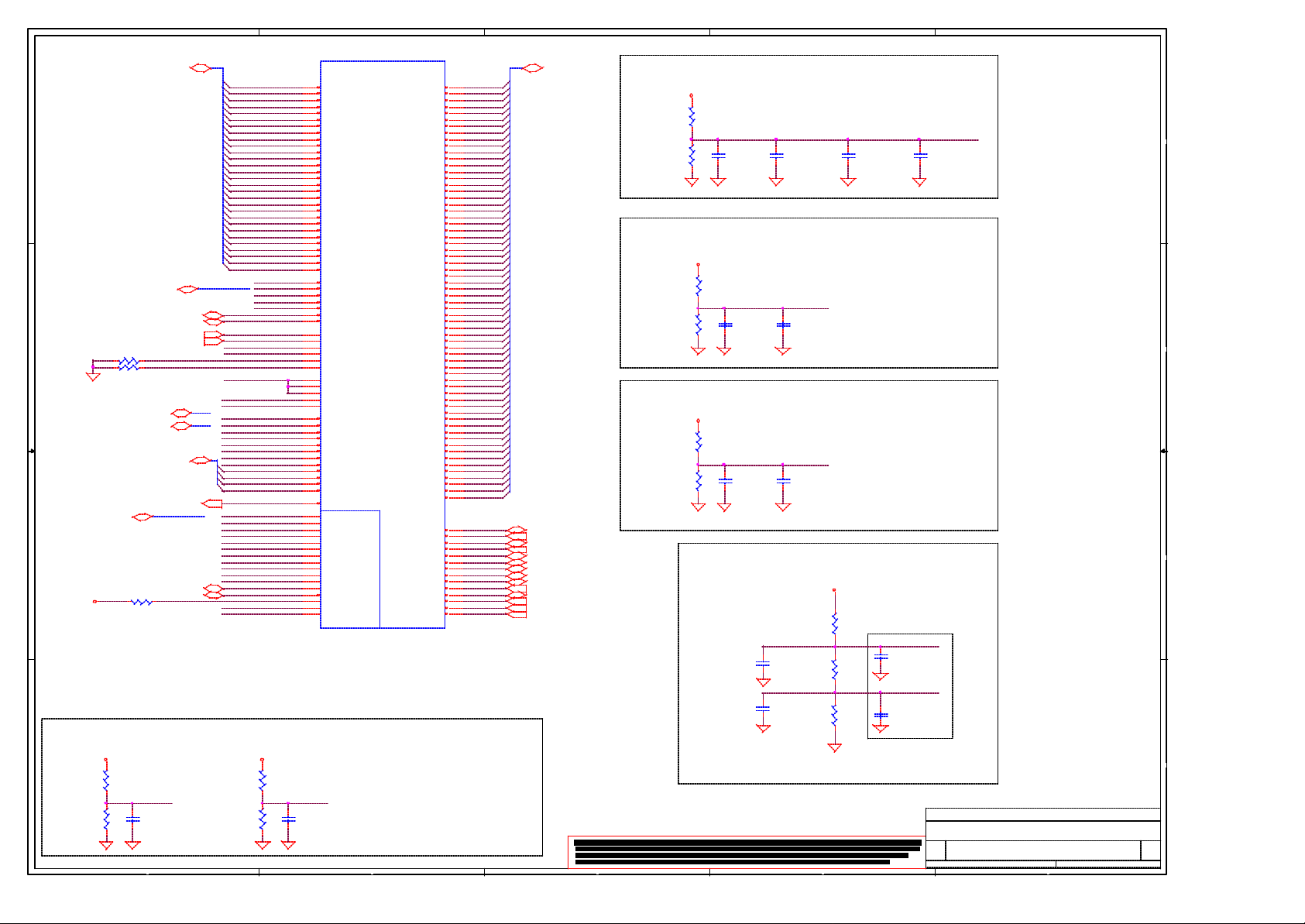

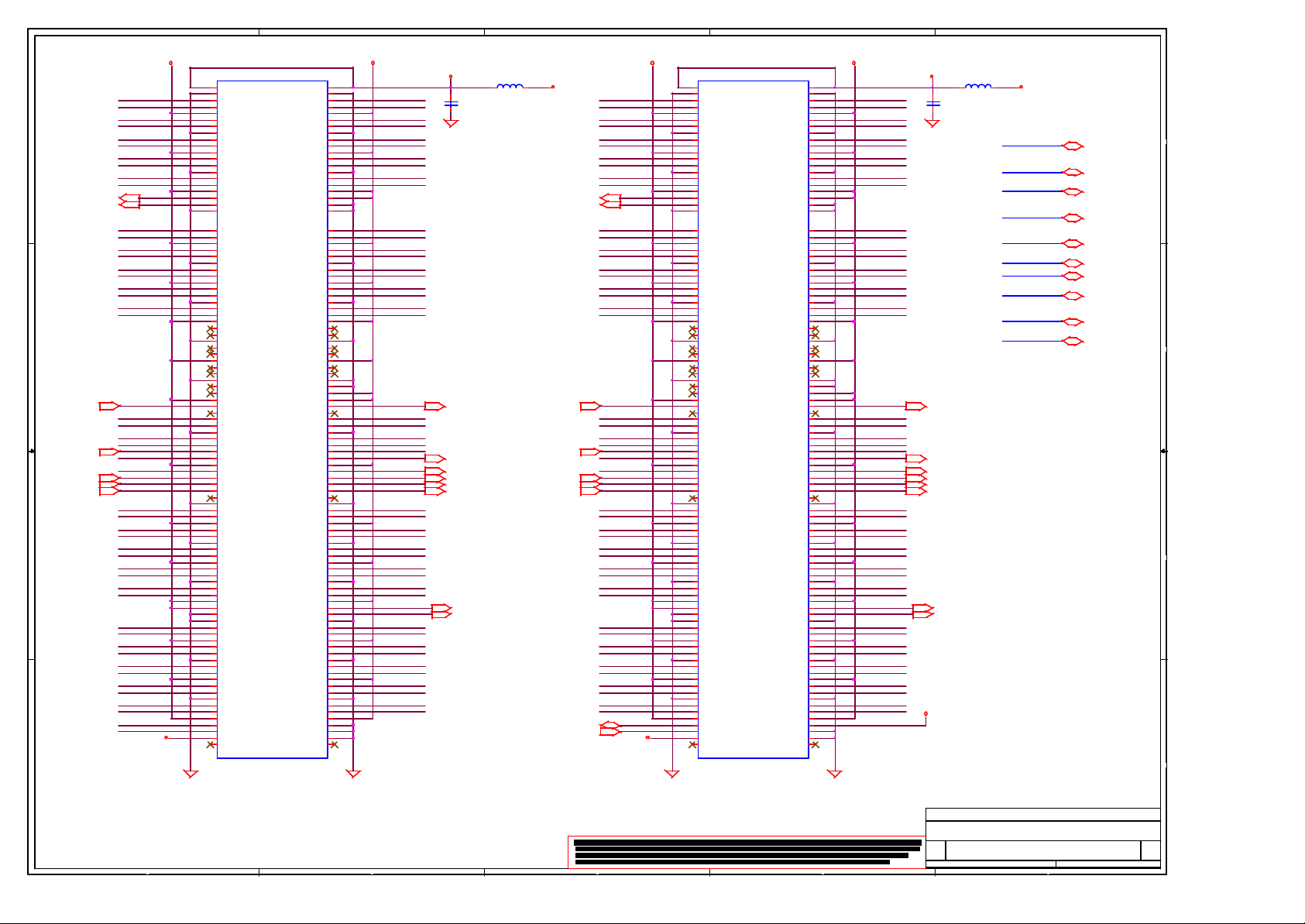

Toshiba Satellite 1130, Satellite 1135 Schematics

A

1 1

2 2

B

C

D

E

LA-1641 REV0.2 Schematic

Docum ent

Intel Mobile P4 uFCBGA/uFCPGA Northwood Celeron

with Montara GML / ICH4-M / Integrated VGA

2002-11-20

3 3

4 4

Compal Electronics, Ltd.

Title

Cover Page

Size Document Number Rev

Custom

LA-1641

A

B

C

D

Date: Sheet of

1 46Monday, November 25, 2002

E

0.3

A

B

COMPAL CONFIDENTIAL

REV:0.3

C

D

E

1 1

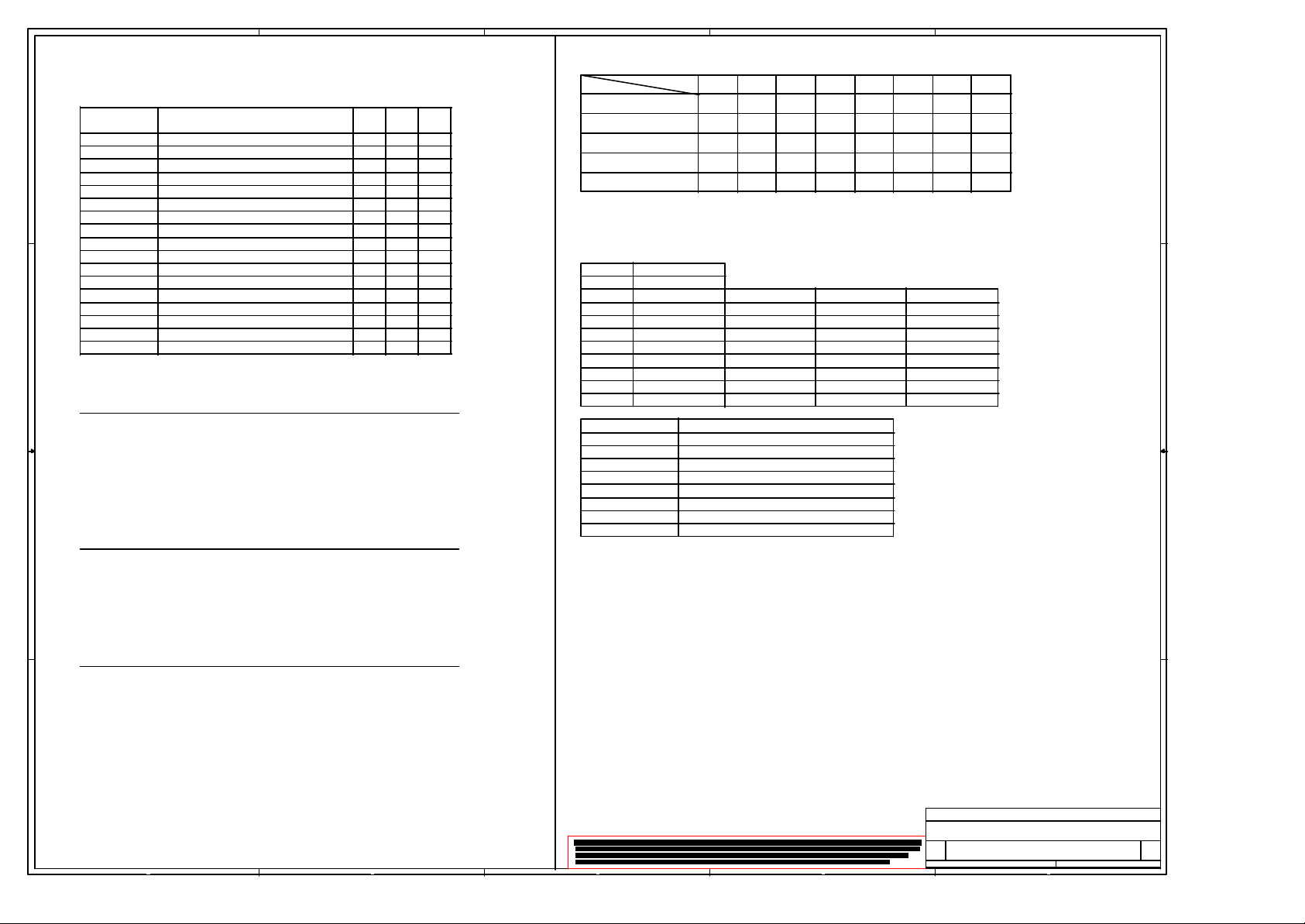

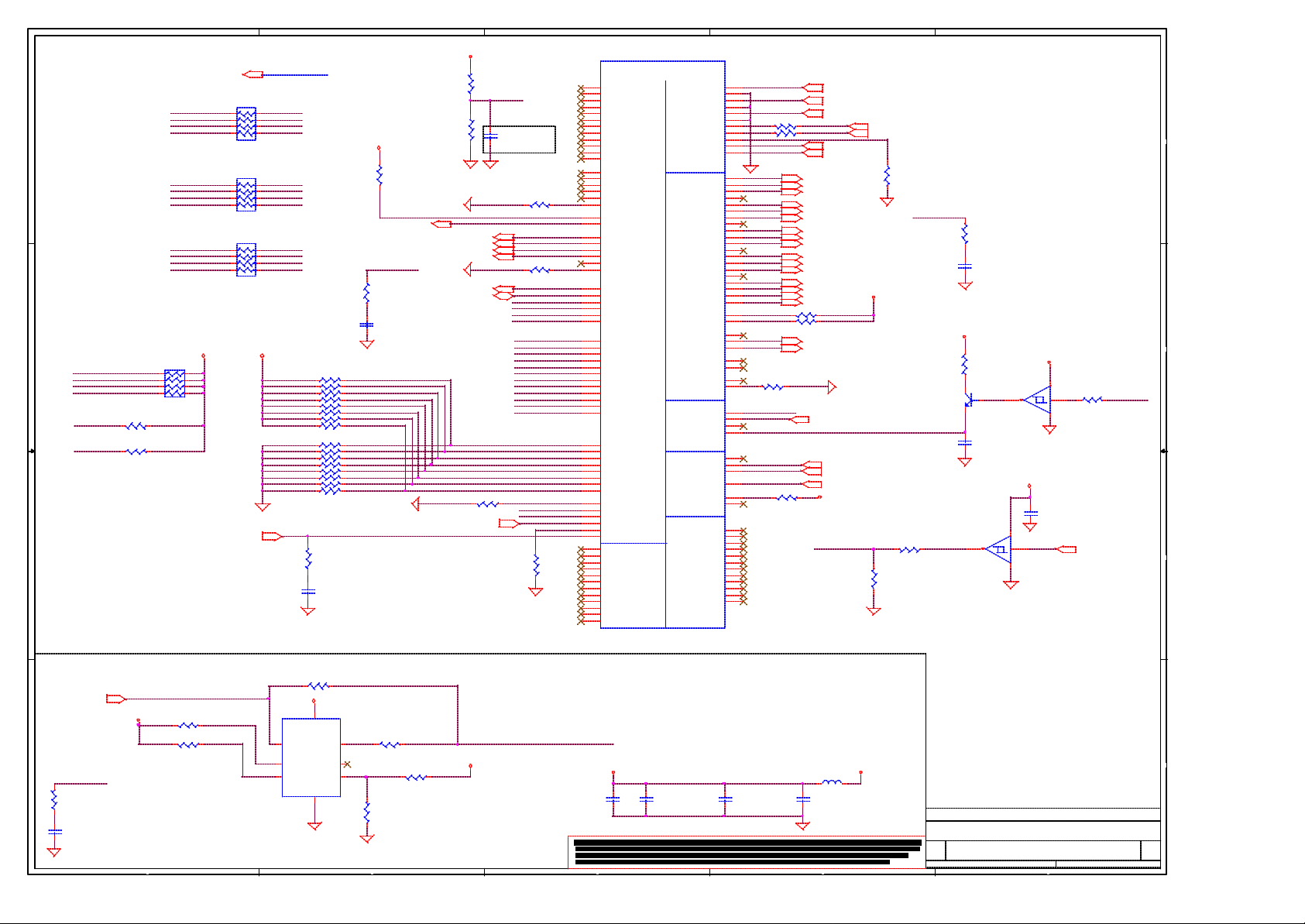

CPU

Thermal

sensor

PAGE 4

Mobile P4

Northwood Celeron

478 uFCPGA

PAGE 4, 5, 6

CLOCK

ICS950810

PAGE 15

PSB

CHRONTEL 7011

TV-OUT Controller

PAGE 14

CRT & LVDS

2 2

Connector

PAGE 13

DVO#C

DVO BUS

LVDS&DAC Interface

Montara GML

VGA Embeded

732 uFCBGA

PAGE 7,8,9,10

MEMORY BUS

DDR DIMM X 2

PAGE 11

DC/DC Interface

PAGE 38

HUB Link

INTERNAL IDE

OZ-168

PAGE 25

INTERNAL IDE

HDD/

CD-ROM

PAGE 26

Secondary IDE

Primary IDE

ICH4-M

421 BGA

USB 2.0 Port X 4/

BlueTooth connector

3 3

PAGE 29

LPC

LPC

PCI BUS

PAGE 16,17,18

LPC

AC LINK

Mini PCI

Connector

MDC

Connector

IDSEL: AD18

MASTER 1

PIRQC#, PIRQD#

(PIRQG#, PIRQH#)

PAGE 24

PAGE 27

IDSEL: AD20

MASTER 2

SIRQ,(PIRQE#, PIRQF#)

PIRQA#, PIRQB#

CARDBUS

OZ6933

PCMCIA

SOCKET

PAGE 20

PAGE 21

IDSEL: AD17

MASTER 3

PIRQB#

(PIRQD)

LAN Controller

RTL8100BL

RJ45/RJ11

Connector

PAGE 22

PAGE 23

IDSEL: AD16

MASTER 3

PIRQA#

1394 Controller

VIA 6307S

PAGE 19

POWER INTERFACE

SD Reader

Winbond

W83L518D

PAGE 33

4 4

Super I/O

LPC-47N227

PAGE 28

Parallel PORT

PAGE 27

EC/KBC

PC87591

BIOS/

Ext. I/O

PAGE 34

PAGE 35

AC97 Codec

ALC202

PAGE 30 PAGE 31

AUDIO

HARDWARE

EQ

Audio AMP

TPA0232

PAGE 32

PowerGood Interface/

System Connector

PAGE 36, 37

B+

+CPU_CORE

+2.5VP

+1.5VALWP

+12VALWP

+5VALWP

+3VALWP

+1.25VSP

+1.2VPP

+1.2VSP

PAGE 39, 40, 41, 42, 43, 44

Compal Electronics, Ltd.

Title

Cover Page

Size Document Number Rev

Custom

LA-1641

A

B

C

D

Date: Sheet of

2 46Monday, November 25, 2002

E

0.3

A

B

C

D

E

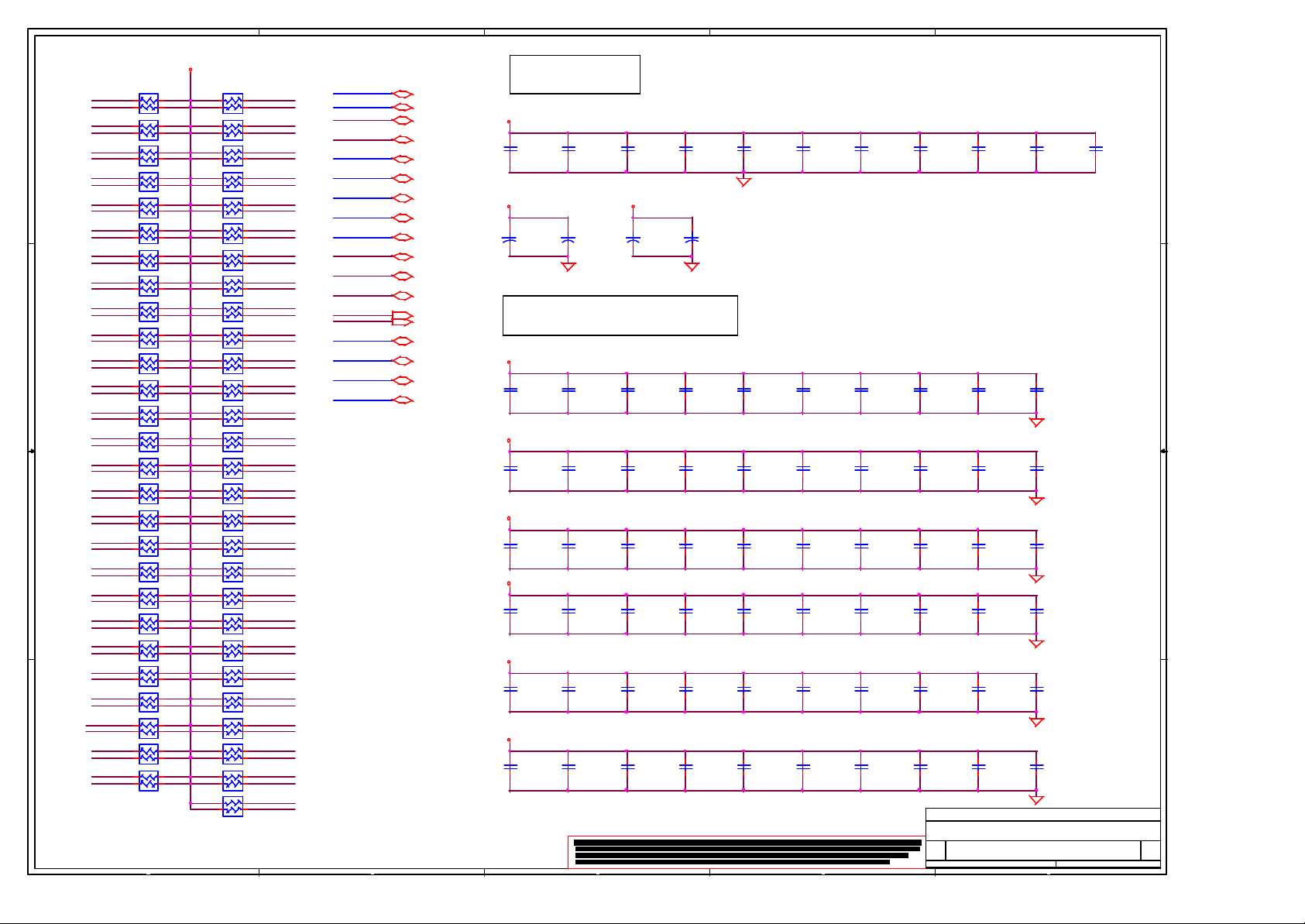

Voltage Rails

STATE

Power Plane Description

1 1

2 2

VIN

B+

+CPU_VCC

+1.2VP

+1.2VS 1.2V switched power rail for Montara core ON OFF OFF

+1.25VS 1.25V switched power rail

+2.5V

+2.5VS 2.5V switched power rail

+3VALW

+3V

+3VS

+5VALW

+5V

+5VS

RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.2V switched power rail for CPU AGTL Bus

AGP 4X ON OFF OFF+1.5VS

2.5V power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V power rail

5V switched power rail

12V always on power rail

RTC power

S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF

ON OFF OFF

ON

ON

ON

ON

ON

ON

ON ON

ON

ON+12VALW

ON

N/AN/AN/A

OFF

OFF

OFF

ON

OFF

OFF

ON ON*

OFF

ON

OFF

OFF

ON

ON*

OFF

OFF

OFF

ON

ON*

ON

ON

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

CardBus

LAN

Mini-PCI

1394

AD20

AD17

AD18

AD16 0

EC SM Bus1 address

3 3

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

Address Address

0001 011X b

1010 000X b

1011 000Xb

2

3 PIRQB(PIRQD)

1/1

PIRQA/PIRQB(PIRQE/PIRQF)

PIRQC/PIRQD(PIRQG/PIRQH)

PIRQA

EC SM Bus2 address

Device

ADM1032

OZ168

Smart Battery

Docking

DOT Board

1001 110X b

0011 0100 b

0001 011X b

0011 011X b

XXXX XXXXb

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

Board ID

Sapporo Z to ZJ BOM modify list :

1.Remove R594

2.Add R112

SIGNAL

100K +/- 5%Ra

Rb V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

0

1

2

3

4

5

6

7

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

AD_BID

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

V typ

0 V

AD_BID

ONONON ON

ON

ON

ON

ON

ON

OFF

OFF

V

AD_BID

ON

OFF

OFF

OFF

max

0 V 0 V

LOW

OFF

OFF

OFF

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

3.300 V

PCB Revision

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

ICH4 SM Bus address

Device

Clock Generator (

ICS-950810)

4 4

A

Address

1101 001X

Compal Electronics, Ltd.

Title

Note List

Size Document Number Rev

Custom

LA-1641

B

C

D

Date: Sheet of

3 46Friday, November 29, 2002

E

0.3

A

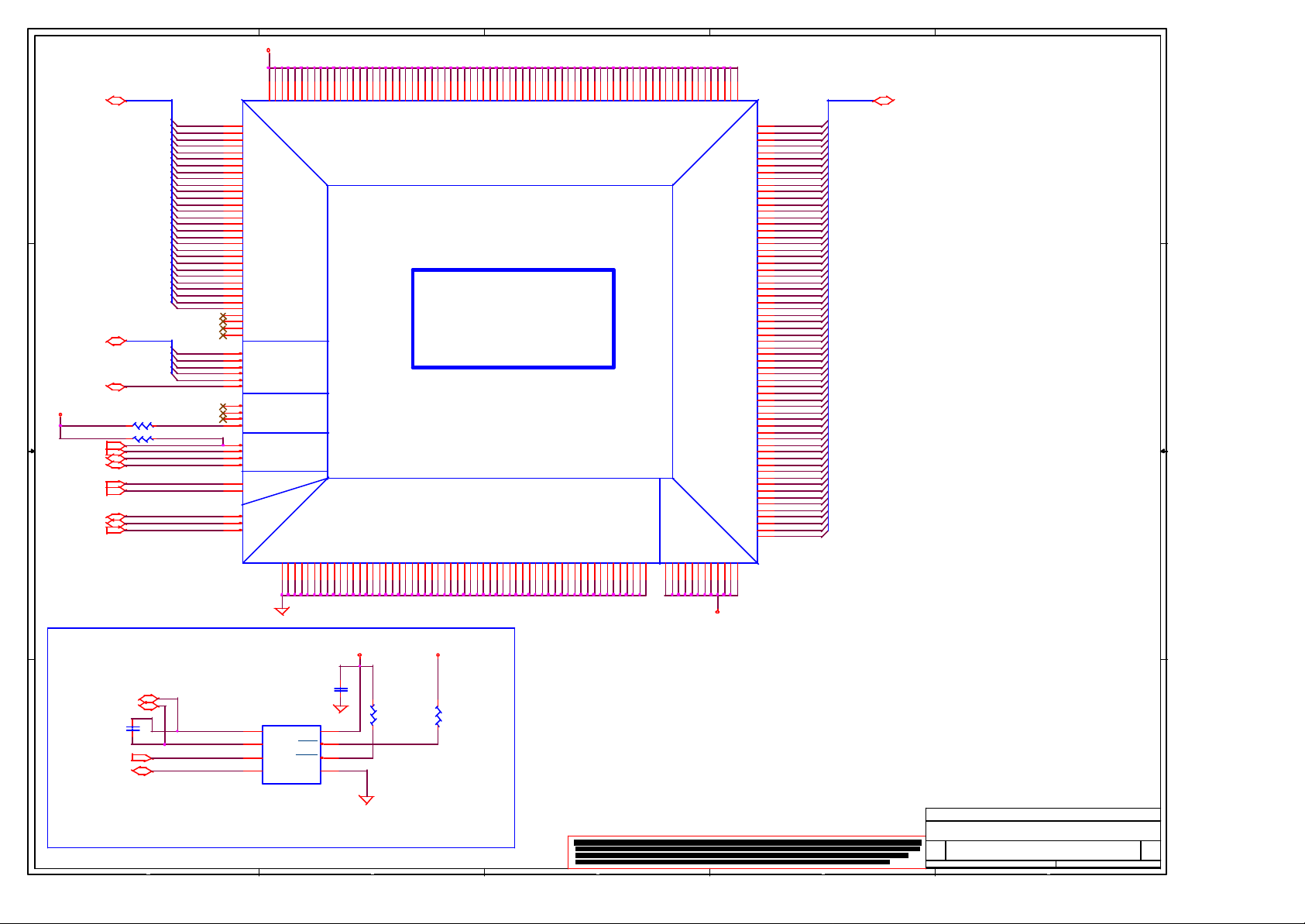

HA#[3..31]7

1 1

HREQ#[0..4]7

2 2

H_ADS#7

+CPU_CORE

H_BREQ0#7

H_BPRI#7

H_BNR#7

H_LOCK#7

CLK_CPU_BCLK15

CLK_CPU_BCLK#15

H_HIT#7

H_HITM#7

H_DEFER#7

3 3

HA#[3..31]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#[0..4]

R91 Close to U37 pinM23

R53 56_0402_5%

R91 220_0402_5%

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

CLK_CPU_BCLK

CLK_CPU_BCLK#

AC1

AC3

AF22

AF23

M6

M3

M4

N1

M1

N2

N4

N5

R2

R3

U1

U3

R6

W1

U4

W2

AB1

H3

G1

AA3

H6

D2

G2

G4

K2

K4

L6

K1

L3

L2

T1

P3

P4

T2

P6

T4

V2

T5

V3

Y1

J1

K5

J4

J3

V5

F3

E3

E2

+CPU_CORE

A10

A12

U40A

VCC_0

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

AP#0

AP#1

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

BCLK0

BCLK1

HIT#

HITM#

DEFER#

A14

A16

VCC_1

VCC_2

VSS_0

H1H4H23

A18

VCC_3

VSS_1

A20A8AA10

VCC_4

VCC_5

VCC_6

VSS_2

VSS_3

VSS_4

H26

A11

A13

AA12

VCC_7

VSS_5

A15

AA14

VCC_8

VSS_6

A17

AA16

VCC_9

VSS_7

A19

AA18

AA8

VCC_10

VCC_11

VSS_8

VSS_9

A21

A24

AB11

AB13

VCC_12

VCC_13

VSS_10

VSS_11

A26A3A9

B

AB15

AB17

VCC_14

VCC_15

VSS_12

VSS_13

AA1

AB19

AB7

VCC_16

VCC_17

VSS_14

VSS_15

AA11

AA13

AB9

AC10

VCC_18

VCC_19

VSS_16

VSS_17

AA15

AA17

AC12

AC14

VCC_20

VCC_21

VSS_18

VSS_19

AA19

AA23

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

NorthWood

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

Mobile

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AF13

AF15

VCC_41

VCC_42

VSS_39

VSS_40

AC19

AC2

AF17

AF19

VCC_43

VCC_44

VSS_41

VSS_42

AC22

AC25

AF2

AF21

VCC_45

VCC_46

VSS_43

VSS_44

AC5

AC7

AF5

AF7

VCC_47

VCC_48

VSS_45

VSS_46

AC9

AD1

C

AF9

B11

VCC_49

VCC_50

VSS_47

VSS_48

AD10

AD12

B13

B15

VCC_51

VCC_52

VSS_49

VSS_50

AD14

AD16

B17

B19B7B9

VCC_53

VCC_54

VSS_51

VSS_52

AD18

AD21

VCC_55

VCC_56

VSS_53

VSS_54

AD23

AD4

C10

C12

VCC_57

VCC_58

VSS_55

VSS_56

AD8

C14

C16

VCC_59

VCC_61

F13

C18

C20C8D11

VCC_62

VCC_63

VCC_81

VCC_82

F15

F17

VCC_64

VCC_65

VCC_83

VCC_84

F19

F9

D13

D15

VCC_66

VCC_67

VCC_80

VCC_85

D17

D19D7D9

VCC_68

VCC_69

VCC_78

VCC_79

E18

E20E8F11

VCC_70

VCC_71

VCC_76

VCC_77

E14

E16

E10

VCC_72

VCC_73

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

VCC_74

VCC_75

NorthWood

E12

B21

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5HA#8

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

D

HD#[0..63]

E

HD#[0..63] 7

+CPU_CORE

+3VS

R376

4.7K_0402_5%

GND

W=15mil

C503

1

6

4

5

+3VS

R377

4.7K_0402_5%

Thermal Sensor

ADM1032AR

H_THERMDA5

H_THERMDC5

C501

2200P_0402_25V7 K

4 4

EC_SMC225,34

EC_SMD225,34

H_THERMDA

H_THERMDC

0.1U_0402_16V4Z

U38

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032AR_SOP-8

VDD1

ALERT

THERM

Address:1001_100X

Compal Electronics, Ltd.

Title

Mobile P4-Celeron (1/2)

Size Document Number Rev

Custom

LA-1641

A

B

C

D

Date: Sheet of

4 46Thursday, November 28, 2002

E

0.3

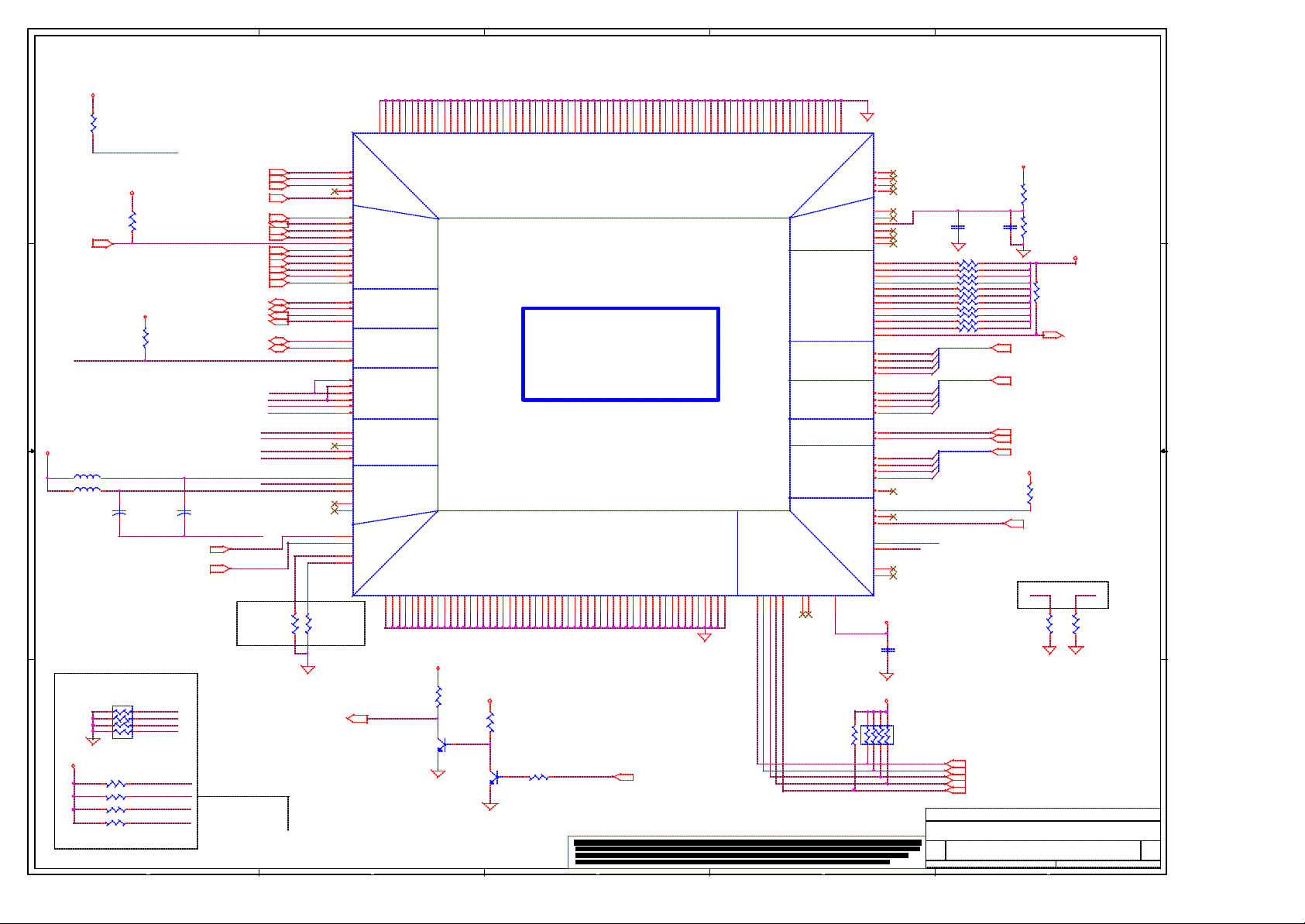

A

+CPU_CORE

R36

1 1

Place R420 near to U12 pinW20

2 2

+1.2VP

3 3

4 4

51.1_1%_0603

1 2

H_RESET#

H_RS#07

H_RS#17

+CPU_CORE

R65

300_0402_5%

H_PWRGD16

Place R65 near to U40 pinAB23

+CPU_CORE

R420

56_0402_5%

H_THERMTRIP#

Murata

LQG21F4R7N00

L4

4.7UH_80mA_0805

1 2

4.7UH_80mA_0805

L3

1 2

R84 R87 placed with in 0.5" of processor,

and at least 25mils away from other signals

+CPU_CORE

12

+

C1

33UF_D2_16V

RP6

1 8

2 7

3 6

4 5

1.5K_8P4R_0804_5%

12

R85 200_0603

12

R80 200_0603

12

R72 200_0603

12

R75 200_0603

CLK_CPU_ITP15

CLK_CPU_ITP#15

ITP_TMS

ITP_TCK

ITP_TRST#

ITP_TDI

ITP_PREQ#

ITP_PRDY#

ITP_BPM0

ITP_BPM1

A

12

+

C433

33UF_D2_16V

H_RS#27

H_TRDY#7

H_A20M#16

H_FERR#16

H_IGNNE#16

H_SMI#16

H_STPCLK#16

H_DPSLP#8,16

H_INTR16

H_NMI16

H_INIT#16

H_CPURST#7

H_DBSY#7

H_DRDY#7

H_BSEL015

H_BSEL115

H_THERMDA4

H_THERMDC4

ITP_BPM0

ITP_BPM1

ITP_PRDY#

ITP_PREQ#

ITP_TCK

ITP_TDI

ITP_TMS

ITP_TRST#

+H_VCCA

TP1

+H_VCCIOPLL

H_VSSA

CLK_CPU_ITP

CLK_CPU_ITP#

R87

51.1_1%_0603

Place pull up resistors near processor

H_A20M#

H_FERR#

H_IGNNE#

H_SMI#

H_PWRGD

H_STPCLK#

H_DPSLP#

H_INTR

H_NMI

H_RESET#

H_THERMDA

H_THERMDC

COMP0

COMP1

51.1_1%_0603

1 2

1 2

EC_CPUPD#34

R84

AB23

AD25

AB25

AD6

AD5

AC6

AC4

AD20

AE23

AF25

AC26

AD26

F1

G5

F4

AB2

J6

C6

B6

B2

B5

Y4

D1

E5

W5

H5

H2

B3

C4

A2

AB5

Y6

AA5

AB4

D4

C1

D5

F7

E6

A5

AF3

L24

P1

B

AE11

U40B

VSS_57

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

DPSLP#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCA

VCCSENSE

VCCIOPLL

NC7

NC8

ITP_CLK0

ITP_CLK1

COMP0

COMP1

B

AE13

AE15

VSS_58

VSS_129

F8

G21

AE17

AE19

AE22

AE24

VSS_59

VSS_60

VSS_61

VSS_62

VSS_130

VSS_131

VSS_132

VSS_133

G24G3G6J2J22

***

Q60

3904

AE26

AE7

VSS_63

VSS_64

VSS_65

VSS_134

VSS_135

VSS_136

J25J5K21

+5V

AE9

AF1

AF10

VSS_66

VSS_67

VSS_137

VSS_138

K24K3K6L1L23

12

R590

10K

3 1

AF12

AF14

VSS_68

VSS_69

VSS_70

VSS_139

VSS_140

VSS_141

2

Q61

3904

AF16

AF18

AF20

AF26

VSS_71

VSS_72

VSS_73

VSS_142

VSS_143

VSS_144

L26L4M2

+CPU_CORE

12

3 1

AF6

AF8

B10

B12

VSS_75

VSS_76

VSS_77

SKTOCC#

VSS_145

VSS_146

VSS_147

VSS_148

M22

M25M5N21

R591

470

2

R592 470

B14

B16

B18

B20

B23

B26B4B8

C11

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

NorthWood

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

N24N3N6P2P22

P25P5R1

12

H_THERMTRIP#

C

C13

C15

C17

C19C2C22

C25C5C7C9D10

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

Mobile

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

R23

R26R4T21

T24T3T6U2U22

THERTRIP# 17

C

VSS_97

VSS_168

U25U5V1

D12

D14

VSS_98

VSS_99

VSS_100

VSS_169

VSS_170

VSS_171

V23

D16

D18

D20

VSS_101

VSS_102

VSS_172

VSS_173

V26V4W21

D21

D24D3D6D8E1

VSS_103

VSS_104

VSS_105

VSS_106

VSS_174

VSS_175

VSS_176

VSS_177

W24W3W6Y2Y22

VSS_107

VSS_108

VSS_109

VSS_178

VSS_179

VSS_180

Y25

E11

E13

VSS_110

VSS_181

Y5

E15

E17

VSS_111

VSS_112

VSS_113

E19

E23

E26E4E7E9F10

VSS_114

VSS_115

VID0

AE5

AE4

VSS_116

VSS_117

VSS_118

VID1

VID2

VID3

AE3

AE2

VSS_119

VID4

AE1

F12

F14

F16

VSS_120

VSS_121

VSS_122

NC5

AE21

AF24

1K_0402_5%

D

F18F2F22

VSS_123

VSS_124

VSS_125

NC6

D

F25

F5

VSS_126

VSS_127

VSS_128

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

PROCHOT#

MCERR#

VSSSENSE

VCCVID

AF4

R328

Layout note :

1. Place R381 and R382 within 0.5" of processor pin F20

2. Place decoupling cap 220PF near CPU.(Within 500mils)

3. GTLREF trace width 7 mils, and keep 10mils separated

from other signals

J26

DP#0

K25

DP#1

K26

DP#2

L25

DP#3

NC1

NC2

GHI#

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

SLP#

VSSA

NC3

NC4

NorthWood

+3VS

1 8

2 7

AA21

AA6

F20

F6

220P_0402_25V8 K

A22

A7

TESTTHI0_1

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

TESTTHI8_10

U6

W4

Y3

GHI#

A6

E22

H_DSTBN#0

H_DSTBN#1

K22

H_DSTBN#2

R22

W22

H_DSTBN#3

H_DSTBP#0

F21

H_DSTBP#1

J23

P23

H_DSTBP#2

H_DSTBP#3

W23

L5

R5

H_DBI#0

E21

H_DBI#1

G25

P26

H_DBI#2

H_DBI#3

V21

AE25

H_PROCHOT#

C3

V6

H_CPUSLP#

AB26

H_VSSA

AD22

A4

TP2

AD2

AD3

+1.2VP

C33

0.1U_0402_16V4Z

1K_8P4R_0804_5%

RP114

3 6

4 5

Title

Size Document Number Rev

Date: Sheet of

2/3VCORE

+GTLREF

C506

1U_0603_10V6 K

R56 56_0402_5%

R59 56_0402_5%

R355 56_0402_5%

R356 56_0402_5%

R58 56_0402_5%

R62 56_0402_5%

R354 56_0402_5%

R353 56_0402_5%

R364 56_0402_5%

R359 56_0402_5%

R66 56_0402_5%

H_DSTBN#[0..3]

H_DSTBP#[0..3]

H_DBI#[0..3]

CPU Voltag e ID

CPU_VID0 45

CPU_VID1 45

CPU_VID2 45

CPU_VID3 45

CPU_VID4 45

Compal Electronics, Ltd.

Mobile P4-Celeron (2/2)

Custom

LA-1641

E

+CPU_CORE

R381

49.9_0402_1%

R382

C504

100_0402_1%

+CPU_CORE

R96

300_0402_5%

R95

56_0402_5%

H_CPUSLP# 16

PM_CPUPERF# 17

H_DSTBN#[0..3] 7

H_DSTBP#[0..3] 7

H_ADSTB#0 7

H_ADSTB#1 7

H_DBI#[0..3] 7

+CPU_CORE

TP1 and TP2 must have test points

TP1

R101

@0_0402_5%

TP2

R98

@0_0402_5%

5 46Thursday, November 28, 2002

E

0.3

A

B

C

D

E

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

Use 2~3 vias per PAD.

1 1

Please place these cap in the socket cavity area

+CPU_CORE

C71

10U_1206_6.3V6M

+CPU_CORE

C130

10U_1206_6.3V6M

Please place these cap on the socket north side

+CPU_CORE

2 2

+CPU_CORE

+CPU_CORE

C44

10U_1206_6.3V6M

C52

10U_1206_6.3V6M

C34

10U_1206_6.3V6M

C70

10U_1206_6.3V6M

C129

10U_1206_6.3V6M

C43

10U_1206_6.3V6M

C48

10U_1206_6.3V6M

C19

10U_1206_6.3V6M

C69

10U_1206_6.3V6 M

C128

10U_1206_6.3V6 M

C42

10U_1206_6.3V6 M

C35

10U_1206_6.3V6 M

C12

10U_1206_6.3V6 M

C68

10U_1206_6.3V6 M

C127

10U_1206_6.3V6 M

C41

10U_1206_6.3V6 M

C22

10U_1206_6.3V6 M

C10

10U_1206_6.3V6 M

C67

10U_1206_6.3V6 M

C126

10U_1206_6.3V6 M

C40

10U_1206_6.3V6 M

C15

10U_1206_6.3V6 M

0.22U_0603_16V7K_V1

0.22U_0603_16V7K_V1

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

+CPU_CORE

12

+

C132

220UF_D2_4V_25m

+CPU_CORE

12

+

C134

220UF_D2_4V_25m

+CPU_CORE

C124

0.22U_0603_16V7K_V1

+CPU_CORE

C482

0.22U_0603_16V7K_V1

Used ESR 25m ohm cap total ESR=2.5m ohm

12

+

C110

220UF_D2_4V_25m

12

+

C113

220UF_D2_4V_25m

C109

0.22U_0603_16V7K_V1

C500

0.22U_0603_16V7K_V1

12

+

C92

220UF_D2_4V_25m

12

+

C94

220UF_D2_4V_25m

C74

C505

12

+

C78

220UF_D2_4V_25m

12

+

C81

220UF_D2_4V_25m

0.22U_0603_16V7K_V1

0.22U_0603_16V7K_V1

C73

C481

12

+

C60

220UF_D2_4V_25m

12

+

C61

220UF_D2_4V_25m

0.22U_0603_16V7K_V1

0.22U_0603_16V7K_V1

C483

C480

Please place these cap on the socket south side

3 3

4 4

+CPU_CORE

+CPU_CORE

+CPU_CORE

C180

10U_1206_6.3V6M

C161

10U_1206_6.3V6M

C148

10U_1206_6.3V6M

A

C175

10U_1206_6.3V6M

C168

10U_1206_6.3V6M

C149

10U_1206_6.3V6M

C165

10U_1206_6.3V6 M

C138

10U_1206_6.3V6 M

C141

10U_1206_6.3V6 M

C155

10U_1206_6.3V6 M

C143

10U_1206_6.3V6 M

C147

10U_1206_6.3V6 M

B

C154

10U_1206_6.3V6 M

C150

10U_1206_6.3V6 M

Compal Electronics, Ltd.

Title

CPU Decoupling

Size Document Number Rev

Custom

LA-1641

C

D

Date: Sheet of

6 46Monday, November 25, 2002

E

0.3

5

HA#[3..31]4 HD#[0..63] 4

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HREQ#[0..4]

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

+HYSWING

+HXSWING

+HYRCOMP

+HXRCOMP

+HDVREF

+HCCVREF

+HAVREF

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_CPURST#

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

HUB_PSTRB

HUB_PSTRB#

HI_RCOMP

+HI_VSWING

+HI_VREF

D D

HREQ#[0..4]4

H_ADSTB#05

H_ADSTB#15

CLK_MCH_BCLK#15

C C

B B

R54 27.4_0402_1%

R35 27.4_0402_1%

HUB_PD[0..10]16

+1.2VS

CLK_MCH_BCLK15

H_DSTBP#[0..3]5

H_DSTBN#[0..3]5

H_DBI#[0..3]5

H_CPURST#5

HUB_PD[0..10]

HUB_PSTRB16

R362 27.4_0402_1%

HUB_PSTRB#16

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

R27

U23

U24

R24

U28

U27

U25

W25

AA27

W24

W23

W27

AA28

W28

AB27

AB28

R28

R23

R25

AA26

AD29

AE29

H28

C27

D18

D26

G19

P23

T25

T28

V28

T27

V27

V26

Y24

V25

V23

Y25

Y27

Y26

P25

T23

T26

K28

B18

B20

K21

J21

J17

Y28

Y22

J28

E22

K27

E21

E18

J25

E25

B25

F15

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

T2

U2

W1

Layout Note:

1.Place R35 and R54 within 0.5" of U37 pinH28 B20

2.Both HYRCOMP and HXRCOMP trace width are 18mil

and 25mils away from other signals

4

U37A

Montara-GM(L)

HA#3

HA#4

HA#5

HA#6

HA7#

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HOST

HADSTB#0

HADSTB#1

HCLKN

HCLKP

HYSWING

HXSWING

HYRCOMP

HXRCOMP

HVREF0

HVREF1

HVREF2

HCCVREF

HAVREF

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

DINV0#

DINV1#

DINV2#

DINV3#

CPURST#

HI_0

HI_1

HI_2

HI_3

HI_4

HI_5

HI_6

HI_7

HI_8

HI_9

HI_10

PSTRBS

PSTRBF

HLRCOMP

PSWING

HI_REF

MONTARA-GM(L)

HUB I/F

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HIT#

HLOCK#

BREQ0#

BNR#

BPRI#

DBSY#

RS#0

RS#1

RS#2

K22

H27

K25

L24

J27

G28

L27

L23

L25

J24

H25

K23

G27

K26

J23

H26

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

L28

M25

N24

M28

N28

N27

P27

M23

N25

P28

M26

N23

P26

M27

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_ADS# 4

H_TRDY# 5

H_DRDY# 5

H_DEFER# 4

H_HITM# 4

H_HIT# 4

H_LOCK# 4

H_BREQ0# 4

H_BNR# 4

H_BPRI# 4

H_DBSY# 5

H_RS#0 5

H_RS#1 5

H_RS#2 5

3

Host data Ref. Voltage

49.9_0402_1%

100_0402_1%

+CPU_CORE

R57

R55

1.Place R57 and R55 within 0.5" of U37 pinK21 J21 J17

2.Place C57 C62 C56 C63 in order from U37 to divider

3.HDVREF 10mil trace, 20mil space.

C63

1U_0603_10V6K

Host address Ref. Voltage

49.9_0402_1%

100_0402_1%

+CPU_CORE

R86

R83

1.Place R86 and R83 within 0.5" of U37 pinY22

2.Place C105, C103 in order from U37 to divider

3.HAVREF 10mil trace, 20mil space.

C103

1U_0603_10V6K

Host common clock Ref. Voltage

49.9_0402_1%

100_0402_1%

+CPU_CORE

R88

R89

1.Place R88 and R89 within 0.5" of U37 pinY28

2.Place C102, C99 in order from U37 to divider

3.HCCVREF 10mil trace, 20mil space.

C102

1U_0603_10V6K

HUB I/F REF VOLTAGE

80.6_0402_1%

C488

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C499

51.1_0603_1%

40.2_0603_1%

2

C56

0.1U_0402_16V4Z

+HAVREF

C105

0.1U_0402_16V4Z

+HCCVREF

C99

0.1U_0402_16V4Z

+1.5VS

R363

R374

R373

C62

0.1U_0402_16V4Z

C57

0.1U_0402_16V4Z

Between divider and GMCH

+HI_VSWING

C496

0.01U_0402_25V7K

+HI_VREF

C498

0.01U_0402_25V7K

1

+HDVREF

HXSWING and HYSWING Ref. Voltage

A A

301_0402_1%

150_0402_1%

+CPU_CORE

R60

R63

+HYSWING

C59

0.1U_0402_16V4Z

5

301_0402_1%

150_0402_1%

R319

R309

+CPU_CORE

1.Place R60 and R63 within 0.5" of U37 pinK28

2.Place R319 and R309 within 0.5" of U37 pinB18

3.+HYSWING, +HXSWING 10mil trace, 20mil space.

+HXSWING

C451

0.1U_0402_16V4Z

4

Place this schematic close to GMCH

Compal Electronics, Ltd.

Title

Montara-GML (HOST)

Size Document Number Rev

Custom

LA-1641

3

2

Date: Sheet of

7 46Thursday, November 28, 2002

1

0.3

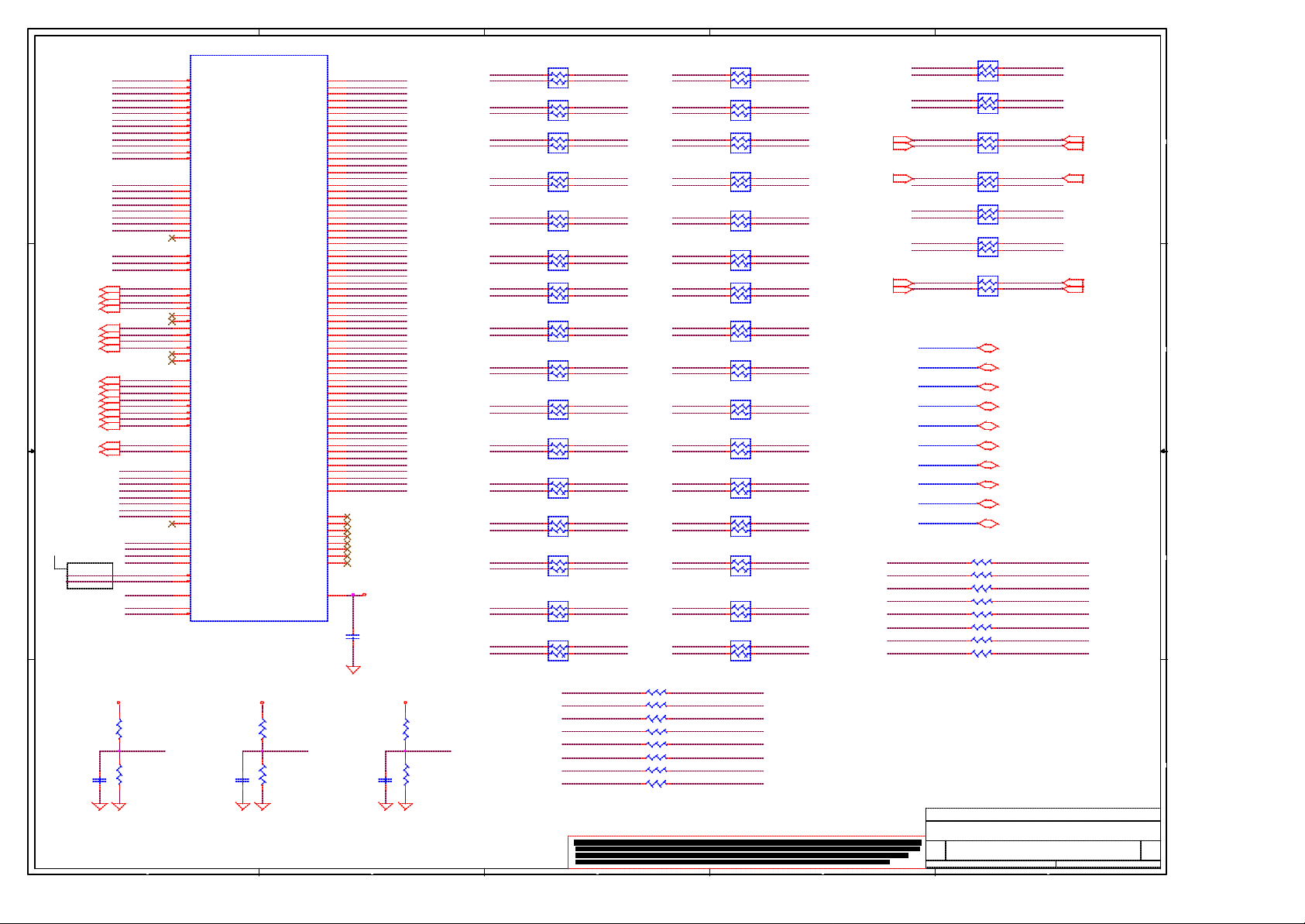

5

RP115

1 8

2 7

3 6

4 5

22_8P4R_1206_5%

RP116

1 8

2 7

3 6

4 5

22_8P4R_1206_5%

RP117

1 8

2 7

3 6

4 5

22_8P4R_1206_5%

+1.5V

DVOC_TV_D[0..11]

DVOC_D0

DVOC_D1

DVOC_D2

DVOC_D3

DVOC_D4

DVOC_D5

DVOC_D6

DVOC_D7

DVOC_D8

DVOC_D9

DVOC_D10

DVOC_D11

@22_0402_5%

@10P_0402_50V8K

R17 @8.2K_0402_5%

R18 @8.2K_0402_5%

R21 @8.2K_0402_5%

R22 @8.2K_0402_5%

R19 @8.2K_0402_5%

R20 @8.2K_0402_5%

R16 @8.2K_0402_5%

R15 @8.2K_0402_5%

R315 @330_0402_5%

R314 @330_0402_5%

R311 @330_0402_5%

R310 @330_0402_5%

R313 @330_0402_5%

R312 @330_0402_5%

R316 @330_0402_5%

R317 330_0402_5%

DVOC_TV_D[0..11]14

DVOC_TV_D0

DVOC_TV_D1

DVOC_TV_D2

D D

I2C BUS PULL UP

C C

MDDCDATA

MDDCCLK

MDVICLK

MDVIDATA

MI2CCLK

R61 2.2K_0402_5%

MI2CDATA

R70 2.2K_0402_5%

DVOC_TV_D3

DVOC_TV_D4

DVOC_TV_D5

DVOC_TV_D6

DVOC_TV_D7

DVOC_TV_D8

DVOC_TV_D9

DVOC_TV_D10

DVOC_TV_D11

RP118

1 8

2 7

3 6

4 5

8P4R-2.2K_0804

+1.5VS

Address: 0x7F

CLK_MCH_66M15

B B

R90

@33_0402_5%

1 2

C115

@10P_0402_50V8K

R572

1K_0402_1%

R67

C66

4

R344

+1.5VS

DVOBC_CLKINT

12

1K_0402_1%

DVOBC_CLKINT14

DVORCOMP should be 10mil width

and 20mil space

DVOC_CLK14

DVOC_CLK#14

DVOC_HSYNC14

DVOC_VSYNC14

MI2CCLK14

MI2CDATA14

AGP_BUSY#17

+1.5VS

R347

1K_0402_1%

+GVREF

Close to Ball F1

C474

0.1U_0402_16V4Z

R574330_0402_5%

40.2_0603_1%

DVOBC_INTR#

DVOBC_CLKINT

DVOC_CLK

DVOC_CLK#

DVOC_HSYNC

DVOC_VSYNC

MI2CCLK

MI2CDATA

MDVICLK

MDVIDATA

MDDCCLK

MDDCDATA

DVOC_D0

DVOC_D1

DVOC_D2

DVOC_D3

DVOC_D4

DVOC_D5

DVOC_D6

DVOC_D7

DVOC_D8

DVOC_D9

DVOC_D10

DVOC_D11

DPMS_CLK

+GVREF

DVORCOMP

R51

3

U37B

Montara-GM(L)

R3

DVOBD0/(NC)

R5

DVOBD1/(NC)

R6

DVOBD2/(NC)

R4

DVOBD3/(NC)

P6

DVOBD4/(NC)

P5

DVOBD5/(NC)

N5

DVOBD6/(NC)

P2

DVOBD7/(NC)

N2

DVOBD8/(NC)

N3

DVOBD9/(NC)

M1

DVOBD10/(NC)

M5

DVOBD11/(NC)

P3

DVOBCLK/(NC)

P4

DVOBCLK#/(NC)

T6

DVOBHSYNC/(NC)

T5

DVOBVSYNC/(NC)

L2

ID0

ID1

ID2

ID3

ID4

ID5

ID6

ID7

DVOBBLANK#/(NC)

M2

DVOBFLDSTL/(NC)

G2

DVOBCINTRB

M3

DVOBCCLKINT

J3

DVOCCLK

J2

DVOCCLK#

K6

DVOCHSYNC

L5

DVOCVSYNC

L3

DVOCBLANK#

H5

DVOCFLDSTL

K7

MI2CCLK

N6

MI2CDATA

N7

MDVICLK

M6

MDVIDATA

P7

MDDCCLK

T7

MDDCDATA

K5

DVOCD0

K1

DVOCD1

K3

DVOCD2

K2

DVOCD3

J6

DVOCD4

J5

DVOCD5

H2

DVOCD6

H1

DVOCD7

H3

DVOCD8

H4

DVOCD9

H6

DVOCD10

G3

DVOCD11

E5

ADDID0

F5

ADDID1

E3

ADDID2

E2

ADDID3

G5

ADDID4

F4

ADDID5

G6

ADDID6

F6

ADDID7

L7

DVODETECT

D5

DPMS

F1

GVREF

F7

AGPBUSY#

D1

GRCOMP

Y3

66IN

AA5

RVSD0

F2

RVSD1

F3

RVSD2

B2

RVSD3

B3

RVSD4

C2

RVSD5

C3

GST[1]

C4

GST[0]

D2

RVSD8

D3

RVSD9

D7

RVSD10

L4

RVSD11

MONTARA-GM(L)

DVO

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

MCHDETECTVSS

R64100K_0402_5%

R573100K_0402_5%

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

HSYNC

VSYNC

REFSET

DDCACLK

DAC

DDCADATA

IYAM0

IYAM1

IYAM2

IYAM3

IYAP0

IYAP1

IYAP2

IYAP3

IYBM0

IYBM1

IYBM2

IYBM3

IYBP0

IYBP1

IYBP2

IYBP3

ICLKAM

ICLKAP

ICLKBM

ICLKBP

DDCPCLK

DDCPDATA

LVDS

LVREFH

LVREFL

LVBG

LIBG

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

CLKSMISCNC

DPWR#/(NC)

DPSLP#

RSTIN#

PWROK

EXTTS0

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

C9

D9

C8

D8

A7

A8

H10

R14 39_0402_5%

R13 39_0402_5%

J9

E8

B6

G9

G14

E15

C15

C13

F14

E14

C14

B13

H12

E12

C12

G11

G12

E11

C11

G10

D14

E13

E10

F10

B4

C5

G8

F8

A5

D12

F12

B12

A10

R30 1.5K_0402_1%

DREFCLK

B7

B17

CLK_VCH

H9

C6

AA22

Y23

AD28

PCIRST#

J11

R24

D6

AJ1

10K_0402_1%

B1

AH1

A2

AJ2

A28

AJ28

A29

B29

AH29

AJ29

AA9

AJ4

2

BLUE 13

GREEN 13

RED 13

DDC_CLK 13

DDC_DATA 13

TXA0- 13

TXA1- 13

TXA2- 13

TXA0+ 13

TXA1+ 13

TXA2+ 13

TXB0- 13

TXB1- 13

TXB2- 13

TXB0+ 13

TXB1+ 13

TXB2+ 13

TXACLK- 13

TXACLK+ 13

TXBCLK- 13

TXBCLK+ 13

R26 2.2K_0402_5%

R25 2.2K_0402_5%

ENABKL 13

ENVDD 13

CLK_VCH 15

H_DPSLP# 5,16

PCIRST# 14,16,19,20,21,22,24,26,28,33,34

SYS_PWROK 17,37

+3VS

604_0603_1%

HSYNC 13

VSYNC 13

R41

137_0402_1%

@33_0402_5%

@10P_0402_50V8K

+3VS

LCLKCTLB

100P_0402_25V8 K

1.5V level clock

R322 732_0603_1%

R318

CLK_VCH

R343

C473

R536

10K_0402_5%

C675

1 2

+3VS

3 1

2

1

74LVC14

Q54

2

3904

U33B

4 3

2 1

74LVC14

+3VS

147

1

+3VS

147

U33A

C467

0.1U_0402_16V4Z

RTCCLKDPMS_CLK

R538

PCIRST#

0_0402_5%

RTCCLK 17,20,21

Speard Spectrum Controller

CLK_MCH_48M15

A A

CLK_MCH_48M

R31

@33_0402_5%

1 2

C17

@10P_0402_50V8K

CLK_MCH_48M

+3VS

R305 1K_0402_5%

R304 1K_0402_5%

5

1 2

1 2

R327 @0_0402_5%1 2

U32

1

X1/CLK

8

FS2

+SVDD

6

CLKOUT

3

VDD

GND

SS%

W181

5

27

X2FS1

4

1 2

R325 22_0402_1%

1 2

R329 1K_0402_5%

R336

1K_0402_5%

1 2

4

+SVDD

Layout Note:

1.Place U54 close to U3

2.CLK_MCH_48M and DREFCLK 5mil Trace and keep

20mil space to other signal.

DREFCLK

+SVDD

C441

0.1U_0402_10V6K

3

1

2

1

C442

0.1U_0402_10V6K

2

1

C38

4.7U_0805_6.3V6K

2

L5

1 2

FCM2012C80_0805

1

C443

0.1U_0402_10V6K

2

2

+3VS

Compal Electronics, Ltd.

Title

Montara-GML (LVDS)

Size Document Number Rev

Custom

LA-1641

Date: Sheet of

8 46Thursday, November 28, 2002

1

0.3

5

4

3

+1.2VS

C18

150U_D2_6.3VM

1

+

150U_D2_6.3VM

2

C46

+

1

2

2

C106

10U_1206_6.3V6 M

C90

0.1U_0402_16V7K

C98

0.1U_0402_16V7K

1

C89

0.1U_0402_16V7K

C54

0.1U_0402_16V7K

U37D

C1

D D

C C

B B

A A

G1

L1

U1

AA1

AE1

R2

AG3

AJ3

D4

G4

K4

N4

T4

W4

AA4

AC4

AE4

B5

U5

Y5

Y6

AG6

C7

E7

G7

J7

M7

R7

AA7

AE7

AJ7

H8

K8

P8

T8

V8

Y8

AC8

E9

L9

N9

R9

U9

W9

AB9

AG9

C10

J10

AA10

AE10

D11

F11

H11

AB11

AC11

AJ11

J12

AA12

AG12

A13

D13

F13

H13

N13

R13

U13

AB13

AE13

J14

P14

T14

AA14

AC14

D15

H15

N15

R15

U15

AB15

AG15

F16

J16

P16

T16

AA16

AE16

A17

D17

H17

N17

MONTARA-GM(L)

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

Montara-GM(L)

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

R17

U17

AB17

AC17

F18

J18

AA18

AG18

A19

D19

H19

AB19

AE19

F20

J20

AA20

AC20

A21

D21

H21

M21

P21

T21

V21

Y21

AA21

AB21

AG21

B24

F22

J22

L22

N22

R22

U22

W22

AE22

A23

D23

AA23

AC23

AJ23

F24

H24

K24

M24

P24

T24

V24

AA24

AG24

A25

D25

AA25

AE25

G26

J26

L26

N26

R26

U26

W26

AB26

A27

F27

AC27

AG27

AJ27

AC28

AE28

C29

E29

G29

J29

L29

N29

U29

W29

AA29

AJ10

AJ12

AJ18

AJ20

C22

D28

E28

L6

T9

AJ26

0.1U_0402_16V7K

+1.2VS

+1.2VS_PLL

+1.5VS_DVO

+1.5VS_DAC

+1.5VS_ALVDS

+1.5VS_DLVDS

+2.5V_TXLVDS

+3VS_GPIO

C26

+1.2VS

N14

R14

U14

AA15

N16

R16

U16

AA17

AA19

W21

H14

D29

G13

D10

J15

P13

T13

P15

T15

P17

T17

V1

Y1

W5

U6

U8

W8

V7

V9

Y2

A6

B16

E1

J1

N1

E4

J4

M4

E6

H7

J8

L8

M8

N8

R8

K9

M9

P9

A9

B9

B8

A11

B11

B14

J13

B15

F9

B10

A12

A3

A4

U37E

Montara-GM(L)

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCCHL0

VCCHL1

VCCHL2

VCCHL3

VCCHL4

VCCHL5

VCCHL6

VCCHL7

VCCAHPLL

VCCAGPLL

VCCADPLLA

VCCADPLLB

VCCDVO_0

VCCDVO_1

VCCDVO_2

VCCDVO_3

VCCDVO_4

VCCDVO_5

VCCDVO_6

VCCDVO_7

VCCDVO_8

VCCDVO_9

VCCDVO_10

VCCDVO_11

VCCDVO_12

VCCDVO_13

VCCDVO_14

VCCDVO_15

VCCADAC0

VCCADAC1

VSSADAC

VCCALVDS

VSSALVDS

VCCDLVDS0

VCCDLVDS1

VCCDLVDS2

VCCDLVDS3

VCCTXLVDS0

VCCTXLVDS1

VCCTXLVDS2

VCCTXLVDS3

VCCGPIO_0

VCCGPIO_1

MONTARA-GM(L)

POWER

VTTLF0

VTTLF1

VTTLF2

VTTLF3

VTTLF4

VTTLF5

VTTLF6

VTTLF7

VTTLF8

VTTLF9

VTTLF10

VTTLF11

VTTLF12

VTTLF13

VTTLF14

VTTLF15

VTTLF16

VTTLF17

VTTLF18

VTTLF19

VTTLF20

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCQSM0

VCCQSM1

VCCASM0

VCCASM1

+CPU_CORE

G15

H16

H18

J19

H20

L21

N21

R21

U21

H22

M22

P22

T22

V22

Y29

K29

F29

AB29

A26

A20

A18

A22

C24 0.1U_0402_16V7K

A24

C23 0.1U_0402_16V7K

H29

C55 0.1U_0402_16V7K

M29

C72 0.1U_0402_16V7K

V29

C95 0.1U_0402_16V7K

AC1

AG1

+2.5V

AB3

AF3

Y4

AJ5

AA6

AB6

AF6

Y7

AA8

AB8

Y9

AF9

AJ9

AB10

AA11

AB12

AF12

AA13

AJ13

AB14

AF15

AB16

AJ17

AB18

AF18

AB20

AF21

AJ21

AB22

AF24

AJ25

AF27

AC29

AF29

AG29

+2.5V_QSM

AJ6

AJ8

+1.2VS_ASM

AD1

AF1

+2.5V

C116

0.1U_0402_16V7K

0.1U_0402_16V7K

1 2

L38

L_0603

0.1U_0402_16V7K

+1.2VS +1.2VS_PLL

+2.5V +2.5V

C121

+1.5VS_DVO+1.5VS

C58

0.1U_0402_16V7K

+1.5VS

1 2

L27

L_0603

C21

0.1U_0402_16V7K

FB1

0.1UH_10%

@220UF_D2_4V_25m

FB2

0.1UH_10%

@220UF_D2_4V_25m

+2.5V +2.5V_QSM

1 2

L11

L_0603

0.1U_0402_16V7K

C117

0.1U_0402_16V7K

C122

0.1U_0402_16V7K

C65

10U_1206_6.3V6M

+1.5VS_DAC

0.01U_0402_16V7K

C14

C13

C146

4.7U_1206_10V7K

+1.2VS

C36

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

C479

C32

@220UF_D2_4V_25m

C450

0.1U_0402_16V7K

C25

0.1U_0402_16V7K

C145

C118

0.1U_0402_16V7K

C111

0.1U_0402_16V7K

150U_D2_6.3VM

C8

+3VS +3VS_GPIO

C104

0.1U_0402_16V7K

C119

0.1U_0402_16V7K

C112

0.1U_0402_16V7K

1

+

C476

+2.5V +2.5V_TXLVDS

R28

0_0805_5%

2

1 2

L28

L_0603

150U_D2_6.3VM

10U_1206_6.3V6M

Close to VCCHL0~7One close to D29, one close to Y2

+1.2VS

C101

10U_1206_6.3V6 M

0.1U_0402_16V7K

0.1U_0402_16V7K

+CPU_CORE

1

+

C80

2

1 2

L7

L_0603

C29

C16

C120

C108

C31

0.1U_0402_16V7K

22U_1206_16V4Z

C123

C107

C37

0.1U_0402_16V7K

+1.5VS +1.5VS_DLVDS

0.1U_0402_16V7K

C91

0.1U_0402_16V7K

+1.5VS +1.5VS_ALVDS

1 2

L1

C114

10U_1206_6.3V6 M

C64

C449

L_0603

0.1U_0402_16V7K

100UF_10V_D2

C144

C30

0.1U_0402_16V7K

+1.2VS +1.2VS_ASM

1 2

L41

C509

L_0603

0.1U_0402_16V7K

C100

0.1U_0402_16V7K

C513

C53

0.1U_0402_16V7K

C444

22U_1206_16V4Z

+

C76

47U_6.3V_M

C448

0.01U_0402_16V7K

100UF_10V_D2

C20

0.1U_0402_16V7K

+

47U_6.3V_M

C511

100UF_D_16V

C7

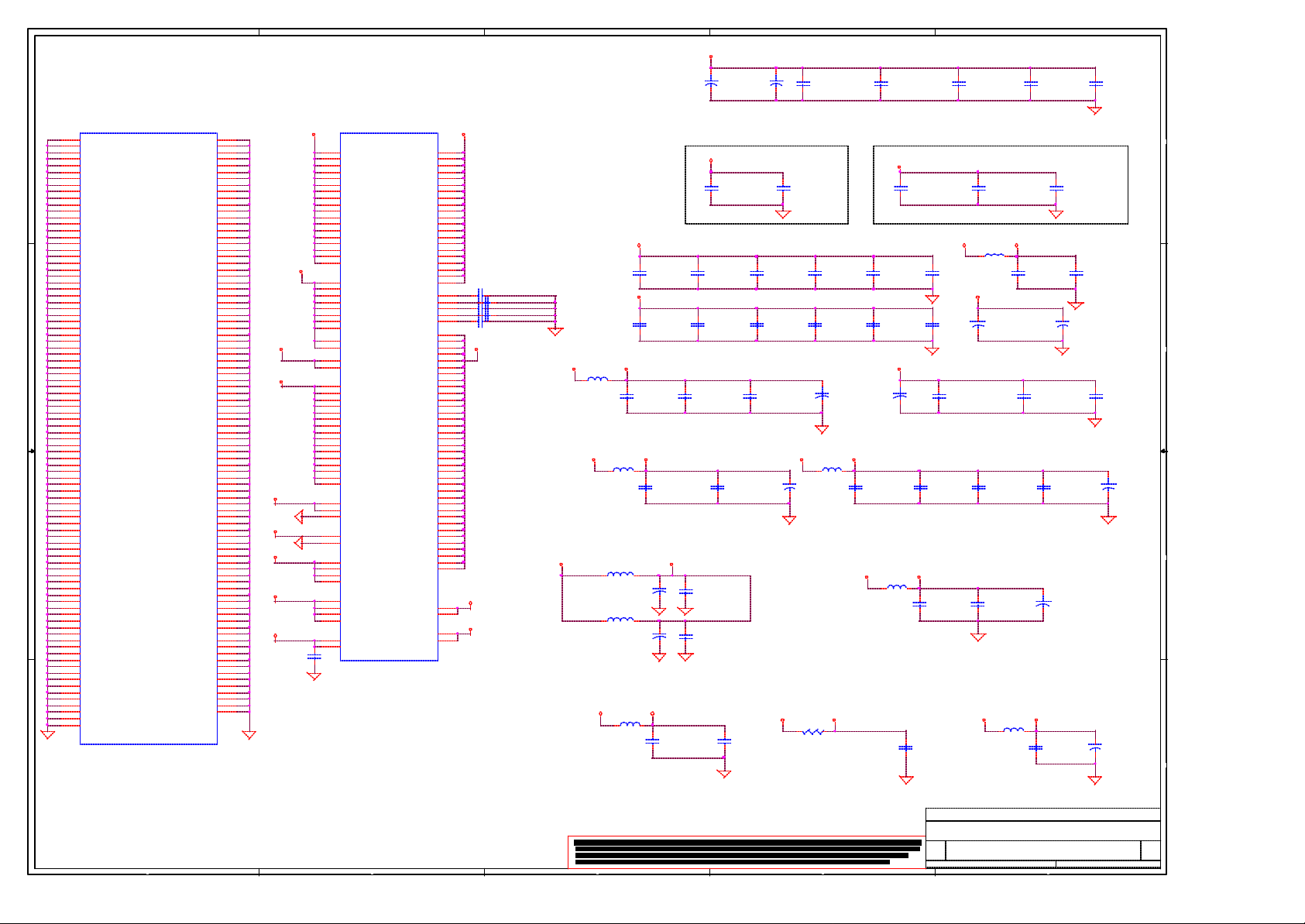

Compal Electronics, Ltd.

Title

Montara-GML (POWER)

Size Document Number Rev

Custom

LA-1641

5

4

3

2

Date: Sheet of

9 46Monday, November 25, 2002

1

0.3

5

U37C

Montara-GM(L)

DDRCLK0

DDRCLK0#

DDRCLK1

DDRCLK1#

DDRCLK3

DDRCLK3#

DDRCLK4

DDRCLK4#

DDR_SBS0

DDR_SBS1

DDR_SDM0

DDR_SDM1

DDR_SDM2

DDR_SDM3

DDR_SDM4

DDR_SDM5

DDR_SDM6

DDR_SDM7

DDR_SMA_B1

DDR_SMA_B2

DDR_SMA_B4

DDR_SMA_B5

+MRCOMP

+MVSWINGL

+MVSWINGH

AC18

AD14

AD13

AD17

AD11

AC13

AD8

AD7

AC6

AC5

AC19

AD5

AG2

AH5

AH8

AE12

AH17

AE21

AH24

AH27

AD15

AD25

AC21

AC24

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AC7

AC9

AC10

AD23

AD26

AC22

AC25

AD22

AD20

AH12

AD19

AD21

AD24

AH28

AH15

AD16

AC12

AF11

AD10

AC15

AC16

AJ22

AJ19

AB5

AB2

AA2

AA3

AB4

AB7

AE5

AE6

AE9

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SMA10

SMA11

SMA12

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SWE#

SRAS#

SCAS#

SCMDCLK0

SCMDCLK0#

SCMDCLK1

SCMDCLK1#

SCMDCLK2

SCMDCLK2#

SCMDCLK3

SCMDCLK3#

SCMDCLK4

SCMDCLK4#

SCMDCLK5

SCMDCLK5#

SCKE0

SCKE1

SCKE2

SCKE3

SCS#0

SCS#1

SCS#2

SCS#3

SBA0#

SBA1#

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

SDM8

SMA_B1

SMA_B2

SMA_B4

SMA_B5

SRCVENOUT#

SRCVENIN#

SMVSWINGL

SMVSWINGH

MONTARA-GM(L)

MEMORY

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

SDQ64

SDQ65

SDQ66

SDQ67

SDQ68

SDQ69

SDQ70

SDQ71

SMVREF0SMRCOMP

0.1U_0402_16V4Z

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

D D

DDR_CLK011

DDR_CLK0#11

DDR_CLK111

DDR_CLK1#11

DDR_CLK311

DDR_CLK3#11

DDR_CLK411

C C

DDR_CLK4#11

DDR_CKE011,12

DDR_CKE111,12

DDR_CKE211,12

DDR_CKE311,12

DDR_SCS#011,12

DDR_SCS#111,12

DDR_SCS#211,12

DDR_SCS#311,12

DDR_SBS011,12

DDR_SBS111,12

Routed with Vias

next to ball.

B B

RCVENOUT#

RCVENIN#

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

DDR_SDQS4

DDR_SDQS5

DDR_SDQS6

DDR_SDQS7

DDR_SWE#

DDR_SRAS#

DDR_SCAS#

DDR REF & SWING VOLTAGE

AF2

AE3

AF4

AH2

AD3

AE2

AG4

AH3

AD6

AG5

AG7

AE8

AF5

AH4

AF7

AH6

AF8

AG8

AH9

AG10

AH7

AD9

AF10

AE11

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ24AB1

C142

4

DDR_SDQ0

DDR_SDQ1

DDR_SDQ2

DDR_SDQ3

DDR_SDQ4

DDR_SDQ5

DDR_SDQ6

DDR_SDQ7

DDR_SDQ8

DDR_SDQ9

DDR_SDQ10

DDR_SDQ11

DDR_SDQ12

DDR_SDQ13

DDR_SDQ14

DDR_SDQ15

DDR_SDQ16

DDR_SDQ17

DDR_SDQ18

DDR_SDQ19

DDR_SDQ20

DDR_SDQ21

DDR_SDQ22

DDR_SDQ23

DDR_SDQ24

DDR_SDQ25

DDR_SDQ26

DDR_SDQ27

DDR_SDQ28

DDR_SDQ29

DDR_SDQ30

DDR_SDQ31

DDR_SDQ32

DDR_SDQ33

DDR_SDQ34

DDR_SDQ35

DDR_SDQ36

DDR_SDQ37

DDR_SDQ38

DDR_SDQ39

DDR_SDQ40

DDR_SDQ41

DDR_SDQ42

DDR_SDQ43

DDR_SDQ44

DDR_SDQ45

DDR_SDQ46

DDR_SDQ47

DDR_SDQ48

DDR_SDQ49

DDR_SDQ50

DDR_SDQ51

DDR_SDQ52

DDR_SDQ53

DDR_SDQ54

DDR_SDQ55

DDR_SDQ56

DDR_SDQ57

DDR_SDQ58

DDR_SDQ59

DDR_SDQ60

DDR_SDQ61

DDR_SDQ62

DDR_SDQ63

+SDREF

3

RP45 4P2R_10

DDR_SDQ0 DDR_DQ0

1 4

2 3

DDR_SDQ1 DDR_DQ1

RP44 4P2R_10

DDR_SDQ6 DDR_DQ6

1 4

2 3

DDR_SDQ7 DDR_DQ7

RP43 4P2R_10

1 4

2 3

RP42 4P2R_10

1 4

DDR_SDQ14 DDR_DQ14

DDR_SDQ11 DDR_DQ11

2 3

RP41 4P2R_10

1 4

2 3

DDR_SDQ16

RP40 4P2R_10

1 4

DDR_SDQ21 DDR_DQ21

2 3

RP39 4P2R_10

1 4

DDR_SDQ26 DDR_DQ26

2 3

RP38 4P2R_10

1 4

DDR_SDQ29 DDR_DQ29

2 3

RP35 4P2R_10

1 4

2 3

DDR_SDQ37

RP34 4P2R_10

1 4

DDR_SDQ34

2 3

RP33 4P2R_10

DDR_SDQ40 DDR_DQ40

1 4

2 3

RP32 4P2R_10

1 4

DDR_SDQ41 DDR_DQ41

DDR_SDQ42 DDR_DQ42

2 3

RP31 4P2R_10

DDR_SDQ53 DDR_DQ53

1 4

DDR_SDQ55 DDR_DQ55

2 3

RP30 4P2R_10

DDR_SDQ50 DDR_DQ50

1 4

2 3

DDR_SDQ54 DDR_DQ54

RP29 4P2R_10

1 4

2 3

DDR_SDQ58 DDR_DQ58

RP28 4P2R_10

1 4

DDR_SDQ62

2 3

DDR_DQ12DDR_SDQ12

DDR_DQ15DDR_SDQ15

DDR_DQ20DDR_SDQ20

DDR_DQ16

DDR_DQ23DDR_SDQ23

DDR_DQ28DDR_SDQ28

DDR_DQ27DDR_SDQ27

DDR_DQ38DDR_SDQ38

DDR_DQ37

DDR_DQ35DDR_SDQ35

DDR_DQ34

DDR_DQ46DDR_SDQ46

DDR_DQ57DDR_SDQ57

DDR_DQ59DDR_SDQ59

RP24 4P2R_10

DDR_SDQ4 DDR_DQ4

1 4

2 3

DDR_SDQ5 DDR_DQ5

RP23 4P2R_10

1 4

2 3

DDR_SDQ2

RP22 4P2R_10

1 4

2 3

DDR_SDQ13 DDR_DQ13

RP21 4P2R_10

1 4

DDR_SDQ10 DDR_DQ10

DDR_SDQ8 DDR_DQ8

2 3

RP20 4P2R_10

DDR_SDQ17 DDR_DQ17

1 4

2 3

DDR_SDQ18

RP19 4P2R_10

1 4

DDR_SDQ22

2 3

RP18 4P2R_10

1 4

DDR_SDQ25 DDR_DQ25

DDR_SDQ24

2 3

RP17 4P2R_10

DDR_SDQ31 DDR_DQ31

1 4

DDR_SDQ30

2 3

RP14 4P2R_10

1 4

2 3

DDR_SDQ33

RP13 4P2R_10

1 4

DDR_SDQ36 DDR_DQ36

DDR_SDQ39 DDR_DQ39

2 3

RP12 4P2R_10

1 4

2 3

RP11 4P2R_10

1 4

DDR_SDQ47 DDR_DQ47

2 3

RP10 4P2R_10

1 4

2 3

RP9 4P2R_10

1 4

2 3

RP8 4P2R_10

DDR_SDQ56 DDR_DQ56

1 4

2 3

DDR_SDQ60 DDR_DQ60

RP7 4P2R_10

1 4

DDR_SDQ61

DDR_SDQ63

2 3

DDR_DQ3DDR_SDQ3

DDR_DQ2

DDR_DQ9DDR_SDQ9

DDR_DQ18

DDR_DQ19DDR_SDQ19

DDR_DQ22

DDR_DQ24

DDR_DQ30

DDR_DQ32DDR_SDQ32

DDR_DQ33

DDR_DQ45DDR_SDQ45

DDR_DQ44DDR_SDQ44

DDR_DQ43DDR_SDQ43

DDR_DQ49DDR_SDQ49

DDR_DQ52DDR_SDQ52

DDR_DQ51DDR_SDQ51

DDR_DQ48DDR_SDQ48

DDR_DQ61

DDR_DQ63DDR_DQ62

2

DDR_SMA10 DDR_F_SMA10

DDR_SBS1 DDR_F_SBS1

DDR_SMA8

DDR_SMA0 DDR_F_SMA0

DDR_SBS0 DDR_F_SBS0

DDR_SMA12 DDR_F_SMA12

DDR_SMA11

DDR_SCAS# DDR_F_SCAS#

DDR_SWE#11,12 DDR_F_SWE# 11

DDR_SWE# DDR_F_SWE#

DDR_F_SMA[6..12]

DDR_SMA[1..2]

DDR_SMA_B[1..2]

DDR_SMA_B[4..5]

DDR_SDM0

DDR_SDM1

DDR_SDM2

DDR_SDM3

DDR_SDM4

DDR_SDM5

DDR_SDM6

DDR_SDM7

RP16 4P2R_10

1 4

2 3

RP27 4P2R_10

1 4

2 3

RP37 4P2R_10

1 4

2 3

RP36 4P2R_10

1 4

2 3

RP26 4P2R_10

1 4

2 3

RP25 4P2R_10

1 4

2 3

RP15 4P2R_10

1 4

2 3

DDR_DM[0..7]

DDR_F_SBS[0..1]

DDR_DQS[0..7]

DDR_DQ[0..63]

DDR_SMA[6..12]

DDR_SMA[4..5]

R153 10_0402_5%

R152 10_0402_5%

R151 10_0402_5%

R150 10_0402_5%

R149 10_0402_5%

R148 10_0402_5%

R147 10_0402_5%

R146 10_0402_5%

DDR_DM[0..7] 11,12

DDR_F_SBS[0..1] 11

DDR_DQS[0..7] 11,12

DDR_DQ[0..63] 11,12

DDR_SMA[6..12] 11,12

DDR_F_SMA[6..12] 11

DDR_SMA[1..2] 11,12

DDR_SMA[4..5] 11,12

DDR_SMA_B[1..2] 11,12

DDR_SMA_B[4..5] 11,12

1

DDR_F_SMA9DDR_SMA9

DDR_F_SMA8

DDR_F_SMA3DDR_SMA3

DDR_F_SRAS#DDR_SRAS#

DDR_F_SMA11

DDR_F_SMA7DDR_SMA7

DDR_F_SMA6DDR_SMA6

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

DDR_F_SMA3 11DDR_SMA311,12

DDR_F_SMA0 11DDR_SMA011,12

DDR_F_SRAS# 11DDR_SRAS#11,12

DDR_F_SCAS# 11DDR_SCAS#11,12

+2.5V

R92

60.4_0402_1%

+MRCOMP +MVSWINGL +MVSWINGH

A A

C125

0.1U_0402_16V4Z

R93

60.4_0402_1%

5

0.1U_0402_16V4Z

+2.5V +2.5V

R97

604_0603_1%

R100

150_0402_1%

C139

0.1U_0402_16V4Z

DDR_SDQS1 DDR_DQS1

R102

150_0402_1% R168 10_0402_5%

R107

604_0603_1%

C151

4

DDR_SDQS2 DDR_DQS2

DDR_SDQS3 DDR_DQS3

DDR_SDQS4 DDR_DQS4

R171 10_0402_5%

R170 10_0402_5%

R169 10_0402_5%

R167 10_0402_5%

R166 10_0402_5%

R165 10_0402_5%

R164 10_0402_5%

3

DDR_DQS0DDR_SDQS0

DDR_DQS5DDR_SDQS5

DDR_DQS6DDR_SDQS6

DDR_DQS7DDR_SDQS7

Compal Electronics, Ltd.

Title

Montara-GML (DDR)

Size Document Number Rev

Custom

LA-1641

2

Date: Sheet of

10 46Thursday, November 28, 2002

1

0.3

5

4

3

2

1

+2.5V

JP22

1

VREF

3

DDR_DQ0

DDR_DQ1

DDR_DQS0

DDR_DQ6

D D

DDR_CLK010

DDR_CLK0#10 DDR_CLK3#10

C C

DDR_F_SMA310

DDR_F_SBS010

DDR_F_SWE#10 DDR_SWE#10,12

DDR_SCS#010,12 DDR_SCS#1 10,12 DDR_SCS#210,12 DDR_SCS#3 10,12

B B

A A

DDR_DQ7

DDR_DQ12

DDR_DQ15

DDR_DQS1

DDR_DQ14

DDR_DQ11

DDR_DQ20

DDR_DQ16

DDR_DQS2

DDR_DQ21

DDR_DQ23

DDR_DQ28

DDR_DQ26

DDR_DQS3

DDR_DQ27

DDR_DQ29

DDR_CKE1 DDR_CKE0

DDR_F_SMA12

DDR_F_SMA9

DDR_F_SMA7

DDR_F_SMA3

DDR_SMA1

DDR_F_SMA10

DDR_F_SBS0

DDR_F_SWE#

DDR_SCS#0 DDR_SCS#1 DDR_SCS#2 DDR_SCS#3

DDR_DQ38

DDR_DQ37

DDR_DQS4

DDR_DQ35

DDR_DQ34

DDR_DQ40

DDR_DQ46

DDR_DQS5

DDR_DQ41

DDR_DQ42

DDR_DQ53

DDR_DQ55

DDR_DQS6

DDR_DQ50

DDR_DQ54

DDR_DQ57

DDR_DQ58

DDR_DQS7

DDR_DQ59

DDR_DQ62

SMB_DATA

SMB_CLK

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

AMP1376408_STANDARD

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

A11

VSS

VDD

BA1

RAS#

CAS#

S1#

DU

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

DU

A8

A6

A4

A2

A0

DIMM0

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DDR_DQ4

DDR_DQ5

DDR_DM0

DDR_DQ3

DDR_DQ2

DDR_DQ9

DDR_DQ13

DDR_DM1

DDR_DQ10

DDR_DQ8

DDR_DQ17

DDR_DQ18

DDR_DM2

DDR_DQ19

DDR_DQ22

DDR_DQ25

DDR_DQ24

DDR_DM3

DDR_DQ31

DDR_DQ30

DDR_F_SMA11

DDR_F_SMA8

DDR_F_SMA6

DDR_SMA4DDR_SMA5

DDR_SMA2

DDR_F_SMA0

DDR_F_SBS1

DDR_F_SRAS#

DDR_F_SCAS#

DDR_DQ32

DDR_DQ33

DDR_DM4

DDR_DQ36

DDR_DQ39

DDR_DQ45

DDR_DQ44

DDR_DM5

DDR_DQ47

DDR_DQ43

DDR_DQ49

DDR_DQ52

DDR_DM6

DDR_DQ51

DDR_DQ48

DDR_DQ56

DDR_DQ60

DDR_DM7

DDR_DQ61

DDR_DQ63

+SDREF_R

C208

0.1U_0402_16V4Z

DDR_CKE0 10,12DDR_CKE110,12

DDR_F_SMA0 10

DDR_F_SBS1 10

DDR_F_SRAS# 10

DDR_F_SCAS# 10

DDR_CLK1# 10

DDR_CLK1 10

L18

1 2

MurataBLM21A601S_0805

DDR_CKE310,12

DDR_SMA310,12

DDR_SBS010,12

+SDREF

DDR_CLK310

SMB_DATA15,16

SMB_CLK15,16

DDR_SMA_B1

+2.5V

JP23

1

VREF

3

DDR_DQ0

DDR_DQ1

DDR_DQS0

DDR_DQ6

DDR_DQ7

DDR_DQ12

DDR_DQ15

DDR_DQS1

DDR_DQ14

DDR_DQ11

DDR_DQ20

DDR_DQ16

DDR_DQS2

DDR_DQ21

DDR_DQ23

DDR_DQ28

DDR_DQ26

DDR_DQS3 DDR_DQS[0..7]

DDR_DQ27

DDR_DQ29

DDR_CKE3

DDR_SMA12

DDR_SMA9

DDR_SMA7

DDR_SMA3

DDR_SMA10

DDR_SBS0

DDR_SWE#

DDR_DQ38

DDR_DQ37

DDR_DQS4

DDR_DQ35

DDR_DQ34

DDR_DQ40

DDR_DQ46

DDR_DQS5

DDR_DQ41

DDR_DQ42

DDR_DQ53

DDR_DQ55

DDR_DQS6

DDR_DQ50

DDR_DQ54

DDR_DQ57

DDR_DQ58

DDR_DQS7

DDR_DQ59

DDR_DQ62

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

AMP1376408_REVERSE

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

A11

VSS

VDD

BA1

RAS#

CAS#

S1#

DU

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

DU

A8

A6

A4

A2

A0

+2.5V

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DDR_DQ4

DDR_DQ5