Page 1

NTDPJTV008

TOSHIBA

TECHNICAL TRAINING MANUAL

N7SS CHASSIS

PROJECTION TELEVISION

TOSHIBA AMERICA CONSUMER PRODUCTS, INC.

NATIONAL SERVICE DIVISION

TRAINING DEPARTMENT

1420-B TOSHIBA DRIVE

LEBANON, TENNESSEE 37087

PHONE: (615) 449-2360

FAX: (615) 444-7520

www.toshiba.com/tacp

TP71G90

©1997

Page 2

CONTENTS

SECTION I

OUTLINE...........................1-1

1.OUTLINE....................................................1-2

2.SPECIFICATIONS 37 KEYS...................1-3

3.TP71G90 SERIES DIFFERENCES.........1-4

PC Board Layout.......................................1-5

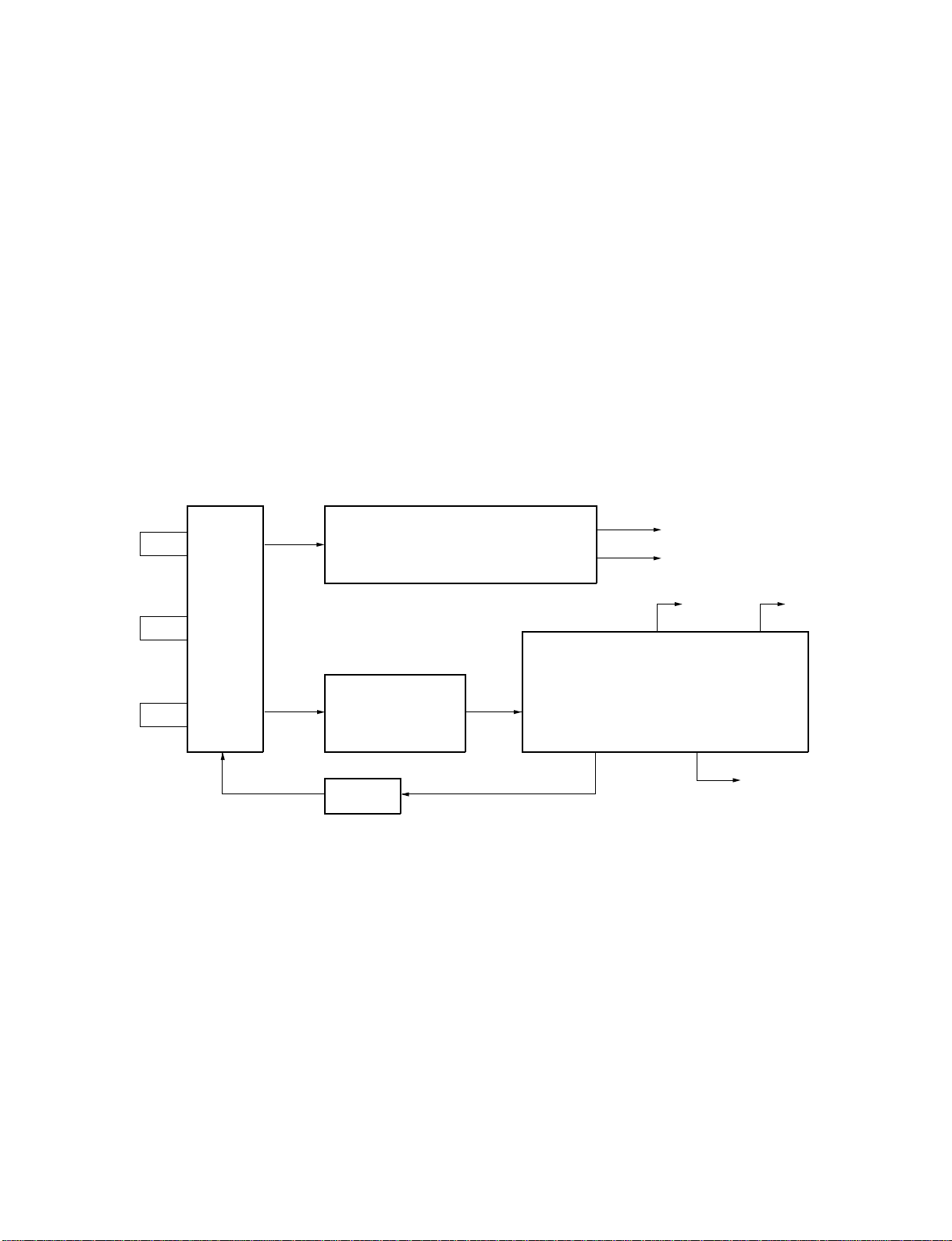

TP71G90 Block Diagram..........................1-6

SECTION II

AUDIO CIRCUIT................2-1

1.GENERAL...................................................2-2

2.FLOW OF SIGNAL...................................2-2

Audio Circuit Block Diagram...................2-3

3.DESCRIPTION OF CIRCUITS...............2-4

3-1.IMA Module (MVUS34S/MVUS34B)........2-4

3-2.A. PRO Circuit............................................2-4

3-3.A/V Selector Circuit...................................2-4

QV01(TA8851CN) Block Diagram...........2-5

3-4.Surround-sound Circuit.............................2-6

3-5.Audio Output Circuit..................................2-6

SECTION III

TUNER/IMA CIRCUIT....3-1

1.CIRCUIT BLOCK.....................................3-2

1-1.Outline........................................................3-2

1-2.RF SW.........................................................3-3

1-3.TUNER........................................................3-3

1-4.TIF for PIP.................................................3-4

1-5.IMA.............................................................3-4

1-6.CATV System AUTO MODE Decision......3-5

2.IF/RF CIRCUIT

TROUBLESHOOTING.............................3-6

2-1.No Picture of VHF/UHF

(Main Screen).............................................3-6

2-2.No Picture of VHF/UHF

(PIP Screen)................................................3-7

SECTION IV

CHANNEL SELECTION

2.HARDWARE COMPONENT...................4-2

3.MICROCOMPUTER.................................4-3

3-1.Microcomputer Terminal Function..........4-4

3-2.Microcomputer Terminal Name

and Operation Logic..................................4-5

4.E2PROM (QA02)........................................4-6

5.ON SCREEN FUNCTION........................4-6

6.SYSTEM BLOCK DIAGRAM.................4-7

7.LOCAL KEY

DETECTION METHOD...........................4-8

8.REMOTE CONTROL CODE

ASSIGNMENT CUSTOM

COES ARE 40-BFH...................................4-9

9.ENTERING TO SERVICE MODE.......4-11

10.TEST SIGNAL SELECTION.................4-11

11.SERVICE ADJUSTMENT......................4-11

12.FAILURE DIAGNOSIS

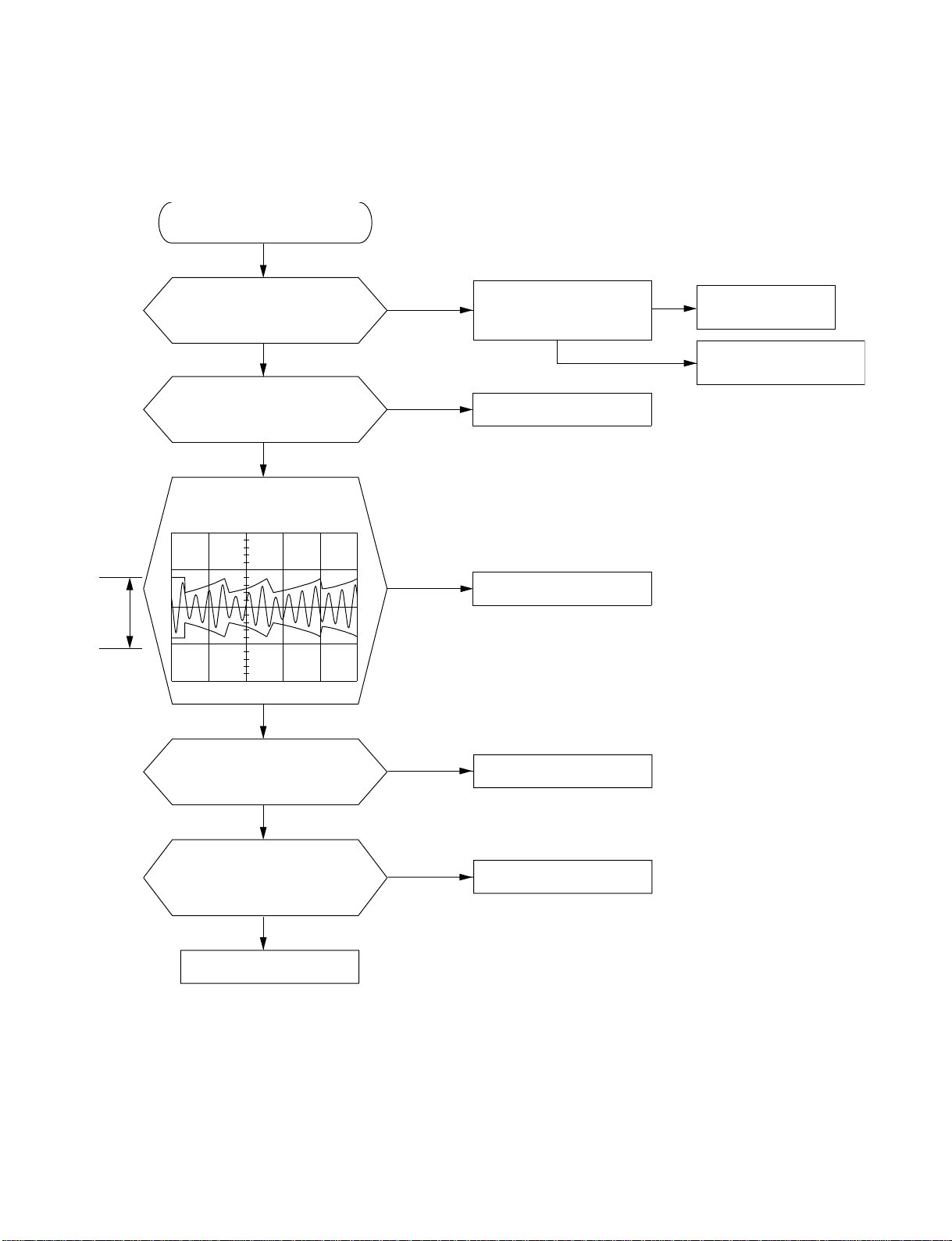

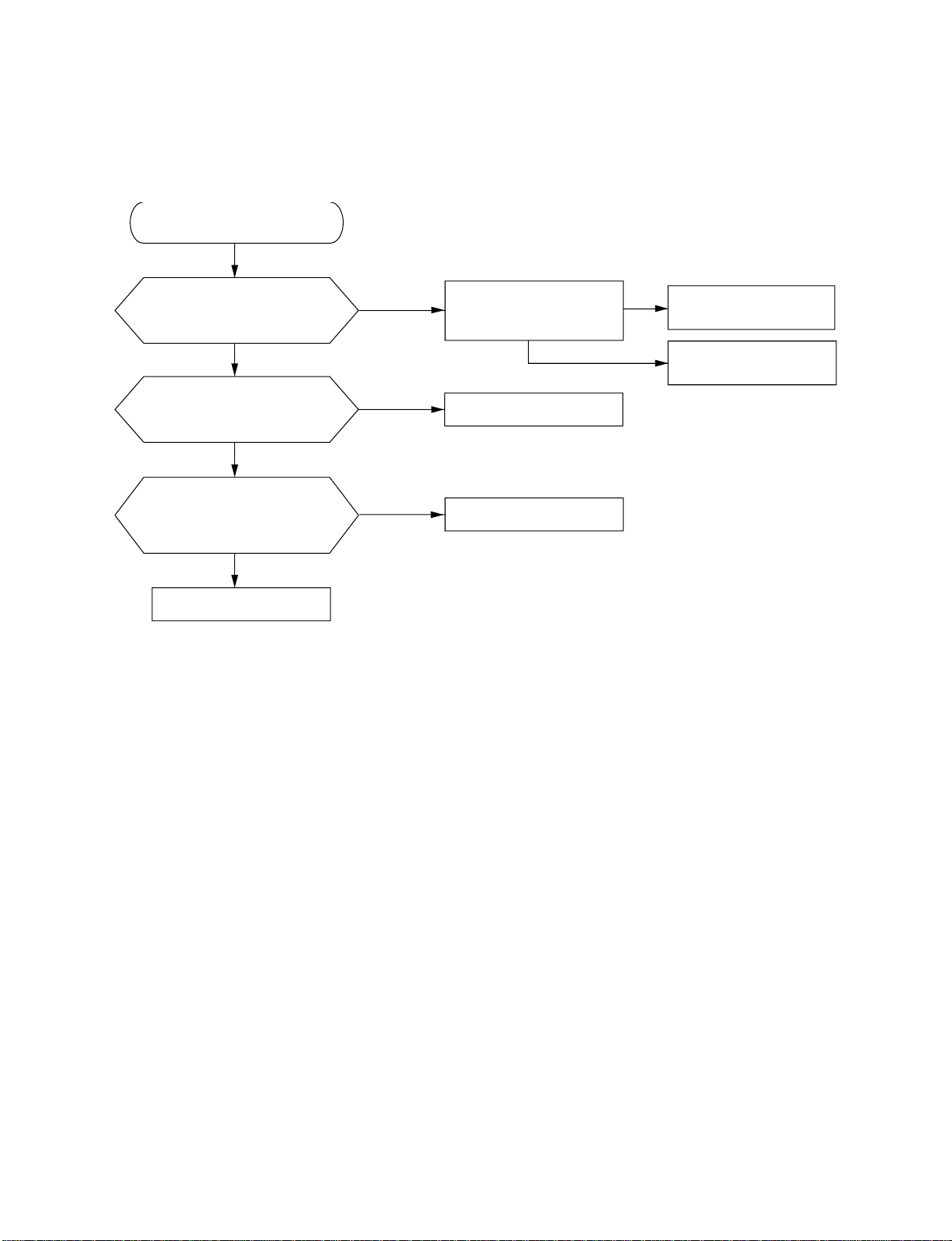

PROCEDURE.....................................................4-12

12-1.Contens to be Confirmed by Customer......4-12

12-4.Understanding Self Diagnosis

Function Indication..................................4-13

13.TROUBLE SHOOTING CHART..........4-14

13-1.TV does not turn ON................................4-15

14-2.No Acception of Key-IN...........................4-15

14-3.No Picture (Snow Noise)...........................4-15

14-4.Memory Circuit Check............................4-16

14-5.No Indication on Screen...........................4-16

SECTION V

VIDEO CIRCUIT..............5-1

1.A/V SELECTOR CIRCUIT......................5-2

1-1.General.......................................................5-2

1-2.Speifications...............................................5-2

1-3.Operation of the Circuit.............................5-3

2.VIDEO PROCESSING CIRCUIT...........5-4

2-1.General.......................................................5-4

2-2.V/C/D IC (Q501).........................................5-4

3.CRT OUTPUT CIRCUIT..........................5-7

3-1.General.......................................................5-7

3-2.Output Circuit............................................5-7

3-3.Blue Extension Circuit...............................5-8

CIRCUIT............................4-1

1.OUTLINE OF CHANNEL

SELECTION CIRCUIT SYSTEM...........4-2

SECTION VI

YCS/DUAL CIRCUIT.......6-1

i

Page 3

1.GENERAL...................................................6-2

2.OPERATION PRINCIPLE.......................6-2

2-1.DUAL Block................................................6-2

2-2.YCS (3-dimension YCS Separator)

Block...........................................................6-2

2-3.Memory Selector Block.............................6-2

3.CIRCUIT OPERATION............................6-2

3-1.DUAL Section.............................................6-2

3-2.YCS Section................................................6-3

4.TERMINAL DESCRIPTION...................6-3

4-1.PY01............................................................6-3

4-2.PZ01............................................................6-3

4-3.QZ01 (TC90A28F).....................................6-4

5.YCS TROUBLESHOOTING....................6-6

6.BLOCK DIAGRAM...................................6-7

VERTICAL OUTPUT CIR-

CUIT...................................9-1

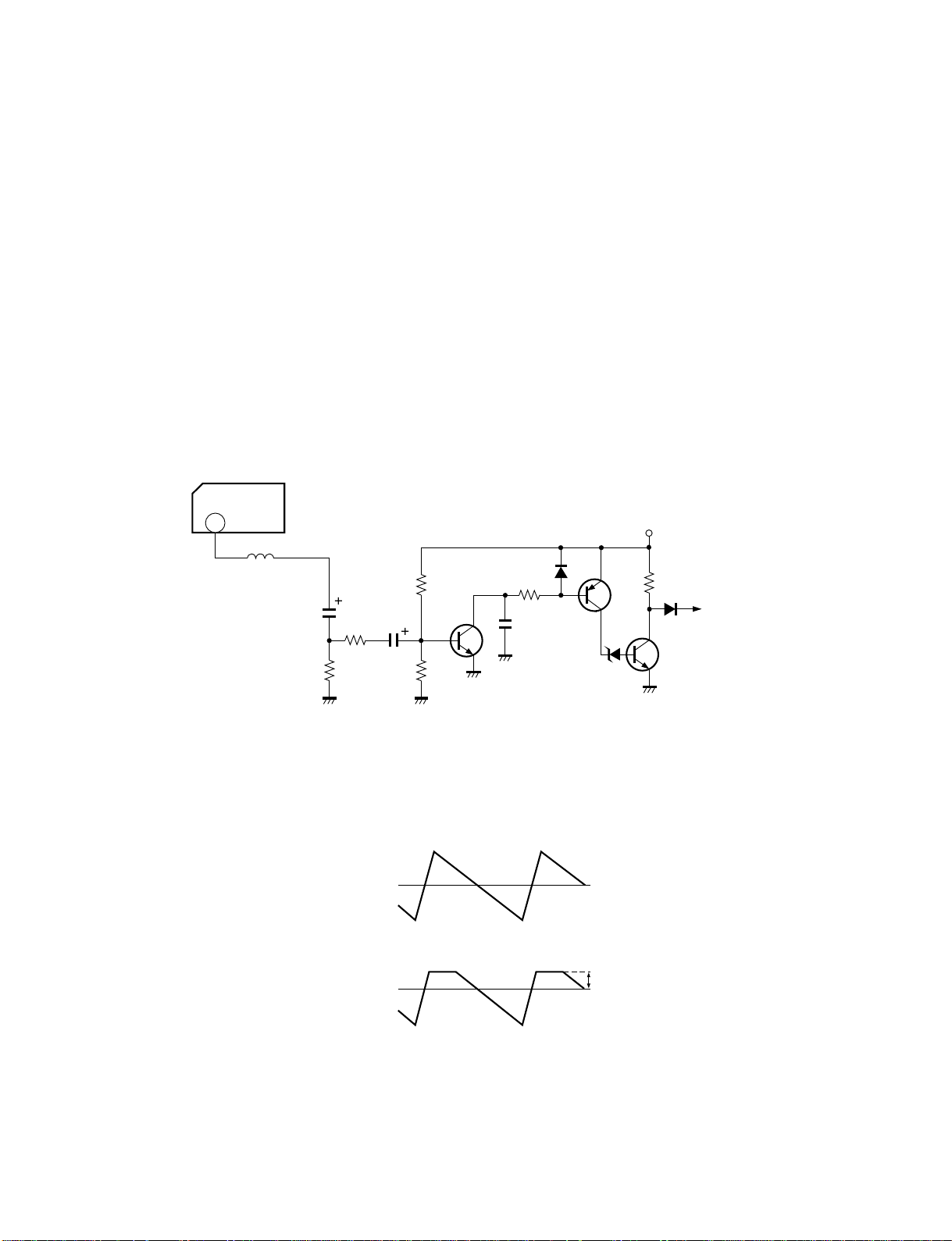

1.OUTLINE....................................................9-2

1-1.Theory of Operation..................................9-2

2.V OUTPUT CIRCUIT...............................9-3

2-1.Actual Circuit.............................................9-3

2-2.Sawtooth Waveform Generation..............9-3

2-3.Vertical Output...........................................9-4

2-4.Vertical Linearity

Characteristic Correction.........................9-6

2-5.Centering Circuit.......................................9-6

3.PROTECTION CIRCUIT FOR

VERTICAL DEFLECTION STOP..........9-7

3-1.+35V Over Current Protection Circuit.....9-8

SECTION VII

DOUBLE-SPEED CIRCUIT

(UPCON)..............................7-1

1.GENERAL...................................................7-2

2.CIRCUIT OPERATION............................7-2

2-1.Signal Flow.................................................7-2

2-2.Clock/Sync Signal......................................7-3

2-3.I2C BUS.......................................................7-3

3.BLOCK DIAGRAM...................................7-4

4.PIN ASSIGNMENT....................................7-5

5TERMINAL DESCRIPTION AND

TROUBLESHOOTING.............................7-8

SECTION VIII

SYNC SEPARATION CIRCUIT &

HORIZONTAL OSCILLATION CIR-

CUIT.........................................

1.OUTLINE....................................................8-2

2.SYNC SEPARATION CIRCUIT

AND 32 fH OSCILLATOR.......................8-4

2-1.Theory of Operation..................................8-4

3.HORIZONTAL AND VERTICAL

OSCILLATION CIRCUIT.......................8-5

3-1.IC (LA7860) Operation.............................8-6

2-2.Horizontal Phase Shift Circuit................8-14

8-1

SECTION IX

SECTION X

HORIZONTAL

DEFLECTION CIRCUIT....10-1

1.OUTLINE..................................................10-2

2.HIGH VOLTAGE CIRCUIT..................10-2

2-1.General.....................................................10-3

2-2.X-ray Protection Circuit..........................10-3

2-3.200V Low Voltage Protection Circuit.....10-4

3.DEFLECTION CIRCUIT.......................10-5

3-1.General.....................................................10-6

3-2.S-character Capacitor Switching............10-6

3-3.Horizontal Stop Protection circuit.........10-6

3-4.CRT Protection Circuit............................10-9

SECTION XI

DYNAMIC FOCUS CIRCUIT

11-1

1.OUTLINE..................................................11-2

SECTION XII

DIGITAL CONVERGENCE

CIRCUIT..........................12-1

1.OUTLINE..................................................12-2

2.CIRCUIT DESCRIPTION......................12-2

2-1.Configuration...........................................12-2

2-2.Circuit Operation.....................................12-2

3.PICTURE ADJUSTMENT......................12-4

3-1.Change of Memory (E2PROM)...............12-4

3-2.Service Mode............................................12-4

4.ADJUSTING PICTURE DIMENSION

ii

Page 4

(GREEN PICTURE) ................................. 12-5

5. KEY FUNCTION OF

REMOTE CONTROL UNIT .................. 12-6

6. TROUBLESHOOTING ........................... 12-6

6-1. Adjusting Procedure in Replacing CR T ......12-6

6-2. Adjusting Procedure in Replacing

Conver gence Unit/Main Def. ...................12-6

7 . DIGITAL CONVERGENCE CIRCUIT .. 12-7

7-1. Outline ...................................................... 12-7

7-2. Screen Adjustment....................................12-7

7-3. Adjustment Procedures when Requesting

Convergence Adjustment...........................12-8

8 . CONVERGENCE OUTPUT CIRCUIT .12-11

8-1. Outline ................................................... 12-11

8-2. Circuit Description................................ 12-11

9. CONVERGENCE

TROUBLESHOOTING CHART ......... 12-13

SECTION XIII

OPTICAL SECTION ......13-1

1. NECK COMPONENTS ...........................13-2

1-1. Outline of Components around Neck

of the Projection Tube ..............................13-2

1-2. Theory of Operation ................................13-2

1-3. Projection Tube ........................................13-2

2 . FUNCTION OF KEY COMPONENTS . . 13-3

2-1. Outline ...................................................... 13-3

2-2. Theory of Operation ................................13-3

2-3. ????...........................................................13-3

2-4. Optical Coupling Effect ........................... 13-4

2-5. Lens ...........................................................13-5

2-6. Focus Adjustment .....................................13-6

4. POWER-2.................................................14-11

4-1. Outline of Current Resonant

T ype Supply ........................................... 14-11

4-2. Fundamental Theory ............................ 14-12

4-3. Actual Circuit ........................................ 14-13

4-4. Main Functions of the Control Unit ...... 14-15

5. PROTECT FUNCTION ......................... 14-17

6. TROUBLESHOOTING ......................... 14-18

SECTION XV

CLOSED CAPTION/EDS

CIRCUIT ..........................15-1

1. OUTLINE .................................................. 15-2

2. DATA TRANSMISSION FORMAT....... 15-2

3. DISPLAY FORMAT ................................. 15-2

4. CIRCUIT OPERATION.......................... 15-2

SECTION XIV

POWER SUPPLY

CIRCUIT ..........................14-1

1. OUTLINE .................................................. 14-2

1-1. ST ANDBY Power Supply.........................14-2

1-2. Power-1 .....................................................14-2

1-3. Power-2 .....................................................14-2

1-4. Protect Function .......................................14-2

1-5. Power Supply Line Connection

Diagram....................................................14-3

2. STANDBY POWER SUPPLY ................. 14-4

3. POWER-1 ................................................... 14-4

3-1. Block Diagram ......................................... 14-4

3-2. STR-6811A Pins and Peripheral

Circuit Operation.....................................14-6

iii

Page 5

SECTION I

OUTLINE

1-1

Page 6

1. OUTLINE

(1) Family common chassis;

TP61G90 (different from TP71G90 in size,

data is different from that in contents.)

TW65G80 (WIDE MODEL)

(2) EDTV Engineering;

• Progressive Scan

• Exclusive CRT (long-neck type)—improving

Linearity.

• Color-lens employed in R/G (flare reduction )

• New 3D-YCS (common with domestic model,

32DW77)

• Protection sheet (coating) low-refection

• PIP picture-quality is the same as the main

picture because of using DUAL-UNIT used.

(3) General feature including adjustment are

common with TP50G60.

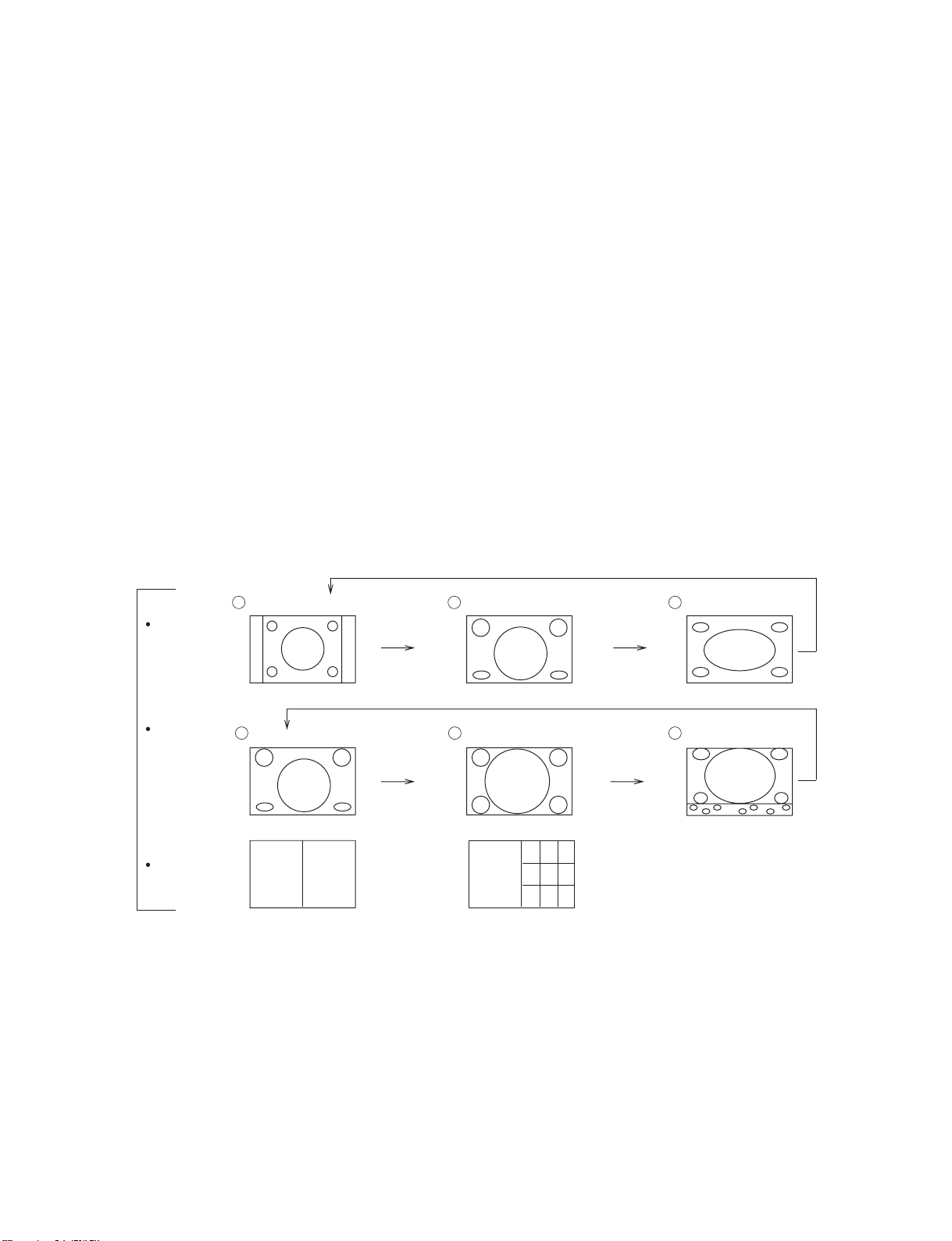

(4) WIDE specifications of TW65G80 are common

with TW40F80/TW56F80. (Fig. 1-1)

SCR EEN

SIZE

TH EATE R

WIDE

DUAL

STANDARD

1

TH EATE R W ID E

2

DUAL 9 SCREEN SEARCH

Fig. 1-1

3

321

FU LL

1-2

Page 7

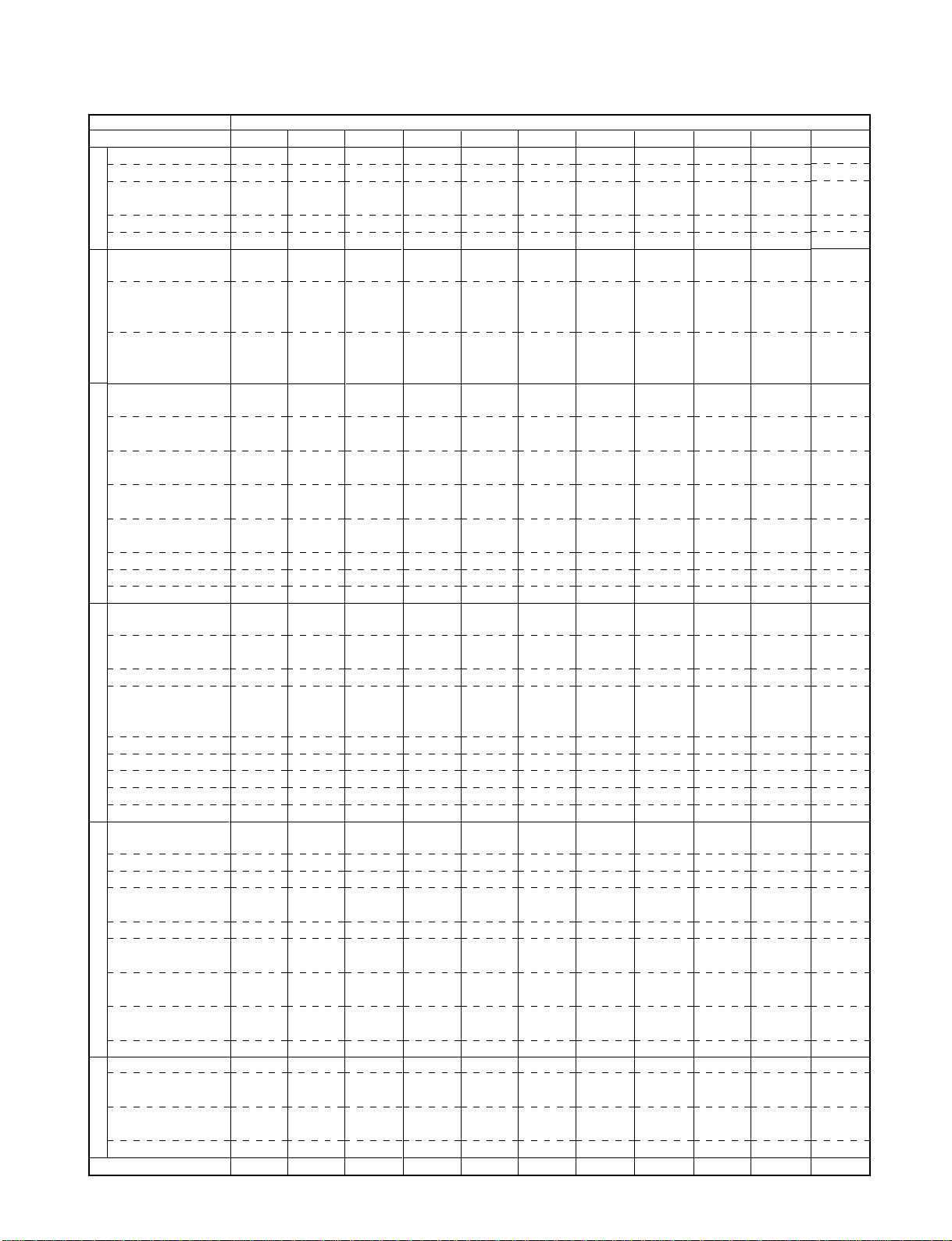

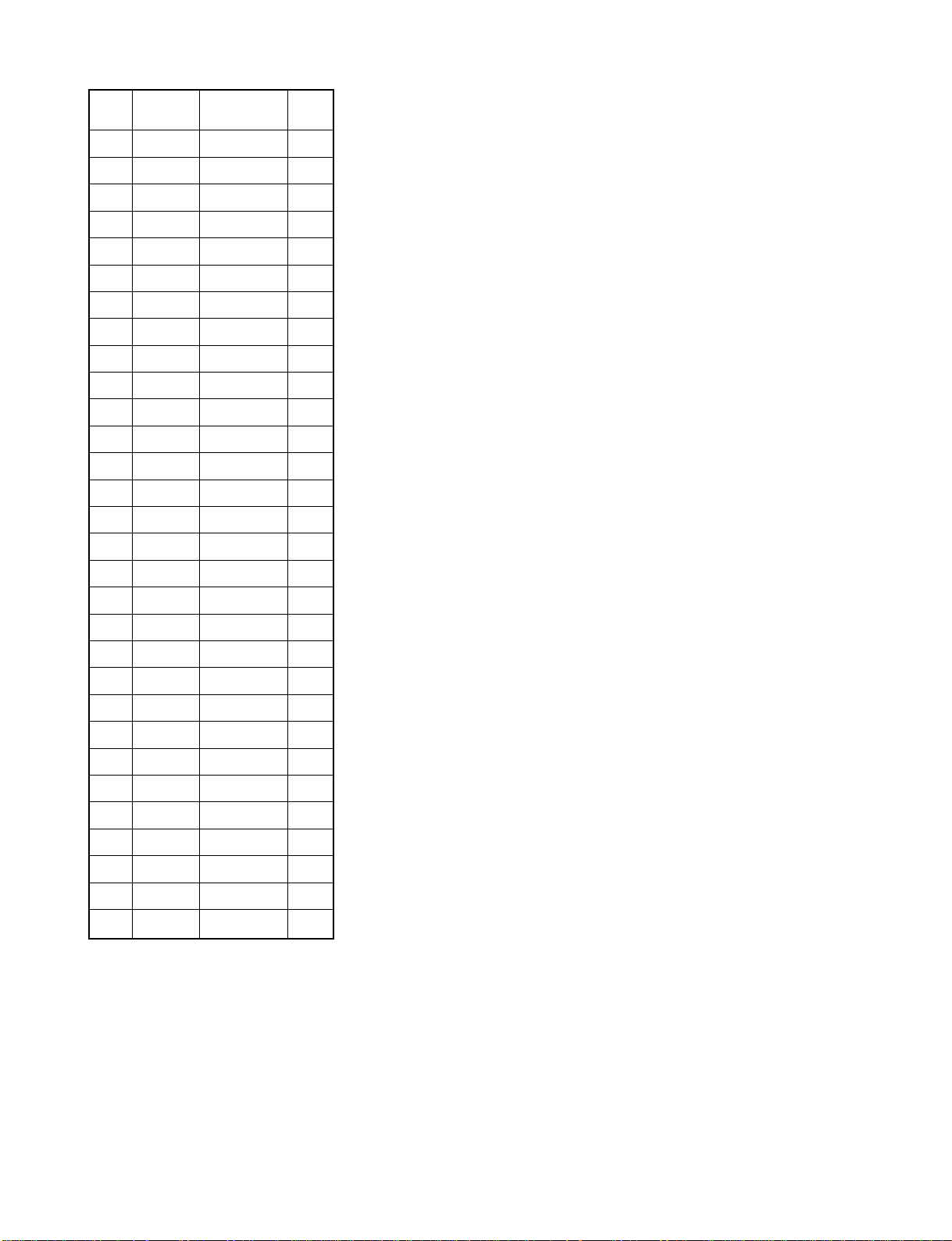

2. SPECIFICATIONS 37 KEYS

Table 1-1

Chassis

Model

CRT

CRT Source

Remote H/U

RMT keys

GENER

PIP

V-Chip

Dolby Surr

Surround

SAP

Cyclone

SBS

SOUND

Audio(W)

Woofer

Rear

Comb-Filter

DOF

Scan-Modul

VCC

Black-Expan

Color-D, E

Pic-Prefer

Color-Temp

PICTURE

Flesh-Tone

Nois-Reduce

Wide Modes

Progressive

Rori-Resolve

Fav-Channel

Ch-label

3-Language

Clock

Ch-Lock/Off

C. Caption

EDS

New-OSD

OTHERS

Multi-Conv

D/A Switch

D/W POP

Multi-Window

S/Sight

S-video In

AV-In/Out

Gold Plated(E2)

Color Differ

Front-Term

A(Var)-OUT

AC-3 A.OUT

2RF-Ter m

SPK-Term

TERMINAL

PIP Audio

C-Ch-Input

E / Jack

S /S-Jack

RGB (F/R)

IR-B & 750

Adapter

Rod-Antenna

SPK-Box

ACCE

EZ RMT

Protective

Cabinet

TP61G90

7

Hitachi

Intell

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

3D-Y/C

·

·

·

·

·

·

·

·

—

¾

·

560DI

·

·

·

·

·

·

¾

·

¾

·

¾

¾

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

·

TP61F80

TP61G60

7

Hitachi

UnIB/L

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

2LDIG

·

·

·

·

·

·

·

·

·

¾

¾

800

·

·

·

·

·

·

·

·

¾

·

¾

¾

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

OPTION

TP61F80

TP55G90

7

TSB

Intell

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

2LDIG

·

·

·

·

·

·

·

·

·

¾

¾

800

·

·

·

·

·

·

·

·

¾

·

¾

¾

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

·

TP55F80

TP55G65

7

Hitachi

UnIB/L

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

2LDIG

·

·

·

·

·

·

·

·

·

¾

¾

800

·

·

·

·

·

·

·

·

¾

·

¾

¾

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

OPTION

TP55F80

C - Chassis

TP55G60

7

TSB

UnIB/L

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

2LDIG

·

·

·

·

·

·

·

·

·

¾

¾

800

·

·

·

·

·

·

·

·

¾

·

¾

¾

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

OPTION

TP55F80

TP71G90

7

Hitachi

Intell

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

3D-Y/C

·

·

·

·

·

·

·

·

—

¾

·

560DI

·

·

·

·

·

·

¾

·

¾

·

¾

¾

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

·

NEW

TW65G80

7

Hitachi

Intell

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

3D-Y/C

·

·

·

·

·

·

·

·

—

·

·

560DI

·

·

·

·

·

·

¾

·

¾

·

·

·

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

*

¾

·

NEW

TP50G90

7

Hitachi

Intell

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

2LDIG

¾

·

·

·

·

·

·

·

·

¾

¾

800

·

·

·

·

·

·

·

·

¾

·

¾

¾

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

·

TP50F60

TP50G60

7

Hitachi

UnIB/L

37key

2-TN

¾

¾

·

·

¾

·

28W

¾

¾

2LDIG

¾

·

·

·

·

·

·

·

·

¾

¾

800

·

·

·

·

·

·

·

·

¾

·

¾

¾

¾

1+1

1+2/1

·

·

·

·

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

OPTION

TP50F60

TP50G50

7

Hitachi

UnIv

38key

1-TN

¾

¾

¾

·

¾

·

28W

¾

¾

2LDIG

¾

¾

·

·

·

·

·

·

·

¾

¾

800

·

·

·

·

·

·

·

¾

¾

¾

¾

¾

¾

1

2/1

¾

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

OPTION

TP50F50

TP48G10

7

Hitachi

UnIv

38key

1-TN

¾

¾

¾

·

¾

·

28W

¾

¾

2LDIG

¾

¾

·

·

·

·

·

·

·

¾

¾

800

·

·

·

·

·

·

·

¾

¾

¾

¾

¾

¾

1

2/1

¾

¾

¾

·

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

OPTION

TP48F50

1-3

Page 8

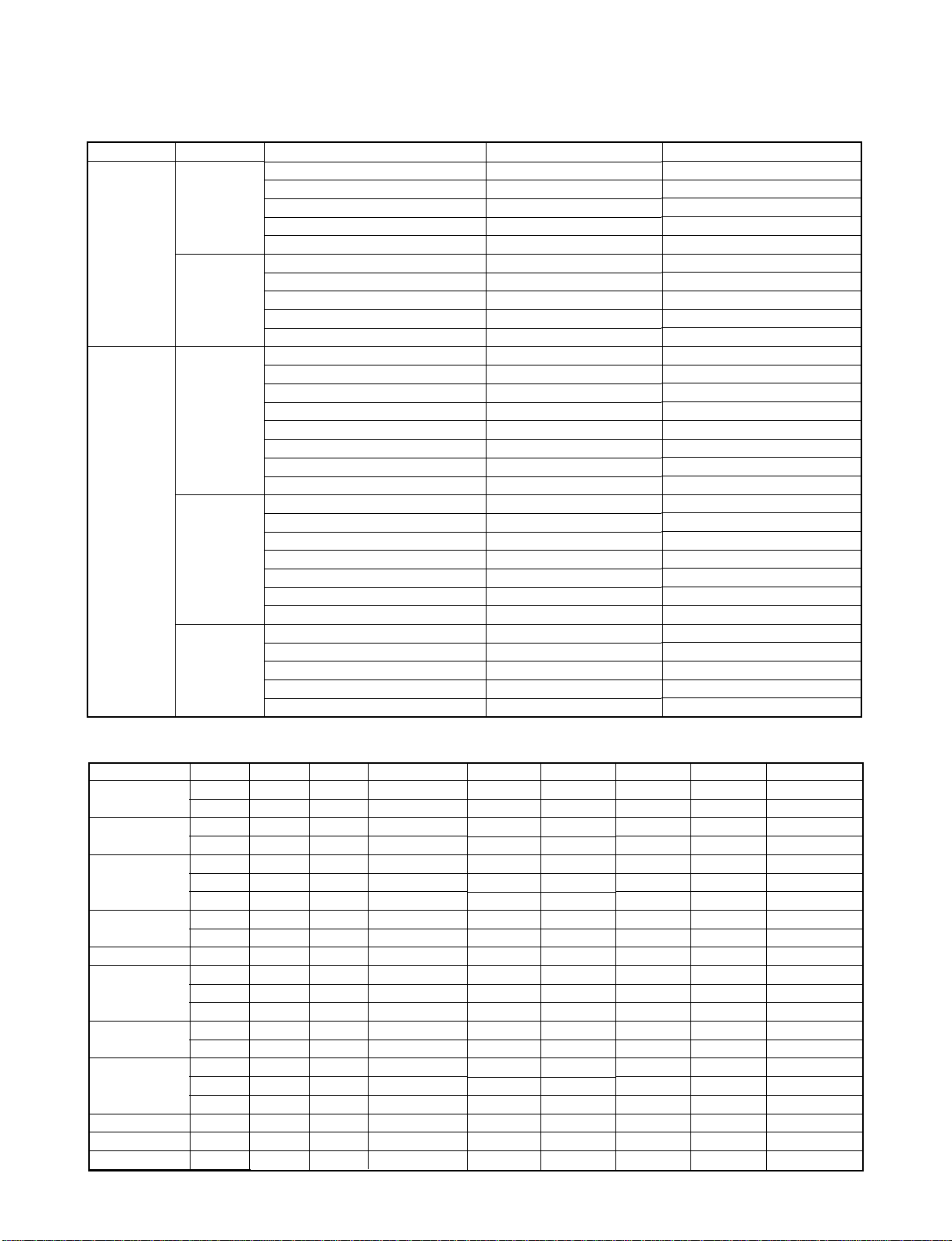

3. TP71G90 SERIES DIFFERENCES

Table 1-2

SIGNAL

DEF

WAC

WAC POWER

D.F.&S.CRRE

V-SHIFT

ABL

WAC-UNIT

L518, L519, L520

GJ21. GJ22. GJ23

GJ28

PW01A. PW02A

QQ03. QQ03A. QQ03B

CQ05. CQ06

RQ03

QA01

QA02(MEMORY)

SR41 (RELAY)

C411

C491

C493

Q490

Q491

R498

D444

C318

Q304

Q305

R321

R322

R323

R324

R218

R220

R219

C220

Q220

TP71G90/TP61G90

DEL.

DEL.

JP

DEL.

DEL.

DEL.

DEL.

DEL.

8700CSN-113

8K

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

DEL.

1/6W10KG

1/6W9.1KG

DEL.

DEL.

DEL.

TW65G80

PB6348

TEM2028K

DEL.

JP

8P-BB

PQ09RF11.H/S

50V10 m16V47m

1/6W4.7K

8700CSN-115

16K

DJ12D1

400V0.027

400V0.15

MO.1

2SC1740S,Q

RN1203

4.7K

1SS133

MO.1

2SA1020Y

RN1203

2R120

2R120

1/6W1K

1/6W5.6K

1/6W12KG

1/6W11KG

1/6W27KG

M0.1

RN1204

SIGNAL

DEF

CONV-OUT

POWER

A/V

CRT-FRONT

OSD

DIGI-CONV

YCS/DUAL

UP-CON

WAC

PB7289

PB7300

PB7290

PB7301

PB7291

PB7396

PB7302

PB7292

PB7303

PB7293

PB7294

PB7571

PB7572

PB7295

PB7333

PB7296

PB7397

PB7304

PB7297

PB7299

PB6348

TP71G90

O

O

O

O

O

O

O

O

O

O

TP61G90

O

O

O

O

O

O

O

O

O

O

O

TW65G80

O

O

O

O

O

O

O

O

O

O

O

Table 1-3

UNIT

23706637

23706652

23706638

23706653

23706639

23706850

23706655

23706640

23706656

23706641

23706642

23781086

23781091

23706648

23706684

23706649

23706851

23706657

23706650

23706651

23705379

1-4

BOARD

23536159

23536169

23536160

23536170

23536161

23536229

23536171

23536162

23536172

23536163

23536164

23526335

23536336

23536165

23536192

23536166

23536230

23536174

23536167

23536168

23535595

BASE

23545340

23545340

23545341

23545341

23545342

23545342

23545342

23545343

23545343

23545344

23545345

23545345

23545296

23545346

23545346

23545347

23545347

23545347

23545348

23545349

23484617B

BASE UNIT

PB7189

PB7342

PB5454ZBW

SPECIFICATION

E2096K459

E2096K469

E2096K460

E2096K470

E2096K461

E2097K003

E2096K471

E2096K462

E2096K472

E2096K463

E2096K464

E2097K041

E2097K042

E2096K465

E2097K001

S2096K466

S2096K004

S2096K473

S2096K467

S2096K468

S9095K112

Page 9

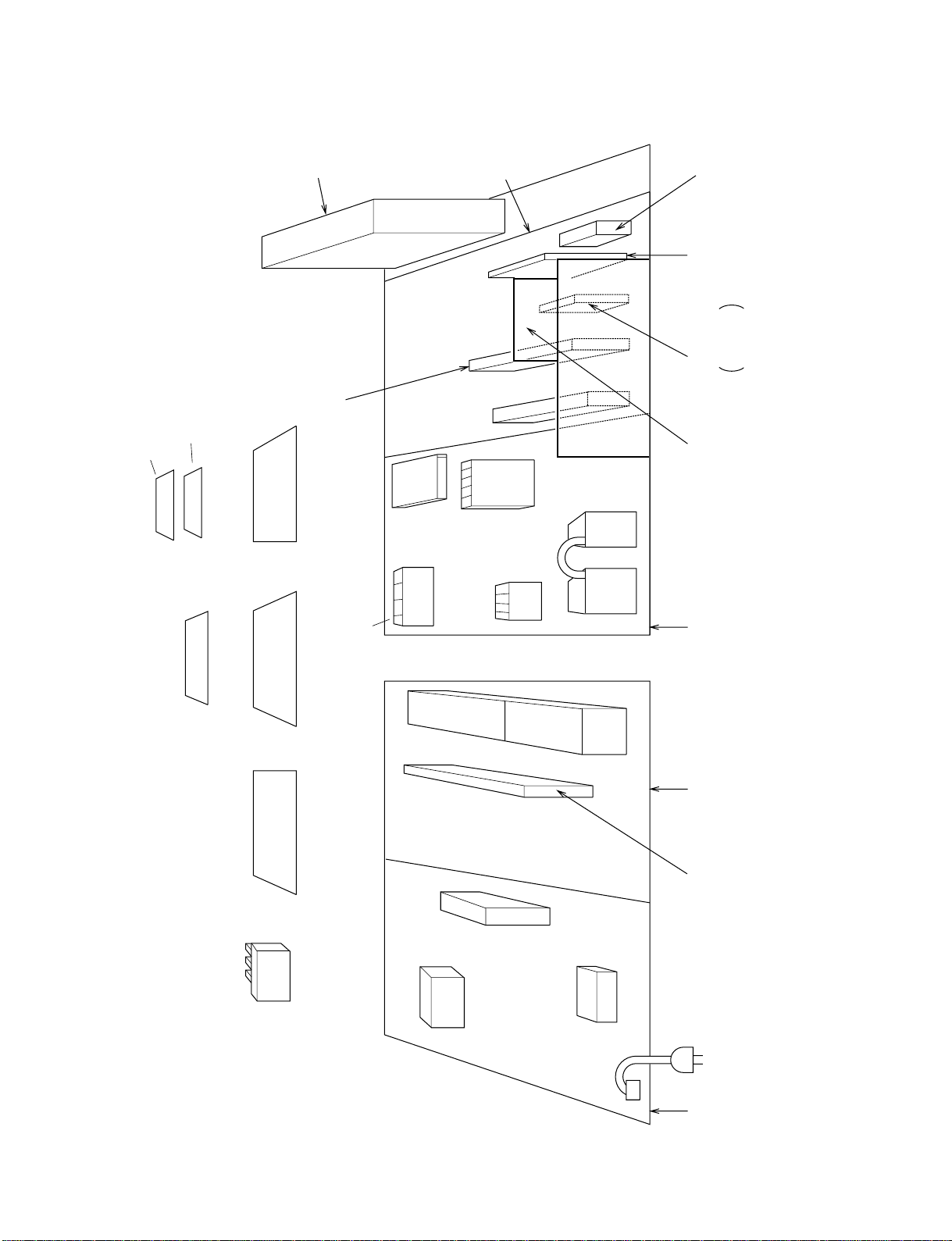

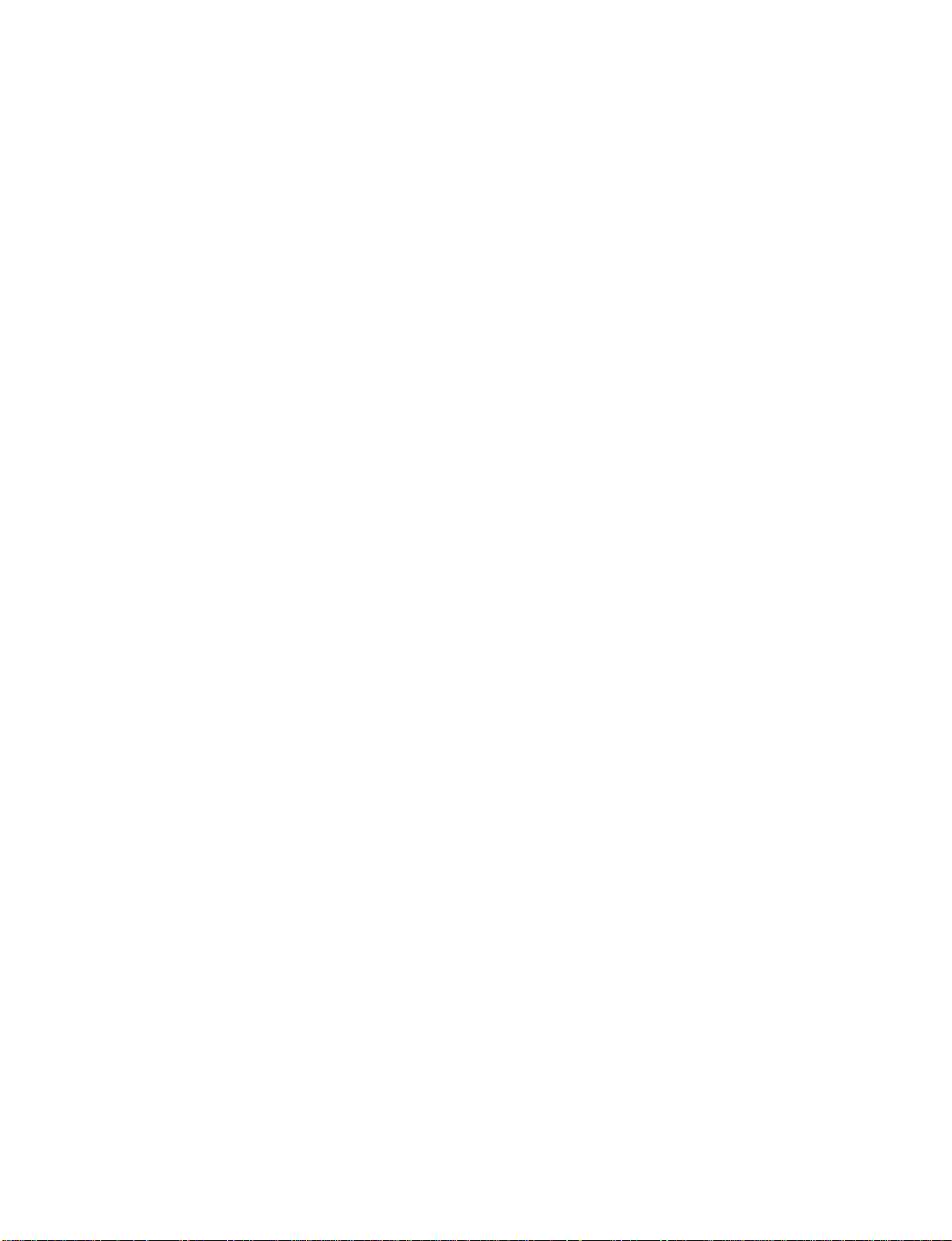

4. TP71G90 (TW65G80) CHASSIS LAYOUT

U901

SIGNAL

FRONT-IN

FRONT-CONT

UX01

UY01

YCS/DUAL

UP - CON

(PIP)

2nd

TUN

(TIF)

UM01

New-OSD

UX02

WAC

ONLY

UV01

A/V

TW65G80

SVM

CRT-D/GCRT-D/B CRT-D/R

DEF-OUT

DPC

POW1

V-

H-

OUT

OUT

U401

DEF

U701

CONV-OUT

UH01

D-CONV

Fig. 1-2

Fo

PAC

1-5

POW2

STANDBY

U801

POWER

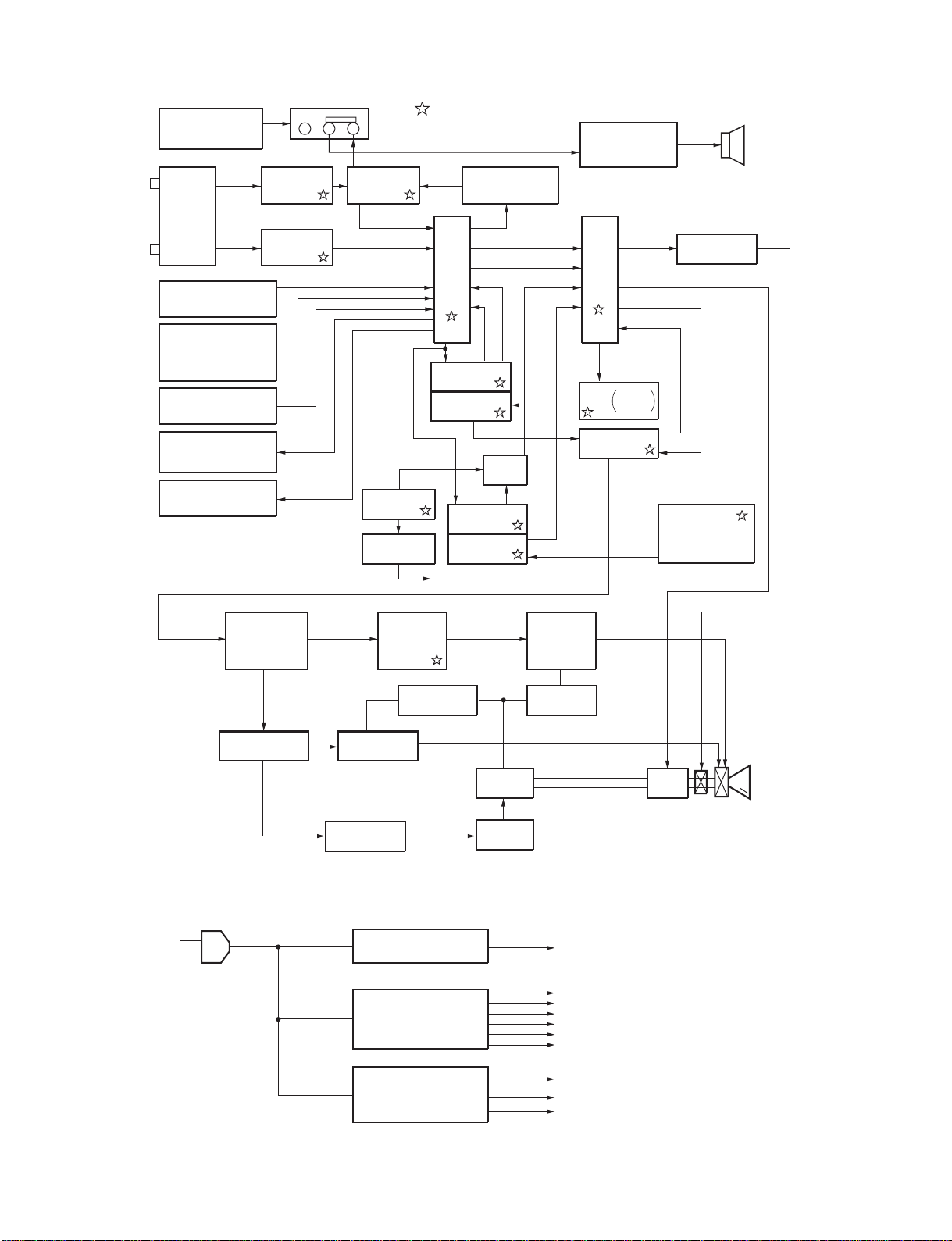

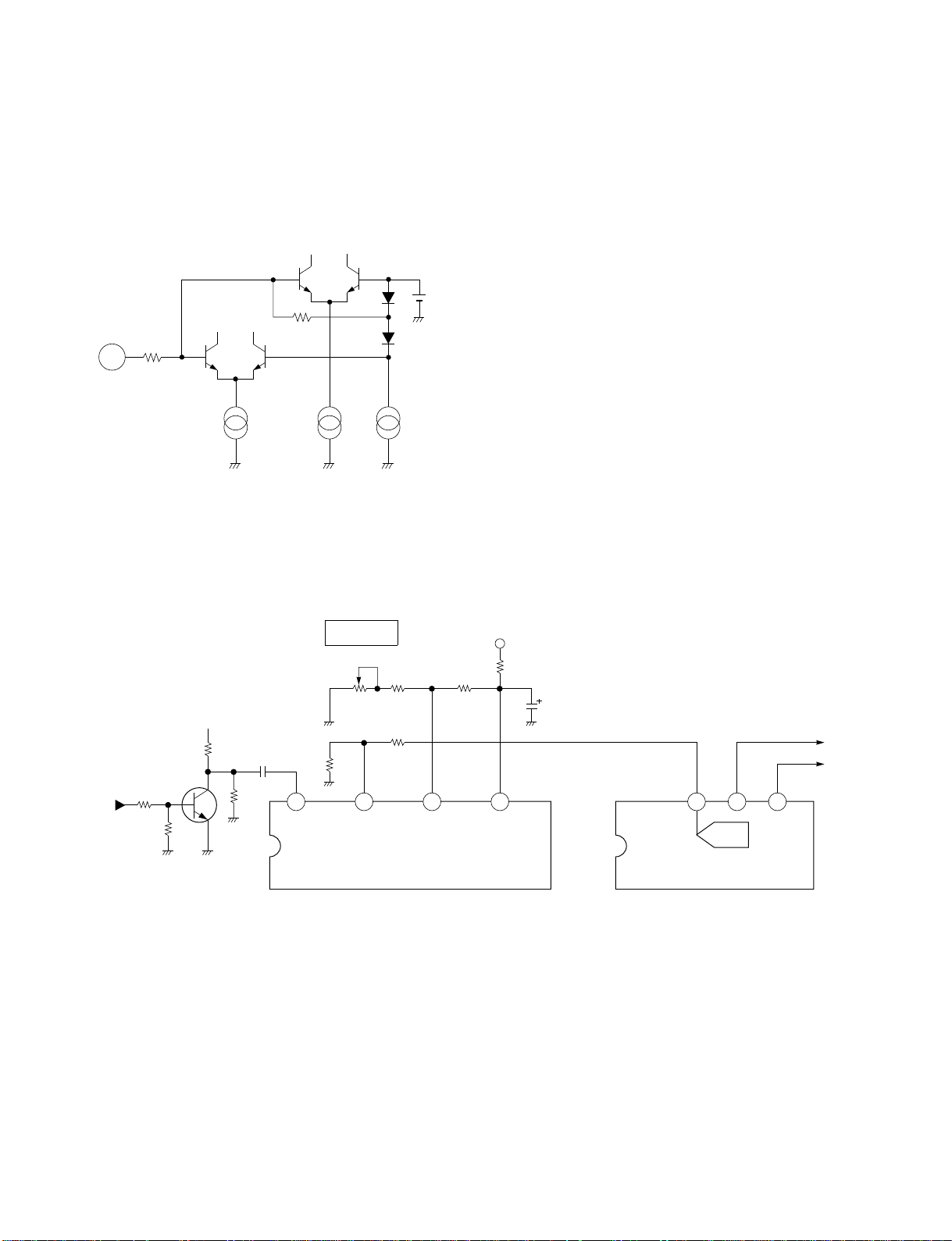

Page 10

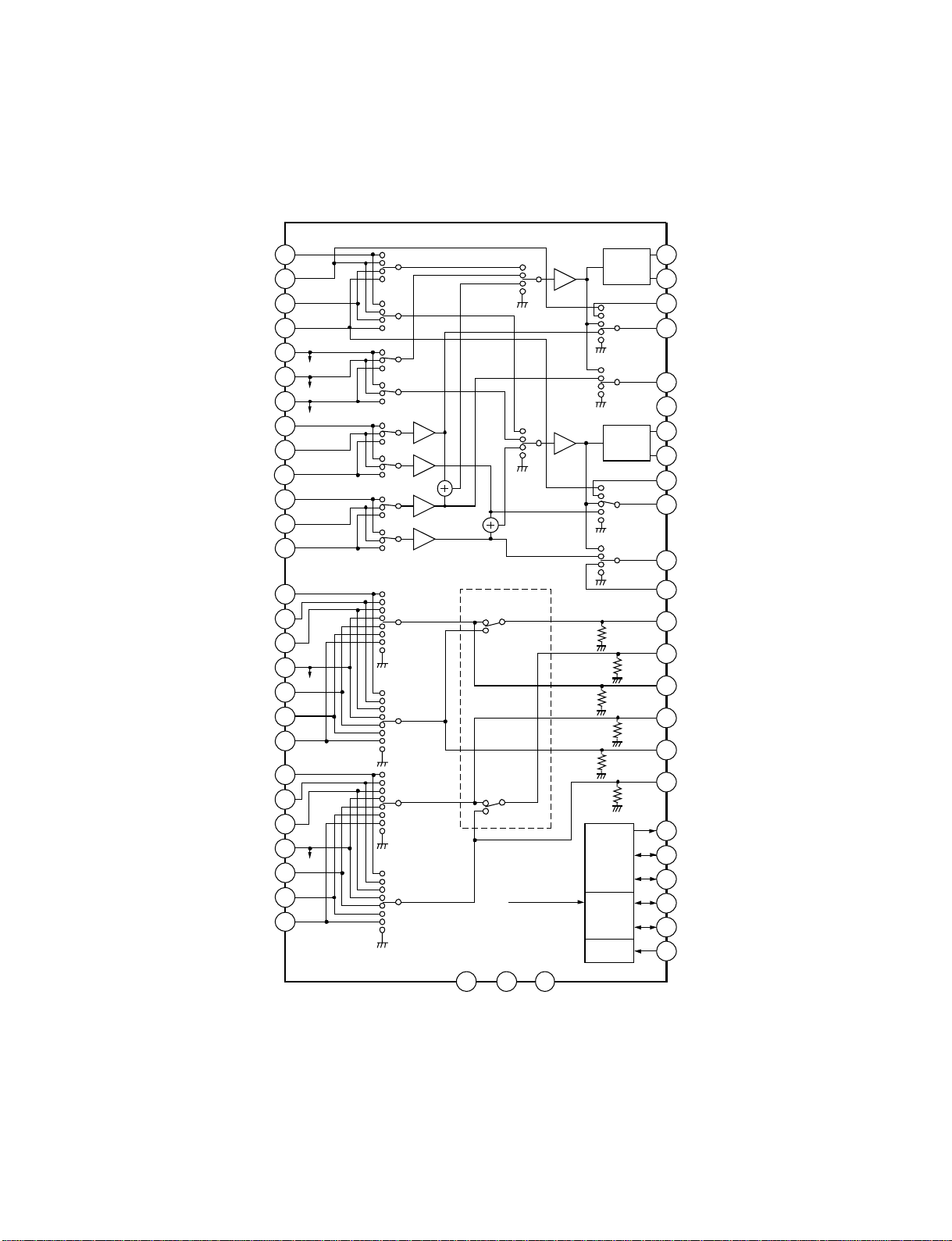

CENTER-IN

ON OFF

2

:I BUS ELEM ENT

SPEAKER

AUDIO AMP

ANT1

OUT

ANT2

VIDEO1 S.V.L.R

V ID E O 2 V .L .R

/D V D C r.C b

VIDEO3 S.V.L.R

MONITO R-OUT

AUDIO VAR I-OUT

2HD, 2VD

TUNER IM A

TIF

DEF IC

PIP-V

TV-V, L, R

D-CONV

CONV-OUT

V . D R IV E

SURROUND IC

SPK-O UT

L/R

AV SW ITCH

VYC

YCS

DUAL

Y. I. Q

SW

C. C. IC

OSD IC

TO DY (SUB YOKE)

MAIN-Y

MAIN-C

RGB

RGB

V. O UT

WAC

2HD.2VD

VCD IC

YIQ

WIDE

ONLY

UP-CON

SVM

RGB

HD, VD

2Y IQ

MICRO

PRO CESSOR

DEF. H. V. DRIVE

A C 120V

H. D. FOCUS

DEF. OUT

FOCUS

PACK

H. V. O UT

FBT

Fig. 1-3 TP71G90 block diagram

POW -STANBY

POW ER1

POW ER2

V.D.FOCUS

SCREEN

FOCUS

CRT-D

5V -1

148V (H -O U T)/120V (S V M )/32V (TU N )

3 5 V (V -O U T )

15V

11V/9V -1/9V -2/9V -3/9V-4(9V-4,W ID E O NLY )

7V-1/5V -3/5V -A /5V -D

7V-2/5V-2/HEATER

35V(A U D IO )

21V(CONV)/5V(D-CONV)

-21V(CO NV)/5V(D -CO NV)

CRT.

Fig. 1-4

1-6

Page 11

SECTION II

AUDIO CIRCUIT

2-1

Page 12

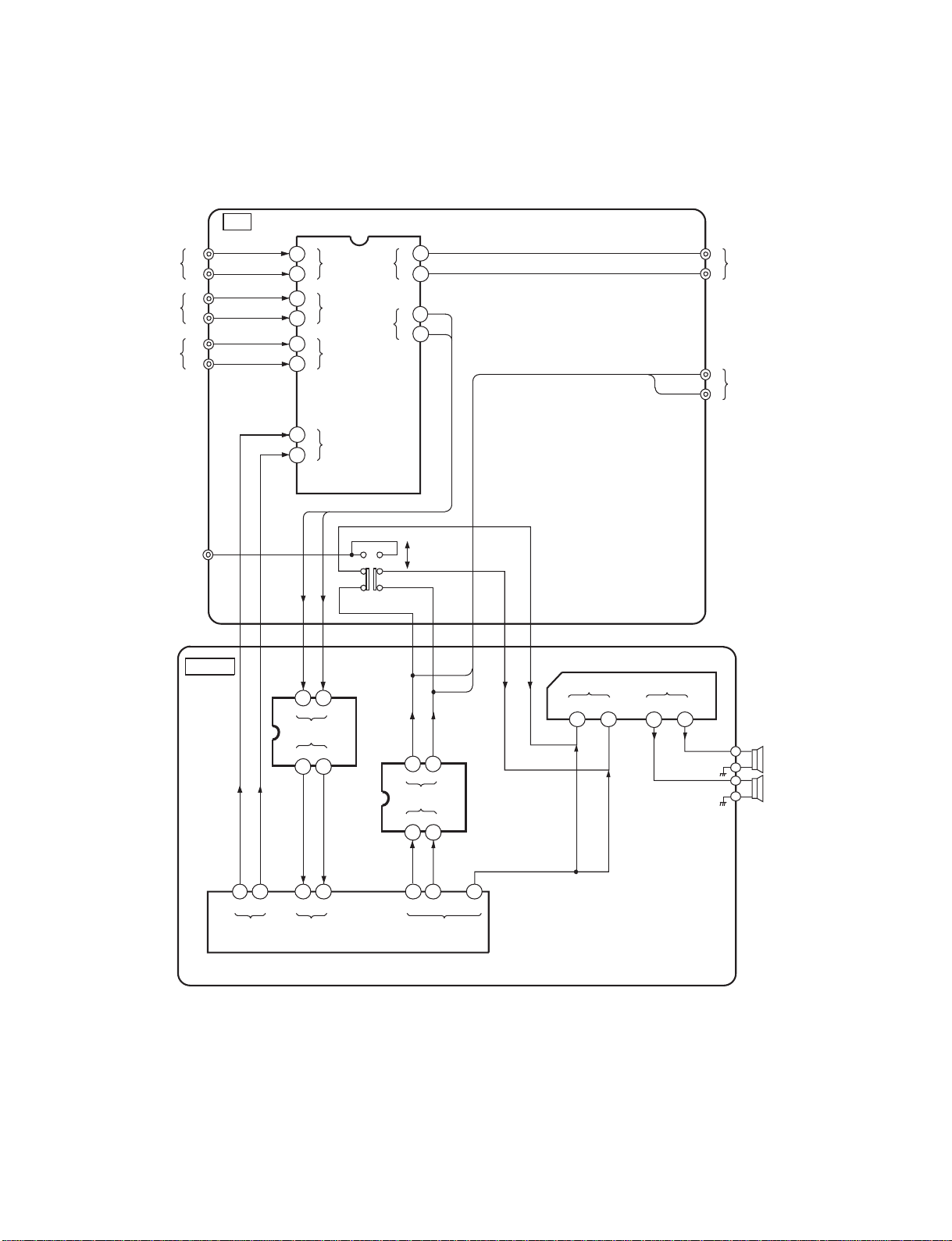

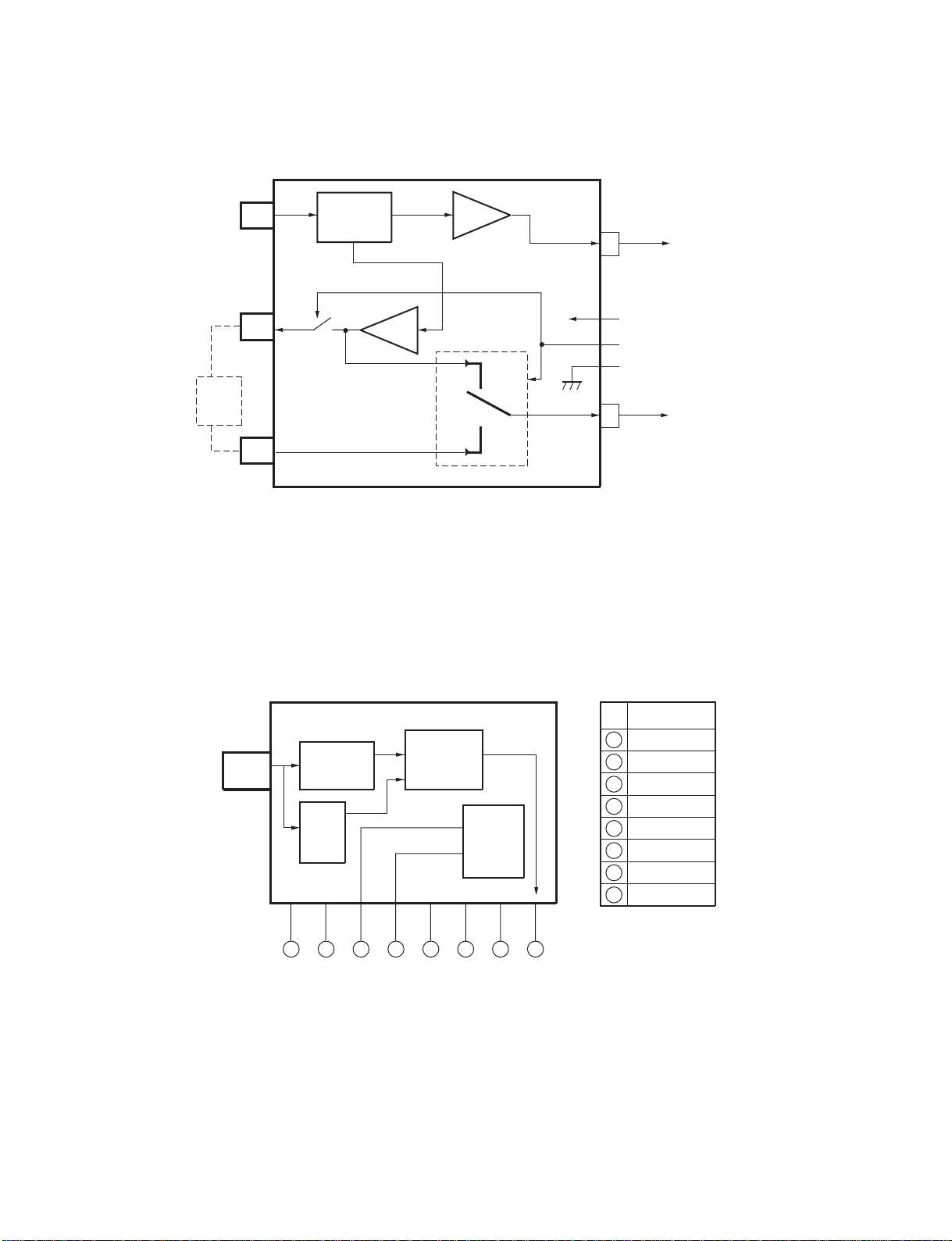

1. GENERAL

The audio signal processing circuit consists of an input

selector IC (QV01 = TA8851CN), a master IMA (H002

= MVUS34S, MVUS34B) modules, a Surround-soundsound IC (QD01 = TA8173AP) and a VARIABLE-AUDIO-AMP (QS101 = M5218AP) and an audio output IC

(Q601 = LA4282). The audio output of TP71G90 is 14W

+14W, which is based on SBS (SUB BASS SYSTEM) as

a basic specification. When the double window feature

is selected, the left-hand screen sound is output.

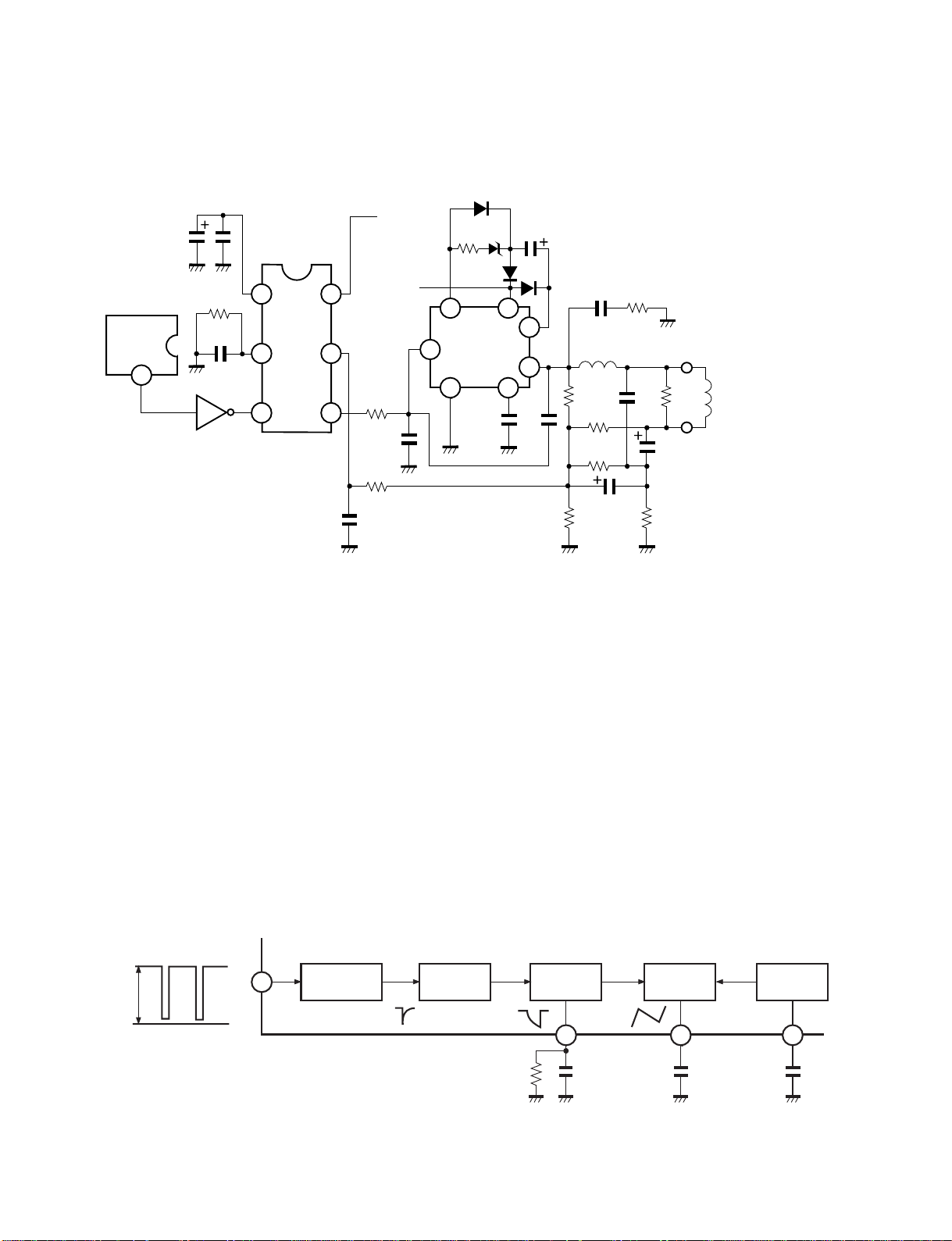

2. FLOW OF SIGNAL

Fig. 2-1 shows a block diagram of the audio circuit of

TP71G90.

• TV detection output

Pins 12 (R-OUT) and 14 (L-OUT) of IMA module

H002.

• A/V selector IC input

Pins 6 (R-IN) and 4 (L-IN) of QV01 (TA8851CN).

This A/V selector IC receives the audio signals from

TV, E1, E2 and E3.

• A/V selector IC output

Pins 39 (R-OUT) and 41 (L-OUT) of QV01.

The signal here is regarded as 1.

• Surround-sound-sound IC input

Pins 16 (R-IN) and 14 (L-IN) of QD01.

• Surround-sound-sound IC output

Pins 9 (R-OUT) and 11 (L-OUT) of QD01.

• IMA module A. PRO input

Pins 16 (R-IN) and 18 (L-IN) of H002.

• IMA module A. PRO output

Pins 26 (R-OUT), 24 (L-OUT) and 22 (W-OUT) of

H002.

• VARIABLE-AUDIO-AMP input

Pins 3 (R-IN) and 5 (L-IN) of QS101.

• VARIABLE-AUDIO-AMP output

Pins 1 (R-OUT) and 7 (L-OUT) of QS101.

• Audio output IC input

Pins 2 (R-IN) and 5 (L-IN) of Q601.

• Audio output IC output

Pins 11 (R-OUT) and 7 (L-OUT) of Q601.

• SPK output

2-2

Page 13

E1

T

E2

E3

R

L

R

L

R

L

A/V

10

8

49

51

22

20

6

4

R

L

R

L

R

L

R

L

QV01

TA 8851C N

MON-out

E1

E2

SPK-out

E3

TV

R

L

R

L

43

45

39

41

R

MONITOR

out

L

VARIABLE

R

AUDIO OUTPU

L

TER M IN A L

CENTER

AUDIO

IN

SIG NAL

QD01

TA 8173AP

16

14

R L

In

Out

R L

9 11

14

12

R L

TV out

16 18

R L

In

H 002 M VUS34S O R M VU S34B

ON

OFF

1

7

R L

Out

In

R L

3

5

26

24

R

L

Out

Q S 101

M 5218AP

22

W

Q 601 LA4282

In

R L

2

5

Out

R L

7

11

SPK

L

R

Fig. 2-1 Audio circuit block diagram

2-3

Page 14

3. DESCRIPTION OF CIRCUITS

3-2. A. PRO Circuit

3-1. IMA Module (MVUS34S/MVUS34B)

3-1-1. MTS Circuit

This has the following functions.

• Discriminating STEREO and SAP

• MATRIX output selection for STEREO and SAP

Table 2-1 shows the output MATRIX in each broadcast

mode.

Table 2-1 Multi-channel MATRIX

R

R

R

Multi-channel

display

Stereo

SAP

O

O

O

Feed

MONO

STEREO

Mode

selection

STEREO

SAP

MONO

STEREO

SAP

MONO

Speaker output

L

MONO

MONO

MONO

MONO

MONO

MONO

L

L

L + R

L + R

The self-made A. PRO TA1217AN is used. This has the

following functions.

• VOLUME CONTROL

• TONE CONTROL (BASS , TREBLE, BALANCE)

• SBS LEVEL CONTROL

• SBS ON/OFF

All these functions are controlled by I2C BUS sent from

a microcomputer.

Fig. 2-2 shows the block diagram of A. PRO.

3-3. A/V Selector Circuit

(1) Input source selected with QV01

Signals from TV, E1, E2 and E3

Fig. 2-3 shows the internal block diagram of QV01

(TA8851CN). Select always the master (left-hand screen)

signal for the SPK-OUT (pins 39 and 41) signal.

MONO +

SAP

STEREO

+ SAP

STEREO

SAP

MONO

STEREO

SAP

MONO

Address

SW

36

35 34

MONO

SAP

MONO

SAP

L + R

L in

MONO

SAP

MONO

L

R

SAP

L + R

32 31 30 29

33

TONE

CONTROL

LPF LEVEL

O

O

O

O

O

O

sre

O

O

O

R in Vcc

28

VOLUME BALANCE

LEVEL

27

R out L out

26 25

vol bass

24

23 22 21

D/A

CONV

I/O

bal

SCL SDA

I C

2

20

OLev

19

1 2

C in W in

3

4

5 6 7

9

WLev

8

Rip

fil

10 11

W out

GND

12 13

P1 P2

Fig. 2-2 TA1217AN block diagram

2-4

14

15 16 17 18

P3 P4

P5 P6

C out

Page 15

VT1

VB1/Y121

VT2

VB2/Y122

VE1

VE2

VE3

YE1

YE2

YE3

CE1

CE2

CE3

TV1 R

E2 R

E1 R

E3 R

TV1 L

E2 L

E1 L

E3 L

5

50

2

53

7

13

19

9

15

21

11

17

23

6

49

3

52

10

16

22

4

51

1

54

8

14

20

DAC

DAC

DAC

DAC

DAC

ST1

ST2

SE1

SE2

SY1

SY2

SC1

SC2

SR1

SR2

SL1

SL2

6dB

AMP

6dB

AMP

6dB

AMP

6dB

AMP

Speaker audio SW

SV1

SV2

PIP output SW

SRT

PIP output

SW

SLT

RB2, LB2,

VE1, VE2, VE3

6dB

AMP

6dB

AMP

Clamp

SOY1

SOC1

Clamp

SOY2

SOC2

I/O

2

I C

DAC

Mute

VO1

46

1

2

fcl1

47

YI11

48

YO1

44

CO1

42

CI1

40

VO2

36

fcl2

37

YI12

38

YO2

34

CO2

32

CI2

30

SPK-out R

39

SPK-out L

41

MON-out R

43

MON-out L

45

33

35

O3

31

I/O1

28

I/O2

29

SDA

26

SCL

27

Mute

25

12

18

Vcc GND1 GND2

24

Fig. 2-3 QV01 (TA8851CN) block dia gram

2-5

Page 16

3-4. Surround-sound Circuit

Surround-sound processing is performed by TA8173AP.

Fig. 2-4 shows the internal block diagram of TA8173AP.

LF1 PS1 PS2 PS3 PS4 LF2 VCC

3

2

5

6

4

7

8

LPF 2 (R-L)

R IN

16

BUF

L IN

14

BUF

REF

15

REF

Fig. 2-4 Surround process IC TA8173AP block diagram

3-5. Audio Output Circuit

This uses LA4282, and permits output of 14W + 14W.

Fig. 2-5 shows the block diagram.

PHASE

SHIFT

t 2 (R-L)

+

R

-

+

L

1

GND

LPF

+

LPF

LPF

N D

BUF

BUF

REF

D/N SW

13

R OUT=R+

9

R LPF

10

L OUT=L - t 2 (R-L)

11

12

L LPF

t 2 (R-L)

1

2

Input (1)

Feed back (1)

30k

300

ch1

+

Ripple

Filter

3 4

Ripple filter

Input side GND

+

5

Input (2)

ch2

30k

300

6

7

Output (2)

Feed back (2)

Muting

Ckt.

8

External mute

Fig. 2-5 LA4282 block diagram

Thermal

shut-down

Over-voltage

Vcc

9

Output side GND (2)

11

10

Output (1)

Power supply

12

Output side GND (1)

2-6

Page 17

Does sound go on

in video 1 mode?

NG

OK

Does VHF/UHF sound

go on?

NG

Go to Fig. 2-8.

Check the output

waveform at QV01,

pins 39 and 40.

OK

Check the output

waveform at QD01,

pins 9 and 11.

OK

NG

NG

Check the voltage of 9V

DC at QV01, pin 18.

OK

Check the input waveform

at QV01, pins 8 and 10.

OK

Replace QV01.

Check the voltage of 9V

DC at QD01, pin 8.

OK

Check the input waveform

at QD01, pins 14 and 16.

OK

Replace QD01.

NG

NG

NG

NG

Check the power supply circuit.

Check the QV01 peripheral

circuit.

Check the power supply circuit.

Check the QD01 peripheral

circuit.

Check the output

waveform at H002,

pins 24 and 26.

OK

Check the output

waveform at QS101

pins 1 and 7.

NG

Check the voltage of 9V

DC at H002, pin 27.

OK

Check the input waveform

at H002, pins 16 and 18.

OK

Replace H002.

Fig. 2-6

2-7

NG

NG

Check the power supply circuit.

Check the H002 peripheral

circuit.

Page 18

Check the output

waveformat at H002,

pins 24 and 26.

OK

Check the output

waveform at QS101,

pins 1 and 7.

OK

Check the output

waveform at Q601,

pins 7 and 11.

OK

Check C609, C610

W661 and W662.

NG

Check the voltage of

9V DC at QS101, pins 8.

OK

Check the input waveform

at QS101, pins 3 and 5.

OK

Replace QS101.

Check the voltage of 34V

DC at Q601, pin 10.

OK

Check the input waveform

at Q601, pins 2 and 5.

OK

Replace Q601.

NG

NG

NG

NG

Check the power supply circuit.

Check the QS101 peripheral

circuit.

Check the power supply circuit.

Check the Q601

peripheral circuit.

Does VHF/UHF sound go on?

NG

Check the output

waveform at H002,

pins 12 and 14.

NG

Fig. 2-7

Check the voltege of

9V DC at H002, pin 4.

OK

Replace H002.

Fig. 2-8

2-8

NG

Check the power supply circuit.

Page 19

SECTION III

TUNER/IMA CIRCUIT

3-1

Page 20

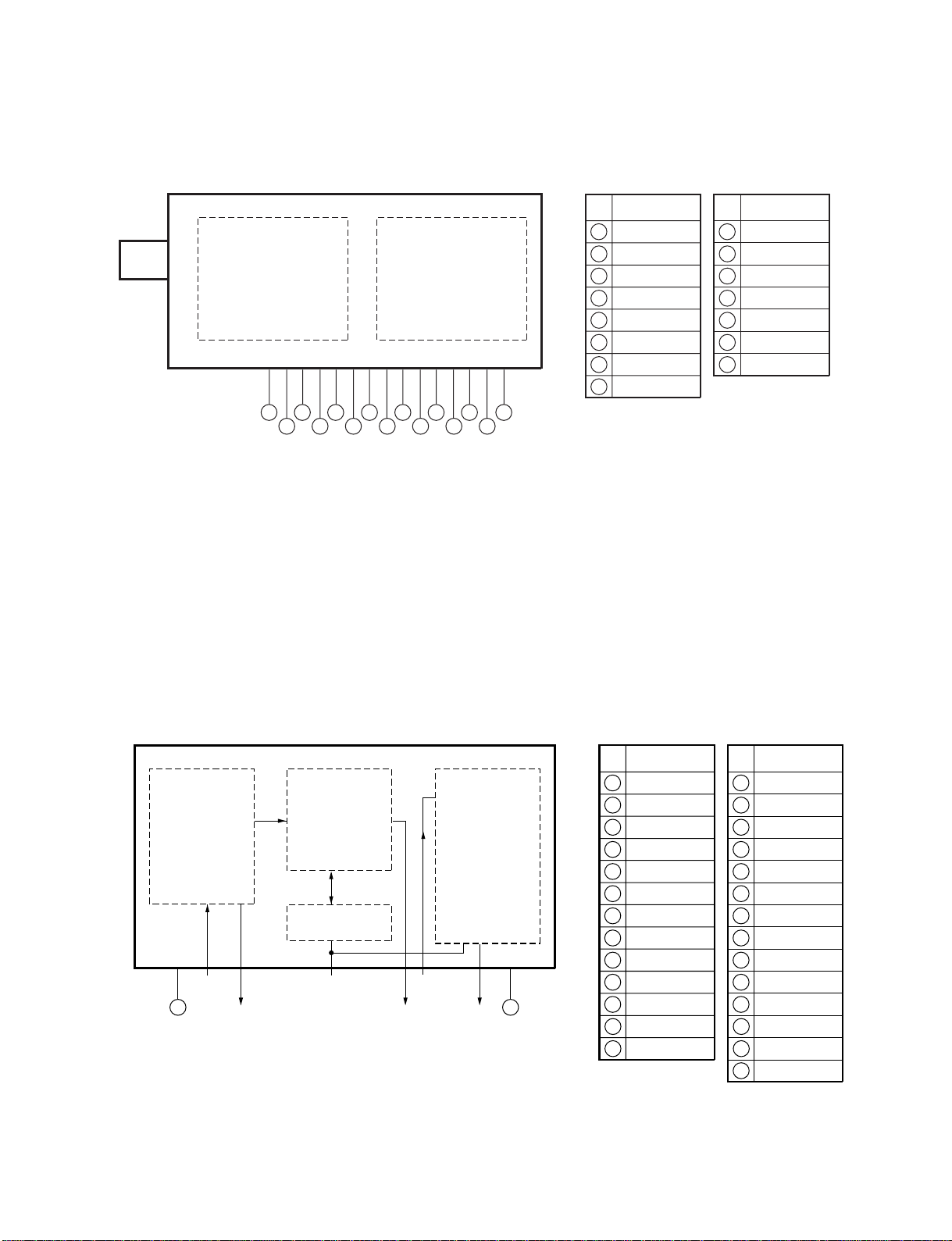

1. CIRCUIT BLOCK

1-1. Outline

A TV signal input to ANT1 is provided to HY01 (TIF for

PIP) and H001 (main tuner) through a splitter H003(RFSW) is a new RF-SWITCH with an isolation amplifir added

to the divider output to improve local interference between

the main and the sub tuner.

H003 controls, signal selection for ANT1 or ANT2 to be

supplied to H001 (main tuner) according to the IMA MODULE-DAC-OUT 2.

H001 is of an international standardtype tuner and supplies the signals (Video: 45.75 MHz Audio: 41.25 MHz)

in the IF (Intermediate-Frequency) band to the IMA.

ANT1

OUT

H003

RF

SW

HY01

TIF for PIP

EL924L2

The TV signal input to ANT1 is always provided to HY01

(TIF for PIP) as the splitter output and demodulated to a

video signal for PIP.

H002 (IMA) is module containing the IF circuit consisting of a split carrier PLL synchronizing detection system

and multiplex sound decorder and audio processer.

But in the MPX section, former HIC type is replaced by a

module consisting of MPX-IC, I2C bus control and sound

multiplex data exclusive memory IC, thereby affering a

non alignment in the replacement service.

AFT2

PIP VIDEO

VIDEO L/R

H002

ANT2

H001

SW Tr

TUNER

ELA12L

Q151/Q152

Fig. 3-1 Block diagram

IMA (IF/MPX/A,PRO)

MVUS34B

DAC

OUT2

AFT1

3-2

Page 21

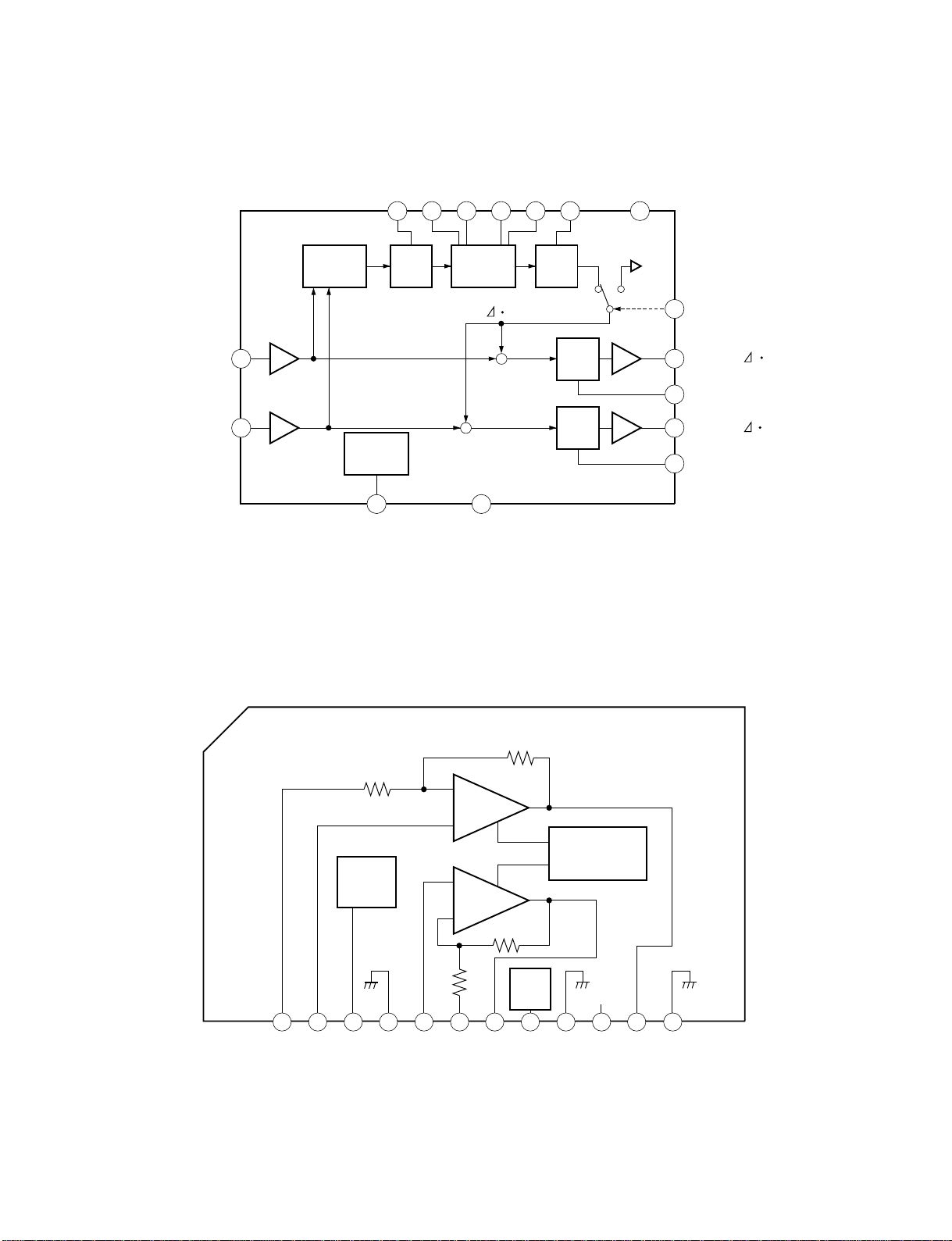

1-2. RF SW

C able

Box

ANT1

OUT

ANT2

DIO DE

SW

H003 Model : RSU134 (SN : 23344412)

D ivider

AM P

RELAY

SW

AM P

Fig. 3-2 Block diagram

PIP TIF

9V

S W C o n tro l(A N T 1 : O P E N )

G N D (A N T 2 : 9 V )

TUNER

1-3. TUNER

H001 Model : ELA12L (SN : 23321223)

ANT in

Pin

No.

UHF

AM P

VHF

AM P

2

1

3

MIX

OSC

45

PLL

6

7

8

1

2

3

4

5

6

7

8

Nam e

AGC

ADD RESS

CLOCK

DATA

9V

5V

32V

IF

Fig. 3-3 Block diagram

Pin2 (ADDRESS) in the main tuner is open and controlled by microcomputer

RECEPTION BAND AREA VHF LOW : CH~2B

VHF HIGH : CHC~LL

UHF : CHMM~69

3-3

Page 22

1-4. TIF for PIP

TIF for PIP with no-sound is newly developed.

HY01 Model : EL924L2 (SN : 23321263)

Pin

No.

ANT in

TUNER

1

2

IF

In te r c a rrie r P L L

3

5

4

6

7

9

8

10

13

11

12

15

14

1

2

3

4

5

6

7

8

Fig. 3-4

The Pin6 (ADDRESS) in the PIP TIF is GND, and controlled by the microcomputer.

RECEPTION BAND AREA VHF LOW : CH2~B

VHF HIGH : CHC~LL

UHF : CHMM~69

Nam e

NC

32V

CLOCK

DATA

NC

ADDRESS

5V

RF AGC

Pin

No.

9

10

11

12

13

14

15

Nam e

9V

NC

GND

AFT

NC

GND

VIDEO

1-5. IMA

H002 Model : MVUS34B (SN : 23148280)

Split carrier

PLL

IF

IF in BUS R/Lin

1

VIDEO TV R/L L/R/Wout

Multiplex

sound

decord

Memory

Audio

procceser

Fig. 3-5

27

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

Name

GND

IF in

NC

9V

RF AGC

AFC

VIDEO

IF AGC

MPX out

SAP VCO

ADDRESS

TV R

DAC out 1

Pin

No.

14

15

16

17

18

19

20

21

22

23

24

25

26

27

Name

TV L

DAC out 2

Rin

Cin

Lin

GND

CLOCK

DATA

W out

C out

L out

GND

R out

9V

3-4

Page 23

The Exclusive IC memory that memories adjustment values for I2C bus control sound multiplex IC is built in module, and this eliminates readjustment of the sound multiplex recontrol in the module-replacement.

1-6. CATV System AUTO MODE Decision

In the initial state (shipping and AC ON), the channel selection is carried out in the STD mode and the pull in

operation is carried out by the sync and AFT signals. By

this time, offset value from STD mode is memorized.

Two memories, memory 1 and memory 2, are required for

the channels 5, 6 and the channels other than the channels

5, 6. A cable mode is decided by this offset values memorized and the start frequency of next channel selection is

determined. The offset value is updated each time. The

criterion of the decision and the start frequency are shown

in tables 3-1 and 3-2.

Table 3-1 Channels other than the channels 5, 6c h

Offset values

+0.75 ~ +2.5 MHz

-0.75 ~ +0.75 MHz

-2.25 ~ -0.75 MHz

Table 3-2 Channels 5, 6

Offset values

+1.375 ~ +2.5 MHz

+0.5 ~ +1.375 MHz

-0.5 ~ +0.5 MHz

-2.25 ~ -0.5 MHz

Decision

NEW

STD/IRC

HRC

Decision

5, 6ch IRC

5, 6ch HRC

5, 6ch STD

5, 6ch OTHER

Start frequency

fo +1.75 MHz

fo

fo -1.25 MHz

Start Frequency

fo +2.00 MHz

fo +0.75 MHz

fo

fo -1.00 MHz

3-5

Page 24

2. IF/RF CIRCUIT TROUBLESHOOTING

2-1. No Picture of VHF/UHF (Main Screen)

No picture of VHF/UHF

250mV

(p-p)

H period

Check waveform

at pin 7 of H002.

AC 1.0V(p-p)

NG

Check power voltage at pin 4

of H002 is 9V.

OK

Check waveform

at pin 2 of H002.

NG

OK

NG

OK

Check waveform at

pin(EP) of A/V connecter.

AC 1.0V(p-p)

NG

Investigate power circuit.

Replace H002.

OK

Check A/V board.

Check pattern from

pin 7 of H002 to pin(EP.)

Check waveform at pins SDA

SCL(BUS line) of H001.

OK

Check power voltage of H001.

9V

5V

32V

OK

Replace H001

NG

NG

Investingate Bus line.

Investingate power circuit.

Fig. 3-6

3-6

Page 25

2-2. No Picture of VHF/UHF (PIP Screen)

No picture of VHF/UHF

Check waveform

at pin 15 of HY01.

AC 1.0V(p-p)

NG

Check waveform at pins 3

and 4 (Bus line) of HY01.

OK

Check power voltage of HY01.

9V

5V

32V

OK

Replace HY01.

OK

NG

NG

Check waveform at

pin(EL) of A/V connecter.

AC 1.0V(p-p)

Investigate Bus line.

Investingate power circuit.

Fig. 3-7

OK

NG

Check A/V board.

Check pattern from

pin 15 of HY01 to pin(EL.)

3-7

Page 26

This page is not printed.

3-8

Page 27

SECTION IV

CHANNEL SELECTION CIRCUIT

4-1

Page 28

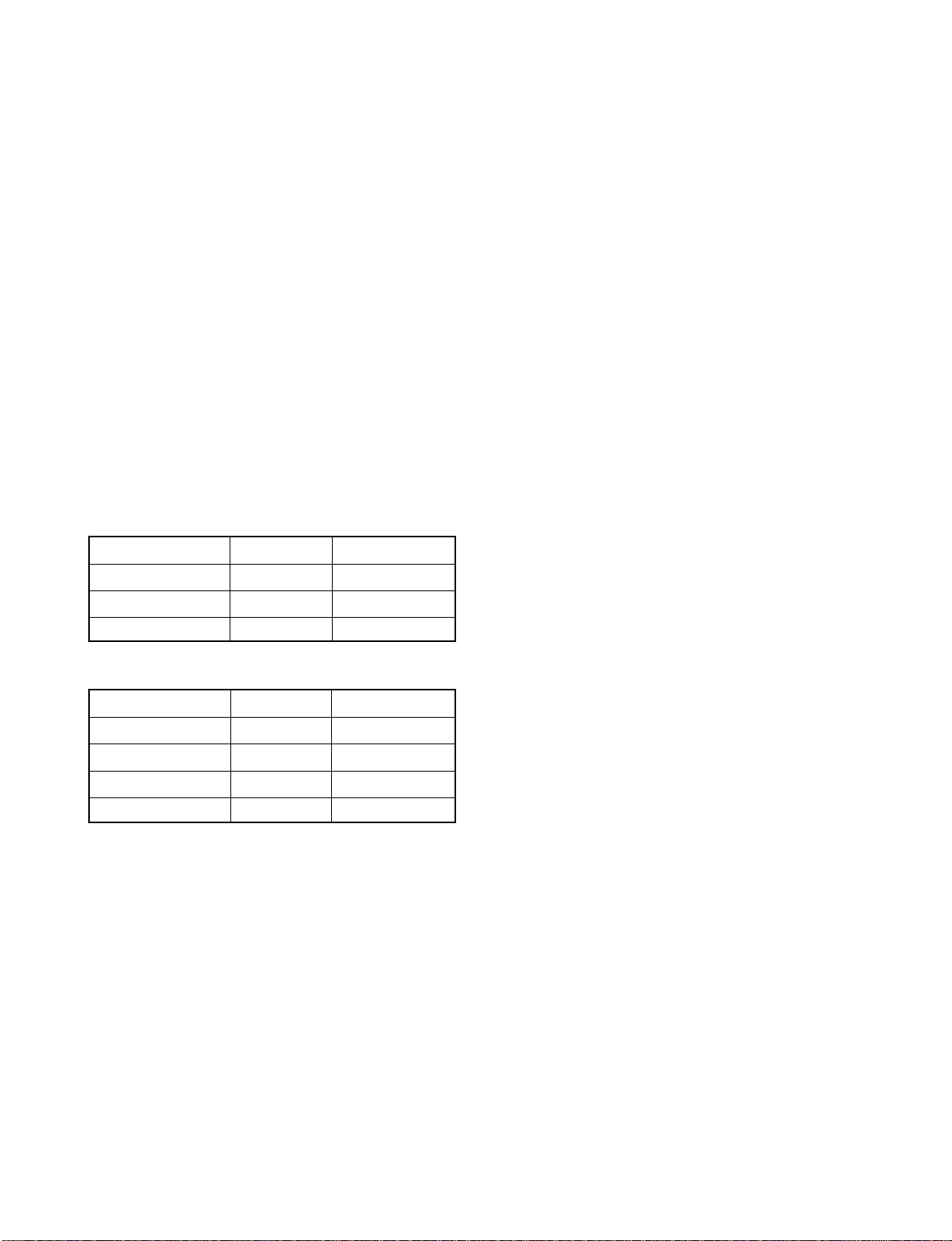

1. OUTLINE OF CHANNEL

SELECTION CIRCUIT SYSTEM

The channel selection circuit in the N7SS chassis employs

a bus system which performs a central control by connecting a channel selection microcomputer to a control

IC in each circuit block through control lines called a bus.

In the bus system which controls each IC, the I2C bus

system (two line bus system) developed by Philips Co.

Ltd. in the Netherlands has been employed.

The ICs controlled by the I2C bus system are : IC for audio signal processing (QN06), IC for V/C/D signal processing (Q501), IC for A/V switching (QV01), IC for non

volatile memory (QA02), Main and sub U/V tuners (H001,

HY01), IC for deflection distortion correction (Q302), IC

for PIP signal processing (QY04), IC for closed caption

control, A.PRO, I/O expander, JFORC, digital convergence, 3D YCS, SLC, V/C/D for PIP.

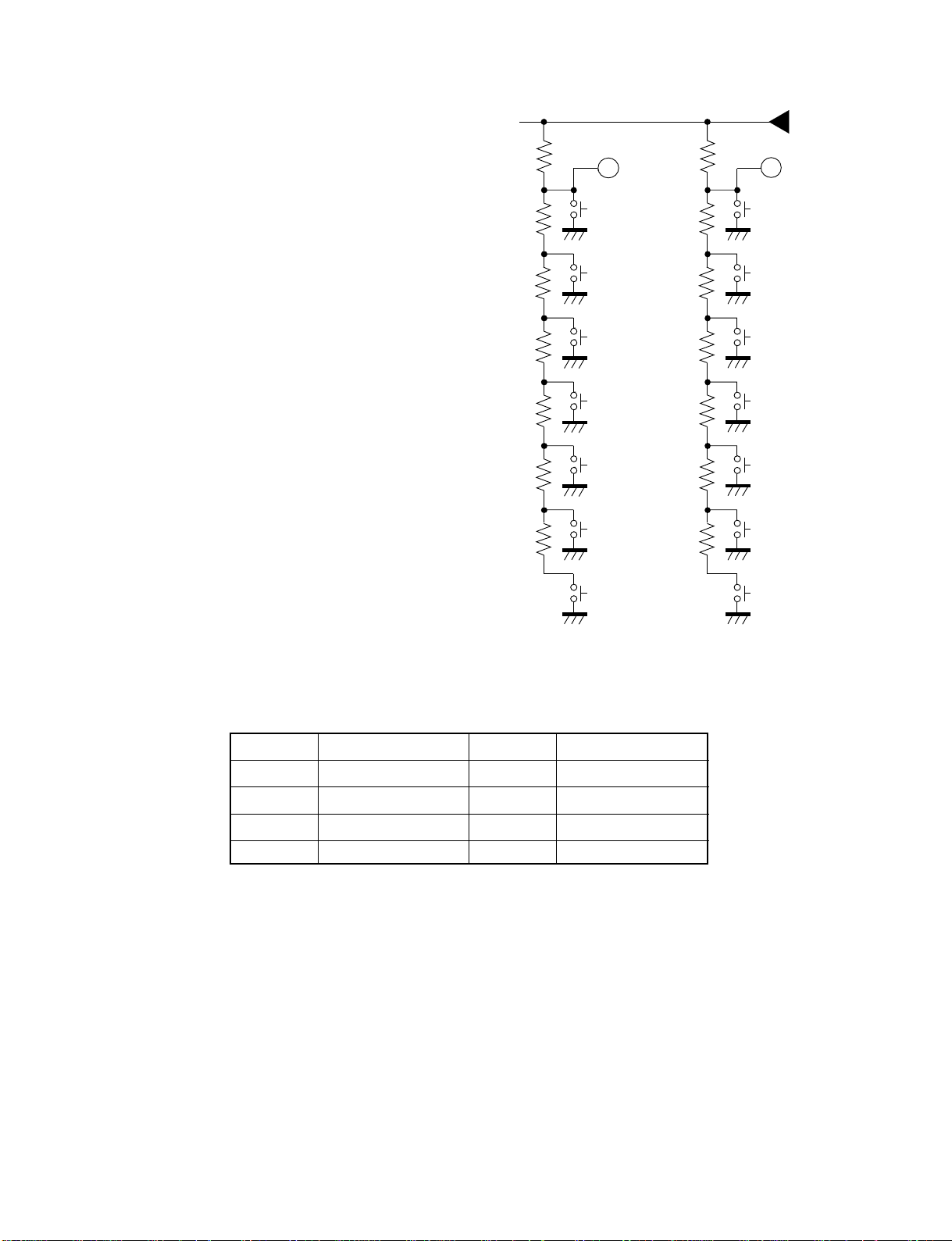

2. HARDWARE COMPONENT

(4) External Input Switching SW IC

(TOSHIBA TA8851CN)

• Performs source switching for main and sub pictures.

• Switches total 4 systems of TV and video 3 inputs.

(5) Memory IC

(MICROCHIP 24LC08BI/P)

• Memorizes the user last status for video and audio adjustment values, volume, external status,

etc.

• Memorizes the parameters which determines the

picture formation and distortion correction of the

white balance data, deflection yoke data, etc.

(6) U/V Tuner Control IC

(MATSUSHITA EL466L)

• Controls U/V channel selection frequency

(1) Channel Selection Microprocessor

The 8-bit single chip microprocessor (TLCS-870

series) is applied. The outline of the microprocessor

is shown below.

• Production type name: TMPA8700CSN-113

• ROM: 60 k X 8 bits

• RAM: 2 k X 8 bits

• Pa ckage : SDIP42-P-600

• OTP built-in: TMPA8700PSN

(2) Audio System Control IC

(TOSHIBA TA1217AN)

• Controls balance, sound quality adjustment such

as high and low sounds and volume.

• Switc hes the SURROUND ON/OFF

• Switches SBS and perfor m level adjustment

• Switches audio mute

(3) Video System Control IC

(TOSHIBA TA1259N)

• Controls video system such as CONTRAST,

BRIGHTNESS, COLOR, TINT, SHARPNESS.

• Adjusts SUB COLOR, SUB BRIGHTNESS, SUB

TINT and other video system parameter.

• Switches the modes for PICTURE PREFERENCE, COLOR TEMPERATURE.

(7) 7DPC Unit Control IC

(TOSHIBA TA1241N)

• Performs pin-cushion distortion correction

(8) PIP Control IC

(TOSHIBA TC90A17F)

• Performs sub picture ON/OFF, LOCATE, STILL,

etc.

(9) C/C Control Microprocessor

(MITUBISHI M37274MX)

• Performs CLOSED CAPTION mode switching

(10) Digital Convergence Control IC

• Performs digital convergence correction control

• Memorizes convergence data

(11) 3D YCS Control IC

(TOSHIBA TC90A28F)

• Performs 3D YCS ON/OFF switc hing (at PIP ON)

• Performs 3D YCS operation control

4-2

Page 29

(12) Video IC for PIP

(TOSHIBA TA1270F)

• Adjusts the video system parameter of SUB

COLOR, SUB BRIGHTNESS, SUB TINT, etc.

for PIP

(13) JFORC (183E2550AF02)

• Controls picture compression/extension in vertical direction

• Controls picture vertical position

(14) SLC (TOSHIBA TC90A04AF)

• Converts in order

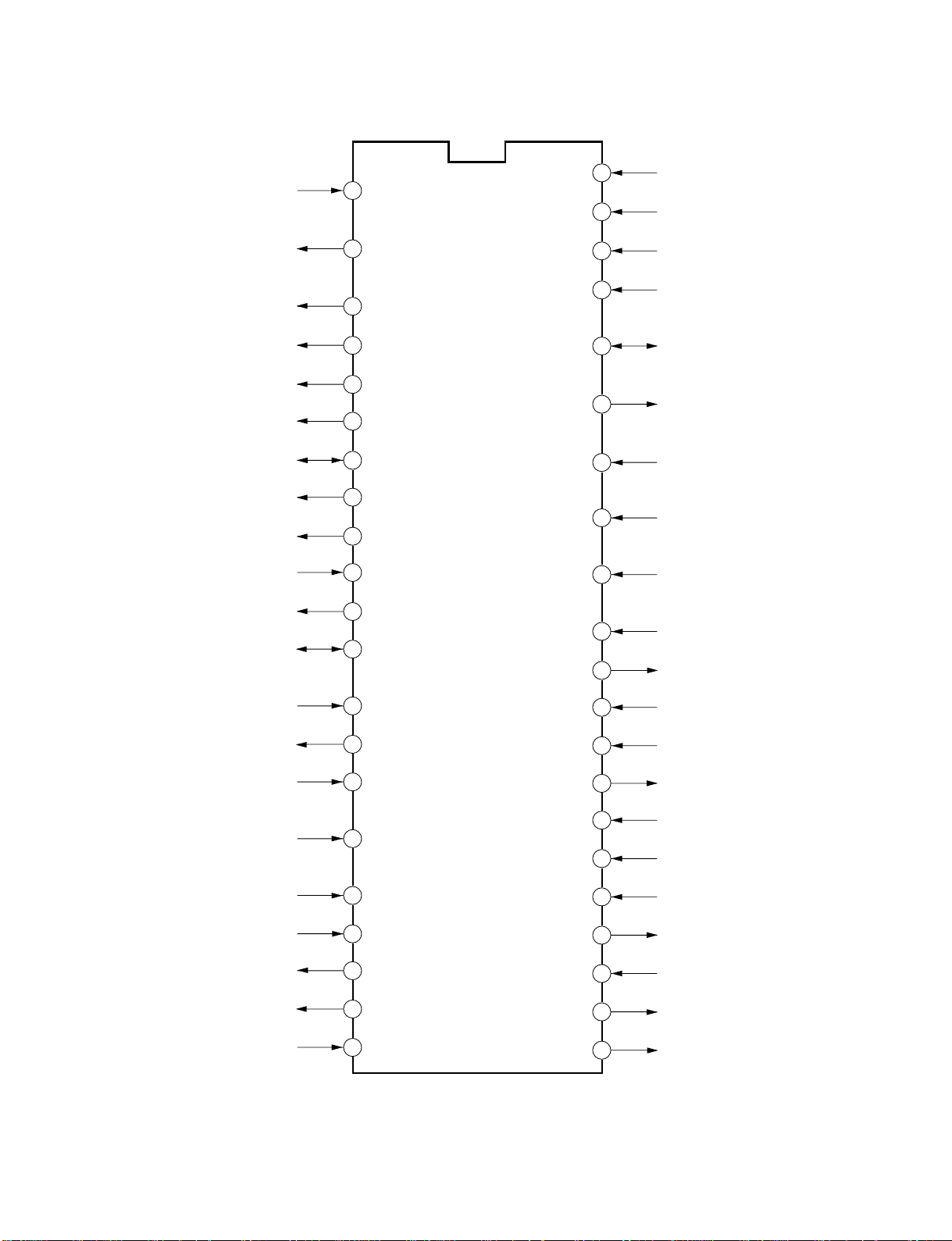

3. MICROCOMPUTER

Microcomputer TMP A8700CSN-113 has 60k byte of R OM

capacity and equipped with OSD function inside.

The specification is as follow.

• Type name : TMPA8700CSN-113

• ROM : 60k byte

• RAM : 2k byte

• Processing speed : 0.5 ms (at 8 MHz with

shortest command)

• Package : 42 pin shrink DIP

•I2C-BUS : two channels

• PWM : 14 bits X 1, 7 bits X 9

• ADC : 8 bits X 6 (Successive

comparison system,

Conversion time 20ms)

This microcomputer performs functions of AD converter,

reception of U/V TV.

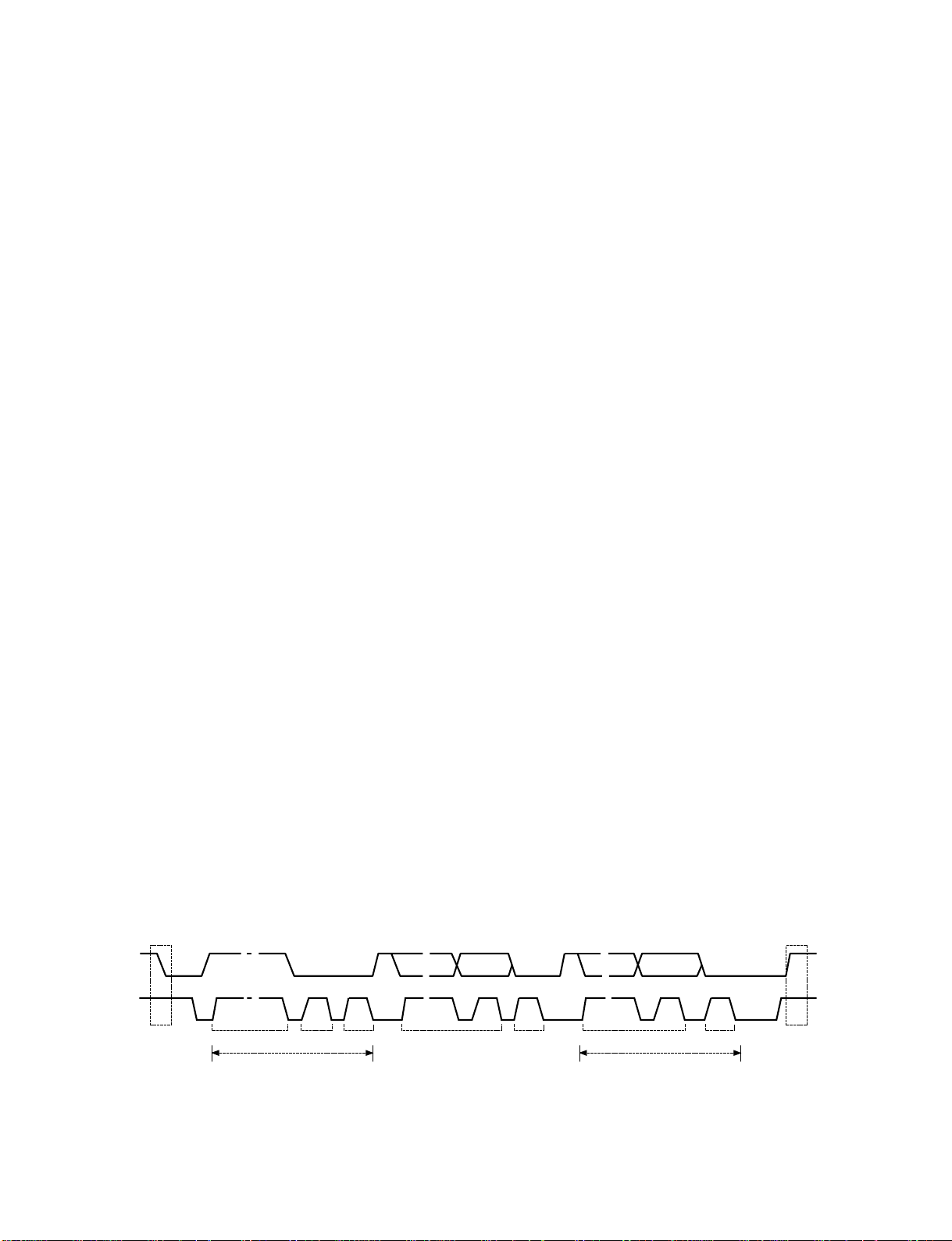

I2C device controls through I2C bus. (Timing chart : See

Fig. 4-1)

• LED uses big current por t for output only.

• For clock oscillation, 8 MHz ceramic oscillator is used.

•I2C has two channels. One is for E2PROM only.

• Self diagnosis function which utilizes ACK function

of I2C is equipped

• Function indication is added to service mode.

• Remote control operation is equipped, and the control

by set no touch is possible. (Bus connector in the conventional bus chassis is deleted.)

• Substantial self diagnosis function

(1) B/W composite video signal generating function

(micom inside)

(2) Generating function of audio signal equivalent to

1 kHz (micom inside)

(3) Detecting function of power protection circuit op-

eration

(4) Detecting function of abnormality in IIC bus line

(5) Functions of LED blink indication and OSD indica-

tion

SDA

SCL

Start

condition

1 - 7

Address

8

R/W

Approx.180 µS

9

Ack Data

1 - 7

Fig. 4-1

4-3

9

8

Ack

1 - 7

Some device may have no data,

or may have data with several

bytes continuing.

8

DATA Ack

9

Stop

condition

Page 30

3-1. Microcomputer Terminal Function

VSS

JRESET

RMT OUT

Lor H

ACTIVE=H, NORMAL=L

ACTIVE=H, NORMAL=L

POWER ON=H, OFF=L

POWER ON=Hz, OFF=L

POWER ON=H, OFF=L

ACTIVE=L, NORMAL=H

AC PULSE INPUT

2

I C - BUS CLOCK

ACTIVE=L, NOT DVD MODE=H

SUB TUNER S

MUTE

SPK MUTE

POWER2

POWER1

LED

PIP RESET

ACP

SCLO

SDAO

2

I C - BUS DATA

SYNC VCD

MAIN SYNC

DVD

AFT2

- CURVE

10

12

13

14

15

11

42

1

<P33>

41

∗

<P40>

∗

2

<P41>

∗

3

<P42>

∗

4

<P43>

∗

5

<P44>

∗

6

<P45>

∗

7

<P46>

∗

8

<P47>

∗

9

<P50>

∗

<P51>

∗

<P52>

∗

<P53>

∗

<P54>

∗

<P55>

∗

<P32>

<P35>

<P34>

<P31>

<P30>

<P20> - -

40

∗

39

38

∗

∗

37

∗

36

∗

35

34

33

32

31

30

29

VDD

PIP VIDEO

PIP SYNC

GND

SDA1

2

I C - BUS DATA

SCL1

2

I C - BUS CLOCK

AV SYNC

SUB SYNC

RMT

VD

RST

NORMAL=H, ACTIVE=L

XOUT

SYSTEM CLOCK

XIN

SYSTEM CLOCK

GND

TEST PORT

OSCO

MAIN TUNER S

NORMAL=L

NORMAL=L

AFT1

- CURVE

KEY - A

ADC 0~5V

KEY - B

ADC 0~5V

SGV

SGA

VSS

16

17

18

19

20

21

<P56>

∗

<P60>

∗

<P61>

∗

<P62>

∗

<P63>

∗

<P57>

∗

Fig. 4-2

4-4

28

<P71> -

27

<P70> -

26

<P67>

∗

25

<P66>

∗

24

<P65>

∗

23

<P64>

∗

22

: TRISTATE I/O

∗

: SYNC OPEN DRAIN OUTPUT

−

OSCI

VSYNC

PIP VSYNC

GND

DATA

OSD IC CONTROL

BUSY

OSD IC CONTROL

CS

OSD IC CONTROL

CLK

OSD IC CONTROL

Page 31

3-2. Microcomputer Terminal Name and Operation Logic

Table 4-1

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

Terminal

Name

VSS

JRESET

REM OUT

MUTE

SPK MUTE

POWER2

POWER1

LED

PIP RST

ACP

SCL0

SDA0

SYNC VCD

DVD

AFT2

AFT1

KEY-A

KEY-B

SGV

SGA

OSD RESET

OSD CLK

OSD CS

OSD BUSY

OSD DATA

VSS

VSYNC

OSCI

OSCO

GND

XIN

XOUT

RST

VD

RMT

AV SYNC

SCL1

SDA1

GND

PIP SYNC

PIP VIDEO

VDD

I/O

O

P4CR (OCH)

O

P4CR (OCH)

O

P4CR (OCH)

O

P4CR (OCH)

O

P4CR (OCH)

O

P4CR (OCH)

I/O

P4CR (OCH)

O

P4CR (OCH)

O

P4CR (OCH)

I

P5CR1 (09H)

O

P5CR2 (FAEH)

I

P5CR2 (FAEH)

I

P5CR1 (09H)

O

P5CR1 (09H)

I

P5CR1 (09H)

I

P5CR1 (09H)

O

O

O

O

O

P5CR1 (09H)

O

O

I

O

I

I

I

O

I

I

O

I

I

I

I

O

I/O

I

I

I

I

P6CR (0DH)

P6CR (0DH)

P6CR (0DH)

P6CR (0DH)

P6CR (0DH)

P6CR (0DH)

P6CR (0DH)

P6CR (0DH)

P7 (07H)

P7 (07H)

—

—

—

—

P2 (02H)

P3 (03H)

P3 (03H)

P3 (03H)

P3 (03H)

—

—

—

—

D0=1

D1=1

D2=1

D3=1

D4=1

D5=0/1

D6=1

D7=1

D0=1

D1=0

D2=0

D3=0

D4=0

D5=0

D6=0

D0=0/1

D1=0/1

D2=1

D3=1

D7=1

D4=1

D5=1

D6=0

D7=1

D0=1

D1=1

D2=1

D3=0

—

—

—

—

D0=1

D0=0

D1=1

D4=1

D5=1

—

—

—

—

Functions & Logic

Microcomputer GND, 0V connection

Active = H, Normal = L

RMT output

Sound mute output, Mute = H, Normal = L

Speaker mute, Mute = H, Noraml = L

DEF power control, POW ON = H, POW OFF = L

Power supply control, POW ON: Hz, POW OFF: L

LED control, ON: H, Reset: L

PIP reset, ON: H, OFF: L

AC pulse input

Non volatile memory I2C-bus clock, rising sync

Non volatile memory I2C bus data

Main sync, negative logic

DVD mode switching, L: at color difference input, H: normal

Sub tuner AFT, S character input

Main tuner AFT, S character input

Local key A control, 0 ~5V

Local key B control, 0 ~ 5V

Test patter n output, Noraml: L

Test audio output, Nor mal:L Active:1 kHz squarewave

OSD IC reset, Normal: H, Reset: L

OSD IC control clock, CLK frequency: approx. 20 kHz

ODS IC control CS, Active: L

OSD IC busy, Nor mal: L, Busy: H

OSD IC control data

0V

PIP vertical sync pulse detection for V-CHIP

Not used.

Not used.

Micorcomputer shipping test

System clock

oscillation connection terminal (8 Hz)

Hard reset terminal, negative logic

Vertical sync pulse detection

Remote control signal detection , Negative logic

RF sync judgement, Sync: H, No sync: L

I2C bus clock, rising sync

I2C bus data

Slicer ground, 0V connection

V-CHIP

terminal

Microcomputer power supply 5V

4-5

Page 32

4. E2PROM (QA02)

E2PROM (non-volatile memory) has function which, in

spite of power-off, memorizes the such condition as channel selecting data, last memory status, user control and

digital processor data. The capacity of E2PROM is 8k bits.

EEPROM (QA02)

1

A0

Device address

GND

A1

A2

Vss

2

3

4

Fig. 4-3

Type name is 24LC08BI/P or ST24C08CB6, and those

are the same in pin allocation and function, and are exchangeable each other. This IC controls through I2C bus.

The power supply of E2PROM and MICOM is common.

Pin function of E2PROM is shown in Fig. 4-3.

Vcc + 5V

8

NC

7

SCL

6

SDA

5

I2C-BUS line

5. ON SCREEN FUNCTION

ON SCREEN FUNCTION indicates data like channel,

volume. RGBI and I/M signals are output from QR60 by

the control from QA01. These signals are input to Q501

and displayed on a screen.

UM01 OSD/CC/RGB SW

SCLK

54

55

56

58

8

9

16

S IN

SCS

TRE

HSYNC

VSYNC

RESET

To

QA01

From

deflection

circuit

To

QA01

CLK

DATA

CS

BUSY

HD2

VD2

OSD

RESET

9

8

7

6

11

12

5

INVERTER

RESET

GENERATION

QR60

VOB2

YM

64

59

R

60

G

61

B

I

62

ATT

1

1

5

2

6

VIDEO

R OUT

G OUT

B OUT

YS-OUT

To Q501

Fig. 4-4

4-6

Page 33

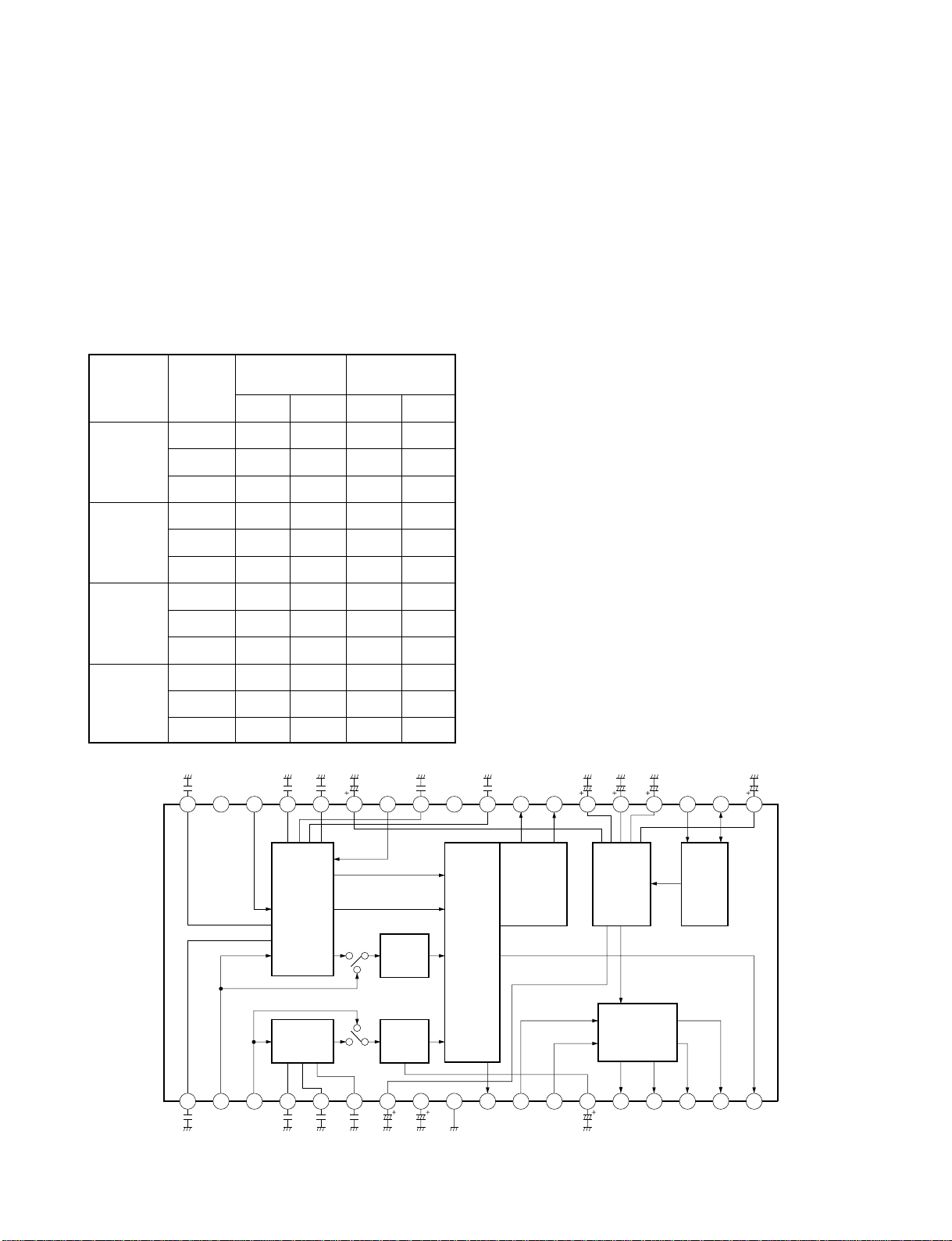

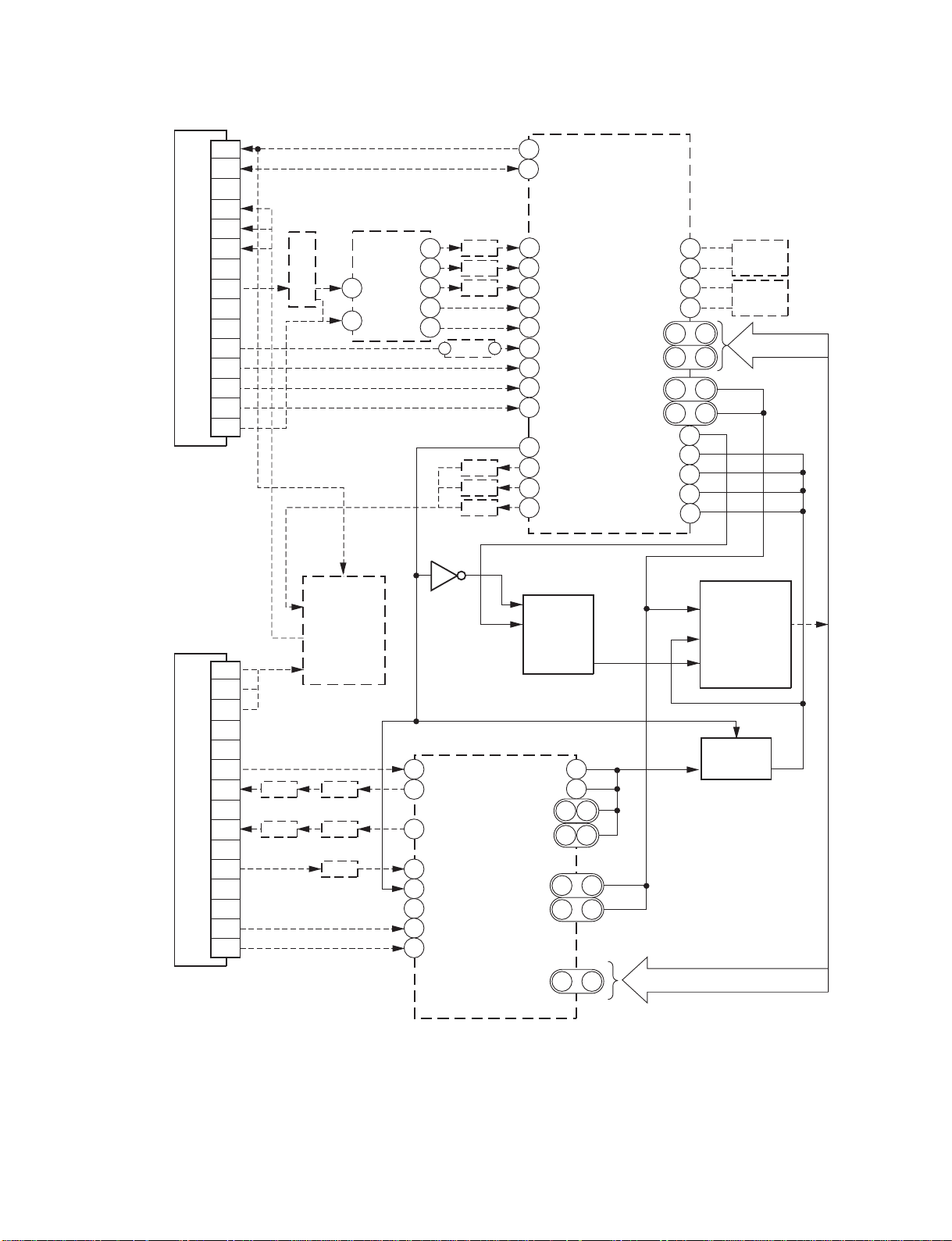

6. SYSTEM BLOCK DIAGRAM

Q A 01

TM PA 8700C SN

Q A 02

MEMORY

24LC 08BI/P

SDA SCL

5

6

SCLO

11

SDAO

12

PIP V SYN C PULSE

V SYNC PULSE

REMO TE

CONTROL

OUTPUT

AUDIO M UTE

27

34

3

4

5

21

22

23

24

25

VD

RM T OUT

MUTE

SPK M UTE SPEAKER M UTE

RESET

CLK

CS

BUSY

DATA

- 113

SDA1

S C L1

RM T

KEY-A

KEY-B

RST

VDD

VSS

POW ER 1

POW ER 2

ACP

XIN

XOU T

SGV

SGA

SYNC VCD

AFT1

SYNC AV

AFT2

38

37

35

17

18

33

42

10

31

32

19

20

13

16

36

15

H 001

P LL

REMO TE CONTROL

LIG HT SENSE UNIT

KEY SW ITCH

POW ER

1

7

6

CIRCUIT

8 M H z

CLO CK

SYGN AL

OUTPUT

SYNC DETECTIO N

AFT DETECTION

SYNC DETECTIO N

AFT DETECTION

SDA SCL

Q 501

VCD

TA 1259N

SDA SCL

27 28

H 002

IM A

M V U S34B

Q V 01

AV SW

TA 8851C N

SDA SCL

26

H Y01

TIF

E L924L2

SDA SCL

27

Q R 60

OSD

- A PG - 129 - SH

M B90091

CLK DATA CS BUSY RST

54 55

56 58

16

JFORC

183E 2550AF 02

Q Y 01

PVCD

TA 1270F

Q Z 01

3D - YCS

TC 90A 28F

SLC

TC 90A 04A F

Fig. 4-5

Q 350

I/O EXPANDER

JLC1562B N

SDA SCL

15

Q M 01

C/C

M 37274M X -

SDA SCL

37

14

XXXSP

39

Q Y 03

DUAL

TC 90A 17F

SDA SCL

82

83

Q H 001

DIGI CO NV

Q 302

DPC

TA 1241

SDA SCL

14

15

4-7

Page 34

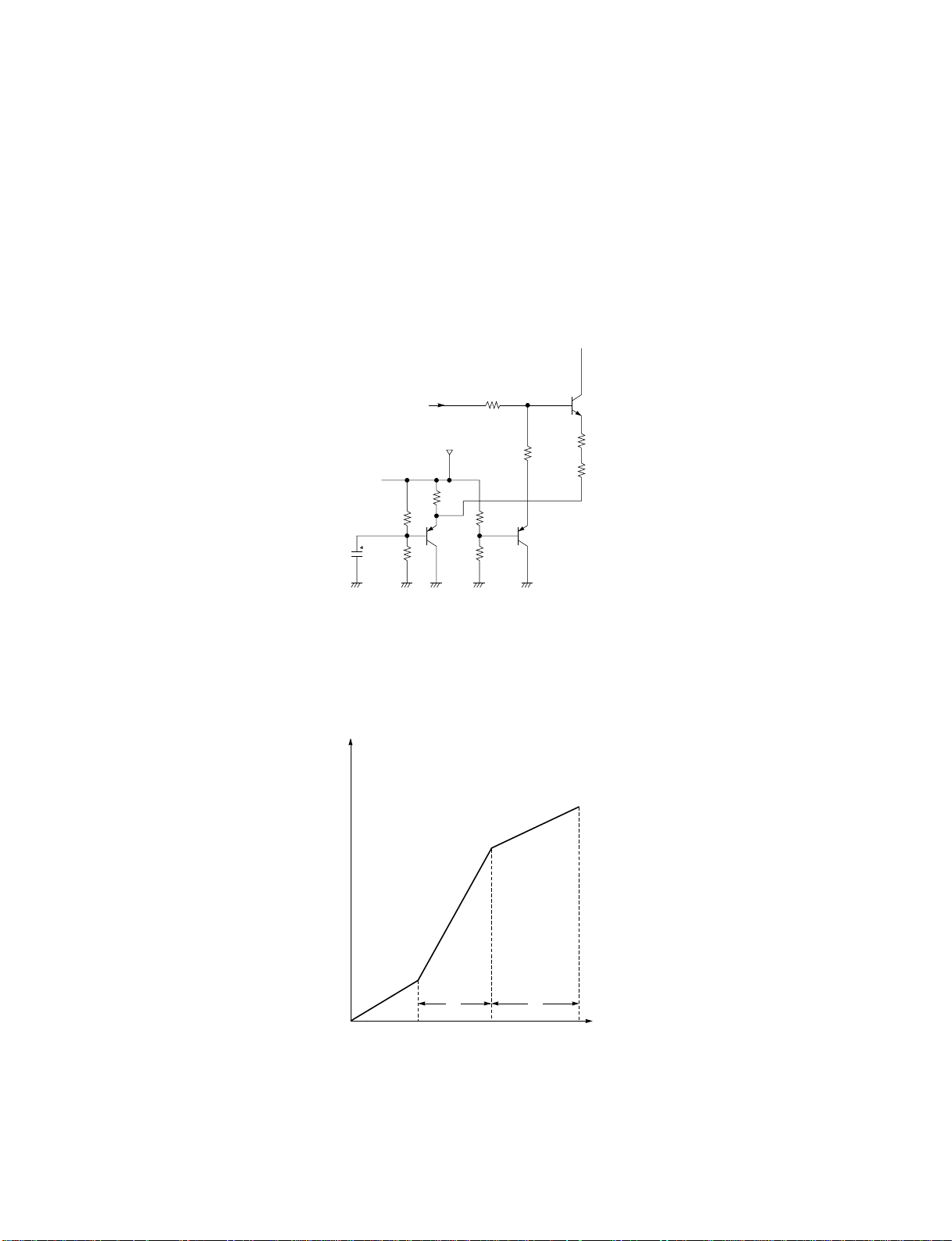

7. LOCAL KEY DETECTION METHOD

V

Local key detection in the N7SS chassis is carried out by

using analog like method which detects a voltage appears

at local key input terminals (pins 17, 18) of the microcomputer when a key is pushed. With this method using

two local key input terminals (pins 17, 18), key detection

up to maximum 14 keys will be carried out.

The circuit diagram shown left is the local key circuit. As

can be seen from the diagram, when one of key among

SA-01 to SA-08 is pressed, each of two input terminal

(pins 17, 18) developes a voltage VIN corresponding to the

key pressed. (The voltage measurement and key identification are carried out by an A/D converter inside the microcomputer and the software.

17

SA08

SA06

SA05

SA07

5

18

SA01

SA02

SA03

SA04

Key No.

SA01

SA-02

SA-03

SA-04

Table 4-2 Local key assignment

Function

DEMO START/STOP

POWER

CH UP

CH DN

Key No.

SA-05

SA-06

SA-07

SA-08

Fig. 4-6 Local key assignment

Function

VOL UP

VOL DN

ANT/VIDEO, ADV

MENU

4-8

Page 35

8. REMOTE CONTROL CODE ASSIGNMENT

Table 4-3

CUSTOM CODES ARE 40-BFH

Code

00H 0 Channel

01H 1 Channel

02H 2 Channel

03H 3 Channel

04H 4 Channel

05H 5 Channel

06H 6 Channel

07H 6 Channel

08H 8 Channel

09H 8 Channel

0AH 100 Channel

0BH ANT 1/2

0CH RESET

0DH AUDIO

0EH PICTURE/FUNC

0FH TV/VIDEO

10H MUTE

11H CHANNEL SEARCH

12H POWER

13H MT S

14H ADD/ERASE

15H TIMER/CLOCK

16H AUTO PROGRAM

17H CHANNEL RETURN

18H DSP/SUR (TV/CATV)

19H CONTROL UP

1AH VOLUME UP

1BH CHANNEL UP

1CH RECALL

1DH CONTROL DOWN

1EH VOLUME DOWN

1FH CHANNEL DOWN

40H PIP LOCATE

41H PIP LOCATE

42H PIP LOCATE

43H PIP LOCATE

44H CARVER

45H SURROUND UP

46H SURROUND DOWN

47H VOCAL ZOOM

48H CHANNEL LOCK

49H

4AH PIP CHANNEL UP

4BH

4CH

4DH

4EH PIP LOCATE (CH SEARCH)

4FH PIP SOURCE

Function to remote

PIP CHANNEL DOWN

PIP STILL/RELEASE

PIP ZOOM, ZOOM SIZE

Applicable

control

Applicable Conti-

to TV set nuty

Custom codes are 40-BFH

Code

50H PIP STILL

51H PIP ON/OFF

52H Do not use. Old type core power ON

53H PIP SWAP

54H PIC SIZE

55H DSP F/R

56H WIDE/SCROLL

57H CAPTION

58H EXIT

59H CYCLONE, SBS

5AH SET UP

5BH OPTION

5CH SUB WOOFER UP

5DH

5EH

5FH

80H MENU

81H EDS

82H ADV UP

83H ADV DWN

84H

85H GUIDE

86H THEME

87H LIST

88H PIP CONTROL

89H ENTER/TUNE

8AH PAGE UP

8BH DATA UP

8CH PAGE DN

8DH DATA DN

8EH CANCEL

8FH REC

90H

91H

92H Do not use. Old type core on.

93H

94H

95H

96H

97H NOISE CLEAN

98H

99H

9AH PIP VOLUME UP

9BH

9CH PIP CONTROL

9DH

9EH

9FH

Function to remote

SUB WOOFER DOWN

PIP VOLUME DOWN

Applicable

control

Applicable Conti-

to TV set nuty

4-9

Page 36

Custom codes are 40-BFH

Custom codes are 40-BFH

Code Applicable Conti-

A0H

A1H

A2H

Function

SUB-BRIGHT ADJUSTMENT

G. DRIVE ADJUSTMENT

B. DRIVE ADJUSTMENT

to TV set nuty

A3H

A4H

CUTOFF DRIVE 40H INITIALIZING, SCREEN, ADJ.

A5H R. CUTOFF ADJUSTMENT

A6H G. CUTOFF ADJUSTMENT

A7H B. CUTOFF ADJUSTMENT

A8H

MEMORY ALL AREA INITIALIZE

A9H PIP BRIGHT ADJUSTMENT

AAH

SUB CONTRAST ADJUSTMENT

ABH

HOR, VER PICTURE POSITON ADJUSTMENT

ACH SUB COLOR ADJUSTMENT

ADH SUB TINT ADJUSTMNET

AEH ADJUSTMENT-UP

AFH ADJUSTMENT-DOWN

B0H

SCREEN ADJ.: SERVICE

B1H DSP ON/OFF

B2H TEXT-1

B3H

TV/PIP VIDEO CHANGE-OVER

B4H CAPTION-1

B5H

B6H

B7H

TV/CABLE CHANGE-OVER IN SAME TIME ON MAN AND SUB

B8H HOTEL SETTING MENU

B9H DATA 4 TIMES SPEED UP

BAH DATA 4 TIMES SPEED DOWN

BBH

CHANGE-OVER OF HOTEL/NORMAL

BCH PIP CENTER

BDH M MODE

BEH CAPTON OFF

BFH ALL CHANNEL PRESET

C0H

C1H DIRECT WIDE 1

C2H DIRECT FULL

C3H

C4H

C5H

C6H

C7H

C8H

C9H

CAH

CBH

CCH

CDH

CEH

DFH

Code Applicable Conti-

Function

to TV set nuty

D0H

D1H

D2H Do not use. Old type core power ON

D3H

D4H

D5H

D6H

D7H PIP VIDEO ADJ.

D8H

STILL, FRAME ADVANCE

D9H

DAH SPEED

DBH

DCH ZOOM

DDH

DEH

DFH

E0H

PINCUTION/EW CORER (PARA/CNR)

E1H

VERTICAL S-CUVE CORRECTION/VERTICAL M-CURVE CORRECTION (VSC/FVC)

E2H

E3H

E4H

E5H

E6H

E7H

E8H

E9H

EAH

HORIZONTAL WIDTH (WID/PARA)

EBH

TRAPEZOIDE CORRECTION (TRAP)

ECH TEST TONE

EDH DOLBY

EEH

3 DIMENTIONAL Y/C SEPARATION

EFH DPC

E0H

STANDARD (HEIGHT LINEARITY) (VLIN/HIT)

E1H

WIDE (HEIGHT LINEARITY) (VLIN)

F2H SCROOL

F3H

WIDE 1, 2, 3

F4H

F5H

F6H

F7H

F8H

F9H

FAH

FBH

FCH

FDH

FEH

FFH

4-10

Page 37

9. ENTERING TO SERVICE MODE

11. SERVICE ADJUSTMENT

(1) Procedures

1) Press once MUTE key of remote hand unit to

indicate MUTE on screen.

2) Press again MUTE key of remote hand unit to

keep pressing until the next procedure.

3) In the status of above (2), wait for disappearing

of indication on screen.

4) In the status of above (3), press MENU (Channel

setting) key on TV set.

(2) Service mode is not memorized as the last-memory.

(3) During service mode, indication S is displayed at

upper right corner on screen.

10. TEST SIGNAL SELECTION

(1) In OFF state of test signal, SGA terminal (Pin 20)

and SGV terminal (Pin 21) are kept “L” condition.

(2) The function of VIDEO test signal selection is cy-

clically changed with VIDEO key (remote unit).

Table 4-4

Test signal

No.

0

1

2

3

4

5

6

7

8

9

10

11

Signal OFF

All black signal + R single color (OSD)

All black signal + G single color (OSD)

All black signal + B single color (OSD)

All black signal

All white signal

W/B

Black cross bar

White cross bar

Black cross hatch

White cross hatch

Black cross dot

Name of pattern

(1) ADJUSTMENT MENU INDICATION ON/OFF :

MENU key (on TV set)

(2) During display of adjustment menu, the followings

are effective.

1) Selection of adjustment item :

POS UP/DN key (on TV/Remote unit)

2) Adjustment of each item :

VOL UP/DN key (on TV/ Remote unit)

3) Direct selection of adjustment item

R CUTOFF: 1 POS (Remote unit)

G CUTOFF: 2 POS (Remote unit)

B CUTOFF: 3 POS (Remote unit)

4) Data setting for PC unit adjustment

SUB CONTRAST: 4 POS (Remote unit)

SUB COLOR: 5 POS (Remote unit)

SUB TINT: 6 POS (Remote unit)

5)

Screen adjustment mode ON/OFF: VIDEO

(TV)

6) Test signal selection: VIDEO (Remote unit)

* In service mode, serviceable items are limited.

(3) Test audio signal ON/OFF: 8 POS (Remote unit)

* Test audio signal: 1 kHz

(4) Self check display: 9 POS (Remote unit)

* Cyclic display (including ON/OFF)

(5) Initialization of memory :

CALL (Remote unit) + POS UP (TV)

(6) Initialization of self check data :

CALL (Remote unit) + POS DN (TV)

(7) BUS OFF :

CALL (Remote unit) + VOL UP (TV)

(8) Convergence adjustment pattern: 7 POS

Pushing once: Convergence adjustment mode

Pushing twice: Data memory

Pushing three times: Escaping from pattern.

12

White cross dot

(3) SGA (audio test signal) output should be square wave

of 1 kHz.

4-11

Page 38

12. FAILURE DIAGNOSIS PROCEDURE

Model of N7SS chassis is equipped with self diagnosis function inside for trouble shooting.

12-1. Contens to be Confirmed by Customer

Table 4-5

Contents of self diagnosis

A. DISPLAY OF FAILURE INFORMATION

IN NO PICTURE (Condition of display)

1. When power protection circuit operates;

2

2. When I

C-BUS line is shorted;

Power indicator lamp blinks and picture does not come.

1. Power indicator red lamp blinks. (0.5 seconds interval)

2. Power indicator red lamp blinks. (1 seconds interval)

If these indications appear, repairing work is required.

Display items and actual operation

12-2. Contents to be Confirmed in Service Wo rk (Check in Self Diagnosis Mode)

Table 4-6

Contents of self diagnosis

Contents of self diagnosis

<Countermeasure in case that phenomenon always

arises.>

B. Detection of shortage in BUS line

C. Check of communication status in BUS line

D. Check of signal line by sync signal detection

E. Indication of part code of microcom. (QA01)

F. Number of operation of power protection circuit

Display items and actual operation

Display items and actual operation

(E xam ple of screen display)

SELF C HECK

N O . 239X XXX

PO W E R : 000000

BUS LINE: O K

BUS C ONT: O K

B L O C K : Q V 0 1 , Q V 0 1 S

Part coce of Q A01

N um ber of operation of

pow er protection circuit

Short check of bus line

C om m unication check of

busline

E

F

B

C

D

12-3. Executing Self Diagnosis Function

12-3-1. Procedures

(1) Set to service mode.

(2) Pressing “9” key on remote unit displays self diag-

nosis result on screen.

Every pressing changes mode as below.

SERVICE mode SELF DIAGNOSIS mode

(3) To exit from service mode, turn power off.

4-12

Page 39

12-4. Understanding Self Diagnosis Function Indication

In case that phenomenon always arises. See Fig. 4-7 .

(E xam ple of screen display)

SELF C HECK

N O . 239X XXX

PO W E R : 000000

BUS LINE: OK

BUS C ONT: OK

B L O C K : Q V 0 1 , Q V 0 1 S

Part coce of QA01

N um ber of operation of

pow er protection circuit

Short check of bus line

C om m unication check of

busline

Fig. 4-7

Table 4-5

E

F

B

C

D

Item

BUS LIME

BUS CONT

BLOCK: QV01

QV01S

Contents

Detection of bus line short

Communication state of bus line

The sync signal part in each video signal

supplied from each block is detected.

Then by checking the existence or non of

sync part, the result of self diagnosis is

displayed on screen. Besides, when "9"

key on remote unit is pressed, diagnosis

operation is first executed once.

Instruction os results

Indication of OK for normal result, NG for abnormal

Indication of OK for normal result

Indication of failure place in abnormality

(Failure place to be indicated)

QA02 NG, H001 NG, Q501 NG, H002 NG

QV01 NG, Q302 NG, QY02 NG, HY01 NG

QD04 NG, QM01 NG, Q701 NG

QA02 E2PROM, Q350 I/O EXP

H001 MTUN, QM30 C/C

Q501 VCD, QX40 JFORC

H002 MTS, Q701 DIG-CONV

QV01 AVSW, QZ01 YCS

Q302 E-WC, QX30 SLC

QY03 DUAL, QY01 PIP/VCD

HY01 PIP TUN, QK06 WAC

Note 1. The indication of failure place is only one place

though failure places are plural. When repair of a

failure place finishes, the next failure place is

inndicated. (The order of priority of indication is

left side.)

*Indication by color

• Normal block : Green

• Non diagnosis block : Cyan

4-13

Page 40

13-4-1. Clearing Method of Self diagnosis Result

In the error count state of screen, press “CHANNEL

DOWN” button on TV set pressing “Recall” button on

remote unit.

Caution:

Allways keep the following caution, in the state of service mode screen.

• Do not press “CHANNEL UP” button. This will cause

initialization of memory IC. (Replacement of memory

IC is required.

• Do not initialize self diagnosis result. This will change

user adjusting contents to factory setting value. (Adjustment is required.)

13-4-2. Method Utilizing Inner Signal

(VIDEO INPUT 1 terminal should be open.)

(1) With service mode screen, press VIDEO button on

remote unit. If inner video signal can be received,

QV01 and after are normal.

(2) With service mode screen, press “8” button on re-

mote unit. If sound of 1 kHz can be heard, QV01

and after are normal.

* By utilizing signal of VIDEO input terminal, each cir-

cuit can be checked. (Composite video signal, audio

signal)

White

Yellow

Cyan

Green

Magenta

Red

Blue

( COLOR BAR SIGNAL)

Color elements are positioned in sequence of high brightness.

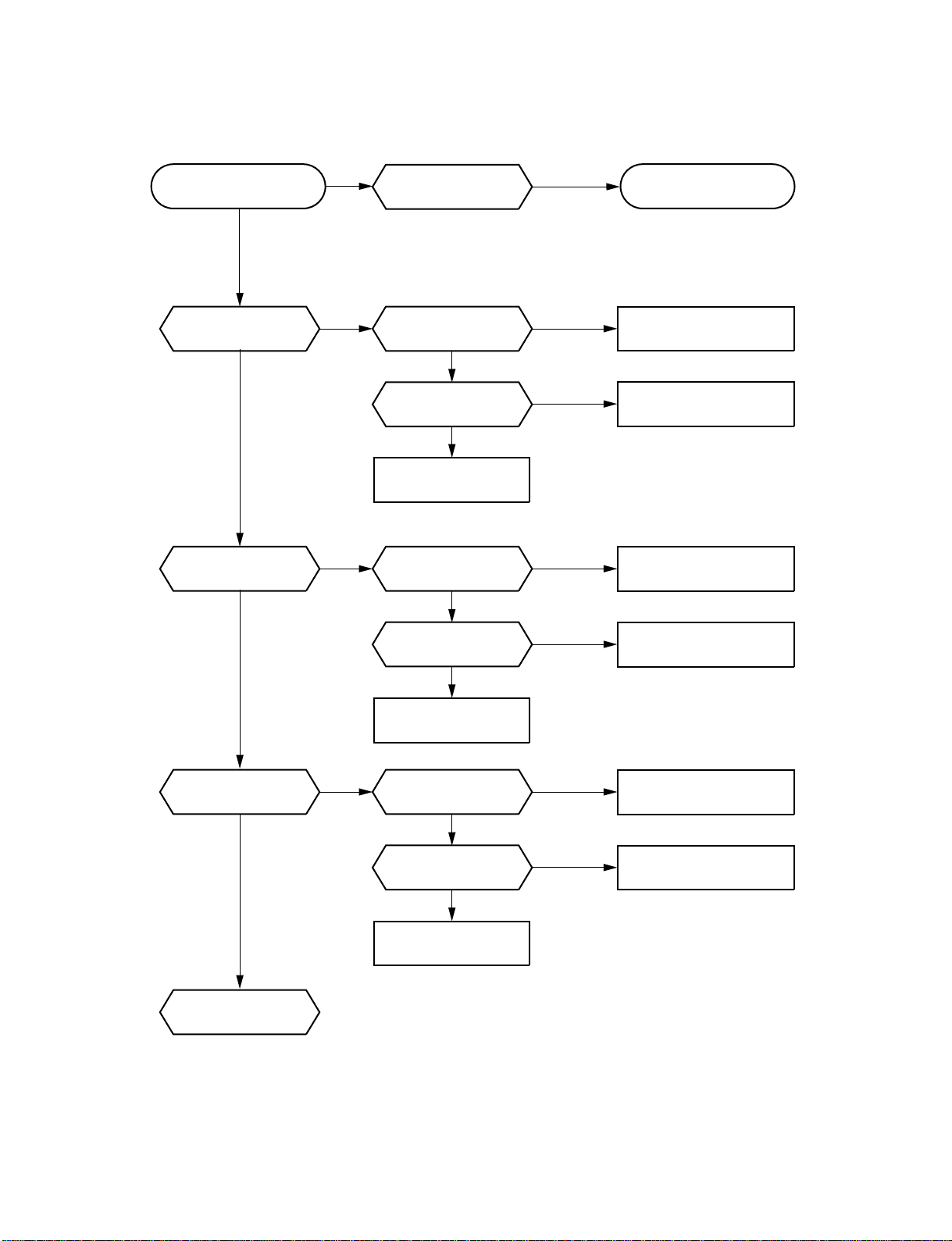

13. TROUBLE SHOOTING CHART

13-1. TV does not turn ON.

Key on TV

Voltage change at pins 17, 18 of

QA01 (5V to 0V).

OK

Replace QA01.

Remote unit key

Pulse input at pin 35 of QA01,

When remote unit key is pressed.

OK

Fig. 4-8

NG

Check key-in circuit.

NG

Replace QA01

Check tuner power circuit.

Fig. 4-9

4-14

Page 41

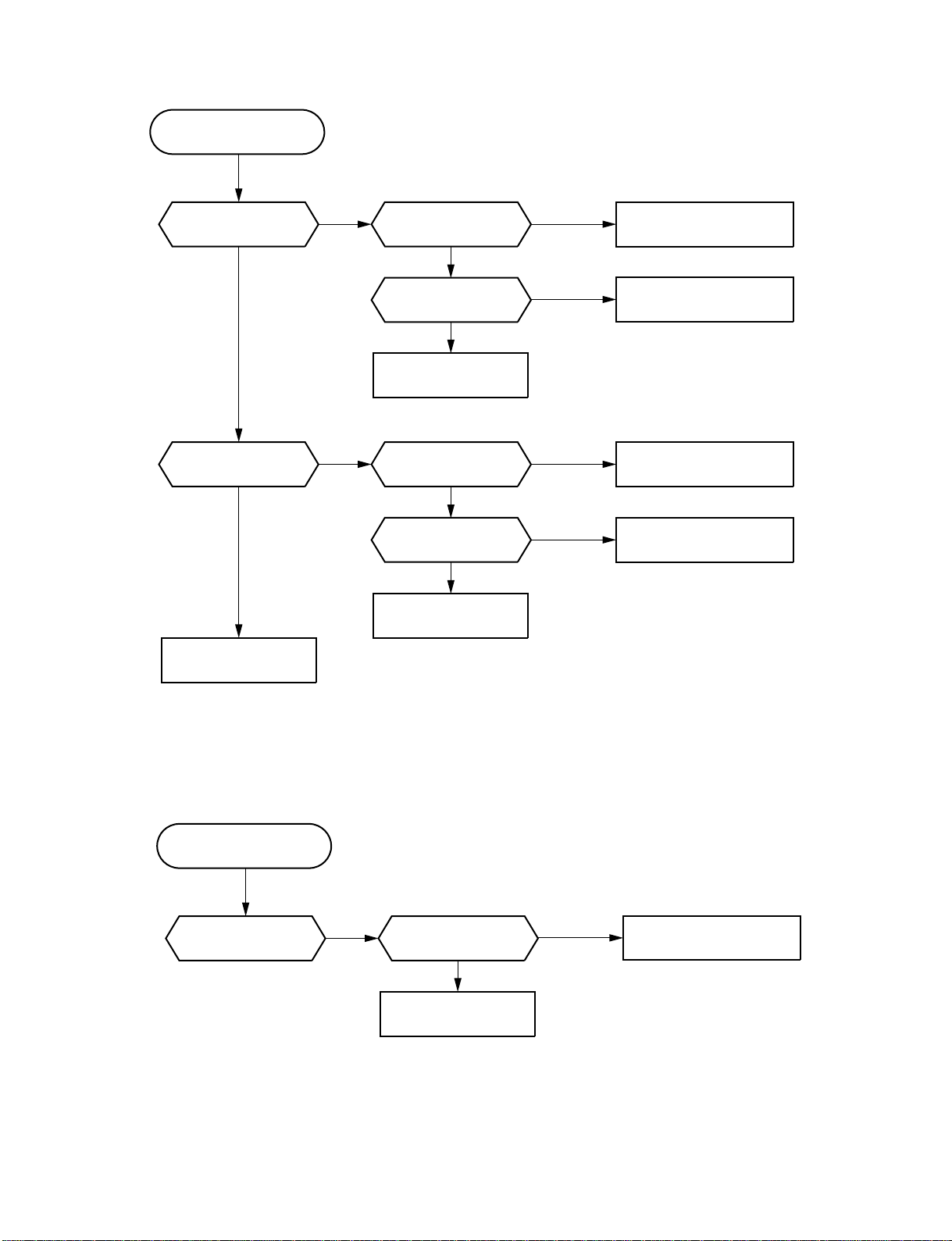

13-2. No Acception of Ke y-IN

Key on TV

Voltage change at pins 17, 18 of

QA01 (5V to 0V).

OK

Replace QA01.

Remote unit key

Pulse input at pin 35 of QA01,

When remote unit key is pressed.

OK

Replace QA01

NG

Check key-in circuit.

NG

Check tuner power circuit.

Fig. 4-10

13-3. No Picture (Snow Noise)

No picture

Voltage at pins of +5V and 32V.

OK

Check H001. Check tuner power circuit.

NG

Fig. 4-11

4-15

Page 42

13-4. Memory Circuit Check

Memory circuit check

Voltage check at pin 8 of QA02 (5V).

NG

Pulse input at pins 5 and 6 of QA02

in memorizing operation.

Replace QA02.

Adjust items of TV set adjustment.

13-5. No Indication on Screen

No indication on screen.

OK

NG

OK

Note: Use replacement parts for QA02.

Fig. 4-12

Check power circuit.

Check QA01.

Check of character signal at pin 23

of QA01. (5V(p-p))

OK

Input of OSC waveform at pin 29 of QA01

with indication key pressed.

OK

Check of sync signal at pins 26, 27 of QA01.

OK

Replace QA01.

Fig. 4-13

NG

Check V/C/D circuit.

NG

Check OSC circuit.

Check sync circuit.

4-16

Page 43

SECTION V

VIDEO CIRCUIT

5-1

Page 44

1. A/V SELECTOR CIRCUIT

1-2. Speifications

1-1. General

The A/V selector circuit selects the video and audio signals from the tuner and external device. Selection of signals is controlled by the microcomputer through the I2C

bus.

U/V tuner (main)

IMA

H001, H002

Equalizer

~QV43

QV40

4

5 6

TIF

HY01

2

V L V R

TV2 TV1

Internal input

External input

Output

Table 5-1

U/V tuner (Main)

U/V tuner (Sub)

Video 1 (with S terminal)

Video 2

Video 3 (Front) (with S terminal)

Video output (V, L, R)

R

43

(Main)

L

To audio SW

45

To monitor output

Video 1

Video 2

Video 3

Y

C

V

L

R

V

L

R

Y

C

V

L

R

9

11

7

10

50

51

49

21

23

19

20

22

8

Y

C

V

L

R

V

L

R

Y

C

V

L

R

E1

QV01

TA8851CN

E2

E3

Fig. 5-1 Block diagram of the A/V selector circuit

(Main)

(Main)

Input

(Main)

Output

(Sub)

Output

Y or V

V

46

3D

Y

48

C

40

C

42

Y

44

C

32

34

comb filter

To Q501

To DUAL unit

5-2

Page 45

1-3. Operation of the Circuit

1-3-1. Composite Video Signal

The selected video signal is sent to pin 46 of QV01, YCseparated through the comb filter, applied to pins 40 & 48

and output to pins 42 & 46 of QV01, then supplied to

Q501 (V/C/D).

The video signal for the subscreen is sent to pins 32 and