Toshiba P35 Schematics

A

1 1

B

C

D

E

LONGBEACH 10/20

2 2

LA-2371 REV

1.0 Schematic

Portability Prescott/Northwood

3 3

RC300ML(RX300ML)+IXP150+ATI M11P(128MB VRAM)

2004-07-23

4 4

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

C

D

Size Document Number Rev

Custom

LA-2371

星期

, 27, 2004

Date: Sheet

二七月

E

of

156

1.0

A

B

C

D

E

Compal confidential

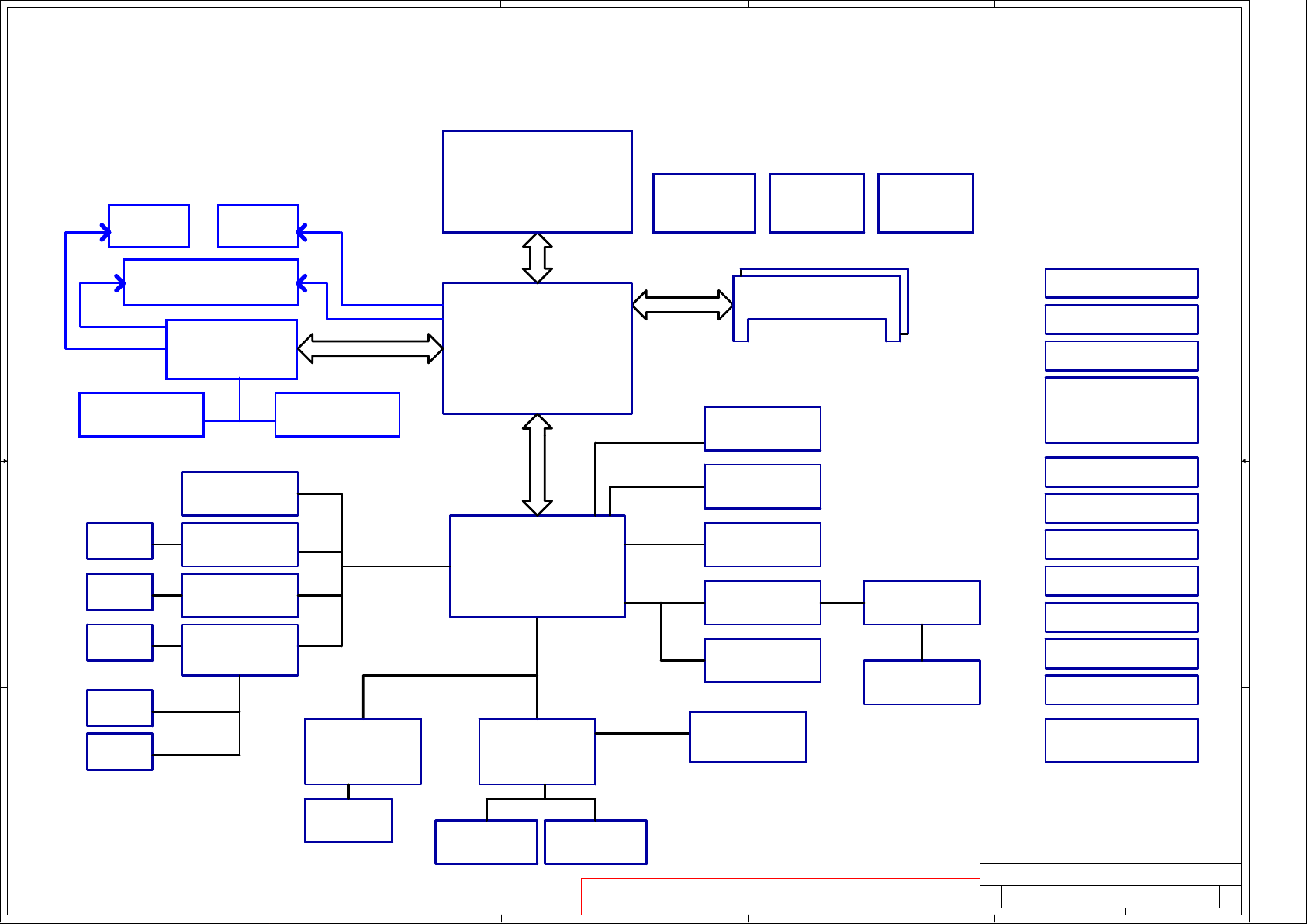

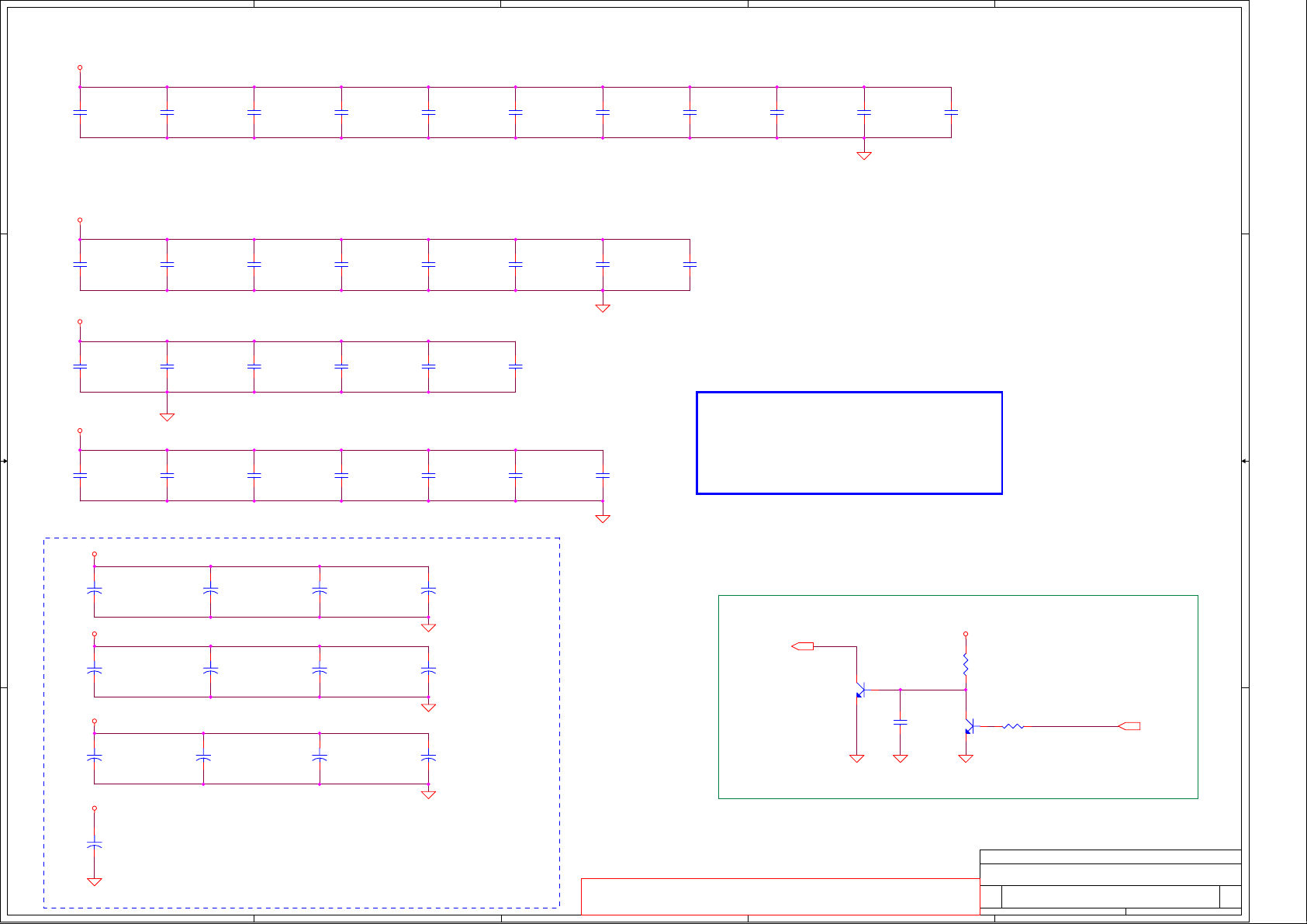

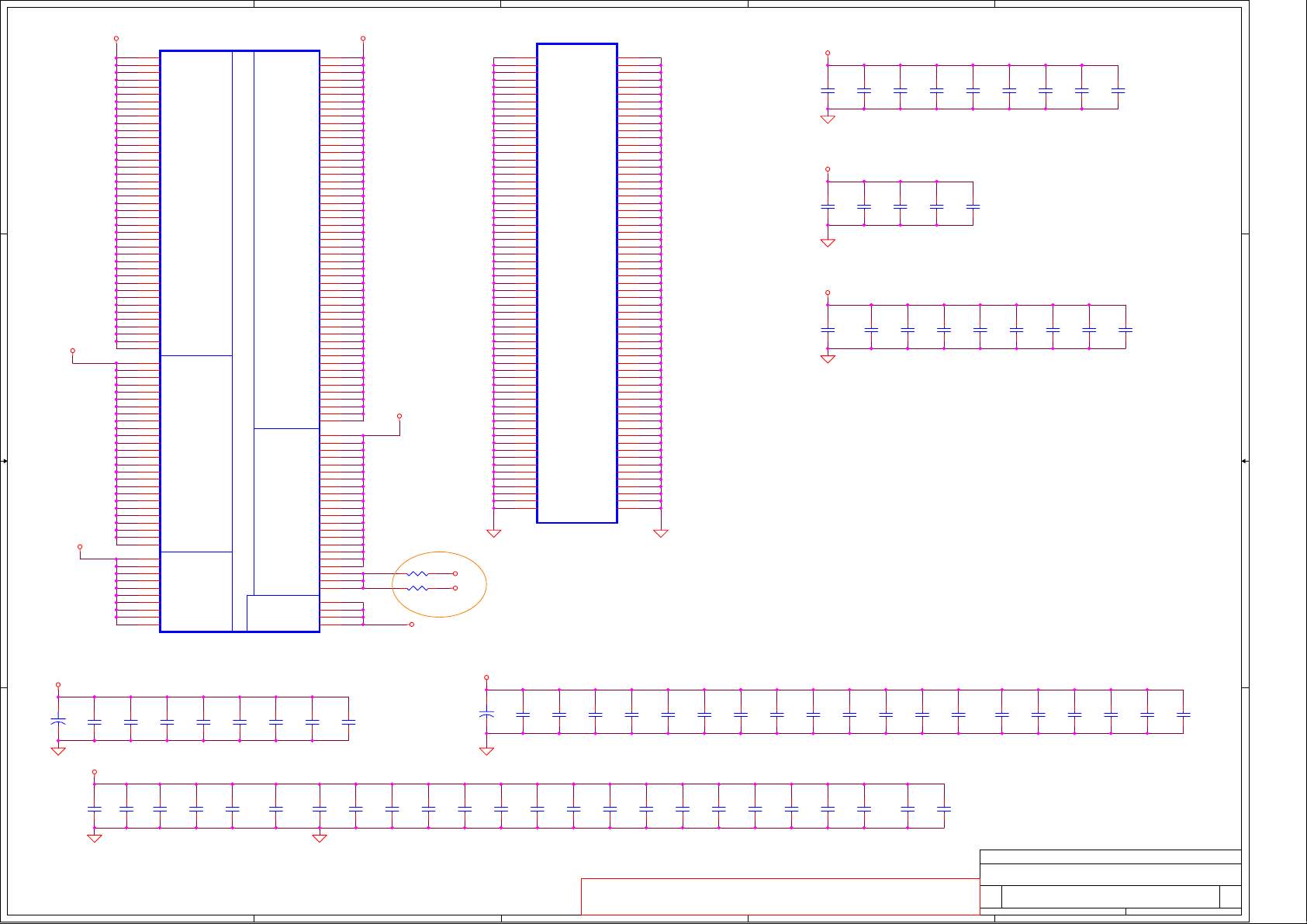

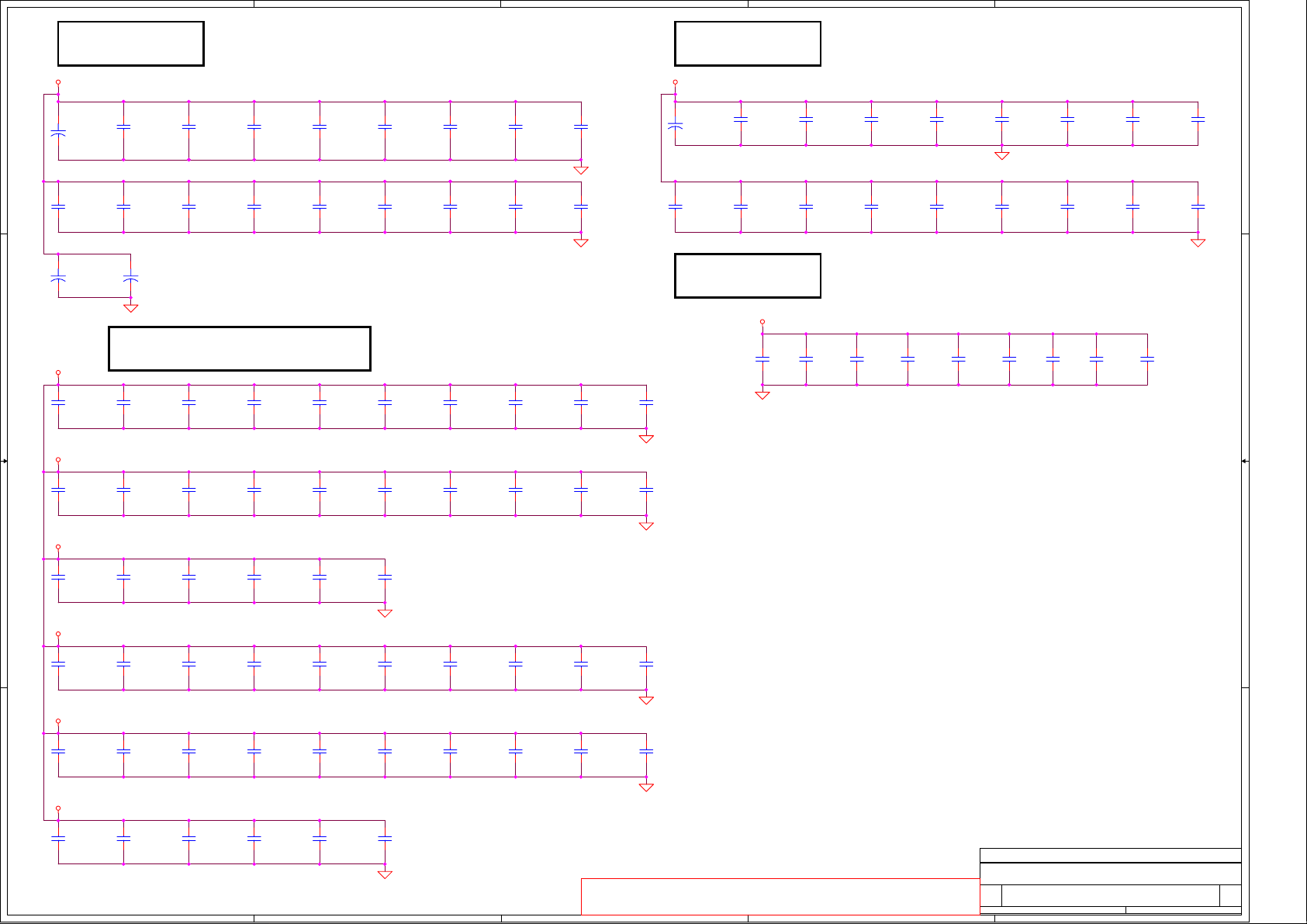

BLOCK DIAGRAM

Model Name : EFQ00 & EEQ00

File Name : LA-2371 Rev: 1.0

4 4

Northwood-MT

Prescott-MT

(uFCPGA-478)

LCD Conn 1

page 24

TV-OUT Conn.&CRT CONN.

W/EXT VGA CHIP

3 3

LCD Conn 2

page 24

page 23,24

ATI-M11P/M10C

page 17,18,19,20

W/INT VGA

533MHz(0.8V)

AGP 8X BUS

FSB

ATI-RC300ML

(ATI-RX300ML)

VGA M9 Embeded

868 pin u-BGA

VGA DDR x2 CHB

page 22 page 21

VGA DDR x2 CHA

A-Link

66MHz(3.3V)

PAGE 4,5,6

533MHz

PAGE 7,8,9,10, 11,12

Thermal Sensor

266/333MHz

(2.5V)

Memory Bus

480MHz(5V)

ADM1032

Clock Generator

ICS951402AGT

PAGE 5

SO-DIMM x2(DDR)

BANK 0,1,2,3

USB 2.0 Port *3

0, 1, 2

PAGE 39

PAGE 16

PAGE 13,14,15

CPU VID

PAGE 51

FAN Controller

RTC Battery

DC/DC Interface

LID/Kill Switch

Power Buttom&

LED & Hibernation

PAGE 24

PAGE 25

PAGE 43

PAGE 42

Primary

ATA-100 (5V)

Mini PCIx2

PAGE 32,33

24.576MHz(3.3V)

PAGE 41

C

Secondary

ATA-100 (5V)

AC-LINK

RJ-45

PAGE 29

2 2

Port 1

PAGE 34

Slot 0

PAGE 31

5IN1 Conn

PAGE 31

CB PWR SW

ENE CP2211

PAGE 31

1 1

A

LAN

RTL8100CL

PAGE 29

IEEE1394

VT6301S

PAGE 34

CARDBUS

ENE CB714/ENE CB1410

PAGE 30

33MHz (3.3V)

Super I/O

LPC47N217

REV B

Serial port

PAGE 39

PCI BUS

PAGE 39

B

ATI-IXP150

LPC BUS 33MHz (3.3V)

Scan KB

BGA 457 pin

PAGE 25,26,27,28

Embedded

Controller

ENE KB910

PAGE 40

PAGE 40

BIOS(1M)

& I/O PORT

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

IDE HDD

IDE ODD

AC97 CODEC

ALC 250

MDC

Connector

CIR Circuit

PAGE44

PAGE 39

PAGE 39

PAGE 35

PAGE 44

HW EQ CKT

Audio Amplifier

TPA6010A4

D

PAGE 37

PAGE 36

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

DCIN&DETECTOR

BATT CONN/OTP

CHARGER

3V/5V/12V

DDR_2.5V/1.25V

1.8V/VGA_CORE

CPU_CORE

Direct CD play BTN&TP CONN.

LA-2371

星期

, 27, 2004

二七月

PAGE 51,52,53

E

PAGE 45

PAGE 46

PAGE 47

PAGE 48

PAGE 49

PAGE 50

PAGE 41

1.0Custom

of

256

A

B

C

D

E

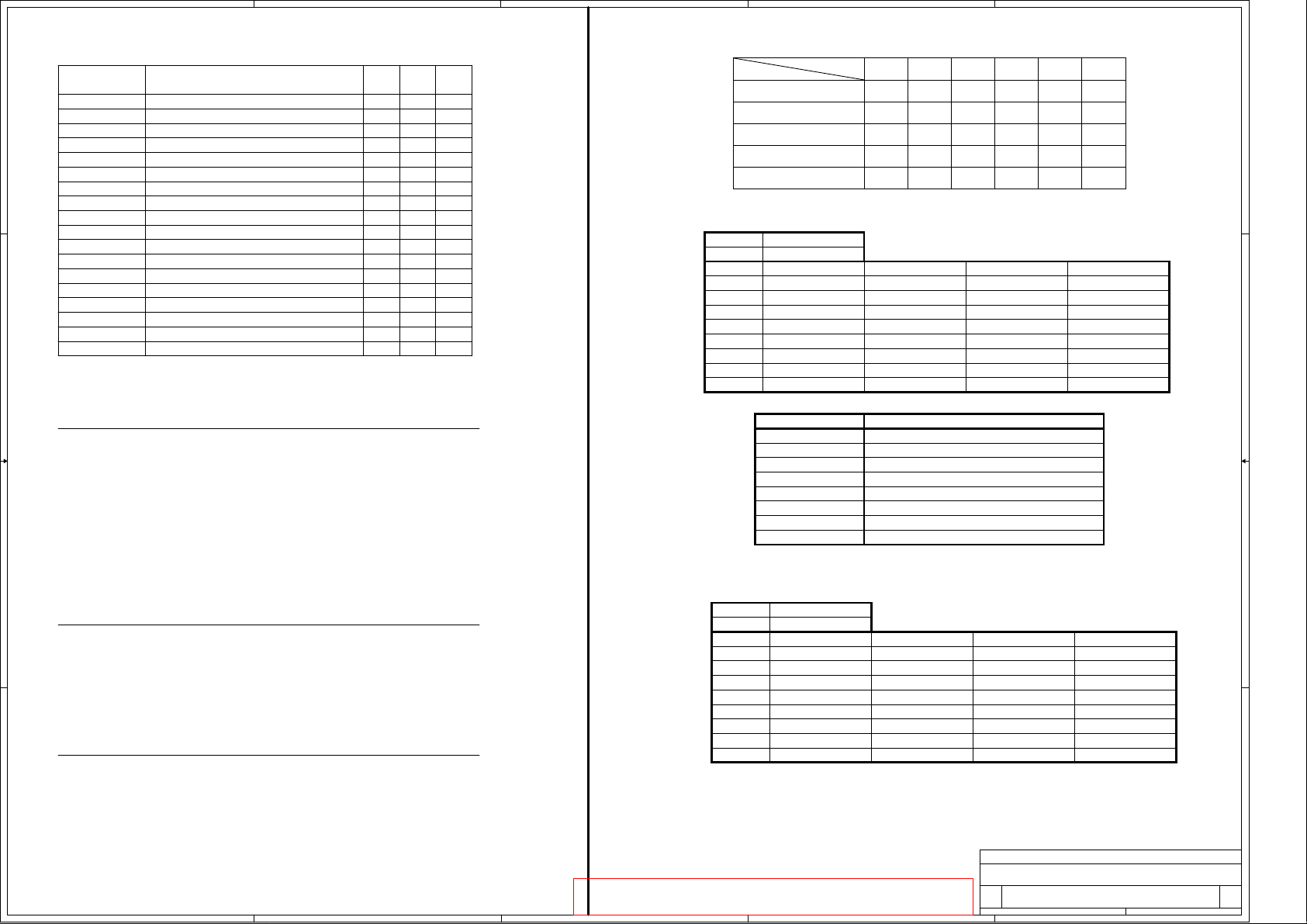

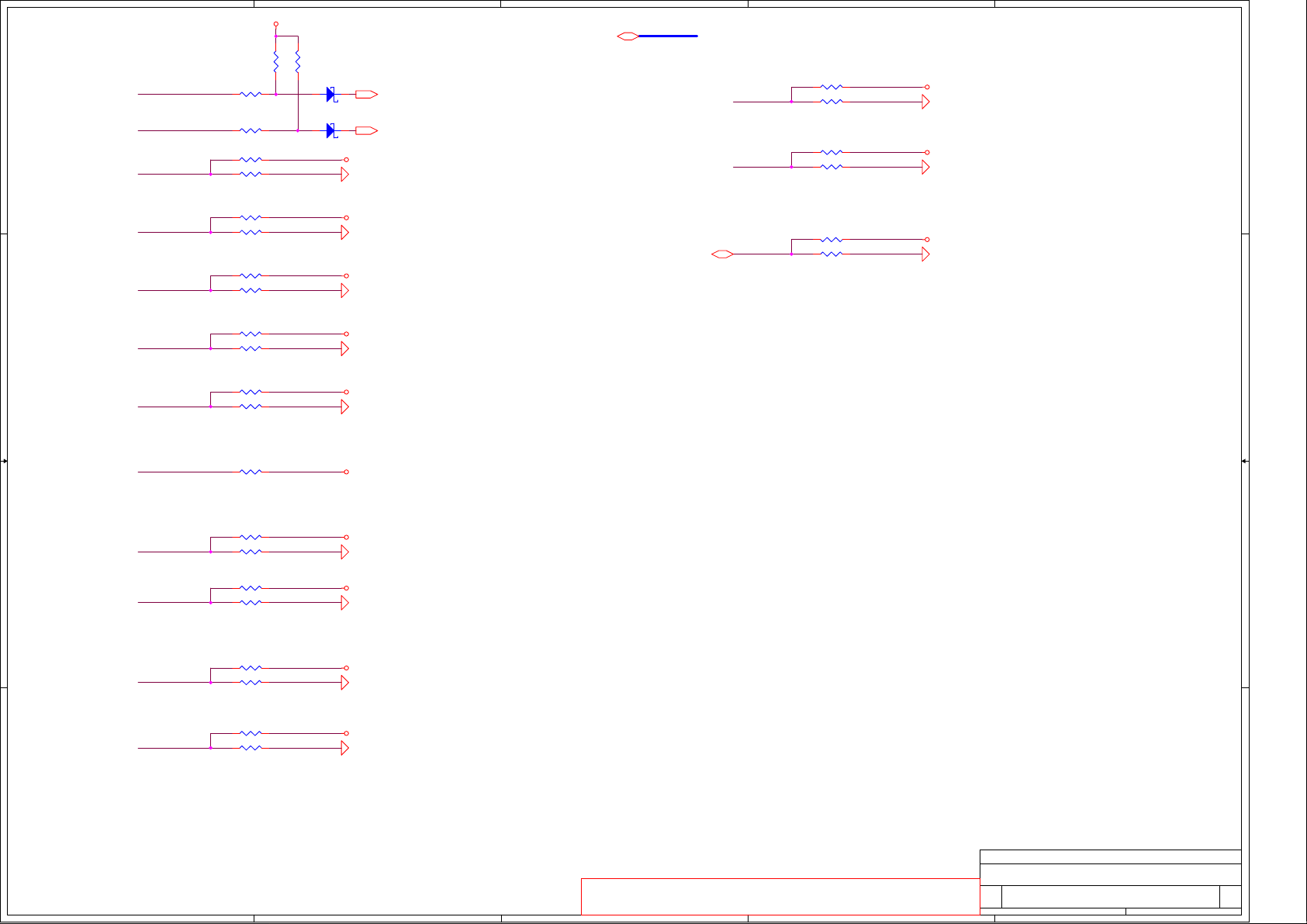

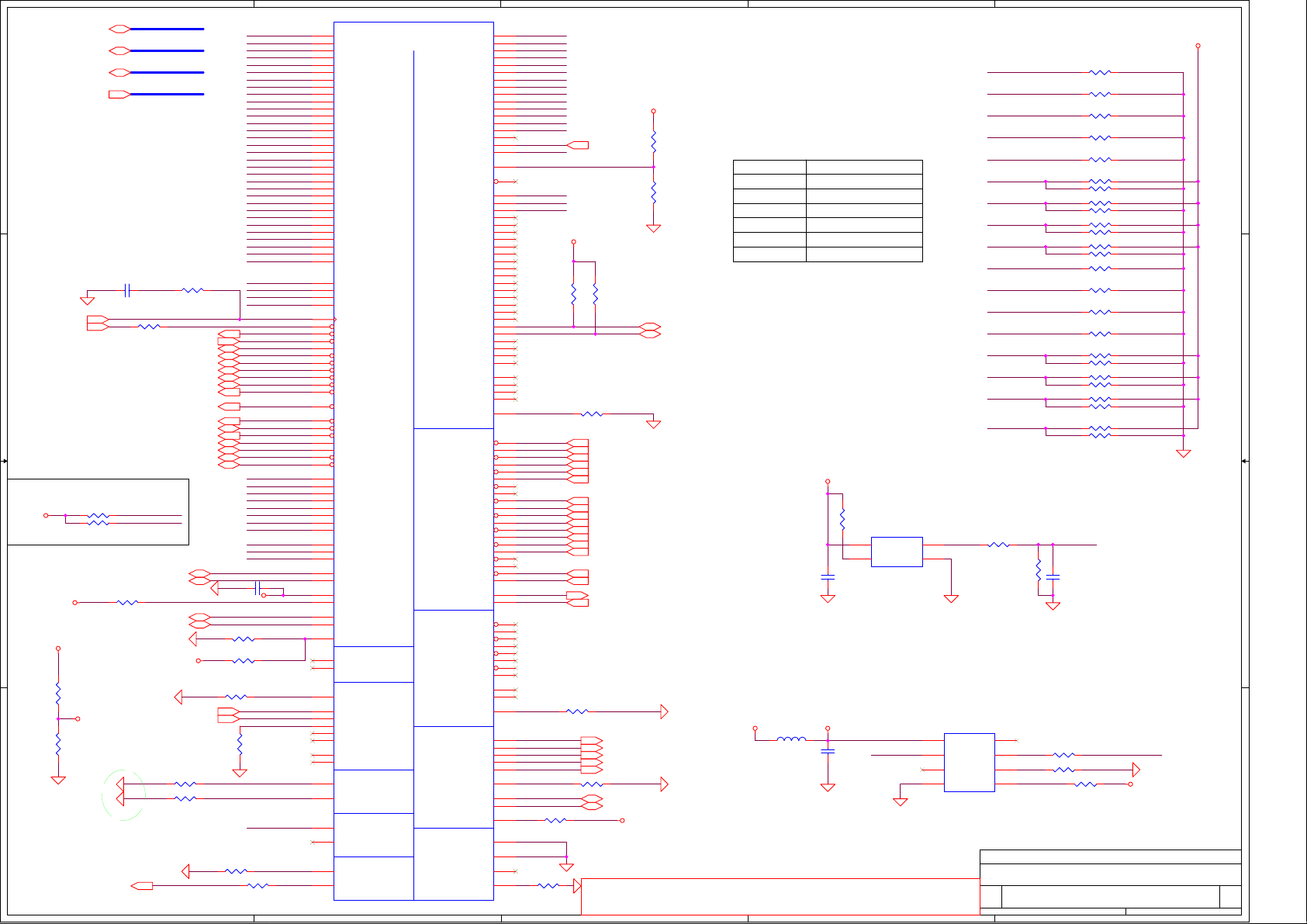

Voltage Rails

Power Plane Description

VIN

1 1

2 2

B+

+CPU_CORE

+CPUVID

+VGA_CORE ON OFF OF F1.0V/1.2V switched power rail for VGA chip

+1.25VS 1.25V switched power rail

+1.5VS

+1.8VS 1.8VS switched power rail OF FOFFON

+2.5VALW 2.5V always on power rail ON*ONON

+2.5V

+3VALW

+3V

+3VS

+5VS

+12VALW

+RTCVCC

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.2V switched power rail for CPU AGTL Bus

AGP 4X/8X

2.5V power rail

2.5V switched power rail+2.5VS

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

12V always on power rail

RTC power

S1 S3 S5

ON

ON ONONON

ON OFF

ON OFF

ON OFF OFF

ON OFF OFF

ON ON

ON

ON

ON

ON

ON+5VALW

ON

ON

ON

OFF

ON

OFF

ON

OFF

ON

ON

ON

OFF

OFF

OFF

OFF

ON*ON

OFF

OFF

ON*

OFF

ON*

ON

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Tabl e for AD channel

Vcc

Ra

Board ID

0

1

2

3

4

5

6

SIGNAL

3.3V +/- 5%

100K +/- 5%

Rb

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC7

Note : ON * m e a n s t h a t t hi s p ow e r pl a ne is ON only with AC power available, otherwise it is OFF.

External PCI Devices

Device IDSE L# REQ#/GNT # Interrupts

VGA

CardBus

LAN

Mini-PCI1

1394

5IN1

Mini-PCI2

AD16

AD20

AD19

AD18

AD16 0

AD20

AD22 4(for TV turner)

2

3PIRQD

1(for Wirele ss Lan)

2

PIRQA

PIRQA

PIRQC/PIRQD

PIRQA

PIRQB

PIRQC/PIRQD

Board ID

0

1

2

3

4

5

6

7

HIGH

LOW

LOW

AD_BID

0.436 V

0.712 V

1.036 V

1.935 V

2.500 V

SLP_S5#STATE

HIGHHIGH

HIGH

HIGH

HIGH

LOWLOW

minV

0 V

PCB Revision

+VALW

ON

ON

ON

ON

ON

0.1

+V

ON

ON

ON

OFF

OFF

AD_BID

0.503 V

0.819 V

1.650 V1.453 V

2.200 V

3.300 V

typV

0 V

+VSSL P _S3#

ON

OFF

OFF

OFF

Clock

ONON

LOW

OFF

OFF

OFF

V

AD_BID

0.289 V0.250 V0.216 V

0.538 V

0.875 V

1.264 V1.185 V

1.759 V

2.341 V

3.300 V

max

0 V

3 3

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

Address Address

1010 000X b

1011 000Xb

EC SM Bus2 address

Device

ADM1032

1001 110X b0001 011X b

IXP150 SM Bus address

Device

Clock Generator

4 4

(ICS951402AGT)

DDR DIMM0

DDR DIMM2

A

Address

1101 001Xb

1010 000Xb

1010 001Xb

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

C

SKU ID Table for AD channel

Vcc

Ra

Board ID

0

1

2

3

4

5

6

BIOS_ID: H EFW00

3.3V +/- 5%

100K +/- 5%

Rb

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

100K +/- 5%

200K +/- 5%

NC7

L EEW00

AD_BID

0.436 V

0.712 V

1.036 V

1.935 V

2.500 V

D

minV

0 V

max

AD_BID

typV

0 V

V

AD_BID

0 V

0.289 V0.250 V0.216 V

0.503 V

0.819 V

0.538 V

0.875 V

1.264 V1.185 V56K +/- 5%

Notes

1.759 V

2.341 V

3.300 V

E

of

356

1.650 V1.453 V

2.200 V

3.300 V

Compal Electronics, Inc.

Title

Size Document Number Rev

Custom

LA-2371

星期

, 27, 2004

Date: Sheet

二七月

1.0

5

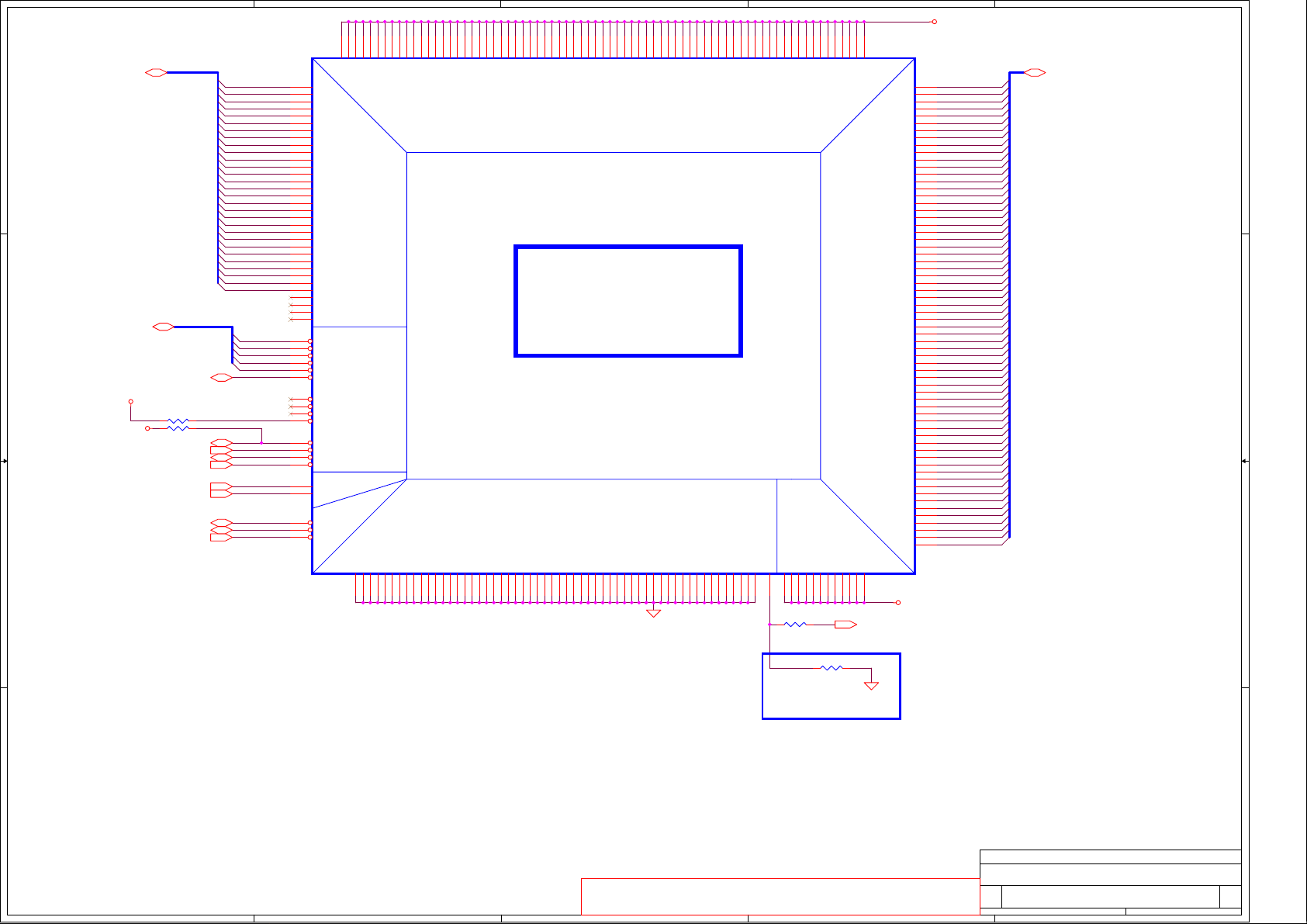

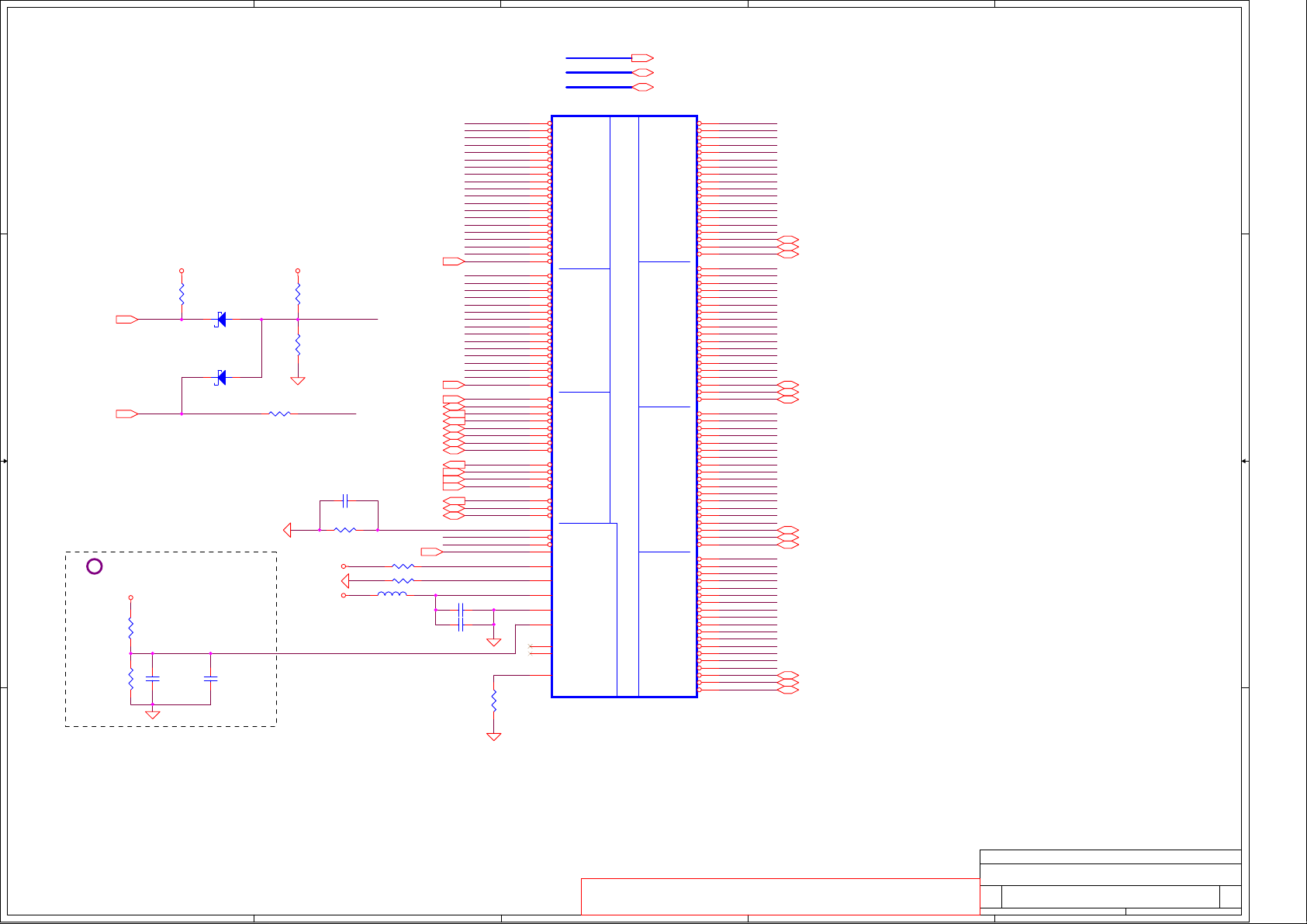

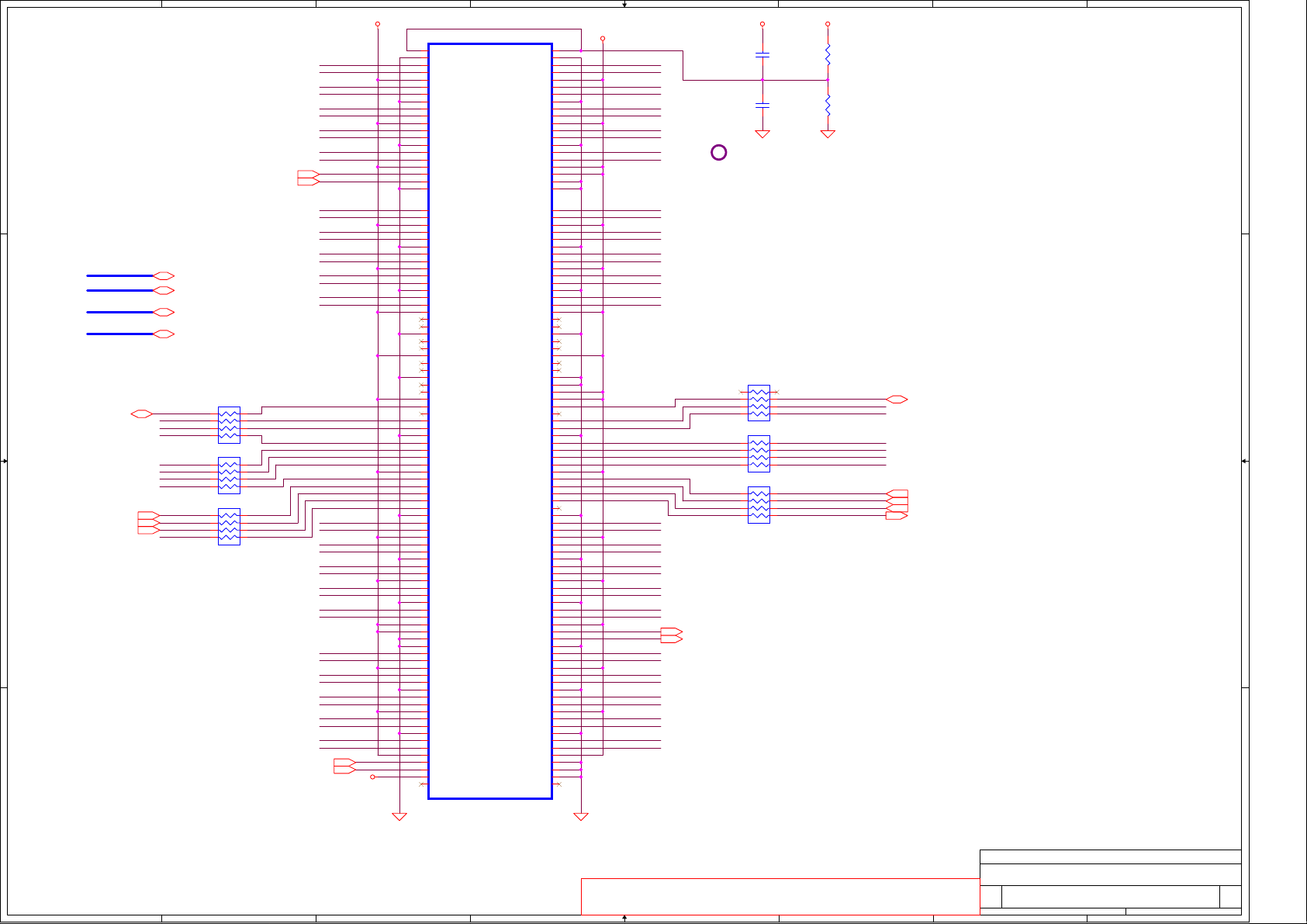

JCPU1A

H_A#[3..31]7

D D

H_REQ#[0..4]7

C C

+CPU_CORE

+CPU_CORE

B B

H_REQ#[0..4]

H_ADS#7

R559 51_0402_5%

1 2

1 2

R120 51_0402_5%

H_BR0#7

H_BPRI#7

H_BNR#7

H_LOCK#7

CLK_BCLK16

CLK_BCLK#16

H_HIT#7

H_HITM#7

H_DEFER#7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADS#

H_IERR#

CLK_BCLK

CLK_BCLK#

FOX_PZ47803-274A-42_Prescott

AF22

AF23

AB1

AC1

AA3

AC3

K2

K4

L6

K1

L3

M6

L2

M3

M4

N1

M1

N2

N4

N5

T1

R2

P3

P4

R3

T2

U1

P6

U3

T4

V2

R6

W1

T5

U4

V3

W2

Y1

J1

K5

J4

J3

H3

G1

V5

H6

D2

G2

G4

F3

E3

E2

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

A#32

A#33

A#34

A#35

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

AP#0

AP#1

BINIT#

IERR#

BR0#

BPRI#

BNR#

LOCK#

BCLK0

BCLK1

CON

HIT#

TROL

HITM#

DEFER#

4

A10

A12

A14

A16

A18

A20

AA10

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6A8VCC_7

HOST

ADDR

CONTROL

CLK

VSS_0H1VSS_1H4VSS_2

VSS_3

VSS_4

VSS_5

A11

A13

H23

H26

AA12

VCC_8

VSS_6

A15

AA14

VCC_9

VSS_7

A17

AA16

AA18

VCC_10

VSS_8

A19

A21

AA8

AB11

VCC_11

VCC_12

VSS_9

VSS_10

A24

A26

AB13

AB15

AB17

VCC_13

VCC_14

VCC_15

VSS_11

VSS_12A3VSS_13A9VSS_14

AA1

AB19

AB7

VCC_16

VCC_17

VSS_15

AA11

AA13

AB9

AC10

VCC_18

VCC_19

VSS_16

VSS_17

AA15

AA17

AC12

AC14

VCC_20

VCC_21

VSS_18

VSS_19

AA19

AA23

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

POWER

Northwood-MT

Prescott-MT

GND

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

AA4

AA7

AA26

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

3

AE6

AE8

VCC_38

VCC_39

VSS_36

VSS_37

AC13

AC15

AF11

AF13

VCC_40

VCC_41

VSS_38

VSS_39

AC17

AC19

AF15

AF17

VCC_42

VCC_43

VSS_40

VSS_41

AC2

AC22

AF19

AF2

VCC_44

VCC_45

VSS_42

VSS_43

AC5

AC25

AF21

AF5

VCC_46

VCC_47

VSS_44

VSS_45

AC7

AC9

AF7

AF9

VCC_48

VCC_49

VSS_46

VSS_47

AD10

AD12

B11

B13

VCC_50

VCC_51

VSS_48

VSS_49

AD14

AD16

B15

B17

VCC_52

VCC_53

VSS_50

VSS_51

AD18

AD21

B19

VCC_54

VCC_55

VSS_52

VSS_53

AD4

AD23

C10

C12

C14

VCC_56B7VCC_57B9VCC_58

VCC_59

BOOTSELECT

VSS_54

VSS_55

AD1

AD8

C16

C18

C20

VCC_61

VCC_62

VCC_63

POWER

VCC_81

VCC_82

F13

F15

F17

0_0402_5%

R_C

D11

D13

D15

D17

D19

VCC_64

VCC_65C8VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

HOST

ADDR

VCC_77

VCC_78

VCC_79

VCC_80

VCC_83

VCC_84

VCC_85

F9

E8

F11

F19

E18

E20

12

R542

1 2

R533

@0_0402_5%

@

Pop: Northwood

Depop: Prescott

2

D9

E10

VCC_71D7VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

E12

E14

E16

H_BOOTSELECT 51

B21

D#0

B22

D#1

A23

D#2

A25

D#3

C21

D#4

D22

D#5

B24

D#6

C23

D#7

C24

D#8

B25

D#9

G22

D#10

H21

D#11

C26

D#12

D23

D#13

J21

D#14

D25

D#15

H22

D#16

E24

D#17

G23

D#18

F23

D#19

F24

D#20

E25

D#21

F26

D#22

D26

D#23

L21

D#24

G26

D#25

H24

D#26

M21

D#27

L22

D#28

J24

D#29

K23

D#30

H25

D#31

M23

D#32

N22

D#33

P21

D#34

M24

D#35

N23

D#36

M26

D#37

N26

D#38

N25

D#39

R21

D#40

P24

D#41

R25

D#42

R24

D#43

T26

D#44

T25

D#45

T22

D#46

T23

D#47

U26

D#48

U24

D#49

U23

D#50

V25

D#51

U21

D#52

V22

D#53

V24

D#54

W26

D#55

Y26

D#56

W25

D#57

Y23

D#58

Y24

D#59

Y21

D#60

AA25

D#61

AA22

D#62

AA24

D#63

+CPU_CORE

+CPU_CORE

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

1

H_D#[0..63] 7

A A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

3

2

Prescott Processor in uFCPGA478 (1/2)

Size Document Number Rev

Custom

LA-2371

星期

, 28, 2004

Date: Sheet

三七月

1

of

456

1.0

5

+CPU_CORE

+CPU_VID

1

6

4

5

H_TRDY#7

H_A20M#25

H_FERR#25

H_IGNNE#25

H_SMI#25

H_PWRGOOD25

H_STPCLK#25

H_INTR25

H_NMI25

H_INIT#25

H_RESET#7

H_DBSY#7

H_DRDY#7

H_THERMTRIP#6

H_VCCA

H_VSSA

H_RS#[0..2]

BSEL012,16

BSEL112,16

1 2

R601

61.9_0603_1%

R508

12

R479

@10K_0402_5%

R481 56_0402_5%

R536 300_0402_5%

D D

R523 51_0402_5%

1 2

1 2

H_PWRGOOD

H_RESET#

H_THERMTRIP#

1 2

H_RS#[0..2]7

Place near CPU

JTAG PULL DOWN

RP1

1 8

2 7

3 6

4 5

1K_8P4R_1206_5%

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_TDI

Close to the CPU

+CPU_CORE

R562 51_0402_5%

1 2

R537 51_0402_5%

1 2

R551 51_0402_5%

1 2

R540 51_0402_5%

1 2

R558 51_0402_5%

1 2

R548 51_0402_5%

C C

Note: Please change to 10uH, DC current

of 100mA parts and close to cap

+CPU_CORE

L19 LQG21F4R7N00_0805

1 2

L18 LQG21F4R7N00_0805

1 2

C272

+

1 2

33U_D2_8M_R35

PLL Layout note :

1.Place cap within 600 mils of

the VCCA and VSSA pins.

2.H_VCCIOPLL,HVCCA,HVSSA trace wide

12 mils(min)

B B

R544 @100K_0402_0.5%

1 2

R565 @100K_0402_0.5%

1 2

Thermal Sensor

H_THERMDA

1

2200P_0402_50V7K

A A

C471

2

H_THERMDC

EC_SMB_CK235,40

EC_SMB_DA235,40

5

U36

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARM_RM8

1 2

VCCSENSE51

VSSSENSE51

Trace >= 25mils

Pop: Prescott

Depop: Northwood

CLK_ITP

CLK_ITP#

+3VS

1

C470

0.1U_0402_16V4Z

2

VDD1

ALERT#

THERM#

GND

4

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_A20M#

H_FERR#

H_IGNNE#

H_SMI#

H_PWRGOOD

H_STPCLK#

H_INTR

H_NMI

H_INIT#

H_RESET#

H_DBSY#

H_DRDY#

H_THERMDA

H_THERMDC

H_THERMTRIP#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TMS

ITP_TRST#

VCCVIDLB

0_0402_5%

1 2

1 2

FOX_PZ47803-274A-42_Prescott

CLK_ITP

CLK_ITP#

COMP0

COMP1

61.9_0603_1%

R518

AB23

AB25

AD20

AE23

AD22

AC26

AD26

F1

G5

F4

AB2

J6

C6

B6

B2

B5

Y4

D1

E5

W5

H5

H2

AD6

AD5

B3

C4

A2

AC6

AB5

AC4

Y6

AA5

AB4

D4

C1

D5

F7

E6

A5

A4

AF3

L24

P1

VID PWRGD Circuit

0.1U_0402_16V4Z

H_VID_PWRGD

SN74LVC125APWLE_TSSOP14

+3V POWER

4

JCPU1B

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCIOPLL

VCCA

VCCSENSE

VSSSENSE

VCCVIDLB

VSSA

ITP_CLK0

ITP_CLK1

COMP0

COMP1

1

C477

2

U40B

6

AE11

AE13

AE15

AE17

AE19

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

CON

TROL

LEGACY

MISC

THER

MAL

MISC

ITP

MISC

ITP

CLK

VSS_129F8VSS_130

VSS_131

VSS_132G3VSS_133G6VSS_134J2VSS_135

G21

G24

4

OE#

I5O

AE22

AE24

AE7

AE9

AF1

AF10

AF12

VSS_62

VSS_63

VSS_65

VSS_66

VSS_67

VSS_68

VSS_136

VSS_137J5VSS_138

VSS_139

J22

J25

K21

K24

+3V

12

R517

10K_0402_5%

1 2

R513 0_0402_5%

AF14

AF16

AF18

AF20

AF6

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_140K3VSS_141K6VSS_142L1VSS_143

VSS_144

L23

L26

AF8

B10

VSS_75

VSS_76

B12

VSS_77

VSS_78

B14

B16

VSS_79

VSS_80

B18

VSS_81

B20

VSS_82

3

B23

VSS_83

B26

VSS_84

VSS_85B4VSS_86B8VSS_87

C11

C13

VSS_88

C15

C17

VSS_89

C19

VSS_90

VSS_91

C22

C25

VSS_92C2VSS_93

VSS_94

D10

D12

VSS_95C5VSS_96C7VSS_97C9VSS_98

VSS_99

D14

D16

VSS_100

VSS_101

D18

D20

VSS_102

VSS_103

D21

D24

VSS_104

VSS_105

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

E11

E13

VSS_111

E15

E17

VSS_112

VSS_113

E19

E23

VSS_114

E26

VSS_115

VSS_116

VSS_117E4VSS_118E7VSS_119E9VSS_120

2

F10

GROUND

Northwood-MT

Prescott-MT

GROUND MISC

VID0

VID1

VID2

VID3

VSS_145L4VSS_146M2VSS_147

VSS_148

VSS_149M5VSS_150

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_156

VSS_157P5VSS_158R1VSS_159

VSS_160

VSS_161R4VSS_162

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

VSS_168

VSS_169U5VSS_170V1VSS_171

VSS_172

VSS_173V4VSS_174

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

VSS_180

VSS_181

T21

P22

P25

N21

N24

M22

M25

VID_PWRGD 51

ENLL 51

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONIC S, INC. AND CONTAI NS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

T24

R23

R26

GTL Reference Voltage

Layout note :

1. Place R_A and R_B near CPU (Within 1.5").

2. +CPU_GTLREF Trace wide 12mils(min),Space 15mils

+CPU_CORE

12

R158

R_A

100_0402_1%

12

R153

R_B

169_0402_1%

V23

V26

U22

U25

W21

CPU_VID051

CPU_VID151

CPU_VID251

CPU_VID351

CPU_VID451

CPU_VID551

+CPU_GTLREF

1

C207

1U_0603_10V4Z

2

Y5

Y22

Y25

W24

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

PM_STPCPU#25,51

VID4

VID5

AE5

AE4

AE3

AE2

AE1

AD3

2

F12

F14

F16

F18

VSS_121

VSS_122

VSS_123

VSS_124

VIDPWRGD

AD2

4.7K_0402_5%

R535

1 2

4.7K_0402_5%

AF26

F22

F25

F5

VSS_125F2VSS_126

VSS_127

VSS_128

SKTOCC#

REF

OPTIMIZED/COMPAT#

ITP

DATA

ADDR

DATA

MISC

VCCVID

AF4

Trace >= 25mils

1

C629

0.1U_0402_10V6K

2

H_VID_PWRGD

+3VS

R553

2

H_SKTOCC#

DP#0

DP#1

DP#2

DP#3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

PROCHOT#

MCERR#

SLP#

+CPU_VID

J26

K25

K26

L25

AA21

AA6

F20

F6

AE26

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

G25

P26

V21

AE25

C3

V6

AB26

A22

NC1

A7

NC2

AF25

NC3

AF24

NC4

AE21

NC5

RE

Pop: Prescott

Depop: Northwood

R570

@0_0402_5%

1 2

+CPU_GTLREF

H_TESTHI0

H_TESTHI1

H_TESTHI2_7

H_TESTHI8

H_TESTHI9

H_TESTHI10

H_GHI#

H_DPSLPR#

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_ADSTB#0

H_ADSTB#1

H_PROCHOT#

H_GHI#

220P_0402_50V7K

R567 @0_0402_5%@

1

1 2

R69 0_0402_5%

Place decoupling cap 220PF near CPU.

C226

1 2

R_G

1 2

R560 56_0402_5%

1 2

R550 56_0402_5%

1 2

R543 56_0402_5%

1 2

R526 56_0402_5%

1 2

R531 56_0402_5%

1 2

R564 56_0402_5%

1 2

R70 300_0402_5%

1 2

R557 56_0402_5%

H_DSTBP#[0..3]

R64130_0402_5%

12

1 2

H_PROCHOT# 26,50

H_SLP# 25

H_DSTBN#[0..3]

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

R_E

R600

680_0603_5%

1 2

12

H_DPSLPR#

Q55

2

MMBT3904_SOT23

3 1

Q54

MMBT3904_SOT23

3 1

Compal Electronics, Inc.

Title

Prescott Processor in uFCPGA478 (2/2)

Size Docume nt N u m b e r Re v

Custom

LA-2371

Date: Sheet

星期三

+CPU_VID

VID PULL HIGH

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

, 28, 2004

七月

1 2

R561 1K_0402_5%

1 2

R555 1K_0402_5%

RP44

1K_8P4R_1206_5%

1

CPU_GHI# 26

Pop: Northwood

Depop: Prescott

+CPU_CORE

H_DSTBN#[0..3] 7

H_DSTBP#[0..3] 7

H_ADSTB#0 7

H_ADSTB#1 7

+CPU_CORE

+3VS

45

36

27

18

556

of

1.0

5

4

3

2

1

+CPU_CORE

1

C146

D D

C C

22U_1206_10V4Z

2

+CPU_CORE

1

C478

2

10U_0805_10V4Z

+CPU_CORE

1

C225

22U_1206_10V4Z

2

+CPU_CORE

1

C187

22U_1206_10V4Z

2

1

C145

22U_1206_10V4Z

2

1

C488

2

10U_0805_10V4Z

1

C227

22U_1206_10V4Z

2

1

C55

22U_1206_10V4Z

2

1

C154

22U_1206_10V4Z

2

Place 8 Inside Socket For Prescott CPU(Stuff all)

1

C500

2

10U_0805_10V4Z

1

C224

22U_1206_10V4Z

2

1

C52

22U_1206_10V4Z

2

Place 11 North of Socket(Stuff 8)

1

C147

22U_1206_10V4Z

2

1

C531

2

10U_0805_10V4Z

1

C223

22U_1206_10V4Z

2

1

C148

22U_1206_10V4Z

2

1

C499

2

10U_0805_10V4Z

1

C208

22U_1206_10V4Z

2

C505

10U_0805_10V4Z

Place 9 South of Socket(Unstuff all)

1

C54

22U_1206_10V4Z

2

1

C53

22U_1206_10V4Z

2

1

C149

22U_1206_10V4Z

2

1

2

1

C198

22U_1206_10V4Z

2

1

C58

22U_1206_10V4Z

2

1

C188

22U_1206_10V4Z

2

1

C533

2

10U_0805_10V4Z

1

C57

22U_1206_10V4Z

2

1

C199

22U_1206_10V4Z

2

1

C479

2

10U_0805_10V4Z

Decoupling Reference Document:

Springdale Chipset Platform Design guide Rev1.11

(12474)page239

Decoupling Reference Requirement:

560uF Polymer, ESR:5m ohm(each) * 10

22uF X5R * 32

1

C209

22U_1206_10V4Z

2

22uF depop reference

Springdale Customer Schematic R1.2 page82

1

C56

22U_1206_10V4Z

2

1

C221

22U_1206_10V4Z

2

+CPU_CORE

B B

A A

1

+

C464

220U_6SVPC220MV_6.3VM_R15

2

+CPU_CORE

1

+

C641

220U_6SVPC220MV_6.3VM_R15

2

+CPU_CORE

1

+

C642

220U_6SVPC220MV_6.3VM_R15

2

+CPU_CORE

1

+

C639

220U_6SVPC220MV_6.3VM_R15

2

5

1

+

C463

220U_6SVPC220MV_6.3VM_R15

2

1

+

C467

220U_6SVPC220MV_6.3VM_R15

2

1

+

C637

220U_6SVPC220MV_6.3VM_R15

2

1

+

C468

220U_6SVPC220MV_6.3VM_R15

2

1

+

C466

220U_6SVPC220MV_6.3VM_R15

2

1

+

C640

220U_6SVPC220MV_6.3VM_R15

2

4

1

+

C465

220U_6SVPC220MV_6.3VM_R15

2

1

+

C636

220U_6SVPC220MV_6.3VM_R15

2

1

+

C638

220U_6SVPC220MV_6.3VM_R15

2

+CPU_CORE

MAINPWON45,46,48

Q50

MMBT3904_SOT23

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

3

2

3 1

2

C461

1

MMBT3904_SOT23

2

0.1U_0402_16V4Z

Q51

12

R475

470_0402_5%

R482

330_0402_5%

2

1 2

3 1

Title

Size Document Number Rev

Custom

Date: Sheet

H_THERMTRIP#

*01

CPU Decoupling

LA-2371

星期

, 28, 2004

三七月

H_THERMTRIP# 5

1

of

656

1.0

5

4

3

2

1

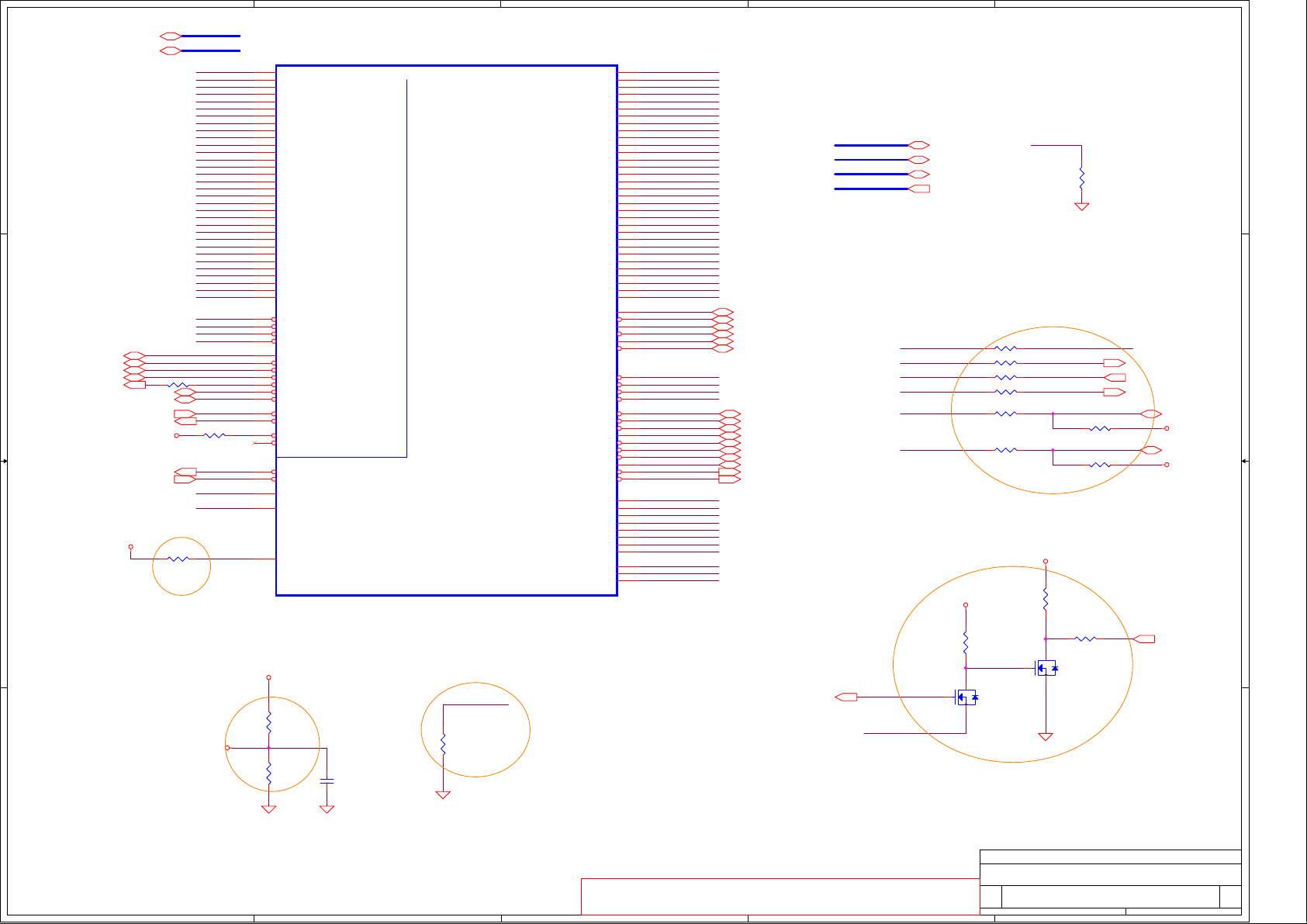

H_A#[3..31]

H_REQ#[0..4]

H_D#[0..63]

D D

+1.8VS+2.5V

R788

1 2

270K_0402_5%

12

R786

27K_0402_5%

NB_SUS_STAT#_A

12

R787

330K_0402_5%

NB_RST#_A

0.1U_0402_10V6K

1 2

330_0402_5%

+CPU_CORE

+1.8VS

C484

12

R503

HB-1M2012-121JT03_0805

**

12

R785

27K_0402_5%

D59

NB_SUS_STAT#26

C C

NB_RST#17,25,40

Note: PLAC E CL OS E T O RC300M,

L

B B

USE 10/10 WIDTH/SPACE

+CPU_CORE

R574

100_0402_1%

169_0402_1%

R576

1 2

12

1

C575

1U_0603_10V4Z

2

21

RB751V_SOD323

D60

21

RB751V_SOD323

1

C576

220P_0402_50V7K

2

H_ADSTB#05

H_ADSTB#15

H_ADS#4

H_BNR#4

H_BPRI#4

H_DEFER#4

H_DRDY#5

H_DBSY#5

H_BR0#4

H_LOCK#4

H_RESET#5

H_RS#25

H_RS#15

H_RS#05

H_TRDY#5

H_HIT#4

H_HITM#4

NB_PWRGD9,24,28

R188 24.9_0402_1%

1 2

R193 49.9_0402_1%

1 2

L44

1 2

@1U_0603_10V4Z

NB_GTLREF

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADSTB#1

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

H_LOCK#

H_RESET#

H_RS#2

H_RS#1

H_RS#0

H_TRDY#

H_HIT#

H_HITM#

NB_SUS_STAT#_A

NB_RST#_A

COMP_N

COMP_P

CPVDD

C532

CPVSS

1 2

1 2

C54310U_0805_10V4Z

12

R115

4.7K_0402_5%

U13A

M28

CPU_A3#

P25

CPU_A4#

M25

CPU_A5#

N29

CPU_A6#

N30

CPU_A7#

M26

CPU_A8#

N28

CPU_A9#

P29

CPU_A10#

P26

CPU_A11#

R29

CPU_A12#

P30

CPU_A13#

P28

CPU_A14#

N26

CPU_A15#

N27

CPU_A16#

M29

CPU_REQ0#

N25

CPU_REQ1#

R26

CPU_REQ2#

L28

CPU_REQ3#

L29

CPU_REQ4#

R27

CPU_ADSTB0#

U30

CPU_A17#

T30

CPU_A18#

R28

CPU_A19#

R25

CPU_A20#

U25

CPU_A21#

T28

CPU_A22#

V29

CPU_A23#

T26

CPU_A24#

U29

CPU_A25#

U26

CPU_A26#

V26

CPU_A27#

T25

CPU_A28#

V25

CPU_A29#

U27

CPU_A30#

U28

CPU_A31#

T29

CPU_ADSTB1#

L27

CPU_ADS#

K25

CPU_BNR#

H26

CPU_BPRI#

J27

CPU_DEFER#

L26

CPU_DRDY#

G27

CPU_DBSY#

F25

CPU_BR0#

K26

CPU_LOCK#

A17

CPU_CPURSET#

G25

CPU_RS2#

G26

CPU_RS1#

J25

CPU_RS0#

F26

CPU_TRDY#

J26

CPU_HIT#

H25

CPU_HITM#

A9

CPU_RSET

AH5

SUS_STAT#

AG5

SYSRESET#

C7

POWERGOOD

V28

CPU_COMP_N

W29

CPU_COMP_P

H23

CPVDD

J23

CPVSS

W28

CPU_VREF

Y29

THERMALDIODE_N

Y28

THERMALDIODE_P

B17

TESTMODE

CHS-216IGP9050A21_BGA718

PART 1 OF 6

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

CPU_DSTBN0#

CPU_DSTBP0#

ADDR. GROUP 1 ADDR. GROUP 0CONTROL

CPU_DSTBN1#

CPU_DSTBP1#

AGTL+ I/F

PENTIUM

CPU_DSTBN2#

CPU_DSTBP2#

MISC.

CPU_DSTBN3#

CPU_DSTBP3#

H_A#[3..31] 4

H_REQ#[0..4] 4

H_D#[0..63] 4

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

IV

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

L30

K29

J29

H28

K28

K30

H29

J28

F28

H30

E30

D29

G28

E29

D30

F29

E28

G30

G29

B26

C30

A27

B29

C28

C29

B28

D28

D26

B27

C26

E25

E26

A26

B25

C25

A28

D27

E27

F24

D24

E23

E24

F23

C24

B24

A24

F21

A23

B23

C22

B22

C21

E21

D22

D23

E22

F22

B21

F20

A21

C20

E20

D20

A20

D19

C18

B20

E18

B19

D18

B18

C17

A18

F19

E19

F18

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DINV#0

H_DSTBN#0

H_DSTBP#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DINV#1

H_DSTBN#1

H_DSTBP#1

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DINV#2

H_DSTBN#2

H_DSTBP#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DINV#3

H_DSTBN#3

H_DSTBP#3

H_DINV#0 5

H_DSTBN#0 5

H_DSTBP#0 5

H_DINV#1 5

H_DSTBN#1 5

H_DSTBP#1 5

H_DINV#2 5

H_DSTBN#2 5

H_DSTBP#2 5

H_DINV#3 5

H_DSTBN#3 5

H_DSTBP#3 5

A A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

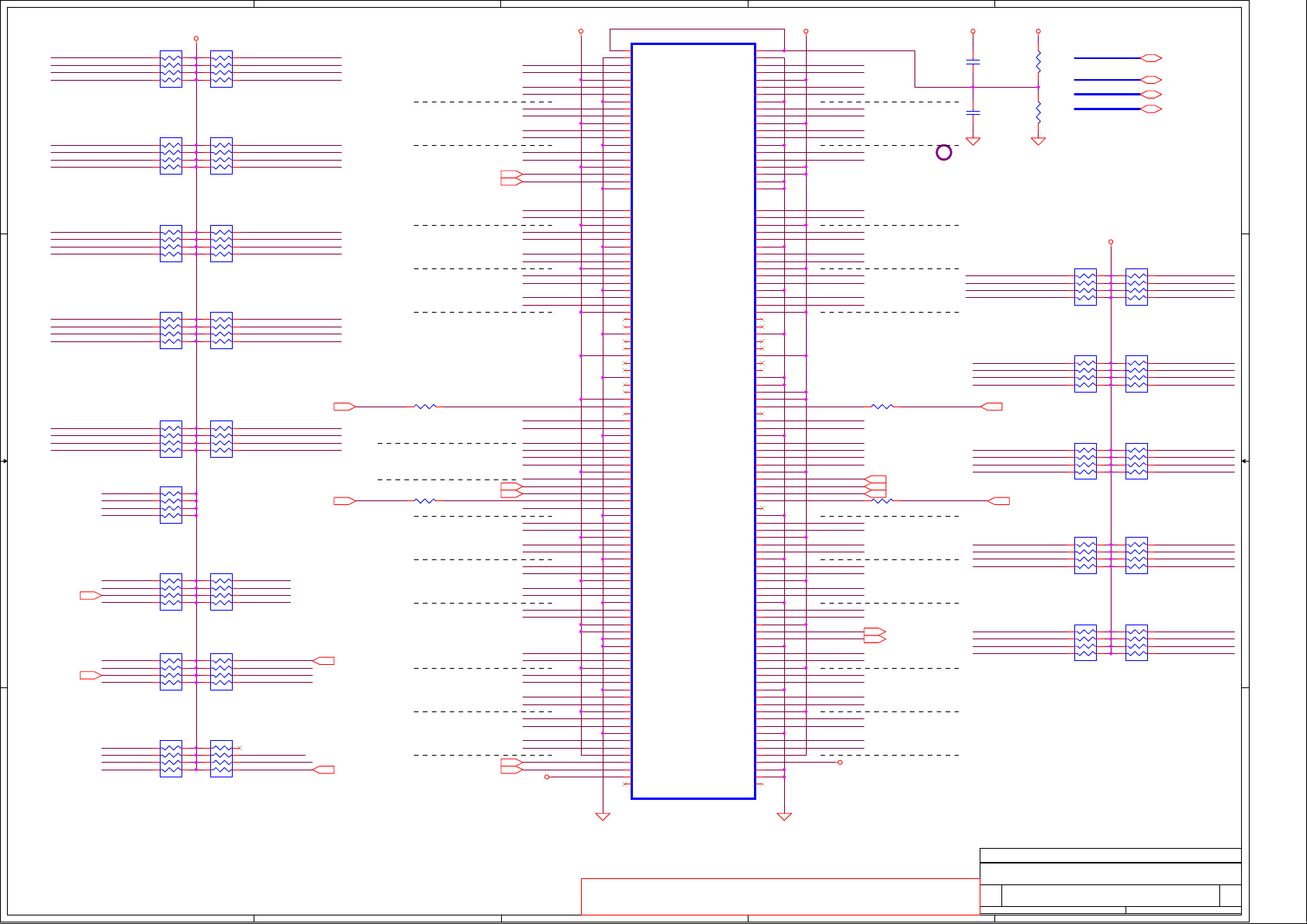

ATI RC300M-AGTL+

, 28, 2004

三七月

LA-2371

星期

1

1.0

of

756

5

D D

DDR_SBS013,14

DDR_SBS113,14

DDR_SRAS#13,14

DDR_SCAS#13,14

DDR_SWE#13,14

C C

DDR_CLK013

DDR_CLK0#13

DDR_CLK113

DDR_CLK1#13

DDR_CLK314

DDR_CLK3#14

DDR_CLK414

DDR_CLK4#14

DDR_SCKE013,14

DDR_SCKE113,14

DDR_SCKE214

DDR_SCKE314

DDR_SCS#013,14

DDR_SCS#113,14

B B

+1.8VS

DDR_SCS#214

DDR_SCS#314

L47

1 2

HB-1M2012-121JT03_0805

2.2U_0805_16V4Z

4

U13B

DDR_SMA0

DDR_SMA1

DDR_SMA2 DDR_DQ2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SMA13

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM7

DDR_SRAS#

DDR_SCAS#

DDR_SWE#

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5

DDR_DQS6

DDR_DQS7

DDR_CLK0

DDR_CLK0#

DDR_CLK1

DDR_CLK1#

DDR_CLK3

DDR_CLK3#

DDR_CLK4

DDR_CLK4#

DDR_SCKE0

DDR_SCKE1

DDR_SCKE2

DDR_SCKE3

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

MPVDD

C586

MPVSS

1 2

AH19

AJ17

AK17

AH16

AK16

AF17

AE18

AF16

AE17

AE16

AJ20

AG15

AF15

AE23

AH20

AE25

AH7

AF10

AJ14

AF21

AH23

AK28

AD29

AB26

AF24

AF25

AE24

AH13

AE21

AJ23

AJ27

AC28

AA25

AK10

AH10

AH18

AJ19

AG30

AG29

AK11

AJ11

AH17

AJ18

AF28

AG28

AF13

AE13

AG14

AF14

AH26

AH27

AF26

AG27

AC18

AD18

AJ8

AF9

PART 2 OF 6

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_A15

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEM_RAS#

MEM_CAS#

MEM_WE#

MEM_DQS0

MEM_DQS1

MEM_DQS2

MEM_DQS3

MEM_DQS4

MEM_DQS5

MEM_DQS6

MEM_DQS7

MEM_CK0

MEM_CK0#

MEM_CK1

MEM_CK1#

MEM_CK2

MEM_CK2#

MEM_CK3

MEM_CK3#

MEM_CK4

MEM_CK4#

MEM_CK5

MEM_CK5#

MEM_CKE0

MEM_CKE1

MEM_CKE2

MEM_CKE3

MEM_CS#0

MEM_CS#1

MEM_CS#2

MEM_CS#3

MPVDD

MPVSS

CHS-216IGP9050A21_BGA718

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM I/F

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_CAP1

MEM_CAP2

MEM_COMP

MEM_DDRVREF

AG6

AJ7

AJ9

AJ10

AJ6

AH6

AH8

AH9

AE7

AE8

AE12

AF12

AF7

AF8

AE11

AF11

AJ12

AH12

AH14

AH15

AH11

AJ13

AJ15

AJ16

AF18

AG20

AG21

AF22

AF19

AF20

AE22

AF23

AJ21

AJ22

AJ24

AK25

AH21

AH22

AH24

AJ25

AK26

AK27

AJ28

AH29

AH25

AJ26

AJ29

AH30

AF29

AE29

AB28

AA28

AE28

AD28

AC29

AB29

AC26

AB25

Y26

W26

AE26

AD26

AA26

Y27

C652 0.47U_0603_10V7K

AF6

C607 0.47U_0603_10V7K

AA29

AK19

AK20

3

DDR_DQ0

DDR_DQ1

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23DDR_DM6

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

DDR_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ44

DDR_DQ45

DDR_DQ46

DDR_DQ47

DDR_DQ48

DDR_DQ49

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ53

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ57

DDR_DQ58

DDR_DQ59

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ63

1 2

1 2

MEN_COMP

R606 49.9_0402_1%

1 2

DDR_DM[0..7]

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_SMA[0..13]

2

DDR_DM[0..7] 13,14

DDR_DQ[0..63] 13,14

DDR_DQS[0..7] 13,14

DDR_SMA[0..13] 13,14

1

+2.5V+2.5V

2

C643

0.1U_0402_10V6K

0.1U_0402_10V6K

A A

L

5

4

1

DDR_VREF

2

C650

1

DDR_VREF trace width of

20mils and space

20mils(min)

12

R609

1K_0402_1%

12

R610

1K_0402_1%

3

Title

Size Document Number Rev

2

Date: Sheet

Compal Electronics, Inc.

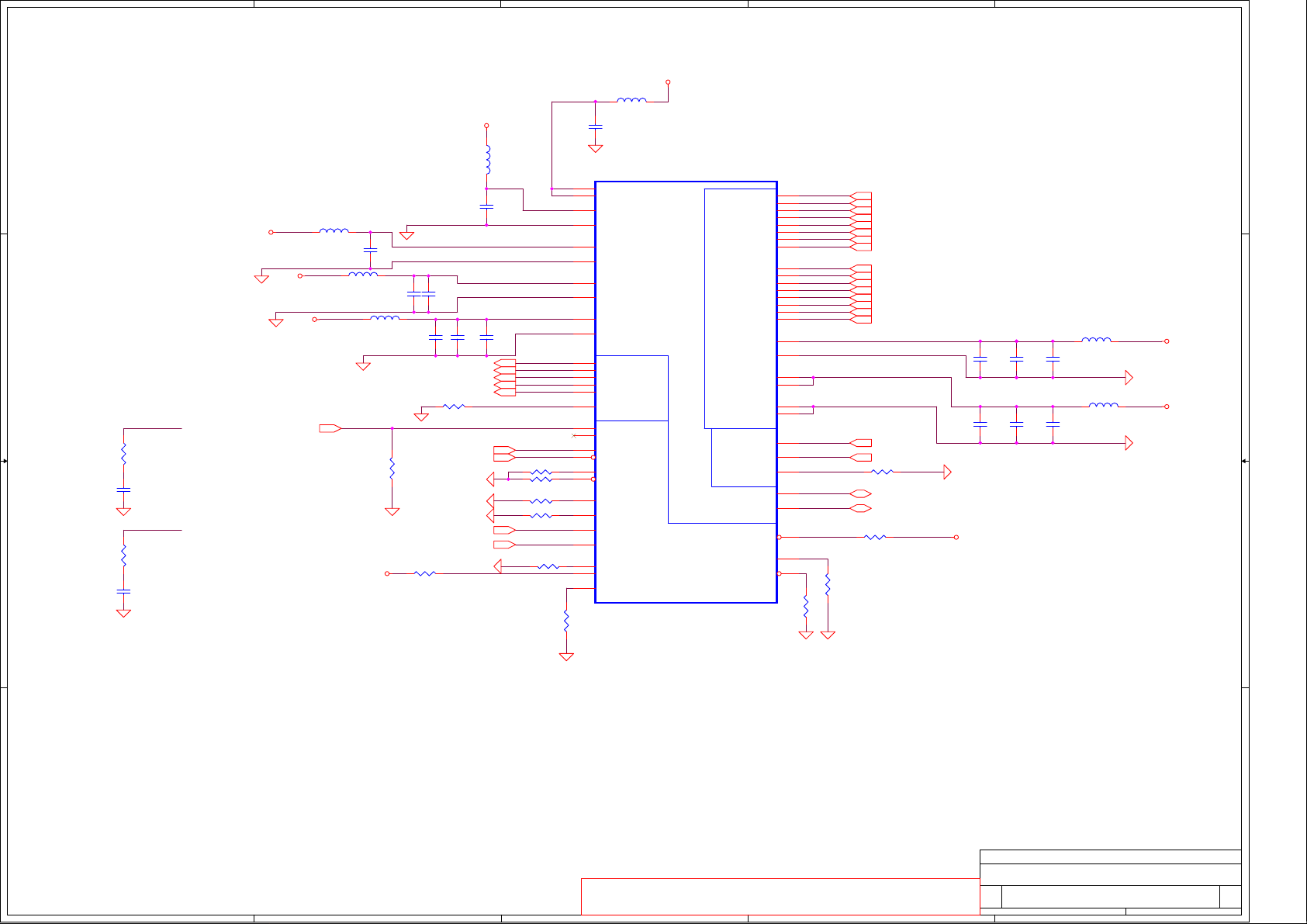

ATI RC300M-DDR I/F

, 28, 2004

三七月

LA-2371

星期

1

1.0

of

856

5

4

3

2

1

A_AD[0..31]12,25

A_CBE#[0..3]25

D D

C C

?

B B

A_PAR12,25

A_STROBE#25

A_ACAT#25

A_END#25

PCI_PIRQA#17,25,30,34

+1.5VS

A_DEVSEL#25

A_SBREQ#25

A_SBGNT#25

AGP_GNT#17

AGP_REQ#17

R532

POP For EFQ00

DEPOP For EEQ00

A A

5

A_AD[0..31]

A_CBE#[0..3]

A_AD0

A_AD1

A_AD2

A_AD3

A_AD4

A_AD5

A_AD6

A_AD7

A_AD8

A_AD9

A_AD10

A_AD11

A_AD12

A_AD13

A_AD14

A_AD15

A_AD16

A_AD17

A_AD18

A_AD19

A_AD20

A_AD21

A_AD22

A_AD23

A_AD24

A_AD25

A_AD26

A_AD27

A_AD28

A_AD29

A_AD30

A_AD31

A_CBE#0

A_CBE#1

A_CBE#2

A_CBE#3

A_PAR

A_STROBE#

A_ACAT#

1 2

1 2

169_0402_1%

+AGP_VREF

A_END#

A_DEVSEL#

A_OFF#

A_SBREQ#

A_SBGNT#

1 2

8.2K_0402_5%

AGP_GNT#

AGP_REQ#

AGP8X_DET#

AGPREF_8X

AGP_COMP

R573 0_0402_5%

A_OFF#25

+3VS

U13C

AK5

ALINK_AD0

AJ5

ALINK_AD1

AJ4

ALINK_AD2

AH4

ALINK_AD3

AJ3

ALINK_AD4

AJ2

ALINK_AD5

AH2

ALINK_AD6

AH1

ALINK_AD7

AG2

ALINK_AD8

AG1

ALINK_AD9

AG3

ALINK_AD10

AF3

ALINK_AD11

AF1

ALINK_AD12

AF2

ALINK_AD13

AF4

ALINK_AD14

AE3

ALINK_AD15

AE4

ALINK_AD16

AE5

ALINK_AD17

AE6

ALINK_AD18

AC2

ALINK_AD19

AC4

ALINK_AD20

AB3

ALINK_AD21

AB2

ALINK_AD22

AB5

ALINK_AD23

AB6

ALINK_AD24

AA2

ALINK_AD25

AA4

ALINK_AD26

AA5

ALINK_AD27

AA6

ALINK_AD28

Y3

ALINK_AD29

Y5

ALINK_AD30

Y6

ALINK_AD31

AG4

ALINK_CBE#0

AE2

ALINK_CBE#1

AC3

ALINK_CBE#2

AA3

ALINK_CBE#3

AD5

PCI_PAR/ALINK_NC

AC6

PCI_FRAME#/ALINK_STROBE#

AC5

PCI_IRDY#/ALINK_ACAT#

AD2

PCI_TRDY#/ALINK_END#

W4

INTA#

AD3

ALINK_DEVSEL#

AD6

PCI_STOP#/ALINK_OFF#

W5

ALINK_SBREQ#

W6

ALINK_SBGNT#

R192

V5

PCI_REQ#0/ALINK_NC

V6

PCI_GNT#0/ALINK_NC

K5

AGP2_GNT#/AGP3_GNT

K6

AGP2_REQ#/AGP3_REQ

M5

AGP8X_DET#

J6

AGP_VREF/TMDS_VREF

J5

AGP_COMP

CHS-216IGP9050A21_BGA718

+1.5VS

12

R539

@1K_0402_1%

AGPREF_8X

12

R549

@1K_0402_1%

POP For EEQ00

DEPOP For EFQ00

2

C526

0.1U_0402_10V6K

1

4

AGP_AD0

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD31

AGP_PAR

AGP_ST0

AGP_ST1

AGP_ST2

Y2

W3

W2

V3

V2

V1

U1

U3

T2

R2

P3

P2

N3

N2

M3

M2

L1

L2

K3

K2

J3

J2

J1

H3

F3

G2

F2

F1

E2

E1

D2

D1

E5

E6

T3

U2

AGP_AD_STBF1

G3

AGP_AD_STBS1

H2

R3

M1

L3

H1

P5

R6

T6

T5

P6

R5

C1

D3

N6

N5

C3

C2

D4

E4

F6

F5

G6

G5

L6

M6

L5

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_SB_STBF

AGP_SB_STBS

AGP_AD_STBF0

AGP_AD_STBS0

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_IRDY#

AGP_TRDY#

AGP_STOP#

AGP_PAR

AGP_FRAME#

AGP_DEVSEL#

AGP_DBI_HI

AGP_DBI_LO

AGP_RBF#

AGP_WBF#

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

PART 3 OF 6

AGP2_SBSTB/AGP3_SBSTBF/NC/LVDS_BLON

AGP2_SBSTB#/AGP3_SBSTBS/NC/ENA_BL

AGP2_ADSTB0/AGP3_ADSTBF0/TMD2_CLK#

AGP2_ADSTB0#/AGP3_ADSTBS0/TMD2_CLK

AGP2_ADSTB1/AGP3_ADSTBF1/TMD1_CLK#

AGP2_ADSTB1#/AGP3_ADSTBS1/TMD1_CLK

PCI Bus 0 / A-Link I/F

AGP2_IRDY#/AGP3_IRDY/GPIO8/I2C_CLK

AGP2_TRDY#/AGP3_TRDY/TMDS_DVI_CLK

AGP2_STOP#/AGP3_STOP/GPIO10/DDC_DATA

AGP2_FRAME#/AGP3_FRAME/TMDS_DVI_DATA

AGP2_DEVSEL#/AGP3_DEVSEL/GPIO9/I2C_DATA

PCI BUS 1 / AGP Bus (GPIO , TMDS , ZVPort)

AGP2_SBA0/AGP3_SBA#0/GPIO0/VDDC_CNTL0

AGP2_SBA1/AGP3_SBA#1/GPIO1/VDDC_CNTL1

AGP2_SBA2/AGP3_SBA#2/GPIO2/LVDS_BLON#

AGP2_SBA3/AGP3_SBA#3/GPIO3/LVDS_DIGON

AGP2_SBA4/AGP3_SBA#4/GPIO4/STP_AGP#

AGP2_SBA5/AGP3_SBA#5/GPIO5/AGP_BUSY#

AGP2_SBA6/AGP3_SBA#6/GPIO6/LVDS_SSOUT

AGP2_SBA7/AGP3_SBA#7/GPIO7/LVDS_SSIN

AGP8X_DET#

12

R554

0_0402_5%

AGP_AD0/TMD2_HSYNC

AGP_AD1/TMD2_VSYNC

AGP_AD2/TMD2_D1

AGP_AD3/TMD2_D0

AGP_AD4/TMD2_D3

AGP_AD5/TMD2_D2

AGP_AD6/TMD2_D5

AGP_AD7/TMD2_D4

AGP_AD8/TMD2_D6

AGP_AD9/TMD2_D9

AGP_AD10/TMD2_D8

AGP_AD11/TMD2_D11

AGP_AD12/TMD2_D10

AGP_AD16/TMD1_VSYNC

AGP_AD17/TMD1_HSYNC

AGP_AD18/TMD1_DE

AGP_AD19/TMD1_D0

AGP_AD20/TMD1_D1

AGP_AD21/TMD1_D2

AGP_AD22/TMD1_D3

AGP_AD23/TMD1_D4

AGP_AD24/TMD1_D7

AGP_AD25/TMD1_D6

AGP_AD26/TMD1_D9

AGP_AD27/TMD1_D8

AGP_AD28/TMD1_D11

AGP_AD29/TMD1_D10

AGP_AD30/TMDS_HPD

AGP2_CBE#0/AGP3_CBE0/TMD2_D7

AGP2_CBE#1/AGP3_CBE1/TMD2_DE

AGP2_CBE#2/AGP3_CBE2

AGP2_CBE#3/AGP3_CBE3/TMD1_D5

AGP2_PIPE#/AGP3_DBI_HI

AGP2_NC/AGP3_DBI_LO

AGP2_RBF#/AGP3_RBF

AGP2_WBF#/AGP3_WBF

POP For EFQ00

DEPOP For EEQ00

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

3

AGP_SB_STBF 17

AGP_SB_STBS 17

AGP_AD_STBF0 17

AGP_AD_STBS0 17

AGP_AD_STBF1 17

AGP_AD_STBS1 17

AGP_IRDY# 17

AGP_TRDY# 17

AGP_STOP# 17

AGP_PAR 17

AGP_FRAME# 17

AGP_DEVSEL# 17

AGP_DBI_HI 17

AGP_DBI_LO 17

AGP_RBF# 17

AGP_WBF# 17

AGP_AD[0..31]

AGP_SBA[0..7]

AGP_C/BE#[0..3]

AGP_ST[0..2]

AGP_AD[0..31] 17

AGP_SBA[0..7] 17

AGP_C/BE#[0..3] 17

AGP_ST[0..2] 17

AGP_PAR

R566

@10K_0402_5%

1 2

POP For EEQ00

DEPOP For EFQ00

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA1

AGP_SBA0

@10K_0402_5%

NB_PWRGD7,24,28

@2N7002_SOT23

ENBKL#

R515 @0_0402_5%

1 2

R520 @0_0402_5%

1 2

R521 @0_0402_5%

1 2

R524 @0_0402_5%

1 2

R139 @0_0402_5%

1 2

R511 @0_0402_5%

1 2

+3VS

R527

1 2

13

D

2

G

S

Q53

+3VS

2

G

1 2

R138 @2.2K_0402_5%

1 2

R509 @2.2K_0402_5%

R154

@10K_0402_5%

1 2

R157

1 2

@0_0402_5%

13

D

S

Q16

@2N7002_SOT23

ENBKL#

NB_EDID_DAT

NB_EDID_CLK

ENVDD 17,24

AGP_STP# 17,26

AGP_BUSY# 17,26

NB_EDID_DAT 24

+3VS

NB_EDID_CLK 24

+3VS

ENBKL 17,40

POP For EEQ00

DEPOP For EFQ00

Title

Size Document Number Rev

2

Date: Sheet

Compal Electronics, Inc.

ATI RC300M-AGP, ALINK BUS

, 28, 2004

三七月

LA-2371

1

星期

1.0

of

956

5

4

3

2

1

FBM-11-160808-700T_0603

+3VS_VDDR3

D D

KC FBM-L11-201209-221LMAT_0805

KC FBM-L11-201209-221LMAT_0805

L35

+1.8VS

C C

CLK_AGP_66M

12

R505

@10_0402_5%

1

C481

@15P_0402_50V8J

2

CLK_MEM

12

R506

B B

@10_0402_5%

1

C480

@15P_0402_50V8J

2

1 2

0.1U_0402_10V6K

L37

+1.8VS

+1.8VS

REFCLK1_NB16

1 2

KC FBM-L11-201209-221LMAT_0805

L42

KC FBM-L11-201209-221LMAT_0805

1

C489

2

0.1U_0402_10V6K

1 2

10U_0805_10V4Z

+3VS

1

1

C487

2

2

C528

0.1U_0402_10V6K

R108 715_0402_1%

R112

56_0402_5%

1 2

R117

10K_0402_5%

+2.5VS

L36

C486

0.1U_0402_10V6K

1

1

C515

2

2

NB_CRT_R23

NB_CRT_G23

NB_CRT_B23

CRT_HSYNC23

CRT_VSYNC23

1 2

CLK_NB_BCLK16

CLK_NB_BCLK#16

CLK_AGP_66M16

CLK_MEM16

12

12

1

C485

0.1U_0402_10V6K

2

+1.8VS_AVDDDI

+1.8VS_AVDDQ

1

C520

0.1U_0402_10V6K

2

@10K_0402_5%

1 2

1 2

1 2

1 2

+2.5VS_AVDD

PLLVDD_18

PLLVSS_18

CRT_HSYNC

CRT_VSYNC

CLK_NB_BCLK

CLK_NB_BCLK#

R101

R110@10K_0402_5%

R504@10K_0402_5%

R113@10K_0402_5%

CLK_AGP_66M

CLK_MEM

R492@10K_0402_5%

1 2

1 2

1

C608

0.1U_0402_10V6K

2

U13D

G9

VDDR3

H9

VDDR3

A14

AVDD_25

B13

AVSSN

B14

AVDDDI_18

C13

AVSSDI

A15

AVDDQ

B15

AVSSQ

H11

PLLVDD_18

G11

PLLVSS

F14

RED

F15

GREEN

E14

BLUE

C8

DACHSYNC

D9

DACVSYNC

C14

RSET

A4

XTALIN

B4

XTALOUT

A5

HCLKIN

B5

HCLKIN#

B6

SYS_FBCLKOUT

A6

SYS_FBCLKOUT#

D8

ALINK_CLK

B2

AGPCLKOUT

B3

AGPCLKIN

A3

EXT_MEM_CLK

D7

USBCLK

B7

REF27

C5

OSC

CHS-216IGP9050A21_BGA718

R493

@10K_0402_5%

1 2

+3VS

L46

PART 4 OF 6

CRT

CLK. GEN.

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXCLK_UN

TXCLK_UP

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXCLK_LN

TXCLK_LP

LPVDD_18

LVDS

LVDDR_18

LVDDR_18

COMP_B

SVID

DACSCL

DACSDA

CPUSTOP#

SYSCLK

SYSCLK#

@10K_0402_5%

LPVSS

LVSSR

LVSSR

C_R

Y_G

D12

E12

F11

F12

D13

D14

E13

F13

E10

D10

B9

C9

D11

E11

B10

C10

A12

A11

B12

C12

B11

C11

TV_CRMA

E15

TV_LUMA

C15

TV_COMPS

D15

3VDDCCL

D6

3VDDCDA

C6

D5

R498 1K_0402_5%

A8

B8

R102

1 2

1 2

TXB0-_NB 24

TXB0+_NB 24

TXB1-_NB 24

TXB1+_NB 24

TXB2-_NB 24

TXB2+_NB 24

TXBCLK-_NB 24

TXBCLK+_NB 24

TXA0-_NB 24

TXA0+_NB 24

TXA1-_NB 24

TXA1+_NB 24

TXA2-_NB 24

TXA2+_NB 24

TXACLK-_NB 24

TXACLK+_NB 24

+1.8VS_LPVDD

+1.8VS_LVDDR

TV_CRMA 24

TV_LUMA 24

1 2

R501 75_0402_5%

3VDDCCL 23

3VDDCDA 23

1 2

R111

@10K_0402_5%

1

C492

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C493

2

0.1U_0402_10V6K

+3VS

KC FBM-L11-201209-221LMAT_0805

0.1U_0402_10V6K

1

C483

C496

2

10U_0805_10V4Z

KC FBM-L11-201209-221LMAT_0805

1

C501

C134

2

10U_0805_10V4Z

1

2

1

2

1 2

L38

1 2

L12

+1.8VS

+1.8VS

A A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

ATI RC300M-AGP, ALINK BUS

, 28, 2004

三七月

LA-2371

1

星期

of

10 56

1.0

5

4

3

2

1

+1.5VS +2.5V

U13E

F10

VDD_CORE

F9

VDD_CORE

G12

VDD_CORE

H12

VDD_CORE

H13

VDD_CORE

M12

VDD_CORE

M13

VDD_CORE

M14

VDD_CORE

M17

VDD_CORE

D D

+1.5VS

C953

220U_D2_4VM

+CPU_CORE

+3VS

1

+

C539

2

0.1U_0402_10V6K

+1.5VS

C541

0.1U_0402_10V6K

1

2

1

2

C C

B B

A A

M18

M19

N12

N13

N14

N17

N18

N19

P12

P13

P14

P17

P18

P19

U12

U13

U14

U17

U18

U19

V12

V13

V14

V17

V18

V19

W12

W13

W14

W17

W18

W19

C16

D16

D17

E16

E17

F16

F17

G17

G21

G23

G24

H16

H17

H19

H21

H24

K23

K24

M23

P23

P24

T23

T24

U23

U24

W30

AA1

AA7

AA8

AC7

AC8

AD1

AD7

AD8

AK3

0.1U_0402_10V6K

1

C563

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C508

C562

2

0.1U_0402_10V6K

5

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDR2_CPU

VDDL_ALINK

VDDL_ALINK

VDDL_ALINK

VDDL_ALINK

VDDL_ALINK

VDDL_ALINK

VDDL_ALINK

VDDL_ALINK

VDDL_ALINK

W8

VDDL_ALINK

CHS-216IGP9050A21_BGA718

0.1U_0402_10V6K

1

2

1

2

1

C566

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C569

2

0.1U_0402_10V6K

C577

CORE PWR

CPU I/F PWRALINK PWR

C552

PART 5 OF 6

POWER

VDDP_AGP/VDDP33

VDDP_AGP/VDDP33

VDDP_AGP/VDDP33

0.1U_0402_10V6K

1

C559

2

1

C548

2

0.1U_0402_10V6K

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

MEM I/F PWR

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

AGP PWR

1

2

0.1U_0402_10V6K

1

2

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDDP_AGP

VDD_18

VDD_18

VDD_18

VDD_18

C534

C570

C547

AA23

AA27

AB30

AC10

AC12

AC13

AC15

AC17

AC19

AC21

AC23

AC24

AC25

AC27

AD10

AD12

AD13

AD15

AD17

AD19

AD21

AD23

AD24

AD25

AD27

AE10

AE14

AE15

AE19

AE20

AE30

AE9

AF27

AG11

AG12

AG17

AG18

AG23

AG24

AG26

AG8

AG9

AJ30

AK14

AK23

AK8

V23

W23

W24

W25

Y25

A2

G4

H5

H6

H7

J4

K8

L4

M7

M8

N4

P1

P7

P8

R4

T8

U4

U5

U6

E7

F7

G8

AC22

AC9

H10

H22

0.1U_0402_10V6K

1

1

2

2

0.1U_0402_10V6K

1

C524

2

0.1U_0402_10V6K

+1.5VS

R547for EFQ00

C540

0.1U_0402_10V6K

1

C538

2

4

R547 0_0603_5%

1 2

1 2

R563 @0_0603_5%

+1.5VS

+3VS

+1.8VS

R563 For EEQ00

150U_D2_6.3VM

0.1U_0402_10V6K

1

1

C549

C516

2

2

0.1U_0402_10V6K

+2.5V

1

+

C658

2

1

C517

2

0.1U_0402_10V6K

A29

AB23

AB24

AB27

AB4

AB8

AC1

AC11

AC14

AC16

AC20

AC30

AD11

AD14

AD16

AD20

AD4

AE27

AF30

AF5

AG10

AG13

AG16

AG19

AG22

AG25

AG7

AH28

AH3

AJ1

AK13

AK2

AK22

AK29

AK4

AK7

B1

B16

B30

C19

C23

C27

C4

D21

D25

E3

E8

E9

F27

F4

F8

G14

G15

G18

G20

H14

H15

H18

H20

H27

H4

H8

J7

0.1U_0402_10V6K

1

C627

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C550

2

U13F

PART 6 OF 6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CHS-216IGP9050A21_BGA718

C626

1

C557

2

0.1U_0402_10V6K

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

0.1U_0402_10V6K

1

1

2

C623

C609

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C565

2

2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

R23

R7

R8

T12

T13

T14

T15

T16

T17

T18

T19

T27

T4

U15

U16

U7

U8

V15

V16

V27

V4

V7

V8

W15

W16

W27

Y1

Y23

Y24

Y30

Y4

Y7

Y8

R19

R18

R17

R16

R15

R14

R13

R12

R1

P4

P27

P16

P15

N8

N24

N23

N16

N15

M4

M27

M16

M15

L8

L7

L25

L24

L23

K4

K27

J8

1

C648

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C555

C561

2

0.1U_0402_10V6K

3

0.1U_0402_10V6K

1

C646

2

1

C556

2

0.1U_0402_10V6K

1

C602

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C536

2

22U_1206_10V4Z

10U_0805_10V4Z

10U_0805_10V4Z

0.1U_0402_10V6K

1

C645

2

1

C579

2

0.1U_0402_10V6K

C222

C581

C573

1

C625

2

0.1U_0402_10V6K

1

C512

2

+CPU_CORE

1

C529

2

0.1U_0402_10V6K

+1.8VS

1

C590

2

0.1U_0402_10V6K

+3VS

1

C603

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

1

C591

2

2

0.1U_0402_10V6K

0.01U_0402_25V4Z

1

2

0.01U_0402_25V4Z

0.1U_0402_10V6K

1

C522

2

0.1U_0402_10V6K

1

C523

2

0.1U_0402_10V6K

1

C647

2

0.1U_0402_10V6K

1

C624

2

1

C560

2

4.7U_0805_10V4Z

2

1

C551

2

0.1U_0402_10V6K

1

C521

2

0.1U_0402_10V6K

1

C592

2

0.1U_0402_10V6K

1

C631

2

1

C568

2

0.1U_0402_10V6K

1

C519

2

1

2

0.1U_0402_10V6K

1

C580

2

1

C601

0.1U_0402_10V6K

2

1

C585

2

4.7U_0805_10V4Z

0.1U_0402_10V6K

1

1

C564

C509

2

2

0.1U_0402_10V6K

1

C593

0.1U_0402_10V6K

2

0.1U_0402_10V6K

1

1

C571

C582

2

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C611

C587

2

0.1U_0402_10V6K

Title

Size Document Number Rev

星期

Date: Sheet

二七月

1

1

C514

2

0.1U_0402_10V6K

1

C606

2

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C595

2

2

0.1U_0402_10V6K

1

2

1

1

C596

2

2

0.1U_0402_10V6K

1

2

0.1U_0402_10V6K

Compal Electronics, Inc.

ATI RC300M-POWER

LA-2371

, 27, 2004

1

C535

0.1U_0402_10V6K

1

C594

2

C574

1

1

2

2

0.1U_0402_10V6K

of

11 56

C589

1.0

5

A_AD31

D D

C C

B B

A_AD30

A_AD29

A_AD28

A_AD27

A_AD26

A_AD25

A_AD24

A_AD23

A_AD22

A_AD21

A_AD20

R197 10K_0402_5%

R191 @4.7K_0402_5%

R198 @10K_0402_5%

R206 4.7K_0402_5%

R216 10K_0402_5%

R212 @4.7K_0402_5%

R230 10K_0402_5%

R224 @4.7K_0402_5%

R210 10K_0402_5%

R203 @4.7K_0402_5%

R244 10K_0402_5%

R231 10K_0402_5%

R238 @4.7K_0402_5%

R223 10K_0402_5%

R215 @4.7K_0402_5%

R226 10K_0402_5%

R234 @4.7K_0402_5%

R237 @4.7K_0402_5%

R243 4.7K_0402_5%

R201

10K_0402_5%

R202

1 2

R208

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

+3VS

1 2

1 2

4.7K_0402_5%

4.7K_0402_5%

R209

10K_0402_5%

D18

2 1

CH751H-40_SC76

D19

2 1

CH751H-40_SC76

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

4

BSEL1 5,16

BSEL0 5,16

A_AD[31..30] : FSB CLK SPEED

DEFAULT: 01

00: 100 MHZ

01: 133 MHZ

10: 200MHZ

11:166 MHZ

A_AD29: STRAP CONFIGURATION

DEFAULT:1

0: REDUCEDE SET

1: FULL SET

A_AD28: SPR EAD SPECTRUM ENABLE

DEFAULT:0

0: DISABLE

1: ENABLE

A_AD27: FrcShortReset#

DEFAULT: 1

0: TEST MODE

1: NORMAL MODE

A_AD26 : ENABLE IOQ

DEFAULT: 1

0: IOQ=1

1: IOQ=12

A_AD25/A_AD17 : CPU VOLTAGE[1..0]

DEFAULT: 10

00: 1.05V

01: 1.35V

11: 1.75V

10: 1.45V

AD25=1 DESTOP CPU

AD25=0 MOBILE CPU

AD17--DON'T CARE

A_AD24 : MOBILE CPU SELECT

DEFAULT: 1

0: BANIAS CPU

1: OTHER CPU

A_AD23 : CLOCK BYPASS DISABLE

DEFAULT: 1

0: TEST MODE

1: NORMAL

A_AD22 : OSC PAD OUTPUT PCICLK

DEFAULT : 1

0: PCICLK OUT

1: OSC CLK OUT

A_AD21 : AUTO_CAL ENABLE

DEFAULT : 1

0: DISABLE

1: ENABLE

A_AD20 : INTERNAL CLK GEN ENABLE

DEFAULT : 0

0: DISABLE

1: ENABLE

3

A_AD[0..31]9,25

A_AD[0..31]

R264 @4.7K_0402_5%

A_AD18

A_AD17

A_PAR9,25

A_PAR

1 2

1 2

R261 4.7K_0402_5%

R257 @4.7K_0402_5%

1 2

1 2

R252 4.7K_0402_5%

R258

1 2

R251

1 2

2

4.7K_0402_5%

@4.7K_0402_5%

+3VS

+3VS

+3VS

1

A_AD18 : ENABLE PHASE CALIBRATION

DEFAULT: 0

0: DISABLE

1:ENABLE

A_AD25/A_AD17 : CPU VOLTAGE[1..0]

DEFAULT: 0

00: 1.05V

01: 1.35V

11: 1.75V

10: 1.45V

PAR: EXTE N DED DE BUG MODE

DEFAULT : 1

0: DEBUG MODE

1: NORMAL

A A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

ATI RC300M-SYSTEM STRAP

, 28, 2004

三七月

LA-2371

星期

1.0

of

12 56

1

A

1 1

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DM[0..7]

DDR_SMA[0..13]

2 2

DDR_SCKE18,14

DDR_SBS08,14

DDR_SWE#8,14

DDR_SCS#08,14

3 3

4 4

DDR_DQ[0..63] 8,14

DDR_DQS[0..7] 8,14

DDR_DM[0..7] 8,14

DDR_SMA[0..13] 8,14

10_0804_8P4R_5%

DDR_SCKE1

DDR_SMA12

DDR_SMA9

DDR_SMA7

10_0804_8P4R_5%

DDR_SMA5

DDR_SMA3

DDR_SMA1

DDR_SMA10

10_0804_8P4R_5%