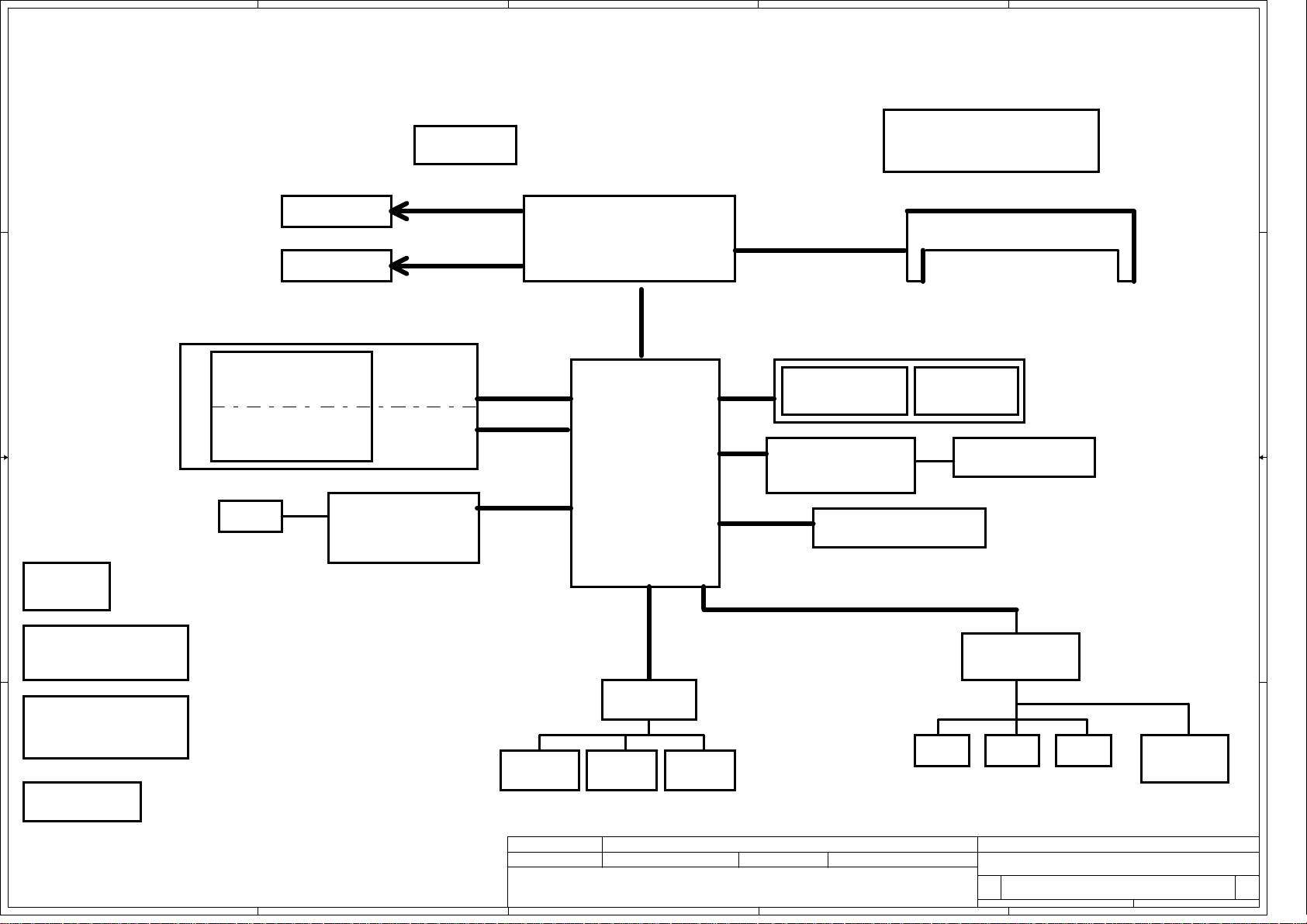

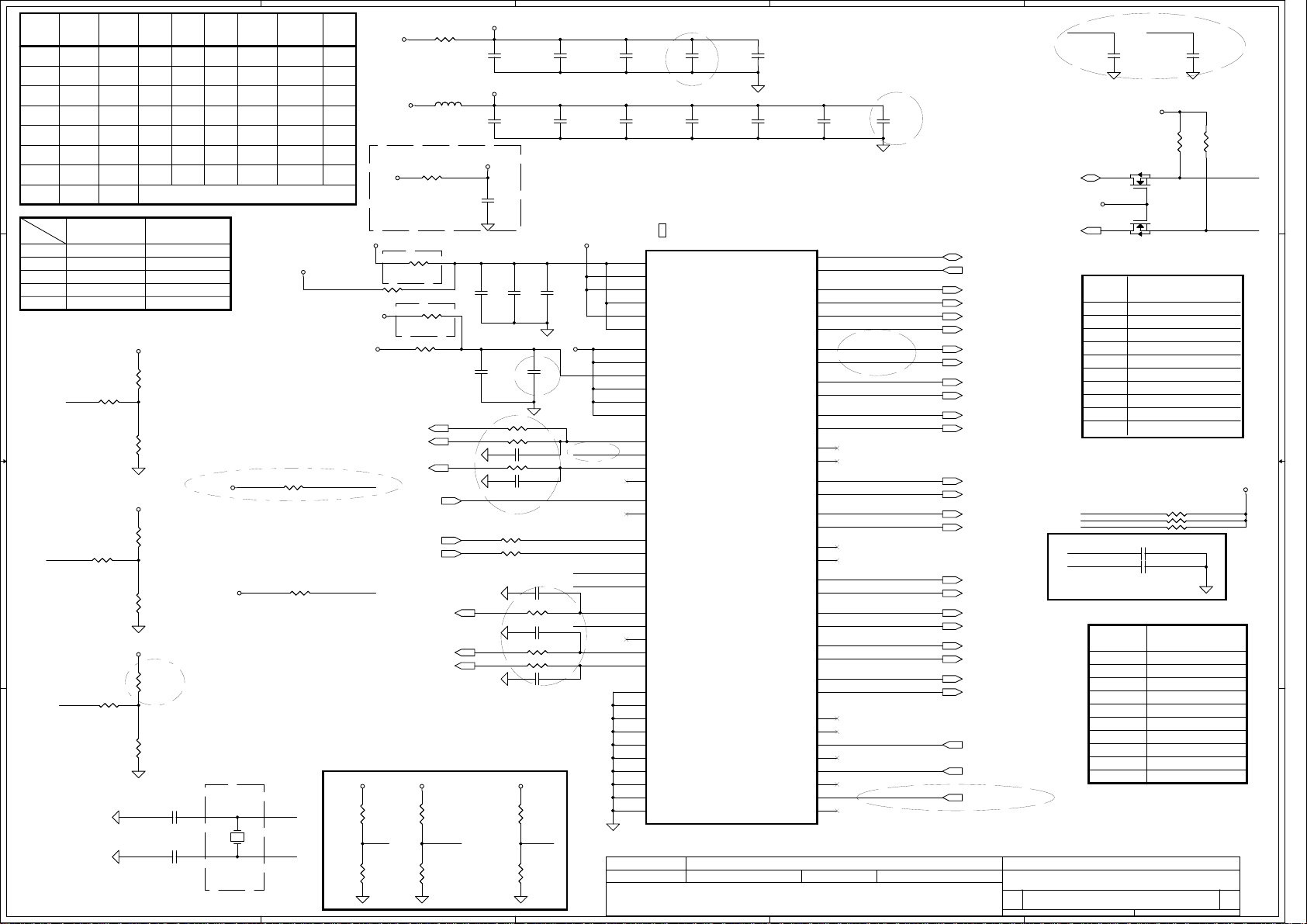

Toshiba NB500, Compal LA-6856P Schematic

A

1 1

B

C

D

E

Compal Confidential

2 2

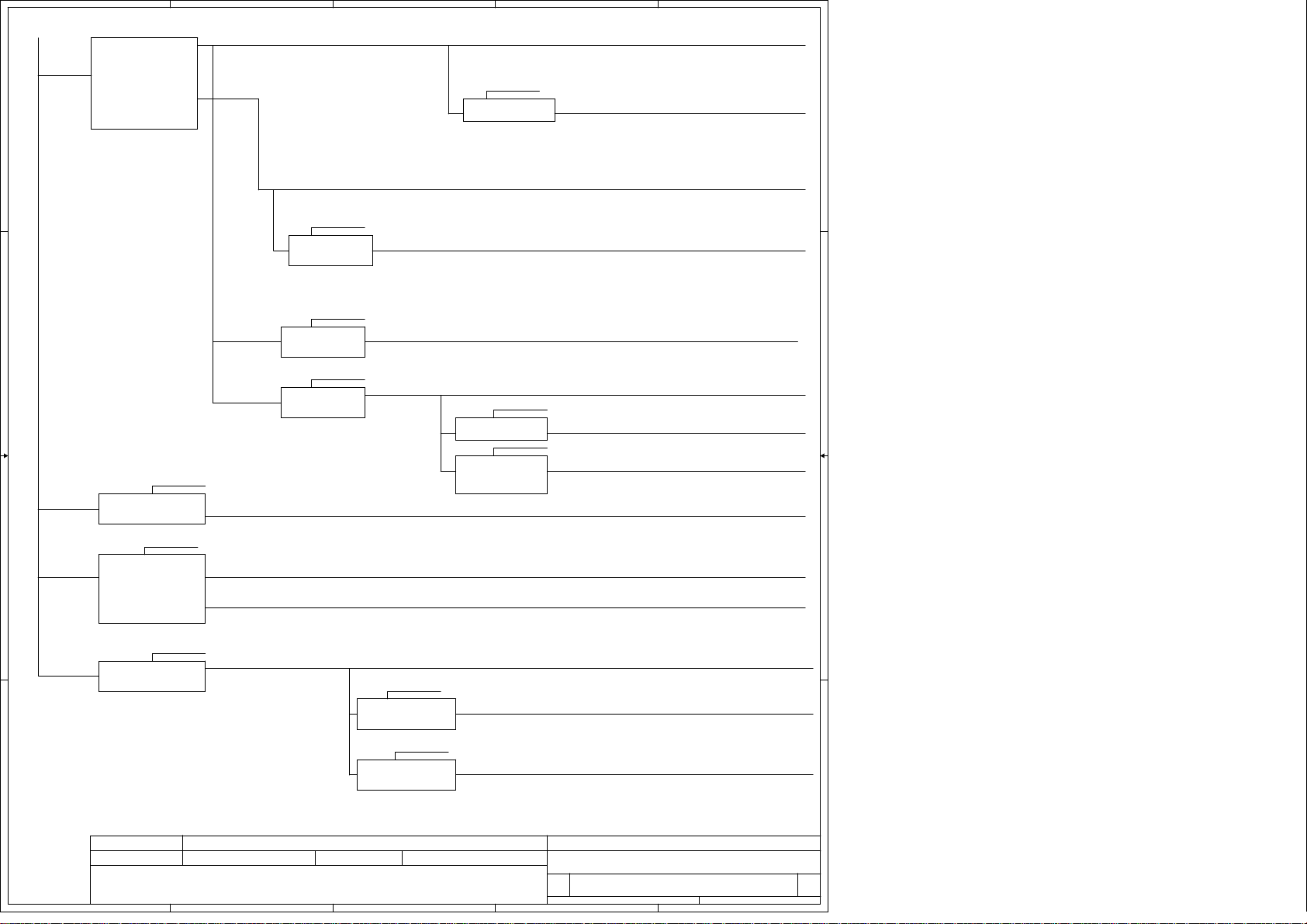

Cougar

Schematics Document

Intel Cedar Trail Processor/ Tiger point

3 3

4 4

A

B

2010-11-05

REV:0.1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTIC MB A6856

4019CG

134Tuesday, December 21, 2010

134Tuesday, December 21, 2010

134Tuesday, December 21, 2010

E

of

of

of

ACustom

ACustom

ACustom

A

B

C

D

E

Compal Confidential

Model Name : PBU00

File Name : P

1 1

HDMI Conn.

page 15

LED Conn.

page 16

Fan Control

ONE CHANNEL

LVDS

page 24

Intel Cedarview

(22x22mm)

page 6,7,8

Memory BUS(DDRIII)

1.5V DDRIII 800

Low Power Clock Generator

ICS9LVRS387AKLFT MLF

page 9

204pin DDRIII-SO-DIMM

page 10

2 2

DMI x 2

PCIeMini Card

WWAN

USB port 6

page 16

PCIeMini Card

WLAN +BT COMBO

PCIe port 2

page 16

RJ45

page 22

3 3

RTC CKT.

page 13

DC/DC Interface CKT.

page 26

(FULL)

(HALF)

RTL8105E

10/100 LAN

PCIe port 3

page 22

USB

5V 480MHz

PCIe 1x [2]

1.5V 2.5GHz(250MB/s)

PCIe 1x

1.5V 2.5GHz(250MB/s)

Tiger Pointer

(17x17mm)

page 11,12,13,14

3.3V 33 MHz

LPC BUS

USB

5V 480MHz

USB

SATA port 0

5V 1.5GHz(150MB/s)

HD Audio

USB Conn X3

USB port 0,1,4

page 18,21

Card Reader

RTL5137

USB port 3

SATA HDD

3.3V 24.576MHz/48Mhz

page 23

Int. Camera

USB port 7

page 16

Card Reader Conn.

page 19

HDA Codec

ALC269

page 23

page 20

ENE KB926 E0

page 25

page 24

SPI ROM

page 25

Int.

page 20 page 21 page 21 page 21

HP CONN SPK CONNMIC CONNMIC CONN

(10A 1X) (10B 2X)

Power Circuit DC/DC

page 27~35

Touch Pad

page 26

4 4

Power/B

page 26

Int.KBD

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEAMTIC MB A6856

4019CG

234Tuesday, December 21, 2010

234Tuesday, December 21, 2010

234Tuesday, December 21, 2010

E

A

A

A

of

of

of

A

B

C

D

E

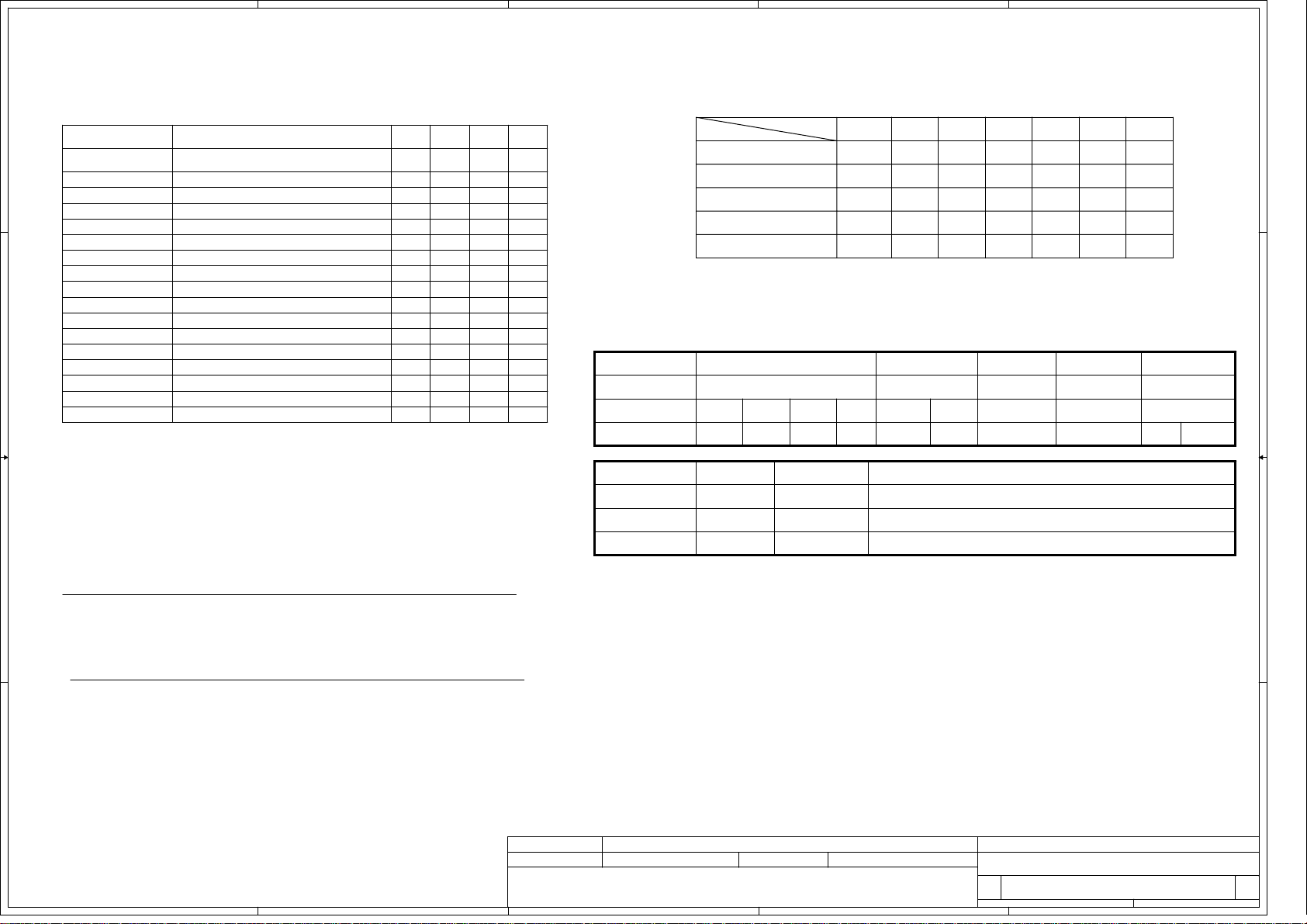

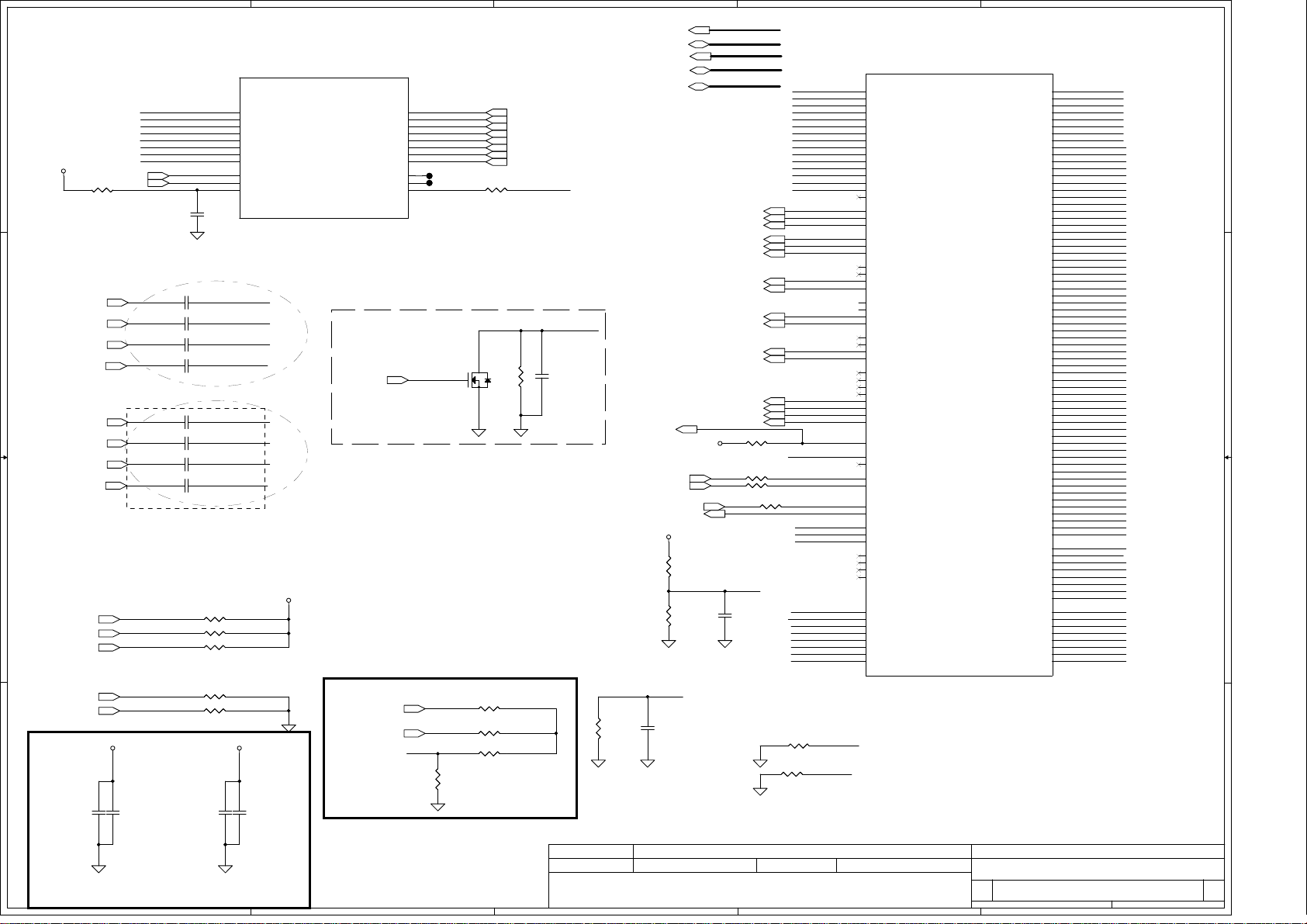

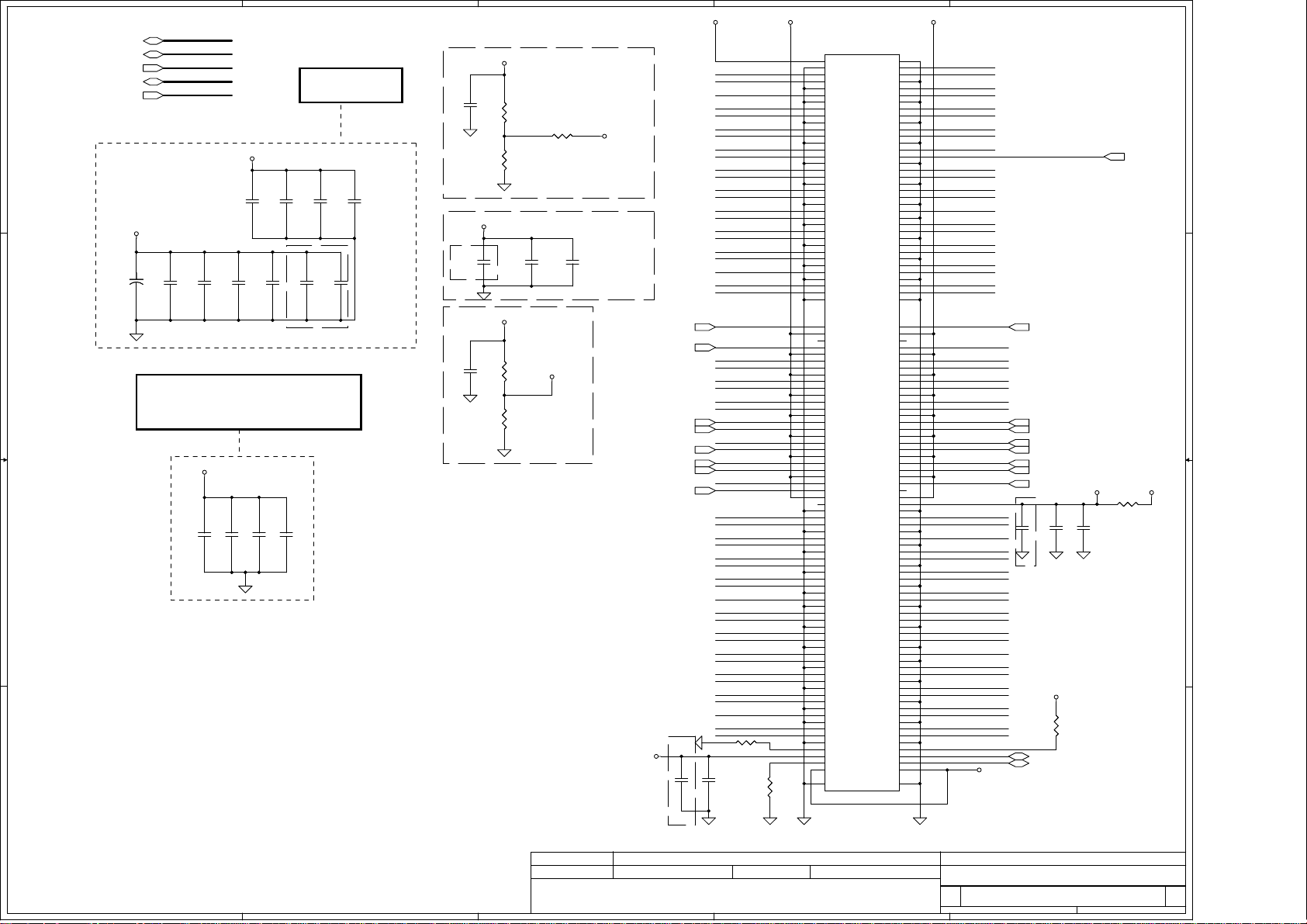

Voltage Rails

1 1

OFF

G3

OFF

Power Plane Description

VIN

B+

+CPU_CORE

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

S1 S3 S5

ON ON ON OFF

ON ON ON ON

ON OFF

+0.89VS 0.89VS GFX support voltage OFFON OFF OFF

+0.75VS 0.75V switched power rail for DDR terminator

+1.05VS

+1.5VS

+1.5V

VCCP switched power rail

1.5V switched power rail

1.5V power rail for DDR

+1.8VS 1.8VS switched power rail

+3VALW

3.3V always on power rail

ON OFF

ON OFF OFF

ON OFF OFF

ON OFF

ON

ON

OFF

ONON ON

+3V_LAN 3.3V power rail for LAN ON

2 2

+3VS

+5VALW 5V always on power rail

+5VS 5V switched power rail

+VSB VSB always on power rail ON

+RTCVCC RTC power

+3V_WLAN

3.3V power rail for LAN ON ON

3.3V switched power rail

ON OFF

ON

ON OFF

OFF OFFONOFF

ON

ON

ON

ON

OFF

OFF

OFF

OFF

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFFON

OFF

OFF

OFFON

OFF

ON

BTO Option Table

Function

description

explain

BTO

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Mini PCI-E SLOT

WLAN@ 3GGPS@

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Function

description

explain

BTO

3 3

EC SM Bus1 address

Device

Smart Battery

Address

EC SM Bus2 address

Device

EMC1402

Address

1001 010X b0001 011X b

WIMAX@

SIGNAL

3GGPSWi-Fi WiMax

SLP_S3#

SLP_S4#

SLP_S5#

HIGH HIGH HIGH

HIGH

LOW

LOW LOW

LOWLOW

CAMERA & MIC

3G

CAMERA MIC

3G@

CAM@ MIC@

HIGHHIGHHIGH

HIGH

HIGH

LOW

+VALW

ON

ON

ON

ON

ON

BLUE TOOTH

BLUE TOOTH

BT@

+V +VS Clock

ON

ON

ON

OFF

OFF

ON

OFF

OFF

OFF

ONON

LOW

OFF

OFF

OFF

low@ normal@

Clock gen

Tpye

ICH7M SM Bus address

Device

Clock Generator

(SLG8SP556VTR)

DDR DIMMA

WWAN/WLAN

4 4

A

Address

1101 001Xb

1010 000Xb

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEAMTIC MB A6856

4019CG

334Tuesday, December 21, 2010

334Tuesday, December 21, 2010

334Tuesday, December 21, 2010

E

ACustom

ACustom

ACustom

of

of

of

5

D D

C C

B B

4

3

2

1

A A

5

4

Security Classification

Security Classification

Security Classification

2010/06/27 2011/6/27

2010/06/27 2011/6/27

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/27 2011/6/27

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTIC MB A6856

4019CG

434Tuesday, December 21, 2010

434Tuesday, December 21, 2010

434Tuesday, December 21, 2010

1

of

of

of

A

A

A

DESIGN CURRENT 250mA

B+

5

4

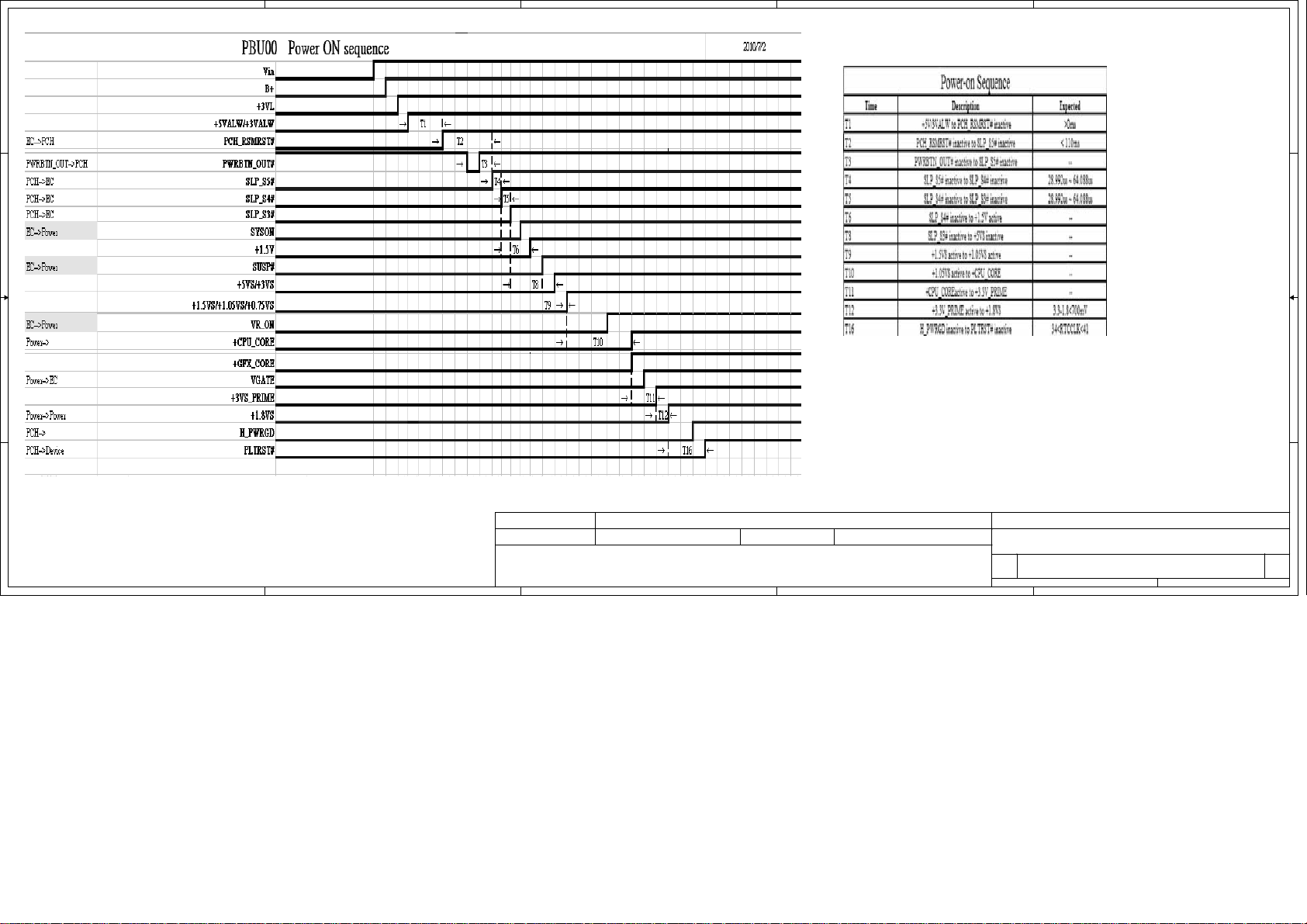

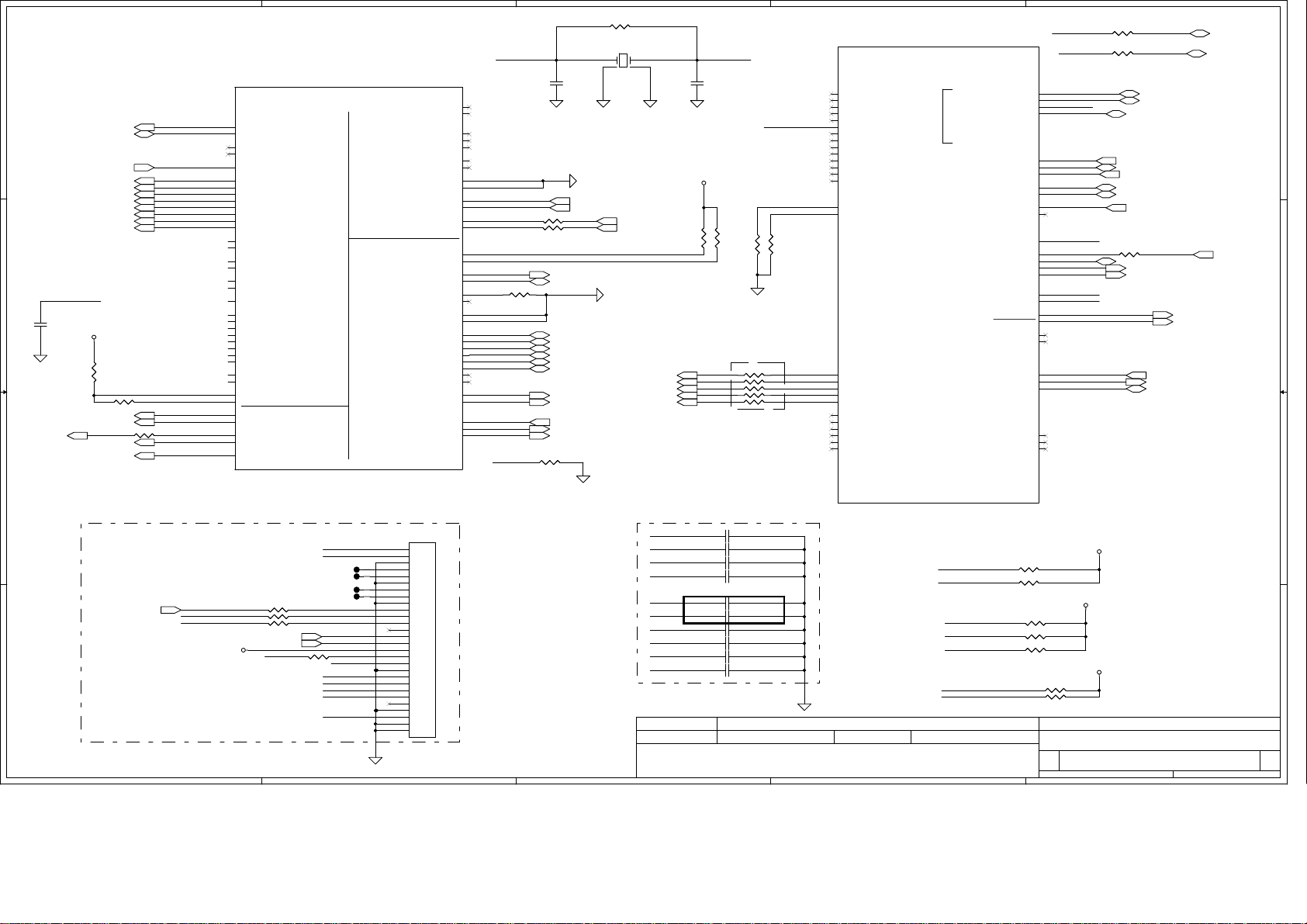

Cougar Power Map

Ipeak=6.97A, Imax=4.88A

3

2

DESIGN CURRENT 522mA

1

+3VALWP +-5%

** The SW just is reserved.

UP6182CQAG

D D

The power passes by jump or

0-ohm resistor.

** P-CHANNEL

AO3413

WOL_EN#

DESIGN CURRENT 300mA

+3V_LAN

Ipeak=3.98A, Imax=2.8A

DESIGN CURRENT 3010mA

+5VALWP +-5%

SUSP

N-CHANNEL

SI4800BDY

DESIGN CURRENT 2286mA

+5VS

VGATE

C C

APL5930KA

DESIGN CURRENT 151mA

SUSP

N-CHANNEL

SI4800BDY

P-CHANNEL

AO3413

ENVDD

DESIGN CURRENT 5586mA

DESIGN CURRENT 2000mA

+1.8VS

+3VS

+LCD_VDD

VGATE#

SUSP#

SY8033BDBC +1.05VSP +-5%

Ipeak=1.308A, Imax=4A

SI4800BDY

N-CHANNEL

DESIGN CURRENT 294mA

DESIGN CURRENT 3489mA

+3VS_PRIME

VR_ON

B B

Imax=3.5A

RT8165BGQW

DESIGN CURRENT 4500mA

DESIGN CURRENT 2000mA

+CPU_COREP

+GFX_COREP

SYSON

G5603RU1U

Ipeak=19.6A, Imax=13.72A

DESIGN CURRENT 2270mA

+1.5VP +-5%

SUSP#

IRF8113PBF

DESIGN CURRENT 2112mA

+1.5VSP

SUSP

UP7711U8

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

4

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

3

DESIGN CURRENT 500mA

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTIC MB A6856

4019CG

2

+0.75VSP

of

of

of

534Tuesday, December 21, 2010

534Tuesday, December 21, 2010

534Tuesday, December 21, 2010

1

ACustom

ACustom

ACustom

5

U1A

U1A

DMI_RXP0_C

12

DMI_RXN0_C

DMI_RXP1_C

DMI_RXN1_C

DMI_RXP2_C

DMI_RXN2_C

DMI_RXP3_C

DMI_RXN3_C

DMI_REF1P5

C948

C948

C949

C949

C950

C950

C951

C951

1 2

1 2

1 2

1 2

D D

+1.5VS

CLK_CPU_EXP<9>

CLK_CPU_EXP#<9>

R973 0_0402_5%R973 0_0402_5%

+1.5V pull up must be placed

within 500 mils from Cedarview

DMI_RXP0<12>

DMI_RXN0<12>

C C

DMI_RXP1<12>

DMI_RXN1<12>

For ES1 sample

C961

C961

C963

C963

C964

C964

C958

C958

1 2

1 2

1 2

1 2

DMI_RXP2<12>

DMI_RXN2<12>

DMI_RXP3<12>

DMI_RXN3<12>

B B

L3

L2

M3

M2

N2

N1

P2

P3

N9

N8

T2

1

C1088

C1088

2

1U_0402_6.3V6K

1U_0402_6.3V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

Close to CPU

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

DMI_REFCLKP

DMI_REFCLKN

DMI_REF1P5

CDV_22MM_REV1P10

CDV_22MM_REV1P10

DMI_RXP0_C

DMI_RXN0_C

DMI_RXP1_C

DMI_RXN1_C

DMI_RXP2_C

DMI_RXN2_C

DMI_RXP3_C

DMI_RXN3_C

XDP Reserve

XDP_TDI

R495

R495

XDP_TDI<7>

XDP_TMS<7>

XDP_TDO<7>

XDP_TRST#<7>

XDP_TCK<7>

A A

C203

C203

68P_0402_50V8J

68P_0402_50V8J

XDP_TMS

XDP_TDO

XDP_TRST#

XDP_TCK

+5VALW +1.5V

1

1

C1050

C1050

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2

1 2

51_0402_5%

51_0402_5%

R496

R496

1 2

51_0402_5%

51_0402_5%

R499

R499

1 2

51_0402_5%

51_0402_5%

R502

R502

1 2

51_0402_5%

51_0402_5%

R505

R505

1 2

51_0402_5%

51_0402_5%

C204

C204

68P_0402_50V8J

68P_0402_50V8J

1

1

2

2

C1065

C1065

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.05VS

CEDARVIEW

CEDARVIEW

REV = 1.10

REV = 1.10

DMI

DMI

1 OF 6

1 OF 6

4

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

RSVD_TP_R8

RSVD_TP_R7

DMI_RCOMP

SYSON#<27>

K6

K5

L5

L6

L9

L8

N5

N6

R8

T1T1

R7

T2T2

T1

?

?

SYSON#

2

G

G

DMI_TXP0 <12>

DMI_TXN0 <12>

DMI_TXP1 <12>

DMI_TXN1 <12>

DMI_TXP2 <12>

DMI_TXN2 <12>

DMI_TXP3 <12>

DMI_TXN3 <12>

R493

R493

7.5K_0402_5%

7.5K_0402_5%

Q37

Q37

2N7002_SOT23

2N7002_SOT23

1 2

DMI_REF1P5DMI_IRCOMP

R880 10K_0402_5%@R880 10K_0402_5%

@

1

2

1 2

+1.5V pull up must be placed

within 500 mils from Cedarview

13

D

D

S

S

Reserve PM_SLP_S4# to turn on DRAM_PWROK

R966

R966

0_0402_5%

0_0402_5%

@

@

XDP_DBREST#<7>

PCH_POK<13>

DRAM_VR_PWRGD

1 2

R967 0_0402_5%R967 0_0402_5%

1 2

1 2

R968

R968

R969

R969

10K_0402_5%

10K_0402_5%

1 2

12.1K_0402_1%

12.1K_0402_1%

@

SMPWROK

C1063 0.1U_0402_16V4Z@C1063 0.1U_0402_16V4Z

3

DDR_A_MA[0..14]<10>

DDR_A_DQS#[0..7]<10>

DDR_A_D[0..63]<10>

1K_0402_1%

1K_0402_1%

1K_0402_1%

1K_0402_1%

DDR_DQPU

12

@

@

C952 0.01U_0402_16V7K

C952 0.01U_0402_16V7K

R893

R893

33.2_0402_1%

33.2_0402_1%

2

DDR_A_DM[0..7]<10>

DDR_A_DQS[0..7]<10>

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_WE#<10>

DDR_A_CAS#<10>

DDR_A_RAS#<10>

DDR_A_BS0<10>

DDR_A_BS1<10>

DDR_A_BS2<10>

DDR_CS2#<10>

DDR_CS3#<10>

DDR_CKE2<10>

DDR_CKE3<10>

M_ODT2<10>

M_ODT3<10>

M_CLK_DDR2<10>

M_CLK_DDR#2<10>

M_CLK_DDR3<10>

DRAMRST#<10>

CLK_CPU_MPLL_C<9>

CLK_CPU_MPLL#_C<9>

SM_PWROK<32>

DRAM_VR_PWRGD<7>

+1.5V

12

R500

R500

12

R504

R504

1

2

M_CLK_DDR#3<10>

R878

@R878

@

1 2

+1.5V

10K_0402_5%

10K_0402_5%

R883 0_0402_5%R883 0_0402_5%

1 2

1 2

R892 0_0402_5%R892 0_0402_5%

R881

R881

DDR_VREF

1

C953

C953

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

DDR_A_WE#

DDR_A_CAS#

DDR_A_RAS#

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_CS2#

DDR_CS3#

DDR_CKE2

DDR_CKE3

M_ODT2

M_ODT3

M_CLK_DDR2

M_CLK_DDR#2

M_CLK_DDR3

M_CLK_DDR#3

DDR_VREF

CLK_CPU_MPLL

CLK_CPU_MPLL#

0_0402_5%

0_0402_5%

1 2

DRAM_VR_PWRGD

R553

R553

22.6_0402_1%

22.6_0402_1%

R503

R503

1 2

270_0402_1%

270_0402_1%

SMPWROK

DDR_ODTPU

DDR_CMDPU

DDR_DQPU

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_CMDPU

DDR_ODTPU

U1B

U1B

AK14

DDR3_MA0

AK16

DDR3_MA1

AJ14

DDR3_MA2

AJ16

DDR3_MA3

AK18

DDR3_MA4

AH18

DDR3_MA5

AJ18

DDR3_MA6

AK20

DDR3_MA7

AJ20

DDR3_MA8

AH20

DDR3_MA9

AJ12

DDR3_MA10

AK21

DDR3_MA11

AJ21

DDR3_MA12

AJ8

DDR3_MA13

AH22

DDR3_MA14

AJ22

DDR3_MA15

AH10

DDR3_WE#

AJ10

DDR3_CAS#

AJ11

DDR3_RAS#

AK12

DDR3_BS0

AH13

DDR3_BS1

AK22

DDR3_BS2

AH12

DDR3_CS#0

AH8

DDR3_CS#1

AK11

DDR3_CS#2

AK8

DDR3_CS#3

AH23

DDR3_CKE0

AJ24

DDR3_CKE1

AK24

DDR3_CKE2

AH24

DDR3_CKE3

AK10

DDR3_ODT0

AK7

DDR3_ODT1

AL9

DDR3_ODT2

AJ7

DDR3_ODT3

AG15

DDR3_CK0

AF15

DDR3_CK#0

AF17

DDR3_CK1

AG17

DDR3_CK#1

AD17

DDR3_CK2

AC17

DDR3_CK#2

AC15

DDR3_CK3

AD15

DDR3_CK#3

AK25

DDR3_DRAMRST#

AJ27

DDR3_VREF

AL28

DDR3_VREF_NCTF

AC19

DDR3_REFP

AB19

DDR3_REFN

AA5

DDR3_DRAM_PWROK

W7

DDR3_VCCA_PWROK

AJ26

DDR3_ODTPU

AJ25

DDR3_CMDPU

AK27

DDR3_DQPU

AB11

RSVD_TP_AB11

AB13

RSVD_TP_AB13

AF19

RSVD_TP_AF19

AG19

RSVD_TP_AG19

Y28

DDR3_DM0

AB26

DDR3_DM1

AE30

DDR3_DM2

AB21

DDR3_DM3

AG11

DDR3_DM4

AG2

DDR3_DM5

AB8

DDR3_DM6

AA3

DDR3_DM7

CDV_22MM_REV1P10

CDV_22MM_REV1P10

DDR3

DDR3

CEDARVIEW

CEDARVIEW

?

?

REV = 1.10

REV = 1.10

DDR3_DQ0

DDR3_DQ1

DDR3_DQ2

DDR3_DQ3

DDR3_DQ4

DDR3_DQ5

DDR3_DQ6

DDR3_DQ7

DDR3_DQ8

DDR3_DQ9

DDR3_DQ10

DDR3_DQ11

DDR3_DQ12

DDR3_DQ13

DDR3_DQ14

DDR3_DQ15

DDR3_DQ16

DDR3_DQ17

DDR3_DQ18

DDR3_DQ19

DDR3_DQ20

DDR3_DQ21

DDR3_DQ22

DDR3_DQ23

DDR3_DQ24

DDR3_DQ25

DDR3_DQ26

DDR3_DQ27

DDR3_DQ28

DDR3_DQ29

DDR3_DQ30

DDR3_DQ31

DDR3_DQ32

DDR3_DQ33

DDR3_DQ34

DDR3_DQ35

DDR3_DQ36

DDR3_DQ37

DDR3_DQ38

DDR3_DQ39

DDR3_DQ40

DDR3_DQ41

DDR3_DQ42

DDR3_DQ43

DDR3_DQ44

DDR3_DQ45

DDR3_DQ46

DDR3_DQ47

DDR3_DQ48

DDR3_DQ49

DDR3_DQ50

DDR3_DQ51

DDR3_DQ52

DDR3_DQ53

DDR3_DQ54

DDR3_DQ55

DDR3_DQ56

DDR3_DQ57

DDR3_DQ58

DDR3_DQ59

DDR3_DQ60

DDR3_DQ61

DDR3_DQ62

DDR3_DQ63

DDR3_DQS0

DDR3_DQS1

DDR3_DQS2

DDR3_DQS3

DDR3_DQS4

DDR3_DQS5

DDR3_DQS6

DDR3_DQS7

DDR3_DQS#0

DDR3_DQS#1

DDR3_DQS#2

DDR3_DQS#3

DDR3_DQS#4

DDR3_DQS#5

DDR3_DQS#6

DDR3_DQS#7

?2 OF 6

?2 OF 6

Y30

Y29

AC30

AC31

W31

W28

AB28

AB30

AA24

AA22

AE27

AE26

AB27

AA25

AD25

AD27

AD29

AE29

AJ30

AK29

AD28

AD30

AG30

AJ29

AE24

AG24

AD22

AC21

AG27

AG25

AG21

AE21

AD13

AD11

AG8

AG7

AG13

AE13

AD10

AF8

AH2

AG3

AD2

AD3

AH4

AK3

AE2

AD4

AD7

AD6

AA6

AB5

AE8

AE5

AB9

AA8

AB2

AB4

W4

V3

AC2

AB3

Y2

W1

AA30

AB24

AF30

AE22

AG10

AF4

AB6

Y3

AA31

AB25

AF29

AF22

AF10

AF3

AB7

AA2

1

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

2010.07.12 RF request

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEAMTIC MB A6856

4019CG

634Tuesday, December 21, 2010

634Tuesday, December 21, 2010

634Tuesday, December 21, 2010

1

ACustom

ACustom

ACustom

of

of

of

5

U1C

U1C

D D

HDMICLK_C<15>

HDMIDAT_C<15>

HPD_C<15>

HDMI_TXD2+<15>

HDMI_TXD2-<15>

HDMI_TXD1+<15>

HDMI_TXD1-<15>

HDMI_TXD0+<15>

HDMI_TXD0-<15>

HDMI_CLK0+<15>

HDMI_CLK0-<15>

C C

BREF_1.5V

HDMI_TXD2+

HDMI_TXD2HDMI_TXD1+

HDMI_TXD1HDMI_TXD0+

HDMI_TXD0HDMI_CLK0+

HDMI_CLK0-

1

C1120

C1120

HDA_SDIN1<13>

B B

A A

+1.5VS

2

1U_0402_6.3V6K

1U_0402_6.3V6K

R903

R903

10_0402_5%

10_0402_5%

1 2

R904 7.5K_0402_1%R904 7.5K_0402_1%

HDA_BITCLK_CPU<13>

HDA_SYNC_CPU<13>

HDA_SDOUT_CPU<13>

HDA_RST#_CPU<13>

DRAM_VR_PWRGD<6>

1 2

R90533_0402_5% R90533_0402_5%

1 2

5

BREF_1.5V

BREFREXT

HDA_BITCLK_CPU

HDA_SYNC_CPU

HDA_SDIN1_CPU

HDA_SDOUT_CPU

HDA_RST#_CPU

H25

DDI0_DDC_SCL

J22

DDI0_DDC_SDA

C8

DDI0_AUXP

B8

DDI0_AUXN

H22

DDI0_HPD

G2

DDI0_TXP0

G3

DDI0_TXN0

F3

DDI0_TXP1

F2

DDI0_TXN1

D4

DDI0_TXP2

C3

DDI0_TXN2

B7

DDI0_TXP3

A7

DDI0_TXN3

H15

RSVD_TP_H15

J15

RSVD_TP_J15

F25

DDI1_DDC_SCL

G27

DDI1_DDC_SDA

D10

DDI1_AUXP

C10

DDI1_AUXN

D26

DDI1_HPD

E11

DDI1_TXP0

F11

DDI1_TXN0

J11

DDI1_TXP1

H11

DDI1_TXN1

F13

DDI1_TXP2

E13

DDI1_TXN2

J13

DDI1_TXP3

K13

DDI1_TXN3

J17

RSVD_TP_J17

H17

RSVD_TP_H17

E15

BREF1P5V

F15

BREFREXT

H21

AZIL_BCLK

F22

AZIL_SYNC

E22

AZIL_SDI

F21

AZIL_SDO

E21

AZIL_RST#

CDV_22MM_REV1P10

CDV_22MM_REV1P10

DRAM_VR_PWRGD

H_PWRGD PWRGD_REQ

H_RSVD_K26

R976 0_0402_5%R976 0_0402_5%

R964 0_0402_5%R964 0_0402_5%

R970 0_0402_5%

R970 0_0402_5%

CPU_ITP<9>

+1.8VS

CPU_ITP#<9>

PLTRST#

@

@

CEDARVIEW

CEDARVIEW

DDI

DDI

IHDA

IHDA

XDP_PREQ#

XDP_PRDY#

12

12

12

CPU_ITP

CPU_ITP#

R965 1K_0402_5%R965 1K_0402_5%

12

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

XDP_TCK

T68T68

T67T67

T69T69

T70T70

XDP_DBREST#

?

?

REV = 1.10

REV = 1.10

LVDS VGA

LVDS VGA

4

CRT_DDC_DATA

CRT_DDC_CLK

DPL_REFSSCCLKP

DPL_REFSSCCLKN

DPL_REFCLKP

DPL_REFCLKN

LVDS_CTRL_CLK

LVDS_CTRL_DATA

LVDS_DDC_CLK

LVDS_DDC_DATA

PANEL_BKLTCTL

PANEL_BKLTEN

PANEL_VDDEN

3 OF 6

3 OF 6

?

?

JXDP1

JXDP1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

G1

28

G2

ACES_85201-2605

ACES_85201-2605

4

18P_0402_50V8J

18P_0402_50V8J

D14

CRT_HSYNC

C14

CRT_VSYNC

B12

CRT_RED

B11

CRT_GREEN

C11

CRT_BLUE

D12

CRT_IRTN

A13

CRT_IREF

E29

E27

CPU_SSCDREFCLK

F17

CPU_SSCDREFCLK#

E17

CPU_DREFCLK_C

B9

CPU_DREFCLK#_C

A9

LVDS_VTRL_CLK

F28

LVDS_VTRL_DATA

E24

G24

H24

L_IBG

R509

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

LVDS_TXP0

LVDS_TXN0

LVDS_TXP1

LVDS_TXN1

LVDS_TXP2

LVDS_TXN2

LVDS_TXP3

LVDS_TXN3

LVDS_CLKP

LVDS_CLKN

E10

F10

H2

H3

G10

H10

F8

E8

H7

H8

G5

G6

H4

J4

G22

E25

F29

2.37K_0402_1%

2.37K_0402_1%

ENBKL

ENBKL

R509

To be placed <500 mils to U1 ball

CONN@

CONN@

1

C1076

C1076

2

CPU_SSCDREFCLK <9>

CPU_SSCDREFCLK# <9>

R897

@R897

@

1 2

0_0402_5%

0_0402_5%

1 2

R898 0_0402_5%@R898 0_0402_5%@

LCD_EDID_CLK <16>

LCD_EDID_DATA <16>

R509 be placed U1.R22

LCD_TXOUT0+ <16>

LCD_TXOUT0- <16>

LCD_TXOUT1+ <16>

LCD_TXOUT1- <16>

LCD_TXOUT2+ <16>

LCD_TXOUT2- <16>

LCD_TXCLK+ <16>

LCD_TXCLK- <16>

GMCH_INVT_PWM <16>

ENBKL <24>

GMCH_ENVDD <16>

R517

R517

100K_0402_5%

100K_0402_5%

3

R894 1M_0402_5%R894 1M_0402_5%

1 2

Y3

Y3

27MHZ_18PF_X3S027000FI1H-X

27MHZ_18PF_X3S027000FI1H-X

1 3

2 4

CPU_DREFCLK <9>

CPU_DREFCLK# <9>

XDP_TCK<6>

XDP_TDI<6>

XDP_TDO<6>

XDP_TMS<6>

XDP_TRST#<6>

H_DPRSTP#

H_DPSLP#

H_PWRGD

H_A20M#

H_INIT#

H_INTR

H_FERR#

H_NMI

H_SMI#

H_STPCLK#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

CPU_DREFCLK#_CCPU_DREFCLK_C

1

C1077

C1077

18P_0402_50V8J

18P_0402_50V8J

2

+3VS

12

49.9_0402_1%

49.9_0402_1%

R900

R900

2.2K_0402_5%

2.2K_0402_5%

R899

2.2K_0402_5%

R899

2.2K_0402_5%

R901

R901

1 2

1 2

Close to CPU

R9590_0402_5% R9590_0402_5%

R9600_0402_5% R9600_0402_5%

R9610_0402_5% R9610_0402_5%

R9620_0402_5% R9620_0402_5%

R9630_0402_5% R9630_0402_5%

C954 220P_0402_50V7K@C954 220P_0402_50V7K@

1 2

C955 220P_0402_50V7K@C955 220P_0402_50V7K@

1 2

C956 220P_0402_50V7K@C956 220P_0402_50V7K@

1 2

C957 220P_0402_50V7K@C957 220P_0402_50V7K@

1 2

C959 220P_0402_50V7KC959 220P_0402_50V7K

1 2

C960 220P_0402_50V7KC960 220P_0402_50V7K

1 2

C962 220P_0402_50V7K@C962 220P_0402_50V7K@

1 2

C965 220P_0402_50V7K@C965 220P_0402_50V7K@

1 2

C966 220P_0402_50V7K@C966 220P_0402_50V7K@

1 2

C967 220P_0402_50V7K@C967 220P_0402_50V7K@

1 2

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

H_RSVD_K26

12

49.9_0402_1%

49.9_0402_1%

R902

R902

XDP_TCK_R

XDP_TDI_R

XDP_TDO_R

XDP_TMS_R

XDP_TRST#_R

U1D

U1D

L26

RSVD_L26

L27

STRAP_L27

K28

STRAP_K28

K25

RSVD_K25

J28

RSVD_J28

K26

RSVD_K26

K27

RSVD_K27

H27

RSVD_H27

K30

RSVD_K30

L29

RSVD_L29

L30

RSVD_L30

K29

RSVD_K29

J31

RSVD_J31

H30

RSVD_H30

K24

HV_GPIO_RCOMP

K23

MV_GPIO_RCOMP

C25

TCLK

C24

TDI

B25

TDO

D24

TMS

B24

TRST#

R5

RSVD_R5

R6

RSVD_R6

W25

RSVD_W25

W26

RSVD_W26

N24

RSVD_N24

N25

RSVD_N25

CDV_22MM_REV1P10

CDV_22MM_REV1P10

?

?

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

?

?

CEDARVIEW

CEDARVIEW

REV = 1.10

REV = 1.10

NMI/LINT10

RSVD_C18

ICH

ICH

INTR/LINT00

THERMTRIP#

RSVD_L11

PROCHOT#

PWRGOOD

HPLL_REFCLK_P

HPLL_REFCLK

SVID_ALERT#

SVID_DATA

R501

R501

R906

R906

R907

R907

R908

R908

R511

R511

RSVD_E19

RSVD_F19

SVID_CLK

RSVD_K21

RSVD_L22

RSVD_L24

CPU

CPU

4 OF 6

4 OF 6

XDP_PREQ#

XDP_PRDY#

SVID_ALERT#

SVID_DATA

H_PROCHOT#

XDP_DBREST#

PWRGD_REQ

2

H_FERR#_CPU

B18

SMI#

C22

C18

D22

STPCLK#

C21

DPRSTP#

B21

DPLSLP#

B22

CPUSLP#

A23

INIT#

D20

B20

L11

C20

PBE#

A19

D23

G30

RESET#

E30

DBR#

H29

PRDY#

G29

PREQ#

J19

K19

E19

F19

B16

D18

C16

K21

L22

L24

1 2

51_0402_5%

51_0402_5%

1 2

51_0402_5%

51_0402_5%

12

75_0402_5%

75_0402_5%

12

110_0402_1%

110_0402_1%

12

100_0402_5%

100_0402_5%

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

1 2

R895 0_0402_5%R895 0_0402_5%

1 2

R896 0_0402_5%R896 0_0402_5%

H_SMI#

H_NMI

H_A20M#_C

H_STPCLK#

H_DPRSTP#

H_DPSLP#

H_CPUSLP#

H_INIT#

H_INTR

H_THERMTRIP#

Close to CPU

H_FERR#_CPU

H_PROCHOT#

H_PWRGD

PLTRST#

XDP_DBREST#

XDP_PRDY#

XDP_PREQ#

CLK_CPU_HPLCLK

CLK_CPU_HPLCLK#

SVID_ALERT#

SVID_CLK

SVID_DATA

+1.8VS

+1.05VS

+3VS

R9711K_0402_1% R9711K_0402_1%

12

R9721K_0402_1% R9721K_0402_1%

12

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEAMTIC MB A6856

4019CG

1

H_FERR#

H_A20M#H_A20M#_C

H_SMI# <11>

H_NMI <11>

H_STPCLK# <11>

H_DPRSTP# <13>

H_DPSLP# <13>

H_CPUSLP# <11>

H_INIT# <11>

H_INTR <11>

H_THERMTRIP# <11>

R958 0_0402_5%R958 0_0402_5%

VR_HOT

1 2

H_PWRGD <13>

PLTRST# <13,17,22>

XDP_DBREST# <6>

SVID_ALERT# <34>

SVID_CLK <34>

SVID_DATA <34>

1

H_FERR# <11>

H_A20M# <11>

VR_HOT <34>

CLK_CPU_HPLCLK <9>

CLK_CPU_HPLCLK# <9>

of

734Tuesday, December 21, 2010

of

734Tuesday, December 21, 2010

of

734Tuesday, December 21, 2010

ACustom

ACustom

ACustom

+1.05VS

723mA

R525

R525

1 2

0_0805_5%

0_0805_5%

C971

C971

@

@

D D

R526

R526

1 2

0_0603_5%

0_0603_5%

R956

R956

1 2

0_0603_5%

0_0603_5%

R910

R910

1 2

0_0603_5%

0_0603_5%

R531

R531

1 2

0_0603_5%

0_0603_5%

C C

+1.5V

1 2

R530

R530

0_0603_5%

0_0603_5%

Please closed U1 ball

+1.5V

R527

R527

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

1 2

0_1206_5%

0_1206_5%

2

C979

C979

1

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

B B

+1.5VS

R919

R919

1 2

0_0603_5%

0_0603_5%

R922

R922

1 2

0_0603_5%

0_0603_5%

A A

@

@

R927

R927

1 2

0_0603_5%

0_0603_5%

5

R909

+VCCA_VCCD

1

1

C972

C972

C970

C970

2

2

@

@

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

22U_0805_6.3V6M

22U_0805_6.3V6M

+1.05VS_EAST

1

C1079

C1079

2

@

@

1U_0402_6.3V6K

1U_0402_6.3V6K

C1079 1UF for

CPU pin N30,N31

1

1

C1083

C1083

C1082

C1082

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C1086

C1086

2

+VCC_DMI

1

C994

C994

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C992

C992

2

22U_0805_6.3V6M

22U_0805_6.3V6M

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

2

2

C981

C981

C982

C980

C980

C982

1

1

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

1

C1097

C1097

2

2

1

+1.5VS +1.5VS +1.5VS

R924

R924

0_0603_5%

0_0603_5%

1 2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C1104

C1104

2

@

@

5

R909

1 2

1

1

C973

C973

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C973 1UF for

CPU pin V4

1

C1080

C1080

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C1080 1UF for

CPU pin L19

+VCCA_VDDR

1

C1084

C1084

2

@

@

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCADP_1.05

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCCK_DDR

1

C993

C993

2

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

+VCCADMI_1.5VS

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCAGPIO1.5V

C1101

C1101

@

@

0.1U_0402_10V6K

0.1U_0402_10V6K

Reserve SFR option

for cedar view

+VCCADP0_SFR +VCCADP1_SFR +VCCSFRMPL

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C1105

C1105

2

+VCCDMPL

0_0603_5%

0_0603_5%

+VCC_SM

+1.8VS

2

1

C1078

C1078

@

@

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

+1.05VS

1

+

+

C1081

C1081

2

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

Close Chipset pin

+3VS_PRIME

R913

R913

1 2

0_0603_5%

0_0603_5%

R914

R914

1 2

0_0603_5%

0_0603_5%

R916

R916

1 2

0_0603_5%

0_0603_5%

1

C983

R921

R921

0_0603_5%

0_0603_5%

C983

2

0.1uH use

0 ohm replace

@

@

R928

R928

1 2

0_0603_5%

0_0603_5%

1U_0402_6.3V6K

1U_0402_6.3V6K

1 2

+1.05VS+1.05VS +1.05VS

+VCCA_VCCD

+1.05VS_EAST

+VCCA_VCCD

+VCCA_VDDR

+VCCCK_DDR

+VCC_SM

+VCCADP_1.05

+VCCADP0_SFR

+VCCADP1_SFR

+1.05VS_EAST

+VCCAGPIO1.5V

+VCCAGPIO1.8V

+VCCAGPIO3.3V

R974 0_0402_5%R974 0_0402_5%

+VCCALVDS

+VCCDLVDS

R975 0_0402_5%R975 0_0402_5%

+VCCAZILAON

+VCCSFRMPL

+VCCDMPL

+VCCPLLCPU0

+VCCPLLCPU1

+VCCAHPLL

+VCCAGPIO3.3V

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

2

C1092

C1092

1

1 2

R918 0_0402_5%R918 0_0402_5%

C1100

C1100

R925

R925

0_0603_5%

0_0603_5%

1 2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C1106

C1106

C1107

C1107

2

@

@

12

12

+VCCAZILAON

2

C1093

C1093

1

+VCCAGPIO1.8V

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4

AA14

AA16

W16

W18

N30

N31

V4

W8

W9

W11

W13

AJ6

AK6

AH14

AH19

AK23

AK5

AL11

AL16

AL21

AG31

B5

C6

D6

K17

L18

L19

L16

N18

D30

D31

B13

H5

L21

B29

A30

AA18

AA11

B27

C29

B30

B26

+VCCDLVDS

+VCCALVDS

1

C986

C986

2

4

U1E

U1E

VCCADDR_1

VCCADDR_2

VCCADDR_3

VCCADDR_4

VCCRAMXXX_1

VCCRAMXXX_2

VCCRAMXXX_3

VCCACKDDR_1

VCCACKDDR_2

VCCADLLDDR_1

VCCADLLDDR_2

VCCCKDDR_1

VCCCKDDR_2

V_SM_1

V_SM_2

V_SM_3

V_SM_4

V_SM_5

V_SM_6

V_SM_7

V_SM_8

VCCADP_1

VCCADP_2

VCCADP_3

VCCADP0_SFR

VCCADP1_SFR

VCCAGPIO_LV

VCCAGPIO_REF

VCCAGPIO_DIO

VCCAGPIO_1

VCCAGPIO_2

VCCADAC

VCCALVDS

J1

VCCDLVDS

VCCDIO

VCCAZILAON_1

VCCAZILAON_2

VCCSFRMPL

VCCDMPL

VCCPLLCPU0

VCCPLLCPU1_1

VCCPLLCPU1_2

VCCAHPLL

CDV_22MM_REV1P10

CDV_22MM_REV1P10

+1.05VS

R917

R917

1 2

0_0603_5%

0_0603_5%

R920

R920

1 2

0_0603_5%

0_0603_5%

R923

R923

1 2

0_0603_5%

0_0603_5%

@

@

R929

R929

1 2

0_0603_5%

0_0603_5%

3

?

?

CEDARVIEW

CEDARVIEW

REV = 1.10

REV = 1.10

DDR

DDR

PLL

PLL

10U_0805_10V4Z

10U_0805_10V4Z

1

2

C1094

C1094

10U_0805_10V4Z

10U_0805_10V4Z

1

2

C1098

C1098

10U_0805_10V4Z

10U_0805_10V4Z

1

2

C1102

C1102

R926

R926

0_0603_5%

0_0603_5%

1 2

10U_0805_10V4Z

10U_0805_10V4Z

1

@

@

2

C1108

C1108

POWER

POWER

5 OF 6

5 OF 6

+VCCPLLCPU0

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

C1095

C1095

+VCCPLLCPU1

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

C1099

C1099

+VCCAHPLL

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

C1103

C1103

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C1109

C1109

2

CPU

CPU

DMI

DMI

VCC_CPU_01

VCC_CPU_02

VCC_CPU_03

VCC_CPU_04

VCC_CPU_05

VCC_CPU_06

VCC_CPU_07

VCC_CPU_08

VCC_CPU_09

VCC_CPU_10

VCC_CPU_11

VCC_CPU_12

VCC_CPU_13

VCC_CPU_14

VCC_CPU_15

VCC_CPU_16

VCC_CPU_17

VCC_CPU_18

VCC_CPU_19

VCC_CPU_20

VCC_CPU_21

VCC_CPU_22

VCC_CPU_23

VCC_CPU_24

VCC_CPU_25

VCC_CPU_26

VCC_CPU_27

VCC_CPU_28

VCC_CPU_29

VCC_GFX_01

VCC_GFX_02

VCC_GFX_03

VCC_GFX_04

VCC_GFX_05

VCC_GFX_06

VCC_GFX_07

VCC_GFX_08

VCC_GFX_09

VCC_GFX_10

VCC_GFX_11

VCCADMI_PLLSFR

VCC_CPUSENSE

VSS_CPUSENSE

VCC_GFXSENSE

VSS_GFXSENSE

VCCTHRM_1

VCCTHRM_2

?

?

4234mA

1U_0402_6.3V6K

1U_0402_6.3V6K

P18

P19

P21

P28

P29

P30

R22

R23

R24

R25

R26

R27

T19

T21

T29

T30

T31

U22

U23

U24

U25

U26

U27

V18

V19

V21

V28

V29

V30

+GFX_CORE

1938mA

N11

N13

P11

P13

R10

R9

T11

T13

U10

V11

V13

+VCC_DMI

B4

VCCADMI_1

C5

VCCADMI_2

A4

VCCADMI_3

VCCFHV_1

VCCFHV_2

VCCFHV_3

K4

V16

T16

V14

VCCSENSE

M28

VSSSENSE

M30

VCC_GFXSENSE

U8

VSS_GFXSENSE

U7

N16

K2

VCC_GFXSENSE

VSS_GFXSENSE

+GFX_CORE

+VCCADMI_1.5VS

+VCCATHRM

1

C1089

C1089

@

@

2

1

C1005

C1005

2

22U_0805_6.3V6M

22U_0805_6.3V6M

Close Chipset pin

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

4.7U_0603_6.3V6K

1

1

C974

C974

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

4.7U_0603_6.3V6K

C975

C975

1

1

C976

C976

2

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

C977

C977

Please closed U1 ball

+CPU_CORE

2 x 330uF(9mohm/2)

1

+

+

C984

C984

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

1

C991

C991

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

R912

R912

R915

R915

1

C1009

C1009

@

@

2

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C1085

C1085

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

10U_0805_10V4Z

10U_0805_10V4Z

C1090

C1090

VCC_GFXSENSE <34>

VSS_GFXSENSE <34>

1

1

+

+

C1004

C1004

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

Compal Secret Data

Compal Secret Data

Compal Secret Data

+CPU_CORE

1

1

C989

C989

C990

C990

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+VCCA_VCCD

R911

R911

1 2

0_0603_5%

0_0603_5%

+GFX_CORE

1U_0402_6.3V6K

1U_0402_6.3V6K

12

100_0402_5%

100_0402_5%

12

100_0402_5%

100_0402_5%

1

1

C1008

C1008

C1007

C1007

C1006

C1006

@

@

@

@

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

1

1

C988

C988

C987

C987

@

@

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

+CPU_CORE

12

100_0402_5%

100_0402_5%

12

+1.8VS

100_0402_5%

100_0402_5%

1

+

+

C1096

C1096

2

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

Deciphered Date

Deciphered Date

Deciphered Date

+CPU_CORE

@

@

R532

R532

R533

R533

2

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

2

1

2

C996

C996

@

@

+

+

C985

C985

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

VCCSENSE <34>

VSSSENSE <34>

1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_CDVDET

VSSA_CRTDAC

6 OF 6

6 OF 6

1 2

C159 22P_0402_50V8J

C159 22P_0402_50V8J

RF@

RF@

1 2

C150 22P_0402_50V8J

C150 22P_0402_50V8J

RF@

RF@

1 2

C153 22P_0402_50V8J

C153 22P_0402_50V8J

RF@

RF@

1 2

C156 22P_0402_50V8J

C156 22P_0402_50V8J

RF@

RF@

H19

H26

H28

H6

J10

J2

J21

J30

K11

K15

K3

K7

K8

K9

L1

L10

L13

L23

L25

L31

L7

M29

M4

N10

N14

N19

N21

N22

N23

N26

N27

N28

N4

N7

P14

P16

P4

T14

T18

T3

U5

U6

U9

V2

W10

W14

W19

W2

W21

W22

W23

W24

W27

W30

W5

W6

Y4

A27

A29

A3

AH1

AJ1

AJ31

AK1

AK2

AK30

AK31

AL2

AL29

AL3

AL30

AL5

B2

B3

B31

C1

C2

C31

E1

L14

D13

AA10

AA13

AA19

AA21

AA23

AA26

AA27

AA29

AB15

AB17

AB23

AB29

AC10

AC11

AC13

AC22

AC28

AD19

AD21

AD24

AD26

AE10

AE11

AE15

AE17

AE19

AE31

AF11

AF13

AF21

AF24

AF28

AG22

AH26

AH28

AK13

AK19

AK28

AL13

AL19

AL23

AL25

+VCCA_VCCD

+VCCCK_DDR

+GFX_CORE

+CPU_CORE

U1F

U1F

A11

VSS

A16

VSS

A21

VSS

A25

VSS

AA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

AC1

VSS

VSS

VSS

VSS

VSS

VSS

AC4

VSS

VSS

VSS

VSS

VSS

AD5

VSS

AD8

VSS

AE1

VSS

VSS

VSS

VSS

VSS

VSS

AE3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF7

VSS

VSS

AG5

VSS

VSS

VSS

AH6

VSS

AH9

VSS

AJ2

VSS

AJ3

VSS

VSS

VSS

VSS

AK9

VSS

VSS

VSS

VSS

VSS

AL7

VSS

B10

VSS

B14

VSS

B19

VSS

B23

VSS

C12

VSS

C26

VSS

C30

VSS

C7

VSS

D19

VSS

D28

VSS

D8

VSS

D9

VSS

E2

VSS

E5

VSS

E7

VSS

F24

VSS

F4

VSS

G1

VSS

G11

VSS

G13

VSS

G15

VSS

G17

VSS

G19

VSS

G21

VSS

G31

VSS

G8

VSS

H13

VSS

CDV_22MM_REV1P10

CDV_22MM_REV1P10

?

?

?

?

CEDARVIEW

CEDARVIEW

REV = 1.10

REV = 1.10

2010.07.12 RF request

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEAMTIC MB A6856

4019CG

1

ACustom

ACustom

834Tuesday, December 21, 2010

834Tuesday, December 21, 2010

834Tuesday, December 21, 2010

ACustom

of

of

of

5

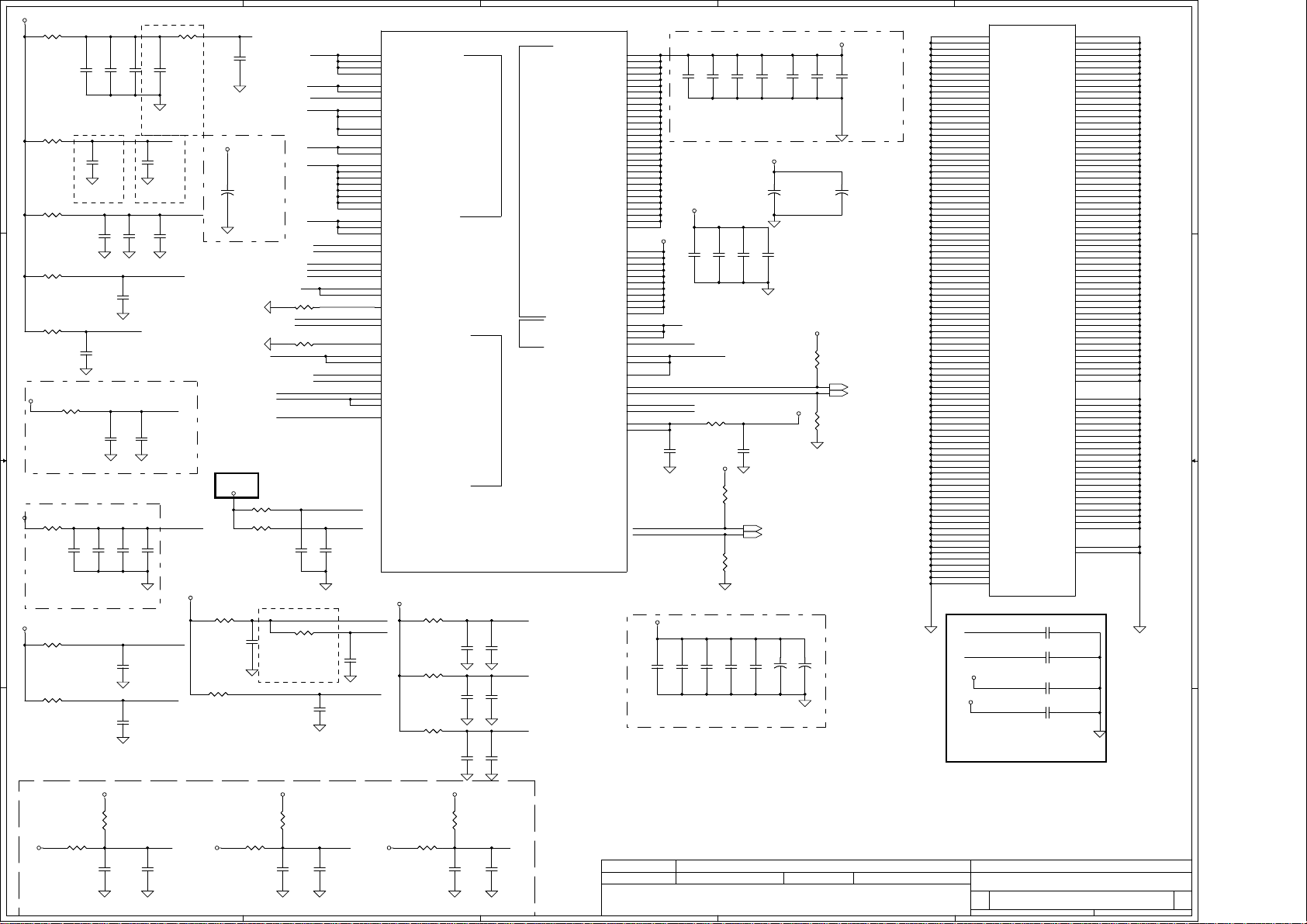

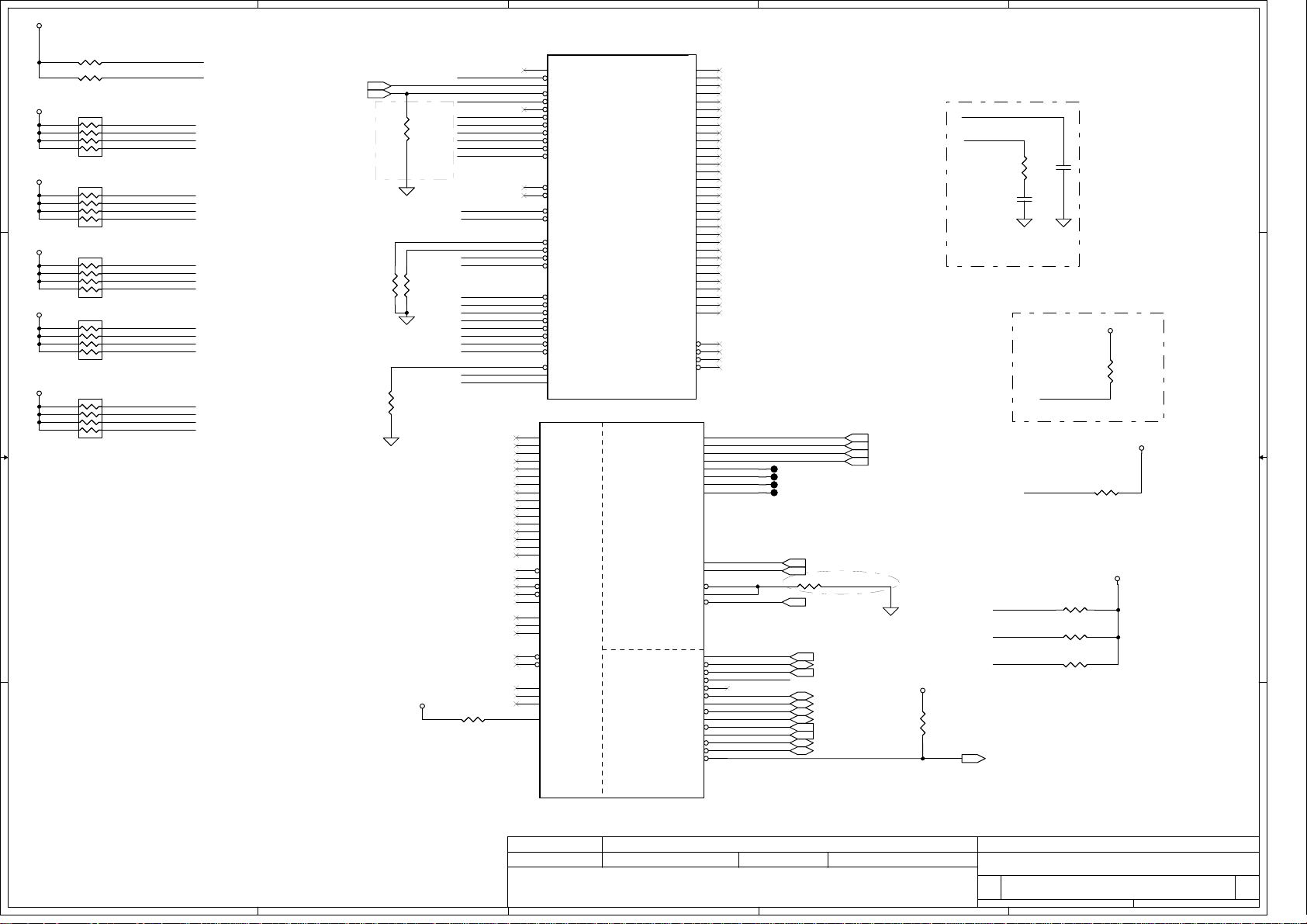

PCI

SRC

CPU

CLKSEL1

0

FSA

CLKSEL0

MHz

266

MHz

1000

MHz

MHz

33.30

14.318 96.0 48.0

DOT_96

MHz

USB

MHz

FSC FSB REF

CLKSEL2

0 1000 133 33.31 14.318 96.0 48.0

0 1001 200 33.30 14.318 96.0 48.0

0 1001 166 33.31 14.318 96.0 48.0

D D

1 1000 333 33.30 14.318 96.0 48.0

1 1000 100 33.31 14.318 96.0 48.0

1 1001 400 33.30 14.318 96.0 48.0

111

Reserved

Normal Power Low Power

R477 @ Stuff

R478

R479

R480

R483

C C

B B

Stuff

Stuff

@

@

+1.05VS

R482

R482

2.2K_0402_5%

2.2K_0402_5%

FSA

FSB

FSC

R486

R486

1K_0402_5%

1K_0402_5%

R490

R490

10K_0402_5%

10K_0402_5%

12

+1.05VS

12

+1.05VS

12

7/22 Add R242 to R253 for Intel request

A A

2010.03.09 Change Y1 to 5 x3.2 size

5

@

@

Stuff

Stuff

12

R481

R481

470_0402_5%

470_0402_5%

8/24 Change net name to FSB for U3.2

12

12

12

12

12

14.31818MHZ 20PF 7A14300003

14.31818MHZ 20PF 7A14300003

7/13 Add 33pF to GND for RF request

R484

@R484

@

7/21 Reserve 33pF to GND for RF request

1K_0402_5%

1K_0402_5%

8/27 C303, C324, C325, C326, C327 to GND for RF request

+3VS

7/22 Add R241 pull up to +3VS for RF Intel request

R485

@R485

@

470_0402_5%

470_0402_5%

R488

R488

0_0402_5%

0_0402_5%

+3VS

8/14 Add R250 pull up for Intel request

R489

R489

470_0402_5%

470_0402_5%

R491

@R491

@

0_0402_5%

0_0402_5%

C147 22P_0402_50V8JC147 22P_0402_50V8J

C148 22P_0402_50V8JC148 22P_0402_50V8J

12

Y1

Y1

Routing the trace at least 10mil

R65

R65

1 2

R608

R608

1 2

CLK_XTAL_IN

CLK_XTAL_OUT

+1.5VM_CK505

+1.05VM_CK505

+1.5VM_CK505

H_STP_CPU#_R

10K_0402_5%

10K_0402_5%

H_STP_PCI#_R

10K_0402_5%

10K_0402_5%

For ITP_EN, 0 =SRC8/SRC8#; 1 = ITP/ITP#

For PCI4_SEL, 0 = Pin24/25 : DOT96 / DOT96#

Pin28/29 : LCDCLK / LCDCLK#

For PCI2_TME:0=Overclocking of CPU and SRC allowed

(ICS only) 1=Overclocking of CPU and SRC NOT allowed

4

+3VM_CK505

R81

R81

1 2

+3VS

0_0603_5%

0_0603_5%

+1.05VM_CK505

+1.05VS

R82

R82

1 2

FBMH1608HM601-T_0603

FBMH1608HM601-T_0603

7/13 For RF request

+1.5VM_CK505

1

C942

C942

2

+3VM_1.5VM_R

1

C943

C943

2

+1.05VM_1.5VM_R

1

C946

C946

2

R432 0_0402_5%R432 0_0402_5%

R427 0_0402_5%R427 0_0402_5%

1 2

+1.5VS

0_0603_5%

0_0603_5%

7/13 For RF request

+3VM_CK505

R478

NORMAL@ R478

NORMAL@

1 2

0_0603_5%

0_0603_5%

R483

LOW@R483

LOW@

1 2

0_0603_5%

0_0603_5%

NORMAL@ R479

NORMAL@

1 2

0_0603_5%

0_0603_5%

R480

LOW@R480

LOW@

1 2

0_0603_5%

0_0603_5%

7/13 For RF request

CLK_48M_CR<23>

CLK_PCH_48M<12>

CLK_PCH_14M<13>

VGATE<13,24,27,33,34>

H_STP_CPU#<13>

H_STP_PCI#<13>

CLK_PCI_DDR<17>

CLK_PCI_LPC<24>

CLK_PCI_PCH<11>

R477

R477

LOW@

LOW@

R479

7/13 Add 33pF to GND for RF request

1 = Pin24/25 : SRC_0 / SRC_0#

Pin28/29 : 27M/27M_SS

+3VS+3VS

R119

R119

10K_0402_5%

10K_0402_5%

1 2

ITP_EN PCI2_TME

R113

10K_0402_5%

10K_0402_5%

1 2

R118

R118

10K_0402_5%

10K_0402_5%

1 2

PCI4_SEL

R114

@R114

@R113

@

4

@

10K_0402_5%

10K_0402_5%

1 2

2010.03.23 Change R81 from bead to 0 ohm

3

250 mA

1

C126

C126

10U_0805_10V4Z

10U_0805_10V4Z

2

1

C127

C127

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C128

C128

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C129

C129

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

80 mA

1

C134

C134

10U_0805_10V4Z

10U_0805_10V4Z

2

1

C135

C135

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C136

C136

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C137

C137

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2010.03.23 Change R477 from bead to 0 ohm

8/27 Delete C93, C94, C95, C102 for low power CLK GEN

SA00003H610 (ICS :CS9LVRS387AKLFT MLF)

Low power CLK Gen.

10U_0805_10V4Z

10U_0805_10V4Z

1

1

C944

C944

C945

C945

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1 2

1 2

1 2

C143 22P_0402_50V8JC143 22P_0402_50V8J

1 2

1 2

C868 22P_0402_50V8JC868 22P_0402_50V8J

1 2

1 2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.05VM_CK505

@

@

C947

C947

47P_0402_50V8J

47P_0402_50V8J

R9210_0402_5% R9210_0402_5%

R9110_0402_5% R9110_0402_5%

R9333_0402_5% R9333_0402_5%

1 2

C144 22P_0402_50V8JC144 22P_0402_50V8J

R10333_0402_5% R10333_0402_5%

1 2

1 2

C145 22P_0402_50V8JC145 22P_0402_50V8J

R10733_0402_5% R10733_0402_5%

1 2

R10833_0402_5% R10833_0402_5%

1 2

1 2

C146 22P_0402_50V8JC146 22P_0402_50V8J

+3VS

R112

R112

10K_0402_5%

10K_0402_5%

1 2

@

@

R115

R115

10K_0402_5%

10K_0402_5%

1 2

+3VM_CK505

H_STP_CPU#_R

LOW@U4

LOW@

FSA

FSB

FSC

VGATE

H_STP_PCI#_R

CLK_XTAL_IN

CLK_XTAL_OUT

CLK_PCI_DDR_R

CLK_PCI_DDR_R

PCI2_TME

PCI4_SEL

PCI4_SEL

ITP_EN

ITP_EN

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

NORMAL@

NORMAL@

U4

U4

RTM875N-397-GR

RTM875N-397-GR

U4

55

VDD_SRC

6

VDD_REF

12

VDD_PCI

72

VDD_CPU

19

VDD_48

27

VDD_PLL3

66

VDD_CPU_IO

31

VDD_PLL3_IO

62

VDD_SRC_IO

52

VDD_SRC_IO

23

VDD_IO

38

VDD_SRC_IO

20

USB_0/FS_A

2

FS_B/TEST_MODE

7

REF_0/FS_C/TEST_

8

REF_1

1

CKPWRGD/PD#

11

NC

53

CPU_STOP#

54

PCI_STOP#

5

XTAL_IN

4

XTAL_OUT

13

PCI_1

14

PCI_2

15

PCI_3

16

PCI_4/SEL_LCDCL

17

PCIF_5/ITP_EN

18

VSS_PCI

3

VSS_REF

22

VSS_48

26

VSS_IO

69

VSS_CPU

30

VSS_PLL3

34

VSS_SRC

59

VSS_SRC

42

VSS_SRC

73

VSS

ICS9LVRS387AKLFT MLF

ICS9LVRS387AKLFT MLF

3

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2

C133

C133

47P_0402_50V8J

47P_0402_50V8J

1

C138

C138

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C139

C139

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C141

C141

47P_0402_50V8J

47P_0402_50V8J

7/21 Delete C296, C297 for RF request

7/13 Add 22pF to gnd and close to U3 for RF request

7/21 Reserve 22pF to gnd and close to U3 for RF request

CPU_0#

CPU_1#

SRC_0/DOT_96

SRC_0#/DOT_96#

LCDCLK/27M

LCDCLK#/27M_SS

SRC_2#

SRC_3#

SRC_4#

SRC_6#

SRC_7#

SRC_8/CPU_ITP

SRC_8#/CPU_ITP#

SRC_9#

SRC_10

SRC_10#

SRC_11

SRC_11#

CLKREQ_3#

CLKREQ_4#

CLKREQ_6#

CLKREQ_7#

CLKREQ_9#

SLKREQ_10#

CLKREQ_11#

USB_1/CLKREQ_A#

Compal Secret Data

Compal Secret Data

Compal Secret Data

SDA

SCL

CPU_0

CPU_1

SRC_2

SRC_3

SRC_4

SRC_6

SRC_7

SRC_9

Deciphered Date

Deciphered Date

Deciphered Date

CLK_SMBDATA

9

CLK_SMBCLK

10

CLK_CPU_HPLCLK

71

CLK_CPU_HPLCLK#

70

CLK_CPU_MPLL_C

68

CLK_CPU_MPLL#_C

67

CPU_SSCDREFCLK

24

CPU_SSCDREFCLK#

25

28

29

CLK_CPU_EXP

32

CLK_CPU_EXP#

33

35

36

CLK_PCIE_SATA

39

CLK_PCIE_SATA#

40

CLK_PCIE_WLAN

57

CLK_PCIE_WLAN#

56

61

60

CPU_ITP

64

CPU_ITP#

63

CLK_PCIE_LAN

44

CLK_PCIE_LAN#

45

CLK_PCIE_PCH

50

CLK_PCIE_PCH#

51

CLK_PCIE_WWAN

48

CLK_PCIE_WWAN#

47

37

41

WLAN_CLKREQ#

58

65

LAN_CLKREQ#

43

49

WWAN_CLKREQ#

46

21

CPU_DREFCLK

CPU_DREFCLK#

7/21 Change WWAN_CLKREQ# from REQ4 to REQ11

2

CPU_SSCDREFCLK CPU_SSCDREFCLK#

1

C940

@C940

@

33P_0402_50V8K

33P_0402_50V8K

2

7/13 For RF request

7/13 Add 33pFfor RF request

7/21 Reserve 33pFfor RF request

Q1A

Q1A

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

6 1

+3VS

3

SRC PORT LIST

PORT

SRC0

SRC2

SRC3

SRC4

SRC6

SRC7

SRC8

SRC9

SRC10

SRC11

WLAN_CLKREQ#

WWAN_CLKREQ#

LAN_CLKREQ#

C1067 56P_0402_50V8@C1067 56P_0402_50V8@

C1066 56P_0402_50V8@C1066 56P_0402_50V8@

REQ PORT LIST

REQ_3#

REQ_4#

REQ_6#

REQ_7#

CLK_SMBDATA <10,17>

CLK_SMBCLK <10,17>

CLK_CPU_HPLCLK <7>

CLK_CPU_HPLCLK# <7>

CLK_CPU_MPLL_C <6>

CLK_CPU_MPLL#_C <6>

CPU_SSCDREFCLK <7>

CPU_SSCDREFCLK# <7>

CPU_DREFCLK <7>

CPU_DREFCLK# <7>

CLK_CPU_EXP <6>

CLK_CPU_EXP# <6>

CLK_PCIE_SATA <11>

CLK_PCIE_SATA# <11>

CLK_PCIE_WLAN <17>

CLK_PCIE_WLAN# <17>

CPU_ITP <7>

CPU_ITP# <7>

CLK_PCIE_LAN <22>

CLK_PCIE_LAN# <22>

CLK_PCIE_PCH <12>

CLK_PCIE_PCH# <12>

CLK_PCIE_WWAN <17>

CLK_PCIE_WWAN# <17>

PCH_SMBDATA<13>

PCH_SMBCLK<13>

CLK_PCIE_PCH

CLK_PCIE_PCH#

2010.07.12 RF request

REQ_9#

REQ_10#

WLAN_CLKREQ# <17>

LAN_CLKREQ# <22>

WWAN_CLKREQ# <17>

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

SCHEAMTIC MB A6856

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

REQ_11#

REQ_A#

4019CG

1

1

C941

@C941

@

33P_0402_50V8K

33P_0402_50V8K

2

+3VS

R83

R83

2.2K_0402_5%

2.2K_0402_5%

2

5

4

Q1B 2N7002DW-T/R7_SOT363-6Q1B 2N7002DW-T/R7_SOT363-6

R84

R84

2.2K_0402_5%

2.2K_0402_5%

DEVICE

CPU_DREFCLK

CPU_EXP

PCIE_SATA

PCIE_WLAN

PCIE_LAN

PCIE_PCH

PCIE_WWAN

R99 10K_0402_5%R99 10K_0402_5%

R100 10K_0402_5%R100 10K_0402_5%

R101 10K_0402_5%R101 10K_0402_5%

1 2

1 2

12

12

12

DEVICEPORT

PEIC_WLAN

PCIE_LAN

PEIC_WWAN

of

of

of

934Tuesday, December 21, 2010

934Tuesday, December 21, 2010

934Tuesday, December 21, 2010

1

CLK_SMBDATA

CLK_SMBCLK

+3VS

A

A

A

5

DDR_A_DQS#[0..7]<6>

DDR_A_D[0..63]<6>

DDR_A_DM[0..7]<6>

DDR_A_DQS[0..7]<6>

DDR_A_MA[0..14]<6>

D D

+1.5V

2

C99

C99

1

+1.5V

1

1

+

+

C106

C106

C107

C107

C108

2

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

C C

B B

A A

C108

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Layout Note:

Place one cap close to every 2 pullup

resistors terminated to +0.75VS

+0.75VS

C111

C111

0.1U_0402_16V4Z

0.1U_0402_16V4Z

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C109

C109

C110

C110

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2010.03.27 Add CZ03,CZ04 for ESD

1

C112

C112

2