Page 1

1

VER : E3D

2

3

4

5

6

7

8

BOM P/N

31TE1MB0010

31TE1MB0120

31TE1MB0130

31TE1MB0140

A A

31TE1MB0170

31TE1MB01N0

31TE1MB01M0

31TE1MB01P0

31TE1MB01Q0

31TE1MB01S0

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : GND1

B B

LAYER 3 : IN1

LAYER 4 : VCC

LAYER 5 : IN2

LAYER 6 : IN3

LAYER 7 : GND2

LAYER 8 : BOT

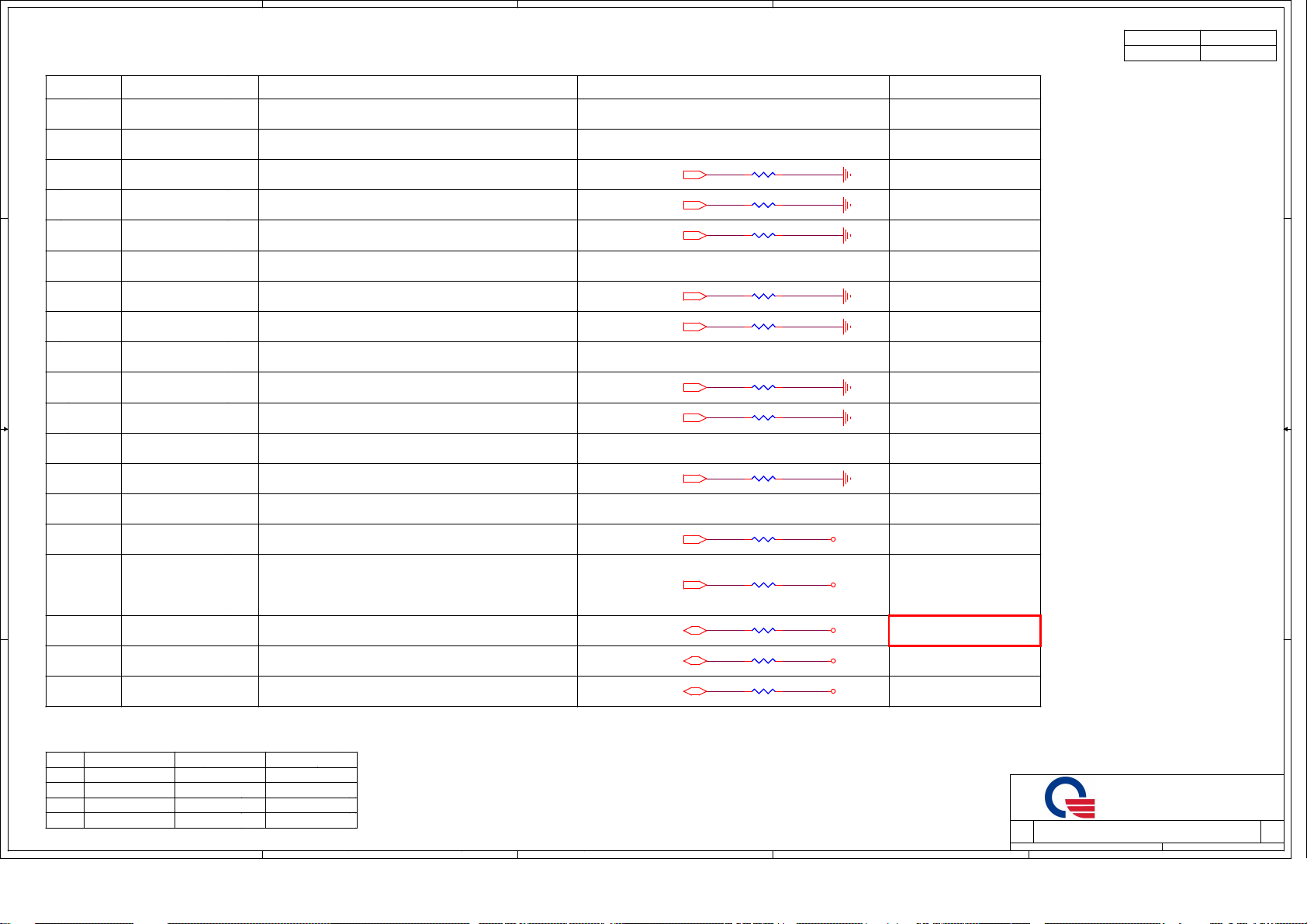

BOM Option Table

Reference

IV@

C C

D D

Description

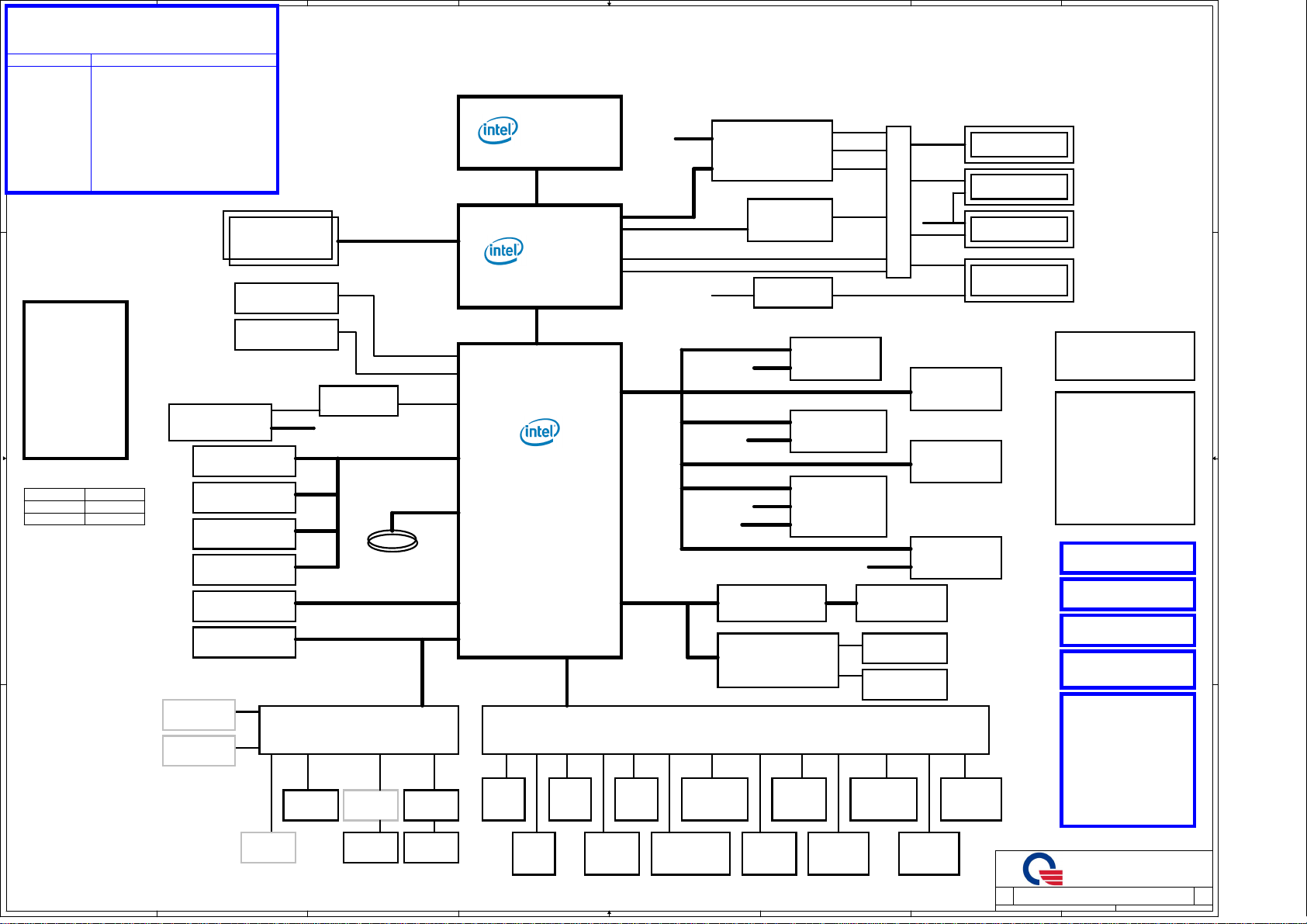

TE1M MB(PM45/RB/MS)WO CPU

TE1M MB(PM45/MAIN/RB/HDMI/CIR)WO CPU

TE1M MB(GM45/EXP/NO CIR/MS)WO CPU

TE1M MB(GM45/GS/EXP/MS)WO CPU

TE1M MB(GM45/GS/EXP/LC)WO CPU

TE1M MB(GM45/HDMI/EXP/MS)WO CPU

TE1M MB(GM45/HDMI/GS/CIR/MS)WO CPU

TE1M MB ASY(GL40/PC/GS/FE/HD/KI,MS)WOCPU

TE1M MB ASY(GM45/PC/GS/FE/HD/KI,MS)WOCPU

TE1M MB(PM45/HDMI/NO CIR/MS)WO CPU

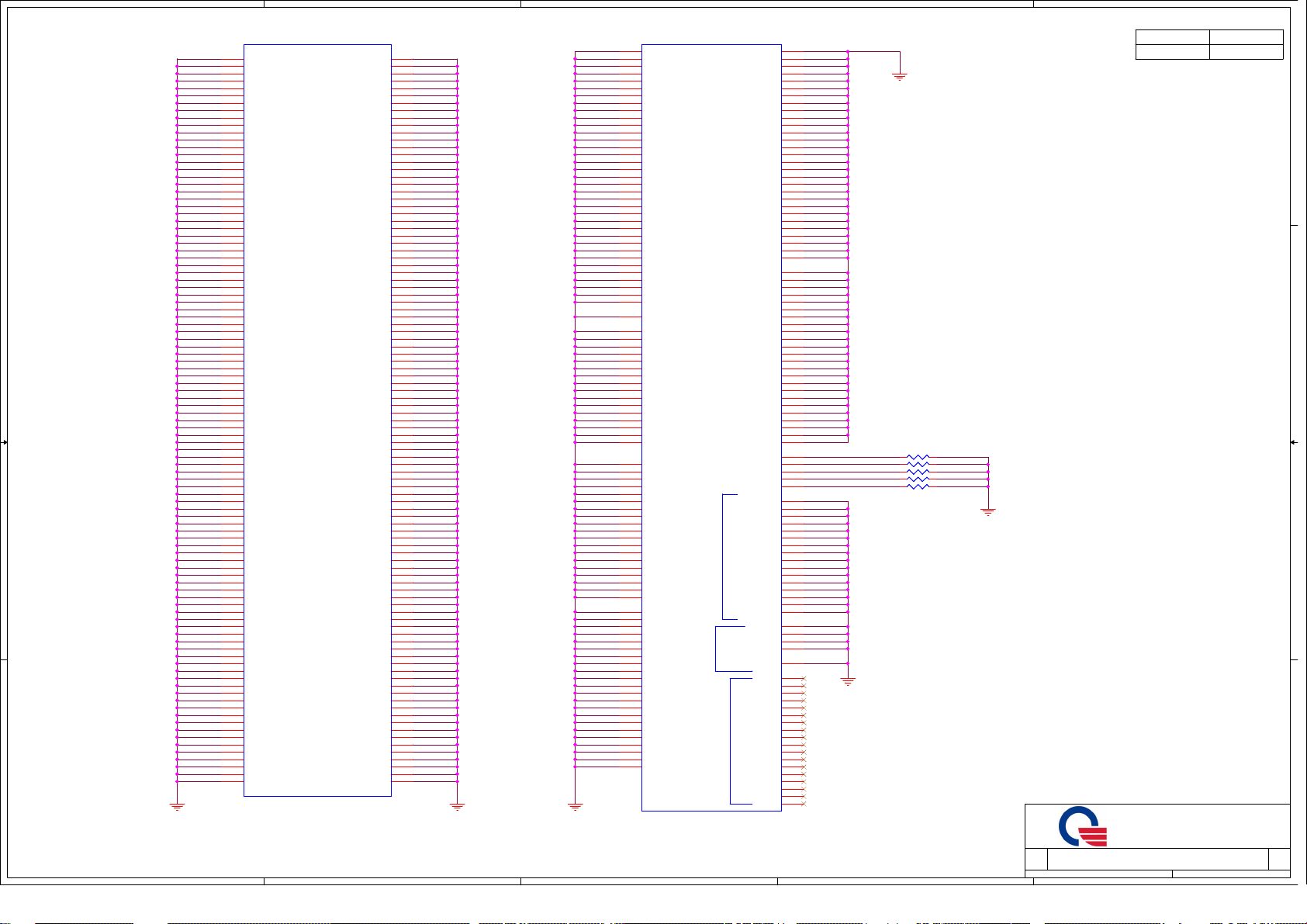

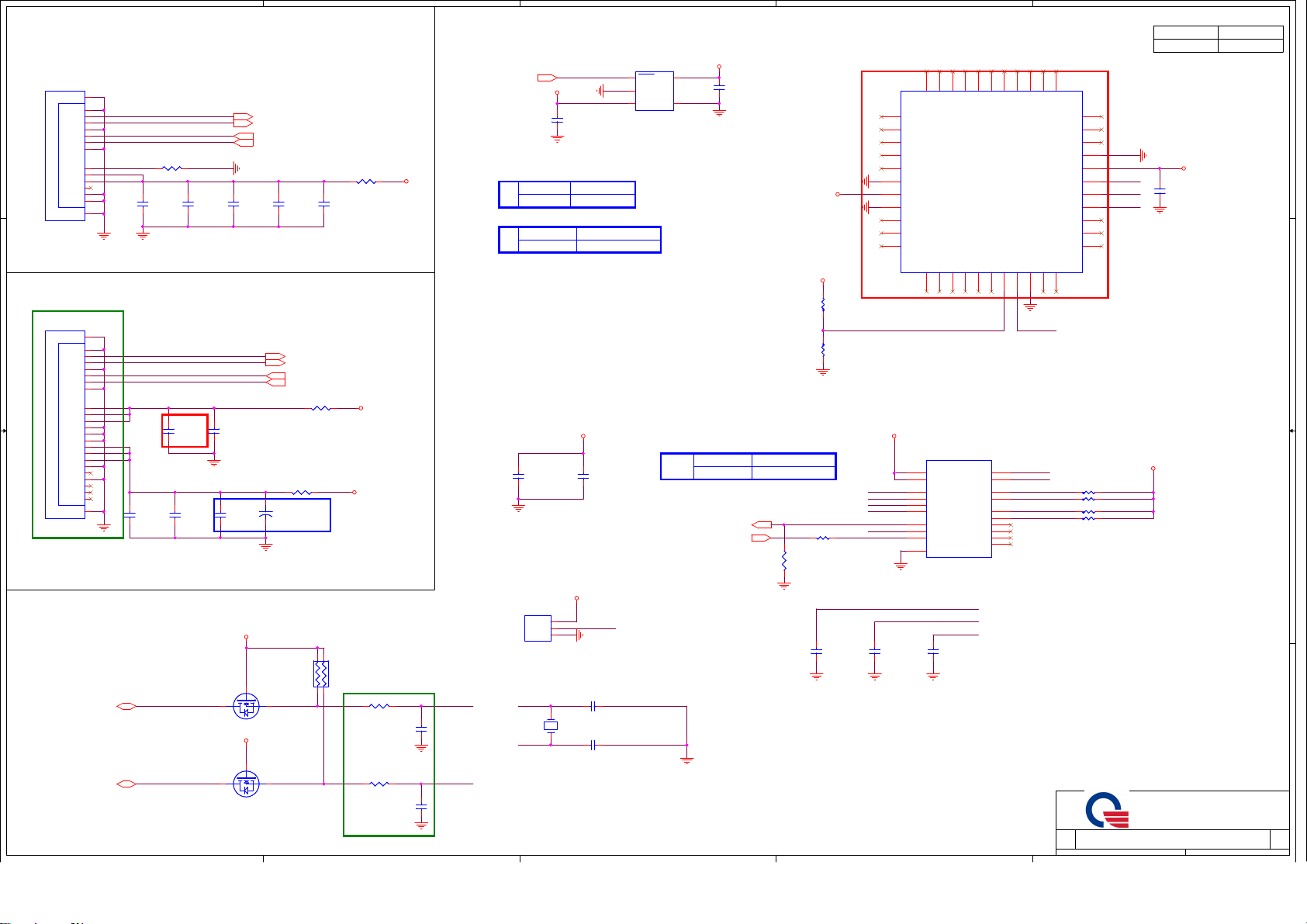

USB/ESATA

Finger Printer

(FTB)

Description

INT VGA

EXT VGAEV@

Bluetooth Con.

Felica Con.

(FTB)

USB Port

W25X16VSS1G

SPI FLASH

MDC Con.

INT_ MIC

INT_ MIC

P19

P29

DDRII-SODIMM1

DDRII-SODIMM2

SATA - HDD

SATA - ODD

USB-7

P27

P26

P26

P26

P27

P13

P30

MIC JACK

Port-C (FM)

P16,17

P22

P22

PI2EQX3201B

Re-driver

USB-1

USB-2

USB-4

USB-6

CX20561-12Z

AUDIO CODEC

Port-B

HP AMP

P30

Dual Channel DDR II

667/800 MHZ

SATA 0

SATA 1

SATA 4

P27

USB 2.0 (Port0~9)

BATTERY

P12

SPI

Azalia

Port-A

SPK AMP

P30

TE1M Block Diagram

P29

DDR SYSTEM MEMORY

SATA

USB

Intel I/O Controller Hub 9

(ICH9M)

NB

RTC

P12, 13, 14, 15

SPI

IHDA

VR

P29

P30

PENRYN

478P uFCPGA

FSB

P3,4

FSB(667/800/1066MHZ)

FSB

PCI-E

CANTIGA

NB

P5,7,8,9,10,11

DMI

DMI(x2/x4)

DMI

PCI-E

PCI

LPC

LPC

WPC8763LDG

EC

Kill SW

Graphics Interfaces

PCI-Express

PCI Bus

CIR

Azalia

VGA Con.

(FOX)

PCI-E x16

PCIE

INT_CRT

INT_LVDS

PCIE-1

PCIE-2

PCIE-3

PCIE-4

PCIE-5

PCIE-6

LIS3L02AQ3

P28 P26

G-Sensor

PI3VDP411LST

HDMI level shift

R5F211A4SP

CEC

USB-9

USB-8

USB-0

Port-C (FM)

CB1410

PCMCIA Controller

OZ129T

Cardreader/1394 Controller

P28

MMB Board

Con.

EXT_CRT

EXT_LVDS

EXT_HDMI

P18

INT_HDMI

P21

CEC_I2CI2C

P21

NEW CARD Con.

P27

MINI CARD-2

U 5.6H_TV/ROBSON

D 7.5H_HD-DVD

LAN/ USB/ FM

Con.

P25

P26

USB-5

PCMCIA SOCKET

P23 P23

Cardreader Con.

5 IN 1

P24

1394 Con.

Touch Pad

Board Con.

P26P27 P22

USB-3

SWITCH CIRCUIT

MINI CARD-3

U 9H_HD-DVD

MINI CARD-4

D ROBSON

MINI CARD-1

U&D 5.6H_WLAN

P24

P24

Power

Board Con.

CRT Con.

LCD/CCD Con.

LED/CCD Con.

HDMI Con.

P25

(FTB)

P25

P25

P26

P20

P19

P19

P21

ICS9LPR365

CLOCK GENERATOR

POWER SYSTEM

ISL88731

ISL6237

ISL6266A

RT8202

TPS51116

APL5913

G909

LED POWER DRIVER

ISL97636

VCC_CORE

+1.5V

+1.05V

+1.8VSUS

+1.8V

+1.5V_S5

+3VPCU

+3V_S5

+3VSUS

+3V

+5VPCU

+5V_S5

+5V

+SMDDR_VTERM

+SMDDR_VREF

CK505

P31

P32

P33

P34

P35

P36

P36

P19

P2

LED Board

Con.

Quanta Computer Inc.

Quanta Computer Inc.

P26P3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

TE1M

TE1M

TE1M

8

1 40Monday, May 26, 2008

1 40Monday, May 26, 2008

1 40Monday, May 26, 2008

E3D

E3D

E3D

P19

Low Cost

Board Con.

6

FM

1

2

HP/SPDIF SPK Con.

P30P29

3

P29

FAN

4

K/B Con.

W25X16VSS1G

SPI FLASH

P28P26 P26

5

EC2648

HALL SENSOR

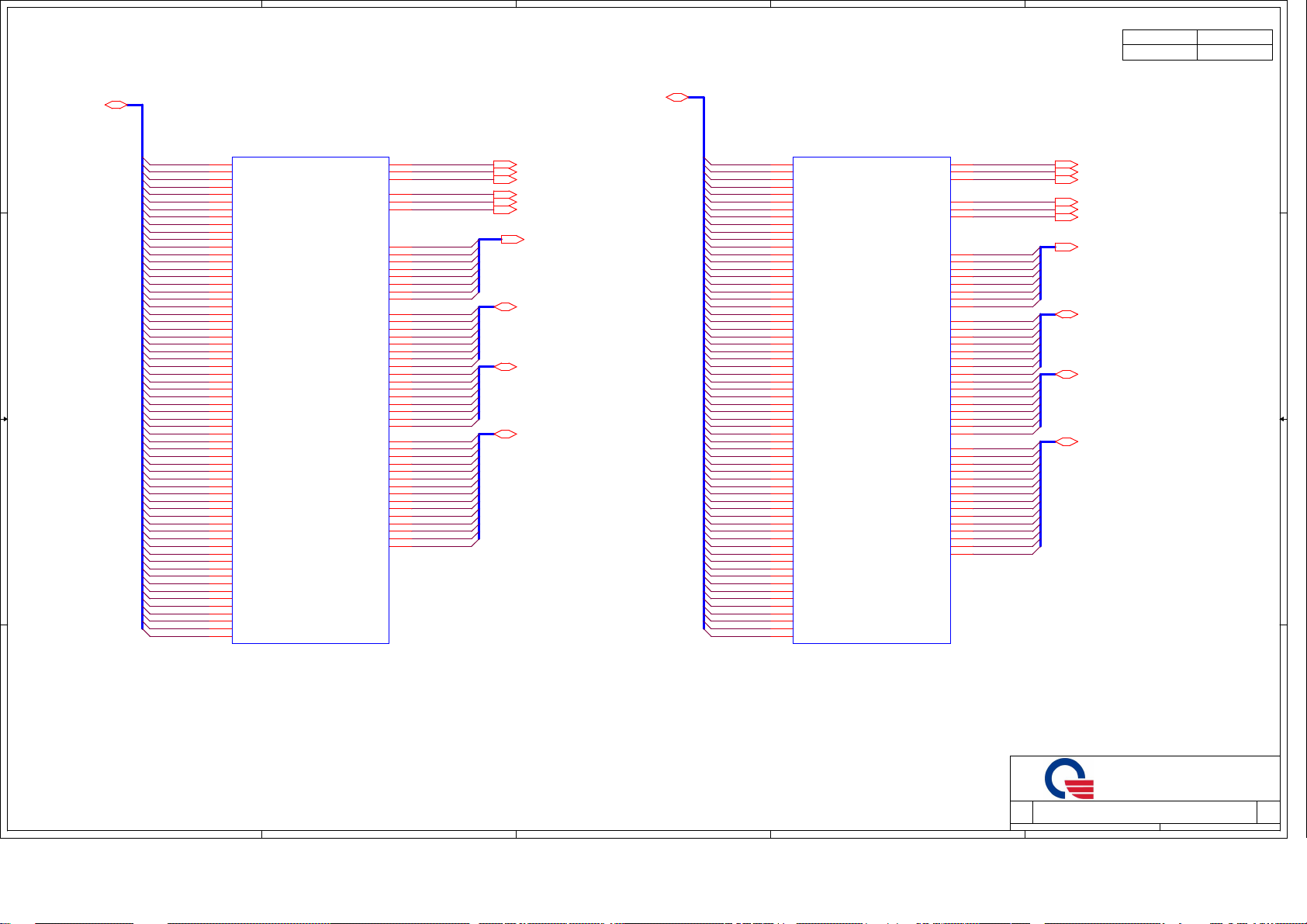

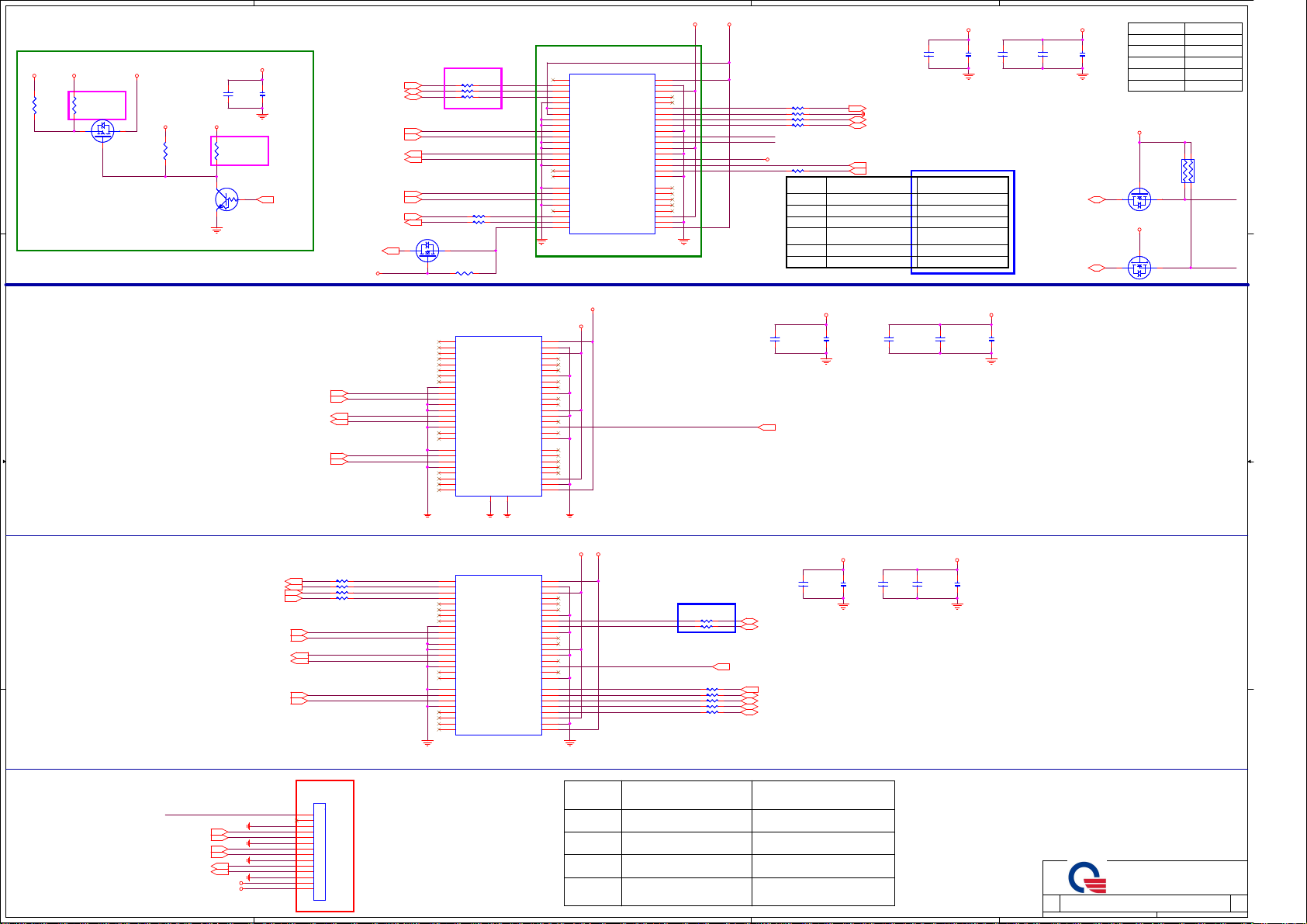

Page 2

5

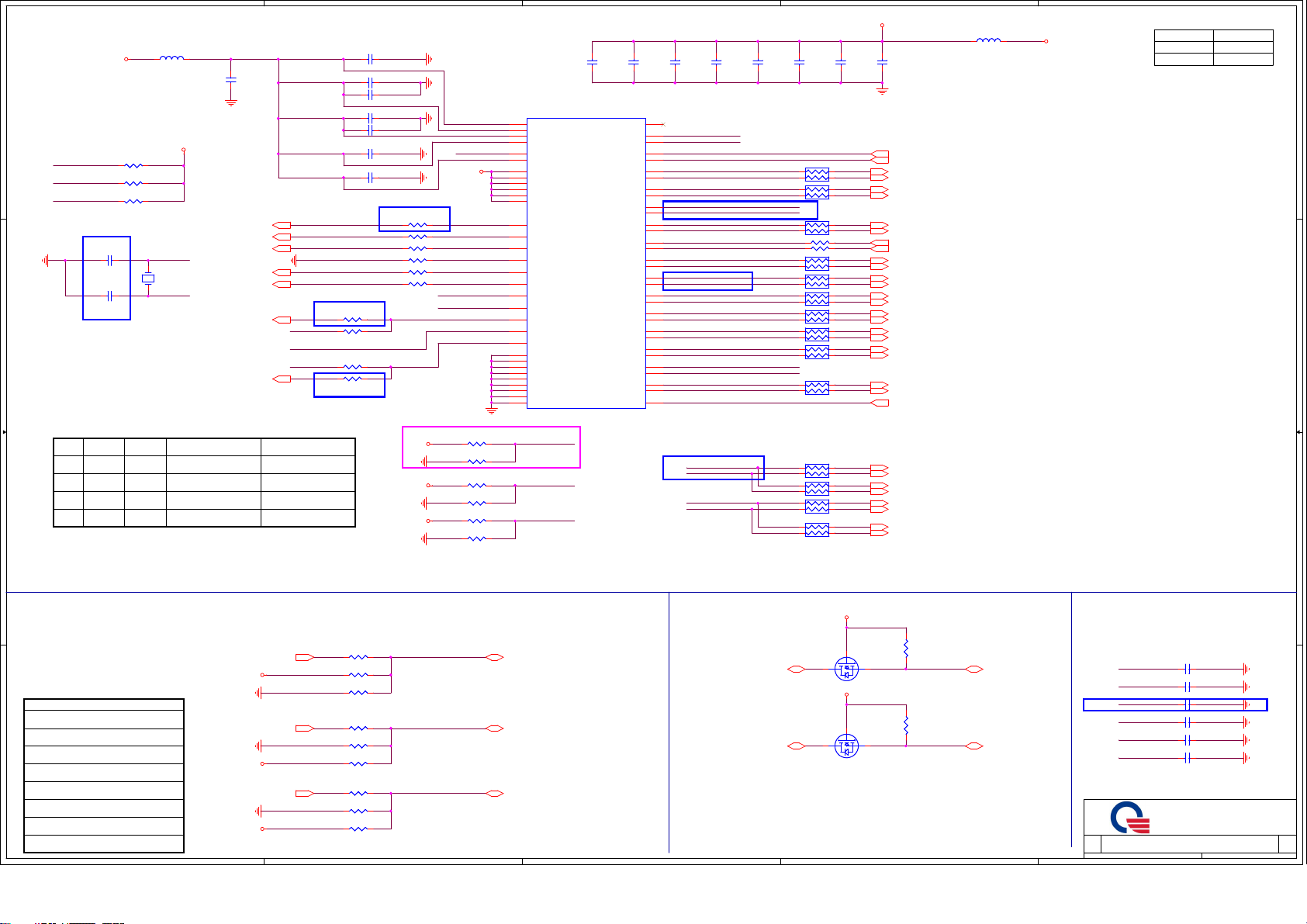

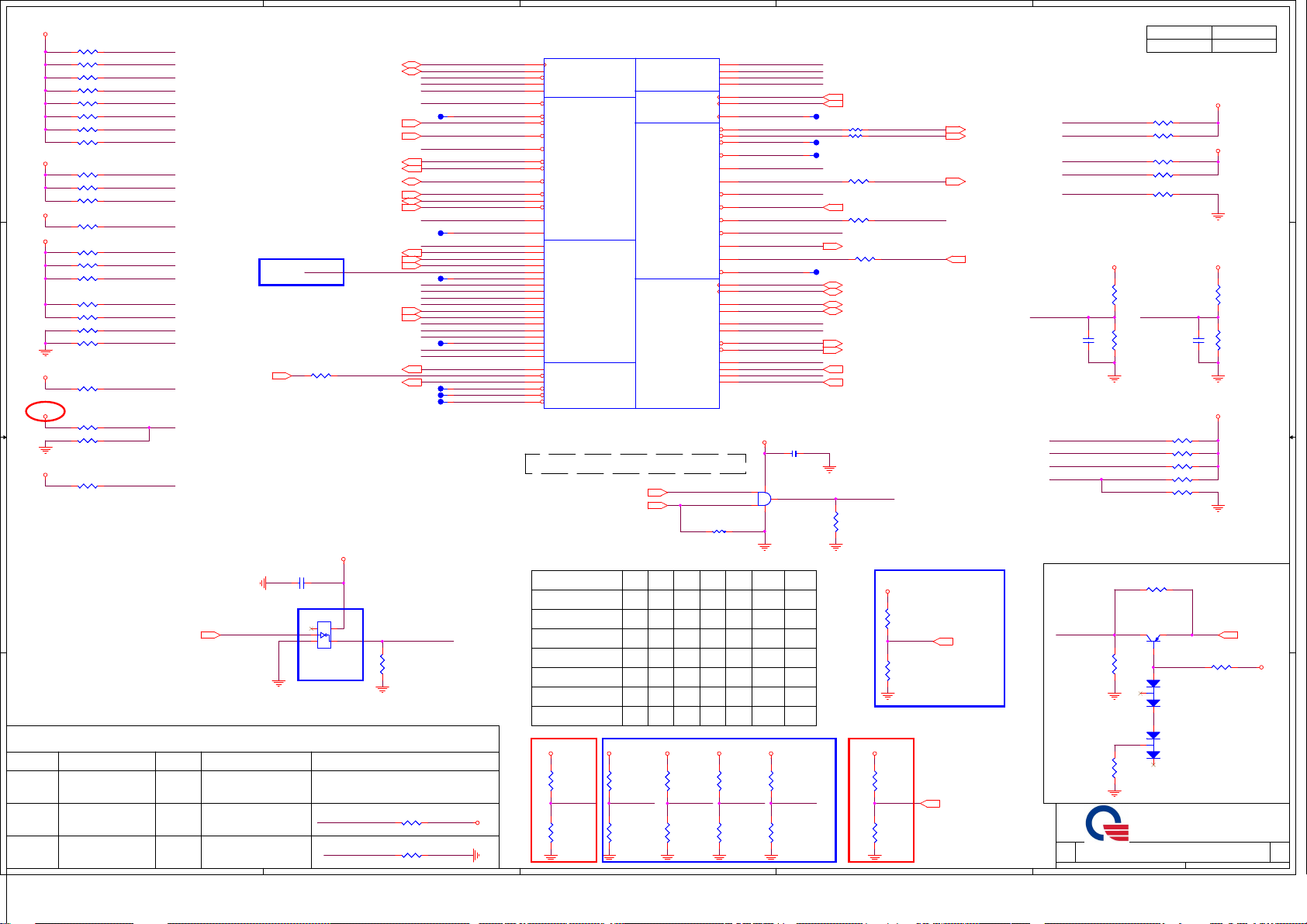

Clock Generator

L518 PBY16080 8T-301Y-N_6L518 PBY16080 8T-301Y-N_6 C700 0.1u/10V _4C700 0.1u/10V _4 C208

+3V

D D

+3V

PM_STPPCI#

PM_STPCPU#

NEW_CLKREQ#_R

R219 2.2 K_4R219 2.2 K_4

R218 2.2 K_4R218 2.2 K_4

R215 10K_4R215 10K_4

C226 27p/50V_4C226 27p/50V_4

CL=20p

C239 27p/50V_4C239 27p/50V_4

CG_XIN PCI_CLK_SIO_R

21

Y3

14.318MHZY314.318MHZ

CG_XOUT

B2A

C C

ICS9LPRS365

RTM875T-606

(ALPRS365K13)

(AL000875K06)

PCI2/TME

PCI2/TME

PCI-3

PCI-4/27M_SEL

PCIF-5/ITP_EN

internal PD

PCI-3/SRC5_EN

internal PD

PCI-4/27M_SEL

internal PD

PCIF-5/ITP_EN

internal PD

Pin 4

Pin 5

Pin 6

Pin 7

B B

PULL HIGH PULL DOWN

NO OVERCLOCKING NORMAL RUN

PIN37/38 IS SRC5

PIN 17/18 IS 27MHz

PIN 46/47 IS CPUITP PIN 46/47 IS SRC8

C704

C704

10u/10V_8

10u/10V_8

PCLK_DEB UG25

PCLK_PCM23

PCLK_OZ1 2924

PCLK_59128

PCLK_ICH13

CLKUSB_4 814

14M_ICH14

(default)

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

PIN37/38 IS

PCI_STOP/CPU_STOP

PIN 17/18

IS SRC/DOT

PCLK_OZ1 29

PCLK_ICH

B2A

R234 47_4R234 47_4

R227 2.2K_4R227 2.2K _4

R243 10K_4R243 10K_ 4

R237 47_4R237 47_4

B2A

(default)

(default)

(default)

4

C695 0.1u/10V _4C695 0.1u/10V _4

C706 10u/10V_8C706 10u/10V_8

C694 0.1u/10V _4C694 0.1u/10V _4

C676 0.1u/10V _4C676 0.1u/10V _4

C643 0.1u/10V _4C643 0.1u/10V _4

C699 0.1u/10V _4C699 0.1u/10V _4

B2A

R252 47_4R252 47_4

R249 33_4R249 33_4

R247 33_4R247 33_4

R244 10K_4R244 10K_4

R238 33_4R238 33_4

R235 33_4R235 33_4

C3B

+3V

+3V

+3V

VDD_CK_VDD_PCI

VDD_CK_VDD_48

VDD_CK_VDD_PCI

VDD_CK_VDD_REF

VDD_CK_VDD_PCI

VDD_CK_VDD_CPU

+1.05V_V DD

PCLK_DEB UG_RPCLK_DEB UG

PCLK_PCM_R

PCLK_OZ1 29_R

PCLK_591_RPCLK_591

PCLK_ICH_ R

CG_XIN

CG_XOUT

FSA

FSB

FSC

R250 10K_4R250 10K_ 4

R246 *10K_4R246 *10K_4

R242 *10K_4R242 *10K_4

R241 10K_4R241 10K_ 4

R230 *10K_4R230 *10K_4

R229 10K_4R229 10K_ 4

U12

U12

2

VDD_PCI

9

VDD_48

16

VDD_PLL3

61

VDD_REF

39

VDD_SRC

55

VDD_CPU

12

VDD_96_IO

20

VDD_PLL3_IO

26

VDD_SRC_IO_1

45

VDD_SRC_IO_3

36

VDD_SRC_IO_2

49

VDD_CPU_IO

1

PCI0/CR#_A

3

PCI1/CR#_B

4

PCI2/TME

5

PCI3

6

PCI4/SRC5_EN

7

PCIF5/ITP_EN

60

XTAL_IN

59

XTAL_OUT

10

USB_48/FSA

57

FSB/TEST/MODE

62

REF0/FSC/TESTSEL

8

VSS_PCI

11

VSS_48

15

VSS_IO

19

VSS_PLL3

52

VSS_CPU

23

VSS_SRC1

29

VSS_SRC2

42

VSS_SRC3

58

VSS_REF

PCLK_OZ1 29

PCLK_591

HIGH 27MHz

LOW SRC

PCLK_ICH

3

C204

C204

C205

C205

*10u/10V _8

*10u/10V _8

10u/10V_8

10u/10V_8

48

IO_VOUT

CGCLK_SMB

64

SCLK

CGDAT_SMB

63

CK505

CK505

CKPWRGD/PWRDWN#

SDA

PM_STPPCI#

CPU0

CPU0#

CPU1

CPU1#

SRC8/ITP

SRC8#/ITP#

SRC10#

SRC10

SRC11/CR#_H

SRC11#/CR#_G

SRC9

SRC9#

SRC7/CR#_F

SRC7#/CR#_E

SRC6

SRC6#

SRC4

SRC4#

SRC3/CR#_C

SRC3#/CR#_D

SRC2/SATA

SRC2#/SATA#

SRC1/SE1

SRC1#/SE2

SRC0/DOT96

SRC0#/DOT96#

ICS9LPRS365BGLFT

ICS9LPRS365BGLFT

38

PM_STPCPU#

37

CLK_CPU_BCLK_R

54

CLK_CPU_BCLK#_R

53

CLK_MCH_B CLK_R

51

CLK_MCH_B CLK#_R

50

CLK_PCIE_MINI2&4_R

47

CLK_PCIE_MINI2&4#_R

46

CLK_PCIE_3GPLL# _R

35

CLK_PCIE_3GPLL_ R

34

CLK_MCH_O E#_R

33

NEW_CLKREQ#_R

32

CLK_PCIE_NEW_R

30

CLK_PCIE_NEW_R#

31

CLK_PCIE_MINI3_R

44

CLK_PCIE_MINI3#_R

43

CLK_PCIE_MINI_R

41

CLK_PCIE_MINI#_R

40

CLK_PCIE_LAN_R

27

CLK_PCIE_LAN#_R

28

CLK_PCIE_ICH_R

24

CLK_PCIE_ICH#_R

25

CLK_PCIE_SATA_R

21

CLK_PCIE_SATA#_R

22

DREFSSCLK _R

17

DREFSSCLK #_R

18

DREFCLK_R

13

DREFCLK#_ R

14

56

SRC5/PCI_STOP#

SRC5#/CPU_STOP#

<MAIN>:ICS9LPRS365BGLFT QCI:ALPRS365K13

<SECOND>:SLG8SP512TTR: QCI:AL8SP512K05

B2A

C685

C685

0.1u/10V _4

0.1u/10V _4

CLK_PCIE_MINI2&4_R

CLK_PCIE_MINI2&4#_R

DREFSSCLK _R

DREFSSCLK #_R

C206

C206

0.1u/10V _4

0.1u/10V _4

B2A

C207

C207

C677

C677

0.1u/10V _4

0.1u/10V _4

0.1u/10V _4

0.1u/10V _4

RP52 0 X2RP52 0 X2

RP50 0 X2RP50 0 X2

RP42 0 X2RP42 0 X2

R217 475/F_4R217 475/F_4

R216 475/F_4R216 475/F_4

RP43 0 X2RP43 0 X2

RP47 0 X2RP47 0 X2

RP45 0 X2RP45 0 X2

RP44 0 X2RP44 0 X2

RP46 0 X2RP46 0 X2

RP48 0 X2RP48 0 X2

RP53 IV@0X2RP53 IV@0X2

RP49 IV@0X2RP49 IV@0X2

RP514 EV@0X2RP514 EV@0X2

RP512 IV@0X2RP512 IV@0X2

RP51 E V@0X2RP51 EV @0X2

1

3

1

3

1

3

3

1

1

3

1

3

3

1

3

1

3

1

3

1

1

3

3

1

1

3

3

1

B2A

2

4

2

4

2

4

4

2

2

4

2

4

4

2

4

2

4

2

4

2

2

4

4

2

2

4

4

2

C211

C211

0.1u/10V _4

0.1u/10V _4

+1.05V_V DD

2

C208

0.1u/10V _4

0.1u/10V _4

PM_STPPCI# 14

PM_STPCPU# 14

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

CLK_MCH_B CLK 5

CLK_MCH_B CLK# 5

CLK_PCIE_3GPLL# 6

CLK_PCIE_3GPLL 6

CLK_MCH_O E# 6

NEW_CLKREQ# 27

CLK_PCIE_NEW 27

CLK_PCIE_NEW# 27

CLK_PCIE_MINI3 25

CLK_PCIE_MINI3# 25

CLK_PCIE_MINI 25

CLK_PCIE_MINI# 25

CLK_PCIE_LAN 26

CLK_PCIE_LAN# 26

CLK_PCIE_ICH 13

CLK_PCIE_ICH# 13

CLK_PCIE_SATA 12

CLK_PCIE_SATA# 12

DREFCLK 6

DREFCLK# 6

CK_PWRGD 14

CLK_PCIE_MINI2 25

CLK_PCIE_MINI2# 25

CLK_PCIE_MINI4 25

CLK_PCIE_MINI4# 25

DREFSSCLK 6

DREFSSCLK # 6

CLK_MXM 18

CLK_MXM# 18

L17PBY16080 8T-301Y-N_6 L17PBY160808T-301 Y-N_6

To SB

To CPU

To NB

To NB

To New Card

To MINI3

To MINI1

To LAN

To SB

To SB

To NB

To MINI2

To MINI4

To NB

To VGA Card

+1.05V

1

BOM Option Table

Reference

IV@

Description

INT VGA

EXT VGAEV@

Clock Gen I2CFREQ. SEL TABLE

R601 0_4R601 0_4

R600 *5 6_4R600 *5 6_4

R602 1K_4R602 1K_4

BSEL Frequency Select Table

CPU_BSEL 03

+1.05V

FSC FSB FSA Frequency

0

0

266Mhz0

0

0

1

A A

0

1

0

1

1

1

0

1

0

1

133Mhz

1

166Mhz

0

200Mhz

400Mhz

011

1

Reserved

1

100Mhz

0

333Mhz

5

CPU_BSEL 13

+1.05V

CPU_BSEL 23

+1.05V

R228 0_4R228 0_4

R226 *0 _4R226 *0 _4

R225 1K_4R225 1K_4

R598 0_4R598 0_4

R232 *0 _4R232 *0 _4

R593 1K_4R593 1K_4

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

4

MCH_BSEL0 6

MCH_BSEL1 6

MCH_BSEL2 6

SDATA14,21,25 ,27

SCLK14,21,25 ,27

3

+3V

R245

Q507

Q507

2

RHU002N06

RHU002N06

3

+3V

Q509

Q509

2

RHU002N06

RHU002N06

3

R245

10K_4

10K_4

2

R248

R248

10K_4

10K_4

CGDAT_SMB

CGCLK_SMB

CGDAT_SMB 17

CGCLK_SMB 17

1

1

PCLK_PCM

C225 *33p/50V _4C225 *33p/50V_4

PCLK_591

C219 *33p/50V _4C219 *33p/50V_4

CLKUSB_4 8

B2A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Clock Gen

Clock Gen

Clock Gen

Date: Sheet of

Date: Sheet of

Date: Sheet of

C214 15p/50V_4C214 15p/50V_4

14M_ICH

C216 *33p/50V _4C216 *33p/50V_4

PCLK_ICH

C215 *33p/50V _4C215 *33p/50V_4

PCLK_DEB UG

C224 *33p/50V _4C224 *33p/50V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

TE1M

TE1M

TE1M

2 40Monday, May 26, 2 008

2 40Monday, May 26, 2 008

2 40Monday, May 26, 2 008

E3D

E3D

E3D

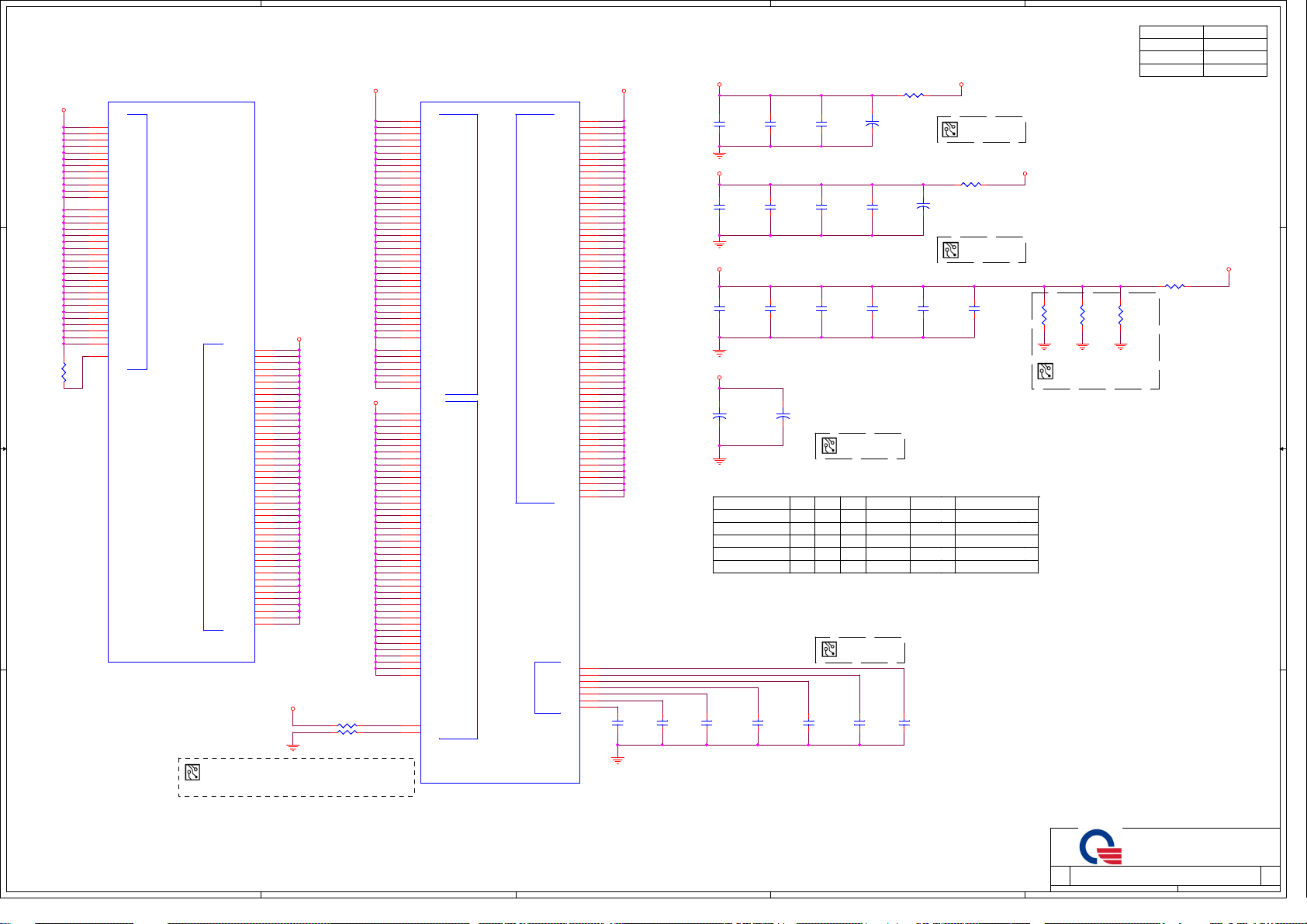

Page 3

5

H_A#[3..1 6]5

D D

H_ADSTB#05

H_REQ#[0..4]5

H_A#[17..35]5

H_ADSTB#15

H_A20M#12

H_FERR#12

C C

H_IGNNE#12

H_STPCLK#12

H_INTR12

H_NMI12

H_SMI#12

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

R32 0_4R3 2 0_4

H_INTR

H_NMI

H_SMI#

T6T6

T7T7

T8T8

T9T9

T502T502

T501T501

T14T14

T500T500

T10T10

AA4

AB2

AA3

D22

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

K3

H2

K2

J3

L1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

D2

D3

F6

U501A

U501A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

Penryn_1p0

Penryn_1p0

ADDR GROUP_0

ADDR GROUP_0

ADDR GROUP_1

ADDR GROUP_1

ICH

ICH

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

THERMAL

THERMAL

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

RESERVED

RESERVED

TDI

H_ADS#

H1

H_BNR#

E2

H_BPRI#

G5

H_DEFER#

H5

H_DRDY#

F21

H_DBSY#

E1

H_BREQ#

F1

H_IERR#

D20

H_INIT#

B3

H_LOCK#

H4

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

H_TRDY#

G2

H_HIT#

G6

H_HITM#

E4

XDP_BPM# 0

AD4

XDP_BPM# 1

AD3

XDP_BPM# 2

AD1

XDP_BPM# 3

AC4

XDP_BPM# 4

AC2

XDP_BPM# 5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

XDP_TDO

AB3

XDP_TMS

AB5

XDP_TRST#

AB6

C20

H_PROCHOT#_ D

D21

H_THERMDA

A24

H_THERMDC

B25

CPU_PM_THRMTRIP #

C7

CLK_CPU_BCLK

A22

CLK_CPU_BCLK#

A21

4

H_ADS# 5

H_BNR# 5

H_BPRI# 5

H_DEFER# 5

H_DRDY# 5

H_DBSY# 5

H_BREQ# 5

H_INIT# 12

H_LOCK# 5

H_RS#0 5

H_RS#1 5

H_RS#2 5

H_TRDY# 5

H_HIT# 5

H_HITM# 5

T12T12

T11T11

T3T3

T13T13

T2T2

T1T1

R44 0_4R4 4 0_4

CLK_CPU_BCLK 2

CLK_CPU_BCLK# 2

ZS2 Default no use this function

R46 56_4R46 56_4

C3A

L54 BK1608L M252-T_6L54 BK1608L M252-T_6

near CPU side

Connect it to CPU DBR# is for ITP debug port

or CPU interposer (like ICE) to reset the system

SYS_RST#XDP_DBRESET#

SYS_RST# 14

H_CPURST#

+1.05V

Layout note:

H_GTLREF: Zo=55 ohm,L<0.5"

2/3*VCCP+-2%

H_CPURST# 5

+1.05V

R81

R81

1K/F_4

1K/F_4

R75

R75

2K/F_4

2K/F_4

3

H_D#[0..63]

U501B

AD26

AF26

G22

G25

G24

H22

H23

H26

H25

N22

R23

M24

M23

R24

N25

M26

N24

C23

D25

C24

AF1

C21

E22

F24

E26

F23

E25

E23

K24

J24

J23

F26

K22

J26

K25

P26

L23

L22

P25

P23

P22

T24

L25

T25

L26

A26

B22

B23

C3

U501B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

BSEL[0]

BSEL[1]

BSEL[2]

Penryn_1p0

Penryn_1p0

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#05

H_DSTBP#05

H_DINV#05

H_DSTBN#15

H_DSTBP#15

H_DINV#15

CPU_BSEL 02

CPU_BSEL 12

CPU_BSEL 22

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

H_GTLREF

CPU_TEST1

T15T15

CPU_TEST2

T17T17

CPU_TEST3

T16T16

CPU_TEST4

T21T21

CPU_TEST5

T4T4

CPU_TEST6

T20T20

CPU_TEST7

T5T5

CPU_BSEL 0

CPU_BSEL 1

CPU_BSEL 2

MISC

MISC

DATA GRP 0

DATA GRP 0

DATA GRP 1

DATA GRP 1

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

2

H_D#[0..63] 5

H_D#32

Y22

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

H_DSTBN#2

Y26

H_DSTBP#2

AA26

H_DINV#2

U22

H_D#48

AE24

H_D#49

AD24

H_D#50

AA21

H_D#51

AB22

H_D#52

AB21

H_D#53

AC26

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AC25

H_D#58

AE21

H_D#59

AD21

H_D#60

AC22

H_D#61

AD23

H_D#62

AF22

H_D#63

AC23

H_DSTBN#3

AE25

H_DSTBP#3

AF24

H_DINV#3

AC20

COMP0

COMP1

COMP2

COMP3

ICH_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGD

H_CPUSLP#

PSI#

R80 27.4/F_6R80 27.4/F_6

R74 54.9/F_4R74 54.9/F_4

R22 27.4/F_6R22 27.4/F_6

R21 54.9/F_4R21 54.9/F_4

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

PSI#

H_DSTBN#2 5

H_DSTBP#2 5

H_DINV#2 5

H_DSTBN#3 5

H_DSTBP#3 5

H_DINV#3 5

ICH_DPRSTP# 6 ,12,33

H_DPSLP# 12

H_DPWR# 5

H_CPUSLP# 5

PSI# 33

Layout note:

ICH_DPRSTP# , Daisy Chain

(SB>PowerIC>NB>CPU)

1

BOM Option Table

Reference

N/A

Layout note:

comp0,2: Zo=27.4ohm, L<0.5"

comp1,3: Zo=55ohm, L<0.5"

H_PWRGD 12

B2A

Description

N/A

Thermal Trip

DELAY_VR_ PWRGOO D6,14,33

B B

+1.05V

Processor hot

A A

H_PROCHOT#_ D

+1.05V

3

Q5

2

FDV301NQ5FDV301N

1

C3A

R41

R41

1K_4

1K_4

R37

+1.05V

R37

56.2/F_4

56.2/F_4

Q6

2

MMBT3904Q6MMBT3904

SYS_SHDN#CPU_PM_THRMTRIP #

1 3

B2A

R38 *0_4R3 8 *0_4

R48

R48

56_4

56_4

PM_THRMTRIP#

No use Thermal trip CPU side still PU 56ohm.

Use Thermal trip can share PU at SB side

No use PROCHOT CPU side still PU 56ohm.

Use PROCHOT to optional receiver CPU side PU

68ohm and through isolat 2.2K ohm to receiver

side

R51 *2.2K_4R51 *2.2K_4

R57 *0_4R5 7 *0_4

5

+1.05V

R40

R40

*10K_4

*10K_4

R39

R39

100K_4

100K_4

SYS_SHDN# 32

PM_THRMTRIP# 6,12

D2

*BAS316D2*BAS316

H_PROCHOT# 33

+1.05V

R31

R31

*51/F_4

*51/F_4

H_CPURST#

Reserve 1K for XDP function

CPU FAN CTRL

SYSFANON#18

VFAN28

4

12

+5V

C89 2.2u/6.3V_6C89 2.2u/6.3V_6

R94 0_4R9 4 0_4

B2A

U502

U502

VIN2VO

GND

1

/FON

GND

GND

4

VSET

GND

G995

G995

FANPWR = 1.6*VSET

Reserve 1K for XDP function

XDP_TDO

R23 *51/F_4R23 *51/F_4

XDP_TDI

R24 56_4R24 56_4

XDP_TMS

R19 54.9/F_4R19 54.9/F_4

XDP_TCK

R25 56_4R25 56_4

XDP_TRST#

R20 56_4R20 56_4

TH_FAN_POW ER

3

5

6

C87

C87

7

8

10u/10V_8

10u/10V_8

FANSIG28

C90

C90

0.01u/16 V_4

0.01u/16 V_4

3

+1.05V

FANSIG

C91

C91

*0.01u/16V_4

*0.01u/16V_4

+3V

R95

R95

10K_4

10K_4

CN504

CN504

1

2

3

FAN_CON

FAN_CON

B2A

CPU Thermal monitorXDP

+3V

2

Q11

Q11

SYS_SHDN#32

3

RHU002N06

RHU002N06

+3V

+3V

+3V

2ND_MBCLK22,28

2ND_MBDATA22,28

THERM_ALERT#14

1

2

3

Q10 RHU002N06Q10 RHU002N06

NS LM95245 PU this pin

R93 10K_4R93 10K_4

R97 *0_4R9 7 *0_4

R49 10K_4R49 10K_4

R79 330_4R79 330_4

Q7 MMBT3904Q7 MMBT3904

C62

C62

*1u/16V_ 6

*1u/16V_ 6

2

1

2

2ND_MBCLK #

2ND_MBDATA#

THERM_ALERT#_R

THER_SHD#

13

B2A

R92

R92

10K_4

10K_4

+3V+3V

LM86VCC

R50 200_6R5 0 200_6

R91

R91

10K_4

10K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

MSOP8

C3A

U503

U503

8

VCC

SCLK

7

DXP

SDA

6

DXN

ALERT#

4

GND

OVERT#

LM95245

LM95245

ADDRESS: 98H

LM95245 : AL095245000

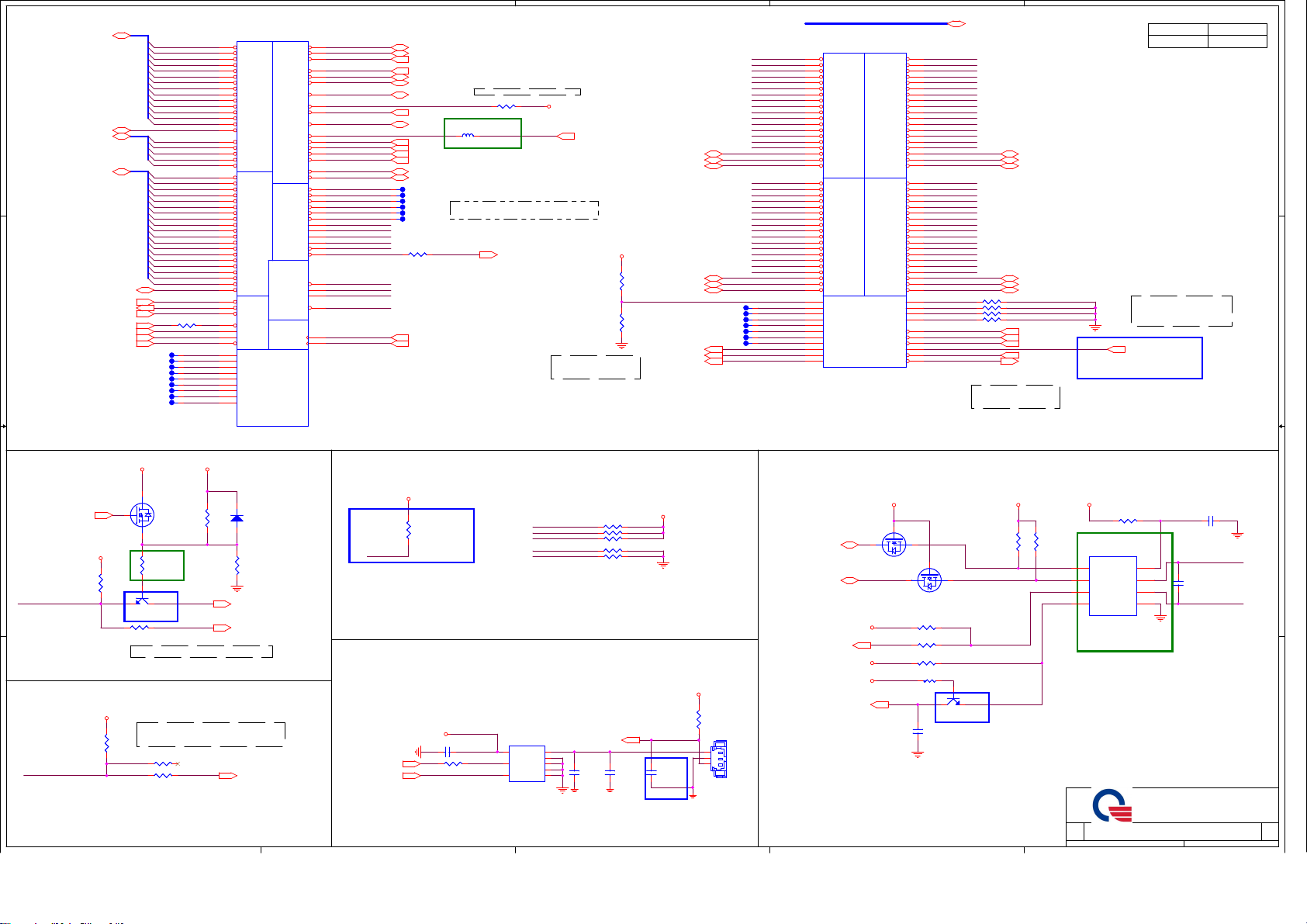

CPU(1/2)- Host Bus

CPU(1/2)- Host Bus

CPU(1/2)- Host Bus

C68 0.1u/10V_4C68 0.1u/10V_4

C560

C560

2200p/50V_4

2200p/50V_4

TE1M

TE1M

TE1M

H_THERMDA

H_THERMDC

1

2

3

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

E3D

E3D

3 40Monday, May 26, 2008

3 40Monday, May 26, 2008

3 40Monday, May 26, 2008

E3D

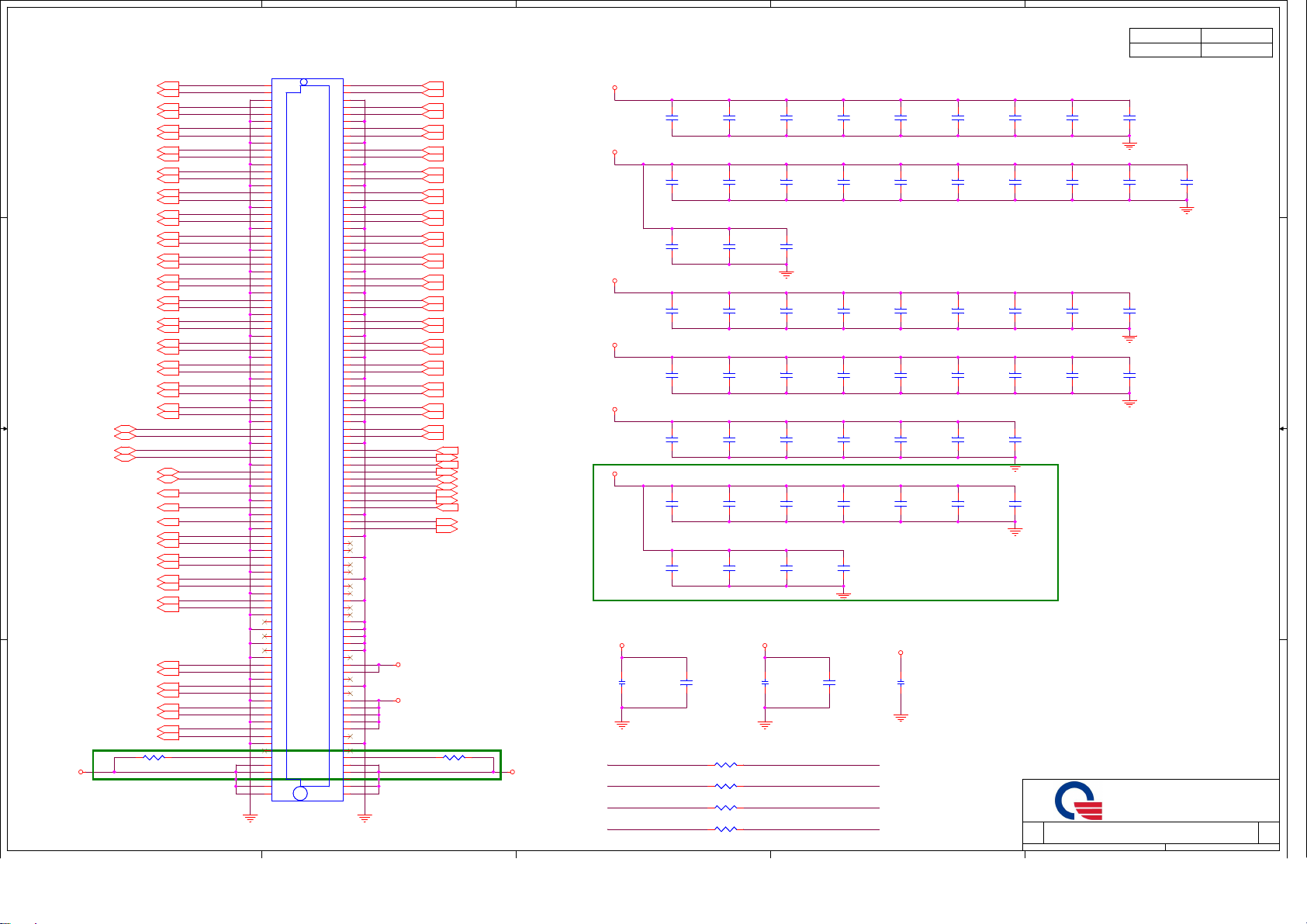

Page 4

5

4

3

2

1

BOM Option Table

Reference

N/A

Description

N/A

Need NC 20PCS 10u before A1 BOM released(A0 all stuff)

D D

C C

B B

A A

U501D

U501D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Penryn_1p0

Penryn_1p0

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

.

Place these parts reference

to Intel demo board.

C529

C548

C548

10u/10V_8

10u/10V_8

C546

C546

10u/10V_8

10u/10V_8

C547

C547

10u/10V_8

10u/10V_8

C540

C540

10u/10V_8

10u/10V_8

C54

C54

+

+

330u/2V_7343

330u/2V_7343

C530

C530

10u/10V_8

10u/10V_8

C43

C43

10u/10V_8

10u/10V_8

C544

C544

10u/10V_8

10u/10V_8

C538

C538

10u/10V_8

10u/10V_8

VCC_CORE

Power require

C37

C37

10u/10V_8

10u/10V_8

C60

C60

10u/10V_8

10u/10V_8

C52

C52

10u/10V_8

10u/10V_8

C531

C531

10u/10V_8

10u/10V_8

C55

C55

+

+

330u/2V_7343

330u/2V_7343

C3A

C529

10u/10V_8

10u/10V_8

C46

C46

10u/10V_8

10u/10V_8

C48

C48

10u/10V_8

10u/10V_8

C549

C549

10u/10V_8

10u/10V_8

C533

C533

C42

C42

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

C528

C528

C527

C527

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

C38

C38

C526

C526

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

C541

C541

C537

C537

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

VCC_CORE Bulk CAPs place

to BOT of CPU centeral

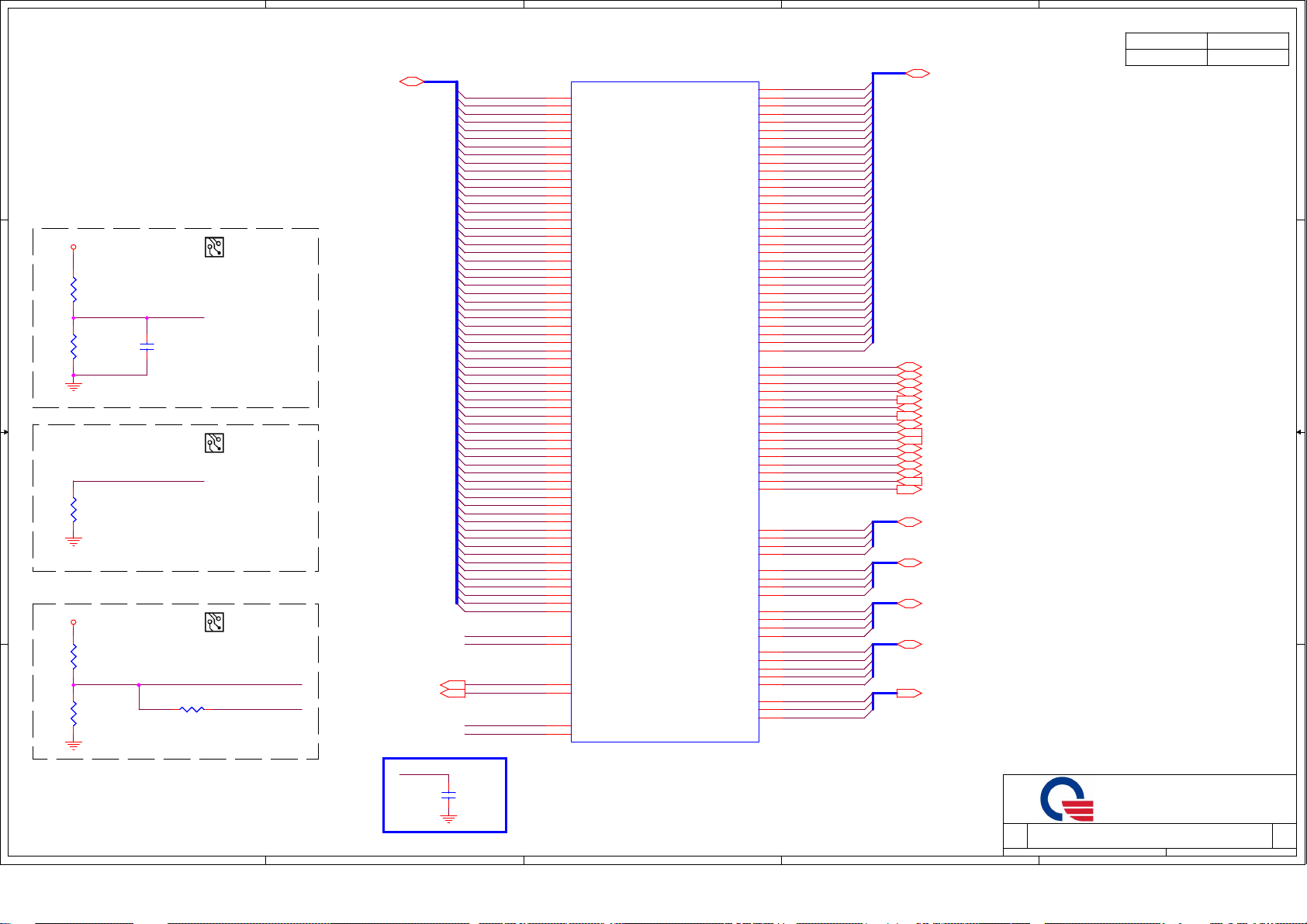

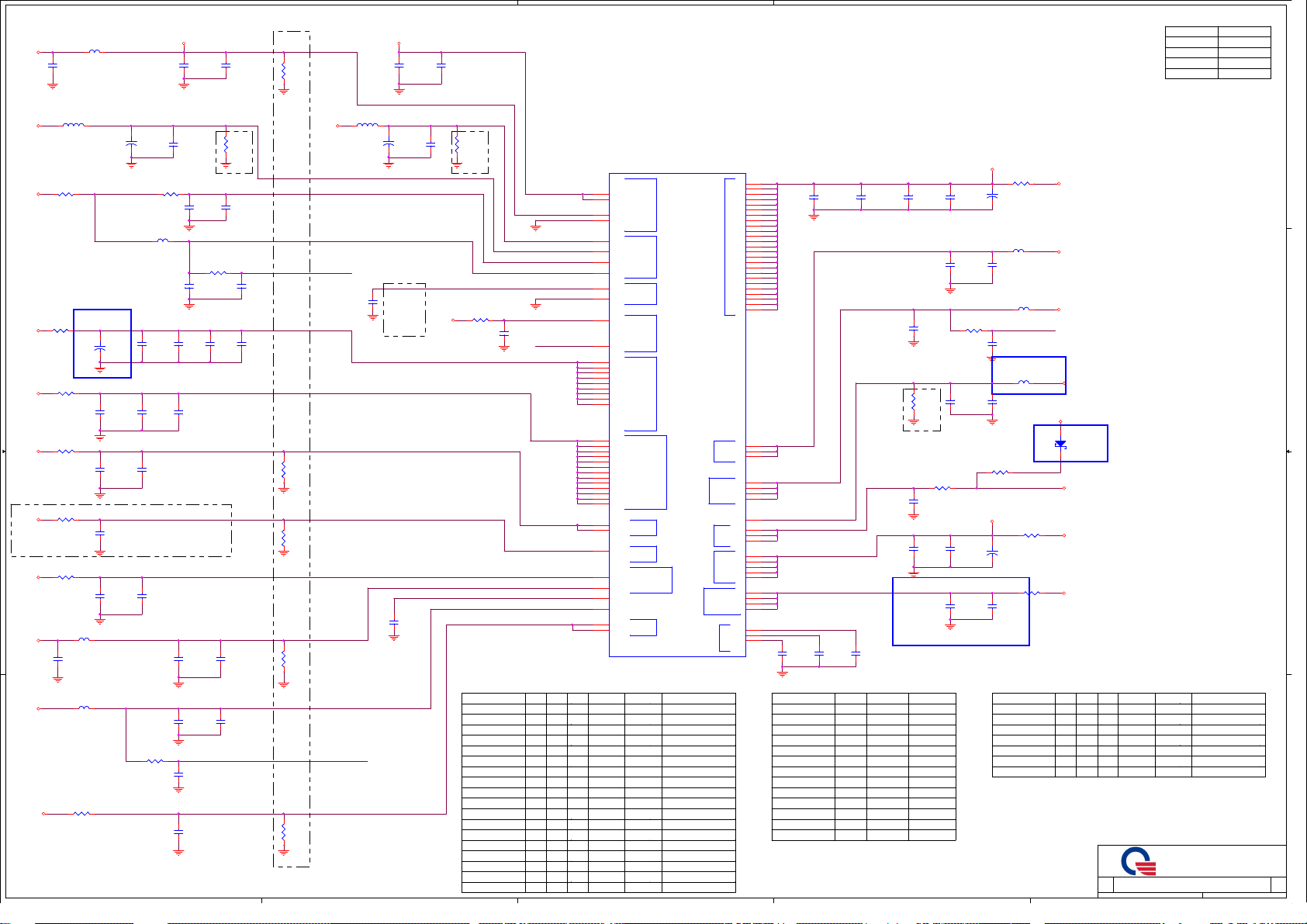

Penryn CPU Power Status and max current table

POWER PLANE

VCC_CORE

VCC_CORE

VCC_CORE

VCC_CORE

VCCA

VCCP

VCCP

S0

S3

S4/S5

X

X

O

O

O

O

O

O

O

X

X

X

X

X

X

X

X

X

X

X

X

Voltage

VID

VID

VID

VID

+1.5V

+1.05V

+1.05V

I(max)

47A

50A

TBD

67A

130mA

4.5A

2.5A

Standard Voltage CPU

SV Design Target

Extreme Edition CPU

EE Design Target

Before VCC Stable

After VCC Stable

C536

C536

10u/10V_8

10u/10V_8

C63

C63

10u/10V_8

10u/10V_8

C53

C53

10u/10V_8

10u/10V_8

C542

C542

10u/10V_8

10u/10V_8

Note

C51

C51

10u/10V_8

10u/10V_8

C41

C41

10u/10V_8

10u/10V_8

C40

C40

10u/10V_8

10u/10V_8

C539

C539

10u/10V_8

10u/10V_8

VCC_CORE

C61

C61

10u/10V_8

10u/10V_8

VCC_CORE

C45

C45

10u/10V_8

10u/10V_8

VCC_CORE

C545

C545

10u/10V_8

10u/10V_8

VCC_CORE

C550

C550

10u/10V_8

10u/10V_8

VCC_CORE VCC_CORE

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AB9

U501C

U501C

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

Penryn_1p0

Penryn_1p0

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

CPU_G21

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

+VCCA_PROC

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

.

.

+1.04V

R42 0_4R42 0_4

H_VID0 33

H_VID1 33

H_VID2 33

H_VID3 33

H_VID4 33

H_VID5 33

H_VID6 33

VCC_CORE

R512

R512

100/F_6

100/F_6

R511

R511

100/F_6

100/F_6

(See Penryn EMTS Rev:1.0 Table7,8 for voltage and current)

(See Penryn EMTS Rev:1.0 Table-3 for VID table)

5

4

3

2

Layout Note:

Inside CPU center cavity in 2 rows

+1.05V

C64

C33

C33

0.1u/10V_4

0.1u/10V_4

C35

C35

0.1u/10V_4

0.1u/10V_4

+1.05V

+

+

+1.04V

C71

C71

0.01u/16V_4

0.01u/16V_4

Layout Note:

Route VCCSENSE and VSSSENSE traces at

27.4 Ohms with 50 mil spacing.

Place PU and PD within 1 inch of CPU.

C79

C79

10u/10V_8

10u/10V_8

VCCSENSE 33

VSSSENSE 33

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

CPU(2/2)- Power

CPU(2/2)- Power

CPU(2/2)- Power

Date: Sheet of

Date: Sheet of

Date: Sheet of

C65

C65

0.1u/10V_4

0.1u/10V_4

C34

C34

0.1u/10V_4

0.1u/10V_4

C58

C58

330u/2.5V_7343

330u/2.5V_7343

R76 0_6R76 0_6

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

C64

0.1u/10V_4

0.1u/10V_4

+1.05V

C66

C66

0.1u/10V_4

0.1u/10V_4

VCCP Bulk CAP

close to Pin

+1.5V

Place 0.01u

near pin-B26

1

TE1M

TE1M

TE1M

4 40Monday, May 26, 2008

4 40Monday, May 26, 2008

4 40Monday, May 26, 2008

E3D

E3D

E3D

Page 5

5

4

3

2

1

BOM Option Table

Reference

EV_IV@

U504A

H_D#[63..0]3

D D

+1.05V_VCCP_GMCH

R532

R532

221/F_4

221/F_4

C C

R531

R531

100/F_4

100/F_4

H_SWING

C568

C568

0.1u/10V_4

0.1u/10V_4

0.3125*VCCP

W:10,S:20 , L<0.5"

W:10,S:20 , L<0.5"

H_RCOMP

R108

R108

24.9/F_4

24.9/F_4

B B

+1.05V_VCCP_GMCH

R534

R534

1K/F_4

1K/F_4

R536

2K/F_4

2K/F_4

A A

R535 0_4R535 0_4R536

2/3*VCCP

W:10,S:20 , L<0.5"

H_AVREF

H_DVREF

H_CPURST#3

H_CPURST#

B2A

5

4

C802

C802

*0.1u/10V_4

*0.1u/10V_4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

U504A

F2

H_D#_0

G8

H_D#_1

F8

H_D#_2

E6

H_D#_3

G2

H_D#_4

H6

H_D#_5

H2

H_D#_6

F6

H_D#_7

D4

H_D#_8

H3

H_D#_9

M9

H_D#_10

M11

H_D#_11

J1

H_D#_12

J2

H_D#_13

N12

H_D#_14

J6

H_D#_15

P2

H_D#_16

L2

H_D#_17

R2

H_D#_18

N9

H_D#_19

L6

H_D#_20

M5

H_D#_21

J3

H_D#_22

N2

H_D#_23

R1

H_D#_24

N5

H_D#_25

N6

H_D#_26

P13

H_D#_27

N8

H_D#_28

L7

H_D#_29

N10

H_D#_30

M3

H_D#_31

Y3

H_D#_32

AD14

H_D#_33

Y6

H_D#_34

Y10

H_D#_35

Y12

H_D#_36

Y14

H_D#_37

Y7

H_D#_38

W2

H_D#_39

AA8

H_D#_40

Y9

H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

C5

H_SWING

E3

H_RCOMP

C12

H_CPURST#

E11

H_CPUSLP#

A11

H_AVREF

B11

H_DVREF

EV_IV@CANTIGA_1p2

EV_IV@CANTIGA_1p2

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

HOST

HOST

GM PN=> AJSLB940T05

PM PN=> AJSLB970T03

3

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

CLK_MCH_BCLK

CLK_MCH_BCLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_A#[35..3] 3

H_ADS# 3

H_ADSTB#0 3

H_ADSTB#1 3

H_BNR# 3

H_BPRI# 3

H_BREQ# 3

H_DEFER# 3

H_DBSY# 3

CLK_MCH_BCLK 2

CLK_MCH_BCLK# 2

H_DPWR# 3

H_DRDY# 3

H_HIT# 3

H_HITM# 3

H_LOCK# 3

H_TRDY# 3

H_DINV#[3..0] 3

H_DSTBN#[3..0] 3

H_DSTBP#[3..0] 3

H_REQ#[4..0] 3

H_RS#[2..0] 3H_CPUSLP#3

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

NB (1/7)- HOST

NB (1/7)- HOST

NB (1/7)- HOST

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

1

EV&IV diff. BOM

TE1M

TE1M

TE1M

5 40Monday, May 26, 2008

5 40Monday, May 26, 2008

5 40Monday, May 26, 2008

Description

E3D

E3D

E3D

Page 6

5

U504B

MCH_RSVD1

T69T69

MCH_RSVD2

T76T76

MCH_RSVD3

T73T73

MCH_RSVD4

T67T67

MCH_RSVD5

T38T38

MCH_RSVD6

T39T39

MCH_RSVD7

T41T41

MCH_RSVD8

T43T43

MCH_RSVD9

T40T40

MCH_RSVD14

T52T52

D D

MCH_BSEL02

MCH_BSEL12

C C

PM_SYNC#14

ICH_DPRSTP#3,12,33

PM_EXTTS#017

PM_EXTTS#117

DELAY_VR_PWRGOOD3,14,33

PLT_RST#_NB13

PM_THRMTRIP#3,12

PM_DPRSLPVR14,33

NB Thermal trip pin

No use Thermal trip NB side can

NC.(NB has ODT)

PM_DPRSTP#

The Daisy chain topology should

be routed from ICH9M to IMVP ,

then to (G)MCH and CPU, in that

B B

Check list note : CL_REF=0.35V

A A

order.

MCH_CLVREF_R SM_VREF

+1.8VSUS_GMCH +1.8VSUS_GMCH

R547

R547

80.6/F_4

80.6/F_4

R548

R548

*20/F_4

*20/F_4

MCH_BSEL22

MCH_CFG_511

MCH_CFG_611

MCH_CFG_711

MCH_CFG_911

MCH_CFG_1011

MCH_CFG_1211

MCH_CFG_1311

MCH_CFG_1611

MCH_CFG_1911

MCH_CFG_2011

R126 0_4R126 0_4

R533 0_4R533 0_4

R183 0_4R183 0_4

R178 0_4R178 0_4

R207 0_4R207 0_4

R114 100_4R114 100_4

R120 *0_4R1 20 *0_4

R138 0_4R138 0_4

+1.05V

R180

R180

1K/F_4

1K/F_4

R181

R181

C164

C164

511/F_6

511/F_6

0.1u/10V_4

0.1u/10V_4

R545

R545

*20/F_4

*20/F_4

M_RCOMP#M_RCOMP SM_RCOMP_VOL

R546

R546

80.6/F_4

80.6/F_4

5

MCH_RSVD15

T60T60

MCH_RSVD17

T24T24

MCH_RSVD20

T50T50

MCH_RSVD21

T27T27

MCH_RSVD22

T54T54

MCH_RSVD23

T51T51

MCH_RSVD24

T506T506

MCH_RSVD25

T42T42

JTAG_TCK

T68T68

JTAG_TDI

T70T70

JTAG_TDO

T66T66

JTAG_TMS

T80T80

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

MCH_CFG_3

T46T46

MCH_CFG_4

T58T58

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

T48T48

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

T45T45

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

T47T47

MCH_CFG_15

T44T44

MCH_CFG_16

MCH_CFG_17

T49T49

MCH_CFG_18

T59T59

MCH_CFG_19

MCH_CFG_20

PM_SYNC#_R

ICH_DPRSTP#_R

PM_EXTTS#0_1_EC_RP M_EXTTS#0

TS#DIMM0_1_RPM_EXTTS#1

RST_IN#_MCH

THRMTRIP#_R

DPRSLPVR_R

TP_MCH_NC1

T512T512

TP_MCH_NC2

T513T513

TP_MCH_NC3

T516T516

TP_MCH_NC4

T515T515

TP_MCH_NC5

T511T511

TP_MCH_NC6

T89T89

TP_MCH_NC7

T514T514

TP_MCH_NC8

T510T510

TP_MCH_NC9

T88T88

TP_MCH_NC10

T509T509

TP_MCH_NC11

T508T508

TP_MCH_NC12

T507T507

TP_MCH_NC13

T34T34

TP_MCH_NC14

T37T37

TP_MCH_NC15

T32T32

TP_MCH_NC16

T36T36

TP_MCH_NC17

T35T35

TP_MCH_NC18

T30T30

TP_MCH_NC19

T33T33

TP_MCH_NC20

T22T22

TP_MCH_NC21 HDA_SDIN_HDMI

T28T28

TP_MCH_NC22

T31T31

TP_MCH_NC23

T29T29

TP_MCH_NC24

T26T26

TP_MCH_NC25

T23T23

SM_VREF.Default use voltage divider for poor layout cause +SMDDR_VREF not

meet spec.And Intel circuit PU/PD is 1K,But Check list PU/PD is 10K.

+1.8VSUS_GMCH

R553 1K/F_4R553 1K/F_4

M36

N36

R33

T33

AH9

AH10

AH12

AH13

K12

T24

B31

M1

AY21

B2

BG23

BF23

BH18

BF18

AL34

AK34

AN35

AM35

T25

R25

P25

P20

P24

C25

N24

M24

E21

C23

C24

N21

P21

T21

R20

M20

L21

H21

P29

R28

T28

R29

B7

N33

P32

AT40

AT11

T20

R32

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

F1

EV_IV@CANTIGA_1p2

EV_IV@CANTIGA_1p2

R206 *0_6R2 06 *0_6

R191 10K/F_4R191 10K/F_4

R205

R205

10K/F_4

10K/F_4

R551

R551

3.01K/F_4

3.01K/F_4

R550

R550

1K/F_4

1K/F_4

U504B

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD14

RSVD15

RSVD17

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

ME_JTAG_TCK

ME_JTAG_TDI

ME_JTAG_TDO

ME_JTAG_TMS

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_SYNC#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

CFG

CFG

PM

PM

+SMDDR_VREF

+1.8VSUS_GMCH

SM_RCOMP_VOH

C585

C585

0.01u/16V_4

0.01u/16V_4

C583

C583

0.01u/16V_4

0.01u/16V_4

RSVD

RSVD

ME JTAG

ME JTAG

NC

NC

4

SA_CK_0

SA_CK_1

SB_CK_0

SB_CK_1

SA_CK#_0

SA_CK#_1

SB_CK#_0

SB_CK#_1

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DPLL_REF_CLK

DDR CLK/ CONTROL/COMPENSATION

DDR CLK/ CONTROL/COMPENSATION

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

CLK

CLK

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI

DMI

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

GRAPHICS VID

GRAPHICS VID

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

MEHDA

MEHDA

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

TSATN#

MISC

MISC

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

<Checklist ver0.8>

If TSATN# is not used, then it must be terminated

with a 56- pull-up resistor to VCCP.

SM_PWROK only for DDR3.(DDR2 PD only)

C589

C589

2.2u/6.3V_6

2.2u/6.3V_6

C584

C584

2.2u/6.3V_6

2.2u/6.3V_6

4

AP24

AT21

AV24

AU20

AR24

AR21

AU24

AV20

BC28

AY28

AY36

BB36

BA17

AY16

AV16

AR13

BD17

AY17

BF15

AY13

BG22

BH21

BF28

BH28

AV42

AR36

BF17

BC36

B38

A38

E41

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

AH34

N28

M28

G36

E36

K36

H36

B12

B28

B30

B29

C29

A28

TSATN#

CLK_MCH_OE#

PM_EXTTS#0

PM_EXTTS#1

SM_REXT

SM_PWROK

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR3

M_CLK_DDR4

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#3

M_CLK_DDR#4

M_CKE0

M_CKE1

M_CKE3

M_CKE4

M_CS#0

M_CS#1

M_CS#2

M_CS#3

M_ODT0

M_ODT1

M_ODT2

M_ODT3

M_RCOMP

M_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

MCH_SM_DRAMRST#

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

CL_CLK0

CL_DATA0

MPWROK

CL_RST#0

MCH_CLVREF_R

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLK_MCH_OE#

MCH_ICH_SYNC#

TSATN#

HDA_BIT_CLK_HDMI

HDA_RST#_HDMI

HDA_SDOUT_HDMI

HDA_SYNC_HDMI

R194

R194

*12K/F_4

*12K/F_4

R186

R186

10K/F_6

10K/F_6

T77T77

T57T57

R17210K_4 R17210K_4

R18410K_4 R18410K_4

R17910K_4 R17910K_4

R132 499/F_4R132 499/F_4

HWPG_1.8V 28, 35

M_CLK_DDR0 17

M_CLK_DDR1 17

M_CLK_DDR3 17

M_CLK_DDR4 17

M_CLK_DDR#0 17

M_CLK_DDR#1 17

M_CLK_DDR#3 17

M_CLK_DDR#4 17

M_CKE0 16,17

M_CKE1 16,17

M_CKE3 16,17

M_CKE4 16,17

M_CS#0 16,17

M_CS#1 16,17

M_CS#2 16,17

M_CS#3 16,17

M_ODT0 16,17

M_ODT1 16,17

M_ODT2 16,17

M_ODT3 16,17

SM_DRAMRST# only for

DDR3.(DDR2 NC).

DREFCLK 2

DREFCLK# 2

DREFSSCLK 2

DREFSSCLK# 2

CLK_PCIE_3GPLL 2

CLK_PCIE_3GPLL# 2

DMI_TXN[3:0] 13

DMI_TXP[3:0] 13

DMI_RXN[3:0] 13

DMI_RXP[3:0] 13

CL_CLK0 14

CL_DATA0 14

MPWROK 14

CL_RST#0 14

DDPC_CTRL for HDMI port C

SDVO_CTRL for HDMI port B

DDPC_CTRLDATA 11

SDVO_CTRLCLK 21

SDVO_CTRLDATA 11,21

CLK_MCH_OE# 2

MCH_ICH_SYNC# 14

HDA_BIT_CLK_HDMI 12

HDA_RST#_HDMI 12

HDA_SDIN_HDMI 12

HDA_SDOUT_HDMI 12

HDA_SYNC_HDMI 12

+1.05V

R53756_4 R53756_ 4

+3V

3

GM PN=> AJSLB940T05

PM PN=> AJSLB970T03

LVDS I/F

INT_LVDS_PWM19

INT_LVDS_BLON19

INT_LVDS_EDIDCLK19

INT_LVDS_EDIDDATA11,19

INT_LVDS_DIGON19

INT_TXLCLKOUT-19

INT_TXLCLKOUT+19

INT_TXLOUT0-19

INT_TXLOUT1-19

INT_TXLOUT2-19

INT_TXLOUT0+19

INT_TXLOUT1+19

INT_TXLOUT2+19

TV IF (Disable)

CRT I/F

INT_CRT_DDCCLK20

INT_CRT_DDCDAT20

INT_HSYNC20

INT_VSYNC20

HSYNC/VSYNC serial R place close to NB

NOTE:

If (G)MCH's HD Audio signals are connected to ICH9M for

iHDMI, VCCHDA and VCCSUSHDA on ICH9M should be

only on 1.5V. These power pins on ICH9M can be supplied

with 3.3V if and only if (G)MCH's HDA is not con nected to

ICH9M. Consequently, only 1.5V audio/modem codec s can

be used on the platform.

IV&EV Dis/Enable LVDS setting(See DG 1.0 P190 Table 103)

R190 IV@0_4R190 IV@0_4

R563 IV@2.37K/F_4R563 IV@2.37K/F_4

R154 IV@10K_4R154 IV@10K_4

+3V

R155 IV@10K_4R155 IV@10K_4

LVDS_VREFH

LVDS_VREFL

LVDS_IBG

L_CTRL_CLK

L_CTRL_DATA

T85T85

T65T65

T71T71

T74T74

T78T78

T84T84

T83T83

T75T75

T86T86

T79T79

T82T82

T72T72

T81T81

INT_CRT_BLU20

INT_CRT_GRN20

INT_CRT_RED20

R163 IV@30.1/F_4R163 IV@30.1/F_4

R165 IV@30.1/F_4R165 IV@30.1/F_4

For IV @ Connect to 30.1ohm

For EV@ NC

For IV @ 0ohm

For EV@ NC

For IV @ 2.37K/F

For EV@ NC

For IV @ 10K

For EV@ NC

INT_LVDS_PWM

INT_LVDS_BLON

L_CTRL_CLK

L_CTRL_DATA

INT_LVDS_EDIDCLK

INT_LVDS_EDIDDATA

INT_LVDS_DIGON

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

INT_TXLCLKOUTINT_TXLCLKOUT+

INT_TXUCLKOUTINT_TXUCLKOUT+

INT_TXLOUT0INT_TXLOUT1INT_TXLOUT2INT_TXLOUT3-

INT_TXLOUT0+

INT_TXLOUT1+

INT_TXLOUT2+

INT_TXLOUT3+

INT_TXUOUT0INT_TXUOUT1INT_TXUOUT2INT_TXUOUT3-

INT_TXUOUT0+

INT_TXUOUT1+

INT_TXUOUT2+

INT_TXUOUT3+

INT_TV_COMP

INT_TV_Y/G

INT_TV_C/R

INT_TV_RNT

TV_DCONSEL_0

TV_DCONSEL_1

INT_CRT_BLU

INT_CRT_GRN

INT_CRT_RED

CRT_IRTN

INT_CRT_DDCCLK

INT_CRT_DDCDAT

HSYNC_GINT_HSYNC

CRTIREF

VSYNC_GINT_VSYNC

M32

M33

M29

U504C

U504C

L32

L_BKLT_CTRL

G32

L_BKLT_EN

L_CTRL_CLK

L_CTRL_DATA

K33

L_DDC_CLK

J33

L_DDC_DATA

L_VDD_EN

C44

LVDS_IBG

B43

LVDS_VBG

E37

LVDS_VREFH

E38

LVDS_VREFL

C41

LVDSA_CLK#

C40

LVDSA_CLK

B37

LVDSB_CLK#

A37

LVDSB_CLK

H47

LVDSA_DATA#_0

E46

LVDSA_DATA#_1

G40

LVDSA_DATA#_2

A40

LVDSA_DATA#_3

H48

LVDSA_DATA_0

D45

LVDSA_DATA_1

F40

LVDSA_DATA_2

B40

LVDSA_DATA_3

A41

LVDSB_DATA#_0

H38

LVDSB_DATA#_1

G37

LVDSB_DATA#_2

J37

LVDSB_DATA#_3

B42

LVDSB_DATA_0

G38

LVDSB_DATA_1

F37

LVDSB_DATA_2

K37

LVDSB_DATA_3

F25

TVA_DAC

H25

TVB_DAC

K25

TVC_DAC

H24

TV_RTN

C31

TV_DCONSEL_0

E32

TV_DCONSEL_1

E28

CRT_BLUE

G28

CRT_GREEN

J28

CRT_RED

G29

CRT_IRTN

H32

CRT_DDC_CLK

J32

CRT_DDC_DATA

J29

CRT_HSYNC

E29

CRT_TVO_IREF

L29

CRT_VSYNC

EV_IV@CANTIGA_1p2

EV_IV@CANTIGA_1p2

2

LVDS

LVDS

TV

TV

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

VGA

VGA

UMA iHDMI I/F

C_PEG_TXP0

C_PEG_TXN0

C_PEG_TXP1

C_PEG_TXN1

C_PEG_TXP2

C_PEG_TXN2

C_PEG_TXP3

C_PEG_TXN3

IV&EV Dis/Enable CRT setting(See DG 1.0 P190 Table 103) Dis TV/En CRT( See DG1.0 P208 Table 118)

R176 *EV@0_4R176 *EV@0_4

R177 *EV@0_4R177 *EV@0_4

R162 EV@0_4R162 EV@0_4

R164 EV@0_4R164 EV@0_4

R159 EV_IV@150/F_4R159 EV_IV@150/F_4

R160 EV_IV@150/F_4R160 EV_IV@150/F_4

R161 EV_IV@150/F_4R161 EV_IV@150/F_4

R157 EV_IV@1K/F_4R157 EV_IV@1K/F_4

3

INT_CRT_DDCCLK

INT_CRT_DDCDAT

HSYNC_G

VSYNC_G

INT_CRT_BLU

INT_CRT_GRN

INT_CRT_RED

CRTIREF

Layout Note :See DG1.0 P180

For IV @ NC

For EV@ 0ohm to GND or NC

For IV @ NC

For EV@ 0ohm to GND

For IV @ Connect to 150ohm/F

For EV@ Connect to 0ohm GND

For IV @ Connect to 1.02K/F

For EV@ Connect to 0ohm GND

R142 EV_IV@75_4R142 EV_IV@75_4

R143 EV_IV@75_4R143 EV_IV@75_4

R144 EV_IV@75_4R144 EV_IV@75_4

R158 0_4R158 0_4

R175 0_4R175 0_4

IV&EV Dis/Enable PLL setting(See DG 1.0 P190 Table 103)

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

2

R561 EV@0_4R561 EV@0_4

R562 EV@0_4R562 EV@0_4

R197 EV@0_4R197 EV@0_4

R198 EV@0_4R198 EV@0_4

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

RAMP2

R200 IV@0_4R200 IV@0_4

C680 IHM@0.1u/10V_4C680 IHM@0.1u/10V_4

C672 IHM@0.1u/10V_4C672 IHM@0.1u/10V_4

C671 IHM@0.1u/10V_4C671 IHM@0.1u/10V_4

C670 IHM@0.1u/10V_4C670 IHM@0.1u/10V_4

C669 IHM@0.1u/10V_4C669 IHM@0.1u/10V_4

C668 IHM@0.1u/10V_4C668 IHM@0.1u/10V_4

C667 IHM@0.1u/10V_4C667 IHM@0.1u/10V_4

C666 IHM@0.1u/10V_4C666 IHM@0.1u/10V_4

INT_TV_COMP

INT_TV_Y/G

INT_TV_C/R

TV_DCONSEL_0

TV_DCONSEL_1

L<0.5" , If PCIE not support

still connect to +VCC_PEG

EXP_A_COMPX

T37

T36

PEG_RXN0

H44

PEG_RXN1

J46

PEG_RXN2

L44

PEG_RXN3

L40

PEG_RXN4

N41

PEG_RXN5

P48

PEG_RXN6

N44

PEG_RXN7

T43

PEG_RXN8

U43

PEG_RXN9

Y43

PEG_RXN10

Y48

PEG_RXN11

Y36

PEG_RXN12

AA43

PEG_RXN13

AD37

PEG_RXN14

AC47

PEG_RXN15

AD39

PEG_RXP0

H43

PEG_RXP1

J44

PEG_RXP2

L43

PEG_RXP3

L41

PEG_RXP4

N40

PEG_RXP5

P47

PEG_RXP6

N43

PEG_RXP7

T42

PEG_RXP8

U42

PEG_RXP9

Y42

PEG_RXP10

W47

PEG_RXP11

Y37

PEG_RXP12

AA42

PEG_RXP13

AD36

PEG_RXP14

AC48

PEG_RXP15

AD40

C_PEG_TXN0

J41

C_PEG_TXN1

M46

C_PEG_TXN2

M47

C_PEG_TXN3

M40

C_PEG_TXN4

M42

C_PEG_TXN5

R48

C_PEG_TXN6

N38

C_PEG_TXN7

T40

C_PEG_TXN8

U37

C_PEG_TXN9

U40

C_PEG_TXN10

Y40

C_PEG_TXN11

AA46

C_PEG_TXN12

AA37

C_PEG_TXN13

AA40

C_PEG_TXN14

AD43

C_PEG_TXN15

AC46

C_PEG_TXP0

J42

C_PEG_TXP1

L46

C_PEG_TXP2

M48

C_PEG_TXP3

M39

C_PEG_TXP4

M43

C_PEG_TXP5

R47

C_PEG_TXP6

N37

C_PEG_TXP7

T39

C_PEG_TXP8

U36

C_PEG_TXP9

U39

C_PEG_TXP10

Y39

C_PEG_TXP11

Y46

C_PEG_TXP12

AA36

C_PEG_TXP13

AA39

C_PEG_TXP14

AD42

C_PEG_TXP15

AD46

For IV @ 75ohm to GND

For EV@ 0ohm to GND

For IV @ 0ohm to GND

For EV@ 0ohm to GND

For IV @ NC

For EV@ 0ohm to GND

1

BOM Option Table

Reference

+1.05V_VCC_PEG

R204 49.9/F_4R204 49.9/F_4

PEG_RXN[15:0] 18

PEG_RXP[15:0] 18

C690 EV@0.1u/10V_4C690 EV @0.1u/10V_4

C692 EV@0.1u/10V_4C692 EV @0.1u/10V_4

C688 EV@0.1u/10V_4C688 EV @0.1u/10V_4

C686 EV@0.1u/10V_4C686 EV @0.1u/10V_4

C654 EV@0.1u/10V_4C654 EV @0.1u/10V_4

C681 EV@0.1u/10V_4C681 EV @0.1u/10V_4

C663 EV@0.1u/10V_4C663 EV @0.1u/10V_4

C656 EV@0.1u/10V_4C656 EV @0.1u/10V_4

C644 EV@0.1u/10V_4C644 EV @0.1u/10V_4

C646 EV@0.1u/10V_4C646 EV @0.1u/10V_4

C673 EV@0.1u/10V_4C673 EV @0.1u/10V_4

C649 EV@0.1u/10V_4C649 EV @0.1u/10V_4

C678 EV@0.1u/10V_4C678 EV @0.1u/10V_4

C651 EV@0.1u/10V_4C651 EV @0.1u/10V_4

C661 EV@0.1u/10V_4C661 EV @0.1u/10V_4

C683 EV@0.1u/10V_4C683 EV @0.1u/10V_4

C691 EV@0.1u/10V_4C691 EV @0.1u/10V_4

C693 EV@0.1u/10V_4C693 EV @0.1u/10V_4

C689 EV@0.1u/10V_4C689 EV @0.1u/10V_4

C687 EV@0.1u/10V_4C687 EV @0.1u/10V_4

C655 EV@0.1u/10V_4C655 EV @0.1u/10V_4

C682 EV@0.1u/10V_4C682 EV @0.1u/10V_4

C664 EV@0.1u/10V_4C664 EV @0.1u/10V_4

C657 EV@0.1u/10V_4C657 EV @0.1u/10V_4

C645 EV@0.1u/10V_4C645 EV @0.1u/10V_4

C642 EV@0.1u/10V_4C642 EV @0.1u/10V_4

C674 EV@0.1u/10V_4C674 EV @0.1u/10V_4

C650 EV@0.1u/10V_4C650 EV @0.1u/10V_4

C679 EV@0.1u/10V_4C679 EV @0.1u/10V_4

C652 EV@0.1u/10V_4C652 EV @0.1u/10V_4

C662 EV@0.1u/10V_4C662 EV @0.1u/10V_4

C684 EV@0.1u/10V_4C684 EV @0.1u/10V_4

Port-B_HPD#PEG_RXP3

TMDSB_DATA2

TMDSB_DATA2#

TMDSB_DATA1

TMDSB_DATA1#

TMDSB_DATA0

TMDSB_DATA0#

TMDSB_CLK

TMDSB_CLK#

Port-B_HPD# 21

TMDSB_DATA2 21

TMDSB_DATA2# 21

TMDSB_DATA1 21

TMDSB_DATA1# 21

TMDSB_DATA0 21

TMDSB_DATA0# 21

TMDSB_CLK 21

TMDSB_CLK# 21

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

NB (2/7)- VGA, MDI

NB (2/7)- VGA, MDI

NB (2/7)- VGA, MDI

Date: Sheet of

Date: Sheet of

Date: Sheet of

Description

INT VGAIV@

EXT VGAEV@

IHM@ INT HDMI

EV_IV@ EV&IV diff. BOM

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

PEG_TXN[15:0] 18

PEG_TXP[15:0] 18

TE1M

TE1M

TE1M

6 40Friday, J une 13, 2008

6 40Friday, J une 13, 2008

6 40Friday, J une 13, 2008

E3D

E3D

E3D

Page 7

5

4

3

2

1

BOM Option Table

Reference

EV_IV@

GM PN=> AJSLB940T05

PM PN=> AJSLB970T03

M_A_DQ[63:0]17

D D

U504D

M_A_DQ0 M_A_BS#0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

C C

B B

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

U504D

AJ38

SA_DQ_0

AJ41

SA_DQ_1

AN38

SA_DQ_2

AM38

SA_DQ_3

AJ36

SA_DQ_4

AJ40

SA_DQ_5

AM44

SA_DQ_6

AM42

SA_DQ_7

AN43

SA_DQ_8

AN44

SA_DQ_9

AU40

SA_DQ_10

AT38

SA_DQ_11

AN41

SA_DQ_12

AN39

SA_DQ_13

AU44

SA_DQ_14

AU42

SA_DQ_15

AV39

SA_DQ_16

AY44

SA_DQ_17

BA40

SA_DQ_18

BD43

SA_DQ_19

AV41

SA_DQ_20

AY43

SA_DQ_21

BB41

SA_DQ_22

BC40

SA_DQ_23

AY37

SA_DQ_24

BD38

SA_DQ_25

AV37

SA_DQ_26

AT36

SA_DQ_27

AY38

SA_DQ_28

BB38

SA_DQ_29

AV36

SA_DQ_30

AW36

SA_DQ_31

BD13

SA_DQ_32

AU11

SA_DQ_33

BC11

SA_DQ_34

BA12

SA_DQ_35

AU13

SA_DQ_36

AV13

SA_DQ_37

BD12

SA_DQ_38

BC12

SA_DQ_39

BB9

SA_DQ_40

BA9

SA_DQ_41

AU10

SA_DQ_42

AV9

SA_DQ_43

BA11

SA_DQ_44

BD9

SA_DQ_45

AY8

SA_DQ_46

BA6

SA_DQ_47

AV5

SA_DQ_48

AV7

SA_DQ_49

AT9

SA_DQ_50

AN8

SA_DQ_51

AU5

SA_DQ_52

AU6

SA_DQ_53

AT5

SA_DQ_54

AN10

SA_DQ_55

AM11

SA_DQ_56

AM5

SA_DQ_57

AJ9

SA_DQ_58

AJ8

SA_DQ_59

AN12

SA_DQ_60

AM13

SA_DQ_61

AJ11

SA_DQ_62

AJ12

SA_DQ_63

EV_IV@CANTIGA_1p2

EV_IV@CANTIGA_1p2

BD21

SA_BS_0

SA_BS_1

SA_BS_2

SA_RAS#

SA_CAS#

SA_WE#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

BG18

AT25

BB20

BD20

AY20

AM37

AT41

AY41

AU39

BB12

AY6

AT7

AJ5

AJ44

AT44

BA43

BC37

AW12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW24

BC21

BG26

BH26

BH17

AY25

M_A_BS#1

M_A_BS#2

M_A_RAS#

M_A_CAS#

M_A_WE#

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_BS#0 16,17

M_A_BS#1 16,17

M_A_BS#2 16,17

M_A_RAS# 16,17

M_A_CAS# 16,17

M_A_WE# 16,17

M_A_DM[7:0] 17

M_A_DQS[7:0] 17

M_A_DQS#[7:0] 17

M_A_A[14:0] 16,17

M_B_DQ[63:0]17

U504E

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

U504E

AK47

SB_DQ_0

AH46

SB_DQ_1

AP47

SB_DQ_2

AP46

SB_DQ_3

AJ46

SB_DQ_4

AJ48

SB_DQ_5

AM48

SB_DQ_6

AP48