Page 1

Data Book

It’s first version technical data sheet.

Since this revision 0.2 is still under working, there may

be some mistakes in it.

When you will start to design, please order the latest

one.

32bit Micro controller

TLCS-900/H1 series

TMP92CZ26AXBG

TENTATIVE

Rev0.2 09/Dec./2005

Page 2

Table of Contents

TLCS-900/H1 Devices

TMP92CZ26A

1. Outline and Features ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-1

2. Pin Assignment and Pin Functions ・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-6

2.1 Pin Assignment Diagram ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-6

2.2 Pin names and Functions ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-8

3. Operation ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-14

3.1 CPU ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-14

3.2 Memory Map ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-19

3.3 Clock Function and Standby Function ・・・・・・・・・・・・・・・・・・・・ 92CZ26A-20

3.4 Boot ROM ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-43

3.5 Interrupts ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-67

3.6 DMAC (DMA contro ller) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-88

3.7 Function of Ports・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-110

3.7.1 Port 1 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-117

3.7.2 Port 4 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-119

3.7.3 Port 5 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-121

3.7.4 Port 6 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-123

3.7.5 Port 7 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-125

3.7.6 Port 8 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-128

3.7.7 Port 9 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-130

3.7.8 Port A ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-133

3.7.9 Port C ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-135

3.7.10 Port F ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-139

3.7.11 Port G ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-143

3.7.12 Port J ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-145

3.7.13 Port K ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・92CZ26A-148

3.7.14 Port L ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-150

3.7.15 Port M ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-152

3.7.16 Port N ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-155

3.7.17 Port P ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-157

3.7.18 Port R ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-161

3.7.19 Port T ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-164

3.7.20 Port U ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-166

3.7.21 Port V ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-169

3.7.22 Port W ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-172

3.7.23 Port X ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-174

3.7.24 Port Z ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-177

3.8 Memory Controller (MEMC) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-180

3.9 External Memory Extension Function (MMU) ・・・・・・・・・・・・・ 92CZ26A-204

3.10 SDRAM Controller (SDRAMC) ・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-220

3.11 NAND-Flash controller ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-238

Page 3

3.12 8 bit timers (TMRA) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-266

3.13 16 bit timer (TMRB) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-294

3.14 Serial channel (SIO) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-315

3.15 Serial Bus Interface (SBI) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-344

3.16 USB controller ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-366

3.17 SPIC (SPI controller) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-477

3.18 I2S ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-496

3.19 LCD controller (LCDC) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-508

3.20 Touch screen inter face (TSI) ・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-564

3.21 Real time clock (RTC) ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-574

3.22 Melody/Alarm generator ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-589

3.23 Analog/Digital Converter ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-595

3.24 Watch dog timer ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-615

3.25 Power Management Circuit (PMC) ・・・・・・・・・・・・・・・・・・・・ 92CZ26A-619

3.26 Multiply and Accumulate Ca lculation unit (MAC) ・・・・・・・ 92CZ26A-628

3.27 Debug mode ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-633

4. Electrical Characteristics ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-640

5. Table of Special function registers (SFRs) ・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-665

6. Package ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 92CZ26A-748

Page 4

CMOS 32-Bit Micro controllers

1. Outline and Features

TMP92CZ26A is high-speed advanced 32-bit micro-controller developed for controlling equipment which

processes mass data.

TMP92CZ26AXBG is housed in a 228-pin BGA package.

(1) CPU : 32-bit CPU(High-speed 900/H1 CPU)

• Compatible with TLCS-900/L1 instruction code

• 16Mbytes of linear address space

• General-purpose register and register banks

• Micro DMA : 8channels (62.5ns/4 bytes at f

TMP92CZ26AXBG

= 80MHz, best case)

SYS

TMP92CZ26A

(2) Minimum instruction execution time : 12.5ns ( at f

(3) Internal RAM: 288K-byte (can be used for program, data and display memory)

Internal ROM: 8 K-byte(memory for Boot only)

It enables that load user program from USB, UART to Internal RAM.

= 80MHz)

SYS

92CZ26A-1

Page 5

(4) External memory expansion

• Expandable up to 3.1G bytes (shared program/data area)

• Can simultaneously support 8/16-bit width external data bus

…… Dynamic data bus sizing

• Separate bus system

(5) Memory controller

• Chip select output : 4 channel

• One channel in 4 channels is enabled detailed AC enable setting

(6) 8-bit timers : 8 channels

(7) 16-bit timer/event counter : 2 channel

(8) General-purpose serial interface : 1 channels

• UART/synchronous mode

• IrDA ver1.0 (115.2 kbps) selectable :

(There is the restriction in the setting baud rate when use this function together other functions)

TMP92CZ26A

(9) Serial bus interface: 1 channel

2

• I

C bus mode only

(10) USB (universal serial bus) controller: 1 channel

• Support to USB (REV1.1)

• Full-speed (12 Mbps) (Low-speed is not supported.)

• Endpoint 0: Control 64 bytes × 1-FIFO

Endpoint 1: BULK (output) 64 bytes × 2-FIFO

Endpoint 2: BULK (input) 64 bytes × 2-FIFO

Endpoint 3: Interrupt (input) 8 bytes × 1-FIFO

• Descriptor RAM: 384 bytes

2

S (Inter-IC Sound)interface: 2 channel

(11) I

2

• I

S bus mode selectable (Master, transmission only)

• Data Format is supported Left/Right Justify

• Built in FIFO buffer of 128 bytes (64 bytes × 2) every each channels.

(12) LCD controller

• Supported up to monochrome, 4, 16 and 64 gray levels and 256/4096 color for STN

• Supported up to 4096/65536/262144/16777216 color for TFT

• Supported up to PIP (Picture In Picture Display)

• Supported up to H/W Rotation function for support to various LCDM

(13) SDRAM controller :1 channel

• Supported 16M, 64M, 128M, 256M and 512Mbit SDR (Single-data-rate) SDRAM

• Can use not only as Data RAM for LCD display but also operate program direct from SDRAM

(14) Timer for real-time clock (RTC)

• Based on TC8521A

(15) Key-on wakeup (Interrupt key input)

(16) 10-bit A/D converter (Built in Sample Hold circuit) : 6 channels

92CZ26A-2

Page 6

(17) Touch screen interface

• Built-in Switch of Low-resistor, and available to delete external components for shift change

row/column

(18) Watch dog timer

(19) Melody/alarm generator

• Melody: Output of clock 4 to 5461Hz

• Alarm: Output of the 8 kinds of alarm pattern

• 5 kinds of interval interrupt

(20) MMU

• Expandable up to 3.1G bytes (3 local area/8 bank method)

• Independent bank for each Program, Read-data, Write-data, Source and Destination of DMAC (Odd

channel/Even channel) and LCD-display-data

(21) Interrupts: 56 interrupts

• 9 CPU interrupts …… Software interrupt instruction and illegal instruction

• 38 internal interrupts …… Seven selectable priority levels

• 9 external interrupts …… Seven selectable priority levels

TMP92CZ26A

(8 interrupt selectable negative/positive of edge)

(22) DMAC function: 6 channels

• High-speed data transfer enable by controlling which convert micro DMA function and this function

(23) Input/Output ports : 136 pins (Except Data bus (16bit), Address bus (24bit) and RD pin)

(24) Nand_Flash interface: 2 channel

• Available to connect directly with NAND flash

• Supported up to SLC type and MLC type

• Data Bus 8/16 Bit, Page Size 512/2048 Bytes

• Built-in Rees Solomon calculation circuits which enabled correct 4-address, and detect error more

than 5-address

(25) SPI controller : 1 channel

• Supported up to SPI mode of SD card and MMC card

• Built-in FIFO buffer of 32 bytes to each Input/Output

(26) Product/Sum calculation: 1 channel

• calculation 32×32+64 =64Bit , 64-32×32 = 64Bit , 32×32-64 =64Bit

• I/O method

(27) Signed calculation is supported.

92CZ26A-3

Page 7

(28) Stand-by function

• Three Halt modes : IDLE2 (programmable), IDLE1, STOP

• Each pin status programmable for stand-by mode

• Built-in power supply management circuits (PMC) for leak current provision

(29) Clock controller

• Built-in two blocks of clock doubler (PLL). PLL supplies 48 MHz for USB and 80 MHz for CPU from

10MHz

• Clock gear function: Selectable high-frequency clock fc to fc/16

• Clock for Timer (fs = 32.768 kHz)

(30) Operating voltage:

• Internal V

• 2 power supplies (Internal power supply (1.4 to 1.6), External power supply (3.0 to 3.6)

(31) Package

• 228 pin FBGA :P-FBGA228-1515-0.80A5

= 1.5V, External I/O Vcc = 3.0 to 3.6 V

CC

TMP92CZ26A

92CZ26A-4

Page 8

(

]

(AN0 to AN1)PG0 to PG1

(

r

X

(

(

(

(

7

(

(

(

)

(

)

(

(

(

(

(

8BIT TIMER

(

r

(

(

(

(

(

(

)

(

)

(

(

)

)

)

(

)

(AN3, MY,

AN4 to AN5)PG4 to PG5

(AN2, MX)PG2

ADTRG )PG3

AVCC, AVSS

VREFH, VREFL

(PX, INT4)P96

(PY)P97

(TXD0)P90

RXD0)P91

(CTS0, SCLK0)P92

(I2S0CKO)PF0

I2S0DO)PF1

I2S0WS)PF2

(I2S1CKO)PF3

I2S1DO)PF4

I2S1WS)PF5

(SDA)PV6

(SCL)PV

(X1USB) PX5

D+

D -

(TA0IN, INT1)PC1

(TA1OUT, MLDALM)PM1

(TA2IN, INT3)PC3

TA3OUT)PP1

(TA5OUT)PP2

TA7OUT, INT5)PP3

(TB0IN0, INT6)PP4

(TB1IN0, INT7)PP5

LGOE2 to 0)PK7 to 5

LD22 to 16)PU6 to 0

LD23, EO_TRGOUT

CLKOUT, LDIV)PX4

(

SDRAS,SRLLB

(

SDCAS, SRLUB

(

(TB0OUT0)PP6

(TB1OUT0)PP7

(SPDI)PR0

(SPDO)PR1

) PR2

(

SPCS

(SPCLK)PR3

LCP0)PK0

LLOAD)PK1

LFR)PK2

LVSYNC)PK3

LHSYNC)PK4

LD7 to 0)PL7 to 0

LD15 to 8)PT7 to 0

PU7

SDWE,SRWR

(SDLLDQM)PJ3

SDLUDQM)PJ4

(SDCLK)PF7

PX7

)PJ0

)PJ1

)PJ2

SDCKE)PJ7

10-bit 6ch

AD

900/H1 CPU

Converter

Touch Screen

I/F

(TSI)

SERIAL I/O

SIO0

I2S

2

(I

S0)

I2S

2

(I

S1)

SBI (I2Cbus)

USB

XBC

XDE

XHL

XIX

XIY

XIZ

XSP

32bit

P C

XWA

A W

C B

E D

L H

IX

IY

IZ

SP

F SR

Controlle

8BIT TIMER

(TMRA0)

8BIT TIMER

(TMRA1)

8BIT TIMER

(TMRA2)

8BIT TIMER

(TMRA3)

8BIT TIMER

(TMRA4)

8BIT TIMER

(TMRA5)

8BIT TIMER

(TMRA6)

(TMRA7)

16BIT TIMER

(TMRB0)

16BIT TIMER

(TMRB1)

WATCH-DOG TIMER

MMU

MAC

DMAC

PLL

H-OSC

Clock gear

L-OSC

DSU

PMC

Interrupt

Controlle

PORT1

PORT4

PORT5

PORT6

PORT7

PORT8

SPI

Controller

288KB RAM

NAND-FLASH

I/F (2ch)

LCD

Controller

BOOT ROM 8KB

KEY-BOARD

I/F

RTC

TMP92CZ26A

DVCC3A [12]

DVCC3B [1]

DVCC1A [5]

DVCC1B [1]

DVSSCOM

DVCC1C [1]

DVSS1C [1]

X1

X2

XT1

T2

RESET

DBGE

AM[1:0

PZ0 (EI_PODDATA)

PZ1 (EI_SYNCLK)

PZ2 (EI_PODREQ)

PZ3(EI_REFCLK)

PZ4(EI_TRGIN)

PZ5(EI_COMRESET)

PZ6(EO_MCUDATA)

PZ7(EO_MCUREQ)

PM7 (PWE)

PC0 (INT0)

INT2

PC2

D0 to D7

P10 to P17 (D8 to D15)

P40 to P47(A0 to A7

P50 to P57(A8 to A15

P60 to P67

A16 to A23

P70 ( RD )

P73 (EA24)

P74 (EA25)

P75(R/

W , NDR/ B )

P76 (

WAIT )

P80 (

P81 (

P82 (

P83 (

P84 (

P85

)

0CS

1CS,SDCS

2CS,CSZA,SDCS

3CS,CSXA

)

CSZB

CSZC

)

)

P71 ( WRLL ,NDRE )

P72 (

P86 (

P87 (

,NDWE )

WRLU

,

CSZD

CSXB,CE1ND

)

CE0ND

)

PJ5 (NDALE)

PJ6

NDCLE

PA0 to PA7 (KI0 to KI7)

PN0 to PN7 (KO0 to KO7)

PC7 (KO8)

PM2

ALARM,MLDALM

)

MELODY/

ALARM-OUT

PV3

PV4

PV0 (SCLK0)

PV1

PV2

PW7 to 0

PC4 (EA26)

PC5 (EA27)

PC6 (EA28)

SDRAM

Controller

PORTV

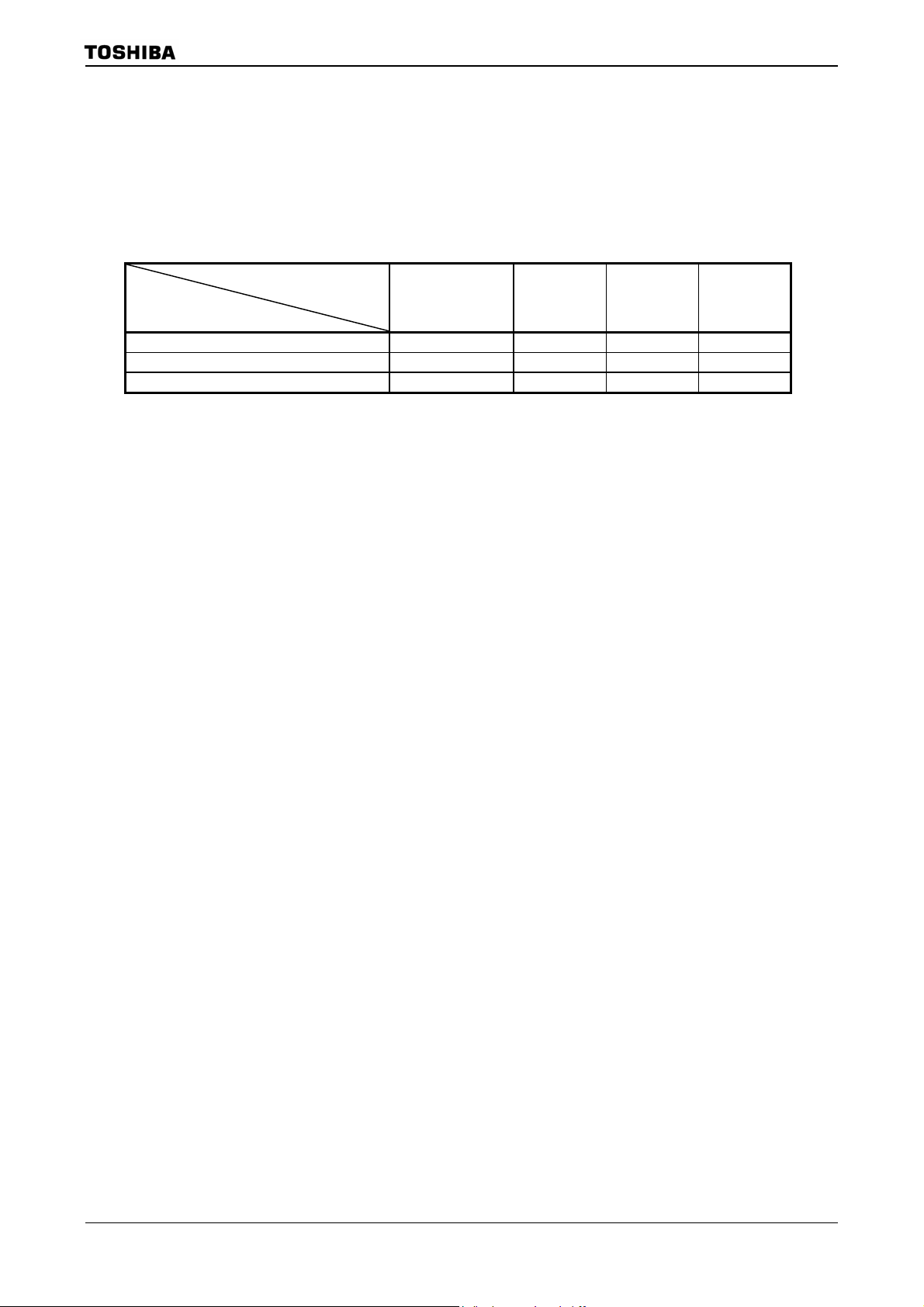

Figure 1.1 Block Diagram of TMP92CZ26A

92CZ26A-5

Page 9

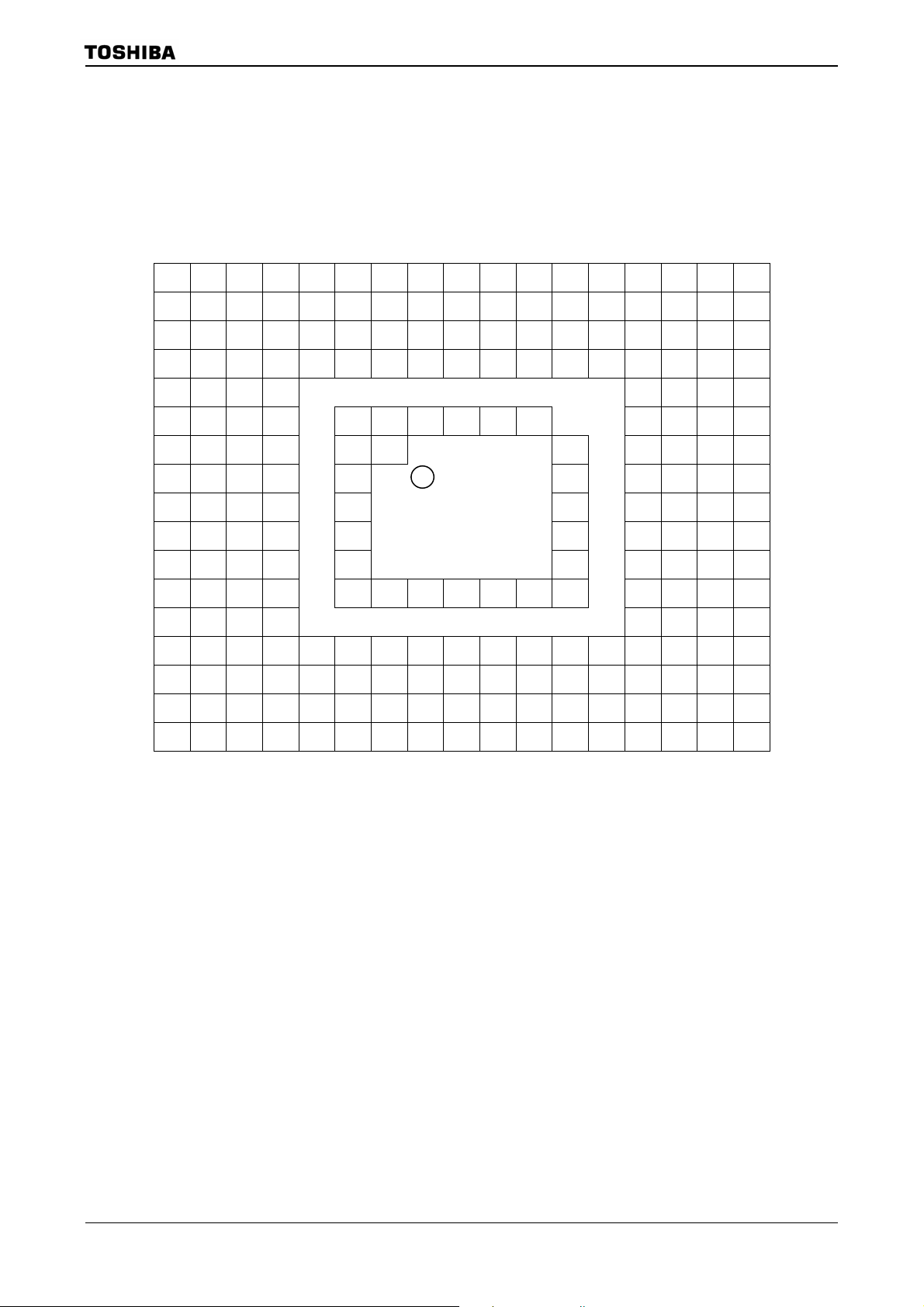

2. Pin Assignment and Pin Functions

The assignment of input/output pins for TMP92CZ26A, their names and functions are as follows;

2.1 Pin Assignment Diagram (Top View)

Figure 2.1.1 shows the pin assignment of the TMP92CZ26A.

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17

B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 C14 C15 C16 C17

D1 D2 D3 D5 D6 D7 D8 D9 D10 D11 D12 D13 D15 D16 D17

E1 E2 E3 E4 E14 E15 E16 E17

F1 F2 F3 F4 F6 F7 F8 F9 F10 F11 F14 F15 F16 F17

G1 G2 G3 G4 G6 G7 G12 G14 G15 G16 G17

H1 H2 H3 H4 H6 H12 H14 H15 H16 H17

TMP92CZ26A

J1 J2 J3 J4 J6 J12 J14 J15 J16 J17

K1 K2 K3 K4 K6 K12 K14 K15 K16 K17

L1 L2 L3 L4 L6 L12 L14 L15 L16 L17

M1 M2 M3 M4 M6 M7 M8 M9 M10 M11 M12 M14 M15 M16 M17

N1 N2 N3 N4 N14 N15 N16 N17

P1 P2 P3 P5 P6 P7 P8 P9 P10 P11 P12 P13 P15 P16 P17

R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R14 R15 R16 R17

T1 T2 T3 T4 T5 T6 T7 T8 T9 T10 T11 T12 T13 T14 T15 T16 T17

U1 U2 U3 U4 U5 U6 U7 U8 U9 U10 U11 U12 U13 U14 U15 U16 U17

Figure 2.1.1 Pin assignment diagram (P-FBGA228)

4 balls of A1, A17, U1 and U17 (most outside 4 corner of BGA package) are Dummy Balls.

These balls are not connected with internal LSI chip, electr ical characteristics.

A1 and U1, A17 and U17 are shorted in internal package. It is recommended that using to

OPEN check of mounting if mounting this LSI to Target board.

TMP92CZ26A

P-FBGA228

TOP VIEW

Example: If checking signal (or voltage) via A1-U1-U17-A17, short U17 and U1 on Target board

beforehand, and input signal (or voltage) from A1, and check voltage of A17.

92CZ26A-6

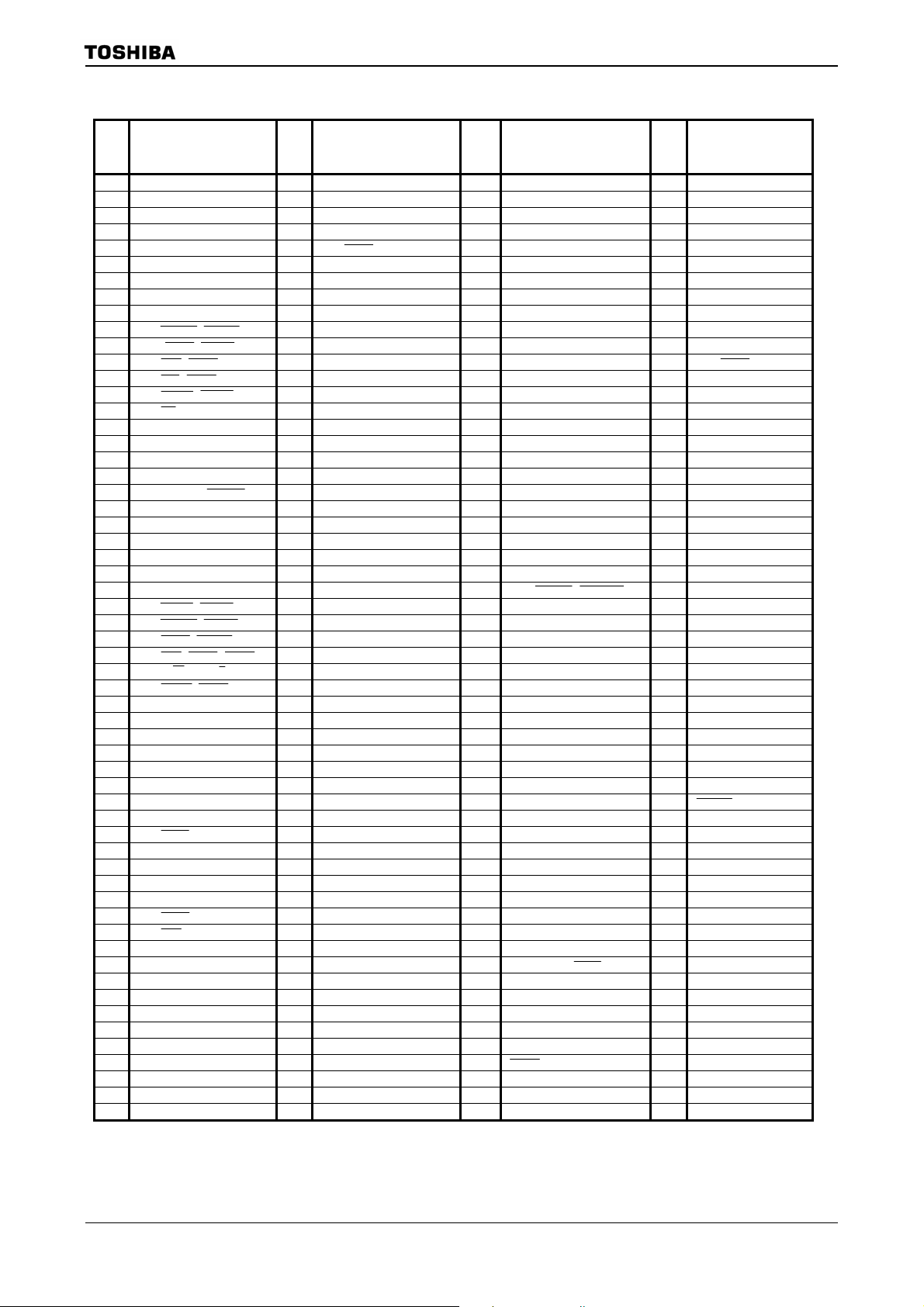

Page 10

TMP92CZ26A

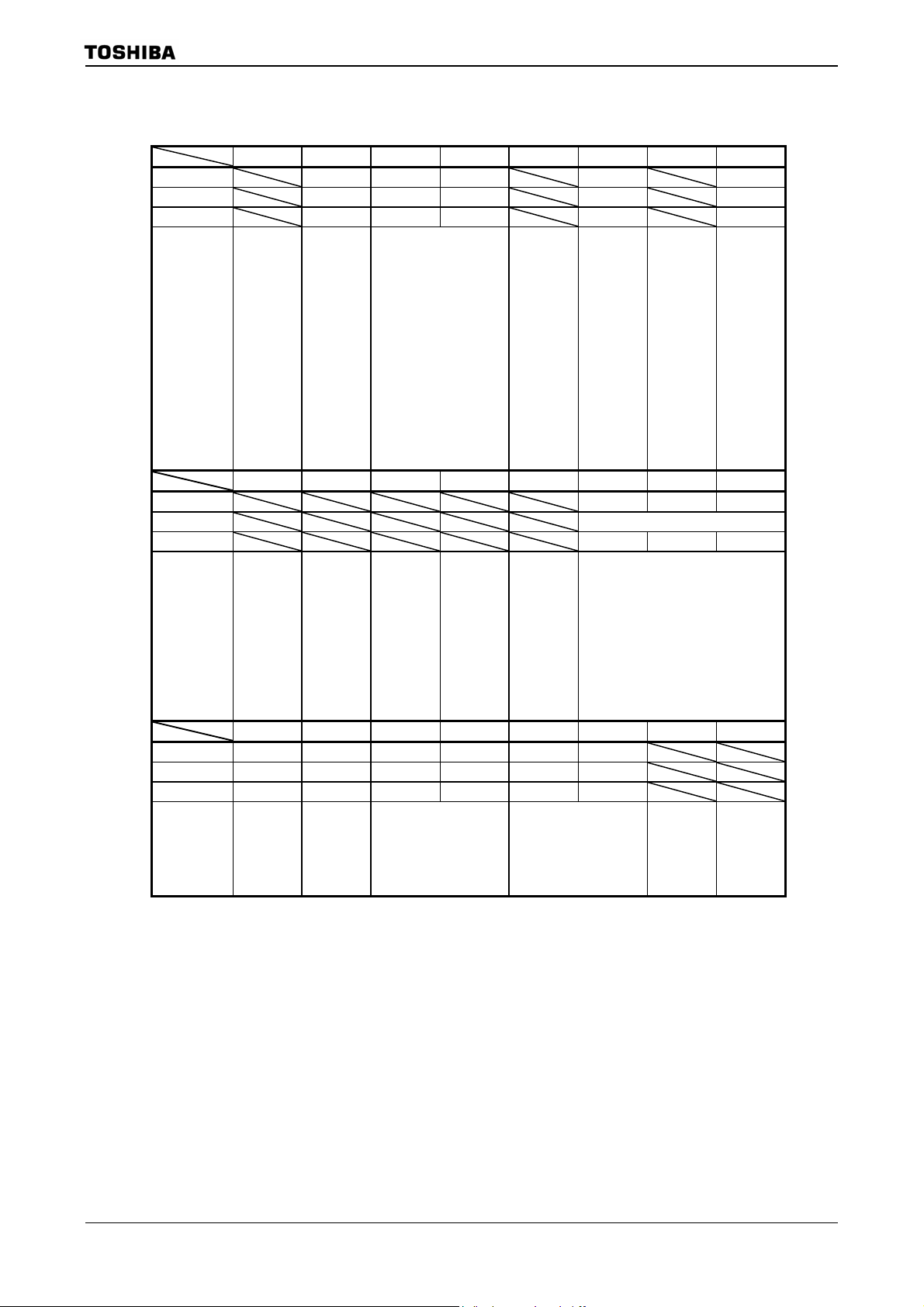

Table 2.1.1 Pin number and the name

Ball

No.

A1 Dummy1 D9 P73,EA24 J15 PT5,LD13 P15 PK4,LHSYNC

A2 PG2,AN2, MX D10 PF4,I2S1DO J16 P47,A7 P16 P13,D11

A3 PA6,KI6 D11 PF7,SDCLK J17 P46,A6 P17 P14,D12

A4 PA5,KI5 D12 PJ4,SDLUDQM K1 PN3,KO3 R1 X2

A5 PA3,KI3 D13 P85,

A6 PA1,KI1 D15 PU6,LD22 K3 PN5,KO5 R3 PC3,INT3,TA2IN

A7 DVCC1A5 D16 P61,A17 K4 PN6,KO6 R4 PX5,X1USB

A8 PF1,I2S0DO D17 P60,A16 K6 DVCC3A2 R5 PP7,TB1OUT0

A9 PJ6,NDCLE E1 P96,PX,INT4 K12 DVCC3A7 R6 PP1,TA3OUT

A10 PJ1,

A11 P87,

A12 P83,

A13 P81,

A14 P72,

A15 P70,RD E16 P57,A15 L2 PN7,KO7 R12 PZ2,EI_PODREQ

A16 P65,A21 E17 P56,A14 L3 PM1,MLDALM,TA1OUT R13 PZ4,EI_TRGIN

A17 Dummy3 F1 DVCC1B1 L4 PM7,PWE R14 PZ6,EO_MCUDATA

B1 VREFH F2 PW6 L6 DVSS3 R15 PZ7,EO_MCUREQ

B2 PG5,AN5 F3 PW5 L12 DVSS7 R16 P15,D13

B3 PG3,AN3,MY,

B4 PA7,KI7 F6 DVCC3A12 L15 PT1,LD9 T1 X1

B5 PA2,KI2 F7 DVCC3A11 L16 P43,A3 T2 AM0

B6 PA0,KI0 F8 DVSS11 L17 P42,A2 T3 AM1

B7 PF2,I2S0WS F9 DVCC3A10 M1 PK3,LVSYNC T4 PP6,TB0OUT0

B8 PF0,I2S0CKO F10 DVSS10 M2 PC0,INT0 T5 PL0,LD0

B9 PJ5,NDALE F11 DVCC3A9 M3 PM2,

B10 PJ2,

B11 PJ0,

B12 P86.

B13 P82,

B14 P75,R/W,NDR/B G1 DVCC3B1 M9 DVSS5 T11 PK1,LLOAD

B15 P71,

B16 P64,A20 G3 PV0,SCLK0 M11 DVSS6 T13 P02,D2

B17 DVCC1A4 G4 PV1 M12 DVCC3A6 T14 P04,D4

C1 AVCC G6 DVSS1 M14 PK7,LGOE2 T15 P06,D6

C2 VREFL G7 DVSS12 M15 PT0,LD8 T16 P11,D9

C3 PG4,AN4 G12 DVSS9 M16 P41,A1 T17 P12,D10

C4 PG1,AN1 G14 PU3,LD19 M17 P40,A0 U1 Dummy2

C5 PA4,KI4 G15 PU0,LD16 N1 DVCC1A1 U2

C6 PC5,EA27 G16 P53,A11 N2 PC1,INT1,TA0IN U3 D+

C7 P76,

C8 PF5,I2S1WS H1 PV7,SCL N4 DVSS1C U5 DVCC1A2

C9 PF3,I2S1CKO H2 PV6,SDA N14 PK6,LGOE1 U6 PL1,LD1

C10 PJ7,SDCKE H3 PV3 N15 PK5,LGOE0 U7 PL3,LD3

C11 PJ3,SDLLDQM H4 PV2 N16 P17,D15 U8 XT1

C12 P84,

C13 P80,

C14 P67,A23 H14 PU1,LD17 P2 PC2,INT2 U11 PK0,LCP0

C15 P66,A22 H15 PT7,LD15 P3 P92,SCLK0,

C16 P63,A19 H16 P51,A9 P5 PX4,CLKOUT, LDIV U13 P03,D3

C17 P62,A18 H17 P50,A8 P6 PP2,TA5OUT U14 P05,D5

D1 P97,PY J1 PN2,KO2 P7 PP4,INT6,TB0IN0 U15 P07,D7

D2 AVSS J2 PN1,KO1 P8 PR0,SPDI U16 P10,D8

D3 PW0 J3 PN0,KO0 P9 PR3,SPCLK U17 Dummy4

D5 PG0,AN0 J4 PV4 P10

D6 PC6,EA28 J6 DVSS2 P11 PZ1,EI_SYNCLK

D7 PC4,EA26 J12 DVSS8 P12 PZ3,EI_REFCLK

D8 P74,EA25 J14 PT6,LD14 P13 PZ5,EI_COMRESET

Pin name

SDCAS,SRLUB

CSXB,CE1ND

3CS,CSXA

1CS,SDCS

WRLU

SDWE,SRWR

SDRAS,SRLLB

CSZD,CE0ND

2CS,CSZA,SDCS

WRLL,NDRE

G17 P52,A10 N3 P91,RXD0 U4 D-

WAIT

CSZB

H12 DVCC3A8 P1 DVCC1C U10 PL7.LD7

0CS

E3 PW2 K15 PT3,LD11 R8 PP5,INT7,TB1IN0

E4 PW3 K16 P45,A5 R9 PR2,

E14 PU7,LD23,EO_TRGOUT K17 P44,A4 R10 PX7

,

E15 PU4,LD20 L1 PK2,LFR R11 PZ0,EI_PODDATA

NDWE

ADTRG

F14 PU5,LD21 M4 P90,TXD0 T7 PL4,LD4

F16 P55,A13 M7 DVSS4 T9 PR1,SPDO

G2 PW7 M10 DVCC3A5 T12 P00,D0

H6 DVCC3A1 N17 P16,D14 U9 XT2

Ball

No.

E2 PW1 K14 PT4,LD12 R7 PP3,INT5,TA7OUT

F4 PW4 L14 PT2,LD10 R17 DVCC1A3

F15 PU2,LD18 M6 DVCC3A3 T8 PL5,LD5

F17 P54,A12 M8 DVCC3A4 T10 PL6,LD6

Pin name

K2 PN4,KO4 R2 PC7,KO8

CSZC

Ball

No.

Pin name

ALARM,MLDALM

U12 P01,D1

0CTS

DBGE

Ball

No.

T6 PL2,LD2

RESET

Pin name

SPCS

Note1: The P96, P97 and PG0~PG5 operate with the AVCC power supply.

Note2: The PW0~PW7 and PV0~PV7 operate with the DVCC3B power supply.

Note3: The X1 and X2 operate with the DVCC1C power supply.

92CZ26A-7

Page 11

2.2 Pin names and Functions

The names of the input/output pins and their functions are described below.

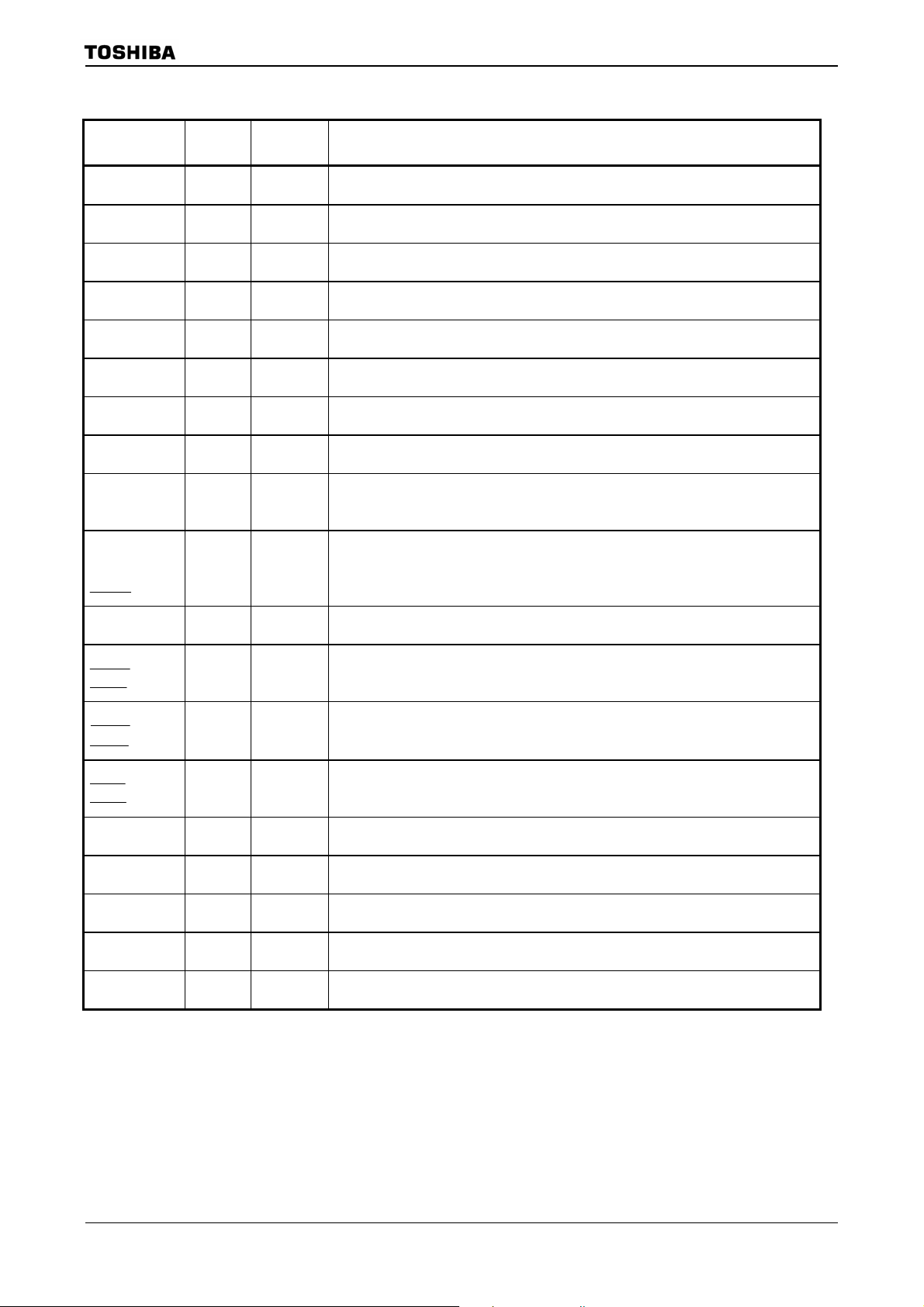

Table 2.2.1 Pin names and functions (1/6)

TMP92CZ26A

Pin name

D0 to D7 8 I/O Data: Data bus D0 to D7.

P10 to P17

D8 to D15

P40 to P47

A0 to A7

P50 to P57

A8 to A15

P60 to P67

A16 to A23

P70

RD

P71

WRLL

NDRE

P72

WRLU

NDWE

P73

EA24

P74

EA25

P75

R/

W

NDR/

B

P76

WAIT

P80

0CS

P81

1CS

SDCS

P82

2CS

CSZA

SDCS

P83

3CS

CSXA

P84

CSZB

P85

CSZC

Number of

Pins

8

8

8

8

1 Output

1 I/O

1 I/O

1 I/O

1 I/O

1 I/O

1

1

1 Output

1 Output

1 Output

1 Output

1 Output

I/O Functions

I/O

I/O

Output

Output

Output

Output

I/O

Output

Output

Output

Output

Output

Output

Output

Output

Output

Input

I/O

Input

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Port 1: I/O port. Input or output is specifiable in units of bit.

Data : Data bus D8 to D15.

Port 4: Output port.

Address : Address bus A0 to A7.

Port 5: Output port.

Address : Address bus A8 to A15.

Port 6 : I/O port. Input or output is specifiable in units of bit.

Address : Address bus A16 to A23.

Port 70 : Output port.

Read : Outputs strobe signal to read external memory.

Port 71 : Output port.

Write : Outputs strobe signal to write data on pins D0 to D7.

NAND Flash read : Outputs strobe signal to read external NAND-Flash.

Port 72 : I/O port.

Write : Outputs strobe signal to write data on pins D8 to D15.

NAND Flash write : Write enable for NAND Flash.

Port 73 : I/O port.

Expanded address 24.

Port 74 : I/O port.

Expanded address 25.

Port 75 : I/O port.

Read/Write : “High” represents read or dummy cycle and “Low” write cycle.

NAND Flash Ready(1) / Busy(0) input.

Port 76: I/O port.

Wait: Signal used to request CPU bus wait.

Port 80: Output port.

Chip select 0: Outputs “Low” when address is within specified address area.

Port 81 : Output port

Chip select 1: Outputs “Low” when address is within specified address area.

Chip select for SDRAM : Outputs “Low” when the address is within SDRAM address area.

Port 82 : Output port.

Chip select 2: Outputs “Low” when address is within specified address area.

Expanded address ZA : Outputs “Low” when address is within specified address area.

Chip select for SDRAM : Outputs “0” when the address is within SDRAM address area.

Port 83 : Output port.

Chip select 3: Outputs “Low” when address is within specified address area.

Expanded address XA : Outputs “Low” when address is within specified address area.

Port 84 : Output port.

Expanded address ZB : Outputs “Low” when address is within specified address area.

Port 85 : Output port.

Expanded address ZC : Outputs “Low” when address is within specified address area.

92CZ26A-8

Page 12

TMP92CZ26A

Pin name

P86

CSZD

CE0ND

P87

CSXB

CE1ND

P90

TXD0

P91

RXD0

P92

SCLK0

0CTS

P96

INT4

PX

P97

PY

PA0 to PA7

KI0 to KI7

PC0

INT0

PC1

INT1

TA0IN

PC2

INT2

PC3

INT3

TA2IN

PC4

EA26

PC5

EA27

PC6

EA28

PC7

KO8

Table 2.2.1 Pin names and functions (2/6)

Number

of Pins

1

1

1

1

1

1 Input

1 Input

8

1

1

1

1

1

1

1

1

I/O Functions

Output

Output

Output

Output

Output

Output

I/O

Output

I/O

Input

I/O

I/O

Input

Input

Output

Output

Input

Input

I/O

Input

I/O

Input

Input

I/O

Input

I/O

Input

Input

I/O

Output

I/O

Output

I/O

Output

I/O

Output

Port 86 : Output port.

Expanded address ZD : Outputs “Low” when address is within specified address area.

Chip select of NAND Flash 0: Outputs “Low” when NAND Flash 0 is enable.

Port 87 : Output port.

Expanded address XB : Outputs “Low” when address is within specified address area.

Chip select of NAND Flash 1: Outputs “Low” when NAND Flash 1 is enable.

Port 90: I/O port.

Transmit data of serial 0: programmable open drain output.

Port 91: I/O port. (Schmitt input)

Receive data of serial 0.

Port 92: I/O port. (Schmitt input)

Clock I/O of serial 0

Enable to send data of serial 0 (Clear to send).

Port 96: Input port. (schmitt input, with pull-up resistor)

Interrupt request pin 4 : Interrupt request pin with programmable rising/falling edge.

X-Plus : Pin connected to X+ pin for Touch Screen I/F.

Port 97: Input port. (schmitt input)

Y-Plus : Pin connected to Y+ pin for Touch Screen I/F.

Port A0 to A7: Input port.

Key input 0 to 7: For key on wake-up 0 to 7. (Schmitt input, with pull-up resistor)

Port C0: I/O port. (Schmitt input)

Interrupt request pin 0 : Interrupt request pin with programmable rising/falling edge.

Port C1: I/O port. (Schmitt input)

Interrupt request pin 1 : Interrupt request pin with programmable rising/falling edge.

Timer A0 input: Input pin of 8 bit timer 0.

Port C2: I/O port. (Schmitt input)

Interrupt request pin 2 : Interrupt request pin with programmable rising/falling edge.

Port C3: I/O port. (Schmitt input)

Interrupt request pin 3 : Interrupt request pin with programmable rising/falling edge.

Timer A2 input: Input pin of 8 bit timer 2.

Port C4: I/O port.

Expanded address 26.

Port C5: I/O port.

Expanded address 27.

Port C6: I/O port.

Expanded address 28.

Port C7: I/O port.

Key output 8: Key scan strobe pin (programmable open drain output).

92CZ26A-9

Page 13

TMP92CZ26A

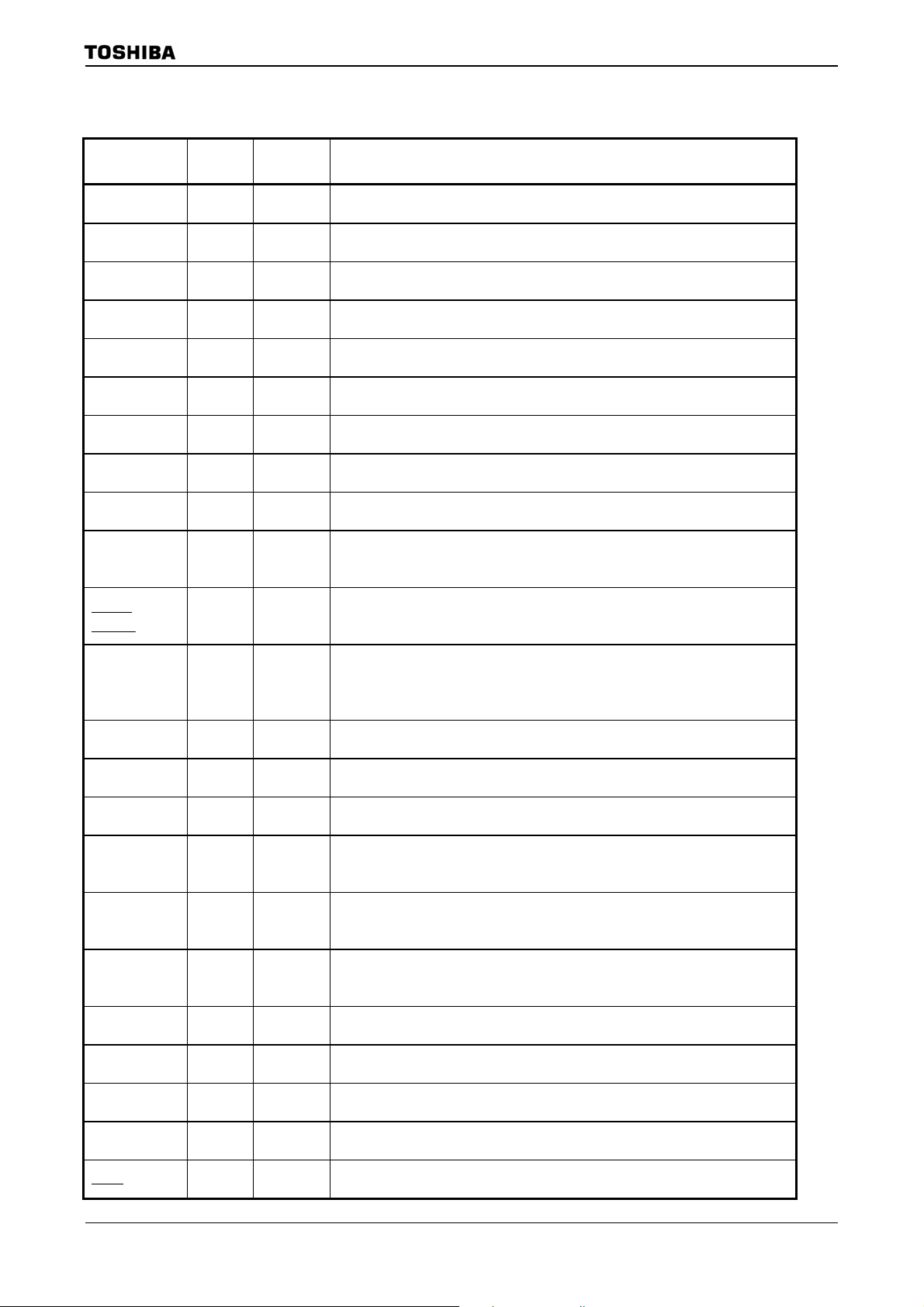

Table 2.2.1 Pin names and functions (3/6)

Pin name

PF0

I2S0CKO

PF1

I2S0DO

PF2

I2S0WS

PF3

I2S0WS

PF4

I2S1CKO

PF5

I2S1WS

PF7

SDCLK

PG0 to PG1

AN0 to AN1

PG2

AN2

MX

PG3

AN3

MY

ADTRG

PG4 to PG5

AN4 to AN5

PJ0

SDRAS

SRLLB

PJ1

SDCAS

SRLUB

PJ2

SDWE

SRWR

PJ3

SDLLDQM

PJ4

SDLUDQM

PJ5

NDALE

PJ6

NDCLE

PJ7

SDCKE

Number of

Pins

1

1

1

1

1

1

1

2

1

1

2

1

1

1

1

1

1

1

1

I/O Functions

I/O

Output

I/O

Output

I/O

Output

I/O

Output

I/O

Output

I/O

Output

Output

Output

Input

Input

Input

Input

Output

Input

Input

Output

Input

Input

Input

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

I/O

Output

I/O

Output

Output

Output

Port F0: I/O port.

Outputs clock of I2S0.

Port F1: I/O port.

Outputs data of I2S0.

Port F2: I/O port.

Outputs word select signal of I2S0.

Port F3: I/O port.

Outputs clock of I2S1.

Port F4: I/O port.

Outputs data of I2S1.

Port F5: I/O port.

Outputs word select signal of I2S1.

Port F7: Output port.

Clock for SDRAM.

Port G0 to G1: Input port.

Analog input pin 0 to 1 : Input pin of A/D converter.

Port G2: Input port.

Analog input pin 2 : Input pin of A/D converter.

X-Minus : Pin connected to X- pin for Touch Screen I/F.

Port G3: Input port.

Analog input pin 3 : Input pin of A/D converter.

Y-Minus : Pin connected to Y- pin for Touch Screen I/F.

A/D Trigger : Request signal of A/D start.

Port G4 to G5: Input port.

Analog input pin 4 to 5 : Input pin of A/D converter.

Port J0: Output port.

Outputs strobe signal of SDRAM row address.

Data enable signal for D0 to D7 of SRAM.

Port J1: Output port.

Outputs strobe signal of SDRAM column address.

Data enable signal for D8 to D15 of SRAM.

Port J2: Output port.

Outputs write enable signal of SDRAM.

Write enable of SRAM: Outputs strobe signal to write data.

Port J3: Output port.

Data enable signal for D0 to D7 of SDRAM.

Port J4: Output port.

Data enable signal for D8 to D15 of SDRAM.

Port J5: I/O port.

Address latch enable signal of NAND Flash.

Port J6: I/O port.

Command latch enable signal of NAND Flash.

Port J7: Output port.

Clock enable signal of SDRAM.

92CZ26A-10

Page 14

TMP92CZ26A

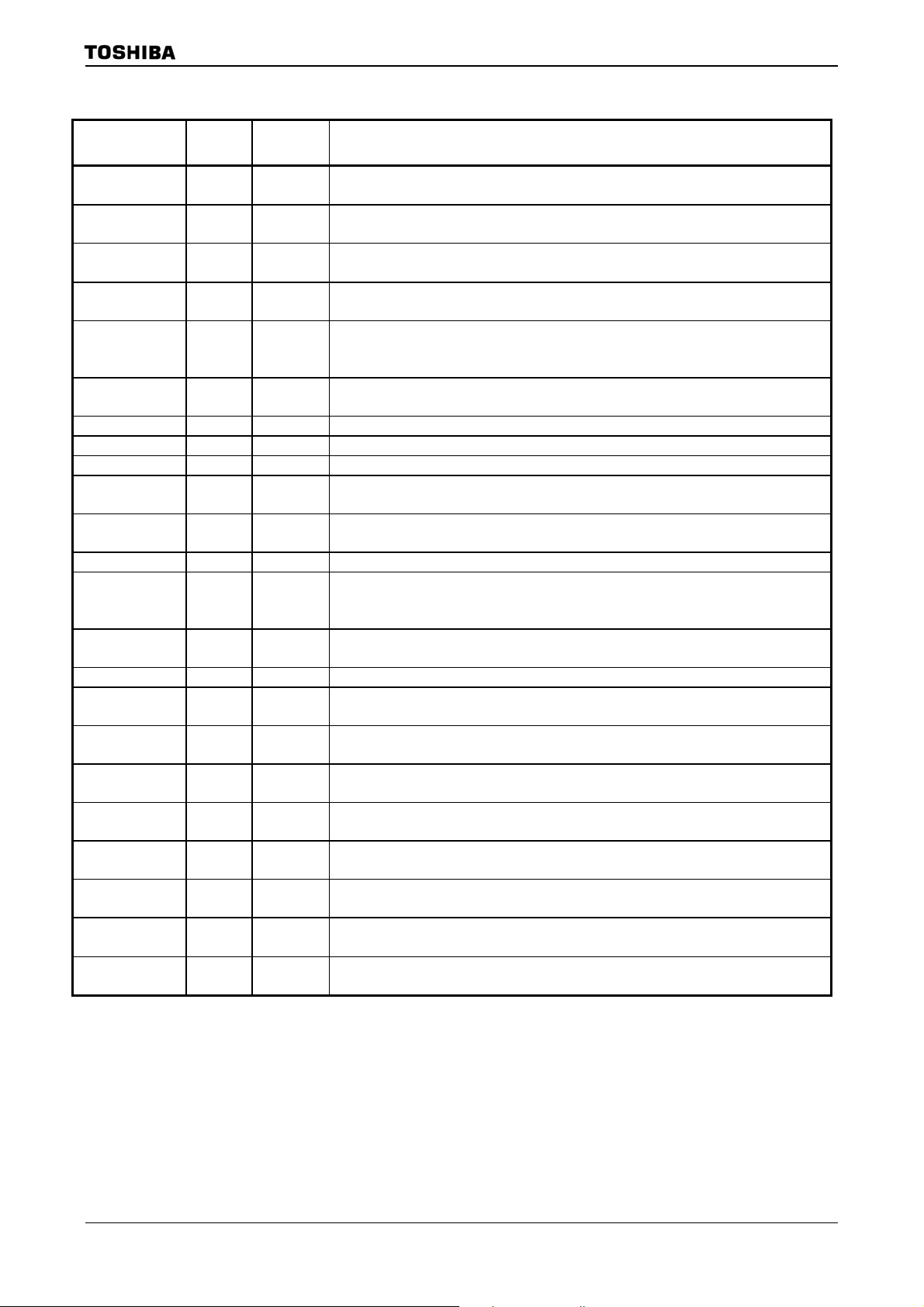

Table 2.2.1 Pin names and functions (4/6)

Pin name

PK0

LCP0

PK1

LLOAD

PK2

LFR

PK3

LVSYNC

PK4

LHSYNC

PK5

LGOE0

PK6

LGOE1

PK7

LGOE2

PL0 to PL7

LD0 to LD7

PM1

TA1OUT

MLDALM

PM2

ALARM

SPCS

MLDALM

PM7

PWE

PN0 to PN7

KO0 to KO7

PP1

TA3OUT

PP2

TA5OUT

PP3

INT5

TA7OUT

PP4

INT6

TB0IN0

PP5

INT7

TB1IN0

PP6

TB0OUT0

PP7

TB1OUT0

PR0

SPDI

PR1

SPDO

PR2

Number of

Pins

1

1

1

1

1

1

1

1

8

1

1

1

8

1

1

1

1

1

1

1

1

1

1

I/O Functions

Output

Output

Output

Output

Output

Output

Output

Output

Output

Input

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

Output

I/O

Output

I/O

Output

I/O

Output

I/O

Input

Output

I/O

Input

Input

I/O

Input

Input

Output

Output

Output

Output

I/O

Input

I/O

Output

I/O

Output

Port K0: Output port.

Signal for LCD driver.

Port K1: Output port.

Signal for LCD driver.: Data load signal

Port K2: Output port.

Signal for LCD driver.

Port K3: Output port.

Signal for LCD driver. : Vertical sync signal

Port K4: Output port.

Signal for LCD driver. : Horizontal sync signal.

Port K5: Output port.

Signal for LCD driver.

Port K6: Output port.

Signal for LCD driver.

Port K7: Output port.

Signal for LCD driver.

Port L0 to L7: Output port.

Data bus for LCD driver: LD0 to LD7.

Port M1: Output port.

Timer A1 output: Output pin of 8 bit timer 1.

Melody / Alarm output pin.

Port M2: Output port.

Alarm output from RTC.

Melody / Alarm output pin (inverted).

Port M7 : Output port

External power supply control output: Pin to control ON/OFF of external power

supply. In st and-by mode, outputs “L” level. In other than stand-by mode, outputs

“H” level.

Port N: I/O port.

Key output 0 to 7 : Key scan strobe pin (programmable open drain output).

Port P1: I/O port.

Timer A3 output: Output pin of 8 bit timer 3.

Port P2: I/O port.

Timer A5 output: Output pin of 8 bit timer 5.

Port P3: I/O port. (Schmitt input)

Interrupt request pin 5 : Interrupt request pin with programmable rising/falling edge.

Timer A7 output: Output pin of 8 bit timer 7.

Port P4: I/O port. (Schmitt input)

Interrupt request pin 6 : Interrupt request pin with programmable rising/falling edge.

Timer B0 input: Input pin of 16 bit timer 0.

Port P5: I/O port. (Schmitt input)

Interrupt request pin 7 : Interrupt request pin with programmable rising/falling edge.

Timer B1 input: Input pin of 16 bit timer 1.

Port P6: I/O port.

Timer B0 output: Output pin of 16 bit timer 0.

Port P7: I/O port.

Timer B1 output: Output pin of 16 bit timer 1.

Port R0: I/O port.

Data input pin of SD card.

Port R1: I/O port.

Data output pin of SD card.

Port R2: I/O port.

Chip select signal of SD card.

92CZ26A-11

Page 15

TMP92CZ26A

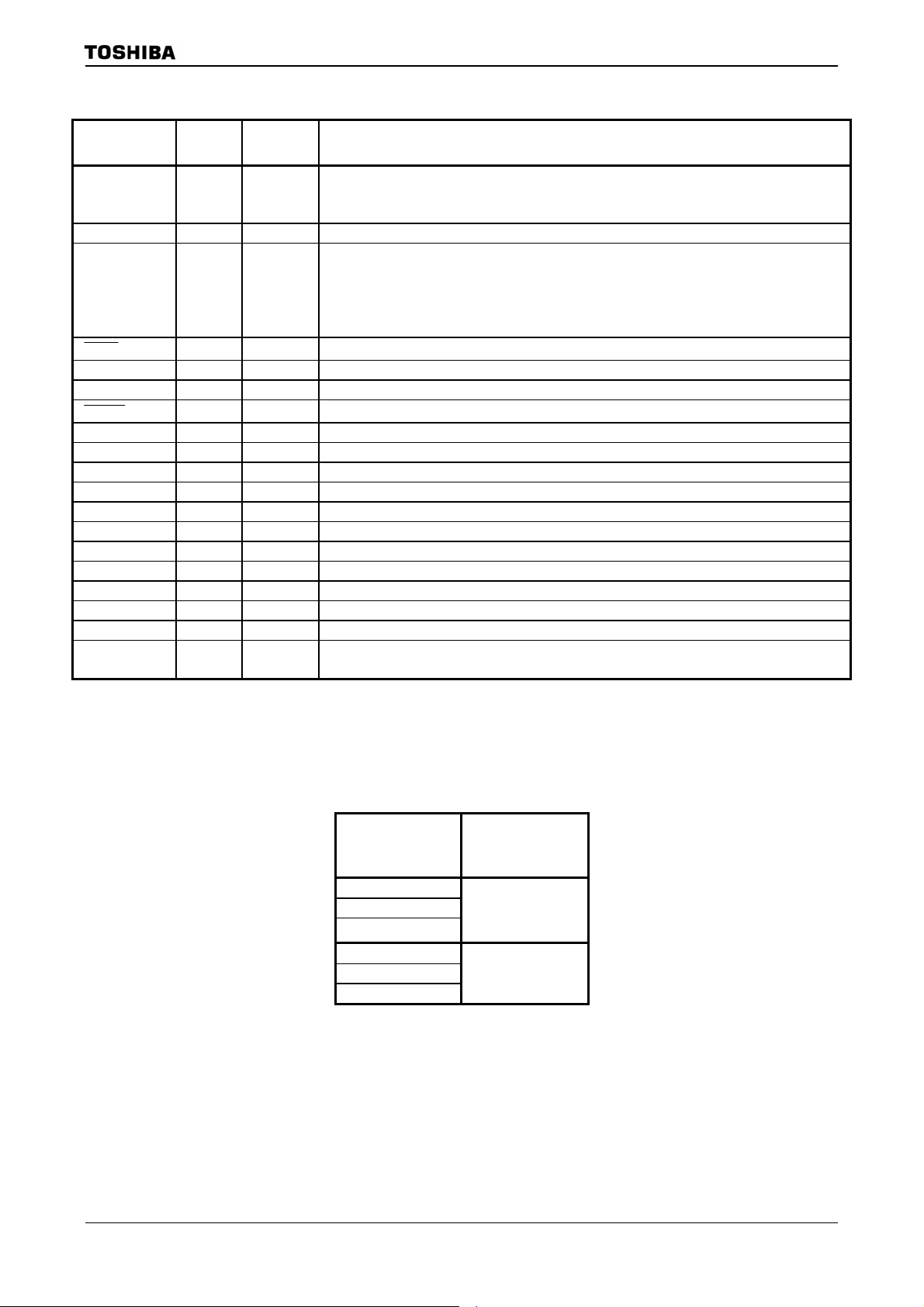

Table 2.2.1 Pin names and functions (5/6)

Pin name

PR3

SPCLK

PT0 to PT7

LD8 to LD15

PU0 to PU4,PU6

LD16 to LD20,LD22

PU5

LD21

PU7

LD23

EO_TRGOUT

PV0

SCLK0

PV1 1 I/O Port V1: I/O port.

PV2 1 I/O Port V2: I/O port.

PV3 to PV4 2 Output Port V3 to V4: Output port.

PV6

SDA

PV7

SCL

PW0 to PW7 8 I/O Port W0 to W7: I/O port.

PX4

CLKOUT

LDIV

PX5

X1USB

PX7 1 I/O Port X7: I/O port.

PZ0

EI_PODDATA

PZ1

EI_SYNCLK

PZ2

EI_PODREQ

PZ3

EI_REFCLK

PZ4

EI_TRGIN

PZ5

EI_COMRESET

PZ6

EO_MCUDATA

PZ7

EO_MCUREQ

Number of

Pins

1

8

6

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

I/O Functions

I/O

Output

I/O

Output

I/O

Output

I/O

Output

I/O

Output

Output

I/O

Output

I/O

I/O

I/O

I/O

Output

Output

Output

I/O

Input

I/O

Input

I/O

Input

I/O

Input

I/O

Input

I/O

Input

I/O

Input

I/O

Output

I/O

Output

Port R3: I/O port.

Clock output pin of SD card.

Port T0 to T7: I/O port.

Data bus for LCD driver: LD8 to LD15.

Port U0 to U4 , U6: I/O port

Data bus for LCD driver: LD16 to LD20, LD22.

Port U5: I/O port

Data bus for LCD driver: LD21

Port U7: I/O port

Data bus for LCD driver: LD23

Debug mode output pin

Port V0 : I/O port

Clock I/O of serial 0.

Port V6: I/O port

Send/receive data in I

Port V7: I/O port

Input/output clock in I

Port X4 : Output port

Internal clock output pin

Output pin for LCD driver

Port X5: I/O port.

Clock input pin of USB.

Port Z0: I/O port. (Schmitt input)

Debug mode input pin

Port Z1: I/O port. (Schmitt input)

Debug mode input pin

Port Z2: I/O port. (Schmitt input)

Debug mode input pin

Port Z3: I/O port. (Schmitt input)

Debug mode input pin

Port Z4: I/O port. (Schmitt input)

Debug mode input pin

Port Z5: I/O port. (Schmitt input)

Debug mode input pin

Port Z6: I/O port. (Schmitt input)

Debug mode output pin

Port Z7: I/O port. (Schmitt input)

Debug mode output pin

2

C mode.

2

C mode.

92CZ26A-12

Page 16

TMP92CZ26A

Table 2.2.1 Pin names and functions (6/6)

Pin name

D+, D- 2 I/O

CLKOUT 1 Output Internal clock output pin.

AM1,AM0 2 Input

DBGE

X1/X2 2 I/O High-frequency oscillator circuit connection pin.

XT1/XT2 2 I/O Low-frequency oscillator circuit connection pin.

RESET

VREFH 1 Input Pin for reference voltage input to A/D converter(H).

VREFL 1 Input Pin for reference voltage input to A/D converter(L).

AVCC 1

AVSS 1

DVCC3A 12

DVCC3B 1

DVCC1A 5

DVCC1B 1

DVSSCOM 12

DVCC1C 1

DVSS1C 1

Dummy4-1 4

Number of

Pins

1 Input Input pin in debug mode. (This pin is set to “Debug mode” by input “0”.)

1 Input Reset : Initialize TMP92CZ26A (schmitt input , with pull-up resistor)

I/O Functions

Data pin connected to USB.

In case USB is not used, connect both pins to pull-up(DVCC3A) or pull-down resistor for protect

current flows it.

Operation mode;

Fix to AM1=”0”,AM0=”1” for 16 bit external bus starting.

Fix to AM1=”1”,AM0=”0” is prohibit to set.

Fix to AM1=”1”,AM0=”1” for BOOT (32 bit internal Mask ROM) starting.

Fix to AM1=”0”,AM0=”0” is prohibited to set.

−

−

−

−

−

−

−

−

−

−

Power supply pin for A/D converter.

GND pin for AD converter (0V).

Power supply pin for peripheral I/O-A (Connect all DVCC3A pins to power supply pin.)

Power supply pin for peripheral I/O-B (Connect all DVCC3B pins to power supply pin.)

Power supply pin for internal logic-A. (Connect all DVCC1A pins to power supply pin.)

Power supply pin for internal logic-B. (Keep the voltage DVCC1A level.)

GND pin (0V). (Connect all DVSS pins to GND(0V).)

Power supply pin for High speed oscillator. (Keep the voltage DVCC1A level.)

GND pin (0V). (Connect to GND(0V).)

Dummy1 and Dummy2, Dummy3 and Dummy4 are shorted in package. (These pins are not

connected with internal LSI chip.)

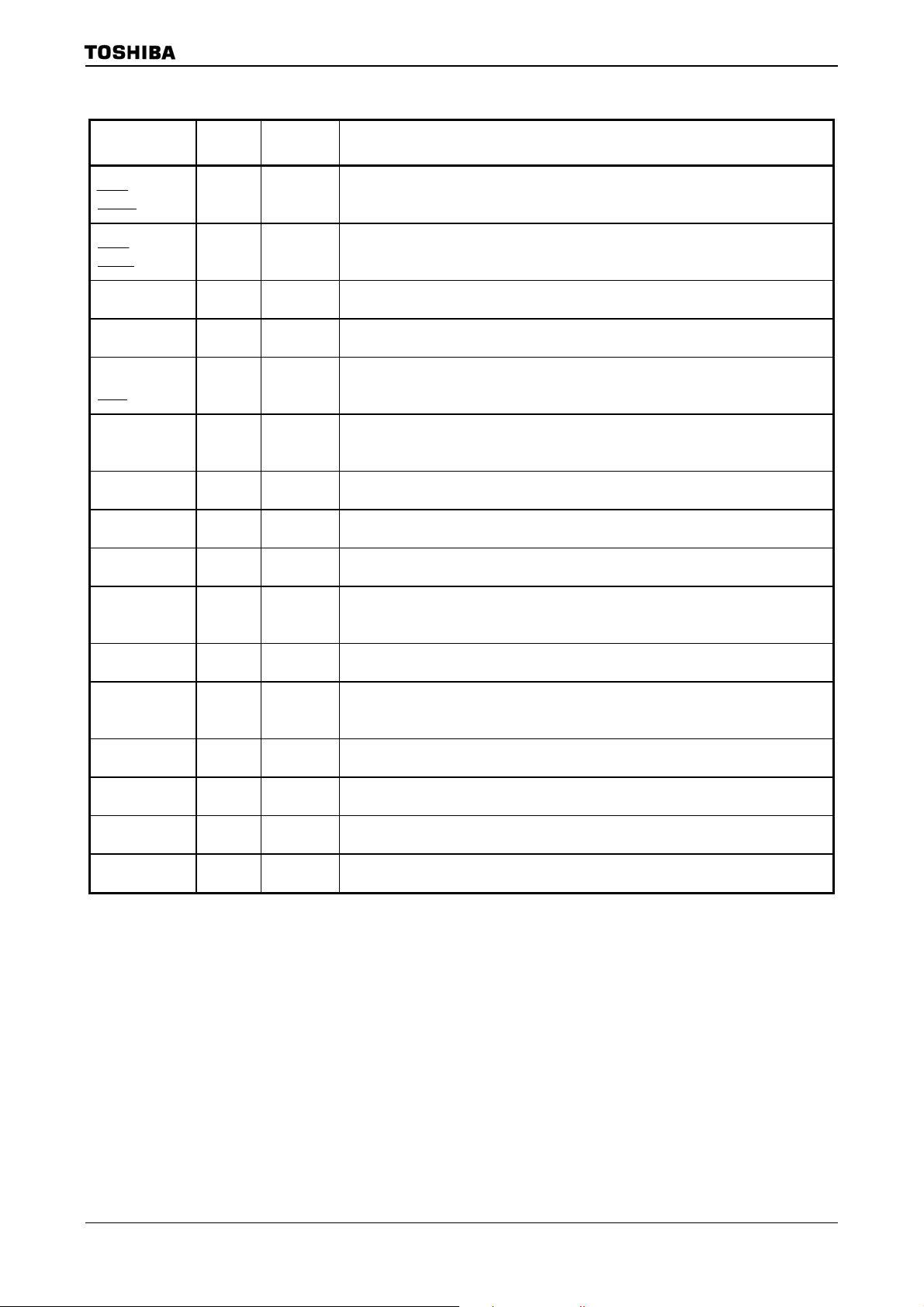

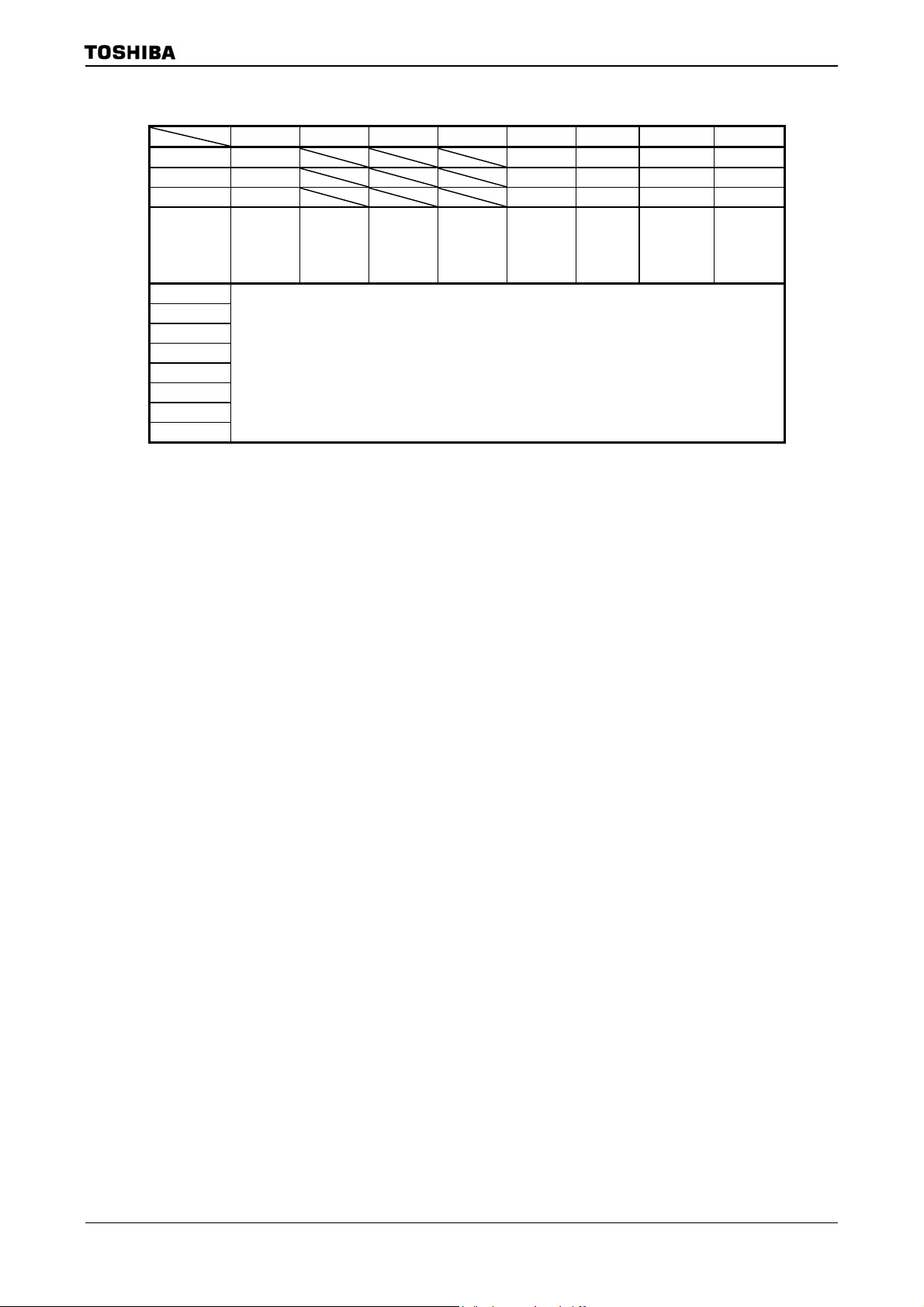

Tabl e 2.2.2 shows the range of operational voltage for power supply pins.

Table 2.2.2 the range of operational voltage for power supply pins

Range of

Power supply pin

operational

voltage

DVCC1A

DVCC1B

DVCC1C

DVCC3A

DVCC3B

AVCC

1.4V~1.6V

3.0V~3.6V

92CZ26A-13

Page 17

3. Operation

This section describes the basic components, functions and operation of the TMP92CZ26A.

3.1 CPU

The TMP92CZ26A c onta ins an ad vanced high-speed 32-bit CPU (900/H1 CPU)

3.1.1 CPU Outline

900/H1 CPU is high-speed and high-performance CPU based on 900/L1 CPU. 900/H1

CPU has expanded 32-bit internal data bus to process Instructions more quickly.

Outline is as follows:

TMP92CZ26A

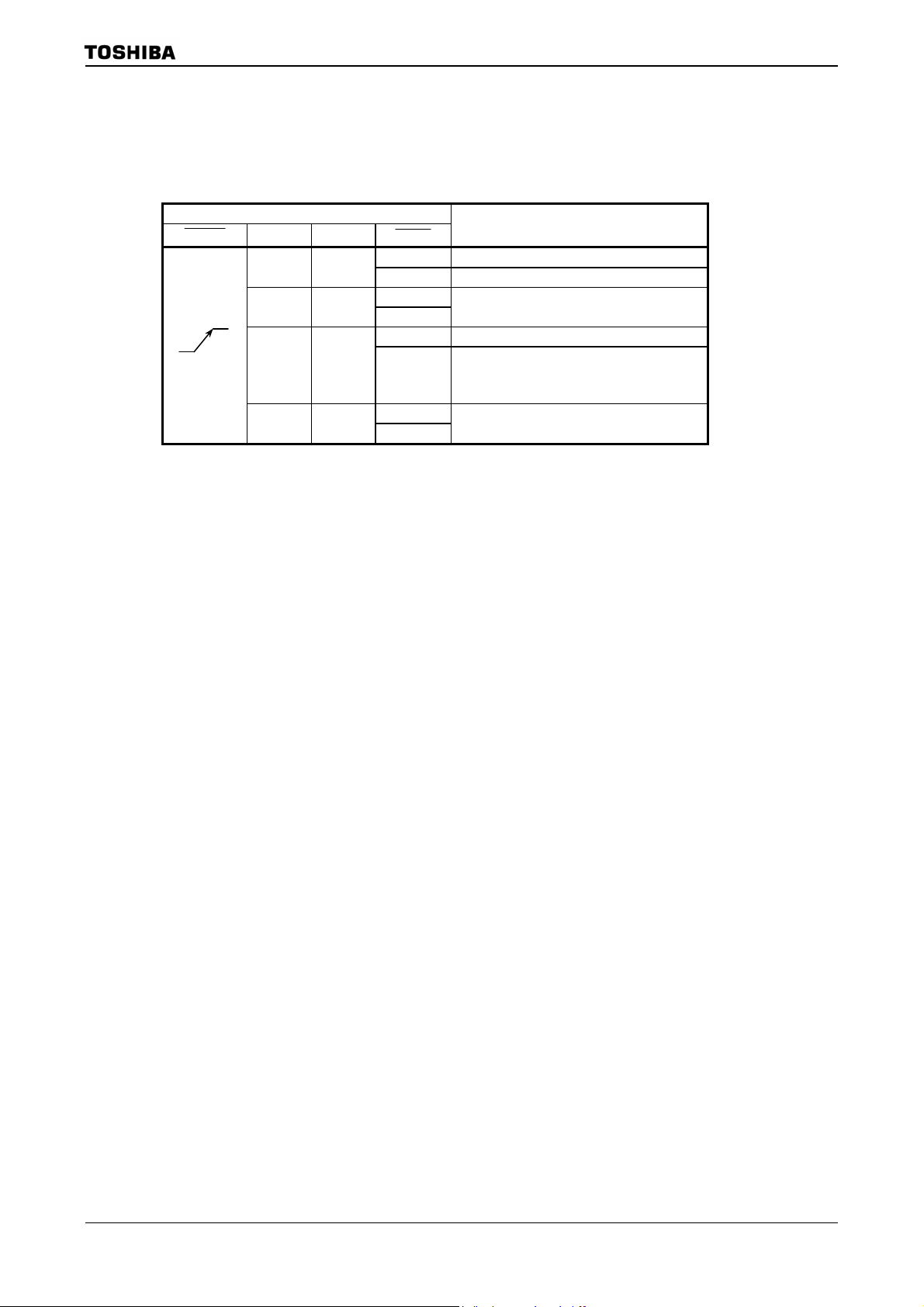

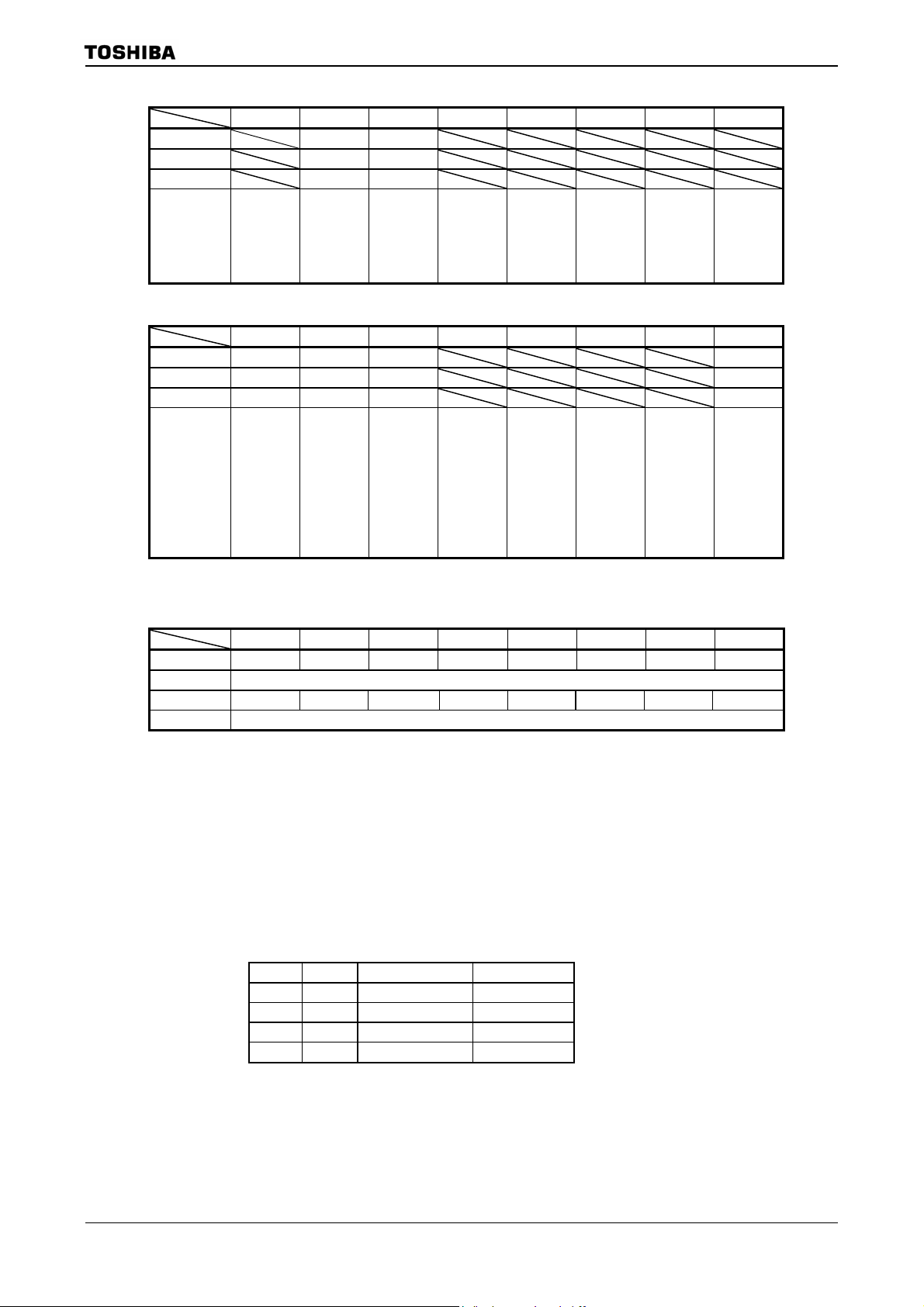

Table 3.1.1Outline of TMP92CZ26A

Parameter TMP92CZ26A

Width of CPU Address Bus 24-bit

Width of CPU Data Bus 32-bit

Internal Operating Frequency Max 80MHz

Minimum Bus Cycle 1-clock access

(12.5ns at 80MHz)

Internal RAM 32-bit 2-1-1-1 clock access

Internal Boot ROM 32 bit 2-clock access

Internal I/O

8-bit,

2-clock access

16-bit,

2-clock access

32-bit,

2-clock access

INTC,SDRAMC,

MEMC,LCDC,

TSI,PORT,

PMC

MMU,USB,

NDFC,SPIC,DMAC

I2S

MAC

32-bit,

1-clock access

8-bit,

5 to 6-clock access

External memory

(SRAM, MASKROM etc.)

External memory

(SDRAM)

External memory

(NAND FLASH)

Minimum Instruction

Execution Cycle

Conditional Jump 2-clock(25.0ns at 80MHz)

Instruction Queue Buffer 12-byte

Instruction Set Compatible with TLCS-900/L1

CPU mode Only maximum mode

Micro DMA 8-channel

Hardware DMA 6-channel

8/16-bit 2-clock access

(can insert some waits)

16-bit 1-clock access

8/16-bit 2-clock access

(can inset some waits)

1-clock(12.5ns at 80MHz)

(LDX instruction is deleted)

MAC

TMRA,TMRB,

SIO,RTC,

MLD/ALM, SBI

CGEAR,ADC,WDT

92CZ26A-14

Page 18

3.1.2 Reset Operation

When resetting the TMP92CZ26A microcontroller, ensure that the power supply voltage

is within the operating voltage range, and that the internal high-frequency oscillator has

stabilized. Then hold the

X1=10MHz).

At reset, since the clock doublers (PLL0) is bypassed and clock-gear is set to 1/16, system

clock operates at 625 kHz(X1=10MHz).

When the Reset has been accepted, the CPU performs the following. CPU internal

registers do not change when the Reset is released.

• Sets the Stack Pointer (XSP) to 00000000H.

• Sets bits <IFF2:0> of the Status Register (SR) to “111” (thereby setting the Interrupt

Level Mask Register to level 7).

• Clears bits <RFP1:0> of the Status Register to 00 (thereby selecting Register Bank 0).

When the Reset is released, the CPU starts executing instructions according to the

Program Counter settings.

• Sets the Program Counter (PC) as follows in accordance with the Reset Vector stored

at address FFFF00H~FFFF02H:

TMP92CZ26A

RESET input Low for at least 20 system clocks (32µs at

PC<7:0> ← data in location FFFF00H

PC<15:8> ← data in location FFFF01H

PC<23:16> ← data in location FFFF02H

When the Reset is accepted, the CPU sets internal I/O, ports and other pins as follows.

• Initializes the internal I/O registers as table of “Special Function Register” in Section

5.

Note1: This LSI builds in RAM internally. However, the data in internal RAM may not be held by Reset

operation. After reset, initialize the data in internal RAM.

Note2: This LSI builds in PMC function (for reducing stand-by current by blocking the power supply of

DVCC1A and DVCC1C). However, if executing reset operation without supplying DVCC1A and

DVCC1C, the current may flow to internal. When reset this LSI, supply the power of DVCC1A and

DVCC1C first and wait until the power supply stabilizes.

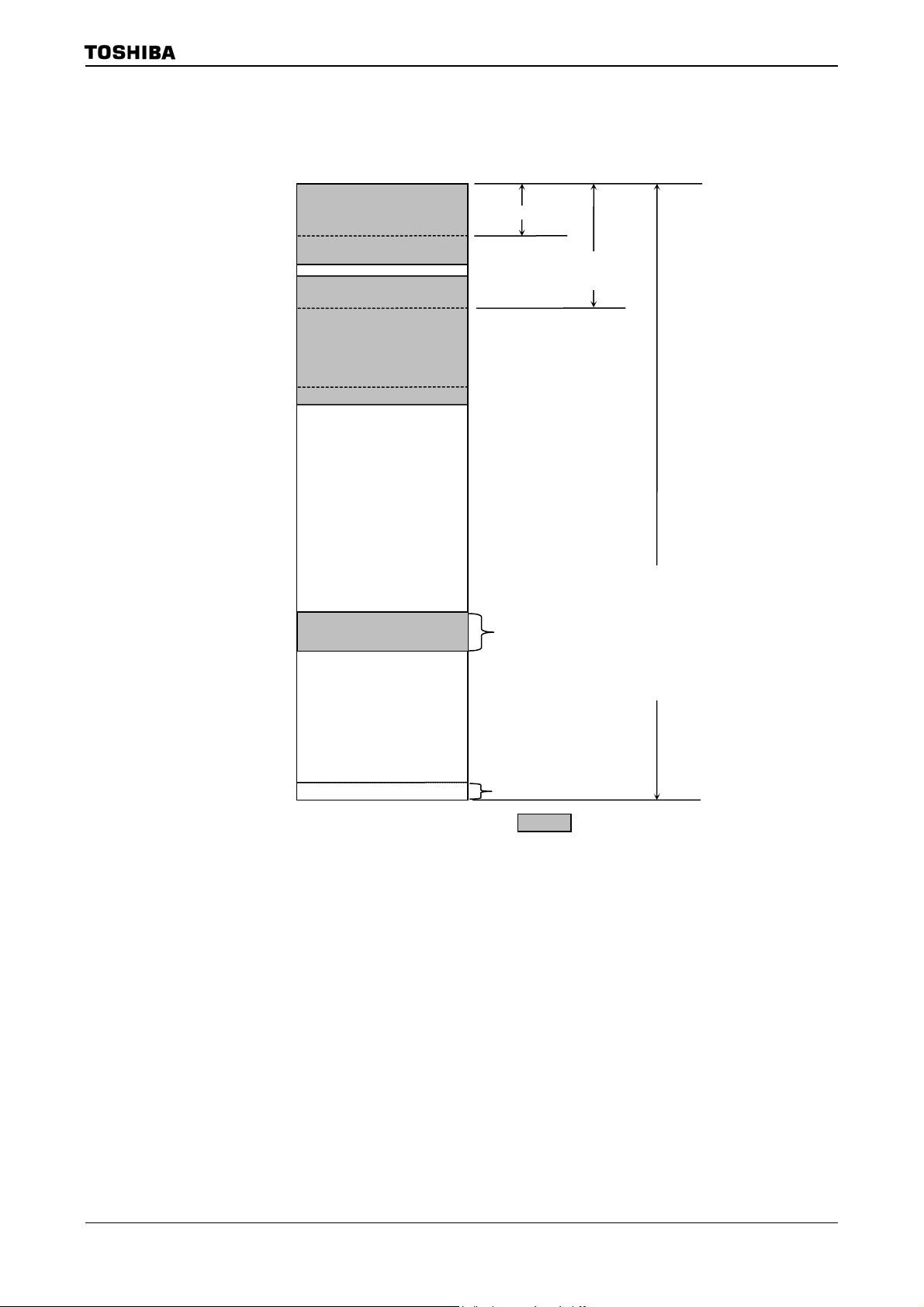

Figure 3.1.2 shows reset timing chart. Figure 3.1.2 shows the example of or der of supplying

power and the timing of releasing reset.

92CZ26A-15

Page 19

A

TMP92CZ26A

Read

Write

0FFFF00H

DATA-IN

(After reset is released, it is started

from 1 wait read cycle)

×(15.5∼16.5) Clock

SYS

f

Sampling

Sampling

sys

RESET

f

23∼0

CS2

CS0,1, 3

Figure 3.1.1 TMP92CZ26A Reset timing chart

DATA-IN

D0∼15

RD

SRxxB

DATA-OUT

D0∼15

WRxx

SRWR

: High-Z

SRxxB

92CZ26A-16

Page 20

)

1.5V

Power

3.3V

Power

This LSI has the restriction for the order of supplying power. Be sure to supply external

3.3V power with 1.5V power is supplied.

DVCC1A

DVCC1B

DVCC1C

After 1.5V power

supply is rising,

set 3.3V to ON.

DVCC3A

DVCC3B

AVCC

RESET

Power On

Power supply is rising with

in 100mS, and stabilizes.

High-frequency oscillation

stabilization time

+20 system clock

Stand-by Mode (PMC

Power supply is falling with

in 100mS, and stabilizes.

TMP92CZ26A

Power Off

After 1.5V power

supply is falling, set

3.3V to OFF.

PWE terminal

Note1: Inernal 1.5 V and External 3.3V power supply can be set to ON/OFF at the same time. However, external pin

may become unstable condition momentary. Therefore, set external power supply to ON/OFF during internal

power supply is stabile like above figure if there is possibility to affect machinery connected with micro controller.

Note2: When setting to ON, don’t set 3.3V power supply earlier than 1.5V power supply. When setting to OFF, don’t

set to 3.3V power supply later than 1.5 V power supply.

Figure 3.1.2 Power on Reset Timing Example

92CZ26A-17

Page 21

3.1.3 Setting of AM0 and AM1

Set AM1 and AM0 pins as Table 3.1.2 shows according to system usage.

Mode Setup input pin

RESET

AM1 AM0

0 1

1 0

1 1

0 0

Table 3.1.2 Operation Mode Setup Table

DBGE

0 Debug mode

1

0

1

0

1

0

1

Operation Mode

16-bit external bus starting

Test mode (Prohibit to set)

Test mode (Prohibit to set)

BOOT(32-bit internal-MROM )

starting

(BOOT mode)

Test mode (Prohibit to set)

TMP92CZ26A

92CZ26A-18

Page 22

3.2 Memory Map

Figure 3.2.1 is a memory map of the TMP92CZ26A.

000000H

000100H

001FF0H

002000H

010000H

046000H

04A000H

F00000H

F10000H

FFFF00H

FFFFFFH

Internal I/O

(8 Kbyte)

Internal RAM

(288 Kbyte)

(Internal Back Up RAM 16kbyte)

External memory

Provisional Emulator Control Area

(64kbyte)

External memory

Vector table (256 Byte)

Direct area(n)

64Kbyte area

(nn)

16Mbyte area

(R)

(

(Note1)

(R

(R

(R + d8/16)

(nnn)

( = Internal area)

TMP92CZ26A

−R)

+)

+ R8/16)

Figure 3.2.1 Memory Map

Note1: Don’t use specified 64kbyte area of above 16M byte when using debug mode. This is because the area is reserved

for control in the debug mode.

Note2: Don’t use the last 16-byte area (FFFFF0H to FFFFFFH). This area is reserved as internal area.

92CZ26A-19

Page 23

3.3 Clock Function and Standby Function

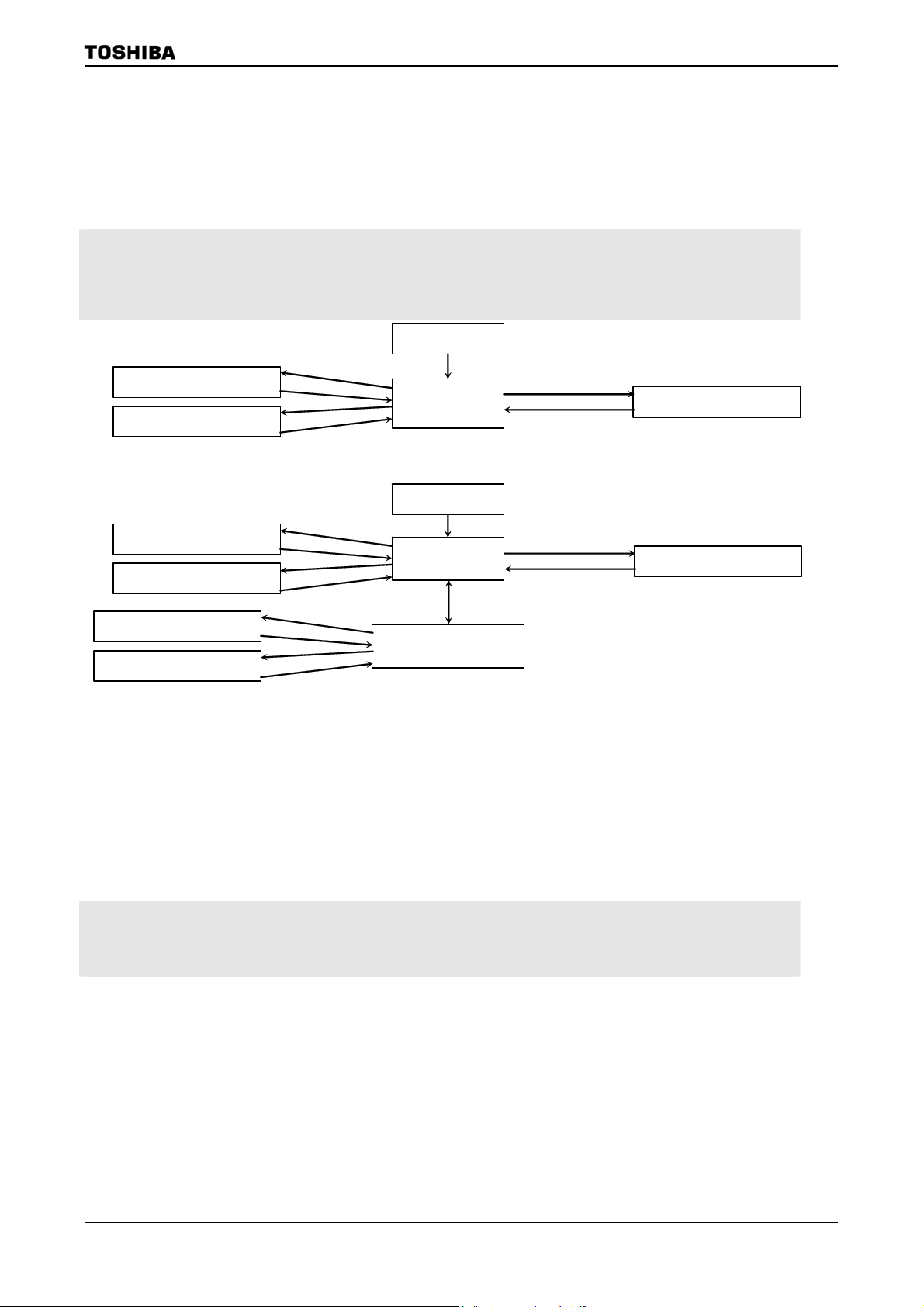

TMP92CZ26A contains (1) clock gear, (2) clock doubler (PLL), (3) standby controller and (4)

noise-reducing circuit. They are used for low-power, low-noise systems.

This chapter is organized as follows:

3.3.1 Block diagram of system clock

3.3.2 SFRs

3.3.3 System clock controller

3.3.4 Prescaler clock controller

3.3.5 Noise-reducing circuit

3.3.7 Standby controller

TMP92CZ26A

92CZ26A-20

Page 24

The clock operating modes are as follows: (a) PLL-OFF Mode (X1, X2 pins only),

(b) PLL-ON Mode (X1, X2, and PLL).

Figure 3.3.1 shows a transition figure.

The clock frequency input from the X1 and X2 pins is called fOSCH and the clock

frequency input from the XT1 and XT2 pins is called fs. The clock frequency selected by

SYSCR1<GEAR2:0> is called the system clock fSYS. And one cycle of fSYS is defined to

as one state.

IDLE2 mode

(I/O operate)

IDLE1 mode

(Operate only oscillator)

IDLE2 mode

(I/O operate)

IDLE1 mode

(Operate only oscillator)

IDLE2 mode

(I/O operate)

IDLE1 mode

(Operate only oscillator)

instruction

interrupt

instruction

interrupt

instruction

interrupt

instruction

interrupt

instruction

interrupt

instruction

interrupt

Reset

(f

/16)

OSCH

release Reset

PLL-OFF mode

/gear value)

(f

(a) PLL-OFF mode transition figure

OSCH

(f

PLL-OFF mode

(f

OSCH

PLL-ON mode

((12 or 16)×f

Reset

/16)

OSCH

release Reset

/gear value)

Instruction (Note)

/gear value)

OSCH

instruction

interrupt

instruction

interrupt

TMP92CZ26A

STOP mode

(Stops all circuits)

STOP mode

(Stops all circuits)

(b) PLL-OFF , PLL-ON mode transition figure

Note 1: If you shift from PLL-ON mode to PLL-OFF mode, execute following setting in the same order.

(1) Change CPU clock (Set “0” to PLLCR0<FCSEL>)

(2) Stop PLL circuit (Set “0” to PLLCR1<PLLON>)

Note 2: It’s prohibited to shift from PLL-ON mode to STOP mode directly.

You should set PLL-OFF mode once, and then shift to STOP mode.

Figure 3.3.1 System clock block diagram

The clock frequency input from the X1 and X2 pins is called f

called fs. The clock frequency selected by SYSCR1<GEAR2:0> is called the sy stem clock f

to as one state.

and the clock frequency input from the XT1 and XT2 pins is

OSCH

. And one cycle of f

SYS

is defined

SYS

92CZ26A-21

Page 25

R

r

r

(

3.3.1 Block diagram of system clock

SYSCR0<WUEF>

SYSCR2<WUPTM1:0>

TMP92CZ26A

SYSCR0<XTEN >

XT1

XT2

X1

X2

X1USB

Low frequency

Oscillator circuit

High frequency

Oscillator circuit

φT0TMR

Warming up timer

(High/Low frequency oscillator circuit)

Lock up timer

(PLL)

PLLCR1<PLLON>,

fs

Clock Doubler0

×

f

OSCH

PLLCR0<LUPFG>

(PLL0)

12 or16)

÷2

f

PLL

PLLCR0<FCSEL>

Clock Doubler1

(PLL1)× 24

f

SYS

f

io

TMRA0:7,TMRB0:1

Prescaler

SIO0

φT0

Prescaler

SBI

Prescaler

fc

fc/2

÷2 ÷16÷4

÷5

fc/4

fc/8

÷8

Clock gear

f

PLLUSB

÷2

÷8

SYSCR0<PRCK>

fc/16

SYSCR1<GEAR2:0>

SYSCR0<USBCLK1:0>

CPU

RAM

Interrupt

NAND-Flash

Controller

I/O ports

SDRAMC

DMAC

÷4

LCDC

Memory

Controlle

Controlle

2

S

I

TSI

SPIC

÷2

÷2

φT0

φT0TM

fs

f

SYS

fIO

f

USB

f

OSCH4

RTC

MAC

fs

MLD/ALM

ADC

f

USB

USB

Figure 3.3.2 Block Diagram of System clock

92CZ26A-22

Page 26

TMP92CZ26A

TMP92CZ26A has two PLL circuits: one is for CPU (PLL0) and the other for USB (PLL1).

Each PLL can be controlled independently. Frequency of external oscillator is 6 to 10MHz.

Don’t connect oscillator m ore than 10 MH z. When clo ck is in put by usin g ext ern al osci llato r,

range of input frequency is 6 to10MHz. Don’t input the clock over 10MHz.

Table 3.3.1 Setting example for f

(a) PLL, USB (PLL0 ON/PLL1ON) 10.0 MHz Max 80 MHz Max 60 MHz 48 MHz

(b) PLL, No USB (PLL0 ON/PLL1OFF) Max 10.0 MHz Max 80 MHz Max 60 MHz

(c) No PLL, No USB (PLL0 OFF/PLL1OFF) Max 10.0 MHz Max 10 MHz Max 10 MHz

Note: When using USB, set high-frequency oscillator to 10.0 MHz.

High frequency:

f

OSCH

System

clock:

f

OSCH

SYS

System

clock:

f

SYS

USB

clock:

f

USB

−

−

92CZ26A-23

Page 27

3.3.2 SFR

SYSCR0

(10E0H)

SYSCR1

(10E1H)

SYSCR2

(10E2H)

TMP92CZ26A

7 6 5 4 3 2 1 0

bit Symbol XTEN

USBCLK1 USBCLK0

Read/write R/W R/W R/W R/W R/W

After Reset 1 0 0 0 0

Select the clock of

USB(f

)

USB

00:Disable

01: Reserved

10:X1USB

11:f

PLLUSB

Function

Low

-frequency

oscillator

circuit (fs)

0: Stop

1: Oscillation

WUEF PRCK

Warm-up

Timer

0: Write

Don’t care

Note3

1: Write

start timer

0: Read

end

warm-up

1: Read

do not end

warm-up

Select

Prescaler

clock

0: f

SYS

1: f

SYS

/2

/8

7 6 5 4 3 2 1 0

bit Symbol GEAR2 GEAR1 GEAR0

Read/write R/W

After Reset 1 0 0

Function

Select gear value of high frequency (fc)

000: fc

001: fc/2

010: fc/4

011: fc/8

100: fc/16

101: Reserved

110: Reserved

111: Reserved

7 6 5 4 3 2 1 0

bit Symbol

–

Read/write R/W R/W R/W R/W R/W R/W

After Reset 0 0 1 0 1 1

Always

write “0”

Function

Note1: SYSCR0<bit7><bit3><bit1>,SYSCR1<bit7:3> and SYSCR2<bit1:0> are read as undefined value.

Note2: By reset, low frequency oscillator circuit is enabled.

Note3: Don’t write SYSCR0 resiter during warming up. Because the warm-up end flag doesn’t become enable if

write ”0” to SYSCR0<WUEF> bit during warming up.

( Read-modify-write is prohibited for SYSCR0 register during warming up.)

CKOSEL WUPTM1 WUPTM0 HALTM1 HALTM0

Select

CLKOUT

0: f

SYS

1: fS

Warm-Up Timer

00: reserved

8

01: 2

/inputted frequency

14

10:2

/inputted frequency

16

11:2

/inputted frequency

HALT mode

00: Reserved

01: STOP mode

10: IDLE1 mode

11: IDLE2 mode

Figure 3.3.3 SFR for system clock

92CZ26A-24

Page 28

EMCCR0

(10E3H)

EMCCR1

(10E4H)

EMCCR2

(10E5H)

TMP92CZ26A

7 6 5 4 3 2 1 0

Bit symbol

Read/Write R R/W R/W R/W R/W

After reset 0 0 0 1 1

Function

Bit symbol

Read/Write

After reset

Function

Bit symbol

Read/Write

After reset

Function

Note: In case restarting the oscillator in the stop oscillation state (e.g. Restart the oscillator in STOP mode), set

PROTECT

Protect flag

0: OFF

1: ON

EMCCR0<DRVOSCH>, <DRVOSCL>

Switching the protect ON/OFF by write to following 1

st

1

-KEY: EMCCR1=5AH,EMCCR2=A5H in succession write

nd

2

-KEY: EMCCR1=A5H,EMCCR2=5AH in succession write

=”1”.

−

Always

write “0”.

EXTIN DRVOSCH DRVOSCL

1: External

clock

st

-KEY,2nd-KEY

fc oscillator

drive ability

1: NORMAL

0: WEAK

fs oscillator

drive ability

1: NORMAL

0: WEAK

Figure 3.3.4 SFR for system clock

92CZ26A-25

Page 29

PLLCR0

(10E8H)

PLLCR1

(10E9H)

TMP92CZ26A

7 6 5 4 3 2 1 0

bit symbol FCSEL LUPFG

Read/Write R/W R

After reset 0 0

Function

Note: Be carefull that logic of PLLCR0<LUPFG> is different from 900/L1’s DFM.

Select

fc-clock

0 : f

OSCH

1 : f

PLL

Lock-up

timer

Status flag

0 : not end

1 : end

7 6 5 4 3 2 1 0

bit symbol PLL0 PLL1 LUPSEL

Read/Write R/W R/W R/W R/W

After reset 0 0 0 0

Select the

Function

PLL0 for

CPU

0: Off

1: On

PLL1 for

USB

0: Off

1: On

Select

stage of

Lock up

counter

0: 12 stage

(for PLL0)

1:13 stage

(for PLL1)

PLLTIMES

number of

PLL

0: ×12

1: ×16

PxDR

(xxxxH)

Figure 3.3.5 SFR for PLL

7 6 5 4 3 2 1 0

bit symbol Px7D Px6D Px5D Px4D Px3D Px2D Px1D Px0D

Read/Write R/W

After reset 1 1 1 1 1 1 1 1

Function Output/Input buffer drive-register for standby-mode

(Purpose and method of using)

• This register is used to set each pin-status at stand-by mode.

• All ports have this format’s register. (“x” means port-name.)

• For each register, refer to 3.5 Function of Ports.

• Before “HALT” instruction is executed, set each register pin-status. They will be

effective after CPU executes “HALT” instructi on.

• This register is effective in all stand-by modes (IDLE2, IDLE1 or STOP).

• This register is effective when using PMC function. For details, refer to PMC

section.

The truth table to control Output/Input-buffer is below.

OE PxnD Output buffer Input buffer

0 0 OFF OFF

0 1 OFF ON

1 0 OFF OFF

1 1 ON OFF

Note1: OE means an output enable signal before stand-by mode. Basically, PxCR is used as OE.

Note2: “n” in PxnD means bit-number of PORTx.

Figure 3.3.6 SFR for drive register

92CZ26A-26

Page 30

3.3.3 System clock controller

TMP92CZ26A

The system clock controller generates the system clock signal (f

) for the CPU core and

SYS

internal I/O.

SYSCR0<XEN> and SYSCR0<XTEN> control enabling and disabling of each oscillator.

SYSCR1<GEAR2:0> sets the high frequency clock gear to either 1, 2, 4, 8 or 16 (fc, fc/2, fc/4,

fc/8, fc/16). These functions can reduce the power consumption of the equipment in which

the device is installed.

The combination of settings <XEN> = “1”, <SYSCK> = “0” and <GEAR2 to 0> = “100” will

be PLL-OFF mode and cause the system clock (f

For example, f

is set to 625 kHz when the 10MHz oscillator is conn ected to the X1 an d

SYS

) to be set to fc/16 after reset.

SYS

X2 pins.

(1) Clock gear controller

is set according to the contents of the Clock Gear Select Register SYSCR1<GEAR2:

f

SYS

0> to either fc, fc/2, fc/4, fc/8 or fc/16. Using the clock gear to select a lower value of f

SYS

reduces power consumption.

(Example)

Changing clock gear

SYSCR1 EQU 10E1H

LD (SYSCR1),XXXXX001B ; Changes system clock f

LD (DUMMY),00H Dummy instruction

X: don't care

SYS to

fc/2

(High-speed clock gear changing)

To change the clock gear, write the register value to the SYSCR1<GEAR2 to 0> register.

It is necessary the warming up time until changing after writ ing the register value.

There is the possibility that the instruction next to the cl ock gea r changing i n struction is

executed by the clock gear before changing. To execu te the instruction next to the cl ock gear

switching instruction by the clock gear after changing, input the dummy instruction as

follows (instruction to execute the write cycle).

(Example)

SYSCR1 EQU 10E1H

LD (SYSCR1),XXXXX010B ; Changes f

LD (DUMMY),00H ; Dummy instruction

Instruction to be executed after clock gear changed

SYS

to fc/4

92CZ26A-27

Page 31

3.3.4 Clock doubler (PLL)

TMP92CZ26A

PLL0 outputs the f

clock signal, which is 12 or 16 times as fast as f

PLL

. That is, the

OSCH

low-speed frequency oscillator can be used as external oscillator, even though the internal

clock is high-frequency.

Since Reset initializes PLL0 to stop status, setting to PLLCR0 and PLLCR1-register is

needed before use.

Like an oscillator, this circuit require s time to stabilize. This is called the lock-up time

and it is measured by 12-stage binary counter. Lock-up time is about 0.41ms at f

OSCH

=

10MHz.

PLL (PLL1) which is special for USB is build in. Lock-up time is about 0.82ms at f

OSCH

=

10MHz measured by 13-stage binary counter.

Note1: Input frequency limitation for PLL

The limitation of input frequency (High frequency oscillation) for PLL is following.

= X to X MHz (Vcc = 1.4 to 1.6V)

f

OSCH

Note2: PLLCR0<LUPFG>

The logic of PLLCR0<LUPFG> is different from 900/L1’s DFM.

Be careful to judge an end of lock-up time.

Note3: PLLCR1<PLL0>, PLLCR1<PLL1>

It’s prohibited to turn ON both PLL0 and PLL1 simultaneously.

If turning ON simultaneously, one PLL should be turn ON after finishing the lock up of the other PLL.

Figure 3.3.7 shows the frequency of f

when using PLL and clock gear at f

SYS

OSCH

=10MHz.

f

f

OSH

10MHz

×12 120MHz 60MHz 30MHz 15MHz 7.5MHz 3.75MHz

×16 160MHz 80MHz 40MHz 20MHz 10MHz 5MHz

PLL

f

10MHz 10MHz 5MHz 2.5MHz 1.25MHz 625KHz

OSH

fc fc/2 fc/4 fc/8 fc/16

Frequency of f

SYS

Figure 3.3.7 The frequency of f

SYS

at f

=10MHz

OSH

92CZ26A-28

Page 32

A

TMP92CZ26A

The following is a setting example for PLL0-starting and PLL0-stopping.

(Example-1) PLL0-starting

PLLCR0 EQU 10E8H

PLLCR1 EQU 10E9H

LD (PLLCR1),1XXXXXXXXB ;

LUP: BIT 5,(PLLCR0) ;

JR Z,LUP ;

LD (PLLCR0), X1XXXXXXB ; Changes fc from 10 MHz to 60 MHz.

X: Don't care

<PLL0>

<FCSEL>

PLL output: f

PLL

Enables PLL0 operation and starts lock-up

Detects end of lock-up

.

Lockup timer

<LUPFG>

System clock f

SYS

Counts up by f

Starts PLL0 operation and

Starts lock-up.

OSCH

During lock-up

fter lock-up

Changes from 10MHz to 60MHz.

Ends of lock-up

(Example-2) PLL0-stopping

PLLCR0 EQU 10E8H

PLLCR1 EQU 10E9H

LD (PLLCR0),X0XXXXXXB ; Changes fc from 60 MHz to10 MHz.

LD (PLLCR1),0XXXXXXXB ; Stop PLL

X: Don't care

<FCSEL>

<PLL0>

PLL0 output: f

System clock f

PLL

SYS

Changes from 60MHz to 10 MHz.

Stops PLL0 operation .

Note) PLL1 operates as well.

92CZ26A-29

Page 33

TMP92CZ26A

Limitation point on the use of PLL0

1. If you stop PLL operation during using PLL0, you should execute following setting in

the same order.

LD (PLLCR0),X0XXXXXXB ;

LD (PLLCR1),0XXXXXXXB ; Stop PLL0

X: Don't care

Change the clock f

PLL

to f

OSCH

2. If you shift to STOP mode during using PLL, you should execute following setting in the

same order.

LD (SYSCR2), XXXX01XXB ;

LD (PLLCR0), X0XXXXXXB ;

LD (PLLCR1), 0XXXXXXXB ; Stop PLL0

HALT ; Shift to STOP mode

X: Don't care

Set the STOP mode

Change the system clock f

PLL

to f

OSCH

Examples of settings are below;

(1) Start Up / Change Control

(OK) High frequency oscillator operati on m ode(f

→ PLL0 use mode (f

LD (PLLCR1), 1XXXXXXXB ; PLL0 start up / lock up start

LUP: BIT 5,(PLLCR0) ;

JR Z,LUP ; Check for the flag of lock up end

LD (PLLCR0), X1XXXXXXB ; Change the system clock fOSCH to fPLL

X: Don't care

PLL

)

)→PLL0 start up

OSCH

(2) Change / Stop Control

(OK) PLL0 use mode (f

)→ High frequency oscillator operation mode(f

PLL

OSCH

)

→ PLL0 Stop

LD (PLLCR0),X0XXXXXXB ; Change the system clock fPLL to fOSCH

LD (PLLCR1),0XXXXXXXB ; Stop PLL0

X: Don't care

(OK) PLL0 use mode (f

→High frequency oscillator operation mode (f

) → Set the STOP mode

PLL

) → PLL stop

OSCH

→ HALT(High frequency oscillator stop)

LD (SYSCR2),XXXX01XXB ; Set the STOP mode

(This command can be executed before use of PLL0)

LD (PLLCR0),X0XXXXXXB ;

LD (PLLCR1),0XXXXXXXB ; Stop PLL0

HALT ; Shift to STOP mode

X: Don't care

Change the system clock f

PLL

to f

OSCH

(NG) PLL0 use mode (f

) → Set the STOP mode

PLL

→ HALT(High frequency oscillator stop)

LD (SYSCR2),XXXX01XXB ; Set the STOP mode

(This command can be executed before use of PLL0)

HALT ; Shift to STOP mode

X: Don't care

92CZ26A-30

Page 34

3.3.5 Noise reduction circuits

Noise reduction circuits are built in, allowing implementation of the following features.

(1) Reduced drivability for high-frequency oscillator circuit

(2) Reduced drivability for low-frequency osci llator circuit

(3) Single drive for high-frequency oscillator circuit

(4) SFR protection of register contents

These are set in EMCCR0 to EMCCR2 registers.

(1) Reduced drivability for high-frequency oscillator circuit

(Purpose)

Reduces noise and power for oscillator when a reson ator is used.

(Clock diagram)

C1

X1 pin

f

OSCH

Enable oscillation

TMP92CZ26A

resonator

C2

X2 pin

EMCCR0<DRVOSCH>

(Setting method)

The drivability of the oscillator is reduced by writing”0” to EMCCR0<DRVOSCH>

register . By reset, <DR VOSCH> is initializ ed to “1” and the oscillator starts oscillat ion

by normal-drivability when the power-supply is on.

Note: This function (EMCCR0<DRVODCH>= “0”) is available to use in case f

= 6 to 10MHz condition.

OSCH

92CZ26A-31

Page 35

TMP92CZ26A

(2) Reduced drivability for low-freq uency oscillator circuit

(Purpose)

Reduces noise and power for oscillator when a reson ator is used.

(Block diagram)

C1

XT1 pin

Enable oscillation

Resonator

C2

XT2 pin

EMCCR0<DRVOSCL>

f

S

(Setting method)

The drivability of the oscillator is reduc ed by writing 0 to the EM CCR0<DR VOSCL>

register. By Reset, <DRVOSCL> is initialized to “1 ”.

(3) Single drive for high-frequenc y oscillator circuit

(Purpose)

Not need twin-drive and protect mistake-operat ion by inputted noise to X2 pin when

the external-oscillator is used

.

(Block diagram)

f

X1 pin

Enable oscillation

OSCH

EMCCR0<DRVOSCH>

X2 pin

(Setting method)

The oscillator is disabled and starts operation as buffer by writing “1” to

EMCCR0<EXTIN> register. X2-pin is always outputted”1”.

By reset,<EXTIN> is initialized to “0”.

Note: Do not write EMCCR0<EXTIN> = “1” when using external resonator.

92CZ26A-32

Page 36

TMP92CZ26A

(4) Runaway provision with SFR protection register

(Purpose)

Provision in runaway of program by noise mixing.

Write operation to speci fied SFR is prohibited so that provision program in runaway

prevents that it is in the state which is fetch impossibility by stopping of clock,

memory control register (Memory controller, MMU) is changed.

And error handling in runaway becomes easy by INTP0 interruption.

Specified SFR list

1. Memory controller

B0CSL/H, B1CSL/H, B2CSL/H, B3CSL/H, BECSL/H

MSAR0, MSAR1, MSAR2, MSAR3,

MAMR0, MAMR1, MAMR2, MAMR3, PMEMCR,

MEMCR0, CSTMGCR, WRTMGCR, RDTMGCR0

RDTMGCR1, BROMCR

2. MMU

LOCALPX/PY/PZ, LOCALLX/LY/LZ,

LOCALRX/RY/RZ, LOCALWX/WY/WZ,

LOCALESX/ESY/ESZ, LOCALEDX/EDY/EDZ,

LOCALOSX/OSY/OSZ, LOCALODX/ODY/ODZ

3. Clock gear

SYSCR0, SYSCR1, SYSCR2, EMCCR0

4. PLL

PLLCR0,PLLCR1

5. PMC

PMCCTL

(Operation explanation)

Execute and release of protection (write operation to specified SFR) becomes

possible by setting up a double key to EMCCR1 and EMCCR2 register.

(Double key)

st

-KEY: Succession writes in 5AH at EMCCR1 and A5H at EMCCR2

1

nd

-KEY: Succession writes in A5H at EMCCR1 and 5AH at EMCCR2

2

A state of pr otection can be confirmed by reading EMCCR0<PROTECT>.

By reset, protection becomes OFF.

And INTP0 interruption occurs when write operation to specified SFR was execu ted

with protection on state.

92CZ26A-33

Page 37

3.3.6 Standby controller

(1) Halt Modes and Port Drive-register

When the HALT instruction is executed, the operating mode switches to IDLE2,

IDLE1 or STOP Mode, depending on the contents of the SYSCR2<HALTM1 to 0>

register and each pin-status is set according to PxDR-register.

7 6 5 4 3 2 1 0

PxDR

(xxxxH)

bit symbol Px7D Px6D Px5D Px4D Px3D Px2D Px1D Px0D

Read/Write R/W

After reset 1 1 1 1 1 1 1 1

Function Output/Input buffer drive-register for standby-mode

(Purpose and method of using)

• This register is used to set each pin-status at stand-by mode.

• All ports have this format’s register. (“x” means port-name.)

• For each register, refer to 3.5 Function of Ports.

• Before “HALT” instruction is executed, set each register pin-status. They will be

effective after CPU executes “HALT” instructi on.

• This register is effective in all stand-by modes (IDLE2, IDLE1 or STOP).

• This register is effective when using PMC function. For details, refer to PMC

section.

The truth table to control Output/Input-buffer is below.

Note1: OE means an output enable signal before stand-by mode.Basically, PxCR is used as OE.

Note2: “n” in PxnD means bit-number of PORTx.

The subsequent actions performed in each mode are as follows:

TMP92CZ26A

OE PxnD Output buffer Input buffer

0 0 OFF OFF

0 1 OFF ON

1 0 OFF OFF

1 1 ON OFF

a. IDLE2: Only the CPU halts.

The internal I/O is available to select operation during IDLE2 mode by

setting the following register.

Tabl e 3. 3. 2 shows the registers of setting operation during IDLE2 mode.

Table 3.3.2 SFR setting operation during IDLE2 mode

Internal I/O SFR

TMRA01 TA01RUN<I2TA01>

TMRA23 TA23RUN<I2TA23>

TMRA45 TA45RUN<I2TA45>

TMRA67 TA67RUN<I2TA67>

TMRB0 TB0RUN<I2TB0>

TMRB1 TB1RUN<I2TB1>

SIO0 SC0MOD1<I2S0>

SBI SBIBR0<I2SBI>

A/D converter ADMOD1<I2AD>

WDT WDMOD<I2WDT>

b. IDLE1: Only the oscillator, RTC (real-time clock), and MLD continue to

operate.

c. STOP: All internal circuits stop operating.

92CZ26A-34

Page 38

TMP92CZ26A

The operation of each of the different Halt Modes is described in

Table 3.3.3 .

Table 3.3.3 I/O operation during Halt Modes

Halt Mode IDLE2 IDLE1 STOP

SYSCR2 <HAL TM1:0 > 1 1 10 01

CPU, MAC Stop

I/O ports Depends on PxDR register setting

TMRA, TMRB

SIO,SBI

A/D converter

Block

WDT

I2S, LCDC, SDRAMC,

Interrupt controller,

SPIC, DMAC, NDFC,

USB

RTC, MLD

Available to select

Operation block

Stop

Operate

Operate

(2) How to release the Halt mode

These HALT states can be released by resetting or requesting an interru pt. The halt

release sources are determined by the combination between the states of interrupt

mask register <IFF2:0> and the halt modes. The details for releasing the HALT status

are shown in

Table 3.3.4.

• Released by requesting an interrupt

The operating released from the halt mode depends on th e interrupt enab led status.

When the interrupt request level set before executing the HALT instruction exceeds

the value of interrupt mask register, the interrupt due to the source is processed after

releasing the halt mode, and CPU status executing an instruction that follows the

HALT instruction. When the interrupt request level set before executing the HALT

instruction is less than the value of the interrupt mask register, releasing the halt

mode is not executed.(in non-maskable interrupts, interrupt processing is processed

after releasing the halt mode regardless of the value of the mask register.) However

only for INT0 to INT5, INT6, INT7(unsynchronous interrupt), INTKEY,INTRTC,

INTALM int errupts, ev en if th e int errupt requ est level s et befor e executi ng the H ALT

instruction is less than the value of the interrupt mask register, releasing the halt

mode is executed. In this case, interrupt processing, and CPU starts executing the

instruction next to the HALT instruction, but the interrupt request flag is held at “1”.

• Releasing by resetting

Releasing all halt status is executed by resetting.

When the STOP mode is released by RESET, it is necessary enough resetting time to

set the operation of the oscillator to be stabl e.

When releasing the halt mode by resetting, the internal RAM data keeps the state

before the “HALT” instruction is executed. However the other settings contents are

initialized. (Releasing due to interrup ts keeps the state b efore t he “HALT” instruction

is executed.)

92CZ26A-35

Page 39

Table 3.3.4 Source of Halt state clearance and Halt clearance operation

Status of Received Interrupt

Halt mode IDLE2 IDLE1 STOP IDLE2 IDLE1 STOP

INTWDT

INT0 to 5 (Note1)

INTKEY

INTUSB

INT6 to 7(PORT) (Note1)

INT6 to 7(TMRB)

INTALM, INTRTC

INTTA0 to 7, INTTP0

Interrupt

INTTB00 to 01, INTTB10 to 11

INTRX,INTTX, INTSBI

INTI2S0 to 1, INTLCD,

INTAD, INTADHP

Source of Halt state clearance

INTSPIRX,INTSPITX

INTRSC, INTRDY

INTDMA0 to 5

RESET Reset initializes the LSI

: After clearing the Halt mode, CPU starts interrupt processing.

{: After clearing the Halt mode, CPU resumes executing starting from instruction following the HALT instruction.

×: It can not be used to release the halt mode.

−: The priority level (interrupt request level) of non-maskable interrupts is fixed to 7, the highest priority level. There is

not this combination type.

*1: Releasing the halt mode is executed after passing the warmming-up time.

*2: 6 interrupts of all 24 INTUSB sources can release Halt state from IDLE1 mode. Therefore, the system of low

power dissipation can be built. However, the way of use is limited as below.

• Shift to IDLE1 mode :

Execute Halt instruction when the flag of INT_SUS or INT_CLKSTOP is “1” ( SUSPEND state )

• Release from IDLE1 mode :

Release Halt state by the request of INT_RESUME or INT_CLKON ( request of release SUSPEND )

Release Halt state by the request of INT_URST_STR or INT_URST_END ( request of RESET )

Note1: When the Halt mode is cleared by an INT0 interrupt of the level mode in the interrupt enabled status, hold level

H until starting interrupt processing. If level L is set before holding level L, interrupt processing is correctly

started.

TMP92CZ26A

Interrupt Enabled

(interrupt level) ≥ (interrupt mask)

× × − − −

× × × × ×

× { { ×

*2

× { {*2 ×

× × × × ×

(interrupt level) < (interrupt mask)

*1

{ { {*1

*1

{ { {*1

Interrupt Disabled

92CZ26A-36

Page 40

TMP92CZ26A

(Example - releasing IDLE1 Mode)

An INT0 interrupt clears the Halt state when the device is in IDLE1 Mode.

Address

8200H LD (PCFC), 02H ; Sets PC1 to INT0 interrupt.

8203H LD (IIMC0), 00H ; Select INT0 interrupt rising edge.

8206H LD (INTE0), 06H ; Sets INT0 interrupt level to 6.

8209H EI 5 ; Sets CPU interrupt level to 5.

820BH LD (SYSCR2), 28H ; Sets Halt mode to IDLE1 mode.

820EH HALT ; Halts CPU.

INT0 INT0 interrupt routine.

RETI

820FH LD XX, XX

92CZ26A-37

Page 41

r

r

(3) Operation

Interrupt fo

releasing Halt

TMP92CZ26A

a. IDLE2 Mode

In IDLE2 Mode, only specific internal I/O operations, as designated by the

IDLE2 Setting Register, can take place. Instruction execution by the CPU stops.

Figure 3.3.8 illustrates an example of the timing for clearance of the IDLE2

Mode Halt state by an interrupt.

X1

A0~A23

D0~D31

RD

WR

Data

IDLE2

mode

Data

Figure 3.3.8 Timing chart for IDLE2 Mode Halt state cleared by interrupt

b. IDLE1 Mode

In IDLE1 Mode, only the internal oscillator and the RTC and MLD continue to

operate. The system clock stops.

In the Halt state, the interrupt request is sampled asynchronously with the

system clock; however, clearance of the Halt state (i.e. restart of operation) is

synchronous with it.

Figure 3.3.9 illustrates the timing for clearance of the IDLE1 Mode Halt state b y

an interrupt.

X1

A0~A23

D0~D31

RD

Data Data

releasing Halt

WR

Interrupt fo

IDLE1

mode

Figure 3.3.9 Timing chart for IDLE1 Mode Halt state cleared by interrupt

92CZ26A-38

Page 42

r

A0~A23

D0~D31

Interrupt fo

releasing Halt

TMP92CZ26A

c. STOP Mode

When STOP Mode is selected, all internal circuits stop, including the internal

oscillator.

After STOP Mode has been cleared system clock output starts when the warm-up

time has elapsed, in order to allow oscillation to stabiliz e.

Figure 3.3.10 illustrates the timing for clearance of the STOP Mode Halt state by a n

interrupt.

Warm-up

time

X1

Data

RD

STOP

mode

Data

Figure 3.3.10 Timing chart for STOP Mode Halt state cleared by interrupt

Table 3.3.5 Example of warming-up time after releasing STOP-mode

@f

OSCH

=10 MHz

SYSCR2<WUPTM1:0>

01 (28) 10 (214) 11 (216)

25.6 us 1.6384 ms 6.5536 ms

92CZ26A-39

Page 43

TMP92CZ26A

Table 3.3.6 Input Buffer State Table

Input Buffer State

Port Name

D0-D7 D0-D7 OFF − − −

P10-P17 D8-D15

P60-P67 −

P71-P74 − − − −