Page 1

NTDCTV05

TECHNICAL TRAINING MANUAL

N5SS (TG-1, C) CHASSIS

COLOR TELEVISION

CN27E90, CX32E70

CN32E90, CN35E15

CF35E50, CX35E60

CX35E70, CX35E81

CN35E90, CN35E95

PRINTED IN JAPAN Aug. 1995 So

Page 2

Contents

SECTION I

OUTLINE ...................................................................... 6

1. OUTLINE OF N5SS CHASSIS (CN32E90, CN35E90) .................................................................... 7

2. PC BOARD CONFIGURATION ........................................................................................................ 7

3. MAJOR SPECIFICATIONS (NEW FUNCTIONS IN ADDITION TO THOSE OF N5SS) ........ 7

4. MODIFICATIONS ON CHASSIS ..................................................................................................... 7

5. CONSTRUCTION OF CHASSIS ...................................................................................................... 8

6. LOCATION OF CONTROLS ............................................................................................................ 9

7. CN32D90 BLOCK DIAGRAM ......................................................................................................... 13

8. [US, CANADA] SPECIFICATION FOR MODEL's 1995 ............................................................ 14

SECTION II

TUNER, IF/MTS/S.PRO MODULE ......................... 16

1. CIRCUIT BLOCK ............................................................................................................................. 17

2. TUNER ................................................................................................................................................ 18

3. IF/MTS/S.PRO MODULE ................................................................................................................. 19

4. PIP TUNER ......................................................................................................................................... 23

SECTION III

CHANNEL SELECTION CIRCUIT ........................ 24

1. OUTLINE OF CHANNEL SELECTION CIRCUIT SYSTEM .................................................... 25

2. OPERATION OF CHANNEL SELECTION CIRCUIT ................................................................ 25

3. MICROCOMPUTER ......................................................................................................................... 26

4. MICROCOMPUTER TERMINAL FUNCTION ........................................................................... 27

5. EEPROM (QA02) ............................................................................................................................... 29

6. ON SCREEN FUNCTION................................................................................................................. 29

7. SYSTEM BLOCK DIAGRAM .........................................................................................................30

8. LOCAL KEY DETECTION METHOD .......................................................................................... 31

9. REMOTE CONTROL CODE ASSIGNMENT ............................................................................... 32

10. ENTERING TO SERVICE MODE ................................................................................................ 35

11. TEST SIGNAL SELECTION ......................................................................................................... 35

12. SERVICE ADJUSTMENT .............................................................................................................. 35

13. FAILURE DIAGNOSIS PROCEDURE ......................................................................................... 36

14. TROUBLE SHOOTING CHART .................................................................................................. 38

SECTION IV

AUDIO OUTPUT CIRCUIT ..................................... 41

1. OUTLINE ............................................................................................................................................ 42

2. AUDIO OUT IC .................................................................................................................................. 43

2

Page 3

SECTION V

A/V SWITCHING CIRCUIT .................................... 44

1. OUTLINE ............................................................................................................................................ 45

2. IN / OUT TERMINALS ..................................................................................................................... 45

3. CIRCUIT OPERATION .................................................................................................................... 45

SECTION VI

VIDEO PROCESSING CIRCUIT ............................ 47

1. OUTLINE ............................................................................................................................................ 48

2. SIGNAL FLOW .................................................................................................................................. 48

3. CIRCUIT OPERATION .................................................................................................................... 48

SECTION VII

V/C/D/IC ...................................................................... 52

1. OUTLINE ............................................................................................................................................ 53

2. LARGE SCALE EMPLOYMENT OF BUS CONTROL OF PARAMETER FOR PICTURE

CONTROLS ...................................................................................................................................... 53

3. EMPLOYMENT OF CONTAINING EACH VIDEO BAND FILTER INSIDE.......................... 53

4. EMPLOYMENT OF CONTAINING EACH FILTER (FOR S/H) INSIDE................................. 53

5. LOW COST OF IC ............................................................................................................................ 53

SECTION VIII

PIP MODULE ............................................................. 55

SECTION IX

SYNC SEPARATION, H-AFC,

H-OSCILLATOR CIRCUITS .............................. 58

1. SYNC SEPARATION CIRCUIT ......................................................................................................59

2. H AFC (Automatic Frequency Control) CIRCUIT......................................................................... 60

3. H OSCILLATOR CIRCUIT ............................................................................................................. 61

SECTION X

VERTICAL OUTPUT CIRCUIT ............................. 63

1. OUTLINE ............................................................................................................................................ 64

2. V OUTPUT CIRCUIT ....................................................................................................................... 65

3

Page 4

SECTION XI

HORIZONTAL DEFLECTION CIRCUIT.............. 69

1. OUTLINE ............................................................................................................................................ 70

2. HORIZONTAL DRIVE CIRCUIT ................................................................................................... 70

3. BASIC OPERATION OF HORIZONTAL DRIVE ........................................................................ 71

4. HORIZONTAL OUTPUT CIRCUIT ............................................................................................... 74

5. HIGH VOLTAGE GENERATION CIRCUIT ................................................................................. 79

6. X-RAY PROTECTION CIRCUIT ................................................................................................... 82

7. OVER CURRENT PROTECTION CIRCUIT................................................................................ 83

8. KINK CORRECTION CIRCUIT..................................................................................................... 84

SECTION XII

DEFLECTION DISTORTION CORRECTION

CIRCUIT (Side DPC Circuit).............................. 85

1. DEFLECTION DISTORTION CORRECTION IC (TA8859P) .................................................... 86

2. SIDE DPC ............................................................................................................................................ 87

3. DIODE MODULATOR CIRCUIT ................................................................................................... 88

4. ACTUAL CIRCUIT ........................................................................................................................... 89

SECTION XIII

CLOSED CAPTION/EDS CIRCUIT ....................... 92

1. OUTLINE ............................................................................................................................................ 93

2. DATA TRANSMISSION FORMAT ................................................................................................ 93

3. DISPLAY FORMAT........................................................................................................................... 94

4. CIRCUIT OPERATION .................................................................................................................... 95

SECTION XIV

POWER CIRCUIT ..................................................... 98

1. OUTLINE ............................................................................................................................................ 99

2. RECTIFYING CIRCUIT AND STANDBY POWER SUPPLY ................................................... 100

3. MAIN SUPPLY CIRCUIT ............................................................................................................... 100

4. OUTLINE OF CURRENT RESONANT TYPE SUPPLY ........................................................... 101

5. FUNDAMENTAL THEORY........................................................................................................... 101

6. ACTUAL CIRCUIT ......................................................................................................................... 102

7. OTHER POWER CIRCUIT ........................................................................................................... 105

8. PROTECTOR MODULE (Z801).................................................................................................... 106

4

Page 5

SECTION XV

DSP CIRCUIT .......................................................... 109

1. ORIGINS OF DOLBY SURROUND ............................................................................................. 110

2. THE DOLBY MP MATRIX ............................................................................................................ 110

3. THE DOLBY SURROUND DECODER ......................................................................................... 111

4. DSP CIRCUIT ................................................................................................................................... 111

5. DSP (Digital Surround Processor) IC ............................................................................................. 114

6. SURROUND CIRCUIT ................................................................................................................... 116

7. INPUT BALANCE CIRCUIT ......................................................................................................... 116

8. MATRIX CIRCUIT ......................................................................................................................... 117

9. FILTER CIRCUIT (ANTI-ALIAS FILTER)................................................................................. 117

10. DSP CIRCUIT (DELAY) ............................................................................................................... 118

11. 7 kHz LOW PASS FILTER ........................................................................................................... 119

12. DOLBY NR CIRCUIT ................................................................................................................... 120

13. DSP FRONT ADDITION CIRCUIT ............................................................................................ 121

14. BUS CONVERTER ........................................................................................................................ 122

15. NEUTRAL BIAS ............................................................................................................................ 122

16. AUDIO OUTPUT AMPLIFIER (For Rear SP) .......................................................................... 123

17. TROUBLESHOOTING CHART ................................................................................................. 124

SECTION XVI

FAILURE DIAGNOSIS PROCEDURES............... 125

1. H STARTING CIRCUIT FAILURE DIAGNOSIS PROCEDURES ........................................... 126

2. DEFLECTION CIRCUIT FAILURE DIAGNOSIS PROCEDURES ......................................... 127

3. LEFT-RIGHT PIN-CUSHION DISTORTION CORRECTION CIRCUIT .............................. 128

4. X-RAY PROTECTION CIRCUIT FAILURE DIAGNOSIS PROCEDURES ........................... 129

5. PROTECTION CIRCUIT DIAGNOSIS PROCEDURE ............................................................. 130

6. VIDEO CIRCUIT DIAGNOSIS PROCEDURES ......................................................................... 131

5

Page 6

SECTION I

OUTLINE

6

Page 7

1. OUTLINE OF N5SS CHASSIS

(CN32E90, CN35E90)

The N5SS chassis is a complete bus control type

chassis where the deflection circuit is controlled by a newly

developed I2C-bus line control system.

3. MAJOR SPECIFICATIONS (NEW

FUNCTIONS IN ADDITION TO THOSE

OF N5SS)

(1) EOS (Extended-Data-Service)

(2) Center-Ch-Audio-Input provided

2. PC BOARD CONFIGURATION

(1) Signal unit

(2) Power/def unit

(3) A/V, CRT-D, SP-TERM

(4) CCD, comb (CN32E90)

Digital comb (CN35E90)

(5) D.S.P unit

(6) C.C, EDS/R.G.B SW

4. MODIFICATIONS ON CHASSIS

(1) Serviceability improved with direct, front access system

employed.

(2) One touch cabinet securing (CN32E90) to the chassis.

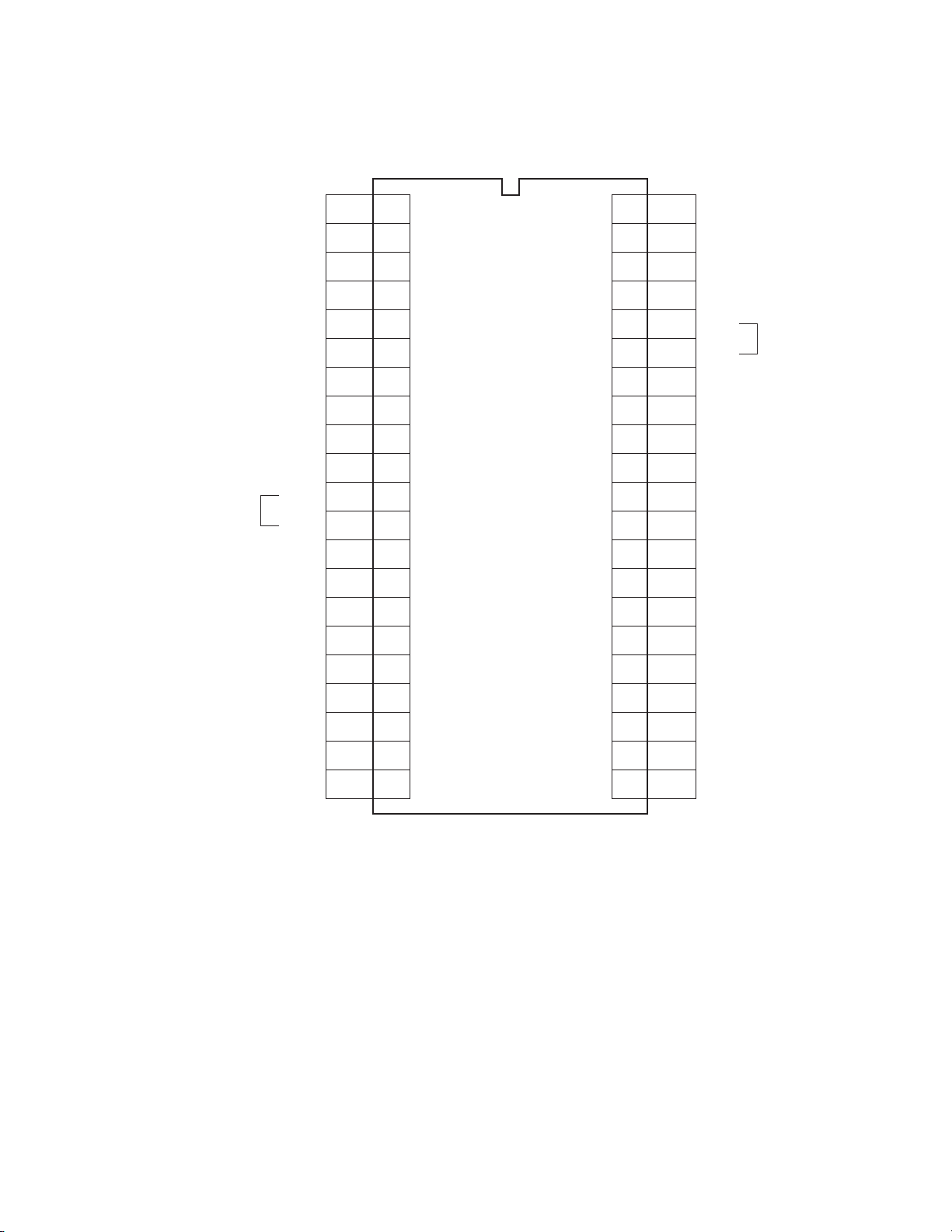

(3) Improved serviceability with the bus control system

employed for the defection circuits.

(4) Improved serviceability with the white balance bus

control system employed.

(5) Digital comb/CCD miniaturized into a socketable size.

7

Page 8

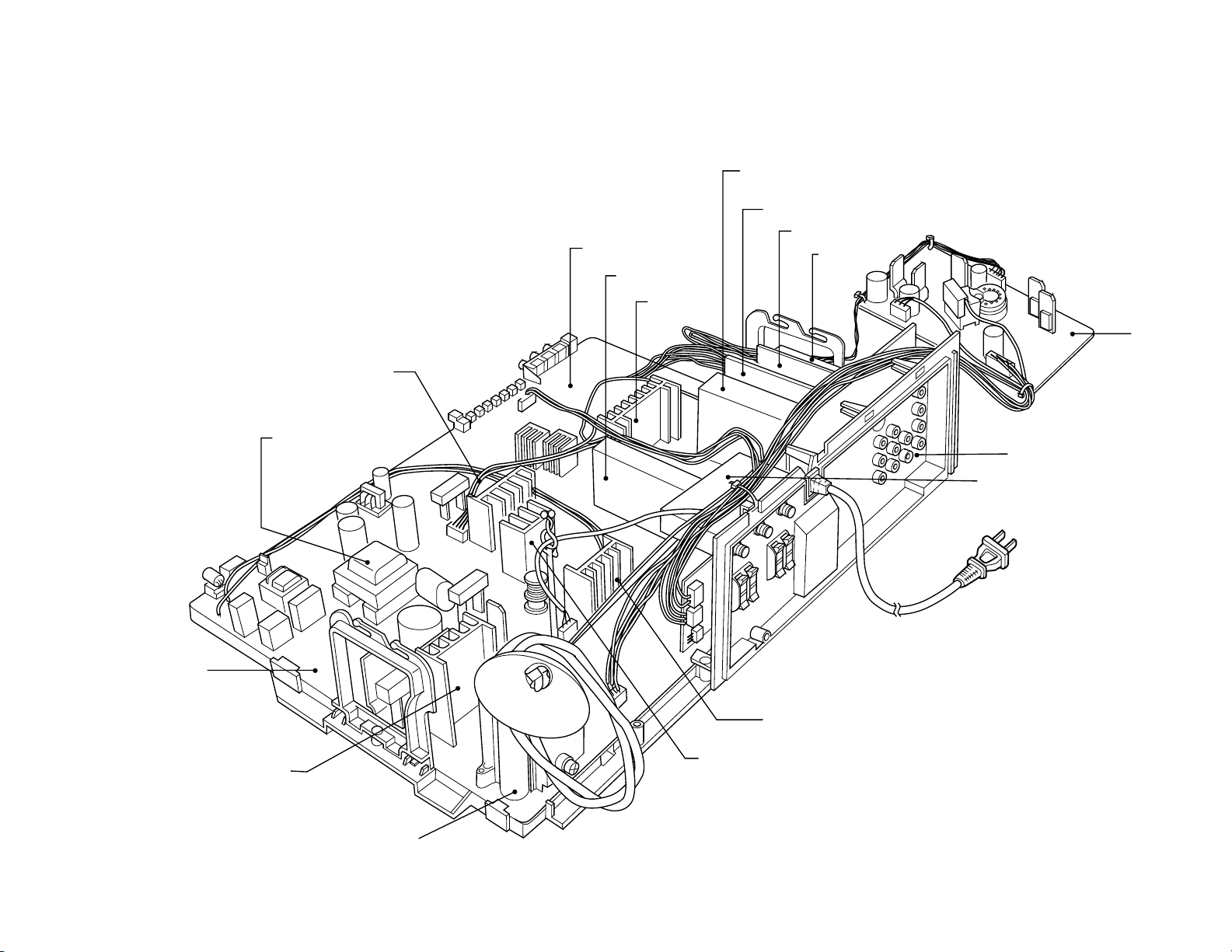

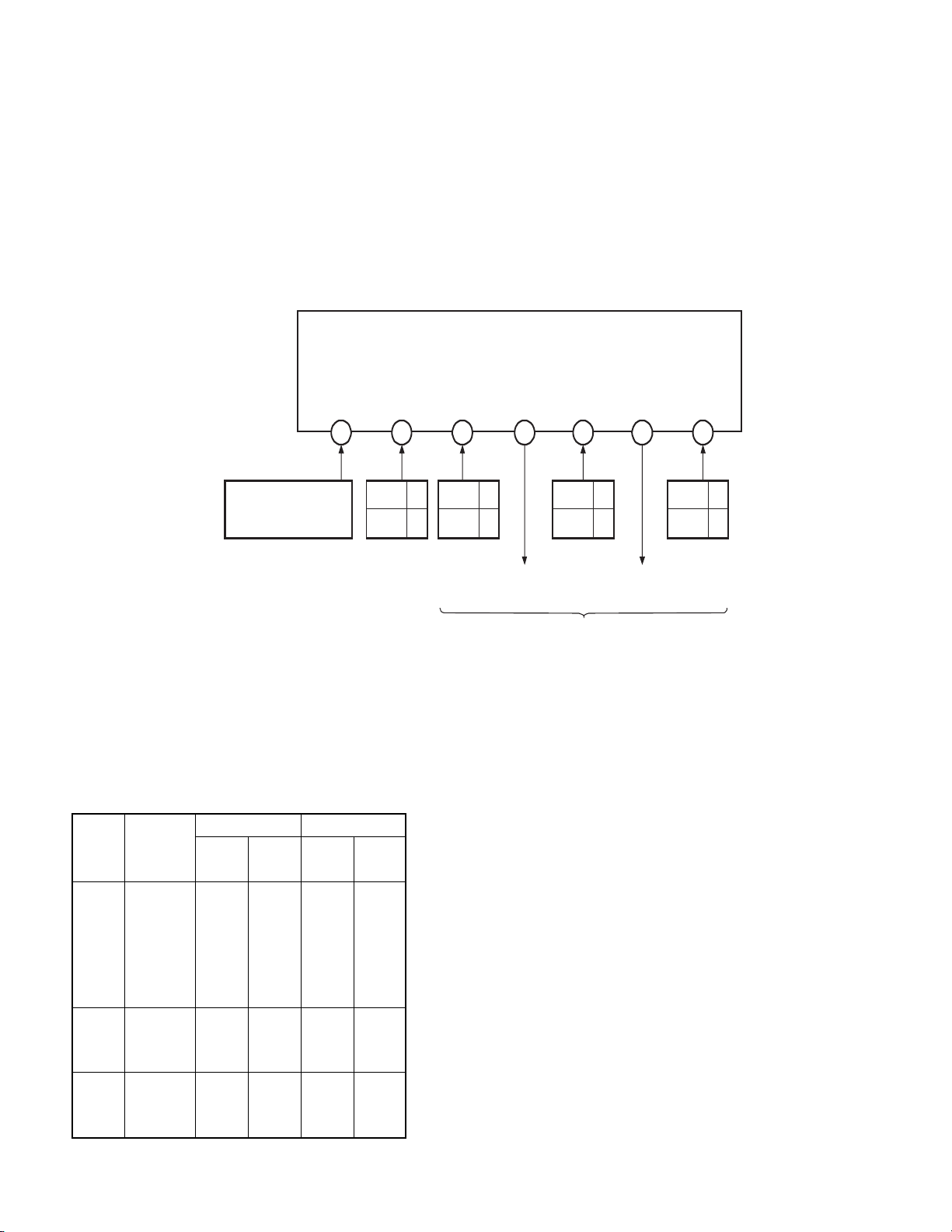

5. CONSTRUCTION OF CHASSIS

REAR AMP circuit

SIGNAL circuit

IF/MTS/A-PRO

module

DPC circuit

CCD circuit

PIP circuit

EDS, RGB SW

circuit

AUDIO OUT

CRT circuit

8

Fig. 1-1

POWER/DEF circuit

CONVERTER trans

A/V circuit

RF SW

V. OUT

DPC circuit

H.OUT

H.OUT trans

Page 9

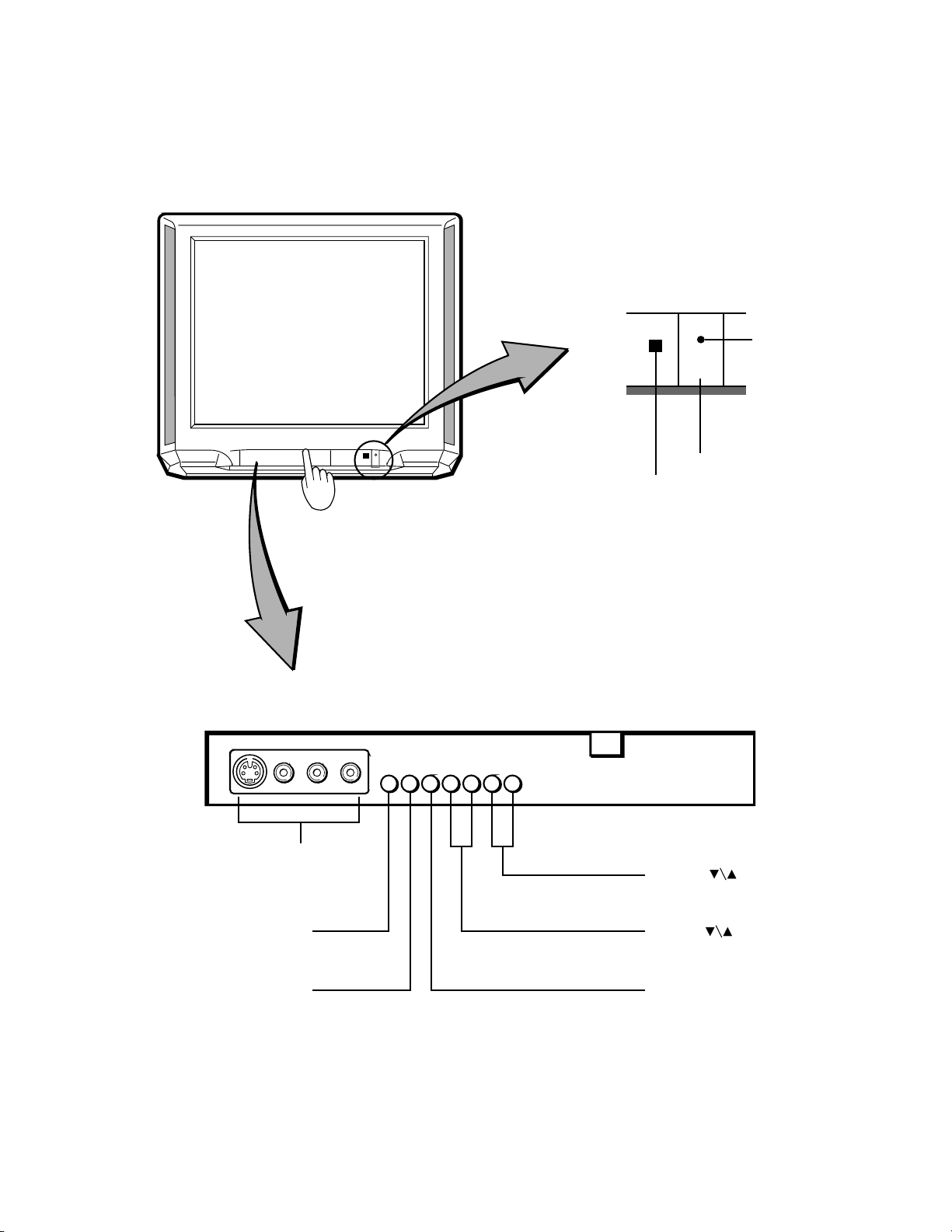

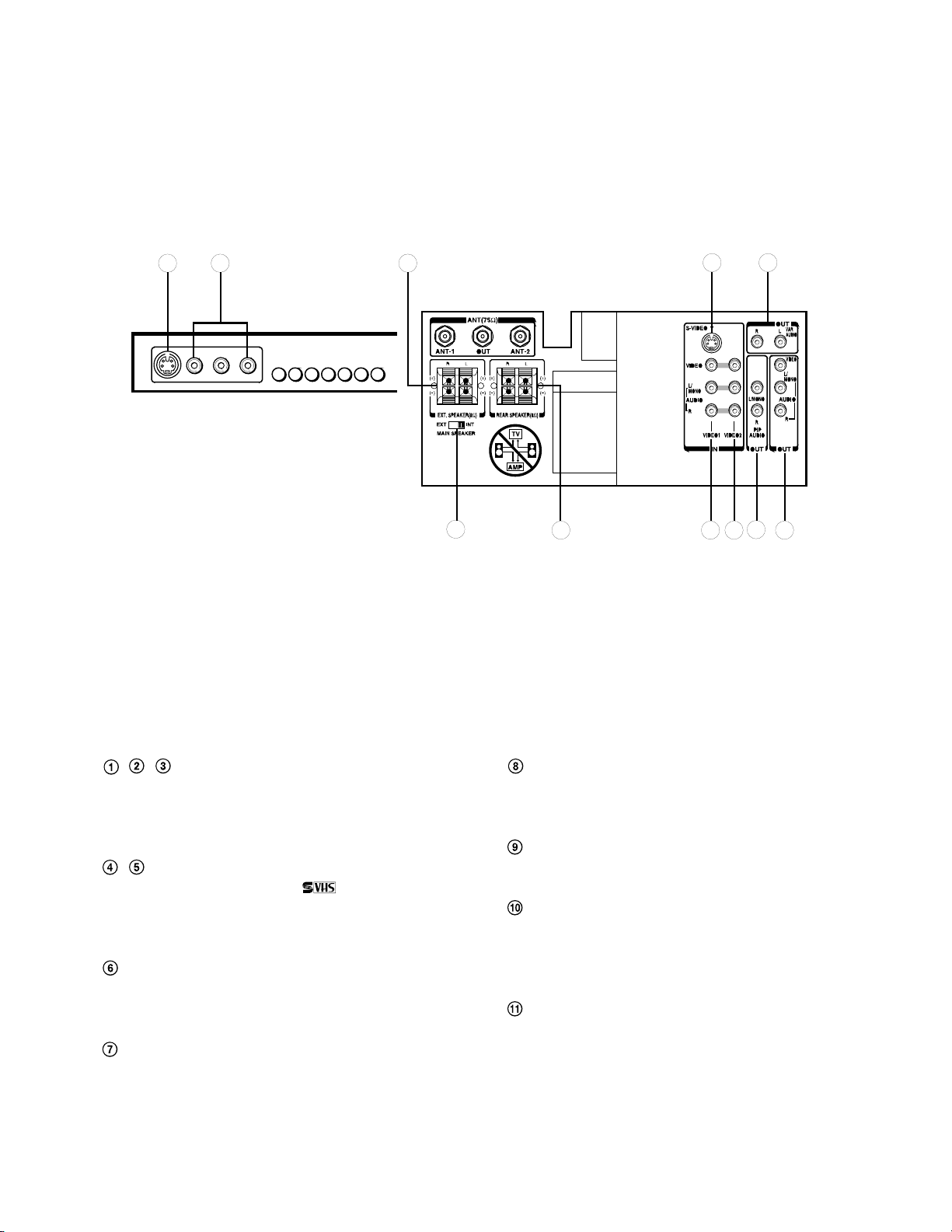

6. LOCATION OF CONTROLS

r

6-1. TV Set

For specific use of each control, consult the corresponding page numbers in brackets.

Front View

POWER indicato

POWER

POWER button

Remote sensor

Behind the door

VIDEO/AUDIO IN

jacks <VIDEO 3>

DEMO button

MENU button

Press to open

the door

CHANNEL

VOLUME

-/+buttons

ANT/VIDEO button

ADV button

buttons

buttons

Fig. 1-2

9

Page 10

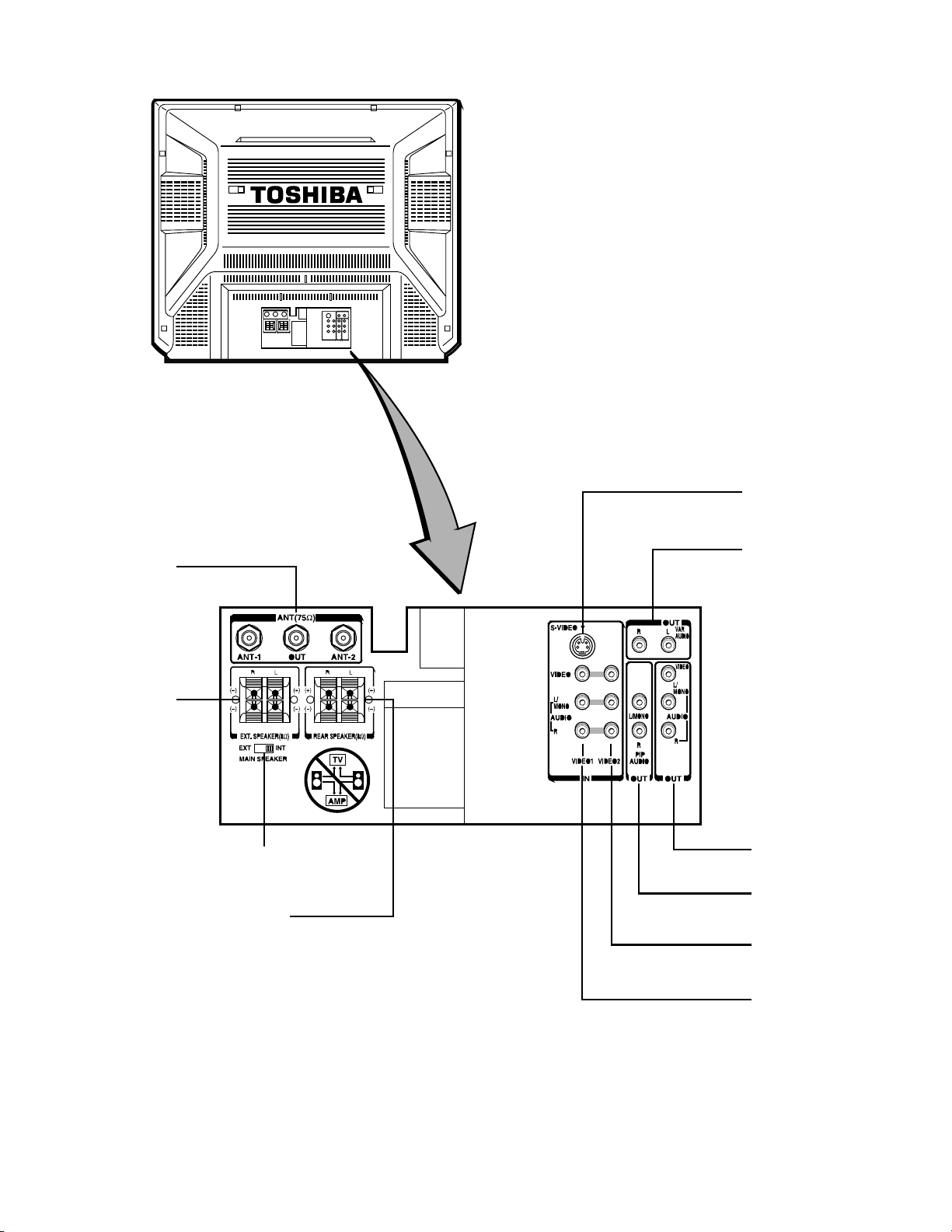

Rear view

t

S-VIDEO IN jack <VIDEO 1>

VARiable AUDIO OUT

ANTenna terminals

EXTernal SPEAKER

erminals

MAIN SPEAKER

switch

REAR SPEAKER

terminals

jacks

VIDEO AUDIO OUT

jacks

PIP AUDIO OUT

jacks

VIDEO/AUDIO IN jacks

<VIDEO 2>

VIDEO/AUDIO IN jacks

<VIDEO 1>

Fig. 1-3

10

Page 11

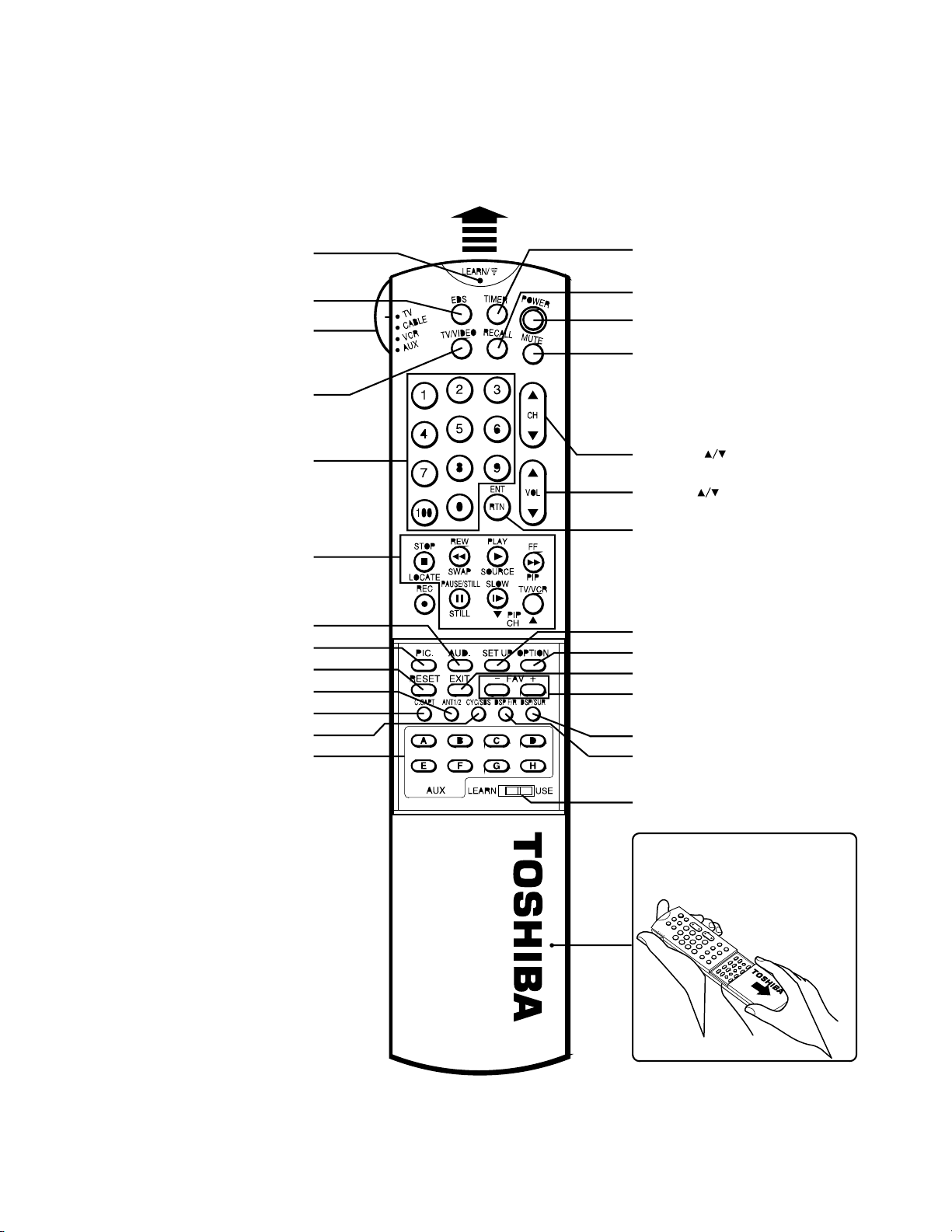

6-2 Location of Controls (Remote Control)

Only the buttons that are used to operate the TV set are described here.

For details on the use of each control, refer to pages in brackets.

Aim at the remote sensor on the TV

Learn/Transmit indicator

EDS button

TV/CABLE/VCR/AUX switch

Set to "TV" to control the TV.

TV/VIDEO

Channel Number buttons

PIP function buttons

AUDio button

PICture button

RESET button

ANT 1/2 button

C.CAPT button

CYS/SBS button

Learning buttons

You can use these eight

buttons only as Learning

function buttons.

They are not affected by

Mode selection (TV/CABLE/

VCR/AUX).

TIMER button

RECALL button

POWER button

MUTE button

CHANNEL buttons

VOLUME buttons

RTN buttons

SET UP button

OPTION button

EXIT button

-\+ buttons

FAV -/+ buttons

DSP/SUR button

DSP F/R button

LEAR/USE switch

To operate buttons inside the cover,

slide the cover down and toward you.

Fig. 1-4

11

Page 12

6-3 Monitor Panel

This TV set is equipped with S-VIDEO INPUT jacks,

VIDEO/AUDIO INPUT jacks, VIDEO/AUDIO OUTPUT

jacks, VARIABLE AUDIO OUTPUT jacks, PIP AUDIO

OUTPUT jacks and EXTERNAL SPEAKER terminals for

connecting your desired video/audio equipment.

TV Front

935

TV Rear

10

11 1 2

74

8

6

Fig. 1-5

, , VIDEO 1/VIDEO 2/VIDEO 3 IN Jacks —

provide for direct connection of video devices

(VCR, video disc player, camcorder, etc.) with

video/audio outputs.

, S-VIDEO IN Jacks —provide for direct S-video

connection from an

VCR or a video disc

player. The TV's VIDEO 1/3 audio jacks can

also be used to connect the VCR's audio cables.

VIDEO/AUDIO OUT Jacks --- provide fixedlevel audio and video outputs from whatever is

displayed on the screen.

VARIABLE AUDIO OUT Jacks --- feed

volume-controlled stereo audio out from

whatever is displayed on the screen, allows

connection of audio amplifier and lets you adjust

sound level with TV's remote.

12

PIP AUDIO OUT Jacks — provide fixed-level

audio outputs from whatever is displayed on the

PIP window screen.

EXTERNAL SPEAKER Terminals — provide

for direct connection of external speakers.

MAIN SPEAKER Switch — lets you turn off

TV's built-in speakers so that sound will instead

come through speakers connected to

EXTERNAL SPEAKER terminals.

REAR SPEAKER Terminals — provide for

direct connection of the supplied Surround

Speakers.

Page 13

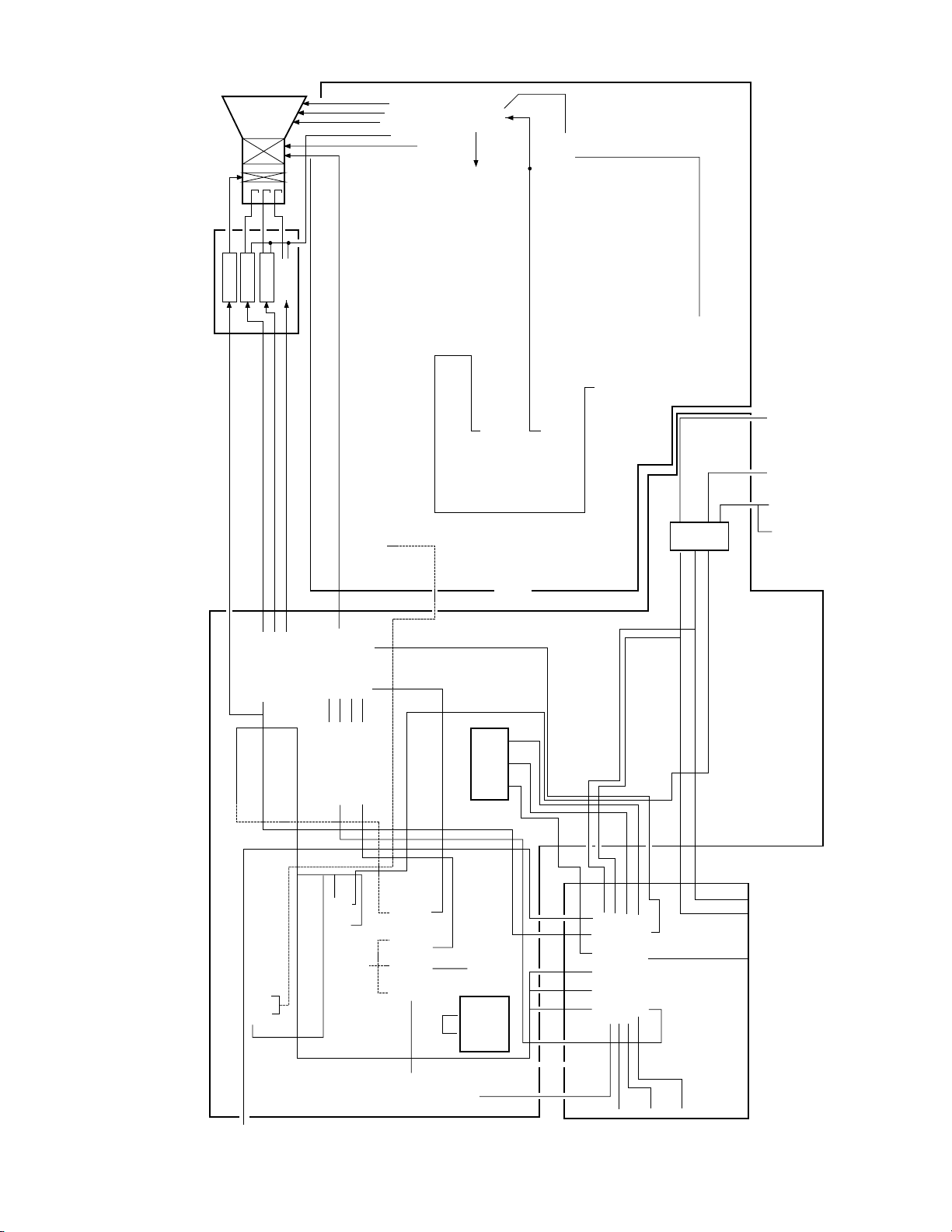

7. CN32D90 BLOCK DIAGRAM

13

Page 14

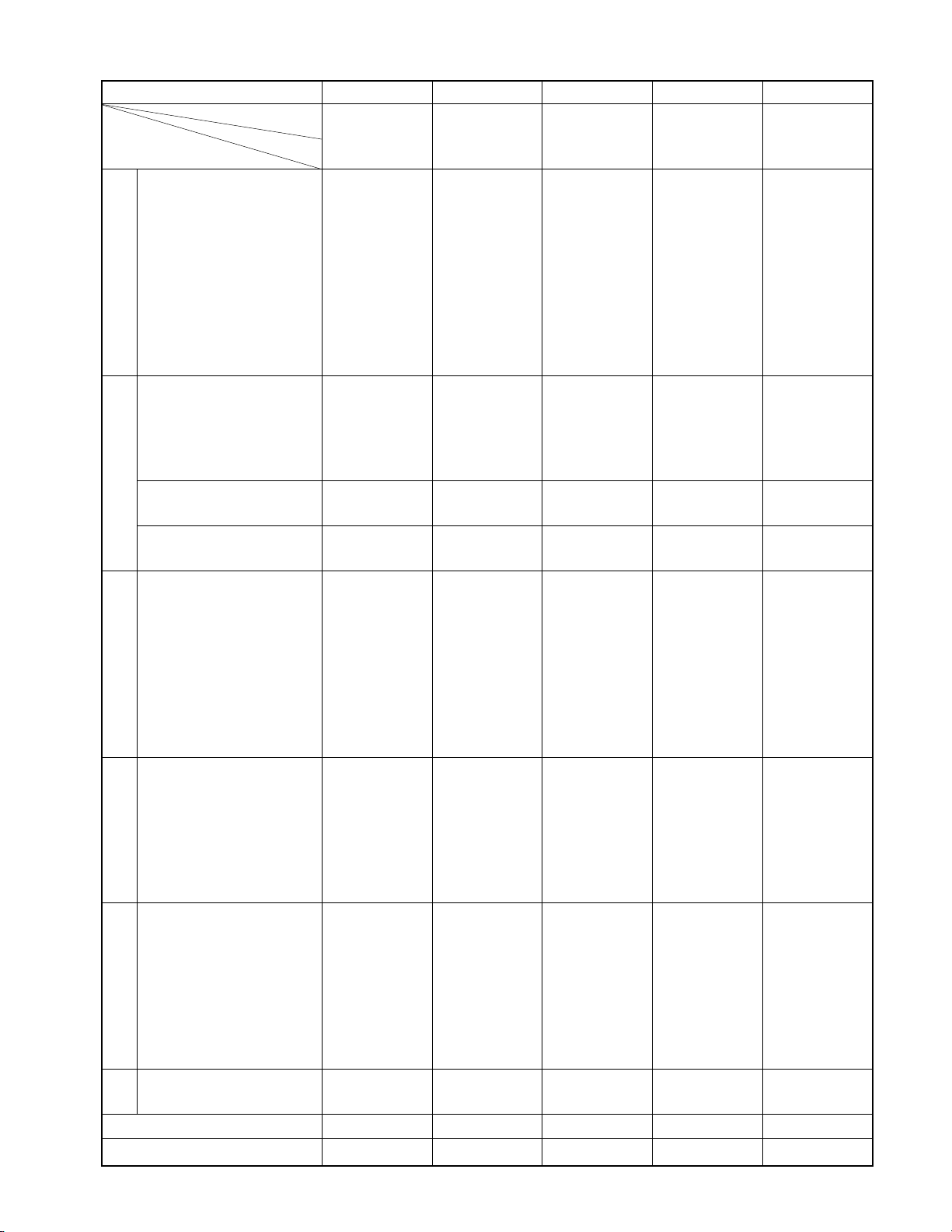

8. [US, CANADA] SPECIFICATION FOR MODEL's 1995

CHASSIS C C C C C

MODEL Nbr CN27E90 CX32E70 CN32E90 CE35E15 CF35E50

SPECIFICATION HITACHI TDD TDD *TDD *TDD

1 Picture Tube *FST-D/T NF-D/T NF-D/T *FST-D/T FST-D/T

2 Channel Capacity 181ch 181ch 181ch 181ch 181ch

*

3 C. Caption ●●●●●

G

4 MTS with dbx ●●●●●

E

N

5 Bass, Tre, Balance ●●●●●

E

6 Sub-Audio-Program ●●●●●

R

7 Remote band unit *A-Univ (42k) *A-Univ (42k) *Intelig+EZ *Unive (36k) *Unive (36k)

A

8 Picture-in-Picture ● (2TN) ● (2TN) ● (2TN) *● (1TN) ● (1TN)

L

9 LED Indicators (RED) ● (Power) ● (Power) ● (Power) *● (Power) ● (Power)

10 Local Keys 8key 8key 8key 8key 8key

11 Dolby Surround — — ● ——

12 Dig-Sound Processor — — ● (DSP4ch) — —

*

13 Front Surround ●●—●●

S

14 Cyclone ABX ● — ● ——

O

15 Sub-Bass-System — ● ———

U

16 Audio Output *10Wx2 & 13W 10Wx2 10Wx2 & 10Wx2 10Wx2

N

D

17 Speaker Size & Nbr *80x120x2 70x130x2 80x120x2 70x130x2 70x30x2

18 Comb Filter *● (GLS) ● (CCD) ● (CCD) ● (CCD) ● (GLS)

*

19 Dy-Quadruple Focus — — — — —

P

20 Scan Velocity Modu ●● ●●●

I

21 Vert Contour Corre ●●●● ●

C

22 Black Level Expand ●●●●●

T

23 Flesh Tone Correct *●●●●●

U

R

24 Dynamic Noise Reduc *●●●●●

E

25 Picture Preference ●●●● ●

26 Horiz Resolution 650 700 700 800 800

27 Parental-Ch Lock ●●●●●

*

28 Channel Label (32ch) ●●●●●

O

29 3-Language Display ●●●●●

T

30 Clock/Off-Timer *●/●●/●●/●●/●●/●

H

31 Favorite Channel *● *● *● *● *●

E

R

32 Extended-Data-Servi *● *● *● *● *●

33 Star-Sight-decoder — — — — —

34 S-Video In-Term ● (1+1) ● (1+1) ● (1+1) ● (1) ● (1)

35 Audio, Video-In/Out 1+2/— 1+2/1 1+2/1 *3/1 3/1

*

36 Front AV Jack *●●●——

T

E

37 Variable Audio Out ●●●●●

R

38 2-RF Input ●●●——

M

39 Ext Speaker Term ●●●●●

S

40 PIP Audio Out Jack — *— *● ——

41 Center-Ch-Aud-Input — *● *— — —

42 Speaker-Box -- — ● SS-SR94 — —

*

AC

43 Others — — — — —

*Cabinet NEW CX32D70 CN32D90 *CE35D10 CF35D50

PARTS SUPPLY (ISO) — — — — —

CRT

13W & 5Wx2

& 100R (Hon) 100R & REAR

DERIV

14

Page 15

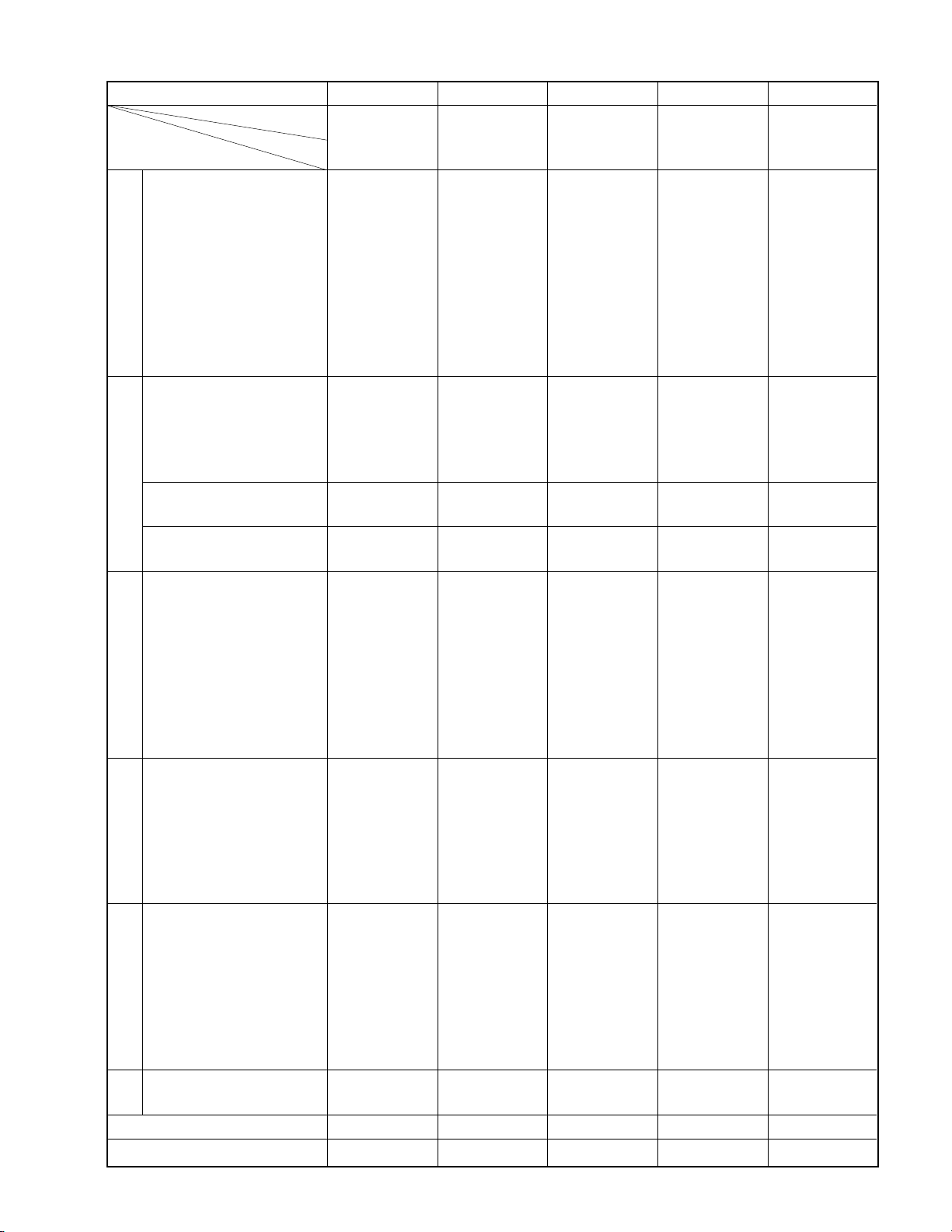

CHASSIS C C C C C

MODEL Nbr CX35E60 CX35E70 CX35E81 CN35E90 CN35E95

SPECIFICATION TDD TDD TDD TDD TDD

1 Picture Tube FST-D/T NF-D/T NF-D/T NF-D/T NF-D/T

2 Channel Capacity 181ch 181ch 181ch 181ch 181ch

*

3 C. Caption ●●●●●

G

4 MTS with dbx ●●●●●

E

N

5 Bass, Tre, Balance ●●●●●

E

6 Sub-Audio-Program ●●●●*●

R

7 Remote band unit *A-Univ (42k) *A-Univ (42k) *A-Univ (42k) *Intelig+EZ *Intelig+EZ

A

8 Picture-in-Picture ● (2TN) ● (2TN) ● (2TN) ● (2TN) ● (2TN)

L

9 LED Indicators (RED) ● (Power) ● (Power) ● (Power) ● (Power) ● (Power)

10 Local Keys 8key 8key 8key *8key *8key

11 Dolby Surround — — — ●●

12 Dig-Sound Processor — — — ● (DSP4ch) ● (DSP4ch)

*

13 Front Surround ●●●——

S

14 Cyclone ABX — — — ●●

O

15 Sub-Bass-System ●●●——

U

16 Audio Output 10Wx2 10Wx2 10Wx2 10Wx2 10Wx2

N

D

17 Speaker Size & Nbr 70x130x2 70x130x2 70x130x2 80x120x2 & 80x120x2 &

18 Comb Filter ● (DIG) ● (DIG) ● (DIG) ● (DIG) ● (DIG)

*

19 Dy-Quadruple Focus ●●●●●

P

20 Scan Velocity Modu ●●●●●

I

21 Vert Contour Corre ●●●●●

C

22 Black Level Expand ●●●●●

T

23 Flesh Tone Correct ●●●●●

U

R

24 Dynamic Noise Reduc ●●●●●

E

25 Picture Preference ●●●●●

26 Horiz Resolution 800 800 800 800 800

27 Parental-Ch Lock ●●●●●

*

28 Channel Label (32ch) ●●●●●

O

29 3-Language Display ●●●●●

T

30 Clock/Off-Timer ●/●●/●●/●●/●●/●

H

31 Favorite Channel *● *● *● *● *●

E

R

32 Extended-Data-Servi *● *● *● *● *●

33 Star-Sight-decoder — — — — —

34 S-Video In-Term ● (1+1) ● (1+1) ● (1+1) ● (1+1) ● (1+1)

35 Audio, Video-In/Out 1+2/1 1+2/1 1+2/1 1+2/1 1+2/1

*

36 Front AV Jack ●●●●●

T

E

37 Variable Audio Out ●●●●●

R

38 2-RF Input ●●●●●

M

39 Ext Speaker Term ●●●●●

S

40 PIP Audio Out Jack — *— *— *● *●

41 Center-Ch-Aud-Input — *● *● *— *—

42 Speaker-Box — — — ● SS-SR94 ● SS-SR94

*

AC

43 Others — *VCR-Storate — *VCR-Stora

*Cabinet C35D60 CX35D70 NEW (DAX) CN35D90 NEW (BLK)

PARTS SUPPLY (ISO) — — — — —

CRT

CONSOLE CINEMA

& 13W, 5Wx2 & 13W, 5Wx2

*100R, REAR *120R, REAR

15

Page 16

SECTION II

TUNER, IF/MTS/S.PRO MODULE

16

Page 17

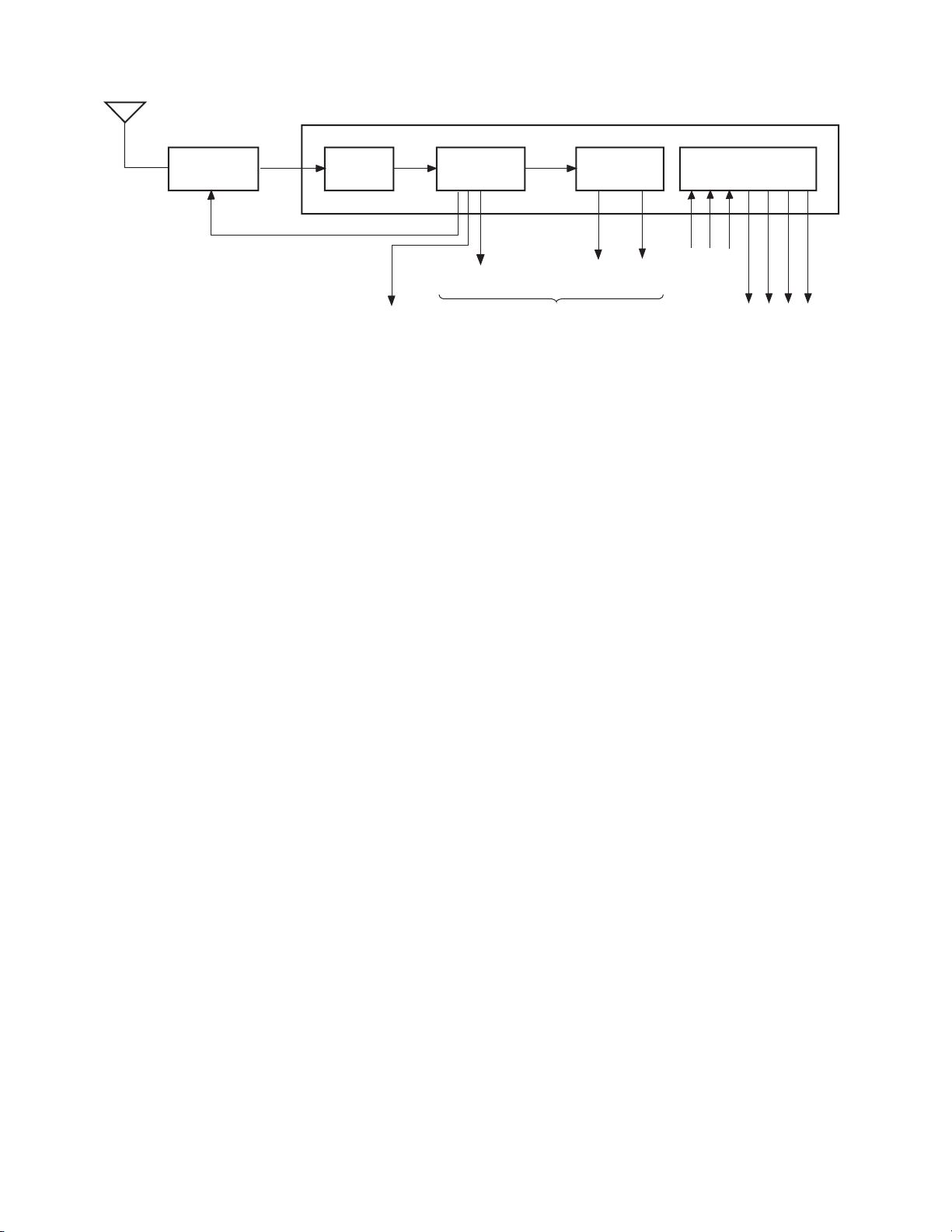

1. CIRCUIT BLOCK

T

EL466L

Tuner

RF AGC

1-1. Outline

IF/MTS/S.PRO Module MVUS34S

SAW

Filter

AFT output

VIF/SIF

Circuit

TP12

Video output

Fig. 2-1 Block diagram

SIF

output

To A/V switch circuit

Multiplex

TV

R-OUTTVL-OUT

Sound

Circuit

C-IN

S.PRO Circuit

R-IN L-IN

R-OUT

L-OUT

(L+R)

-OUT

C-OU

(1) RF signals sent from an antenna are converted into

intermediate frequency band signals (video: 45.75 MHz,

audio: 41.25 MHz) in the tuner. (Hereafter, these signals

are called IF signals.)

(2) The IF signals are band-limited in passing through a

SAW filter.

(3) The IF signals band-limited are detected in the VIF

circuit to develop video and AFT signals.

(4) The band-limited IF signals are detected in the SIF

circuit and the detected output is demodulated by the

audio multiplexer, developing R and L channel outputs.

These outputs are fed to the A/V switch circuit.

(5) A sound processor (S.PRO.) is provided.

1-2. Major Features

(1) The VIF/SIF circuit is fabricated into a small module by

using chip parts considerably.

(2) As the tuner, EL466L that which contains an integrated

PLL circuit is employed.

(3) Wide band double SAW filter F1802R used.

(4) FS (frequency synthesizer) type channel selection system

employed.

(5) VIF/SIF circuit uses PLL sync detection system to

improve performances shown below:

• Telop buzz in video over modulation

• DP, DG characteristics (video high-fidelity

reproduction)

• Cross color characteristic (coloring phenomenon at

color less high frequency signal objects)

(6) HIC SBX1637A-22 is used in the audio multiplexer

circuit to minimize the size with increased performance.

(7) As a sound control processor, TA1217N is used. I

2

Cbus data control the DAC inside the IC to perform

switching of the audio multiplexer modes.

17

Page 18

2. TUNER

2-1. Outline

(1) Type name: EL466L

(2) Applicable 181CH

(3) I2C-bus version

(4) PLL-integrated

2-2-2. Terminals (Tuner section)

Name Function

IF OUT IF outputs (P=45.75 MHz, C=42.17 MHz,

S=41.25 MHz)

BM Tuner power supply (9V)

RF AGC Gain control terminal to obtain constant

IF output

VT Control voltage to select channels

PLL Selection

EL466L

Tuner Section

1 2 3 4 5 6 7 8 9

Terminal No. Name

1 32V

25V

3 S-CLOCK

4 S-DATA

5 ADDRESS

6 IF OUT

7 BM (9V)

8 RF AGC

9VT

Fig. 2-2 Tuner terminal layout

2-2-3. Tuner VT Voltage (unit: V)

(1) VHF (2) UHF

CH VT voltage (TYP)

2 1.4

6 6.4

A-2 12.8

B 20.0

C 1.4

I 3.5

10 5.6

J 7.6

N 9.7

R 11.8

W 14.2

FF 17.9

LL 24.2

CH VT voltage (TYP)

MM 1.1

QQ 2.2

WW 4.0

14 5.8

20 7.8

26 9.2

32 10.8

38 12.5

44 13.9

50 15.0

56 17.2

62 19.4

69 23.6

* VT voltage not indicated for a channel falls between

those values for channels just upper and lower the channel.

2-2. Operation of the Tuner

2-2-1. Receiver Channels

VHF 2~13CH

UHF 14~69CH 181CH in total

CATV A-6~, J~W, AA~BBB, 65~92, 100~127CH

18

Page 19

3. IF/MTS/S.PRO MODULE

The IF/MTS/S.PRO module (MVUS34S) limits bandwidth

of IF signals and detects video and audio signals. The module

consists of IF amplifiers, SAW (surface acoustic wave)

filter, and PIF IC. The SAW filter has a wideband response

to improve picture quality and audio buzz characteristic and,

develops separate outputs of video and audio signals. The

PIF IC employs a PLL complete sync detection + audio split

carrier system.

3-1-2 Video PIF Circuit

A PIF detector switching carrier is oscillating at a frequency

adjusted to 45.75 MHz with L051 (VCO CW coil) under no

RF signal input. When an RF signal enters, an IF video

carrier is fed to APC section from IF AMP inside the IC, and

the detector switching carrier is adjusted by the APC, VCO,

etc. in the PLL circuit so that its frequency and phase are

matched to those of the IF video carrier to perform precise

sync detection. Thus processed video output is developed at

pin 21.

3-1. IF/MTS/S.PRO Module (MVUS34S)

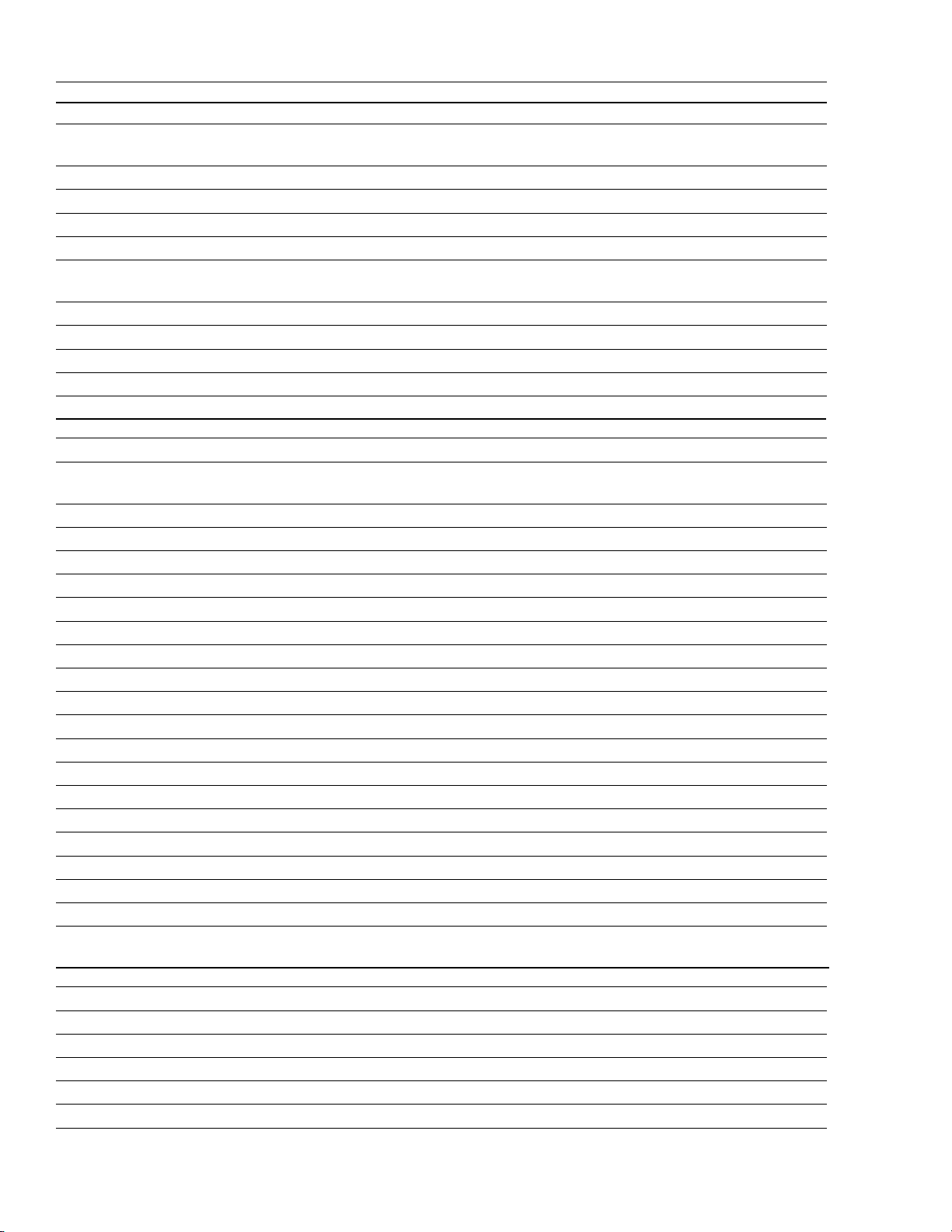

3-1-1. Module Terminal Layout

91

27

12

Pin No. Name Pin No. Name

1 GND 15 DAC-OUT2

2 IF-IN 16 R-IN

3 NC 17 C-IN

4 +9V 18 L-IN

5 RF AGC 19 GND

6 AFC 20 SCL

7 VIDEO OUT 21 SDA

8 ADR SW 22 W-OUT

9 MPX OUT 23 C-OUT

10 --- 24 L-OUT

11 --- 25 GND

12 TV R-OUT 26 R-OUT

13 DAC-OUT1 27 +9V

14 TV L-OUT

PLL lock speed is automatically controlled by adding the

video signal at pin 21 to pin 1. That is, since the video signal

is not output at operations of power on, CH switching, etc.,

the APC filter between pin 16 and GND consists of C022 and

C053, and R018, and the filter effect decreases, thus increasing

PLL lock speed.

Next, when a video out exists, the internal resistance is shortcircuited and the APC filter consists of C022 and C053,

internal resistance, and R018. As a result, the filter effect

increases and the PLL lock speed decreases. Consequently,

under normal signal reception, phase of the detector switching

carrier is locked in a stable condition if an IF video carrier is

lost for a short time due to over modulation, etc. By combining

such a PLL complete sync detection system and a wideband

SAW filter shown in Fig. 2-4, a wideband (4.2 MHz) video

detection output with less beat interference will be obtained.

3-1-3. Audio PIF Circuit

The IF signal fed through Q003 (Fig. 2-4) enters an audio

section of the SAW filter (Z001) which has an IF bandwidth

for dedicated audio signals, and only the audio signal of

41.25 MHz is fed to pin 7. The signal is sync-detected with

the detection carrier completely synchronized with the IF

video carrier and pin 14 develops a 4.5 MHz SIF signal. By

using the PLL split carrier system just stated, audio signals

with less buzz by the video signal will be reproduced. The 4.5

MHz SIF enters pin 15 through a 4.5 MHz filter, Z003 and

pin 9 develops a FM-detected audio signal.

Fig. 2-3 IF/MTS/S.PRO module terminal layout

19

Page 20

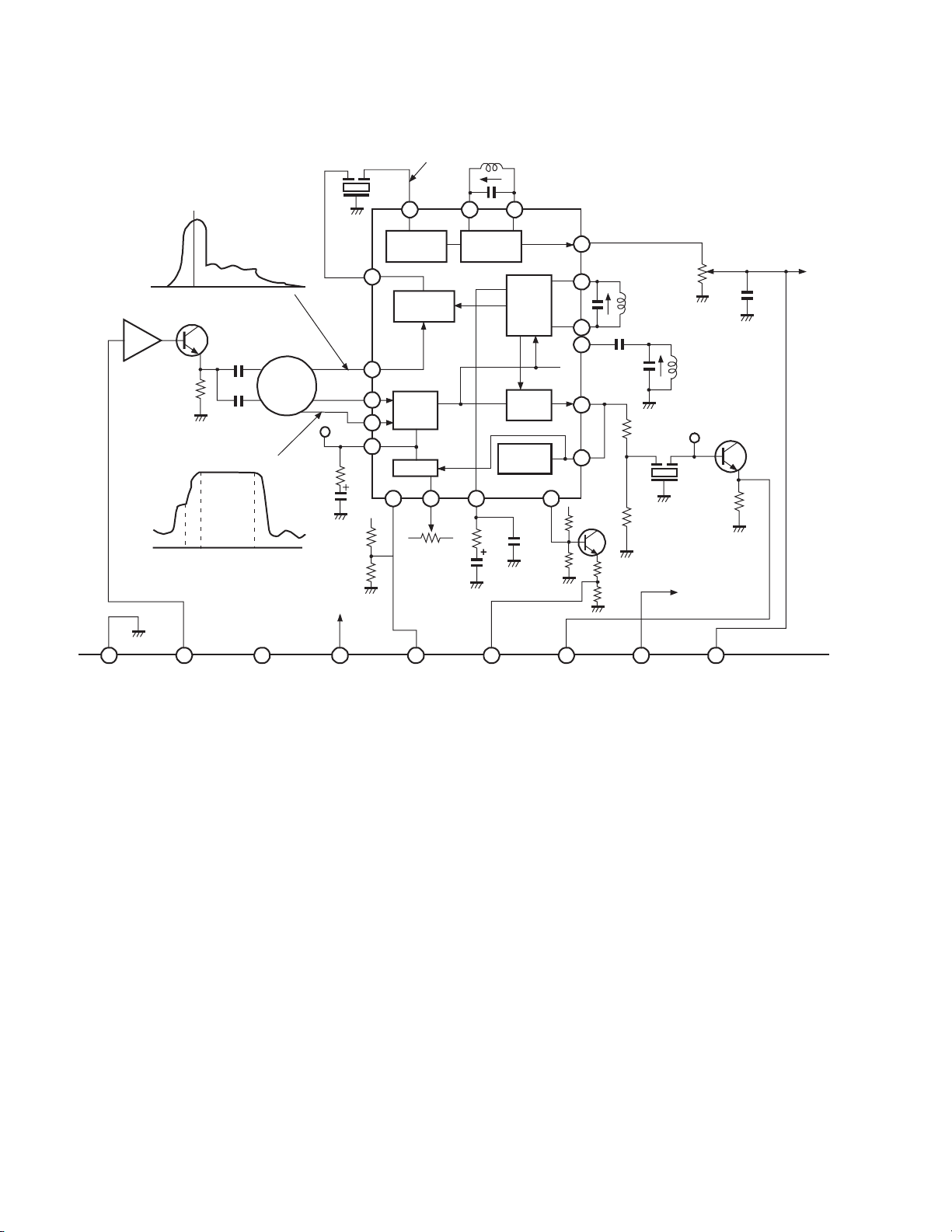

SIF BANDWIDTH

M

D

Z003

4.5MHz SIF SIGNAL

15

11 12

FM DET. COIL

L053

9

17.

18

23

21

1

R151

L051

VCO

CW COIL

L502

AFT COIL

TP12

R021

Z002

R022

TO SOUN

MPX IC

C106

Q004

Q002

Q003

IF AMP

GAIN – 14dB

-15dB

S C P

41.25M 45.75M

S

Z001

SAW

FILTER

F1802R

-6dB

SIF LIMIT FM DET.

14.

SIF DET

7

5

IF

AMP

4

22

AGC

2

13 16 20

RF AGC

R051

R018

C053

APC

VCD

VIDEO

DET.

LOCK

CONTROL

C022

VIDEO IF BANDWIDTH

1 2

3

4 5 6

7

8

9

GND IF-IN N.C +B(9V) RF AGC AFC VIDEO OUT ADR SW

Fig. 2-4 IF/MTS/S. PRO circuit diagram

20

Page 21

3-1-4. Audio Multiplex Demodulation Circuit

The sound multiplex composite signal FM-detected in the

PIF circuit enters pin 12 of HIC (hybrid IC) in passing

through the separation adjustment VR RV2 and amplified.

After the amplification, the signal is split into two: one enters

a de-emphasis circuit, and only the main signal with the LR signal and a SAP signal removed enters the matrix circuit.

At the same time, the other passes through various filters and

trap circuits, and the L-R signal is AM-demodulated, and the

SAP is FM-demodulated.

MVUS32S

Then, both are fed to the matrix circuit. At the same time,

each of the stereo pilot signal fH and the SAP pilot signal 5fH

is also demodulated to obtain an identification voltage. With

the identification voltage thus obtained and the user control

voltage are used to control the matrix.

The audio signals obtained by demodulating the sound

multiplex signal develop at pin 10 and 11 of HIC and develop

the terminals of 12 and 14 of the module.

MPX

Out

9

Monitor the input

pin for multiplex

sound IC

10

Stereo 0V

Other 0V

Fig. 2-5 Block diagram of MVUS32S

Table 2-1 Matrix for broadcasting conditions and

reception mode

Output OSD display

Broad- Switching

casted mode

12 pin 14 pin

(R) (L)

Stereo SAP

Stereo STE R L O X

SAP R L O X

MONO L+R L+R O X

Mono STE L+R L+R X X

SAP L+R L+R X X

MONO L+R L+R X X

Stereo STE R L O O

+ SAP SAP SAP O O

SAP MONO L+R L+R O O

Mono STE L+R L+R X O

+ SAP SAP SAP X O

SAP MONO L+R L+R X O

DAC-out1 DAC-out2

TV TV

(SURR OFF)

R-Out

11

SAP 0V

Other 0V

TV waveform detection

12 13 14

OFF 0V

ON 9V

Not used for

CN32E90.

output (R)

To AV select circuit

Note:

Of the mode selection voltages, switching voltages for STE,

SAP, MONO do not output outside the module.

They are used inside the module to control the BUS.

L-Out

TV waveform detection

output (L)

(RFSW)

14

RF1 0V

RF1 9V

21

Page 22

3-1-5. A.PRO Section (Audio Processor)

The S.PRO section has following functions.

(1) Woofer processing (L+R output)

(2) High band, low band, balance control

(3) Sound volume control, cyclone level control

(4) Cyclone ON/OFF

TA1217N

All these processing are carried out according to the BUS

signals sent from a microcomputer.

Fig. 2-6 shows a block diagram of the A.PRO IC.

Lin

Rin

Cin

Win

SDA

SGL

1272922 32

30

34

2

3

20

21

TONE CONTROL

LPF

4

33

Center

LEVEL

Woofer

LEVEL

2

I C

56 73124

D/A

CONV

VOLUME

23 22 19

30 9 8 28

BALANCE

I/O

26

Lout

Rout

25

Cout

18

Wout

10

17

16

15

14

13

12

11

SAP det.

STE det.

16

R-in C-in L-in

From From From

A/V Dolby A/V

18 19 20 21 22

17

24

23

SCL SDA W-out O-out L-out R-out

Q670 Q640 Q670 Q670

Via QS101

26 27

25

Fig. 2-6 A.PRO block diagram

22

9V

Page 23

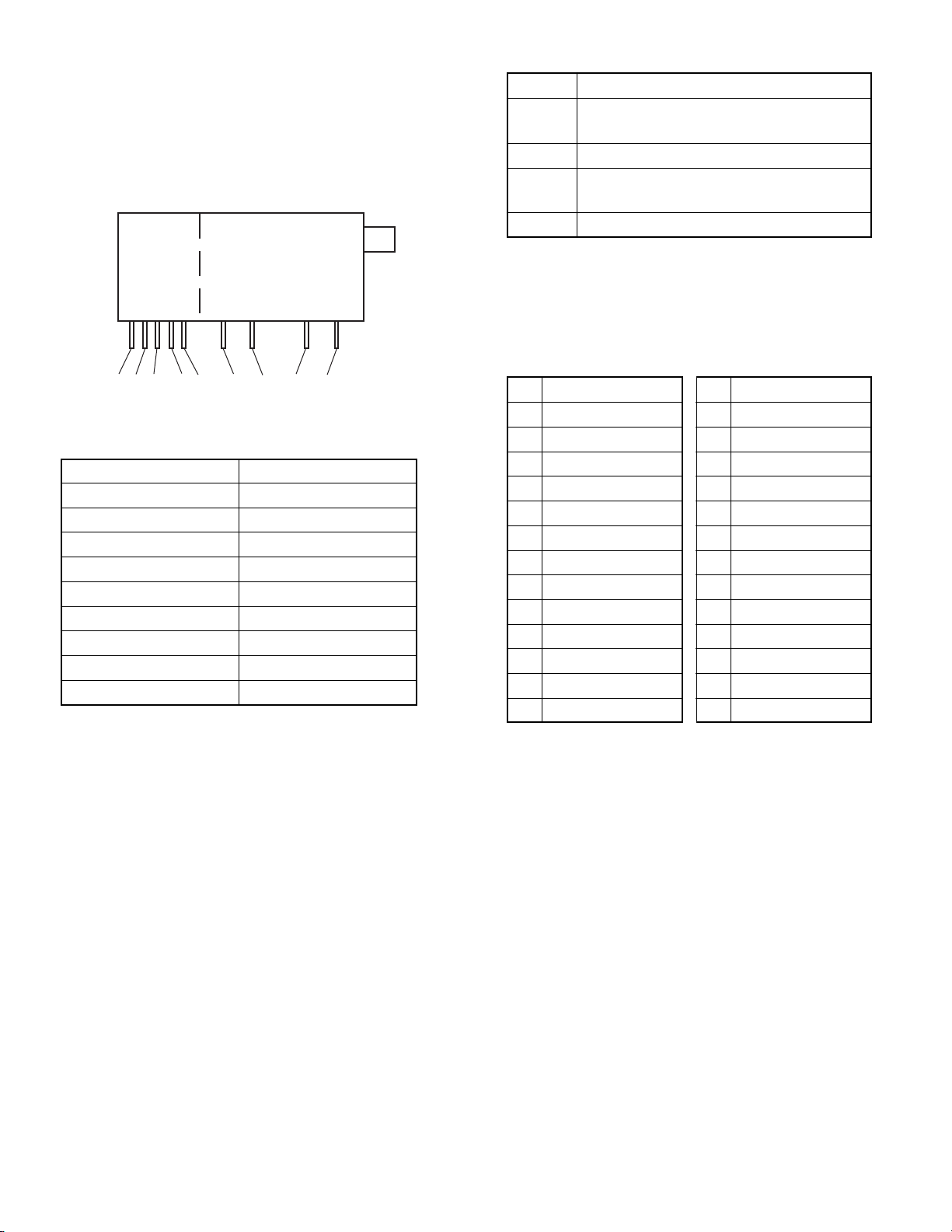

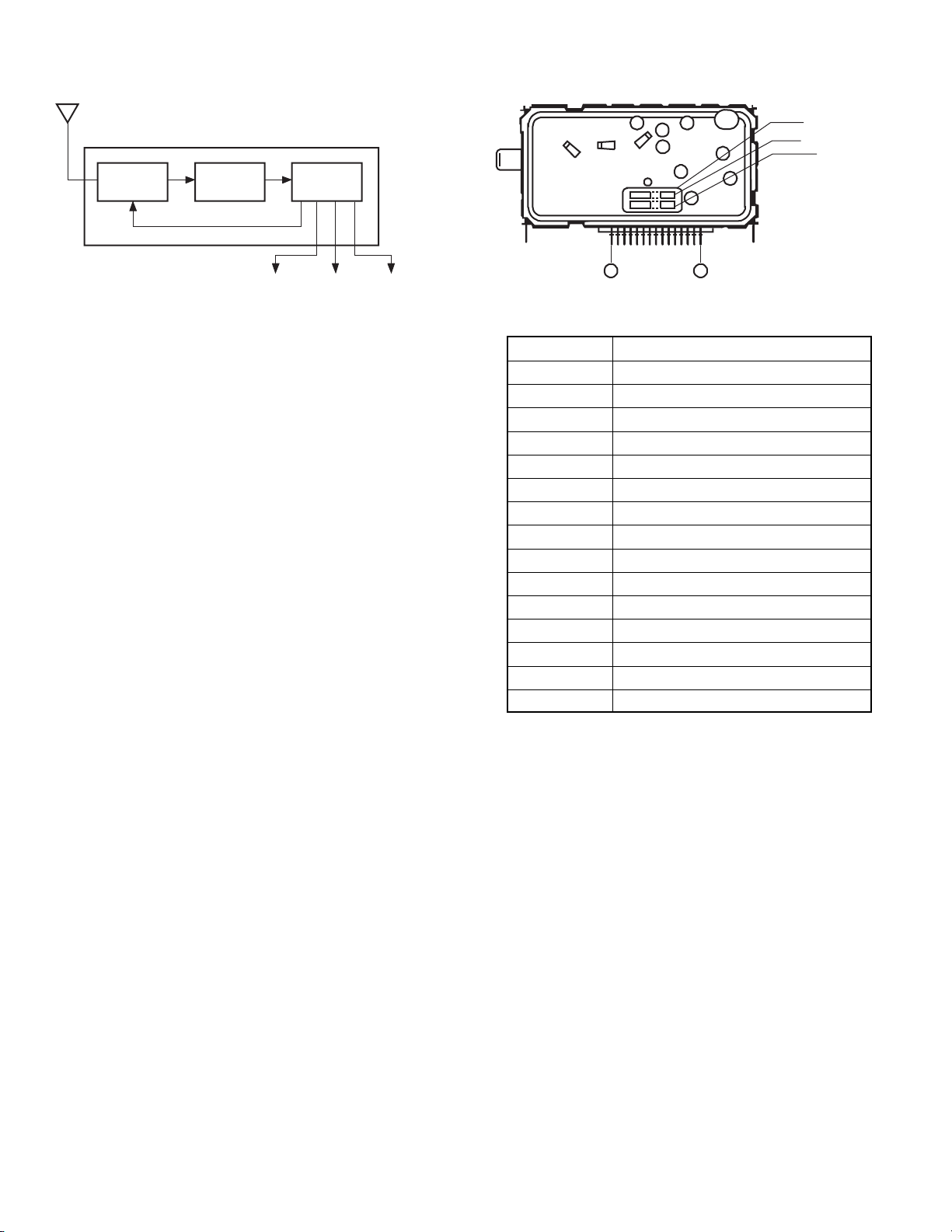

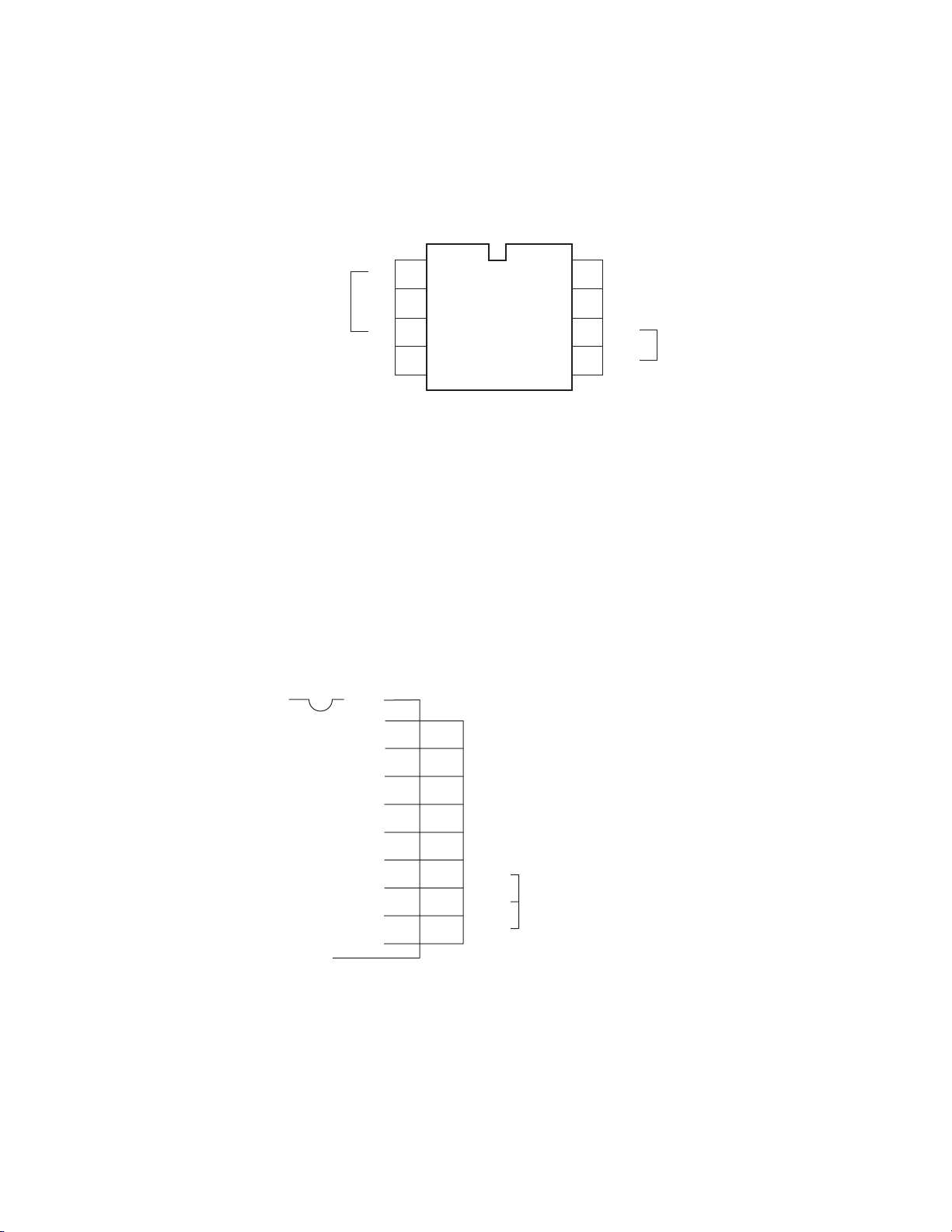

4. PIP TUNER

Lable

Name

Lot No.

1

15

TUNER

SECTION

RF AGC

SAW

FILTER

AFT

OUTPUT

VIF/SIF

CIRCUIT

VIDEO

OUTPUT

AUDIO

OUTPUT

Fig. 2-7

4-1. Outline

The PIP tuner (EL922L) consists of a tuner and an IF block

integrated into one unit. The tuner receives RF signals

induced on an antenna and develops an AFT output, video

output, and audio output.

The tuner has receive channels of 181 as in the tuner for the

main screen and it is also controlled through the I2C-bus.

As the IC for the IF, a PLL complete sync detection plus

audio inter carrier system are employed.

Terminal No. Name

1NC

2 32V

3 S-CLOCK

4 S-DATA

5NC

6 ADDRESS

75V

8 RF AGC

99V

10 AUDIO

11 GND

12 AFT

13 NC

14 GND

15 VIDEO

Fig. 2-8 Tuner terminal layout

23

Page 24

SECTION III

CHANNEL SELECTION CIRCUIT

24

Page 25

1. OUTLINE OF CHANNEL SELECTION

CIRCUIT SYSTEM

The channel selection circuit in the N5SS chassis employs

a bus system which performs a central control by connecting

a channel selection microcomputer to a control IC in each

circuit block through control lines called a bus. In the bus

system which controls each IC, the I2C bus system (two line

bus system) developed by Philips Co. Ltd. in the Netherlands

has been employed.

The ICs controlled by the I2C bus system are : IC for audio

signal processing (QN06), IC for V/C/D signal processing

(Q501), IC for A/V switching (QV01), IC for non volatile

memory (QA02), Main and sub U/V tuners (H001, HY01),

IC for deflection distortion correction (Q302), IC for PIP

signal processing (QY04), IC for DSP (QM01), IC for

closed caption control (Q701).

Differences from N4SS chassis are as follows;

1. On-screen function inside microcomputer is used.

Separate IC is not used for on-screen.

2. The microcomputer does not have the closed caption

function, but controls separate IC for closed caption.

3. The system uses two channels of I2C bus. One is only

for non-volatile memory.

2. OPERATION OF CHANNEL

SELECTION CIRCUIT

Toshiba made 8 bit microcomputer TLCS-870 series for TV

receiver, TMP87CS38N-3152 is employed for QA01.

With this microcomputer, each IC and circuit shown below

are controlled.

(1) CONTROL OF AUDIO SIGNAL PROCESS IC (QN06

Toshiba TA1217N)

• Adjustments for volume, treble, bass and balance

• Selection between surround mode and DSP mode,

and level adjustment

• Level adjustment of BAZOOKA system

• Audio muting during channel selection or no signal

reception.

(2) CONTROL OF VIDEO/CHROMA/DEF SIGNAL

PROCESS IC (Q501 Toshiba TA1222N)

• Adjustments for uni-color, brightness, tint, color

gain, sharpness and PIP uni-color

• Setting of adjustment memory values for subbrightness, sub-color and sub-tint, etc.

• Setting of memory values for video parameters

such as white balance (RGB cutoff, GB drive) and

gcorrection, etc.

• Setting of video parameters of video modes

(Standard, Movie, Memory)

(3) CONTROL OF A/V SWITCH IC (QV01 Toshiba

TA1219N)

• Preforms source switching for main screen and

sub screen

• Performs source switching for TV and three video

inputs

(4) CONTROL OF NON-VOLATILE MEMORY IC

(QA02 Microchip 24LC04BI/P)

• Memorizes data for video and audio signal

adjustment values, volume and woofer adjustment

values, external input status, etc.

• Memorizes adjustment data for white balance

(RGB cutoff, GB drive), sub-brightness, sub color,

sub tint, etc.

• Memorizes deflection distortion correction value

data adjusted for each unit.

(5) CONTROL OF U/V TUNER UNIT (H001 Matsushita

EL466L, HY01 Toshiba EL922L)

• A desired channel can be tuned by transferring a

channel selection frequency data (divided ratio

data) to the I2C bus type frequency synthesizer

equipped in the tuner, and by setting a band switch

data which selects the UHF or VHF band.

(6) CONTROL OF DEFLECTION DISTORTION

CORRECTION IC (Q302 Toshiba TA8859P)

• Sets adjustment memory value for vertical

amplitude, linearity, horizontal amplitude,

parabola, corner, trapezoid distortion.

(7) CONTROL OF PIP SIGNAL PROCESS IC (QY04

Toshiba TC9083F)

• Controls ON/OFF and position shift of PIP.

(8) CONTROL OF DIGITAL SOUND PROCESSOR IC

(QM04 Yamaha YSS238-D)

• Performs mode switching of DSP.

(9) CONTROL OF CLOSED CAPTION/EDS (QM01

Motorola XC144144P)

• Controls Closed Caption/EDS.

25

Page 26

3. MICROCOMPUTER

SDA

SCL

1 - 7

8

9 1 - 7

8

9

1 - 7

8

9

START

CONDITION

STOP

CONDITION

ADDRESS

R/W

Ack DATA

Ack

DATA Ack

Approx.180

m

S

Some device may have no data,

or may have data with several

bytes continuing.

Microcomputer TMP87CS38N-3152 has 60k byte of ROM

capacity and equipped with OSD function inside.

The specification is as follow.

• Type name : TMP87CS38N-3152

• ROM : 60k byte

• RAM : 2k byte

• Processing speed : 0.5m s (at 8MHz with Shortest

command)

• Package : 42 pin shrink DIP

• I2C-BUS : two channels

• PWM : 14 bit x 1, 7 bit x 9

• ADC : 8 bit x 6 (Successive comparison system,

Conversion time 20ms)

• OSD

Character kinds : 256

Character display : 24 characters x 12 lines

Character dot : 14 x 18 dots

Character size : 3 kinds (Selected by line)

Character color : 8 colors (Selected by character)

Display position : Horizontal 128 steps, Vertical

256 steps

This microcomputer performs functions of AD converter,

reception of U/V TV and OSD display in one chip.

IIC device controls through I2C bus. (Timing chart : See fig.

3-1)

• LED uses big current port for output only.

• For clock oscillation, 8MHz ceramic oscillator is used.

• I2C has two channels. One is for EPROM only.

• Self diagnosis function which utilizes ACK function of

I2C is equipped

• Function indication is added to service mode.

• Remote control operation is equipped, and the control

by set no touch is possible. (Bus connector in the

conventional bus chassis is deleted.)

• Substantial self diagnosis function

(1) B/W composite video signal generating function

(micom inside, green crossbar added)

(2) Generating function of audio signal equivalent

to 1kHz (micom inside)

(3) Detecting function of power protection circuit

operation

(4) Detecting function of abnormality in IIC bus

line

(5) Functions of LED blink indication and OSD

indication

(6) Block diagnosis function which uses new VCD

and AV SW

Fig. 3-1

26

Page 27

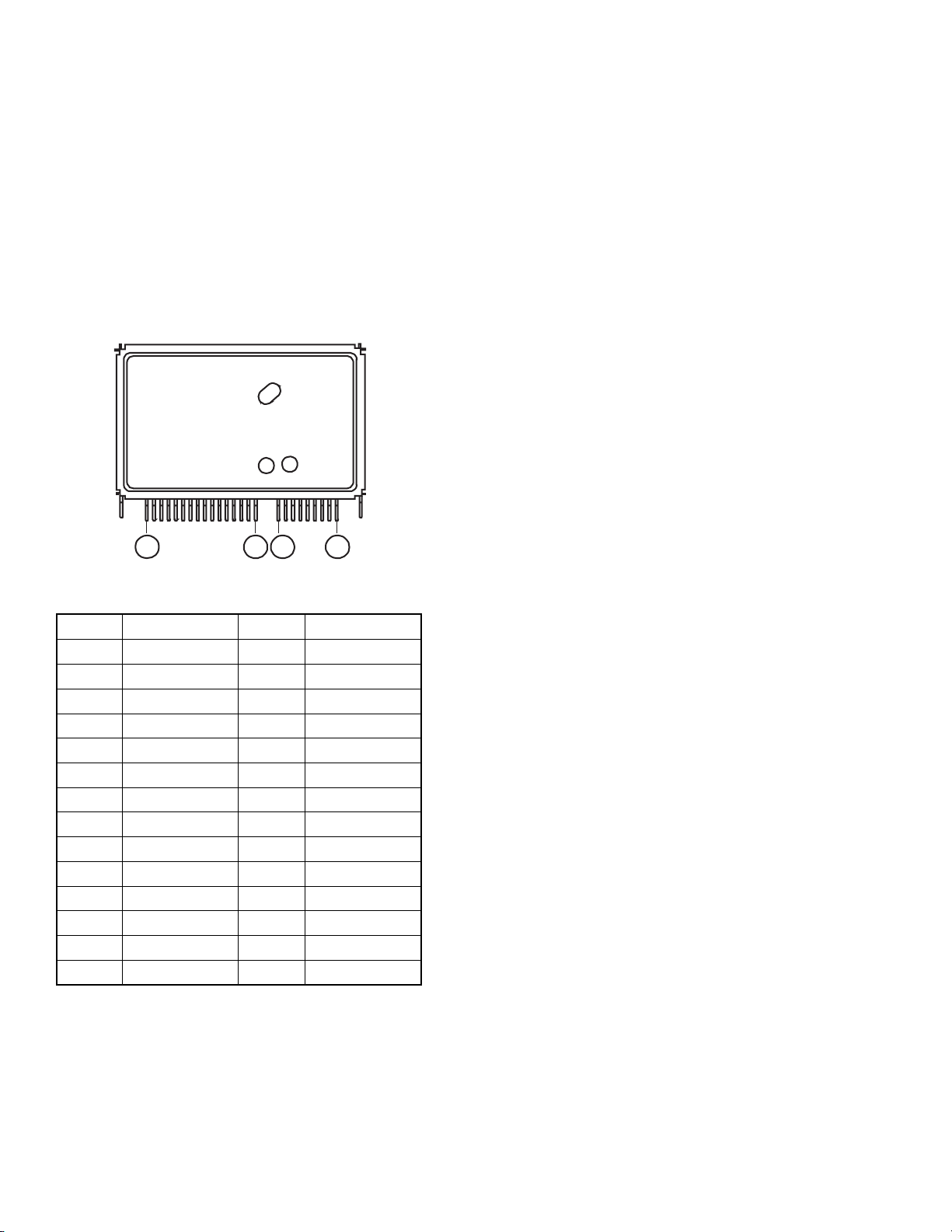

4. MICROCOMPUTER TERMINAL FUNCTION

TMP87CS38N3152 (QA01)

GND

1

GND

VDD

42

VDD

IIC

-BUS

BAL

REM OUT

MUTE

SP MUTE

NC

POWER

LED

NC

NC

SCL0

SDA0

SYNC VCD

NC

AFT2

AFT1

KEY-A

KEY-B

SGV

SGA

GND

10

11

12

13

14

15

16

17

18

19

20

21

2

I

P40 (PWM0)

3

O

P41 (PWM1)

4

O

P42 (PWM2)

5

O

P43 (PWM3)

6

O

P44 (PWM4)

7

O

P45 (PWM5)

8

O

P46 (PWM6)

9

O

P47 (PWM7)

I

P50 (PWM8/TC2)

O

P51 (SCL1)

IO

P52 (SDA1)

I

P53 (AINO/TC1)

I

P54 (AIN1)

I

P55 (AIN2)

I

P56 (AIN3)

I

P60 (AIN4)

I

P61 (AIN5)

O

P62

O

P63

VSS

P57

P32

P57

SDA0

SCL0

(TC3)P31

(RXIN)P30

P20

RESET

XOUT

XIN

TEST

0SC2

0SC1

VD

HD

Y/BL

I

IO

O

I

I

I

I

O

I

I

O

I

I

I

O

O

B

O

G

O

R

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

ACP

NC

GND

SDA1

SCL1

SYNC AV1

RMT IN

SW IN

RESET

XOUT

XIN

TEST

0SC1

0SC2

VSYNC

HSYNC

Ys

BOUT

GOUT

ROUT

IIC BUS

Fig. 3-2

27

Page 28

<< MICROCOMPUTER TERMINAL NAME AND OPERATION LOGIC >>

No. Terminal Name Function In/Out Logic Remarks

1 GND 0V

2 BAL INPUT BALANCE Out PWM out

3 REM OUT REMOTE CONTROL Out Remote control output

SIGNAL OUT

4 MUTE SOUND MUTE OUT Out Sound mute output

5 SP MUTE SPEAKER MUTE Out In muting = H

6 DEF POW Out

7 POWER POWER ON/OFF OUT Out Power control In ON=H

8 LED POWER LED OUTPUT Out Power LED on-control

LED lighting=L

9 POWER LNB Out 0V

10 LNB DET In 0V

11 SCL() IIC BUS CLOCK OUT Out IIC bus clock output 0

12 SDA() IIC BUS DATA IN/OUT In/Out IIC bus data input/output 0

13 SYNC VCD H SYNC INPUT In Main picture H. sync signal input

14

15 AFT2 IN In Sub tuner AFT S-curve input

16 AFT1 UV MAIN S-CURVE In Main tuner AFT S-curve

SIGNAL signal input

17 KEY A LOCAL KEY INPUT In Local key detection: 0 to 5V

18 KEY B LOCAL KEY INPUT In Local key detection: 0 to 5V

19 SGV TEST SIGNAL OUT Out Test signal output In normal=L 0V

20 SGA TEST AUDIO OUT Out Test audio output In normal=L 0V

21 VSS POWER GROUNDING — 0V: Gounding voltage 0V

22 R R Out At display on:Pulse

23 G G Out At dispaly on:Pulse

24 B B Out At dispaly on:Pulse

25 Y/BL BL Out At dispaly on:Pulse

26 HSYNC In HSYNC for OSD display Pulse

27 VSYNC In VSYNC for OSD display Pulse

28 OSC1 DISPLAY CLOCK Out 4.5MHz Pulse

29 OSC2 DISPLAY CLOCK In Pulse

30 TEST TEST MODE In GND fixed 0V

31 XIN SYSTEM CLOCK In System clock input 8MHz pulse

32 XOUT SYSTEM CLOCK Out System clock output 8MHz 8MHz pulse

33 RESET SYSTEM RESET In System reset input (In reset=L) 5V

34 SW IN

35 RMT IN REMOTE CONTROL IN In remote control pulse input=L In reception of

SIGNAL INPUT remote pulse

36 SYNC AV1 HSYNC INPUT In External H. sync signal input Pulse

37 SCL1 IIC BUS CLOCK OUT Out IIC bus clock output 1 Pulse

38 SDA1 IIC BUS DATA IN/OUT In/Out IIC bus data input/output 1 Pulse

39 GND 0V

40 NC

41 ACP NSYNC INPUT In AC pulse input

42 VDD POWER — 5V 5V

28

Page 29

5. EEPROM (QA02)

EEPROM (Non volatile memory) has function which, in spite of power-off, memorizes the such condition as channel selecting

data, last memory status, user control and digital processor data. The capacity of EEPROM is 8k bits. Type name is 24LC04BI/

P or ST24C04CB6, and those are the same in pin allocation and function, and are exchangeable each other. This IC controls

through I2C bus. The power supply of EEPROM and MICOM is common. Pin function of EEPROM is shown in Figure 3-3.

EEPROM(QA02)

1

Device adress

GND

A0

A1

A2

Vss

2

3

4

Fig. 3-3

8

7

6

5

Vcc + 5V

NC

SCL

SDA

2

C-BUS line

I

6. ON SCREEN FUNCTION

ON SCREEN FUNCTION indicates data like channel, volume. Formerly, exclusive use of OSD IC was used, but in N5SS,

OSD function is involved in microcomputer. Pin function concerning on-screen is shown in figure 3-4. Oscillation clock of OSD

is approx. 4.5MHz. 9MHz which becomes twice in microcomputer is dot clock. For oscillation coil, TRF1160D (LA02) is used.

QA01

OSC2

OSC1

VD

HD

Y/BL

O

29

OSC2 OSC OUT

I

28

OSC1 OSC IN

I

27

VSYNC H. SYNC SIGNAL

I

26

HSYNC V. SYNC SIGNAL

O

25

Ys/Ym HALF TONE SIGNAL

B

O

G

O

R

O

BOUT

24

23

GOUT COLOR SIGNAL

22

ROUT

G

V

Fig. 3-4

29

Page 30

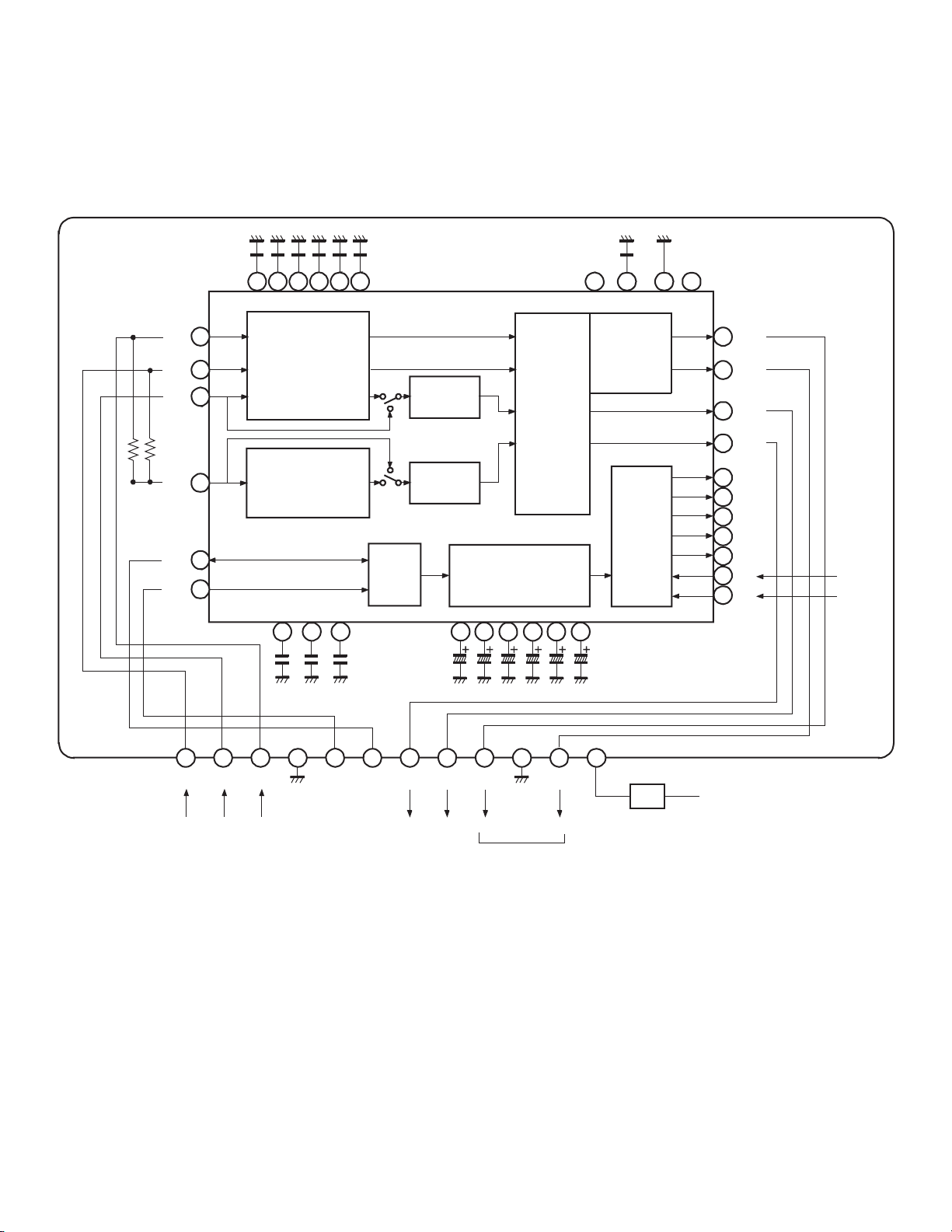

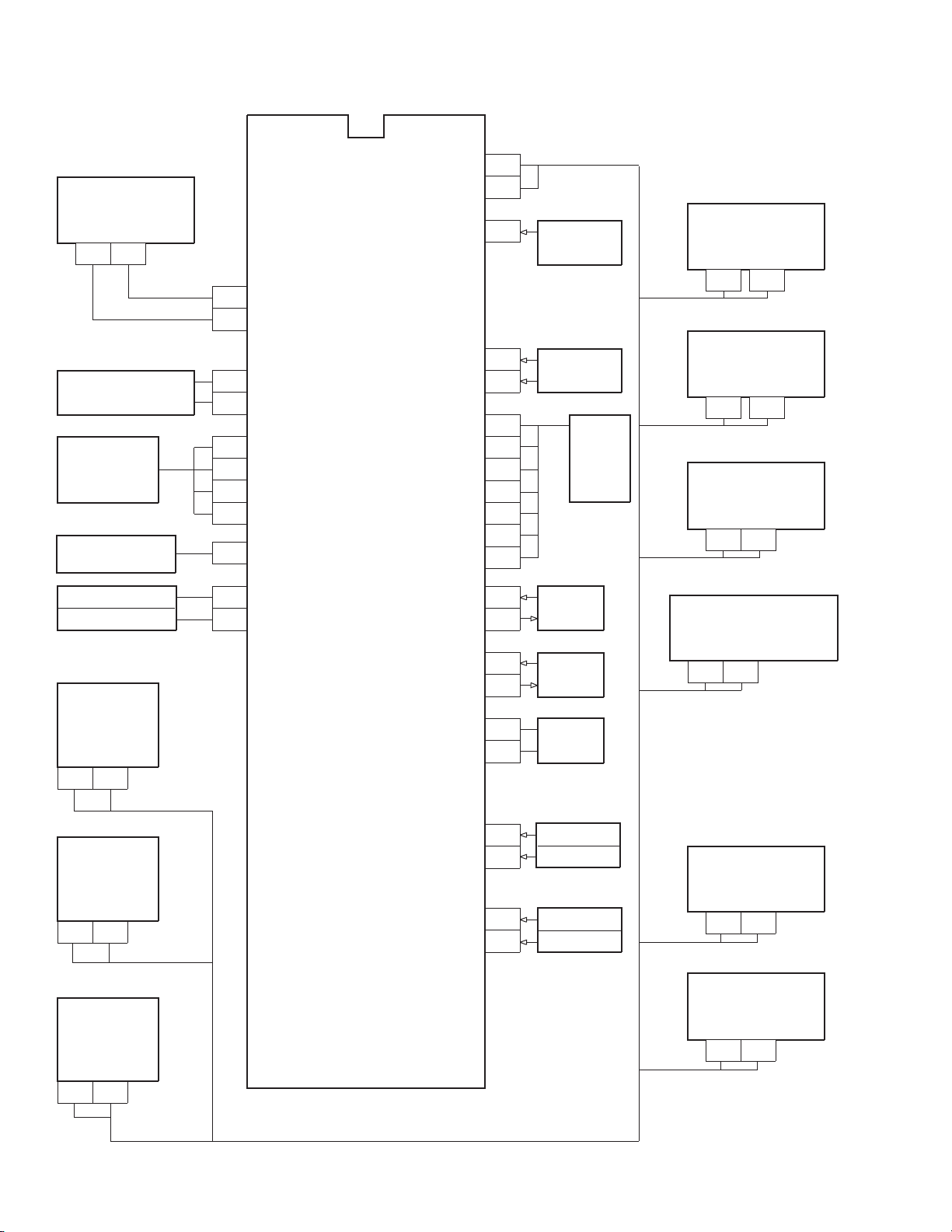

7. SYSTEM BLOCK DIAGRAM

TMP87CS38N-3152

QA01

QA02

MEMORY

24LC04B1/P

SDA SCL

5 6

H. SYNC PULSE

VSYNC PULSE

VIDEO SIGNAL

PROCESS

CIRCUIT

REMOTE CONTROL

OUTPUT

SOUND MUTE

SPEAKER MUTE

Q701

C/C, EDS

XC144144P

DATA CLK

11

12

26

27

22

23

24

25

3

4

5

SCL 0

SDA 0

HSYNC

VSYNC

R

G

B

YS/TM

RMT OUT

MUTE

SP MUTE

SDA 1

SCL 1

RMT

KEY-A

KEY-B

RST

VDD

GND

VSS

POWER

ACP

LED

XIN

XOUT

OSCI

OSCO

SGV

SGA

38

37

35

17

18

33

42

21

41

31

32

28

29

19

20

1

7

8

REMOTE

SENSOR

UNIT

KEY SWITCH

POWER

SUPPLY

CIRCUIT

8MHz

CLOCK

6.1MHz

CLOCK

SIGNAL

OUTPUT

H001

MAIN U/V TUNER

EL446L

SDA SCL

HY01

SUB U/V TUNER

EL922L

SDA SCL

Q501

VCD

TA1222

SDA SCL

27 28

H002

IF/MPX

MVUS345

SDA SCL

21 20

DPC UNIT

DATA CLK

QY04

PIP CONTROL

DATA CLK

6 5

SYNC-AV1

AFT1 IN

SYCN-AV2

AFT2 IN

36

16

13

Fig. 3-5

30

MAIN SCREEN

SUB SCREEN

2

SYNC DET.

AFT DET.

SYNC DET.

AFT DET.

QV01

AV SW

TA1219N

SDA SCL

26 27

QM01

DSP

SDA SCL

Page 31

8. LOCAL KEY DETECTION METHOD

15 16

S15-1

S16-1

Local key detection in the N5SS chassis is carried out by

using analog like method which detects

a voltage appears at local key input terminals (pins 17, 18) of

the microcomputer when a key is

pushed. With this method using two local key input terminals

( pins 17,18), key detection up to

maximum 14 keys will be carried out.

S15-2

S15-3

S15-4

S15-5

S15-6

S15-7

Fig. 3-6. Local key assignment

S16-2

S16-3

S16-4

S16-5

S16-6

S16-7

The circuit diagram shown left is the local key circuit. As can

be seen from the diagram, when

one of key among SA-01 to SA-08 is pressed, each of two

input terminal (pins 17, 18) developes

a voltage Vin corresponding to the key pressed. (The voltage

measurement and key identification

are carried out by an A/D converter inside the microcomputer

and the software.

Key No. Function Key No. Function

SA-02 POWER SA-01

DEMO START/STOP

SA-03 CH UP

SA-04 CH DN

SA-05 VOL UP

SA-06 VOL DN

SA-07 ANT/VIDEO, ADV

SA-08 MENU

Table 3-1. Local key assinment

31

Page 32

9. REMOTE CONTROL CODE ASSIGNMENT

Custom codes are 40-BFH

Code

00H 0 Channel

01H 1 Channel

02H 2 Channel

03H 3 Channel

04H 4 Channel

05H 5 Channel

06H 6 Channel

07H 6 Channel

08H 8 Channel

09H 8 Channel

0AH 100 Channel

0BH ANT 1/2

0CH RESET

0DH AUDIO

0EH PICTURE/FUNC

0FH TV/VIDEO

10H MUTE

11H CHANNEL SEARCH

12H POWER

13H MTS

14H ADD/ERASE

15H TIMER/CLOCK

16H AUTO PROGRAM

17H CHANNEL RETURN

18H DSP/SUR (TV/CATV)

19H CONTROL UP

1AH VOLUME UP

1BH CHANNEL UP

1CH RECALL

1DH CONTROL DOWN

1EH VOLUME DOWN

1FH CHANNEL DOWN

40H PIP LOCATE

41H PIP LOCATE

42H PIP LOCATE

43H PIP LOCATE

44H CARVER

45H SURROUND UP

46H SURROUND DOWN

47H VOCAL ZOOM

48H CHANNEL LOCK

49H

4AH PIP CHANNEL UP

4BH

4CH

4DH

4EH PIP LOCATE

4FH PIP SOURCE

Function to remote

PIP CHANNEL DOWN

PIP STILL/RELEASE

PIP ZOOM, ZOOM SIZE

Applicable

control

Applicable Conti-

to TV set nuty

Custom codes are 40-BFH

Code

50H PIP STILL

51H PIP ON/OFF

52H Do not use. Old type core power ON

53H PIP SWAP

54H PIC SIZE

55H DSP F/R

56H WIDE/SCROLL

57H CAPTION

58H EXIT

59H CYCLONE, SBS

5AH SER UP

5BH OPTION

5CH SUB WOOFER UP

5DH

SUB WOOFER DOWN

5EH

5FH

80H MENU

81H EDS

82H ADV UP

83H ADV DWN

84H

85H

86H

87H

88H PIP CONTROL

89H

8AH

8BH

8CH

8DH

8EH

8FH

90H

91H

92H

93H

94H Do not use. Old type core power ON

95H

96H

97H NOISE CLEAN

98H

99H

9AH PIP VOLUME UP

9BH

9CH PIP CONTROL

9DH

9EH

PIP VOLUME DOWN

9FH

Function to remote

Applicable

control

Applicable Conti-

to TV set nuty

32

Page 33

Custom codes are 40-BFH

Code

Function to remote

Applicable

control

C0H

C1H

C2H

C3H

C4H PIP LOCATE

C5H PIP LOCATE

C6H PIP LOCATE

C7H PIP LOCATE

C8H PIP STROBE

C9H PIP STROBE SPEED

CAH

PIP CHANNEL SEARCH

CBH

CCH

CDH

CEH

DFH

D0H

D1H

D2H Do not use. Old type core power ON

D3H

D4H

D5H

D6H

D7H PIP VIDEO ADJ.

D8H

STILL, FRAME ADVANCE

D9H

DAH SPEED

DBH

DCH ZOOM

DDH

DEH

DFH

Applicable Conti-

to TV set nuty

Custom codes are 40-BFH

Code Applicable Conti-

A0H

SUB-BRIGHT ADJUSTMENT

A1H

G. DRIVE ADJUSTMENT

A2H

B. DRIVE ADJUSTMENT

Function

to TV set nuty

A3H

A4H

CUTOFF DRIVE 40H INITIALIZING, HORIZONTAL ONE LINE

A5H R. CUTOFF ADJUSTMENT

A6H G. CUTOFF ADJUSTMENT

A7H B. CUTOFF ADJUSTMENT

A8H

MEMORY ALL AREA INITIALIZE

A9H PIP BRIGHT ADJUSTMENT

AAH

SUB CONTRAST ADJUSTMENT

ABH

HOR, VER PICTURE POSITON ADJUSTMENT

ACH SUB COLOR ADJUSTMENT

ADH SUB TINT ADJUSTMNET

AEH ADJUSTMENT-UP

AFH ADJUSTMENT-DOWN

B0H

HORIZONTAL ONE LINE: SERVICE

B1H DSP ON/OFF

B2H TEXT-1

B3H

TV/PIP VIDEO CHANGE-OVER

B4H CAPTION-1

B5H

B6H

B7H

TV/CABLE CHANGE-OVER IN SAME TIME ON MAN AND SUB

B8H HOTEL SETTING MENU

B9H DATA 4 TIMES SPEED UP

BAH DATA 4 TIMES SPEED DOWN

BBH

CHANGE-OVER OF HOTEL/NORMAL

BCH PIP CENTER

BDH M MODE

BEH CAPTON OFF

BFH ALL CHANNEL PRESET

33

Page 34

Custom codes are 40-BFH

Code Applicable Conti-

E0H

PINCUTION/EW CORER (PARA/CNR)

E1H

VERTICAL S-CUVE CORRECTION/VERTICAL M-CURVE CORRECTION (VSC/FVC)

Function

to TV set nuty

E2H

E3H

E4H

E5H

E6H

E7H

E8H

E9H

EAH

HORIZONTAL WIDTH (WID/PARA)

EBH

TRAPEZOIDE CORRECTION (TRAP)

ECH TEST TONE

EDH DOLBY

EEH

3 DIMENTIONAL Y/C SEPARATION

EFH DPC

E0H

STANDARD (HEIGHT LINEARITY) (VLIN/HIT)

E1H

WIDE (HEIGHT LINEARITY) (VLIN)

F2H SCROOL

F3H

WIDE 1, 2, 3

F4H

F5H

F6H

F7H

F8H

F9H

FAH

FBH

FCH

FDH

FEH

FFH

34

Page 35

10. ENTERING TO SERVICE MODE

12. SERVICE ADJUSTMENT

1. PROCEDURE

(1) Press once MUTE key of remote hand unit to

indicate MUTE on screen.

(2) Press again MUTE key of remote hand unit to keep

pressing until the next procedure.

(3) In the status of above (2), wait for disappearing of

indication on screen.

(4) In the status of above (3), press MENU (Channel

setting) key on TV set.

2. Service mode is not memorized as the last-memory.

3. During service mode, indication S is displayed at upper

right corner on screen.

11. TEST SIGNAL SELECTION

1. In OFF state of test signal, SGA terminal (Pin 20) and

SGV terminal (Pin 21) are kept “L” condition.

2. The function of VIDEO test signal selection is cyclically

changed with VIDEO key (remote unit).

Test Signal No. Name of Pattern

0 Signal OFF

1 All black signal + R single color (OSD)

2 All black signal + G single color (OSD)

3 All black signal + B single color (OSD)

4 All black signal

5 All white signal

6 W/B

7 Black cross bar

8 White cross bar

9 Black cross hatch

10 White cross hatch

11 White cross dot

12 Black cross dot

13 H signal (bright area)

14 H signal (dark area)

15 Black cross + G

1. ADJUSTMENT MENU INDICATION ON/OFF :

MENU key ( on TV set)

2. During display of adjustment menu, the followings are

effective.

a) Selection of adjustment item :

POS UP/DN key (on TV/remote unit)

b) Adjustment of each item :

VOL UP/ DN key (on TV / remote unit)

c) Direct selection of adjustment item

R CUTOFF : 1 POS (remote unit)

G CUTOFF : 2 POS (remote unit)

B CUTOFF : 3 POS (remote unit)

d) Data setting for PC unit adjustment

SUB CONTRAST : 4 POS (remote unit)

SUB COLOR : 5 POS (remote unit)

SUB TINT : 6 POS (remote unit)

e) Horizontal line ON/OFF : VIDEO (TV)

f) Test signal selection : VIDEO (remote unit)

* In service mode, serviceable items are limited.

3. Test audio signal ON / OFF : 8 POS (remote unit)

* Test audio signal : 1kHz

4. Self check display : 9 POS (remote unit)

* Cyclic display (including ON/OFF)

5. Initialization of memory :

CALL (remote unit) + POS UP (TV)

6. Initialization of self check data :

CALL (remote unit) + POS DN (TV)

7. BUS OFF :

CALL (remote unit) + VOL UP (TV)

(3) SGA (audio test signal) output should be square

wave of 1kHz.

35

Page 36

13. FAILURE DIAGNOSIS PROCEDURE

Model of N5SS chassis is equipped with self diagnosis function inside for trouble shooting.

1. CONTENTS TO BE CONFIRMED BY CUSTOMER

Contents of self diagnosis Display items and actual operation

A. DISPLAY OF FAILURE INFORMATION Power indicator lamp blinks and picture does not come.

IN NO PICTURE

(Condition of display)

1. When power protection circuit operates; 1.

2. When I2C-BUS line is shorted; 2. Power indicator red lamp blinks. (1 seconds interval)

2. CONTENTS TO BE CONFIRMED IN SERVICE WORK (Check in self diagnosis mode)

Contents of self diagnosis Display items and actual operation

Contents of self diagnosis Display items and actual operation

<Countermeasure in case that phenomenon

always arises.>

B.Detection of shortage in BUS line (Example of screen display)

C.Check of comunication status in BUS line

D.Check of signal line by sync signal detection

E. Indication of part code of microcom.(QA01)

F. Number of operation of power protection circuit

Power indicator red lamp blinks. (0.5 seconds interval)

If these indication appears, repairing work is required.

SELF CHECK

No. 2390XXXX Part code of QA01

POWER : 000000 Number of operation of

power protection circuit

BUS LINE : OK Short check of bus line

BUS CONT : OK Comunication check of

busline

BLOCK : UV V1 V2

QV01, QV01S

E

F

B

C

D

Fig. 2-4

3. EXECUTING SELF DIAGNOSIS FUNCTION

[CAUTION]

(1) When executing block diagnosis, get the desired input mode (U/V BS VIDEO1,2,3) screen, and then enter the self diagnosis

mode.

(2) When diagnos other input mode, do again diagnosis operation.

(PROCEDURE)

(1) Set to service mode.

(2) Pressing “9” key on remote unit displays self diagnosis result on screen.

Every pressing changes mode as below.

SERVICE mode SELF DIAGNOSIS mode

(3) To exit from service mode, turn power off.

36

Page 37

4. UNDERSTANDING SELF DIAGNOSIS INDICATION

In case that phenomenon always arises. See figure 3-4 .

Item Contents Instruction of results

BUS LINE Detection of bus line short Indication of OK for normal result, NG for abnormal

Indication of OK for normal result

Indication of failure place in abnormality

(Failure place to be indicated)

QA02 NG, H001 NG, Q501 NG, H002 NG

QV01 NG, Q302 NG, QY02 NG, HY01 NG

QD04 NG, QM01 NG, Q701 NG

BUS CONT Communication state of bus line Note 1. The indication of failure place is only one place

though failure places are plural. When repair of a

failure place finishes, the next failure place is indi

cated. (The order of priority of indication is left side.)

BLOCK:BS The sync signal part in *Indication by color

UV1 each video signal supplied from • Normal block : Green

UV2 each block is detected. • Non diagnosis block : Cyan

V1 Then by checking the existence or

V2 non of sync part, the result of self

diagnosis is displayed on screen.

Besides, when “9” key on remote

unit is pressed,diagnosis operation

is first executed once.

<Clearing method of self diagnosis result>

In the error count state of screen, press “CHANNEL DOWN” button on TV set pressing “DISPLAY” button on

remote unit.

[CAUTION]

All ways keep the following caution, in the state of

service mode screen.

• Do not press “CHANNEL UP” button. This will cause

initialization of memory IC. (Replacement of memory IC is

required.

• Do not initialize self diagnosis result. This will change user

adjusting contents to factory setting value. ( Adjustment is

required.)

White

Yellow

Cyan

Green

Magenta

Red

Blue

( COLOR BAR SIGNAL)

Color elements are positioned in sequence of high brightness.

<Method utilizing inner signal> (VIDEO INPUT 1 terminal should be open.)

(1) With service mode screen, press VIDEO button on remote unit. If inner video signal can be received, QV01 and after are normal.

(2) With service mode screen, press “8” button on remote unit. If sound of 1kHz can be heard, QV01 and after are normal.

* By utilizing signal of VIDEO input terminal, each circuit can be checked. (Composite video signal, audio signal)

37

Page 38

14. TROUBLE SHOOTING CHART

(1) TV DOES NOT TURNED ON

TV does not turned on.

Relay sound

YES

NO

Check of voltage at pin 7 of QA01

(DC 5V).

OK

8MHz oscillation waveform

at pin 32 of QA01.

OK

Pulse output at pins 37 and 38 of QA01.

OK

NG

NG

Check power circuit.

Check OSC circuit.

Replace QA01.

NG

Voltage check at pin 32 of QA01

(DC 5V)

NG

Check reset circuit.

OK

Check relay driving circuit.

Replace QA01.

38

Page 39

(2) NO ACCEPTION OF KEY-IN

Key on TV

Voltage change at pins 17, 18 of

QA01 (5V to 0V).

OK

Replace QA01.

Remote unit key

Pulse input at pin 35 of QA01,

When remote unit key is pressed.

OK

Replace QA01

(3) NO PICTURE (SNOW NOISE)

NG

Check key-in circuit.

NG

Check tuner power circuit.

No picture

Voltage at pins of +5V, and 32V.

OK

Check H001. Check tuner power circuit.

NG

39

Page 40

(4) MEMORY CIRCUIT CHECK

Memory circuit check

Voltage check at pin 8 of QA02 (5V).

NG

Pulse input at pins 5 and 6 of QA02

in memorizing operation.

Replace QA02.

Adjust items of TV set adjustment.

(5) NO INDICATION ON SCREEN

No indication on screen.

OK

NG

OK

Note: Use replacement parts for QA02.

Check power circuit.

Check QA01.

Check of character signal at pin 23

of QA01. (5V

Input of OSC waveform at pin 29 of QA01

with indication key pressed.

Check of sync signal at pins 26, 27 of QA01.

Replace QA01.

)

P-P

OK

OK

OK

NG

Check V/C/D circuit.

NG

Check OSC circuit.

Check sync circuit.

40

Page 41

SECTION IV

AUDIO OUTPUT CIRCUIT

41

Page 42

1. OUTLINE

Configuration of the audio circuit and signal flow are given

in Fig 4-1.

A/V PCB

VIF+MTS+S.PRO

MODULE

12

R

14

L

EQ

ER

ICV01

R

6

MOTHER

TV

L

7

CHILD

TV

29

L

31

R

FOR PIP

IF MODULE

AUDIO

VIDEO 1

VIDEO 2

VIDEO 3

(FRONT INPUT)

R L

R L

R L

2

L

L

11

VIDEO 1

13

R

3

L

VIDEO 2

9

R

L

15

VIDEO 3

17

R

VARIABLE

AUDIO OUTPUT

TERMINAL

R

R

L

1

OUTPUT

TERMINAL

35

37

VIDEO

RL

AS

AR

L

PIP OUT

(AUDIO)

R

VIF+MTS+A.PRO

Q670

MODULE

R out

DSP

CIRCUIT

PIP

OUTPUT

AI

AJ

16

18

25

R

L out

24

L

W out

22

R

2

12

L

W

2

4

1

11

R

L

W

Fig. 4-1

42

Page 43

2. AUDIO OUT IC

2-1. OUTLINE

In the model, CN32E90, the main amplifiers and woofer

output amplifiers use bipolar IC TA8256H and develop out

powers of 10W x 2+13W.

2-2. THORY OF OPERATION

2-2-1. Operatin of TA8256H

The TA8256H is a modified version of TA8128AH used in

the N4SS chassis as an audio ouput IC. In the TA8256H, one

channel is added and a total of 3 channels can be used, but

performance for each channel is the same as that of the

TA8218H. Fig. 4-2 shows a block diagram of the IC.

47mF

4

L

3

PRE

GND

2

RIPPLE FILTER

4k

30k

350W

350W

4k

30k

1mF

L

47mF

F

1m

R

R

69

Vcc

OUTPUT-2

AMP-2

POW

GND

(R)

AMP-3

OUTPUT-3

10

12

8

5

(mute)

2.2W

0.12mF

0.12mF

2.2W

470mF

470mF

Vcc

25.5V

(L)

R

L

R

(R)

L

MUTING

7

11

(S) or (W)

1mF

W

1

W

4k

350W

30k

OUTPUT-3

AMP-1

20kW

(mute Tc)

2.2W

0.12mF

1000mF

(W)

R

L

Fig. 4-2

43

Page 44

SECTION V

A/V SWITCHING CIRCUIT

44

Page 45

1. OUTLINE

A/V switching circuit performs change-over of video and

audio signals from tuner and external input. The selecting

operation is controlled by microcomputer through IIC bus.

2. IN / OUT TERMINALS

INNER INPUT U/V Tuner (Main)

U/V Tuner (Sub) .................................. For sub picture (PIP)

EXTERNAL INPUT VIDEO1 With S-terminal

VIDEO2

VIDEO3 (Front) With S-terminal........ Excepting CF35E50, CL37E56, CE35E15

VIDEO3 (Back) .................................. Only for CF35E50, CL37E56, CE35E15

OUTPUT VIDEO OUTPUT (V, L, R) .................... Excepting CN27E90

AUDIO ON SUB-PICTURE ................... Only for CN32E90, CN35E90, CN35E95

3. CIRCUIT OPERATION

This circuit consists of A/V SW IC; TA1218N (QV01), and

selects signals from U/V tuner (Main), U/V tuner (Sub),

E1, E2 and E3.

3-1 COMPOSITE VIDEO SIGNAL

The selected video signal is output to pin 38 of QV01, and

separated by comb filter into Y and C. The resulted signal

is input to pins 30 and 32 of QV01, and is output to pins 36

and 34 to be supplied to Q501 (V/C/D).

Video signal for sub picture is output to pin 42 of QV01, and

is supplied to PIP unit (ZY01).

3-2 S-VIDEO SIGNAL

When a cable is connected to S-VIDEO terminal, inner

switch of S-VIDEO terminal is shorted to ground to turn off

the transistor (QV05 for VIDEO1 input) for S-VIDEO

terminal detection. Then chroma input terminal (Pin 14 for

VIDEO1 input) of QV01 turns open. From pins 36 and 34

(Y/C output) of QV01, Y/C signal of selected source is

output.

45

Page 46

AV SW CIRCUIT

VIDEO 3

VIDEO 1

VIDEO 2

TUNR/IMA

L/R V out

EQ

18

17

16

15

14

13

12

11

10

TIF

V Aout

QV01 TA1218N

C in

Y in

C in

26

28

29

30

31

32

34

35

R in

S in

L in

C in

R in

S in

L in

V in

R in

9

L in

8

SYNC OUT

PIP TV in

PIP L in

PIP R in

C out

R out

DSP

L/R in

QA01

SYNC in

COMB

FILTER

Y out

V in

C out

C in

Q501

PIP AUDIO

OUT

MONITOR

OUT

7

6

5

2

1

V in

R in

L in

PIP R out

PIP L out

Fig. 5-1

Y out

L out

H out

PIP V out

42

36

37

38

Y in

PIP

V in

46

Page 47

SECTION VI

VIDEO PROCESSING CIRCUIT

47

Page 48

1. OUTLINE

This circuit converts and amplifies video signal (Luminance

and chroma signals) separated into Y/C, to original color

signal, and is supplied to CRT Drive circuit.

2. SIGNAL FLOW

Signal flow chart is shown in fig. 6-2 Block diagram.

(1) Luminance signal is input to pin 15 of Q501, and enters

into delayline inside Q501 to be output to pin 4.

(2) Chroma signal is input to pin 13, and I/Q signal which

is demodulated in color, is output to pins 5 and 6, and

next supplied to pins 51 and 52.

(3) The signal is processed on luminance and chroma

signals, and is converted to original color signal (R,G,B)

by RGB matrix. Next the signal is superimposed with

OSD signal to be output to pins 41, 42 and 43, and is

supplied to CRT Drive circuit.

(4) The signal for Scan Modulation is processed with

differential in Q501 to be output to pin 48 Besides, at

terminal for adjustment TP501, luminance and chroma

signals are automatically output according to the selected

items of service mode.

3. CIRCUIT OPERATION

All processing operation of video signal are done inside

Q501. The outline of Q501 (TA1222N) is explained in the

next section. Here, major terminals excepting input/output

terminals of Q501 are described.

48

Page 49

Terminals concerning Video / Chroma circuit of Q501 are explained here.

# 1 CW OUTPUT 3.58MHz which is synchronized to burst signal is output, and is used for clock of comb filter.

# 2 SCP OUTPUT The signal which is superimposed with burst gate pulse and blanking pulse is output. It is not

used in this time.

# 3 SECAM CONTROL When receiving SECAM (Color system of East Europe) signal, it produces DC output. It is not

used in this time.

# 4 Y1 OUTPUT Luminance signal of Y1 input (# 15) is output through delay line.

# 5 Q OUTPUT Chroma signal of #13 is demodulated in IQ, and Q signal is output.

# 6 I OUTPUT I signal of those of IQ demodulated is output.

# 7 1H DL CONTROL Color demodulation control signal of PAL, SECAM system (European color system) is output.

It is not used in this time.

# 8 XTAL 3 Crystal oscillator terminal. Not used.

# 9 XTAL 2 Ditto

# 10 XTAL 1 3.58MHz crystal oscillation terminal.

# 11 APC FILTER Color sync. phase detecting terminal.

# 12 Vcc 1 5V source (chroma line) terminal

# 13 C INPUT Color signal input terminal

# 14 GND Grounding terminal of chroma circuit

# 15 Y1 INPUT Luminance signal input terminal

# 32 PIP Ys Input terminal for switching pulse signal of PIP signal

# 33 PIP B Input terminal of PIP RGB signal

# 34 PIP G Ditto

# 35 PIP R Ditto

# 36 OSD Ys Input terminal for switching pulse signal of OSD signal

# 37 OSD B Input terminal for OSD RGB signal

# 38 OSD G Ditto

# 39 OSD R Ditto

# 40 Vcc 2 +9V source terminal

# 41 B OUTPUT RGB output terminal

# 42 G OUTPUT Ditto

# 43 R OUTPUT Ditto

# 44 GND Ground terminal of Y, color difference, RGB circuits

# 45 ABL Input terminal for ABL control

# 46 Vcc 3 +9V source terminal

# 47 Ym Input terminal for half tone control pulse which is supplied from

microcomputer

# 48 VSM Output terminal of velocity modulation signal

# 49 APL DET Detects average level of video signal for correcting DC transmission

# 50 BLACK DET Detects black area in video signal for black expanding circuit

# 51 I INPUT Input signal for I signal of IQ demodulation signal

# 52 Q INPUT Input signal for Q signal of IQ demodulation signal

# 53 Y2 INPUT Input terminal for Y-picture control circuit

# 54 COL Terminal for peak hold of color limiter

# 55 DAC 1 Test point (TP501) output terminal

# 56 DAC 2 External circuit control terminal (Not used)

49

Page 50

TO COMB

0.6V

(P)

1V

(P-P)

CW OUTPUT

1

COLOR IDENT. OUTPUT

2

SCP OUTPUT

SECAM CONTROL

3

Y1 OUTPUT

4

Q OUTPUT

56

I OUTPUT

DAC 2 (2bit)

DAC 1 (1bit)

MONITOR OUTPUT

COLOR LIMITER

Y2 INPUT

Q INPUT

I INPUT

56

55 54 53

52

51

1V

(P)

300mV

(P)

1V

(P)

1V

(P)

or

N

300mV

(P)

4.43

M 3.58

pull

or R

1H DL CONTROL

7

XTAL 3

8

XTAL 2

9

10 11 12

XTAL 1

APC FILTER

Vcc 1 (+5V)

13

CHROMA INPUT

14 15

CHROMA GND

Y1 INPUT

16

V. SEP.

17

SYNC INPUT

18

SYNC OUTPUT

19 20

DEF GND

AFC 1

32 x F

21

H

BLACK PEAK HOLD

APL DET.

VSM OUTPUT

Ym INPUT

POWER OFF INPUT

Vcc 3

ABL INPUT

Y, COLOR DIFFERENCE,

RGB GND

R OUTPUT

G OUTPUT

B OUTPUT

Vcc 2 (+9V)

R ANALOG OSD INPUT

G ANALOG OSD INPUT

B ANALOG OSD INPUT

Ys ANALOG OSD INPUT

50 49

48

47

46

45 44

43 42

41

40 39

38

37

36

2.5V

2.8V

(P)(typ)

(P)(typ)

from OSD

0.5V

(P)(typ)

m

Com

+B

<SCL>

<5V

22 23 24 25

DEF Vcc (+9V)

H. OUT

BENDING CORRECT

AFC PULSE INPUT

7.5V

7.5V(AFC)

1.0V(DIR)

BLK INPUT

26

DIGITAL GND

27 28

SDA

EXTERNAL BPP INPUT

SCL

<SDA>

V

peak to peak.

(P)

denotes value of

Fig. 6-1 TA1222N VCD IC PIN LAYOUT CHART

50

R INPUT

G INPUT

B INPUT

Ys INPUT

VP OUTPUT

HD OUTPUT

DAC GND

35

34

33 32

31

30

29

8H

from PIP/TEXT 0.5V

(P)(typ)

1yb

Page 51

VELOCITY

MODULATION

CRT DRIVE

48

51

42

SW

RGB

RGB

MATRIX

41

LUMINANCE

43

PROCESSING

COLOR SIGNAL

SIGNAL

PROCESSING

47

36

37

OSD

R G B Ys Ym

39 38

553123

TP501

Microcomputer OSD

or EDS or C.C

52

53

4

SYNC/DEF

PROCESSING

6

LINE

5

Q I Y Y I/Q VM

COLOR

DEMOD.

C

13

DELAY

Y

15

Sync

17

Y

From A/V Board C

Fig. 6-2 Block diagram of Video Processing circuit

51

H.OUT VP

Q501 V/C/D

Page 52

SECTION VII

V/C/D/IC

52

Page 53

1. OUTLINE