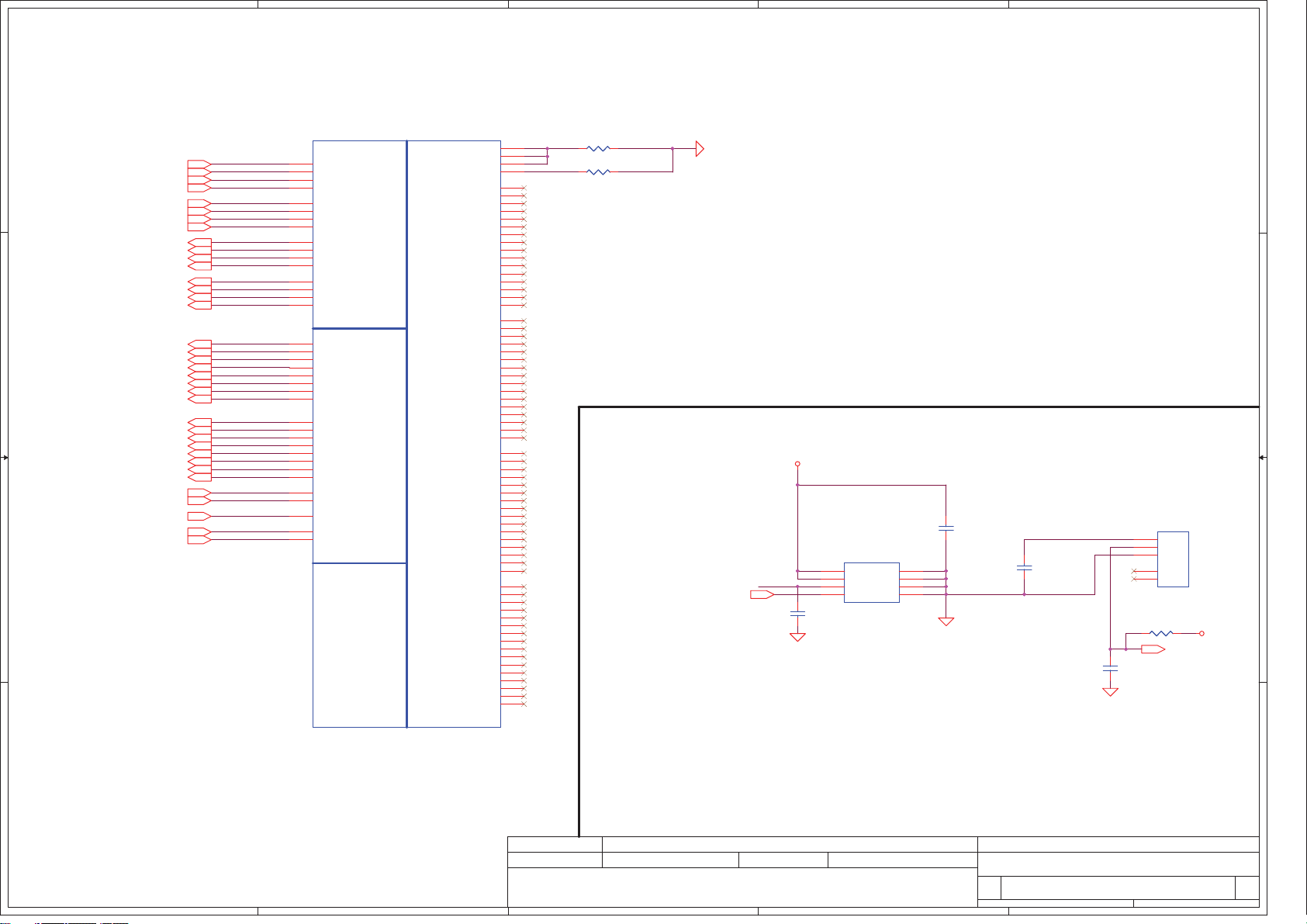

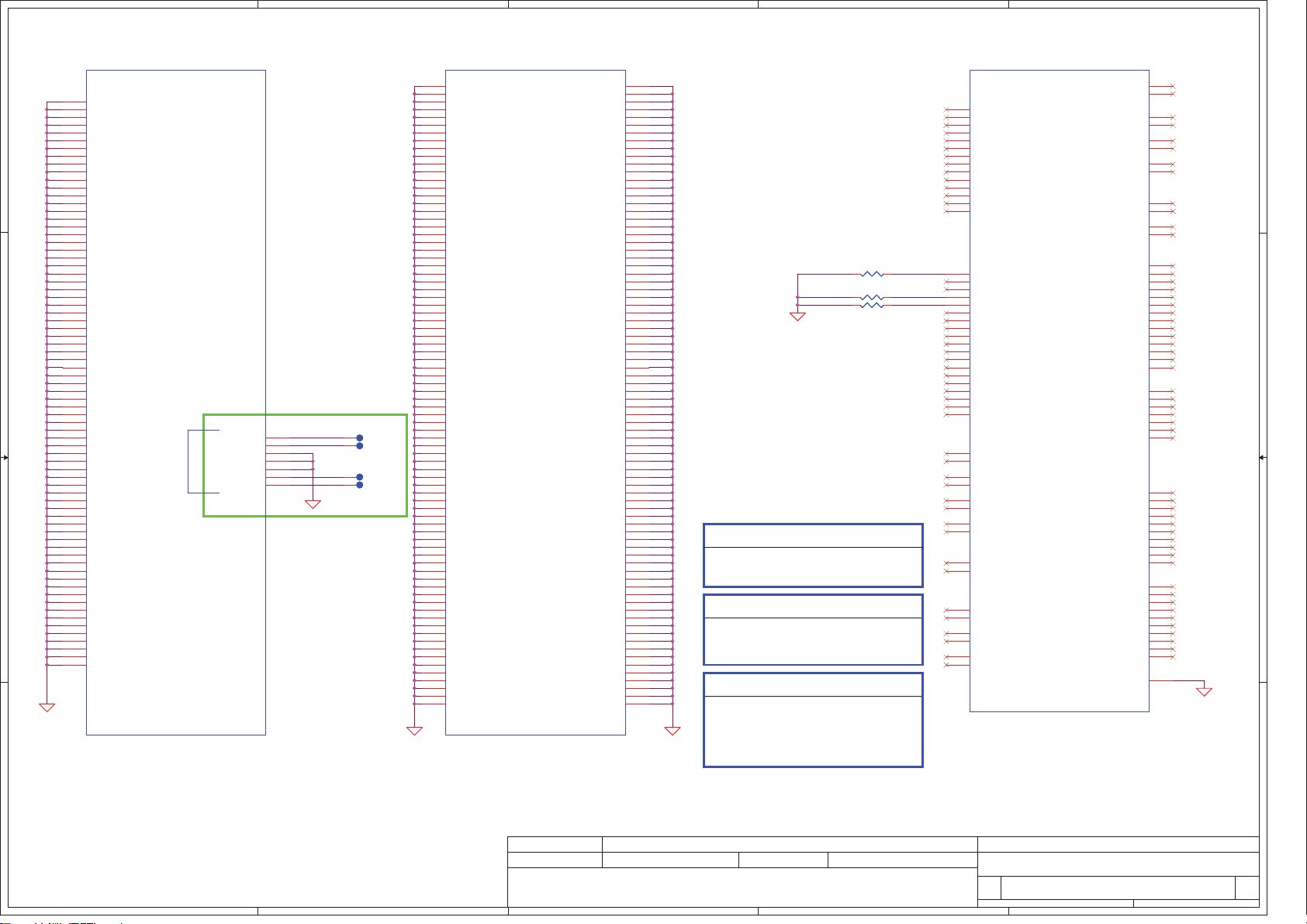

Toshiba C660 Schematics

A

1 1

B

C

D

E

PWWAA

2 2

LC Marseille

LA-6842P SchematicREV 0.2

3 3

4 4

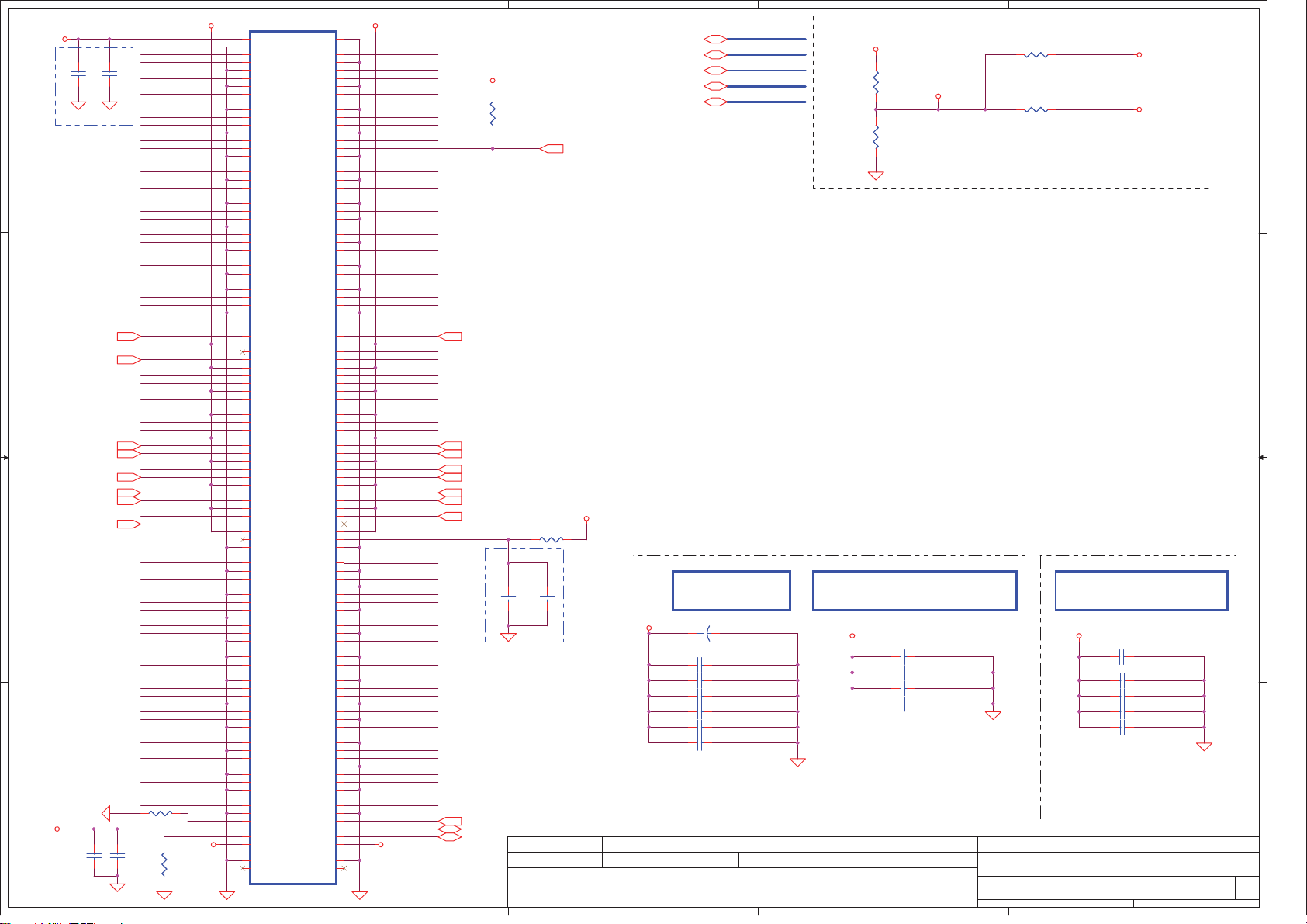

Intel Processor(ARD) /PCH(HM55)

2010-07-22 Rev 0.2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

http://laptop-motherboard-schematic.blogspot.com/

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/21 2011/06/21

2010/06/21 2011/06/21

2010/06/21 2011/06/21

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

145Wednesday, July 28, 2010

145Wednesday, July 28, 2010

145Wednesday, July 28, 2010

E

0.2

0.2

0.2

of

of

of

A

B

C

D

E

Compal Confidential

Model Name : PWWAA

1 1

2 2

File Name : LA-6842P

LCD Conn.

page 13 page 26

CRT

page 14

Intel Arrandale

rPGA-988

page 5,6,7,8,9,10

FDI X8

Intel Ibex Peak

DMI X4

2.5GHz2.7GHz

5V 480MHz

1.5V 2.5GHz(250MB/s)

SATA port 1

5V 3GHz(300MB/s)

Fan Control

APL5607

page 6

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 800/1066 MT/s

USB port 0,1

USB

PCIeMini Card

USB

5V 480MHz

PCIe 1x

WiMax

USB port 13

PCIeMini Card

WLAN

PCIe port 1

SATA HDD0

page 25

200pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

USB

page 25

RTS5137

2IN1

USB port 10

page 27

page 27

Clock Generator

RTM890N-631-GRT

page 11,12

Int. Camera

USB port 11

page 13

page 13

RJ45

RTL8105E-GR 10/100M

PCIe port 0

page 28page 28

PCIe 1x

1.5V 2.5GHz(250MB/s)

BGA-951

SATA port 4

5V 3GHz(300MB/s)

SATA ODD

page 25

PCI

3 3

page 16~24

3.3V/1.5V 24MHz

HDA Codec

ALC259-GR

page 29

Power/B conn.

page 32

RTC CKT.

page 16

SPI ROM

page 16

Debug Port

page 32

3.3V 33 MHz

LPC BUS

ENE KB926 E0

page 31

HD Audio

DC/DC Interface CKT.

page 34

Touch Pad

Power Circuit DC/DC

4 4

page 35~44

page 33

http://laptop-motherboard-schematic.blogspot.com/

A

B

Int.KBD

page 32

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

EC ROM

page 32

Compal Secret Data

Compal Secret Data

2010/06/21 2011/06/21

2010/06/21 2011/06/21

2010/06/21 2011/06/21

C

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Int.

MIC CONN HP CONN

(LVDS CONN)

page 13

D

Ext.

MIC CONN

page 30

page 30

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

SPK CONN

page 30

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

245Wednesday, July 28, 2010

245Wednesday, July 28, 2010

245Wednesday, July 28, 2010

E

0.2

0.2

0.2

of

of

of

5

D D

C C

B B

A A

4

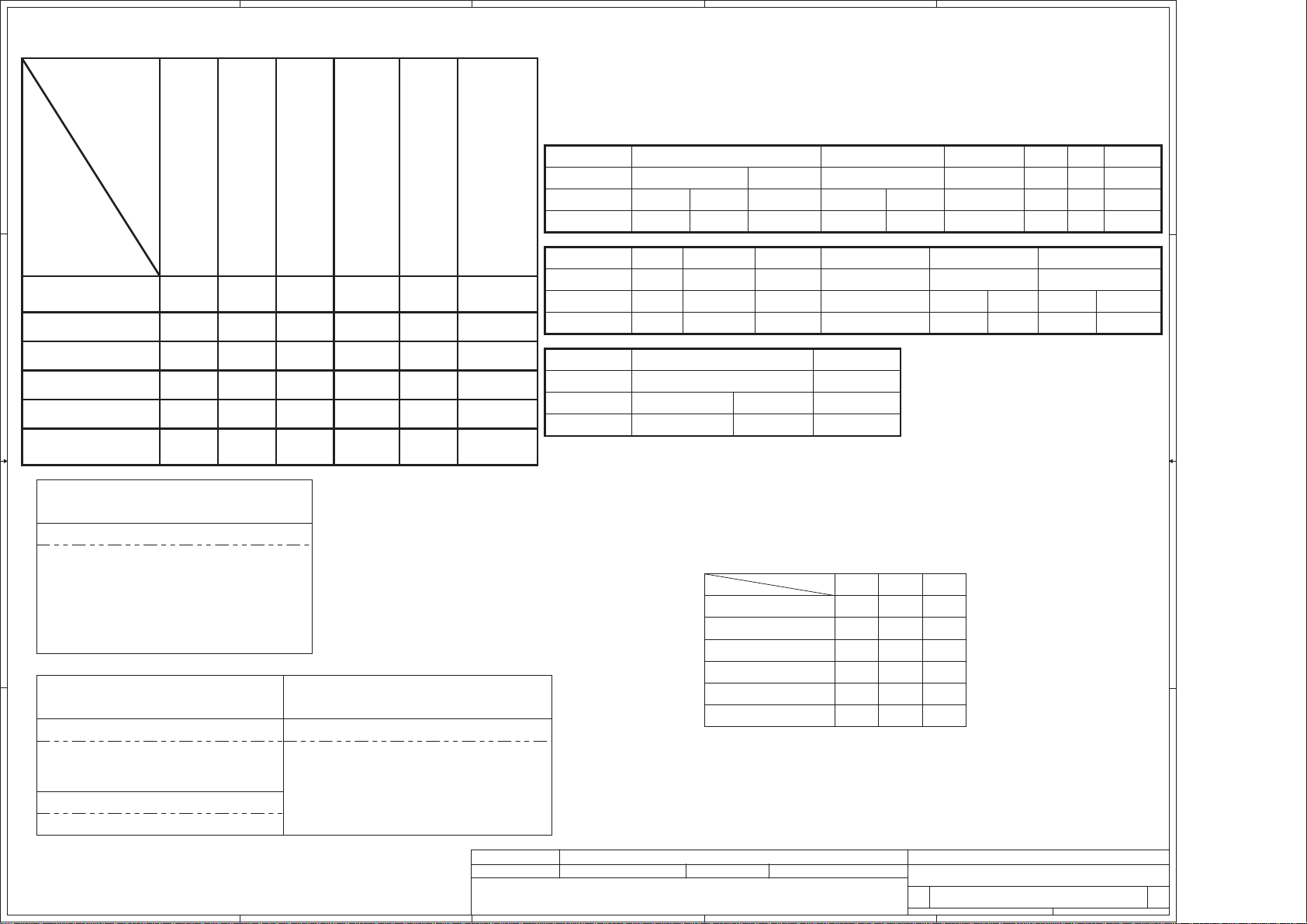

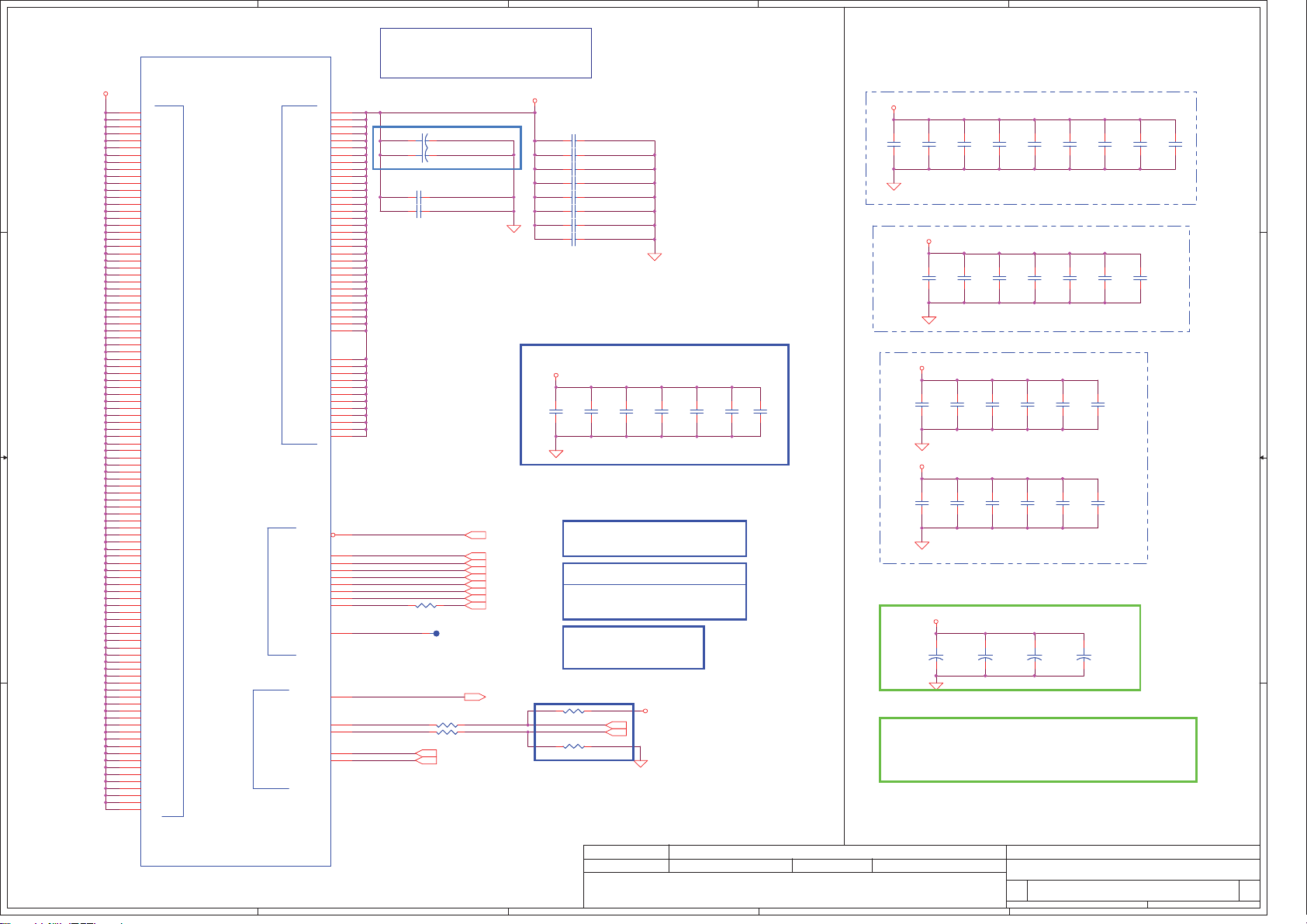

B+

ISL62883HRZ

ADP3211AMNR2G

APW7138NITRL

RT8209BGQW

RT8205EGQW

VR_ON

GFXVR_EN

VTTP_EN

SUSP#

RT8209BGQW

SUSP#

MP2121DQ

N-CHANNEL

SI4800

SUSP

N-CHANNEL

SI4800

3

Ipeak=5A, Imax=3.5A, Iocp min=7.9

SUSP#

SUSP

P-CHANNEL

AO-3413

P-CHANNEL

AO-3413

LDO

G9191

P-CHANNEL

AO-3413

Ipeak=5A, Imax=3.5A, Iocp min=7.7

P-CHANNEL

AO-3413

P-CHANNEL

AO-3415

P-CHANNEL

AO-3413

P-CHANNEL

AO-3413

Ipeak=18A, Imax=12.6A, Iocp min=19.8

Ipeak=7A, Imax=4.9A, Iocp min=7.7

Ipeak=15A, Imax=10.5A, Iocp min=16.5

SUSP

N-CHANNEL

FDS6676AS

SUSP

N-CHANNEL

FDS6676AS

SUSP or 0.75VR_EN#

G2992F1U

BCPWON

KB_LED

+5VS

ODD_EN#

WOL_EN#

LCD_ENVDD

BT_PWR#

FELICA_PWR

2

DESIGN CURRENT 0.1A

DESIGN CURRENT 0.1A

DESIGN CURRENT 5A

DESIGN CURRENT 2A

DESIGN CURRENT 4A

DESIGN CURRENT 0.5A

DESIGN CURRENT 400mA

DESIGN CURRENT 300mA

DESIGN CURRENT 1.6A

DESIGN CURRENT 5A

DESIGN CURRENT 330mA

DESIGN CURRENT 4A

DESIGN CURRENT 1.5A

DESIGN CURRENT 180mA

DESIGN CURRENT 0.5A

DESIGN CURRENT 48A

DESIGN CURRENT 15A

DESIGN CURRENT 18A

DESIGN CURRENT 7A

DESIGN CURRENT 15A

DESIGN CURRENT 2A

DESIGN CURRENT 2A

DESIGN CURRENT 1.5A

+3VL

+5VL

+5VALW

+1.8VS

+5VS

+5VS_L_BCAS

+5VS_LED

+3VS_HDP

+5VS_ODD

+3VALW

+3V_LAN

+3VS

+LCD_VDD

+BT_VCC

+FLICA_VCC

+CPU_CORE

+GFX_CORE

+VTT

+1.05VS

+1.5V

+1.5V_CPU

+1.5VS

+0.75VS

1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPR IETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPR IETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPR IETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMAT ION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMAT ION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMAT ION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CU STODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

http://laptop-motherboard-schematic.blogspot.com/

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/21 2011/06/21

2010/06/21 2011/06/21

2010/06/21 2011/06/21

3

Compal Secret Dat a

Compal Secret Dat a

Compal Secret Dat a

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

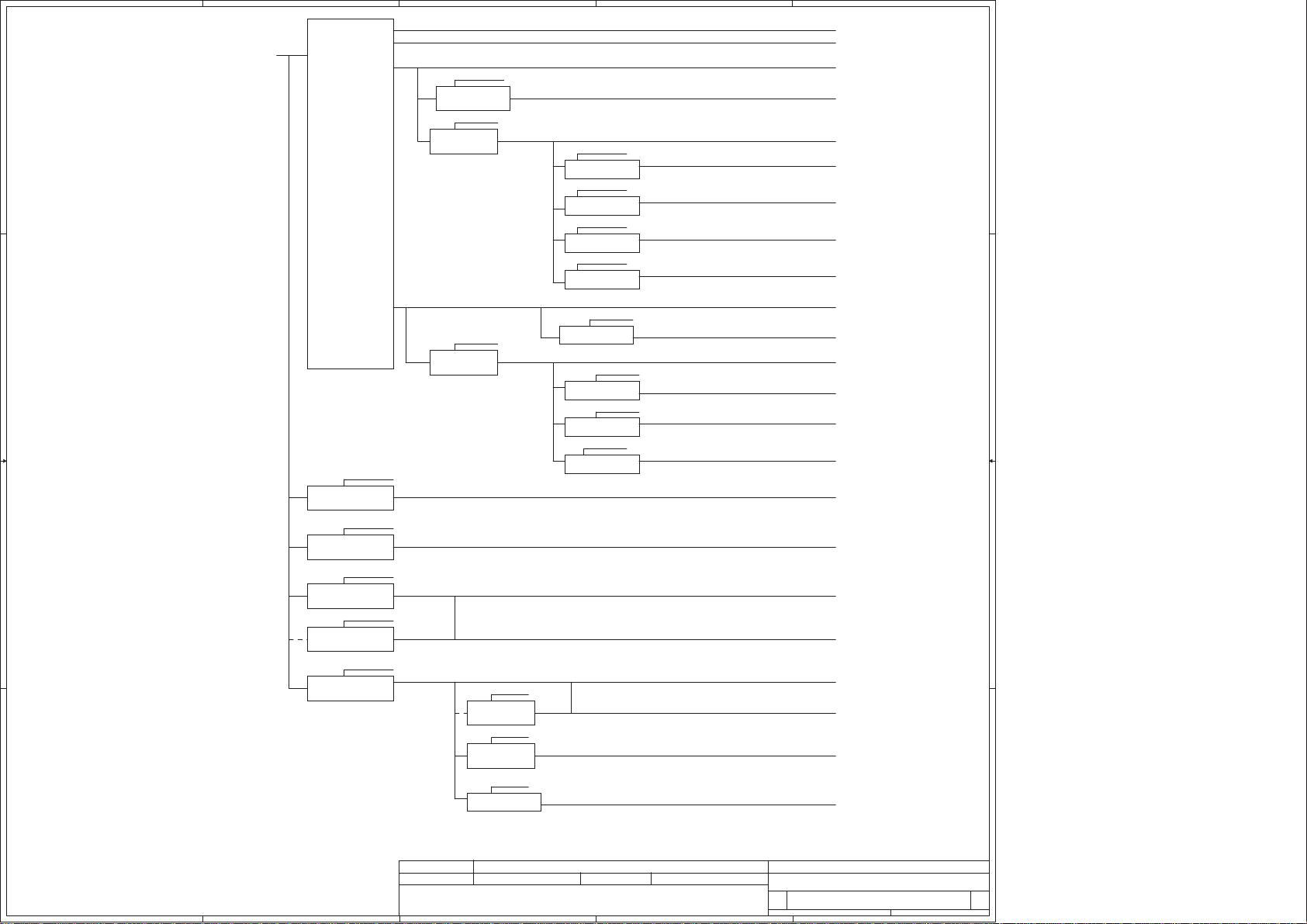

Power Tree

Power Tree

Power Tree

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

345Wednesday, July 28, 2010

345Wednesday, July 28, 2010

345Wednesday, July 28, 2010

1

0.2

0.2

0.2

of

of

of

A

B

C

D

E

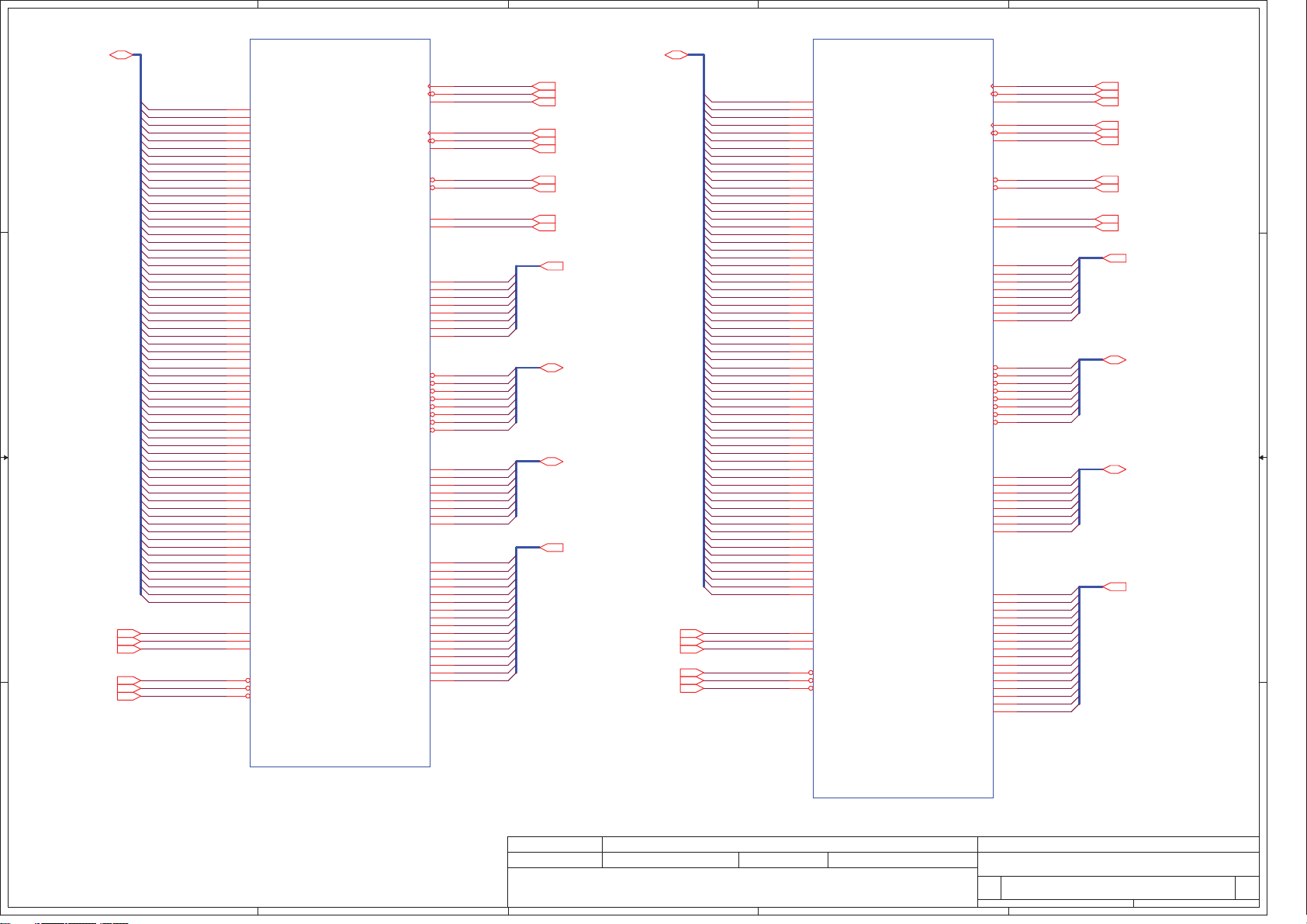

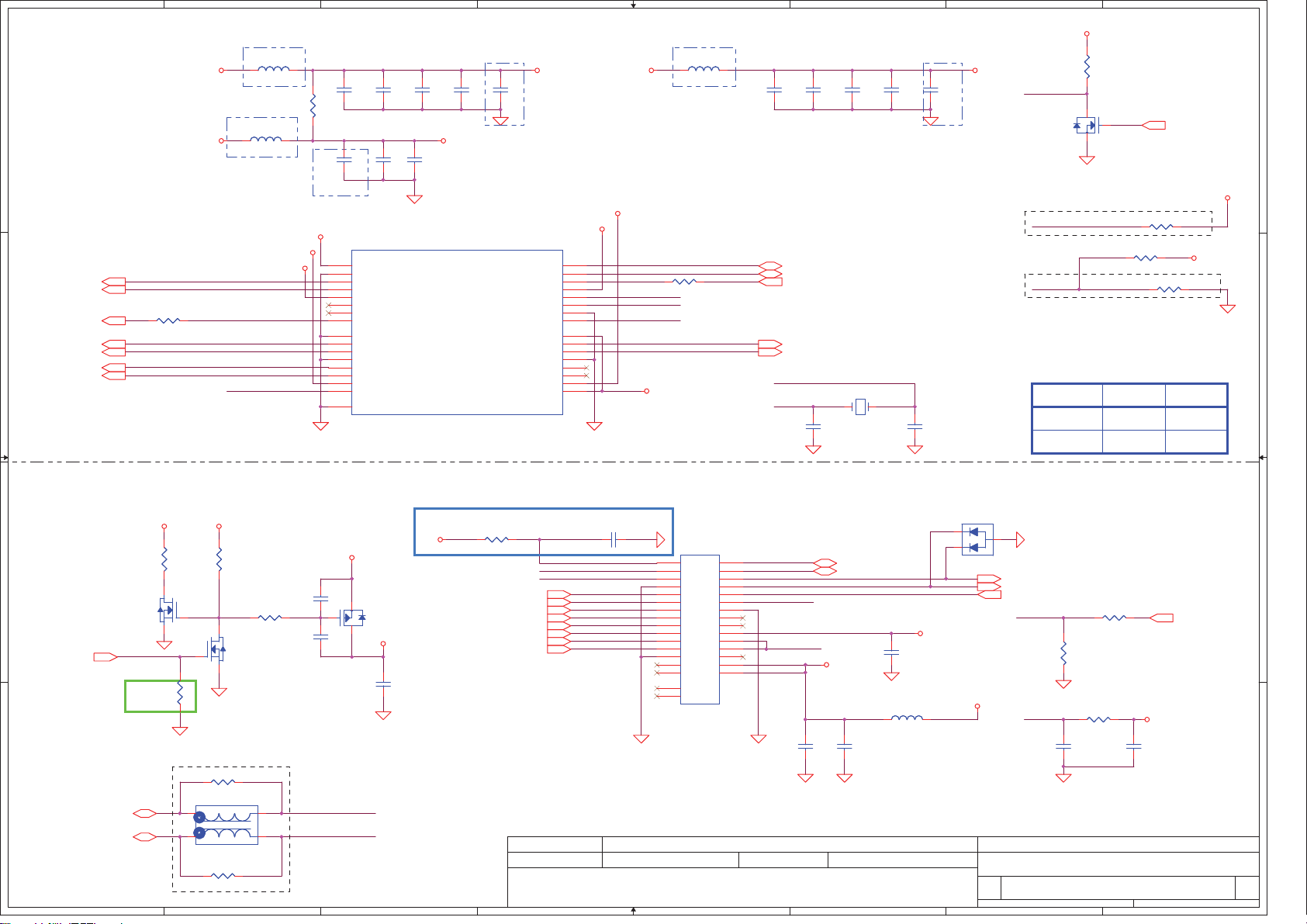

Voltage Rails

State

power

plane

1 1

( O MEANS ON X MEANS OFF )

+RTCVCC

+B

+5VL

+3VL

+5VALW

+3VALW

+VSB

+1.5V

+5VS

+3VS

+1.5VS

+VGA_CORE

+CPU_CORE

+VTT

+1.05VS

+1.8VS

+1.1VS

+0.75VS

BTO Option Table

Function

description

explain

MINI PCI-E SLOT

SLOT1

WLAN/BT

LAN

LAN

10/100M

BTO

Function

description

S0

S1

2 2

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

O

O

O

O

O

O

O

O

O

O

O

X

O

O

O

O

O

X

O

O

O

O

X

X

O

XX

X

XX

OO

OO

X

X

explain

BTO

Function

description

explain

BTO

S3 Power Saving

S3 Power Saving

Power Saving

Camera & Mic

Camera & Mic

Camera & Mic

CAM@

PCH SM Bus Address

HEX

A0 H

D2 H

0001 0110 bSmart Battery

Address

1010 0000 b

1010 0100 bA4 H

1101 0010 b

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

EC SM Bus2 Address

PowerPower

+3VS

Device

96 H

1001 0110 bPCH

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

http://laptop-motherboard-schematic.blogspot.com/

B

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/21 2011/06/21

2010/06/21 2011/06/21

2010/06/21 2011/06/21

C

S5 (Soft OFF)

G3 LOW LOWLOW

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SIGNAL

SLP_S3# SLP_S4# SLP_S5#

HIGH HIGHHIGH

LOW

LOW LOW

D

HIGH HIGHHIGH

HIGH

LOW LOWLOW

Date: Sheet

Date: Sheet

Date: Sheet

HIGH

HIGH

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Compal Electronics, Inc.

Notes List

Notes List

Notes List

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

445Wednesday, July 28, 2010

445Wednesday, July 28, 2010

445Wednesday, July 28, 2010

E

of

of

of

0.2

0.2

0.2

Power

+3VS

3 3

+3VS

+3VS

+3VS

+3VS

+3VS Clock Generator

Device

DDR SO-DIMM 0

DDR SO-DIMM 1

Clock Generator

New Card

WLAN/WIMAX

EC SM Bus1 Address

Device Address Address

+3VL

4 4

A

HEX HEX

16 H

HEXDevice AddressPower

5

1 2

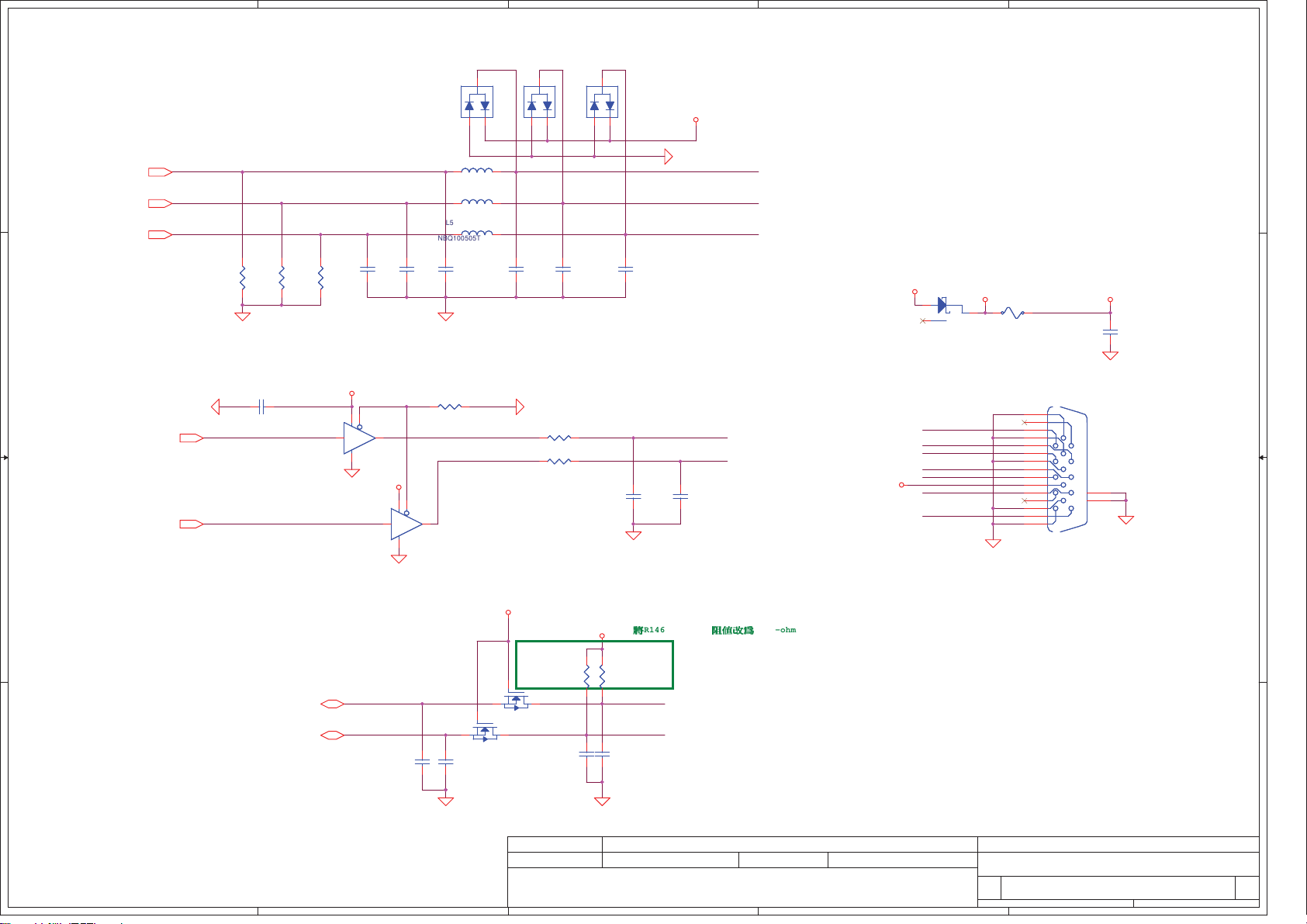

R1 20_0402_1%R1 20_0402_1%

1 2

R2 20_0402_1%R2 20_0402_1%

1 2

R4 49.9_0402_1%R4 49.9_0402_1%

1 2

R3 49.9_0402_1%R3 49.9_0402_1%

D D

+VTT

R10

R10

68_0402_5%

68_0402_5%

@

@

1 2

+1.5V_CPU

C C

R28

@R28

@

1.1K_0402_1%

1.1K_0402_1%

1 2

DRAMPWROK

12

750_0402_1%

750_0402_1%

R29

R29

R28 unmount for NPS@

R29 always mount for PS@

H_THERMTRIP#21

PMSYNCH18

H_PWRGOOD21

DRAMPWROK18

VTTPWROK_CPU39

BUF_PLT_RST#20

+VTT

1 2

R18 49.9_0402_1%R18 49.9_0402_1%

PECI21

Power has removed VR_TT#

+VTT

XDP_RST#_RH_CPURST#

H_PWRGOOD

1 2

R9 68_0402_5%R9 68_0402_5%

1 2

R36 1K_0402_5%R36 1K_0402_5%

TAPPWRGD

R301.5K_0402_1% R301.5K_0402_1%

750_0402_1%

750_0402_1%

T41PAD T41PAD

H_PROCHOT#_D

H_CPURST#

H_PWRGOOD 1_R

12

R250_0402_5% R250_0402_5%

VTTPWROK_CPU

BUF_PLT_RST#_R

R31

R31

4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP_SKTOCC#

CATERR#

DRAMPWROK

JCPUB

JCPUB

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC,AUB_CFD _rPGA,R0P9

IC,AUB_CFD _rPGA,R0P9

@

@

3

MISC THERMAL

MISC THERMAL

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TDI

A16

B16

CLK_CPU_XDP_R

AR30

CLK_CPU_XDP#_R

AT30

E16

D16

A18

A17

SM_DRAMRST#_CPU

F6

SM_RCOMP_0

AL1

SM_RCOMP_1

AM1

SM_RCOMP_2

AN1

PM_EXTTS#0

AN15

PM_EXTTS#_R

AP15

XDP_PRDY#

AT28

XDP_PREQ#

AP27

XDP_TCK

AN28

XDP_TMS

AP28

XDP_TRST#

AT27

XDP_TDI_R

AT29

XDP_TDO_R

AR27

XDP_TDI_M

AR29

XDP_TDO_M

AP29

XDP_DBRESET#

AN25

XDP_BPM#0

AJ22

XDP_BPM#1

AK22

XDP_BPM#2

AK24

XDP_BPM#3

AJ24

AJ25

AH22

AK23

AH23

CLK_CPU_BCLK 21

CLK_CPU_BCLK# 21

1 2

R41 0_0402_5%@R41 0_0402_5%@

1 2

R42 0_0402_5%@R42 0_0402_5%@

CLK_PEG 17

CLK_PEG# 17

Unused by Clarksfield rPGA989

R6 100_0402_1%R6 100_0402_1%

1 2

R7 24.9_0402_1%R7 24.9_0402_1%

1 2

R8 130_0402_1%R8 130_0402_1%

1 2

12

R12 0_0402_5%R12 0_0402_5%

Routed as a single daisy chain

12

R312 1K_0402_5%R312 1K_0402_5%

JTAG MAPPING

Scan Chain

(Default)

CPU Only

GMCH Only

STUFF -> R20, R23, R27

NO STUFF -> R21, R26

STUFF -> R20, R21

NO STUFF -> R23, R26, R27

STUFF -> R26, R27

NO STUFF -> R20, R21, R23

CLK_CPU_XDP

CLK_CPU_XDP#

DDR3 Compensation Signals

Layout Note:Please these

resistors near Processor

PM_EXTTS# 11,12

+3VS

XDP_DBRESET# 18

2

PM_EXTTS#0

PM_EXTTS#_R

1

R15 10K_0402_5%R15 10K_0402_5%

R13 10K_0402_5%R13 10K_0402_5%

12

12

+VTT

R19 unmount for NPS@

@

@

12

R19 0_0402_5%

R19 0_0402_5%

D

S

D

R127

R127

12

S

13

Q41

Q41

G

G

BSS138_NL_SOT23-3

BSS138_NL_SOT23-3

2

C301

C301

0.047U_0402_16V7K

0.047U_0402_16V7K

1 2

SM_DRAMRST# 11,12

RST_GATE 21

C301, Q41,

R127 from PS@

to mount

SM_DRAMRST#_CPU

100K_0402_5%

100K_0402_5%

Add on 10/28

XDP_TDI_R XDP_TDI

XDP_TDO_M

0_0402_5%

0_0402_5%

XDP_TDI_M

XDP_TDO_R

12

R23

R23

1 2

R20 0_0402_5%R20 0_0402_5%

@

@

1 2

R21 0_0402_5%

R21 0_0402_5%

@

@

1 2

R26 0_0402_5%

R26 0_0402_5%

1 2

R27 0_0402_5%R27 0_0402_5%

XDP_TDO

@

B B

For S3 CPU Power Saving

place near JCPU

DRAMPWROK

C4871000P_0402_50V7K C4871000P_0402_50V7K

12

VTTPWROK_CPU

C4881000P_0402_50V7K C4881000P_0402_50V7K

12

VTTPWROK34,39

VTTPWROK

0715 --> change BOM structure to mount

A A

5

+3VALW

1 2

C163 0.1U_0402_16V4ZC163 0.1U_0402_16V4Z

5

U16

U16

1

P

IN1

4

O

2

IN2

G

3

@

4

R33 1.5K_0402_1%R33 1.5K_0402_1%

SN74AHC1G08DCKR_SC70-5

SN74AHC1G08DCKR_SC70-5

12

R840_0402_5%@R840_0402_5%

DRAMPWROK

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_DBRESET# XDP_DBRESET#_R

EMI request, close to JCPU

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

@

R358 0_0402_5%

R358 0_0402_5%

1 2

@

@

R359 0_0402_5%

R359 0_0402_5%

1 2

@

@

R360 0_0402_5%

R360 0_0402_5%

1 2

@

@

R367 0_0402_5%

R367 0_0402_5%

1 2

@

@

R370 0_0402_5%

R370 0_0402_5%

1 2

@

@

R371 0_0402_5%

R371 0_0402_5%

1 2

@

@

R373 0_0402_5%

R373 0_0402_5%

1 2

@

@

R374 0_0402_5%

R374 0_0402_5%

1 2

@

@

R375 0_0402_5%

R375 0_0402_5%

1 2

@

@

R390 0_0402_5%

R390 0_0402_5%

1 2

2010/06/21 2011/06/21

2010/06/21 2011/06/21

2010/06/21 2011/06/21

XDP_PRDY#_R

XDP_PREQ#_R

XDP_TCK_R

XDP_TMS_R

XDP_TRST#_R

XDP_BPM#0_R

XDP_BPM#1_R

XDP_BPM#2_R

XDP_BPM#3_R

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

H_PWRGOOD

TAPPWRGD

+VTT

0.1U_0402_10V6K

0.1U_0402_10V6K

2

XDP Connector

SFF-24Pin

JXDP

1

JXDP

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

GND

24

24

GND

MOLEX_52435-2472

MOLEX_52435-2472

@

@

545Wednesday, July 28, 2010

545Wednesday, July 28, 2010

545Wednesday, July 28, 2010

25

26

0.2

0.2

0.2

of

of

of

XDP_PREQ#_R

XDP_PRDY#_R

XDP_BPM#0_R

XDP_BPM#1_R

XDP_BPM#2_R

R32 1K_0402_5%@R32 1K_0402_5%@

1 2

1 2

R35 0_0402_5%@R35 0_0402_5%@

1

C1

C1

2

@

@

51_0402_5%

51_0402_5%

12

R1451_0402_5% R1451_0402_5%

12

R11

R11

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

XDP_BPM#3_R

H_PWRGOOD _R

TAPPWRGD_R

CLK_CPU_XDP

CLK_CPU_XDP#

XDP_RST#_R

XDP_DBRESET#_R

XDP_TDO

XDP_TRST#_R

XDP_TDI

XDP_TMS_R

XDP_TCK_R

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

CPU CLK/MISC/JTAG

CPU CLK/MISC/JTAG

CPU CLK/MISC/JTAG

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

http://laptop-motherboard-schematic.blogspot.com/

5

4

3

2

1

D D

DMI_PTX_CRX_N018

DMI_PTX_CRX_N118

DMI_PTX_CRX_N218

DMI_PTX_CRX_N318

DMI_PTX_CRX_P018

DMI_PTX_CRX_P118

DMI_PTX_CRX_P218

DMI_PTX_CRX_P318

DMI_CTX_PRX_N018

DMI_CTX_PRX_N118

DMI_CTX_PRX_N218

DMI_CTX_PRX_N318

DMI_CTX_PRX_P018

DMI_CTX_PRX_P118

DMI_CTX_PRX_P218

DMI_CTX_PRX_P318

C C

B B

FDI_CTX_PRX_N018

FDI_CTX_PRX_N118

FDI_CTX_PRX_N218

FDI_CTX_PRX_N318

FDI_CTX_PRX_N418

FDI_CTX_PRX_N518

FDI_CTX_PRX_N618

FDI_CTX_PRX_N718

FDI_CTX_PRX_P018

FDI_CTX_PRX_P118

FDI_CTX_PRX_P218

FDI_CTX_PRX_P318

FDI_CTX_PRX_P418

FDI_CTX_PRX_P518

FDI_CTX_PRX_P618

FDI_CTX_PRX_P718

FDI_FSYNC018

FDI_FSYNC118

FDI_INT18

FDI_LSYNC018

FDI_LSYNC118

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

JCPUA

JCPUA

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

PEG_COMP

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PEG_RBIAS

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

1 2

R38 49.9_0402_1%R38 49.9_0402_1%

1 2

R39 750_0402_1%R39 750_0402_1%

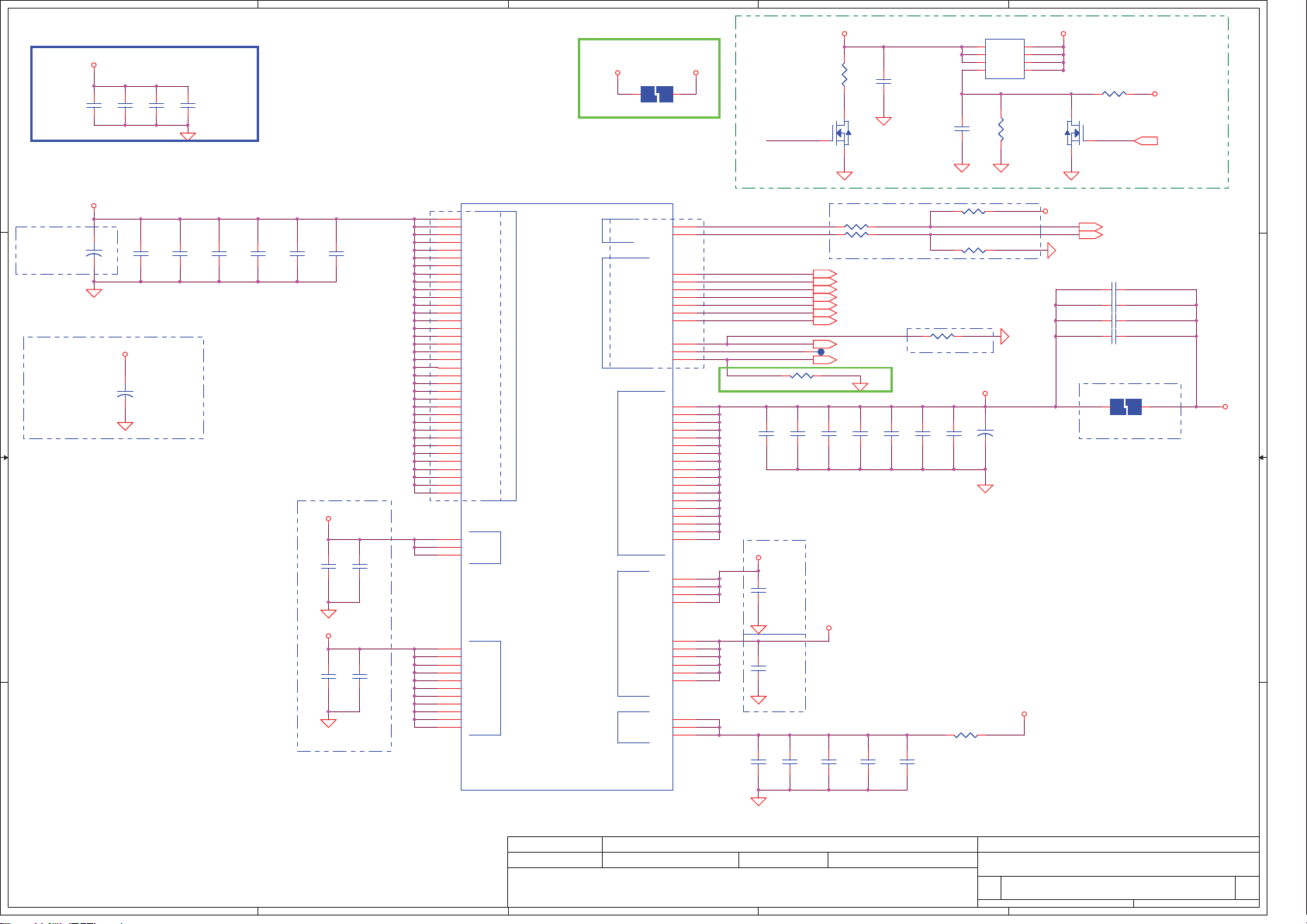

FAN Control Circuit

+5VS

1A

2

C3

C3

10U_0805_10V4Z

10U_0805_10V4Z

U1

U1

1

EN

GND

2

VIN

EN_DFAN131

+FAN1

10mil

1

C5

C5

10U_0805_10V4Z

10U_0805_10V4Z

2

GND

3

VOUT

GND

4

VSET

GND

APL5607KI-TRG_SO8

APL5607KI-TRG_SO8

1

8

7

6

5

+FAN1

2

C4

1000P_0402_25V8J@C41000P_0402_25V8J@

1

0.01U_0402_25V7K

0.01U_0402_25V7K

C6

C6

JFAN

JFAN

@

@

1

1

2

2

3

3

4

GND

5

GND

ACES_85204-0300N

ACES_85204-0300N

R34 10K_0402_5%R34 10K_0402_5%

12

FAN_SPEED1 31

+3VS

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

@

@

Remove Cap, for EMI

A A

Security Classification

Security Classification

Security Classification

2010/06/21 2011/06/21

2010/06/21 2011/06/21

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

http://laptop-motherboard-schematic.blogspot.com/

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/21 2011/06/21

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

CPU DMI/FDI/PEG

CPU DMI/FDI/PEG

CPU DMI/FDI/PEG

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

645Wednesday, July 28, 2010

645Wednesday, July 28, 2010

645Wednesday, July 28, 2010

1

0.2

0.2

0.2

of

of

of

5

JCPUC

JCPUC

DDR_A_D[0..63]11

4

3

JCPUD

JCPUD

DDR_B_D[0..63]12

2

1

AA6

SA_CK[0]

AA7

SA_CK#[0]

P7

DDR_A_D0

DDR_A_D1

D D

C C

B B

DDR_A_BS011

DDR_A_BS111

DDR_A_BS211

DDR_A_CAS#11

DDR_A_RAS#11

DDR_A_WE#11

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

C10

D10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

B10

E10

F10

AJ7

AJ6

AJ9

AL7

AL8

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

G8

K7

G7

J10

M6

M8

K8

N8

P9

U7

J8

J7

L7

L9

L6

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

SA_CKE[0]

Y6

SA_CK[1]

Y5

SA_CK#[1]

P6

SA_CKE[1]

AE2

SA_CS#[0]

AE8

SA_CS#[1]

AD8

SA_ODT[0]

AF9

SA_ODT[1]

DDR_A_DM0

B9

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

D7

H7

M7

AG6

AM7

AN10

AN13

DDR_A_DQS#0

C9

DDR_A_DQS#1

F8

DDR_A_DQS#2

J9

DDR_A_DQS#3

N9

DDR_A_DQS#4

AH7

DDR_A_DQS#5

AK9

DDR_A_DQS#6

AP11

DDR_A_DQS#7

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDRA_CLK0 11 DDRB_CLK0 12

DDRA_CLK0# 11

DDRA_CKE0 11 DDRB_CKE0 12

DDRA_CLK1 11

DDRA_CLK1# 11

DDRA_CKE1 11

DDRA_SCS0# 11

DDRA_SCS1# 11 DDRB_SCS1# 12

DDRA_ODT0 11 DDRB_ODT0 12

DDRA_ODT1 11 DDRB_ODT1 12

DDR_A_DM[0..7] 11

DDR_A_DQS#[0..7] 11

DDR_A_DQS[0..7] 11

DDR_A_MA[0..15] 11

DDR_B_BS012

DDR_B_BS112

DDR_B_BS212

DDR_B_CAS#12

DDR_B_RAS#12

DDR_B_WE#12

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AF3

AG1

AK1

AG4

AG3

AH4

AK3

AK4

AM6

AN2

AK5

AK2

AM4

AM3

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AR10

AT10

AB1

AC5

AC6

AJ3

AJ4

W5

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

M1

K5

K4

M4

N5

R7

Y7

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDRB_CLK0# 12

DDRB_CLK1 12

DDRB_CLK1# 12

DDRB_CKE1 12

DDRB_SCS0# 12

DDR_B_DM[0..7] 12

DDR_B_DQS#[0..7] 12

DDR_B_DQS[0..7] 12

DDR_B_MA[0..15] 12

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

@

@

A A

Security Classification

Security Classification

Security Classification

2010/06/21 2011/06/21

2010/06/21 2011/06/21

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

http://laptop-motherboard-schematic.blogspot.com/

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/21 2011/06/21

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

@

@

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

CPU DDRIII

CPU DDRIII

CPU DDRIII

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

745Wednesday, July 28, 2010

745Wednesday, July 28, 2010

745Wednesday, July 28, 2010

1

0.2

0.2

0.2

of

of

of

5

4

3

2

1

Material Note (+VTT):

JCPUF

JCPUF

+CPU_CORE

D D

C C

B B

A A

Clarksfield: 65A Clarksfield: 21A

Auburndale:48A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

SENSE LINES

SENSE LINES

Auburndale:18A

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

1.1V RAIL POWER

1.1V RAIL POWER

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

PSI#

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

AN35

AJ34

AJ35

B15

A15

390uF/ 10mohm, number are 3,

power x1, HW x2

(Place these capacitors under CPU socket Edge, top layer) (Place these capacitors between inductor and socket on Bottom)

+

+

C144 390U_2.5V_M_R10

C144 390U_2.5V_M_R10

1 2

+

+

C267 390U_2.5V_M_R10

C267 390U_2.5V_M_R10

1 2

C89 22U_0805_6.3V6MC89 22U_0805_6.3V6M

1 2

C91 22U_0805_6.3V6MC91 22U_0805_6.3V6M

1 2

SF000002O00

ESR 10m-ohm

H6.3

H_PSI# 42

CPU_VID0 42

CPU_VID1 42

CPU_VID2 42

CPU_VID3 42

CPU_VID4 42

CPU_VID5 42

T3 PADT3 PAD

CPU_VID6 42

H_DPRSLPVR 42

IMVP_IMON 42

H_DPRSLPVR_R

H_VTTSELECT

VCCSENSE_R

1 2

R62 0_0402_5%R62 0_0402_5%

R65 0_0402_5%R65 0_0402_5%

1 2

R66 0_0402_5%R66 0_0402_5%

1 2

VTT_SENSE 39

VSS_SENSE_VTT 39

+VTT

C81 10U_0805_10V4KC81 10U_0805_10V4K

1 2

C83 10U_0805_10V4KC83 10U_0805_10V4K

1 2

C85 10U_0805_10V4KC85 10U_0805_10V4K

1 2

C87 10U_0805_10V4KC87 10U_0805_10V4K

1 2

C88 10U_0805_10V4KC88 10U_0805_10V4K

1 2

C90 10U_0805_10V4KC90 10U_0805_10V4K

1 2

C92 10U_0805_10V4KC92 10U_0805_10V4K

1 2

C94 10U_0805_10V4K@C94 10U_0805_10V4K@

1 2

Power team request for F-Din

+CPU_CORE

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C179

C179

C131

C114

C114

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C131

2

22U_0805_6.3V6M

22U_0805_6.3V6M

CRB default setting:

VID[6:0]=[0100111]

VTT Rail

Auburndale +1.1VS_VTT=1.05V

Clarksfield +1.1VS_VTT=1.1V

H_VTTSELECT = low, 1.1V

H_VTTSELECT = high, 1.05V

1 2

R64 100_0402_1%R64 100_0402_1%

VCCSENSE

VSSSENSEVSSSENSE_R

1 2

R67 100_0402_1%R67 100_0402_1%

near CPU

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C116

C116

2

2

+CPU_CORE

VCCSENSE 42

VSSSENSE 42

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C132

C132

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C129

C129

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C149

C149

+CPU_CORE

10U_0805_10V4K

10U_0805_10V4K

1

C71

C71

2

10U_0805_10V4K

10U_0805_10V4K

1

C72

C72

2

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

1

C73

C73

2

1

2

1

C75

C75

C74

C74

2

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

1

C76

C76

2

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

1

C77

C77

2

1

C78

C78

2

10U_0805_10V4K

10U_0805_10V4K

1

C79

C79

2

(Place these capacitors under CPU socket, top layer)

+CPU_CORE

10U_0805_10V4K

10U_0805_10V4K

1

C98

C98

2

10U_0805_10V4K

10U_0805_10V4K

1

C99

C99

2

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

1

C100

C100

2

1

C101

C101

2

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

10U_0805_10V4K

1

C102

C102

2

1

1

C103

C103

C104

C104

2

2

10U_0805_10V4K

10U_0805_10V4K

(Place these capacitors on CPU cavity, Bottom Layer)

+CPU_CORE

22U_0805_6.3V6M

1

1

C107

C107

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C113

C113

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C108

C108

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C130

C130

2

22U_0805_6.3V6M

22U_0805_6.3V6M

C109

C109

C115

C115

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C110

C110

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C148

C148

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C106

C106

C105

1

2

C105

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+CPU_CORE

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C112

C112

C111

C111

2

22U_0805_6.3V6M

22U_0805_6.3V6M

TOP side (under inductor)

+CPU_CORE

330U_D2_2.5VM_R9M

1

+

+

C121

C121

330U_D2_2.5VM_R9M

330U_D2_2.5VM_R9M

2

330U_D2_2.5VM_R9M

1

+

+

C122

C122

330U_D2_2.5VM_R9M

330U_D2_2.5VM_R9M

2

C123

C123

330U_D2_2.5VM_R9M

330U_D2_2.5VM_R9M

1

+

+

C124

C124

2

1

+

+

2

Check list:

+CPU_CORE: 6x 470uF, 12x 22uF, 17x 10uF

+VTT: 4x 330uF, 7x 22uF, 8x 10uF

IC,AUB_CFD _rPGA,R0P9

IC,AUB_CFD _rPGA,R0P9

@

@

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEER ING DRAWING IS THE PROPRIETAR Y PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

http://laptop-motherboard-schematic.blogspot.com/

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRI OR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/06/21 2011/06/21

2010/06/21 2011/06/21

2010/06/21 2011/06/21

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

CPU POWER-1

CPU POWER-1

CPU POWER-1

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

1

845Wednesday, July 28, 2010

845Wednesday, July 28, 2010

845Wednesday, July 28, 2010

of

of

of

0.2

0.2

0.2

5

For EMI request

+GFX_CORE

47P_0402_50V8J

C118

C118

@

@

47P_0402_50V8J

12

C119

C119

@

@

12

C93

C93

@

@

47P_0402_50V8J

47P_0402_50V8J

12

12

C97

C97

@

@

D D

47P_0402_50V8J

47P_0402_50V8J

47P_0402_50V8J

47P_0402_50V8J

Change C271 to 4.5mm height OS-CON at PVT

+GFX_CORE

22U_0805_6.3V6M

C271

330U_2.5V_M_R17

330U_2.5V_M_R17

C271

1

+

+

2

22U_0805_6.3V6M

1

C95

C95

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C127

C127

2

1U_0402_6.3V4Z

1U_0402_6.3V4Z

1

C117

C117

2

1U_0402_6.3V4Z

1U_0402_6.3V4Z

1

C96

C96

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C120

C120

2

2

Add C496 Co-Layout with C271

C496

C496

@

@

+GFX_CORE

1

+

+

2

C C

330U_D2_2VM_R6M

330U_D2_2VM_R6M

For POLY Cap.

0714 --> C271 mount,

C496 unmount

+VTT

1

C141

B B

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

C141

C146

C146

2

+VTT

1

2

(Place these capacitors under CPU socket, top layer)

A A

4

C86

C86

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C142

C142

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C147

C147

22U_0805_6.3V6M

22U_0805_6.3V6M

2

JCPUG

JCPUG

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

Auburndale:22A

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

@

@

7/22 modified for cost down.

GRAPHICS

GRAPHICS

Clarksfield: 5A

Auburndale:3A

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

Clarksfield: 21A

Auburndale:18A

Clarksfield: 0.6A

Auburndale:1.35A

3

+1.5V_CPU +1.5VS

PJ32

@PJ32

@

2

112

JUMP_43X79

JUMP_43X79

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

GRAPHICS VIDs

GRAPHICS VIDs

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

VCC_AXG_SENSE_R

VSS_AXG_SENSE_R

GFXVR_EN

GFXVR_DPRSLPVR

GFXVR_IMON

1U_0402_6.3V4Z

1U_0402_6.3V4Z

+1.8VS_H_PLL

C151

C151

1U_0402_6.3V4Z

1U_0402_6.3V4Z

R424

R424

470_0805_5%

470_0805_5%

Q46B

Q46B

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

R687 1K_0402_5%

R687 1K_0402_5%

1

C133

C133

2

+VTT

1

C143

C143

10U_0805_10V4K

10U_0805_10V4K

2

1

C145

C145

22U_0805_6.3V6M

22U_0805_6.3V6M

2

5

R365 0_0402_5%R365 0_0402_5%

R384 0_0402_5%R384 0_0402_5%

12

@

@

1U_0402_6.3V4Z

1U_0402_6.3V4Z

1

1

C135

C135

C134

C134

2

2

1U_0402_6.3V4Z

1U_0402_6.3V4Z

(Place these capacitors under CPU socket Edge, top layer)

+VTT

(Place these capacitors under CPU socket, top layer)

1U_0402_6.3V4Z

1U_0402_6.3V4Z

1

1

1

C152

C152

2

2

2

2.2U_0603_6.3V4Z

2.2U_0603_6.3V4Z

2

1

1 2

2

3

4

1 2

1 2

For Power request

near CPU

GFXVR_VID_0 43

GFXVR_VID_1 43

GFXVR_VID_2 43

GFXVR_VID_3 43

GFXVR_VID_4 43

GFXVR_VID_5 43

GFXVR_VID_6 43

GFXVR_EN 43

T8 PADT8 PAD

GFXVR_IMON 43

1U_0402_6.3V4Z

1U_0402_6.3V4Z

1

C137

C137

C136

C136

2

1U_0402_6.3V4Z

1U_0402_6.3V4Z

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

C153

C153

C154

C154

3A

C273

C273

10U_0805_10V4K

10U_0805_10V4K

C472

C472

1 2

R69 100_0402_1%R69 100_0402_1%

1 2

R82 100_0402_1%R82 100_0402_1%

Change R136 to 470

ohm

for GFX issue

1 2

R50 470_0402_5%R50 470_0402_5%

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

C138

C138

2

1

2

1

C139

C139

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

R71 0_0805_5%R71 0_0805_5%

C155

C155

22U_0805_6.3V6M

22U_0805_6.3V6M

1

S

2

S

3

S

4

G

FDS6676AS_SO8

FDS6676AS_SO8

1

2

0.1U_0402_25V6

0.1U_0402_25V6

+1.5V_CPU

1

+

+

2

12

Q33

Q33

8

D

7

D

6

D

5

D

12

R417

R417

820K_0402_5%

820K_0402_5%

C216

C216

390U_2.5V_M_R10

390U_2.5V_M_R10

+1.8VS

1

+1.5V+1.5V_CPU

form PS@ to mount

R418

R418

1 2

220K_0402_5%

220K_0402_5%

61

Q46A

Q46A

SUSPSUSP

2

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

+GFX_CORE

VCC_AXG_SENSE 43

VSS_AXG_SENSE 43

C230 0.1U_0402_16V4ZC230 0.1U_0402_16V4Z

1 2

C314 0.1U_0402_16V4ZC314 0.1U_0402_16V4Z

1 2

C205 0.1U_0402_16V4ZC205 0.1U_0402_16V4Z

1 2

C186 0.1U_0402_16V4ZC186 0.1U_0402_16V4Z

1 2

remove PJ30

PJ31

@PJ31

@

2

112

JUMP_43X79

JUMP_43X79

PJ31 need to open for

S3 CPU Power Saving

+VSB

SUSP 34,41

+1.5V

Security Classification

Security Classification

Security Classification

2010/06/21 2011/06/21

2010/06/21 2011/06/21

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING I S THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

http://laptop-motherboard-schematic.blogspot.com/

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/21 2011/06/21

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

CPU POWER-2

CPU POWER-2

CPU POWER-2

PWWAA LA6842P M/B

PWWAA LA6842P M/B

PWWAA LA6842P M/B

945Wednesday, July 28, 2010

945Wednesday, July 28, 2010

945Wednesday, July 28, 2010

1

0.2

0.2

0.2

of

of

of

5

JCPUI

JCPUI

K27

VSS161

K9

VSS162

K6

VSS163

D D

C C

B B

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

@

@

VSS

VSS

NCTF

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

H_NCTF1

H_NCTF2

H_NCTF6

H_NCTF7

PADT4PAD

PADT5PAD

PADT6PAD

PADT7PAD

4

JCPUH

JCPUH

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

VSS8

AR17

VSS9

AR15

VSS10

AR12

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

AP20

VSS15

AP17

VSS16

AP13

VSS17

AP10

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

AN34

VSS22

AN31

VSS23

AN23

VSS24

AN20

VSS25

AN17

VSS26

AM29

VSS27

AM27

VSS28

AM25

VSS29

AM20

VSS30

AM17

VSS31

AM14

VSS32

AM11

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

AL34

VSS37

AL31

VSS38

AL23

VSS39

AL20

VSS40

AL17

VSS41

AL12

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

AK29

T4

T5

T6

T7

VSS46

AK27

VSS47

AK25

VSS48

AK20

VSS49

AK17

VSS50

AJ31

VSS51

AJ23

VSS52

AJ20

VSS53

AJ17

VSS54

AJ14

VSS55

AJ11

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

AH35

VSS60

AH34

VSS61

AH33

VSS62

AH32

VSS63

AH31

VSS64

AH30

VSS65

AH29

VSS66

AH28

VSS67

AH27

VSS68

AH26

VSS69

AH20

VSS70

AH17

VSS71

AH13

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

AG10

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

AE35

VSS80

IC,AUB_CFD_rPGA,R0P9

IC,AUB_CFD_rPGA,R0P9

@

@

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

3

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

2

WW41 Recommend not pull down

PCIE2.0 Jitter is over on ES1

R743.01K_0402_1% @ R743.01K_0402_1% @

1 2

R753.01K_0402_1% @ R753.01K_0402_1% @

1 2

R763.01K_0402_1% @ R763.01K_0402_1% @

1 2

CFG0 - PCI-Express Configuration Select

*1:Single PEG

0:Bifurcation enabled

CFG3 - PCI-Express Static Lane Reversal

*1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

CFG4 - Display Port Presence

*1:Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

JCPUE

JCPUE

AP25

RSVD1

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

RSVD6

M27

RSVD7

L28

RSVD8

J17

RSVD9

H17

RSVD10

G25

RSVD11

G17

RSVD12

E31

RSVD13

E30

RSVD14

AM30

CFG[0]

AM28

CFG[1]

AP31

CFG[2]

AL32

CFG[3]

AL30

CFG[4]

AM31

CFG[5]

AN29

CFG[6]

AM32

CFG[7]

AK32

CFG[8]

AK31

CFG[9]

AK28

CFG[10]

AJ28

CFG[11]