Topstar X01 Schematic

5

4

3

2

1

Topstar Digital technologies Co.,LTD

D D

Board name: Mother Board Schematic

Project name: X01

Version: Ver B

Initial Date:

1. System Block Diagram & Schematic page description;

2. Power Block Diagram & Discription;

3. Annotations & information;

4. Schematic modify Item and history;

New update: 5. Power on & off Sequence;

6. ACPI Mode Switch Timings;

7. Power On Sequence Map;

8. CLOCK Distribution;

C C

9. Power Distribution;

Topstar Confidential

Hardware drawing by:

许沐锌

Power drawing by:

B B

Hardware check by: EMI Check by:

Power check by:

Manager Sign by:

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

the expressed written consent of TOPSTAR

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

Swain Xu( )

Swain Xu( )

许沐锌

许沐锌

许沐锌

Title

Title

Title

X01

X01

X01

1

B

B

139Tuesday, September 29, 2009

139Tuesday, September 29, 2009

139Tuesday, September 29, 2009

B

of

of

of

5

4

3

2

1

CONTENT

Topstar Confidential

ShenZhen Topstar Industry Co.,LTD

D D

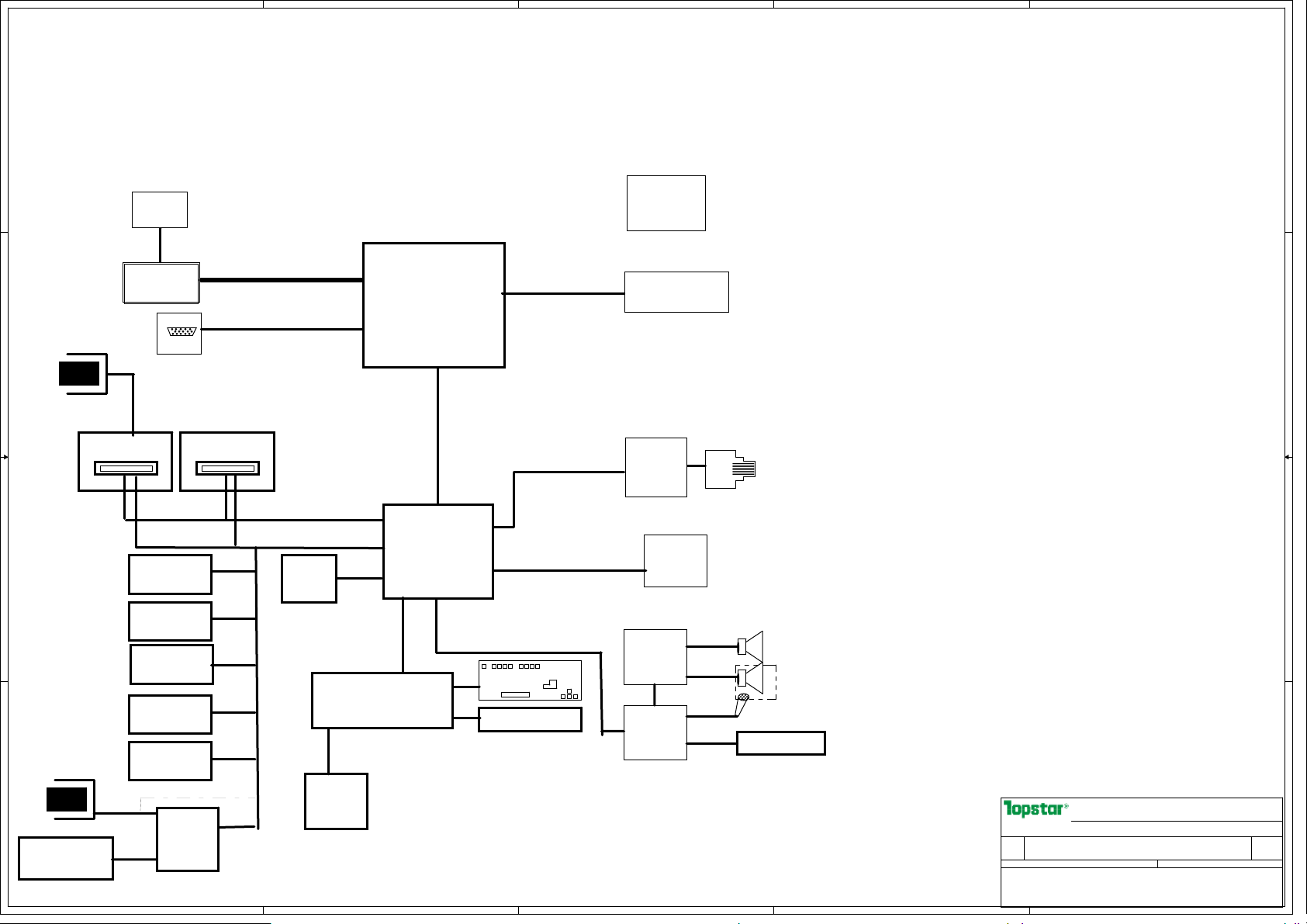

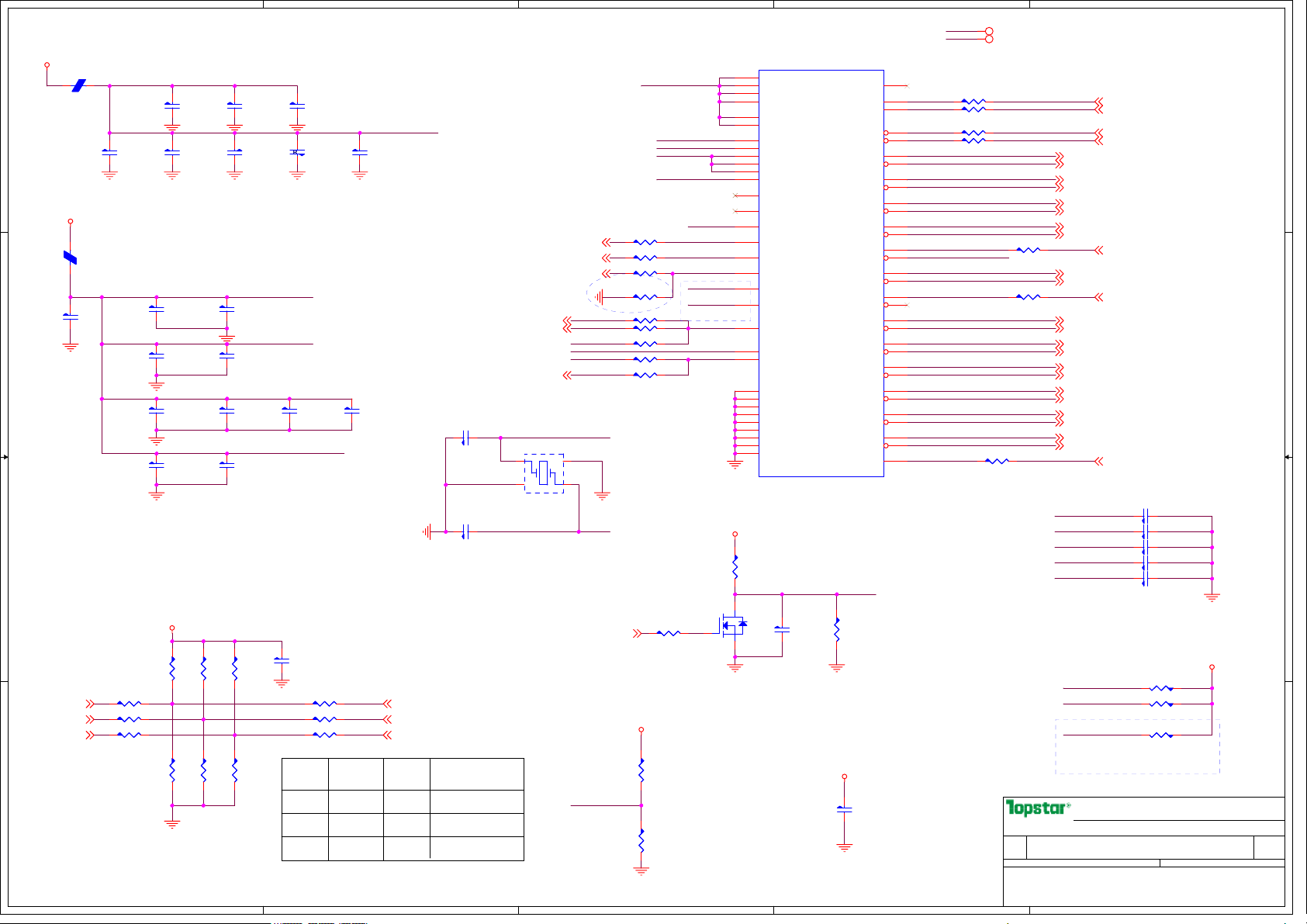

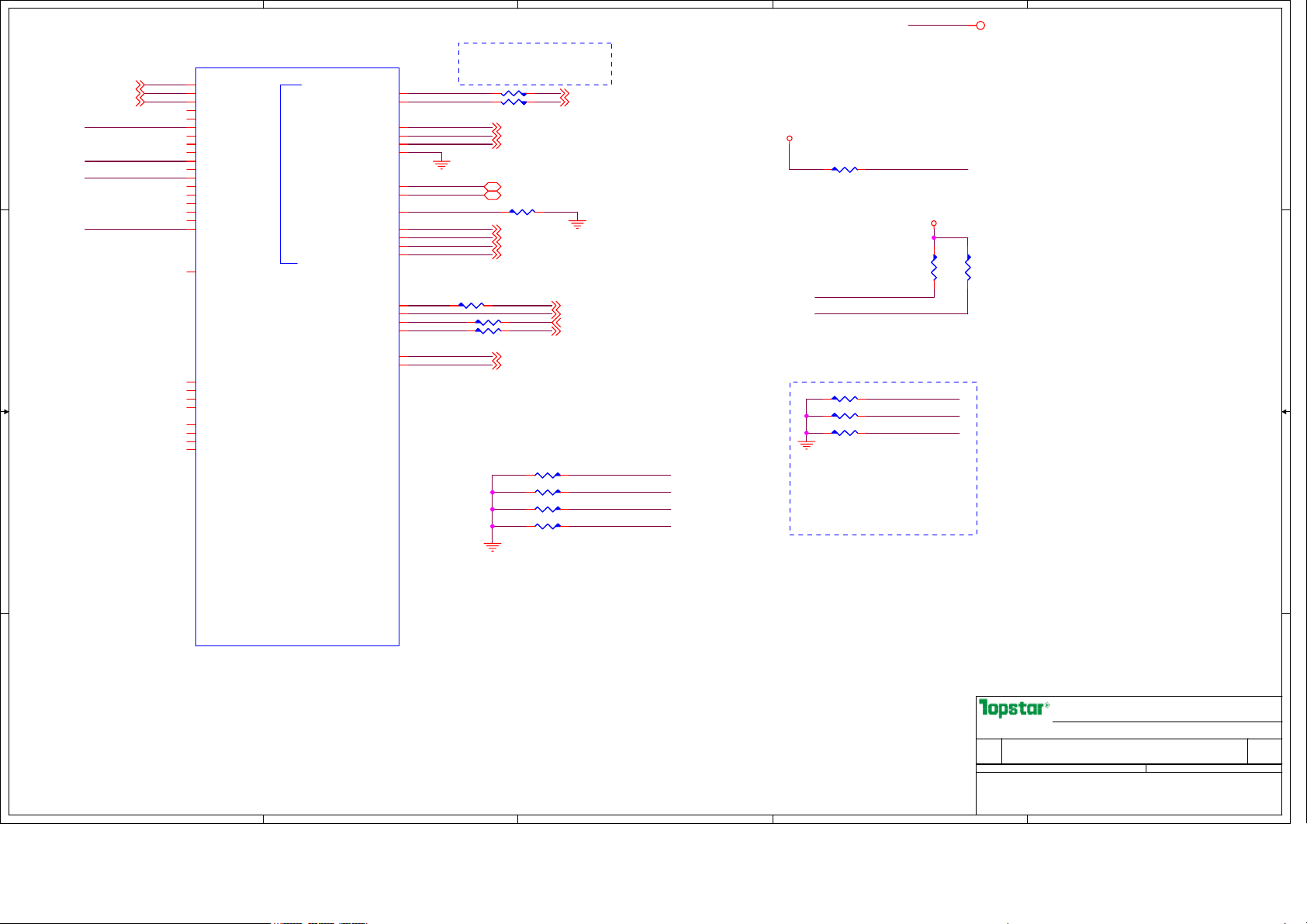

P01 SYSTEM BLOCK Ver:A

CK505M

Backlight

Connector

+VDC

PG 15

10.1' LED

+V3.3S

LVDS

PG 12

VGA

C C

SIM CARD

+V5S

PG 11

R/G/B

PG 20

PCIE mini Card

PG 20

PCIE mini Card

PG 19

PCIE 1X

USB1.1/2.0

B B

Bluetooth

+V5AL

BIOS

8Mbit

+V3.3AL

PG 25

USB PORT1

+V5AL

USB PORT2

+V5AL

KB Controller/EC

USB PORT3

+V5AL

CAM

+V5S

A A

PG 18

SD/MMC/MS/XD CARD

Touch Panel

+V5S

USB HUB

5

KB3310B

BIOS

8Mbit

+V3.3AL

PG 25

+V3.3AL

Pineview

FCBGA 437PIN

+VCC_CORE,+VCCP

+1.05V,+V0.89V,+V1.8V

PG 7,8,9,10

DMI x2

Gen1

Tigerpoint

82801GBM 652 BGA

+V1.05S,+V3.3S

+V3.3AL,+V5AL

+V1.5S,+V5S

+V3.3A_RTC

PG 14,15,16

PG 25

4

DDR2

667

PCIE X1

SATAO(R1.0)

HDA

KB Matrix

LED & TouchPAD

Clocking

ICS9LPRS365

+V3.3S

PG 6

DDR2 SODIMM0

667

+V0.9S,+V1.8,+V3.3S

PG 13

10/100M

LAN

RTL8102E

+V3.3AL,+V3.3S

PG 26

S-ATA

2.5" HHD

+V5S,+V3.3S

PG 17

AMP

TPS6017A2

+V5S

PG 22

AZALIA

ALC662

+V5S,+V3.3S

PG 22

3

RJ45

Speaker

L

R

MiC

PG 22

Audio Jack

2

1 Title

2 System Block & Sch Page

3 PWR Block & description

4 NOTE and Annotations

5 Sch Modify and history

6 CK-505M

7 Pineview Host/k/LVDS/DMI

8 Pineview DDR2

9 Pineview VGA/RVDS

10 Pineview Power

11 CTR CONN

12 LVDS Inverter CONN

13 DDRII SODIMM0

14 Tigerpoint (1of3)

15 Tigerpoint (2of3)

16 Tigerpoint (3of3)

17 SATA HDD

18 Card Reader

19 PCIE MINI SLOT 1

20 PCIE MINI SLOT 2

21 USB Port & FAN

22 Audio (ALC662)

23 LED

24 OTP

25 KBC(KB3310B)

26 LAN(RTL8101E)

27 ADAPTER IN

28 BATTERY JACK

29 V3.3AL/+V5AL POWER

30 DDR V1.8/+V0.9S POWER

31 V1.5S/+V1.05S POWER

32 Power Good Logic_OVP

33 V5S/V3.3S/V1.8S/V1.2 Power

34 VCORE POWER

35 Power Discharge Circuit

36 CHARGER

37 Power On Secquence & Reset M

38 Power ON/OFF

39 Touchpad Board

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

许沐锌

Swain Xu( )

许沐锌

Swain Xu( )

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

许沐锌

System Block & Index

System Block & Index

System Block & Index

X01

X01

X01

1

239Tuesday, September 29, 2009

239Tuesday, September 29, 2009

239Tuesday, September 29, 2009

of

of

of

B

B

B

5

4

3

2

1

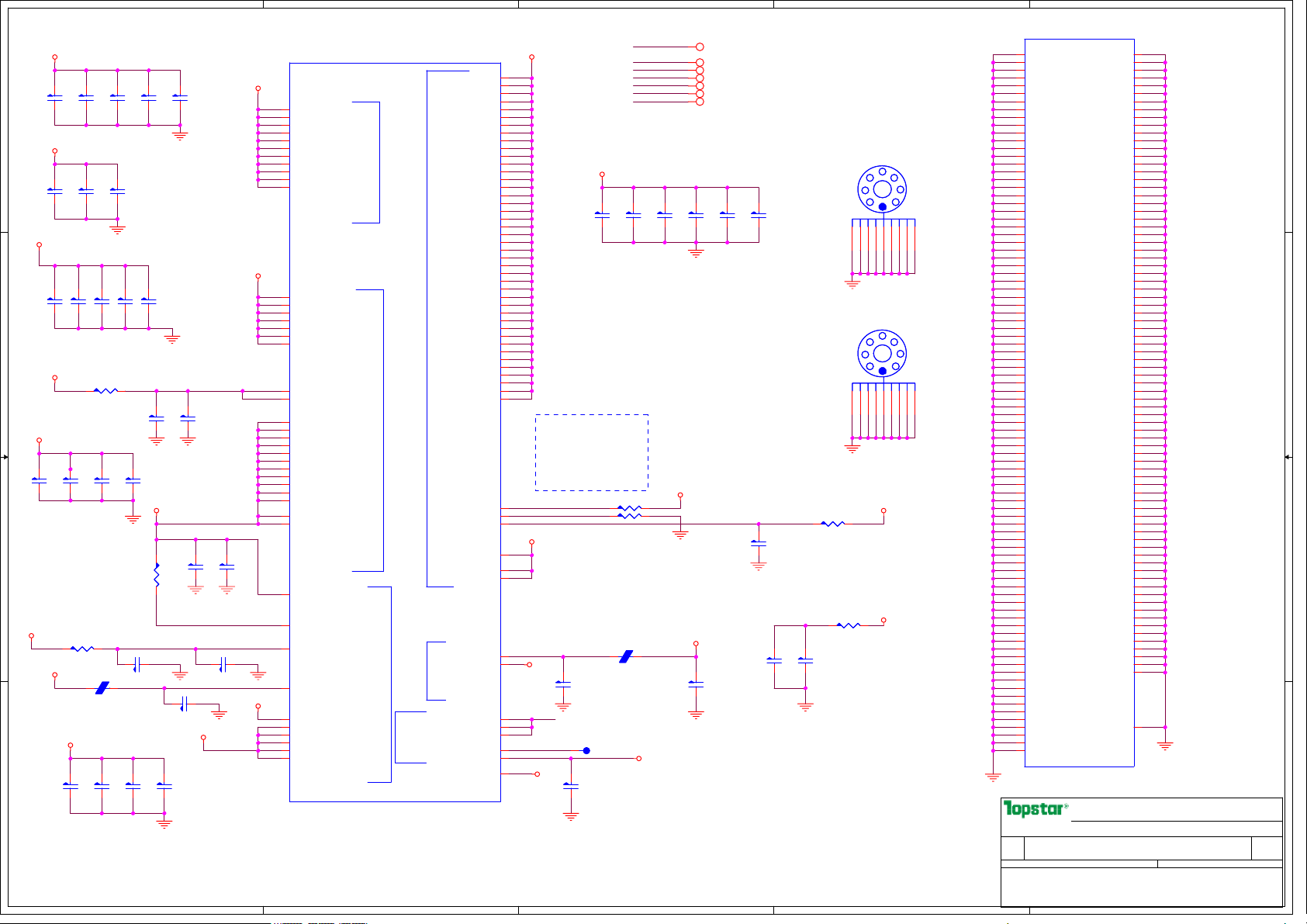

D D

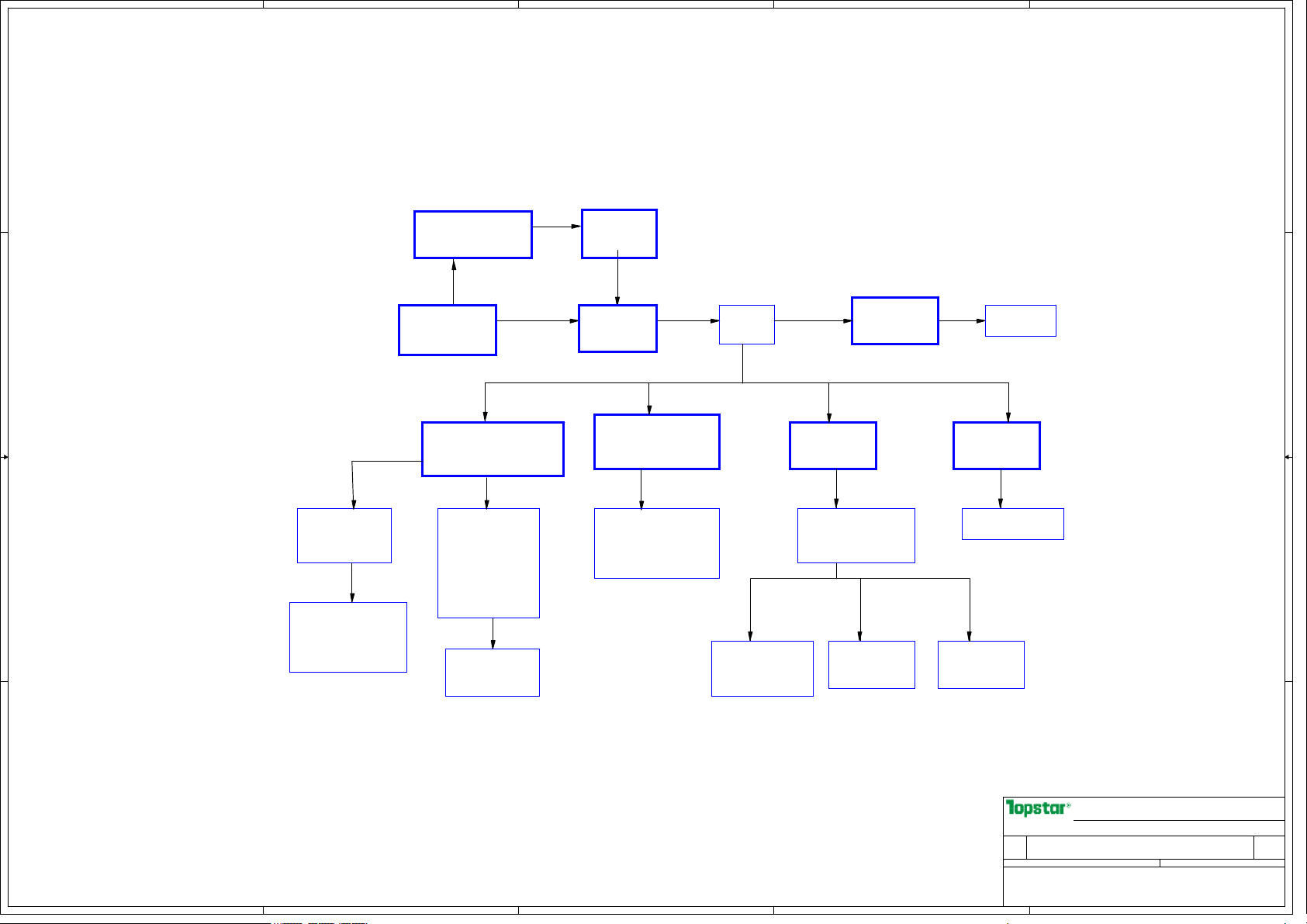

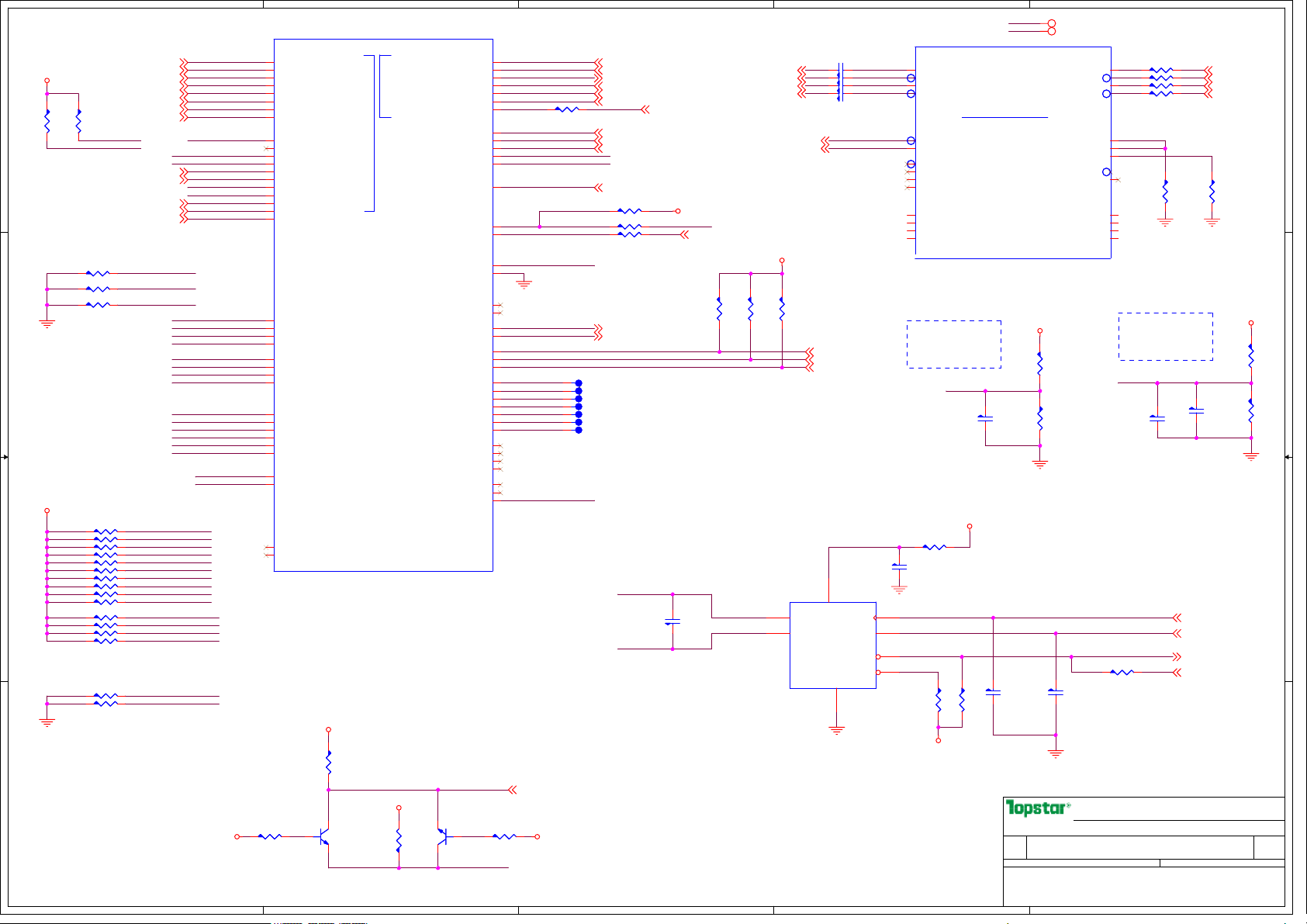

X01 POWER BLOCK Ver:A

Charger power

ISL6251

Battery

11V-12.6V

4A

Adapter

19V 2.1A

C C

40W

Always power

TPS51125

+V5AL 5A,

Cam 0.5A

VCC5refP 10mA

USB(3.5A)

B B

MOSFET

Switch

+V3.3AL,5A

PCIE(1.6A)

Disply(0.08A)

Clock(0.5A)

TGP(0.43A)

LAN(0.2A)

EC,Audio(0.055A)

+V5S 1.5A,

Audio etc (0.5A)

Cam 0.5A

FAN 0.3A

CRT ??

MOSFET

Switch

+V3.3S,4A

LCDVDD 0.5A

Power

Switch

Chipset Power

TPS51218

+V1.05S,3.085A

DMI(0.48A)

DDRAnalog(1.32A)

GIO,DPLLetc(0.33A)

TPT(0.995A)

+VDC

MOSFET

Switch

+V1.8S ( 0.5A)

DMI SFR (0.1A)

LVD(0.06A)

HD(?)

DDR Power

TPS51218

+V1.8 (5.5A)

PLL(0.3A)

DDRIO(0.82A)

DDRII SODIMM0(1.3A)

VCC_CORE

TPS51218

LDO

+V1.5S (1.5A)

ICH (0.85A)

GFX Power

TPS51218

+0.89S ( 1.38A)

GFX

LDO

APL5331APL5331

+V0.9S( 1A)

DDRII SODIMM0CFUSFR (0.15A)

+VCC_CORE

1.1V(4A)

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

the expressed written consent of TOPSTAR

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

PWR Block & description

PWR Block & description

PWR Block & description

Swain Xu( )

Swain Xu( )

Swain Xu( )

X01

X01

X01

1

许沐锌

许沐锌

许沐锌

B

B

339Tuesday, September 29, 2009

339Tuesday, September 29, 2009

339Tuesday, September 29, 2009

B

of

of

of

5

A

4

3

2

1

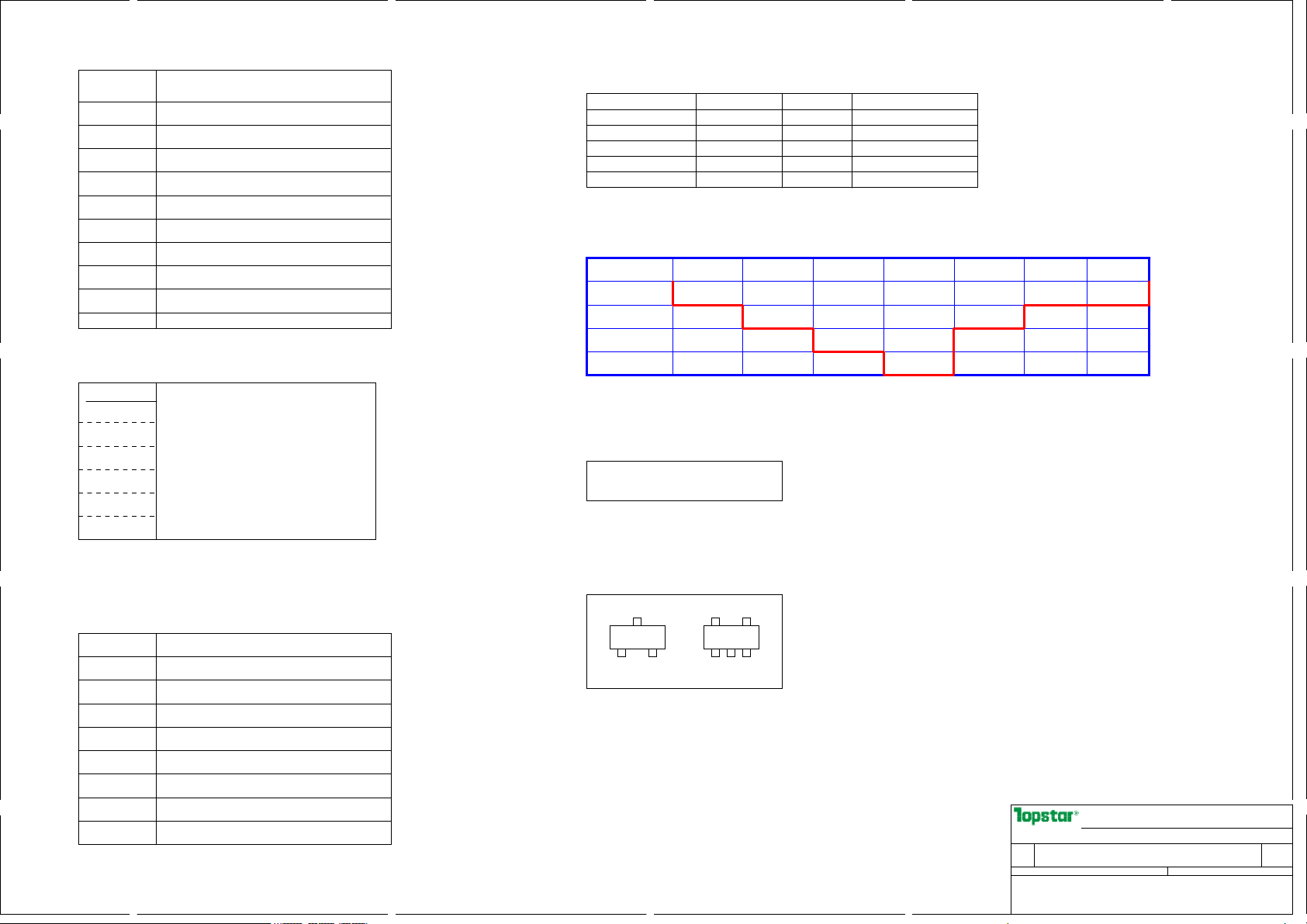

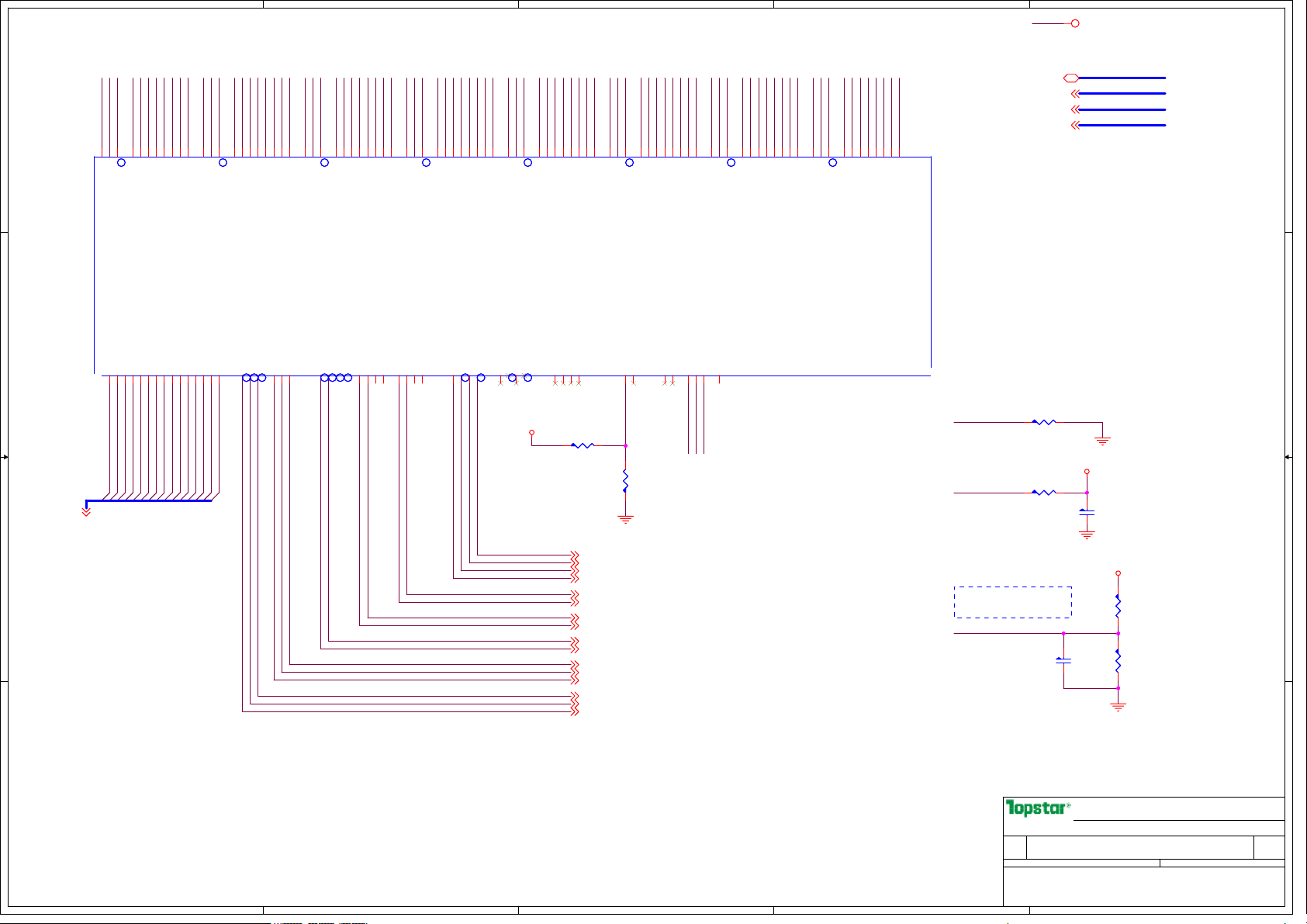

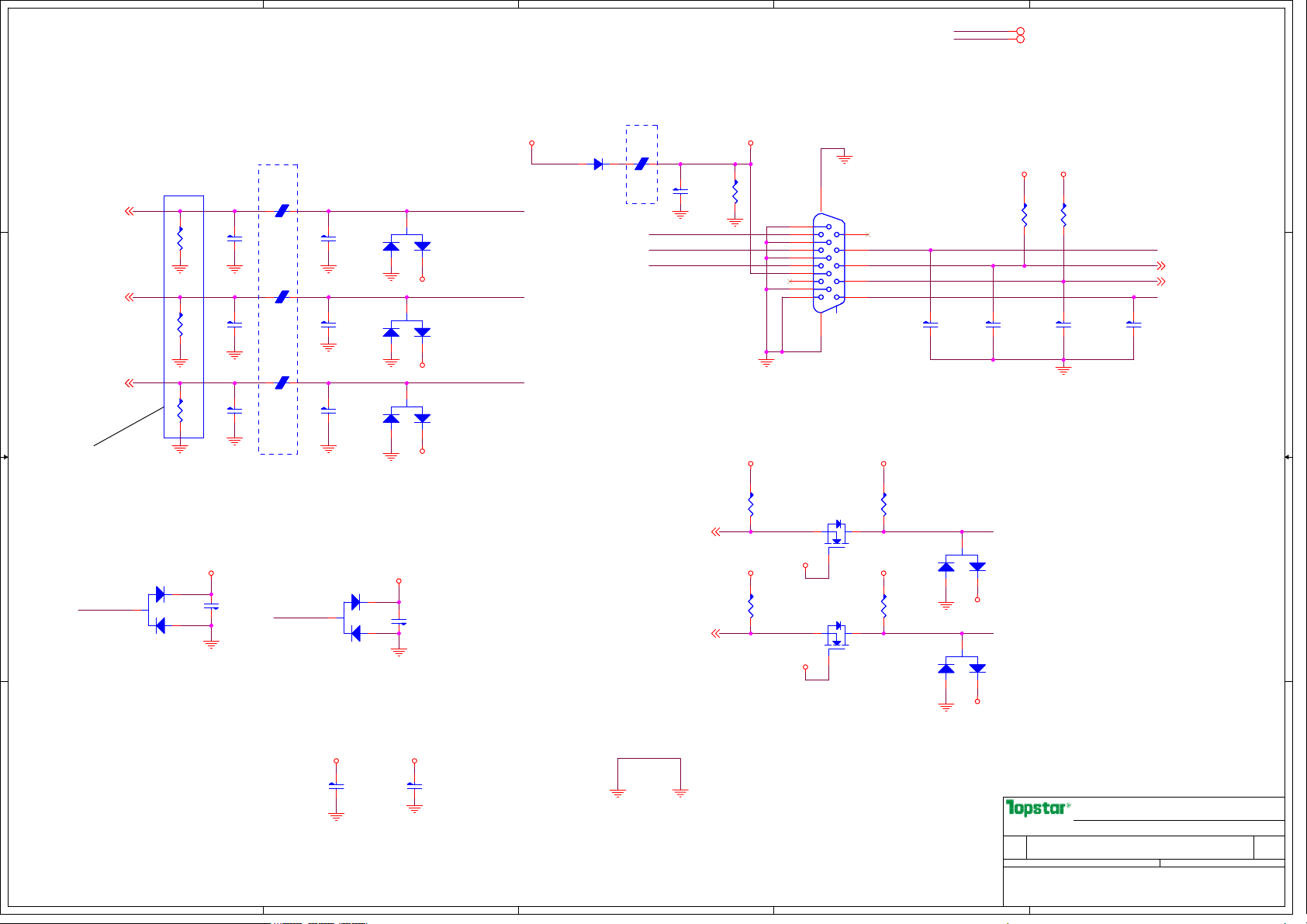

Voltage Rails

+VDC

D D

+VBATTERY

+VCC_CORE

+V1.05S

+V1.8

+V0.9S

+V3.3AL

+V5AL

+V3.3S

+V5S

+V0.89S 0.89V power rail for Pineview Graphics core

Primary DC system power supply (6V-9.5V)

Battery Power supply (6-8.4V)

Core Voltage for CPU

1.05V for Calistoga & ICH7M core / FSB VTT

1.8V power rail for DDR2

0.9V DDR2 Termination voltage

3.3V always on power rail

5V for ICH7-M's VCC5 Refsus

3.3V main power rail

5V main power rail

C C

Board stack up description

PCB Layers

Top(Signal1)

VCC 2

Signal 3

Signal4

Ground 5

Bottom(Signal6)

Trace Impedence:55ohm +/-15%

I2C SMB Address

Device

Clock Generator

SO-DIMM0

CPU Thermal Sensor

Smart Battery

PCIE Slot

Power States

Signal

S0(Full On)

S3(STM)

S4(STD)

S5(SoftOff)

SLP_S3#

HIGH

LOW

LOW OFF

LOW

Wake up Events

LID switch from EC

Power switch from EC

Address Hex

1101 001x

1010 000x

1001 100x

0001 011x

TBD

SLP_S4#

D2

A0

98

16

TBD

HIGH

HIGH ON OFF

LOW

LOW

SLP_S5#

HIGH

HIGH

HIGH

LOW

Master

ICH7-M

ICH7-M

KBC

KBC

ICH7-M

+V*ALW

ON

ON

ON

+V*

ON ON

ON

OFF

+V*S

OFF

OFF

OFF

Clock

ON

OFF

OFF

B B

USB Table

USB Port#

0

1

2

3

4

5

6

7

Function Description

Standard USB2.0 Port

Standard USB2.0 Port

Standard USB2.0 Port

MINICARD_USB

CAM_USB

MINICARD_USB

CR_USB

NC

PCB Footprints

3

SOT23

1 2

5

SOT23_5

3

21

4

ns: Component marked "ns" is not stuff

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

Swain Xu( )

Swain Xu( )

许沐锌

许沐锌

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

NOTE

NOTE

NOTE

X01

X01

X01

许沐锌

439Tuesday, September 29, 2009

439Tuesday, September 29, 2009

439Tuesday, September 29, 2009

of

B

B

B

A

5

4

3

2

1

Schematic modify Item and history:

D D

C C

B B

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

the expressed written consent of TOPSTAR

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

Swain Xu( )

Swain Xu( )

许沐锌

许沐锌

许沐锌

Sch Modify and history

Sch Modify and history

Sch Modify and history

X01

X01

X01

1

B

B

539Tuesday, September 29, 2009

539Tuesday, September 29, 2009

539Tuesday, September 29, 2009

B

of

of

of

5

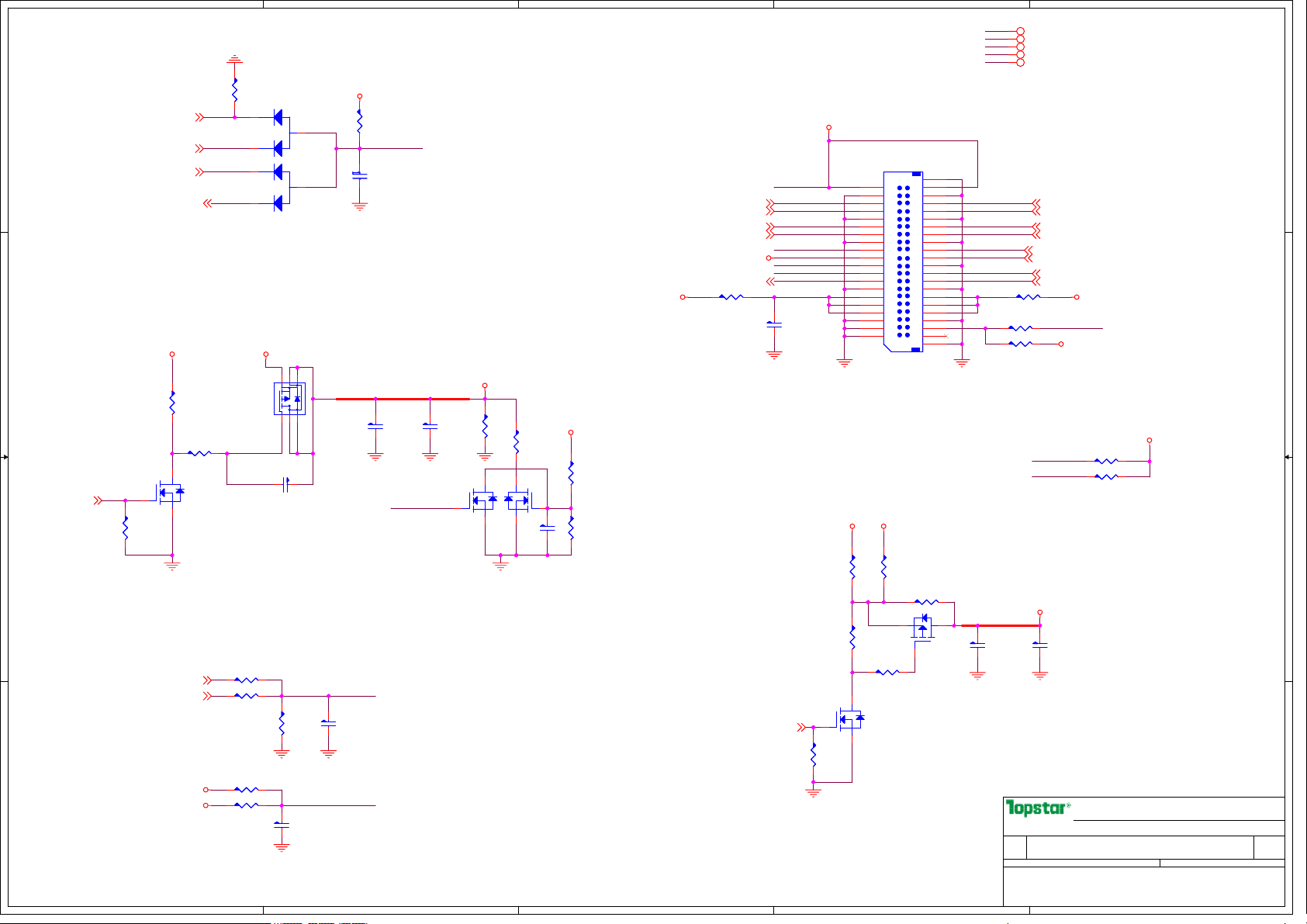

+V3.3S

FB7

FB7

100ohm@100MHz,3A

100ohm@100MHz,3A

FB0805

FB0805

1 2

D D

C98

C98

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

+V3.3S

FB8

FB8

100ohm@100MHz,3A

100ohm@100MHz,3A

FB0805

FB0805

1 2

C106

C106

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C C

B B

C117

C117

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C103

C103

4.7UF/10V,Y5V

4.7UF/10V,Y5V

C0805

C0805

C100

C100

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C99

C99

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C105

C105

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C104

C104

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

ns

ns

C116

C116

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C92

C92

0.047uF/16V,X7R

0.047uF/16V,X7R

C0402

C0402

C119

C119

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C120

C120

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C94

C94

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C95

C95

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

+VDDIO_CLK

+VDDIO_CLK

C115

C115

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C118

C118

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C93

C93

0.047uF/16V,X7R

0.047uF/16V,X7R

C0402

C0402

+VDDIO_CLK

+VDDIO_CLK

BUS FREQUENCE SELECT

+V1.05S

C293

C293

0.1UF/25V,Y5V

R302

56

56

R0402

R0402

ns

ns

CPU_BSEL07

CPU_BSEL17

CPU_BSEL27

A A

R270 0 R0402R270 0 R0402

R275 0 R0402R275 0 R0402 R272 1K R0402R272 1K R0402

R274 0 R0402R274 0 R0402

R303

R303

1K

1K

R0402

R0402

ns

ns

1K

1K

R0402

R0402

ns

ns

R381

R381

0

0

R0402

R0402

ns

ns

1K

1K

R0402

R0402

ns

ns

R392

R392

0

0

R0402

R0402

ns

ns

R383

R383

R382

R382

R302

0.1UF/25V,Y5V

C0402

C0402

CLK_BSEL0

R271 1K R0402R271 1K R0402

CLK_BSEL1

CLK_BSEL2

R273 1K R0402R273 1K R0402

FSC FSB FSA HOST Clock

BSEL2 BSEL1 BSEL0 frequency

0 1 1 166MHz

0 0 1 133MHz

1 0 1 100MHz

5

4

+V3.3S_CK_VDD

C97

C97

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

C96

C96

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

MCH_BSEL0 9

MCH_BSEL1 9

MCH_BSEL2 9

4

C303

C303

27pF/50V,NPO

27pF/50V,NPO

C0402

C0402

C301

C301

27pF/50V,NPO

27pF/50V,NPO

C0402

C0402

update Y6 footprint

许沐锌

PCI_CLK_EC22

PCI_CLK_DEBUG17

PCI_CLK_ICH14

CR_USB4820

CLK_USB4814

CLK_ICH1415

CLK_XTAL_IN

Y6

Y6

2 1

14.318MHz

14.318MHz

XS4_5032_0D8

XS4_5032_0D8

090917

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

43

CLK_XTAL_OUT

CK505_CLK_EN#15,32

27M_SEL

3

+V3.3S_CK_VDD

+VDDIO_CLK

+VDDIO_CLK

+VDDIO_CLK

+VDDIO_CLK

R313 22 R0402R313 22 R0402

R312 22 R0402R312 22 R0402

R311 22 R0402R311 22 R0402

R299 10K R0402R299 10K R0402

Set to SRC8

R316 22 R0402R316 22 R0402

R310 22 R0402R310 22 R0402

R304 2.2K R0402R304 2.2K R0402

R384 10K R0402R384 10K R0402

R395 22 R0402R395 22 R0402

R139

R139

1K

1K

R0402

R0402

ns

ns

+V3.3S

R301

R301

10K

10K

R0402

R0402

ns

ns

R300

R300

10K

10K

R0402

R0402

3

U14

U14

ICS9LPRS365

ICS9LPRS365

TSSOP64_0D5_6D1

TSSOP64_0D5_6D1

2

9

16

61

39

55

12

20

26

36

45

49

1

R131

R131

10K

10K

R0402

R0402

ns

ns

+V3.3S

3

2

3

4

5

6

7

60

59

10

57

62

8

11

15

19

52

23

29

58

42

Q2

Q2

2N7002

2N7002

SOT23

SOT23

ns

ns

TME

27M_SEL

PCIF_ITP_EN

CLK_XTAL_IN

CLK_XTAL_OUT

No more than 500 mil

1

VDD_PCI

VDD_48

VDD_PLL3

VDD_REF

VDD_SRC

VDD_CPU

VDD_IO

VDD_PLL3_IO

VDD_SRC_IO_1

VDD_SRC_IO_2

VDD_SRC_IO_3

VDD_CPU_IO

PCI0/OE#_0/2_A

PCI1/OE#_1/4_A

PCI2/TME

PCI3/FSD

PCI4/SRC5_SEL

PCIF5/ITP_EN

XTAL_IN

XTAL_OUT

USB_48/FSA

FSB/TEST_MODE

REF0/FSC/TEST_SEL

VSS_PCI

VSS_48

VSS_IO

VSS_PLL3

VSS_CPU

VSS_SRC_1

VSS_SRC_2

VSS_REF

VSS_SRC3

VR_CLK_EN

SRC5#/CPU_STOP#

CK_PWRGD/PWRDWN#

C129

C129

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

ns

ns

IO_VOUT

SMB_DATA

SMB_CLK

SRC5/PCI_STOP#

CPU0

CPU0#

CPU1

CPU1#

SRC8/CPU2_ITP

SRC8#/CPU2#_ITP

SRC10

SRC10#

SRC11/OE#_10

SRC11#/OE#_9

SRC9

SRC9#

SRC7/OE#_8

SRC7#/OE#_6

SRC6

SRC6#

SRC4

SRC4#

SRC3/OE#_0/2_B

SRC3#/OE#_1/4_B

SRC2/SATA

SRC2#/SATA#

SRC1/SE1

SRC1#/SE2

SRC0/DOT96

SRC0#/DOT96#

R130

R130

10K

10K

R0402

R0402

ns

ns

+V1.05S

C133

C133

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

2

+V3.3S 7,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,27,28,29,30,31,32

+V1.05S 7,10,15,16,20,21,28,29,31

SMBUS ADD:1101 001X

48

63

64

38

37

54

53

51

50

47

46

34

35

33

32

30

31

44

43

41

40

27

28

24

25

21

22

17

18

13

14

56

EMI CAP

R385 0 R0402R385 0 R0402

R386 0 R0402R386 0 R0402

R372 0 R0402R372 0 R0402

R373 0 R0402R373 0 R0402

CPU0

CPU#0

CPU1

CPU#1

MPCIE_CLKREQ

MCH_CLKREQ

VR_CLK_EN

Remove all 4P2R resitor

许沐锌

2

R375 475,1% R0402 nsR375 475,1% R0402 ns

R380 475,1% R0402 nsR380 475,1% R0402 ns

R512 0 R0402R512 0 R0402

090918

Page Name

Page Name

Page Name

Size

Size

Size

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

1

SMB_DATA_S 13,16,17,18

SMB_CLK_S 13,16,17,18

PM_STP_PCI# 15

PM_STP_CPU# 15

CLK_CPU_BCLK 7

CLK_CPU_BCLK# 7

CLK_MCH_BCLK 9

CLK_MCH_BCLK# 9

CLK_PCIE_EXPCARD2 18

CLK_PCIE_EXPCARD2# 18

CLK_PCIE_EXPCARD 17

CLK_PCIE_EXPCARD# 17

PCIE_CLKREQ# 17

CLK_MCH_EXP 7

CLK_MCH_EXP# 7

PCIE_CLKREQ2# 18

DREFSSCLK 9

DREFSSCLK# 9

CLK_PCIE_ICH 14

CLK_PCIE_ICH# 14

CLK_PCIE_LAN 23

CLK_PCIE_LAN# 23

CLK_ICH_SATA 15

CLK_ICH_SATA# 15

CLK_PCIE_HD 14

CLK_PCIE_HD# 14

DREFCLK 9

DREFCLK# 9

CK505_CLK_EN# 15,32

CLK_ICH14

CLK_USB48

PCI_CLK_DEBUG

PCI_CLK_EC

PCI_CLK_ICH

MCH_CLKREQ

MPCIE_CLKREQ

TME

Project Name Rev

Project Name Rev

Project Name Rev

C313 10PF/50V,NPO ns

C313 10PF/50V,NPO ns

C0402

C0402

C295 10PF/50V,NPO ns

C295 10PF/50V,NPO ns

C0402

C0402

C291 10PF/50V,NPO ns

C291 10PF/50V,NPO ns

C0402

C0402

C292 10PF/50V,NPO ns

C292 10PF/50V,NPO ns

C0402

C0402

C294 10PF/50V,NPO ns

C294 10PF/50V,NPO ns

C0402

C0402

R315 10K R0402R315 10K R0402

R389 10K R0402R389 10K R0402

R314 10K R0402R314 10K R0402

0:Normal mode

1:No Overclocking

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

Swain Xu( )

Swain Xu( )

许沐锌

许沐锌

许沐锌

CK505M

CK505M

CK505M

X01

X01

X01

1

+V3.3S

639Tuesday, September 29, 2009

639Tuesday, September 29, 2009

639Tuesday, September 29, 2009

of

of

of

B

B

B

5

U3D

U3D

LVD_A_CLK_DN12

+V3.3S

R37

R37

2.2K

D D

C C

B B

A A

2.2K

R0402

R0402

NOTE

Place Resistor close to PNV

+V1.05S

R257 51 R0402nsR257 51 R0402ns

R249 51 R0402nsR249 51 R0402ns

R238 51 R0402nsR238 51 R0402ns

R250 51 R0402nsR250 51 R0402ns

R246 51 R0402nsR246 51 R0402ns

R243 51 R0402nsR243 51 R0402ns

R234 51 R0402nsR234 51 R0402ns

R233 51 R0402nsR233 51 R0402ns

R255 51 R0402nsR255 51 R0402ns

R244 51 R0402R244 51 R0402

LVD_A_CLK_DP12

LVD_A_DATA0_DN12

LVD_A_DATA0_DP12

LVD_A_DATA1_DN12

LVD_A_DATA1_DP12

LVD_A_DATA2_DN12

R50

R50

LVD_A_DATA2_DP12

2.2K

2.2K

R0402

R0402

LCTLA_CLK

LCTLA_DATA

LVDS_BKLTEN12,22

LBKLT_CTL12

LDDC_CLK12

LDDC_DATA12

LVDD_EN12

R55 2.37K,1%

R55 2.37K,1%

R0402

R0402

R49 0 R0402R49 0 R0402

R56 0 R0402R56 0 R0402

R266 62 R0603R266 62 R0603

R236 51 R0402R236 51 R0402

R248 51 R0402R248 51 R0402

R254 51 R0402R254 51 R0402

R251 51 R0402R251 51 R0402

R247 51 R0402R247 51 R0402

LVD_VREFH_OUT_R

LVD_VREFL_OUT_R

LVD_IBG

LVD_VREFH_OUT_R

LVD_VREFL_OUT_R

H_BPM_N0

H_BPM_N1

H_BPM_N2

H_BPM_N3

H_BPM2_N0

H_BPM2_N1

H_BPM2_N2

H_BPM2_N3

H_BPM4_PRDY#

H_BPM5_PRDQ#

CPU_RSVD

H_TDI

H_TMS

H_TDO

H_TCK

H_TRST#

5

LVD_IBG

LCTLA_CLK

LCTLA_DATA

H_BPM_N0

H_BPM_N1

H_BPM_N2

H_BPM_N3

H_BPM2_N0

H_BPM2_N1

H_BPM2_N2

H_BPM2_N3

CPU_RSVD

H_TDI

H_TDO

H_TCK

H_TMS

H_TRST#

H_THERMDA

H_THERMDC

+V1.05S

U25

LVD_A_CLKM

U26

LVD_A_CLKP

R23

LVD_A_DATAM_0

R24

LVD_A_DATAP_0

N26

LVD_A_DATAM_1

N27

LVD_A_DATAP_1

R26

LVD_A_DATAM_2

R27

LVD_A_DATAP_2

R22

LVD_IBG

J28

LVD_VBG

N22

LVD_VREFH

N23

LVD_VREFL

L27

LBKLT_EN

L26

LBKLT_CTL

L23

LCTLA_CLK

K25

LCTLB_CLK

K23

LDDC_CLK

K24

LDDC_DATA

H26

LVDD_EN

PNV_22MM_REV1P10

PNV_22MM_REV1P10

G11

BPM_1B_0

E15

BPM_1B_1

G13

BPM_1B_2

F13

BPM_1B_3

B18

BPM_2_0#/RSVD

B20

BPM_2_1#/RSVD

C20

BPM_2_2#/RSVD

B21

BPM_2_3#/RSVD

G5

RSVD_G5

D14

TDI

D13

TDO

B14

TCK

C14

TMS

C16

TRST_B

D30

THRMDA_1

E30

THRMDC_1

C30

RSVD_C30

D31

RSVD_D31

R241

R241

1K

1K

R0402

R0402

R229

R229

10K

10K

R0402

R0402

1

+V3.3S

Q15

Q15

MMBT3904-F

MMBT3904-F

SOT23

SOT23

2 3

PINEVIEW_M

PINEVIEW_M

?

?

REV = 1.1

REV = 1.1

LVDS

LVDS

4

ICH

ICH

CPU

CPU

+V1.05S

4

R230

R230

1K

1K

R0402

R0402

SMI_B

A20M_B

FERR_B

LINT00

LINT10

IGNNE_B

STPCLK_B

DPRSTP_B

DPSLP_B

INIT_B

PRDY_B

PREQ_B

THERMTRIP_B

PROCHOT_B

CPUPWRGOOD

GTLREF

VSS

RSVD_L6

RSVD_E17

BCLKN

BCLKP

BSEL_0

BSEL_1

BSEL_2

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

RSVD_L7

RSVD_D20

RSVD_H13

RSVD_D18

RSVD_TP_K9

RSVD_TP_D19

EXTBGREF

4 OF 6

4 OF 6

?

?

Q16

Q16

MMBT3904-F

MMBT3904-F

23

SOT23

SOT23

1

VR_PROCHOT#

E7

H7

H6

F10

F11

E5

F8

G6

G10

G8

E11

F15

E13

C18

W1

A13

H27

L6

E17

H10

J10

K5

H5

K6

H30

H29

H28

G30

G29

F29

E29

L7

D20

H13

D18

K9

D19

K7

EC_PROCHOT# 22

R235

R235

1K

1K

R0402

R0402

R258 0 R0402R258 0 R0402

H_BPM4_PRDY#

H_BPM5_PRDQ#

GTLREF_EA

T6 ICTP nsT6 ICTP ns

T5 ICTP nsT5 ICTP ns

T7 ICTP nsT7 ICTP ns

T4 ICTP nsT4 ICTP ns

T3 ICTP nsT3 ICTP ns

T2 ICTP nsT2 ICTP ns

T1 ICTP nsT1 ICTP ns

EXTBGREF

+V1.05S

3

H_SMI# 15

H_A20M# 15

H_FERR# 15

H_INTR 15

H_NMI 15

H_IGNNE# 15

R245 68 R0402 nsR245 68 R0402 ns

R232 0 R0402R232 0 R0402

R62 0 R0402R62 0 R0402

CLK_CPU_BCLK# 6

CLK_CPU_BCLK 6

H_STPCLK# 15

H_DPRSTP# 15

H_DPSLP# 15

H_INIT# 15

PM_THRMTRIP# 15,21

PWROK 0 ohm

预留

, debug

电阻 以备 用

许沐锌

H_THERMDA

H_THERMDC

NOTE

1.H_THERMDA/C 10 MILS, ,

然后再包地处理

2.H_THERMDA/C 19V VGA

3

+V1.05S

VR_PROCHOT#

H_PWROK 15

R498

R498

470

470

R0402

R0402

C20

C20

2200pF/25V,X7R

2200pF/25V,X7R

C0402

C0402

2

DXP

3

DXN

G781

G781

ADM1032AR

ADM1032AR

LM86CIM

LM86CIM

MAX6657MSA

MAX6657MSA

SOIC-8

SOIC-8

U2

U2

F75393S

F75393S

SO8_50_150

SO8_50_150

C22 0.1uF/10V,X5RC22 0.1uF/10V,X5R

C21 0.1uF/10V,X5RC21 0.1uF/10V,X5R

C28 0.1uF/10V,X5RC28 0.1uF/10V,X5R

C26 0.1uF/10V,X5RC26 0.1uF/10V,X5R

CPU_BSEL0 6

CPU_BSEL1 6

CPU_BSEL2 6

1

SMBCLK

VCC

SMBDATA

ALERT#

THERM#

GND

5

DMI_TXP014

DMI_TXN014

DMI_TXP114

DMI_TXN114

CLK_MCH_EXP#6

CLK_MCH_EXP6

+V1.05S

R499

R499

R500

R500

470

470

470

470

R0402

R0402

R0402

R0402

线宽 并配对走线

.

走线远离 及 或高速线走线

2

F3

F2

H4

G3

N7

N6

R10

R9

N10

N9

K2

J1

M4

L3

8

7

6

THERM#

4

2

PINEVIEW_M

EXTBGREF

+V3.3S

PINEVIEW_M

C238

C238

C0402

C0402

?

?

REV = 1.1

REV = 1.1

DMI

DMI

+V1.05S

R268

R268

976,1%

976,1%

R0402

R0402

1uF/10V,Y5V

1uF/10V,Y5V

EXP_RCOMPO

RSVD_TP_N11

RSVD_TP_P11

R269

R269

3.32K,1%

3.32K,1%

R0402

R0402

U3A

U3A

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

EXP_CLKINN

EXP_CLKINP

RSVD_R10

RSVD_R9

RSVD_N10

RSVD_N9

RSVD_K2

RSVD_J1

RSVD_M4

RSVD_L3

PNV_22MM_REV1P10

PNV_22MM_REV1P10

Note:

GTLREF MAX TRACE

length of 500 Mil

and 5 Mil spacing

R15

R15

220

220

R0402

R0402

C17

C17

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

EC SMBUS ADD:1001 100X

C18

R31

R31

10K

10K

R0402

R0402

+V3.3S

C18

27pF/50V,NPO

27pF/50V,NPO

R26

R26

C0402

C0402

10K

10K

R0402

R0402

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

1

+V1.05S 6,10,15,16,20,21,28,29,31

+V3.3S 6,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,27,28,29,30,31,32

R28 0 R0402R28 0 R0402

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

EXP_ICOMPI

EXP_RBIAS

RSVD_K3

RSVD_L2

RSVD_M2

RSVD_N2

1 OF 6

1 OF 6

?

?

R27 0 R0402

R27 0 R0402

C19

C19

27pF/50V,NPO

27pF/50V,NPO

C0402

C0402

G2

R29 0 R0402R29 0 R0402

G1

R39 0 R0402R39 0 R0402

H3

R45 0 R0402R45 0 R0402

J2

L10

L9

L8

N11

P11

K3

L2

M2

N2

Note:

CPU GTLREF need to be

2/3 of VCCP1 1.05V

please near GTLREF's pin

GTLREF_EA

C220

C220

C0402

C0402

ns

ns

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

Swain Xu( )

Swain Xu( )

许沐锌

许沐锌

许沐锌

Diamondville(1of2)(Host BUS)

Diamondville(1of2)(Host BUS)

Diamondville(1of2)(Host BUS)

X01

X01

X01

1

DMI_RXP0 14

DMI_RXN0 14

DMI_RXP1 14

DMI_RXN1 14

R277

R277

49.9,1%

49.9,1%

R0402

R0402

1K,1%

1K,1%

R0402

R0402

C221

C221

C0402

C0402

2K,1%

2K,1%

R0402

R0402

1uF/10V,Y5V

1uF/10V,Y5V

220pF/50V,X7R

220pF/50V,X7R

I2C_CLK 22

I2C_DATA 22

OVT_SHUTDOWN# 21

PM_THRM# 15

739Tuesday, September 29, 2009

739Tuesday, September 29, 2009

739Tuesday, September 29, 2009

of

of

of

R278

R278

750

750

R0402

R0402

R253

R253

R252

R252

+V1.05S

B

B

B

5

D D

MA_DQS#0

MA_DQS0

AD3

DDR_A_DQS_0

PINEVIEW_M

PINEVIEW_M

C C

MA_A_A0

MA_A_A[14:0]13

AD2

AH19

MA_DM0

AD4

DDR_A_DQSB_0

DDR_A_MA_0

AJ18

MA_A_A1

DDR_A_DM_0

DDR_A_MA_1

AK18

MA_A_A2

MA_DATA1

MA_DATA0

AC4

DDR_A_DQ_0

DDR_A_MA_2

DDR_A_MA_3

AK16

MA_A_A3

MA_A_A4

MA_DATA2

AC1

DDR_A_DQ_1

DDR_A_MA_4

AJ14

MA_A_A5

MA_DATA3

AF4

AG2

DDR_A_DQ_2

DDR_A_MA_5

AK14

AH14

MA_A_A6

MA_DATA5

MA_DATA4

AB2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_MA_6

DDR_A_MA_7

AJ12

MA_A_A7

MA_A_A8

MA_DATA6

AB3

AE2

DDR_A_DQ_5

DDR_A_MA_8

AK12

AH13

MA_A_A9

MA_DATA7

AE3

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_MA_9

DDR_A_MA_10

AK20

MA_A_A10

MA_A_A11

MA_DQS1

DDR_A_MA_11

AH12

MA_A_A12

MA_DQS#1

AB8

DDR_A_DQS_1

DDR_A_MA_12

AJ11

MA_A_A13

MA_DM1

AD7

DDR_A_DQSB_1

DDR_A_MA_13

AJ24

MA_A_A14

AA9

AJ10

DDR_A_DM_1

DDR_A_MA_14

MA_DATA9

MA_DATA8

AB6

AB7

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_WEB

AK22

MA_DATA12

MA_DATA10

MA_DATA11

AE5

AG5

AA5

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_CASB

DDR_A_RASB

AJ22

AK21

MA_DATA13

MA_DATA14

AB5

AB9

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_BS_0

AJ20

AH20

MA_DATA15

AD6

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_BS_1

DDR_A_BS_2

AK11

MA_DATA17

MA_DATA16

MA_DQS#2

MA_DQS2

MA_DM2

AE8

AD8

AG8

AG7

AD10

DDR_A_DM_2

DDR_A_DQ_16

DDR_A_DQS_2

DDR_A_DQSB_2

DDR_A_CSB_0

DDR_A_CSB_1

DDR_A_CSB_2

AJ21

AJ25

AK25

AH22

MA_DATA18

MA_DATA19

AF10

AG11

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_CSB_3

AH10

MA_DATA21

MA_DATA20

AF7

AF8

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_CKE_0

DDR_A_CKE_1

AH9

AK10

4

MA_DATA22

MA_DATA23

AD11

AE10

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_CKE_2

DDR_A_CKE_3

AJ8

DDR_A_DQ_23

DDR_A_ODT_0

AK24

3

MA_DATA27

MA_DATA24

MA_DATA25

MA_DQS#3

MA_DQS3

MA_DM3

AJ3

AK5

AH1

AK3

DDR_A_DM_3

DDR_A_DQ_24

DDR_A_DQS_3

DDR_A_DQSB_3

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

AK27

AH26

AH24

MA_DATA26

AJ2

AK6

DDR_A_DQ_25

AG15

MA_DATA28

AJ7

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_CK_0

DDR_A_CKB_0

AF15

MA_DATA29

AF3

AH2

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_CK_1

DDR_A_CKB_1

AD13

AC13

MA_DATA31

MA_DATA30

AL5

DDR_A_DQ_30

AJ6

DDR_A_DQ_31

MA_DATA32

MA_DATA33

MA_DATA37

MA_DATA39

MA_DATA35

MA_DATA36

MA_DATA34

AE19

DDR_A_DQ_32

AG19

DDR_A_DQ_33

R71

AF22

DDR_A_DQ_34

RSVD_AD17

AD17

AD22

DDR_A_DQ_35

RSVD_AC17

AC17

AG17

DDR_A_DQ_36

RSVD_AB15

AB15

10K

10K

MA_DATA38

AF19

AE21

DDR_A_DQ_37

DDR_A_DQ_38

RSVD_AB17

AB17

R0402R71

R0402

MA_DQS#4

MA_DQS4

MA_DM4

AD19

AG22

AG21

DDR_A_DM_4

DDR_A_DQS_4

DDR_A_DQSB_4

DDR_A_CK_3

DDR_A_CKB_3

DDR_A_CK_4

DDR_A_CKB_4

AF13

AC15

AD15

AG13

+V1.8

AD21

DDR_A_DQ_39

MA_DATA40

MA_DQS#5

MA_DQS5

MA_DM5

AJ27

AE26

AG27

DDR_A_DM_5

DDR_A_DQS_5

DDR_A_DQSB_5

VSS

RSVD_AK8

AB4

AK8

R69

R69

0

0

R0402

R0402

ns

ns

MA_DATA46

MA_DATA44

MA_DATA45

MA_DATA43

MA_DATA42

MA_DATA41

AE24

DDR_A_DQ_40

MA_DATA47

MA_DQS#6

MA_DQS6

AC22

DDR_A_DQ_43

DDR_A_DQ_44

RSVD_TP_AB11

RSVD_TP_AB13

AB13

AG24

AD27

DDR_A_DQ_45

DDR_A_DQ_46

DDR_VREF

AL28

DDR_VREF

090602

AE27

DDR_A_DQ_47

DDR_RPD

AK28

DDR_RPD

AE30

DDR_A_DQS_6

DDR_RPU

AJ26

DDR_RPU

AG25

AD25

AD24

DDR_A_DQ_41

DDR_A_DQ_42

AB11

Add R915 10K Follow CRB 1.0

许沐锌

AD28

DDR_A_DQ_55

MA_DATA56

MA_DATA57

MA_DQS#7

MA_DQS7

MA_DM7

AB26

AB27

AA24

AB25

AA27

DDR_A_DM_7

DDR_A_DQ_56

DDR_A_DQS_7

DDR_A_DQSB_7

MA_DATA53

MA_DATA51

MA_DATA52

MA_DATA50

MA_DATA55

MA_DATA54

MA_DATA49

MA_DATA48

MA_DM6

AF30

AG31

AG30

AD30

AD29

AJ30

AJ29

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A

DDR_A

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

AE29

DDR_A_DQ_54

AF29

DDR_A_DM_6

DDR_A_DQSB_6

RSVD_AK29

AK29

MA_DATA58

MA_DATA59

W24

W22

DDR_A_DQ_57

DDR_A_DQ_58

MA_DATA60

MA_DATA61

AB24

AB23

DDR_A_DQ_59

DDR_A_DQ_60

2

MA_DATA63

MA_DATA62

AA23

W27

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

U3B

U3B

PNV_22MM_REV1P10

PNV_22MM_REV1P10

REV = 1.1

REV = 1.1

2 OF 6

2 OF 6

?

?

?

?

DDR_RPD

DDR_RPU

MA_DATA[63:0]13

MA_DQS#[7:0]13

MA_DQS[7:0]13

MA_DM[7:0]13

R82 80.6,1%

R82 80.6,1%

R0402

R0402

R81 80.6,1%

R81 80.6,1%

R0402

R0402

1

+V1.8 10,13,27,28,29,30,31

+V1.8

C270

C270

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

M_CLK_DDR#1 13

M_CLK_DDR1 13

B B

A A

5

4

M_CLK_DDR#0 13

M_CLK_DDR0 13

M_ODT1 13

M_ODT0 13

M_CKE1 13

M_CKE0 13

M_CS#1 13

M_CS#0 13

MA_A_BS#2 13

MA_A_BS#1 13

MA_A_BS#0 13

MA_A_RAS# 13

MA_A_CAS# 13

MA_A_WE# 13

Note:

COLSE TO MCH PIN ON MCH_VREF

DDR_VREF

C65

C65

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

3

2

the expressed written consent of TOPSTAR

+V1.8

R84

R84

1K,1%

1K,1%

R0402

R0402

R83

R83

1K,1%

1K,1%

R0402

R0402

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

Swain Xu( )

Swain Xu( )

Diamondville (PWR&GND)(2of2)

Diamondville (PWR&GND)(2of2)

Diamondville (PWR&GND)(2of2)

X01

X01

X01

1

许沐锌

许沐锌

许沐锌

B

B

B

of

of

of

839Tuesday, September 29, 2009

839Tuesday, September 29, 2009

839Tuesday, September 29, 2009

5

4

3

2

+V3.3S 6,7,10,11,12,13,14,15,16,17,18,19,20,21,22,23,27,28,29,30,31,32

1

PINEVIEW_M

U3C

U3C

MCH_BSEL06

MCH_BSEL16

D D

C C

B B

MCH_BSEL26

XDP_RSVD_5

XDP_RSVD_9

XDP_RSVD_11

XDP_RSVD_17

D12

XDP_RSVD_00

A7

XDP_RSVD_01

D6

XDP_RSVD_02

C5

XDP_RSVD_03

C7

XDP_RSVD_04

C6

XDP_RSVD_05

D8

XDP_RSVD_06

B7

XDP_RSVD_07

A9

XDP_RSVD_08

D9

XDP_RSVD_09

C8

XDP_RSVD_10

B8

XDP_RSVD_11

C10

XDP_RSVD_12

D10

XDP_RSVD_13

B11

XDP_RSVD_14

B10

XDP_RSVD_15

B12

XDP_RSVD_16

C11

XDP_RSVD_17

L11

RSVD_L11

PNV_22MM_REV1P10

PNV_22MM_REV1P10

AA7

RSVD_TP_AA7

AA6

RSVD_TP_AA6

R5

RSVD_TP_R5

R6

RSVD_TP_R6

AA21

RSVD_TP_AA21

W21

RSVD_TP_W21

T21

RSVD_TP_T21

V21

RSVD_TP_V21

PINEVIEW_M

?

?

REV = 1.1

REV = 1.1

VGA

VGA

PM_EXTTS#_1/DPRSLPVR

MISC

MISC

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

CRT_DDC_DATA

CRT_DDC_CLK

DAC_IREF

DPL_REFCLKINP

DPL_REFCLKINN

DPL_REFSSCLKINP

DPL_REFSSCLKINN

3 OF 6

3 OF 6

PM_EXTTS#_0

PWROK

RSTINB

HPL_CLKINN

HPL_CLKINP

M30

M29

N31

P30

P29

N30

L31

L30

P28

Y30

Y29

AA30

AA31

K29

?

?

J30

L5

AA3

W8

W9

Note:

HSYNC/VSYNC: Locate series

esistor strsps within 750 mil of MCH

R4210R0402 R4210R0402

R4110R0402 R4110R0402

CRT_RED 11

CRT_GREEN 11

CRT_BLUE 11

CRT_DDC_DATA 11

DACREFSET

R33 0 R0402R33 0 R0402

CRT_DDC_CLK 11

R70 665,1%R0402R70 665,1%R0402

DREFCLK 6

DREFCLK# 6

DREFSSCLK 6

DREFSSCLK# 6

R51 0 R0402R51 0 R0402

R64 0 R0402R64 0 R0402

CLK_MCH_BCLK# 6

CLK_MCH_BCLK 6

R240 1K,1% R0402 nsR240 1K,1% R0402 ns

R256 1K,1% R0402R256 1K,1% R0402

R239 1K,1% R0402 nsR239 1K,1% R0402 ns

R237 1K,1% R0402 nsR237 1K,1% R0402 ns

PM_DPRSLPVR 15

PM_EXTTS0# 13

BUF_PLT_RST# 14,15,17,18,22,23

CRT_HSYNC 11

CRT_VSYNC 11

R70 T ,

为 物料 需要修改

090513

许沐锌

update R70 to R0402

0900917

许沐锌

IMVP_PWRGD 15,22,32

XDP_RSVD_5

XDP_RSVD_9

XDP_RSVD_11

XDP_RSVD_17

注意这一点的命名

090514

许沐锌

+V3.3S

R30 10K R0402R30 10K R0402

CRT_DDC_DATA

CRT_DDC_CLK

R54 150,1% R0402R54 150,1% R0402

R60 150,1% R0402R60 150,1% R0402

R48 150,1% R0402R48 150,1% R0402

150ohm GMCH

走线阻抗

150ohm VGA

走线阻抗

PLACE 150 OHM

RESISTORS CLOSE TO

GMCH

PM_EXTTS0#

+V3.3S

CRT_BLUE

CRT_GREEN

CRT_RED

电阻到

37.5ohm

电阻到 口

50ohm

R35

R35

2.2K

2.2K

R0402

R0402

R36

R36

2.2K

2.2K

R0402

R0402

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

许沐锌

许沐锌

许沐锌

Swain Xu( )

Swain Xu( )

A A

5

4

3

2

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

Swain Xu( )

Calistoga(HOST)

Calistoga(HOST)

Calistoga(HOST)

X01

X01

X01

B

B

B

of

of

of

939Tuesday, September 29, 2009

939Tuesday, September 29, 2009

939Tuesday, September 29, 2009

1

5

+V0.89S

1.38A

C244

C244

C0402

C0402

ns

ns

0.1uF/10V,X5R

0.1uF/10V,X5R

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

0.35A

+V0.89S

+V1.8

+V3.3S

C248

C247

C247

C257

C257

C0402

C0402

C0402

C0402

D D

C C

B B

A A

+V1.8

+V1.05S

+V1.8S

C229

C229

C0805

C0805

1uF/10V,X5R

1uF/10V,X5R

+V0.89S

C250

C250

C0603

C0603

2.2UF/10V,X5R

2.2UF/10V,X5R

C276

C276

C271

C271

C0402

C0402

C0402

C0402

ns

ns

1uF/10V,X5R

1uF/10V,X5R

+V1.8

C242

C242

C0805

C0805

4.7uF/10V,X5R

4.7uF/10V,X5R

R75 0 R0805R75 0 R0805

+V1.8S

600ohm@100MHz,1.5A

600ohm@100MHz,1.5A

+V1.05S

C243

C243

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

C254

C254

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

C269

C269

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

R2830 R0805R2830 R0805

C153

C153

C0805

C0805

10uF/6.3V,X5R

10uF/6.3V,X5R

L1

L1

1 2

FB0805

FB0805

C233

C233

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

C248

C246

C246

C0402

C0402

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

C255

C255

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

C275

C275

C277

C277

C0402

C0402

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,X5R

+V1.8 2.3A共

C272

C272

C0805

C0805

C253

C253

C0402

C0402

+V1.05S

10uF/6.3V,X5R

10uF/6.3V,X5R

1uF/10V,X5R

1uF/10V,X5R

R280

R280

0

0

R0402

R0402

C54 1uF/10V,X5R

C54 1uF/10V,X5R

C0402

C0402

C41 1uF/10V,X5R

C41 1uF/10V,X5R

C263

C263

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

1uF/10V,Y5V

1uF/10V,Y5V

5

C256

C256

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

C274

C274

C0402

C0402

ns

ns

0.1uF/10V,X5R

0.1uF/10V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

1.4A

C228

C228

C0402

C0402

ns

ns

C56 1uF/10V,X5R

C56 1uF/10V,X5R

C0402

C0402

+V1.05S

C249

C249

C0402

C0402

1uF/10V,Y5V

1uF/10V,Y5V

W14

W16

W18

W19

AK13

AK19

AK9

AL11

AL16

AL21

AL25

AK7

AL7

U10

W10

W11

AA10

AA11

AA19

V11

AC31

A21

T13

T14

T16

T18

T19

V13

V19

T30

T31

J31

U5

U6

U7

U8

U9

V2

V3

V4

C3

B2

C2

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCCK_DDR

VCCCK_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCACK_DDR

VCCACK_DDR

VCCD_AB_DPL

VCCD_HMPLL

VCCSFR_AB_DPL

VCCACRTDAC

VCC_GIO

VCCRING_EAST

VCCRING_WEST

VCCRING_WEST

VCCRING_WEST

VCC_LGI_VID

U3E

U3E

PNV_22MM_REV1P10

PNV_22MM_REV1P10

PINEVIEW_M

PINEVIEW_M

GFX/MCH

GFX/MCH

DDR

DDR

4

?

?

REV = 1.1

REV = 1.1

EXP\CRT\PLL

EXP\CRT\PLL

4

POWER

POWER

DMI

DMI

VCCSFR_DMIHMPLL

CPU

CPU

LVDS

LVDS

5 OF 6

5 OF 6

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

?

?

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCSENSE

VSSSENSE

VCCA

VCC

VCCP

VCCP

VCCALVD

VCCDLVD

VCCA_DMI

VCCA_DMI

VCCA_DMI

RSVD

VCCP

+VCC_CORE

A23

A25

A27

4A

B23

B24

B25

B26

B27

C24

C26

D23

D24

D26

D28

E22

E24

E27

F21

F22

F25

G19

G21

G24

H17

H19

H22

H24

J17

J19

J21

J22

K15

K17

K21

L14

L16

L19

L21

N14

N16

N19

N21

Layout Note: VCCSENSE

and VSSSENSE lines

should be of equal

length

Route VCCSENSE and VSSSENSE

traces at 27.4 Ohms with 50

mil spacing

C29

B29

Y2

+V1.05S

D4

B4

B3

V30

W31

+V1.8S

C47

C47

C0805

C0805

10uF/6.3V,X5R

10uF/6.3V,X5R

VCCA_DMI

T1

T2

T3

P2

AA1

E2

+V1.05S

0.48A

T8 ICTP nsT8 ICTP ns

C48

C48

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

3

+V3.3S 6,7,9,11,12,13,14,15,16,17,18,19,20,21,22,23,27,28,29,30,31,32

+V1.8 8,13,27,28,29,30,31

+V1.05S 6,7,15,16,20,21,28,29,31

+V1.5S 14,16,17,18,28,29,31

+VCC_CORE 29,32

+V0.89S 28,31

+V1.8S 14,30

+VCC_CORE

C240

C234

C234

C0402

C0402

1uF/10V,Y5V

1uF/10V,Y5V

C231

C231

C0402

C0402

1uF/10V,Y5V

1uF/10V,Y5V

C230

C230

C0402

C0402

1uF/10V,Y5V

1uF/10V,Y5V

C240

C0402

C0402

1uF/10V,Y5V

1uF/10V,Y5V

C364

C364

C0805

C0805

10uF/6.3V,X5R

10uF/6.3V,X5R

Totol:

+VCC_CORE: 4A

+V0.89S : 1.38A

+V1.05S: 2.2A

+V1.5S: 0.15A

+V1.8: 2.3A

+V1.8S: 0.3A

+VCC_CORE

R16 100,1%R0402R16 100,1%R0402

R18 100,1% R0402R18 100,1% R0402

FB6

FB6

0.06A

1 2

600ohm@100MHz,1.5A

600ohm@100MHz,1.5A

FB0805

FB0805

+V1.8S

0.104A

Demo 1.0 P2pin NC

许沐锌

3

+V1.8S

C51

C51

C0402

C0402

ns

ns

1uF/10V,X5R

1uF/10V,X5R

版把 变成

090605

0.08A

C363

C363

C0805

C0805

10uF/6.3V,X5R

10uF/6.3V,X5R

C43

C43

0.01uF/16V,X7R

0.01uF/16V,X7R

C0402

C0402

VCCA_DMI

C37

C37

C0402

C0402

ns

ns

1uF/10V,X5R

1uF/10V,X5R

HCPU1

HCPU1

HCPU2

HCPU2

R65 0 R0402R65 0 R0402

R58 0

R58 0

R0603

R0603

C38

C38

C0402

C0402

1uF/10V,X5R

1uF/10V,X5R

2

CPU_HOLE

CPU_HOLE

11223344556677889

CPU_HOLE

CPU_HOLE

11223344556677889

+V1.5S

+V1.05S

2

1

PINEVIEW_M

PINEVIEW_M

U3F

U3F

A11

VSS

A16

VSS

A19

VSS

A29

RSVD_NCTF

A3

RSVD_NCTF

A30

RSVD_NCTF

A4

RSVD_NCTF

AA13

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA2

VSS

AA22

VSS

AA25

VSS

AA26

VSS

AA29

VSS

AA8

VSS

AB19

VSS

AB21

VSS

AB28

VSS

AB29

ns

ns

9

ns

ns

9

VSS

AB30

VSS

AC10

VSS

AC11

VSS

AC19

VSS

AC2

VSS

AC21

VSS

AC28

VSS

PNV_22MM_REV1P10

AC30

AD26

AE11

AE13

AE15

AE17

AE22

AE31

AG10

AH18

AH23

AH28

AK23

AK30

AK31

PNV_22MM_REV1P10

VSS

VSS

AD5

VSS

AE1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF11

VSS

AF17

VSS

AF21

VSS

AF24

VSS

AF28

VSS

VSS

AG3

VSS

VSS

VSS

VSS

AH4

VSS

AH6

VSS

AH8

VSS

AJ1

RSVD_NCTF

AJ16

VSS

AJ31

VSS

AK1

RSVD_NCTF

AK2

RSVD_NCTF

VSS

RSVD_NCTF

RSVD_NCTF

AL13

VSS

AL19

VSS

AL2

RSVD_NCTF

AL23

VSS

AL29

RSVD_NCTF

AL3

RSVD_NCTF

AL30

RSVD_NCTF

AL9

VSS

B13

VSS

B16

VSS

B19

VSS

B22

VSS

B30

RSVD_NCTF

B31

RSVD_NCTF

B5

VSS

B9

VSS

C1

RSVD_NCTF

C12

VSS

C21

VSS

C22

VSS

C25

VSS

C31

RSVD_NCTF

D22

VSS

E1

RSVD_NCTF

E10

VSS

E19

VSS

E21

VSS

E25

VSS

E8

VSS

F17

VSS

F19

VSS

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

GND

GND

?

?

REV = 1.1

REV = 1.1

F24

VSS

F28

VSS

F4

VSS

G15

VSS

G17

VSS

G22

VSS

G27

VSS

G31

VSS

H11

VSS

H15

VSS

H2

VSS

H21

VSS

H25

VSS

H8

VSS

J11

VSS

J13

VSS

J15

VSS

J4

VSS

K11

VSS

K13

VSS

K19

VSS

K26

VSS

K27

VSS

K28

VSS

K30

VSS

K4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

Swain Xu( )

Swain Xu( )

Calistoga(Graphic)

Calistoga(Graphic)

Calistoga(Graphic)

X01

X01

X01

K8

L1

L13

L18

L22

L24

L25

L29

M28

M3

N1

N13

N18

N24

N25

N28

N4

N5

N8

P13

P14

P16

P18

P19

P21

P3

P4

R25

R7

R8

T11

U22

U23

U24

U27

V14

V16

V18

V28

V29

W13

W2

W23

W25

W26

W28

W30

W4

W5

W6

W7

Y28

Y3

Y4

T29

许沐锌

许沐锌

许沐锌

1

6 OF 6

6 OF 6

?

?

B

B

10 39Tuesday, September 29, 2009

10 39Tuesday, September 29, 2009

10 39Tuesday, September 29, 2009

of

of

of

B

5

4

3

2

+V5S 12,14,16,19,20,22,28,30,31,32

+V3.3S 6,7,9,10,12,13,14,15,16,17,18,19,20,21,22,23,27,28,29,30,31,32

1

D D

Cross moat

place

FB5

FB5

47ohm@100MHz,500mA

47ohm@100MHz,500mA

FB0603

FB0603

C44

C44

5.6pF/50V NPO

5.6pF/50V NPO

C0402

C0402

C29

C29

5.6pF/50V NPO

5.6pF/50V NPO

C0402

C0402

C24

C24

5.6pF/50V NPO

5.6pF/50V NPO

C0402

C0402

C241

C241

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

1 2

FB4

FB4

47ohm@100MHz,500mA

47ohm@100MHz,500mA

FB0603

FB0603

1 2

FB3

FB3

47ohm@100MHz,500mA

47ohm@100MHz,500mA

FB0603

FB0603

1 2

GND_VGA

GND_VGA

GND_VGA

CRT_VSYNC

3

C45

C45

5.6pF/50V NPO

5.6pF/50V NPO

C0402

C0402

C30

C30

5.6pF/50V NPO

5.6pF/50V NPO

C0402

C0402

GND_VGA

C25

C25

5.6pF/50V NPO

5.6pF/50V NPO

C0402

C0402

D27

D27

BAT54S

BAT54S

SOT23

SOT23

D8

D8

BAT54S

BAT54S

SOT23

SOT23

132

+V3.3S

GND_VGA

D7

D7

BAT54S

BAT54S

SOT23

SOT23

132

+V3.3S

D4

D4

BAT54S

BAT54S

SOT23

SOT23

132

+V3.3S

GND_VGA

+V3.3S+V3.3S +V5_VGA

2

C237

C237

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

1

GND_VGA

CRT_RED9

R63

R63

150,1%

150,1%

R0402

R0402

CRT_GREEN9

R47

R47

150,1%

150,1%

R0402

C C

R0402

CRT_BLUE9

R32

R32

150,1%

150,1%

R0402

R0402

150ohm

电阻前

50ohm

走线阻抗

B B

CRT_HSYNC

D28

D28

2

3

1

BAT54S

BAT54S

SOT23

SOT23

GND_VGA

+V5S +V5_VGA

ROUT

GOUT

BOUT

Cross moat place

FB2

D3

D3

1 2

1N5819HW-F

1N5819HW-F

SOD123

SOD123

Update FB2 to 500mA

许沐锌

090713

FB2

1 2

120ohm@100MHz,500mA

120ohm@100MHz,500mA

FB0603

FB0603

GND_VGA

ROUT

GOUT

BOUT

C258

C258

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

GND_VGA

R264

R264

100K

100K

R0402

R0402

GND_VGA

GND_VGA

VGA

VGA

VGADMF

VGADMF

CONNECTOR TOP VIEW

GND

GND

6

NC

NC

R

R

1

11

GND

GND

7

SDA

SDA

G

G

2

12

GND

GND

8

HSYNC

HSYNC

B

B

3

13

NC

NC

9

NC

NC

VSYNC

VSYNC

4

14

GND

GND

10

GND

GND

CLK

CLK

5

15

shell

shell

shell

shell

16 17

C10518-11505-L

C10518-11505-L

VGA M12,S46 connector

公用

090713

许沐锌

C252

C252

15PF/50V,NPO

15PF/50V,NPO

C0402

C0402

ns

ns

+V3.3S +V3.3S

R276

R276

R265

R265

1K

1K

1K

1K

R0402

R0402

R0402

R0402

ns

ns

ns

ns

5VDDCDA

C239

C239

15PF/50V,NPO

15PF/50V,NPO

C0402

C0402

CRT_HSYNC

CRT_VSYNC

5VDDCCK

C235

C235

15PF/50V,NPO

15PF/50V,NPO

C0402

C0402

CRT_HSYNC 9

CRT_VSYNC 9

C227

C227

15PF/50V,NPO

15PF/50V,NPO

C0402

C0402

ns

ns

GND_VGA

No external level shifter for HSync & VSync at PINEVIEW

许沐锌

090605

+V5_VGA+V3.3S

R267

R267

2.2K

2.2K

R0402

R0402

CRT_DDC_CLK9

R281

R281

2.2K

2.2K

R0402

R0402

+V3.3S

+V3.3S

CRT_DDC_DATA9

+V3.3S

Q17

Q17

BSS138

BSS138

2

1

Q18

Q18

BSS138

BSS138

2

1

R263

R263

2.2K

2.2K

R0402

R0402

3

R282

R282

2.2K

2.2K

R0402

R0402

3

5VDDCCK

132

GND_VGA

5VDDCDA

132

GND_VGA

+V5_VGA

+V5_VGA

D26

D26

BAT54S

BAT54S

SOT23

SOT23

D29

D29

BAT54S

BAT54S

SOT23

SOT23

+V5_VGA

C23

C23

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

A A

C0402

GND_VGA

5

4

+V3.3S

GND_VGA

C49

C49

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

Add C323 for EMI issue

许沐锌

081222

GND_VGA

Connect GND to GND_VGA for EMI requirement

Swain 080724

3

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

许沐锌

许沐锌

许沐锌

Swain Xu( )

Swain Xu( )

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

the expressed written consent of TOPSTAR

Swain Xu( )

CRT CONN & S TV OUT & LIDR SWITCH

CRT CONN & S TV OUT & LIDR SWITCH

CRT CONN & S TV OUT & LIDR SWITCH

X01

X01

X01

11 39Tuesday, September 29, 2009

11 39Tuesday, September 29, 2009

11 39Tuesday, September 29, 2009

of

of

of

1

B

B

B

5

High : Enable

Low : Disable

HW_OFF_BKLT#22

1

R220

R220

100K

100K

R0402

R0402

LVDS_BKLTEN7,22

LIDR#19,22

PM_SUS_STAT#15,22

+V3.3AL

R208

R208

10K

10K

R0402

R0402

R209

R209

100K

100K

R0402

R0402

3

Q14

Q14

2N7002E-T1

2N7002E-T1

SOT23

SOT23

2

D D

C C

LVDD_EN7

R1

R1

100K

100K

R0402

R0402

2

1

2

1

+V3.3S

D1

D1

3

BAT54A

BAT54A

SOT23

SOT23

D16

D16

3

BAT54A

BAT54A

SOT23

SOT23

Q11

Q11

AO6409

AO6409

TSOP6_0D95_1D6

TSOP6_0D95_1D6

564

S

S

D

D

G

G

123

C210

C210

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

SPWG Require LCDVDD rising time

B B

EC_BKLT_PWM22

LBKLT_CTL7

A A

5

is 0.5-10ms,1-10ms is better

R4 0 R0402R4 0 R0402

R3 0 R0402

R3 0 R0402

ns

ns

+V3.3AL

+V3.3S

R207 0 R0402 nsR207 0 R0402 ns

R210 0 R0402R210 0 R0402

R2

R2

10K

10K

R0402

R0402

C212

C212

100pF/50V,NPO

100pF/50V,NPO

C0402

C0402

BKLT_PWM

C4

C4

100pF/50V,NPO

100pF/50V,NPO

C0402

C0402

EDID_PWR

4

+V3.3S

R5

R5

1K

1K

CLOSE TO INTCON

R0402

R0402

BKLT_ON

C5

C5

1000pF/50V,X7R

1000pF/50V,X7R

C0402

C0402

500mA

C214

C214

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

LVDD_EN

4

C215

C215

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

PQ45

PQ45

2N7002

2N7002

SOT23

SOT23

1

ns

ns

LCDVDD

R215

R215

2.2K

2.2K

R0402

R0402

ns

ns

3

2

3

2

R221

R221

100

100

R0603

R0603

ns

ns

PQ46

PQ46

2N7002

2N7002

SOT23ns

SOT23ns

+VDC

R226

R226

100K

100K

ns

ns

3

LCDVDD

LCDVDD

LVD_A_DATA1_DN7

LVD_A_DATA1_DP7

LVD_A_CLK_DP7

+VDC

LVD_A_CLK_DN7

+V5AL_CAM

IVT_I_ADJ22

FB1 0 R0805FB1 0 R0805

EDID_PWR

BKLT_PWM

BKLT_ON

INVT_VDD

C3

C3

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

LCDCONN , 620904000008

改成立式 料号小雷已申请

090713

许沐锌

500mA

LCDCON

LCDCON

88242-4001

88242-4001

CNS40_LCDB

CNS40_LCDB

112

334

556

778

9910

111112

131314

151516

171718

191920

212122

232324

252526

272728

292930

31

31

33

33

35

35

37

37

39

39

2

+V3.3AL 14,15,16,17,18,19,20,22,23,24,25,26,27,28,29,30,32

+V3.3S 6,7,9,10,11,13,14,15,16,17,18,19,20,21,22,23,27,28,29,30,31,32

+V5AL 16,19,20,26,27,28,29,30

+VDC 17,20,24,26,27,28,29,30,31,32

+V5S 11,14,16,19,20,22,28,30,31,32

Add R698,R701 at SM BUS

许沐锌

41

41

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

32

34

34

36

36

38

38

40

40

42

42

081218

LVD_A_DATA0_DN 7

LVD_A_DATA0_DP 7

LVD_A_DATA2_DN 7

LVD_A_DATA2_DP 7

USB_CAM_PN5 14

USB_CAM_PP5 14

R211 0 R0805R211 0 R0805

R447 0 R0402R447 0 R0402

R463 10K

R463 10K

1A1A

R0402

R0402

LDDC_CLK

LDDC_DATA

LDDC_CLK 7

LDDC_DATA 7

+V5S

LVDD_EN

+V3.3S

R43 2.2KR0402R43 2.2K R0402

R34 2.2KR0402R34 2.2K R0402

1

+V3.3S

1

+V5AL

R213

R213

0

0

R0805

R0805

ns

ns

R224

R224

10K

10K

R0402

R0402

ns

ns

R223 10K

R223 10K

3

Q12

Q12

2

2N7002E-T1

2N7002E-T1

SOT23

SOT23

ns

ns

+V5S

R0402

R0402

ns

ns

R212

R212

0

0

R0805

R0805

R214 0 R0805R214 0 R0805

2

Q13

Q13

SOT23

SOT23

AO3415

AO3415

1

ns

ns

Add +5S to CAM POWER

许沐锌

2

3

081111

500mA

+V5AL_CAM

C213

C211

C211

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C213

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu( )

Swain Xu( )

Swain Xu( )

许沐锌

许沐锌

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

LVDS

LVDS

LVDS

X01

X01

X01

许沐锌

1

12 39Tuesday, September 29, 2009

12 39Tuesday, September 29, 2009

12 39Tuesday, September 29, 2009

B

B

B

of

of

of

C216

C216

R225

R225