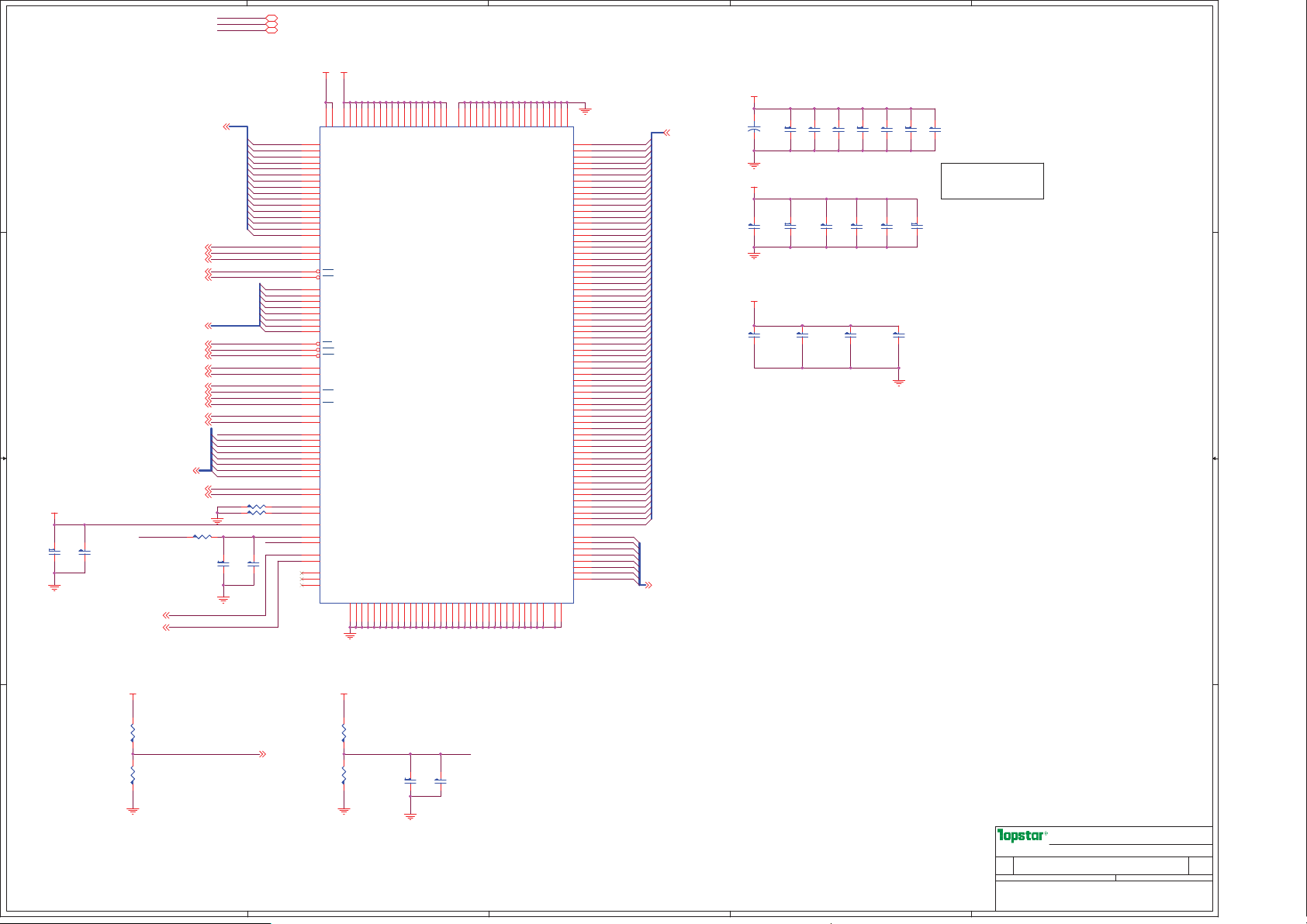

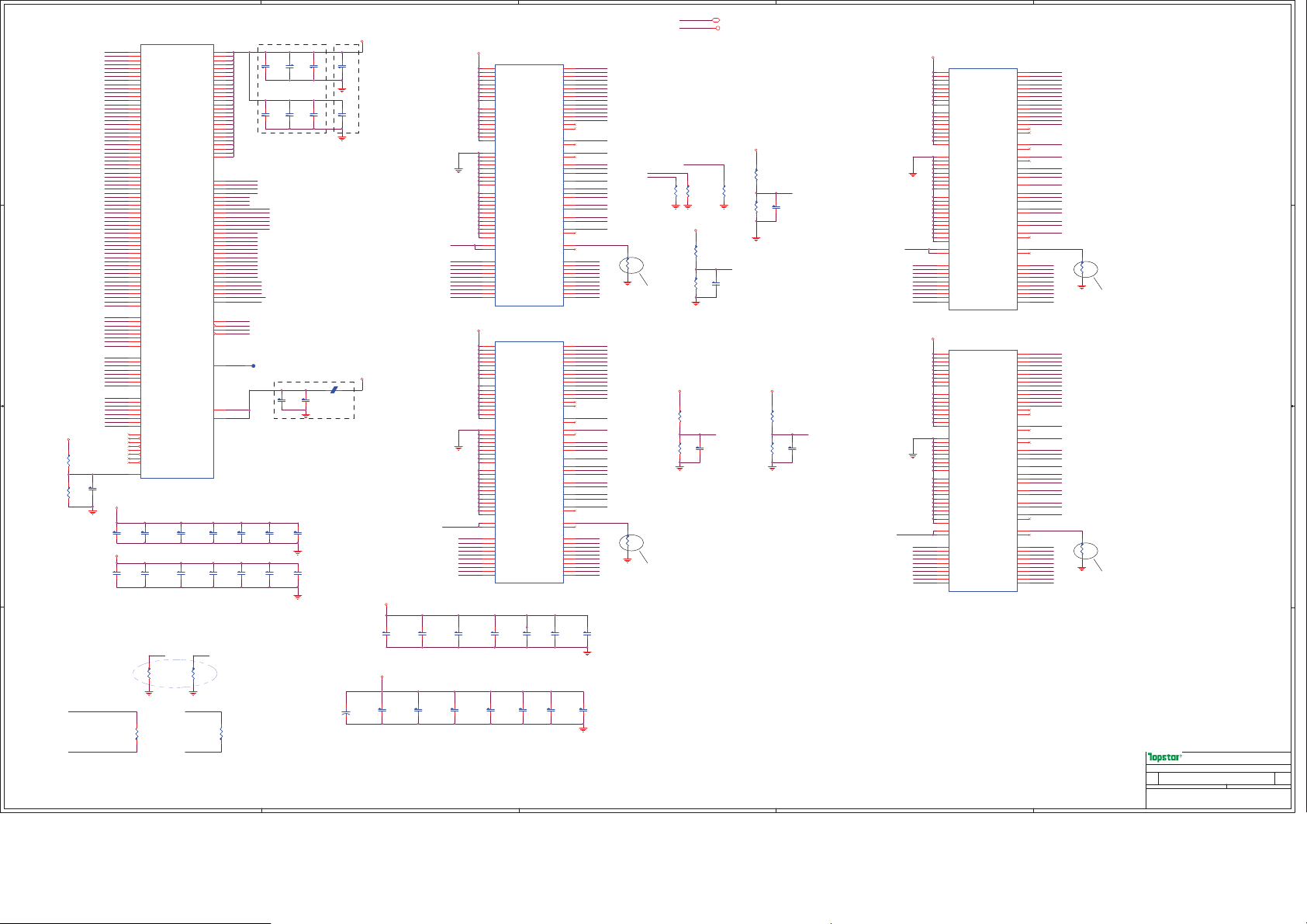

TOPSTAR S42G Schematics

5

http://hobi-elektronika.net

4

3

2

1

Topstar Digital technologies Co.,LTD

D D

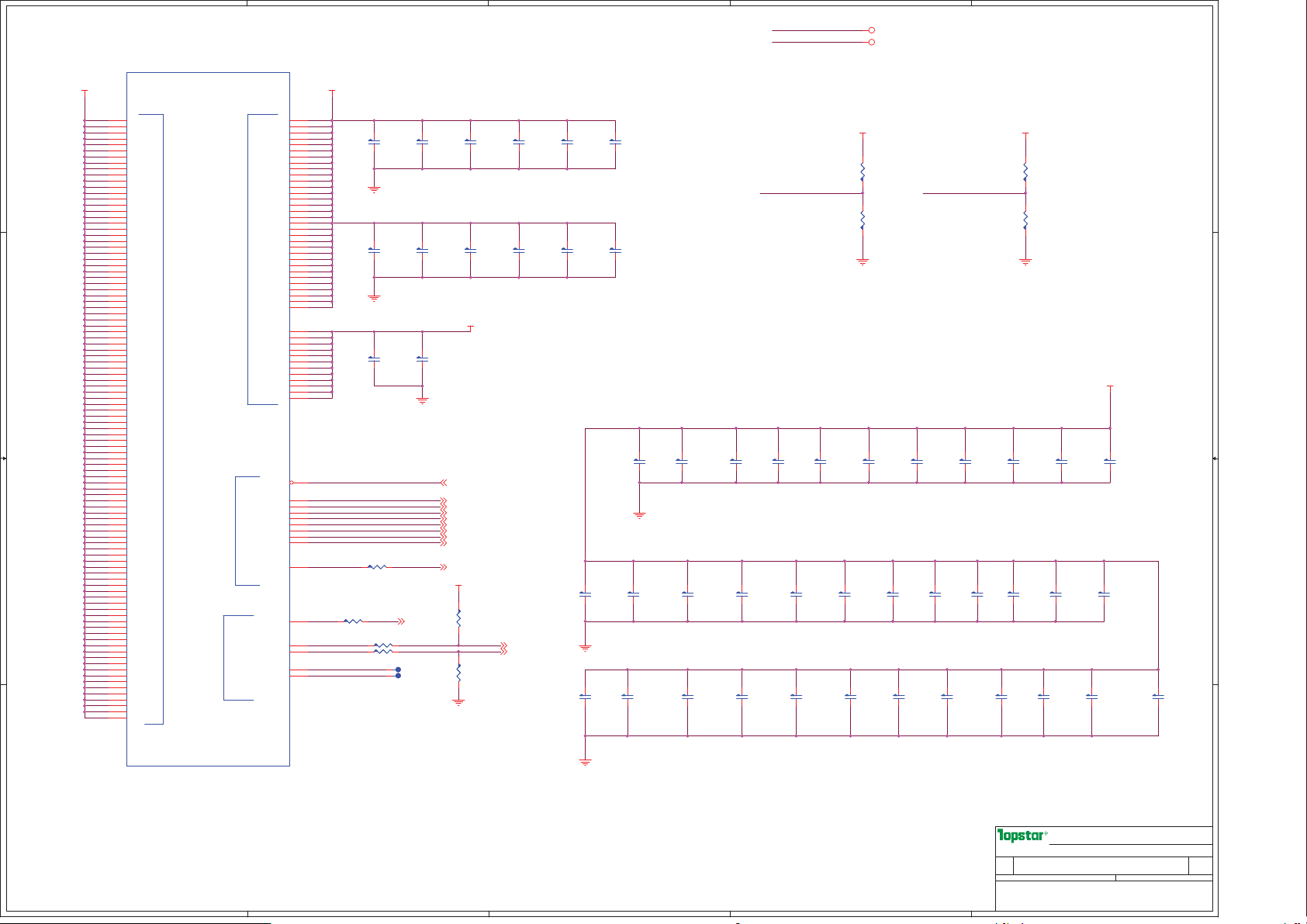

Board name: MotherBoard Schematic

Project name: C49

Version: VerA

Initial Date: 2010-04-01

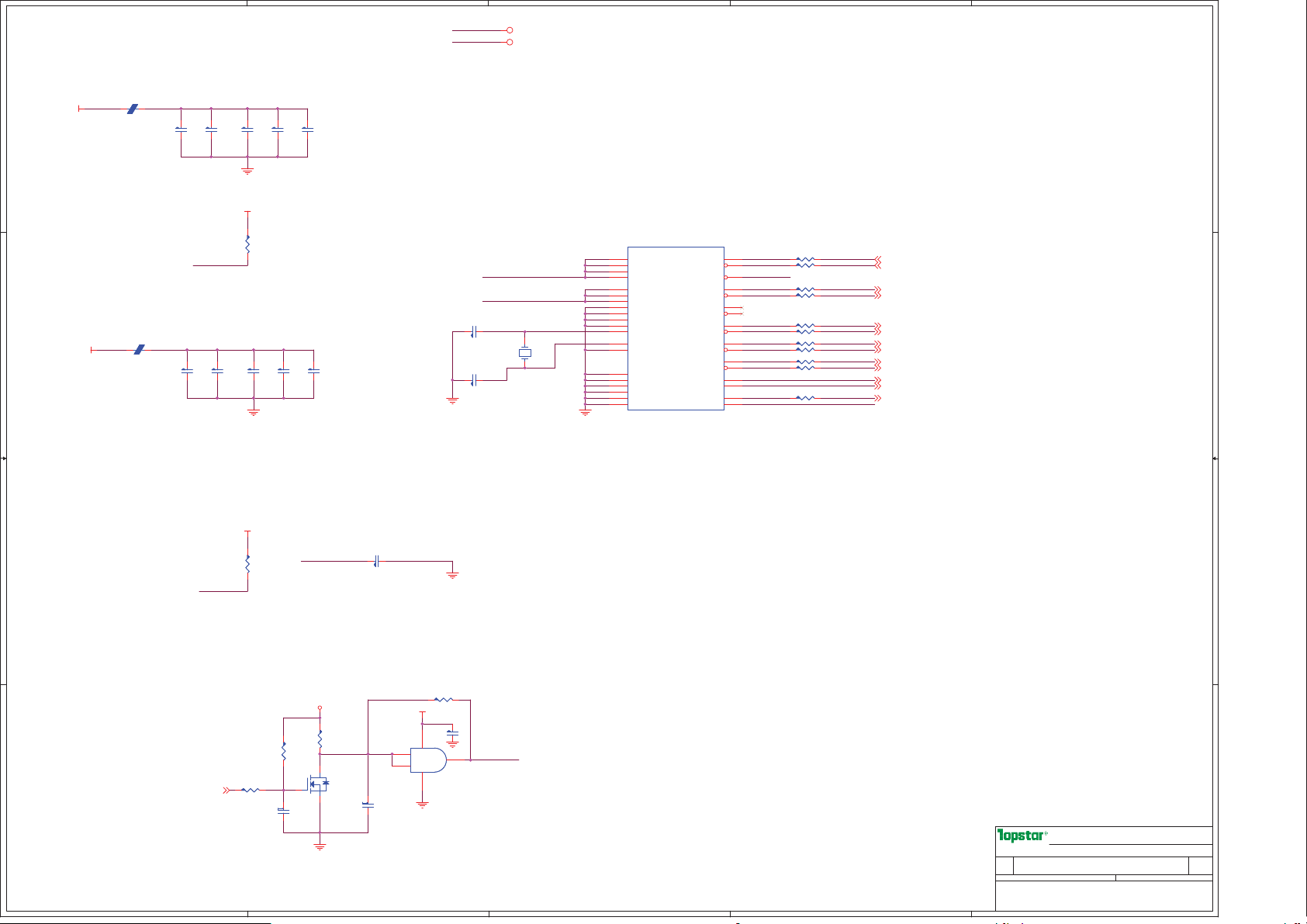

02. System block & Index

03. PWR Block & Description

04. Notes & Annotations

05. Schematic Modify and History

06. CLOCK Distribution

Topstar Confidential

C C

Hardware drawing by:

Power drawing by:

Hardware check by: EMI Check by:

Power check by:

Manager Sign by:

B B

A A

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Joseph

Joseph

Joseph

Title

Title

Title

C49

C49

C49

1

A

A

A

of

of

of

159Friday, May 07, 2010

159Friday, May 07, 2010

159Friday, May 07, 2010

5

4

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

3

2

the expressed written consent of TOPSTAR

5

http://hobi-elektronika.net

4

3

2

1

Topstar Confidential

ShenZhen Topstar Industry Co.,LTD

D D

Backlight

Connector

+VDC

TFT

+V3.3S

C C

B B

LVDS switch

PCIE mini Card

VGA

+V5S

PCIE mini Card

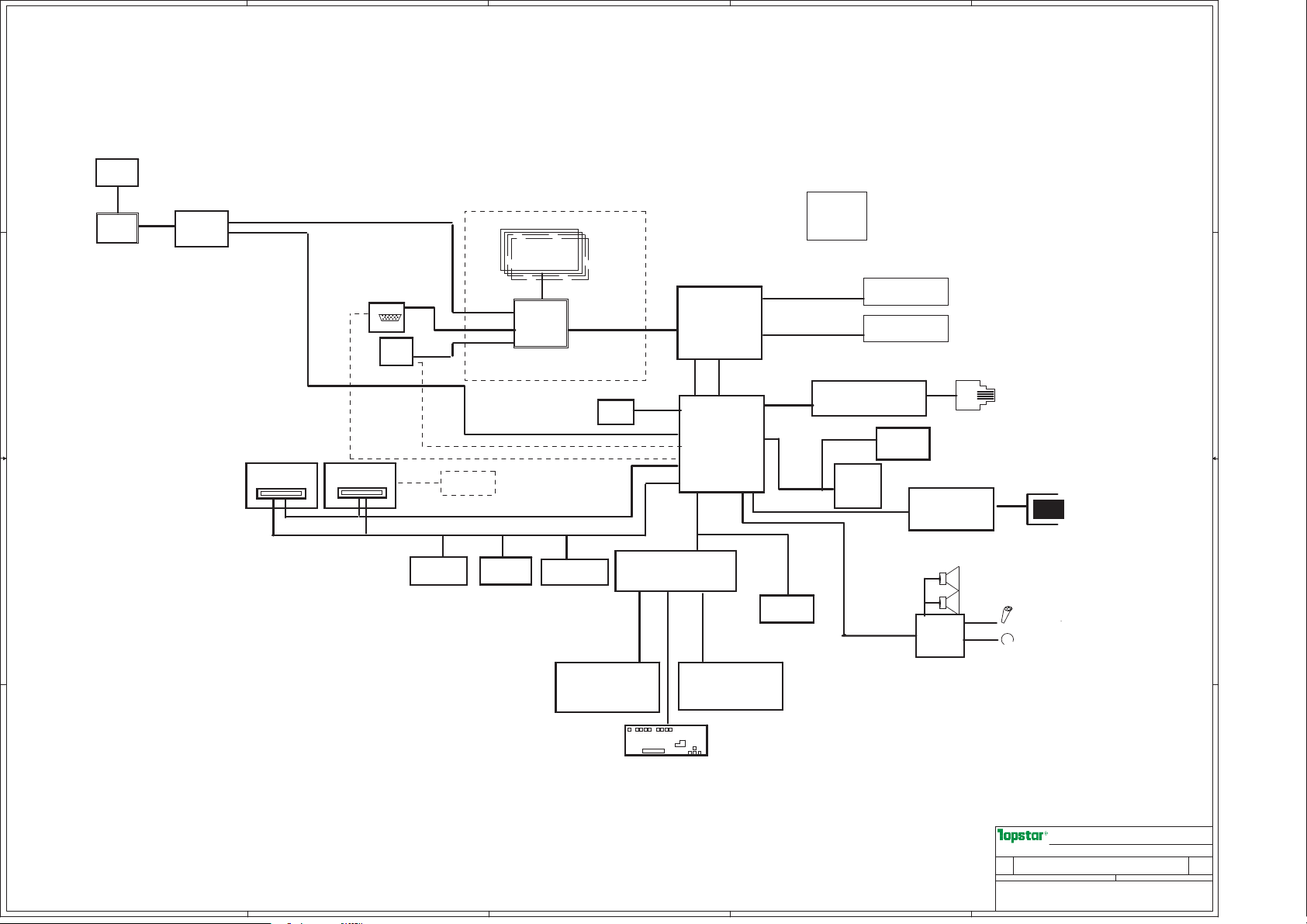

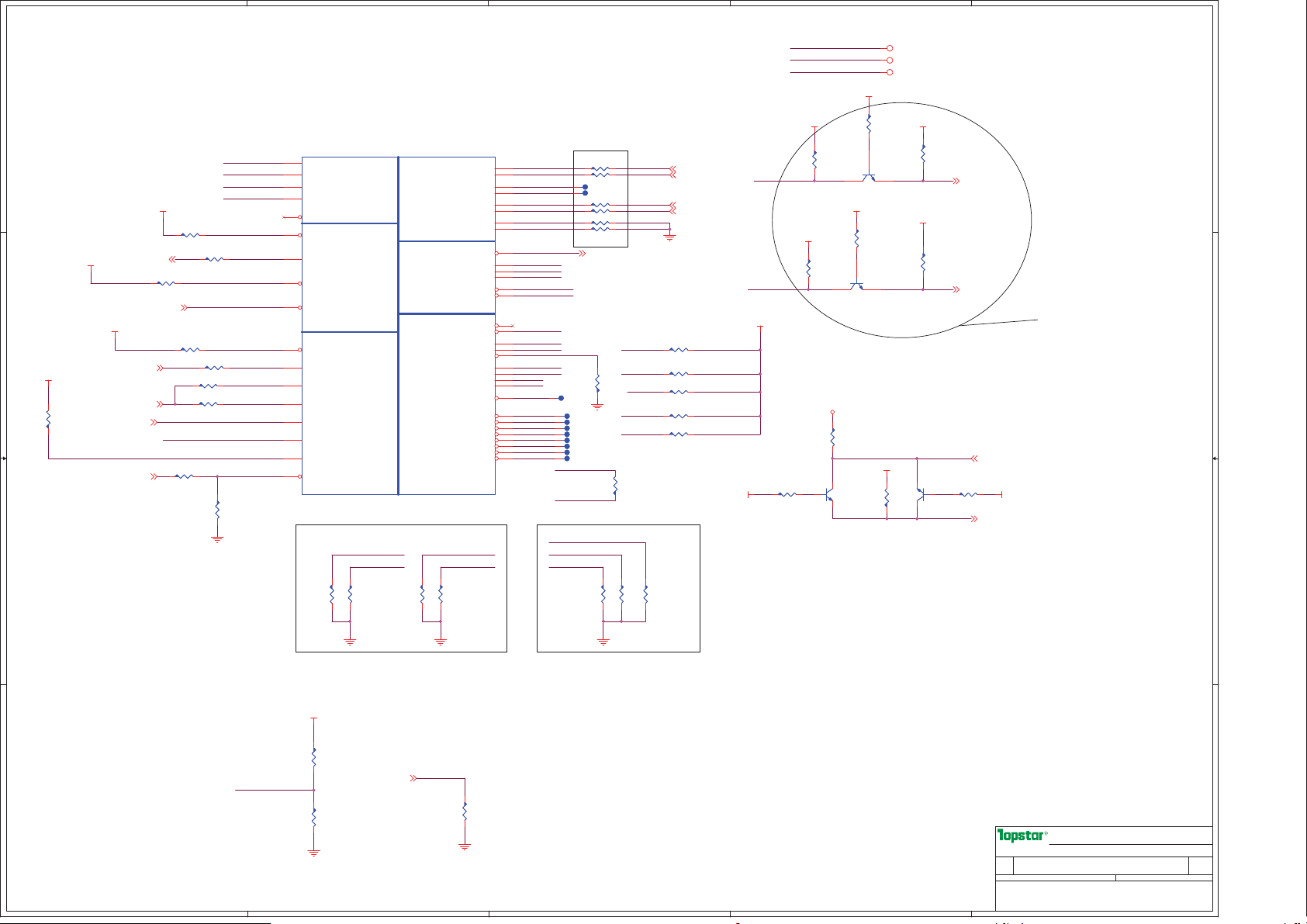

C49 SYSTEM BLOCK Ver:A

Only for PM

64M*16Bit*4 DDRIII

+V1.5GDDR

Memory

Nvidia

NB11M

LVDS

HDMI

R/G/B

interface

+VGA_CORE,

+V1.05GPU

+V1.8GDDR,

+V3.3GPU

+V1.5GPU

PCIE 1X

USB PORT(3)

+V5AL

HDMI

CONN

SIM Card

Blue Tooth

+V3.3AL

LVDS

R/G/B

TMDS

USB1.1/2.0

Camera

1.3M ODULE

+V3.3S

PEGX16 /eDP

BIOS

8Mbit

+V3.3AL

Arrandule/clarsfield

989rPGA

+VCC_CORE,+VccGFX

+V1.5S, +V1.8S,

+V1.1S_VTT

FDI

SPI

Ibex_peak

1071 BGA

+V3.3A,+V3.3S,+V1.5S,

+V1.05S,+V1.8S,

+V5A,+V5S

LPC

KB Controller/EC

ENE 3926

+V3.3AL,+V3.3S,+V5AL

DMI*4 100MHz

CK505M

Clocking

SLG8SP585

+V3.3S

DDR3 800/1066

DDR3 800/1066

PCIE 1X

USB1.1/2.0

AZALIA

TCM

(Reserve)

DDR3 SODIMM0

800/1066

+V0.75S,+V1.5,+V3.3S

DDR3 SODIMM1

800/1066

+V0.75S,+V1.5,+V3.3S

RTL8102E/8111D

+V3.3S,+V3.3AL

SATA ODD

S-ATA

2.5" HDD

+V5S

+V5S

Card Reader

ITE 1337

+V3.3AL

L

R

AZALIA

ALC662

+V5S,+V3.3S

RJ45

.

.

SD/MMC/MS CARD

MiC In

Line Out

LED/TouchPAD/Button/

Switch Board

DAUGHTER BOARD

KB Matrix

A A

5

4

3

LID Switch

DAUGHTER BOARD

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Joseph

Joseph

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

the expressed written consent of TOPSTAR

Joseph

Sys block

Sys block

Sys block

C49

C49

C49

1

A

A

A

of

of

of

259Friday, May 07, 2010

259Friday, May 07, 2010

259Friday, May 07, 2010

5

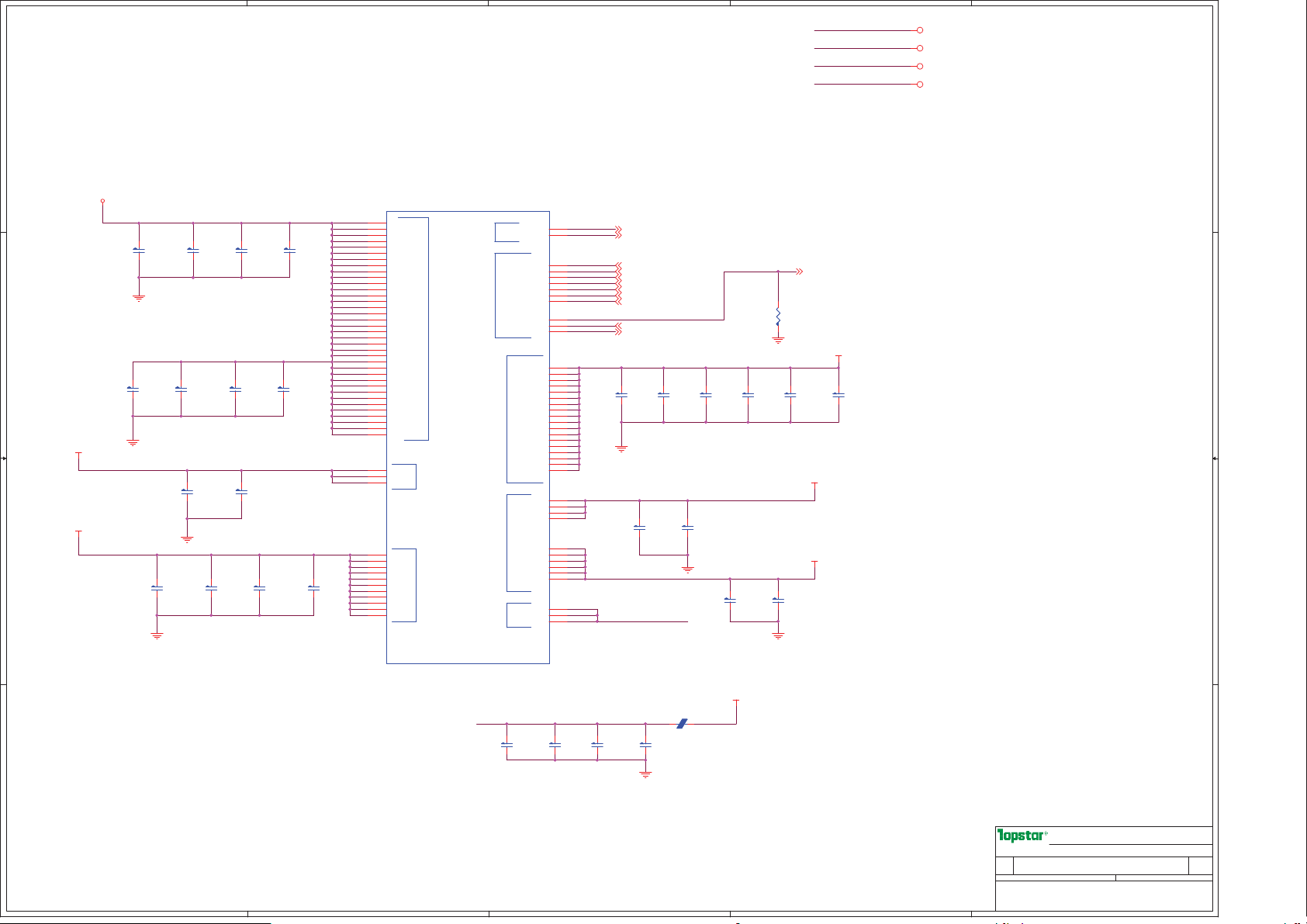

3ODWIRUP

/RJLF

&/.

&+,3

3&+ &380

,093

6\VWHP3RZHU

9B6

$

$$

$GDSWHU

$

&KDUJH

,6/

$$

736

$OZD\VB2Q

3RZHU

736

$

,6/

3RZHU

6ZLWFK

9&&B&25(

,6/

$

''53RZHU

736

$3/

%DWWHU\

$

$

,6/

$

$

$

736

$

http://hobi-elektronika.net

4

3

2

1

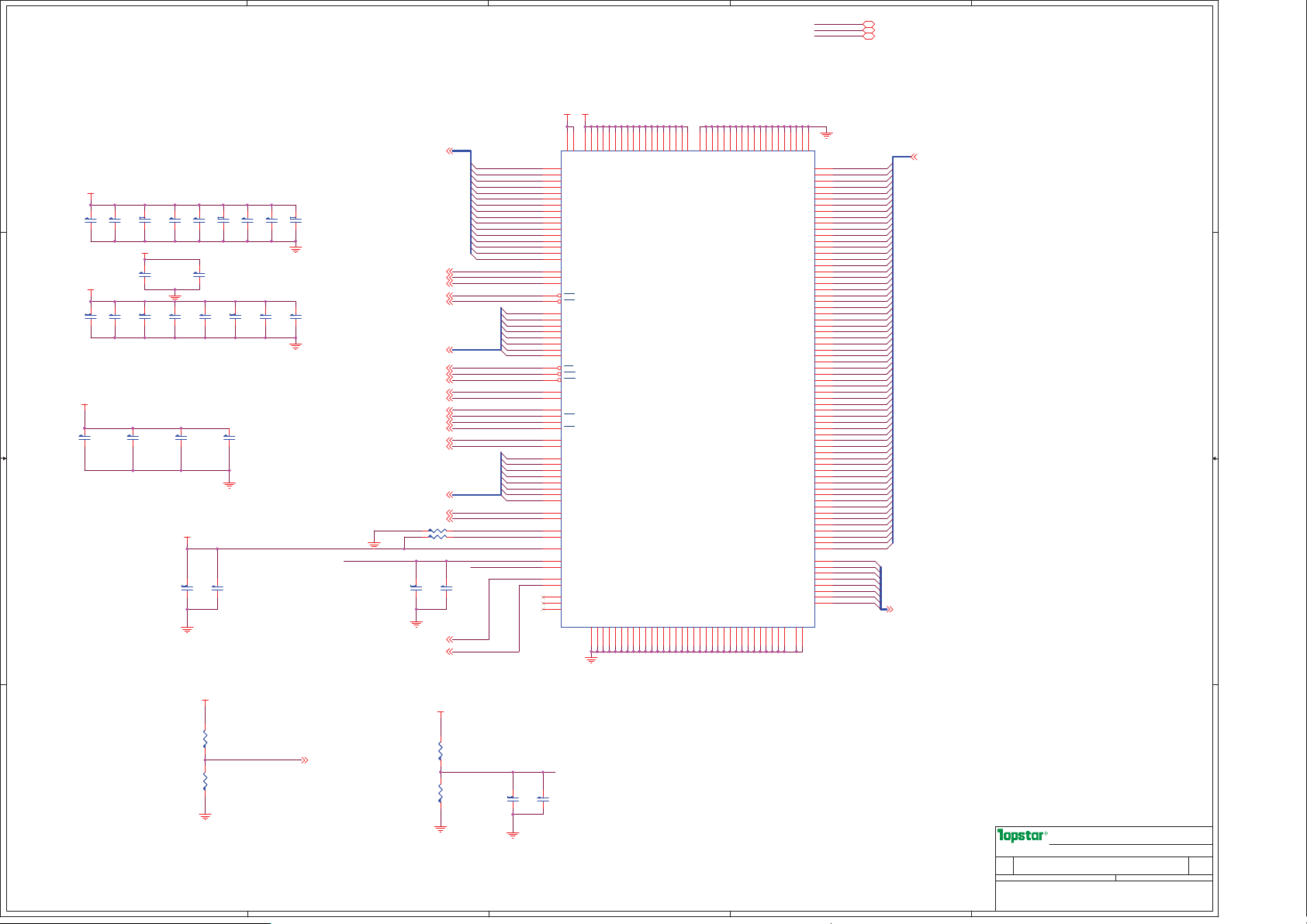

C46 POWER BLOCK Ver:A

D D

9,1

⊼ᛣ

㰮㒓㸼⼎⬉⑤⬉ֵোDŽ

9B

9B

95B21

VCC_SENCE

VSS_SENCE

IMON

95B77

9FFBFRUH

9,'>@

36,

'356/395

C C

9*$B&25(

B B

9*);

65/90W

96

9*38

96B977

MOSFET

+V3.3GPU

9$/

9$/

MOSFET

9'&

MOSFET

+V1.5GPU

9

96

9&&B&25(

+V1.5S

+V1.8S

KIA1117

96

96

MOSFET

MOSFET

+V1.8GPU

&/.B(1$%/(

,093B3:5*'

&38B3:5*'

36,

352&+27

A A

TOPSTAR TECHNOLOG

TOPSTAR TECHNOLOG

TOPSTAR TECHNOLOG

Joseph

Joseph

Joseph

PWR Block

PWR Block

PWR Block

C49

C49

C49

1

A

A

359Friday, May 07, 2010

359Friday, May 07, 2010

359Friday, May 07, 2010

A

of

of

of

5

4

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

3

2

5

6670

6/3B6

6/3B6

96

6LJQDO

66RIW2II

6/3B6

6)XOO2Q

9

667'

9$/

&ORFN

http://hobi-elektronika.net

4

3

2

1

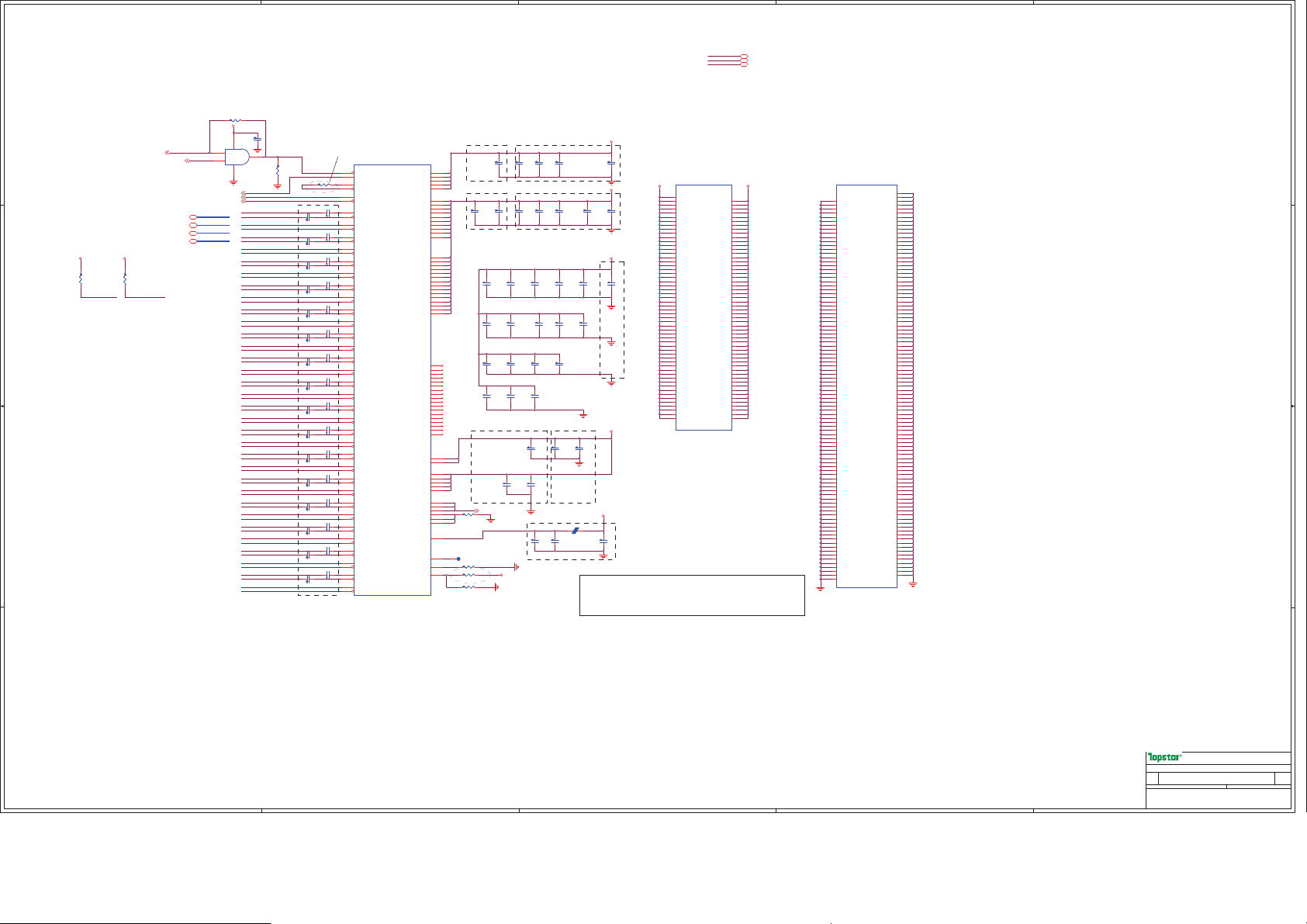

Voltage Rails

+VDC

D D

+VCC_CORE

+V1.1S_VTT

+V1.05S

+V0.75S

+V1.5

+V3.3AL

+V3.3S

+V5AL

+V5S

+VGA_CORE

+V1.5S

+V1.8S

+V3.3GPU

+V1.05GPU

C C

+V1.8GPU 1.8V for external GPU

+V1.5GPU 1.5V for external GPU

Primary DC system power supply(9V-19V)

Core voltage for processor

1.1V for CPU

1.05V for PCH core

0.75V DDR3 Termination voltage

1.5V power rail for DDR3

3.3V always on power rail

3.3V main power rail

5V for USB Device

5V main power rail

0.8--1.03V for GPU NB8M core voltage

1.5S for PCIE Device

1.8V for display votage

3.3V for external GPU

1.05V for external GPU

I2C SMB Address

Device

Clock Generator

SO-DIMM0

SO-DIMM1

NEW CARD

PCIE Mini CARD

Smart Battery

Touch sensor IC

0001 011x 16 I2C ENE3926

1000 110x 8C SMB1_PCH ENE3926

Address

1101 001x

1010 000x

1010 010x

Variable Variable SMB1_PCHPCH

BusHex

SMB_PCH

D2

SMB_PCH

A0

SMB_PCH

A4

SMB_PCH

VariableVariable

SMB_PCH

VariableVariable

Master

PCH

PCH

PCH

PCH

PCH

ENE3926

Power States/AC mode

Board stack up description

PCB Layers

TOP

GND

IN1

IN2

VCC

IN3

B B

GND

Bottom

Trace Impedence:50ohm +/-15%(Default)

+,*+

/2:

/2: 2))

/2:

+,*+

+,*+ 21 2))

/2:

/2:

+,*+

+,*+

+,*+

/2:

21

21

21

21 21

21

2))

2))

2))

2))

21

2))

2))

Wake up Events

USB Table

USB Port#

A A

Function Description

0

Express Card

1

minicard1

reserved

2

3

camera

4

USB port1

5

Bluetooth

6

Reserved

7

Reserved

8

CARD Reader

9

minicard2

10

USB port2

11

USB port3

5

4

3

LID switch from EC

Power switch from EC

TOPSTAR TECHNOLOG

TOPSTAR TECHNOLOG

TOPSTAR TECHNOLOG

Joseph

Joseph

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

the expressed written consent of TOPSTAR

Notes

Notes

Notes

C49

C49

C49

Joseph

A

A

459Friday, May 07, 2010

459Friday, May 07, 2010

459Friday, May 07, 2010

1

A

of

of

of

5

http://hobi-elektronika.net

4

3

2

1

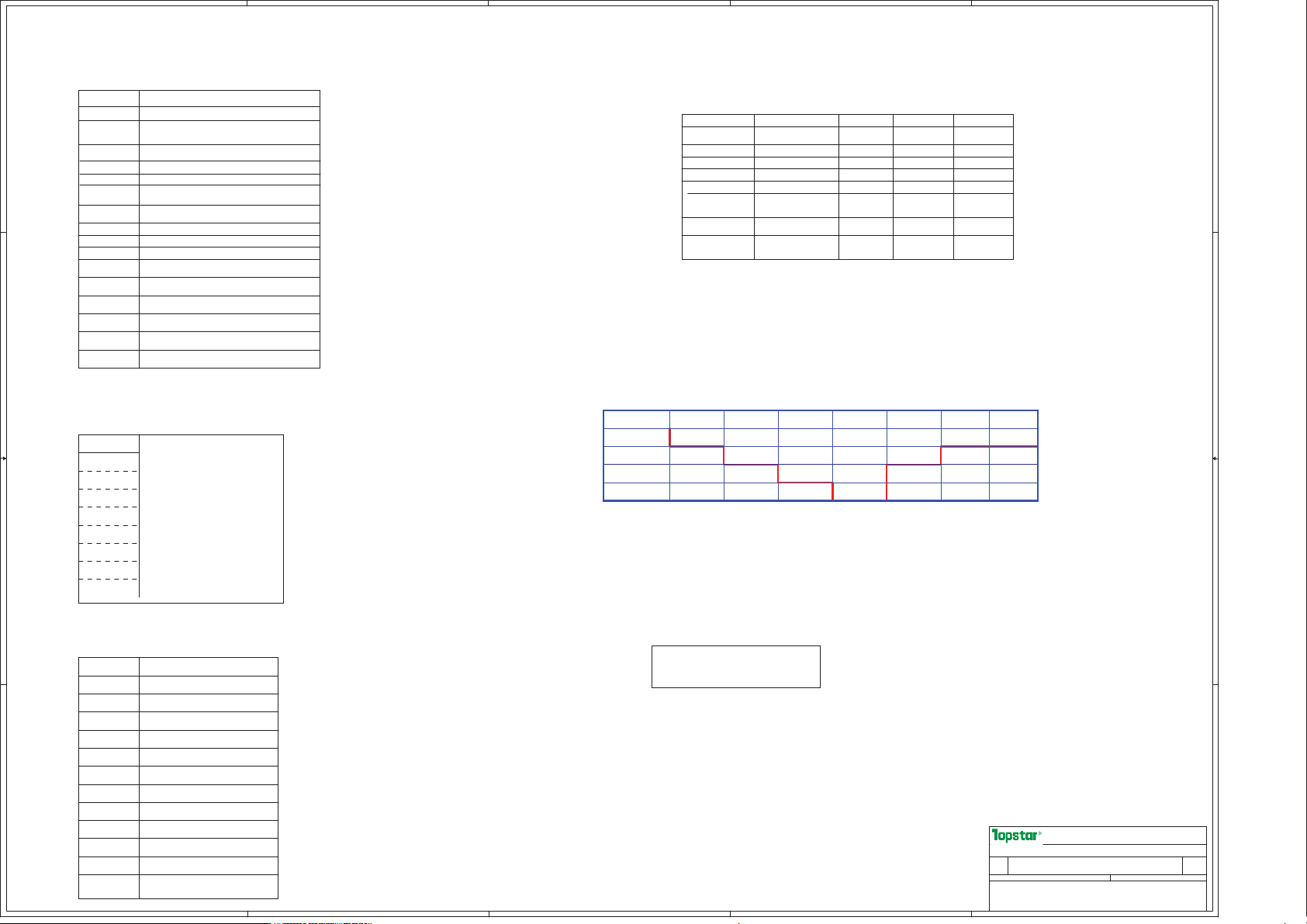

C48 VerB to VerC change

1:GPURST#

GPURST#ϢPLATRST#

Փ⫼Ϣ䮼ࠊ˄

䖭ḋخⱘህᰃབᵰྟ㒜⬅

Ў⛁ࡼⱘ䖛Ё

᳝ৃ㛑Ӯᡧϡࠄ

D D

2

˖⅏䫕⬉䆱䆒䅵বˈ⬉䏃ᬍবᦣ䗄བϟ˖

PLTRST#

I GU1 ,NI GR1

ৠℹˈ⬅

EC_GPURST#

PLTRST#

PLTRST#

㹿ᢝϟᴹⱘᯊ䯈ᴀϞህ

˅ˈ⬅

PLTRST#ϢEC_GPURST#

ࠊˈخᰒߛᤶⱘᯊ⬅

䗮䖛պ⌟

PLTRST#

ᴹࠊ

5ms

݅ৠࠊˈℷᐌⱘᓔ݇ᴎⱘᯊ

EC_GPURST#

GPURST#

ˈ

Ꮊেˈ㗠ECⱘᠿᦣᳳህᰃ

ϔϾব࣪ⱘ䖛㗠ֱᣕϔⳈЎ催ˈӮ䗴៤ᰒ偅ࡼⱘ϶༅ㄝᓖᐌ⦄䈵DŽ

ࠊ

GPURST#

ˈ

5ms,

EC_GPURST#

ྟ㒜Ў催⬉ᑇˈ

NI Q31,PZ8,change PR187 from 100 ohm to 2K ohm,change PR24 from 51k to 15K

বབϟ˖

᠔᳝

GPU

⬉䛑Ӯᥝϟᴹˈ᠔ҹ

䗮䖛

BIOS

䇏প✊ৢথ䗕㒭

ህㅫ᳝⅏䫕ֵোথߎᴹˈЎ

থ⦄〇ㅵ䱣ⴔ⏽ᑺব࣪ⓣ⬉⌕Ӯˈৃ㛑Ӯᇐ㟈ᓖᐌ⅏䫕ˈৠᯊЎ

ᬙএᥝ

PZ8

Q31

ᰃᰒ

EC

ϡӮᇍ㒓䏃᳝ᕅડDŽ

GPU_OVT#

ࠊ⅏䫕⬉䏃ⱘ䗮䘧ˈЎ㋏㒳ϟ㽕خᰒߛᤶˈᔧҢ⣀ᰒߛࠄ䲚ᰒⱘᯊˈ

GPU_OVT#

ˈ⬅ECࠊDŽ

51K100ohm

гӮᥝϟᴹˈӮᇐ㟈ᓖᐌ⅏䫕ˈ᠔ҹϡ㛑䖭ḋࠊˈ⦄

PR187

ᤶ៤

2K,PR24

ᤶ៤

15K

ⱘᰃЎПࠡⱘ㒘ড়ϡ㛑⅏䫕ˈ

ߚˈߚߎᴹⱘ⬉ϡ㛑㓈ᣕ⅏䫕⬉䏃ˈৠᯊএᥝ

3.3AL

㢃⠛ݙ䚼᳝䖛ֱᡸࡳ㛑ˈ

GPU

PZ8

ᰃЎПࠡ

⏽ᑺպ⌟ᰃ

3˖TP_CON2

Пࠡⱘ㒓䏃Ϟা᳝ϔϾ

4˖PWRLED#

C C

ᇐ㟈䖭ϸϾ

5˖Audio Jack

SPK CONN

6˖USB conn

7

˖㔥

⬅Пࠡⱘ

ֵোৠᯊࠊ

PWR

6Pin

ᤶ៤

7pin,

বⱘᰃЏᵓ㽕ݐᆍ

EC GPIO

ˈᬙ䳔㽕ࡴ

POWER1ϢPWRLED1

♃ϡ㛑ৠℹˈϡ⒵䎇䆒䅵㽕∖DŽ

⠽᭭বˈ⬅Пࠡⱘ

SMD

᭭ߛᤶࠄ

⠽᭭Ў៤ᴀ㋴ˈг᳝বЎ᱂䗮Փ⫼ⱘ

⠽᭭বˈЎПࠡⱘ

CO-lay

ܚ

Option for C49,

USB conn

ԧ㒓䏃ব䇋খ㗗㒓䏃DŽ

C49

ˈ㗠

C49

1pin

DŽ

ˈПࠡ㒓䏃䆒䅵

DIP

᭭ˈⳌⱘܗӊ

CONN

PWRLED#

ˈϢ

RTC CONN

Ϟ䳔㽕ϸϾ

াࠊ

POWER1,㗠PWRLED1

Symbol

г᳝বDŽৠᯊ

ϔ㟈ˈϡ⍝ঞ㒓䏃বDŽ

ECⱘGPIO

ᰃডⱘˈӮ㒭⫼᠋Փ⫼䗴៤ೄᡄˈ㒓䏃বখ㗗㒓䏃

ࠊϸϾᓔ݇ˈ

ᰃՓ⫼݊Ҫ

Audio

ᇣᵓϞⱘ

ECⱘGPIO

ࠊˈ

C48 VerC to C49 VerA change

1˖PROCHOT#

2

˖

B B

PCH GPIO33

3˖MCH_HDMI_HPD

4

˖䖲ᰒⱘ

5

˖ߴ䰸㪱⠭ЏᵓϞⱘ

6

˖

GPU_OVT#

7˖ESATA USB CONN

˖ߴ䰸

8

˖䇗ᭈ

9

10

˖䇗ᭈ

11˖PWR_LAN

˖এᥝ

12

13

˖ᬍ⅏䫕⬉䏃䆒䅵

A A

⬅ⳌবঠⳌˈ

䖲ࠄ

EC pin 104(EC

EC

Ⳉ

SMBUSϢECⱘSMBUS

CONN

ˈᇚ㪱⠭ֵো䖲ࠄ

䖲ࠄECⱘ

Pin88(EC

বЎϾⱘ

E-CARD Function

RSMRST#Ϣ+V3.3AL

ᥝ⬉ᯊᑣˈ

C49_switch2ࠄ110pin(EC

ϢЏᵓ䖲㒓⬅

+V1.05S

㒓䏃ˈ݅⫼

5

30pin

+V1.1S_VTT

Ўࠊֵো䕧ߎ

䕧ߎ)ˈЎ

ˈՓECⳈ䇏পᰒ⏽ᑺ

LCD CONN

䕧ֵܹো

)

USB CONN

ALW_PWROK ҢPin110

䕧ܹ

)

⬉ᄤ㒓বЎ1Ͼ

ˈЁ䯈Փ⫼

4

EC_ME_LOCK#

বࠄ

8pin

ⱘ⬉ᄤ㒓˄

Open

⚍Ϣ⬉䰏䖲

ࠊֵো

Pin95(EC

For

䕧ܹ&Ёᮁ

⬉⑤˅ϢϔϾ

3

pin)

20pin FFC conn(For

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

㔥

)

TOPSTAR TECHNOLOG

TOPSTAR TECHNOLOG

TOPSTAR TECHNOLOG

Joseph

Joseph

Joseph

history

history

history

C49

C49

C49

A

A

A

of

of

559Friday, May 07, 2010

559Friday, May 07, 2010

559Friday, May 07, 2010

1

5

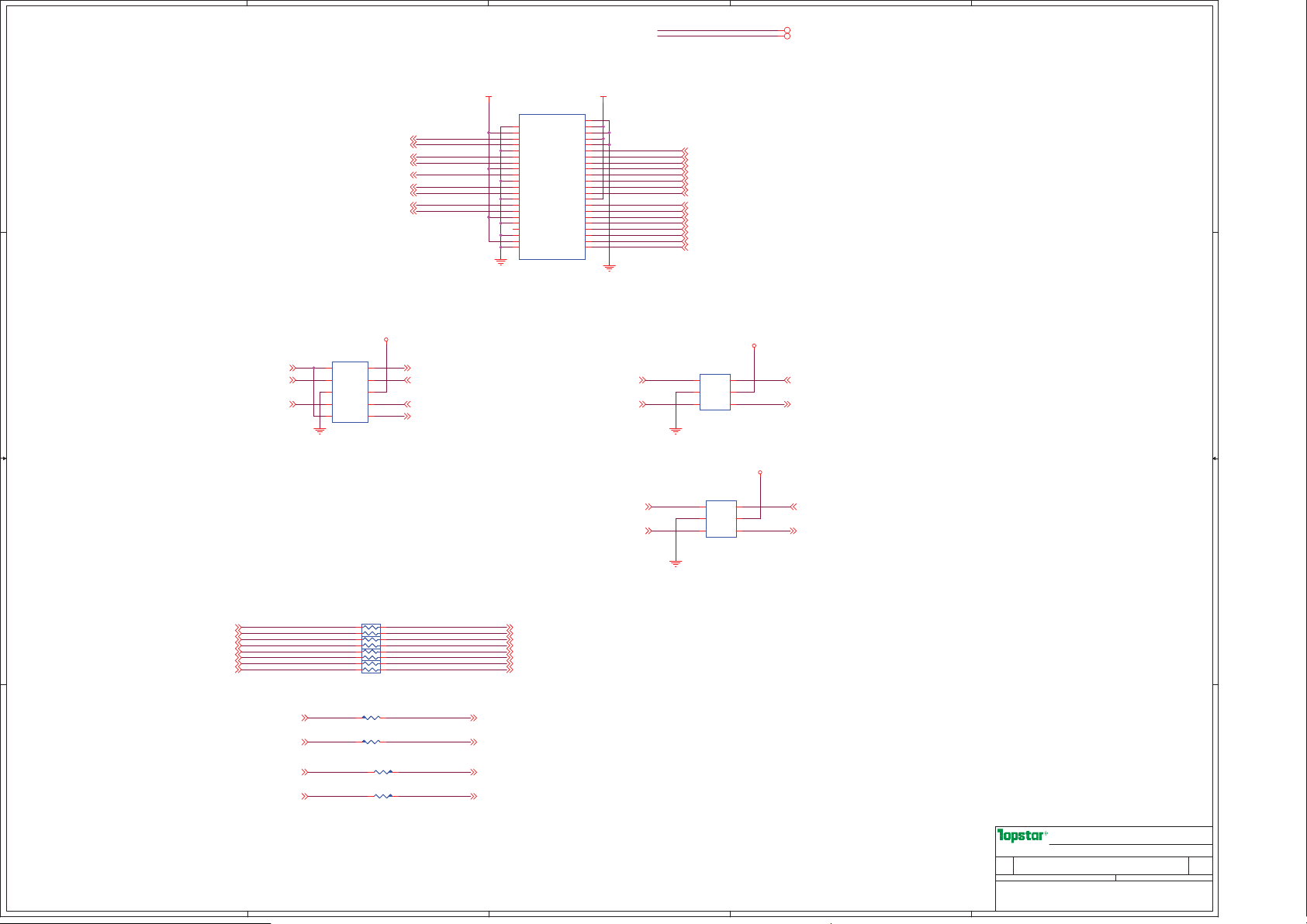

http://hobi-elektronika.net

4

+V3.3S {8,14,15,16,22,23,24,25,26,27,28,29,30,32,33,34,35,36,37,38,40,41,42,43,47,48,49,50,51,53,54,55,56}

+V3.3AL {22,23,24,25,27,28,30,32,34,35,36,37,41,42,43,44,45,46,47,48,49,50,51,54,56}

3

2

1

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C7

C7

C3

C3

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

+V3.3S

R573

R573

10K

10K

R0402

R0402

C8

C8

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

+V3.3S

R10

R10

10K

10K

R0402

R0402

ns

ns

+V3.3S_CK_VDD

C4

C4

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

+VDDIO_CLK

C9

C9

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

C5

C5

C0402

C0402

Layout Note:

Cap Close to CK505 PWR pin

C10

C10

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

CLK_BUF_REF14

C13 10PF/50V,NPOnsC0402C13 10PF/50V,NPOnsC0402

+V3.3S_CK_VDD

+VDDIO_CLK

C11 27pF/50V,NPO

C11 27pF/50V,NPO

C0402

C0402

C12 27pF/50V,NPO

C12 27pF/50V,NPO

C0402

C0402

No more than 500 mil

12

Y1

Y1

14.31818MHz

14.31818MHz

XS2_3D3

XS2_3D3

XTAL_IN

XTAL_OUT

1

5

17

29

24

18

15

G1

G2

G3

G4

28

27

G5

2

8

9

12

21

26

U1

U1

VDD_DOT

VDD_27

VDD_SRC

VDD_REF

VDD_CPU

VDD_CPU_IO

VDD_SRC_IO

GND1

GND2

GND3

GND4

XTAL_IN

XTAL_OUT

GND5

VSS_DOT

VSS_27

VSS_SATA

VSS_SRC

VSS_CPU

VSS_REF

CK505QFN32

CK505QFN32

SMB_DATA

SMB_CLK

CPU_STOP#

CPU0

CPU0#

CPU1

CPU1#

DOT96

DOT96#

SRC0/SATA

SRC0#/SATA

SRC1

SRC1#

27M_NSS

27M_SS

REF/FS

CK_PWRGD/PWRDWN#

SMBUS ADD:1101 001X

31

32

16

23

22

20

19

3

4

10

11

13

14

6

7

30

25

R955 0 R0402R955 0 R0402

R956 0 R0402R956 0 R0402

CPU_STOP#

BCLK

R1 0 R0402R1 0 R0402

BCLK#

R2 0 R0402R2 0 R0402

Integrated resistors on differentail clk

DOT96

R3 0 R0402R3 0 R0402

DOT96#

R4 0 R0402R4 0 R0402

R5 0 R0402R5 0 R0402

R6 0 R0402R6 0 R0402

R7 0 R0402R7 0 R0402

R8 0 R0402R8 0 R0402

BCLK_FS

R9 33 R0402R9 33 R0402

CLK_PWRGD

SMB_DATA_S {14,15,24,37}

SMB_CLK_S {14,15,24,37}

CLK_BUF_BCLK_P {24}

CLK_BUF_BCLK_N {24}

CLK_BUF_DOT96_P {24}

CLK_BUF_DOT96_N {24}

CLK_BUF_SATA_P {24}

CLK_BUF_SATA_N {24}

CLK_BUF_EXP_P {24}

CLK_BUF_EXP_N {24}

27M_nonSSC {20}

27M_SSC {20}

CLK_BUF_REF14 {24}

FB1 100ohm@100MHz,3A

FB1 100ohm@100MHz,3A

D D

C C

B B

+V3.3S

+V3.3S

12

FB0805

FB0805

C1

C1

10UF/6.3V,X5R

10UF/6.3V,X5R

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0805

C0805

CPU_STOP#

FB2 100ohm@100MHz,3A

FB2 100ohm@100MHz,3A

1 2

FB0805

FB0805

C6

C6

10UF/6.3V,X5R

10UF/6.3V,X5R

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

Frequence Select

High:100Mhz

Low:133Mhz(Default)

C2

C2

C0402

C0402

C0805

C0805

BCLK_FS

+V3.3S

R896

R896

10K

10K

R897

R897

R0402

R0402

10K

10K

R0402

R0402

ns

ns

3

PQ85

PQ85

2N7002

2N7002

SOT23

R898 1K

A A

5

CK505_CLK_EN#{53}

R898 1K

R0402

R0402

C535

C535

C0402

C0402

0.1UF/25V,Y5V

0.1UF/25V,Y5V

ns

ns

SOT23

1

2

C536

C536

C0402

C0402

0.1UF/25V,Y5V

0.1UF/25V,Y5V

4

+V3.3AL

VCC

VCC

1

2

GND

GND

R895 0 nsR895 0 ns

53

4

SOT23_5

SOT23_5

SN74AHC1G08DBV

SN74AHC1G08DBV

U30

U30

C534

C534

0.1UF/10V,X7R

0.1UF/10V,X7R

CLK_PWRGD

TOPSTAR TECHNOLOG

TOPSTAR TECHNOLOG

TOPSTAR TECHNOLOG

Joseph

Joseph

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

3

2

the expressed written consent of TOPSTAR

CK505M

CK505M

CK505M

C49

C49

C49

Joseph

1

A

A

659Friday, May 07, 2010

659Friday, May 07, 2010

659Friday, May 07, 2010

A

of

of

of

5

http://hobi-elektronika.net

4

3

2

1

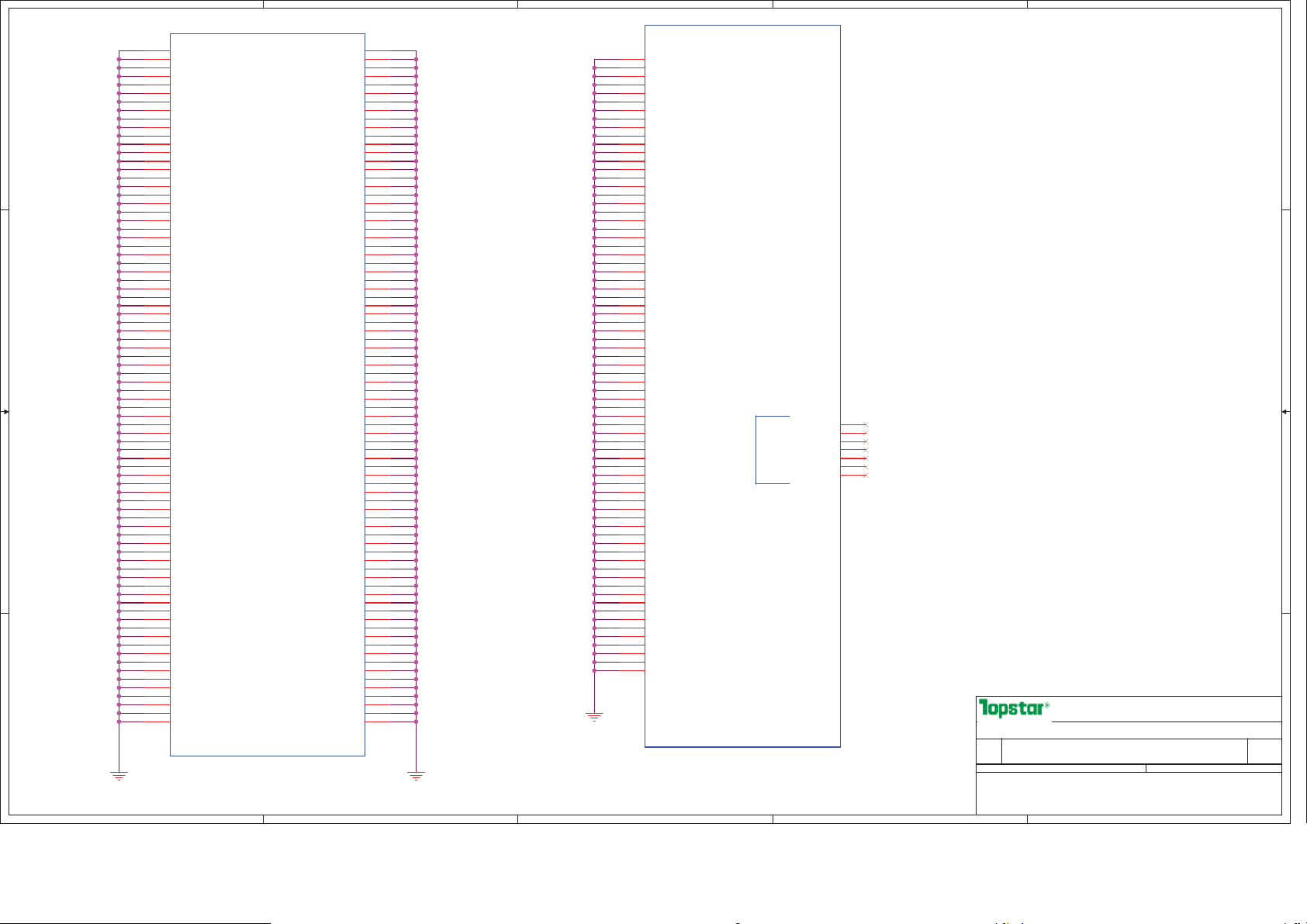

U2A

U2A

D D

C C

B B

A A

5

DMI_TXN0{25}

DMI_TXN1{25}

DMI_TXN2{25}

DMI_TXN3{25}

DMI_TXP0{25}

DMI_TXP1{25}

DMI_TXP2{25}

DMI_TXP3{25}

DMI_RXN0{25}

DMI_RXN1{25}

DMI_RXN2{25}

DMI_RXN3{25}

DMI_RXP0{25}

DMI_RXP1{25}

DMI_RXP2{25}

DMI_RXP3{25}

FDI_TXN[7:0]{25}

FDI_TXP[7:0]{25}

FDI_FSYNC0{25}

FDI_FSYNC1{25}

FDI_INT{25}

FDI_LSYNC0{25}

FDI_LSYNC1{25}

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

DMI Intel(R) FDI

DMI Intel(R) FDI

4

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PEG_IRCOMP_R

EXP_RBIAS

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

GC2190.1UF/10V,X7RPMGC2190.1UF/10V,X7R

GC2210.1UF/10V,X7RPMGC2210.1UF/10V,X7R

GC2230.1UF/10V,X7RPMGC2230.1UF/10V,X7R

GC2220.1UF/10V,X7RPMGC2220.1UF/10V,X7R

GC2240.1UF/10V,X7RPMGC2240.1UF/10V,X7R

GC2250.1UF/10V,X7RPMGC2250.1UF/10V,X7R

GC2270.1UF/10V,X7RPMGC2270.1UF/10V,X7R

GC2260.1UF/10V,X7RPMGC2260.1UF/10V,X7R

GC2280.1UF/10V,X7RPMGC2280.1UF/10V,X7R

GC2290.1UF/10V,X7RPMGC2290.1UF/10V,X7R

GC2310.1UF/10V,X7RPMGC2310.1UF/10V,X7R

GC2370.1UF/10V,X7R

GC2370.1UF/10V,X7R

GC2400.1UF/10V,X7R

GC2400.1UF/10V,X7R

GC2420.1UF/10V,X7R

GC2420.1UF/10V,X7R

GC2410.1UF/10V,X7R

GC2410.1UF/10V,X7R

GC2380.1UF/10V,X7R

GC2380.1UF/10V,X7R

GC2430.1UF/10V,X7R

GC2430.1UF/10V,X7R

GC2390.1UF/10V,X7R

GC2390.1UF/10V,X7R

GC2440.1UF/10V,X7R

GC2440.1UF/10V,X7R

GC2450.1UF/10V,X7R

GC2450.1UF/10V,X7R

GC2470.1UF/10V,X7R

GC2470.1UF/10V,X7R

GC2460.1UF/10V,X7R

GC2460.1UF/10V,X7R

GC2480.1UF/10V,X7R

GC2480.1UF/10V,X7R

GC2350.1UF/10V,X7R

GC2350.1UF/10V,X7R

GC2330.1UF/10V,X7R

GC2330.1UF/10V,X7R

GC2360.1UF/10V,X7R

GC2360.1UF/10V,X7R

GC2340.1UF/10V,X7R

GC2340.1UF/10V,X7R

GC2170.1UF/10V,X7RPMGC2170.1UF/10V,X7R

GC2180.1UF/10V,X7RPMGC2180.1UF/10V,X7R

GC2200.1UF/10V,X7RPMGC2200.1UF/10V,X7R

GC2300.1UF/10V,X7RPMGC2300.1UF/10V,X7R

GC2320.1UF/10V,X7RPMGC2320.1UF/10V,X7R

R11 49.9,1%

R11 49.9,1%

R12 750 OHM

R12 750 OHM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

PM

3

R0402

R0402

R0402

R0402

PEG_TXN[15..0] {17}

PEG_TXP[15..0] {17}

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_RXN[15..0] {17}

PEG_RXP[15..0] {17}

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Joseph

Joseph

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

the expressed written consent of TOPSTAR

Joseph

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

C49

C49

C49

1

A

A

A

of

of

of

759Friday, May 07, 2010

759Friday, May 07, 2010

759Friday, May 07, 2010

5

http://hobi-elektronika.net

D D

U2B

H_COMP3

H_COMP2

H_COMP1

S_Top

S_Top

S_Top

S_Top

S_Top

S_Top

S_Top

S_Top

S_Top

S_Top

VR_PROCHOT#

VCCPWRGOOD_1_R

VCCPWRGD_0_R

PLT_RST#_R

H_COMP0

H_CATERR#

H_PECI_R

H_CPURST#_R

H_PM_SYNC_R

+V1.1S_VTT

R21 49.9,1% R0402

R21 49.9,1% R0402

R23 0 R0402

R23 0 R0402

S_Top

S_Top

R26 68 R0402 ns

R26 68 R0402 ns

S_Top

S_Top

R27 0 R0402

R27 0 R0402

R487 0 R0402

R487 0 R0402

R488 0 R0402

R488 0 R0402

PM_DRAM_PWRGD

CPU_VTT_PWG

H_PWRGD_XDP_R

R29 1.5K,1% R0402

R29 1.5K,1% R0402

S_Top

S_Top

R33

R33

750 OHM

750 OHM

R0402

R0402

S_Top

S_Top

+V1.1S_VTT

H_PM_SYNC{25}

VCCPWRGD_0{28}

PM_DRAM_PWRGD{25}

BUF_PLT_RST#{17,27,34,35,37,41,42}

H_PECI{28}

R25 68 R0402 ns

R25 68 R0402 ns

THERMTRIP#{28,34}

+V1.1S_VTT

C C

+V1.1S_VTT

R413

R413

1K,1%

1K,1%

R0402

R0402

ns

ns

S_Top

S_Top

B B

U2B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

S_Bot

S_Bot

R34

R34

49.9,1%

49.9,1%

R0402

R0402

S_Top

S_Top

4

MISC THERMAL

MISC THERMAL

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

Processor Compensation

Signals

H_COMP1

H_COMP0

R36

R35

R35

49.9,1%

49.9,1%

R0402

R0402

S_Top

S_Top

R36

20,1%

20,1%

r0402

r0402

S_Bot

S_Bot

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

H_COMP3

H_COMP2

R37

R37

20,1%

20,1%

r0402

r0402

S_Bot

S_Bot

3

PM_EXT_TS#0

R30

R30

1K

1K

R0402ns

R0402ns

S_Top

S_Top

+V1.1S_VTT

R15

R15

10K

10K

R0402

R0402

S_Top

S_Top

+V1.1S_VTT

R22

R22

10K

10K

R0402

R0402

S_Top

S_Top

Layout Note:

Place close to CPU

BCLK_CPU_P_R

A16

BCLK_CPU_N_R

B16

BCLK_ITP_P

AR30

BCLK_ITP_N

AT30

CLK_EXP_P_R

E16

CLK_EXP_N_R

D16

CLK_DP_P_R

A18

CLK_DP_N_R

A17

F6

SM_RCOMP_0

AL1

SM_RCOMP_1

AM1

SM_RCOMP_2

AN1

AN15

PM_EXT_TS#1

AP15

AT28

AP27

AN28

TCK

AP28

TMS

AT27

AT29

TDI

AR27

TDO

TDI_M

AR29

TDO_M

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

XDP_REQ

TCK

TMS

TDI

TDO

R13 0 R0402

R13 0 R0402

R14 0 R0402

R14 0 R0402

R17 0 R0402

R17 0 R0402

R18 0 R0402

R18 0 R0402

R19 0 R0402 ns

R19 0 R0402 ns

R20 0 R0402 ns

R20 0 R0402 ns

TRST#

R562

R562

49.9,1%

49.9,1%

R0402

R0402

S_Bot

S_Bot

T48

T48

T20

T20

T42

T42

T43

T43

T44

T44

T46

T46

T45

T45

T47

T47

T37

T37

TDI_M

TDO_M

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

100,1%

100,1%

R0402

R0402

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

ns

ns

T24

T24

ns

ns

T36

T36

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

S_Bot

DDR3_DRAMRST# {14,15}

TDO

TMS

ns

ns

TCK

TDI

ns

ns

S_Top

S_Top

ns

ns

ns

ns

XDP_REQ

ns

ns

S_Top

S_Top

ns

ns

S_Top

S_Top

ns

ns

S_Top

S_Top

ns

ns

S_Top

S_Top

ns

ns

S_Top

S_Top

S_Top

S_Top

S_Top

S_Top

R265

R265

S_Top

S_Top

0

0

R0402

R0402

ns

ns

S_Top

S_Top

DDR3 Compensation Signals

R38

R38

R39

R39

24.9,1%

24.9,1%

R0402

R0402

S_Bot

S_Bot

BCLK_CPU_P {28}

BCLK_CPU_N {28}

CLK_EXP_P {24}

CLK_EXP_N {24}

R566 49.9,1% R0402

R566 49.9,1% R0402

ns

ns

S_Bot

S_Bot

R253 49.9,1% R0402

R253 49.9,1% R0402

ns

ns

S_Bot

S_Bot

R267 49.9,1% R0402

R267 49.9,1% R0402

ns

ns

S_Bot

S_Bot

R296 49.9,1% R0402

R296 49.9,1% R0402

ns

ns

S_Bot

S_Bot

R325 49.9,1% R0402

R325 49.9,1% R0402

ns

ns

S_Bot

S_Bot

R40

R40

130,1%

130,1%

R0402

R0402

S_Bot

S_Bot

PM_EXT_TS#1PM_EXT_TS#0

+V1.1S_VTT

1

R28

R28

10K

10K

R0402

R0402

S_Top

S_Top

+V3.3S

+V1.1S_VTT

R154

R154

1K

1K

R0402

R0402

ns

ns

S_Top

S_Top

Q28

Q28

Q1

Q1

MMBT3904-F

MMBT3904-F

SOT23

SOT23

ns

ns

2 3

S_Top

S_Top

2

+V1.1S_VTT {10,11,48,49,53}

+V3.3S {6,14,15,16,22,23,24,25,26,27,28,29,30,32,33,34,35,36,37,38,40,41,42,43,47,48,49,50,51,53,54,55,56}

+V1.5 {11,14,15,47,54,55,56}

+V1.1S_VTT

R59

R59

1K

1K

R0402

R0402

ns

ns

S_Top

S_Top

Q27

Q27

1

MMBT3904-FSOT23

MMBT3904-FSOT23

S_Top

S_Top

1

ns

ns

23

MMBT3904-FSOT23

MMBT3904-FSOT23

S_Top

S_Top

ns

ns

23

R51

R51

10K

10K

R0402

R0402

ns

ns

S_Top

S_Top

R24

R24

10K

10K

R0402

R0402

ns

ns

S_Top

S_Top

+V3.3S

+V3.3S

Voltage Level?

DIM_EXTTS#0 {14}

Voltage Level?

DIM_EXTTS#1 {15}

Ⳃࠡ៥Ӏ⫼ⱘݙᄬッ≵᳝خ䖛⏽ⱘࡳ㛑DŽ

+V1.1S_VTT

R31

R31

1K

1K

R0402

R0402

S_Top

S_Top

Q2

Q2

MMBT3904-F

MMBT3904-F

23

SOT23

SOT23

S_Top

S_Top

VR_PROCHOT#

EC_PROCHOT# {42}

R32

R32

1K

1K

R0402

R0402

S_Top

S_Top

1

+V1.1S_VTT+V1.1S_VTT

VR_PROCHOT# {53}

1

+V1.5

R215

R215

1.21K,1%

1.21K,1%

S_Top

S_Top

R234

R234

3.3K

3.3K

S_Top

S_Top

CPU_VTT_PWG{42}

R899

R899

750 OHM

750 OHM

S_Bot

S_Bot

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

4

3

2

the expressed written consent of TOPSTAR

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Joseph

Joseph

Joseph

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

C49

C49

C49

1

A

A

A

of

of

of

859Friday, May 07, 2010

859Friday, May 07, 2010

859Friday, May 07, 2010

A A

5

PM_DRAM_PWRGD

5

http://hobi-elektronika.net

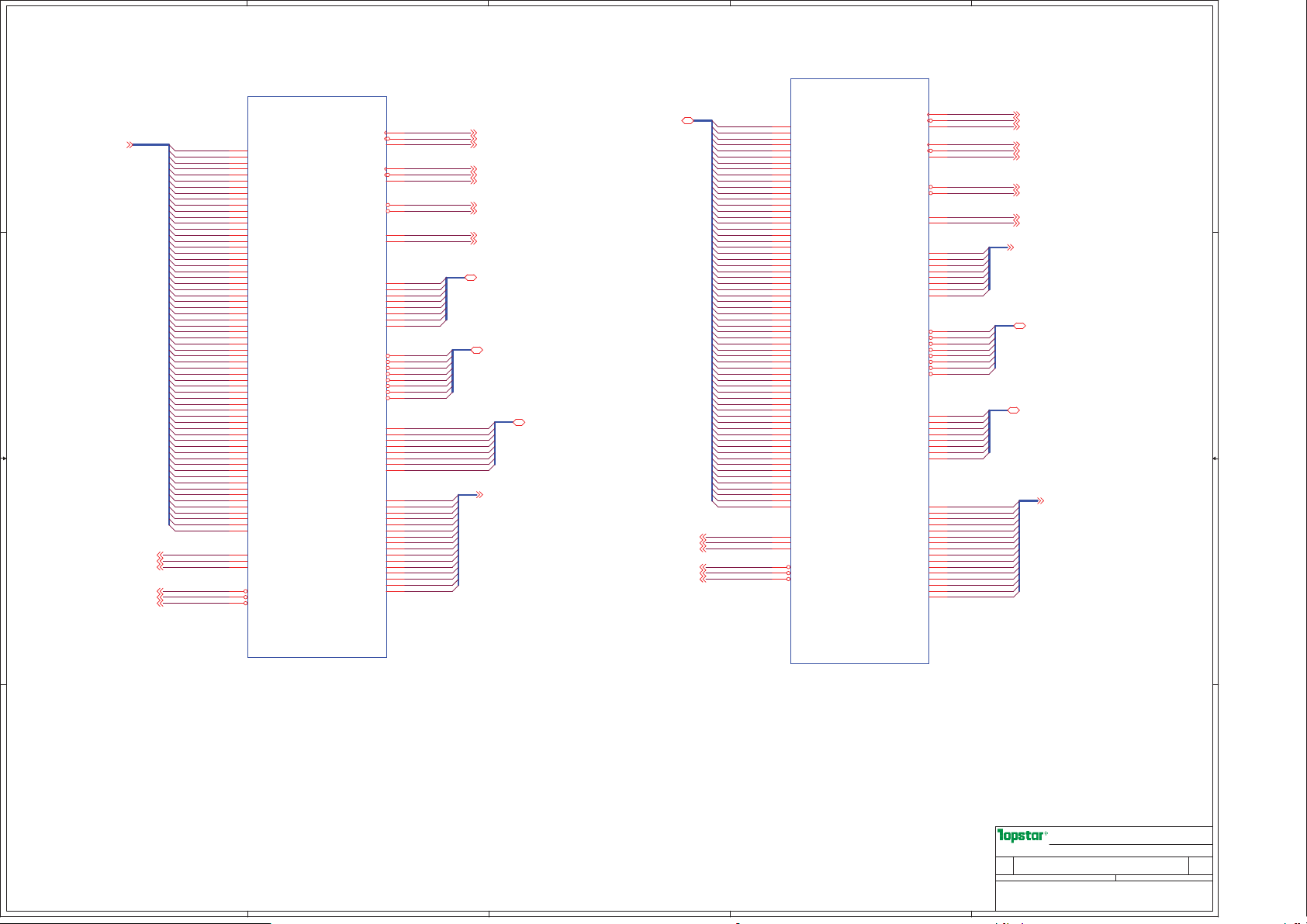

U2C

U2C

D D

MA_DATA[63:0]{14}

C C

MA_A_BS0{14}

MA_A_BS1{14}

B B

MA_A_BS2{14}

MA_A_CAS#{14}

MA_A_RAS#{14}

MA_A_WE#{14}

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

AM10

AM12

AM13

AJ10

AL10

AK12

AK11

AR11

AL11

AT11

AP12

AN12

AT14

AT12

AL13

AR14

AP14

A10

SA_DQ[0]

C10

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

B10

SA_DQ[4]

D10

SA_DQ[5]

E10

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

H10

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

G10

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

AH5

SA_DQ[32]

AF5

SA_DQ[33]

AK6

SA_DQ[34]

AK7

SA_DQ[35]

AF6

SA_DQ[36]

AG5

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

AK8

SA_DQ[44]

AL7

SA_DQ[45]

SA_DQ[46]

AL8

SA_DQ[47]

AN8

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

AM9

SA_DQ[52]

AN9

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AC3

SA_BS[0]

AB2

SA_BS[1]

U7

SA_BS[2]

AE1

SA_CAS#

AB3

SA_RAS#

AE9

SA_WE#

4

AA6

SA_CK[0]

AA7

SA_CK#[0]

P7

SA_CKE[0]

Y6

SA_CK[1]

Y5

SA_CK#[1]

P6

SA_CKE[1]

AE2

SA_CS#[0]

AE8

SA_CS#[1]

AD8

SA_ODT[0]

AF9

SA_ODT[1]

MA_DM0

B9

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

MA_DM1

D7

MA_DM2

H7

MA_DM3

M7

MA_DM4

AG6

MA_DM5

AM7

MA_DM6

AN10

MA_DM7

AN13

MA_DQS#0

C9

MA_DQS#1

F8

MA_DQS#2

J9

MA_DQS#3

N9

MA_DQS#4

AH7

MA_DQS#5

AK9

MA_DQS#6

AP11

MA_DQS#7

AT13

MA_DQS0

C8

MA_DQS1

F9

MA_DQS2

H9

MA_DQS3

M9

MA_DQS4

AH8

MA_DQS5

AK10

MA_DQS6

AN11

MA_DQS7

AR13

MA_A_A0

Y3

MA_A_A1

W1

MA_A_A2

AA8

MA_A_A3

AA3

MA_A_A4

V1

MA_A_A5

AA9

MA_A_A6

V8

MA_A_A7

T1

MA_A_A8

Y9

MA_A_A9

U6

MA_A_A10

AD4

MA_A_A11

T2

MA_A_A12

U3

MA_A_A13

AG8

MA_A_A14

T3

MA_A_A15 MB_B_A14

V9

M_CLK_DDR0 {14}

M_CLK_DDR#0 {14}

M_CKE0 {14}

M_CLK_DDR1 {14}

M_CLK_DDR#1 {14}

M_CKE1 {14}

M_CS#0 {14}

M_CS#1 {14}

M_ODT0 {14}

M_ODT1 {14}

MA_DM[7:0] {14}

MA_DQS#[7:0] {14}

MA_A_A[15:0] {14}

MA_DQS[7:0] {14}

3

U2D

U2D

MB_DATA[63:0]{15}

MB_B_BS0{15}

MB_B_BS1{15}

MB_B_BS2{15}

MB_B_CAS#{15}

MB_B_RAS#{15}

MB_B_WE#{15}

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

AR10

AT10

B5

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

2

W8

SB_CK[0]

W9

SB_CK#[0]

M3

SB_CKE[0]

V7

SB_CK[1]

V6

SB_CK#[1]

M2

SB_CKE[1]

AB8

SB_CS#[0]

AD6

SB_CS#[1]

AC7

SB_ODT[0]

AD1

SB_ODT[1]

MB_DM0

D4

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

MB_DM1

E1

MB_DM2

H3

MB_DM3

K1

MB_DM4

AH1

MB_DM5

AL2

MB_DM6

AR4

MB_DM7

AT8

MB_DQS#0

D5

MB_DQS#1

F4

MB_DQS#2

J4

MB_DQS#3

L4

MB_DQS#4

AH2

MB_DQS#5

AL4

MB_DQS#6

AR5

MB_DQS#7

AR8

MB_DQS0

C5

MB_DQS1

E3

MB_DQS2

H4

MB_DQS3

M5

MB_DQS4

AG2

MB_DQS5

AL5

MB_DQS6

AP5

MB_DQS7

AR7

MB_B_A0

U5

MB_B_A1

V2

MB_B_A2

T5

MB_B_A3

V3

MB_B_A4

R1

MB_B_A5

T8

MB_B_A6

R2

MB_B_A7

R6

MB_B_A8

R4

MB_B_A9

R5

MB_B_A10

AB5

MB_B_A11

P3

MB_B_A12

R3

MB_B_A13

AF7

P5

MB_B_A15

N1

M_CLK_DDR2 {15}

M_CLK_DDR#2 {15}

M_CKE2 {15}

M_CLK_DDR3 {15}

M_CLK_DDR#3 {15}

M_CKE3 {15}

M_CS#2 {15}

M_CS#3 {15}

M_ODT2 {15}

M_ODT3 {15}

MB_DM[7:0] {15}

MB_DQS#[7:0] {15}

MB_DQS[7:0] {15}

MB_B_A[15:0] {15}

1

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

A A

5

4

3

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Joseph

Joseph

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

the expressed written consent of TOPSTAR

Joseph

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

C49

C49

C49

1

A

A

A

of

of

of

959Friday, May 07, 2010

959Friday, May 07, 2010

959Friday, May 07, 2010

5

http://hobi-elektronika.net

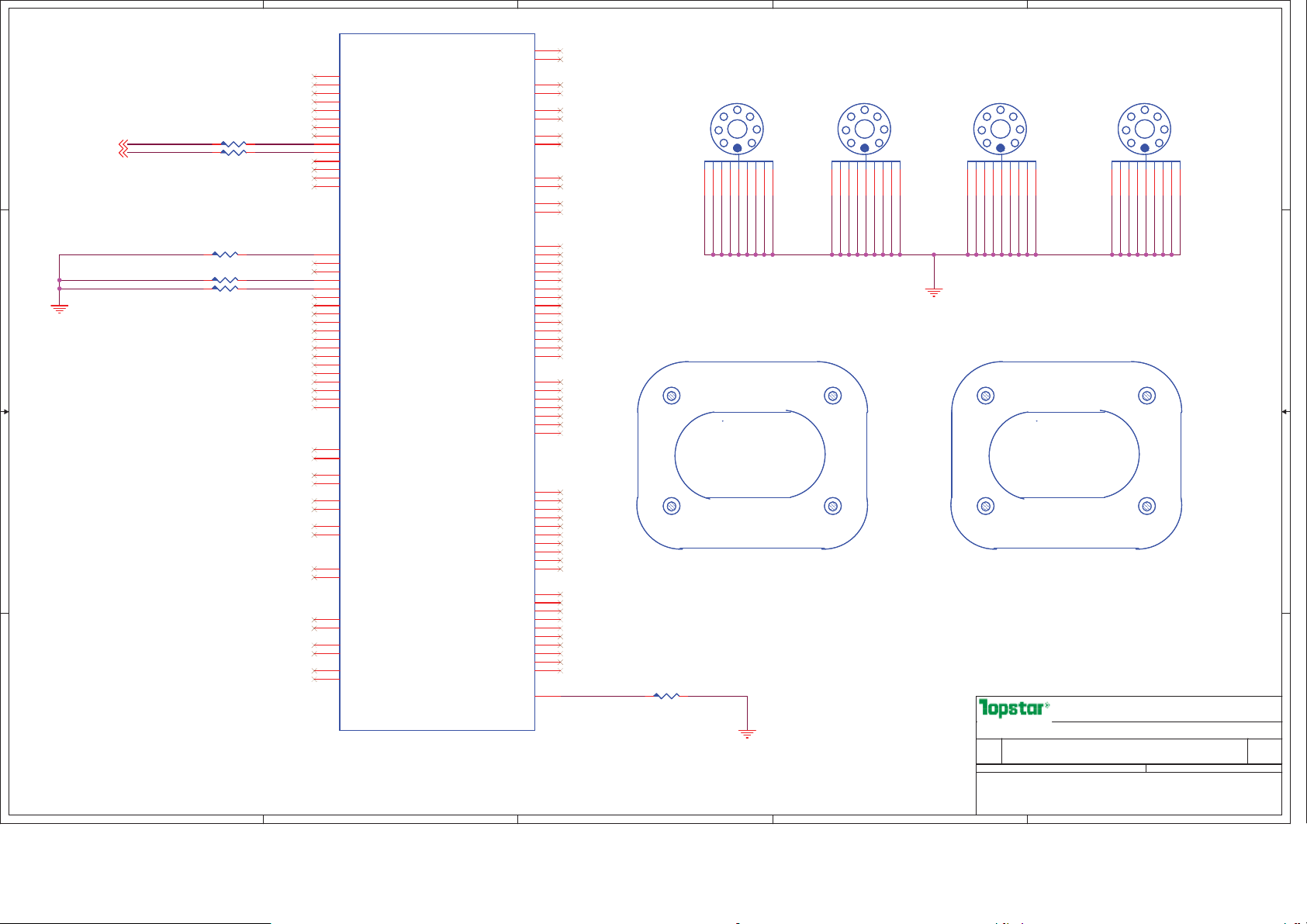

U2F

U2F

+VCC_CORE +V1.1S_VTT

4

Clarksfield 1.1v

3

2

+VCC_CORE {53}

+V1.1S_VTT {8,11,48,49,53}

1

Arrandale 1.05v

D D

C C

B B

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

PSI#

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

VTT_SELECT_R

G15

Vcore_IMON_R

AN35

VCCSENSE_R

AJ34

VSSSENSE_R

AJ35

B15

A15

C14

C14

10uF/6.3V,X5R

10uF/6.3V,X5R

C20

C20

10uF/6.3V,X5R

10uF/6.3V,X5R

C26

C26

10uF/6.3V,X5R

10uF/6.3V,X5R

R41 0R0402R41 0R0402

R42 0

R42 0

R0402

R0402

R44 0R0402R44 0R0402

R45 0R0402R45 0R0402

C15

C15

10uF/6.3V,X5R

10uF/6.3V,X5R

C21

C21

10uF/6.3V,X5R

10uF/6.3V,X5R

C27

C27

10uF/6.3V,X5R

10uF/6.3V,X5R

Vcore_IMON {53}

ns

ns

ICTP

ICTP

T3

T3

ns

ns

ICTP

ICTP

T1

T1

C16

C16

10uF/6.3V,X5R

10uF/6.3V,X5R

C22

C22

10uF/6.3V,X5R

10uF/6.3V,X5R

+V1.1S_VTT

PM_PSI# {53}

H_VID0 {53}

H_VID1 {53}

H_VID2 {53}

H_VID3 {53}

H_VID4 {53}

H_VID5 {53}

H_VID6 {53}

PM_DPRSLPVR {53}

VTT_SELECT {48}

+VCC_CORE

R43

R43

100,1%

100,1%

R0402

R0402

R46

R46

100,1%

100,1%

R0402

R0402

C17

C17

10uF/6.3V,X5R

10uF/6.3V,X5R

C23

C23

10uF/6.3V,X5R

10uF/6.3V,X5R

VCCSENSE {53}

VSSSENSE {53}

C18

C18

10uF/6.3V,X5R

10uF/6.3V,X5R

C24

C24

0.22uF/10V,X7R

0.22uF/10V,X7R

C39

C39

10uF/6.3V,X5R

10uF/6.3V,X5R

C51

C51

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C19

C19

10uF/6.3V,X5R

10uF/6.3V,X5R

C25

C25

0.01uF/25V,X7R

0.01uF/25V,X7R

C28

C28

10uF/6.3V,X5R

10uF/6.3V,X5R

C40

C40

10uF/6.3V,X5R

10uF/6.3V,X5R

C52

C52

10uF/6.3V,X5R

10uF/6.3V,X5R

C29

C29

10uF/6.3V,X5R

10uF/6.3V,X5R

C41

C41

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C53

C53

10uF/6.3V,X5R

10uF/6.3V,X5R

PM_PSI# PM_DPRSLPVR

C31

C31

C30

C30

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C42

C42

10uF/6.3V,X5R

10uF/6.3V,X5R

C54

C54

10uF/6.3V,X5R

10uF/6.3V,X5R

+V1.1S_VTT +V1.1S_VTT

R58

R58

1K

1K

R0402

R0402

ns

ns

R155

R155

1K

1K

R0402

R0402

C32

C32

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C43

C43

10uF/6.3V,X5R

10uF/6.3V,X5R

C55

C55

10uF/6.3V,X5R

10uF/6.3V,X5R

C44

C44

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C56

C56

1uF/10V,X7R

1uF/10V,X7R

C33

C33

10uF/6.3V,X5R

10uF/6.3V,X5R

C45

C45

10uF/6.3V,X5R

10uF/6.3V,X5R

C34

C34

10uF/6.3V,X5R

10uF/6.3V,X5R

C57

C57

1uF/10V,X7R

1uF/10V,X7R

C46

C46

10uF/6.3V,X5R

10uF/6.3V,X5R

C35

C35

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C58

C58

0.22uF/10V,X7R

0.22uF/10V,X7R

C47

C47

10uF/6.3V,X5R

10uF/6.3V,X5R

C59

C59

0.22uF/10V,X7R

0.22uF/10V,X7R

R156

R156

1K

1K

R0402

R0402

R157

R157

1K

1K

R0402

R0402

ns

ns

C36

C36

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C48

C48

10uF/6.3V,X5R

10uF/6.3V,X5R

C37

C37

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C49

C49

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C60

C60

0.01uF/25V,X7R

0.01uF/25V,X7R

+VCC_CORE

C38

C38

10uF/6.3V,X5R

10uF/6.3V,X5R

C50

C50

10uF/6.3V,X5R

10uF/6.3V,X5R

ns

ns

C61

C61

0.01uF/25V,X7R

0.01uF/25V,X7R

C62

C62

10uF/6.3V,X5R

10uF/6.3V,X5R

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

A A

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Joseph

Joseph

Joseph

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

C49

C49

C49

1

A

A

A

of

of

of

10 59Friday, May 07, 2010

10 59Friday, May 07, 2010

10 59Friday, May 07, 2010

5

4

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

3

2

the expressed written consent of TOPSTAR

5

http://hobi-elektronika.net

D D

4

3

2

+VGFX {49}

+V1.1S_VTT {8,10,48,49,53}

+V1.5 {8,14,15,47,54,55,56}

+V1.8S {16,27,29,30,47,54,55}

1

+VGFX

C64

C64

10uF/6.3V,X5R

10uF/6.3V,X5R

C C

C67

C67

0.22uF/10V,X7R

0.22uF/10V,X7R

+V1.1S_VTT

+V1.1S_VTT

B B

C68

C68

0.01uF/25V,X7R

0.01uF/25V,X7R

C81

C81

10uF/6.3V,X5R

10uF/6.3V,X5R

C65

C65

10uF/6.3V,X5R

10uF/6.3V,X5R

C77

C77

10uF/6.3V,X5R

10uF/6.3V,X5R

C82

10uF/6.3V,X5R

10uF/6.3V,X5R

C82

C66

C66

10uF/6.3V,X5R

10uF/6.3V,X5R

C69

C69

10uF/6.3V,X5R

10uF/6.3V,X5R

C78

C78

10uF/6.3V,X5R

10uF/6.3V,X5R

C70

C70

10uF/6.3V,X5R

10uF/6.3V,X5R

C83

C83

10uF/6.3V,X5R

10uF/6.3V,X5R

C63

C63

10uF/6.3V,X5R

10uF/6.3V,X5R

C84

C84

10uF/6.3V,X5R

10uF/6.3V,X5R

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AK21

AK19

AK18

AK16

AH21

AH19

AH18

AH16

AL21

AL19

AL18

AL16

AJ21

AJ19

AJ18

AJ16

U2G

U2G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

GRAPHICS

GRAPHICS

FDI PEG & DMI

FDI PEG & DMI

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GFX_DPRSLPVR

GRAPHICS VIDs

GRAPHICS VIDs

POWER

POWER

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

VAXG_SENSE

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

VGFXVCCSEN {49}

VGFXVSSSEN {49}

GFXVR_VID_0 {49}

GFXVR_VID_1 {49}

GFXVR_VID_2 {49}

GFXVR_VID_3 {49}

GFXVR_VID_4 {49}

GFXVR_VID_5 {49}

GFXVR_VID_6 {49}

GFXVR_DPRSLPVR {49}

VGFX_IMON {49}

C72

C72

C71

C71

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

10uF/6.3V,X5R

C79

C79

10uF/6.3V,X5R

10uF/6.3V,X5R

VCCPLL

C73

C73

1uF/10V,X7R

1uF/10V,X7R

C80

C80

10uF/6.3V,X5R

10uF/6.3V,X5R

C74

C74

1uF/10V,X7R

1uF/10V,X7R

C85

C85

10uF/6.3V,X5R

10uF/6.3V,X5R

GFXVR_EN {49}

R705

R705

470

470

R0402

R0402

C75

C75

1uF/10V,X7R

1uF/10V,X7R

+V1.1S_VTT

+V1.1S_VTT

C86

C86

10uF/6.3V,X5R

10uF/6.3V,X5R

+V1.5

C76

C76

1uF/10V,X7R

1uF/10V,X7R

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

+V1.8S

VCCPLL

C87

C87

1uF/10V,X7R

1uF/10V,X7R

A A

5

4

C88

C88

1uF/10V,X7R

1uF/10V,X7R

C89

C89

1uF/10V,X7R

1uF/10V,X7R

3

FB3

1 2

300ohm@100MHz,1.5A

300ohm@100MHz,1.5A

C90

C90

10uF/6.3V,X5R

10uF/6.3V,X5R

FB0805FB3

FB0805

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Joseph

Joseph

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

the expressed written consent of TOPSTAR

Joseph

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

N11M PCIE&PWR&GND

C49

C49

C49

1

A

A

A

of

of

of

11 59Friday, May 07, 2010

11 59Friday, May 07, 2010

11 59Friday, May 07, 2010

5

http://hobi-elektronika.net

U2H

U2H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

D D

C C

B B

A A

VSS8

AR17

VSS9

AR15

VSS10

AR12

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

AP20

VSS15

AP17

VSS16

AP13

VSS17

AP10

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

AN34

VSS22

AN31

VSS23

AN23

VSS24

AN20

VSS25

AN17

VSS26

AM29

VSS27

AM27

VSS28

AM25

VSS29

AM20

VSS30

AM17

VSS31

AM14

VSS32

AM11

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

AL34

VSS37

AL31

VSS38

AL23

VSS39

AL20

VSS40

AL17

VSS41

AL12

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

AK29

VSS46

AK27

VSS47

AK25

VSS48

AK20

VSS49

AK17

VSS50

AJ31

VSS51

AJ23

VSS52

AJ20

VSS53

AJ17

VSS54

AJ14

VSS55

AJ11

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

AH35

VSS60

AH34

VSS61

AH33

VSS62

AH32

VSS63

AH31

VSS64

AH30

VSS65

AH29

VSS66

AH28

VSS67

AH27

VSS68

AH26

VSS69

AH20

VSS70

AH17

VSS71

AH13

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

AG10

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

AE35

VSS80

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

5

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

4

4

3

U2I

U2I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

3

VSS

VSS

NCTF

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

2

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

B

B

B

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to