TOPSTAR N01 Schematics

5

4

3

2

1

Topstar Digital technologies Co.,LTD

D D

Board name: Mother Board Schematic

Project name: N01

Version: VerA

initial Date:

1. System Block Diagram & Schematic page description;

2. Power Block Diagram & Discription;

3. Annotations & information;

4. Schematic modify Item and history;

New update: 5. Power on & off Sequence;

6. ACPI Mode Switch Timings;

7. Power On Sequence Map;

8. CLOCK Distribution;

C C

9. Power Distribution;

Topstar Confidential

Hardware drawing by: Hardware check by: EMI Check by:

Power drawing by:

B B

Power check by:

Manager Sign by:

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

the expressed written consent of TOPSTAR

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

Title

Title

Title

N01

N01

N01

1

A

A

142Wednesday, July 16, 2008

142Wednesday, July 16, 2008

142Wednesday, July 16, 2008

A

of

of

of

5

4

3

2

1

CONTENT

Topstar Confidential

1 Title

ShenZhen Topstar Industry Co.,LTD

D D

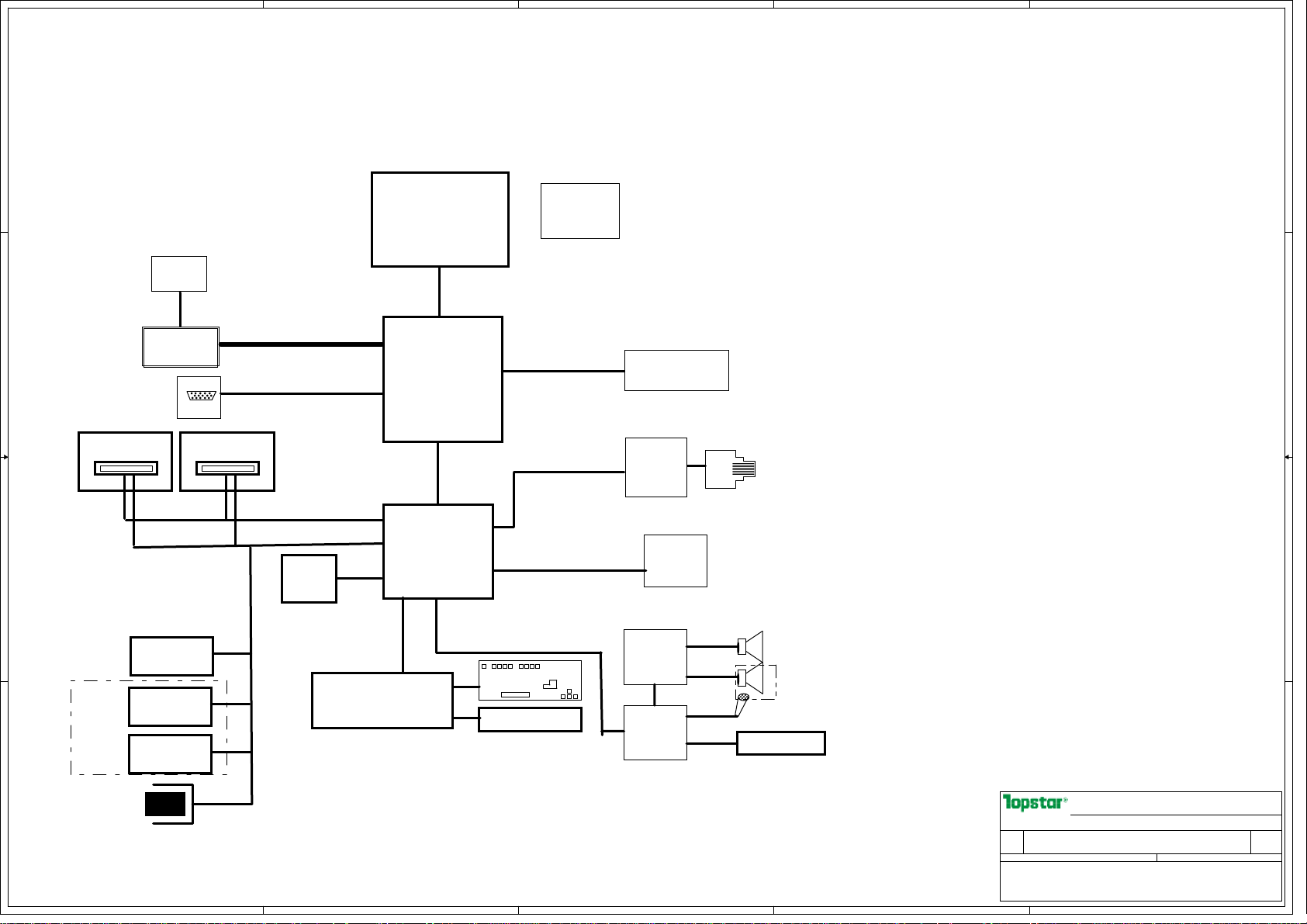

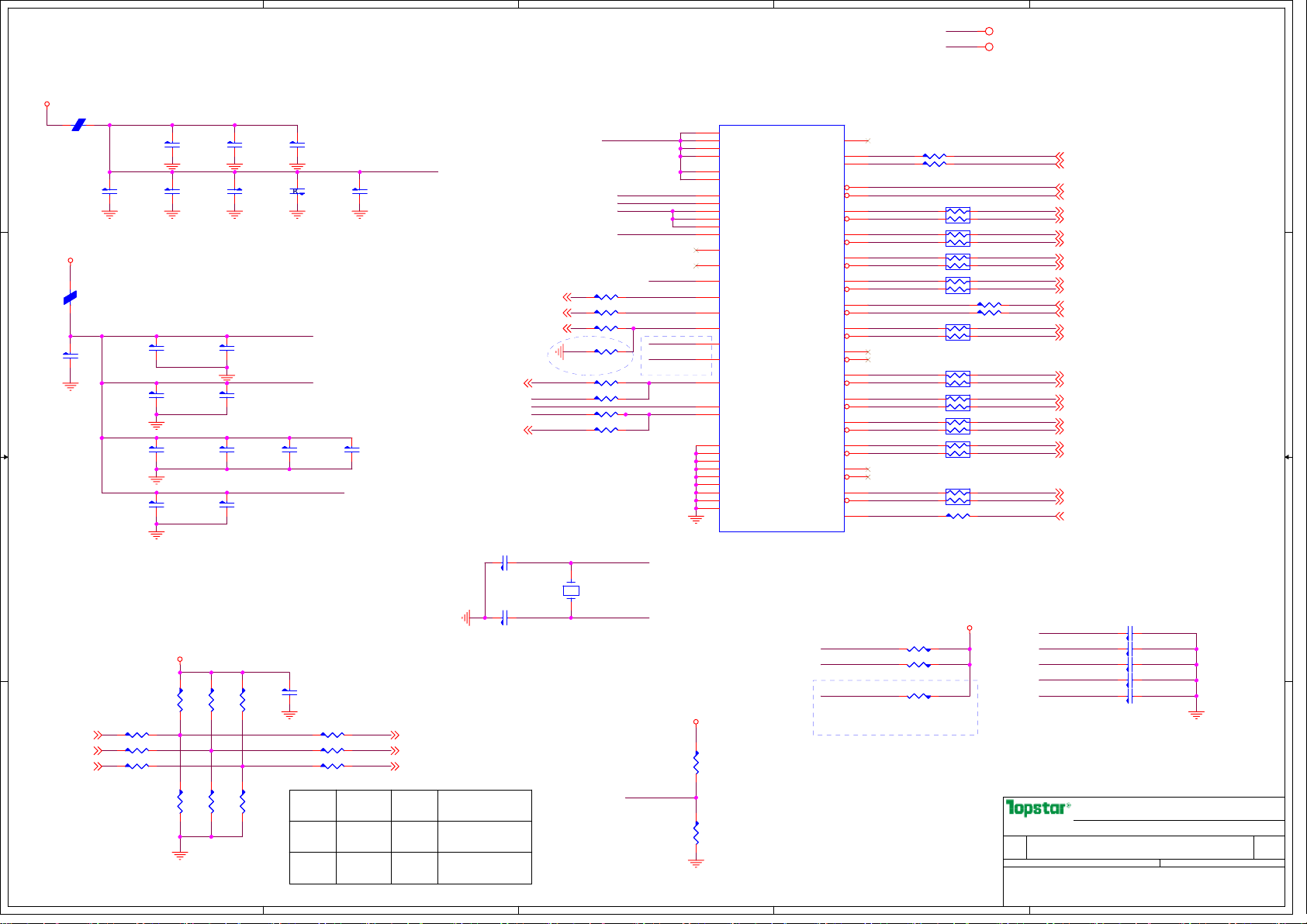

N01 SYSTEM BLOCK Ver:A

Diamondville SC

FCBGA 437PIN

+VCC_CORE,+VCCP

+VCCA1.5

Backlight

Connector

+VDC

PG 15

10.21' TFT

C C

PCIE mini Card

PG 24

+V3.3S

PG 15

VGA

+V5S

PG 16

PCIE mini Card

PG 23

LVDS

R/G/B

PCIE 1X

USB1.1/2.0

B B

BIOS

8Mbit

+V3.3AL

PG 18

USB PORT1

+V5AL

PG 25

USB PORT2

+V5AL

USB PORT3

+V5AL

Daught Board

A A

SD/MMC/MS/XD CARD

KB Controller/EC

W83L951DG

+V3.3AL

PG 22

5

PG 7,8

FSB

533MHz

Calistoga GSE

998 FCBGA

+V3.3S,+V1.5S,

+V1.05S,+V1.8

+V2.5S

PG 9,10,11,

12,13

DMI

x2

ICH7-M

82801GBM 652 BGA

+V1.05S,+V3.3S

+V3.3AL,+V5AL

+V1.5S,+V5S

+V3.3A_RTC

PG 17,18,19,20

PG 29

4

LED & TouchPAD

KB Matrix

CK505M

Clocking

CY28548

+V3.3S

DDR2

400/533

PCIE X1

SATAO(R1.0)

HDA

PG 6

DDR2 SODIMM1

400/533

+V0.9S,+V1.8,+V3.3S

PG 14

10/100M

LAN

RTL8101E

+V5S,+V3.3S

PG 30

S-ATA

2.5" HHD

+V5S,+V3.3S

PG 21

AMP

TPS6017A2

+V5S

PG 26

AZALIA

ALC662

+V5S,+V3.3S

PG 26

3

RJ45

Speaker

L

R

MiC

PG 26

Audio Jack

2 System Block & Sch Page

3 PWR Block & description

4 NOTE and Annotations

5 Sch Modify and history

6 CK-505M

7 Diamondvill (1of2)(Host BUS)

8 Diamondvill (2of2)(Power &GND)

9 Calistoga(HOST)

10 Calistoga(Graphic)

11 Calisoga(DDRII& NCTF)

12 Calisoga(Power)

13 Calistoga(VSS&NC)

14 DDRII SODIMM0

15 LVDS Inverter CONN

16 CRT CONN

17 ICH7_M(1 of 4)

18 ICH7_M(2 of 4)

19 ICH7_M(3 of 4)

20 ICH7_M(4 of 4

21 SATA HDD

22 Card Reader(UB6232 USB)

23 PCIE MINI SLOT 1

24 PCIE MINI SLOT 2

25 USB Port & FAN

26 Audio (ALC662)

27 LED

28 OTP

29 KBC(W83L951DG)

30 LAN(RTL8101E)

31 ADAPTER IN

32 BATTERY JACK

33 V3.3AL/+V5AL POWER

34 DDR V1.8/+V0.9S POWER

35 V1.5S/+V1.05S POWER

36 Power Good Logic_OVP

37 Power Discharge Circuit

38 System 2.5V

39 VCORE POWER

40 CHARGER

41 Power On Secquence & Reset M

42 Power ON/OFF

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

System Block & Index

System Block & Index

System Block & Index

N01

N01

N01

1

A

A

A

of

of

of

242Wednesday, July 16, 2008

242Wednesday, July 16, 2008

242Wednesday, July 16, 2008

5

4

3

2

1

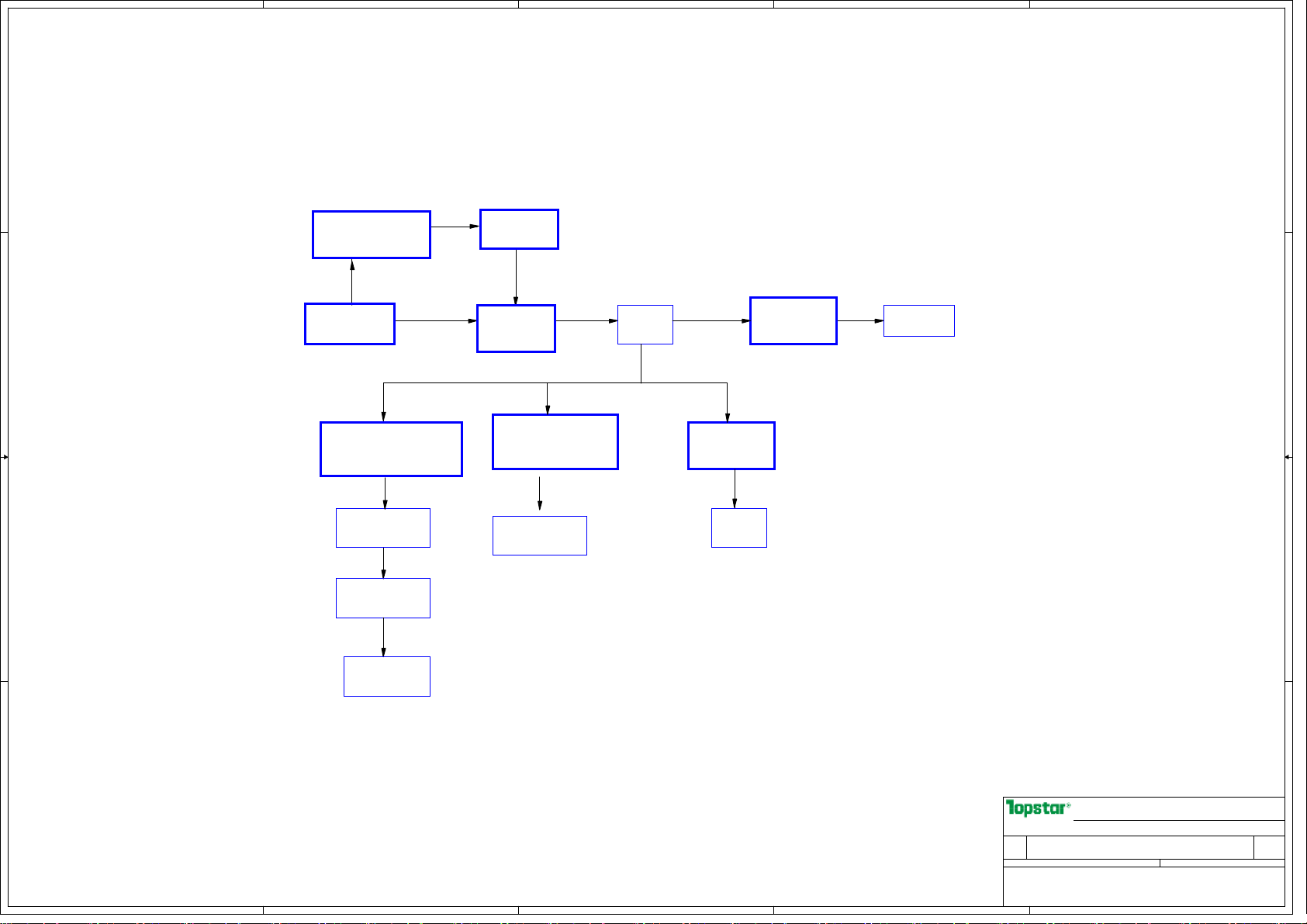

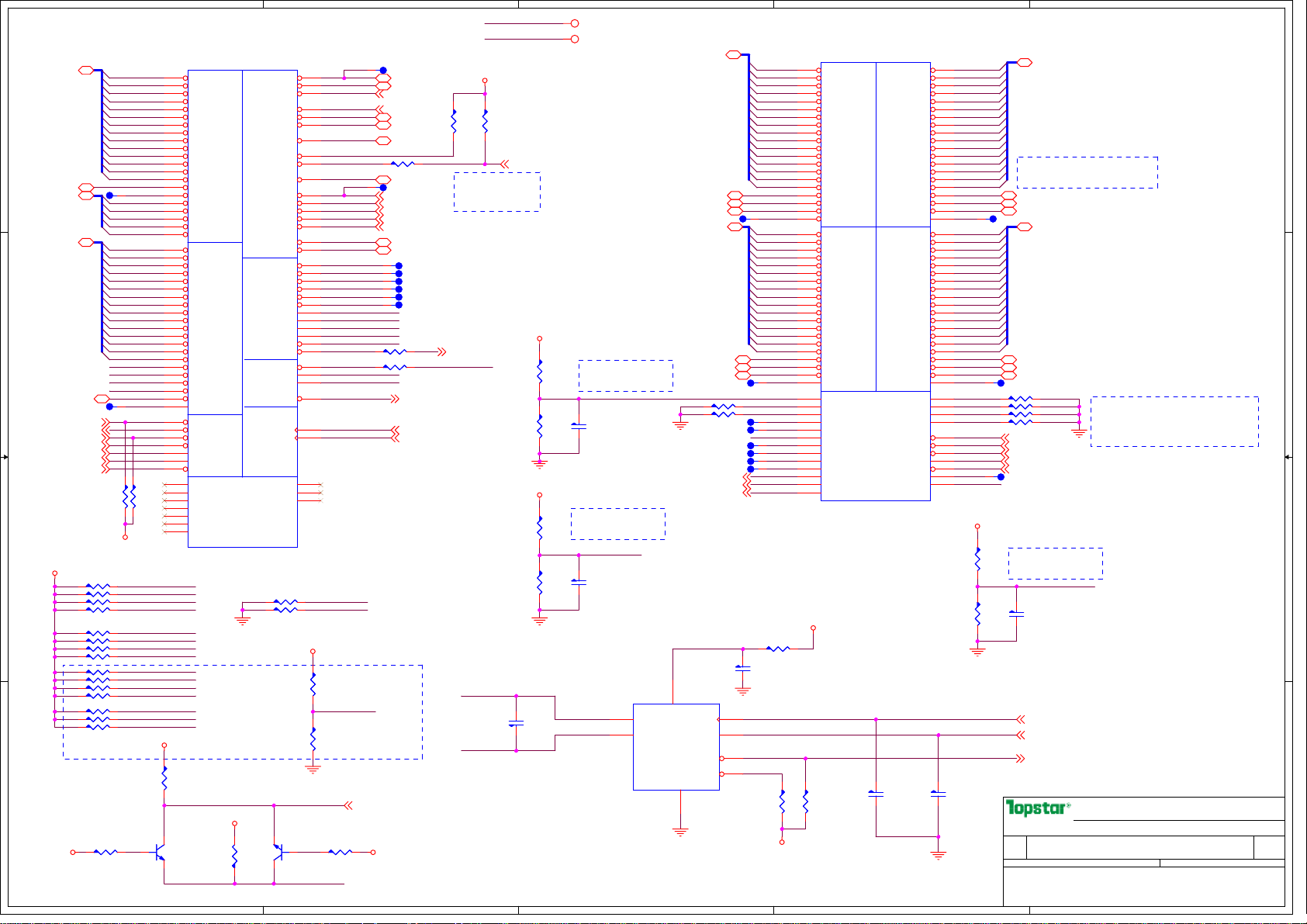

N01 POWER BLOCK Ver:A

D D

Charger power

ISL6251

PU9

Adapter

12V 2.5A

C C

Always power

ISL6545

PU1/PU2

+V3.3AL,2A

/+V5AL,3A

MOSFET

B B

Switch

Battery

7.4V-8.4V

4A

Power

Switch

Chipset Power

ISL6545

PU4/PU5

+V1.5S,3A

/+V1.05S,3A

+VDC

DDR Power

TPS51116

PU3

+V1.8

+V0.9S

VCC_CORE

ISL6545

PU8

+VCC_CORE

1.1V,5A

+V3.3S,2A

/+V5S,3A

LDO

+V2.5S,0.5A

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

the expressed written consent of TOPSTAR

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

PWR Block & description

PWR Block & description

PWR Block & description

N01

N01

N01

1

A

A

342Wednesday, July 16, 2008

342Wednesday, July 16, 2008

342Wednesday, July 16, 2008

A

of

of

of

5

A

4

3

2

1

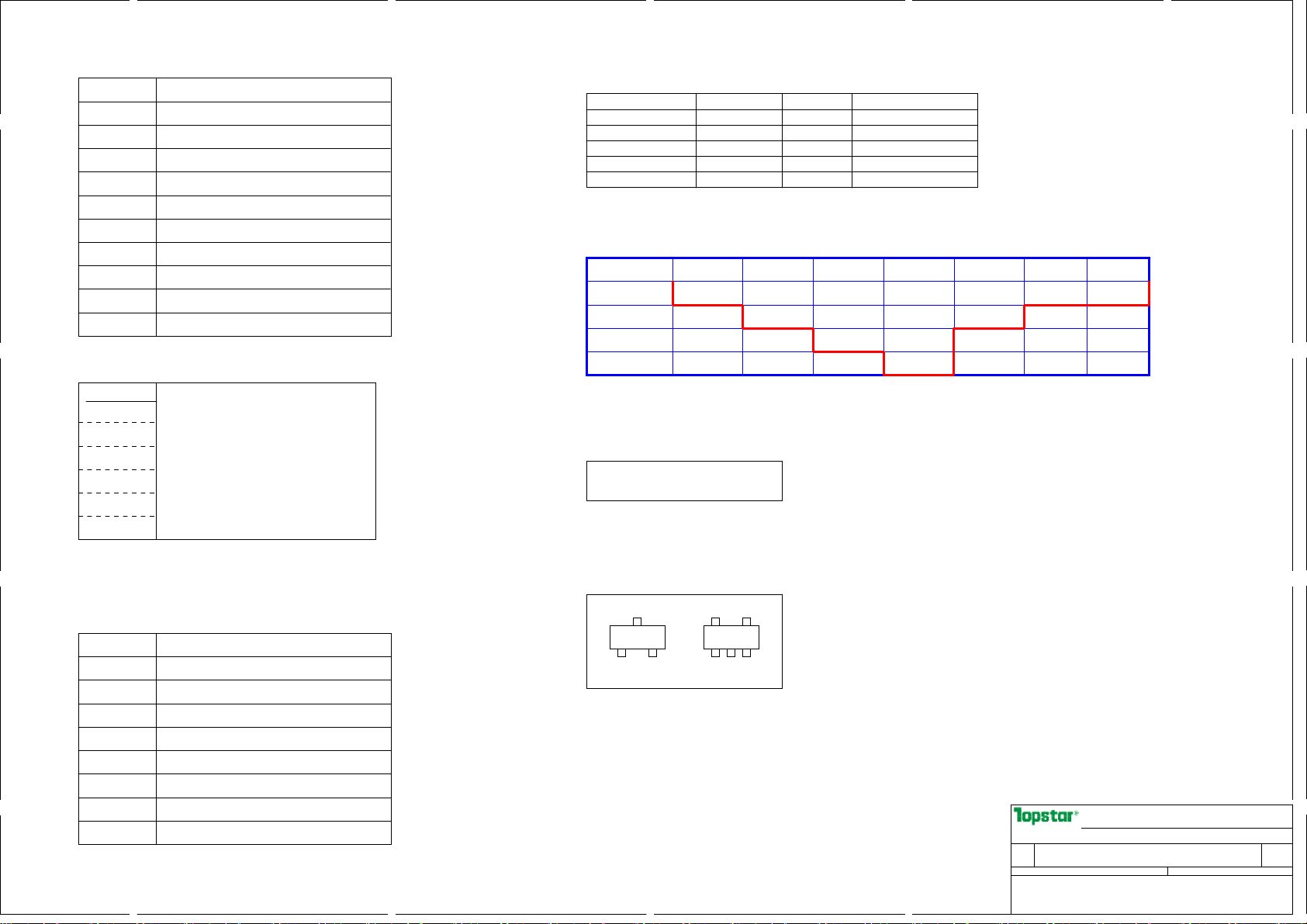

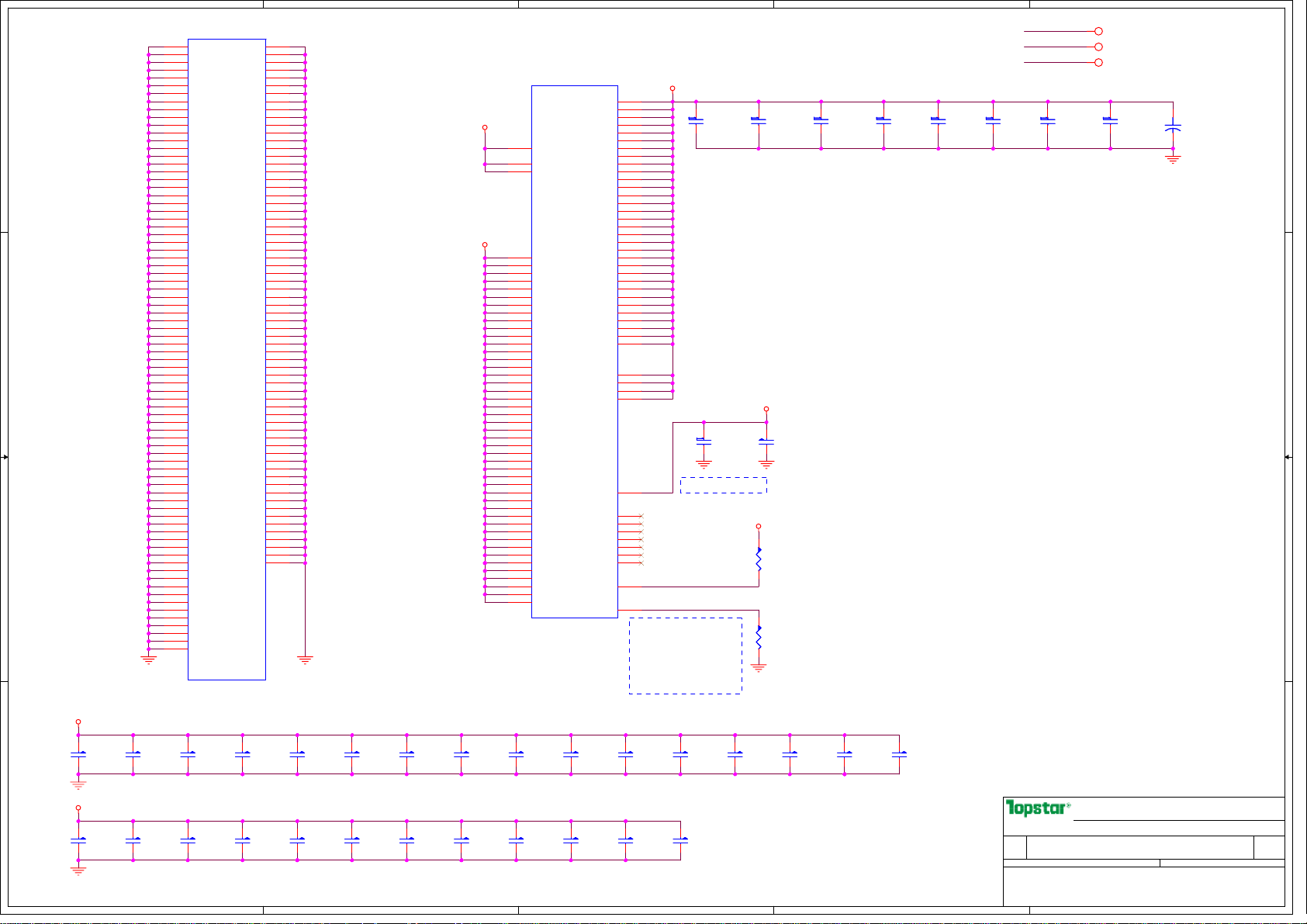

Voltage Rails

+VDC

D D

+VBATTERY

+VCC_CORE

+V1.05S

+V1.8

+V0.9S

+V3.3AL

+V5AL

+V3.3S

+V5S

+V2.5S 2.5V power rail for 945GMS

Primary DC system power supply (6V-9.5V)

Battery Power supply (6-8.4V)

Core Voltage for CPU

1.05V for Calistoga & ICH7M core / FSB VTT

1.8V power rail for DDR2

0.9V DDR2 Termination voltage

3.3V always on power rail

5V for ICH7-M's VCC5 Refsus

3.3V main power rail

5V main power rail

C C

Board stack up description

PCB Layers

Top(Signal1)

VCC 2

Signal 3

Signal4

Ground 5

Bottom(Signal6)

Trace Impedence:55ohm +/-15%

I2C SMB Address

Device

Clock Generator

SO-DIMM0

CPU Thermal Sensor

Smart Battery

PCIE Slot

Power States

Signal

S0(Full On)

S3(STM)

S4(STD)

S5(SoftOff)

SLP_S3#

HIGH

LOW

LOW OFF

LOW

Wake up Events

LID switch from EC

Power switch from EC

Address Hex

1101 001x

1010 000x

1001 100x

0001 011x

TBD

SLP_S4#

D2

A0

98

16

TBD

HIGH

HIGH ON OFF

LOW

LOW

SLP_S5#

HIGH

HIGH

HIGH

LOW

Master

ICH7-M

ICH7-M

KBC

KBC

ICH7-M

+V*ALW

ON

ON

ON

+V*

ON ON

ON

OFF

+V*S

OFF

OFF

OFF

Clock

ON

OFF

OFF

B B

USB Table

USB Port#

0

1

2

3

4

5

6

7

Function Description

Standard USB2.0 Port

Standard USB2.0 Port

Standard USB2.0 Port

MINICARD_USB

CAM_USB

MINICARD_USB

CR_USB

NC

PCB Footprints

3

SOT23

1 2

5

SOT23_5

3

21

4

ns: Component marked "ns" is not stuff

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

Swain Xu

NOTE

NOTE

NOTE

N01

N01

N01

442Wednesday, July 16, 2008

442Wednesday, July 16, 2008

442Wednesday, July 16, 2008

of

of

of

A

A

A

A

5

4

3

2

1

Schematic modify Item and history:

D D

C C

B B

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

the expressed written consent of TOPSTAR

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

Sch Modify and history

Sch Modify and history

Sch Modify and history

A

A

A

1

A

A

542Wednesday, July 16, 2008

542Wednesday, July 16, 2008

542Wednesday, July 16, 2008

A

of

of

of

5

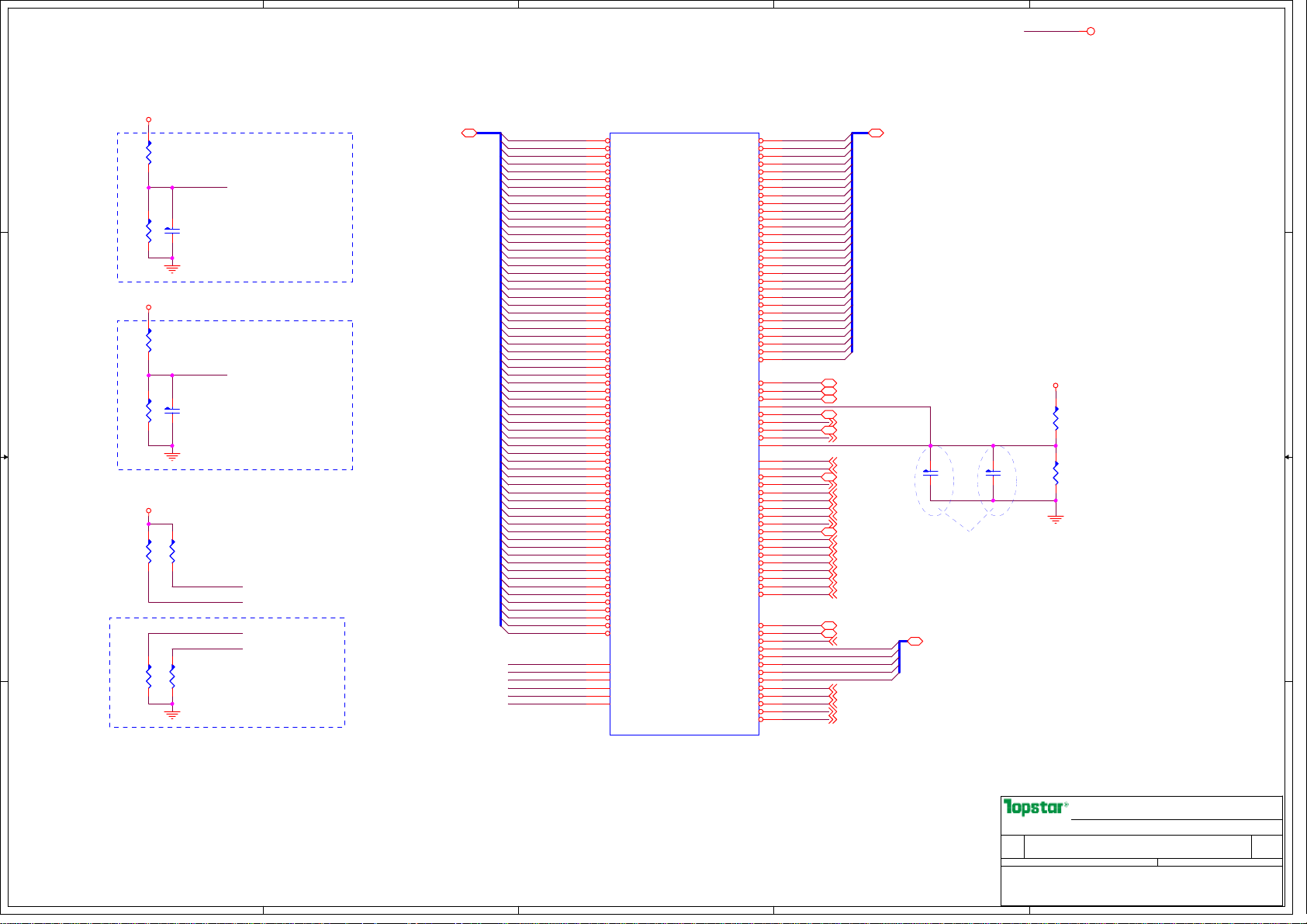

+V3.3S

FB28

FB28

FB0805

FB0805

100ohm@100MHz,3A

100ohm@100MHz,3A

D D

C C

1 2

+V3.3S

12

FB29

FB29

100ohm@100MHz,3A

100ohm@100MHz,3A

FB0805

FB0805

C394

C394

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C388

C388

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C390

C390

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C392

C392

4.7UF/10V,Y5V

4.7UF/10V,Y5V

C0805

C0805

C395

C395

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C399

C399

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C401

C401

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

C405

C405

10UF/6.3V,X5R

10UF/6.3V,X5R

C0805

C0805

ns

ns

C391

C391

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C393

C393

0.047uF/16V,X7R

0.047uF/16V,X7R

C0402

C0402

+VDDIO_CLK

C396

C396

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

+VDDIO_CLK

C400

C400

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C402

C402

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C406

C406

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C389

C389

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C398

C398

0.047uF/16V,X7R

0.047uF/16V,X7R

C0402

C0402

+VDDIO_CLK

C403

C403

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

+VDDIO_CLK

4

+V3.3S_CK_VDD

C397

C397

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

C404

C404

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

3

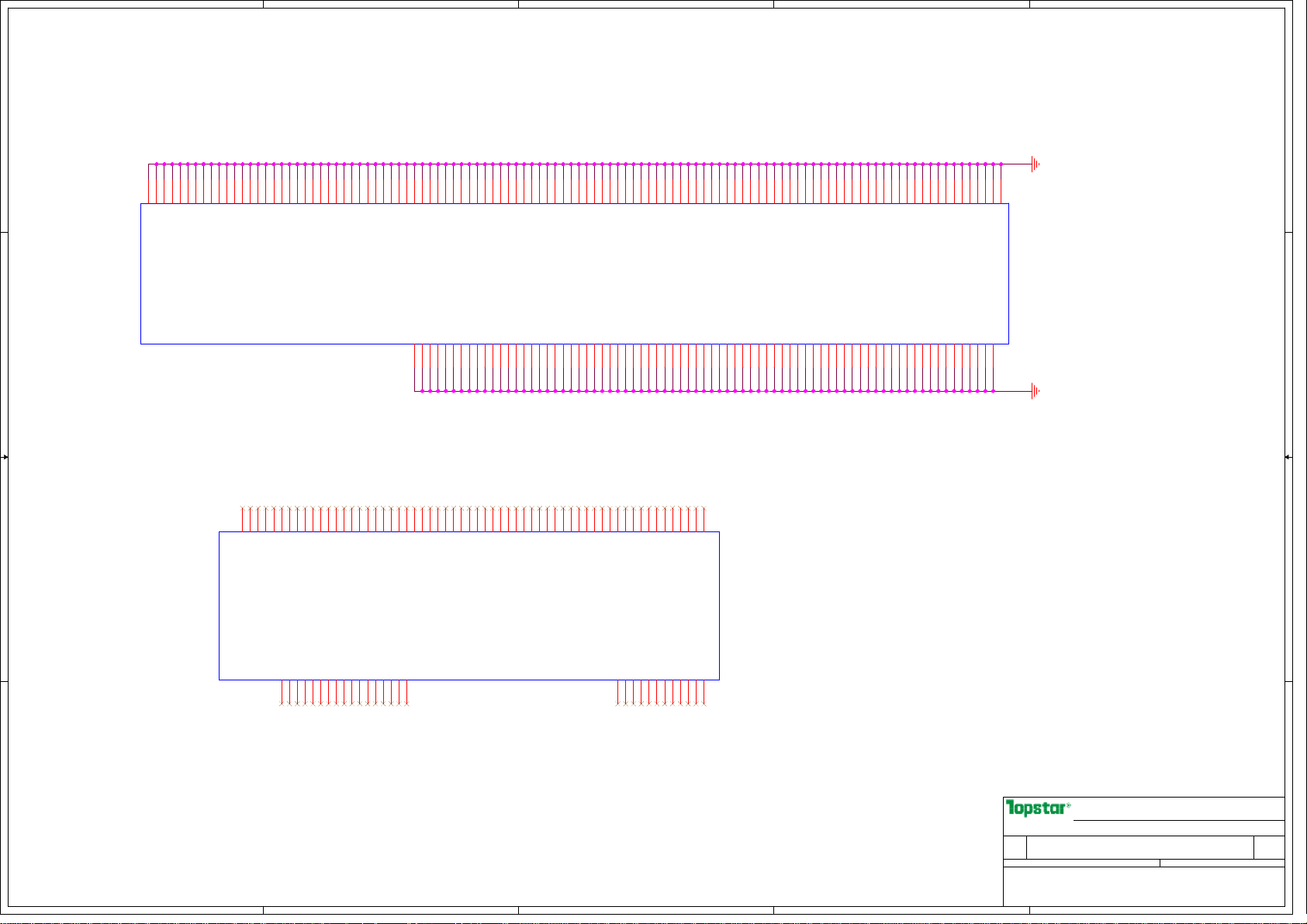

U36

U36

CY28548

CY28548

TSSOP64_0D5_6D1

TSSOP64_0D5_6D1

2

+V3.3S_CK_VDD

+VDDIO_CLK

+VDDIO_CLK

+VDDIO_CLK

+VDDIO_CLK

TME

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

R631 22 R0402R631 22 R0402

R632 22 R0402R632 22 R0402

R635 22 R0402R635 22 R0402

R640 10K R0402R640 10K R0402

Set to SRC8

R636 33 R0402R636 33 R0402

R637 2.2K R0402R637 2.2K R0402

R639 10K R0402R639 10K R0402

R638 33 R0402R638 33 R0402

27M_SEL

PCIF_ITP_EN

CLK_XTAL_IN

CLK_XTAL_OUT

No more than 500 mil

PCI_CLK_EC29

PCI_CLK_DEBUG23

PCI_CLK_ICH18

CLK_USB4819

CLK_ICH1419

VDD_PCI

9

VDD_48

16

VDD_PLL3

61

VDD_REF

39

VDD_SRC

55

VDD_CPU

12

VDD_IO

20

VDD_PLL3_IO

26

VDD_SRC_IO_1

36

VDD_SRC_IO_2

45

VDD_SRC_IO_3

49

VDD_CPU_IO

1

PCI0/OE#_0/2_A

3

PCI1/OE#_1/4_A

4

PCI2/TME

5

PCI3/FSD

6

PCI4/SRC5_SEL

7

PCIF5/ITP_EN

60

XTAL_IN

59

XTAL_OUT

10

USB_48/FSA

57

FSB/TEST_MODE

62

REF0/FSC/TEST_SEL

8

VSS_PCI

11

VSS_48

15

VSS_IO

19

VSS_PLL3

52

VSS_CPU

23

VSS_SRC_1

29

VSS_SRC_2

58

VSS_REF

42

VSS_SRC3

IO_VOUT

SMB_DATA

SMB_CLK

SRC5/PCI_STOP#

SRC5#/CPU_STOP#

CPU0

CPU0#

CPU1

CPU1#

SRC8/CPU2_ITP

SRC8#/CPU2#_ITP

SRC10

SRC10#

SRC11/OE#_10

SRC11#/OE#_9

SRC9

SRC9#

SRC7/OE#_8

SRC7#/OE#_6

SRC6

SRC6#

SRC4

SRC4#

SRC3/OE#_0/2_B

SRC3#/OE#_1/4_B

SRC2/SATA

SRC2#/SATA#

SRC1/SE1

SRC1#/SE2

SRC0/DOT96

SRC0#/DOT96#

CK_PWRGD/PWRDWN#

48

63

64

38

37

54

53

51

50

47

46

34

35

33

32

30

31

44

43

41

40

27

28

24

25

21

22

17

18

13

14

56

2

+V3.3S 7,10,11,12,14,15,16,17,18,19,20,21,23,24,25,26,27,28,29,30,35,36,37,39

+V1.05S 7,8,9,11,12,17,20,28,35,36,37

SMBUS ADD:1101 001X

R345 0 R0402R345 0 R0402

R347 0 R0402R347 0 R0402

CPU0

RN7 33

RN7 33

CPU#0

CPU1

CPU#1

MPCIE_CLKREQ

MCH_CLKREQ

1 2

3 4

RN8 33

RN8 33

1 2

3 4

RN18 33

RN18 33

1 2

3 4

RN10 33

RN10 33

3 4

1 2

R643 475,1% R0402 nsR643 475,1% R0402 ns

R634 475,1% R0402 nsR634 475,1% R0402 ns

3 4

1 2

RN11

RN11

33

33

RA0402_4

RA0402_4

1 2

3 4

RN17 33

RN17 33

3 4

1 2

RN12 33

RN12 33

3 4

1 2

RN13 33

RN13 33

3 4

1 2

RN14 33

RN14 33

3 4

1 2

R734 0 R0402R734 0 R0402

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RN16

RN16

33

33

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

RA0402_4

SMB_DATA_S 14,19,23,24

SMB_CLK_S 14,19,23,24

PM_STP_PCI# 19

PM_STP_CPU# 19

CLK_CPU_BCLK 7

CLK_CPU_BCLK# 7

CLK_MCH_BCLK 9

CLK_MCH_BCLK# 9

CLK_PCIE_EXPCARD2 24

CLK_PCIE_EXPCARD2# 24

CLK_PCIE_EXPCARD 23

CLK_PCIE_EXPCARD# 23

PCIE_CLKREQ# 23,24

MCH_CLKREQ# 10

CLK_MCH_3GPLL 10

CLK_MCH_3GPLL# 10

DREFSSCLK 10

DREFSSCLK# 10

CLK_PCIE_ICH 18

CLK_PCIE_ICH# 18

CLK_PCIE_LAN 30

CLK_PCIE_LAN# 30

CLK_ICH_SATA 17

CLK_ICH_SATA# 17

DREFCLK 10

DREFCLK# 10

VR_PWRGD_CLK_EN 19

1

C407

C407

27pF/50V,NPO

27pF/50V,NPO

C0402

B B

C0402

C408

C408

27pF/50V,NPO

27pF/50V,NPO

C0402

C0402

BUS FREQUENCE SELECT

+V1.05S

C409

R650

R650

R641

R641

56

56

R0402

R0402

CPU_BSEL07

CPU_BSEL17

CPU_BSEL27

A A

R642 0 R0402 nsR642 0 R0402 ns

R651 0 R0402 nsR651 0 R0402 ns

R652 0 R0402 nsR652 0 R0402 ns

R645

R645

1K

1K

R0402

R0402

ns

ns

1K

1K

R0402

R0402

ns

ns

R653

R653

0

0

R0402

R0402

R649

R649

1K

1K

R0402

R0402

ns

ns

R655

R655

0

0

R0402

R0402

C409

0.1UF/25V,Y5V

0.1UF/25V,Y5V

C0402

C0402

CLK_BSEL0

CLK_BSEL1

CLK_BSEL2

R670 1K R0402R670 1K R0402

R671 1K R0402R671 1K R0402

R672 1K R0402R672 1K R0402

MCH_BSEL0 10

MCH_BSEL1 10

MCH_BSEL2 10

FSC FSB FSA HOST Clock

BSEL2 BSEL1 BSEL0 frequency

0 0 1 133MHz

1 0 1 100MHz

5

4

CLK_XTAL_IN

12

Y5

Y5

14.318180MHz

14.318180MHz

XS2

XS2

CLK_XTAL_OUT

27M_SEL

3

+V3.3S

R647

R647

10K

10K

R0402

R0402

R654

R654

10K

10K

R0402

R0402

ns

ns

MCH_CLKREQ

MPCIE_CLKREQ

TME

R675 10K R0402R675 10K R0402

R646 10K R0402R646 10K R0402

R648 10K R0402R648 10K R0402

0:Normal mode

1:No Overclocking

+V3.3S

2

CLK_ICH14

CLK_USB48

PCI_CLK_DEBUG

PCI_CLK_EC

PCI_CLK_ICH

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

C410 10PF/50V,NPO ns

C410 10PF/50V,NPO ns

C0402

C0402

C411 10PF/50V,NPO ns

C411 10PF/50V,NPO ns

C0402

C0402

C412 10PF/50V,NPO ns

C412 10PF/50V,NPO ns

C0402

C0402

C413 10PF/50V,NPO ns

C413 10PF/50V,NPO ns

C0402

C0402

C414 10PF/50V,NPO ns

C414 10PF/50V,NPO ns

C0402

C0402

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

CK505M

CK505M

CK505M

A

A

A

642Wednesday, July 16, 2008

642Wednesday, July 16, 2008

642Wednesday, July 16, 2008

1

of

of

of

A

A

A

5

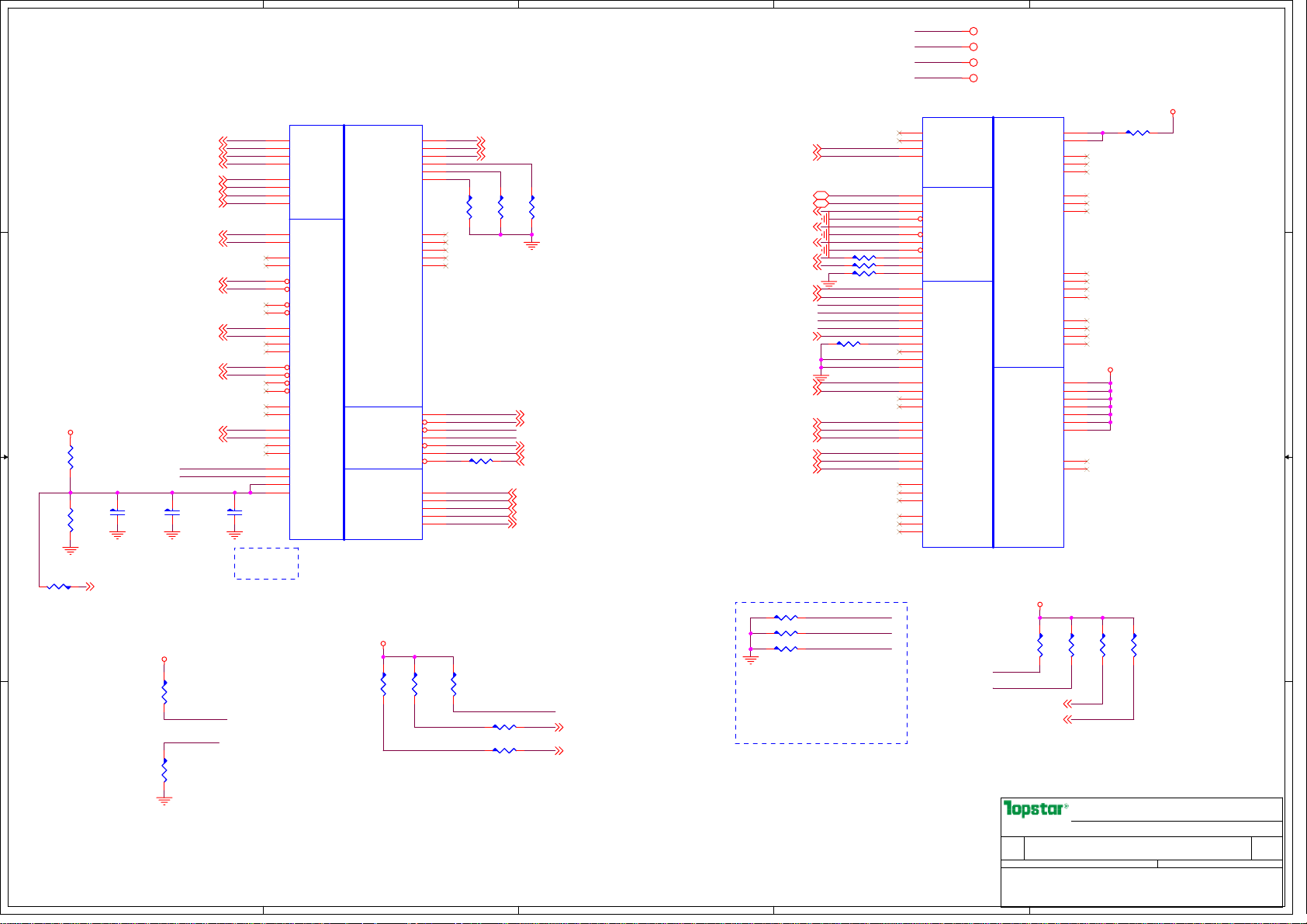

U22A

H_A#[31:3]9

D D

H_ADSTB#09

H_REQ#[4:0]9

H_A#[31:3]9

C C

H_ADSTB#19

H_A20M#17

H_FERR#17

H_IGNNE#17

H_STPCLK#17

H_INTR17

H_NMI17

H_SMI#17

+V1.05S

B B

A A

R79 1K,1% R0402R79 1K,1% R0402

R81 1K,1% R0402R81 1K,1% R0402

R84 1K,1% R0402R84 1K,1% R0402 C21

R150 56 R0402R150 56 R0402

R87 56 R0402R87 56 R0402

R86 56 R0402R86 56 R0402

R88 56 R0402R88 56 R0402

R90 1K,1% R0402 nsR90 1K,1% R0402 ns

R92 1K,1% R0402 nsR92 1K,1% R0402 ns

R91 1K,1% R0402 nsR91 1K,1% R0402 ns

R93 1K,1% R0402 nsR93 1K,1% R0402 ns

R99 1K,1% R0402 nsR99 1K,1% R0402 ns

R96 1K,1% R0402 nsR96 1K,1% R0402 ns

R95 1K,1% R0402 nsR95 1K,1% R0402 ns

+V1.05S

R74

R74

1K,1%

1K,1%

R0402

R0402

R102

R102

1K

1K

R0402

R0402

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#9

H_A#10

H_A#11

H_A#13

H_A#14

H_A#15

H_A#16

T2 ICTPT2 ICTP

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

T14 ICTPT14 ICTP

ns

ns

+V1.05S

5

R75

R75

1K,1%

1K,1%

R0402

R0402

ns

ns

1

P21

H20

N20

R20

J19

N19

G20

M19

H21

L20

M20

K19

J20

L21

K20

D17

N21

J21

G19

P20

R19

C19

F19

E21

A16

D19

C14

C18

C20

E20

D20

B18

C15

B16

B17

C16

A17

B14

B15

A14

B19

M18

U18

T16

R16

T15

R15

U17

G6

M15

L16

H_A#33

H_A#34

H_A#35

H_TDO

H_BPM#5

H_TMS

H_TDI

H_NMI

H_SMI#

H_INTR

H_STPCLK#

H_DPSLP#

H_DPRSTP#

H_PWRGD

+V3.3S

R98

R98

330

330

R0402

R0402

Q1

Q1

MMBT3904-F

MMBT3904-F

SOT23

SOT23

2 3

U22A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

AP0

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

ADDR GROUP 1

ADDR GROUP 1

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

AP1

A20M#

FERR#

J4

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

D6

NC1

NC2

H6

NC3

K4

NC4

K5

NC5

NC6

NC7

Diamondville

Diamondville

For defensive design

reservation only in this

initial release

+V1.05S

ADS#

BNR#

BPRI#

ADDR

GROUP

0

ADDR

GROUP

0

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

BR1#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

PROCHOT#

THRMDA

THRMDC

THERM

THERM

THERMTRIP#

BCLK[0]

BCLK[1]

H CLK

H CLK

RSVD3

RSVD2

NC

NC

RSVD1

R80 56 R0402R80 56 R0402

R83 56 R0402R83 56 R0402

23

R103

R103

56

56

R0402

R0402

V19

Y19

U21

T21

T19

Y18

T20

F16

V16

W20

D15

W18

Y17

U20

W19

AA17

HIT#

V20

K17

J18

H15

J15

K18

J16

M17

TCK

N16

TDI

M16

TDO

L17

TMS

K16

V15

G17

E4

E5

H17

V11

V12

C21

C1

A3

+V1.05S

Q4

Q4

MMBT3904-F

MMBT3904-F

SOT23

SOT23

1

VR_PROCHOT#

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#3

H_BPM#4

H_BPM#5

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST#

H_DBR#

H_THERMDA

H_THERMDC

H_TCK

H_TRST#

R94

R94

1K,1%

1K,1%

R0402

R0402

ns

ns

H_DPWR#

R97

R97

1K,1%

1K,1%

R0402

R0402

ns

ns

R147

R147

1K

1K

R0402

R0402

4

ICTPT1ICTP

T1

H_ADS# 9

H_BNR# 9

H_BPRI# 9

H_DEFER# 9

H_DRDY# 9

H_DBSY# 9

H_BREQ#0 9

H_IERR#

R65 1K,1% R0402R65 1K,1% R0402

H_LOCK# 9

T3 ICTPT3 ICTP

H_CPURST# 9

H_RS#0 9

H_RS#1 9

H_RS#2 9

H_TRDY# 9

H_HIT# 9

H_HITM# 9

T7

T6

T8

T9

T10

T10

T11

T11

R674 0 R0402 nsR674 0 R0402 ns

R104 22 R0402R104 22 R0402

PM_THRMTRIP# 10,17,28

CLK_CPU_BCLK 6

CLK_CPU_BCLK# 6

EC_PROCHOT# 29

+V1.05S

4

ICTPT7ICTP

ICTPT6ICTP

ICTPT8ICTP

ICTPT9ICTP

ICTP

ICTP

ICTP

ICTP

VR_PROCHOT#

+V1.05S

+V3.3S

+V1.05S

R64

R64

R63

R63

330

330

56

56

R0402

R0402

R0402

R0402

Place testpoint on

H_IERR# with a GND

0.1" away

PM_SYSRST# 19

H_THERMDA

H_THERMDC

H_INIT# 17

+V1.05S

+V1.05S

C22

C22

2200pF/25V,X7R

2200pF/25V,X7R

C0402

C0402

+V1.05S 6,8,9,11,12,17,20,28,35,36,37

+V3.3S 6,10,11,12,14,15,16,17,18,19,20,21,23,24,25,26,27,28,29,30,35,36,37,39

R66

R66

1K,1%

1K,1%

R0402

R0402

R71

R71

2K,1%

2K,1%

R0402

R0402

Layout Note: Z=55ohm,

0.5" max for GTLREF

R76

R76

1K,1%

1K,1%

R0402

R0402

R78

R78

2K,1%

2K,1%

R0402

R0402

NOTE

1.H_THERMDA/C 10 MILS, ,

然后再包地处理

2.H_THERMDA/C 19V VGA

线宽 并配对走线

.

走线远离 及 或高速线走线

3

Layout Note: Z=55ohm,

0.5" max for GTLREF

C19

C19

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

EXTBGREF

C20

C20

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402R82 1K,1% R0402R82 1K,1% R0402

2

DXP

3

DXN

G781

G781

ADM1032AR

ADM1032AR

LM86CIM

LM86CIM

MAX6657MSA

MAX6657MSA

SOIC-8

SOIC-8

U4

U4

F75383S

F75383S

SO8_50_150

SO8_50_150

3

H_D#[63:0]9

H_DSTBN#09

H_DSTBP#09

H_DINV#09

H_D#[63:0]9

H_DSTBN#19

H_DSTBP#19

H_DINV#19

R67 1K,1% R0402 nsR67 1K,1% R0402 ns

CPU_BSEL06

CPU_BSEL16

CPU_BSEL26

1

SMBCLK

VCC

SMBDATA

ALERT#

THERM#

GND

5

8

7

6

4

U22B

Y11

W10

Y12

AA14

AA11

W12

AA16

Y10

Y13

W15

AA13

Y16

W13

AA9

W9

Y14

Y15

W16

AA5

W3

W7

W6

AA6

W2

AA8

W4

T17

M6

N15

P17

G5

+V3.3S

U22B

Y9

V9

Y8

U1

Y7

Y3

V3

U2

T3

V2

Y4

Y5

Y6

R4

A7

U5

V5

R6

N6

T6

J6

H5

Diamondville

Diamondville

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

DP#0

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

DP#1

GTLREF

ACLKPH

DCLKPH

BINIT#

EDM

EXTBGREF

FORCEPR#

HFPLL

MCERR#

RSP#

BSEL[0]

BSEL[1]

BSEL[2]

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

MISC

MISC

PWRGOOD

CORE_DET

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6H_A#8

H_D#7

H_D#8

H_D#9

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

T4 ICTPT4 ICTP

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

T12 ICTPT12 ICTP

ACLKPH

DCLKPH

T15 ICTPT15 ICTP

T16 ICTPT16 ICTP

EXTBGREF

T17 ICTPT17 ICTP

T18 ICTPT18 ICTP

T20 ICTPT20 ICTP

T19 ICTPT19 ICTP

R89

R89

220

220

R0402

R0402

C23

C23

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

EC SMBUS ADD:1001 100X

THERM#

C24

R100

R100

10K

10K

R0402

R0402

+V3.3S

R101

R101

10K

10K

R0402

R0402

C24

27pF/50V,NPO

27pF/50V,NPO

C0402

C0402

2

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

DATA GRP 2

DATA GRP 2

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DP#2

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

DATA GRP 3

DATA GRP 3

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

DP#3

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

CMREF[1]

2

H_D#32

R3

H_D#33

R2

H_D#34

P1

H_D#35

N1

H_D#36

M2

H_D#37

P2

H_D#38

J3

H_D#39

N3

H_D#40

G3

H_D#41

H2

H_D#42H_A#12 H_D#10

N2

H_D#43

L2

H_D#44

M3

H_D#45

J2

H_D#46

H1

H_D#47

J1

K2

K3

L1

M4

H_D#48

C2

H_D#49

G2

H_D#50

F1

H_D#51

D3

H_D#52

B4

H_D#53

E1

H_D#54

A5

H_D#55

C3

H_D#56

A6

H_D#57

F2

H_D#58

C6

H_D#59

B6

H_D#60

B3

H_D#61

C4

H_D#62

C7

H_D#63

D2

E2

F3

C5

D4

COMP0

T1

COMP1

T2

COMP2

F20

COMP3

F21

R18

R17

U4

V17

N18

A13

CPU_CMREF

B7

C25

C25

27pF/50V,NPO

27pF/50V,NPO

C0402

C0402

1

H_D#[63:0] 9

H_DSTBN#/H_DSTBP# should route

as differential pair

H_DSTBN#2 9

H_DSTBP#2 9

ICTPT5ICTP

+V1.05S

H_DINV#2 9

T5

H_D#[63:0] 9

H_DSTBN#3 9

H_DSTBP#3 9

H_DINV#3 9

T13ICTPT13ICTP

R68 27.4,1% R0402R68 27.4,1% R0402

R70 54.9,1% R0402R70 54.9,1% R0402

R72 27.4,1% R0402R72 27.4,1% R0402R69 1K,1% R0402 nsR69 1K,1% R0402 ns

R73 54.9,1% R0402R73 54.9,1% R0402

H_DPRSTP# 17

H_DPSLP# 17

H_DPWR# 9

H_PWRGD 17

H_CPUSLP# 9,17

T21ICTPT21ICTP

Layout Note: Zo=55ohm,

R77

R77

0.5" max for GTLREF

1K,1%

1K,1%

R0402

R0402

C21

R85

R85

0.1uF/10V,X5R

0.1uF/10V,X5R

2K,1%

2K,1%

R0402

R0402

C0402

C0402

I2C_CLK 29

I2C_DATA 29

OVT_SHUTDOWN# 28

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

Layout note:

Comp0,2 connec with Zo=27.4ohm,make

trace length shorter than 0.5"

Comp1,3 connec with Zo=55ohm,make

trace length shorter than 0.5"

CPU_CMREFH_A#32

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

Diamondville(1of2)(Host BUS)

Diamondville(1of2)(Host BUS)

Diamondville(1of2)(Host BUS)

A

A

A

1

A

A

742Wednesday, July 16, 2008

742Wednesday, July 16, 2008

742Wednesday, July 16, 2008

A

of

of

of

5

4

3

2

1

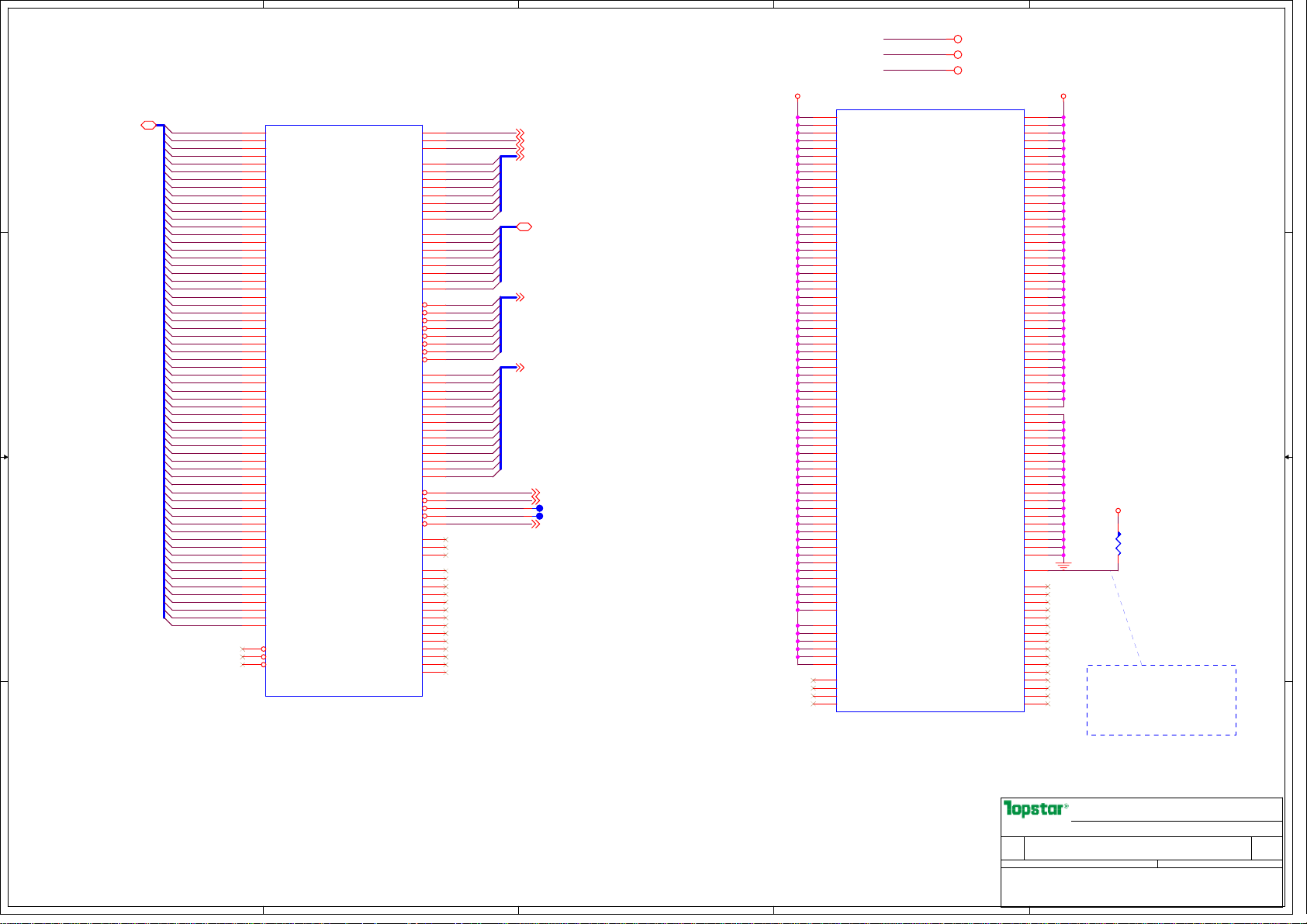

U22D

U22D

A2

VSS1

A4

VSS2

A8

VSS4

A15

VSS5

A18

VSS6

A19

VSS7

A20

VSS8

B1

VSS9

B2

VSS10

B5

VSS11

D D

C C

B B

B13

B20

B21

C17

D14

D18

D21

E15

E16

E19

G13

G21

H13

H16

H18

H19

K13

K15

K21

M13

M21

B8

C8

D1

D5

D8

E3

E6

E7

E8

F4

F5

F6

F7

F17

F18

G1

G4

G7

G9

H3

H4

H7

H9

J5

J7

J9

J13

J17

K1

K6

K7

K9

L3

L4

L5

L6

L7

L9

L13

L15

L18

L19

M1

M5

M7

M9

N4

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS41

VSS42

VSS45

VSS46

VSS48

VSS49

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

Diamondville

Diamondville

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

N5

N7

N9

N13

N17

P3

P4

P5

P6

P7

P9

P13

P15

P16

P18

P19

R1

R5

R7

R9

R13

R21

T4

T5

T7

T9

T10

T11

T12

T13

T18

U3

U6

U7

U15

U16

U19

V1

V4

V6

V7

V8

V13

V14

V18

V21

W1

W5

W8

W11

W14

W17

W21

Y1

Y2

Y20

Y21

AA2

AA3

AA4

AA7

AA10

AA12

AA15

AA18

AA19

AA20

+V1.05S

+VCC_CORE

V10

A10

A11

A12

B10

B11

B12

C10

C11

C12

D10

D11

D12

E10

E11

E12

F10

F11

F12

G10

G11

G12

H10

H11

H12

K10

K11

K12

L10

L11

L12

M10

M11

M12

N10

N11

N12

P10

P11

P12

R10

R11

R12

A9

B9

J10

J11

J12

U22C

U22C

VCCF

VCCQ1

VCCQ2

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VCCP27

VCCP28

VCCP29

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

VCCP35

VCCP36

VCCP37

VCCP38

VCCP39

VCCP40

VCCP41

VCCP42

VCCP43

VCCP44

VCCP45

Diamondville

Diamondville

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VCCPC64

VCCPC63

VCCPC62

VCCPC61

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

+V1.05S

C9

D9

E9

F8

F9

G8

G14

H8

H14

J8

J14

K8

K14

L8

L14

M8

M14

N8

N14

P8

P14

R8

R14

T8

T14

U8

U9

U10

U11

U12

U13

U14

F14

F13

E14

E13

D7

F15

D16

E18

G15

G16

E17

G18

C26

C26

0.1uF/10V,X7R

0.1uF/10V,X7R

C0402

C0402

C35

C35

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

Place near PIN D7

C13

D13

Layout Note: VCCSENSE

and VSSSENSE lines

should be of equal

length

Route VCCSENSE and VSSSENSE

traces at 27.4 Ohms with 50

mil spacing

+V1.5S

+VCC_CORE

C27

C27

0.1uF/10V,X7R

0.1uF/10V,X7R

C0402

C0402

C36

C36

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

ns

ns

R106

R106

100,1%

100,1%

R0402

R0402

R107

R107

100,1%

100,1%

R0402

R0402

C28

C28

0.1uF/10V,X7R

0.1uF/10V,X7R

C0402

C0402

ns

ns

C29

C29

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C30

C30

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

ns

ns

C31

C31

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C32

C32

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

+VCC_CORE 36,39

+V1.5S 10,11,12,20,23,24,35,36,37

+V1.05S 6,7,9,11,12,17,20,28,35,36,37

C33

C33

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

ns

ns

12

1

1

C34

C34

+

+

220uF/2.5V,POSCAP

220uF/2.5V,POSCAP

CT7343_19

CT7343_19

ns

ns

+VCC_CORE

C39

C37

C37

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

A A

+VCC_CORE

C53

C53

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C38

C38

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C54

C54

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

5

C39

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C55

C55

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C40

C40

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C56

C56

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C41

C41

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C57

C57

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C42

C42

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C58

C58

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

4

C43

C43

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C59

C59

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C44

C44

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C60

C60

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C45

C45

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C61

C61

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C46

C46

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C62

C62

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C47

C47

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C63

C63

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

3

C48

C48

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C64

C64

10uF/6.3V,X5R

10uF/6.3V,X5R

C0805

C0805

C49

C49

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C50

C50

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C51

C51

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

C52

C52

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

2

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

Diamondville (PWR&GND)(2of2)

Diamondville (PWR&GND)(2of2)

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

Diamondville (PWR&GND)(2of2)

N01

N01

N01

842Wednesday, July 16, 2008

842Wednesday, July 16, 2008

842Wednesday, July 16, 2008

1

of

of

of

A

A

A

5

4

3

2

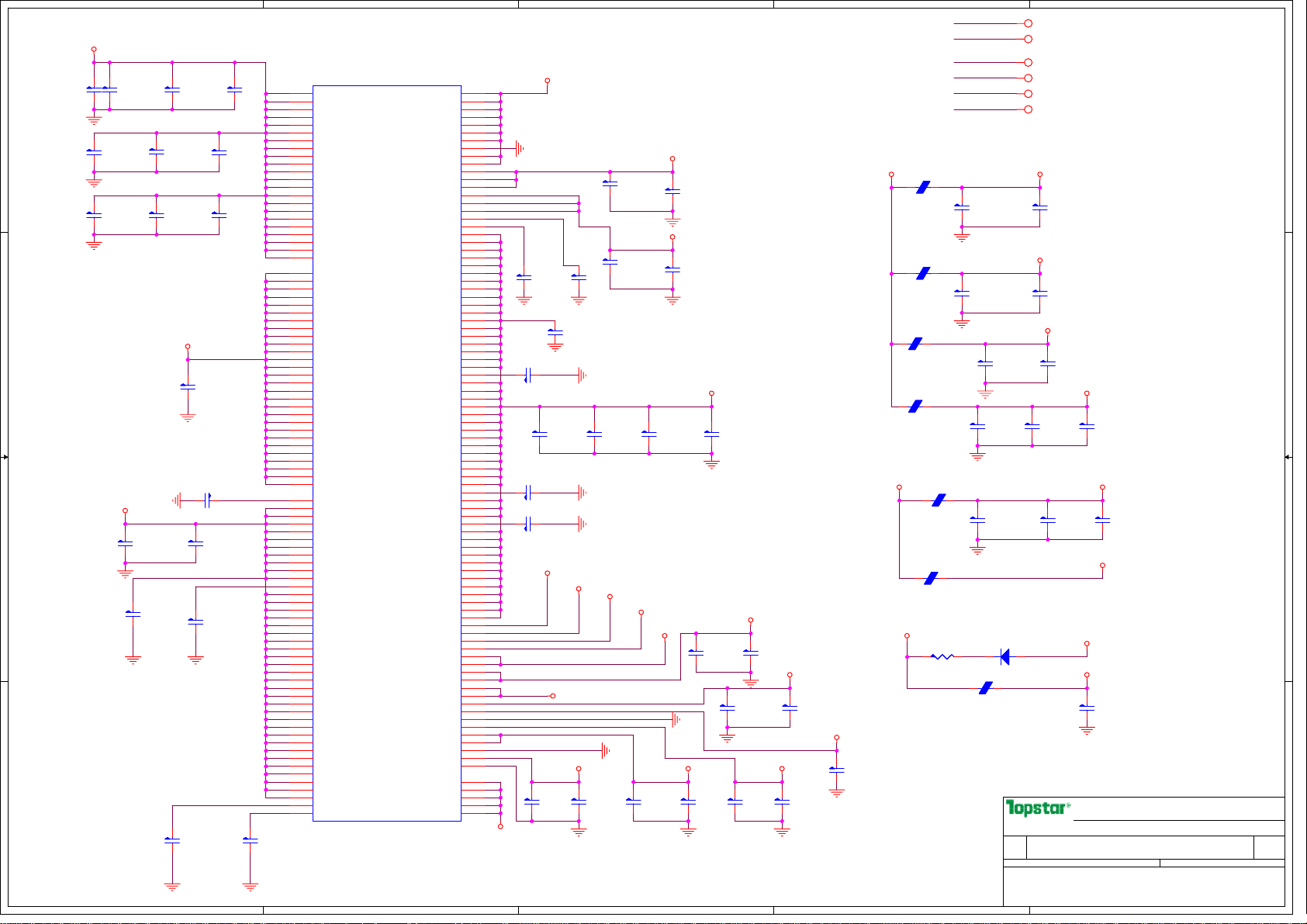

+V1.05S

+V1.05S 6,7,8,11,12,17,20,28,35,36,37

1

R109

R109

100,1%

100,1%

R0402

R0402

R111

R111

100,1%

100,1%

R0402

R0402

R114

R114

54.9,1%

54.9,1%

R0402

R0402

R116

R116

24.9,1%

24.9,1%

R0402

R0402

+V1.05S

+V1.05S

+V1.05S

R108

R108

221,1%

221,1%

R0603

R0603

R110

R110

221,1%

221,1%

R0603

R0603

H_XSWING

C65

C65

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

H_YSWING

C66

C66

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

R115

R115

54.9,1%

54.9,1%

R0402

R0402

H_XSCOMP

H_YSCOMP

H_XRCOMP

H_YRCOMP

R117

R117

24.9,1%

24.9,1%

R0402

R0402

Trace should be 10mil

wide with 20mil

spacing!

Trace should be 10mil

wide with 20mil

spacing!

Trace should be 10mil

wide with 20mil

spacing!

U23A

AB4

AB8

AA9

AA8

AB1

AB7

AA2

AB5

A10

C15

W2

W1

W4

W7

W5

W8

C4

F6

H9

H6

F7

E3

C2

C3

K9

F5

J7

K7

H8

E5

K8

J8

J2

J3

N1

M5

K5

J5

H3

J4

N3

M4

M3

N8

N6

K3

N9

M1

V8

V9

R6

T8

R2

N5

N2

R5

U7

R8

T4

T7

R3

T5

V6

V3

V2

V5

A6

J1

K1

H1

U23A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

HADSTB0#

HADSTB1#

H_AVREF

HBREQ0#

HCPURST#

HDVREF

HOST

HOST

HDBSY#

HDEFER#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HHITM#

HLOCK#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HCPUSLP#

HTRDY#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HBNR#

HBPRI#

HCLKN

HCLKP

HHIT#

HRS0#

HRS1#

HRS2#

F8

D12

C13

A8

E13

E12

J12

B13

A13

G13

A12

D14

F14

J13

E17

H15

G15

G14

A15

B18

B15

E14

H13

C14

A17

E15

H17

D17

G17

F10

C12

H16

E2

B9

C7

G8

B10

E1

AA6

AA5

C10

C6

H5

J6

T9

U6

G7

E6

F3

M8

T1

AA3

F4

M7

T2

AB3

C8

B4

C5

G9

E9

G12

B8

F12

A5

B6

G10

E8

E10

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADS# 7

H_ADSTB#0 7

H_ADSTB#1 7

H_BNR# 7

H_BPRI# 7

H_BREQ#0 7

H_CPURST# 7

CLK_MCH_BCLK# 6

CLK_MCH_BCLK 6

H_DBSY# 7

H_DEFER# 7

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

H_DPWR# 7

H_DRDY# 7

H_DSTBN#0 7

H_DSTBN#1 7

H_DSTBN#2 7

H_DSTBN#3 7

H_DSTBP#0 7

H_DSTBP#1 7

H_DSTBP#2 7

H_DSTBP#3 7

H_HIT# 7

H_HITM# 7

H_LOCK# 7

H_RS#0 7

H_RS#1 7

H_RS#2 7

H_CPUSLP# 7,17

H_TRDY# 7

H_D#[63:0]7 H_A#[31:3] 7

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

C67

C67

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

Place close to PIN-E1/E2

H_REQ#[4:0] 7

C68

C68

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

ns

ns

+V1.05S

R112

R112

100,1%

100,1%

R0402

R0402

R113

R113

200,1%

200,1%

R0402

R0402

D D

C C

B B

945GMS

945GMS

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

the expressed written consent of TOPSTAR

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

Calistoga(HOST)

Calistoga(HOST)

Calistoga(HOST)

N01

N01

N01

1

A

A

942Wednesday, July 16, 2008

942Wednesday, July 16, 2008

942Wednesday, July 16, 2008

A

of

of

of

5

4

3

2

+V3.3S 6,7,11,12,14,15,16,17,18,19,20,21,23,24,25,26,27,28,29,30,35,36,37,39

+V1.5S_PCIE 12

+V1.8

+V1.5S 8,11,12,20,23,24,35,36,37

+V1.8 12,14,34,36,37

1

U23F

AA26

2

H27

Y26

H20

H22

A24

A23

E25

F25

C25

D25

F27

D27

H25

H30

G29

F28

E28

G28

H28

K30

K27

K29

D30

C30

A30

A29

G31

F32

D31

H31

G32

C31

F33

D33

F30

E33

D32

F29

J27

J29

J30

U23F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTRL

LBKLT_EN

LCTLA_CLK

LCTLB_CLK

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

EXP_COMPI

EXP_ICOMPO

SDV0_TVCLKIN#

SDVO_INT#

SDVO_FLDSTALL#

MISC

MISC

SDVO_TVCLKIN

SDVO_FLDSTALL

SDVO

SDVO

SDVOB_RED#

SDVOB_GREEN#

SDVOB_BLUE#

SDVOB_CLKN

SDVOB_RED

SDVOB_GREEN

SDVOB_BLUE

SDVOB_CLKP

TV_REFSET

TV

TV

LVDS VGA

LVDS VGA

TV_DCONSEL0

TV_DCONSEL1

945GMS

945GMS

LCTLA_CLK

LCTLB_DATA

L_DDC_CLK15

L_DDC_DATA15

Page Name

Page Name

Page Name

Size

Size

Size

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

R28

M28

N30

R30

T29

M30

P30

SDVO_INT

T30

P28

N32

P32

T32

N28

M32

P33

R32

+V1.5S

A21

TVDAC_A

C20

TVDAC_B

E20

TVDAC_C

G23

B21

TV_IRTNA

C21

TV_IRTNB

D21

TV_IRTNC

G26

J26

+V3.3S

R126

R126

R127

R127

10K

10K

10K

10K

R0402

R0402

R0402

R0402

Project Name Rev

Project Name Rev

Project Name Rev

U23B

Y29

Y32

Y28

Y31

V28

V31

V29

V32

AF33

AG1

AJ1

AM30

AG33

AF1

AK1

AN30

AN21

AN22

AF26

AF25

AG14

AF12

AK14

AH12

AJ21

AF11

AE12

AF14

AJ14

AJ12

AN12

AN14

AA33

AE1

U23B

DMI_RXN0

DMI_RXN1

DMI_RXP0

DMI_RXP1

DMI_TXN0

DMI_TXN1

DMI_TXP0

DMI_TXP1

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SMOCDCOMP0

SMOCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

945GMS

945GMS

CFG0

CFG1

CFG2

CFG3

CFG5

CFG6

DMI

DMI

MCH_RSVD1

MCH_RSVD2

MCH_RSVD7

MCH_RSVD8

MCH_RSVD9

CFG/RSVD

CFG/RSVD

DDR2 MUXING

DDR2 MUXING

ICHSYNC#

BM_BUSY#

EXT_TS0#

PM

PM

EXT_TS1#/DPRSLPVR

THRMTRIP#

PWROK

RSTIN#

DREF_CLKN

DREF_CLKP

CLK

CLK

DREF_SSCLKN

DREF_SSCLKP

CLKREQB

+V3.3S

R133

R133

R134

R134

10K

10K

10K

10K

R0402

R0402

R0402

R0402

ns

ns

R_PM_EXTTS#0

PM_EXTTS#1

4

C18

E18

G20

G18

J20

J18

K32

K31

C17

F18

A3

E31

G21

F26

H26

J15

AB29

W27

A27

A26

J33

H33

J22

MCH_BSEL0 6

MCH_BSEL1 6

MCH_BSEL2 6

GMS_CFG5

R130

R130

2.2K

2.2K

R0402

R0402

ns

ns

R_PM_EXTTS#0

PM_EXTTS#1

R141 100 R0402R141 100 R0402

R151

R151

10K

10K

R0402

R0402

MCH_CLKREQ#

R138 0 R0402R138 0 R0402

R139 0 R0402R139 0 R0402

R132

R132

R131

R131

2.2K

2.2K

2.2K

2.2K

R0402

R0402

R0402

R0402

ns

ns

MCH_ICH_SYNC# 18

PM_BMBUSY# 19

PM_THRMTRIP# 7,17,28

IMVP_PWRGD 19,29,39

BUF_PLT_RST# 18,19,23,24,29,30

DREFCLK# 6

DREFCLK 6

DREFSSCLK# 6

DREFSSCLK 6

MCH_CLKREQ# 6

PM_EXTTS#0 14

PM_DPRSLPVR 19

CLK_MCH_3GPLL#6

CLK_MCH_3GPLL6

CRT_DDC_CLK16

CRT_DDC_DATA16

CRT_BLUE16

CRT_GREEN16

CRT_RED16

CRT_VSYNC16

CRT_HSYNC16

LVDS_BKLTCTL15

LVDS_BKLTEN15,29

LVDS_VDDEN15

MCH_LVDS_CLKAN15

MCH_LVDS_CLKAP15

MCH_LVDS_YAN015

MCH_LVDS_YAN115

MCH_LVDS_YAN215

MCH_LVDS_YAP015

MCH_LVDS_YAP115

MCH_LVDS_YAP215

R118 150,1% R0402R118 150,1% R0402

R119 150,1% R0402R119 150,1% R0402

R124 150,1% R0402R124 150,1% R0402

150ohm GMCH

走线阻抗

150ohm VGA

走线阻抗

PLACE 150 OHM

R125 39 R0402R125 39 R0402

R120 39 R0402R120 39 R0402

R121 255,1%R0603R121 255,1%R0603

LCTLA_CLK

LCTLB_DATA

L_DDC_CLK

L_DDC_DATA

R122 1.5K,1% R0402R122 1.5K,1% R0402

CRT_BLUE

CRT_GREEN

CRT_RED

电阻到

37.5ohm

电阻到 口

50ohm

RESISTORS CLOSE TO

GMCH

3

D D

DMI_TXN018

DMI_TXN118

DMI_TXP018

DMI_TXP118

DMI_RXN018

DMI_RXN118

DMI_RXP018

DMI_RXP118

M_CLK_DDR014

M_CLK_DDR114

M_CLK_DDR#014

M_CLK_DDR#114

M_CKE014

+V1.8

M_CKE114

M_CS#014

M_CS#114

M_ODT014

M_ODT114

M_RCOMPN

M_RCOMPP

C70

C70

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

R136

R136

80.6,1%

80.6,1%

R0603

R0603

M_RCOMPN

M_RCOMPP

R137

R137

80.6,1%

80.6,1%

R0603

R0603

C71

C71

0.1uF/10V,X5R

0.1uF/10V,X5R

C0402

C0402

Close to GMCH

ONE PIN, ONE CAP

C C

+V1.8

12

R140

R140

10K,1%

10K,1%

12

B B

R733

R733

0

0

R0402

R0402

A A

R142

R142

10K,1%

10K,1%

SM_VREF_L 14,34

C69

C69

2.2uF/10V,X7R

2.2uF/10V,X7R

C0805

C0805

5

+V1.5S_PCIE

R123

R123

24.9,1%

24.9,1%

R0402

R0402

R128

R128

R129

R129

10K

10K

10K

10K

R0402

R0402

R0402

R0402

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Swain Xu

Swain Xu

Swain Xu

Calistoga(Graphic)

Calistoga(Graphic)

Calistoga(Graphic)

N01

N01

N01

1

A

A

10 42Wednesday, July 16, 2008

10 42Wednesday, July 16, 2008

10 42Wednesday, July 16, 2008

of

of

of

A

5

U23C

D D

C C

B B

MA_DATA[63:0]14

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

AC31

AB28

AE33

AF32

AC33

AB32

AB31

AE31

AH31

AK31

AL28

AK27

AH30

AL32

AJ28

AJ27

AH32

AF31

AH27

AF28

AJ32

AG31

AG28

AG27

AN27

AM26

AJ26

AJ25

AL27

AN26

AH25

AG26

AM12

AL11

AH9

AK9

AM11

AK11

AM8

AK8

AG9

AF9

AF8

AK6

AF7

AG11

AJ6

AH6

AN6

AM6

AK3

AL2

AM5

AL5

AJ3

AJ2

AG2

AF3

AE7

AF6

AH5

AG3

AG5

AF5

AG19

AG21

AG20

U23C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SB_CAS#

SB_RAS#

SB_WE#

945GMS

945GMS

4

AK12

SA_BS_0

AH11

SA_BS_1

AG17

SA_BS_2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

DDR2 SYSTEM MEMORY

DDR2 SYSTEM MEMORY

SA_RCVENINB

SA_RCVENOUTB

SA_WEB

SB_BS_0

SB_BS_1

SB_BS_2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

MA_DM0

AB30

MA_DM1

AL31

MA_DM2

AF30

MA_DM3

AK26

MA_DM4

AL9

MA_DM5

AG7

MA_DM6

AK5

MA_DM7

AH3

MA_DQS0

AC28

MA_DQS1

AJ30

MA_DQS2

AK33

MA_DQS3

AL25

MA_DQS4

AN9

MA_DQS5

AH8

MA_DQS6

AM2

MA_DQS7

AE3

MA_DQS#0

AC29

MA_DQS#1

AK30

MA_DQS#2

AJ33

MA_DQS#3

AM25

MA_DQS#4

AN8

MA_DQS#5

AJ8

MA_DQS#6

AM3

MA_DQS#7

AE2

MA_A_A0

AJ15

MA_A_A1

AM17

MA_A_A2

AM15

MA_A_A3

AH15

MA_A_A4

AK15

MA_A_A5

AN15

MA_A_A6

AJ18

MA_A_A7

AF19

MA_A_A8

AN17

MA_A_A9

AL17

MA_A_A10

AG16

MA_A_A11

AL18

MA_A_A12

AG18

MA_A_A13

AL14

AJ17

AK18

TP_MA_RCVENIN#

AN28

TP_MA_RCVENOUT#

AM28

AH17

AH21

AJ20

AE27

AN20

AL21

AK21

AK22

AL22

AH22

AG22

AF21

AM21

AE21

AL20

AE22

AE26

AE20

MA_A_BS#0 14

MA_A_BS#1 14

MA_A_BS#2 14

MA_DM[7:0] 14

MA_DQS[7:0] 14

MA_DQS#[7:0] 14

MA_A_A[13:0] 14

MA_A_CAS# 14

MA_A_RAS# 14

T23 ICTP nsT23 ICTP ns

T22

ICTP

ICTP

MA_A_WE# 14

3

+V1.05S +V1.5S

nsT22

ns

R25

P25

N25

M25

P24

N24

M24

Y22

W22

V22

U22

R22

P22

N22

M22

Y21

W21

V21

U21

R21

P21

N21

M21

Y20

W20

V20

U20

R20

P20

N20

M20

Y19

P19

N19

M19

Y18

P18

N18

M18

Y17

P17

N17

M17

Y16

P16

N16

M16

Y15

P15

N15

M15

Y14

W14

V14

U14

R14

P14

N14

M14

R10

P10

N10

M10

A18

AB10

AA10

T25

T22

T21

T20

T14

T10

L10

D1

945GMS

945GMS

U23H

U23H

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

MCH_RSVD3

MCH_RSVD4

MCH_RSVD5

MCH_RSVD6

2

NCTF

NCTF

1

+V1.05S 6,7,8,9,12,17,20,28,35,36,37

+V1.5S 8,10,12,20,23,24,35,36,37

+V3.3S 6,7,10,12,14,15,16,17,18,19,20,21,23,24,25,26,27,28,29,30,35,36,37,39

CFG19

AD25

AC25

AB25

AD24

AC24

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

K14

AD13

Y13

W13

V13

U13

T13

R13

P13

N13

M13

AD12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

AD11

AD10

K10

AN33

AA25

V25

U25

AA22

AA21

AA20

AA19

AA18

AA17

AA16

AA15

AA14

AA13

A4

A33

B2

AN1

C1

K28

K25

K26

R24

T24

K21

K19

K20

K24

K22

J17

K23

K17

K12

K13

K16

K15

+V3.3S

R143

R143

1K

1K

R0402

R0402

ns

GMS_CFG19

ns

LOW=Normal

High=LANES

REVERSED(945GMS no

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17