Page 1

THOMSON

y

y

Service Manual

42M61NF21

1. Caution··························································································2

2. Specifications of chassis·································································6

3. Alignment Procedure······································································11

4. IC Brief Instruction·········································································19

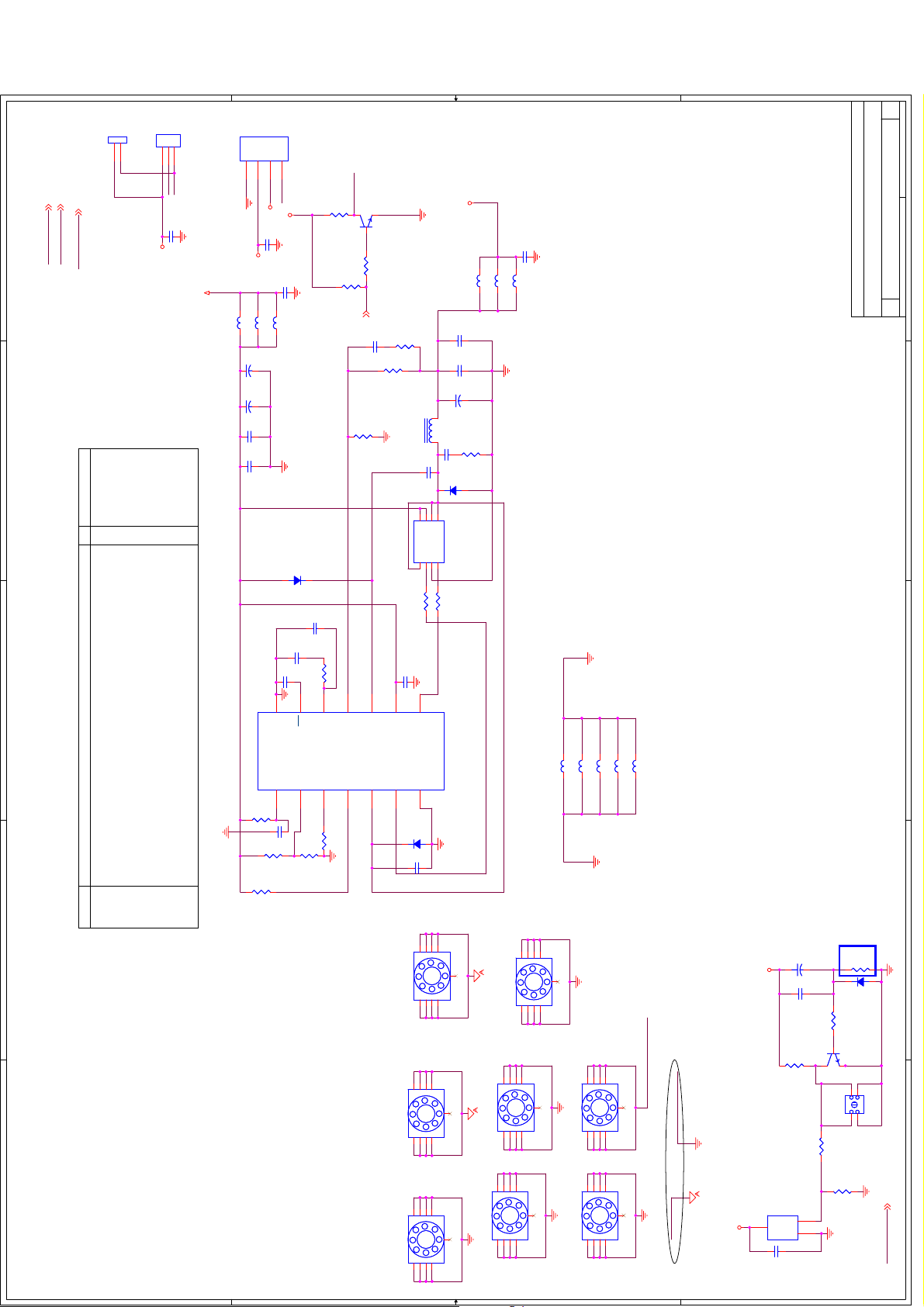

5. Schematic Diagram········································································66

6. Block Diagram···············································································80

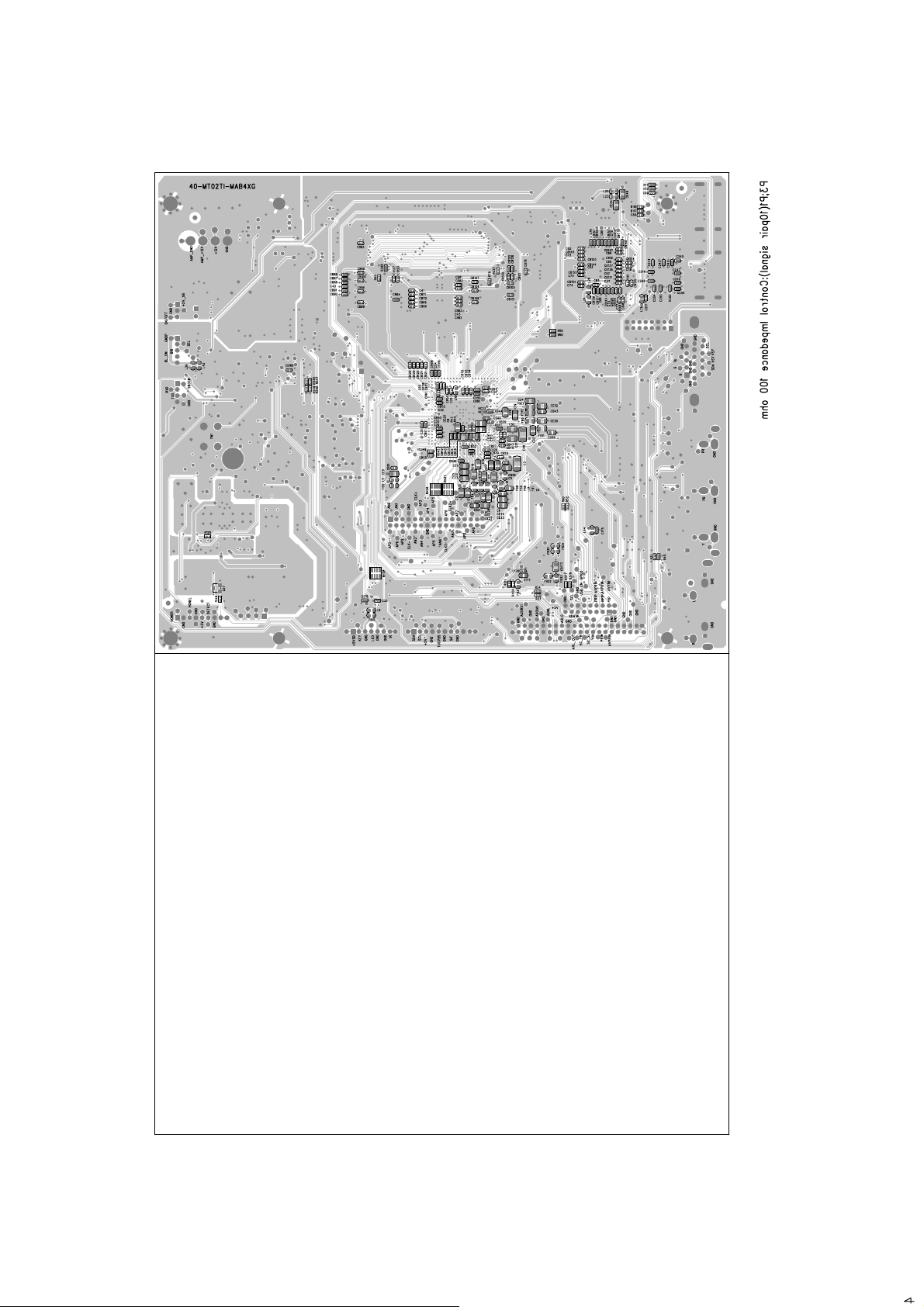

7. PCB Layout···················································································81

8. Explode View·················································································83

9. SpareParts····················································································89

This manual is the latest at the time of printing, and does not

include the modification which ma

the constant improvement of product.

be made after the printing, b

Page 2

CAUTION:

RISK OF ELECTRIC

SHOCK DO NOT OPEN.

1

Use of controls, adjustments or procedures other than those specified herein may result in

hazardous radiation exposure.

CAUTION: TO REDUCE THE RISK OF

CAUTION

The lighting flash with arrowhead symbol, with an equilateral triangle is intended to

alert the user to the presence of uninsulated voltage within the product s

enclosure that may be of sufficient magnitude to constitute a risk of electric shock to

the person.

The exclamation point within an equilateral triangle is intended to alert the user to the

presence of important operating and maintenance (servicing) instructions in the

literature accompanying the appliance.

ELECTRICAL SHOCK, DO NOT REMOVE

COVER (OR BACK). NO USER SERVICEABLE

PARTS INSIDE. REFER SER VICING TO

QUALIFIED SERVICE PERSONNEL.

dangerous

WARNING: TO REDUCE RISK OF FIRE OR ELECTRIC SHOCK, DO NOT

EXPOSE THIS APPLIANCE TO RAIN OR MOISTURE.

2

Page 3

IMPORTANT SAFETY INSTRUCTIONS

CAUTION:

Read all of these instructions. Save these instructions for later use . Follow all Warnings and

Instructions marked on the audio equipment.

1. Read Instructions-All the safety and operating instructions should be read before the product is operated.

2. Retain Instructions- The safety and operating instructions should be retained for future reference.

3. Heed Warnings- All warnings on the product and in the operating instructions should be adhered to.

4. Follow Instructions- All operating and use instructions should be followed.

FOR YOUR PERSONAL SAFETY

1. When the power cord or plug is damaged or frayed, unplug this television set from the wall outlet and refer servicing to

qualified service personnel.

2. Do not overload wall outlets and extension cords as this can result in fire or electric shock.

3. Do not allow anything to rest on or roll over the power cord, and do not place the TV where power cord is subject to

traffic or abuse. This may result in a shock or fire hazard.

4. Do not attempt to service this television set yourself as opening or removing covers may expose you to dangerous

voltage or other hazards. Refer all servicing to qualified service personnel.

5. Never push objects of any kind into this television set through cabinet slots as they may touch dangerous voltage

points or short out parts that could result in a fire or electric shock. Never spill liquid of any kind on the television set.

6. If the television set has been dropped or the cabinet has been damaged, unplug this television set from the wall outlet

and refer servicing to qualified service personnel.

7. If liquid has been spilled into the television set, unplug this television set from the wall outlet and refer servicing to

qualified service personnel.

8. Do not subject your television set to impact of any kind. Be particularly careful not to damage the picture tube surface.

9. Unplug this television set from the wall outlet before cleaning. Do not use liquid cleaners or aerosol cleaners. Use a

damp cloth for cleaning.

10.1. Do not place this television set on an unstable cart, stand, or table. The television set may fall, causing serious injury

to a child or an adult, and serious damage to the appliance. Use only with a cart or stand recommended by the

manufacturer, or sold with the television set. Wall or shelf mounting should follow the manufacturer s instructions, and

should use a mounting kit approved by the manufacturer.

10.2. An appliance and cart combination should be moved with care. Quick stops, excessive force, and uneven surfaces

may cause the appliance and cart combination to overturn.

3

Page 4

PROTECTION AND LOCATION OF YOUR SET

11. Do not use this television set near water ... for example, near a bathtub, washbowl, kitchen sink, or laundry tub, in a

wet basement, or near a swimming pool, etc.

Never expose the set to rain or water. If the set has been exposed to rain or water, unplug the set from the wall

outlet and refer servicing to qualified service personnel.

12. Choose a place where light (artificial or sunlight) does not shine directly on the screen.

13. Avoid dusty places, since piling up of dust inside TV chassis may cause failure of the set when high humidity persists.

14. The set has slots, or openings in the cabinet for ventilation purposes, to provide reliable operation of the receiver, to

protect it from overheating. These openings must not be blocked or covered.

Never cover the slots or openings with cloth or other material.

Never block the bottom ventilation slots of the set by placing it on a bed, sofa, rug, etc.

Never place the set near or over a radiator or heat register.

Never place the set in enclosure, unless proper ventilation is provided.

a built-in

PROTECTION AND LOCATION OF YOUR SET

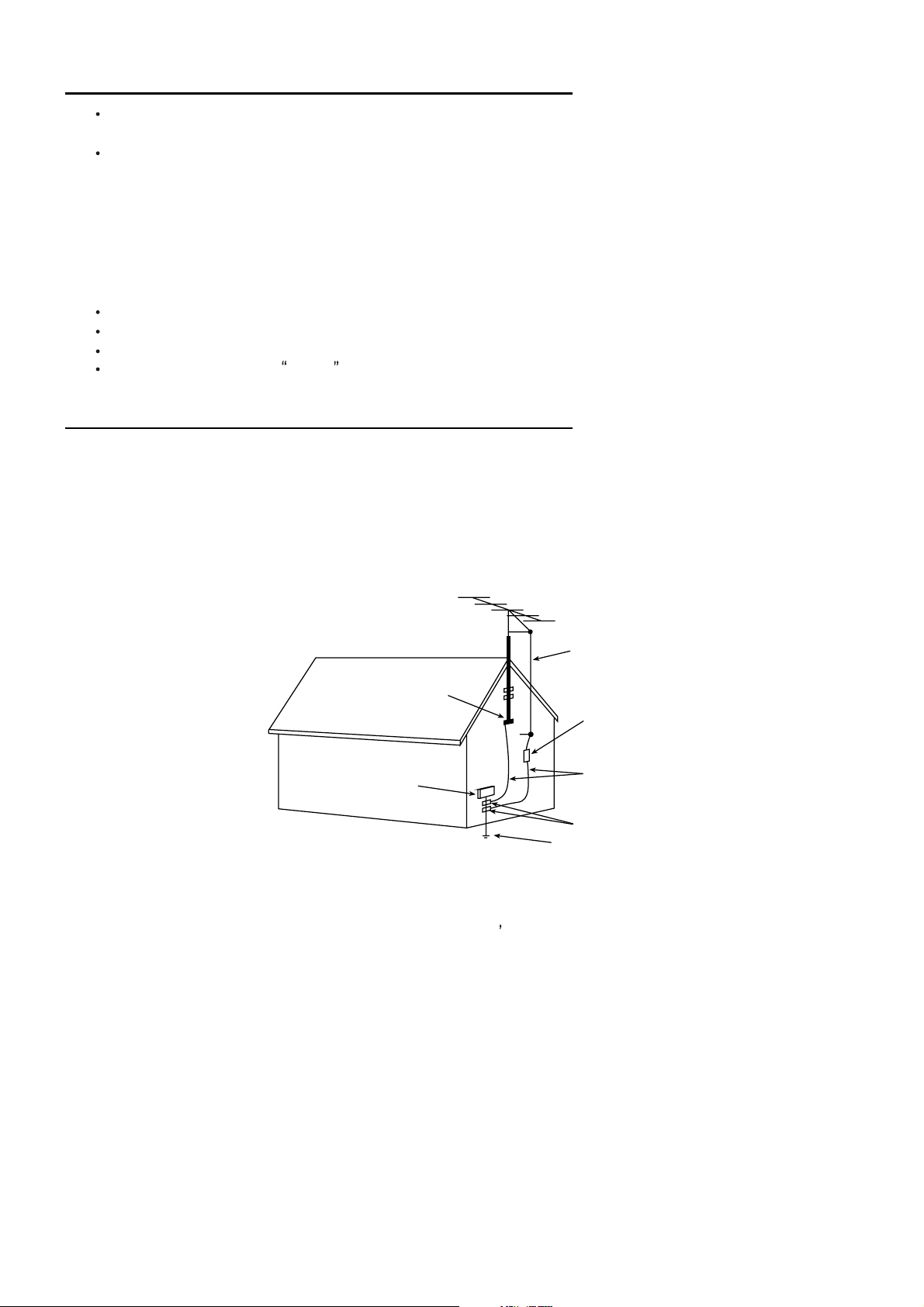

15.1. If an outside antenna is connected to the television set, be sure the antenna system is grounded so as to provide some

protection against voltage surges and built up static charges, Section 810 of the National Electrical Code, NFPA No.

70-1975, provides information with respect to proper grounding of the mast and supporting structure, grounding of the

lead-in wire to an antenna discharge unit, size of grounding conductors, location of antenna discharge unit, connection

to grounding electrode, and requirements for the grounding electrode.

EXAMPLE OF ANTENNA GROUNDING AS PER NATIONAL ELECTRICAL CODE INSTRUCTIONS

EXAMPLE OF ANTENNA GROUNDING AS PER

NATIONAL ELECTRICAL CODE

ANTENNA

LEAD- IN WIRE

GROUND CLAMP

ANTENNA DISCHARGE

UNIT (NEC SECTION

810-20)

GROUNDING

ELECTRIC SERVICE

EQUIPMENT

NEC-NATIONAL ELECTRICAL CODE

15.2. Note to CATV system installer : (Only for the television set with CATV reception)

This reminder is provided to call the CATV system attention to Article 820-40 of the NEC that provides

installer s

guidelines for proper grounding and, in particular, specifies that the cable ground shall be connected to the grounding

system of the building, as close to the point of cable entry as practical.

16. An outside antenna system should not be located in the vicinity of overhead power lines or other electric lights or power

circuits, or where it can fall into such power lines or circuits. When installing an outside antenna system, extreme care

should be taken to keep from touching such power lines or circuits as contact with them might be fatal.

CONDUCTORS

(NEC SECTION810-21)

GROUND CLAMPS

POWER SERVICE GROUNDING

ELECTRODE SYSTEM

(NEC ART 250. PART H)

17. For added protection for this television set during a lightning storm, or when it is left unattended and unused for long

periods of time, unplug it from the wall outlet and disconnect the antenna. This will prevent damage due to lightning

and power-line surges.

4

Page 5

OPERATION OF YOUR SET

18.

This television set should be operated only from the type of power source indicated on the marking label.If you are not

sure of the type of power supply at your home, consult your television dealer or local power company. For television

sets designed to operate from battery power, refer to the operating instructions.

19. If the television set does not operate normally by following the operating instructions, unplug this television set from the

wall outlet and refer servicing to qualified service personnel. Adjust only those controls that are covered in the operating

instructions as improper adjustment of other controls may result in damage and will often require extensive work by a

qualified technician to restore the television set to normal operation.

20. When going on a holiday : If your television set is to remain unused for a period of time, for instance, when you go on

a holiday, turn the television set and unplug the television set from the wall outlet.

off

IF THE SET DOES NOT OPERATE PROPERLY

21. If you are unable to restorenormal operation by followingthe detailed procedure in your operating instructions,

do not attempt any further adjustment. Unplug the set and call your dealer or service technician.

22. Whenever the television set is damaged or fails, or a distinct change in performance indicates a need for

service, unplug the set and have it checked by a professional service technician.

23. It is normal for some TV sets to make occasional snapping or popping sounds, particularly when being

turned on or off. If the snapping or popping is continuous or frequent, unplug the set and consult your

dealer or service technician.

FOR SERVICE AND MODIFICATION

24. Do not use attachments not recommended by the television set manufacturer as they may cause hazards.

25. When replacement parts are required, be sure the service technician has used replacement parts specified

by the manufacturer that have the same characteristics as the original part. Unauthorized substitutions

may result in fire, electric shock, or other hazards.

26. Upon completion of any service or repairs to the television set, ask the service technician to perform

routine safety checks to determine that the television is in safe operating condition.

5

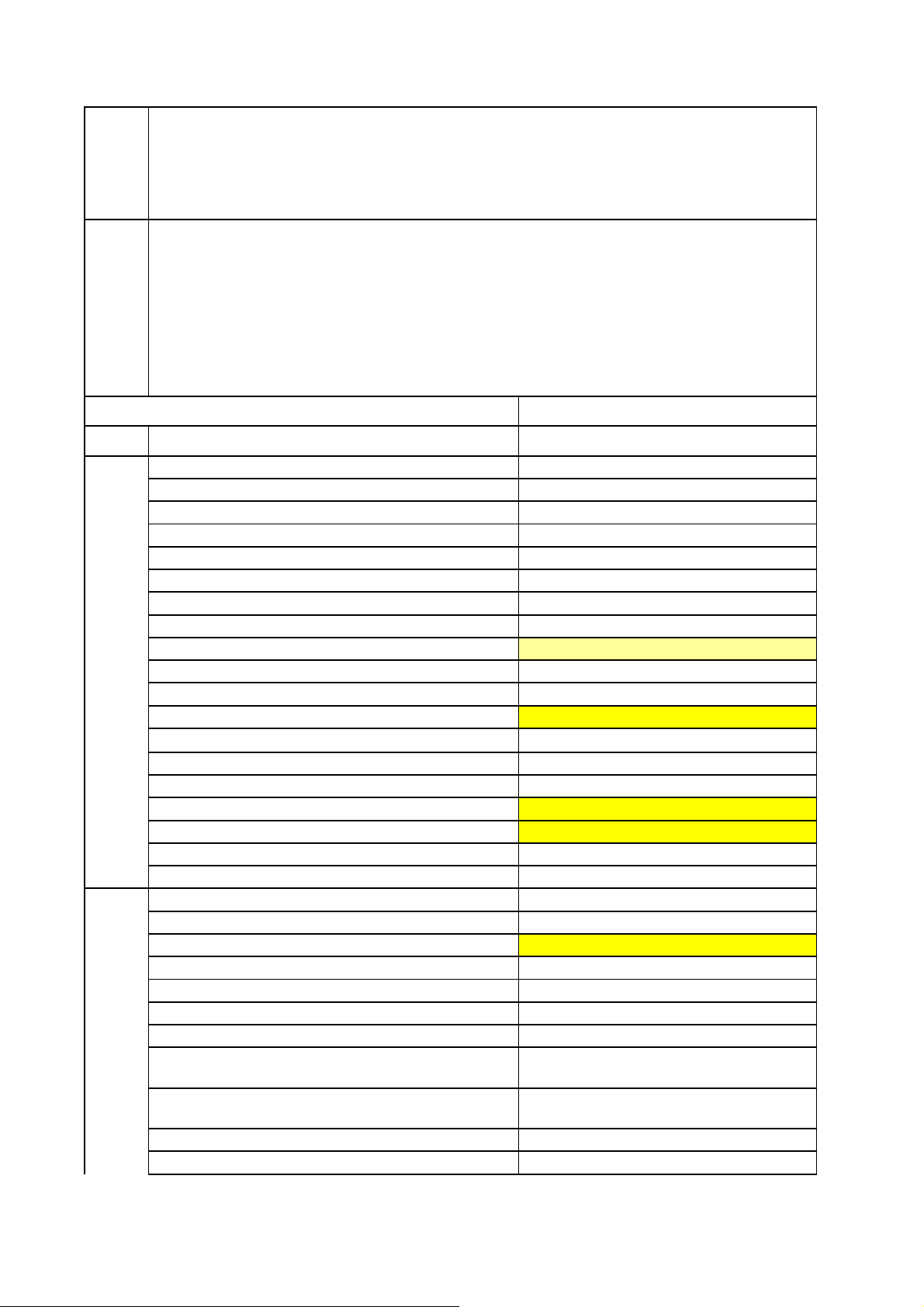

Page 6

Specification

Item description

ID

Brand THOMSON

Panel technology (LCD / PDP) LCD

Display mode TFT LCD

Display Type TFT LCD

Category (Monitor/TV/…) TV

Market Position (Scenium/Intuiva/Mid/Access,,,) ACCESS

FG Supplier (TTE/External supplier) TTE

FG assy location (ZY/AN/HZ/External supplier) ZY

Cabinet Design (Example: SC VII, V 6,,,) M61

PJO Nb M61

General

EAN Code 3244480283943

Tocom code

Product number

Predecessor (replace) Chassis name MT02+DE200

Homologation (Gostandard/CE/MPTT/…) CE

MP date request by PC (ETA)

MP date confirmed by supplier (ETD/ETA)

Screen size : diagonale (inch) 42

Aspect ratio (16/9 // 4/3 // 15/9) 16/9

Color depth (8/10/12 bits) 8

1st panel supplier : panel suppliers 50 Hz progressive scan

1st panel supplier : panel reference LPL

1st panel supplier : resolution

1st panel supplier : pixel Pitch (mmxmm) 1920x1080

1st panel supplier : Horizontal and vertical viewing

angle

1st panel supplier : Typical response time (Grey to

Grey)

1st panel supplier : Typical response time (tr+tf) 8

1st panel supplier : Typical white luminance (Nits) 18

2.Prodcut Specification

Model(型号):LCD42M61NF21

LC420WU1-SLB1

0.1615x0.4845

178/178

Page 7

1st panel supplier : Contrast VESA std 550

e

1st panel supplier : Typical panel Life Time (Hours) 800:1

2st panel supplier : panel suppliers 60,000

Pictur

2st panel supplier : panel reference

2st panel supplier : resolution

2st panel supplier : pixel Pitch (mmxmm)

2st panel supplier : Horizontal and vertical viewing

angle

2st panel supplier : Typical response time (Grey to

Grey)

2st panel supplier : Typical response time (tr+tf)

2st panel supplier : Typical white luminance

(Nits)(1st source/2nd source)

2st panel supplier : Contrast VESA std(1st

source/2nd source)

2st panel supplier : Typical panel Life Time

(Hours)(1st source/2nd source)

Noise Reduction (adaptative/…) Yes

Comb Filter (2D/3D) 3D

Deinterlacer (no/linerar/motion adaptive/motion

compensative)

Film mode / reverse 3:2 pull down yes / yes

Format control (Pin8/WSS) Yes/Yes

16/9 autoformat (black bars canceller) no

Zoom type : 4/3 format Yes

Zoom type : 14/9 Zoom no

Zoom type : 16/9 Zoom Yes

Zoom type : 16/9 Zoom up/down No/No

VideoSound

Zoom type : Cinerama Yes

Zoom type : 16/9Format Yes

Colour preset (Cool/Normal/Warm/Favourite) Cool/Normal/Warm

Contrast expend (low/medium/high) high

Picture Reset on factory menu

Backlight Adjust on factory menu

Picture Autoadjustment (PC mode) Yes

Picture presets : Standard / Film / Studio / Sport /

Personal / Game / Video Camera

Music Power (Watt) 2*15W

RMS Power (Watt) 2*8W

Graphic Equalizer Yes

Treble, Bass, Balance, Volume, Mute Control -/-/ Yes/Yes/Yes

Sound presets (My

sound/Music/Film/Voice/Flat/Standard/Panorama)

Sound techno (Stereo Nicam/Virtual Dolby

Surround/SRS Trusurround XT/BBE Viva/SRS WoW

/…)

Loudspeakers built in (T/M/B) -/2/DPS/DPS+ Standard BG/DK/I/LL`

linerar/motion adaptive/motion

compensative

Standard / Film / Studio / Sport / Personal

normal/personal/rock/pop/live/dance/techn

o/classic/soft

NICAM,German Stereo,Virtual surround

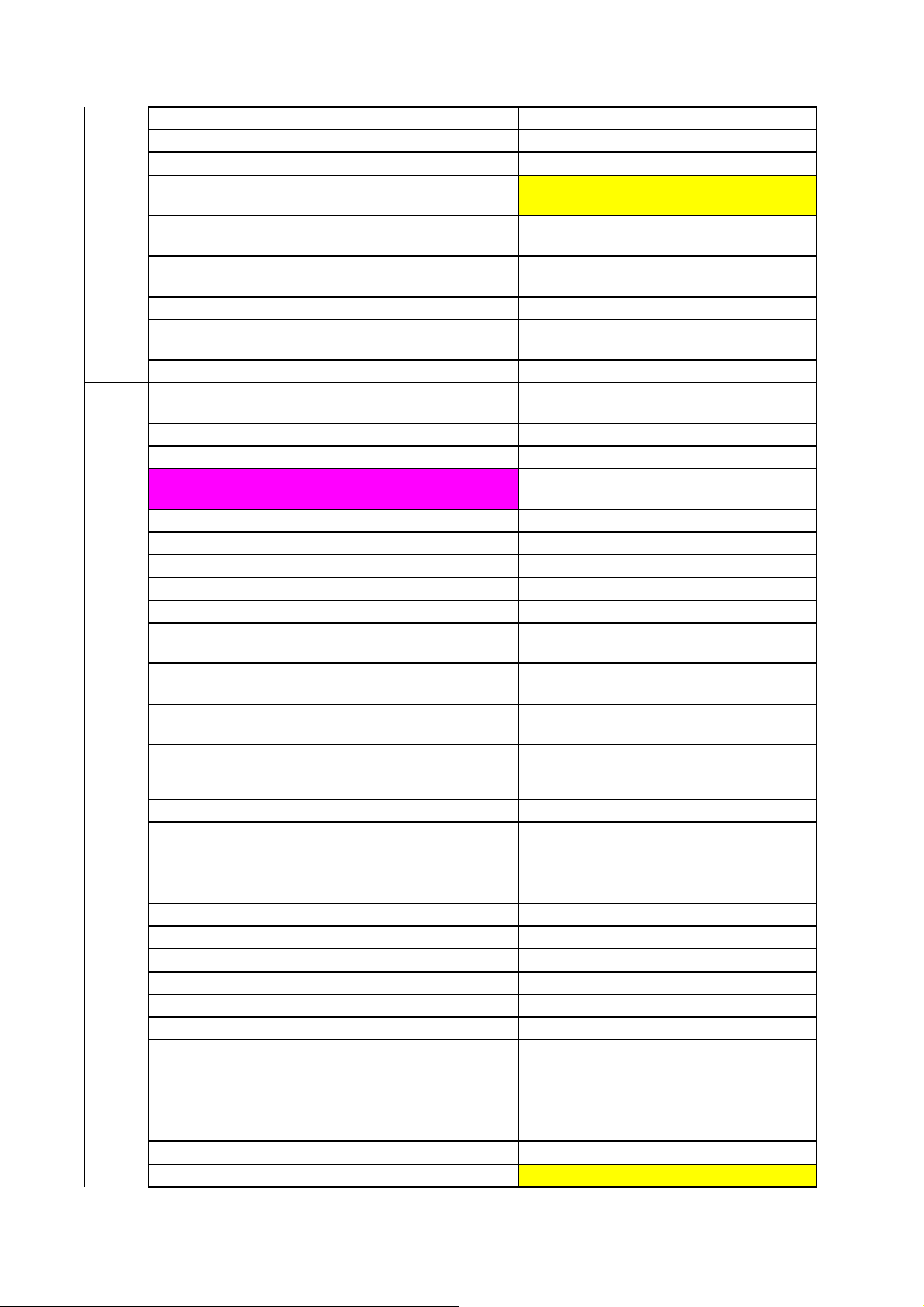

Page 8

Color System (PAL/SECAM/NTSC) PAL/SECAM/NTSC(AV)

prog

)

g

DVBT (yes/no) Yes

Video standard NTSC 3.58 / 4.43 (AV) Yes

HD capability

Compatible video format if DVD/USB:

DviX/VCD/SVCD/JPEG/AVI/MPEG2/WMV- HD/SD

Compatible audio format if DVD/USB:

MP3/WMA/AAC/MPEG1/…

PC capability (up to maximum format) 1280*1024 60Hz

Playable Discs (CD/CD-R(RW)/CD-

Decoding capabilityUser convenience

ROM/DVD+R/+RW/-R/-RW)

Card reader format compatibility -

IB languages

DVD player (No/slot/tray) No

Program Numbers (example: 99+3AV) 99+1AV+2SCART

Number of buttons on cabinet (Power; Vol+/-; Pr+/-,

Menu )

Main switch button (yes/no) No

Clock Yes

Sleep timer Yes

wake-up timer Yes

Calendar / Games Yes/Parent Control - Channel lock (Input code for certain

channel)

Parent Control - Child lock (set the lock of the

keyboard, only the RCU can control the TV)

Parent Control - Kid pass (preset the ontime,

channel for each day of the week)

Parent Control - Channel lock (For digital

transmission and DVD program, to filter some

ramms

Program auto switch off No

OSD Language*

OSD Positioning No

OSD Transparency Adjust No

OSD Timeout Adjust No

Text Standard: (Top, FLOF,,,) TOP & FLOF

Teletext Level: 2.5 / 1.5 1.5

Pages for teletext 1000

Teletext character sets ****

TV Guide No

Auto Naming/Auto Sorting Yes/Yes

YES (720p, 1080i 50/60; 1080p 25/30;

480i/p; 576i/p)

-

-

–

DE, FR, IT, ES, EN, PL, CS, HU, RU, PT,

EL, NL, SV, DA, FI, NO

Power, PR +/–, Vol +/–, Menu

Yes

Yes

No

Yes

Germany、English、Netherlandish、

Italian、Finnish、Spanish、Danish、

French、Portuguese、Poland、

Norwe

Latin Pan-Euro West

Latin Pan-Euro East

Cyrillic West

Greek West

Arabic West

ian、Swedish、 Czechic

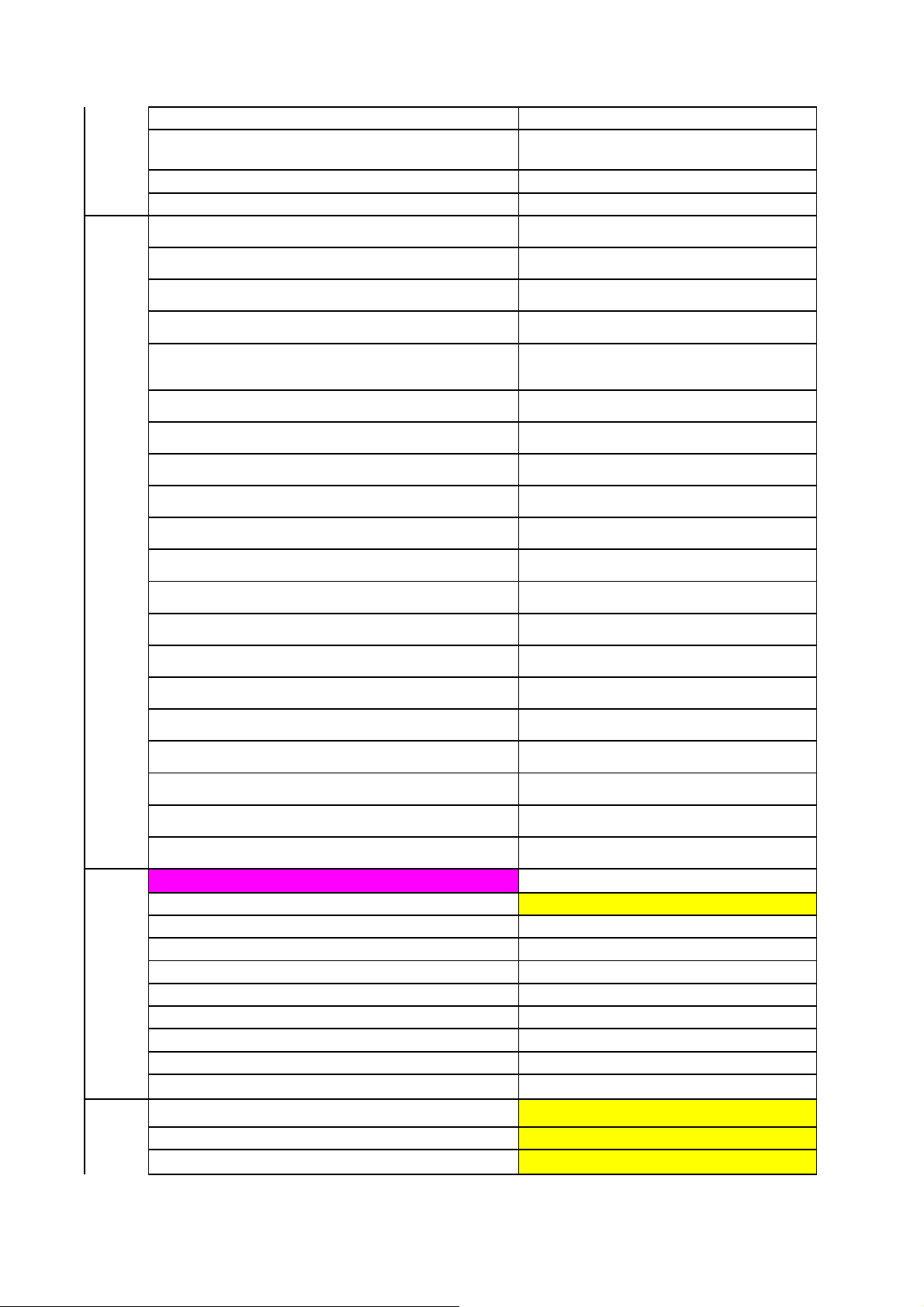

Page 9

Auto update (for DVBT software ugrades) No

Multipicture : PIP (Double Tuner) / PIP (AV) / PAP /

PAT / PIC

Hotel mode (Y/N) No

Tuner FM (yes/no) No

RF Input (Antenna): Analogical / Digital 1 /1

Scart 1 : CVBS / RGB / S-VIDEO 1/1/Scart 2 : CVBS / RGB / S-VIDEO 1/-/1

Scart 3 : CVBS / RGB / S-VIDEO -

only PAT

CINCH audio in / out (No volumpe control on Audio

out/can be jack 3,5mm)

CINCH video in / out 1(side)/S-video in / out -/Component Video Input (YCrCb/YPrPb) 1

Component Audio Input (YCrCb/YPrPb) Share with the VGA Audio input

VGA in / Audio L/R in / Jack audio in 3.5mm 1/1/HDMI 2

DVI-HDCP Share with HDMI

Audio input for DVI – HDCP Share with Audio VGA

CINCH subwoofer out / Coaxial out (SP-DIF) -/Headphone connector (mm) 1 (side)

RS232 (Y/N) Card Readers USB slot (NO/1.1/2) -

Connectors (if possible, please indicate the position)Accessories included

DVBC-I (common interface) yes

1(side)/1

External power converter Remote control reference RCT 311TV1G

Carton (English/French/Spanish) yes(English)

Batteries yes

IB yes

Product registration Card no

AC power cords yes

Audio Cord (Jack 3.5mm) no

VGA Cord no

Wallmount No

Antenna Cable no

Size (W x H x D, with stand) in mm 1058X765X270

Size (W x H x D, without stand) in mm 1058X711X116

Package Size (W x H x D, with stand) in mm 1214*364*889

Data

Page 10

Net Weight in kg 27.5

l

Gross Weight in Kg 33

Power supply 220V50Hz

Genera

Power consumption working / standby / Annual 240W/ 1W /Wallmount VESA compatible (standard reference) VESA compatible

Adaptor for VESA wallmount compatibility

(accessory ref)

Desktop Stand (included/optionnal + ref/NO) yes

Panel Tilt (Fowards/Backwards/Rotation) no

Swivel function desktop stand (yes/no) + motorized? no

Docking station (yes/no) no

Floor Stand (included/optionnal + ref/NO) no

Glass shield (yes/no) no

Finish on Front GES704S as moulded (high glossy black)

Finish on side RBK60TH(A8252) as moulded (black)

Finish on back RBK60TH(A8252) as moulded (black)

ID specification reference (file name) Graphic specification reference (file name) Finish on stand Transparent

number of colors on carton box 1

Brand logo Thomson Inlet

Other logo Full HD/DVB on front

Design / Mechanical

Screen Stikers External AC/DC Power with DC power cord (yes/no)

Handle (yes/no) no

Detachable speaker (yes/no) no

Number of Speaker 2

Rating Label langages

Rating Label Logos/Icons (GOST, Bin, Recycling,

Caution, …)

DE, FR, IT, ES, EN, PL, CS, HU, RU, PT,

no grounded plug

EL, NL, SV, DA, FI, NO

no

no

TBD

Page 11

LCDM61NF21(MT02+DE200) Factory Alignment Specification

ǃ

3.Alignment Procedure

General Description

LCD42/37M61NF21 is designed for Europe, using 37/42 inch Full HD

panel. The main chip is MTK8206. Support 1x RF in, 0.5x SCART, 1XSCART,

1xYPbPr, 1xVGA, 1xside AV include YC input, 2xHDMI,1x headphone out,

1xDVB-T input. The detail please refer the SyRS˅

1

Main board alignment

For Analog part

Before power on, please check and make sure the output of U20ˈU21ˈ

U22ˈU23,U24ˈU30ˈU31 are not shorted to grand.

Supply 5v to P504 and test the output of U20, the normal is 3.3V+/-5%, the

U21 output should be 1.8V+/-5%

Download the SW to the main chip, please see the chapter of how to

download

Check all the function of the all others board on the test tool

For PCMCIA interface

Digital module servicing and debug hints.

Mainly point:

1. Check PCB and each section power supply: 12V, 5V, 1.2V,1.8V ,3.3V.

2. Switch on the power, then measure the signal of output port of video and

audio.

If no output, check the following point:

1) video output of CPU section.

2) 4Mhz clock of the tuner output

3) Output of chip 74AHC1GU04( position U24 of schematic). 4Mhz clock

signal

to CUP(PNX8314).

4) Signal of SDRAM and flash chip when working .

5) Audio DAC ( component’s position U6 of schematic.

By contraries, enter the menu’s manual research item, and set appointed

channel number, check the signal indicator on TV screen.

3. Normal there is a signal level display on the menu.

If no displaying for the signal state indicated information, check the

following point:

1) 4Mhz clock signal of the tuner output,

2) Output of chip 74AHC1GU04(component’s position U23 of

schematic).

3) Else channel decoder schematic section.

4. When it display the signal state indicated information, Press “ok’ button,

and research program. It will not play the program if not get the program

Page 12

LCDM61NF21(MT02+DE200) Factory Alignment Specification

ǃ

list. Please check: components of the TS output from TDA10046 to CPU.

5. Inset the CAM card( PCMCIA CARD) to CI connector, the integrated

system will

detect it. if system has not found it, please check:

1) Input clock of Chip CIMAX SP2, The clock outputs from XD1

(component

XD1 of schematic) to chip CIMAX SP2.

2) Components and schematic of CI section ,

6. If not communication from ATV to digital module, Please check: I2C

of

the ATV( MT01 section) and digital module.

7. Check the SPDIF output. Connect SPDIF to Digital Power Amplifier.

Note: 4Mhz clock signal is sent out from tuner(TD1316A-MK3),

then distributed the clock to tda10046aht and pnx8314.

2

Final alignment

Fix mainboard on the test toolˈpower on ˈcheck and make sure all the port are

good

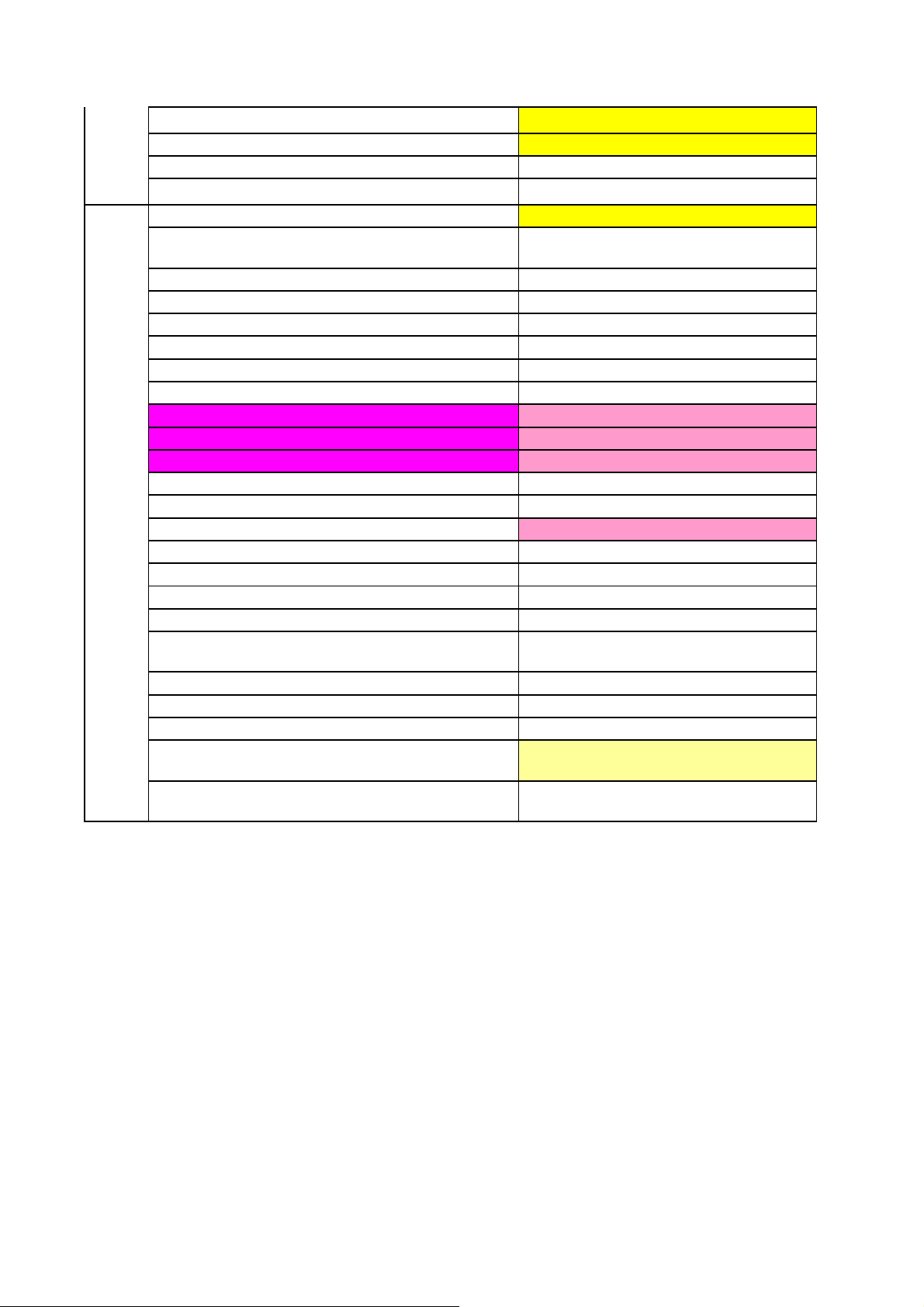

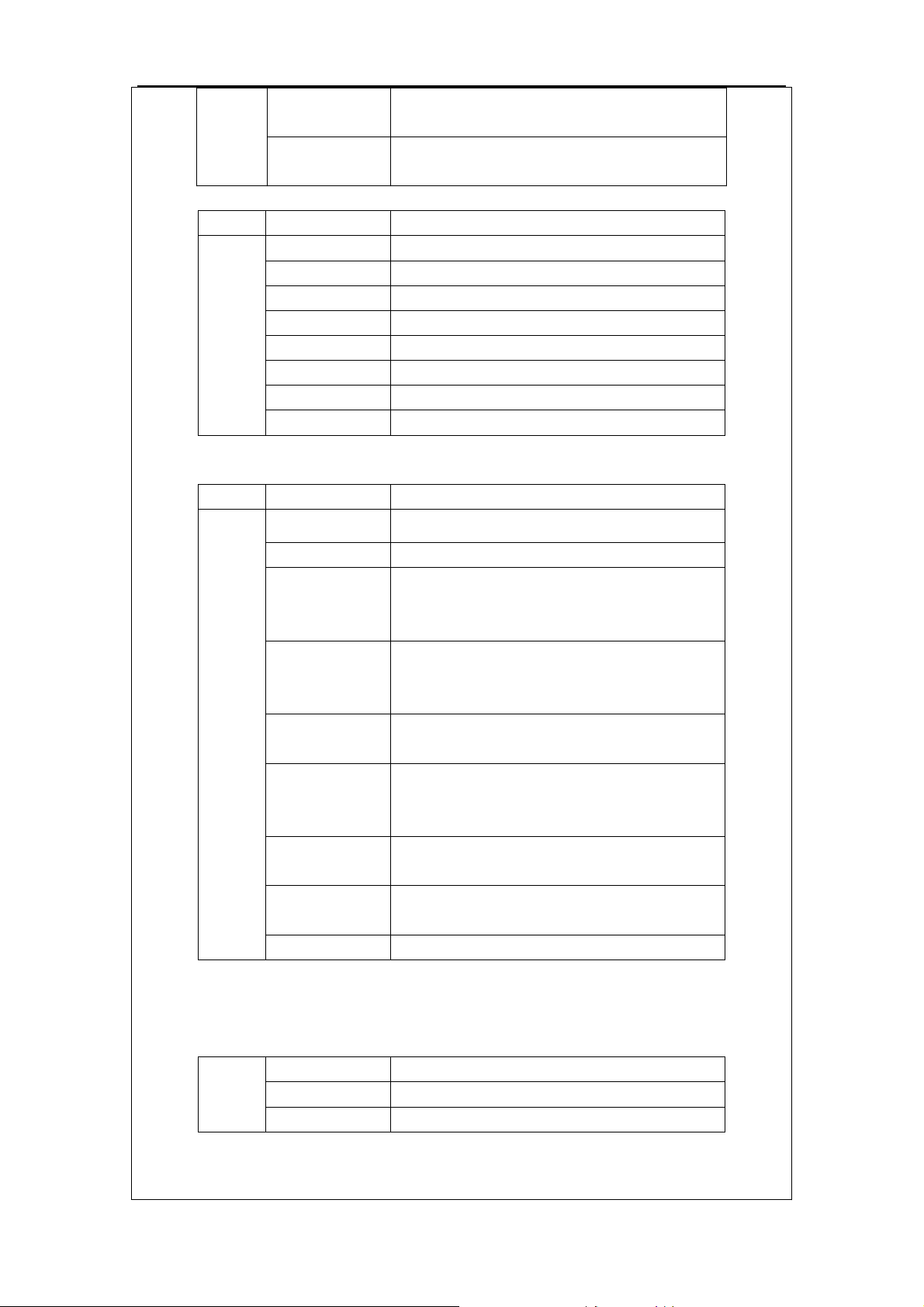

Source Test signal Test pattern Conclusion

Tuner Cable Full band Picture &

sound is ok

SCART1/2/SAV-C

VBS

SCART1/SAV-YC PM5418 PAL, half color &

SCART1/-RGB PM5418 PAL, half color &

PM5418 PAL, half color &

Gray bar

Gray bar

Gray bar

Picture &

sound is ok

Picture &

sound is ok

Picture &

sound is ok

SCART1 CVBS out cable First channel Picture &

sound is ok

HDMI DVD with HDMI

certification

VGA Chorma 2326 or

2327

Movie,720p

@60Hz

1024x768@60Hz

haft color & Gray

Picture &

sound is ok

Picture &

sound is ok

headphone Cable First channel sound is ok

Loud speaker Cable First channel Phase is

OK

YUV(YPbPr) chroma2327/BSG-3

60A/DVD

1080i@60Hz

haft color & Gray

Picture &

sound is ok

3ǃThe way to Factory menu

Page 13

LCDM61NF21(MT02+DE200) Factory Alignment Specification

˖

˅ˊ

Enter the factory menu (can use the IR and press the remote key “vol-”to

“0’, press mute remote key ,then press 9,7,3,5 remote key. Press right key

to

enter the sub-menu and press MENU key to return the main-menu

4ǃBalance Adjust

Adjust the temperature in CMP, VGA, AV. Please make sure the picture

mode is set to “Stand”, the “PictureÆ Black expand” on the user Menu is set to

“OFF”. “OtherÆFlesh Tone & Adaptive Luma Control ” on the factory Menu is

set to “OFF”. After Alignment, all the item will change to “ON”

ADC Adjust

A. For CMP input, the test signal is 576i/50Hz, 100%, 8 steps colour bar.

Select the “BalanceÆRGB Calibrate” on the factory Menu, then press ”Æ”.,

ADC adjust is finished after “OK” is displayed

B. For VGA input, the test signal is 1024h768/60Hzˈwhite/black grid.

Select the “BalanceÆRGB Calibrate” on the factory Menu, then press ”Æ”.,

ADC adjust is finished after “OK” is displayed

1

VGA :

For VGA input, the test signal is 1024h768/60Hzˈ16 steps gray bar. Set

the “BalanceÆ Tone” on factory menu to “Normal”:

AǃFor the third step form the white bar, Adjust the value of White RǃWhite

GǃWhite B, until the color temperature is x=280f5ˈy=290f5ˈY > 220nit

BǃFor the second step form the black bar, Adjust the value of Gray Rǃ

Gray GǃGray B, until the color temperature is x=280f5ˈy=290f5ˈY < 25nit

Cǃrepeat A&B, until all is ok

DǃAdjust the value of Black level

2˅ˊAV

For AV3 input, the test signal is PALˈ8 steps gray bar. Set the “BalanceÆ

Tone” on factory menu to “Normal”:

AǃFor the third step form the white bar, Adjust the value of White RǃWhite

GǃWhite B, until the color temperature is x=280f5ˈy=290f5ˈY > 220nit

BǃFor the second step form the black bar, Adjust the value of Gray Rǃ

Gray GǃGray B, until the color temperature is x=280f5ˈy=290f5ˈY < 25nit

Cǃrepeat A&B, until all is ok

DǃAdjust the value of Black level

3˅ˊCMP

For CMP input, the test signal is 576i/50Hzˈ16 steps gray bar. Set the

“BalanceÆ

Tone” on factory menu to “Normal”:

Page 14

LCDM61NF21(MT02+DE200) Factory Alignment Specification

AǃFor the third step form the white bar, Adjust the value of White RǃWhite

GǃWhite B, until the color temperature is x=280f5ˈy=290f5ˈY > 220nit

BǃFor the second step form the black bar, Adjust the value of Gray Rǃ

Gray GǃGray B, until the color temperature is x=280f5ˈy=290f5ˈY < 25nit

Cǃrepeat A&B, until all is ok

DǃAdjust the value of Black level

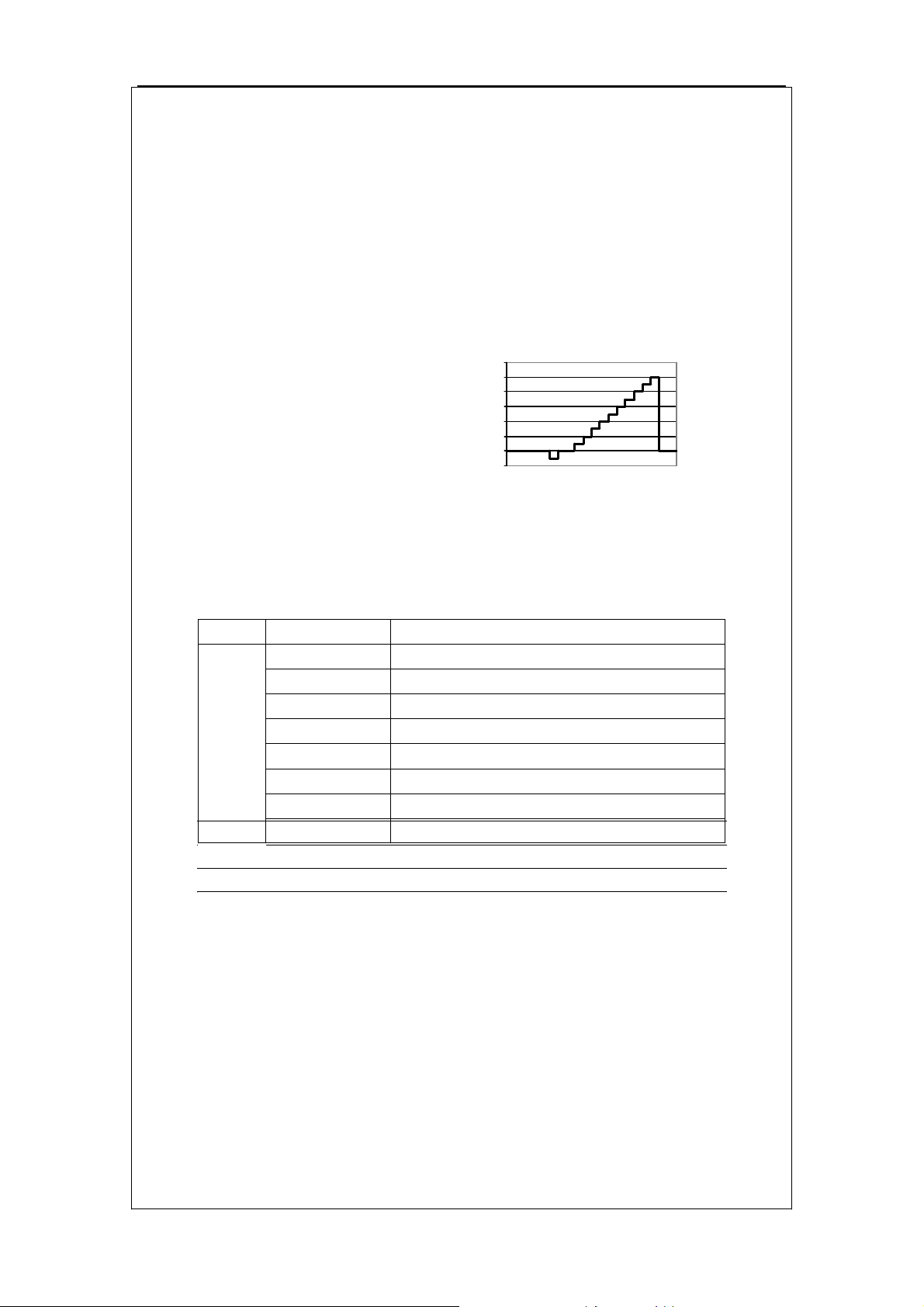

4). Adjust the value of Black level

Measurements are using ‘SCALBRI2.UPA’ patterns with -1% to 10% video

level bars.

12%

10%

8%

6%

4%

2%

video level (%)

0%

-2%

time

Basic video signal is following:

Change the Black level to make sure the value is 0-3%.

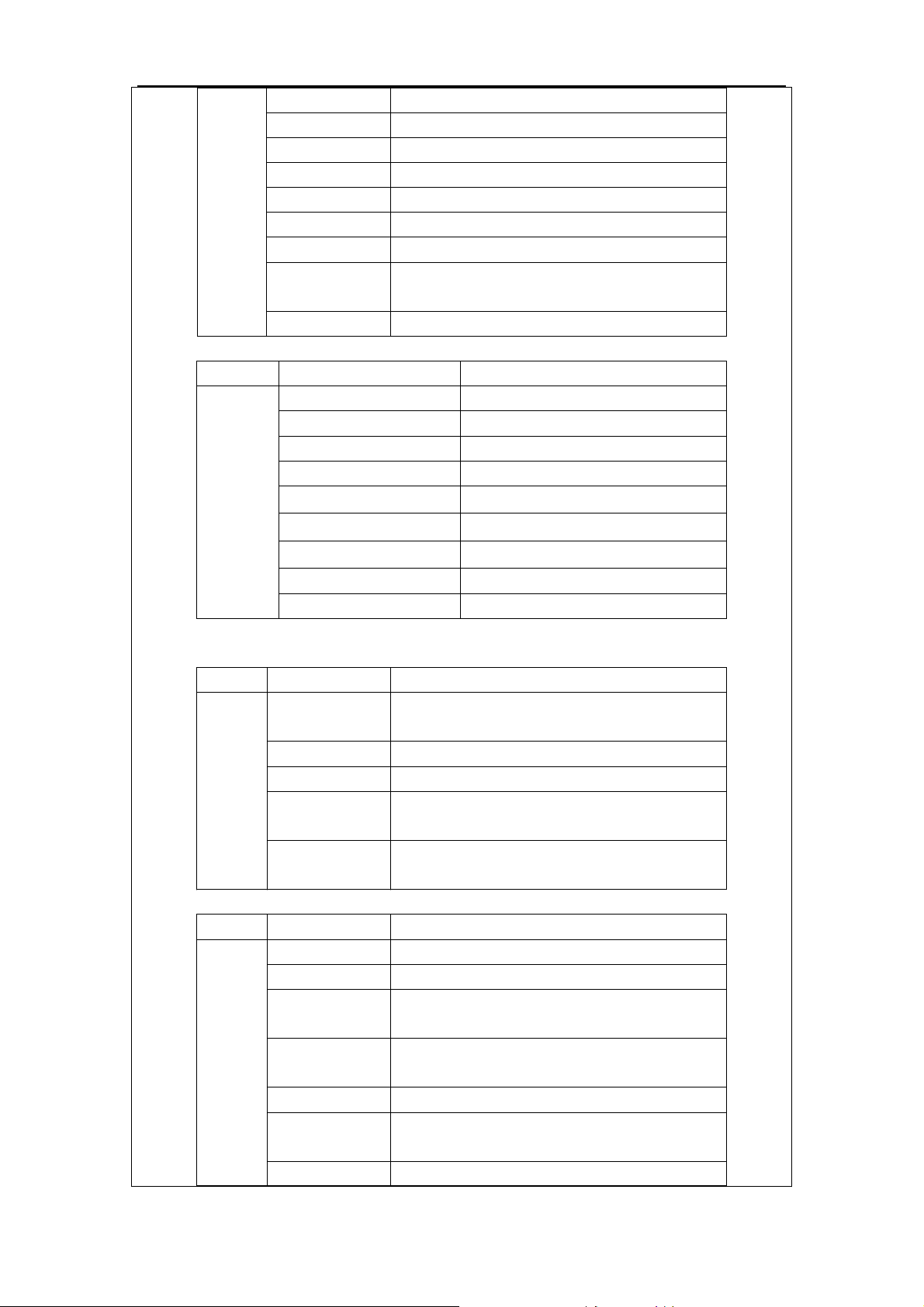

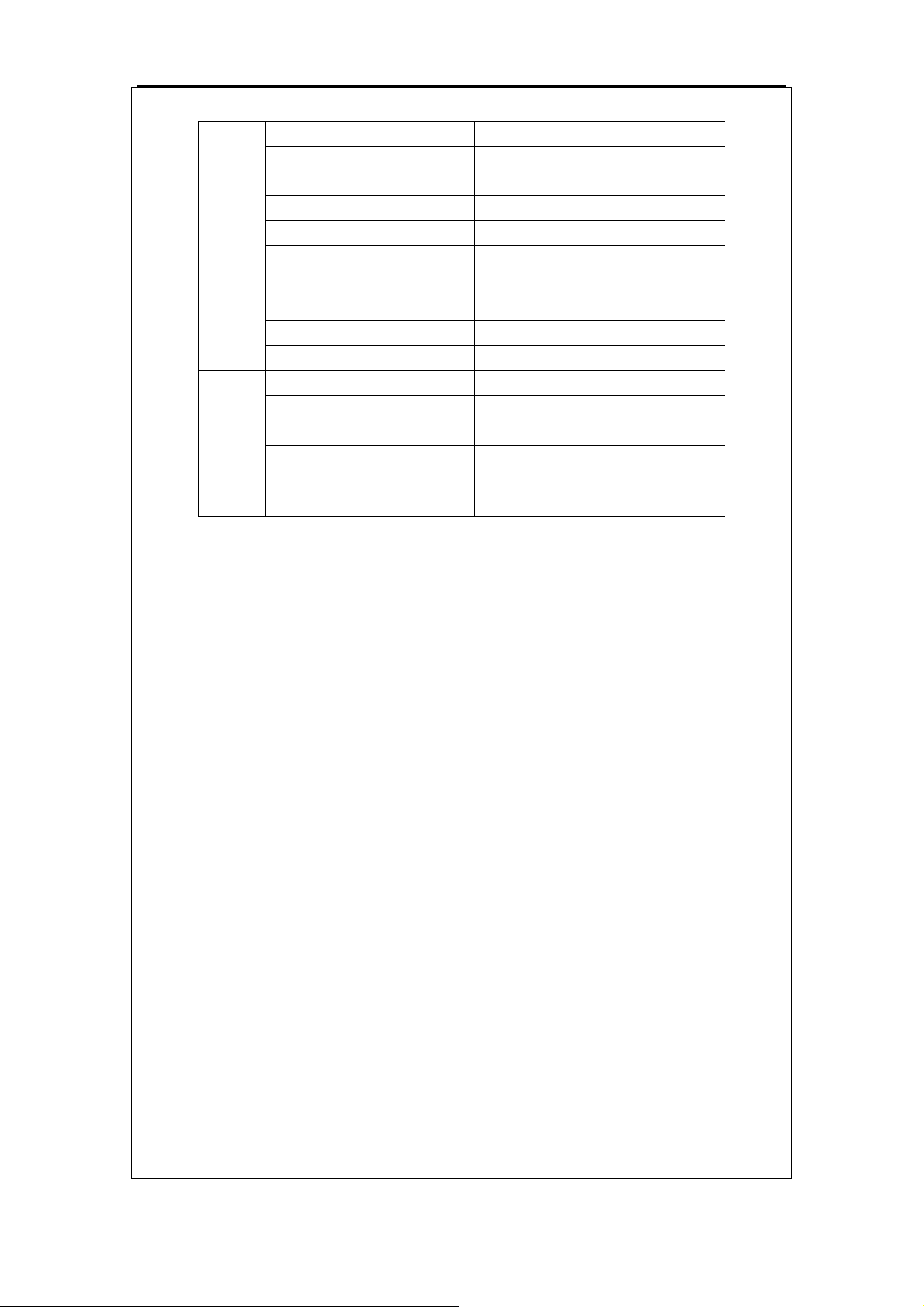

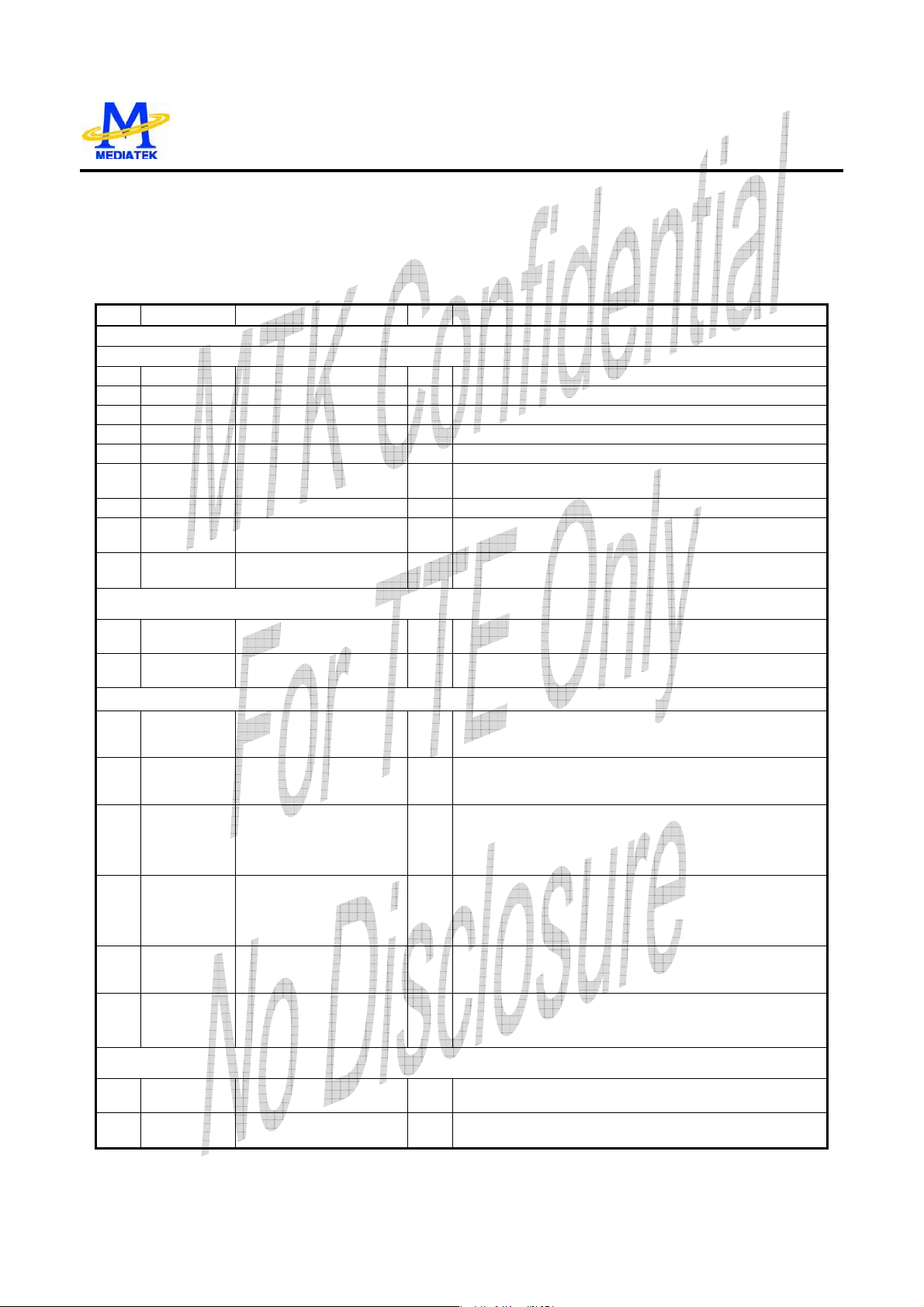

5ǃFactory Menu definition˖

1˅ˊ System

Item Sub-item

Power Mode Remember˖Remember the state of

Factory Key OFF˖Factory Key is invalidation

Tuner AGC 12

Key Board On˖the keypad board is locked, only

LOGO Select the POWER ON LOGO

Pattern Come from IC MT8201. It is used for

Back Light Peak White Alignment

Reset Reset EEPROM data, and load the

2)ˊ Balance

Page 15

LCDM61NF21(MT02+DE200) Factory Alignment Specification

Source For balance source

Balan

ce

Tone Normal/Warm/Cool White R R White balance

White G G White balance

White B B White balance

Gray R R Gray balance

Gray G G Gray balance

Gray B B Gray balance

RGB

ADC adjust

Calibrate

Black Level

3)ˊTV Geometry

Item Sub-item

TV Geo

Color System

H POS Horizontal Position

H SIZE Horizontal Size

V POS Vertical Position

V SIZE Vertical Size

Scaling Brightness User Menu’s Brightness

Scaling Contrast User Menu’s Contrast

Scaling Colour User Menu’s Colour

Scaling Hue User Menu’s Hue

4)ˊNicam All of item are for Debug, Don’t modify!

Item Sub-item

Nicam

Correct

5

Thres

Sync Loop 50

Error Thre 6

ParityErrorT

47

hres

EveryNumFr

32

ames

5)ˊMono All of item are for Debug, Don’t modify!

Item Sub-item

High DEVI OFF

AM Mute ON

AM Mute

69

High

AM Mute

53

Low

Carrier Shift OFF

Saturation

OFF

Mute

FM mute ON

Page 16

LCDM61NF21(MT02+DE200) Factory Alignment Specification

FM mute

24

High

FM mute

19

Low

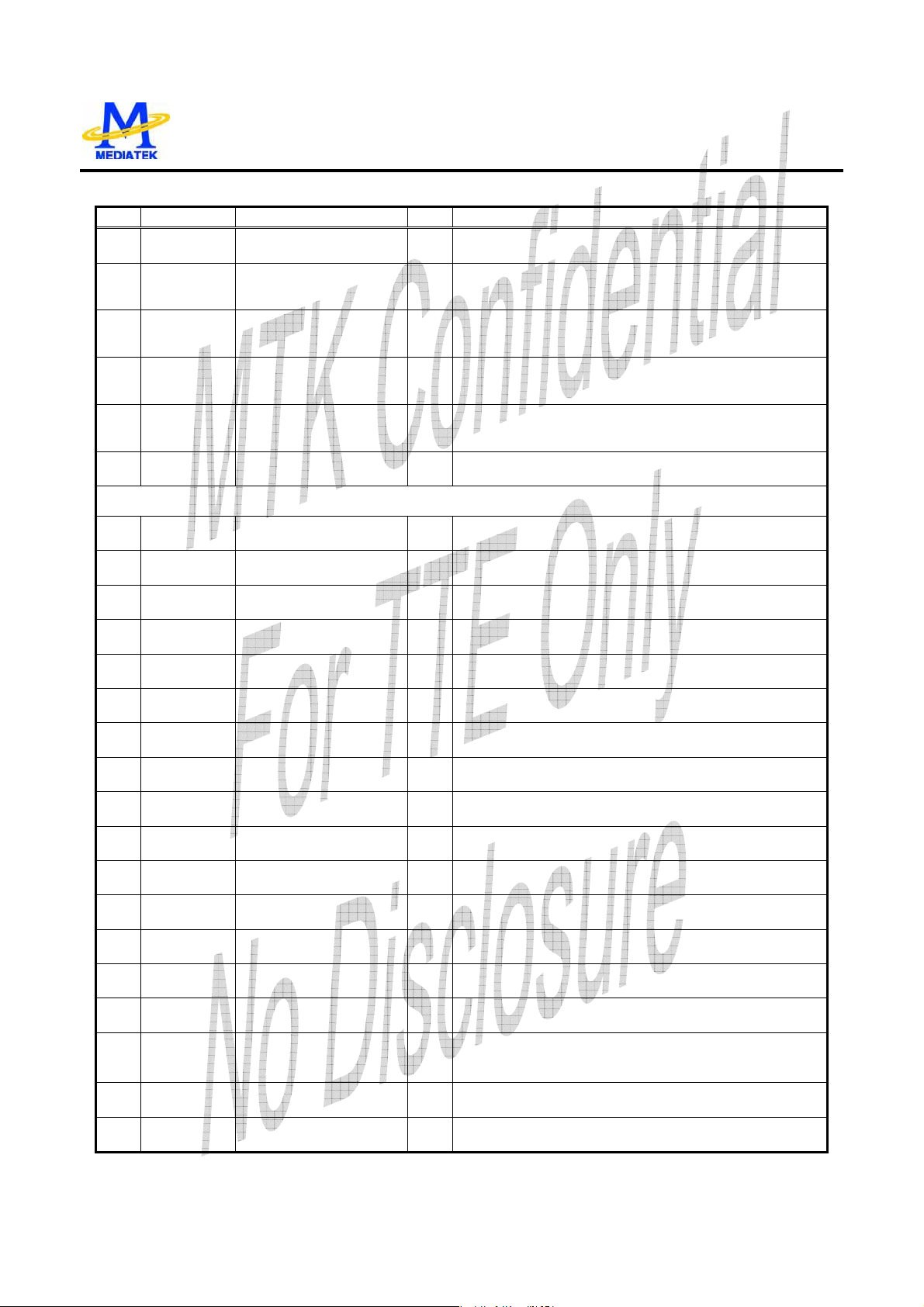

6)ˊSound Volume Curve

Item Sub-item

Soun

d

VOL_0 0

VOL_10 1

VOL_50 60

VOL_90 204

VOL_100 254

TV Pre TV pre- amplify

AV Pre TV pre- amplify

SWPREQ For debug

7)ˊOther乍 All of item are for Debug, Don’t modify!

Item Sub-item

Other

Blue Mute ON

CTI Middle

Flesh Tone Switch to “OFF” during alignment and

CAL Measurement.

Swtich to “ON” for Out of Box Settings

Adap

Luma….

Switch to “OFF” during alignment and

CAL Measurement.

Swtich to “ON” for Out of Box Settings

Deinter

Automatic

Mode

WhitePeak

limitor

Switch to “OFF” during alignment and

CAL Measurement.

Swtich to “ON” for Out of Box Settings

MDDi Edge

High

Pre

TTX

10

Contrast

Seamless Off

8)ˊINFO SW version information

Info

Project LCD32MT01M1

Version XXXXXX

Date 2007-1-5

Page 17

LCDM61NF21(MT02+DE200) Factory Alignment Specification

˖

6ǃFactory default settings

Source TV(channel 1)

Picture Preset Standard

Black expand ON

Tone Normal

USE

R

MEN

U

Noise reduction Low

Volume 30

Sound type Automatic

Virtual Surrond OFF

Auto Volume OFF

Sound effect OFF

FACTTORY-KEY OFF

FACT

TOR

Y

MEN

POWER ON OFF

Flesh Tone ON

Adaptive Luma

Control.

U

ON

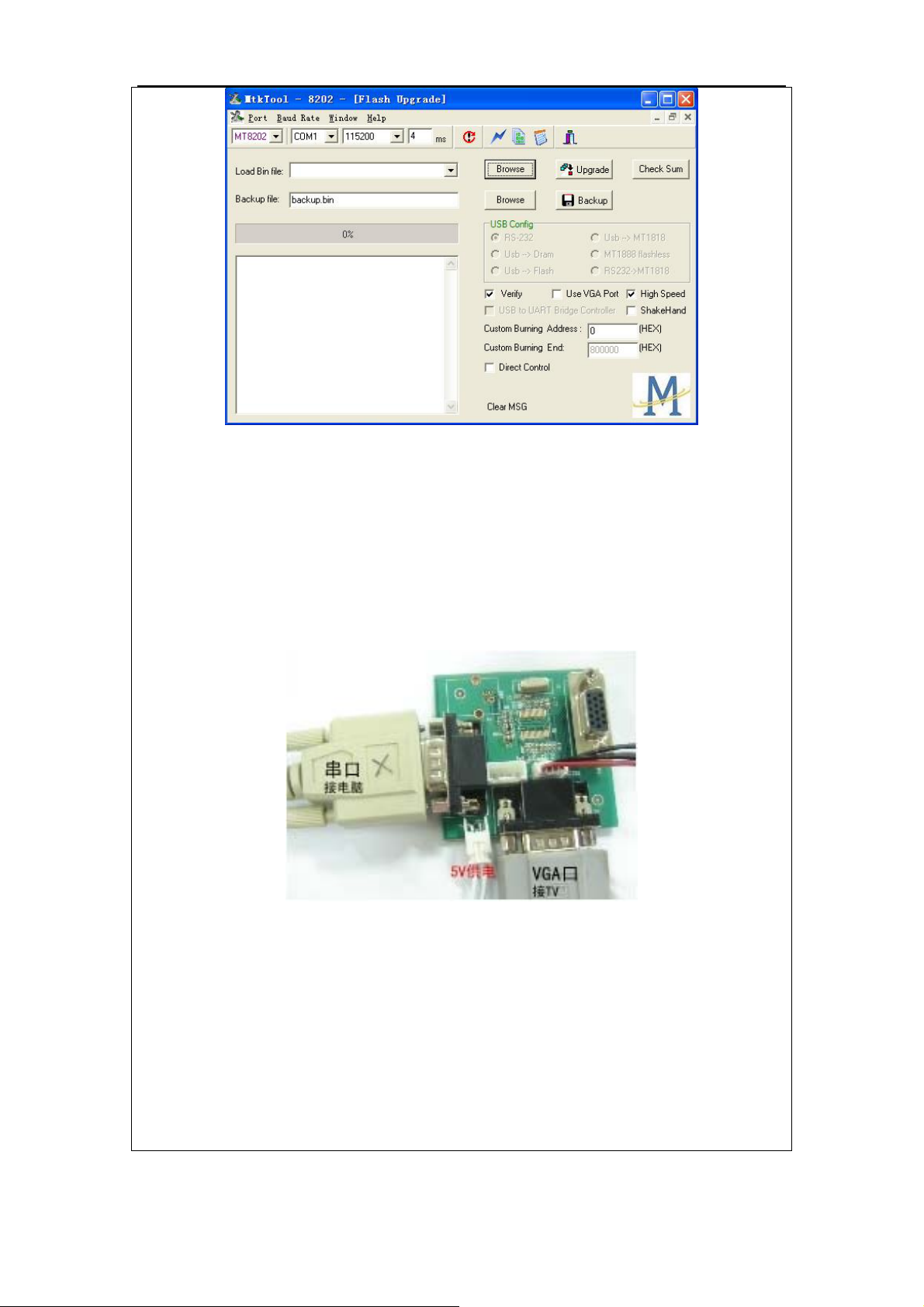

7ˊAnalog board software update

Solution 1˖

Prepare MTKTOOL UPDATE, update board, serial line.

(1)ǃConnect PC, update board, and J3 on the main board with serial line

(2)ǃProvide the STB +5V for main board

(3)ǃOpen “MtkTool.exe” in MTK TOOL program, and set the parameter as

below picture

Page 18

LCDM61NF21(MT02+DE200) Factory Alignment Specification

(4)ǃPress “Browse” for selecting the SW.

(5)ǃPress “Upgrade” to download the SW. It will be OK when it show “100%”

(6)ǃAfter downloading SW, it will be long time for Initializing EEPROM.

Solution 2˖

Preparative is same with above.

Set SYSTEM->FactoryKey on factory MENU to OFF. Connect the device

as below picture.

Update the SW follow solution1- (3), (4), (5), (6)

Page 19

4.IC Brief Instruction

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT8206

1. Features description

MT8206

format up to HDTV. It includes 3D comb filter TV decoder to retrieve the best image from

popular composite signals. Embedded HDTV/VGA decoders enable the high quality video

reproduction. 24/16/8 bits digital port may accept all kinds of external digital input video source.

New 3

video into progressive non-flicking video. 2D Graphic engine generates high quality UI

interface. Advanced full function color processing with fully 10-bit path provides high quality

video contents. Independent two Flexible scalars provide wide adoption to various LCD panels

for two of different video sources at the same time. Its on-chip audio processor decodes

analog signals from tuner with lip sync control, delivering high quality post-processed sound

effect to customers. On-chip microprocessor reduces the system BOM and shortens the

schedule of UI design by high level C program. MT8206 is a cost-effective and high

performance HDTV-ready solution to LCD TV product.

is a highly integrated single chip for LCD TV supporting video input and output

rd

generation advanced motion adaptive de-interlacer converts accordingly the interlace

FEATURE List

Analog front end

1 set of high resolution ADC with corresponding PGAs adopting to 0.5V~2V input dedicated for TV/AV/SV input signals

3 high speed ADCs dedicated for VGA/HDTV input signals up to 160MHz

All 8-bit programmable gain pre-amplifiers

Embedded Schmitt trigger and deglitch circuits on Hsync/Vsync/SOG/SOY inputs

Video Input

Embedded input Multiplexers without external switch including

10 for TV/AV/S-video input pins available for any possible combination

3 sets for VGA/Component/Scart/D-connector with differential input pairs

1 24/16/8 bit digital port for ITU601/656/RGB video format

1 additional 8 bit digital port for ITU656 video format

All the input sources can be flexibly routed to Main/PIP internally

Sync Processor

Two enhance sync processors for all timing detection supporting Macrovision detection

Enhanced measuring mechanism for VGA auto adjustment

Decoder

TVD

Single 3

Automatic TV standard detection supporting NTSC, NTSC-4.43, PAL (B, G, D, H, M, N, I, Nc), PAL (Nc), PAL, SECAM

Enhanced 3

rd

generation TV decoder

rd

generation NTSC/PAL Motion Adaptive 3D comb filter

June, 2006

Page 20

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Embedded VBI decoder for Closed-Caption/XDS/ Teletext/WSS/VPS

Supporting Macro vision detection

YPbPr/Scart/D-connector

Supporting HDTV 480i/480p/576i/576p/720p/1080i input

Smart detection on Scart function for European region

Smart detection on D-connector for Japan region

Supporting SCART RGB inputs mixed with composite signal by adjustable horizontal delay

VGA

Supporting various VGA input timings up to SXGA (1280x1024@75Hz).

Supporting Separate/Composite/SOG sync types

Digital port

1 digital port supporting DVI 24-bit RGB or CCIR-656/601 digital video input format

1 additional 8 bit digital port for ITU656 video format

VBI

Dual VBI decoders for the application of V-Chip/Closed-Caption/XDS/ Teletext/WSS/VPS

Supporting external VBI decoder by YPbPr input

VBI decoder up to 1000 pages Teletext.

Video Processor

Noise Reduction

All Video input source with motion adaptive 3D noise reduction

Color Management

Fully 10-bit processing to enhance the video quality

Advanced flesh tone and multiple-color enhancement. (For skin, sky, and grass…)

Gamma/anti-Gamma correction

Advanced Color Transient Improvement (CTI)

Saturation/hue adjustment

Contrast/Brightness/Sharpness Management

Sharpness and DLTI/DCTI

Brightness and contrast adjustment

Black level extender

Adaptive Luma/Chroma management

De-interlacing

rd

3

generation advanced Motion adaptive de-interlacing

Automatic detect film or video source

3:2/2:2 pull down source detection

Main/PIP 2 independent de-interlacing processor

Scaling

rd

3

generation high resolution arbitrary ratio vertical/horizontal scaling of video, from 1/32X to 32X

Advanced linear and non-linear Panorama scaling.

Picture-in-Picture (PIP)

Picture-Out-Picture (POP)

Display

Advanced dithering processing for LCD display with 6/8/10 bit output

10bit gamma correction

Supporting alpha blending for Video and two OSD planes

Frame rate conversion

Seamless performance comparing demonstration function

MT8206

June, 2006

Page 21

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Support Left/Right video processing comparing function without additional resources (DRAM…) for customers’

demonstration

All the video functions (De-interlace/3D comb/NR/Flesh tone/CTI) can be included

Video Output

Programmable output timing for 1080p panel.

Dual-channel 6/8-bit LVDS, single channel 6/8/10-bit LVDS

Supporting video output mirror and upside down

1 CVBS bypass output of CVBS/S-video(mixed) input

Audio Features

Supporting BTSC/EIAJ/A2/NICAM decode

Stereo demodulation, SAP demodulation

Mode selection (Main/SAP/Stereo)

Equalizer

Sub-woofer/Bass enhancement

MTK proprietary 3D surround processing (Virtual surround)

Audio and video lip synchronization

Supporting Reverberation

MT8206

Audio Input/Output

Decode audio AF from Tuner

1 set of audio L/R digital line in (MT8206 is Master)

7.1-channel slave digital line in

Supporting total 12-channels including full 7.1-channels digital output, 2- channel bypass and 2-channel headphone

output.

Embedded 3 internal audio DACs

Supporting 1 Tuner audio decoder and 1 digital input and both output for SCART1/2 output application

2D-Graphic/OSD processor

Embedded two backend RGB domain OSD planes and one YUV domain OSD plane. To support Main/PIP

Teletext/Close-caption functions together with setup menu

Supporting alpha blending among these two planes and video

Supporting Text/Bitmap decoder

Supporting line/rectangle/gradient fill

Supporting bitblt

Supporting color Key function

Supporting Clip Mask

65535/256/16/4/2-color bitmap format OSD,

Automatic vertical scrolling of OSD image

Supporting OSD mirror and upside down

Host Micro controller

Turbo 8032 micro controller

Built-in internal 373 and 8-bit programmable lower address port

2048-bytes on-chip RAM

June, 2006

Page 22

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Up to 4M bytes FLASH-programming interface

Supporting 5/3.3-Volt. FLASH interface

Supporting power-down mode

Supporting additional serial interface

IR control serial input

Supporting 2 RS232 interface for external source communication

Supporting single interface directly supporting SD/MS/MMC memory card

Supporting 2 PWM output

Programmable GPIO setting for complex external device control

DRAM Controller

Supporting up to 32M-byte SDR/DDR DRAM

Supporting 2x16 bit SDR/DDR bus interfaces

Build in a DRAM interface programmable clock to optimize the DRAM performance

Programmable DRAM access cycle and refresh cycle timings

Supporting 3.3/2.5-Volt SDR/DDR Interface

DRAM Usage

For features of 8206, Dual 8Mx16 DDR are used.

It is recommended to use dual 8Mx16 DDR (32MB) for following basic features.

MT8206

Function Full Screen PIP/POP

3D-Comb Y

MDDi Up to 1080i MDDi

Scale mode Normal/Full Normal/Full

VGA timing Up to

1280x1024@75Hz

Panel 1080P

z For PIP/POP mode, 1280x1024 should be under 60Hz.

z Case lists are evaluated when Dram clock = 169 MHz,DDRx2.

Flash Usage

Flash is used to store FW code, fonts, bitmaps, big tables for VGA, Video, Gamma..

In our demo system, we can support 2-4 languages within 1MB flash.

For single country, we need around 20KB to store font data.

For more bitmaps, we need more flash space to store them.

When POP mode, Main=AV, Sub=1080I, only one of HD MDDi and Comb

can be enable.

(for POP)Case i: Main=AV(with 3D Comb), Sub=1080i(Bob mode)

(for POP)Case ii: Main=1080i(Bob mode), Sub=AV(with 3D Comb)

(for POP)Case iii: Main=AV(without 3D Comb), Sub=1080i(HD MDDi)

(for POP)Case iv: Main=1080i(HD MDDi), Sub= AV(without 3D Comb)

When PIP mode, there is no constraint in 3D-Comb and MDDi.

Up to 1280x1024x60Hz

2Mbytes is recommended to build a general TV model.

Outline

June, 2006

Page 23

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

388-pin BGA package

3.3/2.5V/1.8-Volt. operating voltages

0.18um process

MT8206

June, 2006

Page 24

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT8206

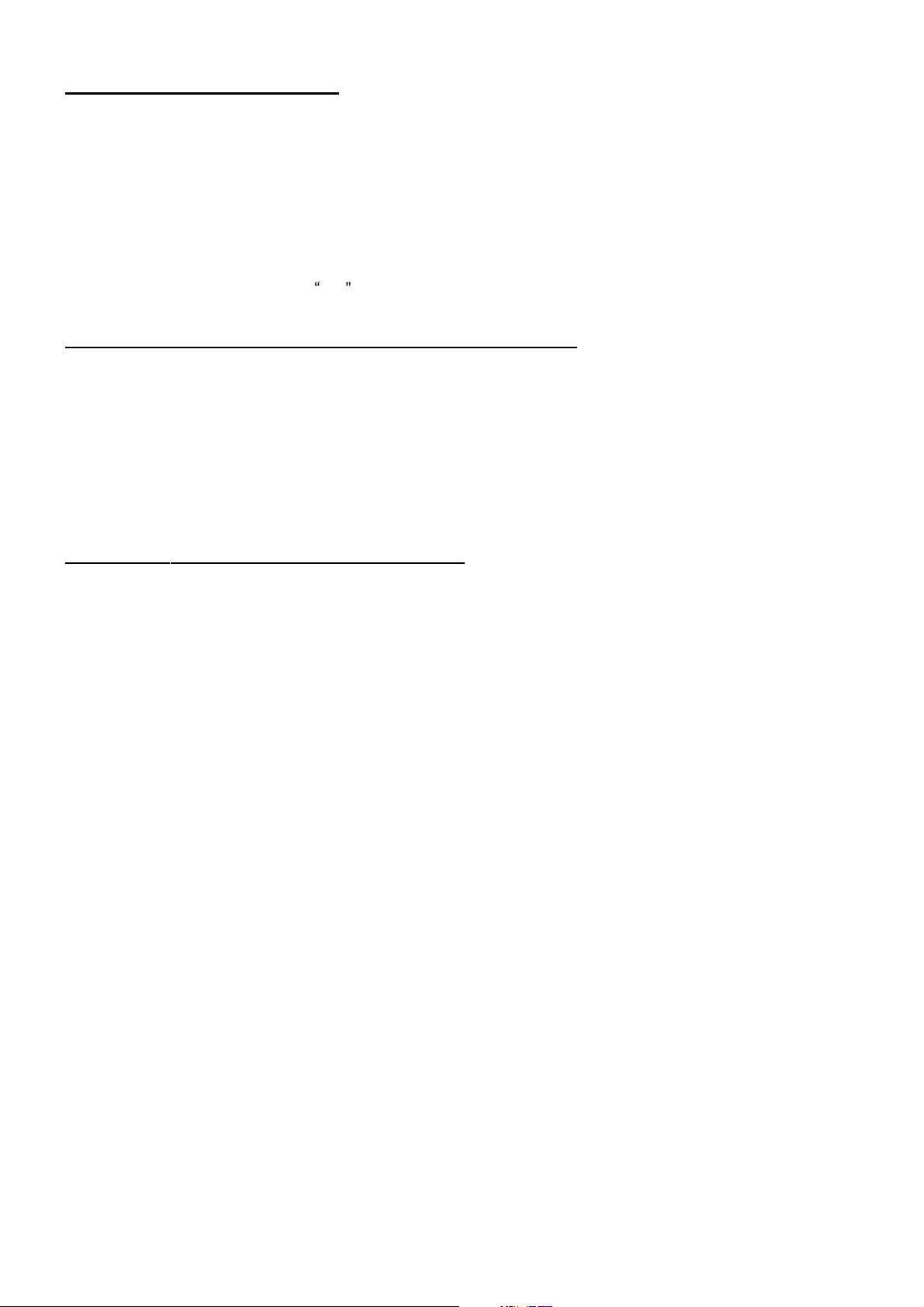

3. BLOCK DIAGRAM

CVBS / SV

(x8)

(Customer)

External

YPbPr

(x2)

Switches

VGA

Digital

Control Signal (GPIO, …)

LVDS

DAC

Analog Front End

ADC

ADC

3D TVD

HDTVD

ADC

VGAD

ADC

Digital Path

LVDS Tx

Gamma

Dithering

Merge

MUX

8032

Main Path

MDDi

PIP Path

MDDi

OSD

Color

Color

DSP

DS

DRAM

DS

US

US

June, 2006

Page 25

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT8206

4. MT8206 PIN DESCRIPTION

4.1GENERAL PIN LIST:

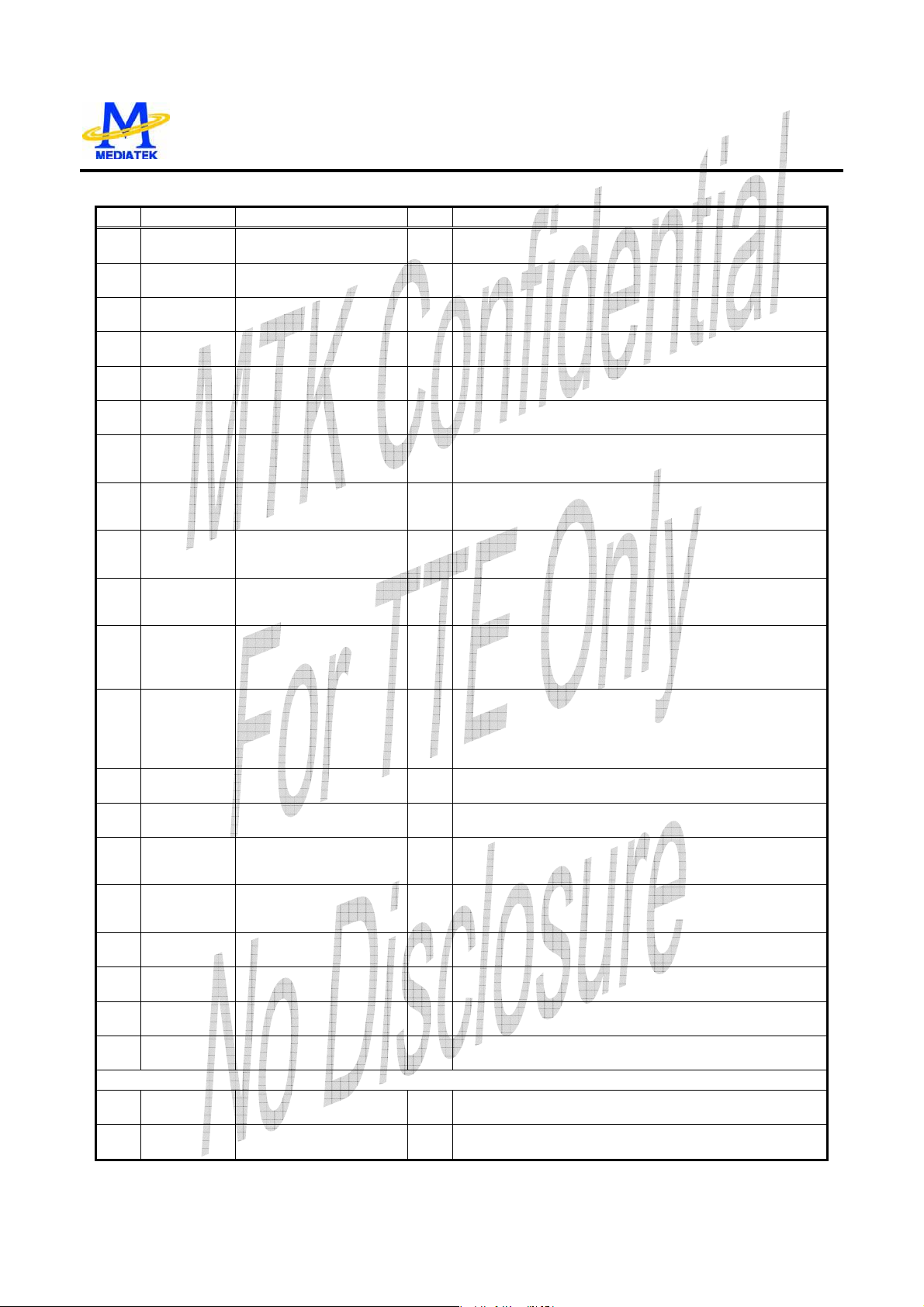

Item Symbol Pin # Type Description

DIGITAL

Power/Ground (41)

1 DVDD33A D5, H4 I 3.3V power (necessary when power saving)

2 DVDD33 AA4, AC17, AC20 I 3.3V power for all the 3.3V I/O pins

2 DVSS33 L11, N12, R15, T16 I 3.3V ground

3 DVDD25 AC5, AC6, AC7, AD5, AD6, I 2.5V power for DDR (for 16/32 bit DDR)

DVDD25OPT AC14, AC15, AD15 I 2.5V power for DDR (for 32 bit DDR), 3.3V power for GPIO

DVSS25 N11, P11, R11, T11, R13,

T13, T14

5 DVDD18A K3, K4 I 1.8 V power (necessary when power saving)

DVDD18 U3, U4, AC8, AC9, AC22,

AC23

6 DVSS18 L12, M11, M12, P12, R12,

R14, R16, T12, T15

I 2.5V ground for DDR (for 16/32 bit DDR)

I 1.8 V power for internal digital part

I 1.8 V ground

RS232 (2)

1 RXD M3 I RS232 received data, 2mA

2 TXD M4 O RS232 transmitted data, 2mA

Serial interface (6)

1 SCL AA2 O

2 SDA AA1 I/O

3 SCL0 U23 I/O

4 SDA0 V23 I/O

5 SCL1 AB24 I/O

6 SDA1 AB23 I/O

Digital Audio Interface (8)

1) GPIO, 2mA

2) Clock of master serial interface, 2mA

1) GPIO, 2mA

2) Data of master serial interface, 2mA

1) Clock of slave0 serial interface, 2mA

2) GPIO

3) RS232 RXD

1) Data of slave0 serial interface, 2mA

2) GPIO

3) RS232 TXD

1) Clock of slave1 serial interface, 2mA

2) GPIO

1) Data of slave1 serial interface, 2mA

2) GPIO

1 AOMCLK M1 O Audio out master clock, 2~16mA, SR(optional), SMT

2 AOLRCK N3 O Audio out left-right clock, 4mA, SR, SMT

June, 2006

Page 26

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

3 AOBCK N1 O Audio out bit clock, 2~16mA, SR(optional), PD(optional), SMT

MT8206

4 AOSDATA0 P1 O

5 AOSDATA1 P2 O

6 AOSDATA2 P3 O

7 AOSDATA3 P4 O

8 LIN N4 I Audio line in

Microcontroller and Flash Interface (38)

1 HIGHA0 G2 I/O

2 HIGHA1 F3 I/O

3 HIGHA2 F4 I/O

4 HIGHA3 E1 I/O

5 HIGHA4 E2 I/O

6 HIGHA5 E3 I/O

7 HIGHA6 E4 I/O

8 HIGHA7 D1 I/O

9 AD7 C4 I/O

10 AD6 B1 I/O

11 AD5 B2 I/O

12 AD4 A2 I/O

13 AD3 B3 I/O

14 AD2 A3 I/O

15 AD1 B4 I/O

1) GPIO (default, input in initial state)

2) Audio out data line 0, 4mA, SR, PD(optional), SMT

1) GPIO (default, input in initial state)

2) Audio out data line 1, 4mA, SR, PD(optional), SMT

1) GPIO (default, input in initial state)

2) Audio out data line 2, 4mA, SR, PD(optional), SMT

1) GPIO (default, input in initial state)

2) Audio out data line 3, 4mA, SR, PD(optional), SMT

Microcontroller address 8, 2~16 mA, PU, works in stand-by

mode

Microcontroller address 9, 2~16 mA, PU, works in stand-by

mode

Microcontroller address 10, 2~16 mA, PU, works in stand-by

mode

Microcontroller address 11, 2~16 mA, PU, works in stand-by

mode

Microcontroller address 12, 2~16 mA, PU, works in stand-by

mode

Microcontroller address 13, 2~16 mA, PU, works in stand-by

mode

Microcontroller address 14, 2~16 mA, PU, works in stand-by

mode

Microcontroller address 15, 2~16 mA, PU, works in stand-by

mode

Microcontroller address/data 7, 2~16 mA, SR, works in

stand-by mode

Microcontroller address/data 6, 2~16 mA, SR, works in

stand-by mode

Microcontroller address/data 5, 2~16 mA, SR, works in

stand-by mode

Microcontroller address/data 4, 2~16 mA, SR, works in

stand-by mode

Microcontroller address/data 3, 2~16 mA, SR, works in

stand-by mode

Microcontroller address/data 2, 2~16 mA, SR, works in

stand-by mode

Microcontroller address/data 1, 2~16 mA, SR, works in

stand-by mode

16 AD0 A4 I/O

17 IOA0 C2 I/O

18 IOA1 C1 I/O

June, 2006

Microcontroller address/data 0, 2~16 mA, SR, works in

stand-by mode

Microcontroller address 0 / IO, 2mA, SR, PU, works in

stand-by mode

Microcontroller address 1 / IO, 2mA, SR, PU, works in

stand-by mode

Page 27

Æ

Æ

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

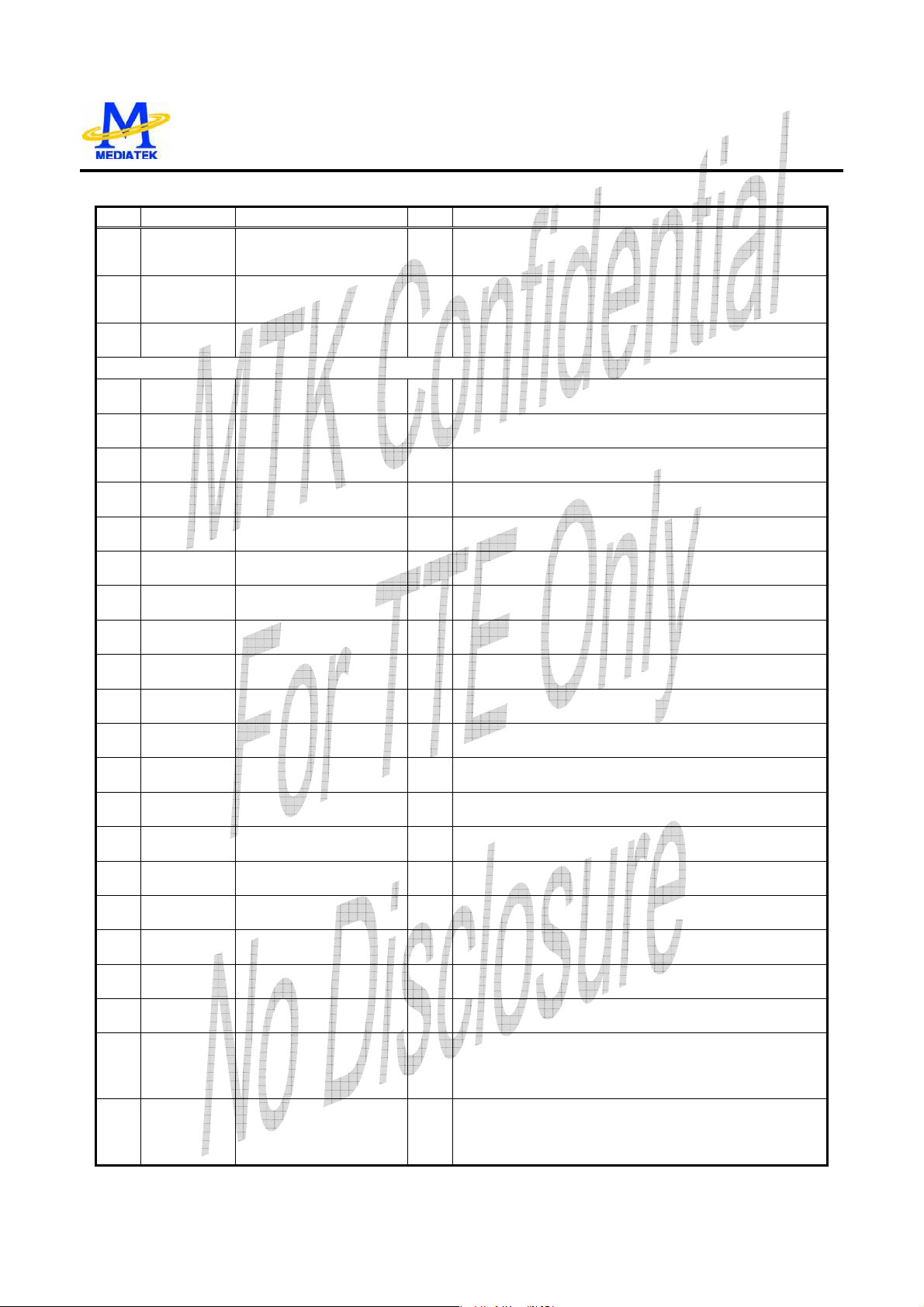

Item Symbol Pin # Type Description

19 IOA2 D4 I/O

20 IOA3 D3 I/O

21 IOA4 G1 I/O

22 IOA5 H3 I/O

23 IOA6 H2 I/O

24 IOA7 H1 I/O

25 A16 D2 I/O

26 A17 C3 I/O

27 IOA18 G3 I/O

28 IOA19 G4 I/O

29 IOA20 F2 I/O

30 IOA21 F1 I/O

31 IOALE J1 I/O

32 IOOE# B5 I/O

33 IOWR# J2 I/O

34 IOCS# A5 I/O

35 UWR# K1 I/O

36 URD# K2 I/O

37 UP3_4 L3 I/O

38 INT0# L1 I/O

DIGITAL MISC (5)

1 PRST_ L2 I

Microcontroller address 2 / IO, 2mA, SR, PU, works in

stand-by mode

Microcontroller address 3 / IO, 2mA, SR, PU, works in

stand-by mode

Microcontroller address 4 / IO, 2mA, SR, PU, works in

stand-by mode

Microcontroller address 5 / IO, 2mA, SR, PU, works in

stand-by mode

Microcontroller address 6 / IO, 2mA, SR, PU, works in

stand-by mode

Microcontroller address 7 / IO, 2mA, SR, PU, works in

stand-by mode

2mA, PU, works in stand-by mode

1) Flash address 16

2) GPIO

2mA, PU, works in stand-by mode

1) Flash address 17

2) GPIO

2mA, SR, PD, SMT, works in stand-by mode

1) Flash address 18 / IO

2) GPIO

2mA, SR, PD, SMT, works in stand-by mode

1) Flash address 19 / IO

2) GPIO

2mA, SR, PD, SMT, works in stand-by mode

1) Flash address 20 / IO

2) GPIO

The GPIO function can work in the standby mode

2mA, SR, PD, SMT, works in stand-by mode

1) Flash address 21 / IO, While External FLASH size <=

2MB

2) GPIO

The GPIO function can work in the standby mode

Microcontroller address latch enable, 2mA, PU, SMT, works

in stand-by mode

Flash output enable, active low / IO, 2mA, SR, PU, SMT,

works in stand-by mode

2mA, PU, SMT, works in stand-by mode

1) Flash write enable, active low / IO

2) GPIO

SmA, SR, SMT, works in stand-by mode

1) Flash chip select, active low / IO

2) GPIO

Microcontroller write strobe, active low, 2mA, PU, SMT, works

in stand-by mode

Microcontroller read strobe, active low, 2mA, PU, SMT, works

in stand-by mode

Microcontroller port 3-4, 2mA, PU, SMT, works in stand-by

mode

Microcontroller external interrupt 0, active low, 2mA, PU,

SMT, works in stand-by mode

power on reset

, works in stand-by mode

MT8206

2 ICE M2 I

June, 2006

ICE mode

, works in stand-by mode

Page 28

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT8206

Item Symbol Pin # Type Description

3 PWM0 AD17 I/O

1) GPIO (default, input in initial state), 2mA

2) PWM output 0, 2mA

4 PWM1 AC18 I/O

1) GPIO (default, input in initial state), 2mA

2) PWM output 1, 2mA

5 IR L4 I/O

IR control signal input, 4mA, SR, SMT, works in stand-by

mode

GPIO (23)

1 GPIO0 R1 I/O

2 GPIO1 R2 I/O

(1) GPIO, 2~16mA, SR, SMT

(2) ASDATA4, ch9 and ch10 audio output

(1) GPIO, 2~16mA, SR, SMT

(2) ASDATA5, ch11 and ch12 audio output

3 GPIO2 R3 I/O GPIO, 2~16mA, SR, SMT

4 GPIO3 R4 I/O GPIO, 2~16mA, SR, SMT

5 GPIO4 T4 I/O GPIO, 2~16mA, SR, SMT

6 GPIO5 U1 I/O

7 GPIO6 U2 I/O

8 GPIO7 V1 I/O

9 GPIO8 V2 I/O

10 GPIO9 V3 I/O

(1) GPIO, 2~16mA, SR, SMT

(2) TXD of the 2

(1) GPIO, 2~16mA, SR, SMT

(2) RXD of the 2

GPIO, 2~16mA, SR, SMT

-> Add function: 2

GPIO, 2~16mA, SR, SMT

-> Add function: 2

GPIO, 2~16mA, SR, SMT

-> Add function: 2

nd

RS232 port

nd

RS232 port

nd

digital audio LRCK output

nd

digital audio AOBCK output

nd

digital audio AOMCLK output

11 GPIO10 V4 I/O GPIO, 2~16mA, SR, SMT

12 GPIO11 W1 I/O GPIO, 2~16mA, SR, SMT

13 GPIO12 W2 I/O GPIO, 2~16mA, SR, SMT

14 GPIO13 W3 I/O GPIO, 2~16mA, SR, SMT

15 GPIO14 W4 I/O GPIO, 2~16mA, SR, SMT

16 GPIO15 Y1 I/O GPIO, 2~16mA, SR, SMT

17 GPIO16 Y2 I/O GPIO, 2~16mA, SR, SMT

18 GPIO17 Y3 I/O GPIO, 2~16mA, SR, SMT

19 GPIO18 Y4 I/O GPIO, 2~16mA, SR, SMT

2mA, works in stand-by mode

20 GPIO19 D7 I/O

1) GPIO (default, input in initial state)

2) Monitored pin

2mA, works in stand-by mode

21 UP3_0 A7 I/O

1) GPIO (default, input in initial state)

2) UP30

June, 2006

Page 29

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

3) Monitored pin

2mA, works in stand-by mode

22 UP3_1 B7 I/O

23 UP3_5 C7 I/O

1 FCIDAT T3 I/O

2 FCICLK T1 O

3 FCICMD T2 I/O

Dram Interface (60)

1) GPIO (default, input in initial state)

2) UP31

3) Monitored pin

2mA, works in stand-by mode

1) GPIO (default, input in initial state)

2) UP35

3) Monitored pin

FCI Interface (3)

2~16mA, SR, PU(optional), PD(optional)

1) GPIO (default, input in initial state)

2) SDIO in ms mode or DAT0 in SD mode

2~16mA, SR

1) GPIO (default, input in initial state)

2) MSCLK in ms mode or SDCLK in SD mode

2~16mA, SR, PU(optional), PD(optional)

1) GPIO (default, input in initial state)

2) BS in ms mode or CMD in SD mode

MT8206

1 DQ0 AB1 I/O dram data bus bit 0

2 DQ1 AB2 I/O dram data bus bit 1

3 DQ2 AB3 I/O dram data bus bit 2

4 DQ3 AB4 I/O dram data bus bit 3

5 DQ4 AC1 I/O dram data bus bit 4

6 DQ5 AC2 I/O dram data bus bit 5

7 DQ6 AC3 I/O dram data bus bit 6

8 DQ7 AC4 I/O dram data bus bit 7

9 DQ8 AF1 I/O dram data bus bit 8

10 DQ9 AE2 I/O dram data bus bit 9

11 DQ10 AF2 I/O dram data bus bit 10

12 DQ11 AE3 I/O dram data bus bit 11

13 DQ12 AF3 I/O dram data bus bit 12

14 DQ13 AD4 I/O dram data bus bit 13

June, 2006

Page 30

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

15 DQ14 AE4 I/O dram data bus bit 14

16 DQ15 AF4 I/O dram data bus bit 15

17 DQ16 AC12 I/O dram data bus bit 16

18 DQ17 AD12 I/O dram data bus bit 17

19 DQ18 AE12 I/O dram data bus bit 18

20 DQ19 AF12 I/O dram data bus bit 19

21 DQ20 AC13 I/O dram data bus bit 20

22 DQ21 AD13 I/O dram data bus bit 21

23 DQ22 AE13 I/O dram data bus bit 22

24 DQ23 AF13 I/O dram data bus bit 23

25 DQ24 AD14 I/O dram data bus bit 24

MT8206

26 DQ25 AE15 I/O dram data bus bit 25

27 DQ26 AF16 I/O dram data bus bit 26

28 DQ27 AE16 I/O dram data bus bit 27

29 DQ28 AD16 I/O dram data bus bit 28

30 DQ29 AC16 I/O dram data bus bit 29

31 DQ30 AF17 I/O dram data bus bit 30

32 DQ31 AE17 I/O dram data bus bit 31

33 RA0 AD8 O dram address bus bit 0

34 RA1 AE8 O dram address bus bit 1

35 RA2 AF8 O dram address bus bit 2

36 RA3 AD9 O dram address bus bit 3

37 RA4 AF11 O dram address bus bit 4

38 RA5 AE11 O dram address bus bit 5

39 RA6 AD11 O dram address bus bit 6

40 RA7 AC11 O dram address bus bit 7

41 RA8 AF10 O dram address bus bit 8

June, 2006

Page 31

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

42 RA9 AE10 O dram address bus bit 9

43 RA10 AF7 O dram address bus bit 10

44 RA11 AD10 O dram address bus bit 11

45 RCS_ AF6 O dram chip select

46 RAS_ AE6 O dram row address strobe

47 CAS_ AF5 O dram column address strobe

48 RWE_ AE5 O dram write enable

49 CKE AC10 O dram clock enable

50 RCLKB AF9 dram clock

51 RCLK AE9 dram clock invert

52 DQM0 AD2 data mask 0

MT8206

53 DQM1 AE14 data mask 1

54 BA0 AD7 bank address 0

55 BA1 AE7 bank address 1

56 RVREF AD3 reference voltage

57 DQS0 AD1 data strobe 0

58 DQS1 AE1 data strobe 1

59 DQS2 AF14 data strobe 2

60 DQS3 AF15 data strobe 3

Digital Video Input (31)

Multi-function, 2mA

1 VI0 AF20 IO

2 VI1 AE20 IO

3 VI2 AD20 IO

4 VI3 AF21 IO

(1) GPIO (default, input in initial state)

(2) R[0]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) R[1]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) R[2]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) R[3]

June, 2006

Page 32

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

Multi-function, 2mA

5 VI4 AE21 IO

6 VI5 AD21 IO

7 VI6 AC21 IO

8 VI7 AF22 IO

9 VI8 AE22 IO

10 VI9 AD22 IO

11 VI10 AF23 IO

12 VI11 AE23 IO

13 VI12 AD23 IO

14 VI13 AF24 IO

15 VI14 AE24 IO

16 VI15 AD24 IO

17 VI16 AF25 IO

18 VI17 AF26 IO

(1) GPIO (default, input in initial state)

(2) R[4]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) R[5]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) R[6]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) R[7]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) G[0]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) G[1]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) G[2]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) G[3]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) G[4]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) G[5]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) G[6]

Multi-function, 2mA

(1) GPIO (default, input in initial state)

(2) G[7]

Multi-function, 2mA

(1) B[0]

(2) GPIO

Multi-function, 2mA

(1) B[1]

(2) GPIO

MT8206

June, 2006

Page 33

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

Multi-function, 2mA

19 VI18 AE25 IO

20 VI19 AE26 IO

21 VI20 AD25 IO

22 VI21 AD26 IO

23 VI22 AC25 IO

24 VI23 AC26 IO

(1) B[2]

(2) GPIO

Multi-function, 2mA

(1) B[3]

(2) GPIO

Multi-function, 2mA

(1) B[4]

(2) GPIO

Multi-function, 2mA

(1) B[5]

(2) GPIO

Multi-function, 2mA

(1) B[6]

(2) GPIO

Multi-function, 2mA

(1) B[7]

(2) GPIO

MT8206

25 HSYNC_DVI AD19 H sync, 2mA

26 VSYNC_DVI AF19 V sync, 2mA

27 DE_DVI AC19 Data enable, 2mA

28 VCLK_DVI AE19 Video Clock input, 2mA

29 DE_SOG AE18

30 OUT_27MHZ AD18

31 CEN_DVI AF18

HDMI Interface(7)

1 HDMIMCLK AB26

2 HDMIBCLK AB25

3 HDMILRCK AC24

4 HDMISD0 AA25

5 HDMISD1 AA26

1) GPIO (default, input in initial state)

2) SOG input from external AD

1) GPIO (default, input in initial state)

2) OSC clock output for external chip

1) GPIO (default, input in initial state)

2) Clock enable input from external SCALER

1) GPIO (default, input in initial state)

2) MCLK for HDMI

1) GPIO (default, input in initial state)

2) BCK for HDMI

1) GPIO (default, input in initial state)

2) LRCK for HDMI

1) GPIO (default, input in initial state)

2) CH 1/2 data input for HDMI

1) GPIO (default, input in initial state)

2) CH 3/4 data input for HDMI

June, 2006

Page 34

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

6 HDMISD2 AA23

7 HDMISD3 AA24

CCIR Interface (9)

1) GPIO (default, input in initial state)

2) CH 5/6 data input for HDMI

1) GPIO (default, input in initial state)

2) CH 7/8 data input for HDMI

MT8206

1 CCIR_VCLK W23

2 CCIR_V0 Y26

3 CCIR_V1 Y25

4 CCIR_V2 Y24

5 CCIR_V3 Y23

6 CCIR_V4 W26

7 CCIR_V5 W25

8 CCIR_V6 W24

9 CCIR_V7 V24

1) GPIO (default, input in initial state)

2) CCIR656 clock input from external TVD

1) GPIO (default, input in initial state)

2) CCIR656 data0 input from external TVD

1) GPIO (default, input in initial state)

2) CCIR656 data1 input from external TVD

1) GPIO (default, input in initial state)

2) CCIR656 data2 input from external TVD

1) GPIO (default, input in initial state)

2) CCIR656 data3 input from external TVD

1) GPIO (default, input in initial state)

2) CCIR656 data4 input from external TVD

1) GPIO (default, input in initial state)

2) CCIR656 data5 input from external TVD

1) GPIO (default, input in initial state)

2) CCIR656 data6 input from external TVD

1) GPIO (default, input in initial state)

2) CCIR656 data7 input from external TVD

TTL Interface (4)

1 DE C6 O

2 VSYNCO B6 O Vertical sync, 2mA

3 HSYNCO A6 O Horizontal sync, 2mA

4 VCLK D6 O

1 TP3 C23 I/O Positive PLL group test pin

2 TN3 D22 I/O Negative PLL group test pin

3 PLLVSS1 B23 GND PLL group ground

June, 2006

1) GPIO (default, input in initial state)

2) Data enable, 2mA

Works in stand-by mode

1) GPIO (default, input in initial state)

2) Video output reference clock, 10mA

ANALOG (117)

PLL Group (12)

Page 35

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

4 PLLVDD1 C22 power 1.8v PLL group power

5 PLLVSS2 B22 GND PLL group ground

6 PLLVDD2 C21 power 1.8v PLL group power

7 PLLVSS3 A23 GND PLL group ground

8 PLLVDD3 B21 power 1.8v PLL group power

9 XTALVDD A22 power 1.8v XTAL power

10 XTALO A20 I/O XTAL I/O clock

11 XTALI A21 I/O XTAL I/O clock

12 XTALVSS A19 GND XTAL ground

Servo ADC (8)

1 ADCVSS D21 GND Servo ADC ground

MT8206

2 ADIN4 D20 I

3 ADIN3 C20 I

4 ADIN2 B20 I

5 ADIN1 C19 I

6 ADIN0 B19 I

7 ADCVDD D18 Power Servo ADC power

8 PWM2VREF C18 I/O Servo ADC reference pin

1 SVM B18 O SVM

2 B A18 O Video DAC output

3 DACVSSA D19 GND Video DAC ground

4 G A17 O Video DAC output

1) Servo ADC input

2) GPIO

1) Servo ADC input

2) GPIO

1) Servo ADC input

2) GPIO

1) Servo ADC input

2) GPIO

1) Servo ADC input

2) GPIO

VDAC output (12)

5 DACVDDA C16 power 1.8v Video DAC power (or 2.0v)

6 DACVSSB C17 GND Video DAC ground

7 DACVDDB D16 power 1.8v Video DAC power (or 2.0v)

June, 2006

Page 36

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT8206

Item Symbol Pin # Type Description

8 R B17 O Video DAC output

9 DACVSSC D17 GND Video DAC ground

10 FS A16 I/O Full scale current generation pin

11 DACVREF B16 I/O Reference voltage pin

12 DACVDDC C15 power 1.8v Video DAC power (or 2.0v)

VPLL (5)

1 TP4 A15 I/O Positive VPLL test pin

2 TN4 B15 I/O Negative VPLL test pin

3 VPLLVDD1 D15 power 1.8v VPLL power

4 VPLLVSS D14 GND

1) VPLL ground

5 VPLLVDD2 A13 power 3.3v VPLL power

LVDS (26)

1 LVDDA D13 power 3.3v LVDS power

2 A7P C12 O LVDS Tx positive output of 4th pair of second port

3 A7N D12 O LVDS Tx negative output of 4th pair of second port

4 CK2P C11 O LVDS Tx positive output of clock pair of second port

5 CK2N D11 O LVDS Tx negative output of clock pair of second port

6 LVSSA C14 GND LVDS ground

7 A6P C10 O LVDS Tx positive output of 3rd pair of second port

8 A6N D10 O LVDS Tx negative output of 3rd pair of second port

9 A5P C9 O LVDS Tx positive output of 2nd pair of second port

10 A5N D9 O LVDS Tx negative output of 2nd pair of second port

11 LVDDB C13 power 3.3v LVDS power

st

12 A4P C8 O

1) LVDS Tx positive output of 1

2) LVDS Tx positive output of 5

13 A4N D8 O

1) LVDS Tx negative output of 1

2) LVDS Tx negative output of 5

pair of second port

th

pair of first port (10bit)

st

pair of second port

th

pair of first port (10bit)

14 A3P A12 O LVDS Tx positive output of 4th pair of first port

15 A3N B12 O LVDS Tx negative output of 4th pair of first port

16 LVSSB B14 GND LVDS ground

June, 2006

Page 37

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

17 CK1P A11 O LVDS Tx positive output of clock pair of first port

18 CK1N B11 O LVDS Tx negative output of clock pair of first port

19 A2P A10 O LVDS Tx positive output of 3rd pair of first port

20 A2N B10 O LVDS Tx negative output of 3rd pair of first port

21 LVDDC B13 power 3.3v LVDS power

22 A1P A9 O LVDS Tx positive output of 2nd pair of first port

23 A1N B9 O LVDS Tx negative output of 2nd pair of first port

24 A0P A8 O LVDS Tx positive output of 1st pair of first port

25 A0N B8 O LVDS Tx negative output of 1st pair of first port

26 LVSSC A14 GND LVDS ground

RGB VFE (29)

MT8206

1 HSYNC V26 I VFE Horizontal sync input

2 VSYNC V25 I VFE Vertical sync input

3 AVSS_VFE1 N24 GND RGB Video front end ground

4 BP U25 I

5 BN U26 I Blue- differential input

6 SOG T24 I Sync on Green

7 GP T25 I

8 GN T26 I Green- negative differential input

9 RP R25 I

10 RN R26 I Red- differential input

11 AVDD_VFE1 R23 Power 1.8v RGB video front end power

12 TN1 R24 I/O negative RGB video front end test pin

13 TP1 P23 I/O positive RGB video front end test pin

14 AVSS_VAD1 M24 GND RGB ADC ground

Blue+ differential input (input range: 0.5V~1.5V)

Green+ differential input (input range: 0.5V~1.5V)

Red+ differential input (input range: 0.5V~1.5V)

15 SOY0 P24 I Sync on Y0

16 Y0P P25 I

17 Y0N P26 I Component Y0- differential input

June, 2006

Component Y0+ differential input (input range: 0.5V~1.5V)

Page 38

Î

Î

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

MT8206

18 PB0P N25 I

19 PB0N N26 I Component Pb0- differential input

20 PR0P M25 I

21 PR0N M26 I Component Pr0- differential input

22 SOY1 L24 I Sync on Y1

23 Y1P L25 I

24 Y1N L26 I Component Y1- differential input

25 PB1P K25 I

26 PB1N K26 I Component Pb1- differential input

27 PR1P J25 I

28 PR1N J26 I Component Pr1- differential input

29 AVDD_VAD1 L23 power 1.8v RGB ADC power

1 AV7 G26 I

Component Pb0+ differential input (input range: 0.5V~1.5V)

Component Pr0+ differential input (input range: 0.5V~1.5V)

Component Y1+ differential input (input range: 0.5V~1.5V)

Component Pb1+ differential input (input range: 0.5V~1.5V)

Component Pr1+ differential input (input range: 0.5V~1.5V)

CVBS VFE (14)

AV7 input (input range: 0.5V~1.5V)

2 AV6 G25 I

3 AV5 F26 I AV5 input (input range: 0.5V~1.5V)

4 AV4 F25 I

5 AVSS_VFE0 H23 GND CVBE video front end ground

6 AVDD_VFE0 J23 power 3.3v CVBS video front end power

7 AV3 E26 I

8 AV2 E25 I

9 AV1 D25 I

10 AV0 D26 I

11 AVSS_VAD0 G23 GND CVBE ADC ground

12 REFP F24 I/O

13 REFN G24 I/O

14 AVDD_VAD0 F23 power 3.3v CVBS ADC power

AV6 input (input range: 0.5V~1.5V)

AV4 input (input range: 0.5V~1.5V)

AV 3 input (input range: 0.5V~1.5V)

AV 2 input (input range: 0.5V~1.5V)

AV 1 input (input range: 0.5V~1.5V)

AV0 input (input range: 0.5V~1.5V)

Positive CVBS ADC Voltage Reference

The function changed to SY2

Negative CVBS ADC Voltage Reference

The function changed to SC2

June, 2006

Page 39

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # Type Description

Audio FE (6)

1 AADCVDD E24 Power 3.3v Audio front end power

2 MPX1 B26 I Audio Frequency input0

3 MPX2 C26 I Audio Frequency input1

4 AADCVSS D24 GND Audio front end ground

5 TN2 C25 I/O negative Audio ADC reference pin

MT8206

6 TP2 B25 I/O

1 ADACVDD C24 Power 3.3v Audio front end power

2 ACENT B24 I/O

3 AVICM A24 Audio DAC input common voltage

4 AL A25 I/O

5 AR A26 I/O

6 ADACVSS D23 GND Video ADC Voltage Reference N0

1) positive Audio ADC reference pin

2) bypass CVBS video output pin

Audio DAC (6)

1) Audio DAC output

2) I2S , ASDATA2

3) GPIO

1) Audio DAC output

2) I2S , ASDATA0

3) GPIO

1) Audio DAC output

2) I2S , ASDATA1

3) GPIO

4.2 NOTICES ABOUT GPIOS:

There are considerably various I/O pins provided by MT8206EG, but some of them are shared by

other function, here we notice some conditions when you use.

When GPIO have to active in power saving mode

1. GPIOs in Stand by mode means UP30, UP31, UP34 and UP35 can be used.

2. Servo ADs can be also used when power saving mode

3. GPIOs which are sharing with servo AD can be also used when power saving mode.

GPIO use DE pin

DE pin is also use for trapping when VGA download have to use. So DE pin should be used carefully.

June, 2006

Page 40

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT8206

When you use DE as GPIO, it is highly recommended that DE can not pull high.

BLOCK DIAGRAM

4.3

(see Next Page)

June, 2006

Page 41

(^6

(^6

(^6

(^6

69

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

6 9

(^6

(^6

69

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

69

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

69

(^6

69

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

69

(^6

(^6

(^6

(^6

(^6

(^6(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

69

(^6

(^6

(^6

9

(^6

9

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

69

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6 (^6

(^6

(^6

(^6

9

9

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

69

9

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

(^69(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

6 9

9

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

6 9

(^6

(^6

(^6

6 9

9

(^6

(^6

9

9

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

6 9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

8 ! 0

9

8

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6(^6(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

9

9

(^6

(^6

(^6

(^6

(^6

6 9

9

(^6

(^6

(^6

(^6

(^6

(^6

69

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

9

9

(^6

(^6

6 9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

6 9

(^6

(^6

(^6

9

(^6

9

9

9

yl 1P 3

OSURE 0

(^6

(^6

6 9

(^6

(^6

6 9

6 9

(^6

(^6

6 9

(^6

6 9

(^6

6 9

(^6

9

(^6

6 9

(^6

6 9

(^6

6 9

(^6

6 9

(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

6 9

(^6

6 9

(^6

6 9

(^6

6 9

(^6

6 9

(^6

9

(^6

9

(^6

6 9

(^6

9

9

yl 1P 3h^6

OSURURE

(^6

(^6

6 9

(^6

(^6

(^6

9

9

(^6

9

(^6

(^6

6 9

(^6

(^6

6 9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

9

(^6

(^6

9

(^6

8

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6 (^6 (^6

(^6

(^6

(^6

9

(^6

9

(^6

(^6

(^6

(^6(^6

(^6

(^6

(^6(^6

(^6

(^6

(^6

(^6

9

9

(^6

(^6

9

(^6

(^6

9

9

9

9 9

(^6

(^6

9 9

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

6 9

(^6

(^6

6 9

(^6

(^6

(^6

(^6 (^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

6 9

(^6

(^6

6 9

(^6

(^69(^6

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

6 9

9

(^6

6 9

9

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

(^6

9

(^6

(^6

(^6

9

(^6

9

(^6

9

(^6

9

69

9

9

9

69

9

69

9

9969

9

9

9

(^6

(^6

(^6

(^6

9

(^6

(^6

9

9

9

(^6

9

(^6

(^6

(^6

9

6 9

9

(^6

E ( G}?

? ! Q

(^6

(^6

9

8 ! 0

9 3

(^6

9

(^69(^69(^6

MT8206

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

yyly

?

y

June, 2006

Page 42

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT8206

5. Video Configuration

CVBS/SV Input Switch, S-first Function

We have 8 CVBS/SV input pins for arbitrary order of customers’ demand. Because there is only 1 TV decoder in MT8206G,

there is only one set (CVBS or SV) through the input pins. However, we can support S-first function without any external

circuits.

CVBS Bypass Output

The pin “TP2 “ can only output the CVBS signal of the chosen input but SV input.

INTERNAL VIDEO SWITCH

Main Path

CVBS / S video (Total

Source

CVBS / S video

(Total 8 input pins)

PIP

path

z Above table is the PIP/POP table if we do not use any extern input switch.

z If video goes through DVI port, then PIP/POP case will not be limited to AD numbers.

Digital Input Pin Swap Selection

YPbPr

RGB

Digital port (DVI /

HDMI / CCIR656 /

CCIR601)

8 input pins)

YPbPr RGB

X

For layout conveniently, 8206 can flexibly swap input pin:

1. If VI0~VI23 configure as 24-bits R/G/B or CB/Y/CR mode -->

8206 can do B/R or CB/CR bus swap or MSB/LSB swap.

Digital port (DVI / HDMI

/ CCIR 656 / CCIR601)

X

2. If VI8~VI23 configure as 16-bits CBCR/Y mode -->

8206 can do B/R or CB/CR bus swap or MSB/LSB swap

3. If VI16~VI23 or VI8~VI15 configure as 8-bits mode -->

June, 2006

Page 43

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

MT8206

8206 can do VI16~VI23/VI16~VI23 two bus swap or MSB/LSB swap.

4. We have second port dedicated for 8-bit ITU656 digital video format.

Clock Spread Spectrum

1. Up-down 2 directions spread spectrum

2. SS frequency: 10Hz~100Hz

3. SS percentage: 0%~5%, 8 bits resolution.

4. Output clock and DRAM clock all available.

6. Audio Configuration

Digital Audio Input Pin Configuration

* Note that there are different input pin configurations for MT8206G on master and slave clock modes.

Master Mode

Description

Data input LIN HDMISD0

Master clock AOMCLK HDMIMCLK

L/R clock AOLRCK HDMILRLK

Bit clock AOBCK HDMIBCLK

Extension Data input 1 HDMISD1 HDMISD1

Extension Data input 2 HDMISD2 HDMISD2

Extension Data input 3 HDMISD3 HDMISD3

Digital Audio Output Mapping Rule

Item Symbol Pin # IO Description: Output Type

1 AOSDATA0 O Audio out data 0: Speaker / AV_LR / Bypass Out

(MT8206G is Master clock

mode)

(MT8206G is Slave clock mode)

Slave Mode

2 AOSDATA1 O Audio out data 1: Speaker / AV_LR / Headphone

3 AOSDATA2 O Audio out data 2: Center(L) / Subwoofer(R)

June, 2006

Page 44

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE MTK CONFIDENTIAL, NO DISCLOSURE

Item Symbol Pin # IO Description: Output Type

4 AOSDATA3 O Audio out data 3: Speaker / AV_LR / Bypass Out / 5.1ch_LS_RS

5 AOSDATA4 I/O Audio out data 4: 7.1ch_LC_RC