Page 1

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

Data Manual

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Literature Number: SCPS183A

October 2007 – Revised March 2008

Page 2

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

www.ti.com

Contents

1 Introduction ....................................................................................................................... 13

1.1 XIO2213A Features ........................................................................................................ 13

2 Overview ........................................................................................................................... 14

2.1 Description .................................................................................................................. 14

2.2 Related Documents ........................................................................................................ 16

2.3 Trademarks ................................................................................................................. 16

2.4 Documents Conventions .................................................................................................. 16

2.5 Ordering Information ....................................................................................................... 17

2.6 Terminal Assignments ..................................................................................................... 17

2.7 Terminal Descriptions ...................................................................................................... 21

3 Feature/Protocol Descriptions .............................................................................................. 29

3.1 Power-Up/-Down Sequencing ............................................................................................ 29

3.1.1 Power-Up Sequence ............................................................................................ 30

3.1.2 Power-Down Sequence ......................................................................................... 31

3.2 XIO2213A Reset Features ................................................................................................ 31

3.3 PCI Express Interface ..................................................................................................... 32

3.3.1 External Reference Clock ...................................................................................... 32

3.3.2 Beacon and Wake ............................................................................................... 32

3.3.3 Initial Flow Control Credits ..................................................................................... 32

3.3.4 PCI Express Message Transactions .......................................................................... 33

3.4 PCI Interrupt Conversion to PCI Express Messages .................................................................. 34

3.5 Two-Wire Serial-Bus Interface ............................................................................................ 34

3.5.1 Serial-Bus Interface Implementation .......................................................................... 34

3.5.2 Serial-Bus Interface Protocol ................................................................................... 35

3.5.3 Serial-Bus EEPROM Application .............................................................................. 37

3.5.4 Accessing Serial-Bus Devices Through Softwaree ......................................................... 39

3.6 Advanced Error Reporting Registers .................................................................................... 40

3.7 Data Error Forwarding Capability ........................................................................................ 40

3.8 General-Purpose I/O Interfacee .......................................................................................... 40

3.9 Set Slot Power Limit Functionality ....................................................................................... 40

3.10 PCI Express and PCI Bus Power Management ........................................................................ 41

3.11 1394b OHCI Controller Functionality .................................................................................... 42

3.11.1 1394b OHCI Power Management ............................................................................. 42

3.11.2 1394b OHCI and V

3.11.3 1394b OHCI and Reset Options ............................................................................... 42

3.11.4 1394b OHCI PCI Bus Master .................................................................................. 42

3.11.5 1394b OHCI Subsystem Identification ........................................................................ 43

3.11.6 1394b OHCI PME Support ..................................................................................... 43

4 Classic PCI Configuration Space .......................................................................................... 44

4.1 Vendor ID Register ......................................................................................................... 45

4.2 Device ID Register ......................................................................................................... 45

4.3 Command Register ........................................................................................................ 45

4.4 Status Register ............................................................................................................. 47

4.5 Class Code and Revision ID Register ................................................................................... 48

4.6 Cache Line Size Register ................................................................................................. 48

4.7 Primary Latency Timer Register .......................................................................................... 48

4.8 Header Type Register ..................................................................................................... 49

4.9 BIST Register ............................................................................................................... 49

4.10 Device Control Base Address Register ................................................................................. 49

4.11 Scratchpad RAM Base Address .......................................................................................... 49

.......................................................................................... 42

AUX

Contents 2 Submit Documentation Feedback

Page 3

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

4.12 Primary Bus Number Register ............................................................................................ 50

4.13 Secondary Bus Number Register ........................................................................................ 50

4.14 Subordinate Bus Number Register ...................................................................................... 50

4.15 Secondary Latency Timer Register ...................................................................................... 51

4.16 I/O Base Register .......................................................................................................... 52

4.17 I/O Limit Register ........................................................................................................... 52

4.18 Secondary Status Register ................................................................................................ 53

4.19 Memory Base Register .................................................................................................... 54

4.20 Memory Limit Register ..................................................................................................... 54

4.21 Prefetchable Memory Base Register .................................................................................... 54

4.22 Prefetchable Memory Limit Register ..................................................................................... 55

4.23 Prefetchable Base Upper 32 Bits Register .............................................................................. 55

4.24 Prefetchable Limit Upper 32 Bits Register .............................................................................. 55

4.25 I/O Base Upper 16 Bits Register ......................................................................................... 56

4.26 I/O Limit Upper 16 Bits Register .......................................................................................... 56

4.27 Capabilities Pointer Register .............................................................................................. 56

4.28 Interrupt Line Register ..................................................................................................... 57

4.29 Interrupt Pin Register ...................................................................................................... 57

4.30 Bridge Control Register .................................................................................................... 58

4.31 Capability ID Register ...................................................................................................... 60

4.32 Next Item Pointer Register ................................................................................................ 60

4.33 Power Management Capabilities Register .............................................................................. 60

4.34 Power Management Control/Status Register ........................................................................... 61

4.35 Power Management Bridge Support Extension Register ............................................................. 61

4.36 Power Management Data Register ...................................................................................... 62

4.37 MSI Capability ID Register ................................................................................................ 62

4.38 Next Item Pointer Register ................................................................................................ 62

4.39 MSI Message Control Register ........................................................................................... 63

4.40 MSI Message Lower Address Register ................................................................................. 63

4.41 MSI Message Upper Address Register ................................................................................. 64

4.42 MSI Message Data Register .............................................................................................. 64

4.43 Capability ID Register ...................................................................................................... 65

4.44 Next Item Pointer Register ............................................................................................... 65

4.45 Subsystem Vendor ID Register ........................................................................................... 65

4.46 Subsystem ID Register .................................................................................................... 65

4.47 PCI Express Capability ID Register ...................................................................................... 65

4.48 Next Item Pointer Register ................................................................................................ 66

4.49 PCI Express Capabilities Register ....................................................................................... 66

4.50 Device Capabilities Register .............................................................................................. 67

4.51 Device Control Register ................................................................................................... 68

4.52 Device Status Register .................................................................................................... 69

4.53 Link Capabilities Register ................................................................................................. 70

4.54 Link Control Register ...................................................................................................... 71

4.55 Link Status Register ........................................................................................................ 72

4.56 Serial-Bus Data Register .................................................................................................. 72

4.57 Serial-Bus Word Address Register ....................................................................................... 72

4.58 Serial-Bus Slave Address Register ..................................................................................... 73

4.59 Serial-Bus Control and Status Register ................................................................................. 73

4.60 GPIO Control Register ..................................................................................................... 75

4.61 GPIO Data Register ........................................................................................................ 76

4.62 Control and Diagnostic Register 0 ....................................................................................... 77

4.63 Control and Diagnostic Register 1 ....................................................................................... 78

4.64 PHY Control and Diagnostic Register 2 ................................................................................. 80

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

Contents 3

Page 4

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

4.65 Subsystem Access Register .............................................................................................. 80

4.66 General Control Register .................................................................................................. 81

4.67 TI Proprietary Register .................................................................................................... 83

4.68 TI Proprietary Register .................................................................................................... 83

4.69 TI Proprietary Register ..................................................................................................... 84

4.70 Arbiter Control Register ................................................................................................... 85

4.71 Arbiter Request Mask Registert .......................................................................................... 86

4.72 Arbiter Time-Out Status Register ........................................................................................ 86

4.73 TI Proprietary Register ..................................................................................................... 87

4.74 TI Proprietary Register .................................................................................................... 87

4.75 TI Proprietary Register ..................................................................................................... 87

5 PCI Express Extended Configuration Space .......................................................................... 89

5.1 Advanced Error Reporting Capability ID Register ..................................................................... 89

5.2 Next Capability Offset/Capability Version Register .................................................................... 89

5.3 Uncorrectable Error Status Register ..................................................................................... 91

5.4 Uncorrectable Error Mask Register ...................................................................................... 91

5.5 Uncorrectable Error Severity Register ................................................................................... 93

5.6 Correctable Error Status Register ........................................................................................ 94

5.7 Correctable Error Mask Register ......................................................................................... 95

5.8 Advanced Error Capabilities and Control Register ..................................................................... 96

5.9 Header Log Register ....................................................................................................... 96

5.10 Secondary Uncorrectable Error Status Register ....................................................................... 97

5.11 Secondary Uncorrectable Error Mask Register ........................................................................ 98

5.12 Secondary Uncorrectable Error Severity ................................................................................ 99

5.13 Secondary Error Capabilities and Control Register .................................................................. 100

5.14 Secondary Header Log Register ........................................................................................ 101

6 Memory-Mapped TI Proprietary Register Space .................................................................... 102

6.1 Device Control Map ID Register ........................................................................................ 102

6.2 Revision ID Register ...................................................................................................... 103

6.3 GPIO Control Register ................................................................................................... 103

6.4 GPIO Data Register ...................................................................................................... 104

6.5 Serial-Bus Data Register ................................................................................................ 105

6.6 Serial-Bus Word Address Register ..................................................................................... 105

6.7 Serial-Bus Slave Address Register .................................................................................... 105

6.8 Serial-Bus Control and Status Register ................................................................................ 105

7 1394 OHCI—PCI Configuration Space ................................................................................. 107

7.1 Vendor ID Register ....................................................................................................... 108

7.2 Device ID Register ........................................................................................................ 108

7.3 Command Register ....................................................................................................... 108

7.4 Status Register ............................................................................................................ 109

7.5 Class Code and Revision ID Register ................................................................................. 110

7.6 Cache Line Size and Latency Timer Register ........................................................................ 110

7.7 Header Type and BIST Register ........................................................................................ 111

7.8 OHCI Base Address Register ........................................................................................... 111

7.9 TI Extension Base Address Register ................................................................................... 112

7.10 CIS Base Address Register ............................................................................................. 113

7.11 CIS Pointer Register ...................................................................................................... 113

7.12 Subsystem Identification Register ...................................................................................... 113

7.13 Power Management Capabilities Pointer Register ................................................................... 114

7.14 Interrupt Line and Pin Register ......................................................................................... 114

7.15 MIN_GNT and MAX_LAT Register ..................................................................................... 114

7.16 OHCI Control Register ................................................................................................... 115

www.ti.com

Contents 4 Submit Documentation Feedback

Page 5

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

7.17 Capability ID and Next Item Pointer Registers ....................................................................... 115

7.18 Power Management Capabilities Register ............................................................................ 116

7.19 Power Management Control and Status Register .................................................................... 116

7.20 Power Management Extension Registers ............................................................................. 117

7.21 PCI Miscellaneous Configuration Register ............................................................................ 118

7.22 Link Enhancement Control Register ................................................................................... 119

7.23 Subsystem Access Register ............................................................................................. 121

8 1394 OHCI Memory-Mapped Register Space ........................................................................ 122

8.1 OHCI Version Register ................................................................................................... 124

8.2 GUID ROM Register ..................................................................................................... 125

8.3 Asynchronous Transmit Retries Register .............................................................................. 126

8.4 CSR Data Register ...................................................................................................... 126

8.5 CSR Compare Register .................................................................................................. 127

8.6 CSR Control Register .................................................................................................... 127

8.7 Configuration ROM Header Register ................................................................................... 127

8.8 Bus Identification Register ............................................................................................... 128

8.9 Bus Options Register ..................................................................................................... 128

8.10 GUID High Register ...................................................................................................... 129

8.11 GUID Low Register ....................................................................................................... 130

8.12 Configuration ROM Mapping Register ................................................................................. 130

8.13 Posted Write Address Low Register ................................................................................... 130

8.14 Posted Write Address High Register ................................................................................... 131

8.15 Vendor ID Register ....................................................................................................... 131

8.16 Host Controller Control Register ........................................................................................ 131

8.17 Self-ID Buffer Pointer Register .......................................................................................... 133

8.18 Self-ID Count Register ................................................................................................... 133

8.19 Isochronous Receive Channel Mask High Register .................................................................. 134

8.20 Isochronous Receive Channel Mask Low Register .................................................................. 135

8.21 Interrupt Event Register .................................................................................................. 135

8.22 Interrupt Mask Register .................................................................................................. 137

8.23 Isochronous Transmit Interrupt Event Register ....................................................................... 139

8.24 Isochronous Transmit Interrupt Mask Register ....................................................................... 139

8.25 Isochronous Receive Interrupt Event Register ........................................................................ 140

8.26 Isochronous Receive Interrupt Mask Register ........................................................................ 140

8.27 Initial Bandwidth Available Register .................................................................................... 141

8.28 Initial Channels Available High Register ............................................................................... 141

8.29 Initial Channels Available Low Register ............................................................................... 142

8.30 Fairness Control Register ................................................................................................ 143

8.31 Link Control Register ..................................................................................................... 144

8.32 Node Identification Register ............................................................................................. 145

8.33 PHY Layer Control Register ............................................................................................. 146

8.34 Isochronous Cycle Timer Register ..................................................................................... 147

8.35 Asynchronous Request Filter High Register ......................................................................... 148

8.36 Asynchronous Request Filter Low Register ........................................................................... 150

8.37 Physical Request Filter High Register ................................................................................. 151

8.38 Physical Request Filter Low Register .................................................................................. 153

8.39 Physical Upper Bound Register (Optional Register) ................................................................. 153

8.40 Asynchronous Context Control Register ............................................................................... 154

8.41 Asynchronous Context Command Pointer Register .................................................................. 155

8.42 Isochronous Transmit Context Control Register ...................................................................... 156

8.43 Isochronous Transmit Context Command Pointer Register ......................................................... 157

8.44 Isochronous Receive Context Control Register ....................................................................... 157

8.45 Isochronous Receive Context Command Pointer Register ......................................................... 158

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

Contents 5

Page 6

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

8.46 Isochronous Receive Context Match Register ........................................................................ 159

9 1394 OHCI Memory-Mapped TI Extension Register Space ...................................................... 160

9.1 DV and MPEG2 Timestamp Enhancements .......................................................................... 160

9.2 Isochronous Receive Digital Video Enhancements .................................................................. 160

9.3 Isochronous Receive Digital Video Enhancements Register ....................................................... 161

9.4 Link Enhancement Register ............................................................................................. 162

9.5 Timestamp Offset Register .............................................................................................. 164

10 PHY Section .................................................................................................................... 165

10.1 PHY Section Register Configuration ................................................................................... 166

10.2 PHY Section Application Information ................................................................................... 172

10.2.1 Power Class Programming ................................................................................... 172

10.2.2 Power-Up Reset ................................................................................................ 172

10.2.3 Crystal Oscillator Selection ................................................................................... 172

10.2.4 Bus Reset ....................................................................................................... 173

11 Electrical Characteristics ................................................................................................... 175

11.1 Absolute Maximum Ratings ............................................................................................. 175

11.2 Recommended Operating Conditions .................................................................................. 175

11.3 PCI Express Differential Transmitter Output Ranges ................................................................ 175

11.4 PCI Express Differential Receiver Input Ranges ..................................................................... 177

11.5 PCI Express Differential Reference Clock Input Ranges ............................................................ 178

11.6 Electrical Characteristics Over Recommended Operating Conditions (3.3-V I/O) ............................... 178

11.7 Electrical Characteristics Over Recommended Operating Conditions (PHY Port Driver) ...................... 179

11.8 Switching Characteristics for PHY Port Driver ....................................................................... 179

11.9 Electrical Characteristics Over Recommended Operating Conditions PHY Port Receiver .................... 180

11.10 Jitter/Skew Characteristics for 1394a PHY Port Receiver ......................................................... 180

11.11 Operating, Timing, and Switching Characteristics of XI ............................................................ 180

11.12 Electrical Characteristics Over Recommended Operating Conditions (1394a Miscellaneous I/O) ........... 180

12 Glossary .......................................................................................................................... 181

13 Mechanical Data ............................................................................................................... 182

Important Notices ...................................................................................................................... 183

www.ti.com

Contents 6 Submit Documentation Feedback

Page 7

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

List of Figures

3-1 XIO2213A Block Diagram ........................................................................................................ 29

3-2 Power-Up Sequence .............................................................................................................. 30

3-3 Power-Down Sequence .......................................................................................................... 31

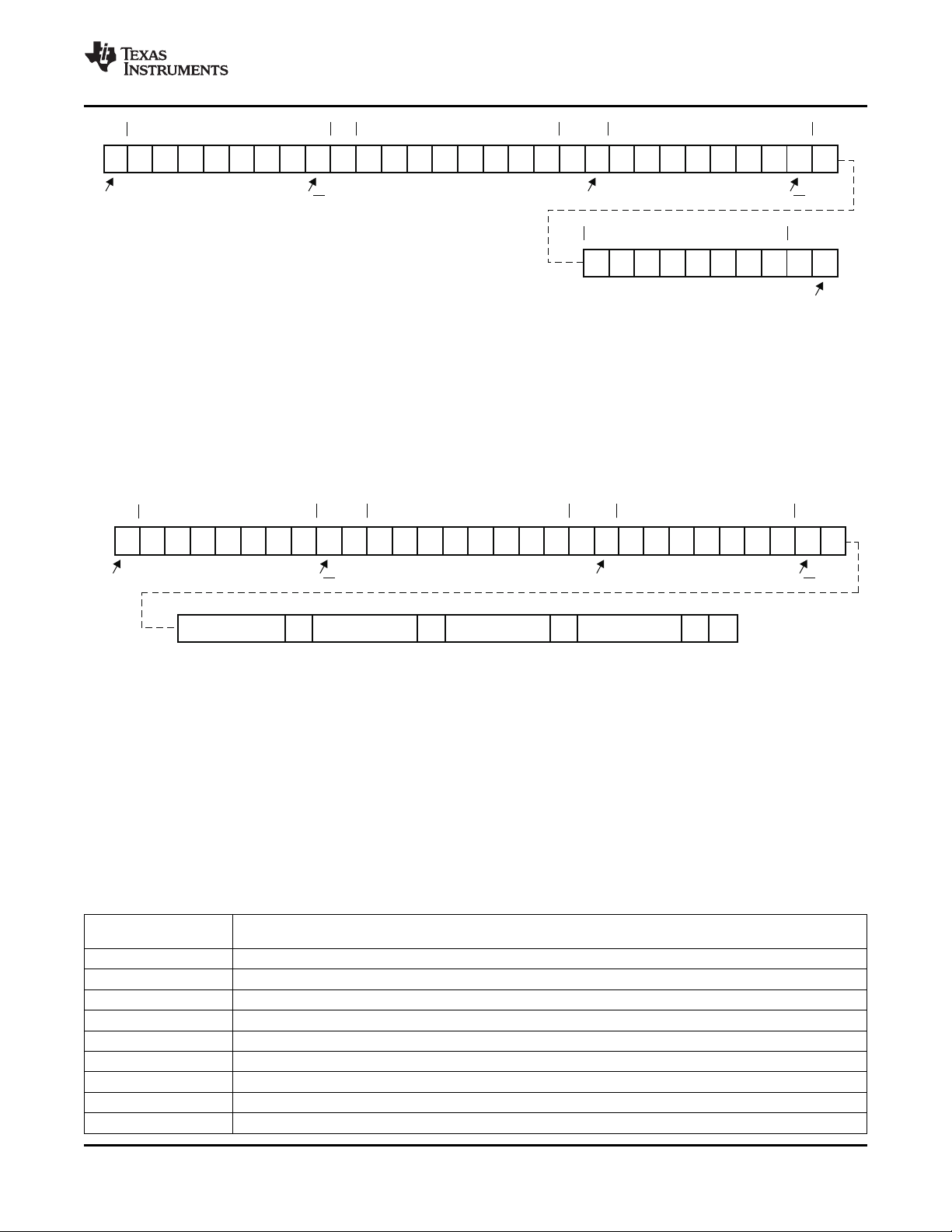

3-4 PCI Express ASSERT_INTA Message ......................................................................................... 34

3-5 PCI Express DEASSERT_INTX Message ..................................................................................... 34

3-6 Serial EEPROM Application ..................................................................................................... 35

3-7 Serial-Bus Start/Stop Conditions and Bit Transfers .......................................................................... 35

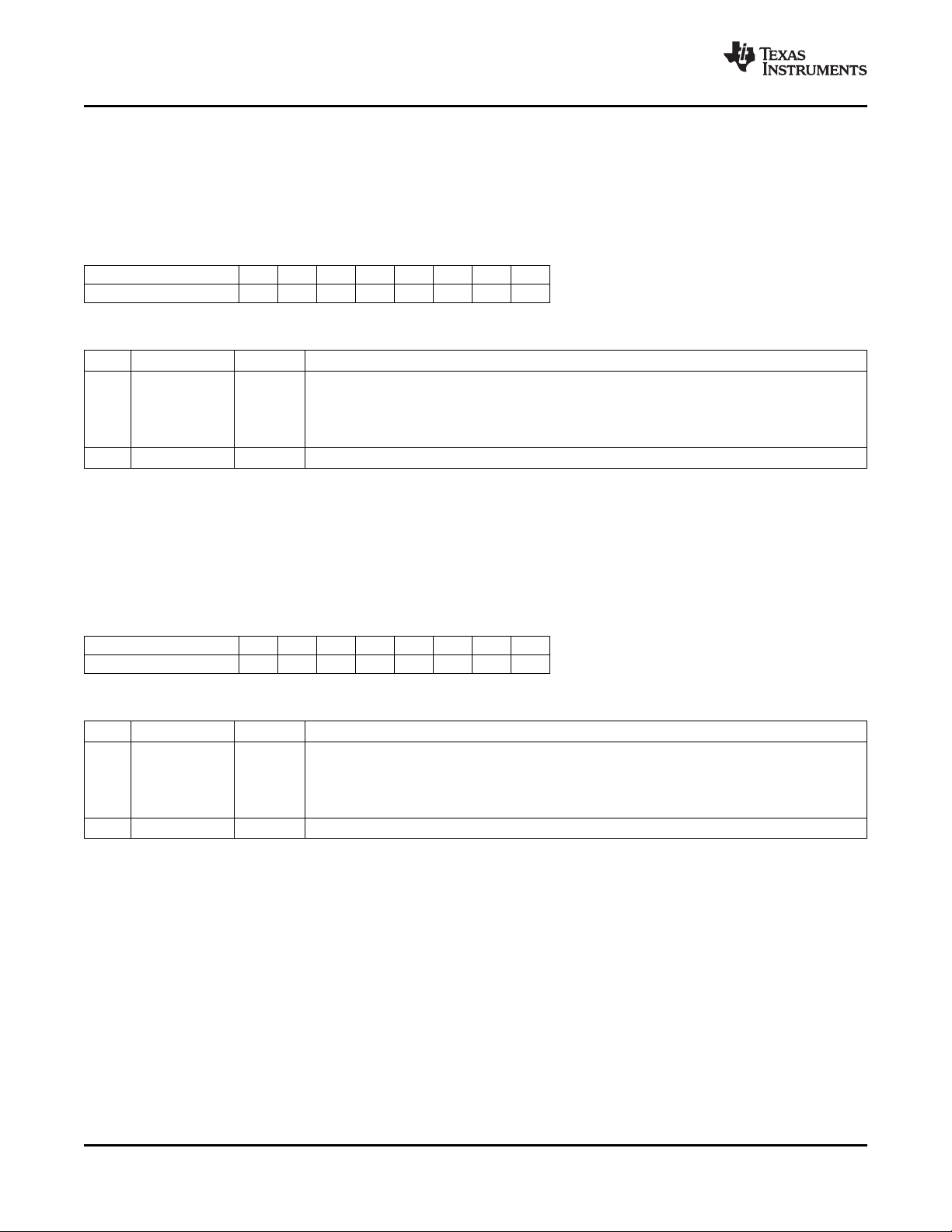

3-8 Serial-Bus Protocol Acknowledge ............................................................................................... 36

3-9 Serial-Bus Protocol – Byte Write ................................................................................................ 36

3-10 Serial-Bus Protocol – Byte Read ................................................................................................ 37

3-11 Serial-Bus Protocol – Multibyte Read .......................................................................................... 37

11-1 Test Load Diagram .............................................................................................................. 179

List of Figures 7

Page 8

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

www.ti.com

List of Tables

2-1 XIO2213AZAY_12x12 Terminals Sorted Alphanumerically ................................................................. 18

2-2 XIO2213AZAY_12x12 Signals Sorted Alphanumerically .................................................................... 20

2-3 Power Supply Terminals ......................................................................................................... 23

2-4 Ground Terminals ................................................................................................................. 23

2-5 PCI Express Terminals ........................................................................................................... 24

2-6 Clock Terminals ................................................................................................................... 24

2-7 1394 Terminals .................................................................................................................... 24

2-8 Reserved Terminals .............................................................................................................. 27

2-9 Miscellaneous Terminals ......................................................................................................... 27

3-1 XIO2213A Reset Options ........................................................................................................ 31

3-2 Initial Flow Control Credit Advertisements ..................................................................................... 32

3-3 Messages Supported byf the Bridge ........................................................................................... 33

3-4 EEPROM Register Loading Map ................................................................................................ 37

3-5 Registers Used To Program Serial-Bus Devices ............................................................................. 39

3-6 Clocking In Low Power States ................................................................................................... 41

3-7 1394b OHCI Configuration Register Map ...................................................................................... 42

3-8 1394 OHCI Memory Command Options ....................................................................................... 43

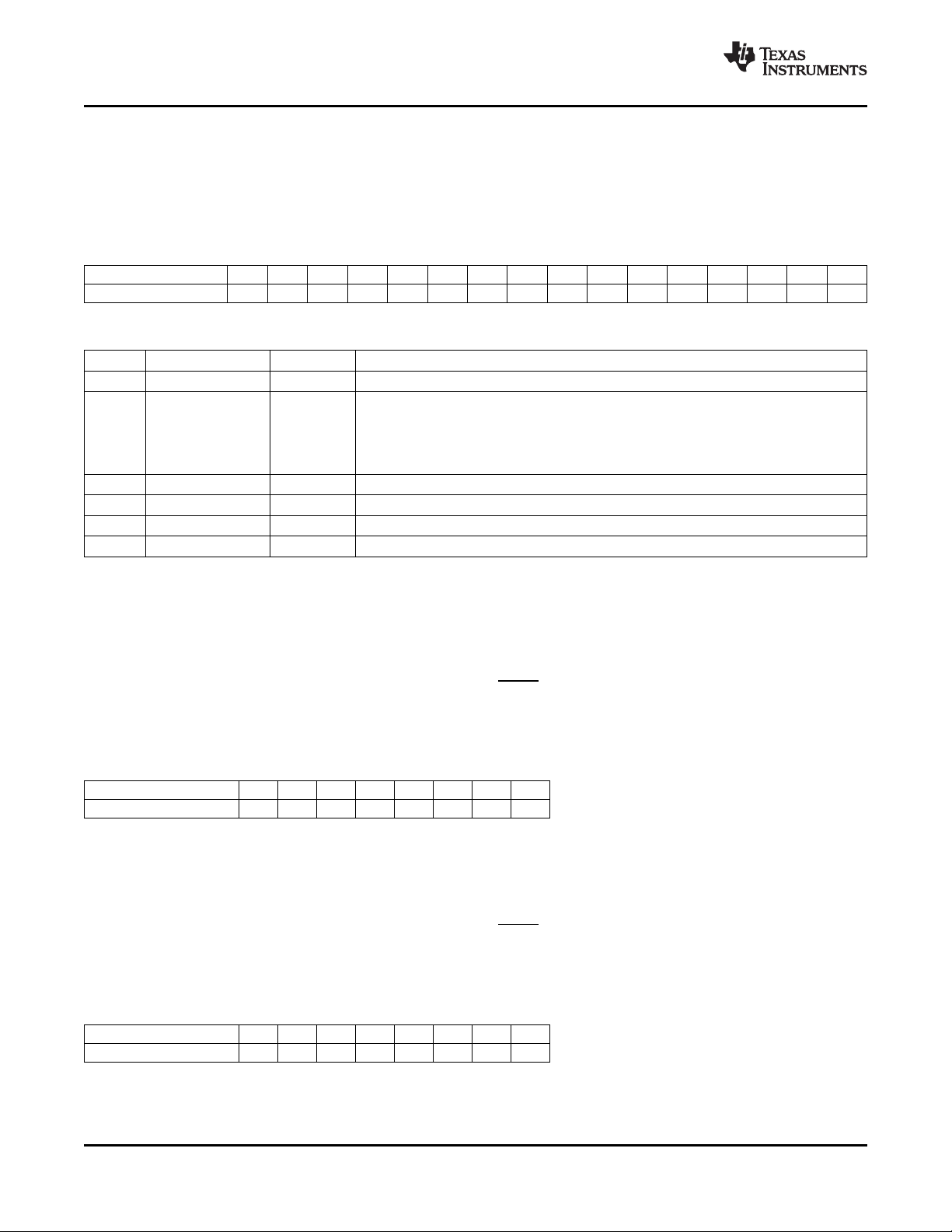

4-1 Classic PCI Configuration Register Map ....................................................................................... 44

4-2 Command Register Description ................................................................................................. 46

4-3 Status Register Description ...................................................................................................... 47

4-4 Class Code and Revision ID Register Description ........................................................................... 48

4-5 Device Control Base Address Register Description .......................................................................... 49

4-6 Device Control Base Address Register Description .......................................................................... 50

4-7 I/O Base Register Description ................................................................................................... 52

4-8 I/O Limit Register Description ................................................................................................... 52

4-9 Secondary Status Register Description ........................................................................................ 53

4-10 Memory Base Register Description ............................................................................................. 54

4-11 Memory Limit Register Description ............................................................................................. 54

4-12 Prefetchable Memory Base Register Description ............................................................................. 54

4-13 Prefetchable Memory Limit Register Description ............................................................................. 55

4-14 Prefetchable Base Upper 32 Bits Register Description ...................................................................... 55

4-15 Prefetchable Limit Upper 32 Bits Register Description ....................................................................... 56

4-16 I/O Base Upper 16 Bits Register Description .................................................................................. 56

4-17 I/O Limit Upper 16 Bits Register Description .................................................................................. 56

4-18 Bridge Control Register Description ............................................................................................ 58

4-19 Power Management Capabilities Register Description ...................................................................... 60

4-20 Power Management Control/Status Register Description ................................................................... 61

4-21 PM Bridge Support Extension Register Description .......................................................................... 62

4-22 MSI Message Control Register Description ................................................................................... 63

List of Tables8 Submit Documentation Feedback

Page 9

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

4-23 MSI Message Lower Address Register Description .......................................................................... 64

4-24 MSI Message Data Register Description ...................................................................................... 64

4-25 PCI Express Capabilities Register Description ................................................................................ 66

4-26 Device Capabilities Register Description ...................................................................................... 67

4-27 Device Control Register Description ............................................................................................ 68

4-28 Device Status Register Description ............................................................................................. 69

4-29 Link Capabilities Register Description .......................................................................................... 70

4-30 Link Control Register Description ............................................................................................... 71

4-31 Link Status Register Description ................................................................................................ 72

4-32 Serial-Bus Slave Address Register Descriptions ............................................................................. 73

4-33 Serial-Bus Control and Status Register Description .......................................................................... 73

4-34 GPIO Control Register Description ............................................................................................. 75

4-35 GPIO Data Register Description ................................................................................................ 76

4-36 Control and Diagnostic Register 0 Description ............................................................................... 77

4-37 Control and Diagnostic Register 1 Description ............................................................................... 78

4-38 Control and Diagnostic Register 2 Description ............................................................................... 80

4-39 Subsystem Access Register Description ....................................................................................... 81

4-40 General Control Register Description .......................................................................................... 81

4-41 Arbiter Control Register Description ............................................................................................ 85

4-42 Arbiter Request Mask Register Description ................................................................................... 86

4-43 Arbiter Time-Out Status Register Description ................................................................................. 86

5-1 PCI Express Extended Configuration Register Map .......................................................................... 89

5-2 Uncorrectable Error Status Register Description ............................................................................. 91

5-3 Uncorrectable Error Mask Register Description ............................................................................... 92

5-4 Uncorrectable Error Severity Register Description ........................................................................... 93

5-5 Correctable Error Status Register Description ................................................................................ 94

5-6 Correctable Error Mask Register Description ................................................................................. 95

5-7 Advanced Error Capabilities and Control Register Description ............................................................. 96

5-8 Secondary Uncorrectable Error Status Register Description ................................................................ 97

5-9 Secondary Uncorrectable Error Mask Register Description ................................................................. 98

5-10 Secondary Uncorrectable Error Severity Register Description ............................................................. 99

5-11 Secondary Error Capabilities and Control Register Description ........................................................... 100

5-12 Secondary Header Log Register Description ................................................................................ 101

6-1 Device Control Memory Window Register Map ............................................................................. 102

6-2 GPIO Control Register Description ............................................................................................ 103

6-3 GPIO Data Register Description ............................................................................................... 104

6-4 Serial-Bus Slave Address Register Descriptions ............................................................................ 105

6-5 Serial-Bus Control and Status Register Description ........................................................................ 106

7-1 1394 OHCI Configuration Register Map ...................................................................................... 107

7-2 Command Register Description ................................................................................................ 108

7-3 Status Register Description .................................................................................................... 109

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

List of Tables 9

Page 10

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

7-4 Class Code and Revision ID Register Description .......................................................................... 110

7-5 Latency Timer and Class Cache Line Size Register Description ......................................................... 111

7-6 Header Type and BIST Register Description ............................................................................... 111

7-7 OHCI Base Address Register Description .................................................................................... 112

7-8 TI Base Address Register Description ........................................................................................ 112

7-9 Subsystem Identification Register Description ............................................................................... 113

7-10 Interrupt Line and Pin Registers Description ................................................................................. 114

7-11 MIN_GNT and MAX_LAT Register Description ............................................................................. 115

7-12 OHCI Control Register Descriptioni ........................................................................................... 115

7-13 Capability ID and Next Item Pointer Registers Description ................................................................ 115

7-14 Interrupt Line and Pin Registers Description ................................................................................. 116

7-15 Power Management Control and Status Register Description ............................................................ 116

7-16 Power Management Extension Registers Description ...................................................................... 117

7-17 Miscellaneous Configuration Register ........................................................................................ 118

7-18 Link Enhancement Control Register Description ............................................................................ 120

7-19 Subsystem Access Register Description ..................................................................................... 121

8-1 OHCI Register Map ............................................................................................................. 122

8-2 OHCI Version Register Description ........................................................................................... 124

8-3 GUID ROM Register Description .............................................................................................. 125

8-4 Asynchronous Transmit Retries Register Description ...................................................................... 126

8-5 CSR Control Register Description ............................................................................................. 127

8-6 Configuration ROM Header Register Description ........................................................................... 128

8-7 Bus Options Register Description ............................................................................................. 128

8-8 Configuration ROM Mapping Register Description .......................................................................... 130

8-9 Posted Write Address Low Register Description ............................................................................ 131

8-10 Posted Write Address High Register Description ........................................................................... 131

8-11 Host Controller Control Register Description ................................................................................ 132

8-12 Self-ID Count Register Description ............................................................................................ 133

8-13 Isochronous Receive Channel Mask High Register Description .......................................................... 134

8-14 Isochronous Receive Channel Mask Low Register Description ........................................................... 135

8-15 Interrupt Event Register Description .......................................................................................... 135

8-16 Interrupt Mask Register Description ........................................................................................... 137

8-17 Isochronous Transmit Interrupt Event Register Description ............................................................... 139

8-18 Isochronous Receive Interrupt Event Register Description ................................................................ 140

8-19 Initial Bandwidth Available Register Description ............................................................................ 141

8-20 Initial Channels Available High Registr Description ......................................................................... 141

8-21 Initial Channels Available Low Register Description ........................................................................ 142

8-22 Fairness Control Registre Description ........................................................................................ 143

8-23 Link Control Register Description ............................................................................................. 144

8-24 Node Identification Register Description ...................................................................................... 145

8-25 PHY Control Register Description ............................................................................................. 146

www.ti.com

List of Tables10 Submit Documentation Feedback

Page 11

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

8-26 Isochronous Cycle Timer Register Description .............................................................................. 147

8-27 Asynchronous Request Filter High Register Description ................................................................... 148

8-28 Asynchronous Request Filter Low Register Description ................................................................... 150

8-29 Physical Request Filter High Register Description .......................................................................... 151

8-30 Physical Request Filter Low Register Description .......................................................................... 153

8-31 Asynchronous Context Control Register Description ....................................................................... 154

8-32 Asynchronous Context Command Pointer Register Description ......................................................... 155

8-33 Isochronous Transmit Context Control Register Description .............................................................. 156

8-34 Isochronous Receive Context Control Register Description ............................................................... 157

8-35 Isochronous Receive Context Match Register Description ................................................................ 159

9-1 TI Extension Register Map ..................................................................................................... 160

9-2 Isochronous Receive Digital Video Enhancements Register Description ................................................ 161

9-3 Link Enhancement Register Description ...................................................................................... 162

9-4 Timestamp Offset Register Description ....................................................................................... 164

10-1 Base Register Description ...................................................................................................... 167

10-2 Base Register Field Description ............................................................................................... 167

10-3 Page-0 (Port Status) Register Description ................................................................................... 169

10-4 Page-0 (Port Status) Register Field Description ............................................................................. 169

10-5 Page 1 (Vendor ID) Register Configuration .................................................................................. 171

10-6 Page 1 (Vendor ID) Register Field Descriptions ............................................................................. 171

10-7 Page 7 (Vendor Dependant) Register Configuration ....................................................................... 171

10-8 Page 7 (Vendor Dependant) Register Field Descriptions .................................................................. 172

10-9 Register Description ............................................................................................................. 172

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

OHCI-Lynx is a trademark of Texas Instruments.

PCI Express is a trademark of PCI-SIG.

List of Tables 11

Page 12

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

www.ti.com

List of Tables12 Submit Documentation Feedback

Page 13

www.ti.com

1 Introduction

1.1 XIO2213A Features

• Full x1 PCI Express Throughput

• Fully Compliant with PCI Express Base

Specification, Revision 1.1

• Utilizes 100-MHz Differential PCI Express

Common Reference Clock or 125-MHz

Single-Ended Reference Clock

• Fully supports provisions of IEEE P1394b-2002

• Fully Compliant With Provisions of IEEE Std

1394-1995 for a High-Performance Serial Bus

and IEEE Std 1394a-2000

• Fully Compliant with 1394 Open Host

Controller Interface Specification, Revision 1.1

and Revision 1.2 draft

• Three IEEE Std 1394b Fully Compliant Cable

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

Ports at 100M Bits/s, 200M Bits/s, 400M Bits/s,

and 800M Bits/s

• Cable Ports Monitor Line Conditions for Active

Connection To Remote Node

• Cable Power Presence Monitoring

• EEPROM Configuration Support to Load the

Global Unique ID for the 1394 Fabric

• Support for D1, D2, D3

• Active State Link Power Management Saves

Power When Packet Activity on the PCI

Express™ Link is Idle, Using Both L0s and L1

States

• Eight 3.3-V, Multifunction, General-Purpose I/O

Terminals

hot

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this document.

OHCI-Lynx is a trademark of Texas Instruments.

PCI Express is a trademark of PCI-SIG.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2007–2008, Texas Instruments Incorporated

Page 14

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

2 Overview

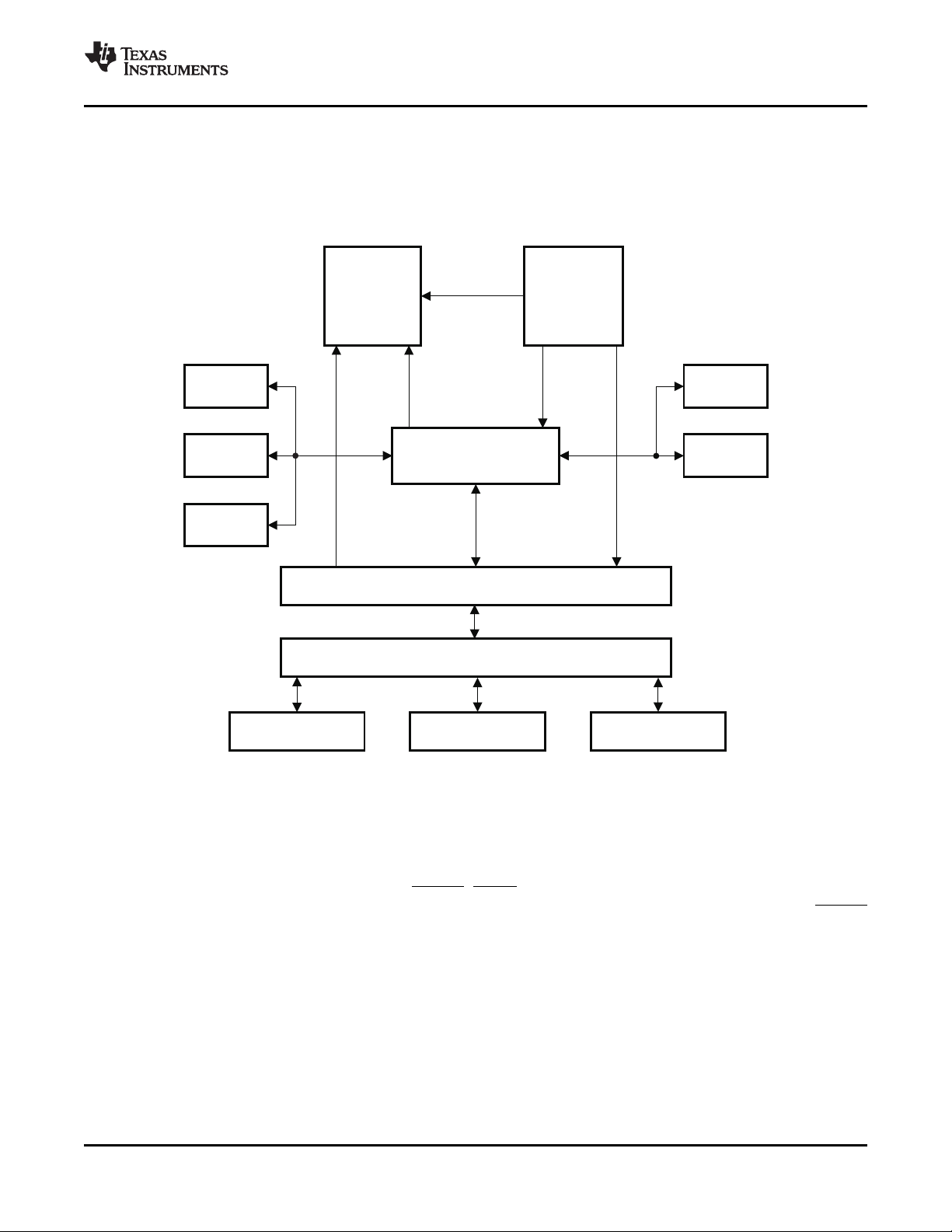

The Texas Instruments XIO2213A is a single-function PCI Express™ to PCI local bus translation bridge

where the PCI bus interface is internally connected to a 1394b open host controller link-layer controller

with a three-port 1394b PHY. When the XIO2213A is properly configured, this solution provides full PCI

Express and 1394b functionality and performance.

2.1 Description

The Texas Instruments XIO2213A is a PCI Express to PCI translation bridge where the PCI bus interface

is internally connected to a 1394b open host controller link-layer controller with a three-port 1394b PHY.

The PCI-Express to PCI translation bridge is fully compatible with the PCI Express to PCI/PCI-X Bridge

Specification, Revision 1.0. Also, the bridge supports the standard PCI-to-PCI bridge programming model.

The 1394b OHCI controller function is fully compatible with IEEE Standard 1394b and the latest 1394

Open Host Controller Interface (OHCI) Specification.

The XIO2213A simultaneously supports up to four posted write transactions, four non-posted transactions,

and four completion transactions pending in each direction at any time. Each posted write data queue and

completion data queue can store up to 8K bytes of data. The non-posted data queues can store up to 128

bytes of data.

The PCI Express interface supports a x1 link operating at full 250 MB/s packet throughput in each

direction simultaneously. Also, the bridge supports the advanced error reporting capability including ECRC

as defined in the PCI Express Base Specification, Revision 1.1. Supplemental firmware or software is

required to fully utilize both of these features.

www.ti.com

Robust pipeline architecture is implemented to minimize system latency. If parity errors are detected, then

packet poisoning is supported for both upstream and downstream operations.

The PCIe Power management (PM) features include active state link PM, PME mechanisms, and all

conventional PCI D-states. If the active state link PM is enabled, then the link automatically saves power

when idle using the L0s and L1 states. PM active state NAK, PM PME, and PME-to-ACK messages are

supported. The bridge is compliant with the latest PCI Bus Power Management Specification and provides

several low-power modes, which enable the host power system to further reduce power consumption

Eight general-purpose inputs and outputs (GPIOs), configured through accesses to the PCI Express

configuration space, allow for further system control and customization.

Deep FIFOs are provided to buffer 1394 data and accommodate large host bus latencies. The device

provides physical write posting and a highly tuned physical data path for SBP-2 performance. The device

is capable of transferring data between the PCI Express bus and the 1394 bus at 100M bits/s, 200M

bits/s, 400M bits/s, and 800M bits/s. The device provides three 1394 ports that have separate cable bias

(TPBIAS).

As required by the 1394 Open Host Controller Interface Specification, internal control registers are

memory-mapped and nonprefetchable. This configuration header is accessed through configuration cycles

specified by PCI Express, and it provides plug-and-play (PnP) compatibility.

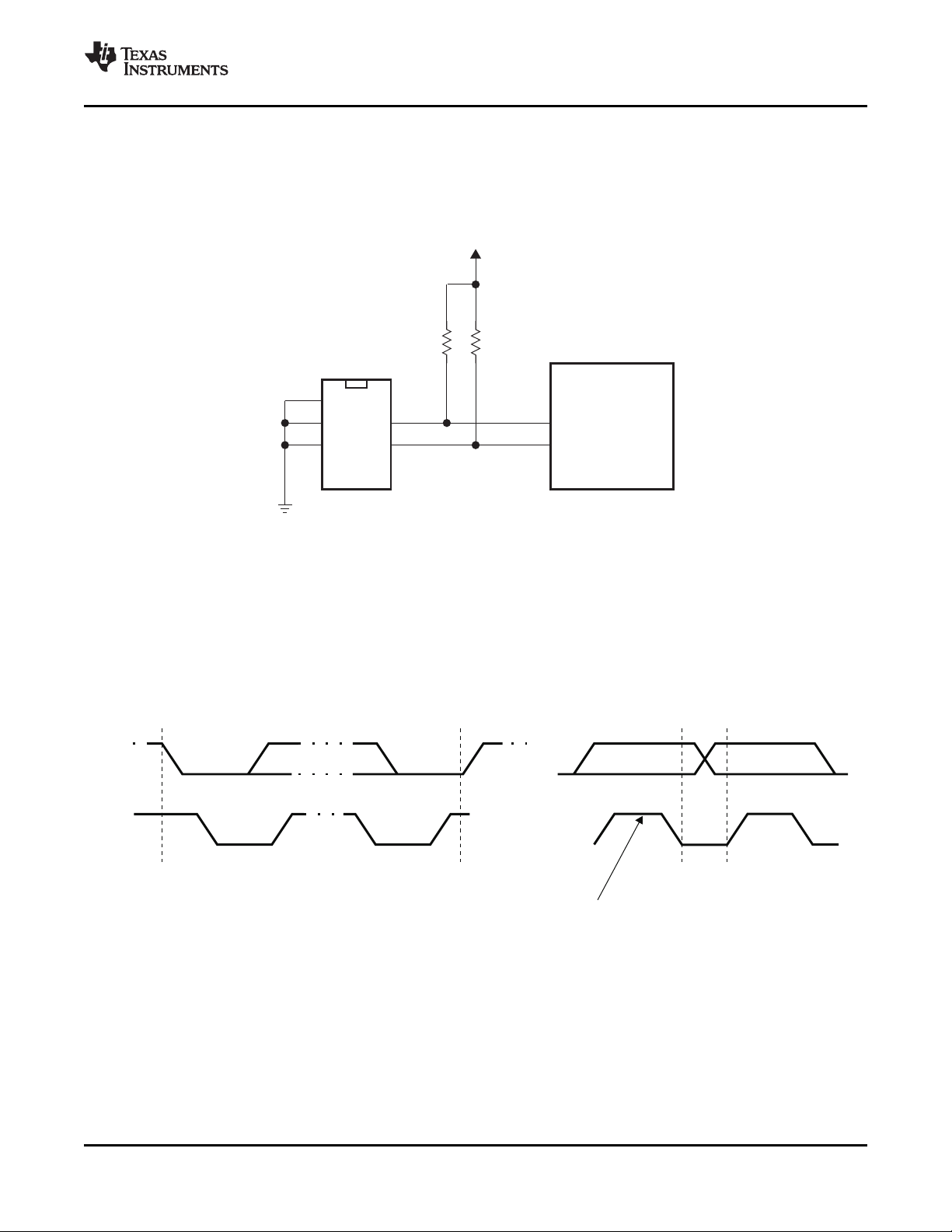

The PHY-layer provides the digital and analog transceiver functions needed to implement a three-port

node in a cable-based 1394 network. Each cable port incorporates two differential line transceivers. The

transceivers include circuitry to monitor the line conditions as needed for determining connection status,

for initialization and arbitration, and for packet reception and transmission. An optional external 2-wire

serial EEPROM interface is provided to load the global unique ID for the 1394 fabric.

Overview 14 Submit Documentation Feedback

Page 15

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

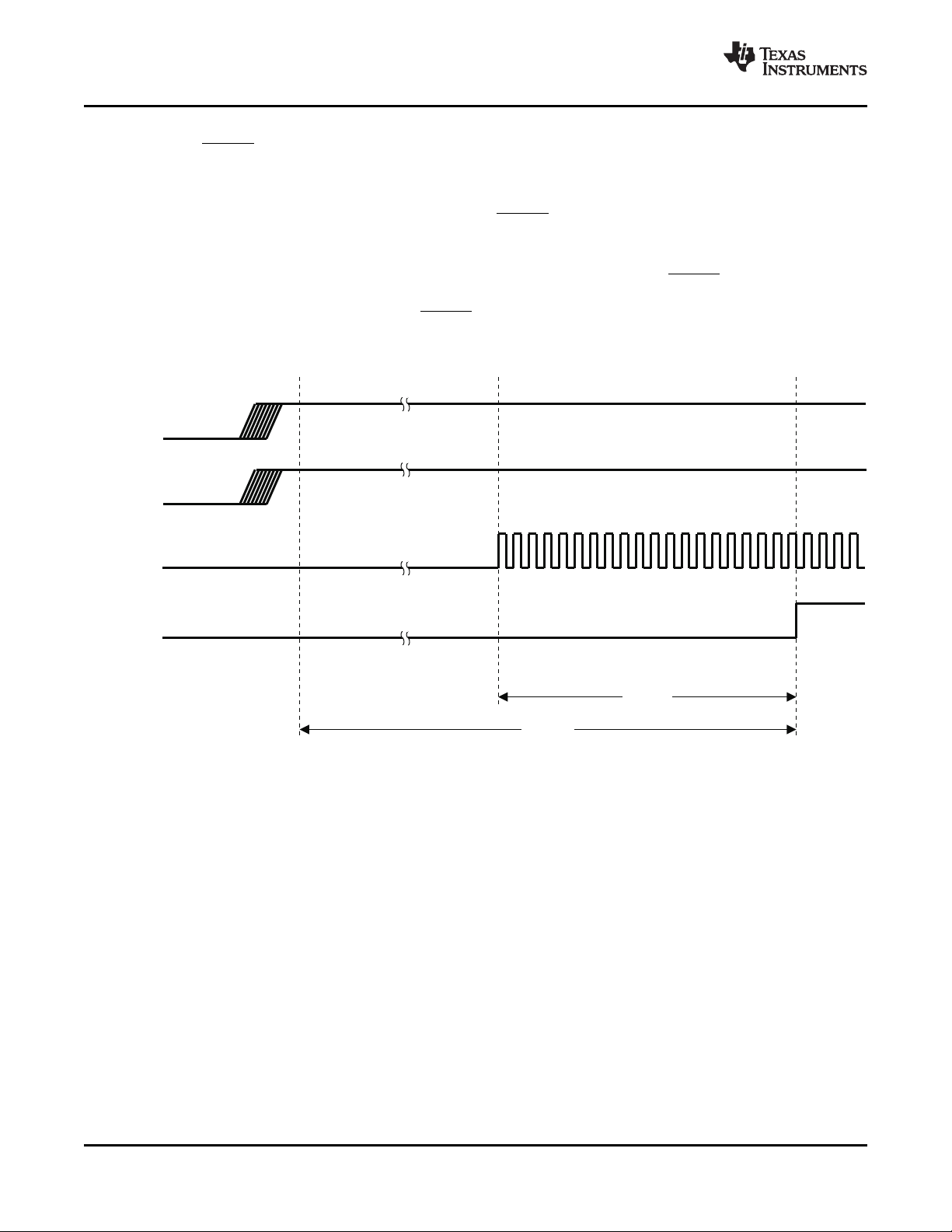

The XIO2213A requires an external 98.304-MHz crystal oscillator to generate a reference clock. The

external clock drives an internal phase-locked loop (PLL), which generates the required reference signal.

This reference signal provides the clock signals that control transmission of the outbound encoded

information. The power-down (PD) function, when enabled by asserting the PD terminal high, stops

operation of the PLL. Data bits to be transmitted through the cable ports are latched internally, combined

serially, encoded, and transmitted at 98.304, 196.608, 393.216, 491.52, or 983.04 Mbps (referred to as

S100, S200, S400, S400B, or S800 speed, respectively) as the outbound information stream.

To ensure that the XIO2213A conforms to the IEEE Std 1394b-2002 standard, the BMODE terminal must

be asserted. The BMODE terminal does not select the cable-interface mode of operation. The BMODE

terminal selects the internal PHY section-LLC section interface mode of operation and affects the

arbitration modes on the cable. BMODE must be pulled high during normal operation.

Three package terminals are used as inputs to set the default value for three configuration status bits in

the self-ID packet. They can be pulled high through a 1-k Ω resistor or hardwired low as a function of the

equipment design. The PC0, PC1, and PC2 terminals indicate the default power class status for the node

(the need for power from the cable or the ability to supply power to the cable). The contender bit in the

PHY register set indicates that the node is a contender either for the isochronous resource manager (IRM)

or for the bus manager (BM). On the XIO2213A, this bit can only be set by a write to the PHY register set.

If a node is to be a contender for IRM or BM, the node software must set this bit in the PHY register set.

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

Submit Documentation Feedback Overview 15

Page 16

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

2.2 Related Documents

• PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0

• PCI Express Base Specification, Revision 1.1

• PCI Express Card Electromechanical Specification, Revision 1.1

• PCI Local Bus Specification, Revision 2.3 and 3.0

• PCI-to-PCI Bridge Architecture Specification, Revision 1.1

• PCI Bus Power Management Interface Specification, Revision 1.1 or 1.2

• 1394 Open Host Controller Interface Specification Release 1.2

• IEEE Standard for a High Performance Serial Bus IEEE Std 1394-1995

• IEEE Standard for a High Performance Serial Bus—Amendment 1 IEEE Std 1394a-2000

• IEEE Standard for a High Performance Serial Bus—Amendment 2 IEEE Std 1394b-2002

• Express Card Standard, Release 1.0 and 1.1

• PCI Express Jitter and BER White Paper

• PCI Mobile Design Guide, Revision 1.1

2.3 Trademarks

• PCI Express is a trademark of PCI-SIG.

• OHCI-Lynx, and MicroStar BGA are trademarks of Texas Instruments.

• Other trademarks are the property of their respective owners.

www.ti.com

2.4 Documents Conventions

Throughout this data manual, several conventions are used to convey information. These conventions are

listed below:

1. To identify a binary number or field, a lower case b follows the numbers. For example: 000b is a 3-bit

binary field.

2. To identify a hexadecimal number or field, a lower case h follows the numbers. For example: 8AFh is a

12-bit hexadecimal field.

3. All other numbers that appear in this document that do not have either a b or h following the number

are assumed to be decimal format.

4. If the signal or terminal name has a bar above the name (for example, GRST), then this indicates the

logical NOT function. When asserted, this signal is a logic low, 0, or 0b.

5. Differential signal names end with P, N, +, or – designators. The P or + designators signify the positive

signal associated with the differential pair. The N or – designators signify the negative signal

associated with the differential pair.

6. RSVD indicates that the referenced item is reserved.

7. In Sections 4 through 6, the configuration space for the bridge is defined. For each register bit, the

software access method is identified in an access column. The legend for this access column includes

the following entries:

– r – read access by software

– u – updates by the bridge internal hardware

– w – write access by software

– c – clear an asserted bit with a write-back of 1b by software. Write of zero to the field has no effect

– s – the field may be set by a write of one. Write of zero to the field has no effect

– na – not accessible or not applicable

8. The XIO2213A consists of a PCI-Express to PCI translation bridge where the secondary PCI bus is

internally connected to a 1394b OHCI with a 3-port PHY. When describing functionality that is specific

to the PCI-Express to PCI translation bridge, the term bridge is used to reduce text. The term 1394b

OHCI is used to reduce text when describing the 1394b OHCI with 3-port PHY function.

Overview 16 Submit Documentation Feedback

Page 17

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

9. LLC is used to refer to the 1394 link layer controller.

2.5 Ordering Information

ORDERING NAME VOLTAGE PACKAGE

NUMBER

XIO2213AZAY PCI-Express to PCI Translation 3.3-V and 1.5-V power terminals 167-terminal ZAY (Lead-Free) PBGA

Bridge with 1394b OHCI and

Three-Port PHY

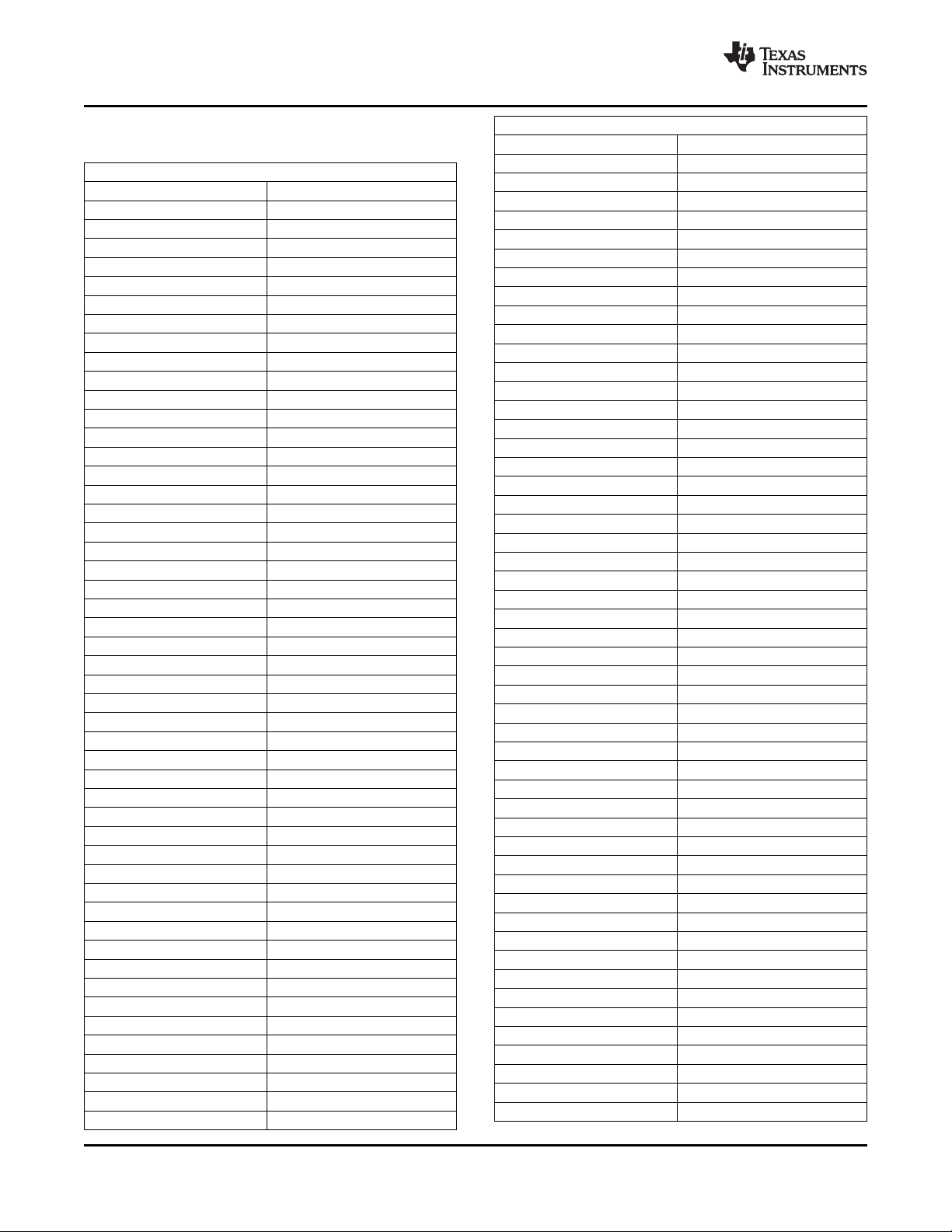

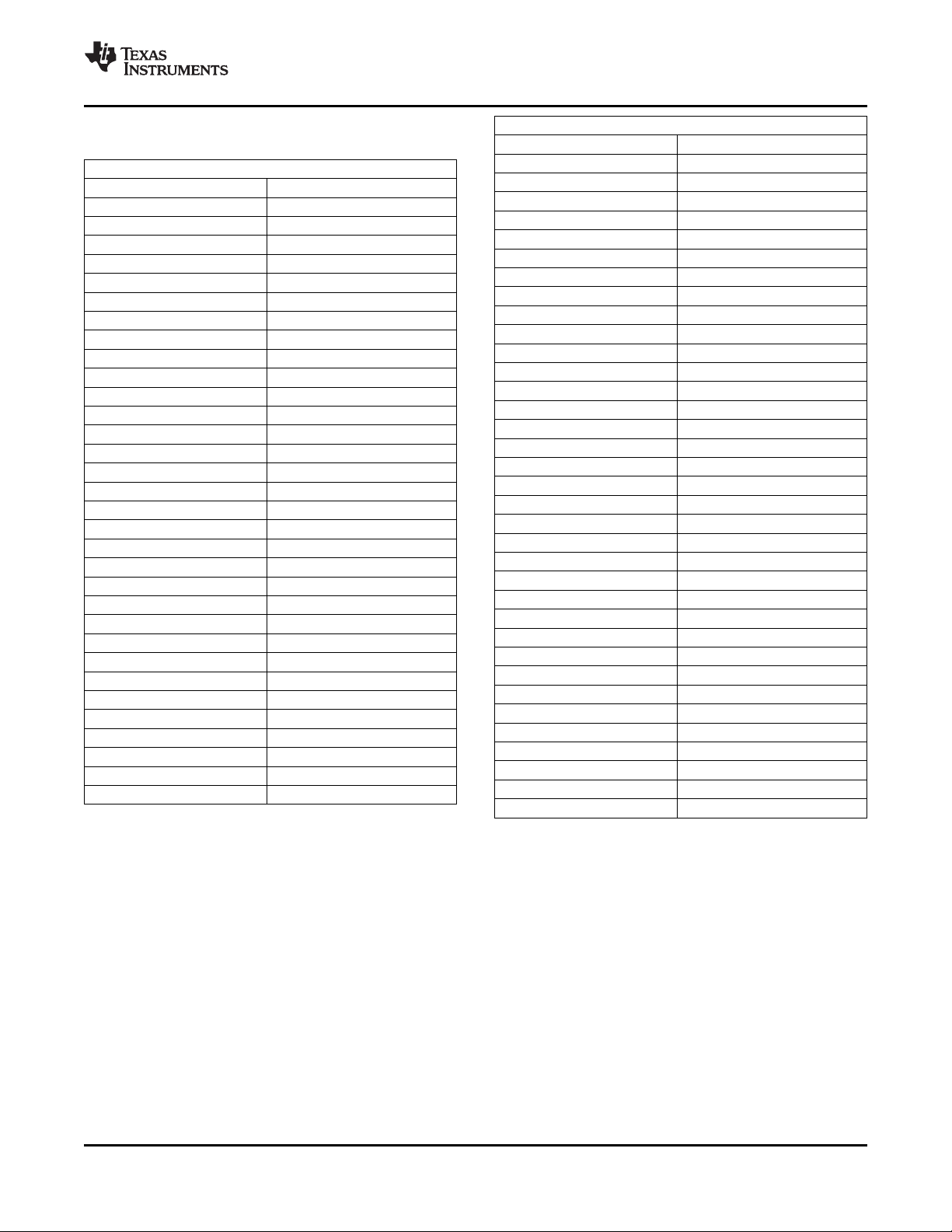

2.6 Terminal Assignments

The XIO2213A is packaged in a 167-ball ZAY PBGA. For the ZAY BGATable 2-1 lists the terminals sorted

alphanumerically. Table 2-2 lists the signals in alphanumerical order.

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

Submit Documentation Feedback Overview 17

Page 18

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

www.ti.com

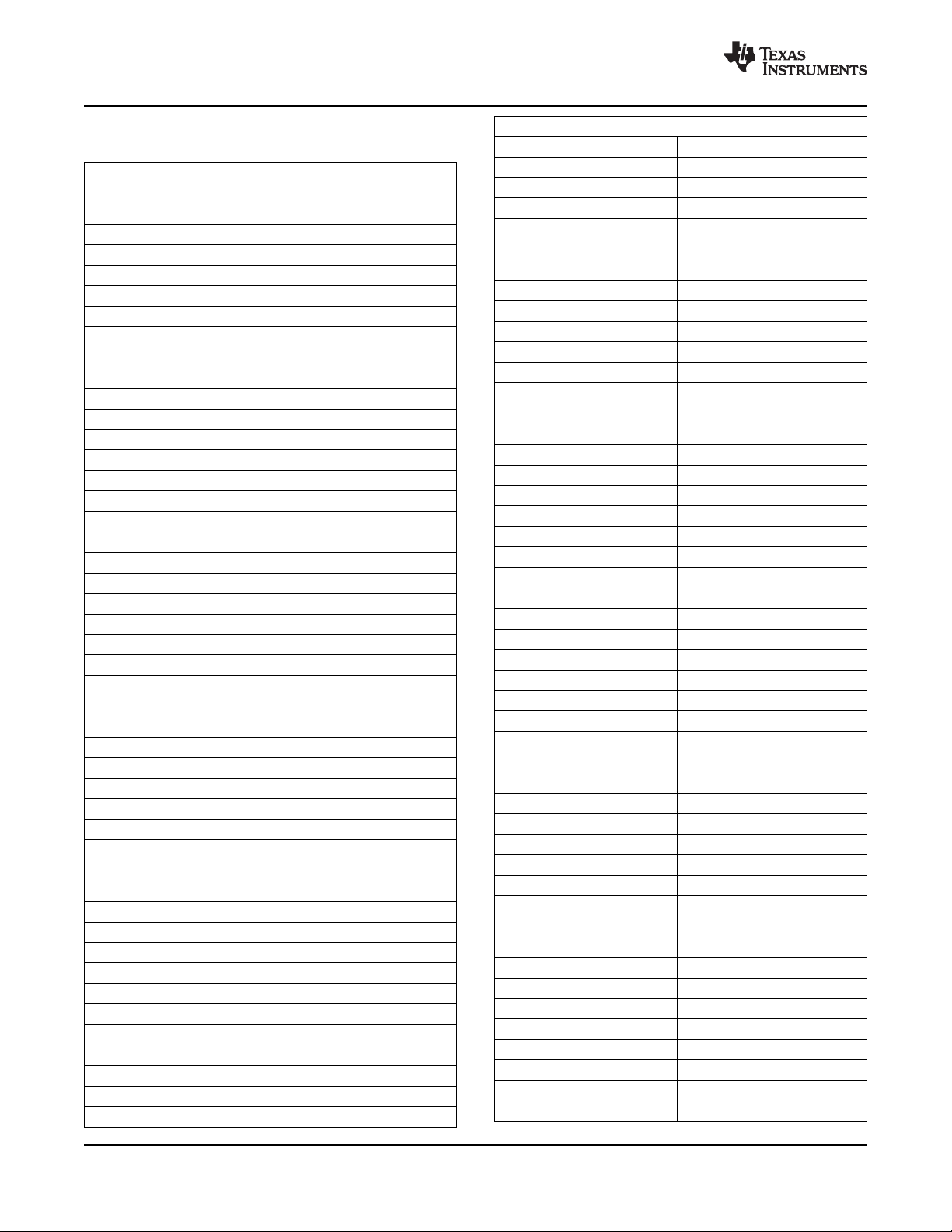

Table 2-1. XIO2213AZAY_12x12 Terminals Sorted

Alphanumerically

XIO2213A

BGA BALL # SIGNAL NAME

A01 REFCLK+

A02 CNA

A03 RXN

A04 RXP

A05 BMODE

A06 TESTW(VREG_PD)

A07 VSS

A08 TXN

A09 TXP

A10 VDDA_33

A11 PC2

A12 REF1_PCIE

A13 REF0_PCIE

A14 VSS

B01 REFCLKB02 TESTM

B03 PD

B04 PHY_RESET#

B05 VDDA_15

B06 VSSA

B07 VDDA_15

B08 VDD_15

B09 VDDA_15

B10 VDDA_15

B11 VDD_33_COMB

B12 VDD_33

B13 PERST#

B14 TPA2+

C01 LPS_L

C02 LPS_P

C03 VDDA_33

C04 VSSA_PCIE

C05 VSSA_PCIE

C06 VSSA_PCIE

C07 VSSA_PCIE

C08 DVDD_3.3

C09 DVDD_CORE

C10 VSSA

C11 VDD_33_COM_IO

C12 VDD_15_COMB

C13 GRST#

C14 TPA2D01 LKON/DS2_P

D02 PINT_L

D03 PINT_P

D12 RSVD

D13 RSVD

D14 TPB2+

E01 LINKON_L

XIO2213A

BGA BALL # SIGNAL NAME

E02 LREQ_P

E03 VDD_33

E06 GND

E07 GND

E08 PC1

E09 PC0

E10 AVDD_3.3

E12 RSVD

E13 TPBIAS2

E14 TPB2F01 PCLK_P

F02 LREQ_L

F03 DVDD_CORE

F05 VSSA

F06 GND

F07 GND

F08 GND

F09 GND

F10 AVDD_3.3

F12 RSVD

F13 RSVD

F14 TPA1+

G01 PCLK_L

G02 LCLK_L

G03 VDD_15

G05 GND

G06 GND

G07 GND

G08 GND

G09 GND

G10 VDD_33

G12 RSVD

G13 TPBIAS1

G14 TPA1H01 CTL0

H02 LCLK_P

H03 VDD_15

H05 GND

H06 GND

H07 GND

H08 GND

H09 GND

H10 VDD_33

H12 SDA

H13 REFCLK_SEL

H14 TPB1+

J01 CTL1

J02 D0

J03 DVDD_3.3

J05 GND

J06 GND

Overview 18 Submit Documentation Feedback

Page 19

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

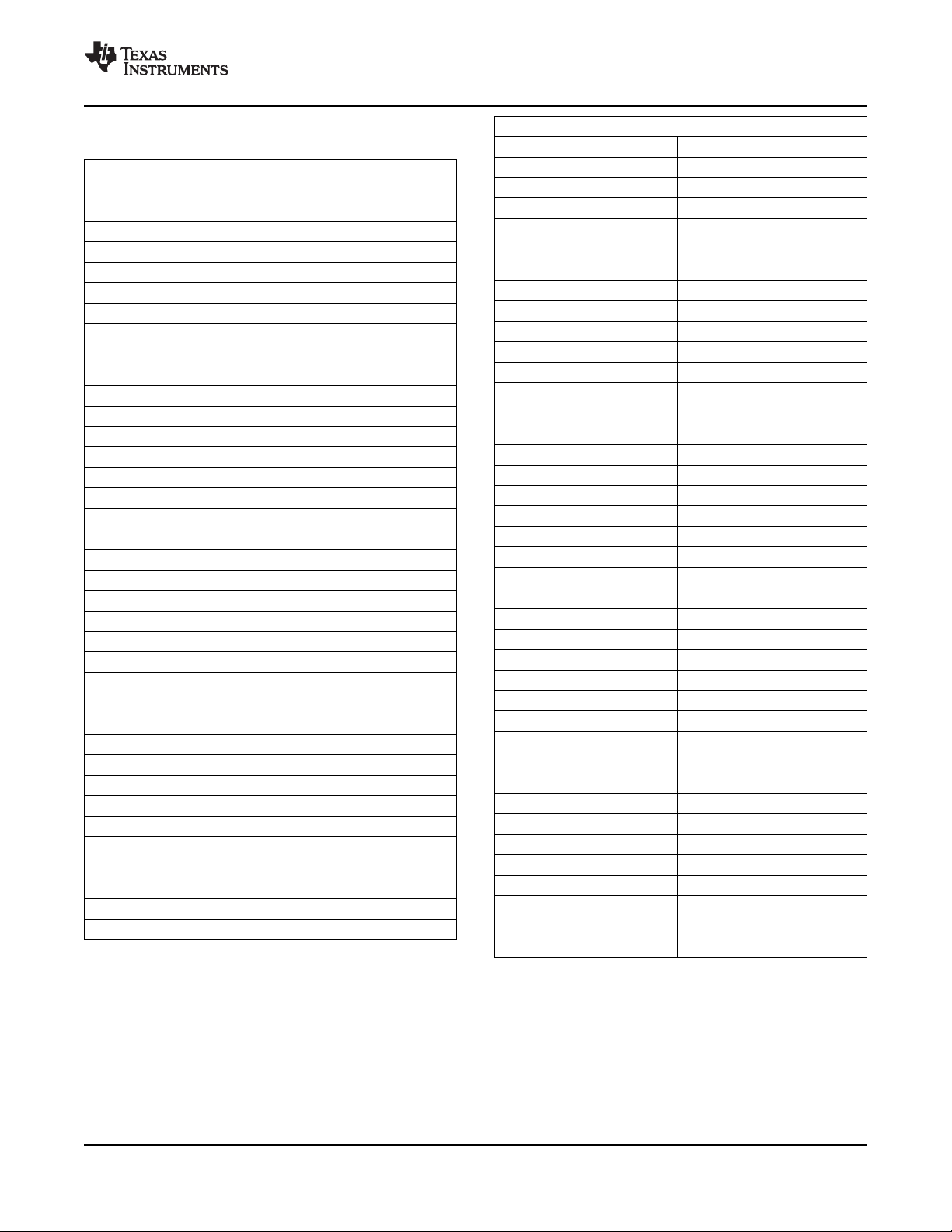

Table 2-1. XIO2213AZAY_12x12 Terminals Sorted

Alphanumerically (continued)

XIO2213A

BGA BALL # SIGNAL NAME

J07 GND

J08 GND

J09 AVDD_3.3

J10 VDD_33

J12 CLKREQ#

J13 SCL

J14 TPB1K01 D2

K02 D1

K03 DVDD_3.3

K05 GND

K06 GND

K07 GND

K08 GND

K09 AVDD_3.3

K10 VDD_15

K12 RSVD

K13 TPBIAS0

K14 TPA0+

L01 D3

L02 D4

L03 D5

L12 RSVD

L13 RSVD

L14 TPA0M01 R1

M02 D6

M03 D7

M04 AVDD_3.3

M05 VDD_33

M06 VDD_15

M07 PLLVDD_CORE

XIO2213A

BGA BALL # SIGNAL NAME

M08 RSVD

M09 DVDD_CORE

M10 AVDD_3.3

M11 RSVD

M12 RSVD

M13 RSVD

M14 TPB0+

N01 R0

N02 GPIO1

N03 GPIO3

N04 GPIO4

N05 PLLGND

N06 GPIO7

N07 PLLVDD_3.3

N08 CYCLEOUT

N09 DS0

N10 RSVD

N11 RSVD

N12 RSVD

N13 RSVD

N14 TPB0P01 GPIO0

P02 GPIO2

P03 RSVD

P04 XI

P05 GPIO5

P06 GPIO6

P07 VDD_15

P08 OHCI_PME#

P09 DS1

P10 RSVD

P11 RSVD

P12 CPS

P13 SE

P14 SM

Submit Documentation Feedback Overview 19

Page 20

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

www.ti.com

Table 2-2. XIO2213AZAY_12x12 Signals Sorted

Alphanumerically

XIO2213A

BGA BALL # SIGNAL NAME

E10 AVDD_3.3

F10 AVDD_3.3

J09 AVDD_3.3

K09 AVDD_3.3

M10 AVDD_3.3

M04 AVDD_3.3

A05 BMODE

J12 CLKREQ#

A02 CNA

P12 CPS

H01 CTL0

J01 CTL1

N08 CYCLEOUT

J02 D0

K02 D1

K01 D2

L01 D3

L02 D4

L03 D5

M02 D6

M03 D7

N09 DS0

P09 DS1

C08 DVDD_3.3

J03 DVDD_3.3

K03 DVDD_3.3

C09 DVDD_CORE

F03 DVDD_CORE

M09 DVDD_CORE

E06 GND

E07 GND

F06 GND

F07 GND

F08 GND

F09 GND

G05 GND

G06 GND

G07 GND

G08 GND

G09 GND

H05 GND

H06 GND

H07 GND

H08 GND

H09 GND

XIO2213A

BGA BALL # SIGNAL NAME

J05 GND

J06 GND

J07 GND

J08 GND

K05 GND

K06 GND

K07 GND

K08 GND

P01 GPIO0

N02 GPIO1

P02 GPIO2

N03 GPIO3

N04 GPIO4

P05 GPIO5

P06 GPIO6

N06 GPIO7

C13 GRST#

G02 LCLK_L

H02 LCLK_P

E01 LINKON_L

D01 LKON/DS2_P

C01 LPS_L

C02 LPS_P

F02 LREQ_L

E02 LREQ_P

P08 OHCI_PME#

E09 PC0

E08 PC1

A11 PC2

G01 PCLK_L

F01 PCLK_P

B03 PD

B13 PERST#

D02 PINT_L

D03 PINT_P

N05 PLLGND

N07 PLLVDD_3.3

M07 PLLVDD_CORE

N01 R0

M01 R1

A13 REF0_PCIE

A12 REF1_PCIE

B01 REFCLKH13 REFCLK_SEL

A01 REFCLK+

B04 PHY_RESET#

G12 RSVD

Overview 20 Submit Documentation Feedback

Page 21

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

Table 2-2. XIO2213AZAY_12x12 Signals Sorted

Alphanumerically (continued)

XIO2213A

BGA BALL # SIGNAL NAME

F13 RSVD

F12 RSVD

E12 RSVD

D12 RSVD

D13 RSVD

M08 RSVD

N10 RSVD

P10 RSVD

P11 RSVD

N11 RSVD

M11 RSVD

N12 RSVD

N13 RSVD

M12 RSVD

M13 RSVD

L13 RSVD

K12 RSVD

L12 RSVD

A03 RXN

A04 RXP

J13 SCL

H12 SDA

P13 SE

P14 SM

B02 TESTM

A06 TESTW(VREG_PD)

L14 TPA0K14 TPA0+

G14 TPA1F14 TPA1+

C14 TPA2B14 TPA2+

N14 TPB0M14 TPB0+

J14 TPB1H14 TPB1+

XIO2213A

BGA BALL # SIGNAL NAME

E14 TPB2D14 TPB2+

K13 TPBIAS0

G13 TPBIAS1

E13 TPBIAS2

A08 TXN

A09 TXP

G03 VDD_15

H03 VDD_15

K10 VDD_15

M06 VDD_15

B08 VDD_15

C12 VDD_15_COMB

E03 VDD_33

G10 VDD_33

H10 VDD_33

J10 VDD_33

M05 VDD_33

B12 VDD_33

C11 VDD_33_COM_IO

B11 VDD_33_COMB

B10 VDDA_15

B09 VDDA_15

B07 VDDA_15

B05 VDDA_15

C03 VDDA_33

A10 VDDA_33

P07 VDD_15

A14 VSS

A07 VSS

F05 VSSA

C10 VSSA

B06 VSSA

C04 VSSA_PCIE

C05 VSSA_PCIE

C06 VSSA_PCIE

C07 VSSA_PCIE

P04 XI

P03 RSVD

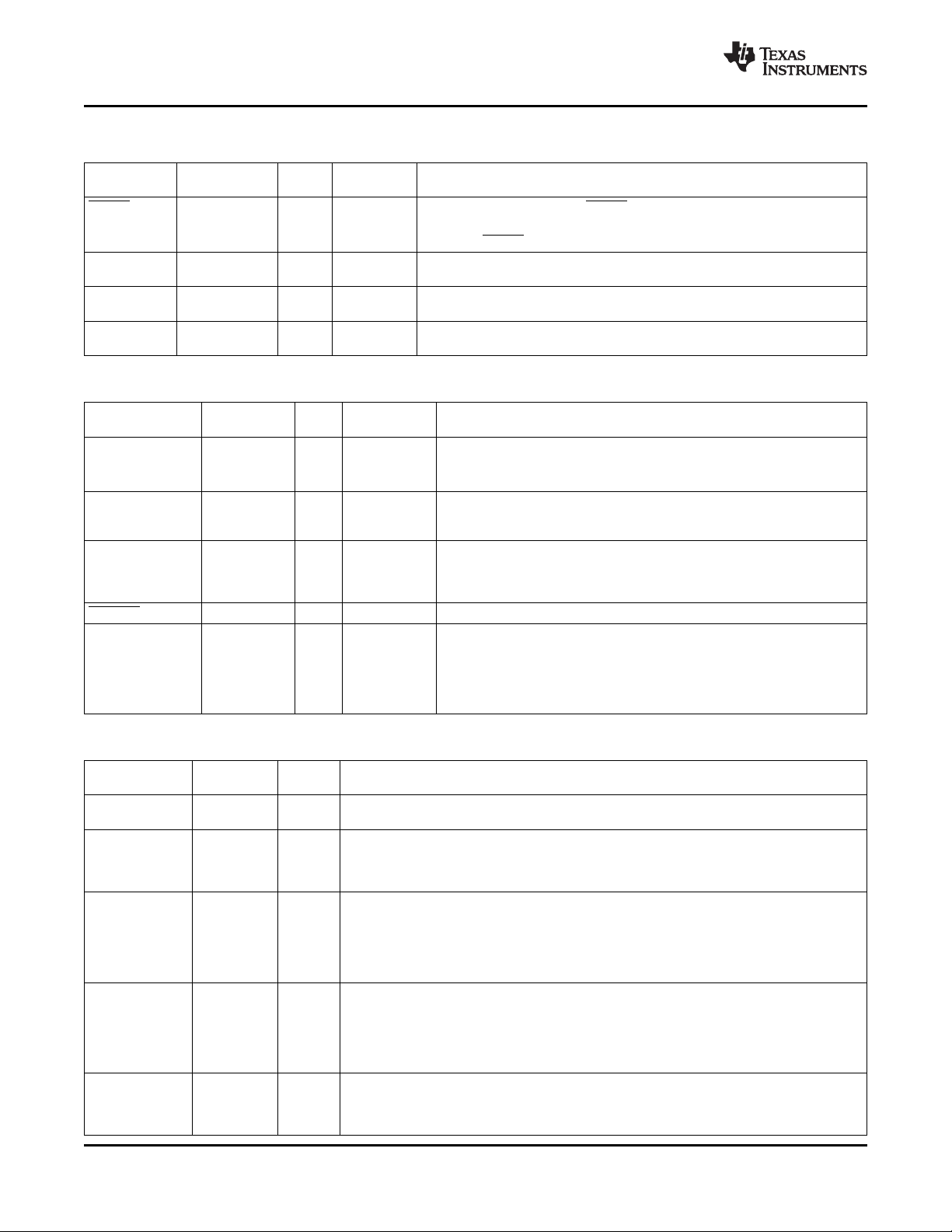

2.7 Terminal Descriptions

The following tables give a description of the terminals. These terminals are grouped in tables by

functionality. Each table includes the terminal name, terminal number, I/O type, and terminal description.

The following list describes the different input/output cell types that appear in the terminal description

tables:

• HS DIFF IN = High speed differential input

• HS DIFF OUT = High speed differential output

Submit Documentation Feedback Overview 21

Page 22

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

• LV CMOS = 3.3-V low voltage CMOS input or output with 3.3-V clamp rail

• BIAS = Input/output terminals that generate a bias voltage to determine a driver's operating current

• Feed through = these terminals connect directly to macros within the part and not through an input or

output cell.

• PWR = Power terminal

• GND = Ground terminal

www.ti.com

22 Overview Submit Documentation Feedback

Page 23

XIO2213A PCI Express to 1394b OHCI with 3-Port PHY

www.ti.com

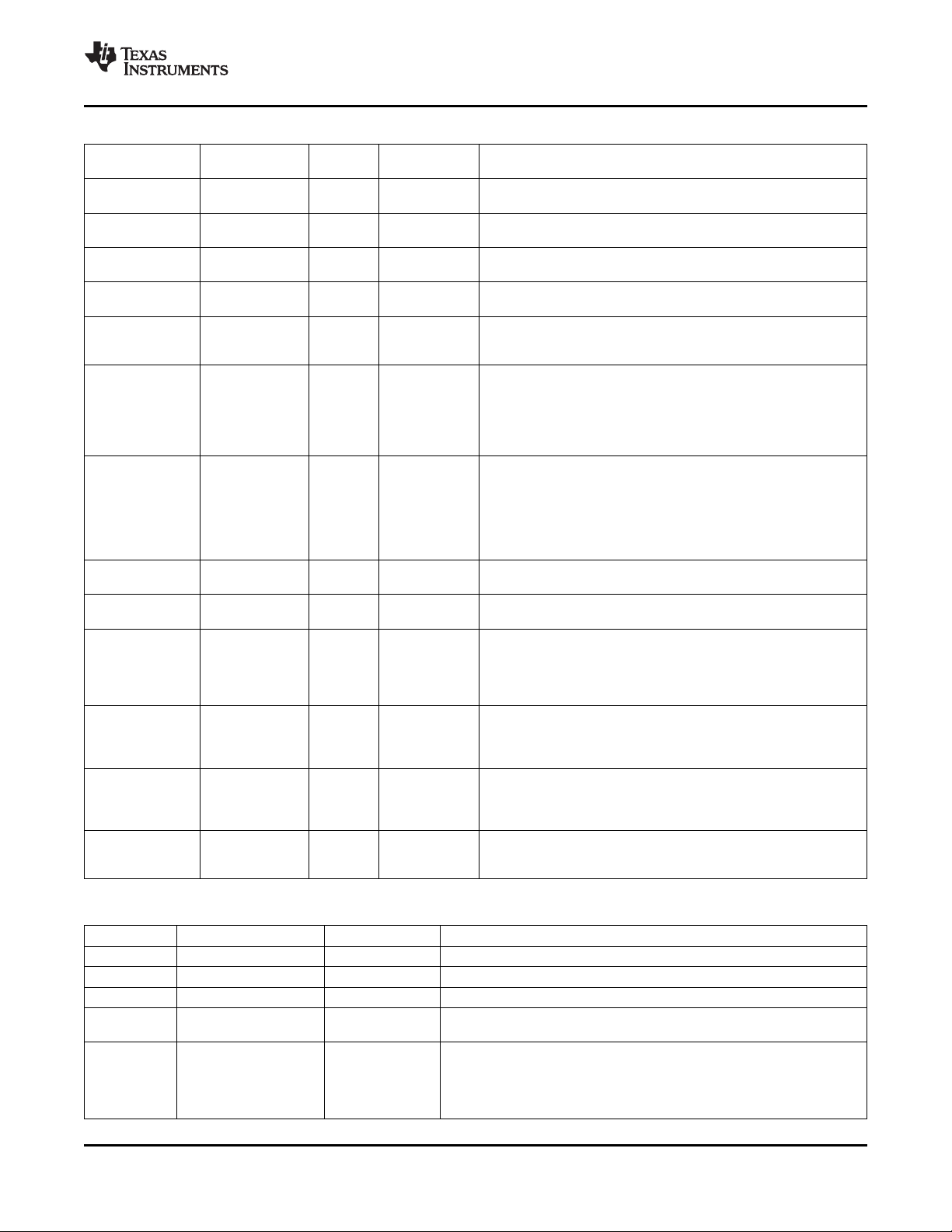

Table 2-3. Power Supply Terminals

SIGNAL BALL 12x12 I/O EXTERNAL DESCRIPTION

V

DD_15

V

DDA_15

V

DD_33

V

DD_33_AUX

V

DDA_33

DVDD_CORE C09 F03 M09 PWR Bypass Digital 1.95-V circuit power for the PHY. A combination of

PLLVDD_CORE M07 PWR Bypass PLL 1.95-V circuit power for the PHY. A combination of

DVDD_33 C08 J03 K03 PWR Bypass 3.3-V digital I/O power terminals for the PHY

AVDD_33 M04 E10 F10 J09 PWR Filter 3.3-V analog power terminals for the PHY

PLLVDD_33 N07 PWR Bypass PLL 3.3-V circuit power for the PHY. This supply terminal is

V

DD_15_COMB

V

DD_33_COMB

V

DD_33_COMBIO

ZAY TYPE PARTS

G03 H03 K10 PWR Bypass 1.5-V digital core power terminals for the link.

M06 B08 P07 capacitors

B10 B09 B07 PWR Filter 1.5-V analog power terminal for the link.

B05

E03 M05 J10 PWR Bypass 3.3-V digital I/O power terminals for the link

H10 G10 capacitors

B12 This terminal is connected to VSS through a pull-down resistor

since the XIO2213A does not support Auxiliary power

C03 A10 PWR Filter 3.3-V analog power terminals for the link. This supply terminal is

separated from the other power terminals internal to the device to

provide noise isolation.

capacitors high-frequency decoupling capacitors near each terminal is

suggested, such as paralleled 0.1- µ F and 0.001- µ F. An additional

1- µ F capacitor is required for voltage regulation. These supply

terminals are separated from the other power terminals internal to

the device to provide noise isolation.

capacitors high-frequency decoupling capacitors near each terminal is

suggested, such as paralleled 0.1- µ F and 0.001- µ F. An additional

1- µ F capacitor is required for voltage regulation, and the

PLLVDD_CORE terminals must be separate from the DVDD_CORE

terminals. These supply terminals are separated from the other

power terminals internal to the device to provide noise isolation.

capacitors

K09 M10

capacitors separated from the other power terminals internal to the device to

provide noise isolation. The PLLVDD_33 and V

be connected together with a low-dc-impedance connection on the

circuit board.

C12 PWR Bypass Internal 1.5-V main power output for external bypass capacitor

capacitors filtering.

Caution: Do not use this terminal to supply external power to other

devices.

B11 PWR Bypass Internal 3.3-V main power output for external bypass capacitor

capacitors filtering.

Caution: Do not use this terminal to supply external power to other

devices.

C11 PWR Bypass Internal 3.3-V IOpower output for external bypass capacitor filtering.

capacitors Caution: Do not use this terminal to supply external power to other

devices.

SCPS183A – OCTOBER 2007 – REVISED MARCH 2008

DDA_33

pins should

Table 2-4. Ground Terminals

SIGNAL BALL 12x12 ZAY I/O TYPE DESCRIPTION

V

SS

V

SSA

V

SSA_PCIE

PLLGND N05 GND PLL circuit ground. This terminal must be tied to the low-impedance

GND E06 E07 F06 F07 F08 GND Ground. These terminals must be tied together to the low-impedance

Submit Documentation Feedback Overview 23

A07 A14 GND Digital ground terminals for link

B06 C10 F05 GND Analog ground terminals for link

C04 C05 C06 C07 GND Analog ground terminals for PCI Express function