l

Data Manua

November 2006 CS Peripheral

SLLS535D

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI’s terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty . Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. To minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third-party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application

solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Interface interface.ti.com Digital Control www.ti.com/digitalcontrol

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

Low Power Wireless www.ti.com/lpw Telephony www.ti.com/telephony

Video & Imaging www.ti.com/video

Wireless www.ti.com/wireless

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright 2006, Texas Instruments Incorporated

Contents

Contents

Section Page

1 Controller Description 1−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Acronyms and Terms 1−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Main Features 2−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Universal Serial Bus (USB) 2−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Microcontroller Unit (MCU) 2−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 ATA/ATAPI Interface Controller 2−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 General Feature 2−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Device Block Diagrams 3−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Device Parameter Information 4−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 Pin Diagram 4−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Terminal Functions 4−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Device Operation 4−5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.1 Device Master Reset 4−5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Clock Generation 4−5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.3 Device Initialization 4−5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Architecture Overview 5−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 Controller Brief Data Flow 5−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Overview of Major Function Blocks 5−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 USB 2.0 UTMI-Compliant PHY 5−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.2 USB 2.0 Parallel Interface Engine (PIE) 5−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3 USB Buffer Manager (UBM) 5−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.4 Embedded Microcontroller Unit (MCU) 5−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.5 ATA/ATAPI Interface Controller 5−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.6 I2C Interface Controller 5−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Other Major Features 5−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Unique Power-On Sequencing to the Storage Device 5−4. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 Die-ID Based USB Device Serial Number 5−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Microcontroller Unit (MCU) 6−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 MCU Memory Map 6−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Internal XDATA Space [E000 → F0F9] 6−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 MCU Control and Status Registers (in SFR and ESFR Space) 6−8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.1 PCON: Power Control Register (at SFR 87h) 6−9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.2 RTKTM: RTK Timer Register (at ESFR F6h) 6−9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.3 WDCSR: Watchdog Timer Control and Status Register (at ESFR FBh) 6−10. . . . . . . . . . . .

6.3.4 MCUCNFG: MCU Configuration Register (at ESFR FCh) 6−10. . . . . . . . . . . . . . . . . . . . . . . .

6.3.5 PWONSUSP: Power-On Reset and Suspend Detection Register (at ESFR FDh) 6−11. . .

7 Interrupts 7−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 8051 Interrupt and Status Registers 7−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.1 IE: Interrupt Enable Register (SFR at A8) 7−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.2 IP: Interrupt Priority Register (SFR at B8) 7−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.3 IE1: Interrupt Enable Register (SFR at E8) 7−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.4 IP1: Interrupt Priority Register (SFR at F8) 7−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.5 TCON: Timer/Counter Control Register (SFR at 88) 7−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 Additional Interrupt Sources 7−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.1 VECINT: Vector Interrupt Register (ESFR at F7) 7−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SLLS535D − November 2006 TUSB6250

iii

Contents

Section Page

8 USB Function and Registers 8−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1 USBCTL: USB Control Register (XDATA at F006) 8−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1.1 USB Enumeration 8−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1.2 USB Reset 8−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1.3 USB 2.0 Test Mode 8−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2 USBMSK: USB Interrupt Mask Register (XDATA at F007) 8−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3 USBSTA: USB Status Register (XDATA at F008) 8−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3.1 USB Suspend 8−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3.2 WAKCLK Interrupt and Remote Wake-Up 8−5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4 FUNADR: Function Address Register (XDATA at F009) 8−9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5 UTMICFG: UTMI Configuration Status Register (XDATA at F00A) 8−9. . . . . . . . . . . . . . . . . . . . . . . . . . .

8.6 USBFCL: USB Frame Counter Low-Byte Register (XDATA at F00B) 8−10. . . . . . . . . . . . . . . . . . . . . . . .

8.7 USBFCH: USB Frame Counter High-Byte Register (XDATA at F00C) 8−10. . . . . . . . . . . . . . . . . . . . . . .

8.8 USBWKUP: USB Wake-Up Reason Register (XDATA at F00D) 8−10. . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.9 Endpoint-0 Descriptor Registers 8−12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.9.1 IEPCNFG_0: Input Endpoint-0 Configuration Register (XDATA at F000) 8−13. . . . . . . . . . .

8.9.2 IEPBCN_0: Input Endpoint-0 Buffer Byte Count Register (XDATA at F001) 8−13. . . . . . . . .

8.9.3 OEPCNFG_0: Output Endpoint-0 Configuration Register (XDATA at F003) 8−14. . . . . . . . .

8.9.4 OEPBCN_0: Output Endpoint-0 Buffer Byte Count Register (XDATA at F004) 8−14. . . . . .

8.10 Endpoint Descriptor Block (EDB-1 to EDB-4) 8−15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.1 IEPCNFG_n: Input Endpoint Configuration (n = 1 to 4)

(XDATA at F010, F020, F030, F040) 8−17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.2 IEPBBADRX_n: Input Endpoint X-Buffer Base Address (n = 1 to 4)

(XDATA at F011, F021, F031, F041) 8−17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.3 IEPBCNLX_n: Input Endpoint X-Buffer Byte Count Low Byte (n = 1 to 4)

(XDATA at F012, F022, F032, F042) 8−18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.4 IEPBCNHX_n: Input Endpoint X-Buffer Byte Count High Byte (n = 1 to 4) (XDATA at

F013, F023, F033, F043) 8−18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.5 IEPSIZXY_n: Input Endpoint X/Y-Buffer Size (n = 1 to 4) (XDATA at F014,

F024, F034, F044) 8−19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.6 IEPBBADRY_n: Input Endpoint Y-Buffer Base Address (n = 1 to 4)

(XDATA at F015, F025, F035, F045) 8−19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.7 IEPBCNLY_n: Input Endpoint Y-Buffer Byte Count Low Byte (n = 1 to 4)

(XDATA at F016, F026, F036, F046) 8−19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.8 IEPBCNHY_n: Input Endpoint Y-Buffer Byte Count High Byte (n = 1 to 4)

(XDATA at F017, F027, F037, F047) 8−20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.9 OEPCNF_n: Output Endpoint Configuration (n = 1 to 4) (XDATA at F018,

F028, F038, F048) 8−20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.10 OEPBBAX_n: Output Endpoint X-Buffer Base Address (n = 1 to 4)

(XDATA at F019, F029, F039, F049) 8−21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.11 OEPBCNLX_n: Output Endpoint X-Buffer Byte Count Low Byte (n = 1 to 4)

(XDATA at F01A, F02A, F03A, F04A) 8−21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.12 OEPBCNHX_n: Output Endpoint X-Buffer Byte Count High Byte (n = 1 to 4)

(XDATA at F01B, F02B, F03B, F04B) 8−21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.13 OEPSIZXY_n: Output Endpoint X/Y-Buffer Size (n = 1 to 4) (XDATA at F01C,

F02C, F03C, F04C) 8−22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.14 OEPBBADRY_n: Output Endpoint Y-Buffer Base Address (n = 1 to 4)

(XDATA at F01D, F02D, F03D, F04D) 8−22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.15 OEPBCNLY_n: Output Endpoint Y-Buffer Byte Count Low Byte (n = 1 to 4)

(XDATA at F01E, F02E, F03E, F04E) 8−22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.10.16 OEPBCNHY_n: Output Endpoint Y-Buffer Byte Count High Byte (n = 1 to 4)

(XDATA at F01F, F02F, F03F, F04F) 8−23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

SLLS535D − November 2006TUSB6250

Contents

Section Page

8.11 Serial Number Registers 8−24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.11.1 SERNUMn: Device Serial Number Register (Byte n, n = 0 to 5)

(XDATA at F080 to F085) 8−24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9 Miscellaneous and GPIO Configuration Registers 9−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.1 MODECNFG: Mode Configuration Register (XDATA at F088) 9−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2 PUPDSLCT_P2: GPIO Pullup and Pulldown Resistor Selection Register for Port 2

(XDATA at F08A) 9−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3 PUPDWDN_P2: GPIO Pullup and Pulldown Resistor Power Down for Port 2

(XDATA at F08B) 9−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4 PUPDSLCT_P3: GPIO Pullup and Pulldown Resistor Selection Register for Port 3

(XDATA at F08C) 9−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5 PUPDPWDN_P3: GPIO Pullup and Pulldown Resistor Power Down Register for Port 3

(XDATA at F08D) 9−5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6 PUPDFUNC: Pullup/Pulldown Configuration Register for Functional Pins (XDATA at F08E) 9−6. . . . .

9.7 PUPDSLCT_ATPOUT: Pullup and Pulldown Resistor Selection Register for ATA/ATAPI

Outputs (XDATA at F08F) 9−7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.8 PUPDPWDN_ATPOUT: Pullup and Pulldown Resistors Power Down Register for

ATA/ATAPI Outputs (XDATA at F090 9−8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

C Interface Controller 10−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 I

10.1 I2C Registers 10−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.1.1 IECSCR: I2C Status and Control Register (XDATA at F0B0) 10−2. . . . . . . . . . . . . . . . . . . . .

10.1.2 I2CADR: I2C Device Address Register (XDATA at F0B1) 10−2. . . . . . . . . . . . . . . . . . . . . . . .

10.1.3 I2CDIN: I2C Data_In Register (XDATA at F0B2) 10−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.1.4 I2CDOUT: I2C Data_Out Register (XDATA at F0B3) 10−3. . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2 Random-Read Operation 10−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3 Current-Address Read Operation 10−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4 Sequential-Read Operation 10−5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.5 Byte-Write Operation 10−6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.6 Page-Write Operation 10−7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.7 I2C EEPROM Head Block 10−8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11 ATA/ATAPI Interface Port 11−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1 TUSB6250 ATA Controller Architecture Overview 11−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.1 ATA Controller State Machine 11−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.2 Sector FIFO Controller 11−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.3 ATA/ATAPI CSR Registers 11−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2 ATA/ATAPI Port Power-On Sequencing and 3-State Control 11−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3 TUSB6250 ATA/ATAPI Controller Transfer Modes 11−6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.4 ATA/ATAPI Group 0 (Task_File) Registers 11−8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5 ATA/ATAPI Group 1 Registers 11−9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5.1 ATPIFCNFG0: ATA/ATAPI Interface Configuration Register 0 (XDATA at F0D0) 11−9. . . .

11.5.2 ATPIFCNFG1: ATA/ATAPI Interface Configuration Register 1 (XDATA at F0D1) 11−11. . .

11.5.3 ATPACSREG0: ATA/ATAPI Access Register 0 (XDATA at F0D2) 11−12. . . . . . . . . . . . . . . .

11.5.4 ATPACSREG1: ATA/ATAPI Access Register 1 (XDATA at F0D3) 11−12. . . . . . . . . . . . . . . .

11.5.5 ATPACSREG2: ATA/ATAPI Access Register 2 (XDATA at F0D4) 11−12. . . . . . . . . . . . . . . .

11.5.6 ATPACSREG3: ATA/ATAPI Access Register 3 (XDATA at F0D5) 11−13. . . . . . . . . . . . . . . .

11.5.7 TRANSBCNT0: USB or ATA/ATAPI Transfer Byte Count Register 0

(XDATA at F0D6) 11−13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5.8 TRANSBCNT1: USB or ATA/ATAPI Transfer Byte Count Register 1

(XDATA at F0D7) 11−14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5.9 TRANSBCNT2: USB or ATA/ATAPI Transfer Byte Count Register 2

(XDATA at F0D8) 11−14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SLLS535D − November 2006 TUSB6250

v

Contents

Section Page

11.5.10 TRANSBCNT3: USB or ATA/ATAPI Transfer Byte Count Register 3

(XDATA at F0D9) 11−14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5.11 CMNDLNGTH: Command Length Register (XDATA at F0DA) 11−15. . . . . . . . . . . . . . . . . . .

11.5.12 PIOSPAS: PIO Transfer Speed (Assertion Time) Register (XDATA at F0DC) 11−15. . . . . .

11.5.13 PIOSPRC: PIO Transfer Speed (Recovery Time) Register (XDATA at F0DD) 11−16. . . . . .

11.5.14 DMASPAS: DMA Transfer Speed (Assertion Time) Register (XDATA at F0DE) 11−16. . . .

11.5.15 DMASPRC: DMA Transfer Speed (Recovery Time) Register (XDATA at F0DF) 11−16. . . .

11.5.16 Data Transfer Mode and Timing Reference Chart 11−17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6 ATA/ATAPI Group 2 Registers 11−19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.1 MCUBYTE0: MCU Data Byte_0 Register (XDATA at F0E0) 11−20. . . . . . . . . . . . . . . . . . . . .

11.6.2 MCUBYTE1: MCU Data Byte_1 Register (XDATA at F0E1) 11−20. . . . . . . . . . . . . . . . . . . . .

11.6.3 MCUBYTE2: MCU Data Byte_2 Register (XDATA at F0E2) 11−20. . . . . . . . . . . . . . . . . . . . .

11.6.4 MCUBYTE3: MCU Data Byte_3 Register (XDATA at F0E3) 11−20. . . . . . . . . . . . . . . . . . . . .

11.6.5 MCUACSL: MCU Access Address Low-Byte Register (XDATA at F0E4 11−21. . . . . . . . . . .

11.6.6 MCUACSH: MCU Access Address High-Byte Register (XDATA at F0E5) 11−21. . . . . . . . .

11.6.7 ATPINTRPT0: ATA/ATAPI Interrupt Register 0 and ATPINTMSK0: ATA/ATAPI

Interrupt Mask Register 0 (XDATA at F0E6, F0E7) 11−21. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.8 ATPINTRPT1: ATA/ATAPI Interrupt Register 1 and ATPINTMSK1: ATA/ATAPI

Interrupt Mask Register 1 (XDATA at F0E8, F0E9) 11−22. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.9 ATPSTATUS: ATA/ATAPI Interface Status Register (XDATA at F0EA) 11−23. . . . . . . . . . . .

11.6.10 SECWRPTL: Sector FIFO Write Pointer Low-Byte Register (XDATA at F0EB) 11−24. . . . .

11.6.11 SECWRPTH: Sector FIFO Write Pointer High-Byte Register (XDATA at F0EC) 11−25. . . .

11.6.12 WRPTBKUPL: Sector FIFO Write Pointer Backup Low-Byte Register

(XDATA at F0ED) 11−25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.13 WRPTBKUPH: Sector FIFO Write Pointer Backup High-Byte Register

(XDATA at F0EE) 11−25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.14 SECRDPTL: Sector FIFO Read Pointer Low-Byte Register (XDATA at F0EF 11−25. . . . . .

11.6.15 SECRDPTH: Sector FIFO Read Pointer High-Byte Register (XDATA at F0F0 11−26. . . . .

11.6.16 RDPTBKUPL: Sector FIFO Read Pointer Backup Low-Byte Register

(XDATA at F0F1 11−26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.17 RDPTBKUPH: Sector FIFO Read Pointer Backup High-Byte Register

(XDATA at F0F2 11−26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.18 ULRCVEXCNT: Ultrareceive Extra Word Count Register (XDATA at F0F9) 11−27. . . . . . . .

12 Electrical Specifications 12−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1 Absolute Maximum Ratings 12−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2 Recommended Operating Conditions 12−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3 Electrical Characteristics for the Digital Core, T

= 25°C, VCC = 3.3 V ±5%, VSS = 0 V 12−2. . . . . . .

A

12.4 Controller Input Supply Current, TA = 25°C, VCC = 3.3 V ±5%, VSS = 0 V 12−2. . . . . . . . . . . . . . . . . . .

12.5 Timing for 5-V Failsafe TTL Compatible LVCMOS I/O Buffer Used in the TUSB6250

ATA/ATAPI Interface 12−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.6 Electrical Characteristics for the Integrated USB 2.0 Transceiver, TA = 25°C,

VCC = 3.3 V ±5%, VSS = 0 V 12−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13 Application Information 13−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1 Crystal Selection and Reference Circuitry 13−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2 Reset Timing Reference 13−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

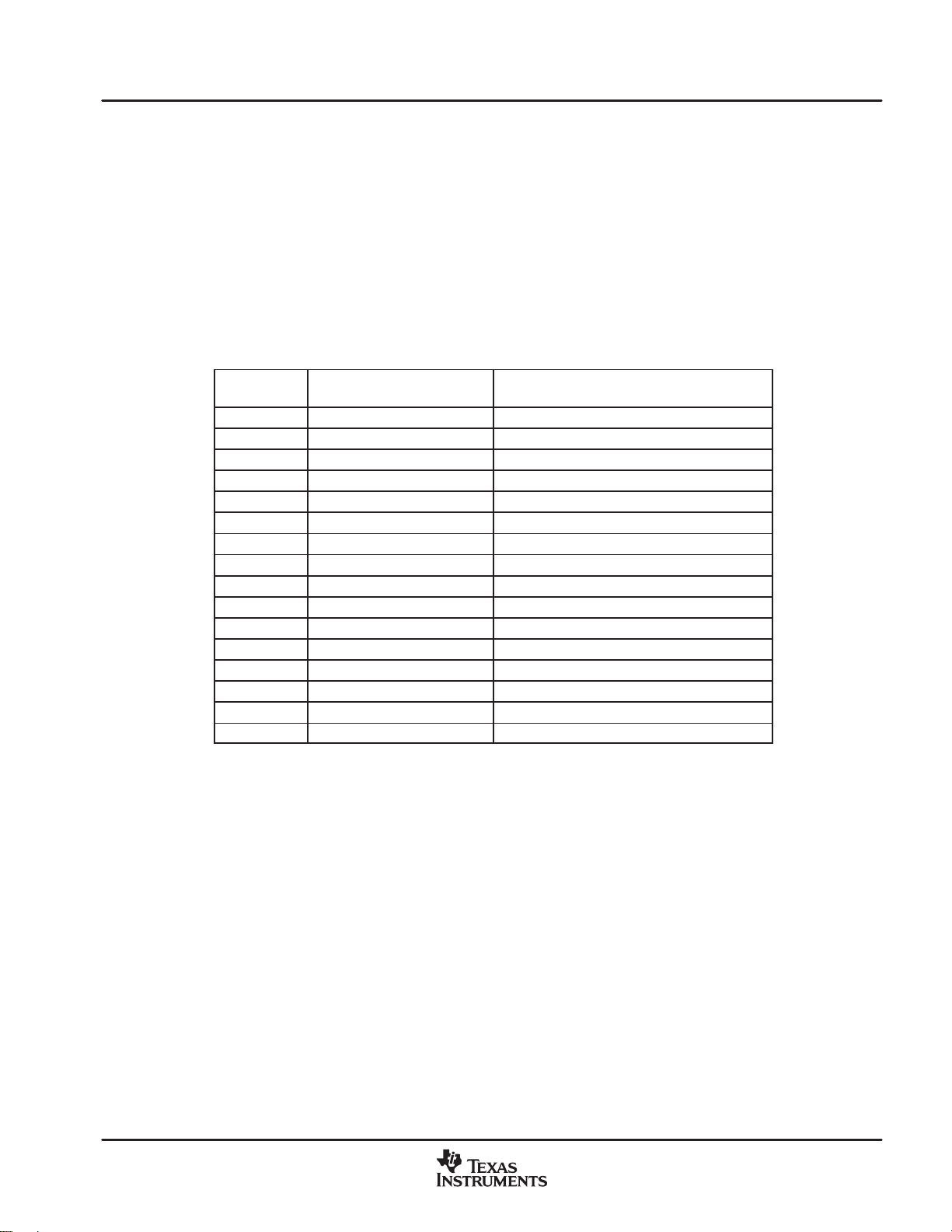

13.3 General ATA/ATAPI Device Application Information 13−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3.1 ATA/ATAPI Connector Pin Diagram 13−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3.2 Special Note About Shaded Signals 13−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3.3 Special Note About Pullup and Pulldown Resistors for ATA/ATAPI Signals 13−5. . . . . . . . .

13.3.4 Series Termination Required for Ultra DMA Operation 13−5. . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

SLLS535D − November 2006TUSB6250

Contents

Section Page

13.4 Compact Flash Storage Card Reader Application 13−6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.1 Brief Introduction 13−6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.2 Pin Assignment and Mapping 13−7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4.3 Power-Up Sequence 13−9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SLLS535D − November 2006 TUSB6250

vii

List of Illustrations

List of Illustrations

Figure Title Page

3−1 TUSB6250 Block Diagram 3−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3−2 USB 20 PEI (Parallel Interface Engine) Block Diagram 3−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

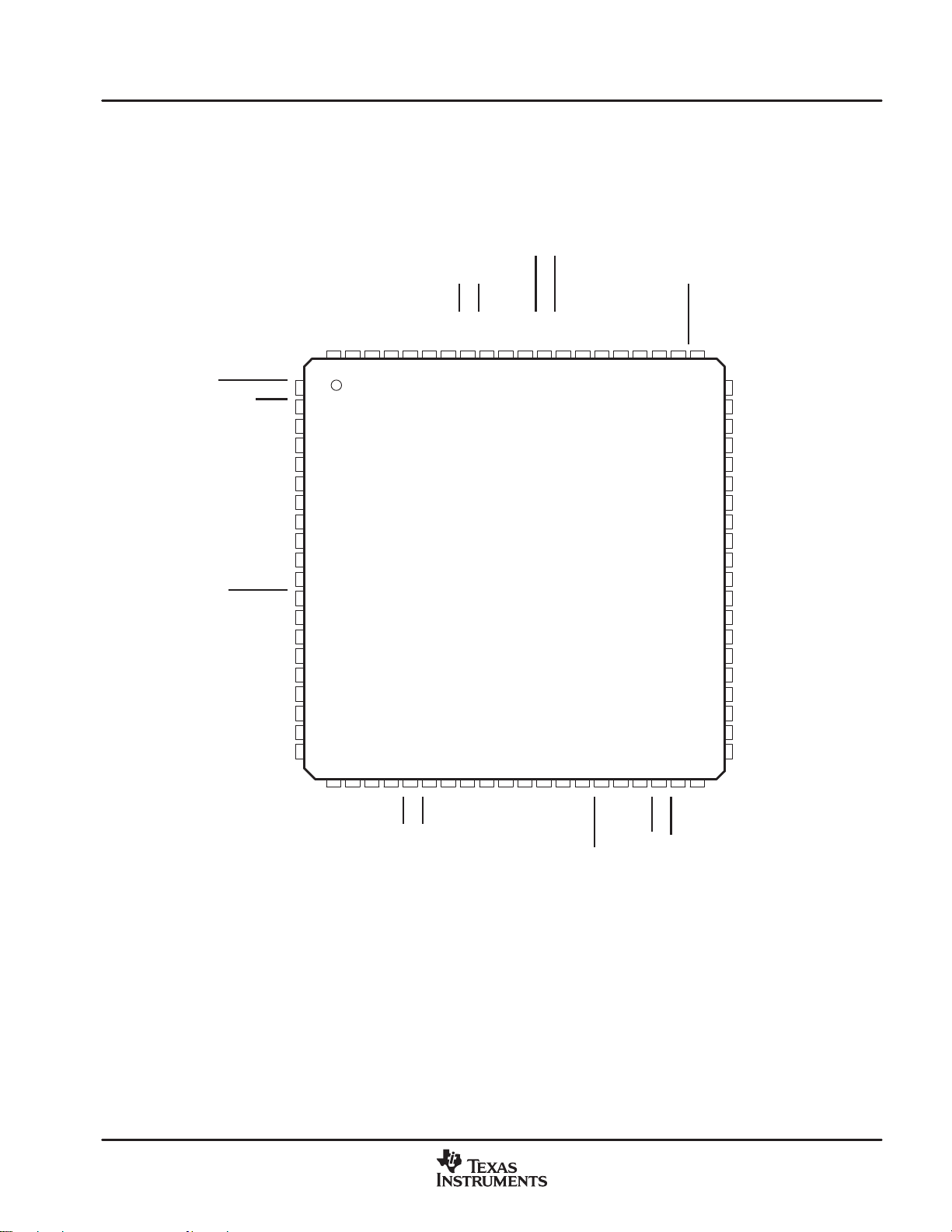

4−1 Controller 80-Pin TQFP Pin Diagram 4−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

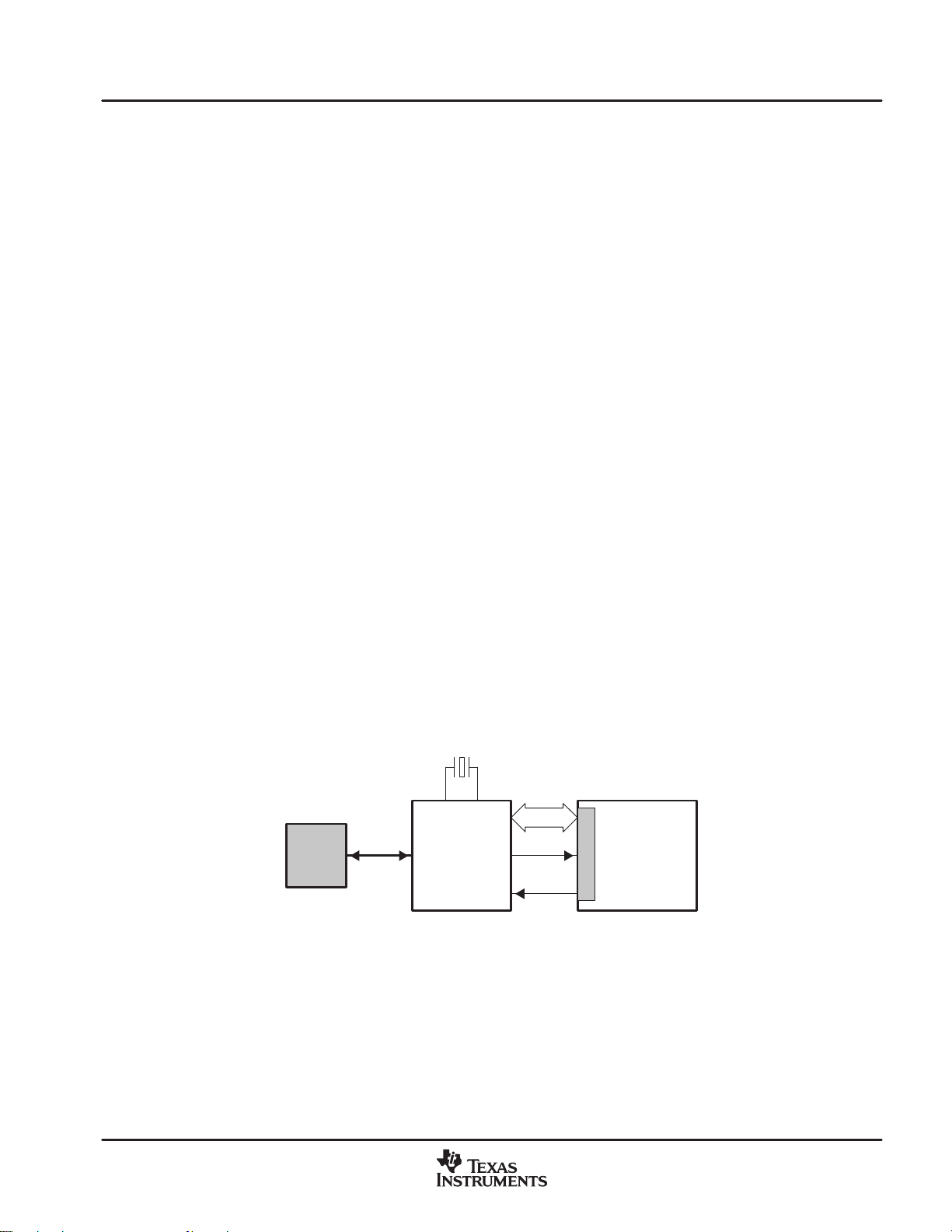

5−1 TUSB6250 Typical Application Diagram 5−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

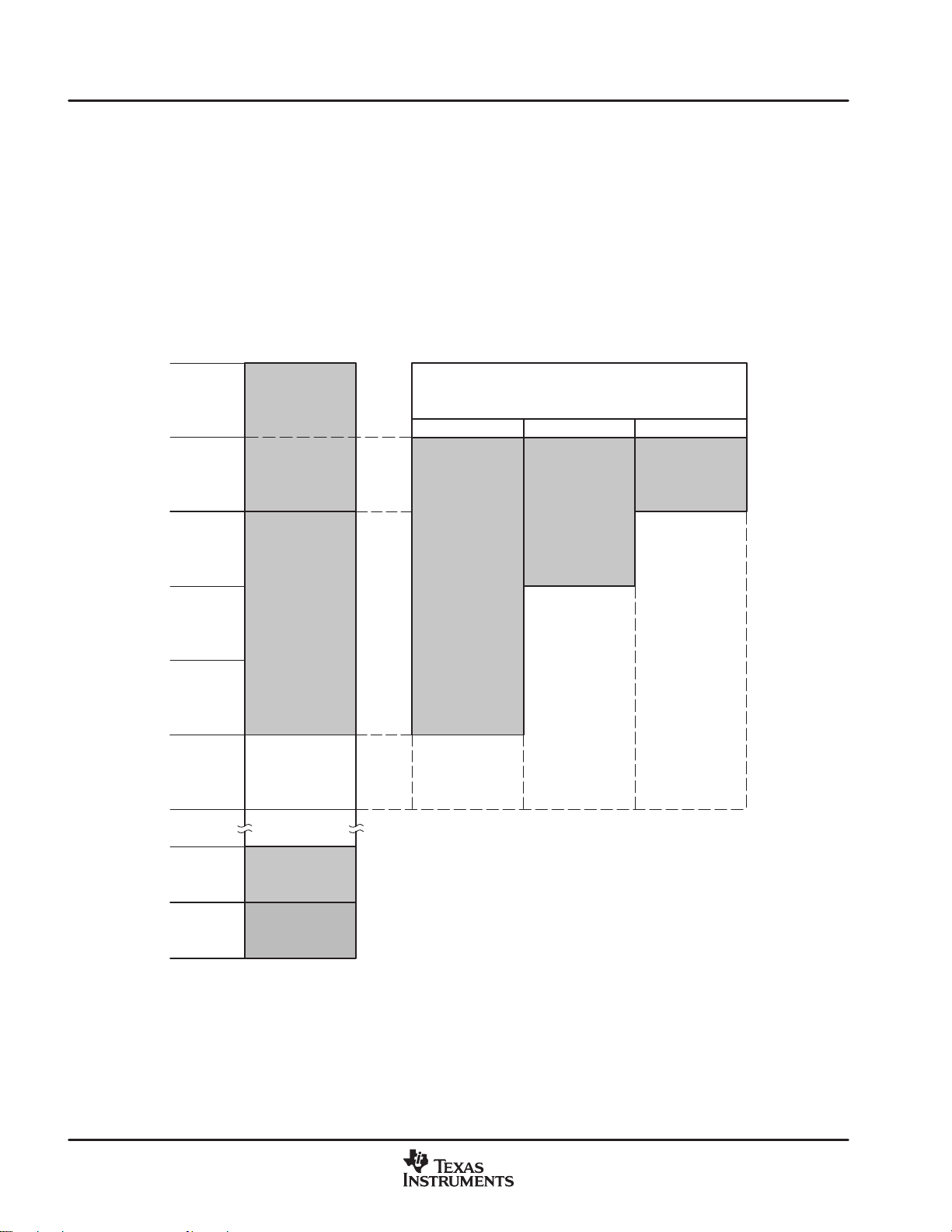

6−1 MCU Memory Map 6−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6−2 IDATA Space Memory Configuration 6−12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8−1 WAKCLK Interrupt and Wake-Up Status Change Illustration Logical Diagram 8−7. . . . . . . . . . . . . . . . . . . . .

8−2 IN-Endpoint Index Generation 8−16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8−3 OUT-Endpoint Index Generation 8−16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8−4 16-Bit EDB Data Buffer Address Generation From the Value of Buffer Base Address 8−16. . . . . . . . . . . . .

11−1 ATA/ATAPI-Port Data Flow Diagram 11−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11−2 TUSB6250 ATA/ATAPI Controller Block Diagram 11−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11−3 ATA/ATAPI Bus Powering and Reset Sequence 11−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13−1 Controller Reference Reset Timing Diagram 13−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

List of Tables

Table Title Page

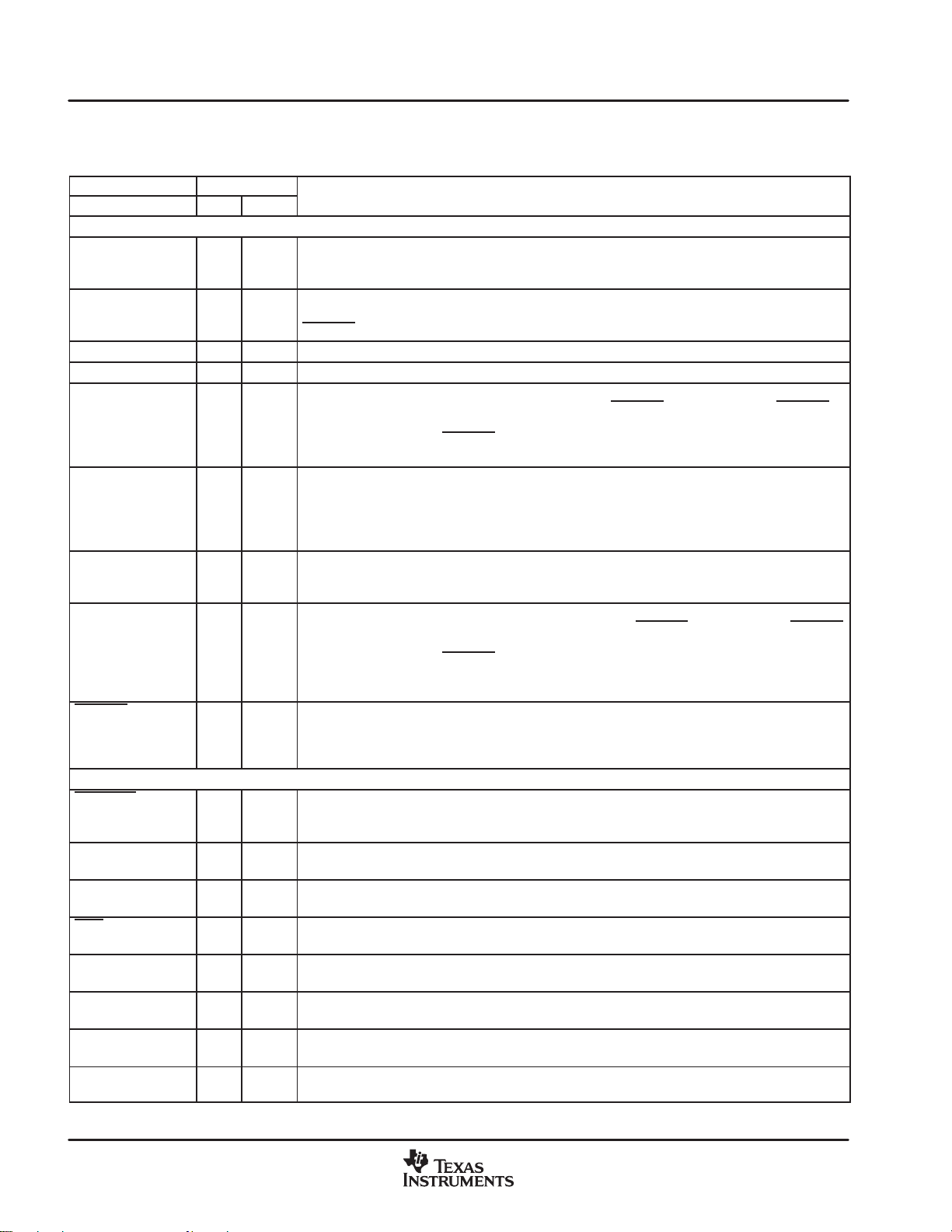

4−1 Controller Terminal Description (80-Pin TQFP) 4−2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6−1 XDATA Space Map [E000 → F0F9] 6−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6−2 Memory Mapped Registers Summary (XDATA Range: F000 → F0F9) 6−3. . . . . . . . . . . . . . . . . . . . . . . . . .

6−3 SFR Map [IDATA: 80 FF] (Shaded Area Indicates ESFRs) 6−8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7−1 8051 Standard/Extended Interrupt Location Map for Application Firmware 7−1. . . . . . . . . . . . . . . . . . . . . . .

7−2 Vector Interrupt Values 7−4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8−1 Register Setting for the WAKCLK Interrupt and Remote Wake-Up 8−8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8−2 Input/Output EDB-0 Registers 8−13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8−3 Input/Output EDB-0 Buffer Location as Defined by BZ[1:0] 8−13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8−4 EDB0 Buffer Locations (in SPRAM) 8−15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8−5 EDB Entries in MMR (n = 1 to 4) 8−16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9−1 Controller MCU GPIO Port Mapping 9−1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10−1 I2C EEPROM Signature in Descriptor Block 10−8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11−1 Task_File Registers (Group 0) 11−8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11−2 Group 1 Registers 11−10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11−3 ATA and ATAPI Command and Control Block Registers 11−14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11−4 PIO Mode and Timing Correlation Chart 11−18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11−5 Multiword DMA Mode and Timing Correlation Chart 11−19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11−6 Ultra DMA Mode and Timing Correlation Chart (applies to UDMA Write only) 11−19. . . . . . . . . . . . . . . . . .

11−7 Group 2 Registers 11−20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13−1 ATA/ATAPI Connector Pin Summary 13−3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

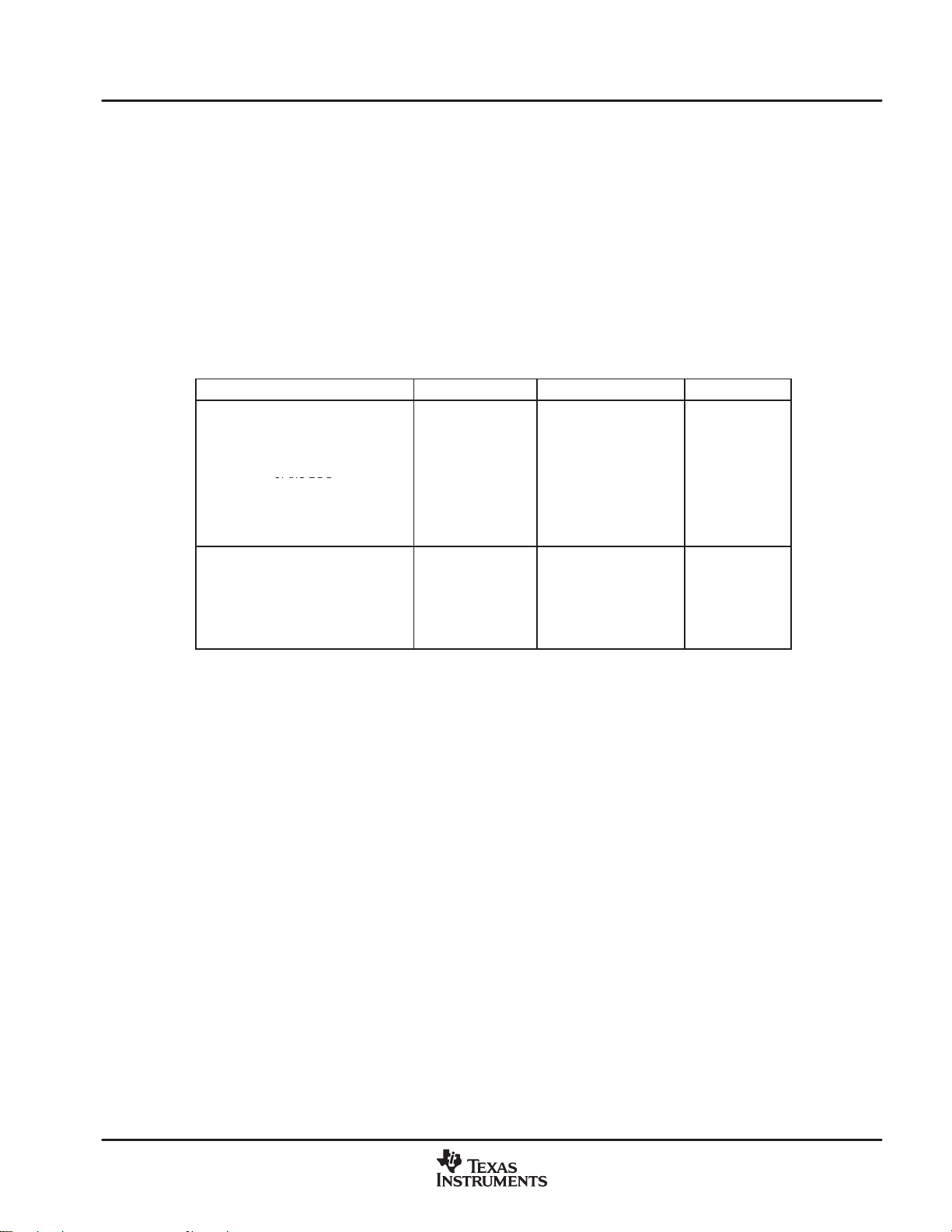

13−2 Compact Flash Power Consumption (Reference Only) 13−6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13−3 Compact Flash Card System Performance (Reference Only) 13−7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13−4 TUSB6250 Based Compact Flash Storage Card Reader Pin Assignment and Mapping 13−8. . . . . . . . . . .

viii

SLLS535D − November 2006TUSB6250

Controller Description

1 Controller Description

The TUSB6250 is a USB 2.0 HS-capable function controller with an integrated UTMI compliant PHY. The

TUSB6250 is intended as a USB 2.0 to AT A/ATAPI bridge for storage devices using a standard ATA or AT API

interface.

The TUSB6250 is designed to use both the fast performance of the state machine and the programmability

and flexibility of the embedded microcontroller and firmware. With the elaborative balance between the

microcontroller unit (MCU) and the state machine, in addition to its embedded fast MCU (up to 30 MIPS), eight

configurable endpoints, up to 40K bytes of configurable code, and data buffer SRAM, the TUSB6250 provides

a bridge solution to meet both the performance and flexibility requirement of the next-generation external

storage devices. With a low-power-consumption USB 2.0 integrated PHY, the TUSB6250 also enables the

true USB 2.0 high-speed bus-powered application.

1.1 Acronyms and Terms

This section lists and defines some terms and abbreviations used throughout this data manual.

R/O Read-only. Implies a certain register bit is read-only.

W/O Write-only. Implies a certain register bit is write-only . The read operation to this bit normally returns

a zero value.

R/W Read/write. Implies a certain register bit can be accessed with both write and read operations.

R/C Read/set-clear. Implies a certain register bit can be read and cleared to its reset default value by

the MCU writing a certain value to it. The write-to-clear value may vary and depends on the

condition defined in a particular register.

W/C Write/clear. Implies a register bit can be written to perform certain clear functions defined in a

particular register. The bit value being written to remains active for one clock cycle. It is cleared

thereafter automatically. The read operation to this bit always returns a zero value.

MCU Microcontroller unit. In this data manual, MCU refers to the microcontroller embedded in the

TUSB6250.

EDB Endpoint descriptor block. This is a set of registers used to define the characteristics of an endpoint

of a USB device.

UBM USB buffer manager. This is a major functional block of the TUSB6250.

SPRAM Single-port RAM

Little-endian For data with multiple bytes, little-endian means that the byte order is organized such that byte 0

is the least significant byte. The bit order within each individual byte is always the same regardless

of which endianness is used; that is, bit 7 is always the most-significant bit.

Big-endian For data with multiple bytes, big-endian means that the byte order is organized such that byte 0

is the most significant byte. The bit order within each individual byte is always the same regardless

of which endianness is used; that is, bit 7 is always the most-significant bit.

SLLS535D − November 2006 TUSB6250

1−1

Controller Description

1−2

SLLS535D − November 2006TUSB6250

2 Main Features

2.1 Universal Serial Bus (USB)

• Fully compliant with USB 2.0 specification: TID #40390418

• Integrated USB 2.0 UTMI compliant transceiver (PHY)

• Supports USB high speed (HS, 480 Mbits/sec) and full speed (FS, 12 Mbits/sec)

• Supports USB suspend/resume and remote wake-up operation

• Supports USB device-unique serial number by using on-chip unique die ID

• Supports eight configurable endpoints (four input and four output) with a user-programmable buffer size,

in addition to the default control endpoint (endpoint 0):

− Each endpoint can be configured for interrupt and bulk (double-buffered) transfers.

− All endpoints share the 4K-byte data buffer implemented in the SPRAM (single-port SRAM).

2.2 Microcontroller Unit (MCU)

• Integrated 60-MHz 8051 microcontroller with two clocks per cycle (up to 30 MIPS)

• Application code is loadable from either the USB host or the external EEPROM (via the I

• 8K bytes of ROM for the boot loader

• 1152 bytes of RAM with multiple bank selectable capability for the internal data buffer (IDATA space)

• 40K bytes of RAM, configurable for either code or data space, which provides flexibility to the end product

application:

− 32K-byte code RAM with 8K-byte sector buffer data space

− 16K-byte code RAM with 24K-byte sector buffer data space

− 8K-byte code RAM with 32K-byte sector buffer data space

• Master I

transfer speed.

• Up to 13 GPIOs and three general-purpose open-drain outputs can be used for end-product-specific

functions.

2

C interface controller for external device accesses capable of 100 Kbits/sec or 400 Kbits/sec

Main Features

2

C interface)

2.3 ATA/ATAPI Interface Controller

• Supports USB mass storage device class specification bulk-only transfer protocol

• Glueless interface to ATA and ATAPI drives with full ATA and ATAPI protocol support

• High-performance DMA engine supports all PIO, multiword DMA, and UDMA transfer modes up to UDMA

mode 4 (UDMA-66 or ATA-66).

• Correctly handles all 13 cases in bulk-only transfer protocol under all supported transfer modes.

• Fully programmable ATA/ATAPI interface access timing

• Provides multiple flexible transfer options to achieve both high-speed transfer by the state machine and

high flexibility with MCU involvement:

− Fully manual transfer (both command and data) by the MCU

− Semi-automatic transfer with command transfer by the MCU and data transfer by the state machine

− High-performance fully automatic data transfer mainly by the state machine with few MCU

involvements

• Supports mass-storage devices compatible with the ATA/ATAPI-5 specification:

− Hard-disk drive

− DVD/CD-ROM

SLLS535D − November 2006 TUSB6250

2−1

Main Features

− CD-R/W, DVD-R/W

− Compact flash

− PCMCIA type II card or hard drive

− MO drive

• Dual-drive support

− Capable of supporting one master and one slave drive in any combination of ATA and ATAPI.

• Provides easy control to put the ATA/ATAPI bus into a high-impedance state through one register bit

setting.

• 5-V failsafe I/Os for the ATA/ATAPI interface

2.4 General Features

• Operates on a 24-MHz external crystal with on-chip APLL

• Low-power mode (compliant with bus power requirement of <500 µA)

• 3.3-V operation with 1.8-V core operating voltage provided by an on-chip 1.8-V voltage regulator

• Available in an 80-pin TQFP package

2−2

SLLS535D − November 2006TUSB6250

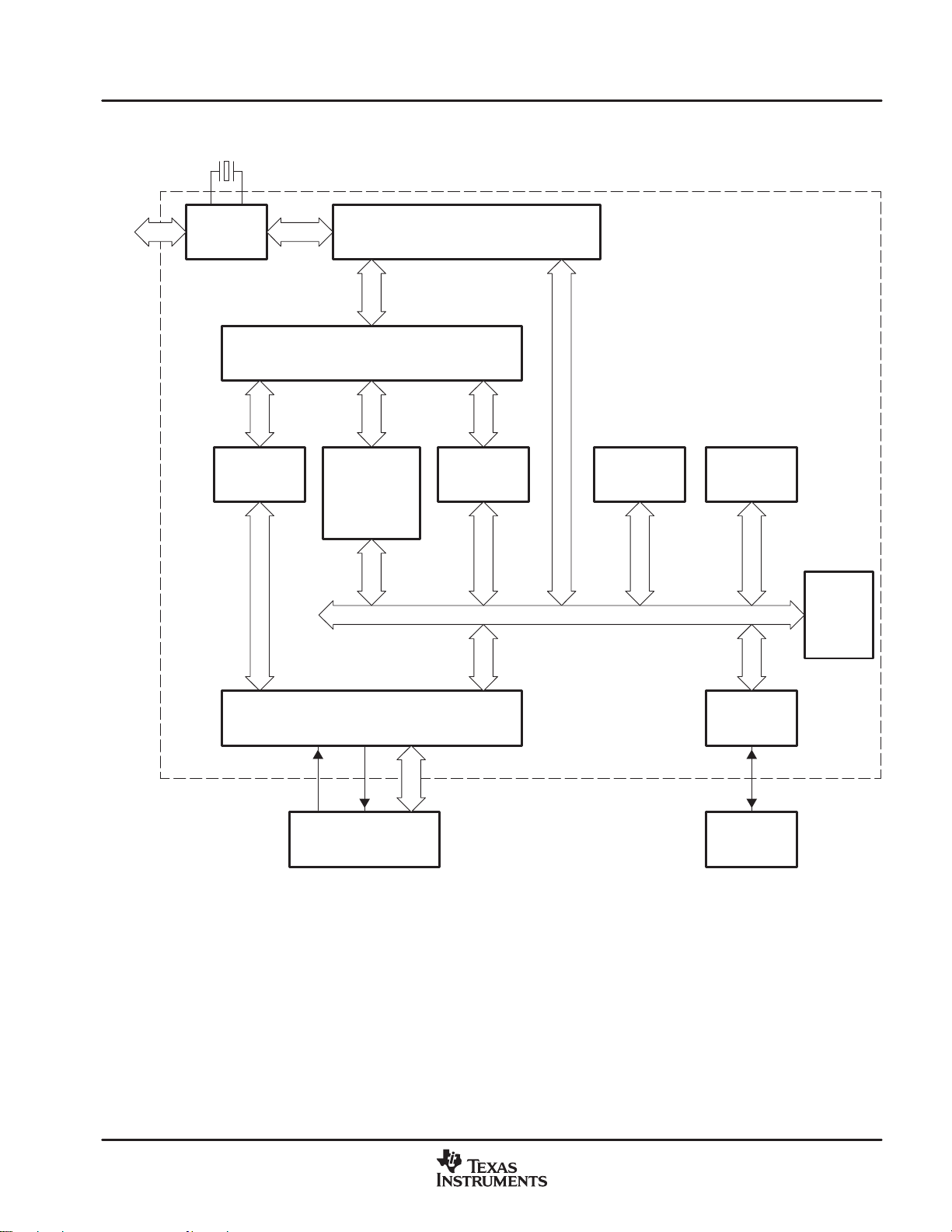

3 Device Block Diagram

24 MHz

Device Block Diagram

USB

Host

USB 2.0

UTMI

8K Byte

(2K × 32)

Data RAM

(See Figure 3−2)

UBM

(USB Buffer Manager)

24K Byte

(6K × 32)

Configurable

RAM for

Code or Data

USB 2.0 PIE

4K Byte

(1K × 32)

SPRAM

8K × 8

Code

RAM

8K × 8

ROM

8051

(60 MHz)

ATA/ATAPI Interface Controller

Standard IDE Devices

Figure 3−1. TUSB6250 Block Diagram

I2C

Controller

I2C

EEPROM

SLLS535D − November 2006 TUSB6250

3−1

Device Block Diagram

Frame Timer

UTMI-Compliant

Phy

Bus Monitor USB Reg. MCU

Transaction Handler

UBM

(USB Buffer Manager)

Figure 3−2. USB 2.0 PIE (Parallel Interface Engine) Block Diagram

3−2

SLLS535D − November 2006TUSB6250

4 Device Parameter Information

4.1 Pin Diagram

SUSPEND

P3.0/SIN

P3.1/SOUT

DVDD

DVDD18

DGND

TQFP PACKAGE

(TOP VIEW)

P2.0

P3.2/CD1

P3.3/CD2

P3.4

P3.5

P2.1/PWR100

P2.2/PWR500

P2.3

DGND

P2.4

P2.5

Device Parameter Information

DVDD

P2.6

RST_ATA

DVREGEN

RSTI

P2.7

VBUS

RPU

AVDD

AGND

PLLVDD18

UDVDD18

AGND

R1

VREGEN

AVDD

DP

DM

AGND

XTAL2

XTAL1

TSTMODE1

TSTMODE2

79 78 77 76 7580 74 72 71 7073

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

22 23

24

SCL

SDA

DVDD

25 26 27 28

CS1

CS0

P3.7

29

DA2

DGND

69 682167 66 65 64

30 31 32 33

DA0

DA1

P3.6

34 35 36 37 38 39 40

DVDD

INTRQ

IORDY

DVDD18

DMACK

63 62 61

DIOR

DGND

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

DIOW

DMARQ

DD7

DD8

DD6

DD9

DGND

DD5

DD10

DVDD

DD4

DD11

DD3

DD12

DGND

DD2

DD13

DVDD

DD1

DD14

DD0

DD15

Figure 4−1. Controller 80-Pin TQFP Pin Diagram

SLLS535D − November 2006 TUSB6250

4−1

Device Parameter Information

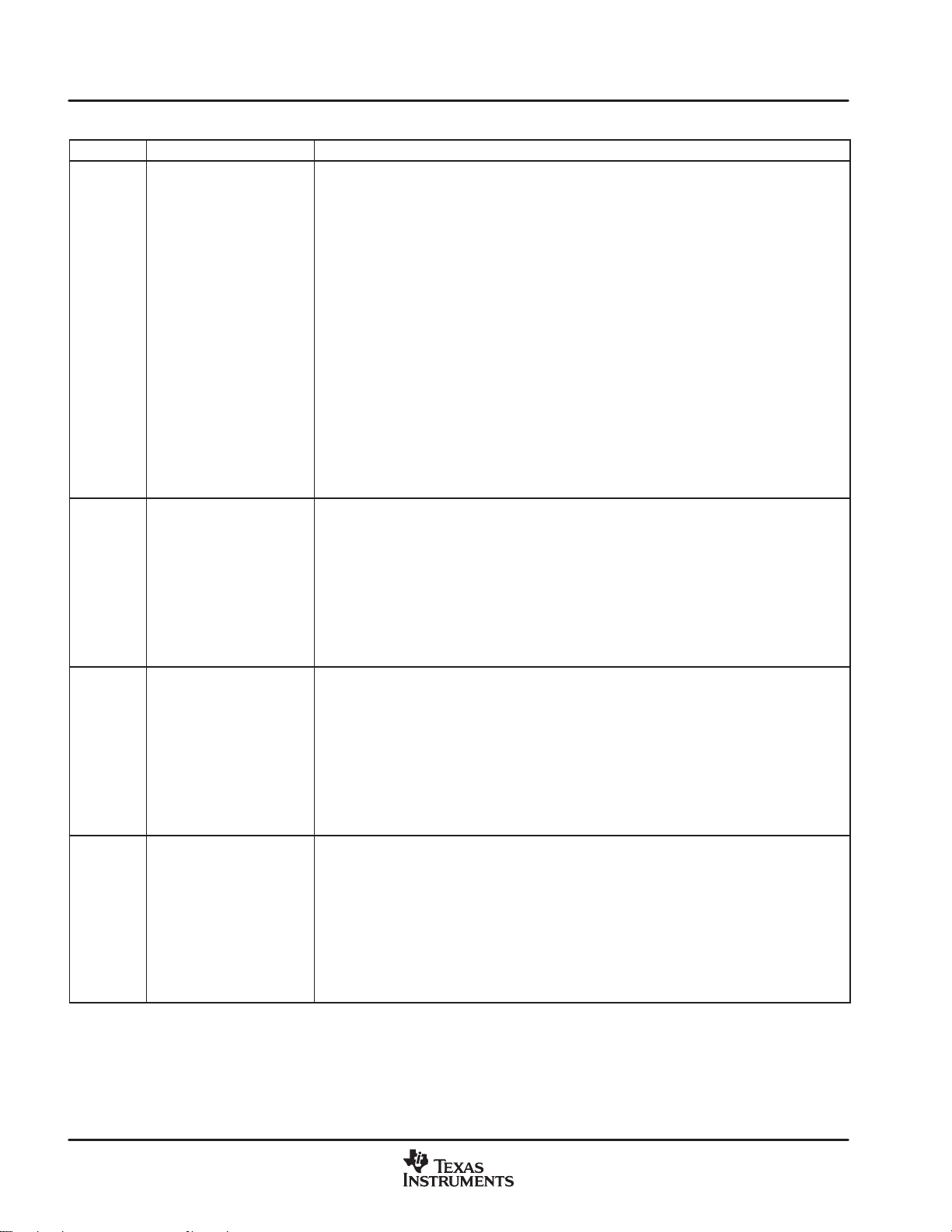

DESCRIPTION

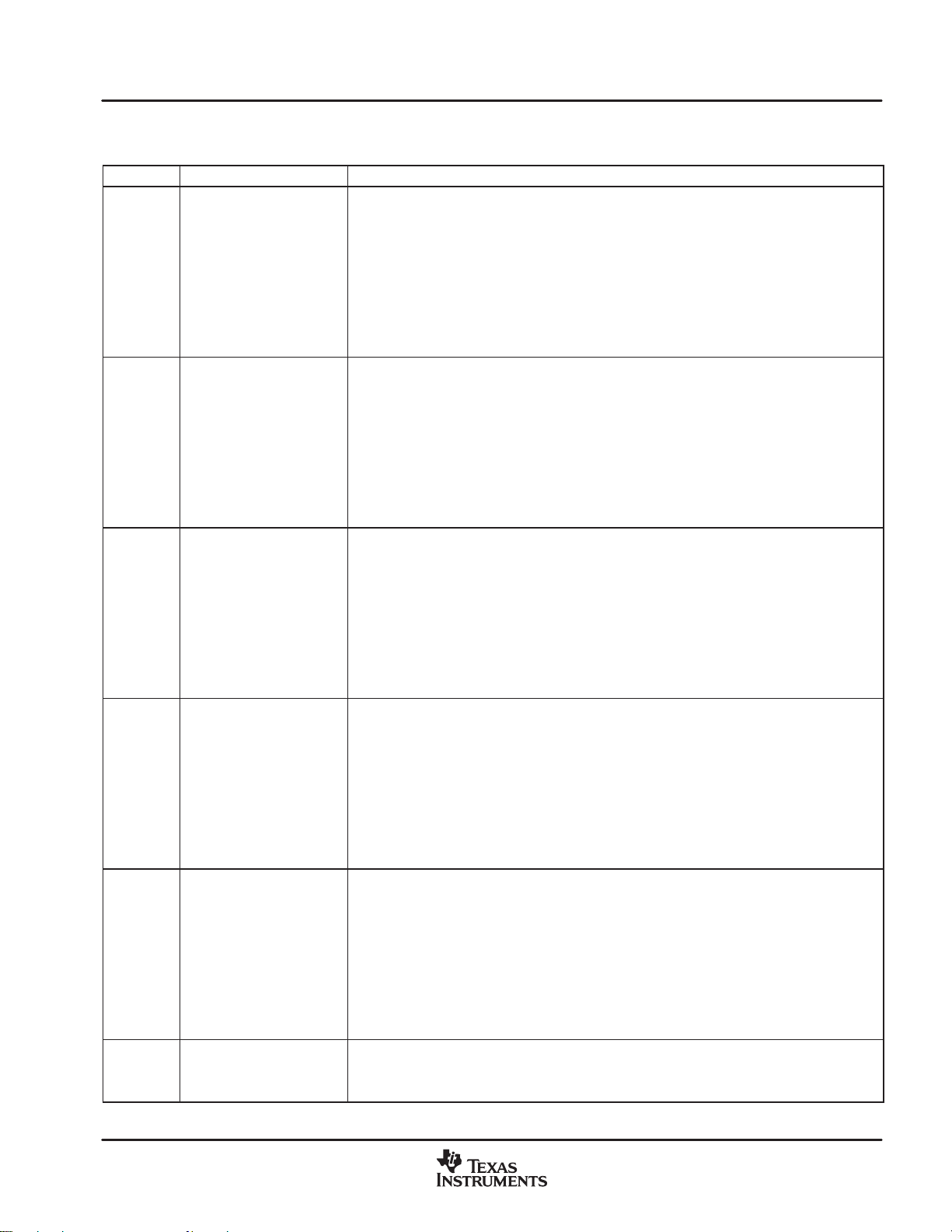

4.2 Terminal Functions

Table 4−1. Controller Terminal Description (80-Pin TQFP)

TERMINAL I/O

NAME NO. TYPE NOTES

INTEGRATED USB 2.0 UTMI-COMPLIANT PHY

AGND 7, 10,16GND Analog ground. All ground terminals should be connected together externally through a

AVDD 6, 13 PWR 3.3-V supply voltage for the integrated USB 2.0 UTMI-compliant PHY’s internal analog circuitry. This

DM 15 I/O USB differential data minus

DP 14 I/O USB differential data plus

PLLVDD18 8 PWR 1.8-V supply for the internal PLL circuitry of the integrated USB 2.0 UTMI-compliant PHY. An internal

R1 11 I/O External reference resistor. An internally generated band-gap voltage is placed on this resistor. The

RPU 5 I/O Pullup resistor connection. This terminal is used to attach and detach the full-speed indicator resistor

UDVDD18 9 PWR 1.92-V supply for the internal digital circuitry of the integrated USB 2.0 UTMI-compliant PHY. An

VREGEN 12 I Voltage regulator enable (active-low). Two internal 3.3-V to 1.8-V voltage regulators supply the digital

CONTROLLER GENERAL

DVREGEN 1 I (4) This active-low terminal is used to enable the 3.3-V to 1.8-V voltage regulator in the TUSB6250’s

P3.0/SIN 79 I/O (1)(6)

P3.1/SOUT 78 I/O (1)(6)

RSTI 2 I (4) The TUSB6250 master reset signal. This active-low terminal is the master reset signal for the

SCL 21 O (7)(8) Master I2C controller: clock signal for external I2C serial EEPROM. The internal 100-µA pullup resistor

SDA 22 I/O (4)(7)

TSTMODE1

TSTMODE21920

VBUS 4 I (5)(10) This terminal monitors the status of the USB upstream VBUS. It has the internal pulldown resistor

I (4)(8) These terminals are used for factory test of the TUSB6250. During normal operation, these terminals

low-impedance path. All bypass capacitors to PLLVDD18, UDVDD18, and AVDD should connect to

ground through a low-impedance path.

supply is also regulated internally down to 1.8 V for use by the PHY’s internal digital circuitry when

VREGEN is asserted. Bypass capacitors to ground are required on these terminals.

voltage regulator generates this supply when terminal VREGEN

de-asserted, 1.8 V must be supplied externally. Bypass capacitance is required on this terminal

regardless of the state of VREGEN. It is recommended that the capacitance on this terminal not be

less then 1 µF.

current through the resistor is mirrored internally to generate the current and voltage used by the

internal analog circuitry. This pin has nominally 1.21 V dc. An external 5.9-kΩ ±1% resistor must be

placed between this terminal and ground. It is recommended that the resistor be placed as close as

possible to this terminal with a minimal trace length to ground.

electrically to/from the DP signal line. An external 1.5-kΩ ±5% resistor must be placed between RPU

and AVDD.

internal voltage regulator generates this supply when terminal VREGEN

is de-asserted, 1.92 V must be supplied externally. Bypass capacitance is required on this terminal

regardless of the state of VREGEN

less then 1 µF. Do not connect the UDVDD18 terminal to the PLLVDD18 or DVDD18 terminal, because

their voltages differ.

and PLL circuitry when this terminal is asserted. When this terminal is de-asserted, the voltage

regulators are disabled and 1.8 V must be supplied externally. TI recommends that this terminal be

tied to ground during normal operation.

digital core. When this terminal is de-asserted, the voltage regulator is disabled and 1.8 V must be

supplied externally. TI recommends that this terminal be tied to ground during normal operation.

This dual-function terminal can be used as either GPIO or the serial data input of the integrated 8051

(8)

microcontroller serial port. The power-up default is to have its internal pullup activated.

This dual-function terminal can be used as either GPIO or the serial data output of the integrated 8051

(8)

microcontroller serial port. The power-up default is to have its internal pullup activated.

TUSB6250. See Section 13.2, Reset Timing Reference, for detailed reset timing information.

on this terminal is always enabled.

Master I2C controller: data signal for external I2C serial EEPROM. The internal 100-µA pullup resistor

(8)

on this terminal is always enabled.

must be left open.

enabled as the power-on reset default.

. It is recommended that the capacitance on this terminal not be

is asserted. When VREGEN is

is asserted. When VREGEN

4−2

SLLS535D − November 2006TUSB6250

Device Parameter Information

DESCRIPTION

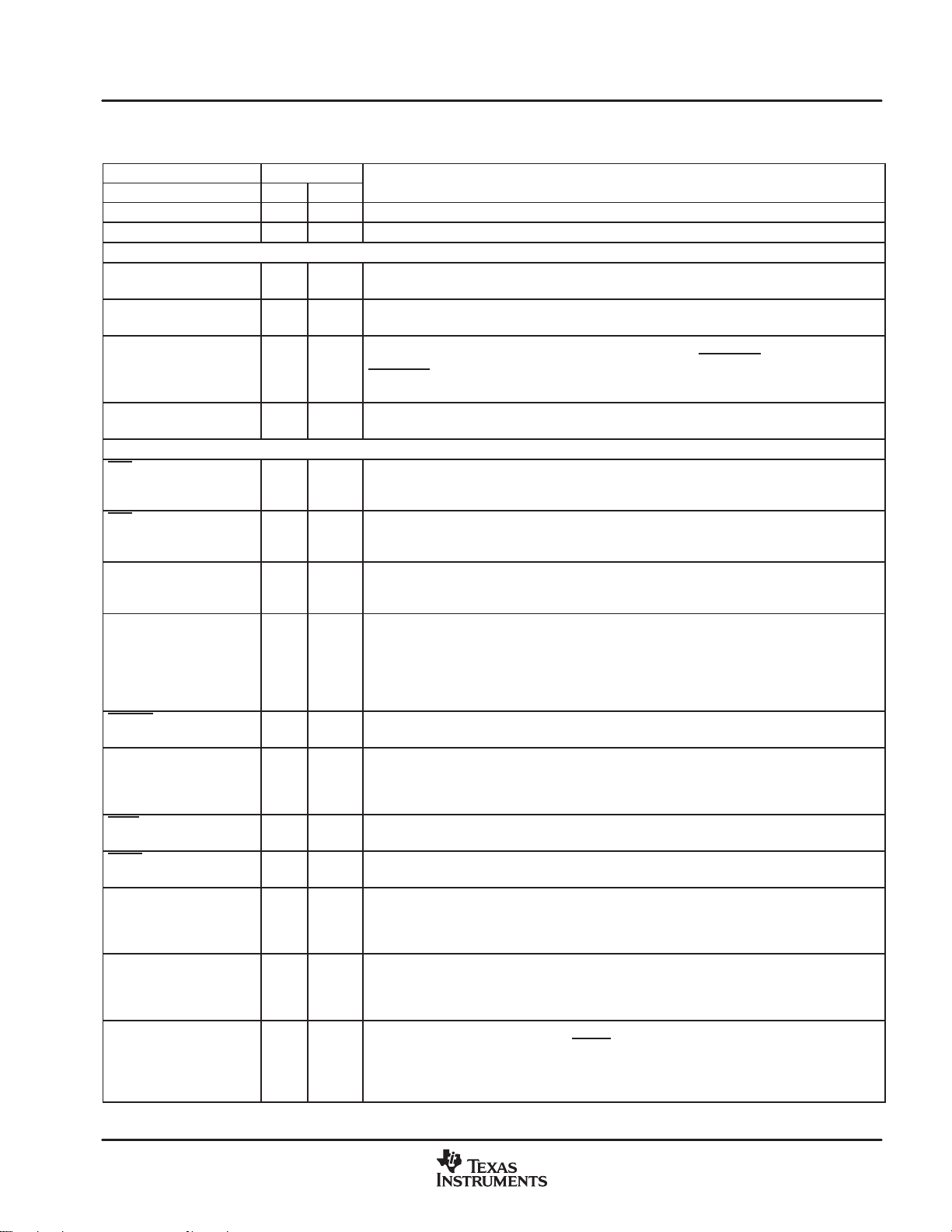

Table 4−1. Controller Terminal Description (80-Pin TQFP) (Continued)

TERMINAL I/O

NAME NO. TYPE NOTES

XTAL2 17 O (12) 24-MHz crystal output. This terminal has a 1.8-V LVCMOS output buffer.

XTAL1 18 I (11) 24-MHz crystal input. This terminal has a 1.8-V LVCMOS input buffer.

CONTROLLER POWER/GROUND

DGND 27,37,48,

56,66,75

DVDD 23,33,45,

53,63,77

DVDD18 32, 76 PWR 1.8-V power supply for the internal digital circuitry of the TUSB6250. An internal voltage

SUSPEND 80 O (1) Suspend status indication. This terminal is low during normal operation and active high during

ATA/ATAPI INTERFACE

CS1 25 O (2)(9) ATA/ATAPI: Drive chip select-1. Used to select the control block registers defined by the

CS0 26 O (2)(9) ATA/ATAPI: Drive chip select-0. Used to select the command block registers defined by the

DA [2:0] 28, 31,

29

DD [15:0] 41,43,46,

49,51,54,

57,59,60,

58,55,52,

50,47,44,

42

DMACK 35 O (2)(9) ATA/ATAPI: DMA acknowledge. This terminal should be connected to the corresponding pin of

DMARQ 40 I (5)(10) ATA/ATAPI: DMA request. This 5-V fail-safe terminal has an internal controllable pulldown

DIOR 38 O (2)(9) ATA/A TAPI: Read strobe signal. This terminal should be connected to the corresponding pin of

DIOW 39 O (2)(9) ATA/ATAPI: W rite strobe signal. This terminal should be connected to the corresponding pin of

INTRQ 34 I (5)(9) ATA/ATAPI: Interrupt request. The AT A device asserts this signal when it has a pending interrupt.

IORDY 36 I (5)(9) ATA/ATAPI: Channel ready. This 5-V fail-safe terminal has internal configurable pullup and

P3.6 30 I/O (2)(5)

GND Digital circuit ground terminals. Each ground terminal should be directly connected through a

PWR 3.3-V power-supply terminals for the internal I/O circuitry . Decoupling and filtering capacitors are

O (2)(9) ATA/ATAPI: These three address lines are used to select the ATA/ATAPI drive registers as

I/O (2)(5)

low-impedance path to the ground plane.

required on these power supply terminals.

regulator generates this supply voltage when terminal DVREGEN

DVREGEN

required on these pins.

suspend. It can be used for external logic power-down operations.

ATA/ATAPI-5 specification. This terminal should be connected to the corresponding pin of the

ATA/ATAPI interface connector on the end-product PCB.

ATA/ATAPI-5 specification. This terminal should be connected to the corresponding pin of the

ATA/ATAPI interface connector on the end-product PCB.

defined by the ATA/ATAPI-5 specification. These terminals should be connected to the

corresponding pins of the ATA/ATAPI interface connector on the end-product PCB.

ATA/ATAPI: 16-bit I/O data bus. These terminals are all 5-V fail-safe with internal controllable

pulldown resistors. These terminals should be connected to the corresponding pins of the

(10)

ATA/ATAPI interface connector on the end-product PCB.

the ATA/ATAPI interface connector on the end-product PCB.

resistor. The power-up default is the pulldown resistor enabled. This terminal should be

connected to the corresponding pin of the ATA/ATAPI interface connector on the end-product

PCB.

the ATA/ATAPI interface connector on the end-product PCB.

the ATA/ATAPI interface connector on the end-product PCB.

This 5-V fail-safe terminal has internal configurable pullup and pulldown resistors. The power-up

default is the pulldown resistor enabled. This terminal should be connected to the corresponding

pin of the ATA/ATAPI interface connector on the end-product PCB.

pulldown resistors. The power-up default is the pullup resistor enabled. This terminal should be

connected to the corresponding pin of the ATA/ATAPI interface connector on the end-product

PCB.

5-V fail-safe general-purpose I/O with internal configurable pullup and pulldown resistors. This

(9)

terminal can be used as a GPIO or PDIAG

developer’s custom firmware. After power-on reset, this terminal defaults as input with the

internal pullup resistor enabled. The MCU can reconfigure the pullup and pulldown resistors, if

desired.

is de-asserted, 1.8 V must be supplied externally. Bypass capacitors to ground are

function to be implemented by the end-product

is asserted. When

SLLS535D − November 2006 TUSB6250

4−3

Device Parameter Information

DESCRIPTION

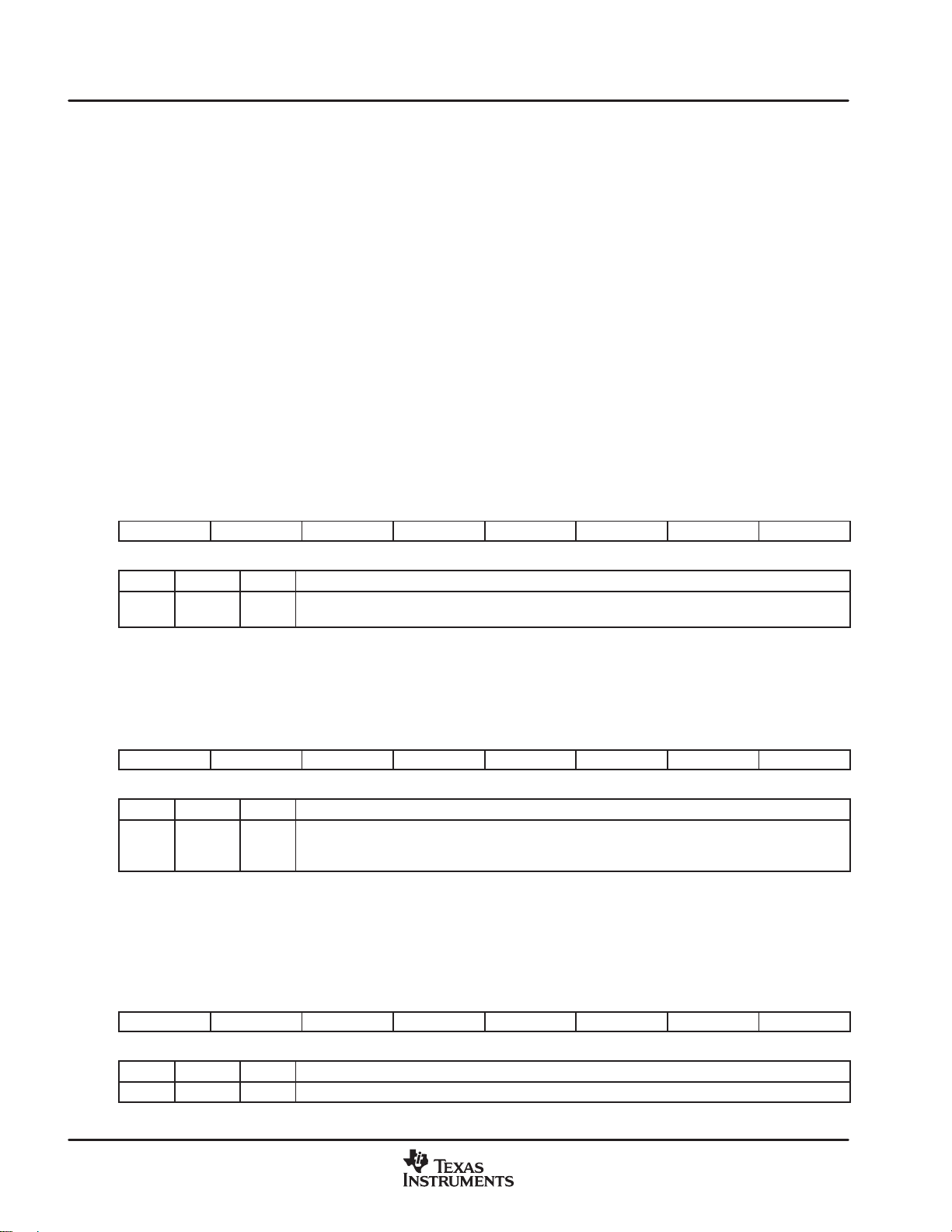

Table 4−1. Controller Terminal Description (80-Pin TQFP) (Continued)

TERMINAL I/O

NAME NO. TYPE NOTES

P3.7 24 I/O (2)(5)

RST_ATA 61 O (2)(9) ATA/ATAPI: Asynchronous drive-reset signal. This terminal should be connected to the corresponding

OTHER GPIOs (GENERAL-PURPOSE I/Os)

P2.7 3 I/O (1)(6)

P2.6

P2.5

P2.4

P2.3 67 O (3) General-purpose open-drain output without internal pullup and pulldown resistors.

P2.2/

PWR500

P2.1/

PWR100

P2.0 74 I/O (2)(5)

P3.5

P3.4

P3.3/CD2

P3.2/CD1

NOTES: 1. 3-state 3.3-V LVCMOS output (±8-mA drive/sink).

62

I/O (2)(5)

64

65

68 O (3) General-purpose open-drain output. This terminal can be controlled by the firmware to inform the

69 O (3) General-purpose open-drain output. During the USB enumeration phase, This terminal is asserted by

7071I/O (2)(5)

7273I/O (2)(5)

2. 3-state 3.3-V LVCMOS output, 5-V fail-safe (±8-mA drive/sink). The 5-V fail-safe means this output buffer can be exposed to a 5-V

application environment. Although it can not output 5 V when interfacing with the 5-V ATA/ATAPI device, an external pullup resistor

to a 5-V power source can be used to pull the output voltage up to 5 V. The fail-safe buffer is designed to be protected from damage

under a condition where the buffer is exposed to 5 V, while the device is powered down (its supply voltage is zero).

3. Open-drain output (8-mA sink), 5-V fail-safe, without internal pullup and pulldown resistors.

4. 3.3-V LVCMOS hysteresis input.

5. TTL-compatible, 5-V fail-safe, hysteresis input.

6. 3.3-V LVCMOS input without hysteresis.

7. Open-drain output (4-mA sink) with an internal pullup resistor.

8. Internal 100-µA active pullup resistor.

9. Configurable internal 200-µA active pullup and pulldown resistors.

10. Controllable internal 200-µA active pulldown resistor

11. 1.8-V LVCMOS input buffer

12. 1.8-V LVCMOS output buffer

5-V fail-safe general-purpose I/O with internal configurable pullup and pulldown resistors. This terminal

can be used as a GPIO or DASP

(9)

firmware. After a power-on reset, this terminal defaults as input with the internal pullup resistor enabled.

The MCU can reconfigure the pullup and pulldown resistors, if desired.

pin of the ATA/ATAPI interface connector on the end-product PCB.

General-purpose I/O with an internal controllable pullup resistor. After a power-on reset, this terminal

defaults as an input with an internal pullup resistor activated. The MCU can disable the pullup resistor

(8)

if desired.

5-V fail-safe general-purpose I/O with internal configurable pullup and pulldown resistors. After

power-on reset, these terminals default as inputs with the internal pullup resistor activated. The MCU

(9)

can reconfigure the pullup and pulldown resistors if desired.

ATA/ATAPI device connected to the TUSB6250 that the end-product device (including the TUSB6250

itself) is allowed to draw 500 mA from the USB after the device is fully enumerated and configured as

a USB-powered device.

the boot code to inform the ATA/ATAPI device connected to the TUSB6250 that the end-product device

(including the TUSB6250 itself) is allowed to draw 100 mA from the USB. After the boot code

relinquishes control to the firmware when USB enumeration, configuration, and firmware download are

finished, the firmware can reconfigure the function of this terminal for other usage, as long as such

usage is not conflicting with the previous usage, which, for example, can be implemented in the end

product for power sequencing control purposes. It should be noted that, for self-powered applications,

if VBUS from the USB is not present (for example, the USB cable is not connected) during boot time,

the boot code does not assert this terminal. In this condition, it is the responsibility of firmware to assert

this terminal, once the firmware is downloaded and gains control.

5-V fail-safe general-purpose I/O with internal configurable pullup and pulldown resistors. After

power-on reset, this terminal defaults as an input with the internal pulldown resistor activated. The MCU

(9)

can reconfigure the pullup and pulldown resistors if desired.

5-V fail-safe general-purpose I/O with internal configurable pullup and pulldown resistors. After

power-on reset, these terminals default as inputs with an internal pullup resistor activated. The MCU

(9)

can reconfigure the pullup and pulldown resistors, if desired. These two terminals can be used as

remote wake-up event inputs. The end-product developer’s custom firmware can use these two

terminals to implement some end-product-specific functions, such as cartridge insertion detection,

eject button pressed, or external control input to request the end-product custom firmware to put the

TUSB6250’s ATA/ATAPI bus into the high-impedance state.

5-V fail-safe general-purpose I/O with internal configurable pullup and pulldown resistors. After

power-on reset, these terminals default as inputs with an internal pullup resistor activated. The MCU

(9)

can reconfigure the pullup and pulldown resistors, if desired. These terminals can be used as GPIOs

or compact flash card insertion/removal detection inputs implemented by the end-product developer’s

custom firmware. These terminals are remote wake-up capable inputs, if enabled.

function, which is implemented by the end-product developer’s custom

4−4

SLLS535D − November 2006TUSB6250

4.3 Device Operation

4.3.1 Device Master Reset

An external master reset signal, asynchronous to the TUSB6250 internal clock, is needed to reset the

TUSB6250. This reset is referred to as the power-on reset throughout this document, which is connected to

the RSTI

terminal of the TUSB6250. Because the TUSB6250 has built-in noise debouncing circuitry, it also

requires a valid clock signal present during the required active-low master reset window. For the details of the

master reset timing requirement, see Section 13.2, Reset Timing Reference.

4.3.2 Clock Generation

The TUSB6250 requires an external 24-MHz crystal to be used. The integrated USB 2.0 UTMI-compliant PHY

generates all of the clock signals needed for the PHY analog, PLL, and digital logic. The PHY also generates

a 60-MHz clock used in the internal digital core of the TUSB6250.

4.3.3 Device Initialization

Because the TUSB6250 contains an integrated MCU, the device initialization process contains the following

two parts:

• Hardware registers and state machines are cleared to their defined default reset state after power-on reset

initialization. The TUSB6250 powers up with a default USB function address of zero and is disconnected

from the USB bus.

Device Parameter Information

• The MCU executes a bootloader program in ROM (starting from address 0000h) to fetch the valid

application code from the external source and prepare for USB enumeration. The application code, once

in charge, may perform some initialization functions to configure the TUSB6250 to meet the requirement

of a particular end-product application.

Because the application code (firmware) space is in the internal RAM, the TUSB6250 firmware needs to be

downloaded from an external source into the RAM space designated for code usage (see Section 6.1, MCU

Memory Map, for detailed information).

After power-on reset is applied to the TUSB6250, the integrated MCU executes the bootloader program (also

referred as boot code) residing in the on-chip 8K-byte ROM mapped to the MCU program memory space; this

process is also referred to as booting.

The major tasks of the boot code are:

• To fetch the descriptors required for itself or the firmware to perform USB enumeration

• To download the application firmware from one of the two external sources available during booting: either

from an external I

2

C EEPROM connected to the I2C interface of the TUSB6250 or from the host PC via

the USB bus connection

2

The MCU executes a read from an external I

C EEPROM and checks whether it contains valid application

code by comparing the read value with the expected boot signature. If it contains valid code, the MCU executes

follow-up reads from the EEPROM and writes the code into the TUSB6250 internal 32K bytes of default code

RAM. If the external EEPROM does not contain any valid code, the MCU proceeds to boot from the USB.

2

The I

C EEPROM normally is preprogrammed with a valid application code image. It also contains all the

configurable USB descriptors and other configurable descriptors or parameters for the mass storage device

connected to the TUSB6250 ATA/A TAPI interface. For the option of booting from the USB host, the application

code may reside in the host PC. However, the external I

2

C EEPROM is still needed to store the USB 2.0

specification-required vendor ID and product ID specific to each individual end-product manufacturer.

SLLS535D − November 2006 TUSB6250

4−5

Device Parameter Information

Depending on the type of firmware used as specified in the header block of the external I2C EEPROM, the

boot code can determine:

• Whether to perform connection to the USB host for enumeration before downloading the firmware into the

internal code RAM

• Whether to remain disconnected during the firmware code downloading process. In this case, the

firmware, once in charge, assumes the responsibility of performing the connect and enumeration tasks.

For details on how to specify the header block of the external I

2

C EEPROM, booting, and enumeration options,

see the TUSB6250 Bootcode Application Note application report (SLLA126).

4−6

SLLS535D − November 2006TUSB6250

5 Architecture Overview

The overall functionality of the TUSB6250 is achieved by the combined interaction of major blocks or

subcontrollers as shown earlier in Figure 3−1. These major blocks include the USB 2.0 UTMI-compliant PHY,

USB 2.0 parallel interface engine (PIE), embedded microcontroller unit (MCU), USB buffer manager (UBM),

ATA/ATAPI interface controller, and the I

5.1 Controller Brief Data Flow

As shown in Figure 5−1, the USB host controller, residing inside a PC, issues commands and/or data to the

TUSB6250-based external USB 2.0 mass storage device. The TUSB6250’s internal data flow is described

as follows (out-transaction example):

1. The USB 2.0 UTMI-compliant PHY receives serial data, either high-speed or full-speed, from the external

upstream USB host controller. The PHY processes this serial data stream and converts it into the

8-bit-wide parallel data packet based on the protocol defined in the USB 2.0 specification and the UTMI

specification.

2. The 8-bit wide parallel data packet, switching at 60-MHz, is passed to the USB 2.0 PIE block. The USB

2.0 PIE processes the data based on the defined USB packet protocol and passes the data to the UBM

block.

3. The UBM performs the endpoint address decoding and then passes the data packet to the addressed data

buffer location, which is either the endpoint buffer space or the sector FIFO space configured by the MCU

and its firmware. The section FIFO is the dedicated data buffer space directly accessible by the TUSB6250

controller’s internal high-performance ATA/ATAPI interface controller. The UBM also generates the

appropriate interrupt to inform the MCU of the arrival of the new packet.

2

C interface controller.

Architecture Overview

4. The embedded MCU, either moves the data manually between the endpoint buffer and the ATA/ATAPI

interface, or enables automatic data movement between the sector FIFO and the ATA/ATAPI interface.

5. If the automatic data movement path is enabled, the data packet targeted to the storage device is loaded

automatically from the UBM into sector FIFO.

6. The ATA/ATAPI interface controller, which is a high-performance DMA engine, automatically moves the

data from sector FIFO to the storage device connected to its ATA/ATAPI interface with the data transfer

protocol and timing configured by the MCU and the firmware.

USB

Host

TUSB6250

ATA or ATAPI

Drive

Figure 5−1. TUSB6250 Typical Application Diagram

SLLS535D − November 2006 TUSB6250

5−1

Architecture Overview

5.2 Overview of Major Function Blocks

5.2.1 USB 2.0 UTMI-Compliant PHY

The main functions of the integrated USB 2.0 UTMI-compliant PHY are to convert the received serial data

stream from the USB host controller into parallel data packets that can be processed by the controller engine

of the TUSB6250 and to perform parallel-to-serial conversion for the data packets to be transmitted to the USB

host.

The integrated PHY communicates to the TUSB6250 controller parallel interface engine (PIE) through two

separate 8-bit-wide transmit and receive data buses and other handshake signals defined in the USB 2.0

UTMI specification version 1.4. The PHY also provides a 60-MHz clock signal to the PIE for synchronization.

It supports both high-speed (480 Mbps) USB signaling and full-speed (12 Mbps) signaling. This backward

compatibility allows the TUSB6250 controller to connect to any legacy USB full-speed hosts and hubs.

The PHY includes circuitry to monitor the line conditions for determining connection status, initialization, and

packet reception and transmission. The integrated PHY requires only an external 24-MHz crystal as a

reference. An external clock, with 1.8-V magnitude, can be provided to the XTAL1 pin instead of a crystal. An

internal oscillator drives an internal phase-locked loop (PLL), which generates the required 480-MHz

reference clock. The reference clock is internally divided to provide the clock signals used to control the

internal receive and transmit circuitry. The suspend function stops the operation of the PLL.

Data bits to be transmitted upstream are received on the 8-bit transmit bus from the PIE of the TUSB6250

controller and latched in synchronization with the 60-MHz clock. These bits are combined serially, encoded

and bit-stuffed as required, and transmitted to the USB host. During packet reception, the transmitters are

disabled. A clock signal and serial data bits are recovered from the received NRZI-encoded and bit-stuffed

information. The serial data bits are bit unstuffed, NRZI decoded, and deserialized. These bits are then

resynchronized to the local 60-MHz clock and sent to the PIE on the 8-bit wide receive bus.

The integrated PHY also provides the 60-MHz clock source to be used on all other blocks of the TUSB6250

controller. It contains two 3.3-V to 1.8-V voltage regulators to supply power for the PHY internal digital and

PLL circuitry.

An external 1.5-kΩ ±5% resistor must be placed between the RPU and AVDD pins. The resistor is required

for full-speed indication and connect signaling. Another external 5.9-kΩ ±1% resistor must be placed between

R1 and ground, which is used to mirror the current for internal analog circuitry reference.

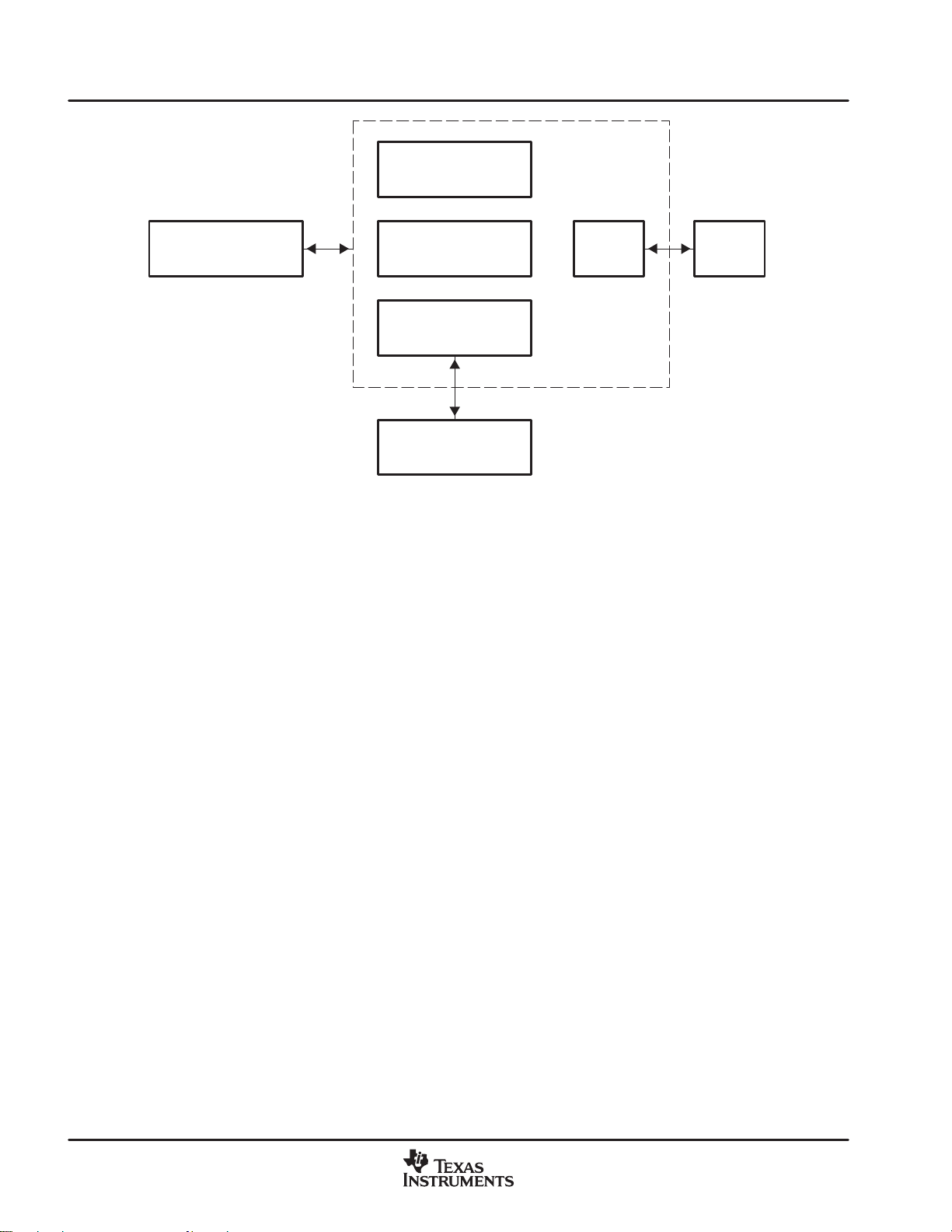

5.2.2 USB 2.0 Parallel Interface Engine (PIE)

As shown in Figure 3−2, the PIE consists of four major blocks: a frame timer, a bus a monitor, a transaction

handler, and USB registers.

The bus monitor, as its name implies, monitors the USB differential signal line status through the USB 2.0

UTMI-compliant PHY. It informs the MCU via updating the UTMICFG:UTMI configuration status register

(XDATA at F00A) with the current line status information, such as high-speed or full-speed mode indication,

VBUS status, idle, and SE0 detection information. While interfacing with the PHY, the bus monitor is able to

perform connect or disconnect according to the configuration set up by the MCU and firmware. It detects and

generates the USB full-speed or high-speed handshake based on the protocol defined in the USB 2.0

specification and provides other capabilities such as suspend, resume, and remote wakeup. The bus monitor

also supports the required USB 2.0 high-speed compliance test modes.

The frame timer is responsible for tracking starts of frames (SOFs) from the bus monitor and generating the

USB frame number and microframe number, which is described in Section 8.6, USBFCL: USB Frame Counter

Low-Byte Register (XDATA at F00B) and Section 8.7, USBFCH: USB Frame Counter High-Byte Register

(XDATA at F00C).

5−2

SLLS535D − November 2006TUSB6250

The transaction handler manages the USB packet protocol requirement for the packets being received and

transmitted on the USB by the TUSB6250. For the received packet, the transaction handler checks the packet

identifier (PID) field to reveal the correct packet type from those defined by the USB 2.0 specification, such

as token, data, handshake, and special packets. It then checks the address, endpoint number, and the CRC

to ensure the received packet is a valid one being addressed to one of the enabled endpoints in the TUSB6250

controller. If the received packet is a data packet, it first notifies the UBM with the endpoint address and

direction information of the incoming data packet and then passes the following data payload. For the packet

being transmitted, the transaction handler gets the data from the UBM and generates the correct PID and CRC

as part of the transmit packet to be transmitted along with the data payload to the USB host. The

synchronization field (SYNC) is generated by the PHY. For the handshake packet, the UBM tells the

transaction handler what kind of handshake packet to send, as long as the CRC is valid. The transaction

handler then performs the task of sending the required handshake packet.

5.2.3 USB Buffer Manager (UBM)

The UBM is a high-performance DMA engine that manages the data movement between the transaction

handler and the TUSB6250 endpoint data buffer or sector FIFO (used by the ATA/ATAPI interface controller

for high-speed data transfer between the TUSB6250 controller and the storage device connected to its

ATA/ATAPI interface). For received packets, the UBM checks the endpoint address, direction information, and

loads (writes) the data payload into the appropriate endpoint data buffer or sector FIFO in the TUSB6250

controller. For the packet being transmitted, the UBM decodes the valid endpoint address, direction

information from the token packet provided by the transaction handler, and performs a read from the correct

endpoint data buffer or sector FIFO location in the TUSB6250 controller. The read-data is then passed to the

transaction handler to be processed and transferred to the USB host.

Architecture Overview

5.2.4 Embedded Microcontroller Unit (MCU)

The integrated MCU in the TUSB6250 controller is a high-speed 8-bit microcontroller core based on the

industry standard 8051 with certain improvements. The MCU operates at 60-MHz clock frequency with up to

30 MIPS performance.

The main functionality of the embedded MCU core of the TUSB6250 controller is to serve as a central

processing platform to allow the boot code (the microcode running at boot time) and firmware to perform the

device configuration and the activity control function by configuring and updating all the registers in the MCU,

USB, ATA/ATAPI, I

2

C, and the GPIO blocks.

5.2.5 ATA/ATAPI Interface Controller

The ATA/ATAPI interface controller is a high-performance DMA engine that continuously monitors the status

and manages the data movement between sector FIFO and the ATA/ATAPI storage device connected to the

TUSB6250 ATA/ATAPI interface, based on the ATA/ATAPI timing and protocol defined by the ATA/ATAPI-5

specification.

The AT A/ATAPI interface controller of the TUSB6250 controller offers both the flexibility of general MCU-based

bridge controllers and the performance of state-machine-based bridge controllers. It allows the MCU to move

the data manually between the endpoint data buffer and the ATA/ATAPI interface, while providing a

high-performance automatic data movement mode, in which the ATA/ATAPI interface controller and the UBM

work together to move the data quickly among the UBM, sector FIFO, and the ATA/ATAPI interface without

MCU involvement during the data stage of the bulk-only data transfer.

Some of the flexibilities offered by the TUSB6250 ATA/ATAPI interface controller include:

• Firmware-configurable IDE data transfer modes and timing that can be configured in the resolution of the

60-MHz clock cycle period

• Many hardware registers that provide information to assist the MCU to handle all 13 case conditions

correctly defined by the USB mass storage bulk-only transfer protocol specification.

SLLS535D − November 2006 TUSB6250

5−3

Architecture Overview

5.2.6 I2C Interface Controller

The master-only I2C interface controller is responsible for acquiring the user-configurable descriptors and

other configurable feature parameters from the external I

to download the application firmware from the external I

controller is controlled by the boot code (the microcode embedded in boot ROM) or application firmware.

2

C EEPROM during initial power up. It is also used

2

C EEPROM. The behavior of the I2C interface

5.3 Other Major Features

5.3.1 Unique Power-On Sequencing to the Storage Device

The TUSB6250 provides unique power-on sequencing features to the storage device. When the TUSB6250

is powered up during the reset period, it turns off all the output buffers and activates all of the internal pulldown

resistors on the ATA/ATAPI bus. After reset, when the TUSB6250 controller is enumerated and configured,

the application firmware in operation decides when to power up the connected ATA/ATAPI drive and

reconfigure all the input, output, and bidirectional buffers, and the pullup and pulldown resistors on the

ATA/ATAPI bus based on their functionality defined in the ATA/ATAPI-5 specification.

This function is critical for implementing a truly bus-powered USB 2.0 mass storage device, because the disk

start-up spinning normally results in a high-current surge that is harmful to the USB device during enumeration.

According to the USB 2.0 specification, a USB device is only allowed to consume up to 100 mA before it is

configured.

This feature is also useful when the TUSB6250 controller interfaces to A TA/AT API mass storage devices that

do not implement fail-safe buffers on their ATA/ATAPI interface. In such conditions, this well controlled

power-on sequencing feature protects the connected storage device without fail-safe I/O buffers from damage

that might be caused by the bridge controller driving the signal lines when the power supply of the storage

devices is not present.

5.3.2 Die-ID Based USB Device Serial Number

The TUSB6250 supports unique USB device serial numbers by using the 48-bit die-ID number unique to each

silicon die. It also allows end-product developers to specify their own custom serial number in the external I

EEPROM to override this default die-ID serial number.

2

C

5−4

SLLS535D − November 2006TUSB6250

6 Microcontroller Unit (MCU)

The embedded MCU is a high-performance version (8051 Warp core) of the standard 8-bit 8051

microcontroller, requiring just two clocks per machine cycle, while keeping functional compatibility with the

standard part. This allows the embedded MCU to run up to six times faster than the standard part for the same

power consumption. The ratio of two clock cycles to one machine cycle is constant across the instruction set

and all addressing modes, so as to maintain instruction execution-time compatibility with other devices.

The MCU is the central processing unit controlling the overall activity of the TUSB6250 controller with the