TPS74401

TPS74401

TPS74401

GND

EN

FB

IN PG

SS

OUT

V

IN

V

OUT

V

PG

R

1

R

2

R

3

C

OUT

Optional

C

IN

1 Fm

C

SS

V

BIAS

C

BIAS

1 Fm

BIAS

1V/div

500mV/div

Time(1ms/div)

C =0 FSSm

C =0.001 FSSm

C =0.0047 FSSm

V

OUT

V

EN

0V

1.1V

TPS74401

www.ti.com

3.0A Ultra-LDO with Programmable Soft-Start

1

FEATURES

2

• Soft-Start (SS) Pin Provides a Linear Startup

with Ramp Time Set by External Capacitor

• 1% Accuracy Over Line, Load, and

Temperature

• Supports Input Voltages as Low as 0.9V with

External Bias Supply

• Adjustable Output (0.8V to 3.6V)

• Ultra-Low Dropout: 115mV at 3.0A (typ)

• Stable with Any or No Output Capacitor

• Excellent Transient Response

• Available in 5mm × 5mm × 1mm QFN and

DDPAK-7 Packages

• Open-Drain Power-Good (QFN only)

• Active High Enable

APPLICATIONS

• FPGA Applications

• DSP Core and I/O Voltages

• Post-Regulation Applications

• Applications with Special Start-Up Time or

Sequencing Requirements

• Hot-Swap and Inrush Controls

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

DESCRIPTION

The TPS74401 low-dropout (LDO) linear regulator

provides an easy-to-use robust power management

solution for a wide variety of applications.

User-programmable soft-start minimizes stress on the

input power source by reducing capacitive inrush

current on start-up. The soft-start is monotonic and

well-suited for powering many different types of

processors and ASICs. The enable input and

power-good output allow easy sequencing with

external regulators. This complete flexibility permits

the user to configure a solution that will meet the

sequencing requirements of FPGAs, DSPs, and other

applications with specific start-up requirements.

A precision reference and error amplifier deliver 1%

accuracy over load, line, temperature, and process.

Each LDO is stable with low-cost ceramic output

capacitors and the device is fully specified from

– 40 ° C to +125 ° C. The TPS74401 is offered in a small

(5mm × 5mm) QFN package, yielding a highly

compact total solution size. For applications that

require additional power dissipation, the DDPAK

(KTW) package is also available.

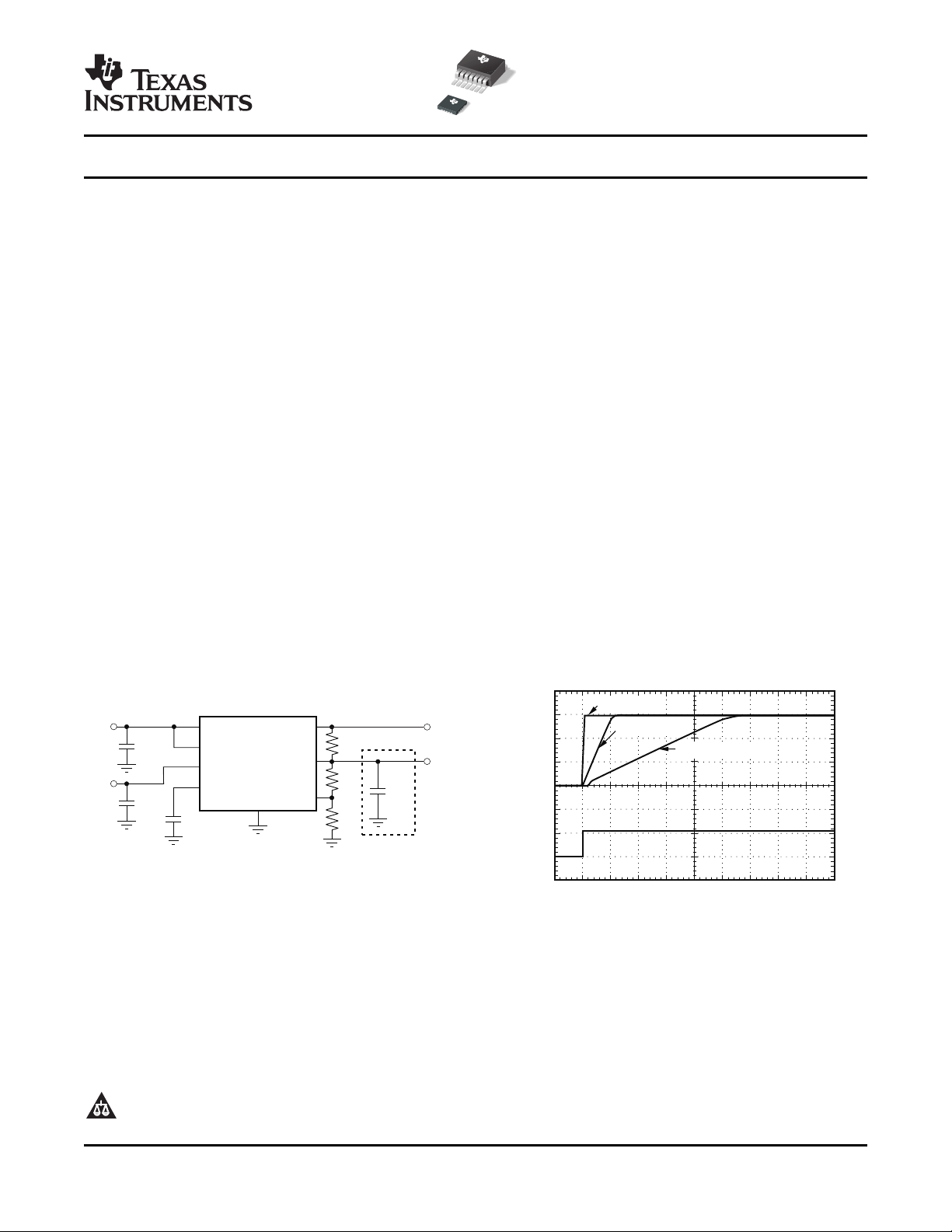

Figure 1. Typical Application Circuit

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

2 All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

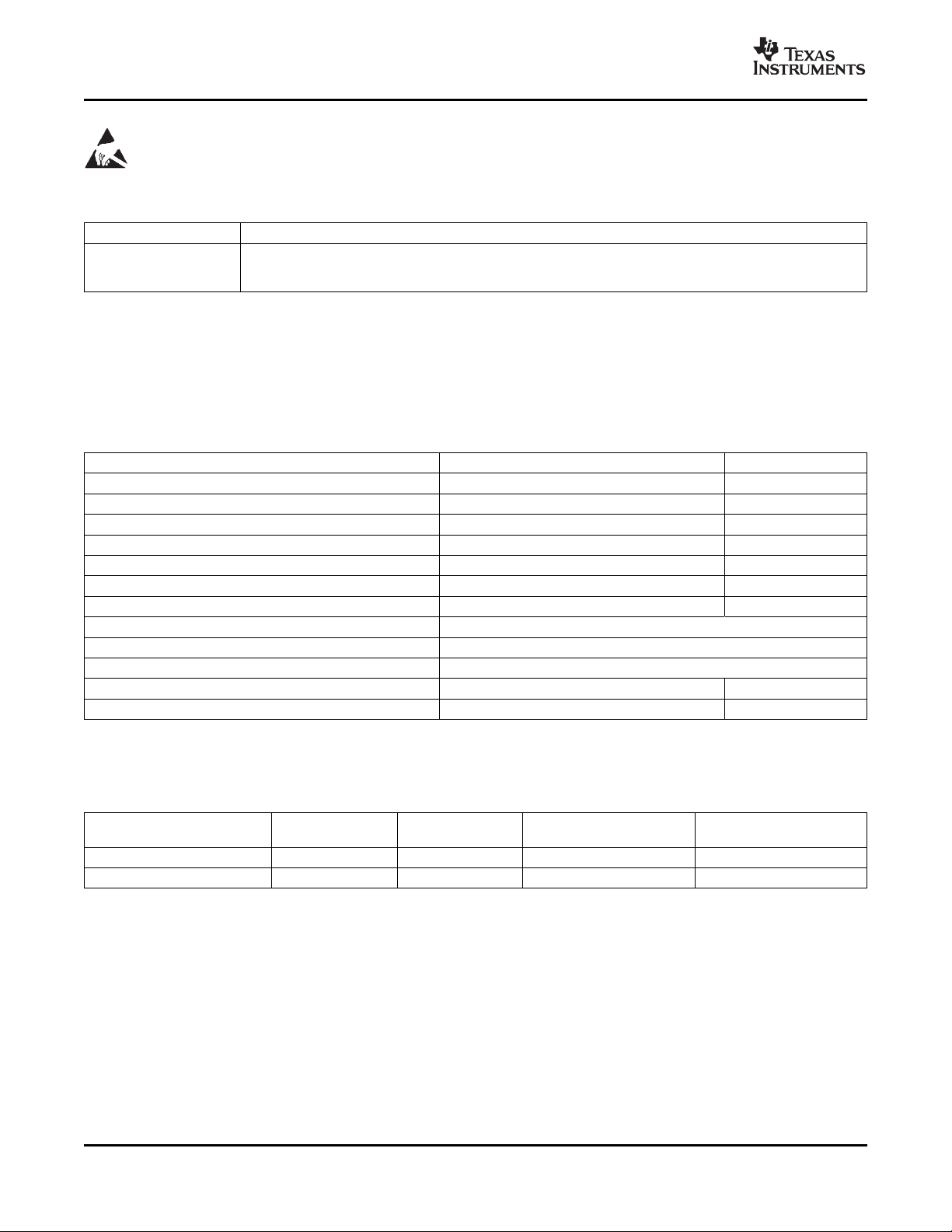

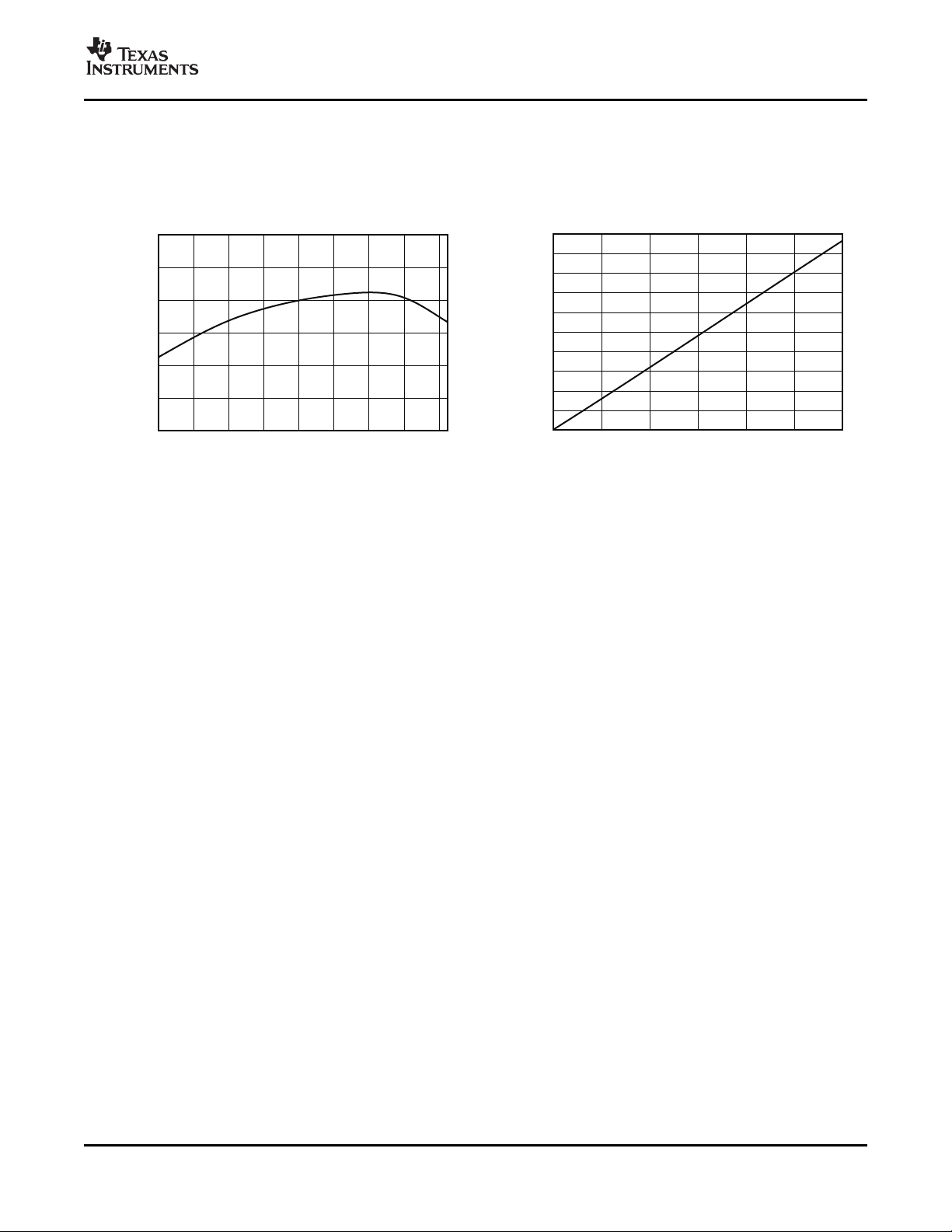

Figure 2. Turn-On Response

Copyright © 2005 – 2008, Texas Instruments Incorporated

www.ti.com

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

ORDERING INFORMATION

PRODUCT V

TPS744 xxyyyz XX is nominal output voltage (for example, 12 = 1.2V, 15 = 1.5V, 01 = Adjustable).

(1)

(2)

OUT

(3)

YYY is package designator.

Z is package quantity.

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI

website at www.ti.com .

(2) Output voltages from 0.9V to 1.5V in 50mV increments and 1.5V to 3.6V in 100mV increments are available through the use of

innovative factory EEPROM programming; minimum order quantities may apply. Contact factory for details and availability.

(3) For fixed 0.8V operation, tie FB to OUT.

ABSOLUTE MAXIMUM RATINGS

(1)

At TJ= – 40 ° C to +125 ° C, unless otherwise noted. All voltages are with respect to GND.

TPS74401 UNIT

VIN, V

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these conditions is not implied. Exposure to absolute-maximum-rated conditions for

extended periods may affect device reliability.

Input voltage range – 0.3 to +6 V

BIAS

V

Enable voltage range – 0.3 to +6 V

EN

V

Power-good voltage range – 0.3 to +6 V

PG

IPGPG sink current 0 to +1.5 mA

V

SS pin voltage range – 0.3 to +6 V

SS

V

Feedback pin voltage range – 0.3 to +6 V

FB

V

Output voltage range – 0.3 to VIN+ 0.3 V

OUT

I

Maximum output current Internally limited

OUT

Output short circuit duration Indefinite

P

Continuous total power dissipation See Dissipation Ratings Table

DISS

TJOperating junction temperature range – 40 to +125 ° C

T

Storage junction temperature range – 55 to +150 ° C

STG

DISSIPATION RATINGS

PACKAGE θ

RGW (QFN)

KTW (DDPAK)

(1)

(2)

JA

36.5 ° C/W 4.05 ° C/W 2.74W 27.4mW/ ° C

18.8 ° C/W 2.32 ° C/W 5.32W 53.2mW/ ° C

θ

JC

(1) See Figure 33 for PCB layout description.

(2) See Figure 36 for PCB layout description.

2 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS74401

TA< +25 ° C DERATING FACTOR

POWER RATING ABOVE TA= +25 ° C

www.ti.com

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

ELECTRICAL CHARACTERISTICS

At V

= 1.1V, V

EN

unless otherwise noted. Typical values are at TJ= +25 ° C.

V

IN

V

BIAS

V

REF

V

OUT

V

/V

OUT

IN

V

/I

OUT

OUT

V

DO

ICLCurrent limit A

I

BIAS

I

SHDN

IFBFeedback pin current

(4)

PSRR

Noise Output noise voltage 16 × V

V

TRAN

t

STR

ISSSoft-start charging current V

V

EN, HI

V

EN, LO

V

EN, HYS

V

EN, DG

IENEnable pin current V

V

IT

V

HYS

V

PG, LO

I

PG, LKG

T

J

= V

OUT

+ 0.3V, C

IN

= C

IN

BIAS

= 0.1 µ F, C

OUT

= 10 µ F, I

OUT

= 50mA, V

BIAS

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Input voltage range V

OUT

Bias pin voltage range 2.375 5.25 V

Internal reference (Adj.) TJ= +25 ° C 0.796 0.8 0.804 V

Output voltage range VIN= 5V, I

Accuracy

Line regulation %/V

Load regulation

VINdropout voltage

V

Bias pin current I

Shutdown supply current

(V

Power-supply rejection

(V

Power-supply rejection

(V

(1)

2.97V ≤ V

V

OUT (NOM)

V

OUT (NOM)

0mA ≤ I

50mA ≤ I

I

= 3.0A, V

(2)

dropout voltage

BIAS

)

IN

(2)

(3)

OUT

I

= 3.0A, V

OUT

DDPAK

I

= 3.0A, VIN= V

OUT

V

= 80% × V

OUT

V

= 80% × V

OUT

= 0mA to 3.0A 2 4 mA

OUT

V

≤ 0.4V 1 100 µ A

EN

I

= 50mA to 3.0A – 250 95 250 nA

OUT

1kHz, I

to V

IN

)

OUT

800kHz, I

V

= 1.5V

OUT

1kHz, I

to V

BIAS

)

OUT

800kHz, I

V

= 1.5V

OUT

100Hz to 100kHz, I

C

= 0.001 µ F

SS

%V

droop during load

OUT

transient

Minimum startup time I

I

= 100mA to 3.0A at 1A/ µ s, C

OUT

= 1.5A, C

OUT

= 0.4V 0.5 0.73 1 µ A

SS

= 1.5A, V

OUT

≤ 5.25V, 50mA ≤ I

BIAS

+ 0.3 ≤ V

+ 0.3 ≤ V

≤ 50mA 0.013 %/mA

OUT

≤ 3.0A 0.03 %/A

OUT

– V

BIAS

– V

BIAS

BIAS

OUT (NOM)

OUT (NOM)

= 1.5A, VIN= 1.8V, V

OUT

= 1.5A, VIN= 1.8V,

OUT

= 1.5A, VIN= 1.8V, V

OUT

= 1.5A, VIN= 1.8V,

OUT

OUT

= open 100 µ s

SS

= 5V V

BIAS

≤ 3.0A – 1 ± 0.2 +1 %

OUT

≤ 5.5V, QFN 0.0005 0.05

IN

≤ 5.5V, DDPAK 0.0005 0.06

IN

OUT (NOM)

OUT (NOM)

≥ 1.62V, QFN 115 195

≥ 1.62V,

, QFN 3.8 6.0

, DDPAK 3.5 6.0

= 1.5V 73

OUT

= 1.5V 62

OUT

= 1.5A,

= 0 µ F 4 %V

OUT

Enable input high level 1.1 5.5 V

Enable input low level 0 0.4 V

Enable pin hysteresis 50 mV

Enable pin deglitch time 20 µ s

= 5V 0.1 1 µ A

EN

PG trip threshold V

decreasing 86.5 90 93.5 %V

OUT

PG trip hysteresis 3 %V

PG output low voltage IPG= 1mA (sinking), V

PG leakage current V

PG

= 5.25V, V

OUT

Operating junction

temperature

< V

OUT

IT

> V

IT

– 40 +125 ° C

TPS74401

= 5.0V, and TJ= – 40 ° C to +125 ° C,

TPS74401

+ V

DO

REF

120 240

42

50

OUT

0.03 1 µ A

5.5 V

3.6 V

1.62 V

0.3 V

mV

dB

dB

µ V

RMS

OUT

OUT

OUT

(1) Adjustable devices tested at 0.8V; external resistor tolerance is not taken into account.

(2) Dropout is defined as the voltage from the input to V

(3) IFBcurrent flow is out of the device.

when V

OUT

is 2% below nominal.

OUT

(4) See Figure 10 to Figure 13 for PSRR at different conditions.

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Link(s): TPS74401

www.ti.com

Thermal

Limit

Soft-Start

Discharge

OUT

V

OUT

FB

PG

IN

BIAS

SS

EN

Hysteresis

andDe-Glitch

Current

Limit

UVLO

0.73 Am

0.8V

Reference

0.9 ´ V

REF

GND

C

SS

R

1

R

2

V =0.8x( )

OUT

1+

R

1

R

2

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

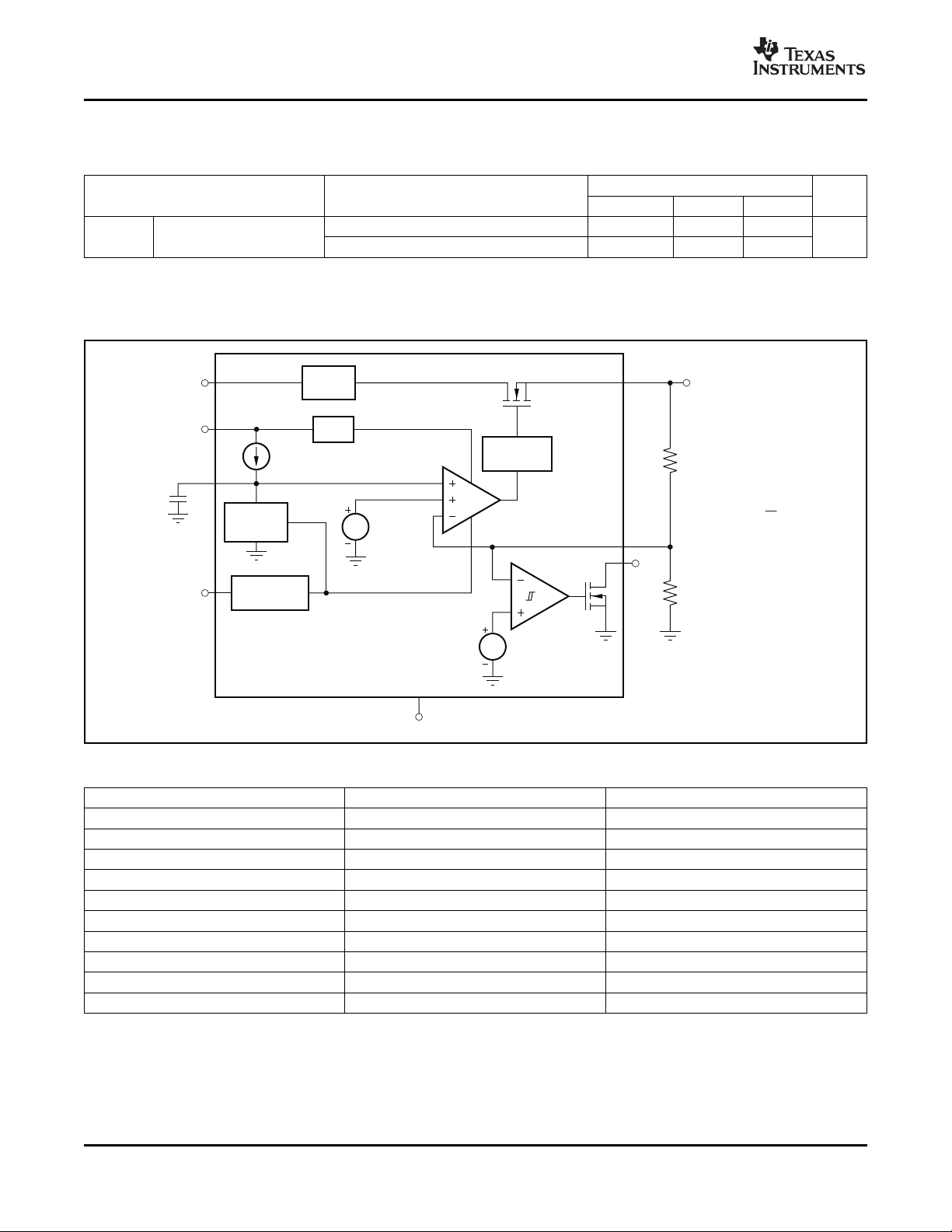

ELECTRICAL CHARACTERISTICS (continued)

At V

= 1.1V, V

EN

unless otherwise noted. Typical values are at TJ= +25 ° C.

T

SD

= V

OUT

+ 0.3V, C

IN

= C

IN

BIAS

= 0.1 µ F, C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Thermal shutdown

temperature

Shutdown, temperature increasing +155

Reset, temperature decreasing +140

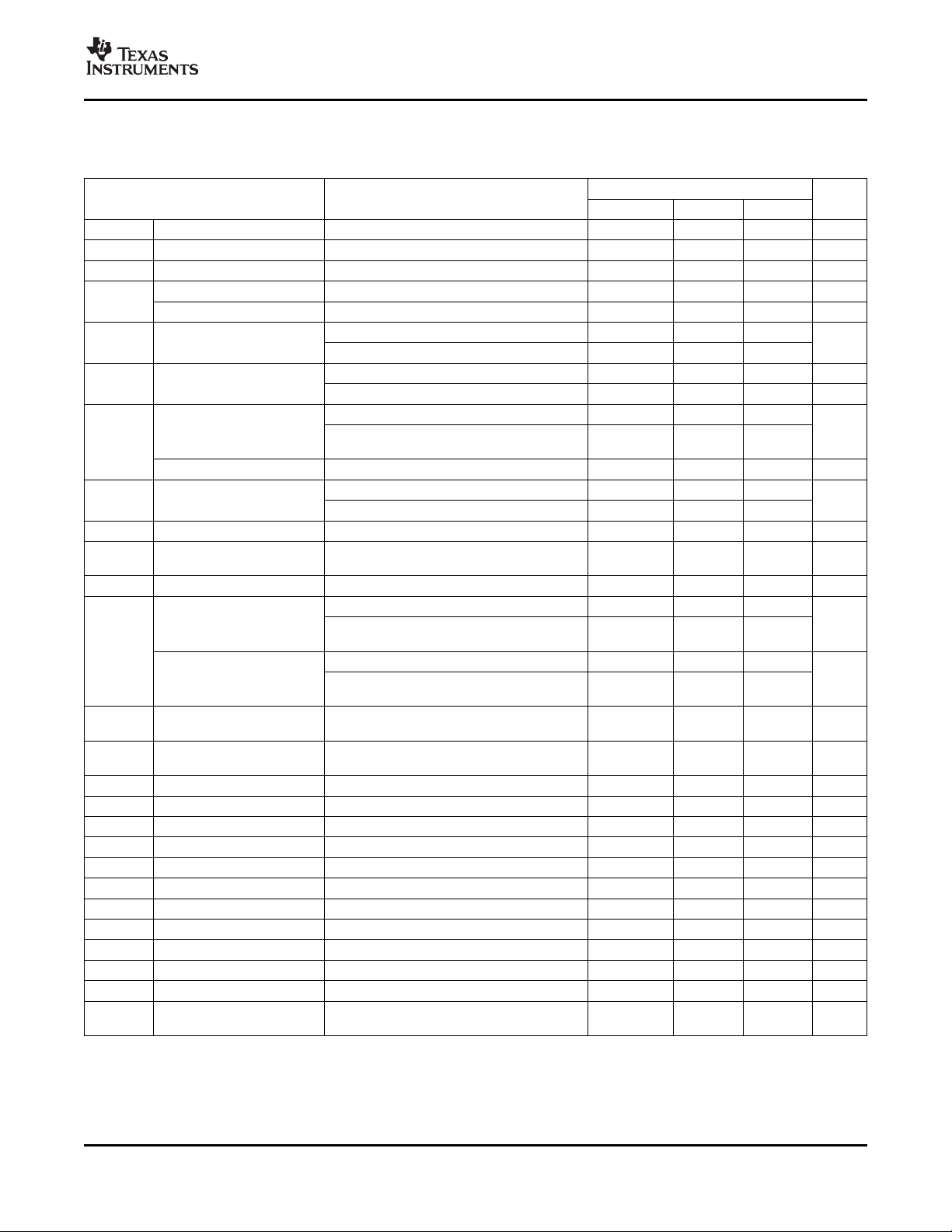

BLOCK DIAGRAM

OUT

= 10 µ F, I

OUT

= 50mA, V

= 5.0V, and TJ= – 40 ° C to +125 ° C,

BIAS

TPS74401

° C

Table 1. Standard 1% Resistor Values for Programming the Output Voltage

R1(k Ω ) R2(k Ω ) V

(1)

(V)

OUT

Short Open 0.8

0.619 4.99 0.9

1.13 4.53 1.0

1.37 4.42 1.05

1.87 4.99 1.1

2.49 4.99 1.2

4.12 4.75 1.5

3.57 2.87 1.8

3.57 1.69 2.5

3.57 1.15 3.3

(1) V

= 0.8 × (1 + R1/R2)

OUT

4 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS74401

www.ti.com

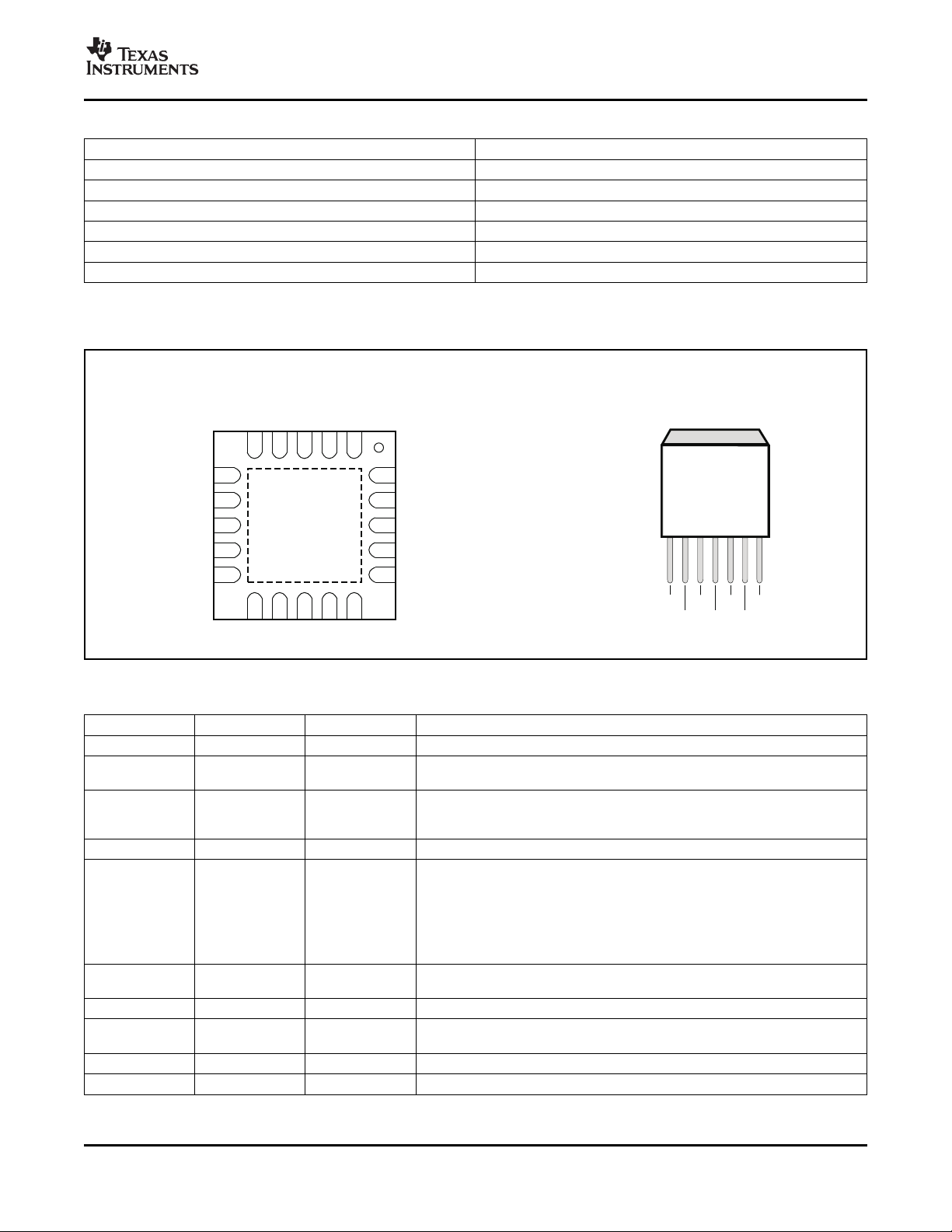

5 5QFN(RGW)´

Package TopView¾

IN

IN

IN

PG

BIAS

OUT

OUT

OUT

NC

FB

TPS74401

IN

EN

11

GND

12

NC

13

NC

14

SS

15

6

7

8

9

10

20

19

18

17

16

5

NC4

NC3

NC2

OUT1

GND

7-Lead

DDPAK(KTW)

Surface-Mount

OUT

GND

BIAS

IN

FB

SS

1 2 3 4

5

6EN7

Table 2. Standard Capacitor Values for Programming the Soft-Start Time

(1) tSS(s) = 0.8 × CSS(F)/7.3 × 10

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

C

SS

SOFT-START TIME

Open 0.1ms

470pF 0.5ms

1000pF 1ms

4700pF 5ms

0.01 µ F 10ms

0.015 µ F 16ms

– 7

TPS74401

(1)

PIN DESCRIPTIONS

NAME KTW (DDPAK) RGW (QFN) DESCRIPTION

IN 5 5 – 8 Unregulated input to the device.

EN 7 11

SS 1 15 Soft-Start pin. A capacitor connected on this pin to ground sets the start-up

BIAS 6 10 Bias input voltage for error amplifier, reference, and internal control circuits.

PG N/A 9 low-impedance state. A pull-up resistor from 10k Ω to 1M Ω should be connected

FB 2 16

OUT 3 1, 18 – 20 Regulated output voltage. No capacitor is required on this pin for stability.

NC N/A 2 – 4, 13, 14, 17

GND 4 12 Ground

PAD/TAB Should be soldered to the ground plane for increased thermal performance.

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 5

Enable pin. Driving this pin high enables the regulator. Driving this pin low puts

the regulator into shutdown mode. This pin must not be left floating.

time. If this pin is left floating, the regulator output soft-start ramp time is

typically 100 µ s.

Power-Good (PG) is an open-drain, active-high output that indicates the status

of V

. When V

OUT

high-impedance state. When V

exceeds the PG trip threshold, the PG pin goes into a

OUT

is below this threshold the pin is driven to a

OUT

from this pin to a supply up to 5.5V. The supply can be higher than the input

voltage. Alternatively, the PG pin can be left floating if output monitoring is not

necessary.

This pin is the feedback connection to the center tap of an external resistor

divider network that sets the output voltage. This pin must not be left floating.

No connection. This pin can be left floating or connected to GND to allow better

thermal contact to the top-side plane.

Product Folder Link(s): TPS74401

www.ti.com

1.0

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

-0.1

0

10 20 30 40

ChangeinV (%)

OUT

I (mA)

OUT

50

+125 C°

+25 C°

-40 C°

ReferredtoI =50mA

OUT

0.050

0.025

0

-0.025

-0.050

-0.075

-0.100

-0.125

-0.150

50

500 1000 1500 2000 2500

ChangeinV (%)

OUT

I (mA)

OUT

3000

+125 C°

+25 C°

- °40 C

ReferredtoI =50mA

OUT

0.05

0.04

0.03

0.02

0.01

0

-0.01

-0.02

-0.03

-0.04

-0.05

0

0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

ChangeinV (%)

OUT

V V-

IN OUT

(V)

4.5

T = 40- °JC

TJ=+25°C

TJ=+125°C

0

500 1000 1500 2000 2500

I (mA)

OUT

3000

200

150

100

50

0

DropoutV

oltage(mV)

+125 C°

+25 C°

- °40 C

300

250

200

150

100

50

0

0.9

1.4 1.9 2.4 2.9 3.4

DropoutV

oltage(mV)

V V-

BIAS OUT

(V)

3.9

+125 C°

+25 C°

- °40 C

I =3.0A

OUT

200

180

160

140

120

100

80

60

40

20

0

0.9

1.4 1.9 2.4 2.9 3.4

DropoutVoltage(mV)

V V-

BIAS OUT

(V)

3.9

+125 C°

+25 C°

-40°C

I =1.5A

OUT

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

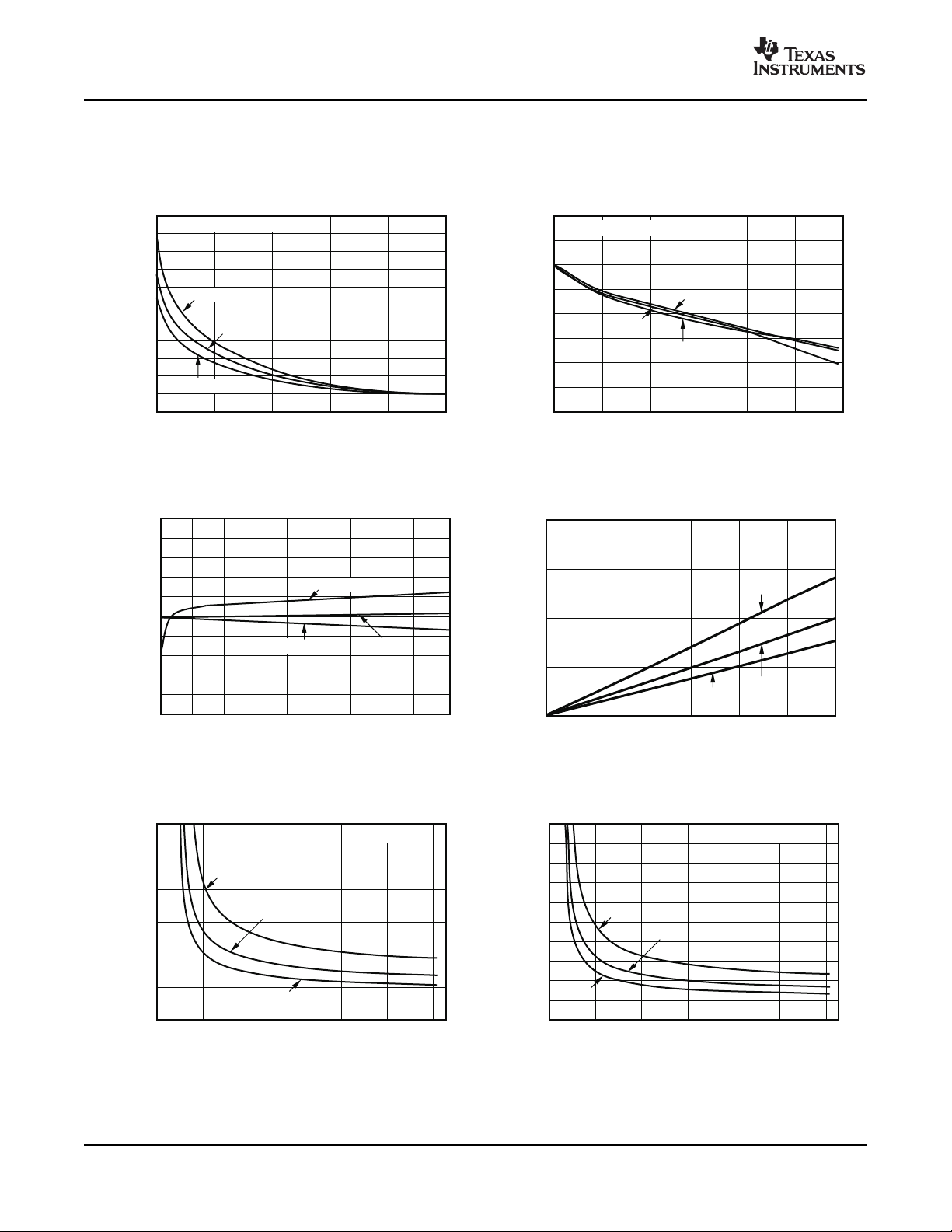

At TJ= +25 ° C, V

OUT

= 1.5V, V

= V

IN

LOAD REGULATION LOAD REGULATION

Figure 3. Figure 4.

TYPICAL CHARACTERISTICS

OUT(TYP)

+ 0.3V, V

C

= 10 µ F, unless otherwise noted.

OUT

BIAS

= 3.3V, I

OUT

= 50mA, C

IN

= 1 µ F, C

= 1 µ F, C

BIAS

SS

= 0.01 µ F, and

LINE REGULATION I

AND TEMPERATURE (TJ)

OUT

Figure 5. Figure 6.

VINDROPOUT VOLTAGE vs VINDROPOUT VOLTAGE vs

V

– V

VINDROPOUT VOLTAGE vs

BIAS

AND TEMPERATURE (TJ) V

OUT

– V

BIAS

AND TEMPERATURE (TJ)

OUT

6 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Figure 7. Figure 8.

Product Folder Link(s): TPS74401

www.ti.com

1400

1300

1200

1100

1000

900

800

700

600

500

0

500 1000 1500 2000 2500

DropoutVoltage(mV)

I (mA)

OUT

3000

+125 C°

+25 C°

-40 C°

V =V

IN BIAS

80

70

60

50

40

30

20

10

0

10

100 1k 10k 100k 1M

Power-SupplyRejectionRatio(dB)

Frequency(Hz)

10M

I =3.0A

OUT

100

90

80

70

60

50

40

30

20

10

0

10

100 1k 10k 100k 1M

Power

-SupplyRejectionRatio(dB)

Frequency(Hz)

10M

V =1.8,V =1.5V

IN OUT OUT

,I =1.5A

C =0 F

OUT

m

C =10 F

OUT

m

C =100 F

OUT

m

100

90

80

70

60

50

40

30

20

10

0

10

100 1k 10k 100k 1M

Power

-SupplyRejectionRatio(dB)

Frequency(Hz)

10M

V =1.8,V =1.5V

IN OUT OUT

,I =100mA

C =10 F

OUT

m

C =100 F

OUT

m

C =0 F

OUT

m

100

90

80

70

60

50

40

30

20

10

0

10

100 1k 10k 100k 1M

Power

-SupplyRejectionRatio(dB)

Frequency(Hz)

10M

V =1.8,V =1.5V

IN OUT OUT

,I =3A

C =100 F

OUT

m

C =0 F

OUT

m

C =10 F

OUT

m

90

80

70

60

50

40

30

20

10

0

0

0.25 0.50 0.75 1.00 1.25 1.50 1.75 2.00 2.25

Power-SupplyRejectionRatio(dB)

V V-

IN OUT

(V)

2.50

1kHz

100kHz

300kHz

700kHz

C =22 F

I =1.5A

m

OUT

OUT

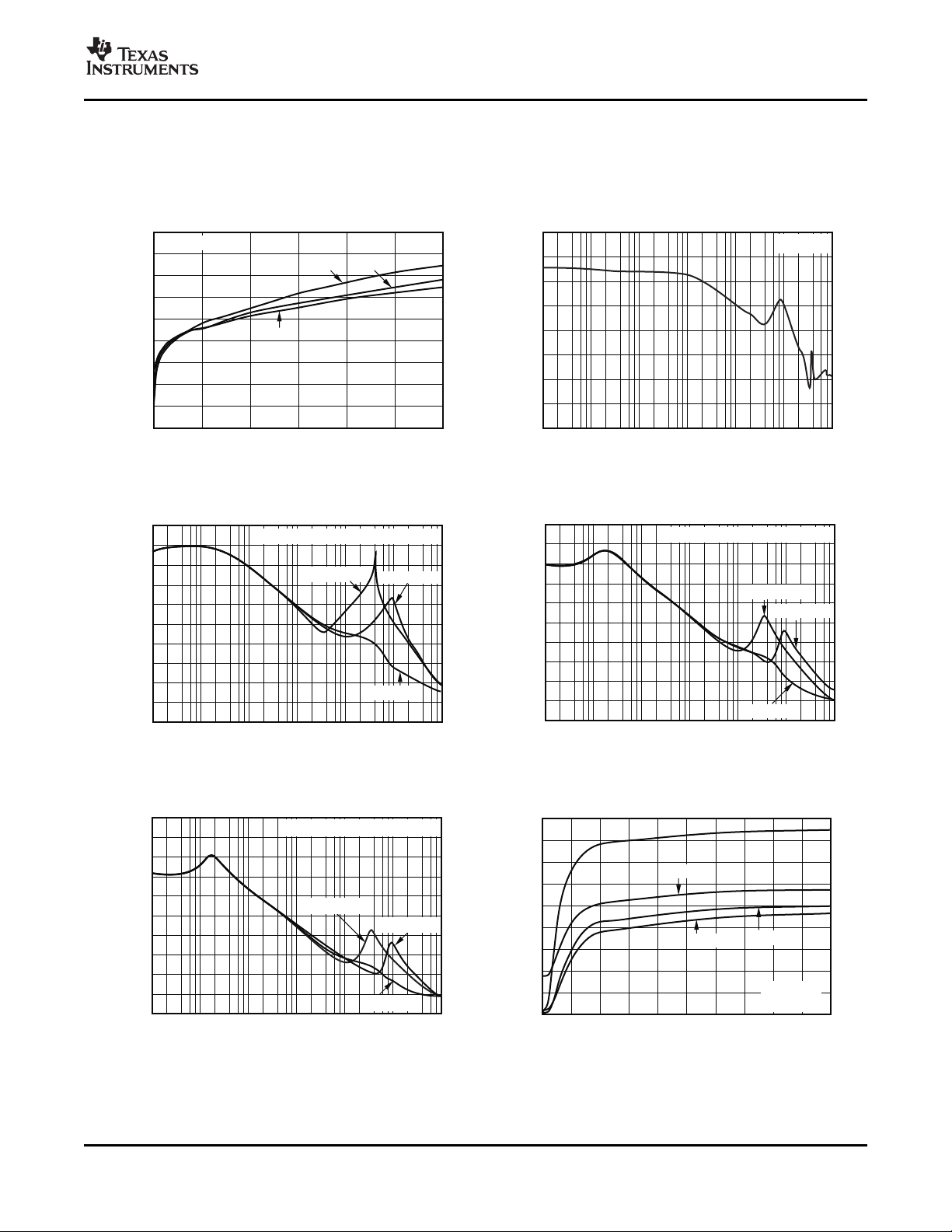

At TJ= +25 ° C, V

C

= 10 µ F, unless otherwise noted.

OUT

TYPICAL CHARACTERISTICS (continued)

= 1.5V, V

OUT

V

BIAS

I

AND TEMPERATURE (TJ) V

OUT

= V

IN

OUT(TYP)

DROPOUT VOLTAGE vs

+ 0.3V, V

BIAS

= 3.3V, I

OUT

= 50mA, C

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

IN

= 1 µ F, C

BIAS

= 1 µ F, C

BIAS

SS

= 0.01 µ F, and

PSRR vs FREQUENCY

Figure 9. Figure 10.

VINPSRR vs FREQUENCY VINPSRR vs FREQUENCY

Figure 11. Figure 12.

VINPSRR vs FREQUENCY VINPSRR vs V

– V

IN

OUT

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 7

Figure 13. Figure 14.

Product Folder Link(s): TPS74401

www.ti.com

1

0.1

0.01

100

1k 10k

OutputSpectralNoiseDensity(

mV/

Ö )Hz

Frequency(Hz)

100k

C =1nF

SS

C =0nF

SS

C =10nF

SS

I =3A

OUT

V =1.1V

OUT

1

0.1

0.01

100

1k 10k

OutputSpectralNoiseDensity( V/

)

m Ö

Hz

Frequency(Hz)

100k

V =3.3V

OUT

V =2.5V

OUT

V =1.5V

OUT

V =1.1V

OUT

V =0.8V

OUT

V :V +1.62V

BIAS OUT

I :3A

OUT

C :1 F(Ceramic)m

IN

C :1 F(Ceramic)m

OUT

R ,R :(seeTable1)

1 2

2.85

2.65

2.45

2.25

2.05

1.85

1.65

1.45

1.25

0

500 1000 1500 2000 2500

BiasCurrent(mA)

I (mA)

OUT

3000

+125 C°

+25 C°

- °40 C

3.0

2.8

2.6

2.4

2.2

2.0

1.8

1.6

1.4

1.2

1.0

2.0

2.5 3.0 3.5 4.0 4.5

BiasCurrent(mA)

V (V)

BIAS

5.0

T =J+125 C°

T =+25 C°

J

T =J- °40 C

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

0

-40

-20 0 20 40 60 80 100

BiasCurrent( A)m

120

V =2.375V

BIAS

V =5.5V

BIAS

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

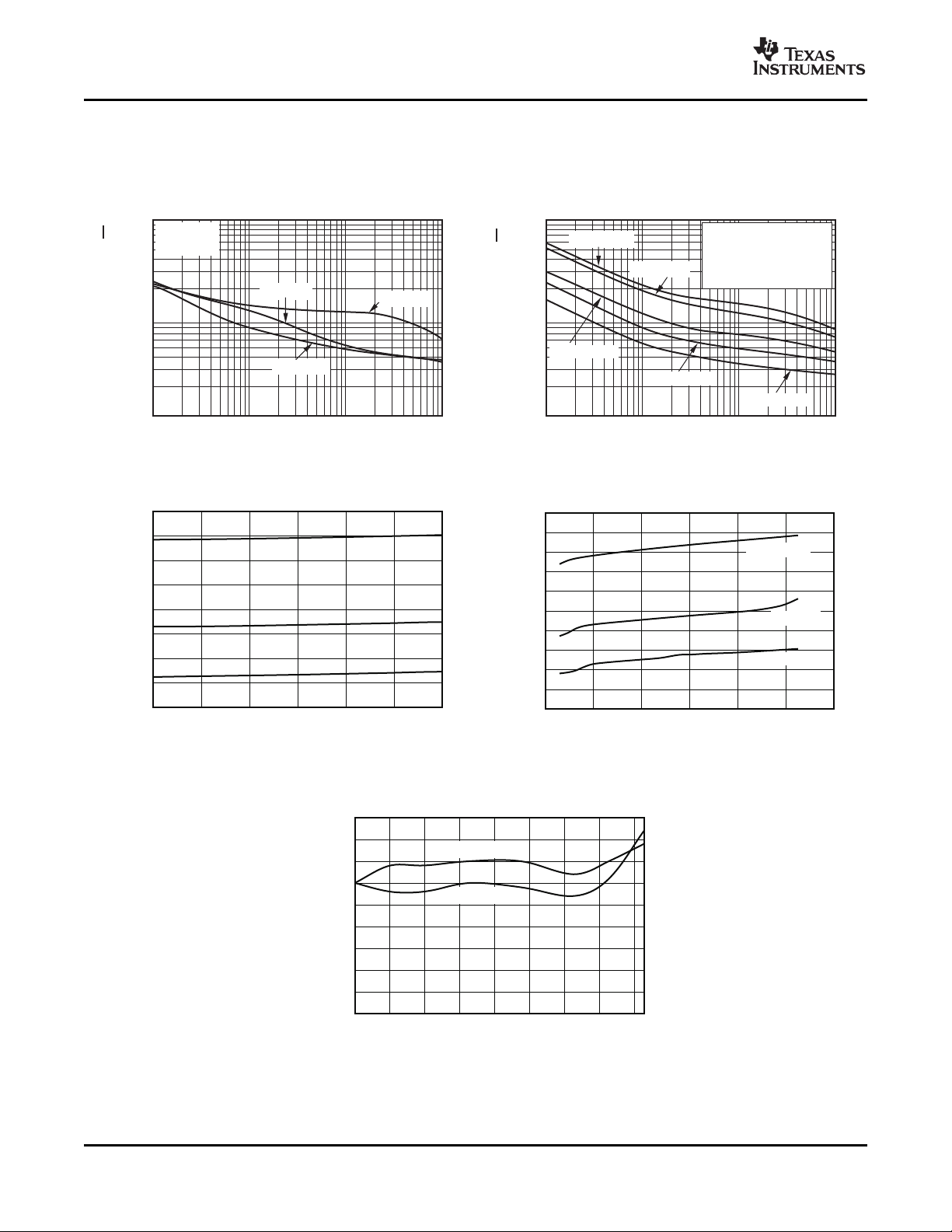

At TJ= +25 ° C, V

C

= 10 µ F, unless otherwise noted.

OUT

OUT

= 1.5V, V

= V

IN

NOISE SPECTRAL DENSITY NOISE SPECTRAL DENSITY

Figure 15. Figure 16.

TYPICAL CHARACTERISTICS (continued)

OUT(TYP)

+ 0.3V, V

BIAS

= 3.3V, I

OUT

= 50mA, C

IN

= 1 µ F, C

= 1 µ F, C

BIAS

SS

= 0.01 µ F, and

I

vs I

BIAS

AND TEMPERATURE I

OUT

vs V

BIAS

AND V

BIAS

OUT

Figure 17. Figure 18.

I

SHUTDOWN vs TEMPERATURE

BIAS

8 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Figure 19.

Product Folder Link(s): TPS74401

www.ti.com

765

750

735

720

705

690

675

-40

-20 0 20 40 60 80 100 120

I

(nA)

SS

1.0

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

V Low-LevelPGVoltage(V)

OL

0

2 4

6 8 10

12

PGCurrent(mA)

At TJ= +25 ° C, V

C

= 10 µ F, unless otherwise noted.

OUT

OUT

= 1.5V, V

TYPICAL CHARACTERISTICS (continued)

= V

IN

OUT(TYP)

+ 0.3V, V

BIAS

= 3.3V, I

OUT

= 50mA, C

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

IN

= 1 µ F, C

= 1 µ F, C

BIAS

SS

= 0.01 µ F, and

SOFT-START CHARGING CURRENT (ISS)

vs TEMPERATURE LOW-LEVEL PG VOLTAGE vs PG CURRENT

Figure 20. Figure 21.

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 9

Product Folder Link(s): TPS74401

www.ti.com

50mV/div

50mV/div

50mV/div

50mV/div

2A/div

Time(50 s/div)m

C = 2x470 F(OSCON)

OUT

m

C = 100 F Cer.

OUT

m

C = 10 F Cer.

OUT

m

C =

OUT

0 Fm

1A/ sm

3.0A

100mA

10mV/div

10mV/div

10mV/div

10mV/div

500mV/div

Time(50 s/div)m

C =2x470 F(OSCON)

OUT

m

C =100 F(Cer.)

OUT

m

C =10 F(Cer.)

OUT

m

C =0 F

OUT

m

1V/ sm

4.3V

3.3V

1V/div

500mV/div

Time(1ms/div)

C =0 FSSm

C =0.001 FSSm

C =0.0047 FSSm

V

OUT

V

EN

0V

1.1V

10mV/div

10mV/div

10mV/div

10mV/div

500mV/div

Time(50 s/div)m

C =2x470 F

OUT

m

C =100 F(Cer.)

OUT

m

C =10 F

OUT

(Cer.)m

C =0 F

OUT

m

1V/ sm

2.5V

1.5V

V =1.2V

OUT

(OSCON)

Time(20 s/div)m

V

OUT

50mV/div

I

OUT

1A/div

OutputOpen

OutputShorted

V =0.8V

OUT

1V/div

Time(20ms/div)

V (500mV/div)

PG

V

OUT

V =V =V

IN BIAS EN

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

At TJ= +25 ° C, V

C

= 10 µ F, unless otherwise noted.

OUT

OUT

= 1.5V, V

= V

IN

TYPICAL CHARACTERISTICS (continued)

OUT(TYP)

+ 0.3V, V

BIAS

= 3.3V, I

OUT

= 50mA, C

IN

= 1 µ F, C

= 1 µ F, C

BIAS

SS

= 0.01 µ F, and

LOAD TRANSIENT RESPONSE V

Figure 22. Figure 23.

VINLINE TRANSIENT (3A) TURN-ON RESPONSE

LINE TRANSIENT (3A)

BIAS

Figure 24. Figure 25.

POWER-UP/POWER-DOWN OUTPUT SHORT-CIRCUIT RECOVERY

10 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Figure 26. Figure 27.

Product Folder Link(s): TPS74401

www.ti.com

TPS74401

GND

EN

FB

IN PG

SS

OUT

V

IN

V

OUT

V

PG

R

1

R

2

R

3

C

OUT

Optional

C

IN

1 Fm

C

SS

V

BIAS

C

BIAS

1 Fm

V =0.8

OUT

´ 1+

R

1

R

2

(

)

BIAS

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

APPLICATION INFORMATION

The TPS74401 belongs to a family of new

generation ultra-low dropout regulators that feature

soft-start and tracking capabilities. These regulators The device does not require any output capacitor for

use a low current bias input to power all internal stability. If an output capacitor is needed, the device

control circuitry, allowing the NMOS pass transistor to is designed to be stable for all available types and

regulate very low input and output voltages. values of output capacitance. The device is also

The use of an NMOS-pass FET offers several critical

advantages for many applications. Unlike a PMOS

topology device, the output capacitor has little effect The capacitance required on the IN and BIAS pins

on loop stability. This architecture allows the strongly depends on the input supply source

TPS74401 to be stable with any or even no output impedance. To counteract any inductance in the

capacitor. Transient response is also superior to input, the minimum recommended capacitor for V

PMOS topologies, particularly for low V

IN

applications. the same supply, the recommended minimum

The TPS74401 features a programmable,

voltage-controlled soft-start circuit that provides a

smooth, monotonic start-up and limits startup inrush

currents that may be caused by large capacitive

loads. A power-good (PG) output is available to allow

supply monitoring and sequencing of other supplies.

An enable (EN) pin with hysteresis and deglitch

allows slow-ramping signals to be used for

sequencing the device. The low V

and V

IN

OUT

capability allows for inexpensive, easy-to-design, and

efficient linear regulation between the multiple supply

voltages often present in processor intensive

systems.

Figure 28 illustrates a typical application circuit for the

TPS74401 adjustable output device.

R

and R

1

can be calculated for any output voltage output capacitance. With a solid input supply, adding

2

using the formula shown in Figure 28 . Refer to additional output capacitance reduces undershoot

Table 1 for sample resistor values of common output and overshoot during a transient at the expense of a

voltages. In order to achieve the maximum accuracy slightly longer V

specifications, R

should be ≤ 4.99k Ω . in the Typical Characteristics section. Since the

2

INPUT, OUTPUT, AND BIAS CAPACITOR REQUIREMENTS

stable with multiple capacitors in parallel, of any type

or value.

and V

capacitor for V

BIAS

is 1 µ F. If V

BIAS

and V

IN

are connected to

BIAS

is 4.7 µ F. Good quality, low ESR

capacitors should be used on the input; ceramic X5R

and X7R capacitors are preferred. These capacitors

should be placed as close the pins as possible for

optimum performance.

TRANSIENT RESPONSE

The TPS74401 was designed to have transient

response within 5% for most applications without any

output capacitor. In some cases, the transient

response may be limited by the transient response of

the input supply. This limitation is especially true in

applications where the difference between the input

and output is less than 300mV. In this case, adding

additional input capacitance improves the transient

response much more than just adding additional

recovery time. Refer to Figure 22

OUT

TPS74401 is stable without an output capacitor,

many applications may allow for little or no

capacitance at the LDO output. For these

applications, local bypass capacitance for the device

under power may be sufficient to meet the transient

requirements of the application. This design reduces

the total solution cost by avoiding the need to use

expensive high-value capacitors at the LDO output.

IN

Figure 28. Typical Application Circuit for the

TPS74401 (Adjustable)

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 11

Product Folder Link(s): TPS74401

www.ti.com

Reference

SimplifiedBlock Diagram

BIAS

FB

IN

V

IN

V =3.3V 5%

BIAS

±

V =3.3V 5%

V =1.5V

I =1.5A

Efficiency=45%

IN

OUT

OUT

±

V

OUT

OUT

Reference

SimplifiedBlock Diagram

V

OUT

OUT

BIAS

FB

IN

V =5V 5%

BIAS

±

V =1.8V

V =1.5V

I =1.5A

Efficiency=83%

IN

OUT

OUT

t

SS

+

ǒ

V

REF

C

SS

Ǔ

I

SS

t

SSCL

+

ǒ

V

OUT(NOM

)

C

OUT

Ǔ

I

CL(MIN

)

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

DROPOUT VOLTAGE

The TPS74401 offers industry-leading dropout

performance, making it well-suited for high-current

low VIN/low V

dropout of the TPS74401 allows the device to be

used in place of a DC/DC converter and still achieve

good efficiencies. This efficiency allows users to

rethink the power architecture for their applications to

achieve the smallest, simplest, and lowest cost

solution.

There are two different specifications for dropout

voltage with the TPS74401. The first specification

(see Figure 29 ) is referred to as V

for users that wish to apply an external bias voltage

to achieve low dropout. This specification assumes

that V

case for V

is at least 1.62V above V

BIAS

BIAS

tolerance and with V

3.3V × 0.95 or V

less than specified.

Figure 29. Typical Application of the TPS74401

Using an Auxiliary Bias Rail

applications. The extremely low

OUT

Dropout and is

IN

, which is the Figure 30. Typical Application of the TPS74401

OUT

when powered by a 3.3V rail with 5%

= 1.5V. If V

OUT

is less than 1.5V, V

OUT

is higher than

BIAS

dropout is

IN

Without an Auxiliary Bias

PROGRAMMABLE SOFT-START

The TPS74401 features a programmable, monotonic,

voltage-controlled soft-start that is set with an

external capacitor (C

many applications because it eliminates power-up

initialization problems when powering FPGAs, DSPs,

or other processors. The controlled voltage ramp of

the output also reduces peak inrush current during

start-up, minimizing start-up transients to the input

power bus.

To achieve a linear and monotonic soft-start, the

TPS74401 error amplifier tracks the voltage ramp of

the external soft-start capacitor until the voltage

exceeds the internal reference. The soft-start ramp

time depends on the soft-start charging current (I

the soft-start capacitance (C

reference voltage (V

Equation 1 :

). This feature is important for

SS

), and the internal

), and can be calculated using

REF

SS

),

SS

The second specification (see Figure 30 ) is referred

to as V

and BIAS together. This option allows the device to

be used in applications where an auxiliary bias

voltage is not available or low dropout is not required.

Dropout is limited by BIAS in these applications

because V

FET and therefore must be 1.62V above V

Because of this usage, IN and BIAS tied together

easily consume huge power. Pay attention not to

exceed the power rating of the IC package.

12 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Dropout and is for users that wish to tie IN

BIAS

provides the gate drive to the pass

BIAS

OUT

Product Folder Link(s): TPS74401

If large output capacitors are used, the device current

limit (I

) and the output capacitor may set the

CL

start-up time. In this case, the start-up time is given

by Equation 2 :

.

V

OUT(NOM)

the user, C

is the nominal set output voltage as set by

is the output capacitance, and I

OUT

is the minimum current limit for the device. In

applications where monotonic startup is required, the

soft-start time given by Equation 1 should be set to

be greater than Equation 2 .

(1)

(2)

CL(MIN)

www.ti.com

V

N

ǒ

mV

RMS

Ǔ

+ 16

ǒ

mV

RMS

V

Ǔ

V

OUT

(V)

TPS74401

GND

SS

OUT

FB

EN

IN

BIAS

V

IN

V

OUT

R

2

R

1

C

SS

C

IN

1 Fm

C

V

BIAS

C

BIAS

1 Fm

R

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

The maximum recommended soft-start capacitor is

0.015 µ F. Larger soft-start capacitors can be used and

will not damage the device; however, the soft-start

capacitor discharge circuit may not be able to fully

discharge the soft-start capacitor when re-enabled.

Soft-start capacitors larger than 0.015 µ F could be a

problem in applications where the user needs to

rapidly pulse the enable pin and still requires the

device to soft-start from ground. C

must be

SS

low-leakage; X7R, X5R, or C0G dielectric materials

are preferred. Refer to Table 2 for suggested

soft-start capacitor values.

OUTPUT NOISE

The TPS74401 provides low output noise when a

soft-start capacitor is used. When the device reaches

the end of the soft-start cycle, the soft-start capacitor

serves as a filter for the internal reference. By using a

0.001 µ F soft-start capacitor, the output noise is

reduced by half and is typically 19 µ V

output (100Hz to 100kHz). Because most of the

output noise is generated by the internal reference,

the noise is a function of the set output voltage. The

RMS noise with a 0.001 µ F soft-start capacitor is

given in Equation 3 .

RMS

SEQUENCING REQUIREMENTS

The device can have V

in any order without causing damage to the device.

However, for the soft-start function to work as

intended, certain sequencing rules must be applied.

Enabling the device after V

preferred, and can be accomplished using a digital

output from a processor or supply supervisor. An

analog signal from an external RC circuit, as shown

in Figure 31 , can also be used as long as the delay

time is long enough for V

Figure 31. Soft-Start Delay Using an RC Circuit on

If a signal is not available to enable the device after

IN and BIAS, simply connecting EN to IN is

acceptable for most applications as long as V

greater than 1.1V and the ramp rate of V

is faster the set soft-start ramp rate. If the ramp rate

of the input sources is slower than the set soft-start

time, the output will track the slower supply minus the

dropout voltage until it reaches the set output voltage.

If EN is connected to BIAS, the device will soft-start

as programmed provided that V

V

. If V

BIAS

and V

BIAS

applied and the set soft-start time has expired then

V

will track VIN.

OUT

NOTE: When V

BIAS

not supplied, this device outputs approximately 50 µ A

of current from OUT. Although this condition will not

cause any damage to the device, the output current

may charge up the OUT node if total resistance

between OUT and GND (including external feedback

resistors) is less than 10k Ω .

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 13

, V

IN

BIAS

and V

IN

and V

IN

Enable

are present before V

EN

and V

are present and V

EN

, and V

BIAS

IN

EN

are present is

BIAS

to be present.

is present before

sequenced

IN

and V

IN

IN

Product Folder Link(s): TPS74401

The low output noise of the TPS74401 makes it a

good choice for powering transceivers, PLLs, or other

noise-sensitive circuitry.

ENABLE/SHUTDOWN

The enable (EN) pin is active high and is compatible

with standard digital signaling levels. V

turns the regulator off, while V

EN

EN

above 1.1V turns the

regulator on. Unlike many regulators, the enable

circuitry has hysteresis and deglitching for use with

relatively slow-ramping analog signals. This

configuration allows the TPS74401 to be enabled by

connecting the output of another supply to the EN

pin. The enable circuitry typically has 50mV of

hysteresis and a deglitch circuit to help avoid on-off

cycling because of small glitches in the V

The enable threshold is typically 0.8V and varies with

temperature and process variations. Temperature

variation is approximately – 1mV/ ° C; therefore,

process variation accounts for most of the variation in

the enable threshold. If precise turn-on timing is

required, a fast rise-time signal should be used to

enable the TPS74401.

is

BIAS

If not used, EN can be connected to either IN or

BIAS. If EN is connected to IN, it should be

connected as close as possible to the largest

capacitance on the input to prevent voltage droops on

that line from triggering the enable circuit.

POWER-GOOD (QFN Package Only)

is

is

IN

The power-good (PG) pin is an open-drain output and

can be connected to any 5.5V or lower rail through an

external pull-up resistor. This pin requires at least

1.1V on V

output is high-impedance when V

V

+ V

IT

HYS

in order to have a valid output. The PG

BIAS

. If V

drops below V

OUT

OUT

IT

is greater than

or if V

below 1.9V, the open-drain output turns on and pulls

the PG output low. The PG pin also asserts when the

device is disabled. The recommended operating

condition of PG pin sink current is up to 1mA, so the

for a 1.2V

(3)

below 0.4V

signal.

EN

drops

BIAS

www.ti.com

P

D

+

ǒ

VIN* V

OUT

Ǔ

I

OUT

R

qJA

+

ǒ

)125°C * T

A

Ǔ

P

D

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

pull-up resistor for PG should be in the range of 10k Ω

LAYOUT RECOMMENDATIONS AND POWER

to 1M Ω . The pull-up resistor for PG should be in the DISSIPATION

range of 10k Ω to 1M Ω . PG is only provided on the

QFN package. If output voltage monitoring is not

needed, the PG pin can be left floating.

INTERNAL CURRENT LIMIT

The TPS74401 features a factory-trimmed, accurate

current limit that is flat over temperature and supply

voltage. The current limit allows the device to supply

surges of up to 3.5A and maintain regulation. The

current limit responds in about 10 µ s to reduce the

current during a short-circuit fault. Recovery from a

short-circuit condition is well-controlled and results in

very little output overshoot when the load is removed.

See Figure 27 in the Typical Characteristics section

for short-circuit recovery performance.

The internal current limit protection circuitry of the

TPS74401 is designed to protect against overload

conditions. It is not intended to allow operation above

the rated current of the device. Continuously running

the TPS74401 above the rated current degrades

device reliability.

An optimal layout can greatly improve transient

performance, PSRR, and noise. To minimize the

voltage droop on the input of the device during load

transients, the capacitance on IN and BIAS should be

connected as close as possible to the device. This

capacitance also minimizes the effects of parasitic

inductance and resistance of the input source and

can therefore improve stability. To achieve optimal

transient performance and accuracy, the top side of

R

in Figure 28 should be connected as close as

1

possible to the load. If BIAS is connected to IN, it is

recommended to connect BIAS as close to the sense

point of the input supply as possible. This connection

minimizes the voltage droop on BIAS during transient

conditions and can improve the turn-on response.

Knowing the device power dissipation and proper

sizing of the thermal plane that is connected to the

tab or pad is critical to avoiding thermal shutdown

and ensuring reliable operation. Power dissipation of

the device depends on input voltage and load

conditions, and can be calculated using Equation 4 :

THERMAL PROTECTION

Thermal protection disables the output when the

junction temperature rises to approximately +155 ° C,

allowing the device to cool. When the junction

temperature cools to approximately +140 ° C, the

output circuitry is enabled. Depending on power On both the QFN (RGW) and DDPAK (KTW)

dissipation, thermal resistance, and ambient packages, the primary conduction path for heat is

temperature the thermal protection circuit may cycle through the exposed pad or tab to the printed circuit

on and off. This cycling limits the dissipation of the board (PCB). The pad or tab can be connected to

regulator, protecting it from damage as a result of ground or be left floating; however, it should be

overheating. attached to an appropriate amount of copper PCB

Activation of the thermal protection circuit indicates

excessive power dissipation or inadequate

heatsinking. For reliable operation, junction

temperature should be limited to +125 ° C maximum.

To estimate the margin of safety in a complete design

(including heatsink), increase the ambient

temperature until thermal protection is triggered; use

worst-case loads and signal conditions. For good

reliability, thermal protection should trigger at least

+30 ° C above the maximum expected ambient

condition of the application. This condition produces a

worst-case junction temperature of +125 ° C at the

highest expected ambient temperature and

worst-case load.

The internal protection circuitry of the TPS74401 is

designed to protect against overload conditions. It is

not intended to replace proper heatsinking.

Continuously running the TPS74401 into thermal

shutdown degrades device reliability.

Power dissipation can be minimized and greater

efficiency can be achieved by using the lowest

possible input voltage necessary to achieve the

required output voltage regulation.

area to ensure the device does not overheat. The

maximum junction-to-ambient thermal resistance

depends on the maximum ambient temperature,

maximum device junction temperature, and power

dissipation of the device, and can be calculated using

Equation 5 :

Knowing the maximum R

and system air flow, the

θ JA

minimum amount of PCB copper area needed for

appropriate heatsinking can be calculated using

Figure 32 through Figure 36 .

(4)

(5)

14 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS74401

www.ti.com

55

50

45

40

35

30

25

0

0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

q

JA

(

°C/W)

Area(in )

2

4.5

0LFM

150LFM

250LFM

T

J

R

qJC

R

qCS

R

qSA

T

C

T

S

T

A

4-layer.0.062” FR4

Viasare0.012” diameter,plated

Top/Bottomlayersare2oz.copper

Innerlayersare1oz.copper

0.062in.

R

qJA

= R +R +R

q q qJC C S SA

PCBCrossSection

PCBTopView

0.5in

2

1.0in

2

2.0in

2

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

Figure 32. PCB Layout and Corresponding R

Data, Buried Thermal Plane, No Vias Under Thermal Pad

θ JA

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 15

Product Folder Link(s): TPS74401

www.ti.com

T

J

R

qJC

R

qCS

R

qSA

T

C

T

S

T

A

4-layer.0.062” FR4

Viasare0.012” diameter,plated

Top/Bottomlayersare2oz.copper

Innerlayersare1oz.copper

0.062in.

R

qJA

= R +R +R

q q qJC C S SA

50

45

40

35

30

25

20

0

0.5 1.0 1.5 2.0 2.5 3.0 3.5

q

JA

(°C/W)

Area(in )

2

4.0

0LFM

150LFM

250LFM

PCBCrossSection

PCBTopView

0.5in

2

1.0in

2

2.0in

2

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

Figure 33. PCB Layout and Corresponding R

Data, Buried Thermal Plane, Vias Under Thermal Pad

θ JA

16 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS74401

www.ti.com

4-layer.0.062” FR4

Viasare0.012” diameter,plated

Top/Bottomlayersare2oz.copper

Innerlayersare1oz.copper

T

J

R

qJC

R

qCS

R

qSA

T

C

T

S

T

A

0.062in.

R

qJA

= R +R +R

q q qJC CS SA

90

80

70

60

50

40

30

0

0.5 1.0 1.5 2.0 2.5 3.0 3.5

q

JA

(°C/W)

Area(in )

2

4.0

0LFM

150LFM

250LFM

PCBCrossSection

PCBTopView

0.5in

2

1.0in

2

2.0in

2

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

Figure 34. PCB Layout and Corresponding R

Data, Top Layer Thermal Plane

θ JA

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 17

Product Folder Link(s): TPS74401

www.ti.com

35

30

25

20

15

0

0.5 1.0 1.5 2.0 2.5 3.0 3.5

q

JA

(°C/W)

Area(in )

2

4.0

0LFM

T

J

R

qJC

R

qCS

R

qSA

T

C

T

S

T

A

4-layer.0.062” FR4

Viasare0.012” diameter,plated

Top/Bottomlayersare2oz.copper

Innerlayersare1oz.copper

0.062in.

R

qJA

= R +R +R

q q qJC CS SA

PCBCrossSection

PCBTopView

0.5in

2

1.0in

2

2.0in

2

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

Figure 35. PCB Layout and Corresponding R

, Buried Thermal Plane

θ JA

18 Submit Documentation Feedback Copyright © 2005 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TPS74401

www.ti.com

4-layer.0.062” FR4

Viasare0.012” diameter,plated

Top/Bottomlayersare2oz.copper

Innerlayersare1oz.copper

T

J

R

qJC

R

qCS

R

qSA

T

C

T

S

T

A

0.062in.

R

qJA

= R +R +R

q q qJC C S SA

55

50

45

40

35

30

25

20

15

10

0

0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

q

JA

(°C/W)

Area(in )

2

4.5

0LFM

PCBCrossSection

PCBTopView

0.5in

2

1.0in

2

2.0in

2

TPS74401

SBVS066H – DECEMBER 2005 – REVISED MARCH 2008

Figure 36. PCB Layout and Corresponding R

, Top Layer Thermal Plane

θ JA

Copyright © 2005 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 19

Product Folder Link(s): TPS74401

PACKAGE OPTION ADDENDUM

www.ti.com

18-Mar-2008

PACKAGING INFORMATION

Orderable Device Status

(1)

Package

Type

Package

Drawing

Pins Package

Qty

Eco Plan

TPS74401KTWR ACTIVE DDPAK KTW 7 500 Green (RoHS &

no Sb/Br)

TPS74401KTWRG3 ACTIVE DDPAK KTW 7 500 Green (RoHS &

no Sb/Br)

TPS74401KTWT ACTIVE DDPAK KTW 7 50 Green (RoHS &

no Sb/Br)

TPS74401KTWTG3 ACTIVE DDPAK KTW 7 50 Green (RoHS &

no Sb/Br)

TPS74401RGWR ACTIVE QFN RGW 20 3000 Green (RoHS &

no Sb/Br)

TPS74401RGWRG4 ACTIVE QFN RGW 20 3000 Green (RoHS &

no Sb/Br)

TPS74401RGWT ACTIVE QFN RGW 20 250 Green (RoHS &

no Sb/Br)

TPS74401RGWTG4 ACTIVE QFN RGW 20 250 Green (RoHS &

no Sb/Br)

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in

a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

Lead/Ball Finish MSL Peak Temp

CU SN Level-3-245C-168 HR

CU SN Level-3-245C-168 HR

CU SN Level-3-245C-168 HR

CU SN Level-3-245C-168 HR

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

(3)

(2)

Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check

http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements

for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered

at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and

package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS

compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame

retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3)

MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder

temperature.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is

provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the

accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take

reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on

incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited

information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI

to Customer on an annual basis.

Addendum-Page 1

PACKAGE MATERIALS INFORMATION

www.ti.com

TAPE AND REEL INFORMATION

18-Mar-2008

*All dimensions are nominal

Device Package

TPS74401KTWR DDPAK KTW 7 500 330.0 24.4 10.6 15.6 4.9 16.0 24.0 Q2

TPS74401KTWT DDPAK KTW 7 50 330.0 24.4 10.6 15.6 4.9 16.0 24.0 Q2

TPS74401RGWR QFN RGW 20 3000 330.0 12.4 5.3 5.3 1.5 8.0 12.0 Q2

TPS74401RGWT QFN RGW 20 250 180.0 12.4 5.3 5.3 1.5 8.0 12.0 Q2

Type

Package

Drawing

Pins SPQ Reel

Diameter

(mm)

Reel

Width

W1 (mm)

A0 (mm) B0 (mm) K0 (mm) P1

(mm)W(mm)

Pin1

Quadrant

Pack Materials-Page 1

PACKAGE MATERIALS INFORMATION

www.ti.com

18-Mar-2008

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

TPS74401KTWR DDPAK KTW 7 500 346.0 346.0 41.0

TPS74401KTWT DDPAK KTW 7 50 346.0 346.0 41.0

TPS74401RGWR QFN RGW 20 3000 346.0 346.0 29.0

TPS74401RGWT QFN RGW 20 250 190.5 212.7 31.8

Pack Materials-Page 2

MECHANICAL DATA

MPSF015 – AUGUST 2001

KTW (R-PSFM-G7) PLASTIC FLANGE-MOUNT

0.0625 (1,587)

0.0585 (1,485)

H

0.605 (15,37)

0.595 (15,11)

H

0.370 (9,40)

0.330 (8,38)

C

C

0.410 (10,41)

0.385 (9,78)

0.303 (7,70)

0.297 (7,54)

0.050 (1,27)

0.034 (0,86)

F

0.022 (0,57)

0.010 (0,25)

–A–

0.055 (1,40)

0.045 (1,14)

A

0.012 (0,305)

0.000 (0,00)

0.019 (0,48)

0.017 (0,43)

0.026 (0,66)

C

0.014 (0,36)

B

A

M

M

C

M

0.006

–B–

0.104 (2,64)

0.096 (2,44)

0.064 (1,63)

0.056 (1,42)

0.187 (4,75)

0.179 (4,55)

H

0°~3°

0.304 (7,72)

0.296 (7,52)

0.300 (7,62)

0.252 (6,40)

0.183 (4,65)

0.170 (4,32)

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Lead width and height dimensions apply to the

plated lead.

D. Leads are not allowed above the Datum B.

E. Stand–off height is measured from lead tip

with reference to Datum B.

F. Lead width dimension does not include dambar

protrusion. Allowable dambar protrusion shall not

cause the lead width to exceed the maximum

dimension by more than 0.003”.

G. Cross–hatch indicates exposed metal surface.

H. Falls within JEDEC MO–169 with the exception

of the dimensions indicated.

4201284/A 08/01

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements,

and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should

obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are

sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard

warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where

mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right,

or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied

by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive

business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional

restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all

express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not

responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably

be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing

such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and

acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products

and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be

provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in

such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at

the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are

designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated

products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Clocks and Timers www.ti.com/clocks Digital Control www.ti.com/digitalcontrol

Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

RFID www.ti-rfid.com Telephony www.ti.com/telephony

RF/IF and ZigBee® Solutions www.ti.com/lprf Video & Imaging www.ti.com/video

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2008, Texas Instruments Incorporated

Wireless www.ti.com/wireless

Loading...

Loading...