Page 1

TPS65917-Q1 Register Map

Technical Reference Manual

Literature Number: SLVUAH1C

June 2015–Revised April 2017

Page 2

This document presents a summary of the hardware interface for the TPS65917-Q1 device. Each module

instance within the design is shown along with the module register map and bit definitions for each bitfield.

1.1 Register Address Mapping

This document describes the register mapping of the TPS65917-Q1 device. The operation of the IC is

described in the device data sheet, TPS65917-Q1 Power Management Unit (PMU) for Processor.

The 3 hex digits of the physical address of the register indicated in this document are mapped as 0xPAA,

while P stands for the page number of the register, and AA stands for the register address within the

memory page. The page numbers are mapped to the slave device address as following:

Page = 0x0 — Slave Device address 0x12 for DVS registers

Page = 0x1 — Slave Device address 0x48 or 0x58 for Power registers

Page = 0x2 — Slave Device address 0x49 or 0x59 for Interfaces and Auxiliaries registers

Page = 0x3 — Slave Device address 0x4A or 0x5A for Trimming and Test registers

Chapter 1

SLVUAH1C–June 2015–Revised April 2017

Introduction

Page = 0x4 —Slave Device address 0x4B or 0x5B for OTP programming registers

For the reset of the registers, the registers are defined by 3 categories:

• POR: Power On Reset registers

• HWRST: Hardware Reset registers

• SWORST: Switch Off Reset registers

These categories of registers (POR, HWRST, SWORST) are described in the device data sheet. When

the reset value of a bit register is 0bX, it means the bit value is coming from the OTP memory.

NOTE: All reserved bits are read only (R). Read to an unmapped register returns previous read

value.

2

Introduction

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 3

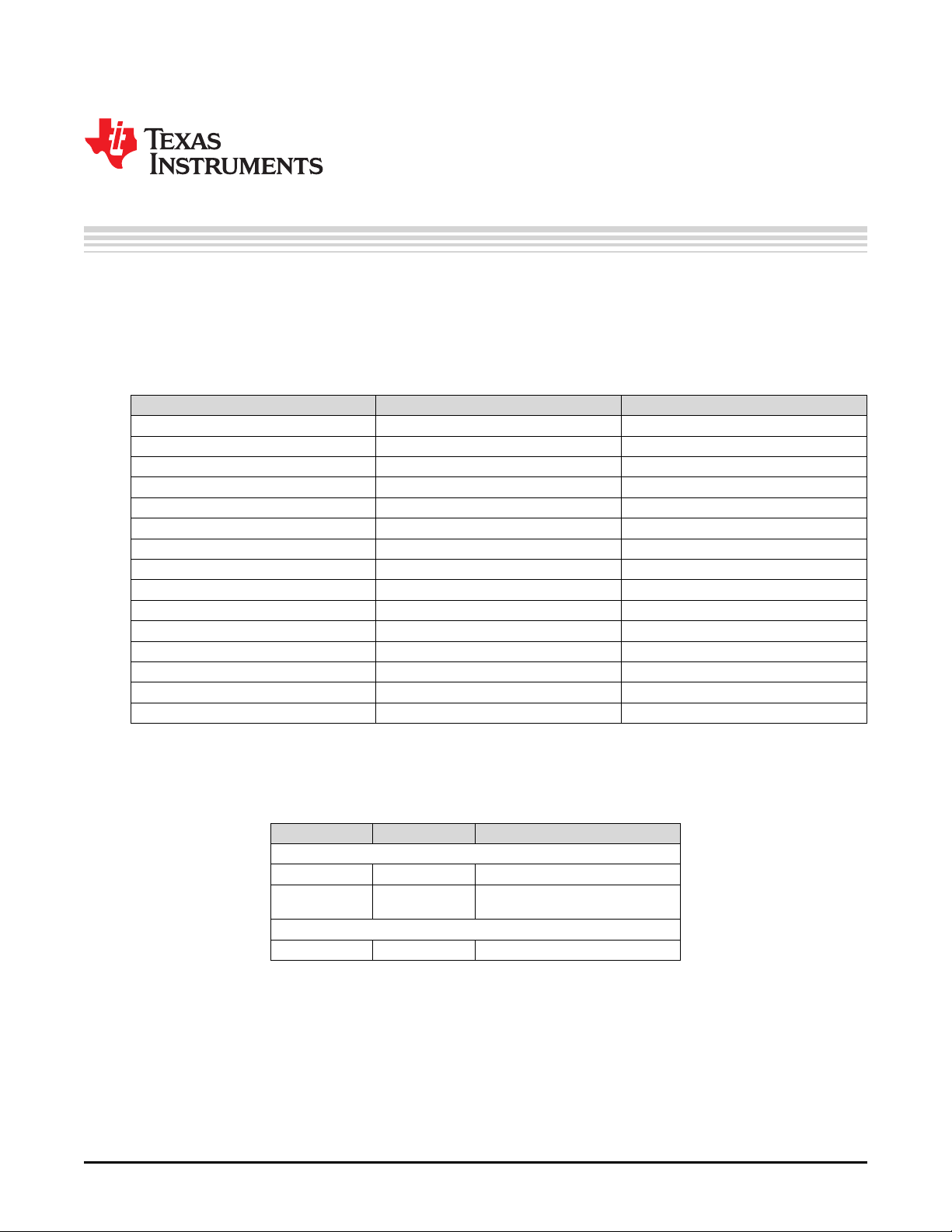

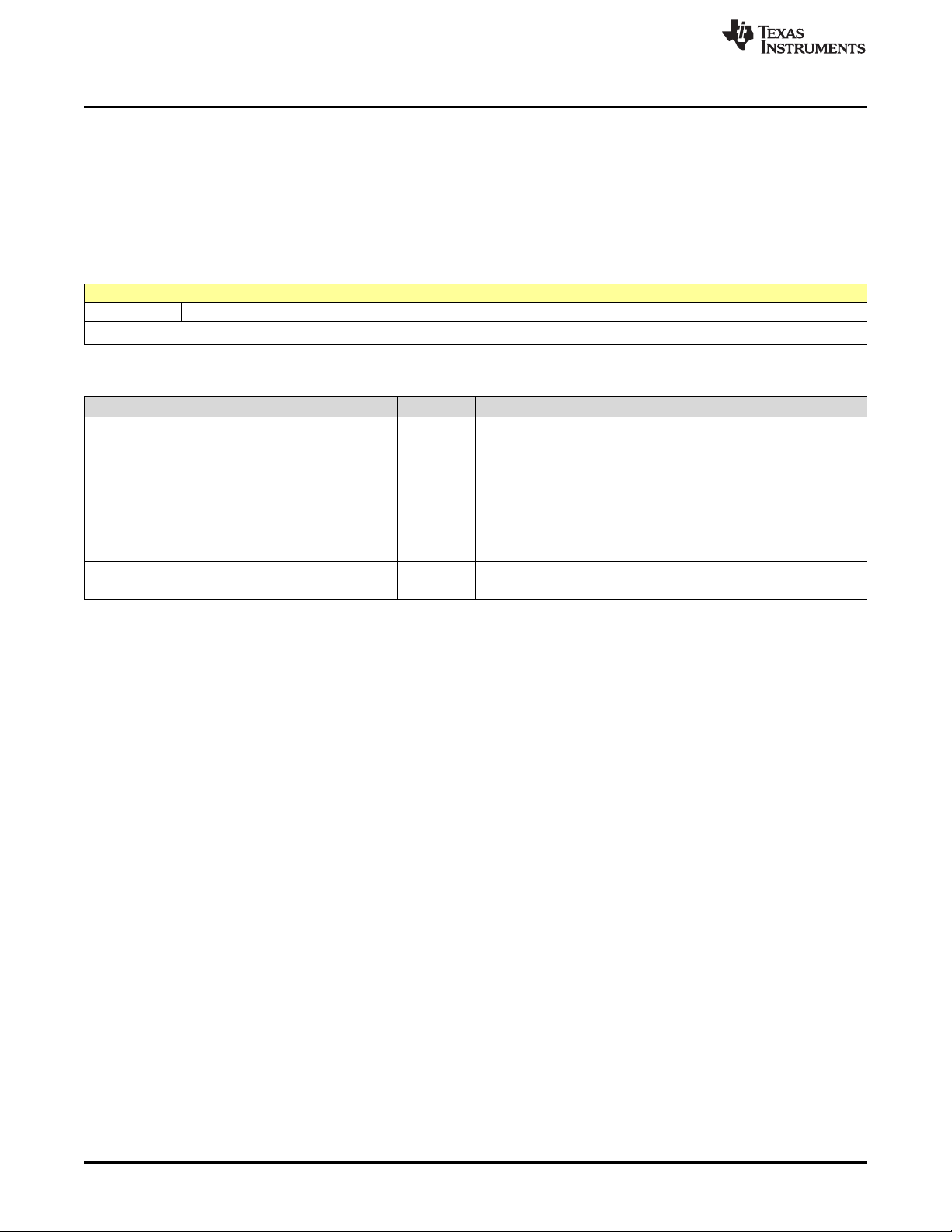

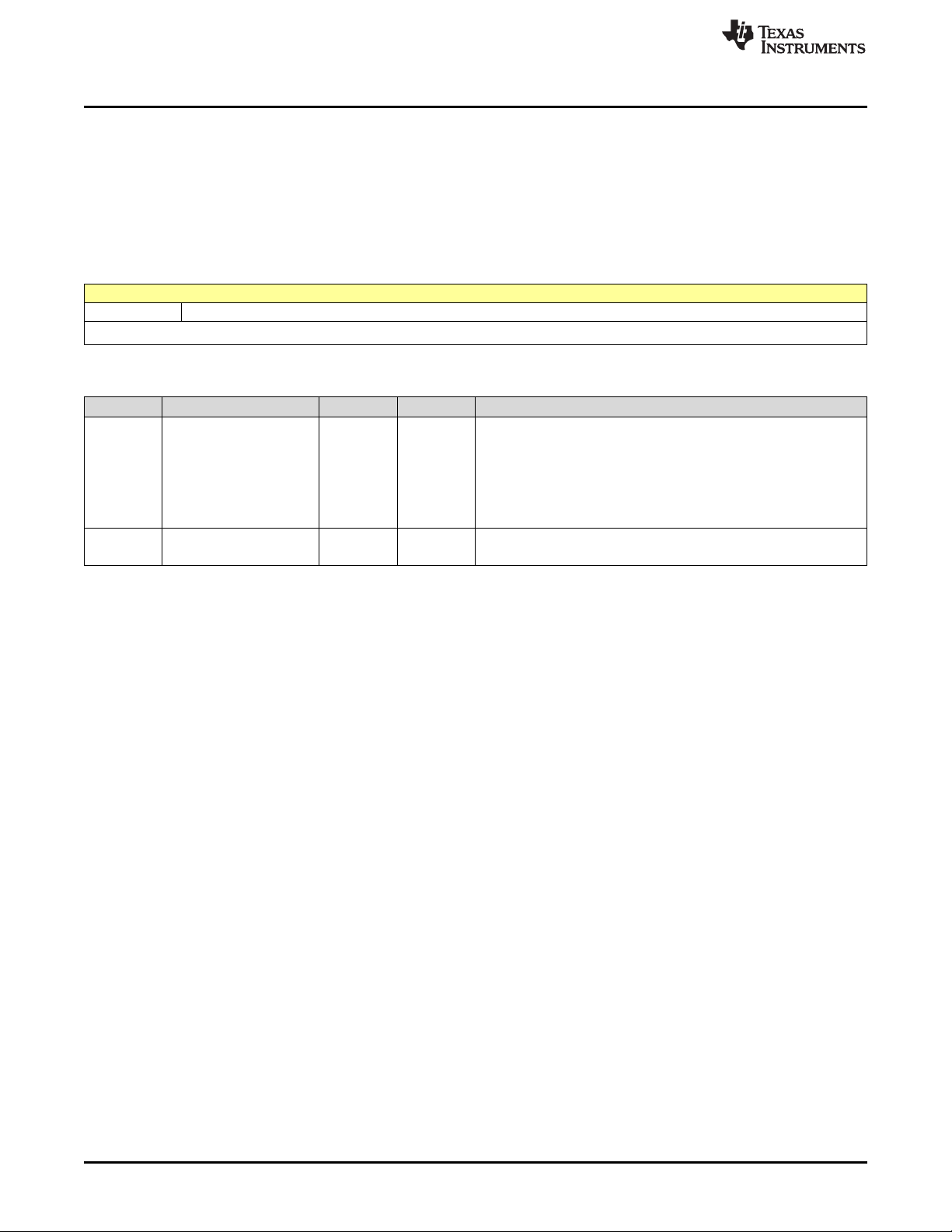

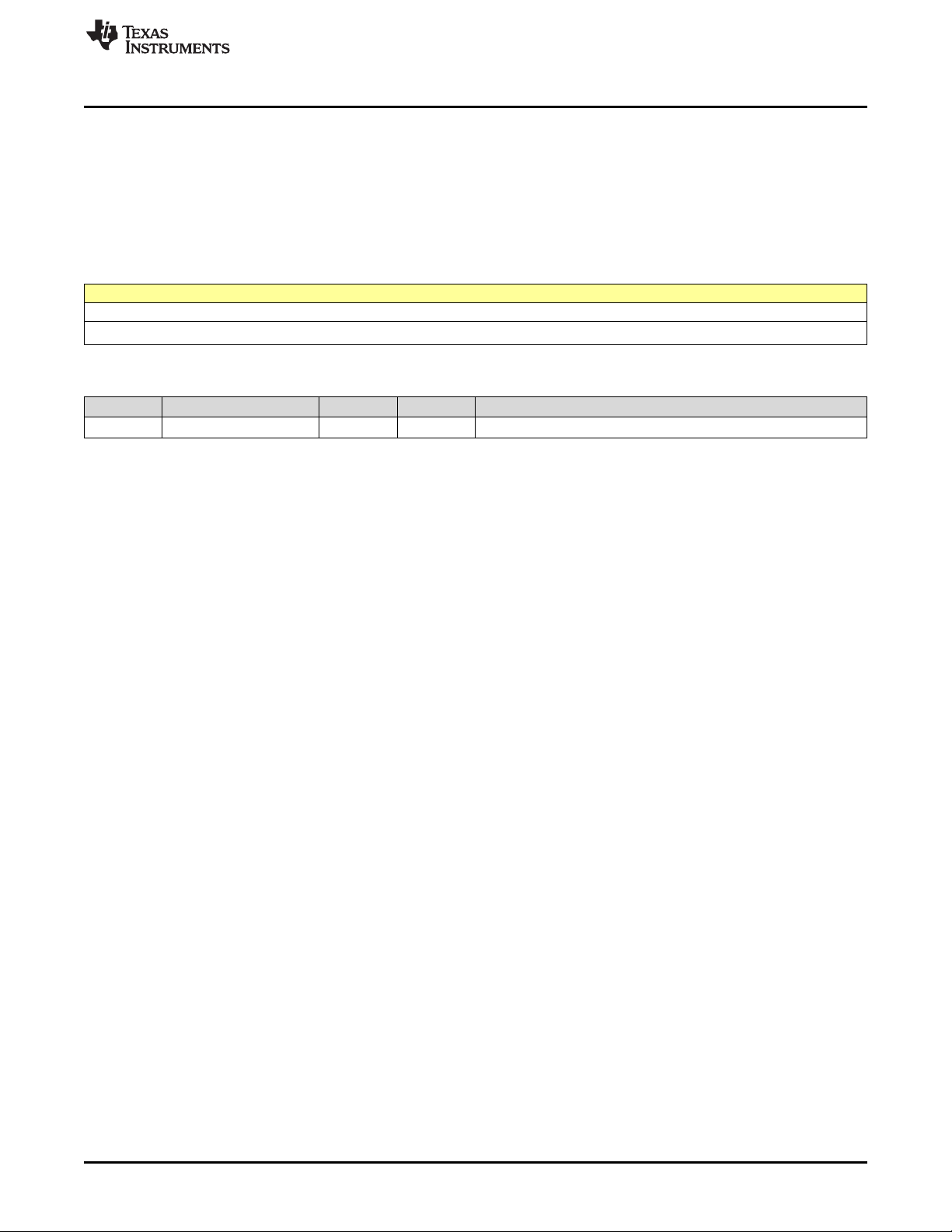

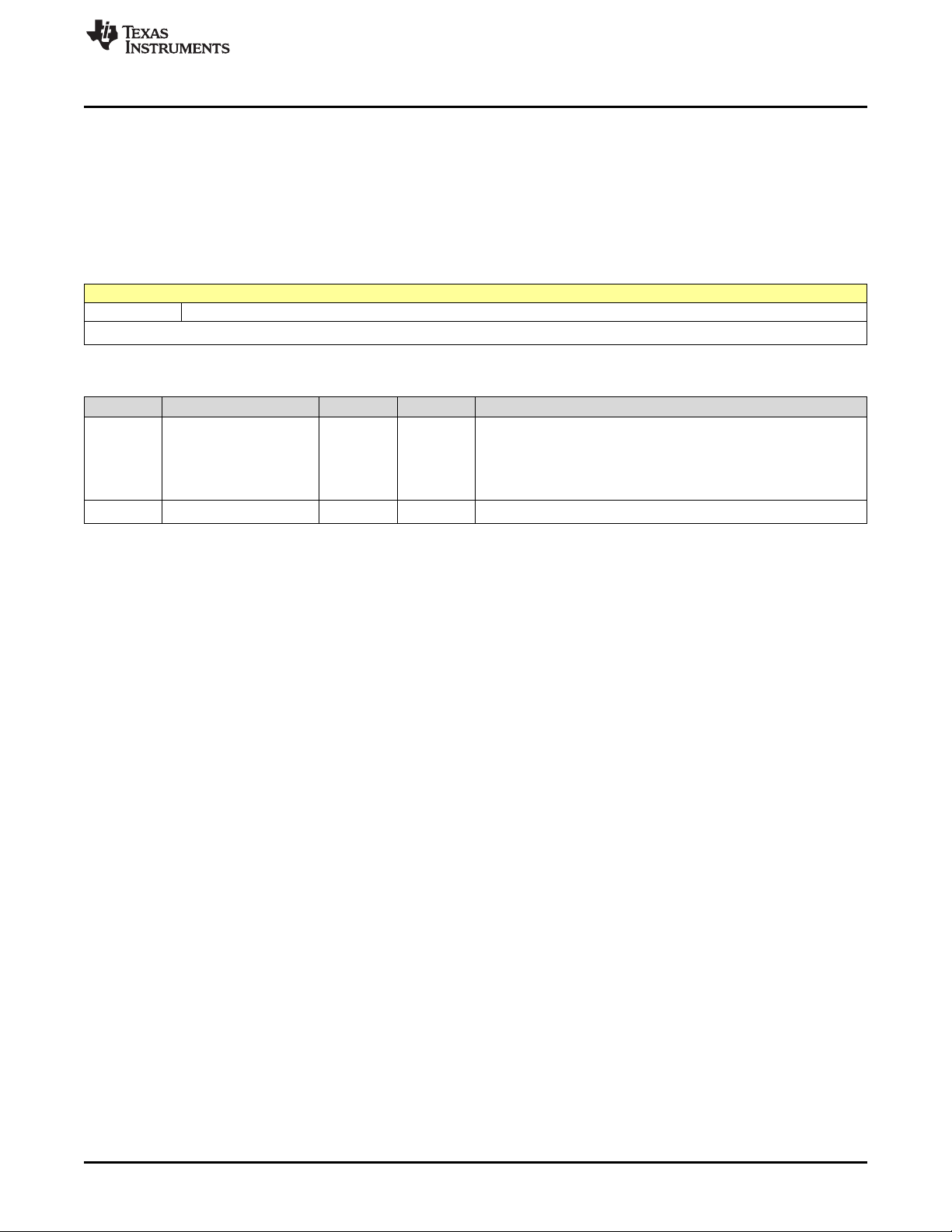

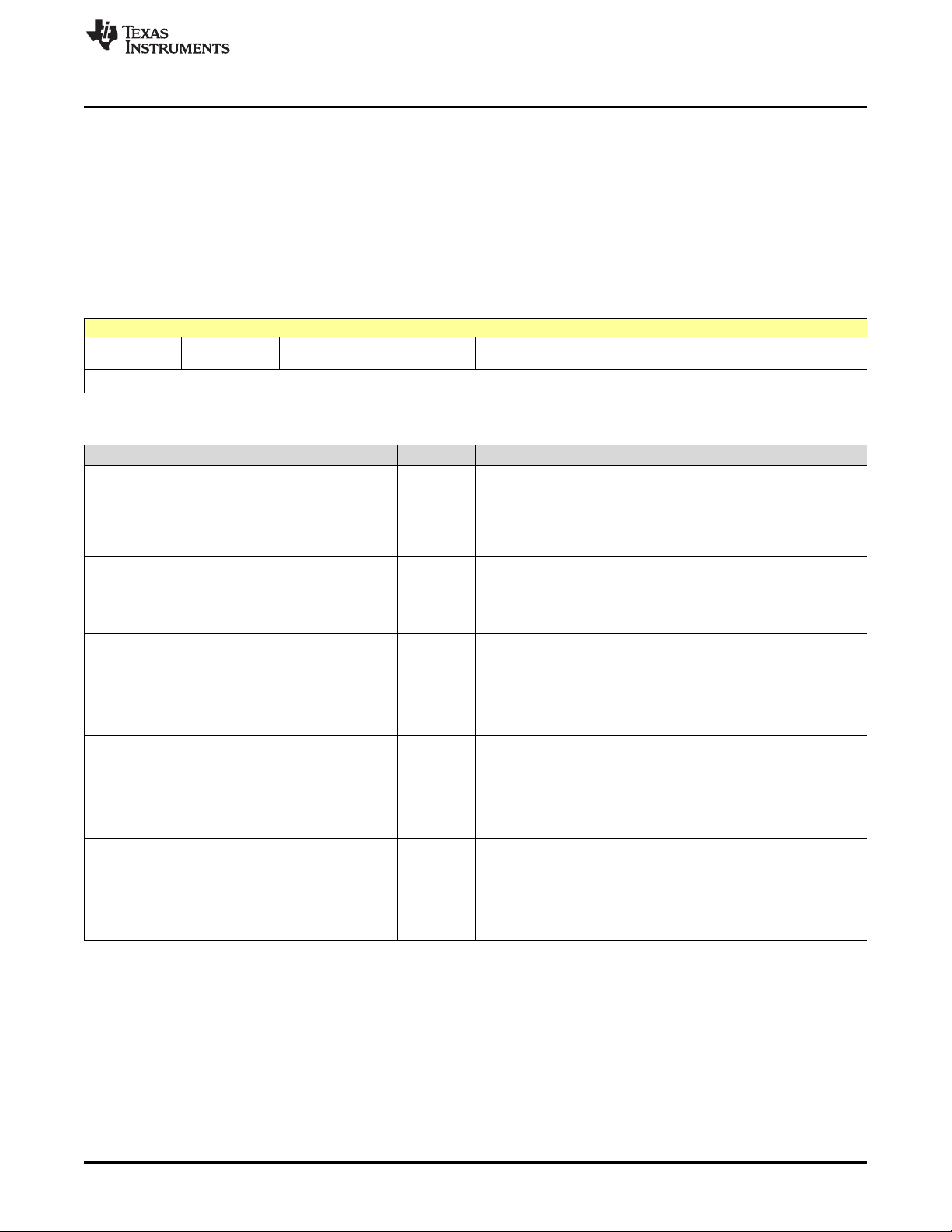

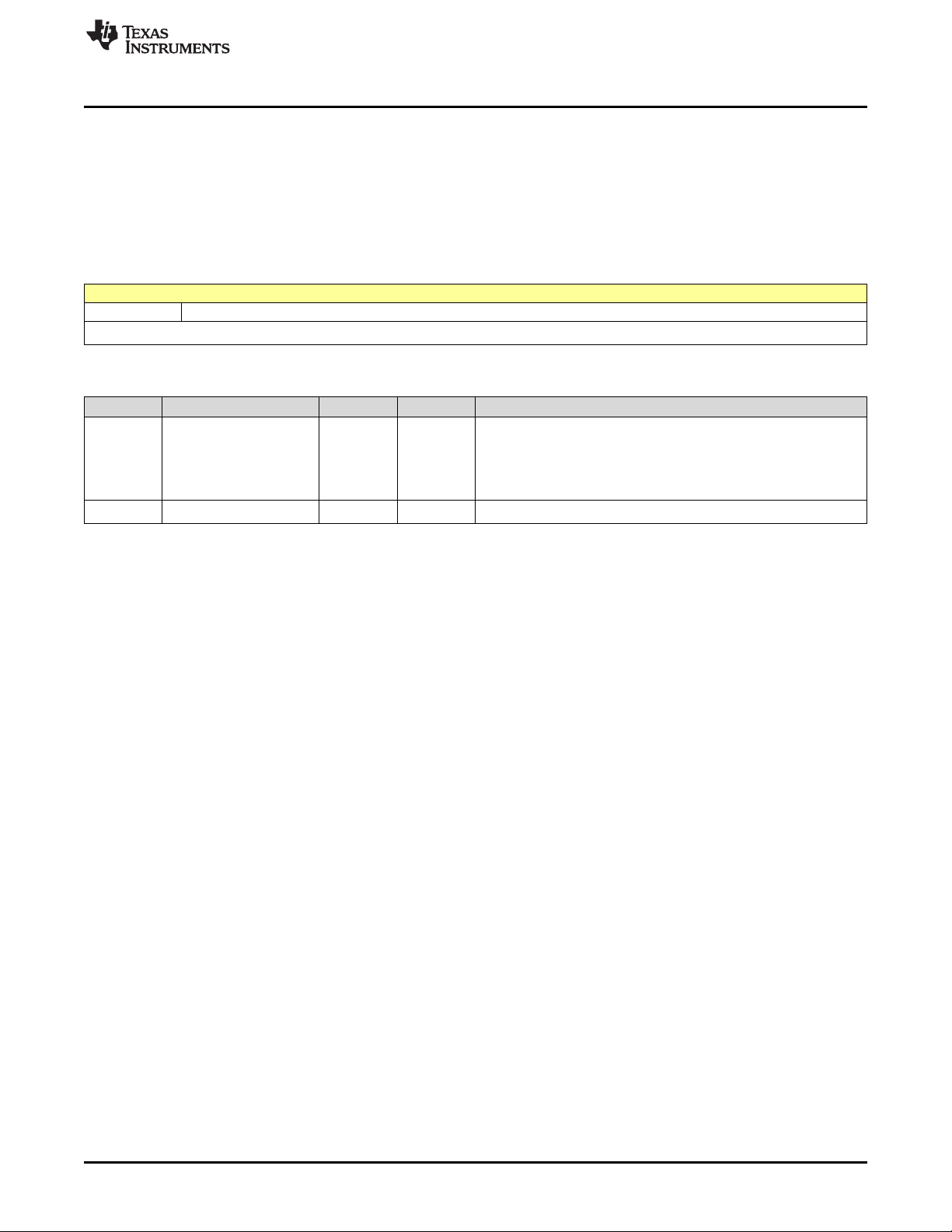

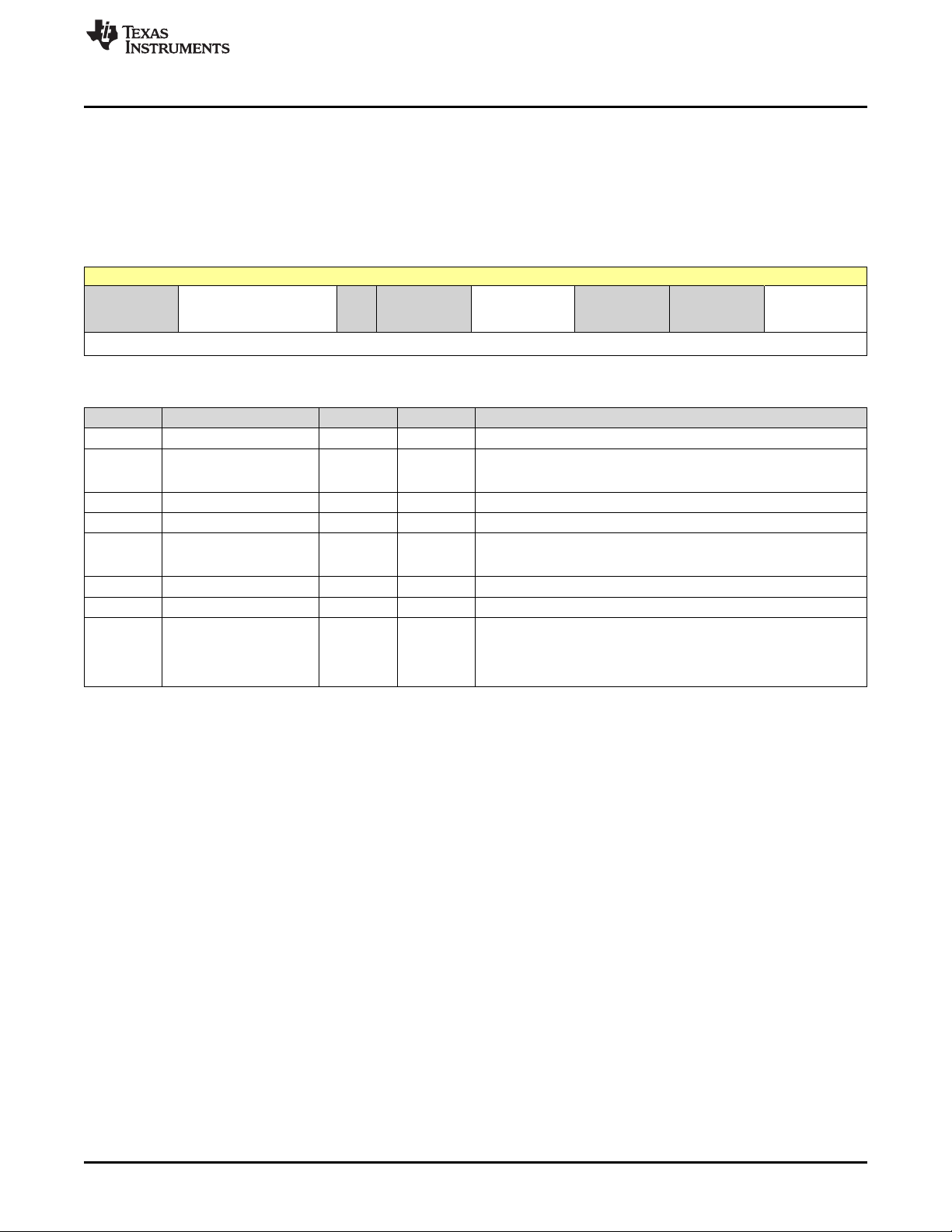

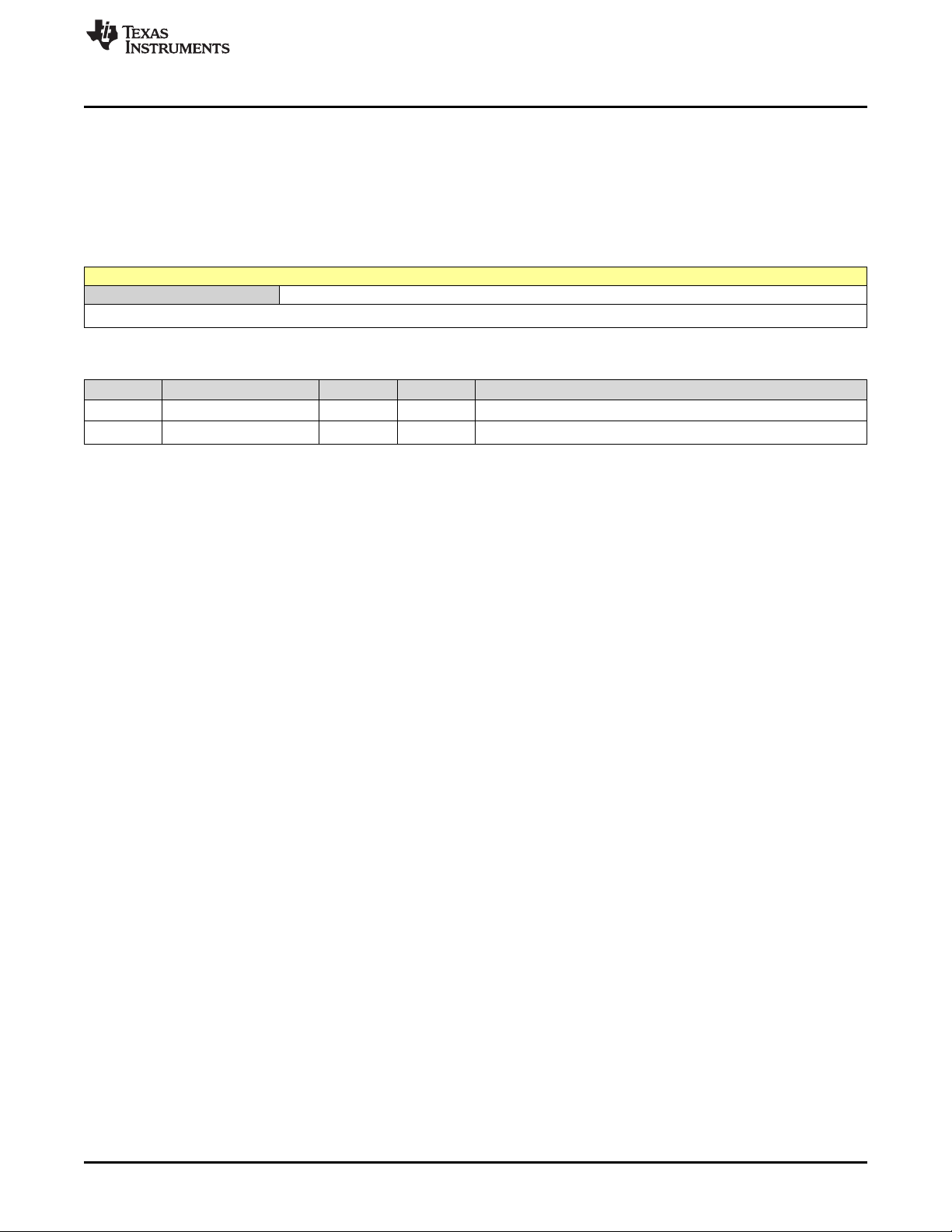

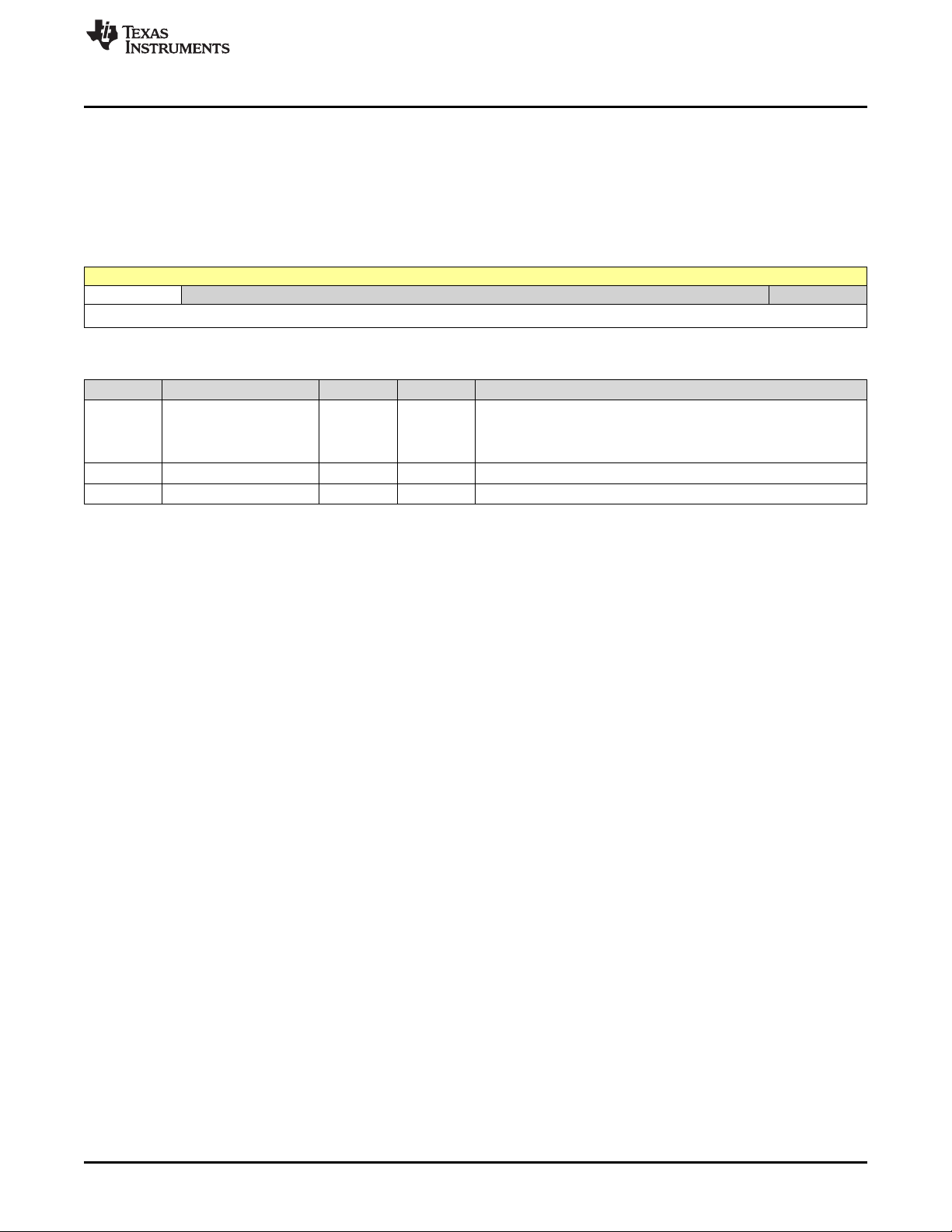

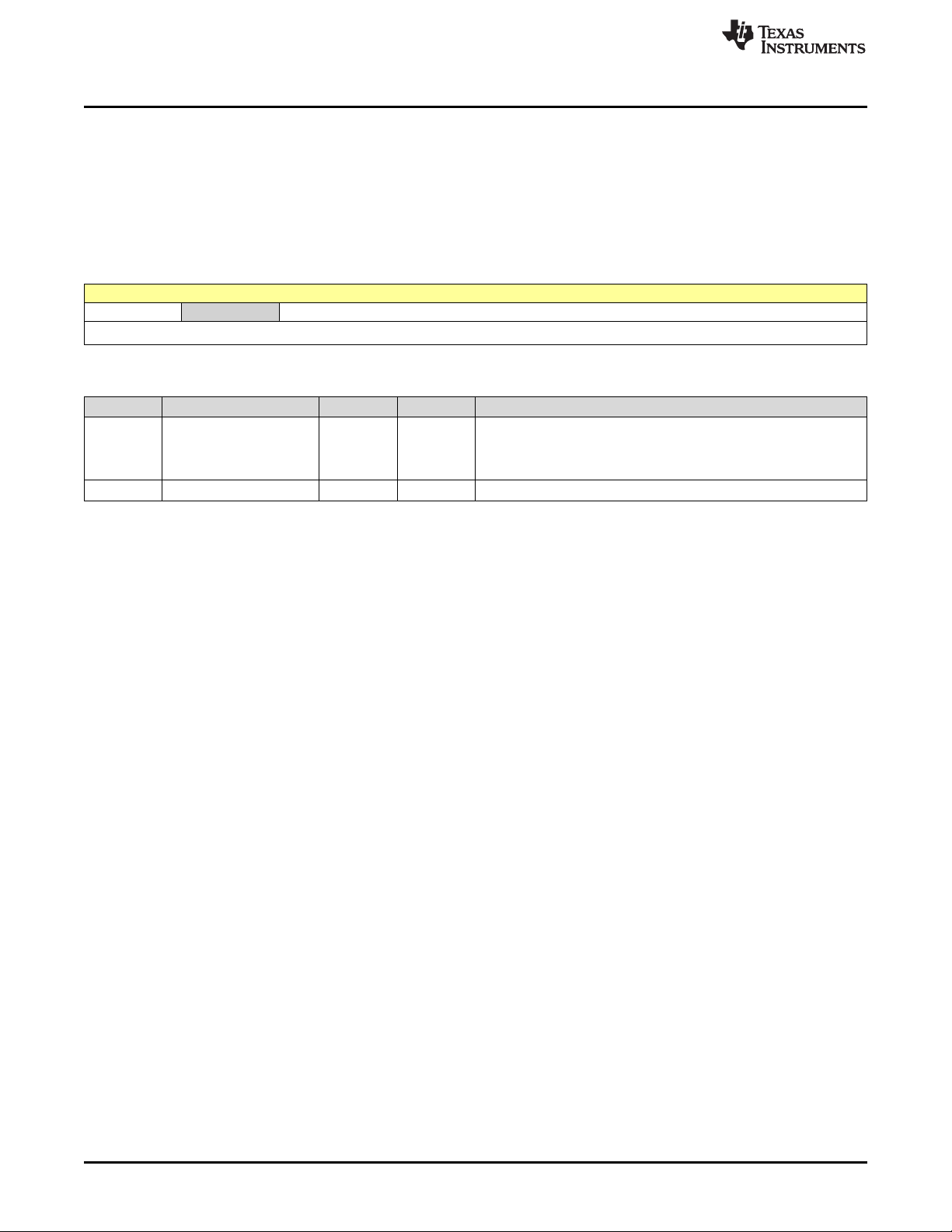

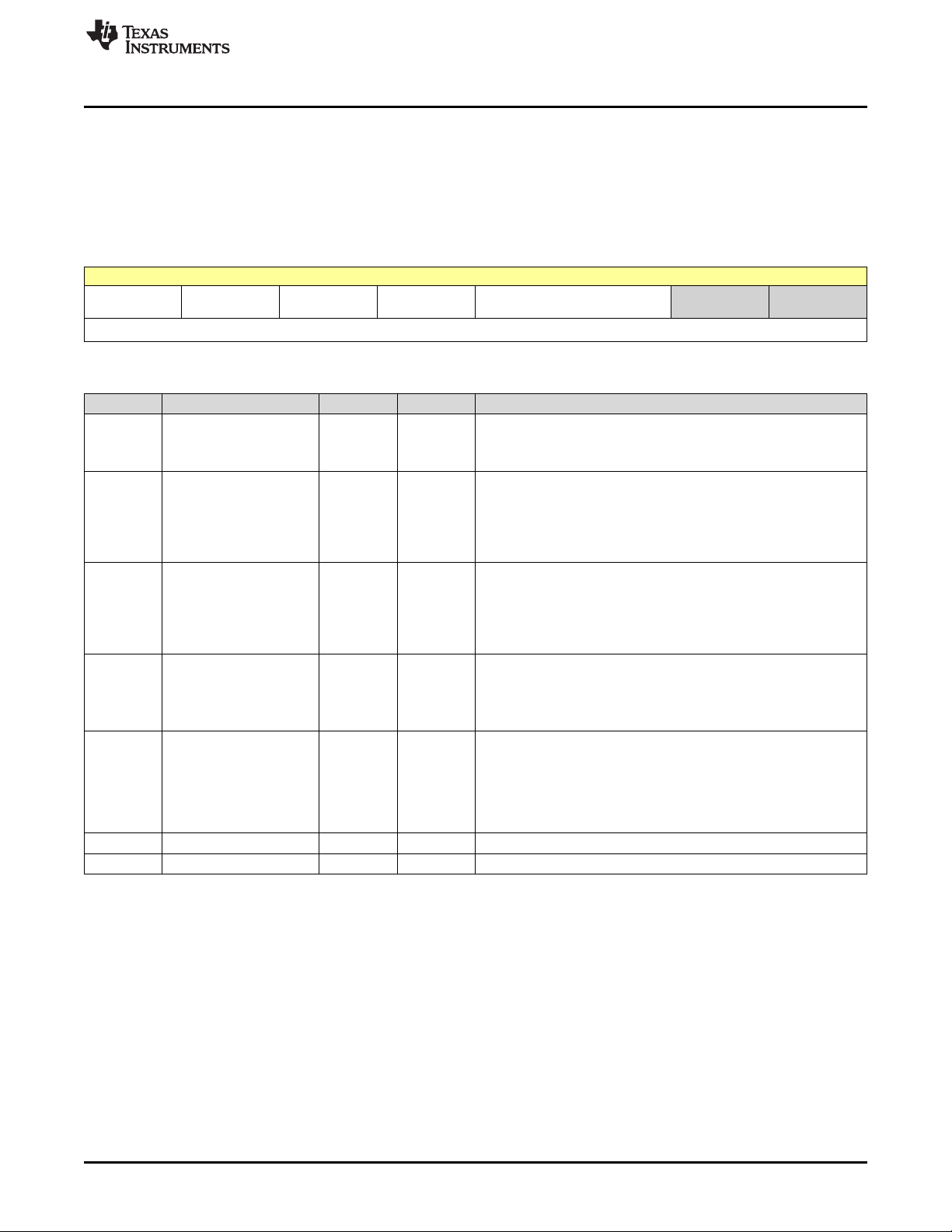

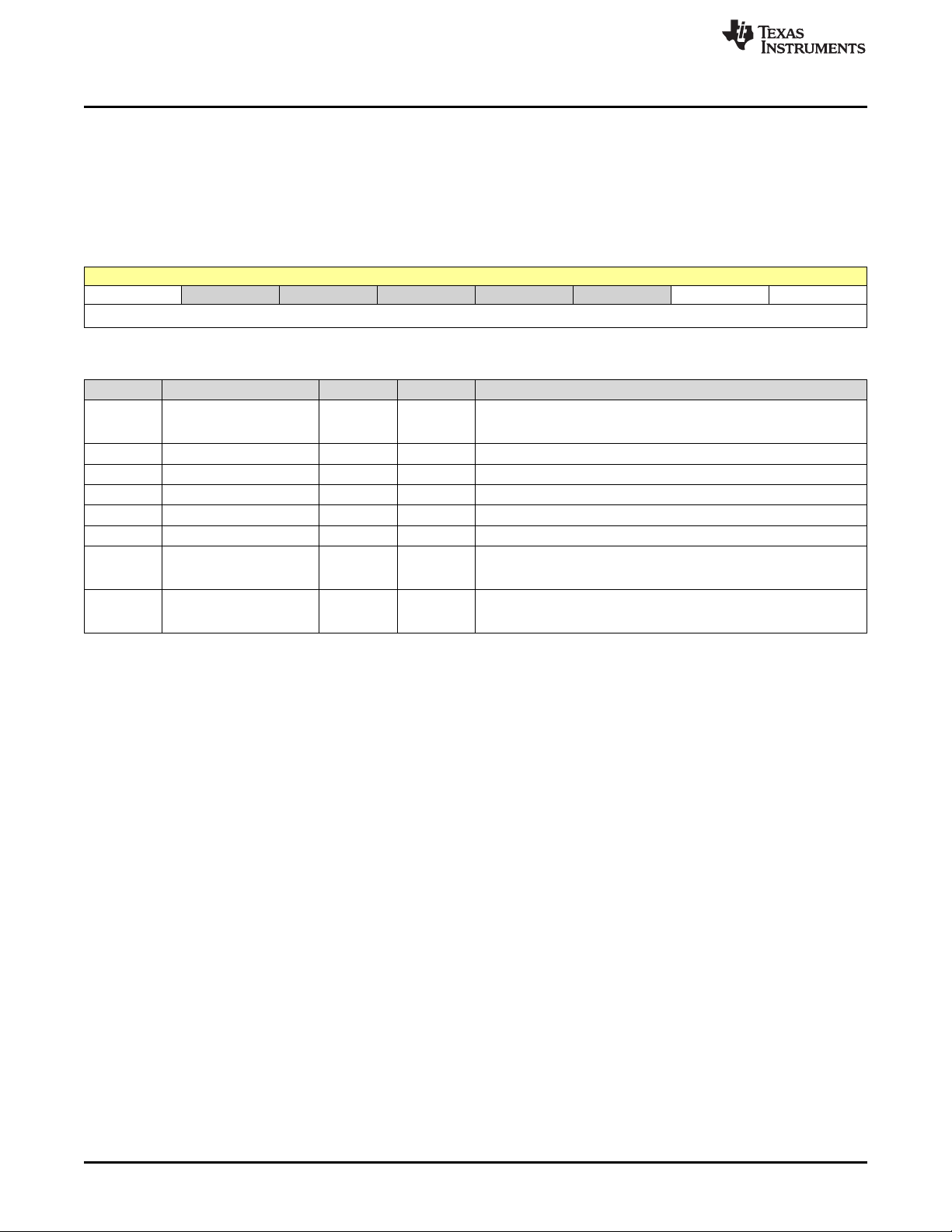

2.1 Register Module Base Address and Size

Table 2-1 lists the base address and address space for the TPS65917-Q1 device functional register

modules.

Table 2-1. TPS65917-Q1 Function Register Module Name and Base Address

Module Name Base Address Size

FUNC_SMPS_DVS 0x020 32 Bytes

FUNC_BACKUP 0x118 8 Bytes

FUNC_SMPS 0x120 48 Bytes

FUNC_LDO 0x150 47 Bytes

FUNC_SPI 0x17F 1 Byte

FUNC_DVFS 0x180 8 Bytes

FUNC_PMU_CONTROL 0x1A0 32 Bytes

FUNC_RESOURCE 0x1D4 28 Bytes

FUNC_PAD_CONTROL 0x1F0 16 Bytes

FUNC_INTERRUPT 0x210 32 Bytes

FUNC_ID 0x24F 4 Bytes

FUNC_GPIO 0x280 20 Bytes

FUNC_GPADC 0x2C0 32 Bytes

FUNC_DESIGNREV 0x357 1 Byte

FUNC_TRIM_GPADC 0x3CD 18 Bytes

Chapter 2

SLVUAH1C–June 2015–Revised April 2017

Register Physical Address

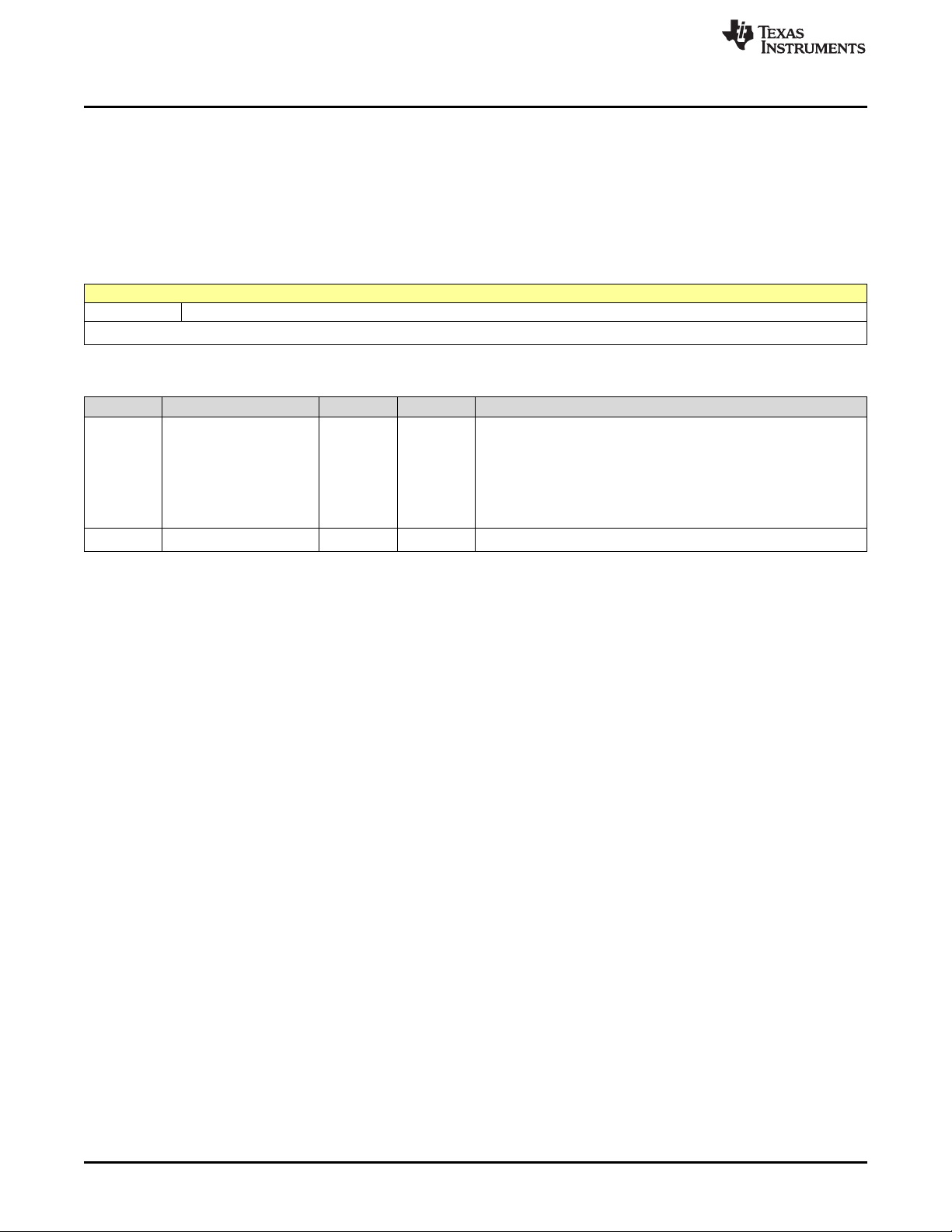

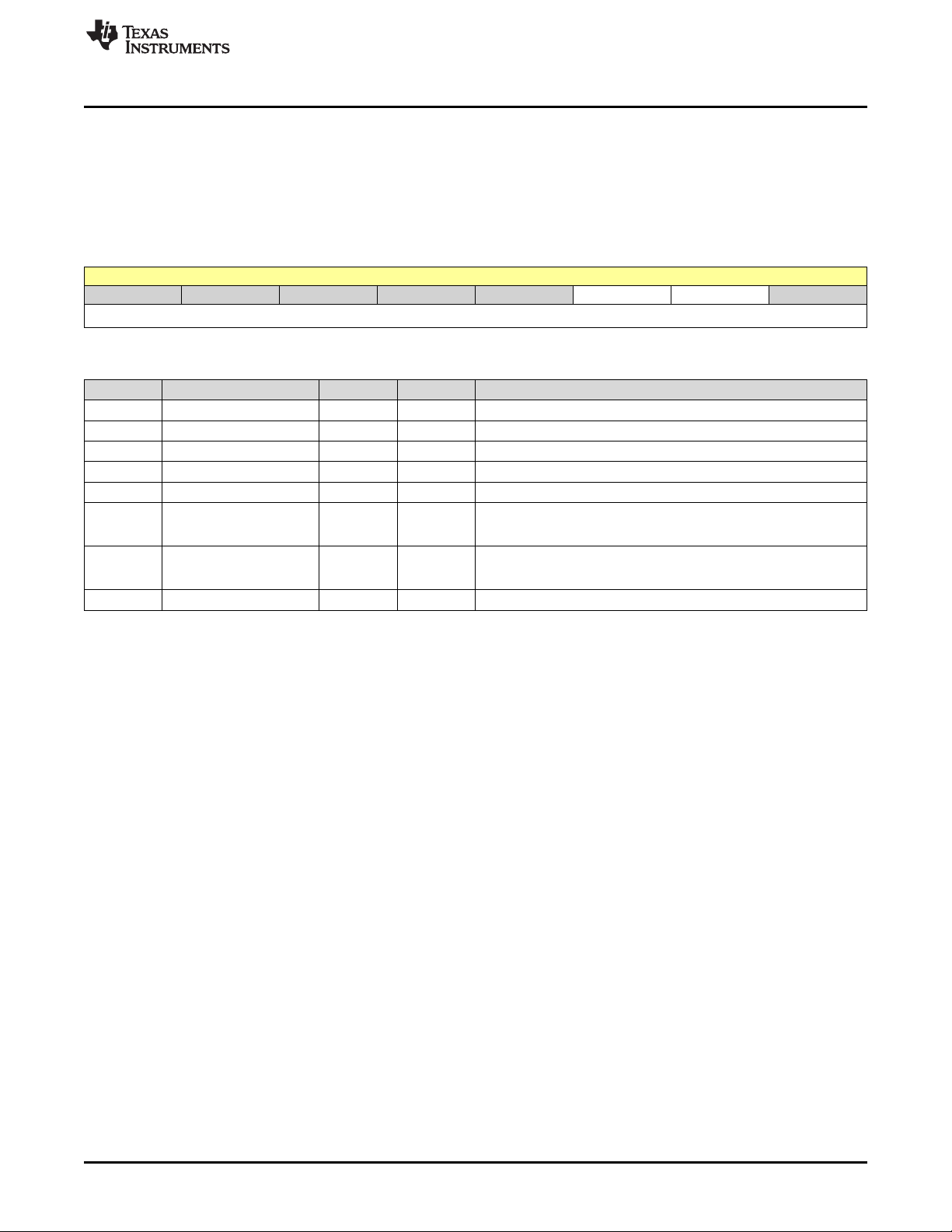

Complex bit access types are encoded to fit into small table cells. Table 2-2 shows the codes that are

used for access types in this document.

Table 2-2. FUNC_PAD_CONTROL Access Type Codes

Access Type Code Description

Read Type

R R Read

RC R

Write Type

W W Write

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

C

Copyright © 2015–2017, Texas Instruments Incorporated

Read

to Clear

Register Physical Address

3

Page 4

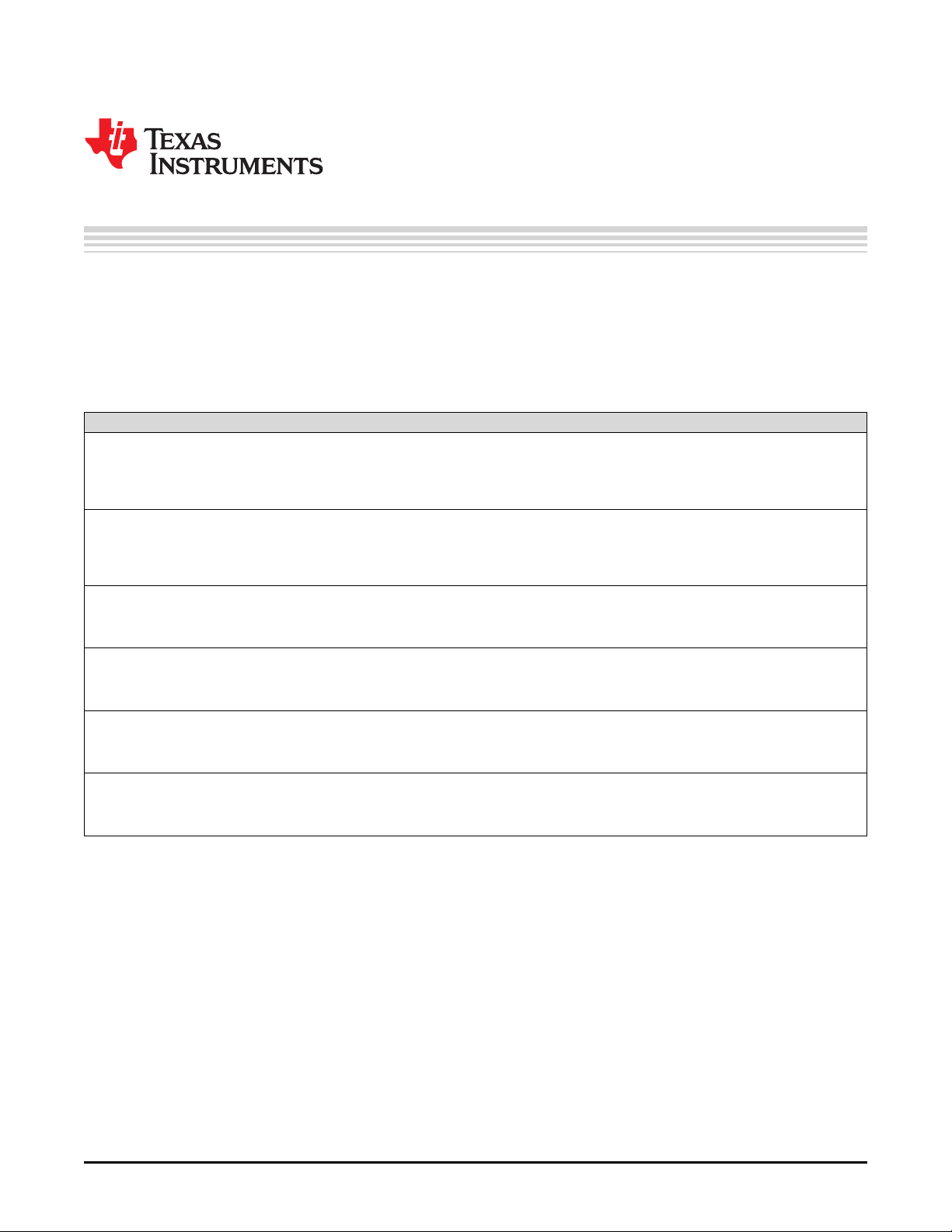

Chapter 3

SLVUAH1C–June 2015–Revised April 2017

Register Descriptions

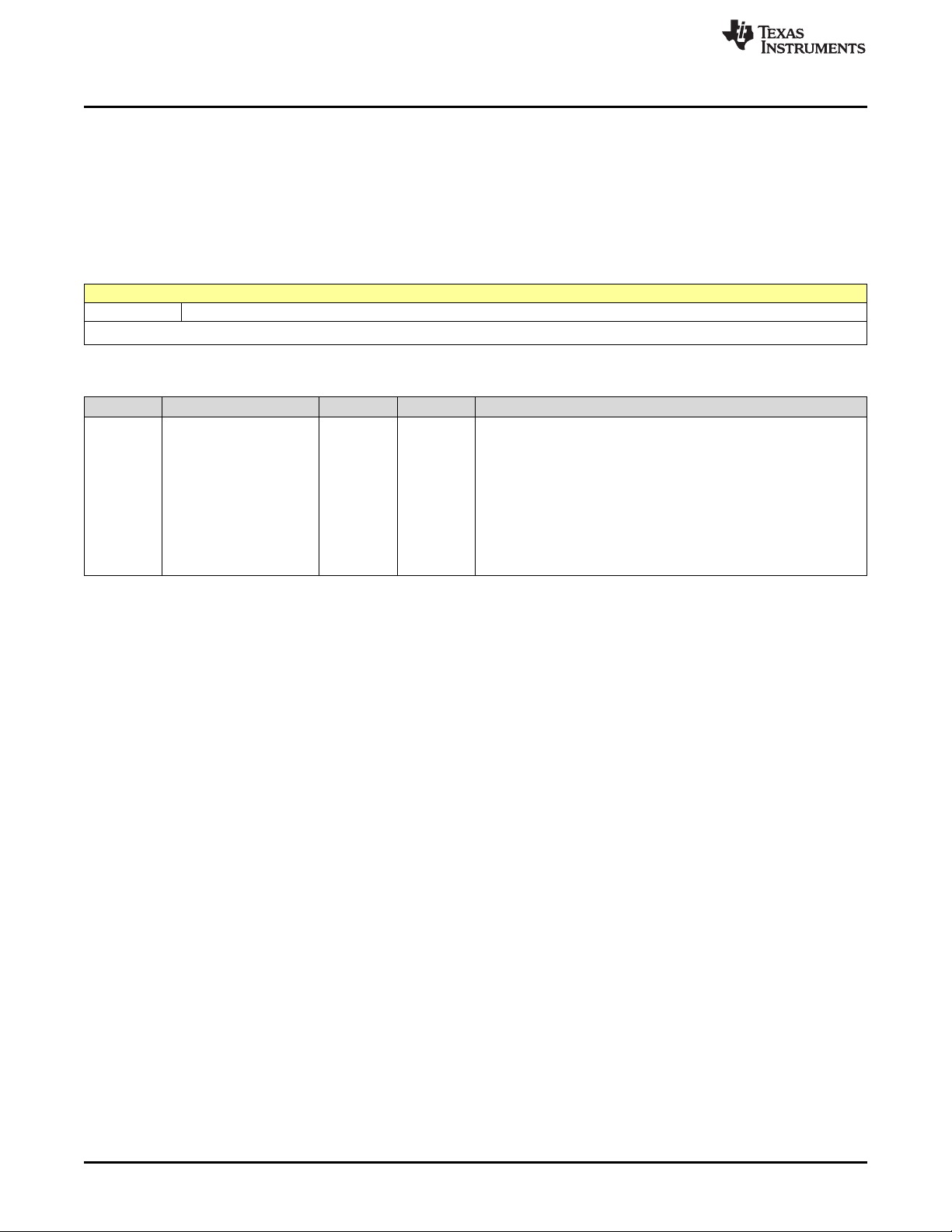

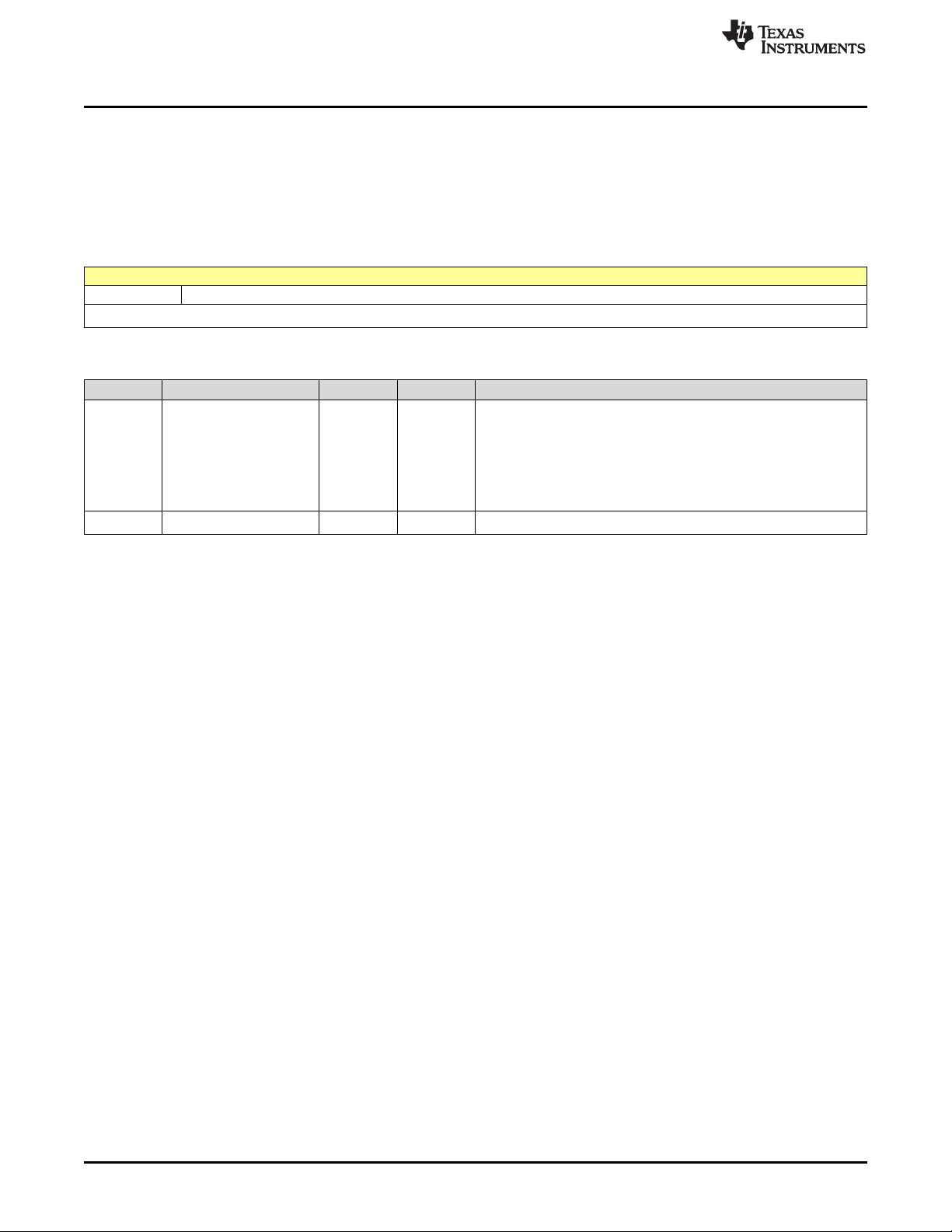

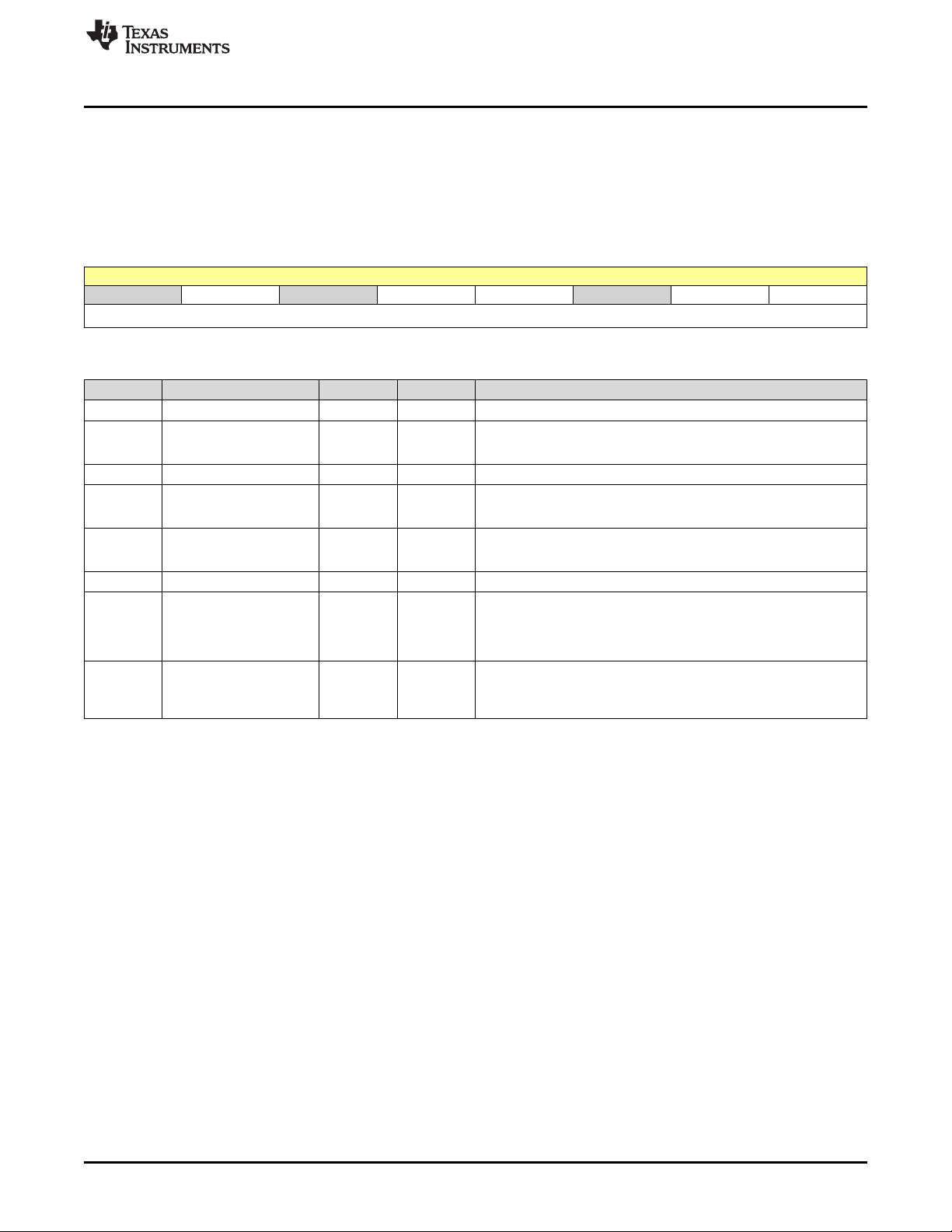

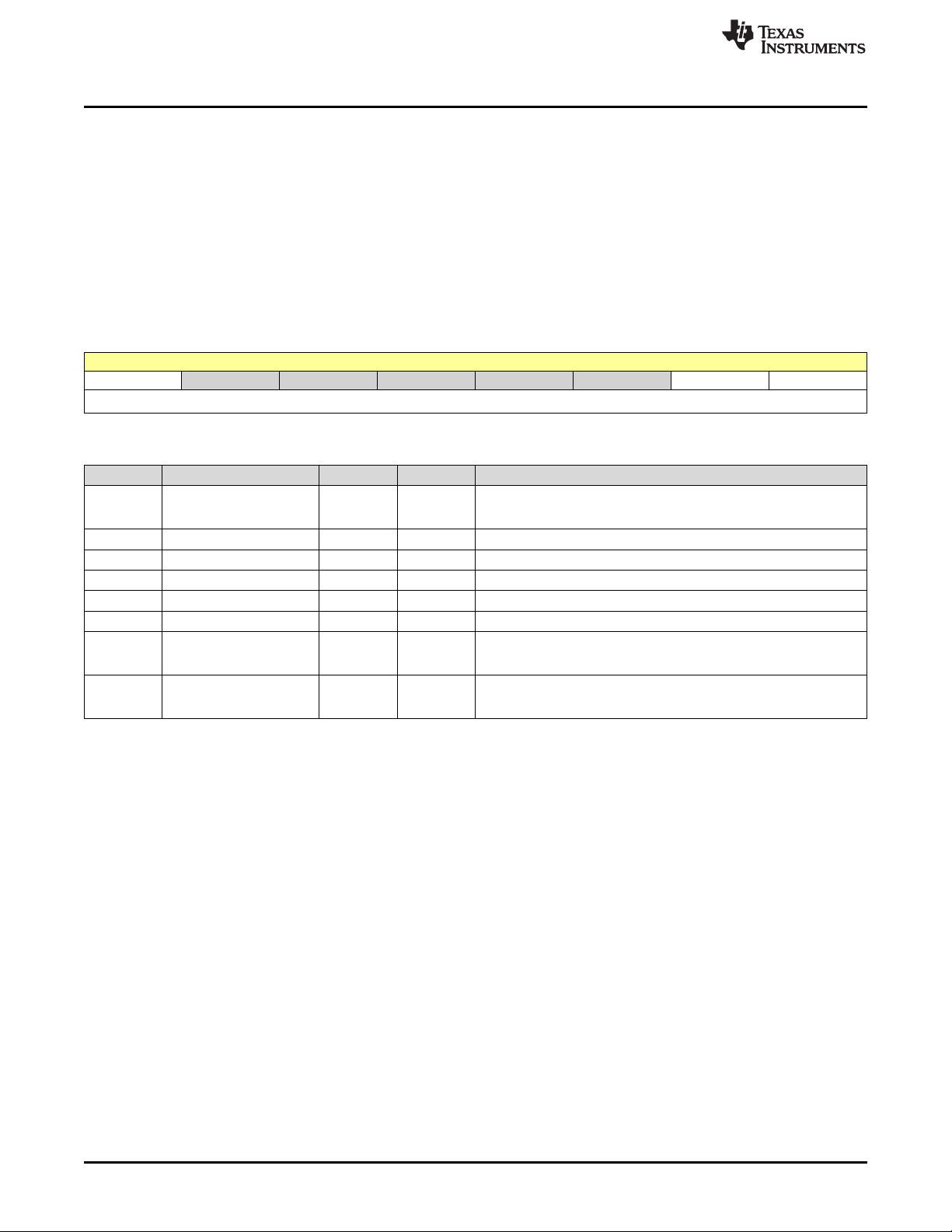

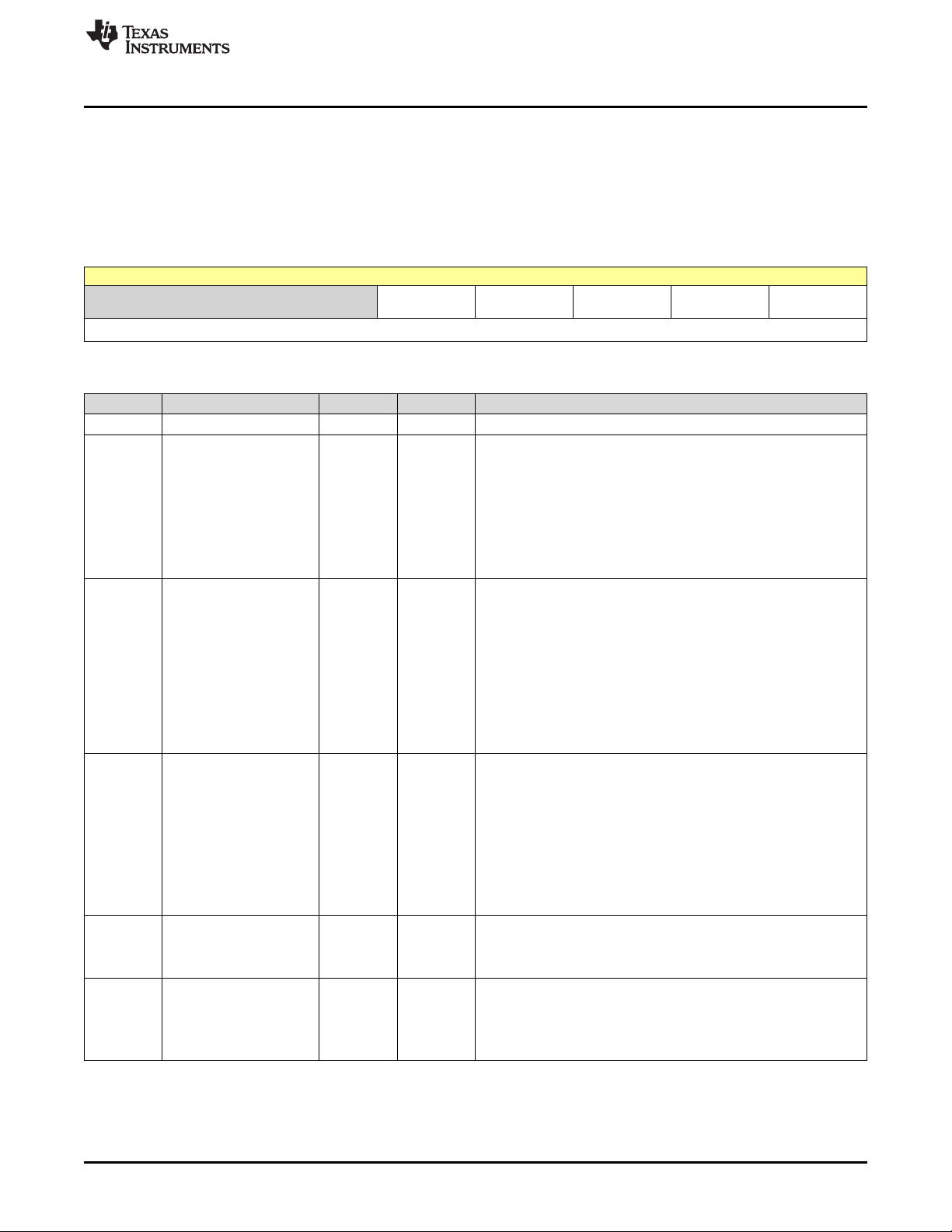

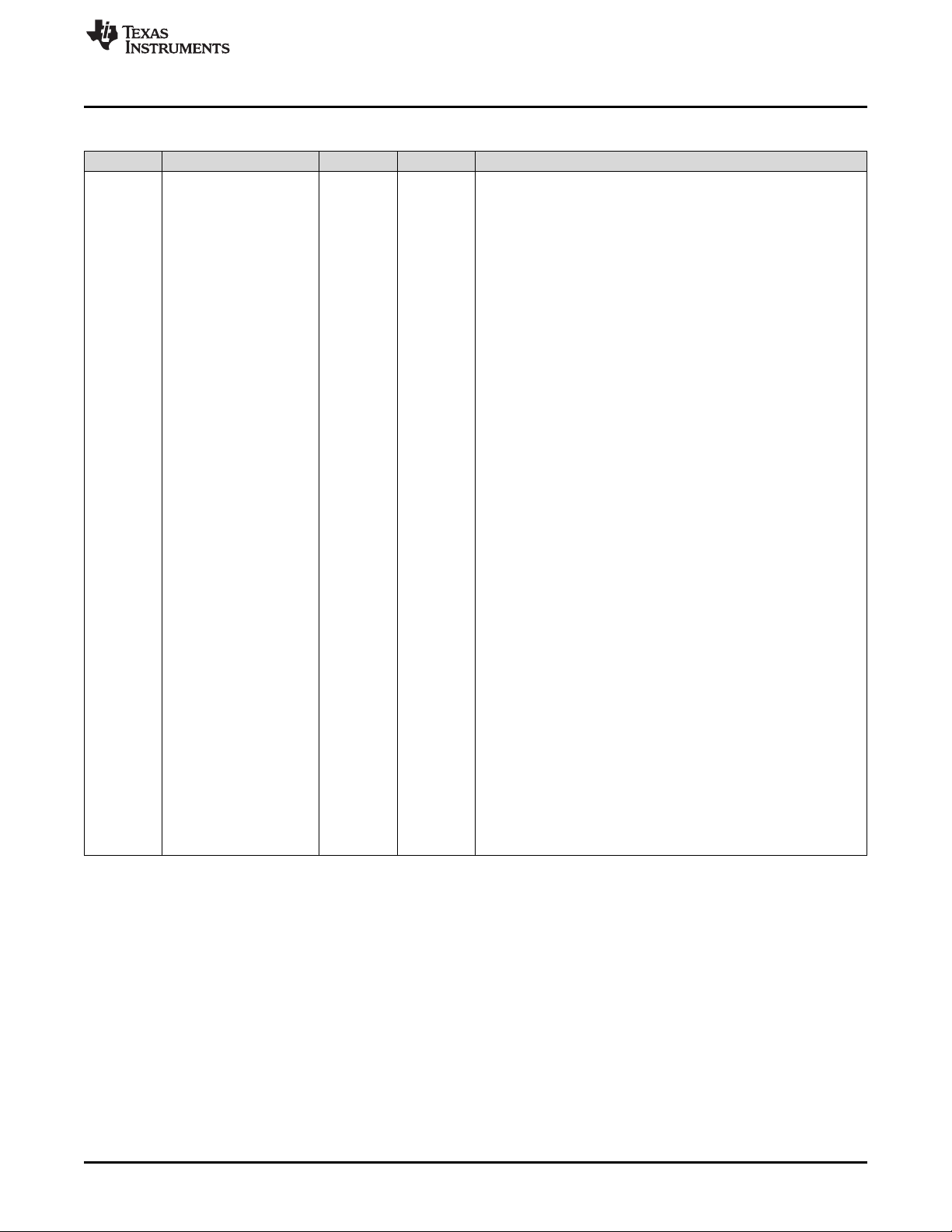

3.1 FUNC_SMPS_DVS Registers

Table 3-1 lists the memory-mapped registers for the FUNC_SMPS_DVS. All register offset addresses not

listed in Table 3-1 should be considered as reserved locations and the register contents should not be

modified.

Table 3-1. FUNC_SMPS_DVS Registers

Address Acronym Register Name Section

22h SMPS1_FORCE SMPS1 (or SMPS12 in case of dual-phase) DVS

register.

Voltage to apply to the resource when it is a DVS force

command (OTP_Config).

RESET register domain: SWORST

23h SMPS1_VOLTAGE SMPS1 (or SMPS12 in case of dual-phase) DVS

register.

Voltage to apply to the resource when it is not a DVS

force command (OTP_Config).r.

RESET register domain: SWORST

26h SMPS2_FORCE SMPS2 DVS register.

Voltage to apply to the resource when it is a DVS force

command (OTP_Config).

RESET register domain: SWORST

27h SMPS2_VOLTAGE SMPS2 DVS register.

Voltage to apply to the resource when it is not a DVS

force command (OTP_Config).

RESET register domain: SWORST

2Eh SMPS3_FORCE SMPS3 DVS register.

Voltage to apply to the resource when it is a DVS force

command (OTP_Config).

RESET register domain: SWORST

2Fh SMPS3_VOLTAGE SMPS3 DVS register.

Voltage to apply to the resource when it is not a DVS

force command (OTP_Config).

RESET register domain: SWORST

Section 3.1.1

Section 3.1.2

Section 3.1.3

Section 3.1.4

Section 3.1.5

Section 3.1.6

4

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 5

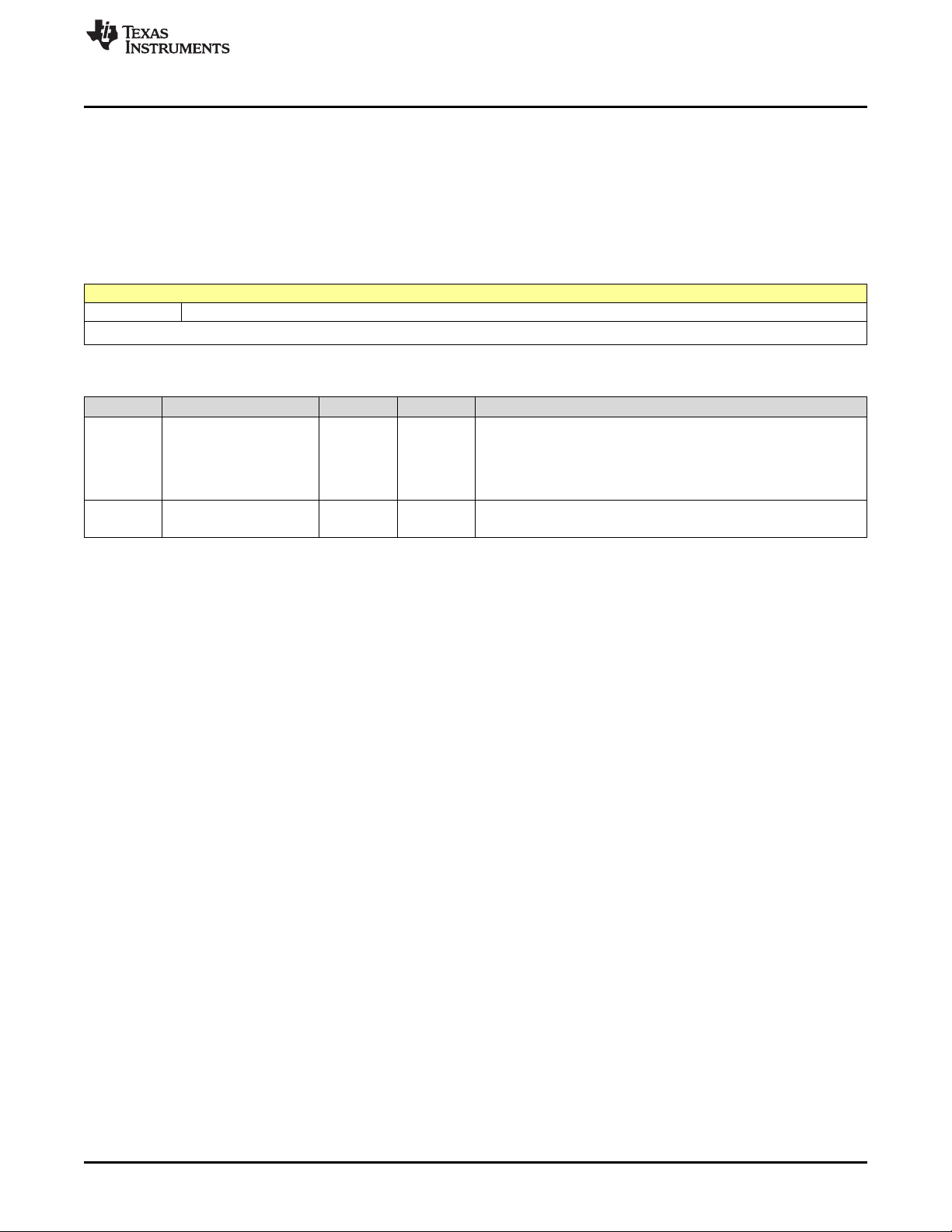

www.ti.com

FUNC_SMPS_DVS Registers

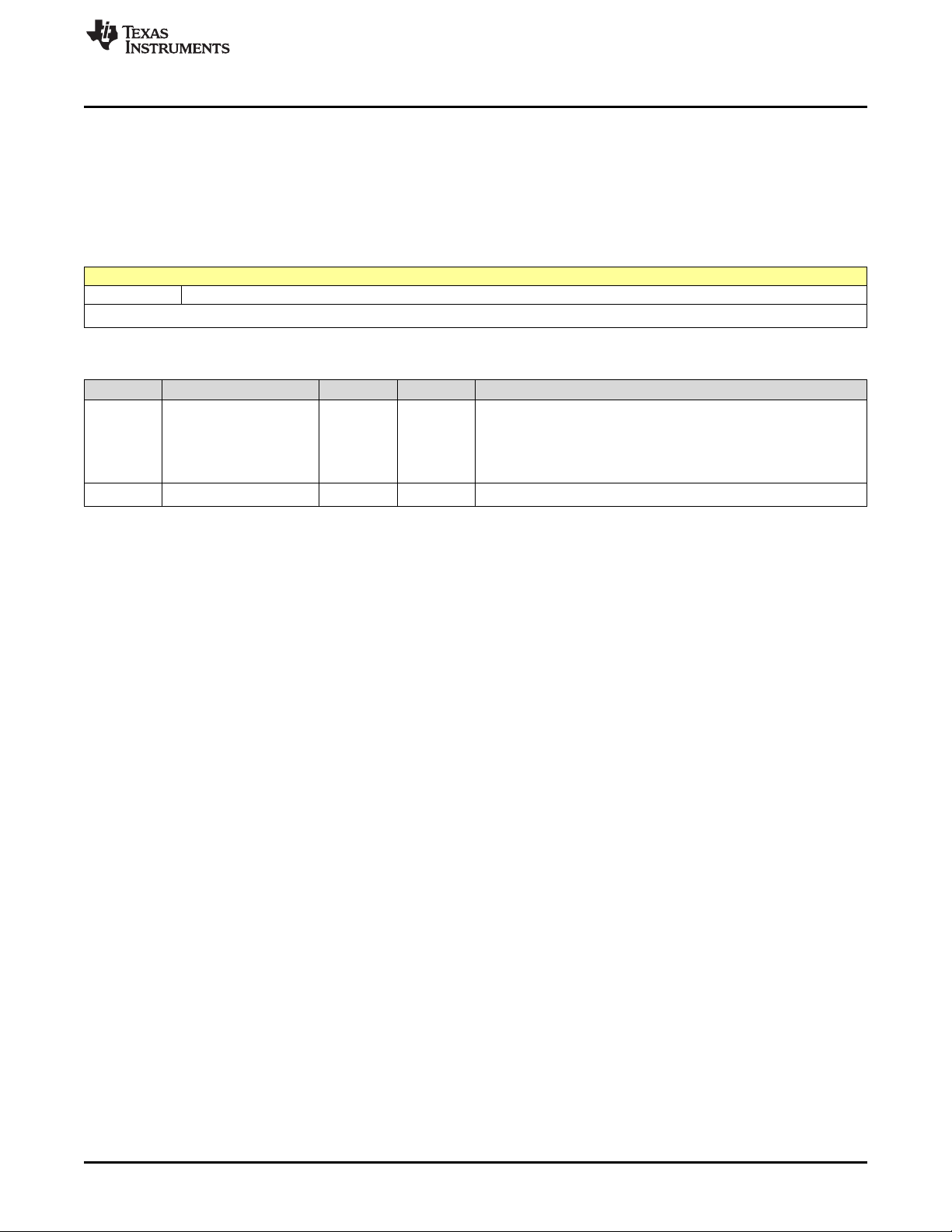

3.1.1 SMPS1_FORCE Register (Address = 22h) [reset = X]

SMPS1_FORCE is shown in Figure 3-1 and described in Table 3-2.

Return to Summary Table.

SMPS1 (or SMPS12 in case of dual-phase) DVS register. Voltage to apply to the resource when it is a

DVS force command (OTP_Config).

RESET register domain: SWORST

Figure 3-1. SMPS1_FORCE Register

7 6 5 4 3 2 1 0

CMD VSEL

R/W-1h R/W-X

Table 3-2. SMPS1_FORCE Register Field Descriptions

Bit Field Type Reset Description

7 CMD R/W 1h

6-0 VSEL R/W X

DVS command register selection:

When 0: SMPS1_FORCE.VSEL voltage is applied

When 1: SMPS1_VOLTAGE.VSEL voltage is applied (default)

CMD is effective if SMPS1_CTRL.ROOF_FLOOR_EN='0'

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register

(page1).

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

5

Page 6

FUNC_SMPS_DVS Registers

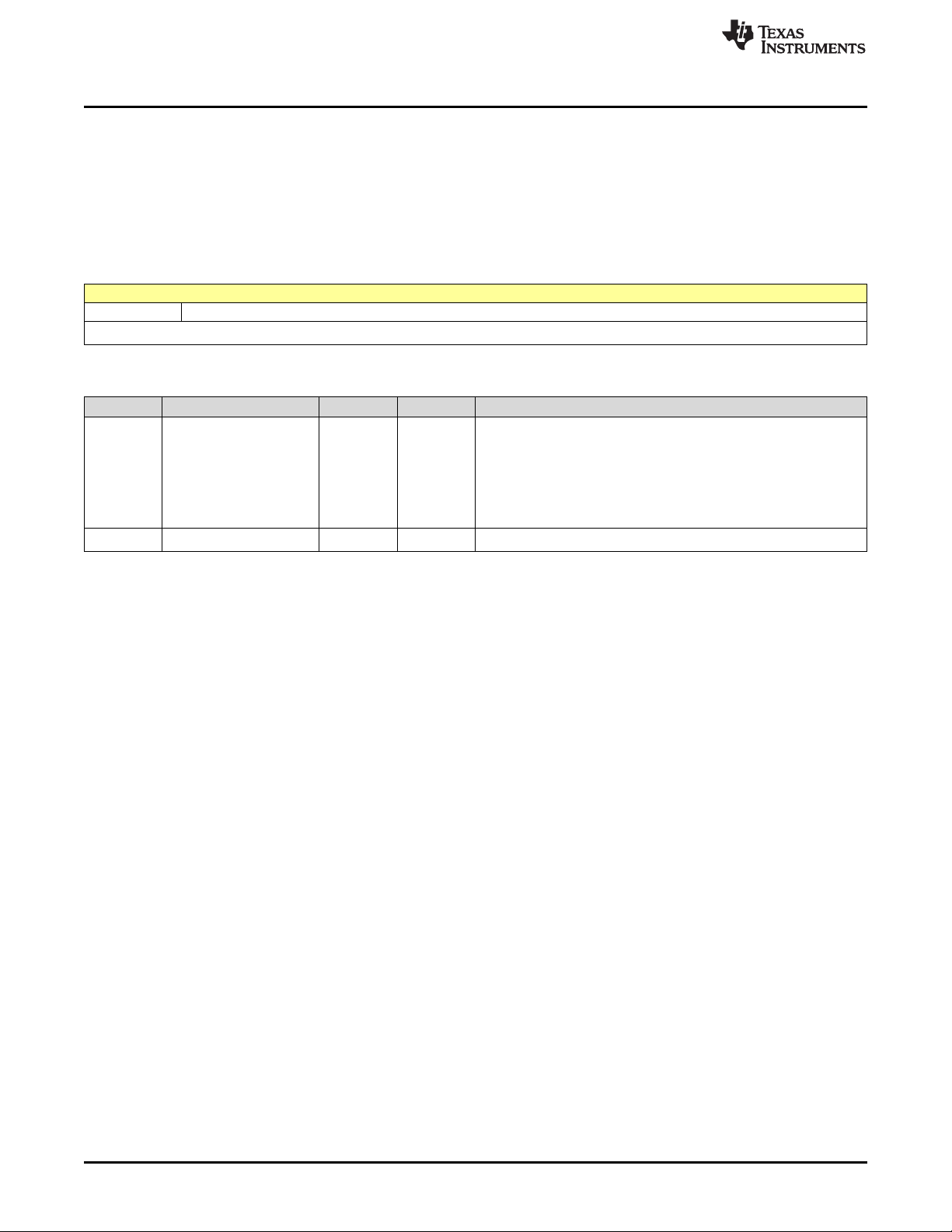

3.1.2 SMPS1_VOLTAGE Register (Address = 23h) [reset = X]

SMPS1_VOLTAGE is shown in Figure 3-2 and described in Table 3-3.

Return to Summary Table.

SMPS1 (or SMPS12 in case of dual-phase) DVS register. Voltage to apply to the resource when it is not a

DVS force command (OTP_Config).r.

RESET register domain: SWORST

Figure 3-2. SMPS1_VOLTAGE Register

7 6 5 4 3 2 1 0

RANGE VSEL

R/W-X R/W-X

Table 3-3. SMPS1_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7 RANGE R/W X

6-0 VSEL R/W X

Range of the VSEL voltage. This bit is applied to

SMPS1_VOLTAGE.VSEL and SPMS1_FORCE.VSEL

0: 0.5V to 1.65V

1: 1.0 to 3.3V

Note:RANGE bit is RO when SMPS1 is ON, RANGE bit is RW when

SMPS1 is OFF

Note: For Dual-phase mode, RANGE=1 (1V to 3.3V) is not

supported.

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register

(page1).

www.ti.com

6

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 7

www.ti.com

FUNC_SMPS_DVS Registers

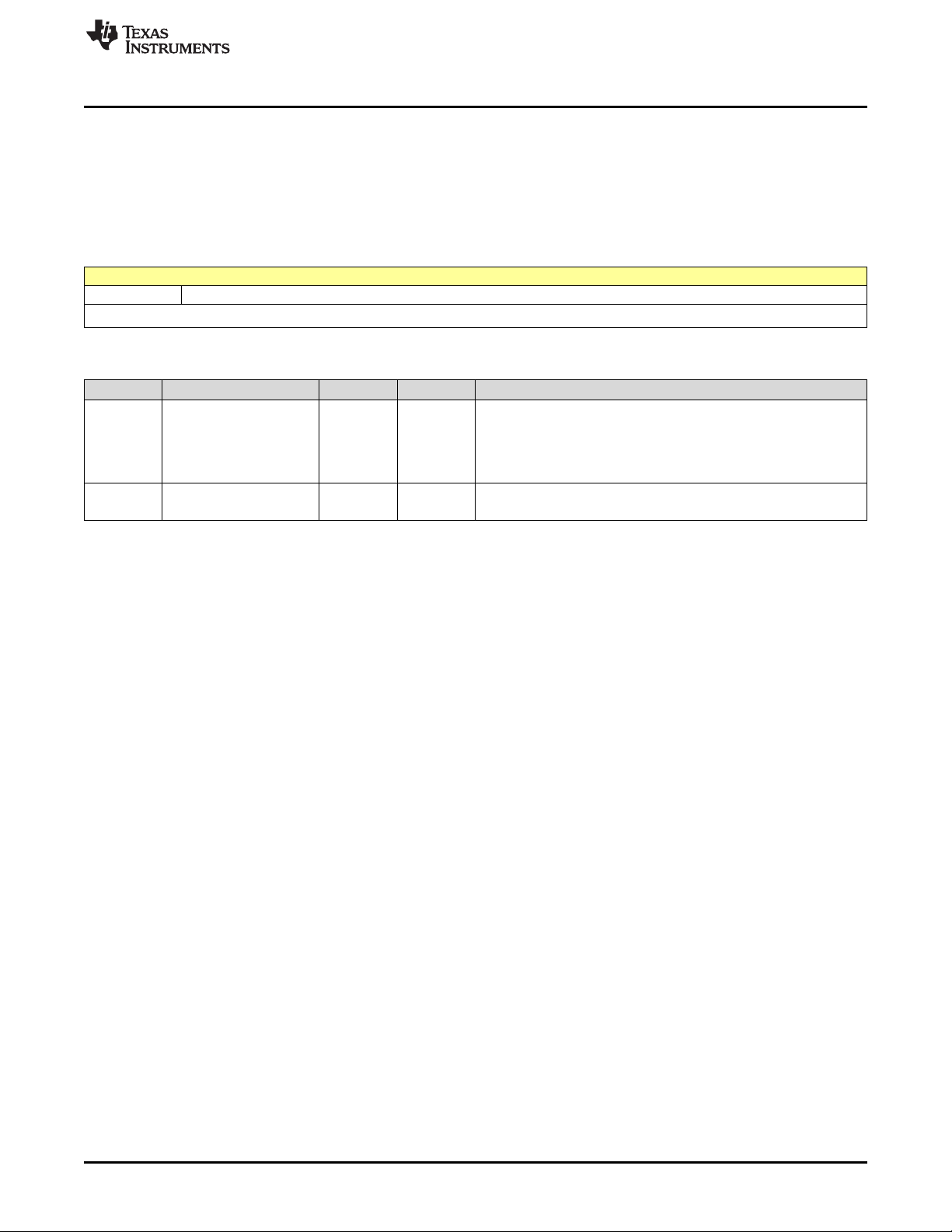

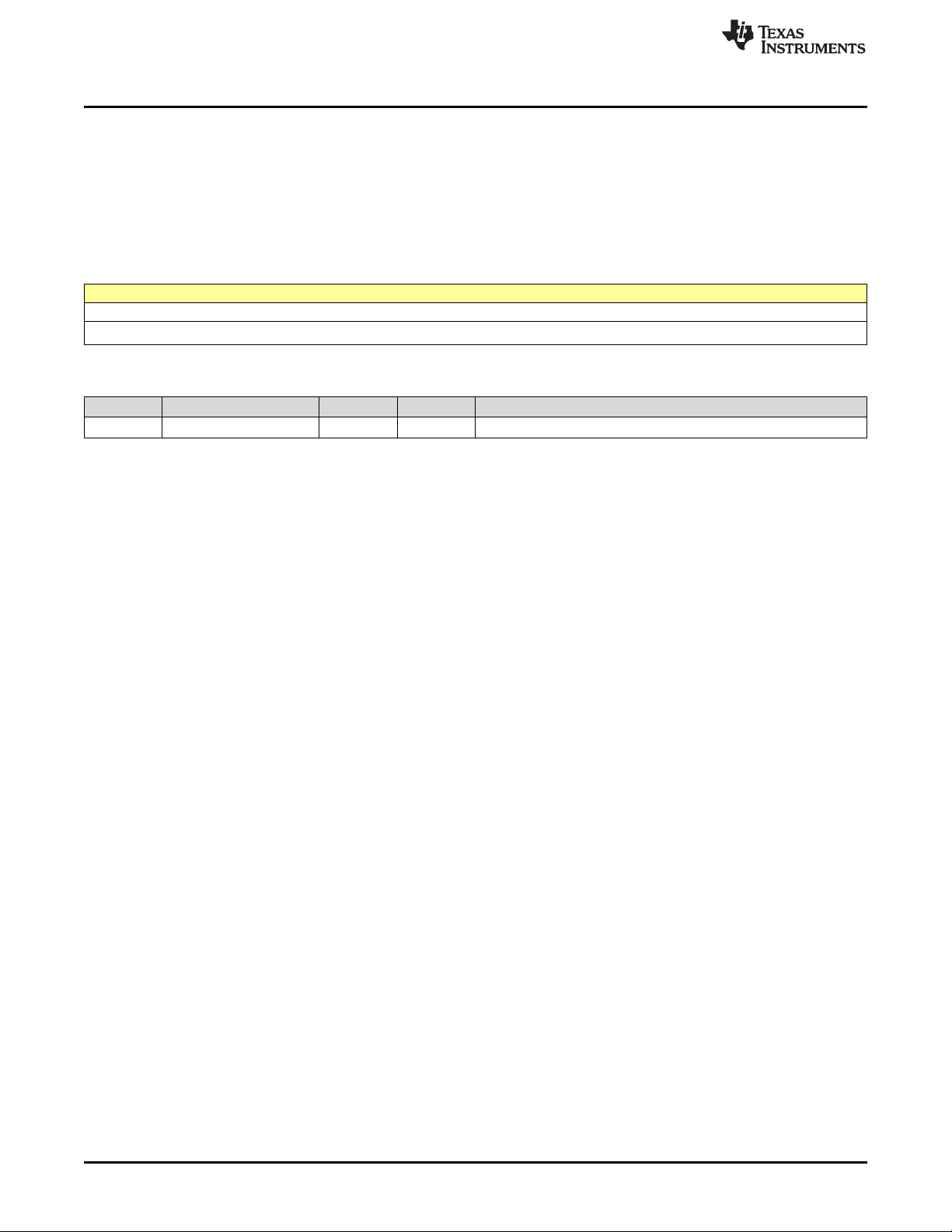

3.1.3 SMPS2_FORCE Register (Address = 26h) [reset = X]

SMPS2_FORCE is shown in Figure 3-3 and described in Table 3-4.

Return to Summary Table.

SMPS2 DVS register. Voltage to apply to the resource when it is a DVS force command (OTP_Config).

RESET register domain: SWORST

Figure 3-3. SMPS2_FORCE Register

7 6 5 4 3 2 1 0

CMD VSEL

R/W-1h R/W-X

Table 3-4. SMPS2_FORCE Register Field Descriptions

Bit Field Type Reset Description

7 CMD R/W 1h

6-0 VSEL R/W X

DVS command register selection:

When 0: SMPS2_FORCE.VSEL voltage is applied

When 1: SMPS2_VOLTAGE.VSEL voltage is applied (default)

CMD is effective if SMPS2_CTRL.ROOF_FLOOR_EN='0'

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register.

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

7

Page 8

FUNC_SMPS_DVS Registers

3.1.4 SMPS2_VOLTAGE Register (Address = 27h) [reset = X]

SMPS2_VOLTAGE is shown in Figure 3-4 and described in Table 3-5.

Return to Summary Table.

SMPS2 DVS register. Voltage to apply to the resource when it is not a DVS force command

(OTP_Config).

RESET register domain: SWORST

Figure 3-4. SMPS2_VOLTAGE Register

7 6 5 4 3 2 1 0

RANGE VSEL

R/W-X R/W-X

Table 3-5. SMPS2_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7 RANGE R/W X

6-0 VSEL R/W X

Range of the VSEL voltage. This bit is applied to

SMPS2_VOLTAGE.VSEL

0: 0.5V to 1.65V

1: 1.0 to 3.3V

Note:RANGE bit is RO when SMPS2 is ON, RANGE bit is RW when

SMPS2 is OFF

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register.

www.ti.com

8

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 9

www.ti.com

FUNC_SMPS_DVS Registers

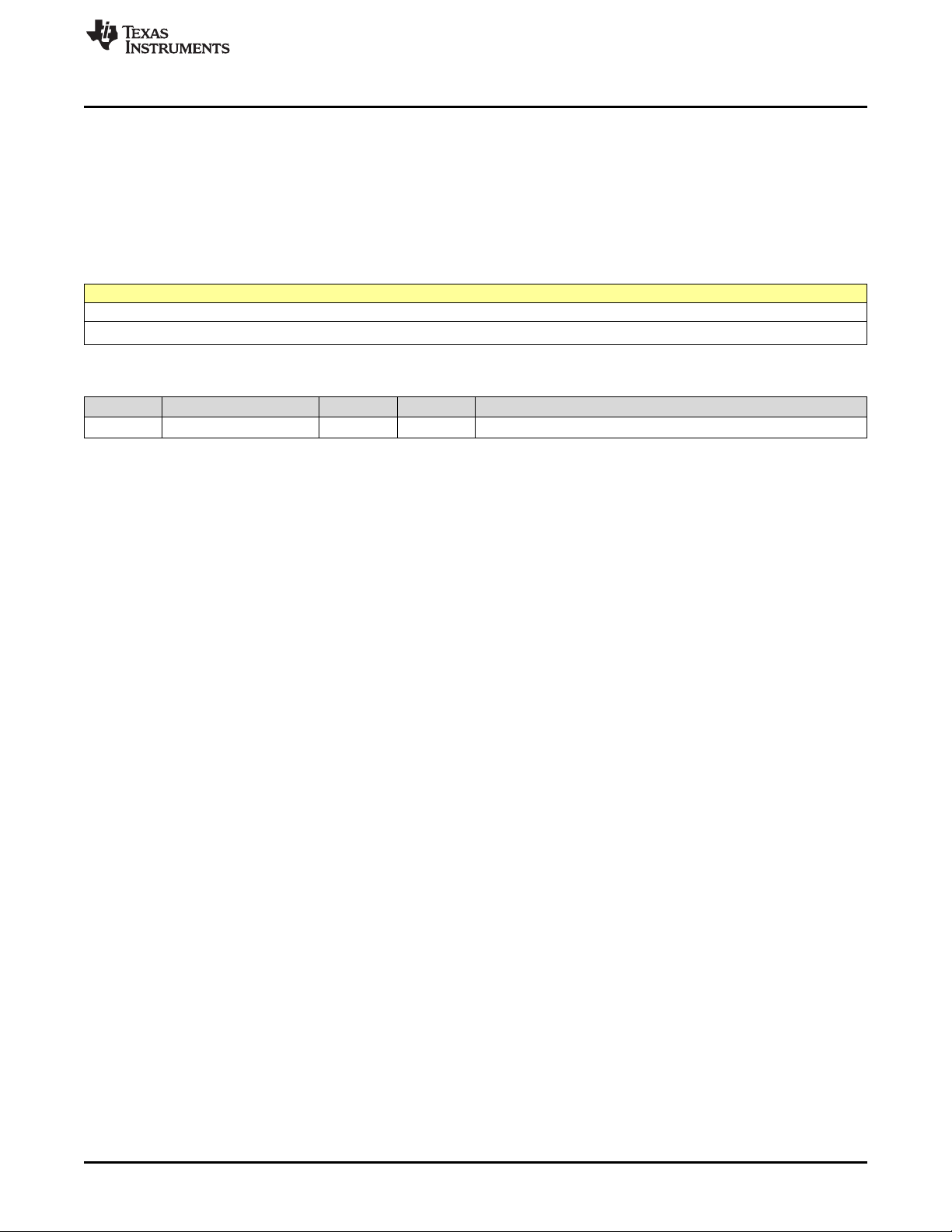

3.1.5 SMPS3_FORCE Register (Address = 2Eh) [reset = X]

SMPS3_FORCE is shown in Figure 3-5 and described in Table 3-6.

Return to Summary Table.

SMPS3 DVS register. Voltage to apply to the resource when it is a DVS force command (OTP_Config).

RESET register domain: SWORST

Figure 3-5. SMPS3_FORCE Register

7 6 5 4 3 2 1 0

CMD VSEL

R/W-1h R/W-X

Table 3-6. SMPS3_FORCE Register Field Descriptions

Bit Field Type Reset Description

7 CMD R/W 1h

6-0 VSEL R/W X

DVS command register selection:

When 0: SMPS3_FORCE.VSEL voltage is applied

When 1: SMPS3_VOLTAGE.VSEL voltage is applied (default)

CMD is effective if SMPS3_CTRL.ROOF_FLOOR_EN='0'

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register

(page1).

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

9

Page 10

FUNC_SMPS_DVS Registers

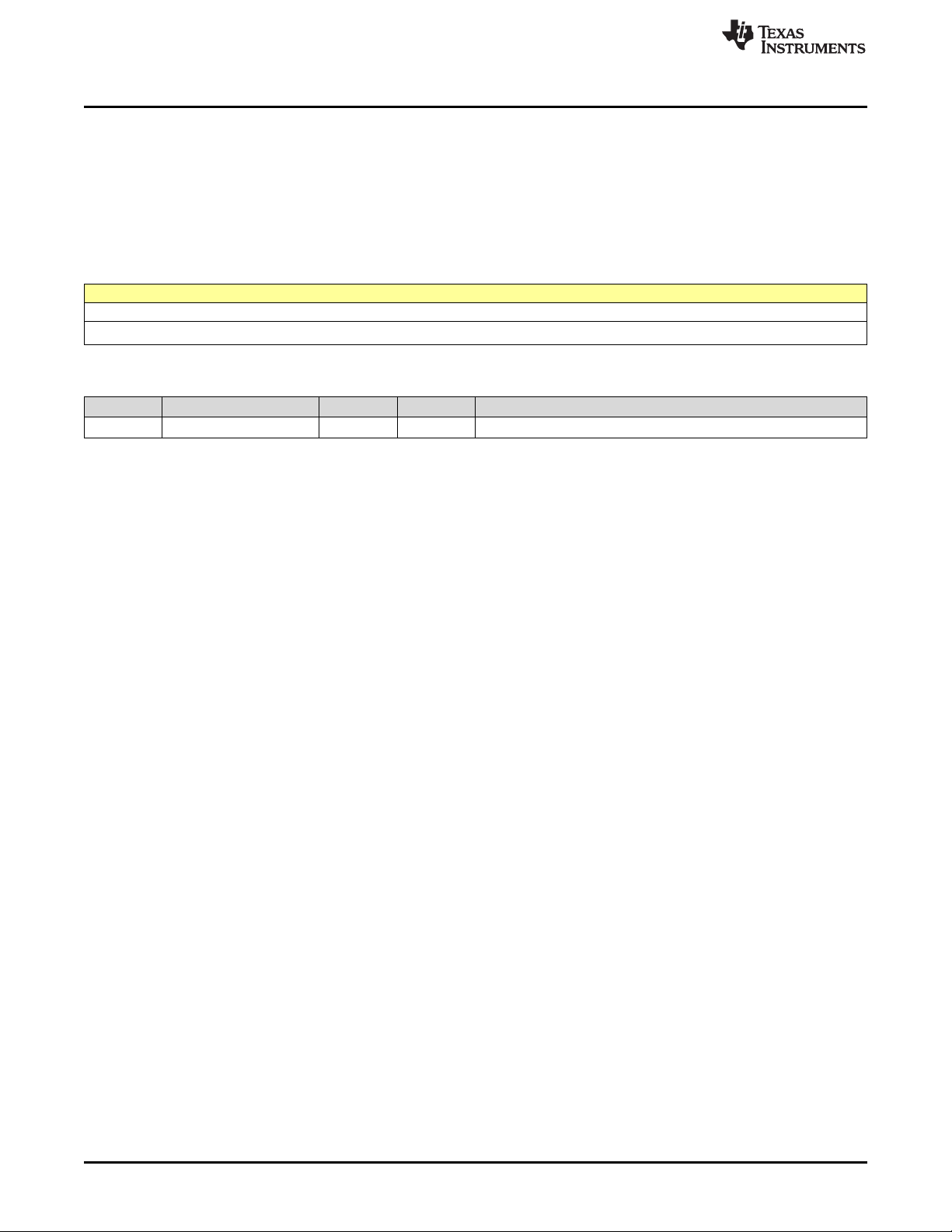

3.1.6 SMPS3_VOLTAGE Register (Address = 2Fh) [reset = X]

SMPS3_VOLTAGE is shown in Figure 3-6 and described in Table 3-7.

Return to Summary Table.

SMPS3 DVS register. Voltage to apply to the resource when it is not a DVS force command

(OTP_Config).

RESET register domain: SWORST

Figure 3-6. SMPS3_VOLTAGE Register

7 6 5 4 3 2 1 0

RANGE VSEL

R/W-X R/W-X

Table 3-7. SMPS3_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7 RANGE R/W X

6-0 VSEL R/W X

Range of the VSEL voltage. This bit is applied to

SMPS3_VOLTAGE.VSEL and SPMS3_FORCE.VSEL

0: 0.5V to 1.65V

1: 1.0 to 3.3V

Note:RANGE bit is RO when SMPS3 is ON, RANGE bit is RW when

SMPS3 is OFF

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register

(page1).

www.ti.com

10

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 11

www.ti.com

FUNC_BACKUP Registers

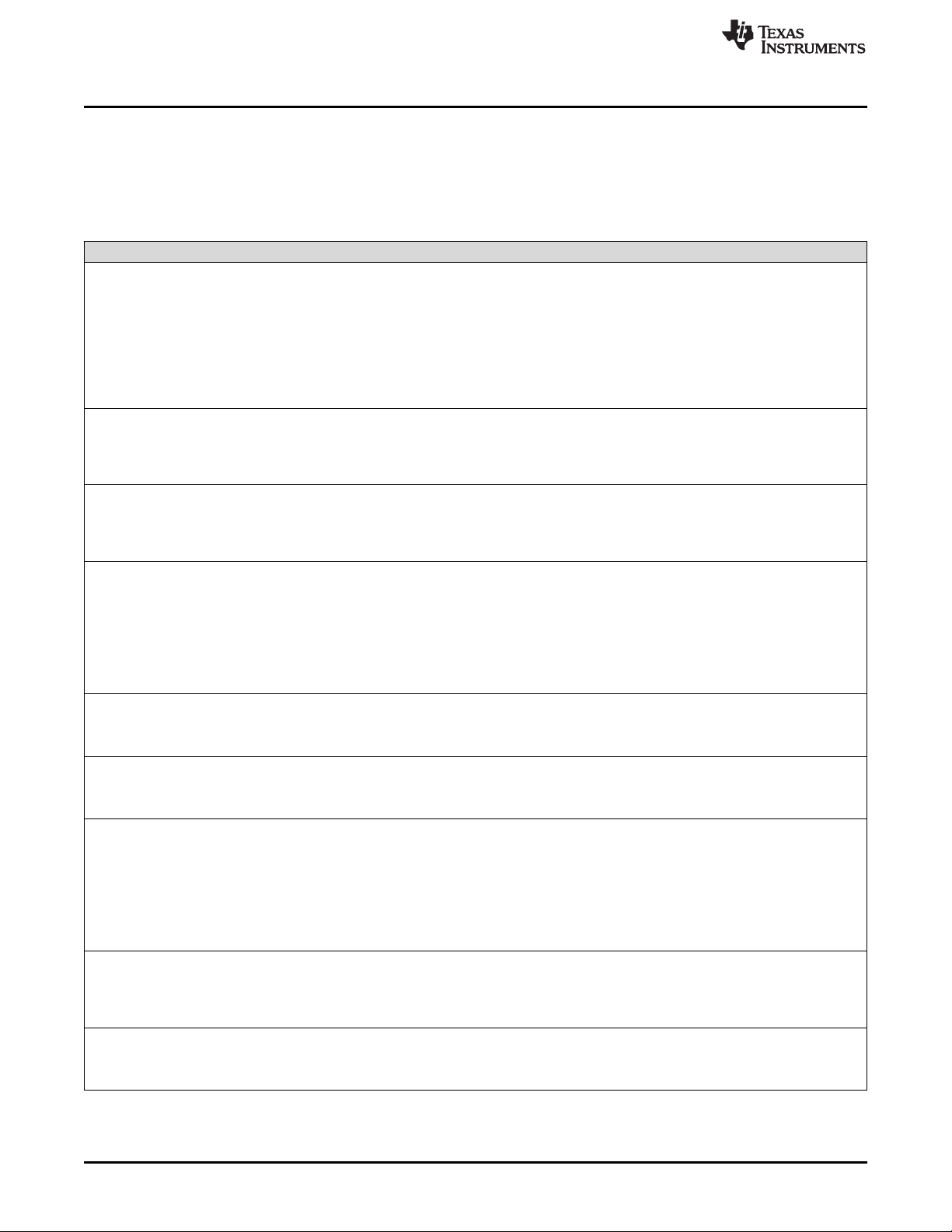

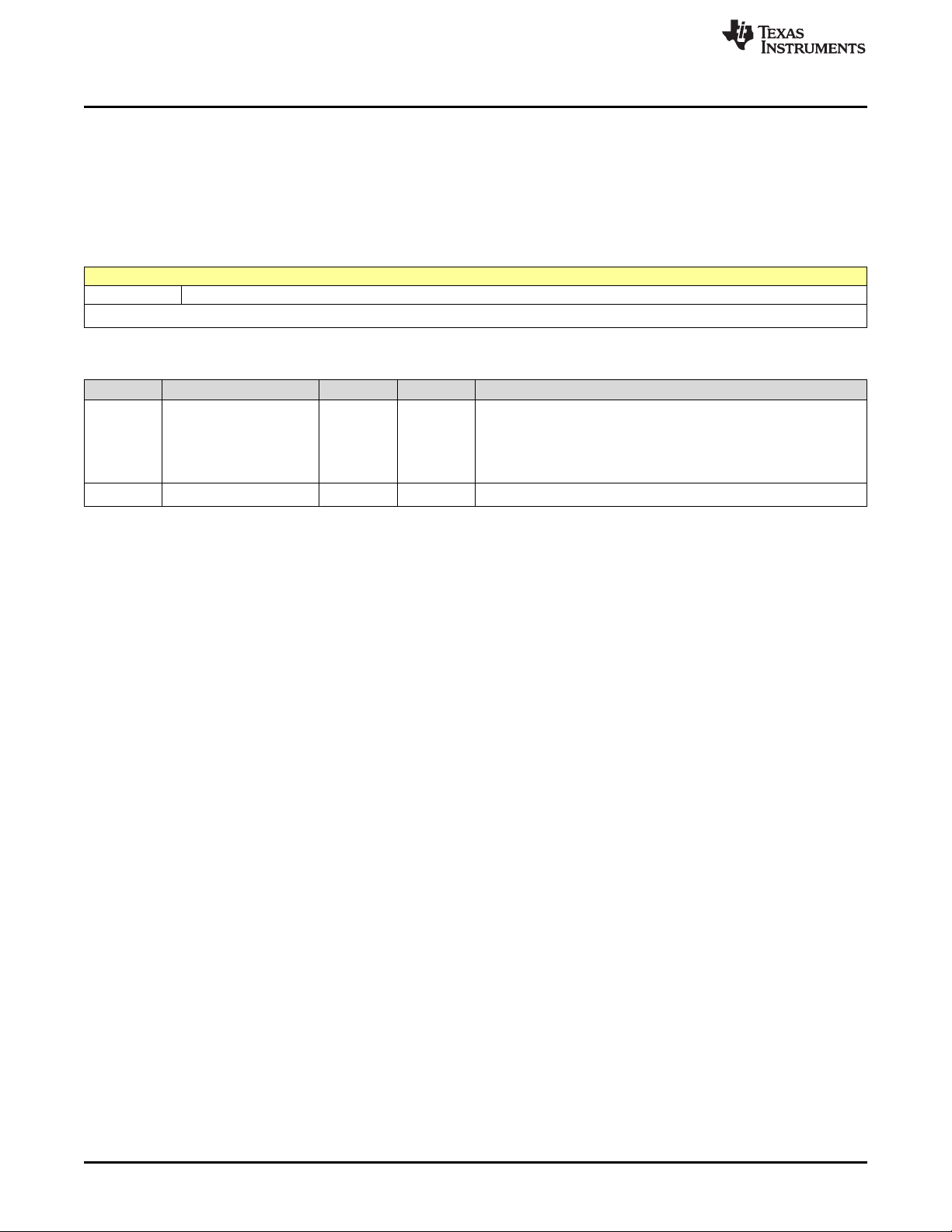

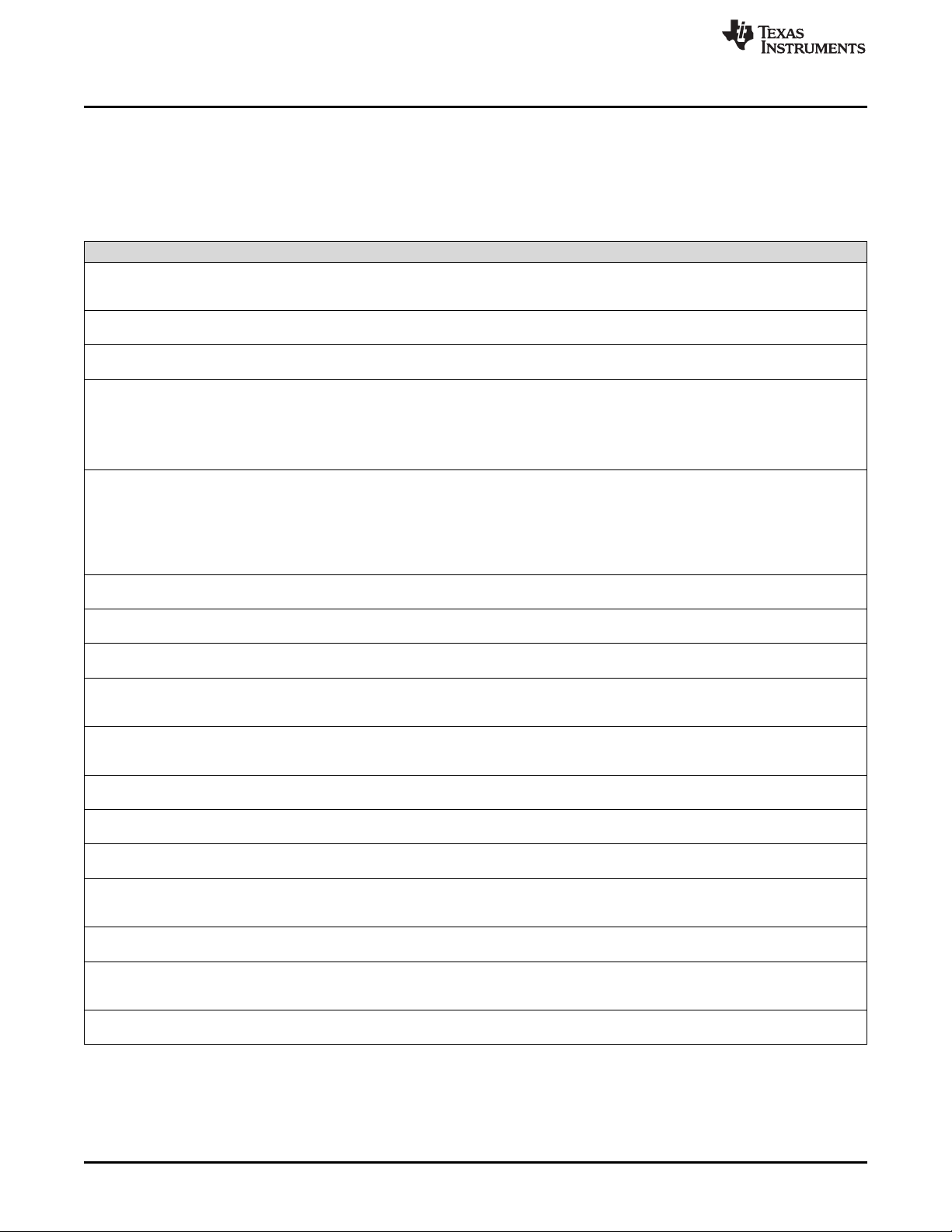

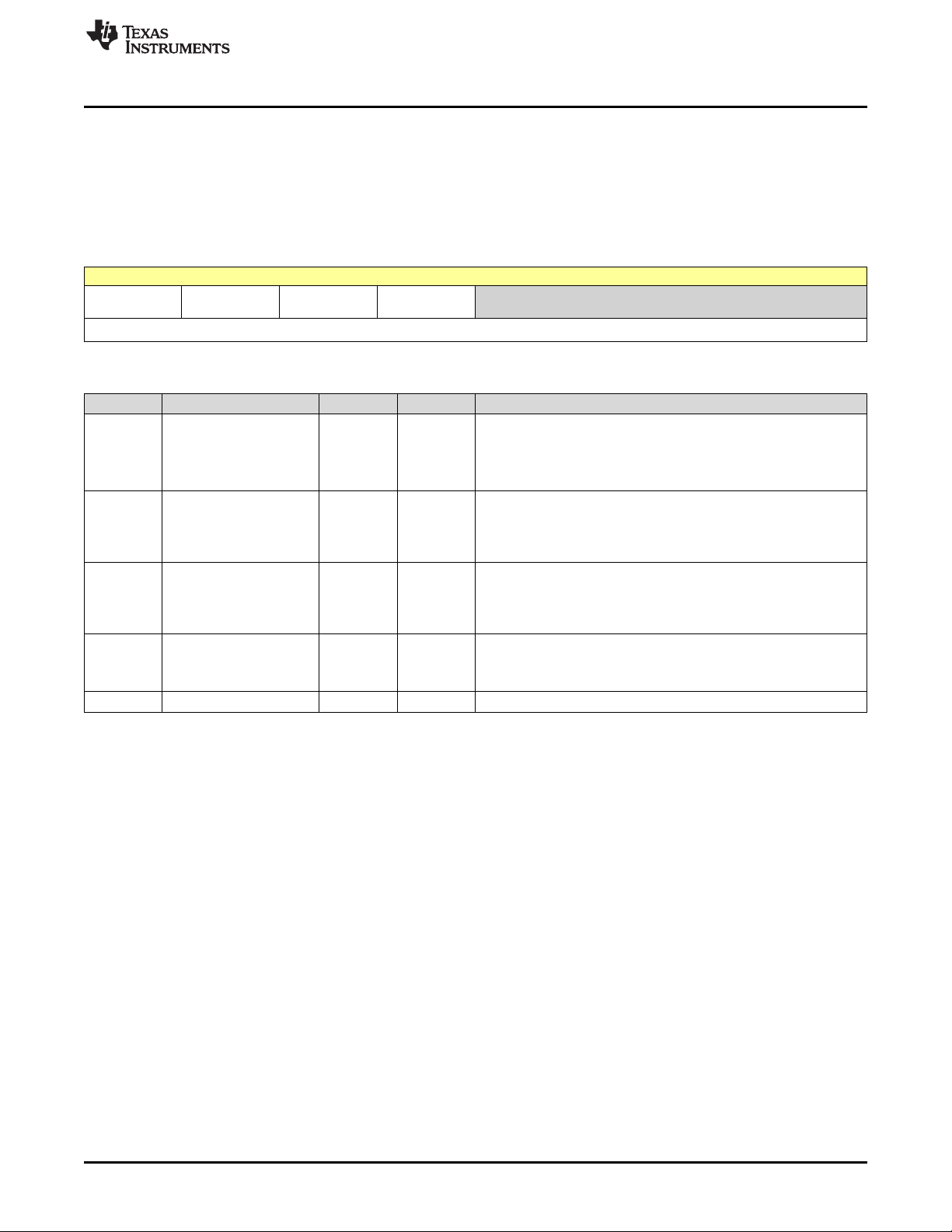

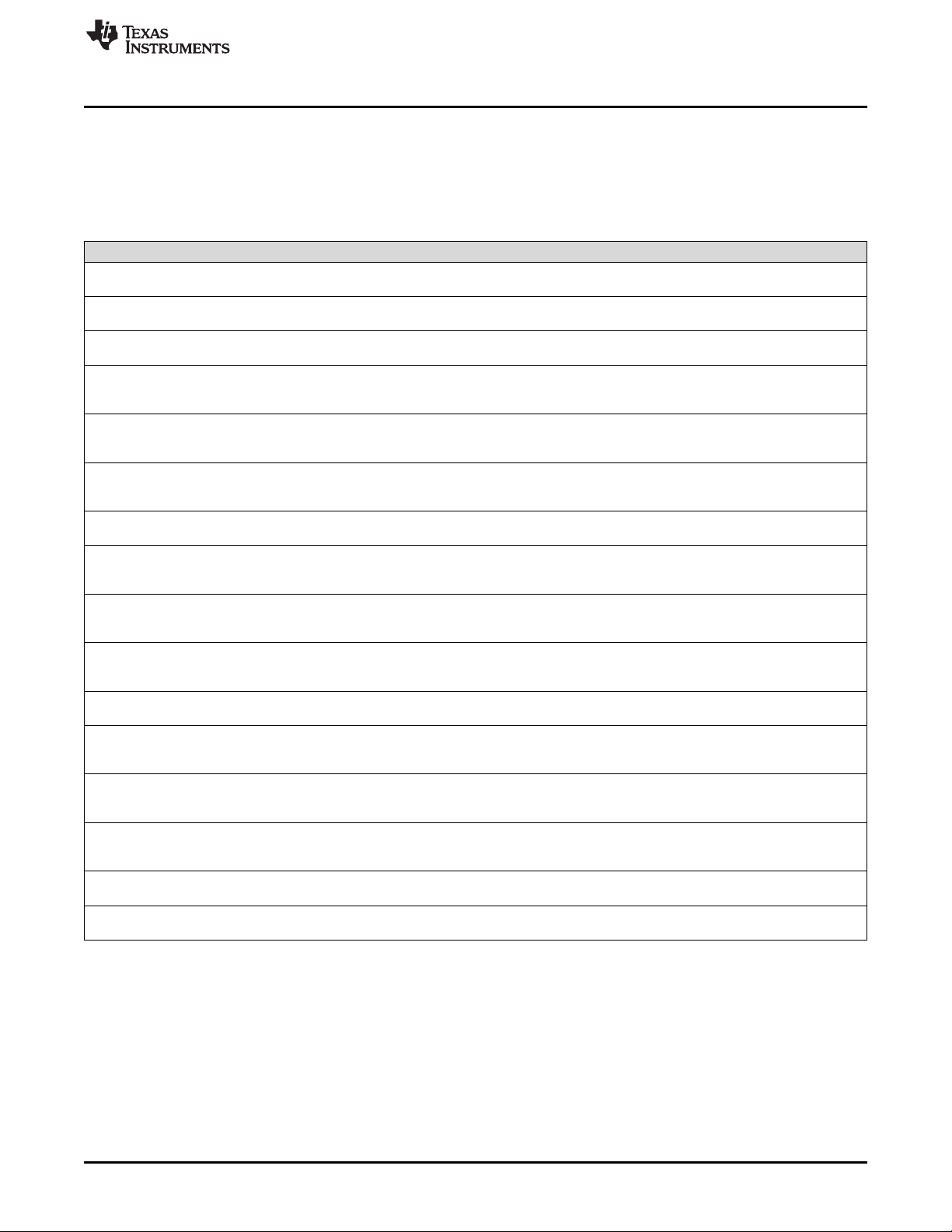

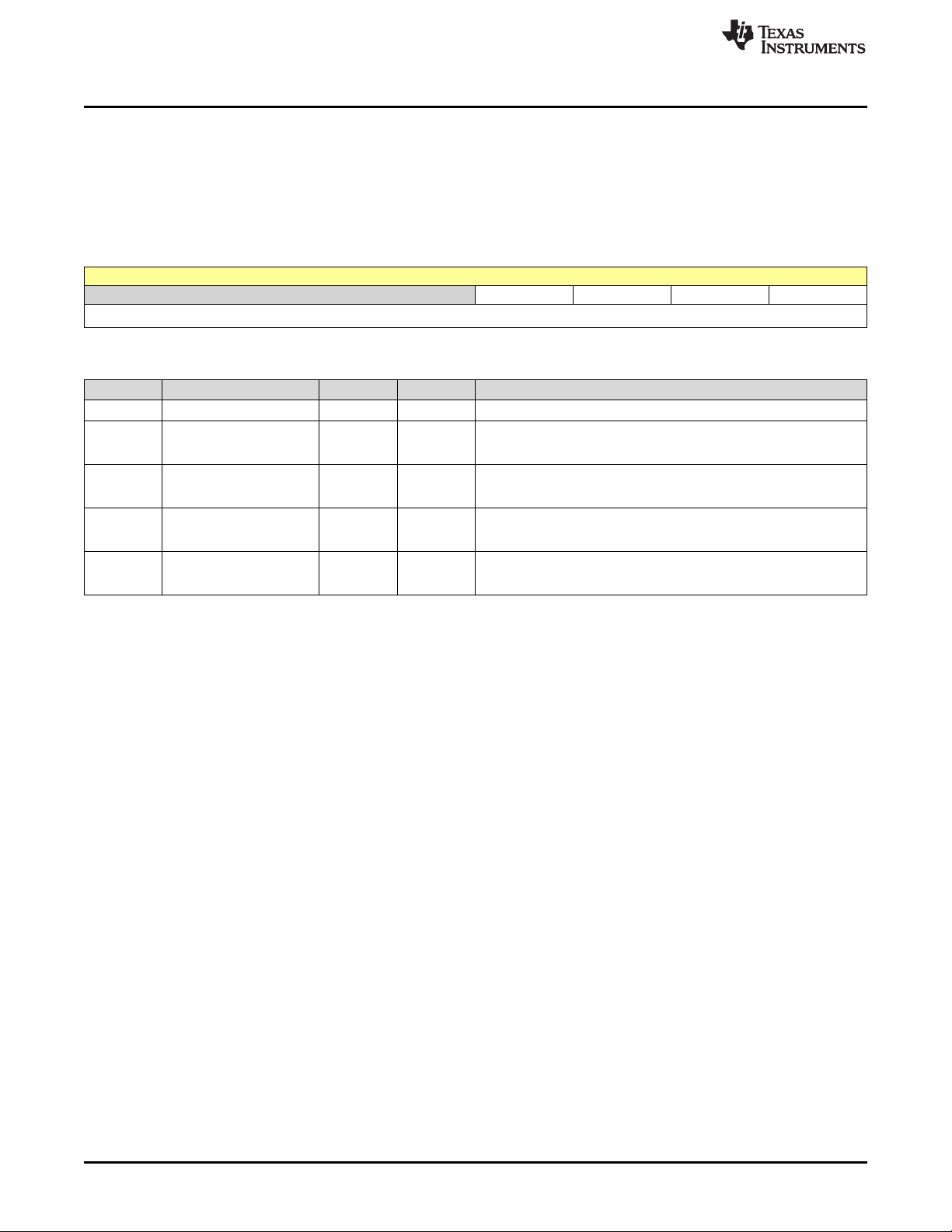

3.2 FUNC_BACKUP Registers

Table 3-8 lists the memory-mapped registers for the FUNC_BACKUP. All register offset addresses not

listed in Table 3-8 should be considered as reserved locations and the register contents should not be

modified.

Table 3-8. FUNC_BACKUP Registers

Address Acronym Register Name Section

118h BACKUP0 Backup register #0 which can be used for storage by the

application firmware when the external host is power

down.

These registers will retain their content as long as VRTC

is active.

RESET register domain: POR

119h BACKUP1 Backup register #1 which can be used for storage by the

application firmware when the external host is power

down.

These registers will retain their content as long as VRTC

is active.

RESET register domain: POR

11Ah BACKUP2 Backup register #2 which can be used for storage by the

application firmware when the external host is power

down.

These registers will retain their content as long as VRTC

is active.

RESET register domain: POR

11Bh BACKUP3 Backup register #3 which can be used for storage by the

application firmware when the external host is power

down.

These registers will retain their content as long as VRTC

is active.

RESET register domain: POR

11Ch BACKUP4 Backup register #4 which can be used for storage by the

application firmware when the external host is power

down.

These registers will retain their content as long as VRTC

is active.

RESET register domain: POR

11Dh BACKUP5 Backup register #5 which can be used for storage by the

application firmware when the external host is power

down.

These registers will retain their content as long as VRTC

is active.

RESET register domain: POR

11Eh BACKUP6 Backup register #6 which can be used for storage by the

application firmware when the external host is power

down.

These registers will retain their content as long as VRTC

is active.

RESET register domain: POR

11Fh BACKUP7 Backup register #7 which can be used for storage by the

application firmware when the external host is power

down.

These registers will retain their content as long as VRTC

is active.

RESET register domain: POR

Section 3.2.1

Section 3.2.2

Section 3.2.3

Section 3.2.4

Section 3.2.5

Section 3.2.6

Section 3.2.7

Section 3.2.8

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

11

Page 12

FUNC_BACKUP Registers

3.2.1 BACKUP0 Register (Address = 118h) [reset = 0h]

BACKUP0 is shown in Figure 3-7 and described in Table 3-9.

Return to Summary Table.

Backup register #0 which can be used for storage by the application firmware when the external host is

power down. These registers will retain their content as long as VRTC is active.

RESET register domain: POR

Figure 3-7. BACKUP0 Register

7 6 5 4 3 2 1 0

BACKUP

R/W-0h

Table 3-9. BACKUP0 Register Field Descriptions

Bit Field Type Reset Description

7-0 BACKUP R/W 0h

www.ti.com

12

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 13

www.ti.com

FUNC_BACKUP Registers

3.2.2 BACKUP1 Register (Address = 119h) [reset = 0h]

BACKUP1 is shown in Figure 3-8 and described in Table 3-10.

Return to Summary Table.

Backup register #1 which can be used for storage by the application firmware when the external host is

power down. These registers will retain their content as long as VRTC is active.

RESET register domain: POR

Figure 3-8. BACKUP1 Register

7 6 5 4 3 2 1 0

BACKUP

R/W-0h

Table 3-10. BACKUP1 Register Field Descriptions

Bit Field Type Reset Description

7-0 BACKUP R/W 0h

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

13

Page 14

FUNC_BACKUP Registers

3.2.3 BACKUP2 Register (Address = 11Ah) [reset = 0h]

BACKUP2 is shown in Figure 3-9 and described in Table 3-11.

Return to Summary Table.

Backup register #2 which can be used for storage by the application firmware when the external host is

power down. These registers will retain their content as long as VRTC is active.

RESET register domain: POR

Figure 3-9. BACKUP2 Register

7 6 5 4 3 2 1 0

BACKUP

R/W-0h

Table 3-11. BACKUP2 Register Field Descriptions

Bit Field Type Reset Description

7-0 BACKUP R/W 0h

www.ti.com

14

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 15

www.ti.com

FUNC_BACKUP Registers

3.2.4 BACKUP3 Register (Address = 11Bh) [reset = 0h]

BACKUP3 is shown in Figure 3-10 and described in Table 3-12.

Return to Summary Table.

Backup register #3 which can be used for storage by the application firmware when the external host is

power down. These registers will retain their content as long as VRTC is active.

RESET register domain: POR

Figure 3-10. BACKUP3 Register

7 6 5 4 3 2 1 0

BACKUP

R/W-0h

Table 3-12. BACKUP3 Register Field Descriptions

Bit Field Type Reset Description

7-0 BACKUP R/W 0h

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

15

Page 16

FUNC_BACKUP Registers

3.2.5 BACKUP4 Register (Address = 11Ch) [reset = 0h]

BACKUP4 is shown in Figure 3-11 and described in Table 3-13.

Return to Summary Table.

Backup register #4 which can be used for storage by the application firmware when the external host is

power down. These registers will retain their content as long as VRTC is active.

RESET register domain: POR

Figure 3-11. BACKUP4 Register

7 6 5 4 3 2 1 0

BACKUP

R/W-0h

Table 3-13. BACKUP4 Register Field Descriptions

Bit Field Type Reset Description

7-0 BACKUP R/W 0h

www.ti.com

16

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 17

www.ti.com

FUNC_BACKUP Registers

3.2.6 BACKUP5 Register (Address = 11Dh) [reset = 0h]

BACKUP5 is shown in Figure 3-12 and described in Table 3-14.

Return to Summary Table.

Backup register #5 which can be used for storage by the application firmware when the external host is

power down. These registers will retain their content as long as VRTC is active.

RESET register domain: POR

Figure 3-12. BACKUP5 Register

7 6 5 4 3 2 1 0

BACKUP

R/W-0h

Table 3-14. BACKUP5 Register Field Descriptions

Bit Field Type Reset Description

7-0 BACKUP R/W 0h

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

17

Page 18

FUNC_BACKUP Registers

3.2.7 BACKUP6 Register (Address = 11Eh) [reset = 0h]

BACKUP6 is shown in Figure 3-13 and described in Table 3-15.

Return to Summary Table.

Backup register #6 which can be used for storage by the application firmware when the external host is

power down. These registers will retain their content as long as VRTC is active.

RESET register domain: POR

Figure 3-13. BACKUP6 Register

7 6 5 4 3 2 1 0

BACKUP

R/W-0h

Table 3-15. BACKUP6 Register Field Descriptions

Bit Field Type Reset Description

7-0 BACKUP R/W 0h

www.ti.com

18

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 19

www.ti.com

FUNC_BACKUP Registers

3.2.8 BACKUP7 Register (Address = 11Fh) [reset = 0h]

BACKUP7 is shown in Figure 3-14 and described in Table 3-16.

Return to Summary Table.

Backup register #7 which can be used for storage by the application firmware when the external host is

power down. These registers will retain their content as long as VRTC is active.

RESET register domain: POR

Figure 3-14. BACKUP7 Register

7 6 5 4 3 2 1 0

BACKUP

R/W-0h

Table 3-16. BACKUP7 Register Field Descriptions

Bit Field Type Reset Description

7-0 BACKUP R/W 0h

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

19

Page 20

FUNC_SMPS Registers

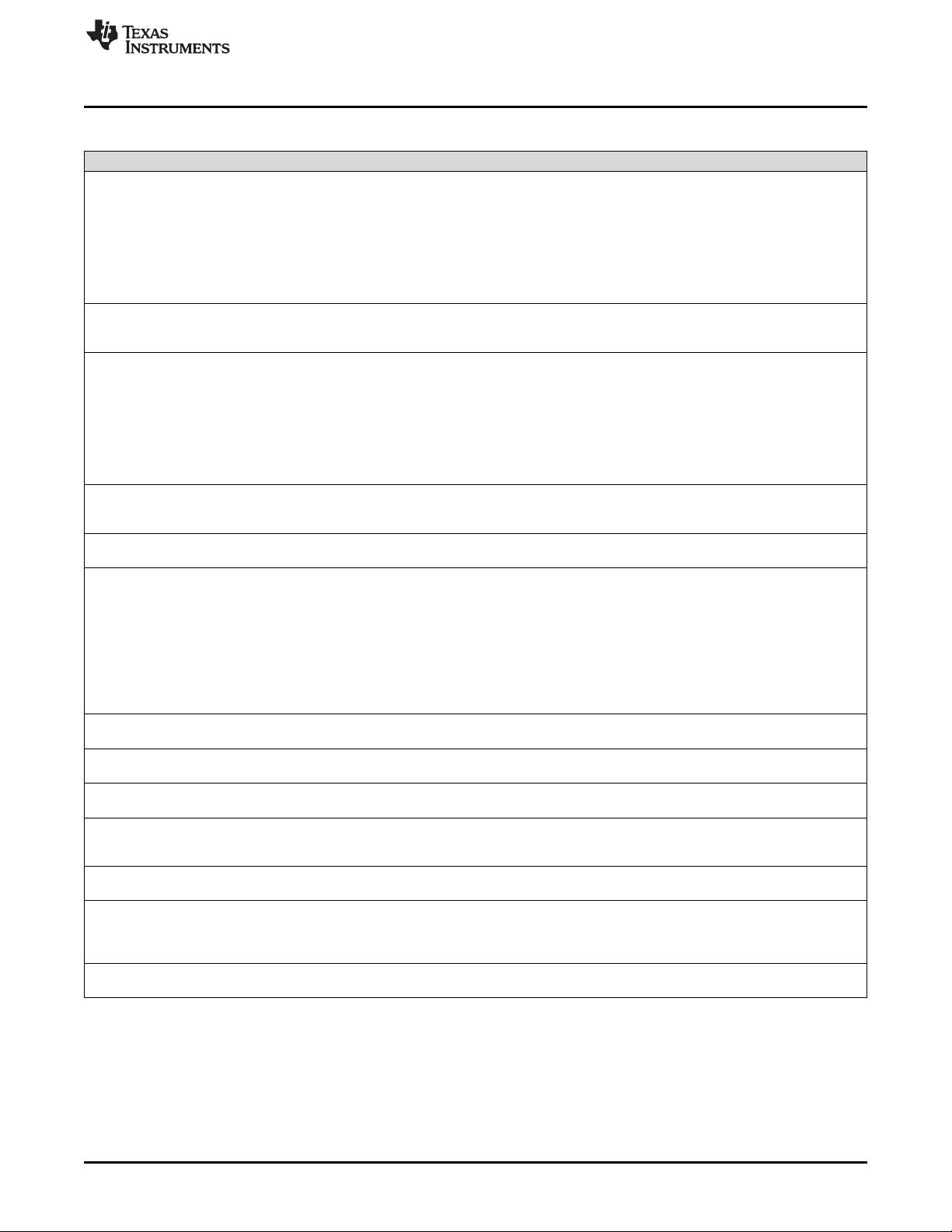

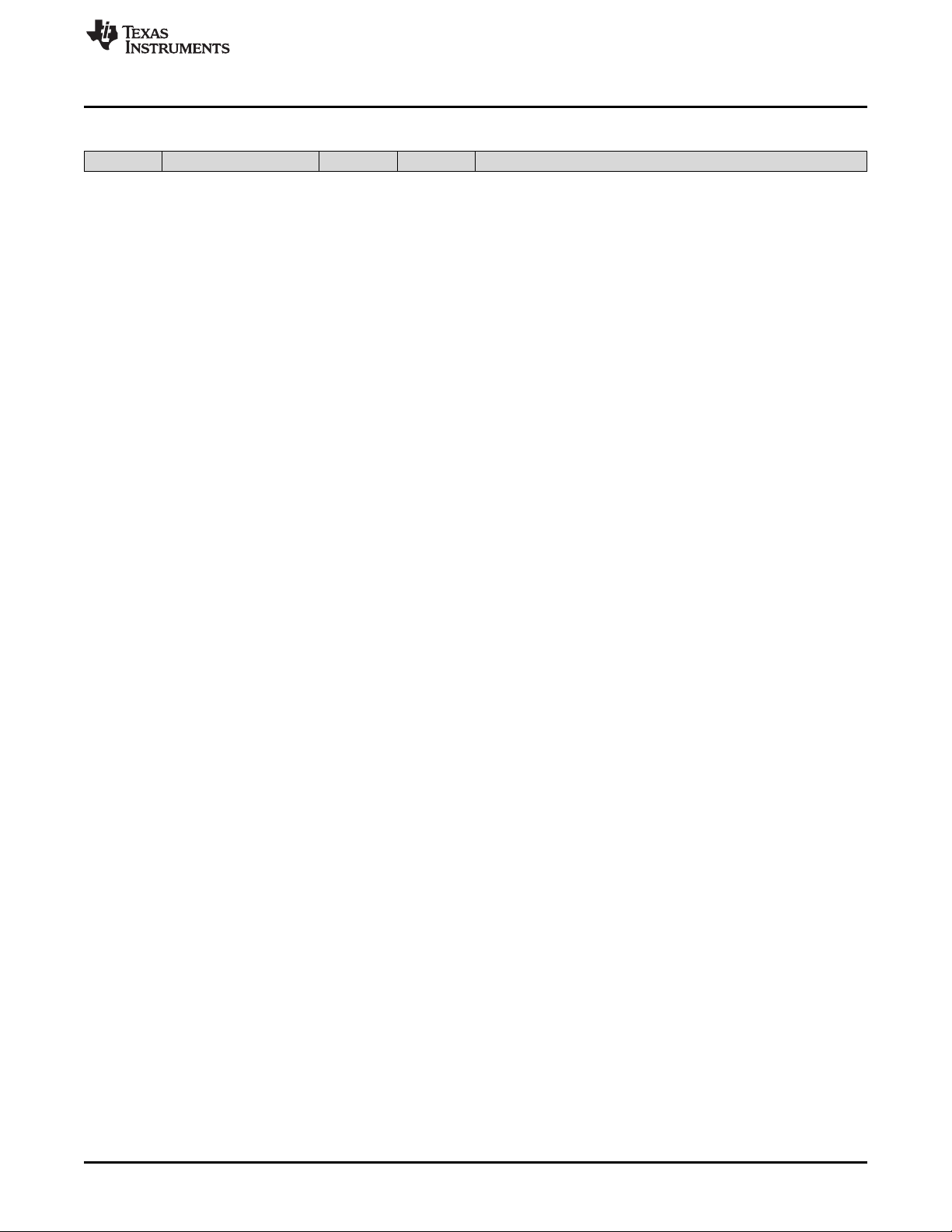

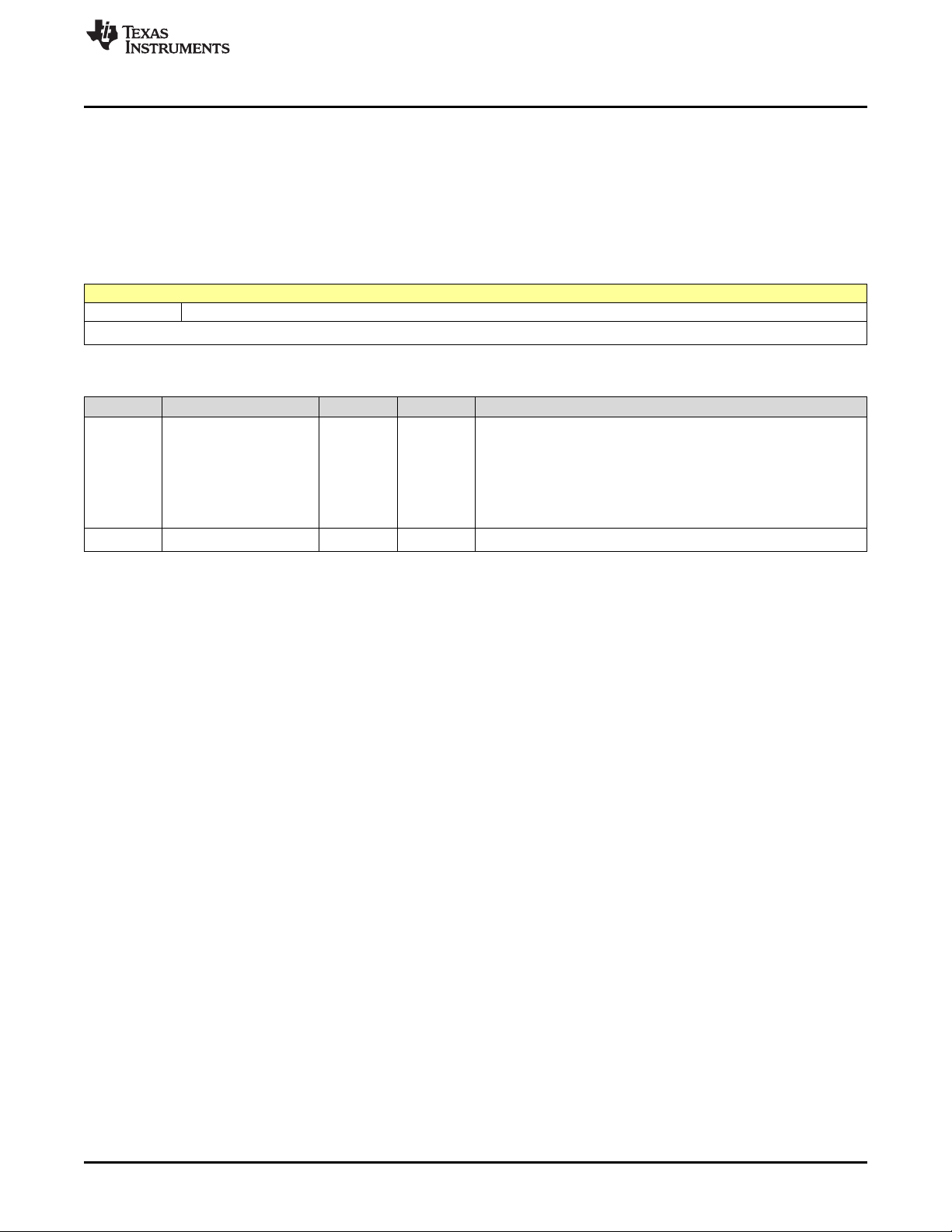

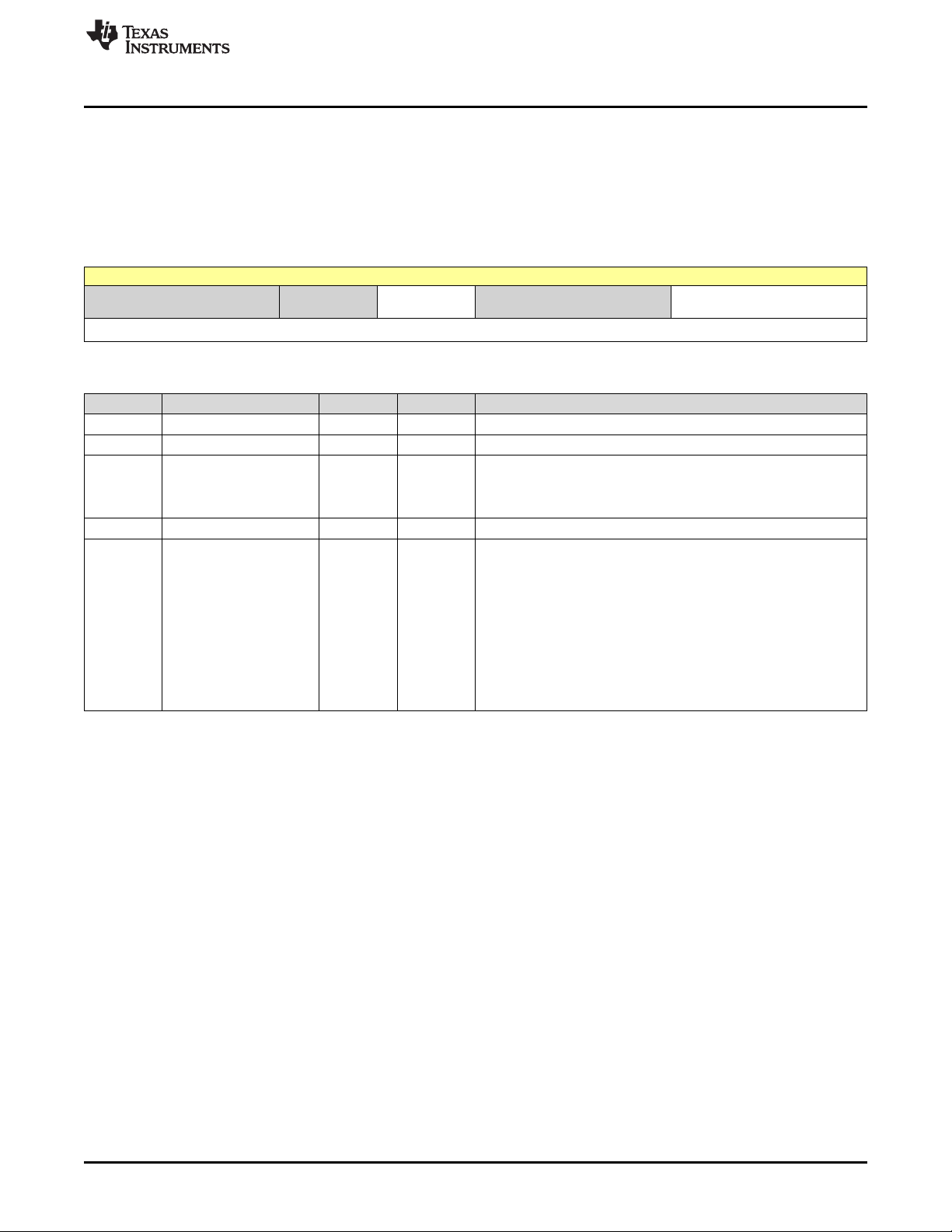

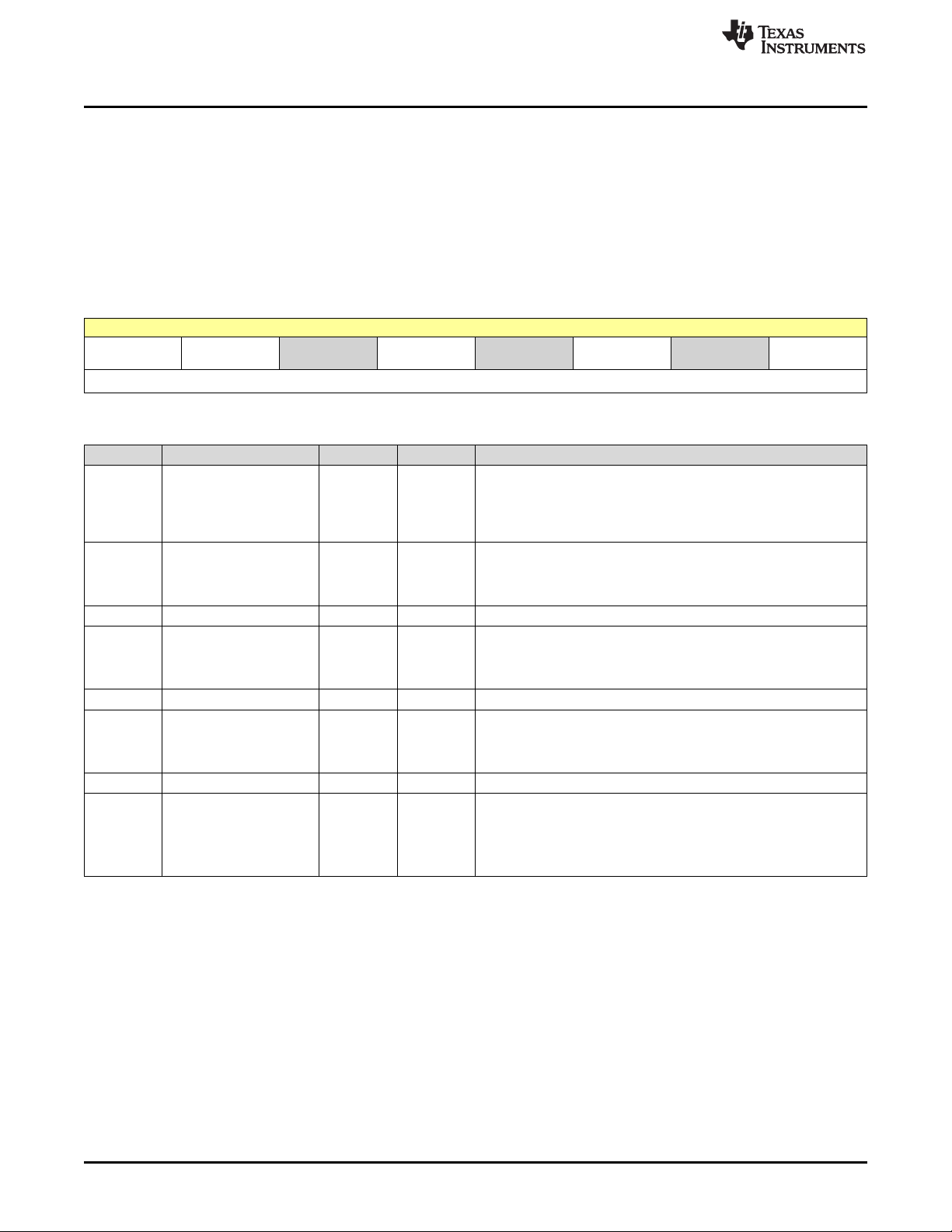

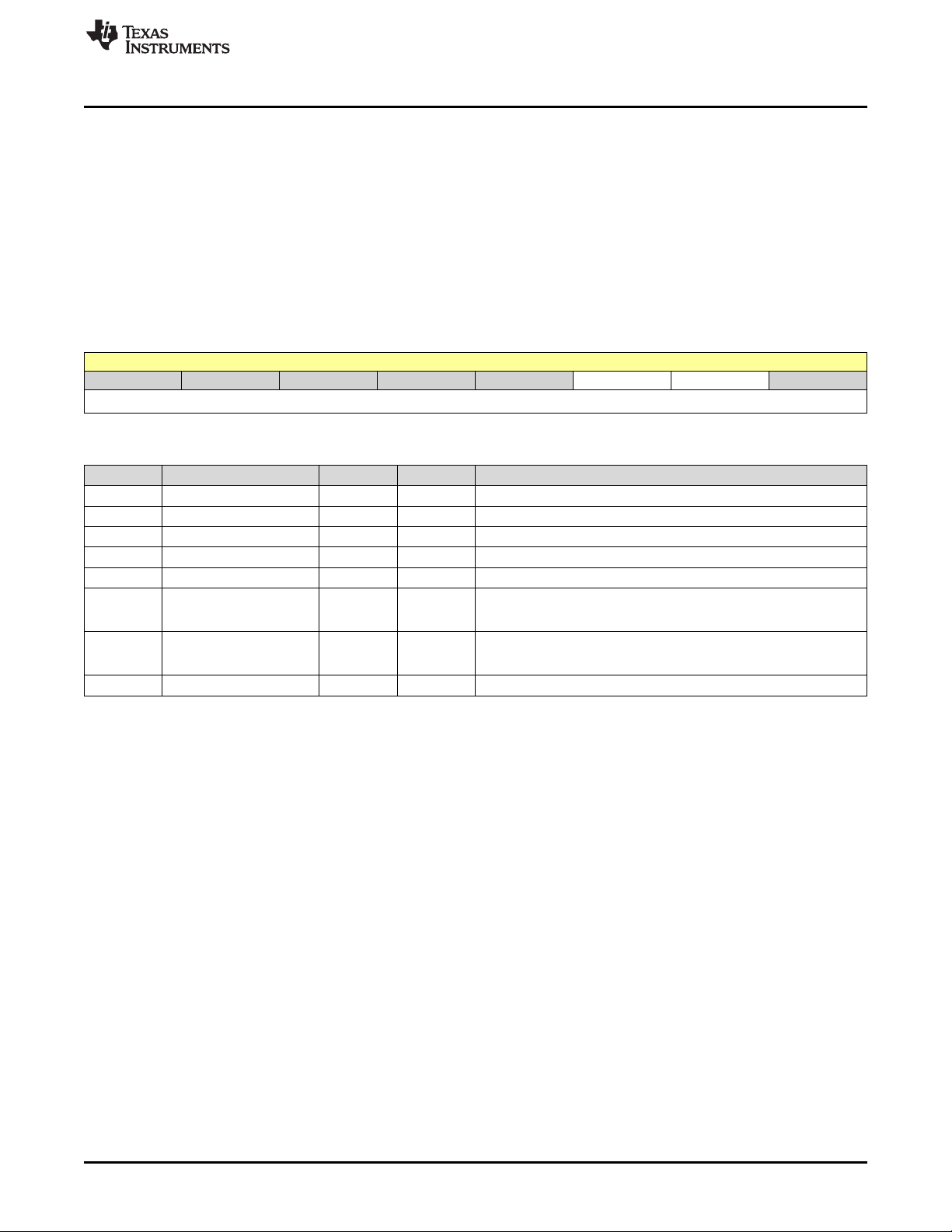

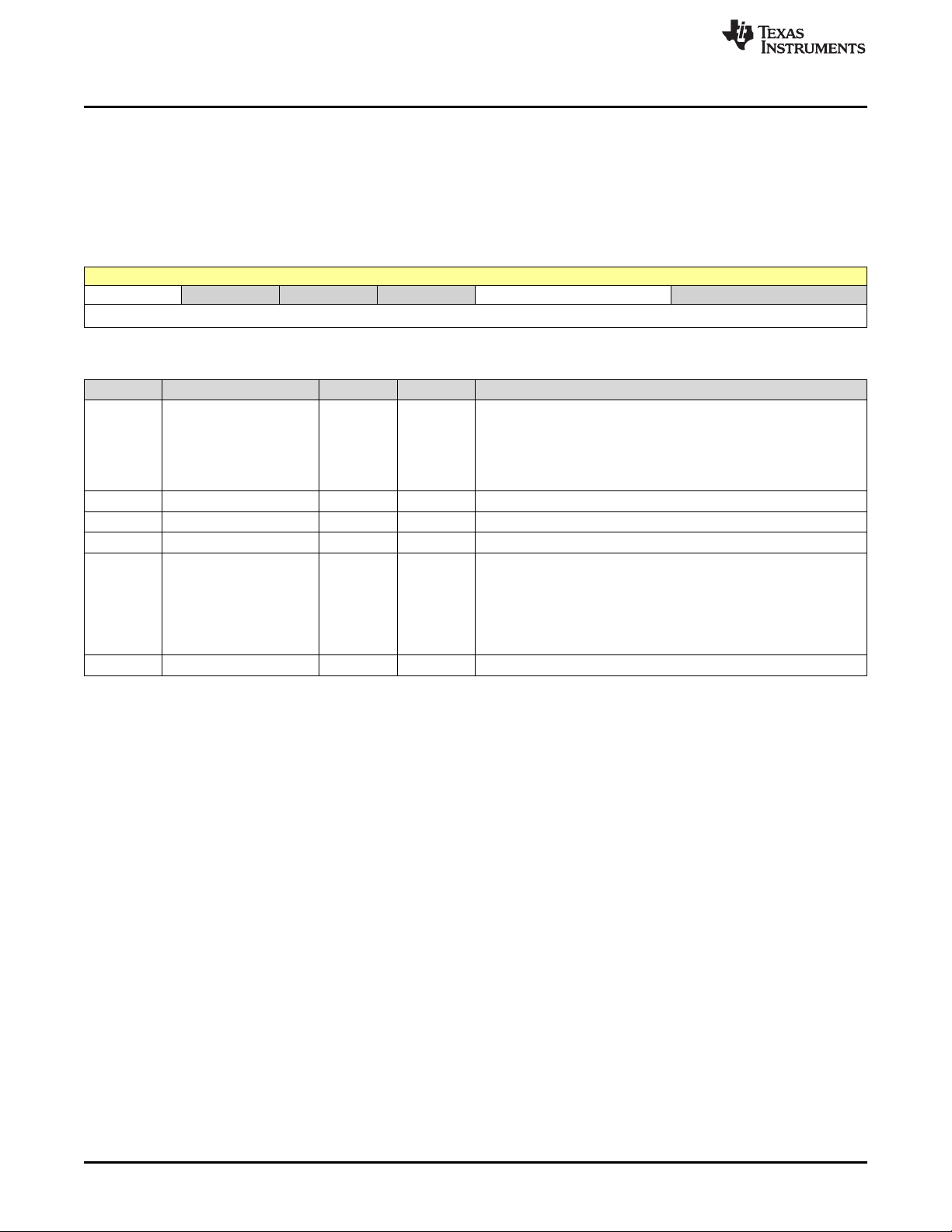

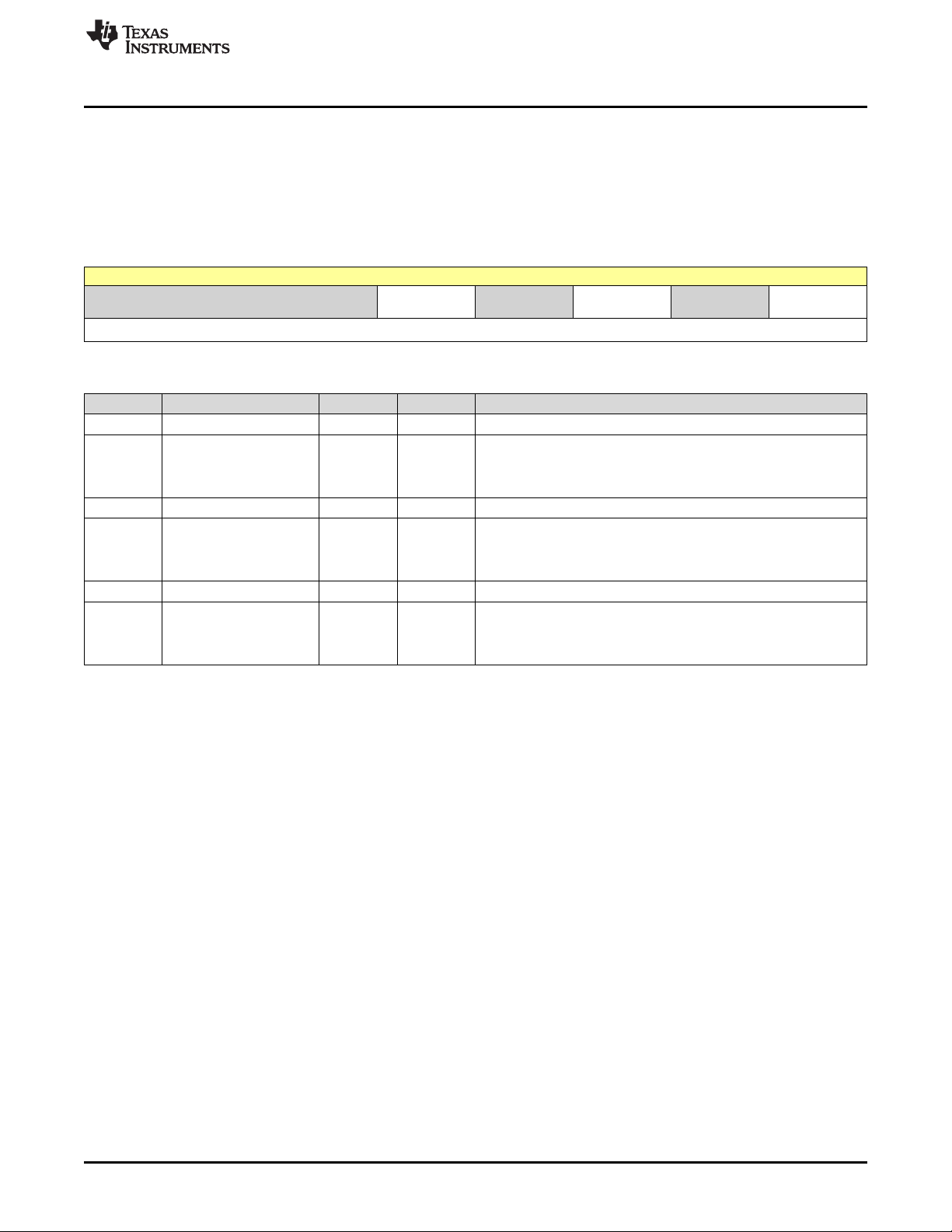

3.3 FUNC_SMPS Registers

Table 3-17 lists the memory-mapped registers for the FUNC_SMPS. All register offset addresses not

listed in Table 3-17 should be considered as reserved locations and the register contents should not be

modified.

Table 3-17. FUNC_SMPS Registers

Address Acronym Register Name Section

120h SMPS1_CTRL SMPS1 (or SMPS12 in case of dual-phase) control

register.

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

122h SMPS1_FORCE SMPS1 (or SMPS12 in case of dual-phase) DVS

register.

Voltage to apply to the resource when it is a DVS force

command (OTP_Config).

RESET register domain: SWORST

123h SMPS1_VOLTAGE SMPS1 (or SMPS12 in case of dual-phase) DVS

register.

Voltage to apply to the resource when it is not a DVS

force command (OTP_Config).

RESET register domain: SWORST

124h SMPS2_CTRL SMPS2 control register.

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

126h SMPS2_FORCE SMPS2 DVS register.

Voltage to apply to the resource when it is a DVS force

command (OTP_Config).

RESET register domain: SWORST

127h SMPS2_VOLTAGE SMPS2 DVS register.

Voltage to apply to the resource when it is not a DVS

force command (OTP_Config).

RESET register domain: SWORST

12Ch SMPS3_CTRL SMPS3 control register.

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

12Eh SMPS3_FORCE SMPS3

DVS register.

Voltage to apply to the resource when it is a DVS force

command (OTP_Config).

RESET register domain: SWORST

12Fh SMPS3_VOLTAGE SMPS3 DVS register.

Voltage to apply to the resource when it is not a DVS

force command (OTP_Config).

RESET register domain: SWORST

Section 3.3.1

Section 3.3.2

Section 3.3.3

Section 3.3.4

Section 3.3.5

Section 3.3.6

Section 3.3.7

Section 3.3.8

Section 3.3.9

www.ti.com

20

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 21

www.ti.com

FUNC_SMPS Registers

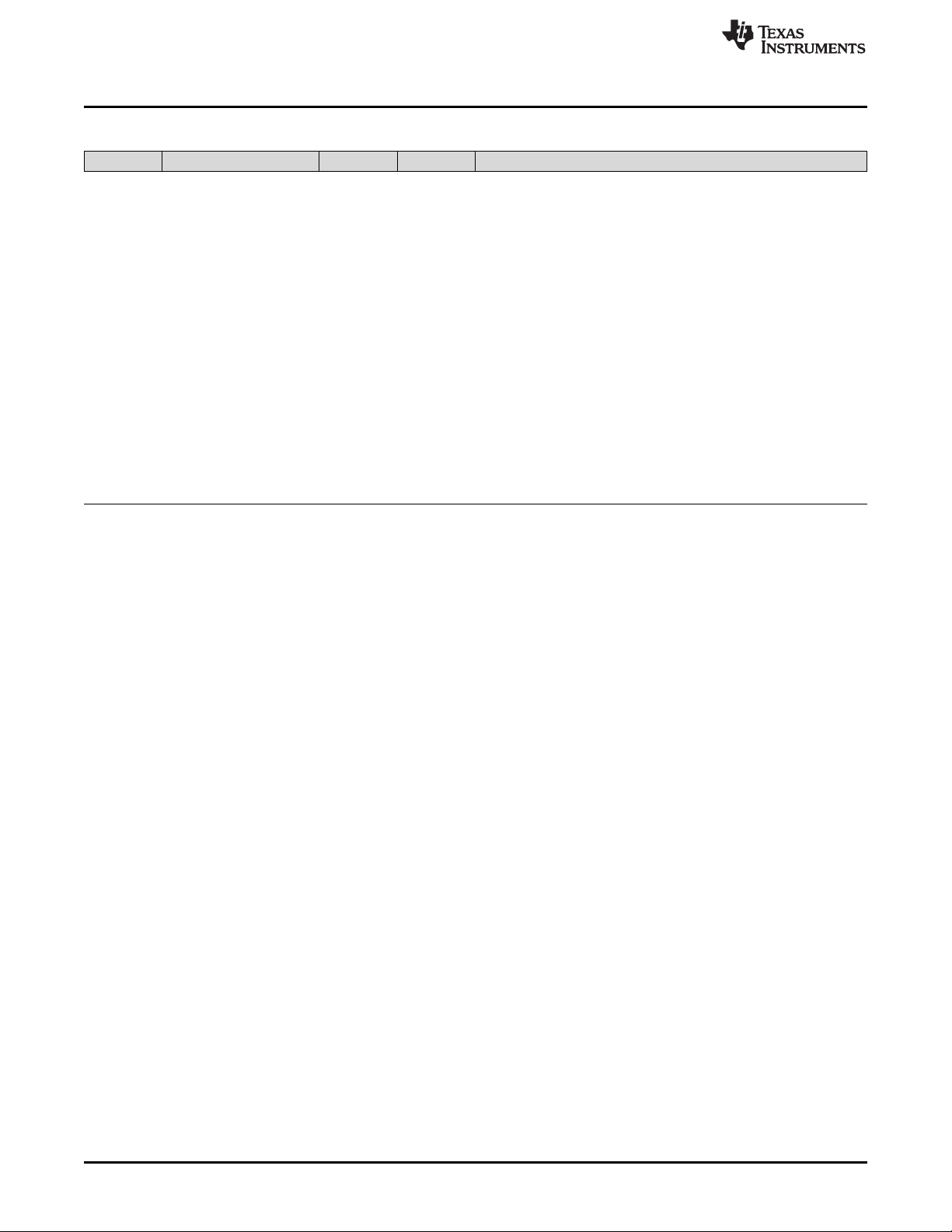

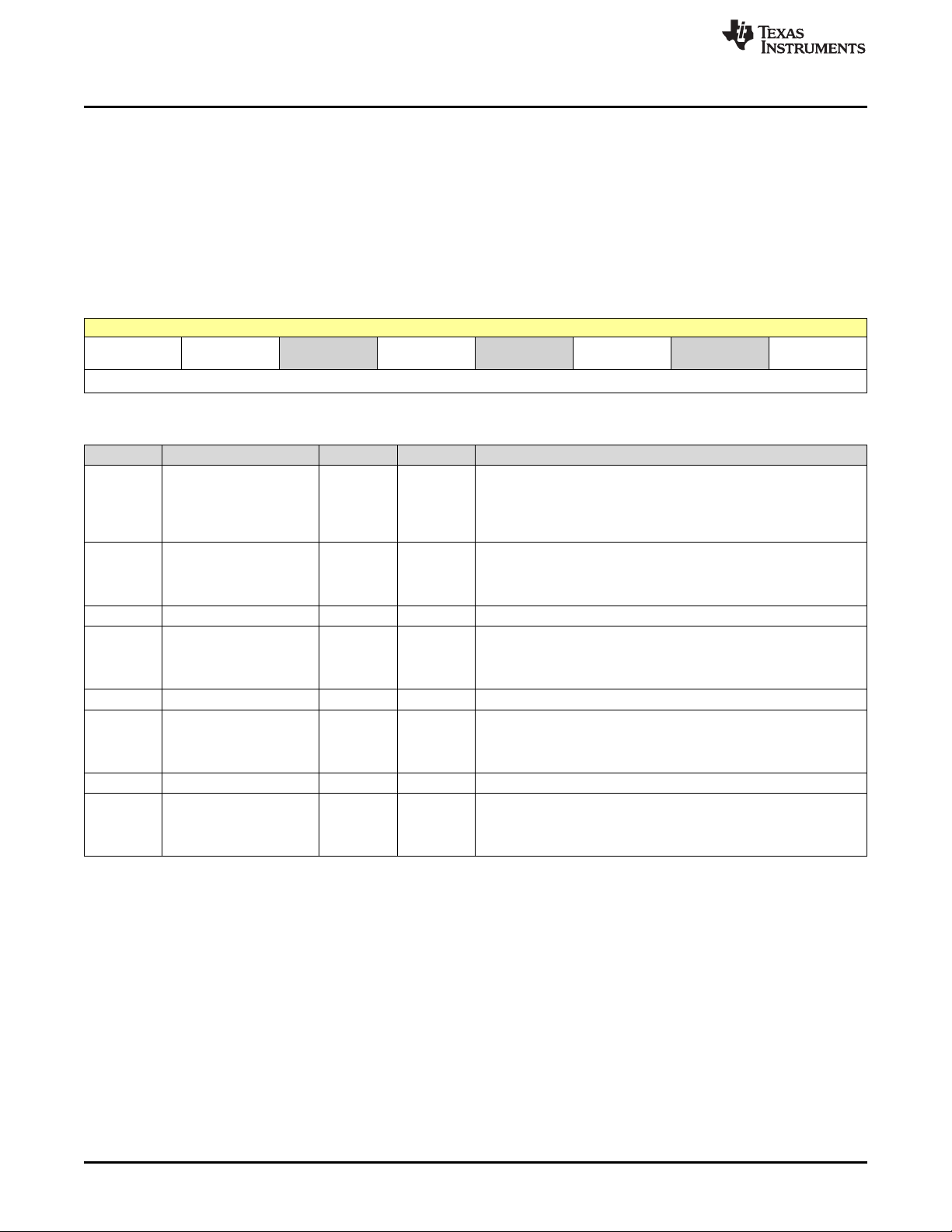

Table 3-17. FUNC_SMPS Registers (continued)

Address Acronym Register Name Section

130h SMPS4_CTRL SMPS4 control register.

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

133h SMPS4_VOLTAGE SMPS4 register.

Voltage to apply to the resource.

RESET register domain: SWORST

138h SMPS5_CTRL SMPS5 control register.

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

13Bh SMPS5_VOLTAGE MPS5 register.

Voltage to apply to the resource.

RESET register domain: SWORST

144h SMPS_CTRL SMPS control register.

RESET register domain: HWRST

145h SMPS_PD_CTRL SMPS Pull-Down enable register.

RESET register domain: HWRST

Notes:

SMPS pull-down register bits validate the control of the

active discharge of each power resource to full-fill the

turn-off timing requirements.

When a pull-down is not enabled, there is always a weak

pull-down present at the output of the power resource,

so that the device restart correctly at the next power-up

sequence.

147h SMPS_THERMAL_EN SMPS Thermal feature enable register.

RESET register domain: HWRST

148h SMPS_THERMAL_STATUS SMPS Thermal status register.

RESET register domain: POR

149h SMPS_SHORT_STATUS SMPS Short circuit status.

RESET register domain: POR

14Ah SMPS_NEGATIVE_CURRENT_LIMIT_EN Iload Negative Current Comparator enable register

(Negative Current measurement).

RESET register domain: HWRST

14Bh SMPS_POWERGOOD_MASK1 SMPS Power Good (POWERGOOD) mask #1

RESET register domain: POR

14Ch SMPS_POWERGOOD_MASK2 SMPS Power Good (POWERGOOD) mask #2

RESET register domain: POR (excepted

POWERGOOD_TYPE_SELECT which is under

HWRST)

14Dh SMPS_PLL_CTRL SMPS PLL control register.

RESET register domain: HWRST

Section 3.3.10

Section 3.3.11

Section 3.3.12

Section 3.3.13

Section 3.3.14

Section 3.3.15

Section 3.3.16

Section 3.3.17

Section 3.3.18

Section 3.3.19

Section 3.3.20

Section 3.3.21

Section 3.3.22

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

21

Page 22

FUNC_SMPS Registers

3.3.1 SMPS1_CTRL Register (Address = 120h) [reset = 0h]

SMPS1_CTRL is shown in Figure 3-15 and described in Table 3-18.

Return to Summary Table.

SMPS1 (or SMPS12 in case of dual-phase) control register.

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP, ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP, ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the Data Manual for details).

Figure 3-15. SMPS1_CTRL Register

7 6 5 4 3 2 1 0

WR_S ROOF_FLOOR

_EN

R/W-0h R/W-0h R-0h R/W-0h R/W-0h

Table 3-18. SMPS1_CTRL Register Field Descriptions

Bit Field Type Reset Description

7 WR_S R/W 0h

6 ROOF_FLOOR_EN R/W 0h

5-4 STATUS R 0h

3-2 MODE_SLEEP R/W 0h

1-0 MODE_ACTIVE R/W 0h

STATUS MODE_SLEEP MODE_ACTIVE

Warm reset sensitivity

0: Re-load the default value (from OTP) in SMPS1_VOLTAGE.VSEL

and SMPS1_FORCE.VSEL register and re-load the default value

(reset value) in SMPS1_FORCE.CMD during Warm Reset.

1: Maintain current voltage during Warm Reset (Registers remain

unchanged - no voltage change).

Roof Floor enable bit (only for DVS)

0: Voltage Selection controlled by SMPS1_FORCE.CMD bit.

1: Voltage Selection controlled by device resource pins (NSLEEP,

ENABLE1, ENABLE2).

SMPS1 (or SMPS12 in case of dual-phase) status

00: OFF

01: Forced PWM

10: ECO

11: Forced PWM

SMPS1 (or SMPS12 in case of dual-phase) SLEEP Mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

SMPS1 (or SMPS12 in case of dual-phase) ACTIVE Mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

www.ti.com

22

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 23

www.ti.com

FUNC_SMPS Registers

3.3.2 SMPS1_FORCE Register (Address = 122h) [reset = X]

SMPS1_FORCE is shown in Figure 3-16 and described in Table 3-19.

Return to Summary Table.

SMPS1 (or SMPS12 in case of dual-phase) DVS register. Voltage to apply to the resource when it is a

DVS force command (OTP_Config).

RESET register domain: SWORST

Figure 3-16. SMPS1_FORCE Register

7 6 5 4 3 2 1 0

CMD VSEL

R/W-1h R/W-X

Table 3-19. SMPS1_FORCE Register Field Descriptions

Bit Field Type Reset Description

7 CMD R/W 1h

6-0 VSEL R/W X

DVS command register selection:

When 0: SMPS1_FORCE.VSEL voltage is applied

When 1: SMPS1_VOLTAGE.VSEL voltage is applied (default)

CMD is effective if SMPS1_CTRL.ROOF_FLOOR_EN='0'

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

23

Page 24

FUNC_SMPS Registers

3.3.3 SMPS1_VOLTAGE Register (Address = 123h) [reset = X]

SMPS1_VOLTAGE is shown in Figure 3-17 and described in Table 3-20.

Return to Summary Table.

SMPS1 (or SMPS12 in case of dual-phase) DVS register. Voltage to apply to the resource when it is not a

DVS force command (OTP_Config).

RESET register domain: SWORST

Figure 3-17. SMPS1_VOLTAGE Register

7 6 5 4 3 2 1 0

RANGE VSEL

R/W-X R/W-X

Table 3-20. SMPS1_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7 RANGE R/W X

Range of the VSEL voltage. This bit is applied to

SMPS1_VOLTAGE.VSEL and SMPS1_FORCE.VSEL

0: 0.5V to 1.65V

1: 1.0 to 3.3V

Note: RANGE bit is RO when SMPS1(or SMPS12 in case of dual-

phase) is ON, RANGE bit is RW when SMPS1 (or SMPS12 in case

of dual-phase) is OFF

Note: For Dual-phase mode, RANGE=1 (1V to 3.3V) is not

supported.

www.ti.com

24

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 25

www.ti.com

Table 3-20. SMPS1_VOLTAGE Register Field Descriptions (continued)

Bit Field Type Reset Description

6-0 VSEL R/W X

FUNC_SMPS Registers

VSEL[6:0] cross table voltage (OFF,0.5V to 3.3V)

RANGE[0]=0 (x1 multiplier)/ 1(x2 multiplier)

0000000 = SMPS OFF/OFF 1000000 = 1.08V/2.16V

0000001 = 0.5V/1V 1000001 = 1.09V/2.18V

0000010 = 0.5V/1V 1000010 = 1.1V/2.2V

0000011 = 0.5V/1V 1000011 = 1.11V/2.22V

0000100 = 0.5V/1V 1000100 = 1.12V/2.24V

0000101 = 0.5V/1V 1000101 = 1.13V/2.26V

0000110 = 0.5V/1V 1000110 = 1.14V/2.28V

0000111 = 0.51V/1.02V 1000111 = 1.15V/2.3V

0001000 = 0.52V/1.04V 1001000 = 1.16V/2.32V

0001001 = 0.53V/1.06V 1001001 = 1.17V/2.34V

0001010 = 0.54V/1.08V 1001010 = 1.18V/2.36V

0001011 = 0.55V/1.1V 1001011 = 1.19V/2.38V

0001100 = 0.56V/1.12V 1001100 = 1.2V/2.4V

0001101 = 0.57V/1.14V 1001101 = 1.21V/2.42V

0001110 = 0.58V/1.16V 1001110 = 1.22V/2.44V

0001111 = 0.59V/1.18V 1001111 = 1.23V/2.46V

0010000 = 0.60V/1.2V 1010000 = 1.24V/2.48V

0010001 = 0.61V/1.22V 1010001 = 1.25V/2.5V

0010010 = 0.62V/1.24V 1010010 = 1.26V/2.52V

0010011 = 0.63V/1.26V 1010011 = 1.27V/2.54V

0010100 = 0.64V/1.28V 1010100 = 1.28V/2.56V

0010101 = 0.65V/1.3V 1010101 = 1.29V/2.58V

0010110 = 0.66V/1.32V 1010110 = 1.3V/2.6V

0010111 = 0.67V/1.34V 1010111 = 1.31V/2.62V

0011000 = 0.68V/1.36V 1011000 = 1.32V/2.64V

0011001 = 0.69V/1.38V 1011001 = 1.33V/2.66V

0011010 = 0.70V/1.4V 1011010 = 1.34V/2.68V

0011011 = 0.71V/1.42V 1011011 = 1.35V/2.7V

0011100 = 0.72V/1.44V 1011100 = 1.36V/2.72V

0011101 = 0.73V/1.46V 1011101 = 1.37V/2.74V

0011110 = 0.74V/1.48V 1011110 = 1.38V/2.76V

0011111 = 0.75V/1.50V 1011111 = 1.39V/2.78V

0100000 = 0.76V/1.52V 1100000 = 1.4V/2.8V

0100001 = 0.77V/1.54V 1100001 = 1.41V/2.82V

0100010 = 0.78V/1.56V 1100010 = 1.42V/2.84V

0100011 = 0.79V/1.58V 1100011 = 1.43V/2.86V

0100100 = 0.8V/1.6V 1100100 = 1.44V/2.88V

0100101 = 0.81V/1.62V 1100101 = 1.45V/2.9V

0100110 = 0.82V/1.64V 1100110 = 1.46V/2.92V

0100111 = 0.83V/1.66V 1100111 = 1.47V/2.94V

0101000 = 0.84V/1.68V 1101000 = 1.48V/2.96V

0101001 = 0.85V/1.7V 1101001= 1.49V/2.98V

0101010 = 0.86V/1.72V 1101010 = 1.5V/3V

0101011 = 0.87V/1.74V 1101011 = 1.51V/3.02V

0101100 = 0.88V/1.76V 1101100 = 1.52V/3.04V

0101101 = 0.89V/1.78V 1101101 = 1.53V/3.06V

0101110 = 0.9V/1.8V 1101110 = 1.54V/3.08V

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

25

Page 26

FUNC_SMPS Registers

Table 3-20. SMPS1_VOLTAGE Register Field Descriptions (continued)

Bit Field Type Reset Description

www.ti.com

0101111 = 0.91V/1.82V 1101111 = 1.55V/3.1V

0110000 = 0.92V/1.84V 1110000 = 1.56V/3.12V

0110001 = 0.93V/1.86V 1110001 = 1.57V/3.14V

0110010 = 0.94V/1.88V 1110010 = 1.58V/3.16V

0110011 = 0.95V/1.90V 1110011 = 1.59V/3.18V

0110100 = 0.96V/1.92V 1110100 = 1.6V/3.2V

0110101 = 0.97V/1.94V 1110101 = 1.61V/3.22V

0110110 = 0.98V/1.96V 1110110 = 1.62V/3.24V

0110111 = 0.99V/1.98V 1110111 = 1.63V/3.26V

0111000 = 1.00V/2V 1111000 = 1.64V/3.28V

0111001 = 1.01V/2.02V 1111001 = 1.65V/3.3V

0111010 = 1.02V/2.04V 1111010 = 1.65V/3.3V

0111011 = 1.03V/2.06V 1111011 = 1.65V/3.3V

0111100 = 1.04V/2.08V 1111100 = 1.65V/3.3V

0111101 = 1.05V/2.1V 1111101 = 1.65V/3.3V

0111110 = 1.06V/2.12V 1111110 = 1.65V/3.3V

0111111 = 1.07V/2.14V 1111111 = 1.65V/3.3V

26

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 27

www.ti.com

FUNC_SMPS Registers

3.3.4 SMPS2_CTRL Register (Address = 124h) [reset = 0h]

SMPS2_CTRL is shown in Figure 3-18 and described in Table 3-21.

Return to Summary Table.

SMPS2 control register.

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP, ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP, ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the Data Manual for details).

Figure 3-18. SMPS2_CTRL Register

7 6 5 4 3 2 1 0

WR_S ROOF_FLOOR

_EN

R/W-0h R/W-0h R-0h R/W-0h R/W-0h

Table 3-21. SMPS2_CTRL Register Field Descriptions

Bit Field Type Reset Description

7 WR_S R/W 0h

6 ROOF_FLOOR_EN R/W 0h

5-4 STATUS R 0h

3-2 MODE_SLEEP R/W 0h

1-0 MODE_ACTIVE R/W 0h

STATUS MODE_SLEEP MODE_ACTIVE

Warm reset sensitivity

0: Re-load the default value (from OTP in SMPS2_VOLTAGE.VSEL

register during Warm Reset.

1: Maintain current voltage during Warm Reset (Registers remain

unchanged - no voltage change).

Roof Floor enable bit (only for DVS)

0: Voltage Selection controlled by SMPS2_FORCE.CMD bit.

1: Voltage Selection controlled by device resource pins (NSLEEP,

ENABLE1, ENABLE2).

SMPS2 Status

00: OFF

01: Forced PWM

10: ECO

11: Forced PWM

SMPS2 SLEEP mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

SMPS2 ACTIVE Mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

27

Page 28

FUNC_SMPS Registers

3.3.5 SMPS2_FORCE Register (Address = 126h) [reset = X]

SMPS2_FORCE is shown in Figure 3-19 and described in Table 3-22.

Return to Summary Table.

SMPS2 DVS register. Voltage to apply to the resource when it is a DVS force command (OTP_Config).

RESET register domain: SWORST

Figure 3-19. SMPS2_FORCE Register

7 6 5 4 3 2 1 0

CMD VSEL

R/W-1h R/W-X

Table 3-22. SMPS2_FORCE Register Field Descriptions

Bit Field Type Reset Description

7 CMD R/W 1h

6-0 VSEL R/W X

DVS command register selection:

When 0: SMPS2_FORCE.VSEL voltage is applied

When 1: SMPS2_VOLTAGE.VSEL voltage is applied (default)

CMD is effective if SMPS2_CTRL.ROOF_FLOOR_EN='0'

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register.

www.ti.com

28

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 29

www.ti.com

FUNC_SMPS Registers

3.3.6 SMPS2_VOLTAGE Register (Address = 127h) [reset = X]

SMPS2_VOLTAGE is shown in Figure 3-20 and described in Table 3-23.

Return to Summary Table.

SMPS2 DVS register. Voltage to apply to the resource when it is not a DVS force command

(OTP_Config).

RESET register domain: SWORST

Figure 3-20. SMPS2_VOLTAGE Register

7 6 5 4 3 2 1 0

RANGE VSEL

R/W-X R/W-X

Table 3-23. SMPS2_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7 RANGE R/W X

6-0 VSEL R/W X

Range of the VSEL voltage. This bit is applied to

SMPS2_VOLTAGE.VSEL

0: 0.5V to 1.65V

1: 1.0 to 3.3V

Note:RANGE bit is RO when SMPS2 is ON, RANGE bit is RW when

SMPS2 is OFF

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register.

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

29

Page 30

FUNC_SMPS Registers

3.3.7 SMPS3_CTRL Register (Address = 12Ch) [reset = 0h]

SMPS3_CTRL is shown in Figure 3-21 and described in Table 3-24.

Return to Summary Table.

SMPS3 control register.

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP, ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP, ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the Data Manual for details).

Figure 3-21. SMPS3_CTRL Register

7 6 5 4 3 2 1 0

WR_S ROOF_FLOOR

_EN

R/W-0h R/W-0h R-0h R/W-0h R/W-0h

Table 3-24. SMPS3_CTRL Register Field Descriptions

Bit Field Type Reset Description

7 WR_S R/W 0h

6 ROOF_FLOOR_EN R/W 0h

5-4 STATUS R 0h

3-2 MODE_SLEEP R/W 0h

1-0 MODE_ACTIVE R/W 0h

STATUS MODE_SLEEP MODE_ACTIVE

Warm reset sensitivity

0: Re-load the default value (from OTP) in SMPS3_VOLTAGE.VSEL

and SMPS3_FORCE.VSEL register and re-load the default value

(reset value) in SMPS3_FORCE.CMD during Warm Reset.

1: Maintain current voltage during Warm Reset (Registers remain

unchanged - no voltage change).

Roof Floor enable bit (only for DVS)

0: Voltage Selection controlled by SMPS3_FORCE.CMD bit.

1: Voltage Selection controlled by device resource pins (NSLEEP,

ENABLE1, ENABLE2).

SMPS3 Status

00: OFF

01: Forced PWM

10: ECO

11: Forced PWM

SMPS3 SLEEP mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

SMPS3 ACTIVE Mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

www.ti.com

30

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 31

www.ti.com

FUNC_SMPS Registers

3.3.8 SMPS3_FORCE Register (Address = 12Eh) [reset = X]

SMPS3_FORCE is shown in Figure 3-22 and described in Table 3-25.

Return to Summary Table.

SMPS3

DVS register. Voltage to apply to the resource when it is a DVS force command (OTP_Config).

RESET register domain: SWORST

Figure 3-22. SMPS3_FORCE Register

7 6 5 4 3 2 1 0

CMD VSEL

R/W-1h R/W-X

Table 3-25. SMPS3_FORCE Register Field Descriptions

Bit Field Type Reset Description

7 CMD R/W 1h

6-0 VSEL R/W X

DVS command register selection:

When 0: SMPS3_FORCE.VSEL voltage is applied

When 1: SMPS3_VOLTAGE.VSEL voltage is applied (default)

CMD is effective if SMPS3_CTRL.ROOF_FLOOR_EN='0'

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register.

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

31

Page 32

FUNC_SMPS Registers

3.3.9 SMPS3_VOLTAGE Register (Address = 12Fh) [reset = X]

SMPS3_VOLTAGE is shown in Figure 3-23 and described in Table 3-26.

Return to Summary Table.

SMPS3 DVS register. Voltage to apply to the resource when it is not a DVS force command

(OTP_Config).

RESET register domain: SWORST

Figure 3-23. SMPS3_VOLTAGE Register

7 6 5 4 3 2 1 0

RANGE VSEL

R/W-X R/W-X

Table 3-26. SMPS3_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7 RANGE R/W X

6-0 VSEL R/W X

Range of the VSEL voltage. This bit is applied to

SMPS3_VOLTAGE.VSEL and SMPS3_FORCE.VSEL

0: 0.5V to 1.65V

1: 1.0 to 3.3V

Note:RANGE bit is RO when SMPS3 is ON, RANGE bit is RW when

SMPS3 is OFF

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register.

www.ti.com

32

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 33

www.ti.com

FUNC_SMPS Registers

3.3.10 SMPS4_CTRL Register (Address = 130h) [reset = 0h]

SMPS4_CTRL is shown in Figure 3-24 and described in Table 3-27.

Return to Summary Table.

SMPS4 control register.

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP, ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP, ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the Data Manual for details).

Figure 3-24. SMPS4_CTRL Register

7 6 5 4 3 2 1 0

WR_S RESERVED STATUS MODE_SLEEP MODE_ACTIVE

R/W-0h R-0h R-0h R/W-0h R/W-0h

Table 3-27. SMPS4_CTRL Register Field Descriptions

Bit Field Type Reset Description

7 WR_S R/W 0h

6 RESERVED R 0h

5-4 STATUS R 0h

3-2 MODE_SLEEP R/W 0h

1-0 MODE_ACTIVE R/W 0h

Warm reset sensitivity

0: Re-load the default value (from OTP) in SMPS4_VOLTAGE.VSEL

register during Warm Reset.

1: Maintain current voltage during Warm Reset (Registers remain

unchanged - no voltage change).

SMPS4 Status

00: OFF

01: Forced PWM

10: ECO

11: Forced PWM

SMPS4 SLEEP mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

SMPS4 ACTIVE Mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

33

Page 34

FUNC_SMPS Registers

3.3.11 SMPS4_VOLTAGE Register (Address = 133h) [reset = X]

SMPS4_VOLTAGE is shown in Figure 3-25 and described in Table 3-28.

Return to Summary Table.

SMPS4 register. Voltage to apply to the resource.

RESET register domain: SWORST

Figure 3-25. SMPS4_VOLTAGE Register

7 6 5 4 3 2 1 0

RANGE VSEL

R/W-X R/W-X

Table 3-28. SMPS4_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7 RANGE R/W X

6-0 VSEL R/W X

Range of the VSEL voltage. This bit is applied to

SMPS4_VOLTAGE.VSEL

0: 0.5V to 1.65V

1: 1.0 to 3.3V

Note:RANGE bit is RO when SMPS4 is ON, RANGE bit is RW when

SMPS4 is OFF

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register.

www.ti.com

34

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 35

www.ti.com

FUNC_SMPS Registers

3.3.12 SMPS5_CTRL Register (Address = 138h) [reset = 0h]

SMPS5_CTRL is shown in Figure 3-26 and described in Table 3-29.

Return to Summary Table.

SMPS5 control register.

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP, ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP, ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the Data Manual for details).

Figure 3-26. SMPS5_CTRL Register

7 6 5 4 3 2 1 0

WR_S RESERVED STATUS MODE_SLEEP MODE_ACTIVE

R/W-0h R-0h R-0h R/W-0h R/W-0h

Table 3-29. SMPS5_CTRL Register Field Descriptions

Bit Field Type Reset Description

7 WR_S R/W 0h

6 RESERVED R 0h

5-4 STATUS R 0h

3-2 MODE_SLEEP R/W 0h

1-0 MODE_ACTIVE R/W 0h

Warm reset sensitivity

0: Re-load the default value (from OTP) in SMPS5_VOLTAGE.VSEL

register during Warm Reset.

1: Maintain current voltage during Warm Reset (Registers remain

unchanged - no voltage change).

SMPS5 Status

00: OFF

01: Forced PWM

10: ECO

11: Forced PWM

SMPS5 SLEEP Mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

SMPS5 ACTIVE Mode

00: OFF (default)

01: Forced PWM

10: ECO

11: Forced PWM

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

35

Page 36

FUNC_SMPS Registers

3.3.13 SMPS5_VOLTAGE Register (Address = 13Bh) [reset = X]

SMPS5_VOLTAGE is shown in Figure 3-27 and described in Table 3-30.

Return to Summary Table.

SMPS5 register. Voltage to apply to the resource.

RESET register domain: SWORST

Figure 3-27. SMPS5_VOLTAGE Register

7 6 5 4 3 2 1 0

RANGE VSEL

R/W-X R/W-X

Table 3-30. SMPS5_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7 RANGE R/W X

6-0 VSEL R/W X

Range of the VSEL voltage. This bit is applied to

SMPS5_VOLTAGE.VSEL

0: 0.5V to 1.65V

1: 1.0 to 3.3V

Note:RANGE bit is RO when SMPS5 is ON, RANGE bit is RW when

SMPS5 is OFF

See VSEL cross table showed in SMPS1_VOLTAGE.VSEL register.

www.ti.com

36

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 37

www.ti.com

FUNC_SMPS Registers

3.3.14 SMPS_CTRL Register (Address = 144h) [reset = X]

SMPS_CTRL is shown in Figure 3-28 and described in Table 3-31.

Return to Summary Table.

SMPS control register.

RESET register domain: HWRST

Figure 3-28. SMPS_CTRL Register

7 6 5 4 3 2 1 0

RESERVED RESERVED SMPS1_SMPS

R-0h R-0h R-X R-0h R/W-0h

12_EN

Table 3-31. SMPS_CTRL Register Field Descriptions

Bit Field Type Reset Description

7-6 RESERVED R 0h

5 RESERVED R 0h

4 SMPS1_SMPS12_EN R X

3-2 RESERVED R 0h

1-0 SMPS12_PHASE_CTRL R/W 0h

Selection of the type of configuration of the SMPS12

0: SMPS1 single phase, SMPS2 single phase

1: SMPS12 dual phase

Selection of the phase mode of the SMPS12 (SMPS1 Single Phase

+ SMPS2 Single Phase configuration or SMPS12 Dual Phase

configuration)

00: Automatic Phase Selection per SMPS - Multi Phase or Single

Phase (default)

11: Automatic Phase Selection per SMPS - Multi Phase or Single

Phase

01: Force Single Phase mode (for SMPS1 and SMPS2)

10: Force Multi Phase mode (for SMPS1 and SMPS2) - Prohibited

under no-load condition

RESERVED SMPS12_PHASE_CTRL

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

37

Page 38

FUNC_SMPS Registers

www.ti.com

3.3.15 SMPS_PD_CTRL Register (Address = 145h) [reset = 5Bh]

SMPS_PD_CTRL is shown in Figure 3-29 and described in Table 3-32.

Return to Summary Table.

SMPS Pull-Down enable register.

RESET register domain: HWRST

Notes:

SMPS pull-down register bits validate the control of the active discharge of each power resource to full-fill

the turn-off timing requirements.

When a pull-down is not enabled, there is always a weak pull-down present at the output of the power

resource, so that the device restart correctly at the next power-up sequence.

Figure 3-29. SMPS_PD_CTRL Register

7 6 5 4 3 2 1 0

RESERVED SMPS5 RESERVED SMPS4 SMPS3 RESERVED SMPS2 SMPS1

R-0h R/W-1h R-0h R/W-1h R/W-1h R-0h R/W-1h R/W-1h

Table 3-32. SMPS_PD_CTRL Register Field Descriptions

Bit Field Type Reset Description

7 RESERVED R 0h

6 SMPS5 R/W 1h

5 RESERVED R 0h

4 SMPS4 R/W 1h

3 SMPS3 R/W 1h

2 RESERVED R 0h

1 SMPS2 R/W 1h

0 SMPS1 R/W 1h

0: Pull-down is disabled

1: Pull-down is enabled when SPMS5 is in OFF state (default)

0: Pull-down is disabled

1: Pull-down is enabled when SPMS4 is in OFF state (default)

0: Pull-down is disabled

1: Pull-down is enabled when SPMS3 is in OFF state (default)

0: Pull-down is disabled

1: Pull-down is enabled when SPMS2 is in OFF state (default)

0: Pull-down is disabled

1: Pull-down is enabled when SPMS1 is in OFF state (default)

38

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 39

www.ti.com

FUNC_SMPS Registers

3.3.16 SMPS_THERMAL_EN Register (Address = 147h) [reset = FFh]

SMPS_THERMAL_EN is shown in Figure 3-30 and described in Table 3-33.

Return to Summary Table.

SMPS Thermal feature enable register.

RESET register domain: HWRST

Figure 3-30. SMPS_THERMAL_EN Register

7 6 5 4 3 2 1 0

RESERVED SMPS5 RES

R-1h R/W-1h R-1h R-1h R/W-1h R-1h R-1h R/W-1h

Table 3-33. SMPS_THERMAL_EN Register Field Descriptions

Bit Field Type Reset Description

7 RESERVED R 1h

6 SMPS5 R/W 1h

5 RESERVED R 1h

4 RESERVED R 1h

3 SMPS3 R/W 1h

2 RESERVED R 1h

1 RESERVED R 1h

0 SMPS12 R/W 1h

RESERVED SMPS3 RESERVED RESERVED SMPS12

ERV

ED

0: SMPS5 Thermal feature is not enabled

1: SMPS5 Thermal feature is enabled (default)

0: SMPS3 Thermal feature is not enabled

1: SMPS3 Thermal feature is enabled (default)

0: SMPS12 Thermal feature is not enabled

1: SMPS12 Thermal feature is enabled (default)

Note: A unique Thermal Sensor is protecting SMPS1 and SMPS2

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

39

Page 40

FUNC_SMPS Registers

www.ti.com

3.3.17 SMPS_THERMAL_STATUS Register (Address = 148h) [reset = 0h]

SMPS_THERMAL_STATUS is shown in Figure 3-31 and described in Table 3-34.

Return to Summary Table.

SMPS Thermal status register.

RESET register domain: POR

Figure 3-31. SMPS_THERMAL_STATUS Register

7 6 5 4 3 2 1 0

RESERVED SMPS5 RESERVED RESERVED SMPS3 RESERVED RESERVED SMPS12

R-0h R-0h R-0h R-0h R-0h R-0h R-0h R-0h

Table 3-34. SMPS_THERMAL_STATUS Register Field Descriptions

Bit Field Type Reset Description

7 RESERVED R 0h

6 SMPS5 R 0h

5 RESERVED R 0h

4 RESERVED R 0h

3 SMPS3 R 0h

2 RESERVED R 0h

1 RESERVED R 0h

0 SMPS12 R 0h

0: SMPS5 Thermal measurement is below the limit (SMPS is

functional)

1: SMPS5 Thermal measurement is over the limit (see specification)

0: SMPS3 Thermal measurement is below the limit (SMPS is

functional)

1: SMPS3 Thermal measurement is over the limit (see specification)

0: SMPS12 Thermal measurement is below the limit (SMPS is

functional)

1: SMPS12 Thermal measurement is over the limit (see

specification)

40

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 41

www.ti.com

FUNC_SMPS Registers

3.3.18 SMPS_SHORT_STATUS Register (Address = 149h) [reset = 0h]

SMPS_SHORT_STATUS is shown in Figure 3-32 and described in Table 3-35.

Return to Summary Table.

SMPS Short circuit status.

RESET register domain: POR

Figure 3-32. SMPS_SHORT_STATUS Register

7 6 5 4 3 2 1 0

RESERVED SMPS5 RESERVED SMPS4 SMPS3 RESERVED SMPS2 SMPS1

R-0h R-0h R-0h R-0h R-0h R-0h R-0h R-0h

Table 3-35. SMPS_SHORT_STATUS Register Field Descriptions

Bit Field Type Reset Description

7 RESERVED R 0h

6 SMPS5 R 0h

5 RESERVED R 0h

4 SMPS4 R 0h

3 SMPS3 R 0h

2 RESERVED R 0h

1 SMPS2 R 0h

0 SMPS1 R 0h

0: SMPS5 is functional . No short detected (default)

1: SMPS5 output is shorted

0: SMPS4 is functional . No short detected (default)

1: SMPS4 output is shorted

0: SMPS3 is functional . No short detected (default)

1: SMPS3 output is shorted

0: SMPS2 is functional . No short detected (default)

1: SMPS2 output is shorted

Note: This bit is un-relevant when SMPS12 is in Dual phase mode

0: SMPS1 (or SMPS12 in Dual phase mode) is functional . No short

detected (default)

1: SMPS1 (or SMPS12 in Dual phase mode) output is shorted

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

41

Page 42

FUNC_SMPS Registers

www.ti.com

3.3.19 SMPS_NEGATIVE_CURRENT_LIMIT_EN Register (Address = 14Ah) [reset = FFh]

SMPS_NEGATIVE_CURRENT_LIMIT_EN is shown in Figure 3-33 and described in Table 3-36.

Return to Summary Table.

Iload Negative Current Comparator enable register (Negative Current measurement).

RESET register domain: HWRST

Figure 3-33. SMPS_NEGATIVE_CURRENT_LIMIT_EN Register

7 6 5 4 3 2 1 0

RESERVED SMPS5 RESERVED SMPS4 SMPS3 RESERVED SMPS2 SMPS1

R-1h R/W-1h R-1h R/W-1h R/W-1h R-1h R/W-1h R/W-1h

Table 3-36. SMPS_NEGATIVE_CURRENT_LIMIT_EN Register Field Descriptions

Bit Field Type Reset Description

7 RESERVED R 1h

6 SMPS5 R/W 1h

5 RESERVED R 1h

4 SMPS4 R/W 1h

3 SMPS3 R/W 1h

2 RESERVED R 1h

1 SMPS2 R/W 1h

0 SMPS1 R/W 1h

0: SMPS5 Negative Current comparator for measurement is not

enabled

1: SMPS5 Negative Current comparator for measurement is enabled

(default)

0: SMPS4 Negative Current comparator for measurement is not

enabled

1: SMPS4 Negative Current comparator for measurement is enabled

(default)

0: SMPS3 Negative Current comparator for measurement is not

enabled

1: SMPS3 Negative Current comparator for measurement is enabled

(default)

0: SMPS2 Negative Current comparator for measurement is not

enabled

1: SMPS2 Negative Current comparator for measurement is enabled

(default)

0: SMPS1 Negative Current comparator for measurement is not

enabled

1: SMPS1 Negative Current comparator for measurement is enabled

(default)

42

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 43

www.ti.com

FUNC_SMPS Registers

3.3.20 SMPS_POWERGOOD_MASK1 Register (Address = 14Bh) [reset = 5Ah]

SMPS_POWERGOOD_MASK1 is shown in Figure 3-34 and described in Table 3-37.

Return to Summary Table.

SMPS Power Good (POWERGOOD) mask #1

RESET register domain: POR

Figure 3-34. SMPS_POWERGOOD_MASK1 Register

7 6 5 4 3 2 1 0

RESERVED SMPS5 RESERVED SMPS4 SMPS3 RESERVED SMPS2 SMPS1

R-0h R/W-1h R-0h R/W-1h R/W-1h R-0h R/W-1h R/W-0h

Table 3-37. SMPS_POWERGOOD_MASK1 Register Field Descriptions

Bit Field Type Reset Description

7 RESERVED R 0h

6 SMPS5 R/W 1h

5 RESERVED R 0h

4 SMPS4 R/W 1h

3 SMPS3 R/W 1h

2 RESERVED R 0h

1 SMPS2 R/W 1h

0 SMPS1 R/W 0h

SMPS5 POWERGOOD Mask bit register

0: SMPS5 line is enabled. The SMPS5 state is generated on

POWERGOOD line

1: SMPS5 line is masked. No SMPS5 state is generated on

POWERGOOD line (default)

SMPS4 POWERGOOD Mask bit register

0: SMPS4 line is enabled. The SMPS4 state is generated on

POWERGOOD line

1: SMPS4 line is masked. No SMPS4 state is generated on

POWERGOOD line (default)

SMPS3 POWERGOOD Mask bit register

0: SMPS3 line is enabled. The SMPS3 state is generated on

POWERGOOD line

1: SMPS3 line is masked. No SMPS3 state is generated on

POWERGOOD line (default)

SMPS2 POWERGOOD Mask bit register

0: SMPS2 line is enabled. The SMPS2 state is generated on

POWERGOOD line

1: SMPS2 line is masked. No SMPS2 state is generated on

POWERGOOD line (default)

SMPS1 POWERGOOD Mask bit register

0: SMPS1 line is enabled. The SMPS1 state is generated on

POWERGOOD line (default)

1: SMPS1 line is masked. No SMPS1 state is generated on

POWERGOOD line

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

43

Page 44

FUNC_SMPS Registers

3.3.21 SMPS_POWERGOOD_MASK2 Register (Address = 14Ch) [reset = 10h]

SMPS_POWERGOOD_MASK2 is shown in Figure 3-35 and described in Table 3-38.

Return to Summary Table.

SMPS Power Good (POWERGOOD) mask #2

RESET register domain: POR (excepted POWERGOOD_TYPE_SELECT which is under HWRST)

Figure 3-35. SMPS_POWERGOOD_MASK2 Register

7 6 5 4 3 2 1 0

POWERGOOD

_TYPE_SELEC

T

R/W-0h R-0h R/W-1h R-0h R-0h R-0h R-0h

Bit Field Type Reset Description

7 POWERGOOD_TYPE_S

ELECT

6-5 RESERVED R 0h

4 OVC_ALARM R/W 1h

3 RESERVED R 0h

2 RESERVED R 0h

1 RESERVED R 0h

0 RESERVED R 0h

RESERVED OVC_ALARM RESERVED RESERVED RESERVED RESERVED

Table 3-38. SMPS_POWERGOOD_MASK2 Register Field Descriptions

R/W 0h

Selection of the POWERGOOD type of monitoring

0: Voltage monitoring (above threshold)) AND Current monitoring

(over current) (default)

1: Current monitoring only (over current)

OVC_ALARM Mask bit register

0: OVC_ALARM line is enabled. The OVC_ALARM state is

generated on POWERGOOD line

1: OVC_ALARM line is masked. No OVC_ALARM state is generated

on POWERGOOD line (default)

www.ti.com

44

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 45

www.ti.com

FUNC_SMPS Registers

3.3.22 SMPS_PLL_CTRL Register (Address = 14Dh) [reset = 0h]

SMPS_PLL_CTRL is shown in Figure 3-36 and described in Table 3-39.

Return to Summary Table.

SMPS PLL control register.

RESET register domain: HWRST

Figure 3-36. SMPS_PLL_CTRL Register

7 6 5 4 3 2 1 0

RESERVED PLL_EN_BYPASSPLL_BYPASS_

R-0h R/W-0h R/W-0h R-0h R-0h

Table 3-39. SMPS_PLL_CTRL Register Field Descriptions

Bit Field Type Reset Description

7-4 RESERVED R 0h

3 PLL_EN_BYPASS R/W 0h

2 PLL_BYPASS_CLK R/W 0h

1 RESERVED R 0h

0 RESERVED R 0h

Enable/disable the bypass mode

0: No Bypass (default)

1: Bypass is enabled

Allow to bypass the 6x frequency clock

0: No Bypass (default)

1: Bypass is enabled

CLK

RESERVED RESERVED

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

45

Page 46

FUNC_LDO Registers

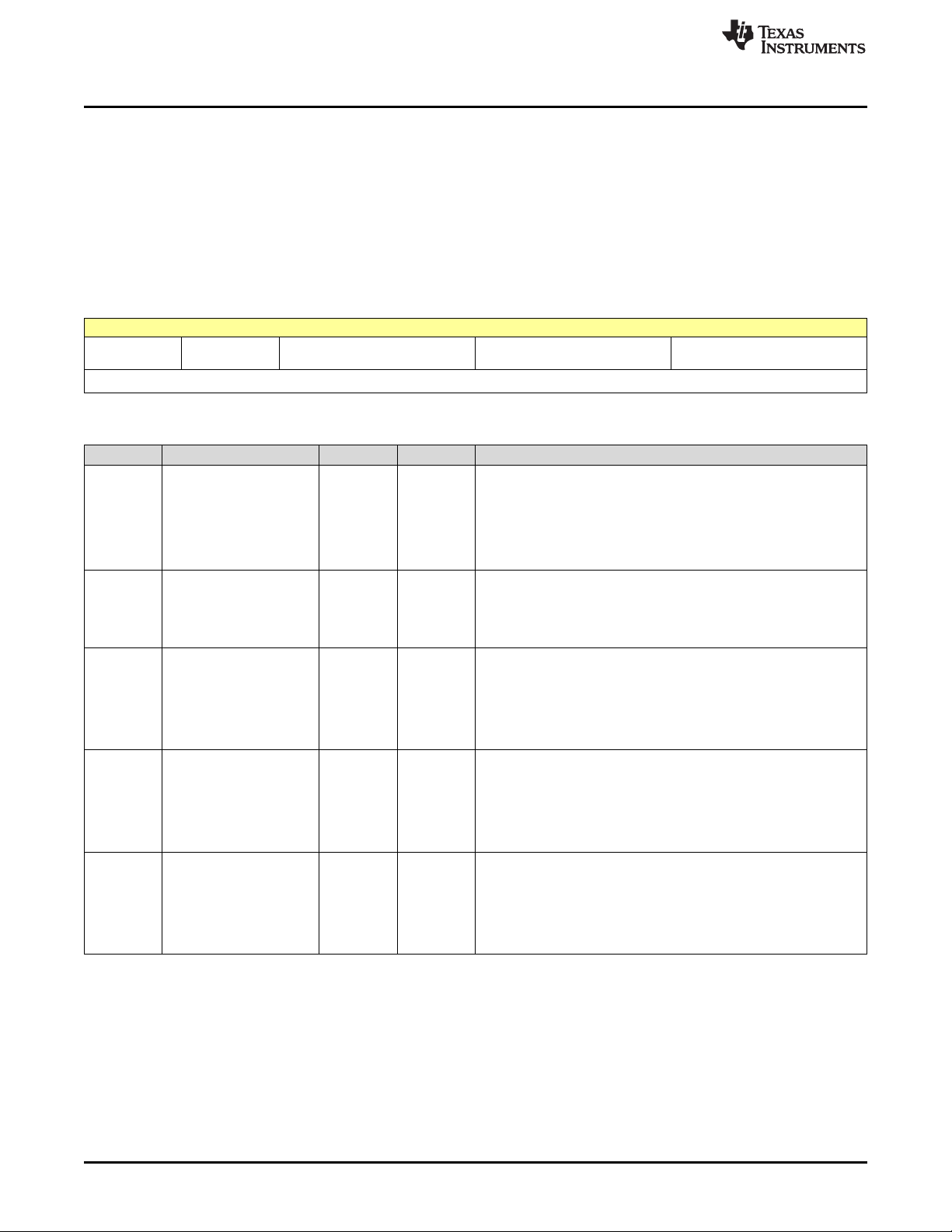

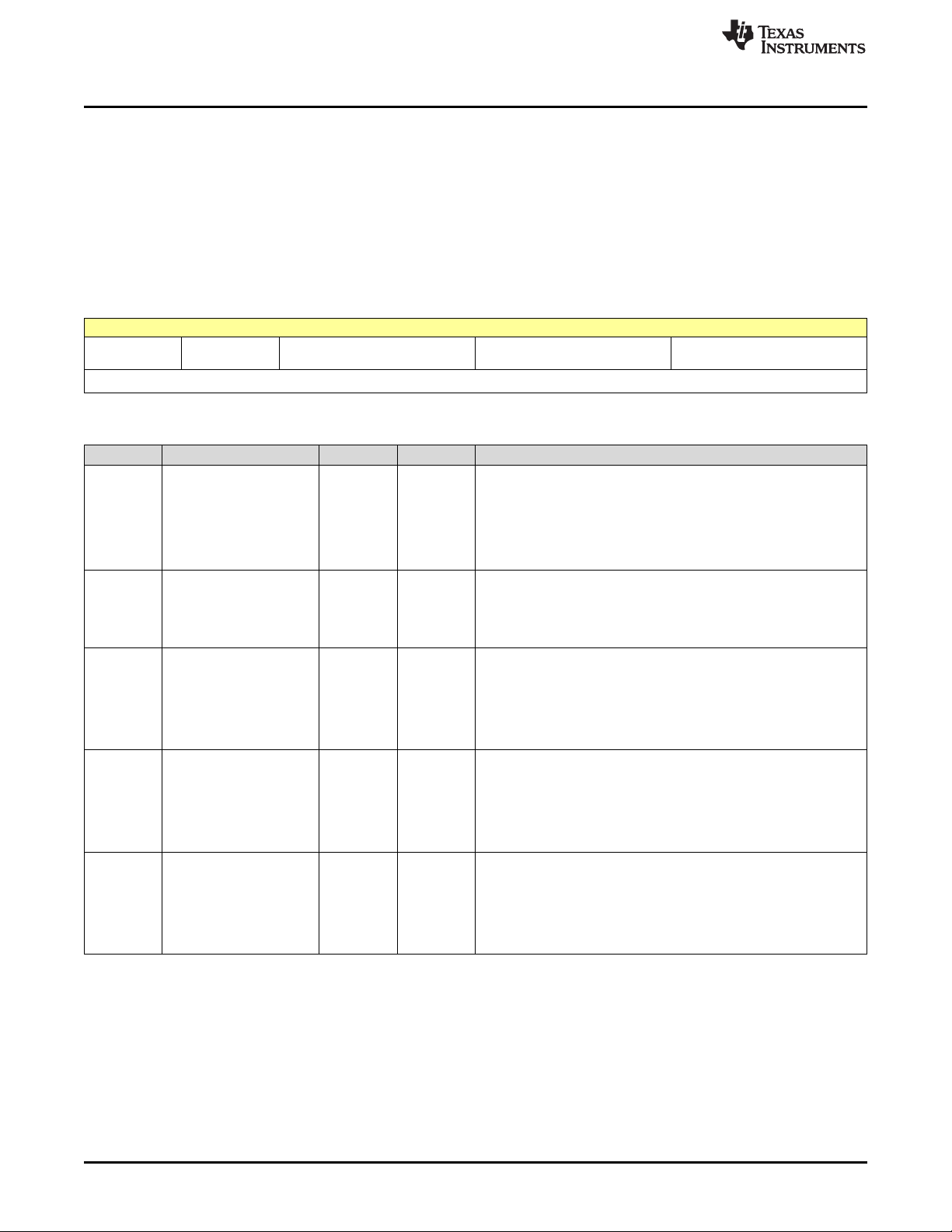

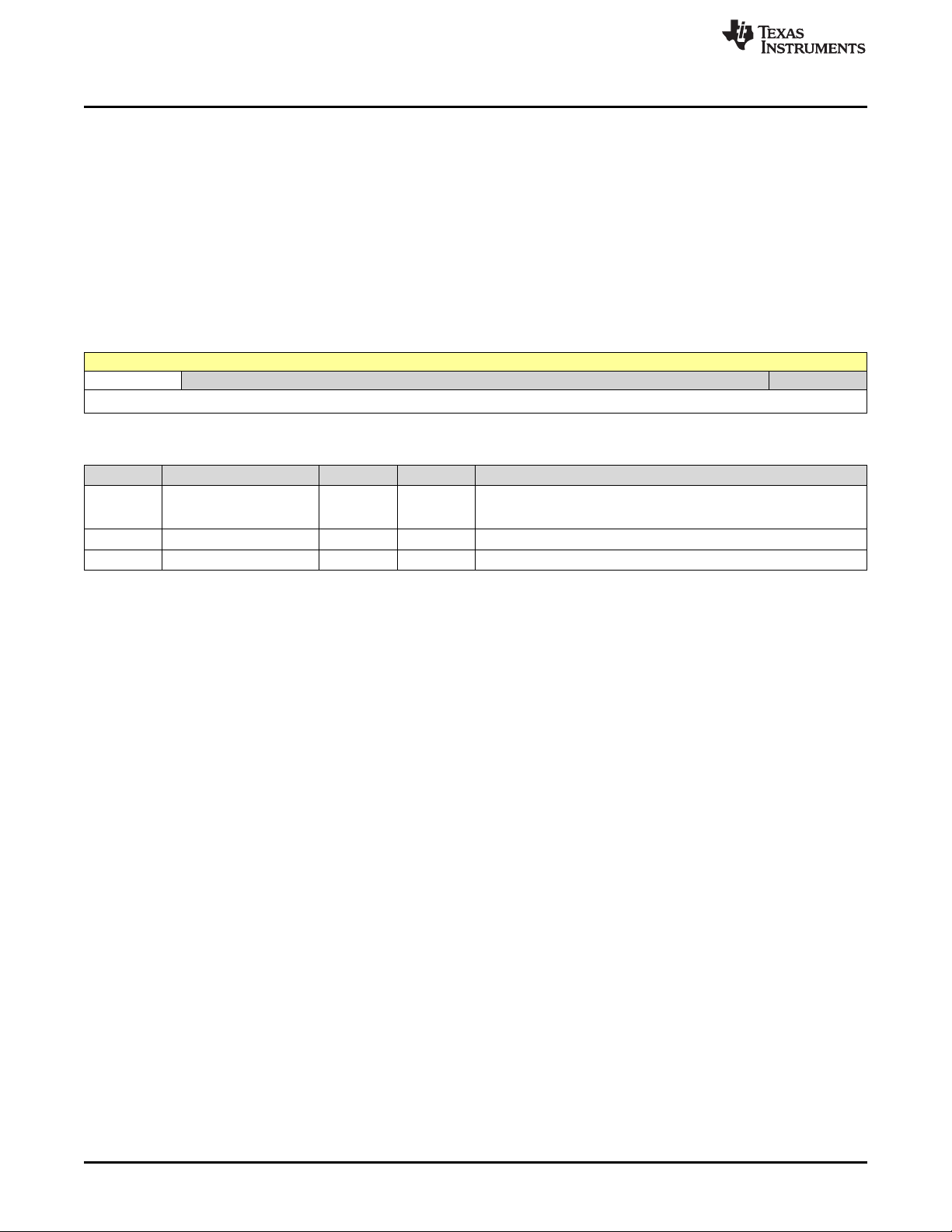

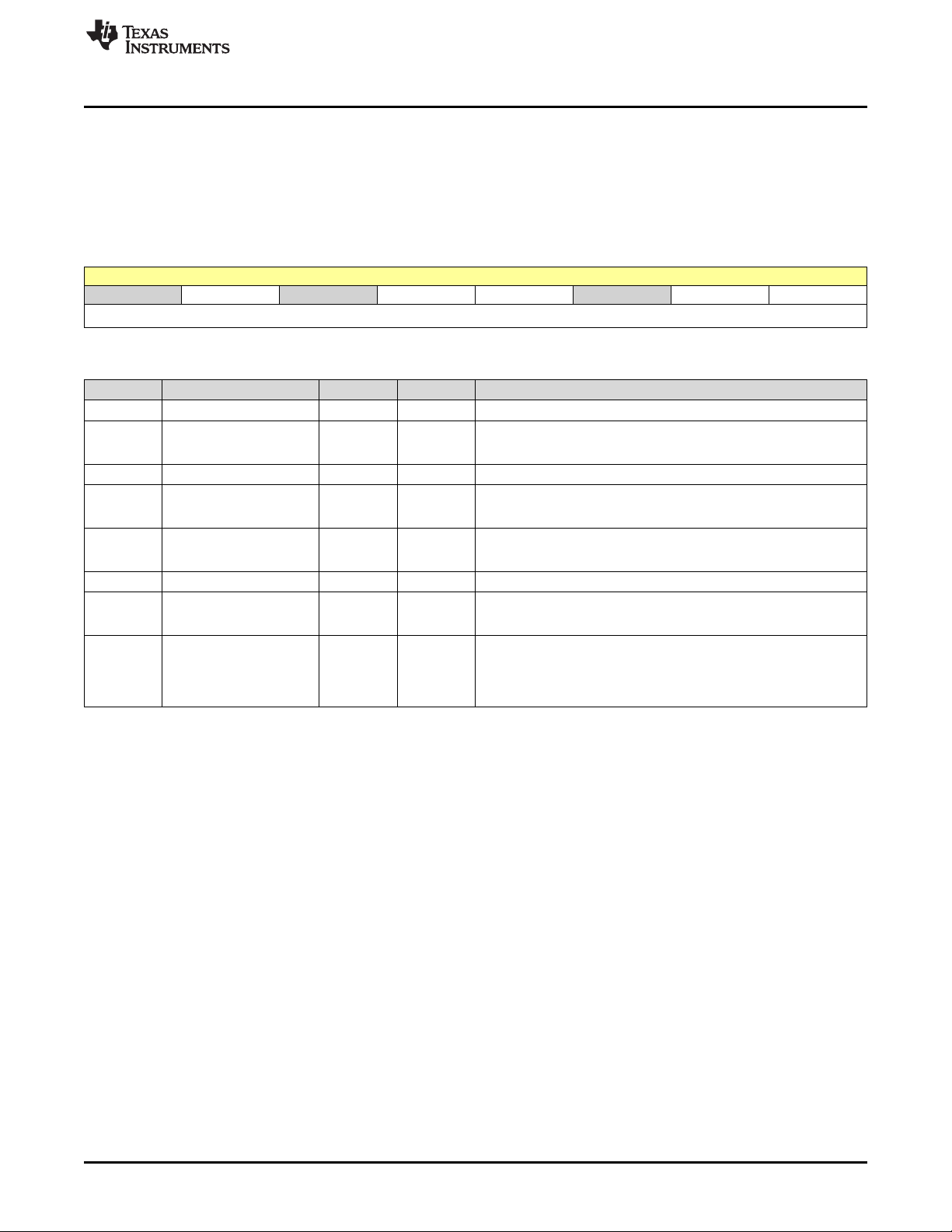

3.4 FUNC_LDO Registers

Table 3-40 lists the memory-mapped registers for the FUNC_LDO. All register offset addresses not listed

in Table 3-40 should be considered as reserved locations and the register contents should not be

modified.

Table 3-40. FUNC_LDO Registers

Address Acronym Register Name Section

150h LDO1_CTRL LDO1 control register

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

151h LDO1_VOLTAGE LDO1 Voltage selection (OTP_Config)

RESET register domain: SWORST

152h LDO2_CTRL LDO2 control register

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

153h LDO2_VOLTAGE LDO2 Voltage selection (OTP_Config)

RESET register domain: SWORST

154h LDO3_CTRL LDO3 control register

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

MODE_SLEEP is used when

NSLEEP/ENABLE1/ENABL2 signals select the resource.

MODE_ACTIVE is used when none of

NSLEEP/ENABLE1/ENABL2 signals select the resource.

155h LDO3_VOLTAGE LDO3 Voltage selection (OTP_Config)

RESET register domain: SWORST

15Eh LDO4_CTRL LDO4 control register

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

15Fh LDO4_VOLTAGE LDO4 Voltage selection (OTP_Config)

RESET register domain: SWORST

162h LDO5_CTRL LDO5 control register

RESET register domain: HWRST (MODE_ACTIVE and

MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP,

ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP,

ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the

Data Manual for details).

163h LDO5_VOLTAGE LDO5 Voltage selection (OTP_Config)

RESET register domain: SWORST

Section 3.4.1

Section 3.4.2

Section 3.4.3

Section 3.4.4

Section 3.4.5

Section 3.4.6

Section 3.4.7

Section 3.4.8

Section 3.4.9

Section 3.4.10

www.ti.com

46

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 47

www.ti.com

FUNC_LDO Registers

Table 3-40. FUNC_LDO Registers (continued)

Address Acronym Register Name Section

16Bh LDO_PD_CTRL1 LDO Pull-Down enable register #1

RESET register domain: HWRST

NOTES:

LDO pull-down enable register bits validate the control of

the active discharge of each power resource to fulfill the

turn-off timing requirements.

When a pull-down is not enabled, there is always a weak

pull-down present at the output of the power resource,

so that the device restarts correctly at the next power-up

sequence.

16Ch LDO_PD_CTRL2 LDO Pull-Down enable register #2

RESET register domain: HWRST

NOTES:

LDO pull-down enable register bits validate the control of

the active discharge of each power resource to fulfill the

turn-off timing requirements.

When a pull-down is not enabled, there is always a weak

pull-down present at the output of the power resource,

so that the device restarts correctly at the next power-up

sequence.

16Dh LDO_SHORT_STATUS1 LDO Short circuit status register #1

At Power-On, LDO short input informations are masked

during 1 ms.

This 1 ms masking is activated and re-started each time

one LDO is enabled.

RESET register domain: POR

16Eh LDO_SHORT_STATUS2 LDO short circuit status register #2

RESET register domain: POR

17Dh LDO_PD_CTRL3 LDO Pull-Down enable register #3

RESET register domain: HWRST

NOTES:

LDO pull-down enable register bits validate the control of

the active discharge of each power resource to fulfill the

turn-off timing requirements.

When a pull-down is not enabled, there is always a weak

pull-down present at the output of the power resource,

so that the device restarts correctly at the next power-up

sequence.

17Eh LDO_SHORT_STATUS3 LDO short circuit status register #3

RESET register domain: POR

Section 3.4.11

Section 3.4.12

Section 3.4.13

Section 3.4.14

Section 3.4.15

Section 3.4.16

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

47

Page 48

FUNC_LDO Registers

3.4.1 LDO1_CTRL Register (Address = 150h) [reset = 0h]

LDO1_CTRL is shown in Figure 3-37 and described in Table 3-41.

Return to Summary Table.

LDO1 control register

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP, ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP, ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the Data Manual for details).

Figure 3-37. LDO1_CTRL Register

7 6 5 4 3 2 1 0

WR_S LDO_BYPASS

_EN

R/W-0h R/W-0h R-0h R-0h R-0h R/W-0h R-0h R/W-0h

Bit Field Type Reset Description

7 WR_S R/W 0h

6 LDO_BYPASS_EN R/W 0h

5 RESERVED R 0h

4 STATUS R 0h

3 RESERVED R 0h

2 MODE_SLEEP R/W 0h

1 RESERVED R 0h

0 MODE_ACTIVE R/W 0h

RESERVED STATUS RESERVED MODE_SLEEP RESERVED MODE_ACTIV

Table 3-41. LDO1_CTRL Register Field Descriptions

Warm reset sensitivity

0: Re-load the default LDO1_VOLTAGE register value during Warm

Reset

1: Maintain current voltage during Warm Reset (no voltage change)

LDO1 bypass enable

0: LDO1 is configured as a standard power resource (default)

1: LDO1 is configured as a bypass LDO (bypass enabled)

LDO1 Status

0: OFF

1: ON

LDO1 SLEEP Mode

0: OFF

1: ON

LDO1 ACTIVE Mode

0: OFF

1: ON

This bit can be updated by power-up sequencer

www.ti.com

E

48

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 49

www.ti.com

3.4.2 LDO1_VOLTAGE Register (Address = 151h) [reset = X]

LDO1_VOLTAGE is shown in Figure 3-38 and described in Table 3-42.

Return to Summary Table.

LDO1 Voltage selection (OTP_Config)

RESET register domain: SWORST

Figure 3-38. LDO1_VOLTAGE Register

7 6 5 4 3 2 1 0

RESERVED VSEL

R-0h R/W-X

Table 3-42. LDO1_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7-6 RESERVED R 0h

5-0 VSEL R/W X

VSEL[5:0] cross table voltage (OFF,0.9V to 3.3V)

000000 0V 100000 2,45V

000001 0,9V 100001 2,5V

000010 0,95V 100010 2,55V

000011 1V 100011 2,6V

000100 1,05V 100100 2,65V

000101 1,1V 100101 2,7V

000110 1,15V 100110 2,75V

000111 1,2V 100111 2,8V

001000 1,25V 101000 2,85V

001001 1,3V 101001 2,9V

001010 1,35V 101010 2,95V

001011 1,4V 101011 3V

001100 1,45V 101100 3,05V

001101 1,5V 101101 3,1V

001110 1,55V 101110 3,15V

001111 1,6V 101111 3,2V

010000 1,65V 110000 3,25V

010001 1,7V 110001 3,3V

010010 1,75V 110010 3,3V

010011 1,8V 110011 3,3V

010100 1,85V 110100 3,3V

010101 1,9V 110101 3,3V

010110 1,95V 110110 3,3V

010111 2V 110111 3,3V

011000 2,05V 111000 3,3V

011001 2,1V 111001 3,3V

011010 2,15V 111010 3,3V

011011 2,2V 111011 3,3V

011100 2,25V 111100 3,3V

011101 2,3V 111101 3,3V

011110 2,35V 111110 3,3V

011111 2,4V 111111 3,3V

FUNC_LDO Registers

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

49

Page 50

FUNC_LDO Registers

3.4.3 LDO2_CTRL Register (Address = 152h) [reset = 0h]

LDO2_CTRL is shown in Figure 3-39 and described in Table 3-43.

Return to Summary Table.

LDO2 control register

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP, ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP, ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the Data Manual for details).

Figure 3-39. LDO2_CTRL Register

7 6 5 4 3 2 1 0

WR_S LDO_BYPASS

_EN

R/W-0h R/W-0h R-0h R-0h R-0h R/W-0h R-0h R/W-0h

Bit Field Type Reset Description

7 WR_S R/W 0h

6 LDO_BYPASS_EN R/W 0h

5 RESERVED R 0h

4 STATUS R 0h

3 RESERVED R 0h

2 MODE_SLEEP R/W 0h

1 RESERVED R 0h

0 MODE_ACTIVE R/W 0h

RESERVED STATUS RESERVED MODE_SLEEP RESERVED MODE_ACTIV

Table 3-43. LDO2_CTRL Register Field Descriptions

Warm reset sensitivity

0: Re-load the default LDO2_VOLTAGE register value during Warm

Reset

1: Maintain current voltage during Warm Reset (no voltage change)

LDO2 bypass enable

0: LDO2 is configured as a standard power resource (default)

1: LDO2 is configured as a bypass LDO (bypass enabled)

LDO2 Status

0: OFF

1: ON

LDO2 SLEEP Mode

0: OFF

1: ON

LDO2 ACTIVE Mode

0: OFF

1: ON

www.ti.com

E

50

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 51

www.ti.com

3.4.4 LDO2_VOLTAGE Register (Address = 153h) [reset = X]

LDO2_VOLTAGE is shown in Figure 3-40 and described in Table 3-44.

Return to Summary Table.

LDO2 Voltage selection (OTP_Config)

RESET register domain: SWORST

Figure 3-40. LDO2_VOLTAGE Register

7 6 5 4 3 2 1 0

RESERVED VSEL

R-0h R/W-X

Table 3-44. LDO2_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7-6 RESERVED R 0h

5-0 VSEL R/W X

See VSEL cross table showed in LDO1_VOLTAGE.VSEL register.

FUNC_LDO Registers

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

51

Page 52

FUNC_LDO Registers

3.4.5 LDO3_CTRL Register (Address = 154h) [reset = 0h]

LDO3_CTRL is shown in Figure 3-41 and described in Table 3-45.

Return to Summary Table.

LDO3 control register

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

MODE_SLEEP is used when NSLEEP/ENABLE1/ENABL2 signals select the resource. MODE_ACTIVE is

used when none of NSLEEP/ENABLE1/ENABL2 signals select the resource.

Figure 3-41. LDO3_CTRL Register

7 6 5 4 3 2 1 0

WR_S RESERVED STATUS RESERVED MODE_SLEEP RESERVED MODE_ACTIV

R/W-0h R-0h R-0h R-0h R/W-0h R-0h R/W-0h

Table 3-45. LDO3_CTRL Register Field Descriptions

Bit Field Type Reset Description

7 WR_S R/W 0h

6-5 RESERVED R 0h

4 STATUS R 0h

3 RESERVED R 0h

2 MODE_SLEEP R/W 0h

1 RESERVED R 0h

0 MODE_ACTIVE R/W 0h

Warm reset sensitivity

0: Re-load the default LDO3_VOLTAGE register value during Warm

Reset

1: Maintain current voltage during Warm Reset (no voltage change)

LDO3 Status

0: OFF

1: ON

LDO3 SLEEP Mode

0: OFF

1: ON

LDO3 ACTIVE Mode

0: OFF

1: ON

www.ti.com

E

52

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 53

www.ti.com

3.4.6 LDO3_VOLTAGE Register (Address = 155h) [reset = X]

LDO3_VOLTAGE is shown in Figure 3-42 and described in Table 3-46.

Return to Summary Table.

LDO3 Voltage selection (OTP_Config)

RESET register domain: SWORST

Figure 3-42. LDO3_VOLTAGE Register

7 6 5 4 3 2 1 0

RESERVED VSEL

R-0h R/W-X

Table 3-46. LDO3_VOLTAGE Register Field Descriptions

Bit Field Type Reset Description

7-6 RESERVED R 0h

5-0 VSEL R/W X

See VSEL cross table showed in LDO1_VOLTAGE.VSEL register.

FUNC_LDO Registers

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Copyright © 2015–2017, Texas Instruments Incorporated

Register Descriptions

53

Page 54

FUNC_LDO Registers

3.4.7 LDO4_CTRL Register (Address = 15Eh) [reset = 0h]

LDO4_CTRL is shown in Figure 3-43 and described in Table 3-47.

Return to Summary Table.

LDO4 control register

RESET register domain: HWRST (MODE_ACTIVE and MODE_SLEEP are in SWORST domain)

Notes: MODE_SLEEP is used when NSLEEP, ENABLE1, ENABLE2 signals select the resource.

MODE_ACTIVE is used when none of NSLEEP, ENABLE1, ENABLE2 signals select resource (see

Resources SLEEP/ACTIVE assignments table in the Data Manual for details).

Figure 3-43. LDO4_CTRL Register

7 6 5 4 3 2 1 0

WR_S RESERVED RESERVED STATUS RESERVED MODE_SLEEP RESERVED MODE_ACTIV

R/W-0h R/W-0h R-0h R-0h R-0h R/W-0h R-0h R/W-0h

Table 3-47. LDO4_CTRL Register Field Descriptions

Bit Field Type Reset Description

7 WR_S R/W 0h

6 RESERVED R/W 0h

5 RESERVED R 0h

4 STATUS R 0h

3 RESERVED R 0h

2 MODE_SLEEP R/W 0h

1 RESERVED R 0h

0 MODE_ACTIVE R/W 0h

Warm reset sensitivity

0: Re-load the default LDO8_VOLTAGE register value during Warm

Reset

1: Maintain current voltage during Warm Reset (no voltage change)

LDO4 Status

0: OFF

1: ON

LDO4 SLEEP Mode

0: OFF

1: ON

LDO4 ACTIVE Mode

0: OFF

1: ON

www.ti.com

E

54

Register Descriptions

Copyright © 2015–2017, Texas Instruments Incorporated

SLVUAH1C–June 2015–Revised April 2017

Submit Documentation Feedback

Page 55

www.ti.com

3.4.8 LDO4_VOLTAGE Register (Address = 15Fh) [reset = X]

LDO4_VOLTAGE is shown in Figure 3-44 and described in Table 3-48.

Return to Summary Table.

LDO4 Voltage selection (OTP_Config)