Page 1

TPIC5203

2-CHANNEL INDEPENDENT GATE-PROTECTED

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

• Low r

DS(on)

• High Voltage Output...60 V

•Extended ESD Capability...4000 V

• Pulsed Current...8 A Per Channel

• Fast Commutation Speed

. . . 0.26 Ω Typ

GND

SOURCE1

GATE2

DRAIN2

D PACKAGE

(TOP VIEW)

1

2

3

4

8

7

6

5

DRAIN1

GATE1

SOURCE2

NC

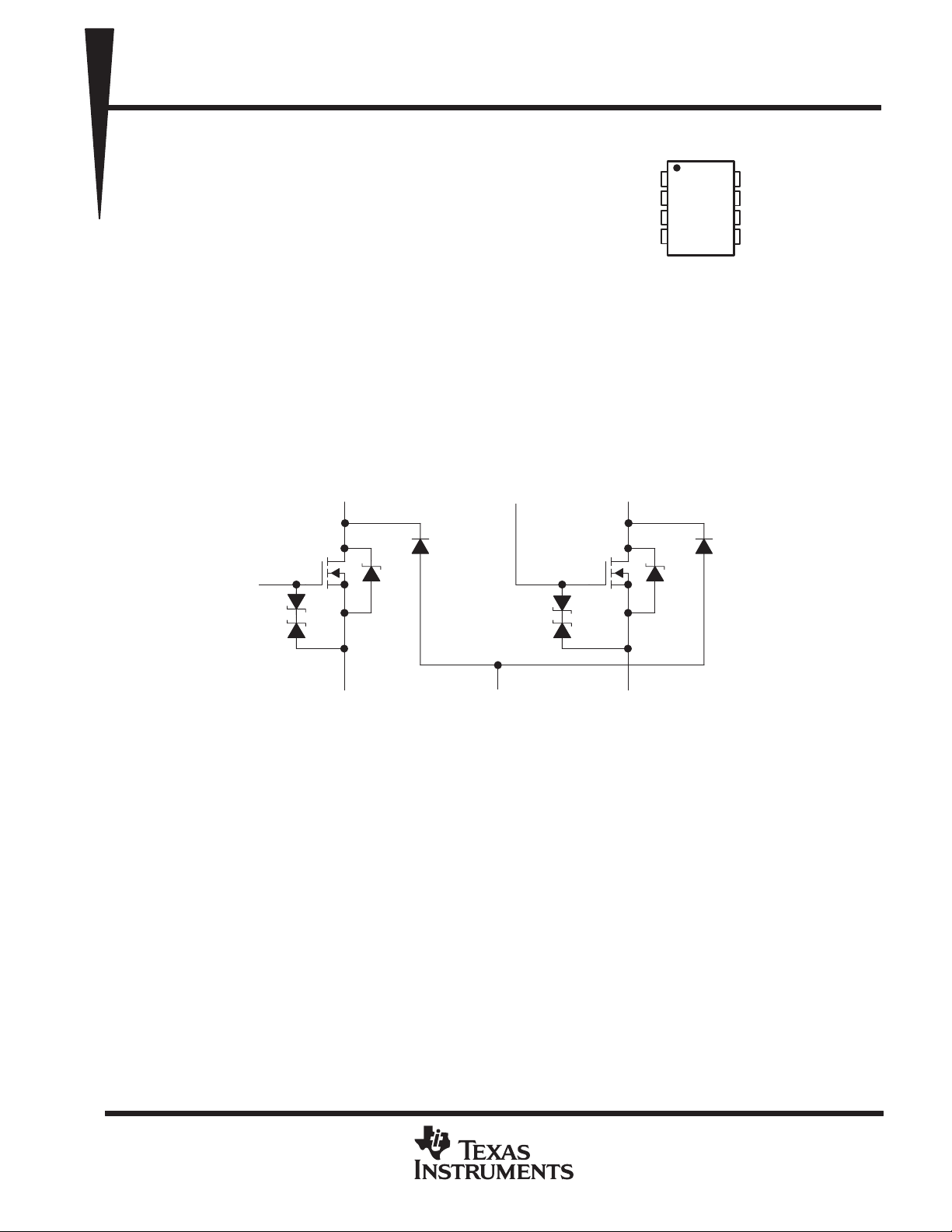

description

NC – No internal connection

The TPIC5203 is a monolithic gate-protected

power DMOS array that consists of two

independent electrically isolated N-channel enhancement-mode DMOS transistors. Each transistor features

integrated high-current zener diodes (Z

CXa

and Z

) to prevent gate damage in the event that an overstress

CXb

condition occurs. These zener diodes also provide up to 4000 V of ESD protection when tested using the

human-body model of a 100-pF capacitor in series with a 1.5-kΩ resistor.

The TPIC5203 is offered in a standard eight-pin small-outline surface-mount (D) package and is characterized

for operation over the case temperature range of –40°C to 125°C.

schematic

GATE1

Z

Z

7

C1b

C1a

DRAIN1

Q1

8

D1

Z1

GATE2

Z

Z

3

C2b

C2a

DRAIN2

Q2

4

D2

Z2

2

SOURCE1

NOTE: For correct operation, no terminal pin may be taken below GND.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

1 6

GND

SOURCE2

Copyright 1994, Texas Instruments Incorporated

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

2–1

Page 2

TPIC5203

2-CHANNEL INDEPENDENT GATE-PROTECTED

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

absolute maximum ratings over operating case temperature range (unless otherwise noted)

Drain-to-source voltage, V

60 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DS

†

Source-to-GND voltage (Q1, Q2) 100 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Drain-to-GND voltage (Q1, Q2) 100 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Gate-to-source voltage range, V

Continuous drain current, each output, T

Continuous source-to-drain diode current, T

Pulsed drain current, each output, I

Continuous gate-to-source zener diode current, T

Pulsed gate-to-source zener-diode current, T

Single-pulse avalanche energy, E

Continuous total dissipation, T

Operating virtual junction temperature range, T

Operating case temperature range, T

Storage temperature range, T

–9 V to 18 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

GS

max

AS

= 25°C (see Figure 15) 962 mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

= 25°C 1.6 A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C

= 25°C 1.6 A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C

, TC = 25°C (see Note 1 and Figure 15) 8 A. . . . . . . . . . . . . . . . . . . . .

= 25°C ±50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C

= 25°C ±500 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C

, TC = 25°C (see Figures 4, 15, and 16) 21.6 mJ. . . . . . . . . . . . . . . . . . .

–40°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

–40°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C

J

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Pulse duration = 10 ms, duty cycle = 2%

2–2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 3

2-CHANNEL INDEPENDENT GATE-PROTECTED

I

Zero-gate-voltage drain current

DS

,

A

I

Leakage current, drain-to-GND

V

V

A

r

Static drain-to-source on-state resistance

D

,

Ω

F

trrReverse-recovery time

ns

V

g

di/dt

100 A/

QRRTotal diode charge

See Figures 1 and 14

nC

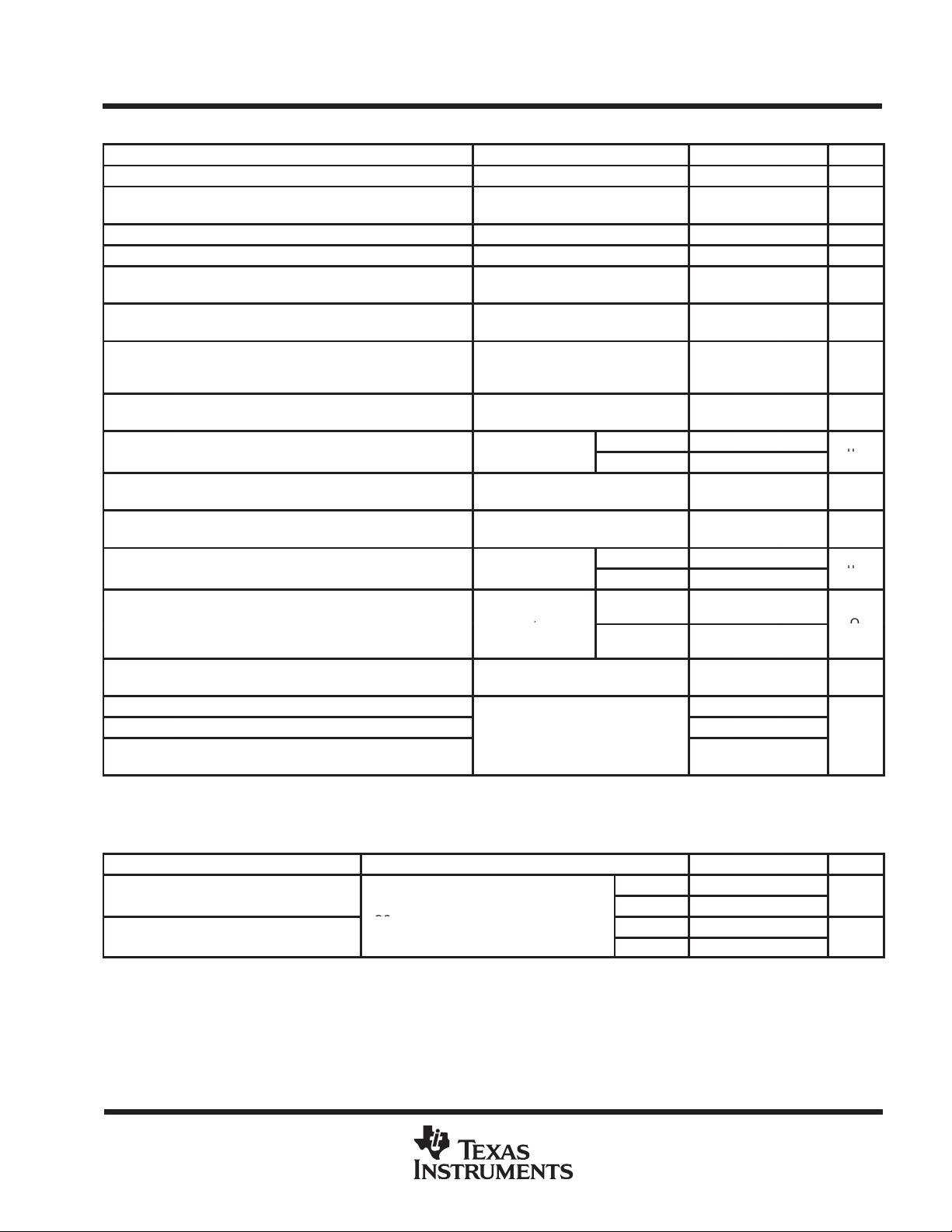

electrical characteristics, TC = 25°C (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

(BR)DSX

V

GS(th)

V

(BR)GS

V

(BR)SG

V

(BR)

V

DS(on)

V

F(SD)

V

F

DSS

I

GSSF

I

GSSR

lkg

DS(on)

g

fs

C

iss

C

oss

C

rss

NOTES: 2. Technique should limit TJ – TC to 10°C maximum.

Drain-to-source breakdown voltage ID = 250 µA, VGS = 0 60 V

Gate-to-source threshold voltage

Gate-to-source breakdown voltage IGS = 250 µA 18 V

Source-to-gate breakdown voltage ISG = 250 µA 9 V

Reverse drain-to-GND breakdown voltage (across

D1, D2)

Drain-to-source on-state voltage

Forward on-state voltage, source-to-drain

Forward on-state voltage, GND-to-drain

Forward-gate current, drain short circuited to

source

Reverse-gate current, drain short circuited to

source

Forward transconductance

Short-circuit input capacitance, common source 150 275

Short-circuit output capacitance, common source

Short-circuit reverse transfer capacitance, common

source

3. These parameters are measured with voltage-sensing contacts separate from the current-carrying contacts.

ID = 1 mA,

See Figure 5

Drain-to-GND current = 250 µA 100 V

ID = 1.6 A,

See Notes 2 and 3

IS = 1.6 A,

VGS = 0 (Z1, Z2),

See Notes 2 and 3 and Figure 12

ID = 1.6 A (D1, D2),

See Notes 2 and 3

V

= 48 V,

VGS = 0

VGS = 15 V, VDS = 0 20 200 nA

VSG = 5 V, VDS = 0 10 100 nA

= 48

DGND

VGS = 10 V,

I

= 1.6 A,

See Notes 2 and 3

and Figures 6 and 7

VDS = 15 V, ID = 800 mA,

See Notes 2 and 3 and Figure 9

VDS = 25 V, VGS = 0,

f = 1 MHz, See Figure 11

TPIC5203

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

VDS = V

VGS = 10 V,

TC = 25°C 0.05 1

TC = 125°C 0.5 10

TC = 25°C 0.05 1

TC = 125°C 0.5 10

TC = 25°C 0.26 0.31

TC = 125°C 0.41 0.45

GS,

1.5 2.05 2.2 V

0.42 0.5 V

1 1.2 V

5 V

1.5 1.83 S

100 150

40 125

µ

µ

p

source-to-drain and GND-to-drain diode characteristics, TC = 25°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

IS = 800 mA,

= 0,

GS

See Fi

ures 1 and 14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

VDS = 48 V,

=

µs,

Z1 and Z2 50

D1 and D2 265

Z1 and Z2

D1 and D2 1240

63

2–3

Page 4

TPIC5203

DD

,

L

,

en

,

ns

See Figure 3

nH

2-CHANNEL INDEPENDENT GATE-PROTECTED

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

resistive-load switching characteristics, TC = 25°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

d(on)

t

d(off)

t

r

t

f

Q

Q

Q

L

D

L

S

R

g

thermal resistance

R

θJA

R

θJB

R

θJP

NOTES: 4. Package mounted on an FR4 printed-circuit board with no heatsink

Turn-on delay time 25 50

Turn-off delay time

Rise time

Fall time 7 15

Total gate charge

g

Threshold gate-to-source charge

gs(th)

Gate-to-drain charge

gd

Internal drain inductance 5

Internal source inductance 5

Internal gate resistance 0.25 Ω

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Junction-to-ambient thermal resistance See Notes 4 and 7 130

Junction-to-board thermal resistance See Notes 5 and 7 79

Junction-to-pin thermal resistance See Notes 6 and 7 34

5. Package mounted on a 24 inch2, 4-layer FR4 printed-circuit board

6. Package mounted in intimate contact with infinite heatsink

7. All outputs with equal power

V

= 25 V, R

t

= 10 ns,

dis

VDS = 48 V,

= 30 Ω,t

See Figure 2

ID = 0.8 A, VGS = 10 V,

= 10 ns,

27 50

15 30

4.7 5.9

0.5 0.6

1.9 2.4

nC

°C/W

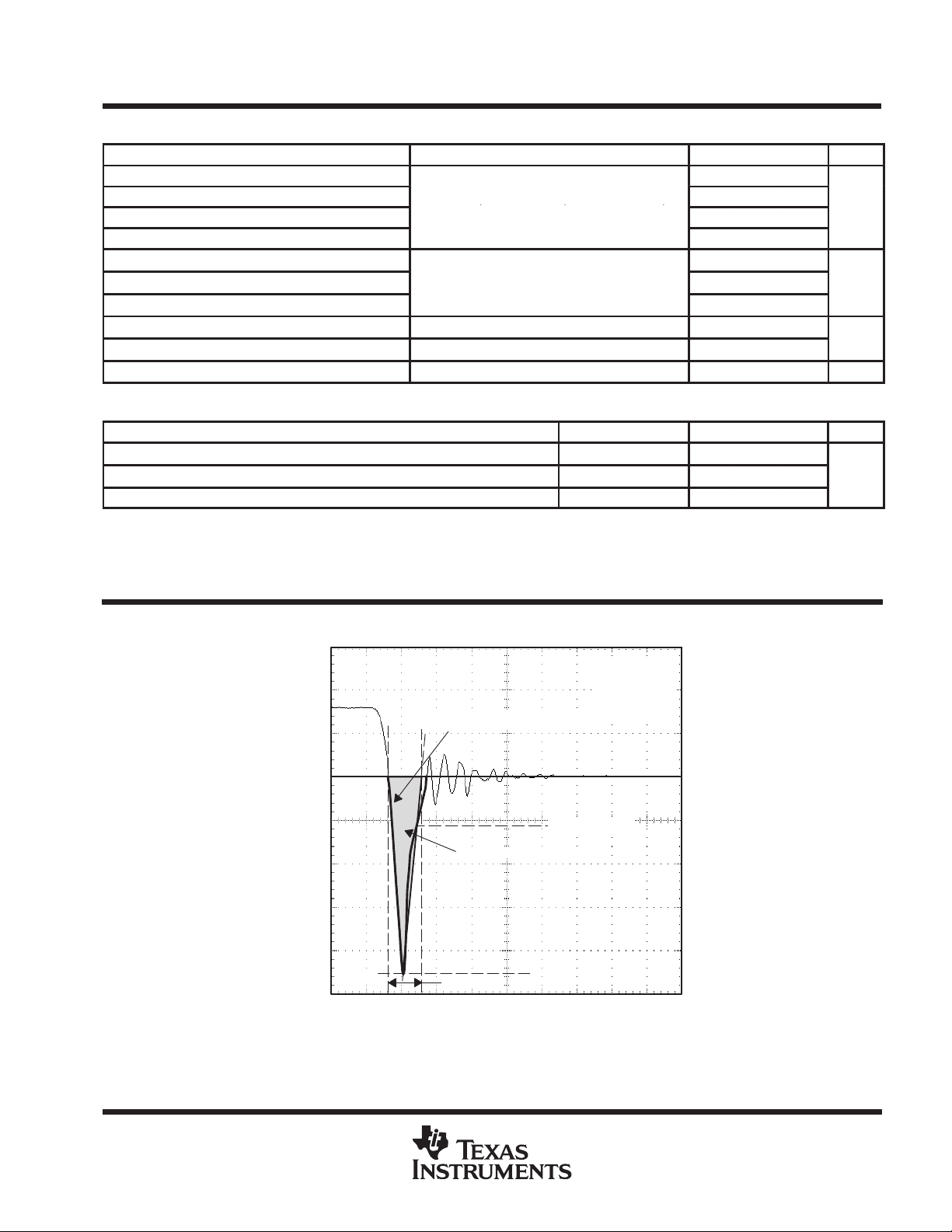

PARAMETER MEASUREMENT INFORMATION

1.5

1

Reverse di/dt = 100 A/µs

0.5

0

– 0.5

– 1

– 1.5

– Source-to-Drain Diode Current – AI

S

– 2

†

I

RM

– 2.5

0 50 100 150 200 250 300 350 400 450 500

†

IRM = maximum recovery current

‡

The above waveform is representative of D1 and D2 in shape only.

Shaded Area = QRR

t

rr(SD)

Time – ns

25% of I

VDS = 48 V

VGS = 0

TJ = 25°C

Z1 and Z2

RM

‡

†

Figure 1. Reverse-Recovery-Current Waveform of Source-to-Drain Diode

2–4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 5

2-CHANNEL INDEPENDENT GATE-PROTECTED

PARAMETER MEASUREMENT INFORMATION

VDD = 25 V

TPIC5203

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

Pulse Generator

R

gen

NOTE A: CL includes probe and jig capacitance.

50 Ω

V

GS

50 Ω

TEST CIRCUIT

Figure 2. Resistive-Switching Test Circuit and Voltage Waveforms

Current

Regulator

12-V

Battery

0.2 µF

50 kΩ

0.3 µF

V

DS

t

V

t

d(on)

V

GS

DS

en

t

f

VOLTAGE WAVEFORMS

10 V

Q

gs(th)

V

GS

Q

g

R

L

V

DS

DUT

CL 30 pF

(see Note A)

Same Type

as DUT

V

DD

t

dis

10 V

0 V

t

d(off)

t

r

V

DD

V

DS(on)

Q

gd

0 V

IG = 100 µA

IG Current-

Sampling Resistor

TEST CIRCUIT

DUT

ID Current-

Sampling Resistor

Figure 3. Gate-Charge Test Circuit and Voltage Waveform

Gate Voltage

Time

VOLTAGE WAVEFORM

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

2–5

Page 6

TPIC5203

2-CHANNEL INDEPENDENT GATE-PROTECTED

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

PARAMETER MEASUREMENT INFORMATION

VDD = 25 V

394 µH

Pulse Generator

(see Note A)

50 Ω

R

gen

TEST CIRCUIT

V

GS

50 Ω

V

I

D

DS

DUT

V

V

GS

DS

t

t

w

I

D

VOLTAGE AND CURRENT WAVEFORMS

av

15 V

0 V

I

AS

(see Note B)

0 V

V

(BR)DSX

0 V

= 60 V Min

NOTES: A. The pulse generator has the following characteristics: tr ≤ 10 ns, tf ≤ 10 ns, ZO = 50 Ω.

B. Input pulse duration (tw) is increased until peak current IAS = 8 A.

IAS

Energy test level is defined as EAS+

V

(BR)DSX

t

2

av

+

21.6 mJ.

Figure 4. Single-Pulse Avalanche Energy Test Circuit and Waveforms

TYPICAL CHARACTERISTICS

GATE-TO-SOURCE THRESHOLD VOLTAGE

vs

JUNCTION TEMPERATURE

2.5

2

ID = 1 mA

ID = 100 µA

1.5

– Gate-to-Source Threshold Voltage – V

VDS = V

GS

STATIC DRAIN-TO-SOURCE ON-STATE RESISTANCE

JUNCTION TEMPERATURE

0.6

ID = 1.6 A

Ω

0.4

– Static Drain-to-Source

0.2

On-State Resistance –

DS(on)

r

vs

VGS = 10 V

VGS = 15 V

GS(th)

V

1

– 40 – 20 0 20 40 60 80 100 120 140 160

TJ – Junction Temperature – °C

Figure 5 Figure 6

2–6

0

– 40 – 20 0 20 40 60 80 100 120 140 160

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TJ – Junction Temperature – °C

Page 7

2-CHANNEL INDEPENDENT GATE-PROTECTED

TYPICAL CHARACTERISTICS

TPIC5203

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

STATIC DRAIN-TO-SOURCE ON-STATE RESISTANCE

vs

DRAIN CURRENT

1

0.9

TJ = 25°C

0.8

0.7

0.6

Ω

0.5

0.4

0.3

– Static Drain-to-Sourcer

On-State Resistance –

DS(on)

0.2

0.1

0.1 1 4

VGS = 10 V

VGS = 15 V

ID – Drain Current – A

Figure 7 Figure 8

DISTRIBUTION OF

FORWARD TRANSCONDUCTANCE

45

Total Number of Units = 1040

40

VDS = 15 V

ID = 0.8 A

TJ = 25°C

35

DRAIN CURRENT

vs

DRAIN-TO-SOURCE VOLTAGE

VGS

= 15 V

7

6

5

4

3

– Drain Current – A

D

I

2

1

0

820.4 0.60.2 6

1234856789100

VGS

= 10 V

VDS – Drain-to-Source Voltage – V

n

VGS = 0.2 V

TJ = 25°C

(unless otherwise

noted)

VGS = 5 V

VGS = 4 V

VGS = 3 V

DRAIN CURRENT

vs

GATE-TO-SOURCE VOLTAGE

8

7

6

TJ = 75°C

TJ = 25°C

TJ = 125°C

20

15

Percentage of Units – %

10

5

0

1.72

1.74251.76

1.73

1.75

gfs – Forward Transconductance – S

5

4

3

– Drain Current – A

D

I

2

TJ = 150°C

1

TJ = –40°C

0

0

1.77

1.78

1.79

1.80301.81

1.82

1.83

1.84

1.85

1.86

1.87

1234

VGS – Gate-to-Source Voltage – V

5678910

Figure 9 Figure 10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

2–7

Page 8

TPIC5203

2-CHANNEL INDEPENDENT GATE-PROTECTED

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

TYPICAL CHARACTERISTICS

CAPACITANCE

DRAIN-TO-SOURCE VOLTAGE

350

315

280

245

210

175

140

Capacitance – pF

105

70

35

VGS = 0

f = 1 MHz

TJ = 25°C

C

= 245 pF

iss(0)

C

= 3700 pF

oss(0)

C

= 132 pF

rss(0)

0

0481216

VDS – Drain-to-Source Voltage – V

Figure 11 Figure 12

DRAIN-TO-SOURCE VOLTAGE AND

GATE-TO-SOURCE VOLTAGE

GATE CHARGE

60

ID = 0.8 A

TJ = 25°C

See Figure 3

50

40

30

20

– Drain-to-Source Voltage – V

DS

10

V

0

0 0.5 1 1.5 2 2.5 3 3.5

VDD = 30 V

Qg – Gate Charge – nC

vs

C

iss

C

oss

C

rss

20 24 28 32 36

vs

VDD = 20 V

VDD = 48 V

VDD = 20 V

4 4.5 5

40

12

10

8

6

4

2

0

0.6

0.4

– Source-to-Drain Diode Current – A

0.2

SD

I

0.1

– Reverse Recovery Time – ns

– Gate-to-Source Voltage – V

rr

GS

t

V

SOURCE-TO-DRAIN DIODE CURRENT

vs

SOURCE-TO-DRAIN VOLTAGE

8

VGS = 0

6

4

2

1

TJ = 125°C

TJ = 150°C

0.1 10

VSD – Source-to-Drain Voltage – V

1

TJ = –40°C

TJ = 25°C

TJ = 75°C

REVERSE RECOVERY TIME

vs

REVERSE di/dt

280

260

240

220

200

180

160

140

120

100

80

60

40

20

0

100 300 500

0 200 400

D1 and D2

Z1 and Z2

Reverse di/dt – A/µs

VDS = 48 V

VGS = 0

IS = 0.8 A

TJ = 25°C

See Figure 1

600

2–8

Figure 13 Figure 14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 9

2-CHANNEL INDEPENDENT GATE-PROTECTED

THERMAL INFORMATION

TPIC5203

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

MAXIMUM DRAIN CURRENT

vs

DRAIN-TO-SOURCE VOLTAGE

10

TC = 25°C

†

500 µs

†

1 ms

†

1

§

R

– Maximum Drain Current – A

D

I

DC Condition

0.1

0.1 1 10 100

†

Less than 2% duty cycle

‡

Device mounted in intimate contact with infinite heatsink.

§

Device mounted on FR4 printed circuit board with no heatsink.

VDS – Drain-to-Source Voltage – V

θJA

1 µs

R

θJP

10 ms

‡

†

Figure 15

MAXIMUM PEAK AVALANCHE CURRENT

vs

TIME DURATION OF AVALANCHE

10

9

8

7

6

5

4

3

TC = 125°C

2

– Maximum Peak Avalanche Current – A

AS

I

1

0.01 0.1 10 100

tav – Time Duration of Avalanche – ms

TC = 25°C

1

See Figure 4

Figure 16

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

2–9

Page 10

TPIC5203

2-CHANNEL INDEPENDENT GATE-PROTECTED

POWER DMOS ARRAY

SLIS040 – SEPTEMBER 1994

THERMAL INFORMATION

C/W

°

100

10

1

DC Conditions

d = 0.5

d = 0.2

d = 0.1

d = 0.05

d = 0.02

d = 0.01

D PACKAGE

†

JUNCTION-TO-BOARD THERMAL RESISTANCE

vs

PULSE DURATION

– Junction-to-Board Thermal Resistance – R

JB

θ

Single Pulse

0.1

0.0001 0.001

†

Device mounted on 24 in2, 4-layer FR4 printed-circuit board with no heatsink

NOTE A. Z

(t) = r(t)R

θJB

tw = pulse duration

tc = cycle time

d = duty cycle = tw/t

θJB

c

0.01 0.1 1 100

tw – Pulse Duration – s

Figure 17

t

c

t

w

10

I

D

0

2–10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 11

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty . Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICA TIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

Loading...

Loading...