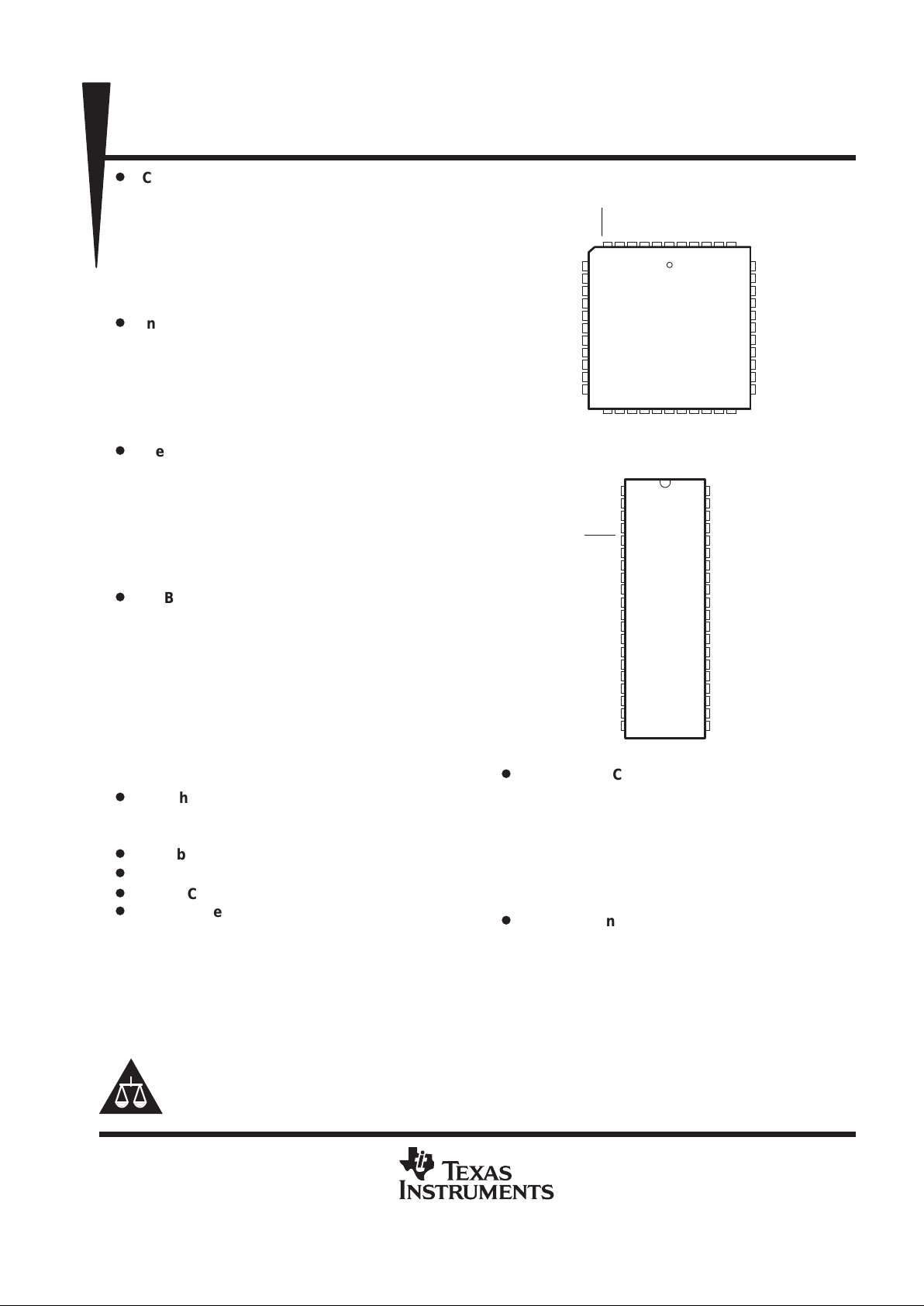

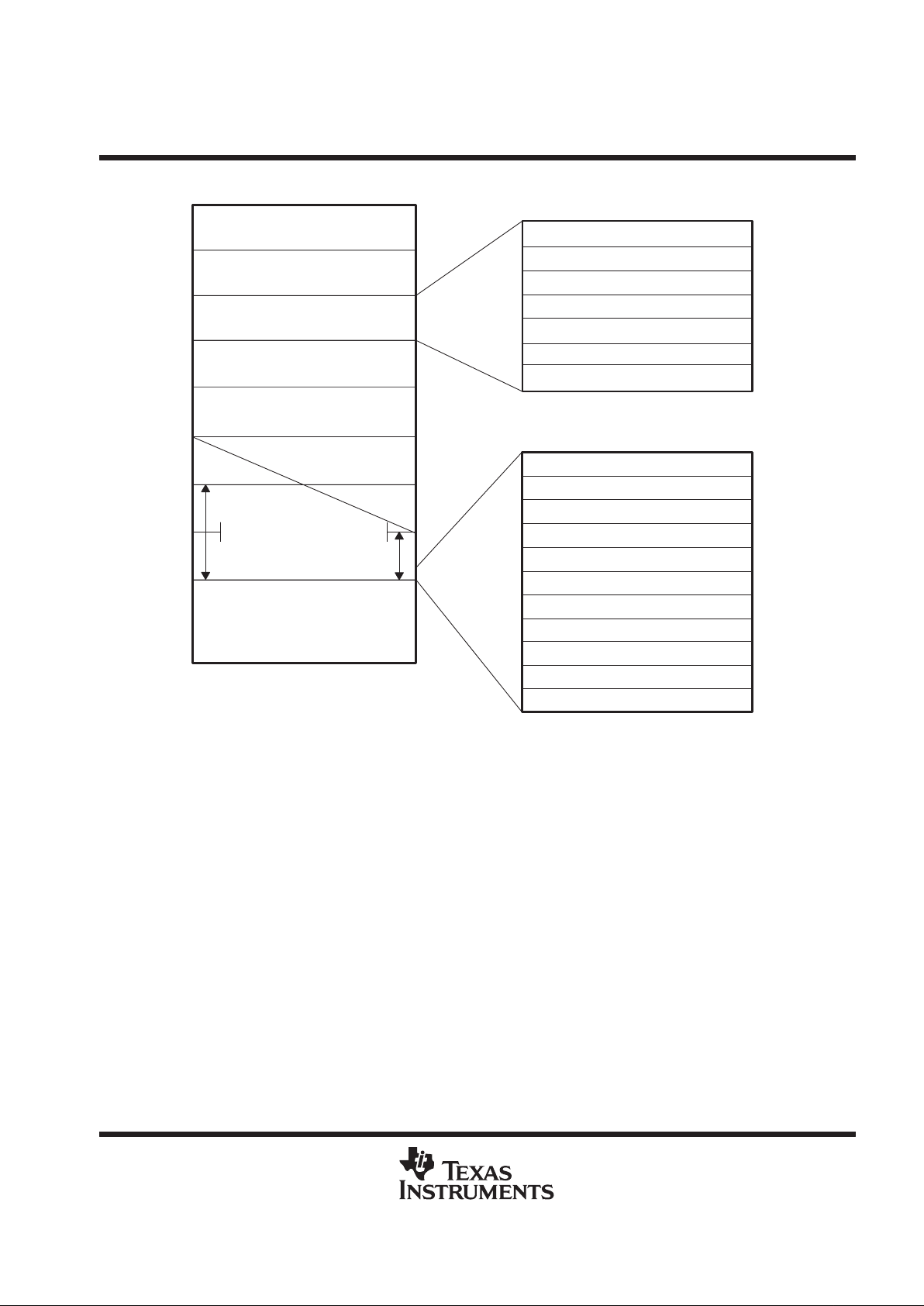

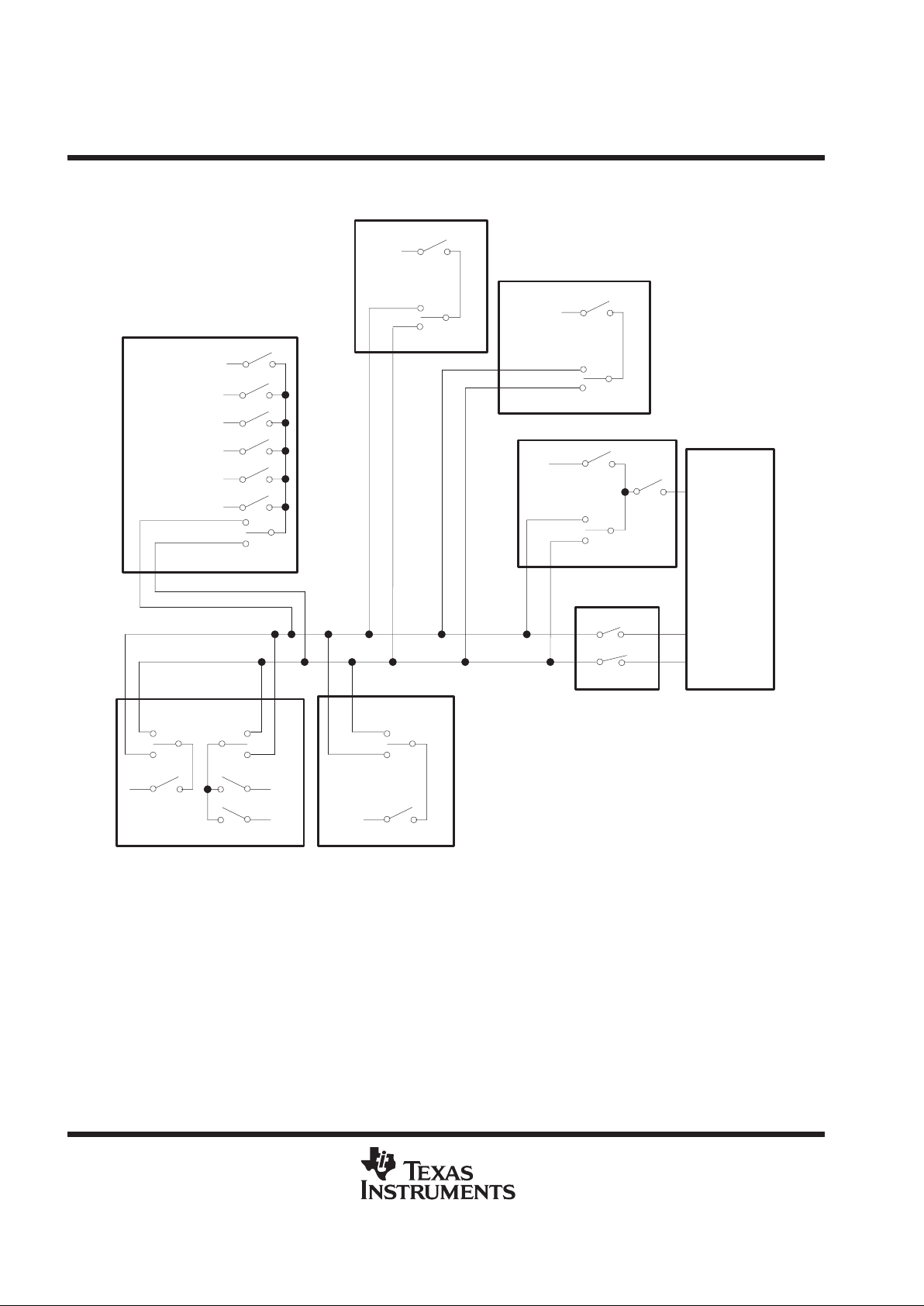

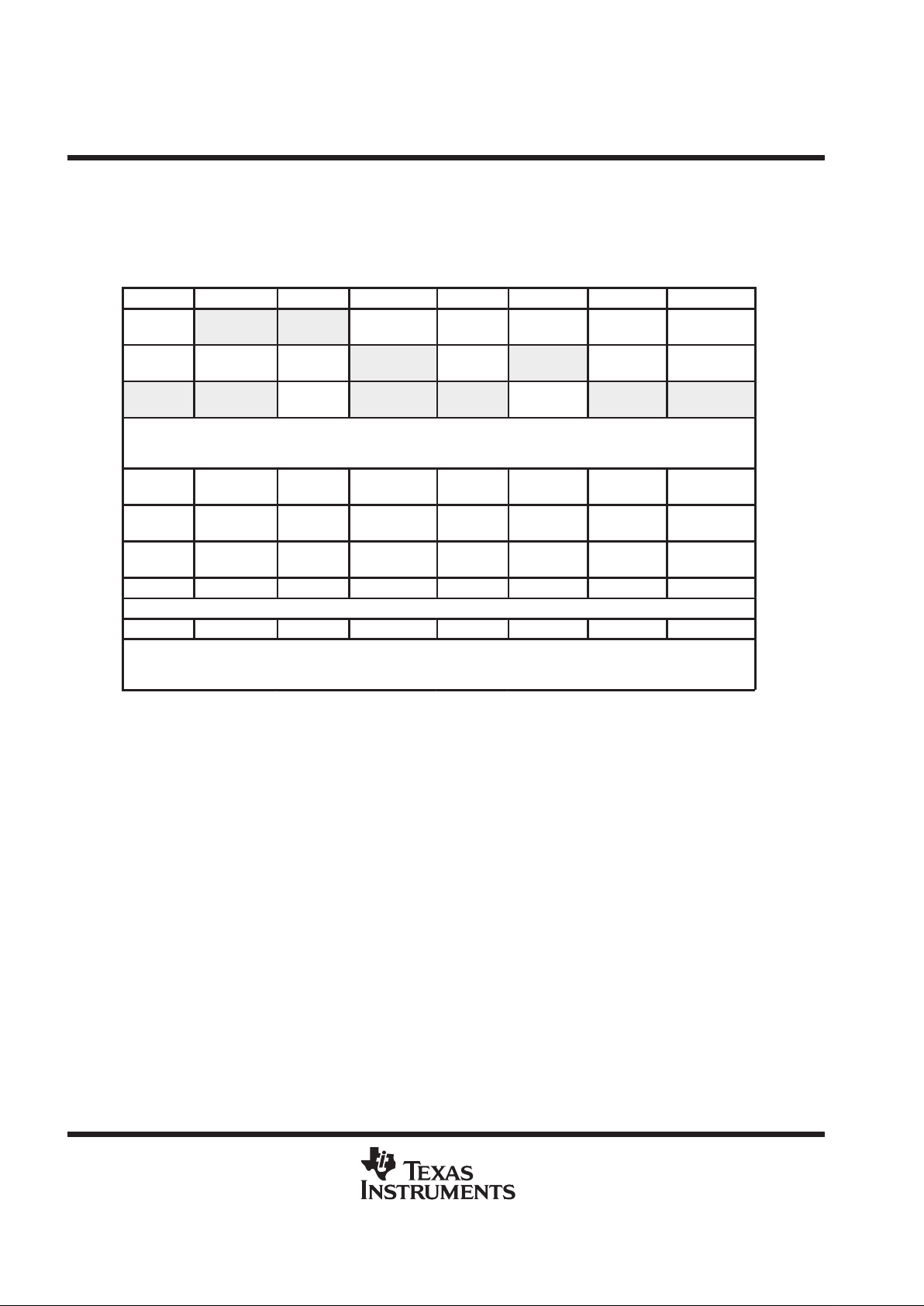

JC, JD, N AND NJ PACKAGES

(TOP VIEW)

B2

B3

B4

C0

RESET

INT1

INT2

INT3

V

CC

A7

A6

V

SS

A5

A4

A3

A2

A1

A0

D7

D4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

B1

B0

SCITXD

SCIRXD

SCICLK

D5

MC

XTAL2/CLKIN

XTAL1

T1IC/CR

T1PWM

T1EVT

SPISOMI

SPISIMO

SPICLK

B7

B6

B5

D6

D3

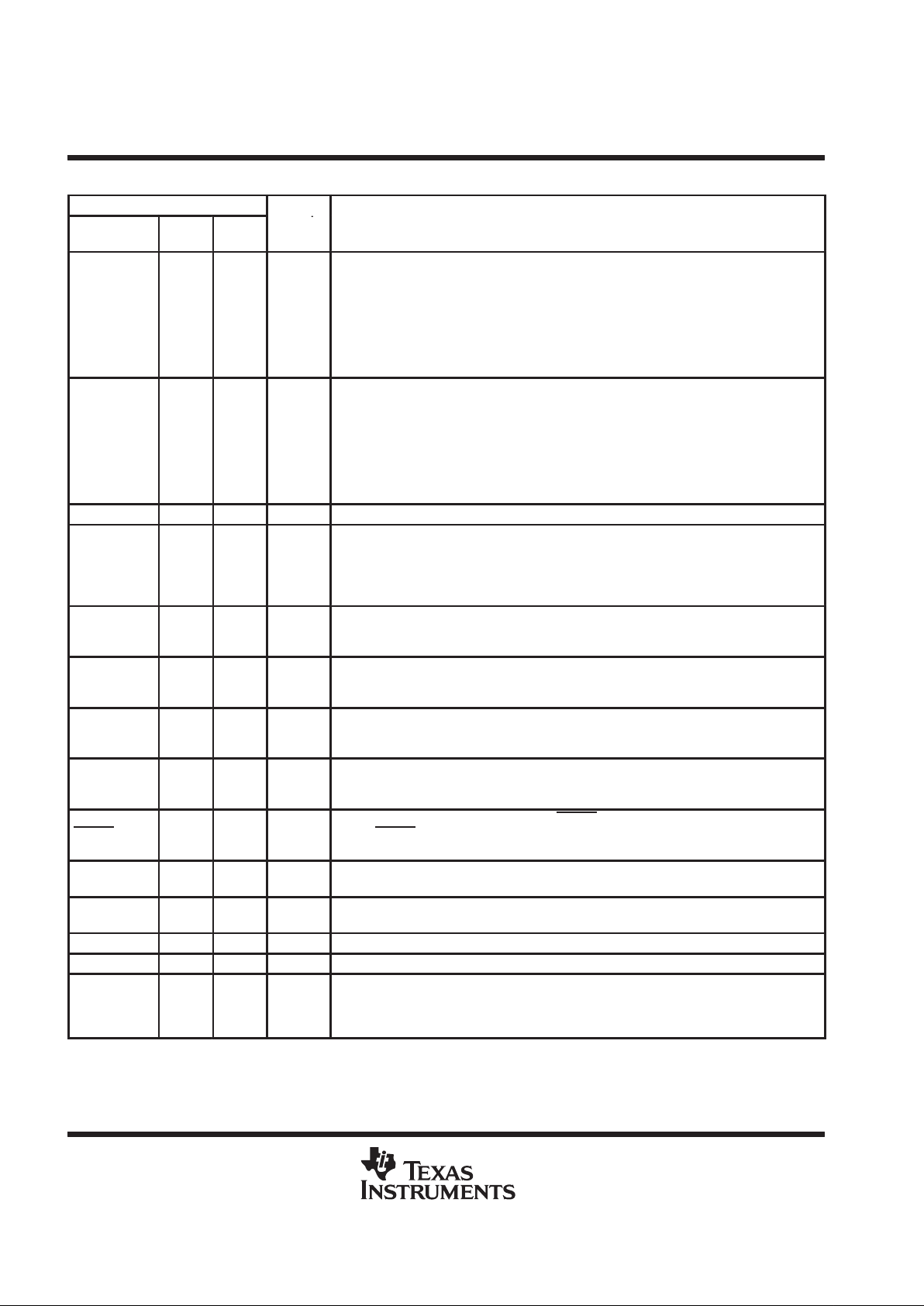

FN AND FZ PACKAGES

(TOP VIEW)

MC

XTAL2/CLKIN

XTAL1

T1IC/CR

T1PWM

T1EVT

NC

SPISOMI

SPISIMO

SPICLK

NC

39

38

37

36

35

34

33

32

31

30

29

18 19

7

8

9

10

11

12

13

14

15

16

17

INT1

INT2

INT3

V

CC

NC

A7

A6

V

SS

A5

A4

A3

20 21 22 23

SCITXD

SCIRXD

SCICLK

D5

54321644

RESETC0B4B3B2B1B0

NC

B5

B6

A2A1A0

D7D4D6

42 41 4043

24 25 26 27 28

B7

D3

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

D

CMOS/EEPROM/EPROM Technologies on

a Single Device

– Mask-ROM Devices for High-Volume

Production

– One-Time-Programmable (OTP) EPROM

Devices for Low-Volume Production

– Reprogrammable-EPROM Devices for

Prototyping Purposes

D

Internal System Memory Configurations

– On-Chip Program Memory Versions

– ROM: 4K or 8K Bytes

– EPROM: 8K Bytes

– Data EEPROM: 256 Bytes

– Static RAM: 256 Bytes Usable as

Registers

D

Flexible Operating Features

– Low-Power Modes: STANDBY and HALT

– Commercial, Industrial, and Automotive

T emperature Ranges

– Clock Options

– Divide-by-1 (2 MHz–5 MHz SYSCLK) PLL

– Divide-by-4 (0.5 MHz–5 MHz SYSCLK)

– Supply Voltage (V

CC

) 5 V ±10%

D

16-Bit General-Purpose Timer

– Software Configurable as

a 16-Bit Event Counter, or

a 16-Bit Pulse Accumulator, or

a 16-Bit Input Capture Function, or

T wo Compare Registers, or a

Self-Contained Pulse-Width-Modulation

(PWM) Function

– Software Programmable Input Polarity

– 8-Bit Prescaler, Providing a 24-Bit

Real-Time Timer

D

On-Chip 24-Bit Watchdog Timer

– Mask-ROM Devices: Hard Watchdog,

Simple Counter, or Standard Watchdog

D

Flexible Interrupt Handling

D

Serial Peripheral Interface (SPI)

D

Serial Communications Interface 1 (SCI1)

D

TMS370 Series Compatibility

– Register-to-Register Architecture

– 128 or 256 General-Purpose Registers

– 14 Powerful Addressing Modes

– Instructions Upwardly Compatible With

All TMS370 Devices

D

CMOS/TTL Compatible I/O Pins/Packages

– All Peripheral Function Pins Software

Configurable for Digital I/O

– 33 Bidirectional Pins, 1 Input Pin

– 44-Pin Plastic and Ceramic Leaded Chip

Carrier (LCC) Packages

– 40-Pin Plastic and Ceramic Dual-In-Line

(DIP) Packages

D

Workstation/PC-Based Development

System

– C Compiler and C Source Debugger

– Real-Time In-Circuit Emulation

– Extensive Breakpoint/Trace Capability

– Multi-Window User Interface

– Microcontroller Programmer

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright 1997, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

2

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Pin Descriptions

PIN

NAME

DIP

(40)

PLCC

(44)

TYPE

†

DESCRIPTION

A0

A1

A2

A3

A4

A5

A6

A7

18

17

16

15

14

13

11

10

20

19

18

17

16

15

13

12

I/O Port A pins are general-purpose bidirectional I/O ports.

B0

B1

B2

B3

B4

B5

B6

B7

39

40

1

2

3

23

24

25

44

1

2

3

4

26

27

28

I/O Port B pins are general-purpose bidirectional I/O ports.

C0 4 5 I/O Port C pin is a general-purpose bidirectional I/O port.

D3

D4

D5

D6

D7

21

20

35

22

19

23

22

40

24

21

I/O Port D pins are general-purpose bidirectional I/O ports. D3 is also configurable as SYSCLK.

INT1

INT2

INT3

6

7

8

7

8

9

I

I/O

I/O

External interrupt (non-maskable or maskable) general-purpose input pin

External maskable interrupt input/general-purpose bidirectional pin

External maskable interrupt input/general-purpose bidirectional pin

T1IC/CR

T1PWM

T1EVT

31

30

29

36

35

34

I/O

Timer 1 input-capture/counter-reset input pin/general-purpose bidirectional pin

Timer 1 pulse width modulation output pin/general-purpose bidirectional pin

Timer 1 external event-input pin/general-purpose bidirectional pin

SPISOMI

SPISIMO

SPICLK

28

27

26

32

31

30

I/O

SPI slave output pin, master input pin/general-purpose bidirectional pin

SPI slave input pin, master output pin/general-purpose bidirectional pin

SPI bidirectional serial clock pin/general-purpose bidirectional pin

SCITXD

SCIRXD

SCICLK

38

37

36

43

42

41

I/O

SCI transmit data output pin/general-purpose bidirectional pin

‡

SCI receive data input pin/general-purpose bidirectional pin

SCI bidirectional serial clock pin/general-purpose bidirectional pin

RESET 5 6 I/O

System reset bidirectional pin; as input, RESET initializes microcontroller; as open-drain

output, RESET

indicates an internal failure was detected by the watchdog or oscillator fault

circuit.

MC 34 39 I

Mode control-input pin. MC enables the EEPROM write-protection override (WPO) mode and

EPROM VPP.

XTAL2/CLKIN

XTAL1

33

32

38

37

I

O

Internal oscillator crystal input/external clock source input

Internal oscillator output for crystal

V

CC

9 10 Positive supply voltage

V

SS

12 14 Ground reference

NC

–

–

–

–

11

25

29

33

No connections

†

I = input, O = output

‡

The three-pin configuration SCI is referred to as SCI1.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

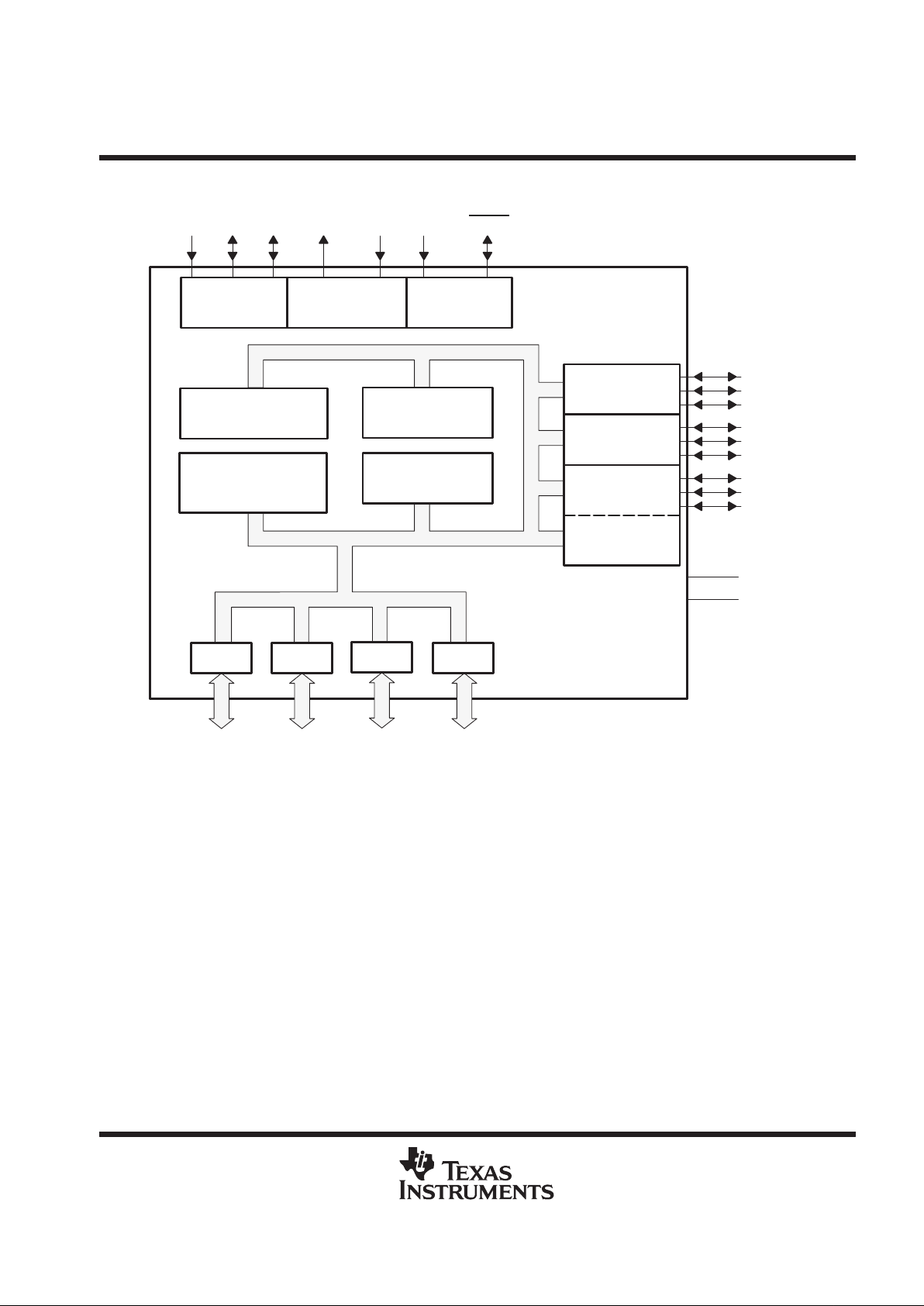

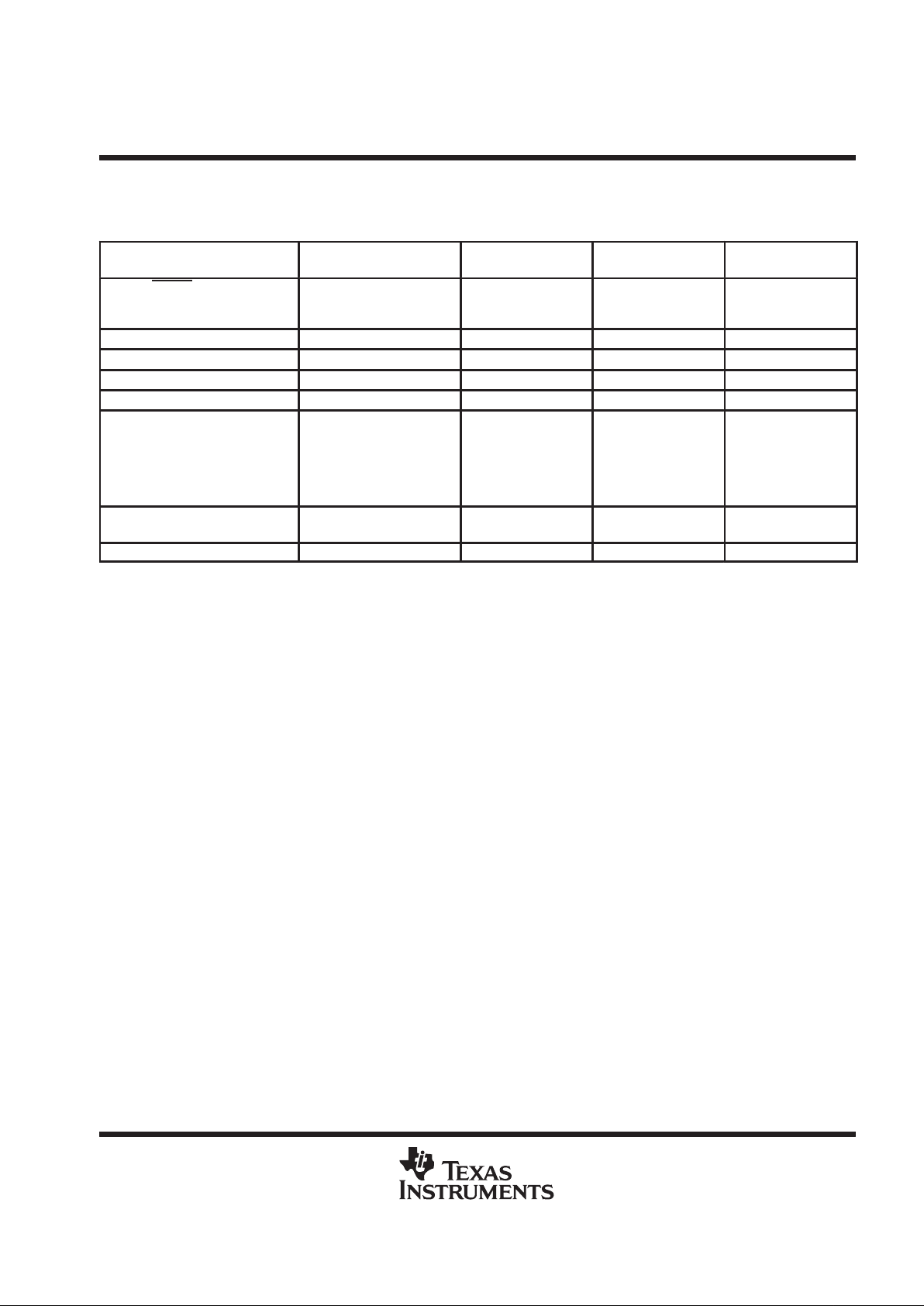

functional block diagram

Clock Options:

Divide-By-4 or

Divide-By-1 (PLL)

Interrupts

System

Control

INT1 INT2 INT3 MC RESET

XTAL1

Timer 1

Watchdog

Serial

Communications

Interface 1

RAM

256 Bytes

Program Memory

ROM: 4K or 8K Bytes

EPROM: 8K Bytes

Data EEPROM

256 Bytes

CPU

XTAL2/

CLKIN

SCIRXD

SCITXD

SCICLK

T1IC/CR

T1EVT

T1PWM

V

CC

V

SS

Port BPort A Port D

85

Port C

81

SPISOMI

SPISIMO

SPICLK

Serial

Peripheral

Interface

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

4

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

description

The TMS370C020A, TMS370C022A, TMS370C320A, TMS370C322A, TMS370C722, and SE370C722

devices are members of the TMS370 family of single-chip 8-bit microcontrollers. Unless otherwise noted, the

term TMS370Cx2x refers to these devices. The TMS370 family provides cost-effective real-time system control

through integration of advanced peripheral modules and various function on-chip memory configurations.

The TMS370Cx2x family uses high-performance silicon-gate CMOS EPROM and EEPROM technology . Low

operating power, wide operating temperature range, and noise immunity of CMOS technology coupled with the

high performance and extensive on-chip peripheral functions make the TMS370Cx2x devices attractive in

system designs for automotive electronics, industrial motor, computer peripheral controls, telecommunications,

and consumer applications.

All TMS370Cx2x devices contain the following on-chip peripheral modules:

D

Serial peripheral interface (SPI)

D

Serial communications interface 1 (SCI1)

D

One 24-bit general-purpose watchdog (WD) timer

D

One 16-bit general-purpose timer with an 8-bit prescaler

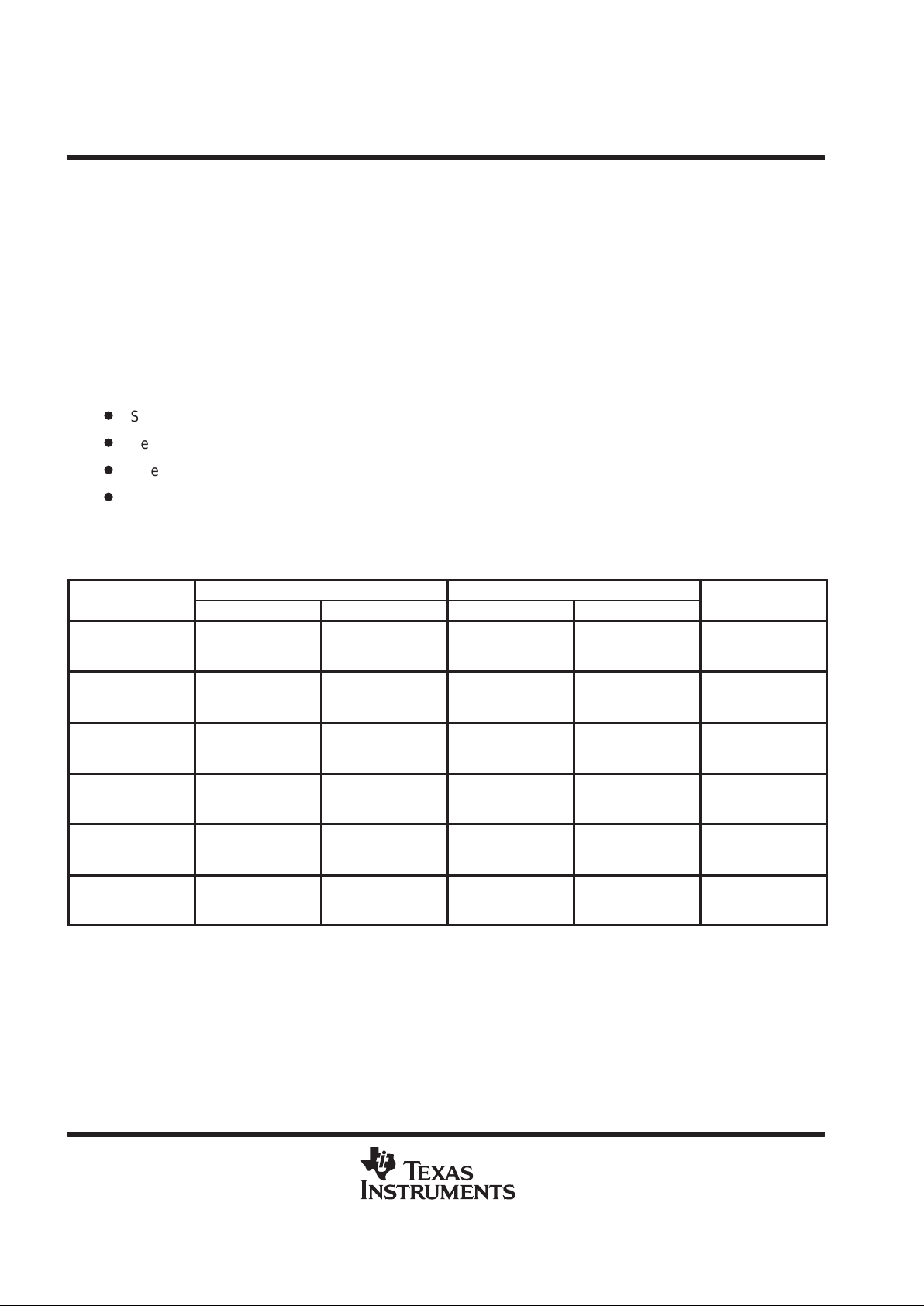

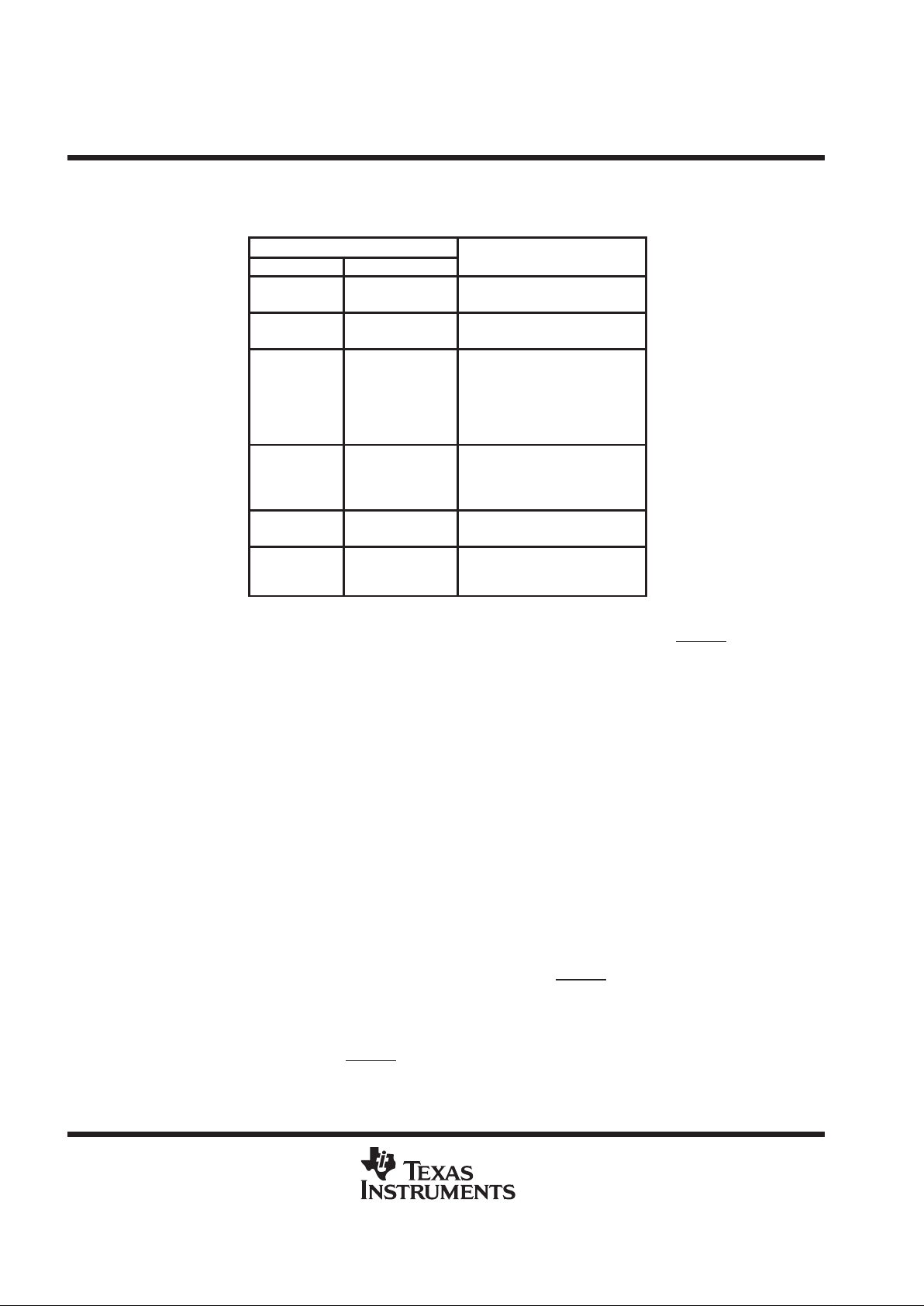

Table 1 lists memory configurations of the TMS370Cx2x devices.

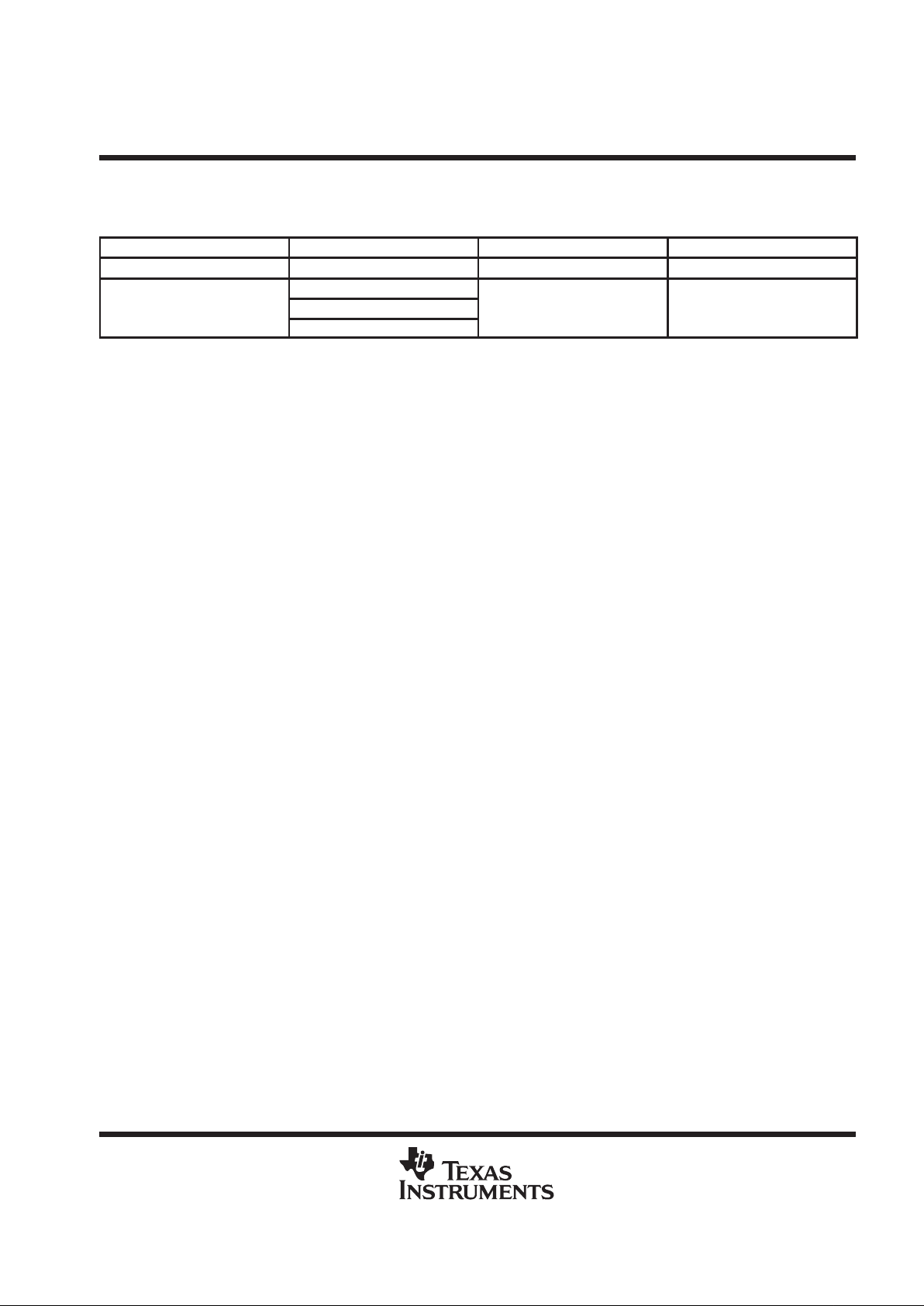

Table 1. Memory Configurations

PROGRAM MEMORY (BYTES) DATA MEMORY (BYTES)

DEVICE

ROM EPROM RAM EEPROM

PIN/PACKAGES

TMS370C020A 4K — 256 256

44/FN-PLCC

40/N-DIP

40/NJ‡-PSDIP

TMS370C022A 8K — 256 256

44/FN-PLCC

40/N-DIP

40/NJ‡-PSDIP

TMS370C320A 4K — 256 —

44/FN-PLCC

40/N-DIP

40/NJ‡-PSDIP

TMS370C322A 8K — 256 —

44/FN-PLCC

40/N-DIP

40/NJ‡-PSDIP

TMS370C722 — 8K 256 256

44/FN-PLCC

40/N-DIP

40/NJ‡-PSDIP

SE370C722

†

— 8K 256 256

44/FZ-CLCC

40/JD-CDIP

40/JC-CSDIP

†

System evaluators and development tools are for use only in a prototype environment, and their reliability has not been characterized.

‡

The NJ designator for the 40-pin plastic shrink DIP package was formerly known as N2. The mechanical drawing of the NJ is identical to the N2

package and did not need to be requalified.

The suffix letter A appended to the device names in Table 1 indicates the configuration of the devices. ROM

or EPROM devices have different configurations as indicated in Table 2. ROM devices with the suffix letter A

are configured through a programmable contact during manufacture.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

5

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

description (continued)

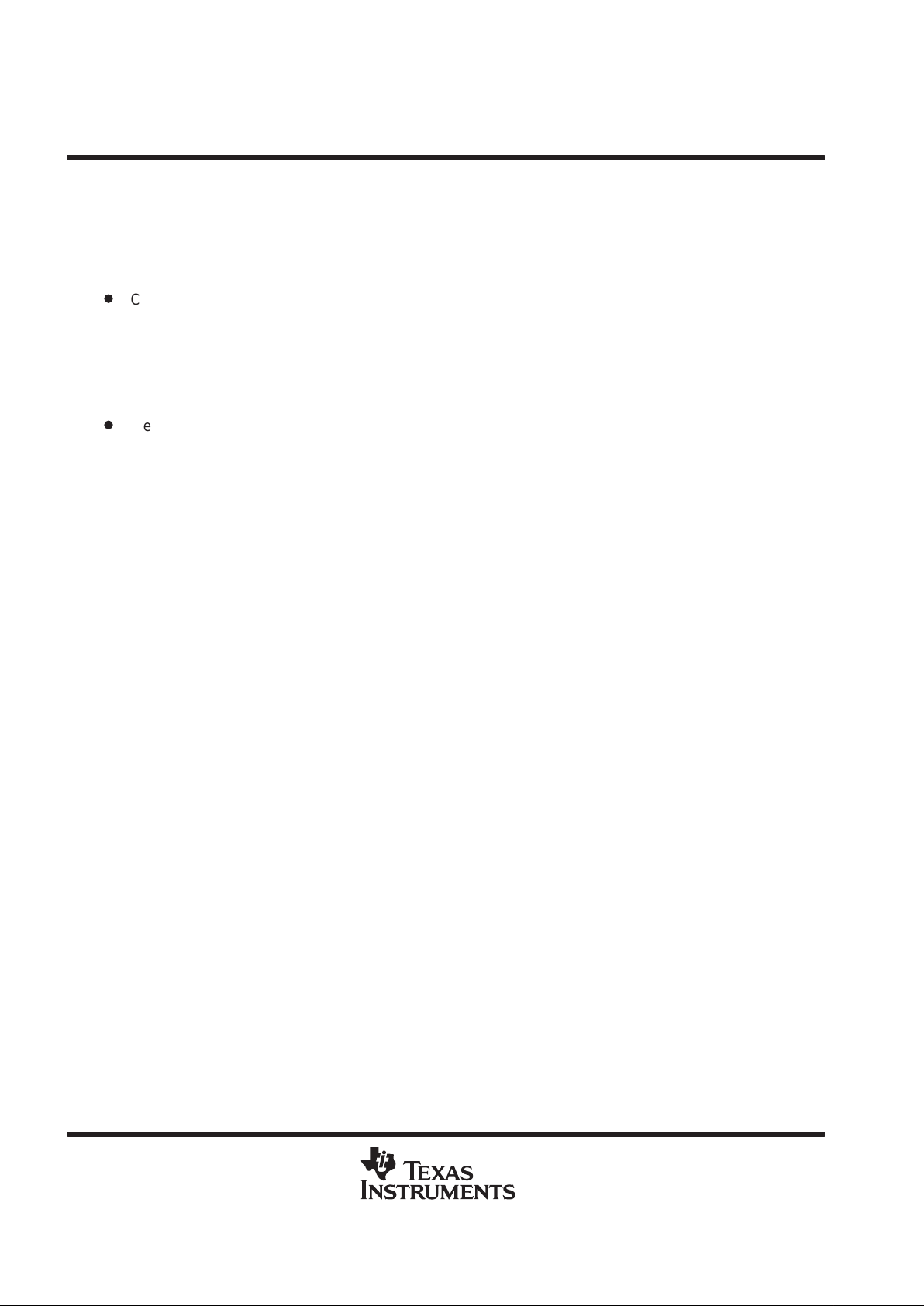

Table 2. Suffix Letter Configuration

DEVICE

†

WATCHDOG TIMER CLOCK LOW-POWER MODE

EPROM without A Standard Divide-by-4 (Standard oscillator) Enabled

Standard

ROM A

Hard

Divide-by-4 or Divide-by-1 (PLL) Enabled or disabled

Simple

†

Refer to the “device numbering conventions” section for device nomenclature and the “device part numbers” section for ordering.

The 4K bytes and 8K bytes of mask-programmable ROM in the TMS370C020, TMS370C022, TMS370C320,

and TMS370C322 are replaced in the TMS370C722 and SE370C722 with 8K bytes of EPROM. All other

available memory and on-chip peripherals are identical, except there are no data EEPROMs on the

TMS370C320 and TMS370C322 devices. OTP (TMS370C722) devices and the reprogrammable device

(SE370C722) are available.

TMS370C722 (OTP) devices are in plastic packages. This microcontroller is effective to use for immediate

production updates for other members of the TMS370Cx2x family or for low-volume production runs when the

mask charge or cycle time for the low-cost mask ROM devices is not practical.

The SE370C722 has a windowed ceramic package to allow reprogramming of the program EPROM memory

during the prototyping phase of design. These SE370C722 devices allow quick updates to breadboards and

prototype systems while creating multiple initial designs.

The TMS370Cx2x family provides two low-power modes (STANDBY and HALT) for applications where low

power consumption is critical. Both modes stop all central processing unit (CPU) activity (that is, no instructions

are executed). In the ST ANDBY mode, the internal oscillator, the general-purpose timer, and the SCI receiver

start-bit detection remain active. In the HAL T mode, all device activity is stopped. The device retains all RAM

data and peripheral configuration bits throughout both low-power modes.

The TMS370Cx2x features advanced register-to-register architecture that allows arithmetic and logical

operations without requiring an accumulator (e.g., ADD R24, R47; add the contents of register 24 to the contents

of register 47 and store the result in register 47). The TMS370Cx2x family is fully instruction-set-compatible,

providing easy transition between members of the TMS370 8-bit microcontroller family.

The SPI provides a convenient method of serial interaction for high speed communications between simpler

shift-register type devices, such as display drivers, analog-to-digital (A/D) converter, PLL, I/O expansion, or

other microcontrollers in the system.

The TMS370Cx2x devices have two operational modes of serial communications provided by the SCI1 module.

The SCI1 allows standard RS-232-C communications with other common data transmission equipment.

The TMS370Cx2x family provides the system designer with an economical, efficient solution to real-time control

applications. The TMS370 family extended development system (XDS) and compact development tool

(CDT) meet the challenge of efficiently developing the software and hardware required to design the

TMS370Cx2x into complex applications. The application source code can be written in assembly and C

language, and the output code can be generated by the linker. The TMS370 family XDS development tool

communicates through a standard RS-232-C interface with a personal computer. This allows the use of the

personal computer editors and software utilities already familiar to the designer. The TMS370 family XDS

emphasizes ease-of-use through extensive menus and screen windowing so that a system designer can begin

developing software with minimal training. Precise real-time in-circuit emulation and extensive symbolic debug

and analysis tools ensure efficient software and hardware implementation as well as a reduced time-to-market

cycle.

XDS and CDT are trademarks of Texas Instruments Incorporated.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

6

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

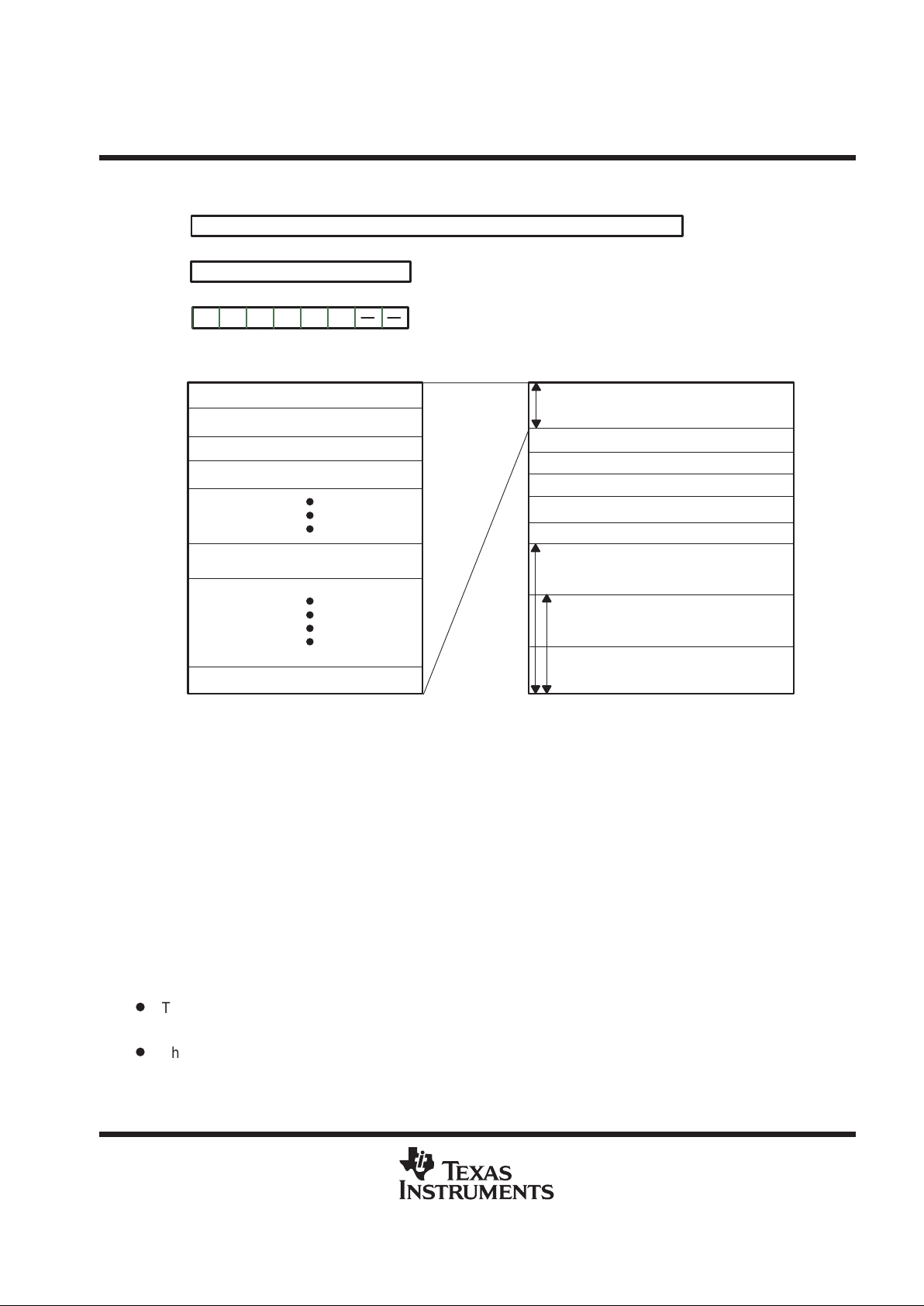

central processing unit (CPU)

The TMS370Cx2x device uses the high-performance 8-bit TMS370 CPU module. The ’x2x uses an efficient

register-to-register architecture that eliminates the conventional accumulator bottleneck. The complete ’x2x

instruction map is shown in Table 17 in the instruction set overview section.

The ’370Cx2x CPU architecture provides the following components:

D

CPU registers:

– A stack pointer that points to the last entry in the memory stack

– A status register that monitors the operation of the instructions and contains the global interrupt-enable

bits

– A program counter that points to the memory location of the next instruction to be executed

D

Memory blocks:

– 256-byte general-purpose RAM that can be used for data memory storage, program instructions,

general purpose register, or the stack

– A peripheral file that provides access to all internal peripheral modules, system-wide control functions,

and EEPROM/EPROM programming control

– 256-byte EEPROM module, that provides in-circuit programmability and data retention in power-off

conditions

– 4K- or 8K-byte ROM or 8K-byte EPROM

Figure 1 illustrates the CPU registers and memory blocks.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

7

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

central processing unit (CPU) (continued)

Reserved

†

Peripheral File

Not Available

‡

0FFFh

1000h

1F00h

1FFFh

2000h

5FFFh

6000h

Interrupts and Reset Vectors;

Trap Vectors

10FFh

1100h

1EFFh

Reserved

†

7FFFh

0

RAM (Includes up to 256-Byte Registers File)

015

Program Counter

7

Legend:

Z=Zero

IE1=Level 1 interrupts Enable

C=Carry

V=Overflow

N=Negative

IE2=Level 2 interrupts Enable

IE1IE2ZNC

01234567

V

Status Register (ST)

Stack Pointer (SP)

R0(A)

R1(B)

R3

R127

0000h

0001h

0002h

007Fh

R255

0003h

R2

00FFh

256-Byte Data EEPROM

6FFFh

7000h

8K-Byte ROM/EPROM (6000h–7FFFh)

4K-Byte ROM (7000h–7FFFh)

7FC0h

7FBFh

00FFh

0100h

256-Byte RAM (0000h–00FFh)

0000h

†

Reserved means the address space is reserved for future expansion.

‡

Not available means the address space is not accessible.

Figure 1. Programmer’s Model

stack pointer (SP)

The SP is an 8-bit CPU register. Stack operates as a last-in, first-out, read/write memory. Typically the stack

is used to store the return address on subroutine calls as well as the status register contents during interrupt

sequences.

The SP points to the last entry or top of the stack. The SP is incremented automatically before data is pushed

onto the stack and decremented after data is popped from the stack. The stack can be placed anywhere in the

on-chip RAM.

status register (ST)

The ST monitors the operation of the instructions and contains the global interrupt-enable bits. The ST includes

four status bits (condition flags) and two interrupt-enable bits.

D

The four status bits indicate the outcome of the previous instruction; conditional instructions (for example,

the conditional-jump instructions) use the status bits to determine program flow.

D

The two interrupt-enable bits control the two interrupt levels.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

8

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

central processing unit (CPU) (continued)

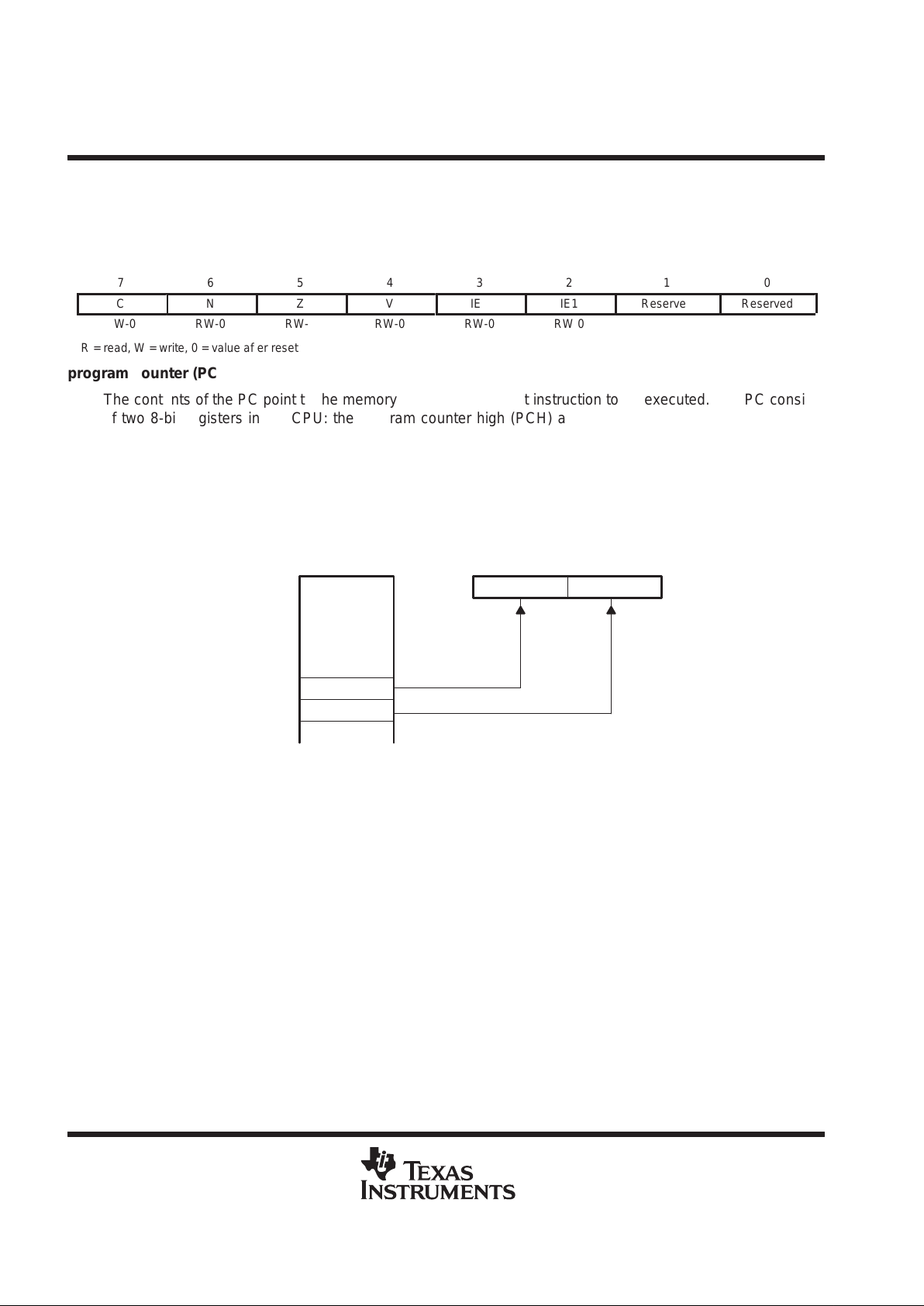

The ST, status-bit notation, and status-bit definitions are shown in Table 3.

Table 3. Status Registers

7

6

5

4

3

2

1

0

C

N

Z

V

IE2

IE1 Reserved Reserved

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

R = read, W = write, 0 = value after reset

program counter (PC)

The contents of the PC point to the memory location of the next instruction to be executed. The PC consists

of two 8-bit registers in the CPU: the program counter high (PCH) and program counter low (PCL). These

registers contain the most significant byte (MSbyte) and least significant byte (LSbyte) of a 16-bit address.

During reset, the contents of the reset vector (7FFEh, 7FFFh) are loaded into the PC. The PCH (MSbyte of the

PC) is loaded with the contents of memory location 7FFEh, and the PCL (LSbyte of the PC) is loaded with the

contents of memory location 7FFFh. Figure 2 shows this operation using an example value of 6000h as the

contents of the reset vector.

Memory

Program Counter (PC)

60 00

PCH PCL

60

00

0000h

7FFEh

7FFFh

Figure 2. Program Counter After Reset

memory map

The TMS370Cx2x architecture is based on the Von Neuman architecture, where the program memory and data

memory share a common address space. All peripheral input/output is memory mapped in this same common

address space. As shown in Figure 3, the TMS370Cx2x provides memory-mapped RAM, ROM, EPROM, data

EEPROM, I/O pins, peripheral functions, and system-interrupt vectors.

The peripheral file contains all I/O port control, peripheral status and control, EEPROM, EPROM, and

system-wide control functions. The peripheral file is located between 1010h to 105Fh and is divided logically

into five peripheral file frames of 16 bytes each. Each on-chip peripheral is assigned to a separate frame through

which peripheral control and data information is passed.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

9

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

memory map (continued)

256-Byte RAM (Register File/Stack)

Reserved

†

Peripheral File

Reserved

†

256-Byte Data EEPROM

Not Available

‡

8K-Byte

7FC0h

Trap 15–0

7FECh

Serial Communication Interface RX

7FEEh

Timer 1

7FF0h

Interrupt 3

7FF2h

Interrupt 2

7FF4h

Interrupt 1

7FF8h

Reset

1000h

Reserved

†

1010h

System Control

1020h

Digital Port Control

1030h

1040h

Timer 1 Control

Vectors

7FDFh

7FEFh

7FF1h

7FF3h

7FF5h

7FF7h

7FF9h

100Fh

101Fh

102Fh

103Fh

104Fh

–

–

–

–

–

–

–

–

–

–

–

Program Memory

(ROM/EPROM)

Not Available

‡

SPI Control

Reserved

†

Reserved

†

Serial Communication Interface TX

7FFAh 7FFBh

–

–

7FFCh 7FFDh–

7FFEh 7FFFh

–

–

1050h

1060h

105Fh

10FFh

–

–

0000h

0100h

00FFh

1000h

10FFh

1100h

1EFFh

1F00h

1FFFh

2000h

5FFFh

6000h

6FFFh

7000h

7FFFh

8000h

FFFFh

0FFFh

Reserved

†

SCI1 Control

7FEDh

–

–

7FF6h

Serial Peripheral Interface

†

Reserved means the address space is reserved for future expansion.

‡

Not available means the address space is not accessible.

Figure 3. TMS370Cx2x Memory Map

RAM/register file (RF)

Locations within the RAM address space can serve as the RF, general-purpose read/write memory, program

memory, or stack instructions. The TMS370Cx2x contains 256 bytes of internal RAM mapped beginning at

location 0000h (R0) and continuing through location 00FFh (R255).

The first two registers, R0 and R1, are also called register A and B, respectively. Some instructions implicitly

use register A or B; for example, the instruction LDSP (load SP) assumes that the value to be loaded into the

stack pointer is contained in register B. Registers A and B are the only registers cleared on reset.

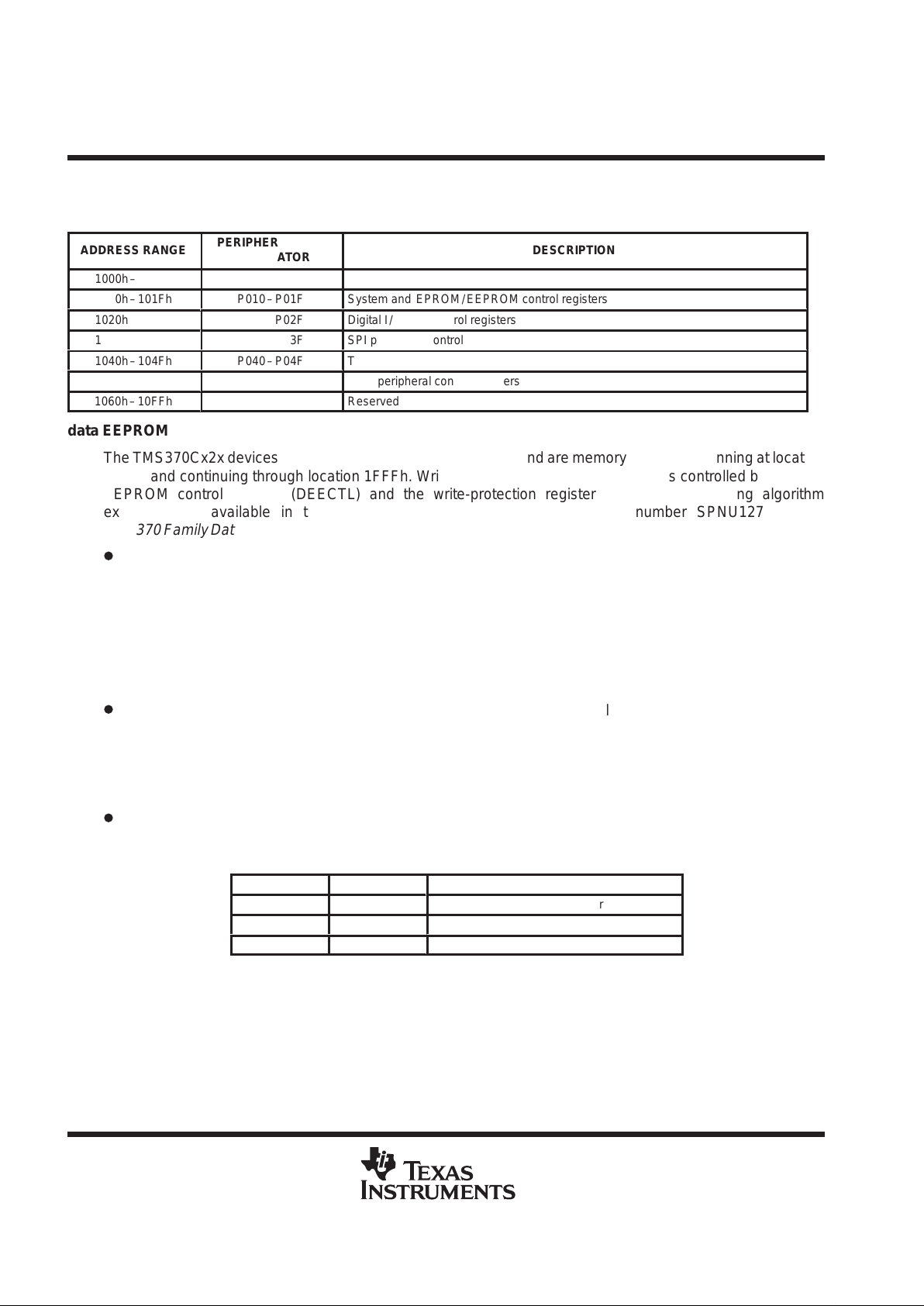

peripheral file (PF)

The TMS370Cx2x control registers contain all the registers necessary to operate the system and peripheral

modules on the device. The instruction set includes some instructions that access the PF directly. These

instructions designate the register by the number of the PF relative to 1000h, preceded by P0 for a hexadecimal

designator or P for a decimal designator. For example, the system-control register 0 (SCCR0) is located at

address 1010h; its peripheral file hexadecimal designator is P010, and its decimal designator is P16. Table 4

shows the TMS370Cx2x PF address map.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

10

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

peripheral file (PF) (continued)

Table 4. TMS370Cx2x Peripheral File Address Map

БББББ

Á

ADDRESS RANGE

БББББ

Á

PERIPHERAL FILE

DESIGNAT OR

БББББББББББББББББББ

Á

DESCRIPTION

1000h–100Fh

P000–P00F Reserved

1010h–101Fh

P010–P01F

System and EPROM/EEPROM control registers

1020h–102Fh

P020–P02F

Digital I/O port control registers

1030h–103Fh

P030–P03F

SPI peripheral control registers

1040h–104Fh

P040–P04F

Timer 1 registers

1050h–105Fh

P050–P05F SCI1 peripheral control registers

1060h–10FFh

P060–P0FF Reserved

data EEPROM

The TMS370Cx2x devices contain 256 bytes of data EEPROM and are memory mapped beginning at location

1F00h and continuing through location 1FFFh. Writing to the data EEPROM module is controlled by the data

EEPROM control register (DEECTL) and the write-protection register (WPR). Programming algorithm

examples are available in the

TMS370 Family User’s Guide

(literature number SPNU127) or the

TMS370 Family Data Manual

(literature number SPNS014B). The data EEPROM features include the following:

D

Programming:

– Bit-, byte-, and block-write/erase modes

– Internal charge pump circuitry. No external EEPROM programming voltage supply is needed.

– Control register: Data EEPROM programming is controlled by the DEECTL located in the PF frame

beginning at location P01A. See Table 5.

– In-circuit programming capability. There is no need to remove the device to program it.

D

Write protection. Writes to the data EEPROM are disabled during the following conditions.

– Reset. All programming of the data EEPROM module is halted.

– Write protection active. There is one write-protect bit per 32-byte EEPROM block.

– Low-power mode operation

D

Write protection can be overridden by applying 12 V to MC.

T able 5. Data EEPROM and Program EPROM Control Registers Memory Map

ADDRESS

SYMBOL

NAME

P01A

DEECTL

Data EEPROM Control Register

P01B

— Reserved

P01C

EPCTL

Program EPROM Control Register

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

11

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

program EPROM

†

The TMS370C722 and SE370C722 devices contain 8K bytes of program EPROM mapped, beginning at

location 6000h and continuing through location 7FFFh, as shown in Figure 3. Reading the program EPROM

modules is identical to reading other internal memory . During programming, the program EPROM is controlled

by the EPROM control register (EPCTL). The program EPROM module features include:

D

Programming

– In-circuit programming capability if V

PP

is applied to MC

– Control register: EPROM programming is controlled by the EPROM control register (EPCTL) located in

the peripheral file (PF) frame at location P01C as shown in Table 5.

D

Write protection: Writes to the program EPROM are disabled under the following conditions:

– Reset: All programming to the EPROM module is halted

– Low-power modes

– 13 V not applied to MC

program ROM

†

The program ROM consists of 4K or 8K bytes of mask programmable read-only memory (see Table 6). The

program ROM is used for permanent storage of data or instructions. Programming of the mask ROM is

performed at the time of device fabrication.

T able 6. Program ROM Memory Map

’x20A ’x22A

ROM size 4K bytes 8K bytes

Memory mapped 7000h–7FFFh 6000h–7FFFh

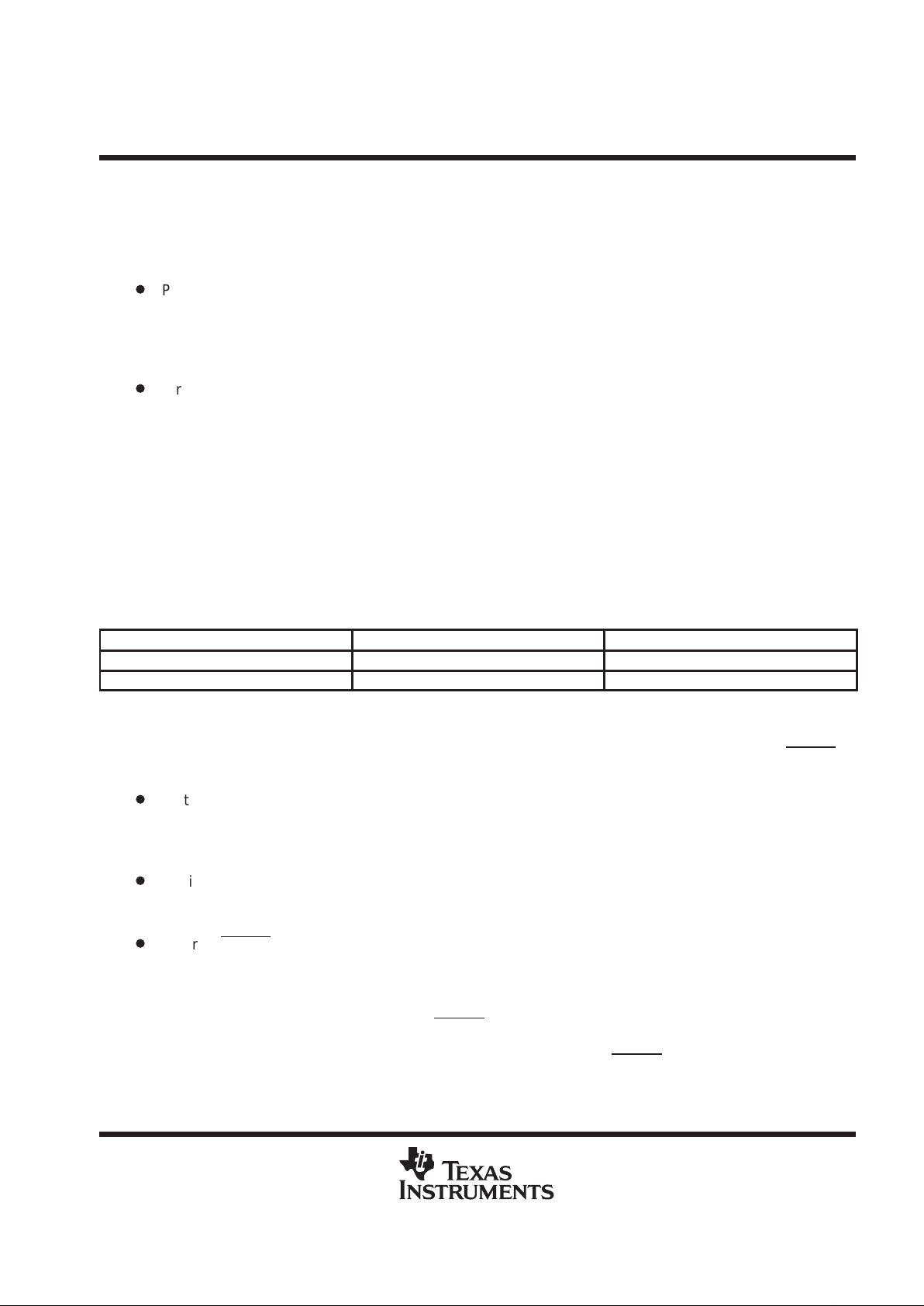

system reset

The system-reset operation ensures an orderly start-up sequence for the TMS370Cx2x CPU-based device.

Three actions can cause a system reset. Two of these actions are internally generated, while one (RESET) is

controlled externally. These actions are as follows:

D

Watchdog (WD) timer. A watchdog-generated reset occurs if an improper value is written to the WD key

register, or if the re-initialization does not occur before the watchdog timer timeout . See the

TMS370 Family

User’s Guide

(literature number SPNU127) or the

TMS370 Family Data Manual

(literature number

SPNS014B) for more information.

D

Oscillator reset. Reset occurs when the oscillator operates outside the recommended operating range. See

the

TMS370 Family User’s Guide

(literature number SPNU127) or the

TMS370 Family Data Manual

(literature number SPNS014B) for more information.

D

External RESET Pin. A low-level signal can trigger an external reset. T o ensure a reset, the external signal

should be held low for one SYSCLK cycle. Signals of less than one SYSCLK can generate a reset. See the

TMS370 Family User’s Guide

(literature number SPNU127) or the

TMS370 Family Data Manual

(literature

number SPNS014B) for more information.

Once a reset source is activated, the external RESET pin is driven (active) low for a minimum of eight SYSCLK

cycles. This allows the ’x2x device to reset external system components. Additionally , if a cold start (V

CC

is off

for several hundred milliseconds) condition or oscillator failure occurs or RESET pin is held low , then the reset

logic holds the device in a reset state for as long as these actions are active.

†

Memory addresses 7FF0h through 7FFFh are reserved for interrupt and reset vectors. Trap vectors, used with TRAP0 through TRAP15

instructions are located between addresses 7FC0h and 7FDFh.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

12

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

system reset (continued)

After a reset, the program can check the oscillator fault flag, the cold start flag and the watchdog reset to

determine the source of the reset. A reset does not clear these flags. Table 7 lists the reset sources.

Table 7. Reset Sources

REGISTER

ADDRESS

PF

BIT NO.

CONTROL BIT

SOURCE OF RESET

SCCR0

1010h

P010

7

COLD START

Cold (power-up)

SCCR0

1010h

P010

4

OSC FLT FLAG

Oscillator out of range

T1CTL2

104Ah

P04A

5

WD OVRFL INT FLAG

Watchdog timer timeout

Once a reset is activated, the following sequence of events occurs:

1. The CPU registers are initialized: ST = 00h, SP = 01h (reset state).

2. Registers A and B are initialized to 00h (no other RAM is changed).

3. The contents of the LSbyte of the reset vector (07FFh) are read and stored in the PCL.

4. The contents of the MSbyte of the reset vector (07FEh) are read and stored in the PCH.

5. Program execution begins with an opcode fetch from the address pointed to by the PC.

The reset sequence takes 20 SYSCLK cycles from the time the reset pulse is released until the first opcode

fetch. During a reset, RAM contents (except for registers A and B) remain unchanged, and the module control

register bits are initialized to their reset state.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

13

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

interrupts

The TMS370 family software-programmable interrupt structure supports flexible on-chip and external-interrupt

configurations to meet real-time interrupt-driven application requirements. The hardware-interrupt structure

incorporates two priority levels as shown in Figure 4. Interrupt level 1 has a higher priority than interrupt

level 2. The two priority levels can be enabled independently by the global-interrupt enable bits (IE1 and IE2)

of the status register.

Each system interrupt is configured independently on either the high- or low-priority chain by the application

program during system initialization. Within each interrupt chain, the interrupt priority is fixed by the position of

the system interrupt. However, since each system interrupt is configured selectively on either the high- or

low-priority interrupt chain, the application program can elevate any system interrupt to the highest priority.

Arbitration between the two priority levels is performed within the CPU. Arbitration within each of the priority

chains is performed within the peripheral modules to support interrupt expansion to future modules. Pending

interrupts are serviced upon completion of current instruction execution, depending on their interrupt mask and

priority conditions.

The TMS370Cx2x has seven hardware system interrupts (plus RESET

) as shown in Table 8. Each system

interrupt has a dedicated interrupt vector located in program memory through which control is passed to the

interrupt service routines. A system interrupt can have multiple interrupt sources (e.g., SCI RXNT has two

interrupt sources). All of the interrupt sources are individually maskable by local interrupt-enable control bits in

the associated peripheral file. Each interrupt source FLAG bit is individually readable for software polling or for

determining which interrupt source generated the associated system interrupt.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

14

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

interrupts (continued)

CPU

NMI

Logic

Enable

IE1

IE2

Level 1 INT

Level 2 INT

Priority

EXT INT 3

INT3 PRI

INT 3

STATUS REG

EXT INT1

INT1 PRI

INT1

SPI INT

SPI PRI

SPI

EXT INT 2

INT2 PRI

INT 2

TIMER 1

T1 PRI

Overflow

Compare1

Ext Edge

Compare2

Input Capture 1

Watchdog

SCI1 INT

RX

BRKDT

RXRDY

TX

TXRDY

TXPRI

RXPRI

Figure 4. Interrupt Control

Four of the system interrupts are generated by on-chip peripheral functions, and three external interrupts are

supported. Software configuration of the external interrupts is performed through the INT1, INT2, and INT3

control registers in peripheral file frame 1. Each external interrupt is individually software configurable for input

polarity (rising or falling) for ease of system interface. External interrupt INT1 is software configurable as either

a maskable or non-maskable interrupt. When INT1 is configured as non-maskable, it cannot be masked by the

individual- or global-enable mask bits. The INT1 NMI bit is protected during non-privileged operation and

therefore should be configured during the initialization sequence following reset. To maximize pin flexibility,

external interrupts INT2 and INT3 can be software configured as general-purpose input/output pins if the

interrupt function is not required (INT1 can be similarly configured as an input pin).

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

15

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

interrupts (continued)

T able 8. Hardware System Interrupts

INTERRUPT SOURCE INTERRUPT FLAG

SYSTEM

INTERRUPT

VECTOR

ADDRESS

PRIORITY

†

External RESET

Watchdog Overflow

Oscillator Fault Detect

COLD START

WD OVRFL INT FLAG

OSC FLT FLAG

RESET

‡

7FFEh, 7FFFh 1

External INT1 INT1 FLAG INT1

‡

7FFCh, 7FFDh 2

External INT2 INT2 FLAG INT2

‡

7FFAh, 7FFBh 3

External INT3 INT3 FLAG INT3

‡

7FF8h, 7FF9h 4

SPI RX/TX Complete SPI INT FLAG SPIINT 7FF6h, 7FF7h 5

Timer 1 Overflow

Timer 1 Compare 1

Timer 1 Compare 2

Timer 1 External Edge

Timer 1 Input-Capture

Watchdog Overflow

T1 OVRFL INT FLAG

T1C1 INT FLAG

T1C2 INT FLAG

T1EDGE INT FLAG

T1IC INT FLAG

WD OVRFL INT FLAG

T1INT

§

7FF4h, 7FF5h 6

SCI RX Data Register Full

SCI RX Break Detect

RXRDY FLAG

BRKDT FLAG

RXINT

‡

7FF2h, 7FF3h 7

SCI TX Data Register Empty TXRDY FLAG TXINT 7FF0h, 7FF1h 8

†

Relative priority within an interrupt level.

‡

Releases microcontroller from STANDBY and HALT low-power modes.

§

Releases microcontroller from STANDBY low-power mode.

privileged operation and EEPROM write-protection override

The TMS370Cx2x family enables the designer to software-configure the system and peripherals to meet the

requirements of a broad variety of applications. The non-privileged mode of operation ensures the integrity of

the system configuration once defined for an end application. Following a hardware reset, the TMS370Cx2x

operates in the privileged mode where all peripheral file registers have unrestricted read/write access and the

application program configures the system during the initialization sequence following reset. As the last step

of system initialization, the PRIVILEGE DISABLE bit (SCCR2.0) is set to 1, causing the device to enter the

non-privileged mode, thus disabling write operations to specific configuration control bits within the peripheral

file. The system configuration bits listed in T able 9 are write-protected during the non-privileged mode and must

be configured by software prior to exiting the privileged mode.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

16

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

privileged operation and EEPROM write-protection override (continued)

Table 9. Privileged Bits

REGISTER

†

NAME LOCATION

CONTROL BIT

SCCR0

P010.5

P010.6

PF AUTO WAIT

OSC POWER

SCCR1

P011.2

P011.4

MEMORY DISABLE

AUTOWAIT DISABLE

SCCR2

P012.0

P012.1

P012.3

P012.4

P012.6

P012.7

PRIVILEGE DISABLE

INT1 NMI

CPU STEST

BUS STEST

PWRDWN/IDLE

HALT/STANDBY

SCIPRI

P05F.4

P05F.5

P05F.6

P05F.6

SCI ESPEN

SCI RX PRIORITY

SCI TX PRIORITY

SCI STEST

T1PRI

P04F.6

P04F.7

T1 PRIORITY

T1 STEST

SPIPRI

P03F.5

P03F.6

P03F.7

SPI ESPEN

SPI PRIORITY

SPI STEST

†

The privileged bits are shown in a bold typeface in Table 11.

The WPO mode provides an external hardware method of overriding the WPR of data EEPROM on the

TMS370Cx2x. WPO mode is entered by applying a 12-V input to the MC pin after the RESET pin input goes

high. The high voltage on the MC pin during the WPO mode is not the programming voltage for the data

EEPROM or program EPROM. All EEPROM programming voltages are generated on-chip. The WPO mode

provides hardware system level capability to modify the personality or calibration information in the data

EEPROM while the device remains in the application, but only while a 12-V external input is present on the MC

pin (normally not available in the end application except in a service or diagnostic environment).

low-power operating modes

The TMS370Cx2x devices have two low-power modes (STANDBY and HALT) and an IDLE mode. For

mask-ROM devices, low-power modes can be disabled permanently through a programmable contact when

the mask is manufactured.

The ST ANDBY and HALT low-power modes significantly reduce power consumption by reducing or stopping

the activity of the various on-chip peripherals when processing is not required. Each of the low-power modes

is entered by executing the IDLE instruction when the PWRDWN/IDLE bit in SCCR2 has been set to 1. The

HALT/STANDBY bit in SCCR2 controls the low-power mode selection.

In the STANDBY mode (HALT/STANDBY = 0), all CPU activity and most peripheral module activity stops;

however, the oscillator , internal clocks, timer 1, and receive start-bit detection circuit of the SCI1 remain active.

System processing is suspended until a qualified interrupt (hardware RESET

, external interrupt on INT1, INT2,

INT3, timer 1 interrupt, or low level on the receive pin of the SCI1) is detected.

In the HALT mode (HALT/STANDBY = 1), the TMS370Cx2x is in its lowest power consumption mode. The

oscillator and internal clocks are stopped, causing all internal activity to be halted. System activity is suspended

until a qualified interrupt (hardware RESET

, external interrupt on the INT1, INT2, INT3, or low level on the

receive pin of the SCI1) is detected. The power-down mode-selection bits are summarized in Table 10.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

17

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

low-power operating modes (continued)

Table 10. Low-Power/Idle Control Bits

POWER-DOWN CONTROL BITS

PWRDWN/IDLE

(SCCR2.6)

HALT/STANDBY

(SCCR2.7)

MODE SELECTED

1 0 STANDBY

1 1 HALT

0 X

†

IDLE

†

Don’t care

When low-power modes are disabled through a programmable contact, writing to the SCCR2.6-7 bits is ignored.

In addition, if an IDLE instruction is executed when low-power modes are disabled, the device always enters

the IDLE mode.

T o provide a method for always exiting low-power modes for mask-ROM devices, INT1 is enabled automatically

as a nonmaskable interrupt (NMI) during low-power modes when the hard watchdog mode is selected. This

means that the NMI always is generated, regardless of the interrupt enable flags.

The following information is preserved throughout both the STANDBY and HALT modes: RAM (register file),

CPU registers (SP , PC, and ST), I/O pin direction and output data, and status registers of all on-chip peripheral

functions. Since all CPU instruction processing is stopped during the ST ANDBY and HAL T modes, the clocking

of the WD timer is inhibited.

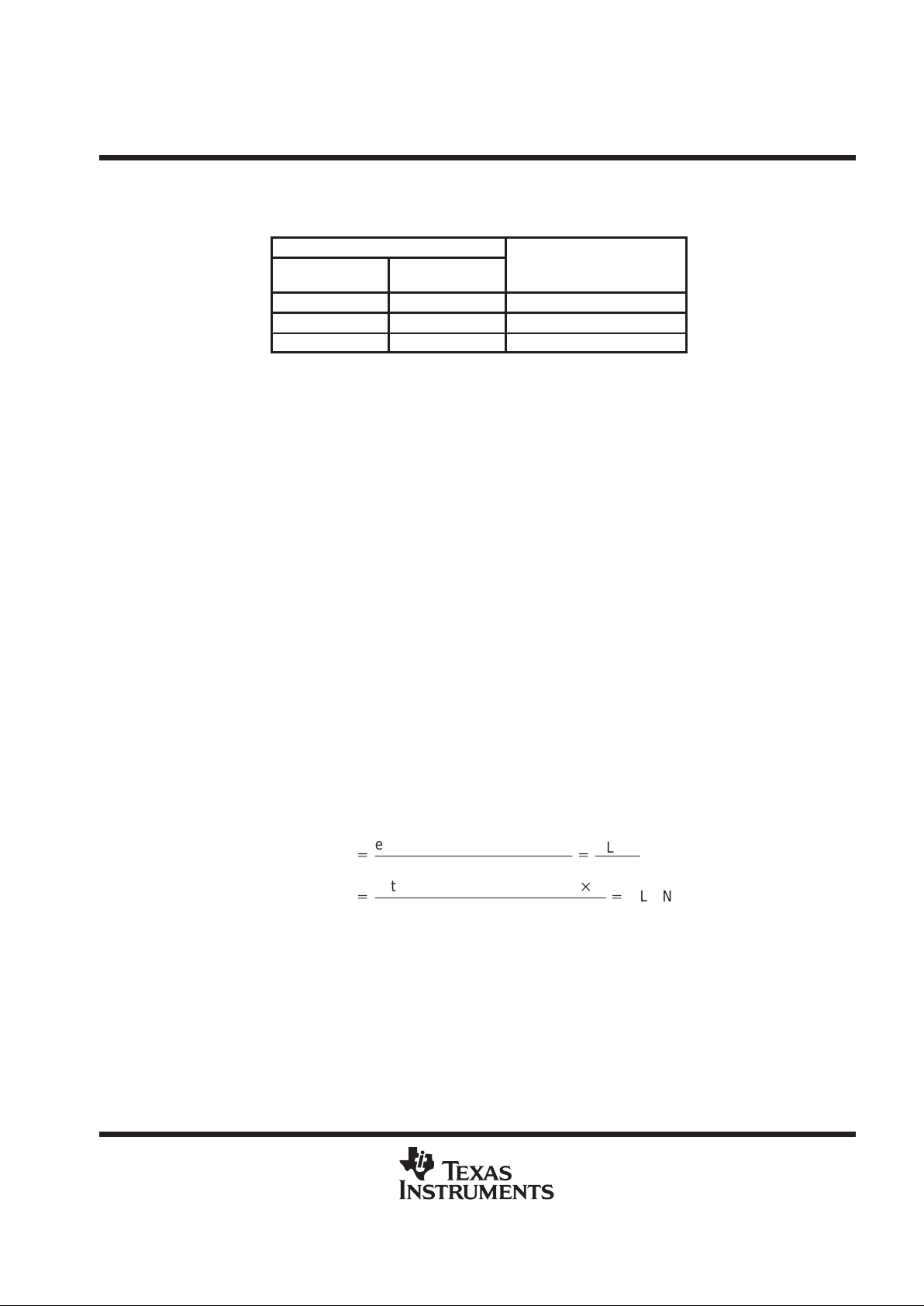

clock modules

The ’x2x family provides two clock options that are referred to as divide-by-1 (phase-locked loop) and

divide-by-4 (standard oscillator). Both the divide-by-1 and divide-by-4 options are configurable during the

manufacturing process of a TMS370 MCU. The ’x2x masked ROM devices offer both options to meet system

engineering requirements. Only one of the two clock options is allowed on each ROM device.

The divide-by-1 clock module option provides reduced electromagnetic interference (EMI) with no added cost.

The divide-by-1 provides a one-to-one match of the external resonator frequency (CLKIN) to the internal system

clock (SYSCLK) frequency , whereas the divide-by-4 produces a SYSCLK which is one-fourth the frequency of

the external resonator. Inside of the divide-by-1 module, the frequency of the external resonator is multiplied

by four, and the clock module then divides the resulting signal by four to provide the four-phased internal system

clock signals. The resulting SYSCLK is equal to the resonator frequency. These are formulated as follows:

Divide-by-4 option : SYSCLK

+

external resonator frequency

4

+

CLKIN

4

Divide-by-1 option : SYSCLK

+

external resonator frequency 4

4

+

CLKIN

The main advantage of a divide-by-1 oscillator is the improved EMI performance. The harmonics of low-speed

resonators extend through fewer of the emissions spectrum than the harmonics of faster resonators. The

divide-by-1 reduces the resonator speed by four, and this results in a steeper decay of emissions produced by

the oscillator.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

18

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

system configuration registers

Table 11 contains peripheral file frame 1 system configuration and control register functions for controlling

EEPROM programming. The privileged bits are shown in bold typeface and shaded.

Table 11. Peripheral File Frame 1: System Configuration and Control Registers

†

PF BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 REG

P010

COLD

START

OSC

POWER

PF AUTO

WAIT

OSC FLT

FLAG

MC PIN

WPO

MC PIN

DATA

—

µP/µC

MODE

SCCR0

P011 — — —

AUTOWAIT

DISABLE

—

MEMORY

DISABLE

— — SCCR1

P012

HALT/

STANDBY

PWRDWN/

IDLE

—

BUS

STEST

CPU

STEST

—

INT1

NMI

PRIVILEGE

DISABLE

SCCR2

P013

to

P016

Reserved

P017

INT1

FLAG

INT1

PIN DATA

— — —

INT1

POLARITY

INT1

PRIORITY

INT1

ENABLE

INT1

P018

INT2

FLAG

INT2

PIN DATA

—

INT2

DATA DIR

INT2

DATA OUT

INT2

POLARITY

INT2

PRIORITY

INT2

ENABLE

INT2

P019

INT3

FLAG

INT3

PIN DATA

—

INT3

DATA DIR

INT3

DATA OUT

INT3

POLARITY

INT3

PRIORITY

INT3

ENABLE

INT3

P01A BUSY — — — — AP W1W0 EXE DEECTL

P01B Reserved

P01C BUSY VPPS — — — — W0 EXE EPCTL

P01D

P01E

P01F

Reserved

†

Privileged bits are shown in bold typeface.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

19

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

peripheral file frame 2

Peripheral file frame 2 contains the digital I/O pin configuration and control registers. Table 12 and Table 13

detail the specific addresses, registers, and control bits within the peripheral file frame.

Table 12. Peripheral File Frame 2: Digital Port Control Registers

PF BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

P020 Reserved APORT1

P021 Port A Control Register 2 (must be 0) APORT2

P022 Port A Data ADAT A

P023 Port A Direction ADIR

P024 Reserved BPOR T1

P025 Port B Control Register 2 (must be 0) BPORT2

P026 Port B Data BDAT A

P027 Port B Direction BDIR

P028 Reserved CPORT1

P029 — — — — — — —

Port C

Control

Register 2

(must be 0)

CPORT2

P02A — — — — — — — Port C Data CDATA

P02B — — — — — — —

Port C

Direction

CDIR

P02C Port D Control Register 1 (must be 0) — — — DPORT1

P02D Port D Control Register 2 (must be 0)

†

— — — DPORT2

P02E Port D Data — — — DDATA

P02F Port D Direction — — — DDIR

†

To configure pin D3 as SYSCLK, set port D control register 2 = 08h.

Table 13. Port Configuration Register Setup

PORT PIN

abcd

00q1

abcd

00y0

A 0–7 Data out q Data in y

B 0–7 Data out q Data in y

C 0 Data out q Data in y

D 3–7 Data out q Data in y

a = Port × Control Register 1

‡

b = Port × Control Register 2

c = Data

d = Direction

‡

DPORT only

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

20

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

programmable timer 1

The programmable timer module of the TMS370Cx2x provides the enhanced timer resources required to

perform real-time system control. The Timer 1 module contains the general-purpose timer T1 and the watchdog

(WD) timer. The two independent 16-bit timers (T1 and WD) allow program selection of input clock sources

(real-time, external event, or pulse-accumulate) with multiple 16-bit registers (input-capture and compare) for

special timer function control. The timer 1 module includes three external device pins that can be used for

multiple counter functions (operation-mode dependent), or used as general-purpose I/O pins. The T1 module

is shown in Figure 5.

T1PWM

T1EVT

T1IC/CR

16

Interrupt

Logic

Interrupt

Logic

16-Bit Watchdog

Counter (Aux. Timer)

8-Bit

Prescaler

16-Bit

Compare Register

16-Bit

Capt/Comp Register

PWM

Toggle

MUX

MUX

Edge

Select

16-Bit Counter

Figure 5. Timer 1 Block Diagram

D

Three T1 I/O pins

– T1IC/CR: T1 input capture / counter-reset input pin, or general-purpose bidirectional I/O pin

– T1PWM: T1 pulse-width-modulation (PWM) output pin, or general-purpose bidirectional I/O pin

– T1EVT: T1 event input pin, or general-purpose bidirectional I/O pin

D

Two operational modes:

– Dual-compare mode: Provides PWM signal

– Capture/compare mode: Provides input capture pin

D

One 16-bit general-purpose resettable counter

D

One 16-bit compare register with associated compare logic

D

One 16-bit capture/compare register, which, depending on the mode of operation, operates as either

capture or compare register

D

One 16-bit WD counter can be used as an event counter, a pulse accumulator, or an interval timer if WD

feature is not needed.

D

Prescaler/clock sources that determine one of eight clock sources for general-purpose timer

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

21

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

programmable timer 1 (continued)

D

Selectable edge-detection circuitry that, depending on the mode of operation, senses active transitions on

the input capture pins (T1IC/CR)

D

Interrupts that can be generated on the occurrence of:

– A capture

– A compare equal

– A counter overflow

– An external edge detection

D

Sixteen T1 module control registers located in the PF frame beginning at address P040

The T1 module control registers are listed in Table 14.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

22

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

programmable timer 1 (continued)

Table 14. Timer Module Register Memory Map

PF

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

REG

Modes: Dual-Compare and Capture/Compare

P040

Bit 15 T1Counter MSbyte Bit 8

T1CNTR

P041

Bit 7 T1 Counter LSbyte Bit 0

P042

Bit 15 Compare Register MSbyte Bit 8

T1C

P043

Bit 7 Compare Register LSbyte Bit 0

P044

Bit 15 Capture/Compare Register MSbyte Bit 8

T1CC

P045

Bit 7 Capture/Compare Register LSbyte Bit 0

P046

Bit 15 Watchdog Counter MSbyte Bit 8

WDCNTR

P047

Bit 7 Watchdog Counter LSbyte Bit 0

P048

Bit 7 Watchdog Reset Key Bit 0

WDRST

ÁÁ

Á

P049

ÁÁ

Á

WD OVRFL

TAP SEL

†

ÁÁ

Á

WD INPUT

SELECT2

†

ÁÁÁ

Á

WD INPUT

SELECT1

†

ÁÁ

Á

WD INPUT

SELECT0

†

ÁÁÁ

Á

—

ÁÁ

Á

T1 INPUT

SELECT2

ÁÁ

Á

T1 INPUT

SELECT1

ÁÁÁ

Á

T1 INPUT

SELECT0

ÁÁ

Á

T1CTL1

P04A

WD OVRFL

RST ENA

†

WD OVRFL

INT ENA

WD OVRFL

INT FLAG

T1 OVRFL

INT ENA

T1 OVRFL

INT FLAG

—

—

T1

SW RESET

T1CTL2

Mode: Dual-Compare

ÁÁ

Á

P04B

ÁÁ

Á

T1EDGE

INT FLAG

ÁÁ

Á

T1C2

INT FLAG

ÁÁÁ

Á

T1C1

INT FLAG

ÁÁ

Á

—

ÁÁÁ

Á

—

ÁÁ

Á

T1EDGE

INT ENA

ÁÁ

Á

T1C2

INT ENA

ÁÁÁ

Á

T1C1

INT ENA

ÁÁ

Á

T1CTL3

P04C

T1

MODE=0

T1C1

OUT ENA

T1C2

OUT ENA

T1C1

RST ENA

T1CR

OUT ENA

T1EDGE

POLARITY

T1CR

RST ENA

T1EDGE

DET ENA

T1CTL4

Mode: Capture/Compare

ÁÁ

Á

P04B

ÁÁ

Á

T1EDGE

INT FLAG

ÁÁ

Á

—

ÁÁÁ

Á

T1C1

INT FLAG

ÁÁ

Á

—

ÁÁÁ

Á

—

ÁÁ

Á

T1EDGE

INT ENA

ÁÁ

Á

—

ÁÁÁ

Á

T1C1

INT ENA

ÁÁ

Á

T1CTL3

P04C

T1

MODE = 1

T1C1

OUT ENA

—

T1C1

RST ENA

—

T1EDGE

POLARITY

—

T1EDGE

DET ENA

T1CTL4

Modes: Dual-Compare and Capture/Compare

ÁÁ

Á

P04D

ÁÁ

Á

—

ÁÁ

Á

—

ÁÁÁ

Á

—

ÁÁ

Á

—

ÁÁÁ

Á

T1EVT

DATA IN

ÁÁ

Á

T1EVT

DATA OUT

ÁÁ

Á

T1EVT

FUNCTION

ÁÁÁ

Á

T1EVT

DATA DIR

ÁÁ

Á

T1PC1

ÁÁ

Á

P04E

ÁÁ

Á

T1PWM

DATA IN

ÁÁ

Á

T1PWM

DATA OUT

ÁÁÁ

Á

T1PWM

FUNCTION

ÁÁ

Á

T1PWM

DATA DIR

ÁÁÁ

Á

T1IC/CR

DATA IN

ÁÁ

Á

T1IC/CR

DATA OUT

ÁÁ

Á

T1IC/CR

FUNCTION

ÁÁÁ

Á

T1IC/CR

DATA DIR

ÁÁ

Á

T1PC2

ÁÁ

Á

P04F T1 STEST

T1

PRIORITY

ÁÁÁ

Á

—

ÁÁ

Á

—

ÁÁÁ

Á

—

ÁÁ

Á

—

ÁÁ

Á

—

ÁÁÁ

Á

—

ÁÁ

Á

T1PRI

†

Once the WD OVRFL RST ENA bit is set, these bits cannot be changed until a reset; this applies only to the standard

watchdog and to simple counter . In the hard watchdog, these bits can be modified at any time; the WD INPUT SELECT2

bits are ignored.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

23

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

programmable timer 1 (continued)

Figure 6 shows the Timer 1 capture/compare mode block diagram. The annotations on the diagram identify the

register and the bit(s) in the PF. For example, the actual address of T1CTL2.0 is 104Ah, bit 0, in the T1CTL2

register.

T1CTL4.2

16

Compare=

Edge

Select

T1IC/CR

T1EDGE POLARITY

T1EDGE DET ENA

Prescale

Clock

Source

16-Bit

Counter

MSB

LSB

T1CNTR.15-0

Reset

T1C1

RST ENA

T1 SW

RESET

T1CTL2.0

T1CTL4.4

T1PC2.3-0

T1CTL4.0

T1EDGE INT FLAG

T1EDGE INT ENA

T1CTL3.7

T1CTL3.2

T1 OVRFL INT FLAG

T1 OVRFL INT ENA

T1CTL2.3

T1CTL2.4

T1C1 INT FLAG

T1C1 INT ENA

T1CTL3.5

T1CTL3.0

T1C1

OUT ENA

T1PWM

T1CTL4.6

Toggle

T1PC2.7-4

16-Bit

Capt/Comp

MSB

LSB

Register

T1CC.15-0

T1C.15-0

16-Bit

Compare

MSB

LSB

Register

T1 PRIORITY

T1PRI.6

Level 1 Int

Level 2 Int

0

1

Figure 6. Capture/Compare Mode

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

24

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

programmable timer 1 (continued)

Figure 7 shows the Timer 1 dual-compare mode block diagram. The annotations on the diagram identify the

register and the bit(s) in the peripheral frame. For example, the actual address of T1CTL2.0 is 104Ah, bit 0, in

the T1CTL2 register.

T1CTL4.1

T1CTL4.4

Prescaler

Clock

Source

16-Bit

Counter

16-Bit

16

Compare=

Compare=

Reset

T1C1

RST ENA

T1 SW

RESET

Edge

Select

T1EDGE DET ENA

Output

Enable

Capt/Comp

Register

MSB

LSB

MSB

LSB

T1CR OUT ENA

T1IC/CR

T1EDGE POLARITY

Toggle

16-Bit

Compare

MSB

LSB

Register

T1CC.15-0

T1C1 INT FLAG

T1CTL3.0

T1CTL3.5

T1C1 INT ENA

T1C2 INT FLAG

T1CTL3.1

T1CTL3.6

T1C2 INT ENA

T1 OVRFL INT FLAG

T1CTL2.4

T1CTL2.3

T1 OVRFL INT ENA

T1EDGE INT FLAG

T1CTL3.2

T1CTL3.7

T1EDGE INT ENA

T1 PRIORITY

T1C2 OUT ENA

T1C1 OUT ENA

T1CTL4.3

T1CTL4.6

T1CTL4.5

T1PWM

T1PC2.7-4

T1PRI.6

T1C.15-0

T1CNTR.15-0

T1CTL2.0

T1CR

RST ENA

T1PC2.3-0

T1CTL4.0

T1CTL4.2

Level 1 Int

Level 2 Int

0

1

Figure 7. Dual-Compare Mode

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

25

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

programmable timer 1 (continued)

The TMS370Cx2x device includes a 24-bit WD timer, contained in the T1 module, which can be programmed

as an event counter, pulse accumulator , or interval timer if the watchdog function is not used. The WD monitors

software and hardware operation, and implements a system reset when the WD counter is not serviced properly

(WD counter overflow or WD counter is re-initialized by an incorrect value). The WD can be configured as one

of the three mask options as follows: standard watchdog, hard WD, or simple counter.

D

Standard watchdog configuration (see Figure 8) for ’C722 EPROM and mask-ROM devices:

– Watchdog mode

– Ten different WD overflow rates ranging from 6.55 ms to 3.35 s at 5-MHz SYSCLK

– A WD reset key (WDRST) register clears the watchdog counter (WDCNTR) when a correct value is

written.

– Generates a system reset if an incorrect value is written to the watchdog reset key or if the counter

overflows

– A watchdog overflow flag (WD OVRFL INT FLAG) bit indicates whether the WD timer initiated a

system reset.

– Non-watchdog mode

– Watchdog timer can be configured as an event counter, pulse accumulator or an interval timer.

16-Bit

Watchdog Counter

Reset

Prescaler

Clock

Watchdog Reset Key

WD OVRFL

TAP SEL

WD OVRFL

RST ENA

System Reset

T1CTL1.7

WDRST.7-0

WDCNTR.15-0

T1CTL2.7

T1CTL2.5

WD OVRFL

INT ENA

Interrupt

T1CTL2.6

WD OVRFL

INT FLAG

Figure 8. Standard Watchdog

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

26

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

programmable timer 1 (continued)

D

Hard watchdog configuration (see Figure 9) for ’C722 EPROM and mask-ROM devices:

– Eight different WD overflow rates ranging from 26.2 ms to 3.35 s at 5-MHz SYSCLK

– A WD reset key (WDRST) register clears the watchdog counter (WDCNTR) when a correct value is

written.

– Generates a system reset if an incorrect value is written to the WDRST or if the counter overflows

– A WD overflow flag (WD OVRFL INT FLAG) bit indicates whether the WD timer initiated a system reset.

– Automatic activation of the WD timer upon power-up reset

– INT1 is enabled as a nonmaskable interrupt during low power modes.

16-Bit

Watchdog Counter

Reset

Prescaler

Clock

Watchdog Reset Key

WD OVRFL

TAP SEL

System Reset

T1CTL1.7

WDRST.7-0

WDCNTR.15-0

T1CTL2.5

WD OVRFL

INT FLAG

Figure 9. Hard Watchdog

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

27

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

programmable timer 1 (continued)

D

Simple counter configuration (see Figure 10) for mask-ROM devices only

– Simple counter can be configured as an event counter, pulse accumulator, or internal timer.

16-Bit

Watchdog Counter

Reset

Prescaler

Clock

Watchdog Reset Key

WD OVRFL

TAP SEL

T1CTL1.7

WDRST.7-0

WDCNTR.15-0

T1CTL2.5

WD OVFL

INT FLAG

WD OVRFL

INT ENA

Interrupt

T1CTL2.6

Figure 10. Simple Counter

serial peripheral interface

The SPI is a high-speed synchronous serial I/O port that allows a serial bit stream of programmed length

(1 to 8 bits) to be shifted into and out of the device at a programmable bit transfer rate. The SPI normally is used

for communications between the microcontroller and external peripherals or another microcontroller. Typical

applications include external I/O or peripheral expansion by way of devices such as shift registers, display

drivers, and A/D converters. Multi-device communications are supported by the master/slave operation of the

SPI. The SPI module features include the following:

D

Three external pins

– SPISOMI: SPI slave output/master input pin or general-purpose bidirectional I/O pin

– SPISIMO: SPI slave input/master output pin or general-purpose bidirectional I/O pin

– SPICLK: SPI serial clock pin or general-purpose bidirectional I/O pin

D

Two operational modes: Master and slave

D

Eight programmable baud rates

– Maximum baud rate in master mode: 2.5M bps at 5 MHz SYSCLK

SPI BAUD RATE

+

SYSCLK

2 2

b

where b=bit rate in SPICCR.5-3 (range 0–7)

– Maximum baud rate in slave mode: 625K bps at 5 MHz SYSCLK

SPI BAUD RA TE < SYSCLK/8

D

Data word format: one to eight data bits

D

Simultaneous receiver and transmitter operations (transmit function can be disabled in software)

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

28

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

serial peripheral interface (continued)

D

Transmitter and receiver operations occur through interrupt-driven or polled algorithms.

D

Seven SPI module control registers located in control register frame beginning at address P030h

The SPI module control registers are listed in Table 15.

Table 15. SPI Module Control Register Memory Map

PF

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

REG

ÁÁ

Á

P030

ÁÁ

Á

SPI SW

RESET

ÁÁÁ

Á

CLOCK

POLARITY

ÁÁ

Á

SPI BIT

RATE2

ÁÁ

Á

SPI BIT

RATE1

ÁÁÁ

Á

SPI BIT

RATE0

ÁÁ

Á

SPI

CHAR2

ÁÁ

Á

SPI

CHAR1

ÁÁÁ

Á

SPI

CHAR0

ÁÁ

Á

SPICCR

P031

RECEIVER

OVERRUN

SPI INT

FLAG

—

—

—

MASTER/

SLAVE

TALK

SPI INT

ENA

SPICTL

ÁÁ

Á

P032

to

P036

Reserved

ÁÁ

Á

P037

RCVD7

RCVD6

RCVD5

RCVD4

RCVD3

RCVD2

RCVD1

RCVD0

SPIBUF

P038 Reserved

P039

SDAT7

SDAT6

SDAT5

SDAT4

SDAT3

SDAT2

SDAT1

SDAT0

SPIDAT

ÁÁ

Á

P03A

to

P03C

Reserved

ÁÁ

Á

ÁÁ

Á

P03D

ÁÁ

Á

—

ÁÁÁ

Á

—

ÁÁ

Á

—

ÁÁ

Á

—

ÁÁÁ

Á

SPICLK

DATA IN

ÁÁ

Á

SPICLK

DATA OUT

ÁÁ

Á

SPICLK

FUNCTION

ÁÁÁ

Á

SPICLK

DATA DIR

ÁÁ

Á

SPIPC1

P03E

SPISIMO

DATA IN

SPISIMO

DATA OUT

SPISIMO

FUNCTION

SPISIMO

DATA DIR

SPISOMI

DATA IN

SPISOMI

DATA OUT

SPISOMI

FUNCTION

SPISOMI

DATA DIR

SPIPC2

ÁÁ

Á

P03F

SPI

STEST

SPI

PRIORITY

SPI

ESPEN

ÁÁ

Á

—

ÁÁÁ

Á

—

ÁÁ

Á

—

ÁÁ

Á

—

ÁÁÁ

Á

—

ÁÁ

Á

SPIPRI

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

29

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

serial peripheral interface (continued)

The SPI block diagram is listed in Figure 11.

SPIBUF Buffer

Register

SPIDAT

Data Register

SPIBUF.7-0

State Control

SPI CHAR

SPI BIT RATE

CLOCK POLARITY

SPI INT FLAG

SPICTL.6

SPIINT ENA

SPICTL.0

RECEIVER

OVERRUN

8

SPIDAT.7-0

SPICTL.1

TALK

201

3

4

5

SPICCR.2-0

SPICCR.5-3

System

Clock

SPICCR.6

SPICLK

MASTER/SLAVE

†

SPICTL.7

Level 2 INT

SPIPRI.6

1

SPIPC2.7-4

SPISIMO

SPICTL.2

SPIPC1.3-0

SPISOMI

SPIPC2.3-0

Level 1 INT

0

†

The diagram shows slave mode.

Figure 11. SPI Block Diagram

serial communications interface 1 (SCI1)

The TMS370x2x devices include a serial communications interface 1 (SCI1) module. The SCI1 module

supports digital communications between the TMS370 devices and other asynchronous peripherals, and uses

the standard non-return-to-zero (NRZ) format. The SCI1’s receiver and transmitter are double buffered, and

each has separate enable and interrupt bits. Both can operate independently or simultaneously in the full-duplex

mode. T o ensure data integrity , the SCI1 checks received data for break detection, parity, overrun, and framing

errors. The bit rate (baud) is programmable to over 65,000 speeds through a 16-bit baud-select register.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

30

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

serial communications interface 1 (SCI1) (continued)

Features of the SCI1 module include:

D

Three external pins:

– SCITXD: SCI transmit output pin or general purpose bidirectional I/O pin

– SCIRXD: SCI receive input pin or general purpose bidirectional I/O pin

– SCICLK: SCI bidirectional serial clock pin, or general purpose bidirectional I/O pin

D

Two communications modes: asynchronous and isosynchronous

†

D

Baud rate: 64K programmable rates

– Asynchronous mode: 3 bps to 156K bps at 5 MHz SYSCLK

ASYNCHRONOUS BAUD

+

SYSCLK

(BAUD REG)1) 32

– Isosynchronous mode: 39 bps to 2.5M bps at 5 MHz SYSCLK

ISOSYNCHRONOUS BAUD

+

SYSCLK

(BAUD REG)1) 2

D

Data word format

– One start bit

– Data word length programmable from 1 to 8 bits

– Optional even/odd/no parity bit

– One or two stop bits

D

Four error-detection flags: parity, overrun, framing, and break detection

D

Two wake-up multiprocessor modes: Idle-line and address bit

D

Half or full-duplex operation

D

Double-buffered receive and transmit functions

D

Interrupt driven or polled algorithms with status flags control transmitter (TX) and receiver (RX) operations.

– Transmitter: TXRDY flag (transmitter buffer register is ready to receive another character) and TX

EMPTY flag (transmitter shift register is empty)

– Receiver: RXRDY flag (receive buffer register ready to receive another character), BRKDT flag (break

condition occurred), and RX ERROR monitoring four interrupt conditions

– Separate enable bits for transmitter and receiver interrupts

– NRZ (non-return-to-zero) format

D

Eleven SCI1 module control registers are located in control register frame beginning at address P050h.

†

Isosynchronous = Isochronous

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

31

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

serial communications interface 1 (SCI1) (continued)

The SCI1 module control registers are listed in Table 16.

Table 16. Peripheral File Frame 5: SCI1 Module Control Registers

†

PF BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 REG

P050

STOP

BITS

EVEN/ODD

PARITY

PARITY

ENABLE

ASYNC/

ISOSYNC

ADDRESS

IDLE WUP

SCI

CHAR2

SCI

CHAR1

SCI

CHAR0

SCICCR

P051 — —

SCI SW

RESET

CLOCK TXWAKE SLEEP TXENA RXENA SCICTL

P052 Bit 15 Baud Rate Select Register MSB Bit 8

BAUD

MSB

P053 Bit 7 Baud Rate Select Register LSB Bit 0

BAUD

LSB

P054 TXRDY

TX

EMPTY

— — — — —

SCI TX

INT ENA

TXCTL

P055

RX

ERROR

RXRDY BRKDT FE OE PE RXWAKE

SCI RX

INT ENA

RXCTL

P056 Reserved

P057 Receive Data Buffer Register RXBUF

P058 Reserved

P059 Transmit Data Buffer Register TXBUF

P05A

P05B Reserved

P05C

P05D — — — —

SCICLK

DATA IN

SCICLK

DATA OUT

SCICLK

FUNCTION

SCICLK

DATA DIR

SCIPC1

P05E

SCI TXD

DATA IN

SCI TXD

DATA OUT

SCI TXD

FUNCTION

SCI TXD

DATA DIR

SCI RXD

DATA IN

SCI RXD

DATA OUT

SCI RXD

FUNCTION

SCI RXD

DATA DIR

SCIPC2

P05F

SCI

STEST

SCI TX

PRIORITY

SCI RX

PRIORITY

SCI

ESPEN

— — — — SCIPRI

†

Privileged bits are shown in bold typeface.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

32

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

serial communications interface 1 (SCI1) (continued)

The SCI1 module block diagram is illustrated in Figure 12.

RXCTL.4–2

FE OE PE

RX ERROR

SCICTL.3

TXWAKE

SCICCR.6 SCICCR.5

EVEN/ODD ENABLE

PARITY

Frame Format and Mode

WUT

TXBUF.7–0

Transmit Data

Buffer Reg.

TXSHF Reg.

TXCTL.7

TXCTL.6

TXRDY

TX EMPTY

SCI TX Interrupt

TXCTL.0

TXENA

8

SCICTL.4

BAUD MSB. 7–0

Baud Rate

MSbyte Reg.

BAUD LSB. 7–0

Baud Rate

LSbyte Reg.

CLOCK

SCICTL.1

SCITXD

SCI TX INT ENA

RXCTL.7

ERR

RXSHF Reg.

RXCTL.1

8

Receive Data

Buffer Reg.

RXBUF.7–0

RXENA

RXCTL.6

RXCTL.5

RXRDY

BRKDT

SCI RX Interrupt

RXCTL.0

SCI RX INT ENA

SCIPRI.6

SCIPRI.5

Level 1 INT

Level 2 INT

Level 1 INT

Level 2 INT

SCITX PRIORITY

SCIRX PRIORITY

SCITXD

SCIPC2.7–4

SCICLK

SCIPC1.3–0

SCIRXD

SCIRXD

SCIPC2.3–0

SCICTL.0

RXWAKE

1

SYSCLK

0

1

0

1

Figure 12. SCI1 Block Diagram

instruction set overview

Table 17 provides an opcode-to-instruction cross reference of all 73 instructions and 274 opcodes of the

‘370Cx2x instruction set. The numbers at the top of this table represent the most significant nibble (MSN) of the

opcode while the numbers at the left side of the table represent the least significant nibble (LSN). The instruction

of these two opcode nibbles contains the mnemonic, operands, and byte/cycle particular to that opcode.

For example, the opcode B5h points to the CLR A instruction. This instruction contains one byte and executes

in eight SYSCLK cycles.

TMS370Cx2x

8-BIT MICROCONTROLLER

SPNS018C – FEBRUARY 1993 – REVISED FEBRUARY 1997

POST OFFICE BOX 1443 HOUSTON, TEXAS 77251–1443

• 33

Table 17. TMS370 Family Opcode/Instruction Map

†

MSN

01234567 8 9 A B C D E F

0

JMP

#ra

2/7

INCW

#ra,Rd

3/11

MOV

Ps,A

2/8

CLRC /

TST A

1/9

MOV

A,B

1/9

MOV

A,Rd

2/7

TRAP

15

1/14

LDST

n

2/6

1JNra

2/5

MOV

A,Pd

2/8

MOV

B,Pd

2/8

MOV

Rs,Pd

3/10

MOV

Ps,B

2/7

MOV

B,Rd

2/7

TRAP

14

1/14

MOV

#ra[SP],A

2/7

2JZra

2/5

MOV

Rs,A

2/7

MOV

#n,A

2/6

MOV

Rs,B

2/7

MOV

Rs,Rd

3/9

MOV

#n,B

2/6

MOV

B,A

1/8

MOV

#n,Rd

3/8

MOV

Ps,Rd

3/10

DEC

A

1/8

DEC

B

1/8

DEC

Rd

2/6

TRAP

13

1/14

MOV

A,*ra[SP]

2/7

3JCra

2/5

AND

Rs,A

2/7

AND

#n,A

2/6

AND

Rs,B

2/7

AND

Rs,Rd

3/9

AND

#n,B

2/6

AND

B,A

1/8

AND

#n,Rd

3/8

AND

A,Pd

2/9

AND

B,Pd

2/9

AND

#n,Pd

3/10

INC

A

1/8

INC

B

1/8

INC

Rd

2/6

TRAP

12

1/14

CMP

*n[SP],A

2/8

4JPra

2/5

OR

Rs,A

2/7

OR

#n,A

2/6

OR

Rs,B

2/7

OR

Rs,Rd

3/9

OR

#n,B

2/6

OR

B,A

1/8

OR

#n,Rd

3/8

OR

A,Pd

2/9

OR

B,Pd

2/9

OR

#n,Pd

3/10

INV

A

1/8

INV

B

1/8

INV

Rd

2/6

TRAP

11

1/14

extend

inst,2

opcodes

L

S

5

JPZ

ra

2/5

XOR

Rs,A

2/7

XOR

#n,A

2/6

XOR

Rs,B

2/7

XOR

Rs,Rd

3/9

XOR

#n,B

2/6

XOR

B,A

1/8

XOR

#n,Rd

3/8

XOR

A,Pd

2/9

XOR

B,Pd

2/9

XOR

#n,Pd

3/10

CLR

A

1/8

CLR

B

1/8

CLR

Rn

2/6

TRAP

10

1/14

N

6

JNZ

ra

2/5

BTJO

Rs,A,ra

3/9

BTJO

#n,A,ra

3/8

BTJO

Rs,B,ra

3/9

BTJO

Rs,Rd,ra

4/11

BTJO

#n,B,ra

3/8

BTJO

B,A,ra

2/10

BTJO

#n,Rd,ra

4/10

BTJO

A,Pd,ra

3/11

BTJO

B,Pd,ra

3/10

BTJO

#n,Pd,ra

4/11

XCHB

A

1/10

XCHB A /

TST B

1/10

XCHB

Rn

2/8

TRAP

9

1/14

IDLE

1/6

7

JNC

ra

2/5

BTJZ

Rs.,A,ra

3/9

BTJZ

#n,A,ra

3/8

BTJZ

Rs,B,ra