Page 1

TMS320DM647/DM648

Video Port/VCXO Interpolated Control (VIC)

Port

User's Guide

Literature Number: SPRUEM1

May 2007

Page 2

2 SPRUEM1 – May 2007

Submit Documentation Feedback

Page 3

Contents

Preface .............................................................................................................................. 13

1 Overview ................................................................................................................. 16

1.1 Video Port ................................................................................................................ 17

1.2 Video Port FIFO ......................................................................................................... 19

1.2.1 EDMA Interface ................................................................................................. 19

1.2.2 Video Capture FIFO Configurations .......................................................................... 20

1.2.3 Video Display FIFO Configurations .......................................................................... 23

1.3 Video Port Registers .................................................................................................. 25

1.4 Video Port Pin Mapping .............................................................................................. 26

1.4.1 VDIN Bus Usage for Capture Modes ........................................................................ 27

1.4.2 VDOUT Data Bus Usage for Display Modes ................................................................ 28

1.5 Video Port Pin Multiplexing ........................................................................................ 28

1.6 VideoPort Clocking .................................................................................................... 28

2 Video Port ............................................................................................................... 29

2.1 Reset Operation ........................................................................................................ 30

2.1.1 Power-On Reset ................................................................................................ 30

2.1.2 Peripheral Bus Reset .......................................................................................... 30

2.1.3 Software Port Reset ............................................................................................ 30

2.1.4 Capture Channel Reset ........................................................................................ 31

2.1.5 Display Channel Reset......................................................................................... 31

2.2 Interrupt Operation .................................................................................................... 31

2.3 EDMA Operation ........................................................................................................ 32

2.3.1 Capture EDMA Event Generation ............................................................................ 32

2.3.2 Display EDMA Event Generation ............................................................................. 33

2.3.3 EDMA Size and Threshold Restrictions ..................................................................... 33

2.3.4 EDMA Interface Operation .................................................................................... 34

2.4 Video Port Control Registers ...................................................................................... 34

2.4.1 Video Port Control Register (VPCTL) ........................................................................ 35

2.4.2 Video Port Status Register (VPSTAT) ....................................................................... 37

2.4.3 Video Port Interrupt Enable Register (VPIE) ................................................................ 38

2.4.4 Video Port Interrupt Status Register (VPIS) ................................................................ 40

3 Video Capture Port ................................................................................................... 45

3.1 Video Capture Mode Selection .................................................................................... 46

3.2 BT.656 Video Capture Mode ........................................................................................ 46

3.2.1 BT.656 Capture Channels ..................................................................................... 46

3.2.2 BT.656 Timing Reference Codes ............................................................................. 46

3.2.3 BT.656 Image Window and Capture ......................................................................... 48

3.2.4 BT.656 Data Sampling ......................................................................................... 49

3.2.5 BT.656 FIFO Packing .......................................................................................... 49

3.3 Y/C Video Capture Mode ............................................................................................ 50

3.3.1 Y/C Capture Channels ......................................................................................... 50

3.3.2 Y/C Timing Reference Codes ................................................................................. 50

SPRUEM1 – May 2007 Table of Contents 3

Submit Documentation Feedback

Page 4

3.3.3 Y/C Image Window and Capture ............................................................................. 50

3.3.4 Y/C FIFO Packing .............................................................................................. 51

3.4 BT.656 and Y/C Mode Field and Frame Operation .......................................................... 51

3.4.1 Capture Determination and Notification ..................................................................... 52

3.4.2 Vertical Synchronization ....................................................................................... 53

3.4.3 Horizontal Synchronization .................................................................................... 55

3.4.4 Field Identification .............................................................................................. 56

3.4.5 Short and Long Field Detect .................................................................................. 57

3.5 Video Input Filtering .................................................................................................. 57

3.5.1 Input Filter Modes .............................................................................................. 58

3.5.2 Chrominance Re-sampling Operation ....................................................................... 58

3.5.3 Scaling Operation ............................................................................................... 58

3.5.4 Edge Pixel Replication ......................................................................................... 59

3.6 Ancillary Data Capture ............................................................................................... 60

3.6.1 Horizontal Ancillary (HANC) Data Capture .................................................................. 61

3.6.2 Vertical Ancillary (VANC) Data Capture ..................................................................... 61

3.7 Raw Data Capture Mode ............................................................................................. 61

3.7.1 Raw Data Capture Notification ................................................................................ 61

3.7.2 Raw Data FIFO Packing ....................................................................................... 62

3.8 TCI Capture Mode ...................................................................................................... 63

3.8.1 TCI Capture Features .......................................................................................... 63

3.8.2 TCI Data Capture ............................................................................................... 63

3.8.3 TCI Capture Error Detection .................................................................................. 64

3.8.4 Synchronizing the System Clock ............................................................................. 64

3.8.5 TCI Data Capture Notification ................................................................................. 65

3.8.6 Writing to the FIFO ............................................................................................. 66

3.8.7 Reading from the FIFO ........................................................................................ 66

3.9 Capture Line Boundary Conditions .............................................................................. 67

3.10 Capturing Video in BT.656 or Y/C Mode ....................................................................... 67

3.10.1 Handling FIFO Overrun in BT.656 or Y/C Mode .......................................................... 68

3.11 Capturing Video in Raw Data Mode ............................................................................. 68

3.11.1 Handling FIFO Overrun Condition in Raw Data Mode ................................................... 69

3.12 Capturing Data in TCI Capture Mode ............................................................................ 69

3.12.1 Handling FIFO Overrun Condition in TCI Capture Mode ................................................. 70

3.13 Video Capture Registers ............................................................................................ 70

3.13.1 Video Capture Channel x Status Register (VCASTAT, VCBSTAT) .................................... 71

3.13.2 Video Capture Channel A Control Register (VCACTL) ................................................... 72

3.13.3 Video Capture Channel x Field 1 Start Register (VCxSTRT1) .......................................... 75

3.13.4 Video Capture Channel x Field 1 Stop Register (VCxSTOP1) .......................................... 76

3.13.5 Video Capture Channel x Field 2 Start Register (VCxSTRT2) .......................................... 77

3.13.6 Video Capture Channel x Field 2 Stop Register (VC xSTOP2) .......................................... 78

3.13.7 Video Capture Channel x Vertical Interrupt Register (VCxVINT) ....................................... 79

3.13.8 Video Capture Channel x Threshold Register (VCATHRLD, VCBTHRLD) ............................ 80

3.13.9 Video Capture Channel x Event Count Register (VCxEVTCT) .......................................... 81

3.13.10 Video Capture Channel B Control Register (VCBCTL) ................................................. 81

3.13.11 TCI Capture Control Register (TCICTL) .................................................................. 84

3.13.12 TCI Clock Initialization LSB Register (TCICLKINITL) ................................................... 85

3.13.13 TCI Clock Initialization MSB Register (TCICLKINITM) .................................................. 86

4 Contents SPRUEM1 – May 2007

Submit Documentation Feedback

Page 5

3.13.14 TCI System Time Clock LSB Register (TCISTCLKL) ................................................... 86

3.13.15 TCI System Time Clock MSB Register (TCISTCLKM) .................................................. 87

3.13.16 TCI System Time Clock Compare LSB Register (TCISTCMPL) ...................................... 88

3.13.17 TCI System Time Clock Compare MSB Register (TCISTCMPM) ..................................... 88

3.13.18 TCI System Time Clock Compare Mask LSB Register (TCISTMSKL) ............................... 89

3.13.19 TCI System Time Clock Compare Mask MSB Register (TCISTMSKM) .............................. 89

3.13.20 TCI System Time Clock Ticks Interrupt Register (TCITICKS) ......................................... 90

3.14 Video Capture FIFO Registers ..................................................................................... 91

4 Video Display Port .................................................................................................... 92

4.1 Video Display Mode Selection ..................................................................................... 93

4.1.1 Image Timing .................................................................................................... 93

4.1.2 Video Display Counters ........................................................................................ 96

4.1.3 Sync Signal Generation ........................................................................................ 98

4.1.4 External Sync Operation ....................................................................................... 98

4.1.5 Port Sync Operation ............................................................................................ 98

4.2 BT.656 Video Display Mode ........................................................................................ 98

4.2.1 Display Timing Reference Codes ............................................................................ 99

4.2.2 Blanking Codes ................................................................................................ 101

4.2.3 BT.656 Image Display ........................................................................................ 101

4.2.4 BT.656 FIFO Unpacking ..................................................................................... 101

4.3 Y/C Video Display Mode ........................................................................................... 102

4.3.1 Y/C Display Timing Reference Codes ...................................................................... 102

4.3.2 Y/C Blanking Codes .......................................................................................... 102

4.3.3 Y/C Image Display ............................................................................................ 102

4.3.4 Y/C FIFO Unpacking .......................................................................................... 103

4.4 Video Output Filtering .............................................................................................. 103

4.4.1 Output Filter Modes ........................................................................................... 103

4.4.2 Chrominance Re-sampling Operation ...................................................................... 104

4.4.3 Scaling Operation ............................................................................................. 104

4.4.4 Edge Pixel Replication ....................................................................................... 105

4.5 Ancillary Data Display .............................................................................................. 106

4.5.1 Horizontal Ancillary (HANC) Data Display ................................................................. 106

4.5.2 Vertical Ancillary (VANC) Data Display .................................................................... 106

4.6 Raw Data Display Mode ............................................................................................ 106

4.6.1 Raw Mode RGB Output Support ............................................................................ 107

4.6.2 Raw Data FIFO Unpacking .................................................................................. 107

4.7 Video Display Field and Frame Operation ................................................................... 108

4.7.1 Display Determination and Notification ..................................................................... 108

4.7.2 Video Display Event Generation ............................................................................ 109

4.8 Display Line Boundary Conditions ............................................................................. 109

4.9 Display Timing Examples ......................................................................................... 110

4.9.1 Interlaced BT.656 Timing Example ......................................................................... 110

4.9.2 Interlaced Raw Display Example ............................................................................ 113

4.9.3 Y/C Progressive Display Example .......................................................................... 116

4.10 Displaying Video in BT.656 or Y/C Mode ..................................................................... 119

4.11 Displaying Video in Raw Data Mode ........................................................................... 120

4.11.1 Handling Under-run Condition of the Display FIFO ..................................................... 121

SPRUEM1 – May 2007 Contents 5

Submit Documentation Feedback

Page 6

4.12 Video Display Registers ........................................................................................... 122

4.12.1 Video Display Status Register (VDSTAT) ................................................................ 122

4.12.2 Video Display Control Register (VDCTL) ................................................................. 123

4.12.3 Video Display Frame Size Register (VDFRMSZ) ........................................................ 127

4.12.4 Video Display Horizontal Blanking Register (VDHBLNK) ............................................... 127

4.12.5 Video Display Field 1 Vertical Blanking Start Register (VDVBLKS1) ................................. 128

4.12.6 Video Display Field 1 Vertical Blanking End Register (VDVBLKE1) .................................. 129

4.12.7 Video Display Field 2 Vertical Blanking Start Register (VDVBLKS2) ................................. 130

4.12.8 Video Display Field 2 Vertical Blanking End Register (VDVBLKE2) .................................. 131

4.12.9 Video Display Field 1 Image Offset Register (VDIMGOFF1) .......................................... 132

4.12.10 Video Display Field 1 Image Size Register (VDIMGSZ1) ............................................. 133

4.12.11 Video Display Field 2 Image Offset Register (VDIMGOFF2) ......................................... 134

4.12.12 Video Display Field 2 Image Size Register (VDIMGSZ2) ............................................. 135

4.12.13 Video Display Field 1 Timing Register (VDFLDT1) .................................................... 135

4.12.14 Video Display Field 2 Timing Register (VDFLDT2) .................................................... 136

4.12.15 Video Display Threshold Register (VDTHRLD) ........................................................ 137

4.12.16 Video Display Horizontal Synchronization Register (VDHSYNC) .................................... 138

4.12.17 Video Display Field 1 Vertical Synchronization Start Register (VDVSYNS1) ...................... 138

4.12.18 Video Display Field 1 Vertical Synchronization End Register (VDVSYNE1) ....................... 139

4.12.19 Video Display Field 2 Vertical Synchronization Start Register (VDVSYNS2) ...................... 140

4.12.20 Video Display Field 2 Vertical Synchronization End Register (VDVSYNE2) ....................... 140

4.12.21 Video Display Counter Reload Register (VDRELOAD) ............................................... 141

4.12.22 Video Display Event Register (VDDISPEVT) ........................................................... 142

4.12.23 Video Display Clipping Register (VDCLIP) .............................................................. 142

4.12.24 Video Display Default Display Value Register (VDDEFVAL) ......................................... 143

4.12.25 Video Display Vertical Interrupt Register (VDVINT) ................................................... 144

4.12.26 Video Display Field Bit Register (VDFBIT) .............................................................. 145

4.12.27 Video Display Field 1 Vertical Blanking Bit Register (VDVBIT1) ..................................... 146

4.12.28 Video Display Field 2 Vertical Blanking Bit Register (VDVBIT2) ..................................... 147

4.13 Video Display Registers Recommended Values ........................................................... 148

4.14 Video Display FIFO Registers .................................................................................... 149

5 General-Purpose I/O Operation ................................................................................. 150

5.1 GPIO Registers ........................................................................................................ 151

5.1.1 Video Port Peripheral Identification Register (VPPID) ................................................... 152

5.1.2 Video Port Peripheral Control Register (PCR) ............................................................ 153

5.1.3 Video Port Pin Function Register (PFUNC) ............................................................... 154

5.1.4 Video Port Pin Direction Register (PDIR) .................................................................. 156

5.1.5 Video Port Pin Data Input Register (PDIN) ................................................................ 158

5.1.6 Video Port Pin Data Output Register (PDOUT) ........................................................... 159

5.1.7 Video Port Pin Data Set Register (PDSET) ............................................................... 161

5.1.8 Video Port Pin Data Clear Register (PDCLR) ............................................................. 162

5.1.9 Video Port Pin Interrupt Enable Register (PIEN) ......................................................... 163

5.1.10 Video Port Pin Interrupt Polarity Register (PIPOL) ...................................................... 164

5.1.11 Video Port Pin Interrupt Status Register (PISTAT) ...................................................... 165

5.1.12 Video Port Pin Interrupt Clear Register (PICLR) ......................................................... 166

6 VCXO Interpolated Control Port ................................................................................ 167

6.1 Overview ................................................................................................................ 168

6.2 Interface ................................................................................................................. 168

6 Contents SPRUEM1 – May 2007

Submit Documentation Feedback

Page 7

6.3 Operational Details .................................................................................................. 169

6.4 Enabling VIC Port .................................................................................................... 170

6.5 VIC Port Registers ................................................................................................... 170

6.5.1 VIC Control Register (VICCTL).............................................................................. 171

6.5.2 VIC Input Register (VICIN) ................................................................................... 172

6.5.3 VIC Clock Divider Register (VICDIV) ....................................................................... 173

SPRUEM1 – May 2007 Contents 7

Submit Documentation Feedback

Page 8

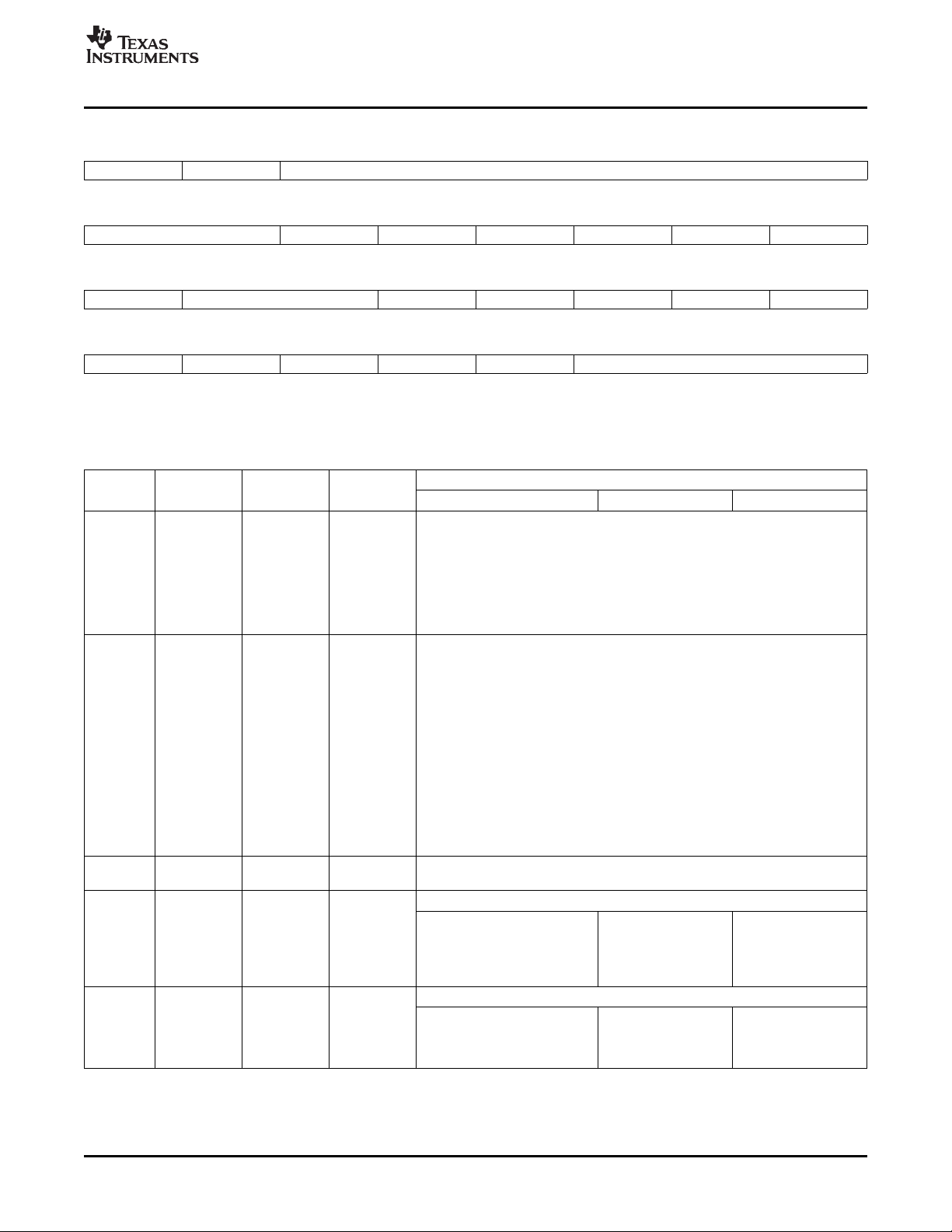

List of Figures

1-1 Video Port Block Diagram ................................................................................................. 18

1-2 BT.656 Video Capture FIFO Configuration ............................................................................. 20

1-3 8-Bit Raw Video Capture and TCI Video Capture FIFO Configuration.............................................. 21

1-4 Y/C Video Capture FIFO Configuration ................................................................................. 22

1-5 16-Bit Raw Video Capture FIFO Configuration ......................................................................... 23

1-6 BT.656 Video Display FIFO Configuration .............................................................................. 23

1-7 8-Bit Raw Video Display FIFO Configuration ........................................................................... 23

1-8 8-Bit Locked Raw Video Display FIFO Configuration ................................................................. 24

1-9 16-Bit Raw Video Display FIFO Configuration ......................................................................... 24

1-10 Y/C Video Display FIFO Configuration .................................................................................. 25

2-1 Video Port Control Register (VPCTL) ................................................................................... 35

2-2 Video Port Status Register (VPSTAT) ................................................................................... 37

2-3 Video Port Interrupt Enable Register (VPIE) ........................................................................... 38

2-4 Video Port Interrupt Status Register (VPIS) ............................................................................ 40

3-1 Video Capture Parameters ................................................................................................ 48

3-2 8-Bit BT.656 FIFO Packing ............................................................................................... 50

3-3 8-Bit Y/C FIFO Packing .................................................................................................... 51

3-4 VCOUNT Operation Example (EXC = 0) ................................................................................ 54

3-5 HCOUNT Operation Example (EXC = 0) ............................................................................... 55

3-6 HCOUNT Operation Example (EXC = 1) ............................................................................... 56

3-7 Field 1 Detection Timing................................................................................................... 57

3-8 Chrominance Re-sampling ................................................................................................ 58

3-9 1/2 Scaled Co-Sited Filtering ............................................................................................. 59

3-10 1/2 Scaled Chrominance Re-sampled Filtering ........................................................................ 59

3-11 Edge Pixel Replication ..................................................................................................... 60

3-12 Capture Window Not Requiring Edge Pixel Replication .............................................................. 60

3-13 8-Bit Raw Data FIFO Packing ............................................................................................ 62

3-14 16-Bit Raw Data FIFO Packing ........................................................................................... 63

3-15 Parallel TCI Capture ....................................................................................................... 64

3-16 Program Clock Reference (PCR) Header Format ..................................................................... 64

3-17 System Time Clock Counter Operation ................................................................................. 65

3-18 TCI FIFO Packing .......................................................................................................... 66

3-19 TCI Timestamp Format (Little Endian) .................................................................................. 66

3-20 Capture Line Boundary Example ......................................................................................... 67

3-21 Video Capture Channel x Status Register (VCxSTAT) ................................................................ 71

3-22 Video Capture Channel A Control Register (VCACTL) ............................................................... 73

3-23 Video Capture Channel x Field 1 Start Register (VCxSTRT1) ....................................................... 76

3-24 Video Capture Channel x Field 1 Stop Register (VCxSTOP1) ....................................................... 77

3-25 Video Capture Channel x Field 2 Start Register (VCxSTRT2) ....................................................... 77

3-26 Video Capture Channel x Field 2 Stop Register (VC xSTOP2) ....................................................... 78

3-27 Video Capture Channel x Vertical Interrupt Register (VCxVINT) .................................................... 79

3-28 Video Capture Channel x Threshold Register (VC xTHRLD) ......................................................... 80

3-29 Video Capture Channel x Event Count Register (VCxEVTCT) ...................................................... 81

3-30 Video Capture Channel B Control Register (VCBCTL) ............................................................... 82

3-31 TCI Capture Control Register (TCICTL) ................................................................................. 84

3-32 TCI Clock Initialization LSB Register (TCICLKINITL) ................................................................. 85

3-33 TCI Clock Initialization MSB Register (TCICLKINITM) ................................................................ 86

3-34 TCI System Time Clock LSB Register (TCISTCLKL) ................................................................. 87

3-35 TCI System Time Clock MSB Register (TCISTCLKM) ................................................................ 87

3-36 TCI System Time Clock Compare LSB Register (TCISTCMPL) ..................................................... 88

3-37 TCI System Time Clock Compare MSB Register (TCISTCMPM) ................................................... 88

3-38 TCI System Time Clock Compare Mask LSB Register (TCISTMSKL) .............................................. 89

8 List of Figures SPRUEM1 – May 2007

Submit Documentation Feedback

Page 9

3-39 TCI System Time Clock Compare Mask MSB Register (TCISTMSKM) ............................................ 90

3-40 TCI System Time Clock Ticks Interrupt Register (TCITICKS) ........................................................ 90

4-1 NTSC Compatible Interlaced Display .................................................................................... 93

4-2 SMPTE 296M Compatible Progressive Scan Display ................................................................. 94

4-3 Interlaced Blanking Intervals and Video Areas ......................................................................... 95

4-4 Progressive Blanking Intervals and Video Area ........................................................................ 96

4-5 Horizontal Blanking and Horizontal Sync Timing ...................................................................... 97

4-6 Vertical Blanking, Sync and Even/Odd Frame Signal Timing ........................................................ 97

4-7 Video Display Module Synchronization Chain .......................................................................... 98

4-8 BT.656 Output Sequence ................................................................................................. 98

4-9 525/60 BT.656 Horizontal Blanking Timing ............................................................................. 99

4-10 625/50 BT.656 Horizontal Blanking Timing ............................................................................. 99

4-11 Digital Vertical F and V Transitions ..................................................................................... 100

4-12 8-Bit BT.656 FIFO Unpacking ........................................................................................... 101

4-13 Y/C Horizontal Blanking Timing (BT.1120 60I) ....................................................................... 102

4-14 8-Bit Y/C FIFO Unpacking ............................................................................................... 103

4-15 Chrominance Re-sampling .............................................................................................. 104

4-16 2x Co-Sited Scaling ...................................................................................................... 104

4-17 2x Interspersed Scaling .................................................................................................. 105

4-18 Output Edge Pixel Replication .......................................................................................... 105

4-19 Luma Edge Replication .................................................................................................. 105

4-20 Interspersed Chroma Edge Replication ................................................................................ 106

4-21 8-Bit Raw FIFO Unpacking .............................................................................................. 107

4-22 16-Bit Raw FIFO Unpacking............................................................................................. 107

4-23 8-Bit Raw FIFO Unpacking ........................................................................................... 107

4-24 Display Line Boundary Example ........................................................................................ 110

4-25 BT.656 Interlaced Display Horizontal Timing Example .............................................................. 111

4-26 BT.656 Interlaced Display Vertical Timing Example ................................................................. 113

4-27 Raw Interlaced Display Horizontal Timing Example ................................................................. 114

4-28 Raw Interlaced Display Vertical Timing Example ..................................................................... 115

4-29 Y/C Progressive Display Horizontal Timing Example ................................................................ 117

4-30 Y/C Progressive Display Vertical Timing Example ................................................................... 118

4-31 Video Display Status Register (VDSTAT) ............................................................................. 123

4-32 Video Display Control Register (VDCTL) .............................................................................. 124

4-33 Video Display Frame Size Register (VDFRMSZ) ..................................................................... 127

4-34 Video Display Horizontal Blanking Register (VDHBLNK) ........................................................... 128

4-35 Video Display Field 1 Vertical Blanking Start Register (VDVBLKS1) .............................................. 129

4-36 Video Display Field 1 Vertical Blanking End Register (VDVBLKE1) ............................................... 129

4-37 Video Display Field 2 Vertical Blanking Start Register (VDVBLKS2) .............................................. 130

4-38 Video Display Field 2 Vertical Blanking End Register (VDVBLKE2) ............................................... 131

4-39 Video Display Field 1 Image Offset Register (VDIMGOFF1) ....................................................... 132

4-40 Video Display Field 1 Image Size Register (VDIMGSZ1) ........................................................... 133

4-41 Video Display Field 2 Image Offset Register (VDIMGOFF2) ....................................................... 134

4-42 Video Display Field 2 Image Size Register (VDIMGSZ2) ........................................................... 135

4-43 Video Display Field 1 Timing Register (VDFLDT1) .................................................................. 136

4-44 Video Display Field 2 Timing Register (VDFLDT2) .................................................................. 136

4-45 Video Display Threshold Register (VDTHRLD) ....................................................................... 137

4-46 Video Display Horizontal Synchronization Register (VDHSYNC) .................................................. 138

4-47 Video Display Field 1 Vertical Synchronization Start Register (VDVSYNS1) ..................................... 139

4-48 Video Display Field 1 Vertical Synchronization End Register (VDVSYNE1) ..................................... 139

4-49 Video Display Field 2 Vertical Synchronization Start Register (VDVSYNS2) ..................................... 140

4-50 Video Display Field 2 Vertical Synchronization End Register (VDVSYNE2) ..................................... 141

4-51 Video Display Counter Reload Register (VDRELOAD) .............................................................. 141

SPRUEM1 – May 2007 List of Figures 9

Submit Documentation Feedback

Page 10

4-52 Video Display Event Register (VDDISPEVT) ......................................................................... 142

4-53 Video Display Clipping Register (VDCLIP) ............................................................................ 143

4-54 Video Display Default Display Value Register (VDDEFVAL) ....................................................... 144

4-55 Video Display Default Display Value Register (VDDEFVAL) - Raw Data Mode ................................. 144

4-56 Video Display Vertical Interrupt Register (VDVINT) .................................................................. 145

4-57 Video Display Field Bit Register (VDFBIT) ............................................................................ 146

4-58 Video Display Field 1 Vertical Blanking Bit Register (VDVBIT1) ................................................... 146

4-59 Video Display Field 2 Vertical Blanking Bit Register (VDVBIT2) ................................................... 147

5-1 Video Port Peripheral Identification Register (VPPID) ............................................................... 152

5-2 Video Port Peripheral Control Register (PCR) ........................................................................ 153

5-3 Video Port Pin Function Register (PFUNC) ........................................................................... 154

5-4 Video Port Pin Direction Register (PDIR) .............................................................................. 156

5-5 Video Port Pin Data Input Register (PDIN) ............................................................................ 158

5-6 Video Port Pin Data Output Register (PDOUT) ....................................................................... 159

5-7 Video Port Pin Data Set Register (PDSET) ........................................................................... 161

5-8 Video Port Pin Data Clear Register (PDCLR) ......................................................................... 162

5-9 Video Port Pin Interrupt Enable Register (PIEN) ..................................................................... 163

5-10 Video Port Pin Interrupt Polarity Register (PIPOL) ................................................................... 164

5-11 Video Port Pin Interrupt Status Register (PISTAT) ................................................................... 165

5-12 Video Port Pin Interrupt Clear Register (PICLR) ..................................................................... 166

6-1 TCI System Block Diagram .............................................................................................. 168

6-2 Program Clock Reference (PCR) Header Format .................................................................... 169

6-3 VIC Control Register (VICCTL) ......................................................................................... 171

6-4 VIC Input Register (VICIN) .............................................................................................. 172

6-5 VIC Clock Divider Register (VICDIV) ................................................................................... 173

10 List of Figures SPRUEM1 – May 2007

Submit Documentation Feedback

Page 11

List of Tables

1-1 Video Capture Signal Mapping ........................................................................................... 26

1-2 Video Display Signal Mapping ............................................................................................ 26

1-3 VDIN Data Bus Usage for Capture Modes ............................................................................. 27

1-4 VDOUT Data Bus Usage for Display Modes ........................................................................... 28

2-1 Video Port Control Registers ............................................................................................. 34

2-2 Video Port Control Register (VPCTL) Field Descriptions ............................................................. 35

2-3 Video Port Operating Mode Selection ................................................................................... 36

2-4 Video Port Status Register (VPSTAT) Field Descriptions ............................................................ 37

2-5 Video Port Interrupt Enable Register (VPIE) Field Descriptions ..................................................... 38

2-6 Video Port Interrupt Status Register (VPIS) Field Descriptions ...................................................... 40

3-1 Video Capture Mode Selection ........................................................................................... 46

3-2 BT.656 Video Timing Reference Codes ................................................................................. 47

3-3 BT.656 Protection Bits ..................................................................................................... 47

3-4 Error Correction by Protection Bits ...................................................................................... 47

3-5 Common Video Source Parameters ..................................................................................... 49

3-6 BT.656 and Y/C Mode Capture Operation .............................................................................. 52

3-7 Vertical Synchronization Programming .................................................................................. 53

3-8 Horizontal Synchronization Programming ............................................................................... 55

3-9 Field Identification Programming ......................................................................................... 56

3-10 Input Filter Mode Selection ............................................................................................... 58

3-11 Raw Data Mode Capture Operation ..................................................................................... 62

3-12 TCI Capture Mode Operation ............................................................................................. 65

3-13 Video Capture Control Registers ........................................................................................ 70

3-14 Video Capture Channel x Status Register (VCxSTAT) Field Descriptions ......................................... 72

3-15 Video Capture Channel A Control Register (VCACTL) Field Descriptions ......................................... 73

3-16 Video Capture Channel x Field 1 Start Register (VCxSTRT1) Field Descriptions ................................. 76

3-17 Video Capture Channel x Field 1 Stop Register (VCxSTOP1) Field Descriptions ................................ 77

3-18 Video Capture Channel x Field 2 Start Register (VCxSTRT2) Field Descriptions ................................. 78

3-19 Video Capture Channel x Field 2 Stop Register (VCxSTOP2) Field Descriptions ................................ 78

3-20 Video Capture Channel x Vertical Interrupt Register (VCxVINT) Field Descriptions .............................. 79

3-21 Video Capture Channel x Threshold Register (VCxTHRLD) Field Descriptions ................................... 80

3-22 Video Capture Channel x Event Count Register (VCxEVTCT) Field Descriptions ................................ 81

3-23 Video Capture Channel B Control Register (VCBCTL) Field Descriptions ......................................... 82

3-24 TCI Capture Control Register (TCICTL) Field Descriptions .......................................................... 84

3-25 TCI Clock Initialization LSB Register (TCICLKINITL) Field Descriptions ........................................... 85

3-26 TCI Clock Initialization MSB Register (TCICLKINITM) Field Descriptions .......................................... 86

3-27 TCI System Time Clock LSB Register (TCISTCLKL) Field Descriptions ........................................... 87

3-28 TCI System Time Clock MSB Register (TCISTCLKM) Field Descriptions .......................................... 87

3-29 TCI System Time Clock Compare LSB Register (TCISTCMPL) Field Descriptions .............................. 88

3-30 TCI System Time Clock Compare MSB Register (TCISTCMPM) Field Descriptions ............................. 89

3-31 TCI System Time Clock Compare Mask LSB Register (TCISTMSKL) Field Descriptions ....................... 89

3-32 TCI System Time Clock Compare Mask MSB Register (TCISTMSKM) Field Descriptions ...................... 90

3-33 TCI System Time Clock Ticks Interrupt Register (TCITICKS) Field Descriptions ................................. 90

3-34 Video Capture FIFO Registers ........................................................................................... 91

3-35 Video Capture FIFO Registers Function ................................................................................ 91

4-1 Video Display Mode Selection ............................................................................................ 93

4-2 BT.656 Frame Timing .................................................................................................... 100

4-3 Output Filter Mode Selection ............................................................................................ 103

4-4 Display Operation ......................................................................................................... 108

SPRUEM1 – May 2007 List of Tables 11

Submit Documentation Feedback

Page 12

4-5 Video Display Control Registers ....................................................................................... 122

4-6 Video Display Status Register (VDSTAT) Field Descriptions ....................................................... 123

4-7 Video Display Control Register (VDCTL) Field Descriptions ........................................................ 124

4-8 Video Display Frame Size Register (VDFRMSZ) Field Descriptions .............................................. 127

4-9 Video Display Horizontal Blanking Register (VDHBLNK) Field Descriptions ..................................... 128

4-10 Video Display Field 1 Vertical Blanking Start Register (VDVBLKS1) Field Descriptions ........................ 129

4-11 Video Display Field 1 Vertical Blanking End Register (VDVBLKE1) Field Descriptions ........................ 130

4-12 Video Display Field 2 Vertical Blanking Start Register (VDVBLKS2) Field Descriptions ........................ 130

4-13 Video Display Field 2 Vertical Blanking End Register (VDVBLKE2) Field Descriptions ........................ 131

4-14 Video Display Field 1 Image Offset Register (VDIMGOFF1) Field Descriptions ................................. 132

4-15 Video Display Field 1 Image Size Register (VDIMGSZ1) Field Descriptions ..................................... 133

4-16 Video Display Field 2 Image Offset Register (VDIMGOFF2) Field Descriptions ................................. 134

4-17 Video Display Field 2 Image Size Register (VDIMGSZ2) Field Descriptions ..................................... 135

4-18 Video Display Field 1 Timing Register (VDFLDT1) Field Descriptions ............................................ 136

4-19 Video Display Field 2 Timing Register (VDFLDT2) Field Descriptions ............................................ 136

4-20 Video Display Threshold Register (VDTHRLD) Field Descriptions ................................................ 137

4-21 Video Display Horizontal Synchronization Register (VDHSYNC) Field Descriptions ............................ 138

4-22 Video Display Field 1 Vertical Synchronization Start Register (VDVSYNS1) Field Descriptions .............. 139

4-23 Video Display Field 1 Vertical Synchronization End Register (VDVSYNE1) Field Descriptions ............... 139

4-24 Video Display Field 2 Vertical Synchronization Start Register (VDVSYNS2) Field Descriptions .............. 140

4-25 Video Display Field 2 Vertical Synchronization End Register (VDVSYNE2) Field Descriptions ............... 141

4-26 Video Display Counter Reload Register (VDRELOAD) Field Descriptions ....................................... 141

4-27 Video Display Event Register (VDDISPEVT) Field Descriptions ................................................... 142

4-28 Video Display Clipping Register (VDCLIP) Field Descriptions ...................................................... 143

4-29 Video Display Default Display Value Register (VDDEFVAL) Field Descriptions ................................. 144

4-30 Video Display Vertical Interrupt Register (VDVINT) Field Descriptions ........................................... 145

4-31 Video Display Field Bit Register (VDFBIT) Field Descriptions ...................................................... 146

4-32 Video Display Field 1 Vertical Blanking Bit Register (VDVBIT1) Field Descriptions ............................. 147

4-33 Video Display Field 2 Vertical Blanking Bit Register (VDVBIT2) Field Descriptions ............................. 147

4-34 Video Display Register Recommended Values ...................................................................... 148

4-35 Video Display FIFO Registers ........................................................................................... 149

4-36 Video Display FIFO Registers Function ............................................................................... 149

5-1 Video Port Registers ..................................................................................................... 151

5-2 Video Port Peripheral Identification Register (VPPID) Field Descriptions ......................................... 152

5-3 Video Port Peripheral Control Register (PCR) Field Descriptions .................................................. 153

5-4 Video Port Pin Function Register (PFUNC) Field Descriptions ..................................................... 154

5-5 Video Port Pin Direction Register (PDIR) Field Descriptions ....................................................... 156

5-6 Video Port Pin Data Input Register (PDIN) Field Descriptions ..................................................... 158

5-7 Video Port Pin Data Out Register (PDOUT) Field Descriptions .................................................... 159

5-8 Video Port Pin Data Set Register (PDSET) Field Descriptions ..................................................... 161

5-9 Video Port Pin Data Clear Register (PDCLR) Field Descriptions .................................................. 162

5-10 Video Port Pin Interrupt Enable Register (PIEN) Field Descriptions ............................................... 163

5-11 Video Port Pin Interrupt Polarity Register (PIPOL) Field Descriptions............................................. 164

5-12 Video Port Pin Interrupt Status Register (PISTAT) Field Descriptions ............................................ 165

5-13 Video Port Pin Interrupt Clear Register (PICLR) Field Descriptions ............................................... 166

6-1 VIC Port Interface Signals ............................................................................................... 168

6-2 Example Values for Interpolation Rate ................................................................................. 169

6-3 VIC Port Registers ........................................................................................................ 170

6-4 VIC Control Register (VICCTL) Field Descriptions ................................................................... 171

6-5 VIC Input Register (VICIN) Field Descriptions ........................................................................ 172

6-6 VIC Clock Divider Register (VICDIV) Field Descriptions ............................................................ 173

12 List of Tables SPRUEM1 – May 2007

Submit Documentation Feedback

Page 13

About This Manual

This document describes the video port and VCXO interpolated control (VIC) port in the digital signal

processors (DSPs).

Notational Conventions

This document uses the following conventions.

• Hexadecimal numbers are shown with the suffix h. For example, the following number is 40

hexadecimal (decimal 64): 40h.

• Registers in this document are shown in figures and described in tables.

– Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its

read/write properties below. A legend explains the notation used for the properties.

– Reserved bits in a register figure designate a bit that is used for future device expansion.

Related Documentation From Texas Instruments

The following documents describe the TMS320DM647/DM648 Digital Signal Processor (DSP). Copies of

these documents are available on the Internet at www.ti.com . Tip: Enter the literature number in the

search box provided at www.ti.com .

SPRS372 — TMS320DM647/DM648 Digital Media Processor Data Manual describes the signals,

specifications and electrical characteristics of the device.

Preface

SPRUEM1 – May 2007

Read This First

SPRU732 — TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide describes the CPU

architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital

signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation

comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of

the C64x DSP with added functionality and an expanded instruction set.

SPRUEK5 — TMS320DM647/DM648 DSP DDR2 Memory Controller User's Guide describes the DDR2

memory controller in the TMS320DM647/DM648 Digital Signal Processor (DSP). The DDR2/mDDR

memory controller is used to interface with JESD79D-2A standard compliant DDR2 SDRAM

devices and standard Mobile DDR SDRAM devices.

SPRUEK6 — TMS320DM647/DM648 DSP External Memory Interface (EMIF) User's Guide describes

the operation of the asynchronous external memory interface (EMIF) in the TMS320DM647/DM648

Digital Signal Processor (DSP). The EMIF supports a glueless interface to a variety of external

devices.

SPRUEK7 — TMS320DM647/DM648 DSP General-Purpose Input/Output (GPIO) User's Guide

describes the general-purpose input/output (GPIO) peripheral in the TMS320DM647/DM648 Digital

Signal Processor (DSP). The GPIO peripheral provides dedicated general-purpose pins that can be

configured as either inputs or outputs. When configured as an input, you can detect the state of the

input by reading the state of an internal register. When configured as an output, you can write to an

internal register to control the state driven on the output pin.

SPRUEM1 – May 2007 Preface 13

Submit Documentation Feedback

Page 14

www.ti.com

Related Documentation From Texas Instruments

SPRUEK8 — TMS320DM647/DM648 DSP Inter-Integrated Circuit (I2C) Module User's Guide

describes the inter-integrated circuit (I2C) peripheral in the TMS320DM647/DM648 Digital Signal

Processor (DSP). The I2C peripheral provides an interface between the DSP and other devices

compliant with the I2C-bus specification and connected by way of an I2C-bus. External components

attached to this 2-wire serial bus can transmit and receive up to 8-bit wide data to and from the

DSP through the I2C peripheral. This document assumes the reader is familiar with the I2C-bus

specification.

SPRUEL0 — TMS320DM647/DM648 DSP 64-Bit Timer User's Guide describes the operation of the

64-bit timer in the TMS320DM647/DM648 Digital Signal Processor (DSP). The timer can be

configured as a general-purpose 64-bit timer, dual general-purpose 32-bit timers, or a watchdog

timer.

SPRUEL1 — TMS320DM647/DM648 DSP Multichannel Audio Serial Port (McASP) User's Guide

describes the multichannel audio serial port (McASP) in the TMS320DM647/DM648 Digital Signal

Processor (DSP). The McASP functions as a general-purpose audio serial port optimized for the

needs of multichannel audio applications. The McASP is useful for time-division multiplexed (TDM)

stream, Inter-Integrated Sound (I2S) protocols, and intercomponent digital audio interface

transmission (DIT).

SPRUEL2 — TMS320DM647/DM648 DSP Enhanced DMA (EDMA) Controller User's Guide describes

the operation of the enhanced direct memory access (EDMA3) controller in the

TMS320DM647/DM648 Digital Signal Processor (DSP). The EDMA3 controller’s primary purpose is

to service user-programmed data transfers between two memory-mapped slave endpoints on the

DSP.

SPRUEL4 — TMS320DM647/DM648 Peripheral Component Interconnect (PCI) User's Guide

describes the peripheral component interconnect (PCI) port in the TMS320DM647/DM648 Digital

Signal Processor (DSP). The PCI port supports connection of the C642x DSP to a PCI host via the

integrated PCI master/slave bus interface. The PCI port interfaces to the DSP via the enhanced

DMA (EDMA) controller. This architecture allows for both PCI master and slave transactions, while

keeping the EDMA channel resources available for other applications.

SPRUEL5 — TMS320DM647/DM648 DSP Host Port Interface (UHPI) User's Guide describes the host

port interface (HPI) in the TMS320DM647/DM648 Digital Signal Processor (DSP). The HPI is a

parallel port through which a host processor can directly access the CPU memory space. The host

device functions as a master to the interface, which increases ease of access. The host and CPU

can exchange information via internal or external memory. The host also has direct access to

memory-mapped peripherals. Connectivity to the CPU memory space is provided through the

enhanced direct memory access (EDMA) controller.

SPRUEL8 — TMS320DM647/DM648 DSP Universal Asynchronous Receiver/Transmitter (UART)

User's Guide describes the universal asynchronous receiver/transmitter (UART) peripheral in the

TMS320DM647/DM648 Digital Signal Processor (DSP). The UART peripheral performs

serial-to-parallel conversion on data received from a peripheral device, and parallel-to-serial

conversion on data received from the CPU.

SPRUEL9 — TMS320DM647/DM648 DSP VLYNQ Port User's Guide describes the VLYNQ port in the

TMS320DM647/DM648 Digital Signal Processor (DSP). The VLYNQ port is a high-speed

point-to-point serial interface for connecting to host processors and other VLYNQ compatible

devices. It is a full-duplex serial bus where transmit and receive operations occur separately and

simultaneously without interference.

SPRUEM1 — TMS320DM647/DM648 DSP Video Port/VCXO Interpolated Control (VIC) Port User's

Guide discusses the video port and VCXO interpolated control (VIC) port in the

TMS320DM647/DM648 Digital Signal Processor (DSP). The video port can operate as a video

capture port, video display port, or transport stream interface (TSI) capture port. The VIC port

provides single-bit interpolated VCXO control with resolution from 9 bits to up to 16 bits. When the

video port is used in TSI mode, the VIC port is used to control the system clock, VCXO, for MPEG

transport stream.

14 Read This First SPRUEM1 – May 2007

Submit Documentation Feedback

Page 15

www.ti.com

Related Documentation From Texas Instruments

SPRUEM2 — TMS320DM647/DM648 DSP Serial Port Interface (SPI) User's Guide discusses the

Serial Port Interface (SPI) in the TMS320DM647/DM648 Digital Signal Processor (DSP). This

reference guide provides the specifications for a 16-bit configurable, synchronous serial peripheral

interface. The SPI is a programmable-length shift register, used for high speed communication

between external peripherals or other DSPs.

Trademarks

SPRUEM1 – May 2007 Read This First 15

Submit Documentation Feedback

Page 16

SPRUEM1 – May 2007

This chapter provides an overview of the video port peripheral in the digital signal

processors (DSPs). An overview of the video port functions, FIFO configurations, and

signal mapping are included.

Topic .................................................................................................. Page

1.1 Video Port ................................................................................ 17

1.2 Video Port FIFO ........................................................................ 19

1.3 Video Port Registers ................................................................. 25

1.4 Video Port Pin Mapping ............................................................. 26

1.5 Video Port Pin Multiplexing ........................................................ 28

1.6 VideoPort Clocking ................................................................... 28

Overview

Overview 16 SPRUEM1 – May 2007

Submit Documentation Feedback

Page 17

www.ti.com

1.1 Video Port

The video port peripheral can operate as a video capture port, video display port, or transport channel

interface (TCI) capture port.

It provides the following functions:

• Video capture mode:

• Video display mode:

• TCI capture mode: Transport channel interface (TCI) from a front-end device (such as demodulator) or

• The port generates up to three events per channel in BT656 and Y/C Mode, one event per channel in

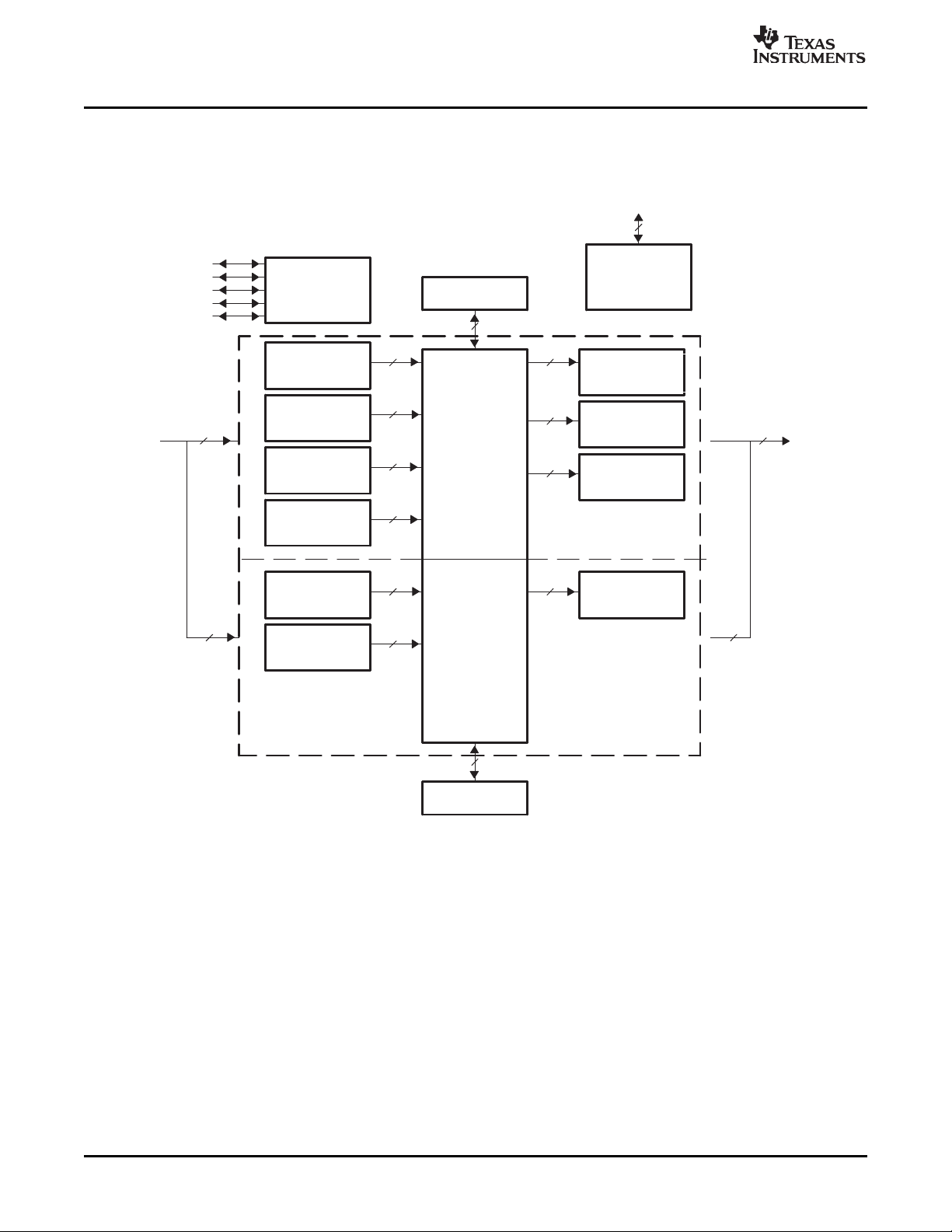

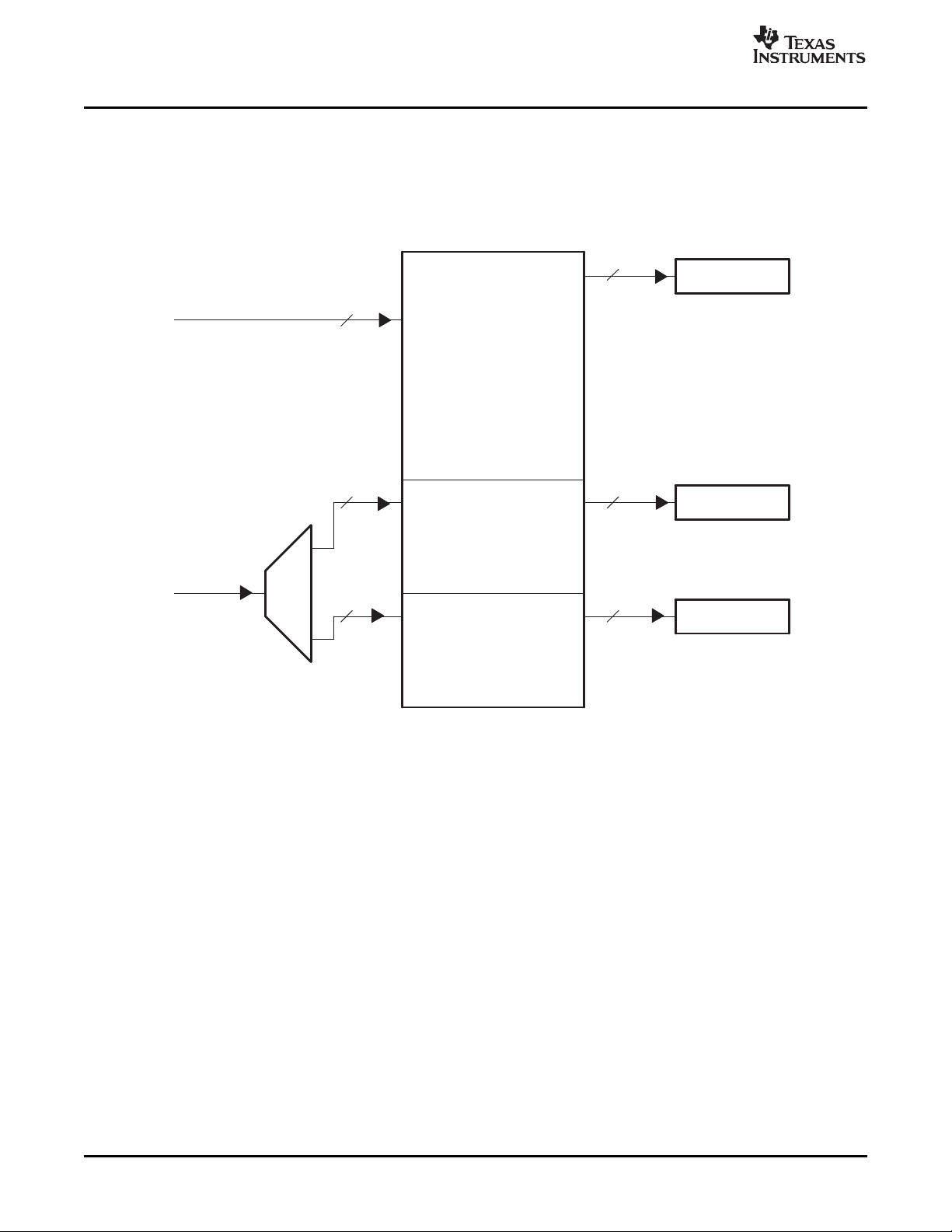

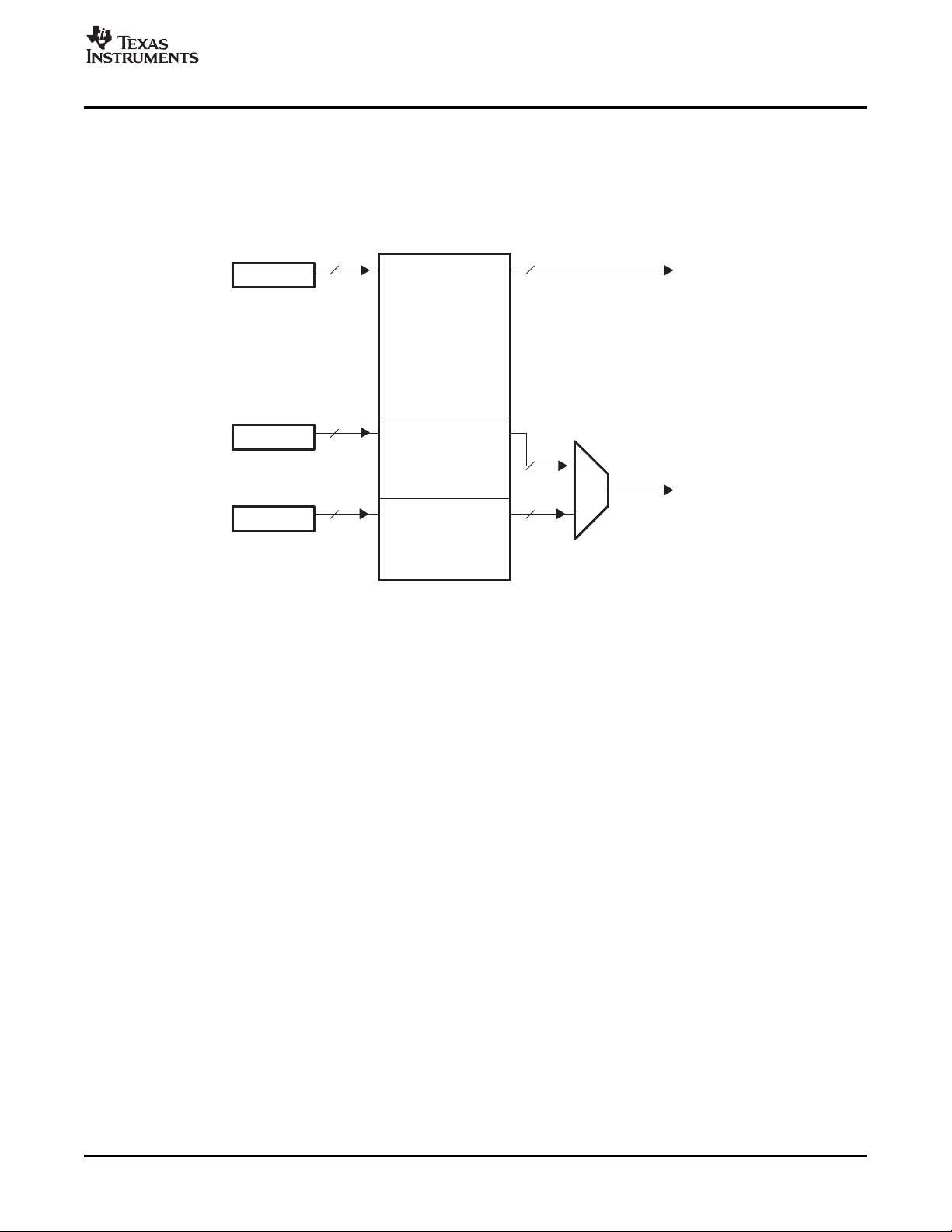

A high-level block diagram of the video port is shown in Figure 1-1 . The port consists of two channels: A

and B. You can split a 5120-byte capture/display buffer between the two channels. The entire port (both

channels) is always configured for either video capture or display only. Separate data pipelines control the

parsing and formatting of video capture or display data for each of the BT.656, Y/C, raw video, and TCI

modes.

For video capture operation, the video port may operate as two 8-bit channels of BT.656 or raw video

capture; or as a single channel of 8-bit BT.656, 8-bit raw video, 8-bit Y/C video, 16-bit raw video, or 8-bit

TCI.

For video display operation, the video port may operate as a single channel of 8-bit BT.656, 8-bit raw

video, 8-bit Y/C video, or 16-bit raw video. It may also operate in a two channel 8-bit raw mode in which

the two channels are locked to the same timing. Channel B is not used during single channel operation.

It is important to note that the VideoPort Data pin numbering is compatible with TMS320DM642 DSP

chip.In case of a 8-bit channel the suffixes for the data pins are mentioned as VDOUT[9-2]for

display/output port and VDIN[9-2]for capture/input port. In case of a 16-bit channel the suffixes for the data

pins are mentioned as VDOUT[19-2]for display/output port and VDIN[19-2]for capture/input port.

Video Port

– Capture rate of up to 80 MHZ.

– Two channels of 8-bit digital video input from a digital camera or an analog camera (using a video

decoder). Digital video input is in YCbCr 4:2:2 format with 8-bit resolution multiplexed in ITU-R

BT.656 format.

– One channel of Y/C 16-bit digital video input in YCbCr 4:2:2 format on separate Y and Cb/Cr inputs.

Supports SMPTE 260M, SMPTE 274M, SMPTE 296M, ITU-BT.1120, etc., as well as older

CCIR601 interfaces.

– YCbCr 4:2:2 to YCbCr 4:2:0 horizontal conversion and 1/2 scaling in 8-bit 4:2:2 modes.

– Direct interface for two channels of up to 8-bit or one channel of up to 16-bit raw video from A/D

converters.

– Display rate of up to 110 MHZ.

– One channel of continuous digital video output. Digital video output is YCbCr 4:2:2 co-sited pixel

data with 8-bit resolution multiplexed in ITU-R BT.656 format.

– One channel of Y/C 16-bit digital video output in YCbCr 4:2:2 format on separate Y and Cb/Cr

outputs. (Supports SMPTE 260M, SMPTE 274M, SMPTE 296M, ITU-BT.1120, etc.)

– YCbCr 4:2:0 to YCbCr 4:2:2 horizontal conversion and 2x scaling of output in 8-bit 4:2:2 modes.

– Programmable clipping of BT.656 and Y/C mode output values.

– One channel of raw data output up to 16-bits for interface to RAMDACs. Two channel synchronized

raw data output.

– Synchronizes to external video controller or another video display port.

– Using the external clock, the frame timing generator provides programmable image timing that

includes horizontal and vertical blanking, start of active video (SAV) and end of active video (EAV)

code insertion, and horizontal and frame timing pulses.

– Generates horizontal and vertical synchronization and blanking signals and a frame synchronization

signal.

a forward error correction device in 8-bit parallel format at up to 30 Mbytes/sec.

RAW and TCI mode and one interrupt to the DSP.

SPRUEM1 – May 2007 Overview 17

Submit Documentation Feedback

Page 18

www.ti.com

Internal peripheral bus

Memory

mapped

registers

Raw video

display pipeline

Channel B

Channel A

Raw video

display pipeline

Y/C video

display pipeline

BT.656 display

pipeline

Y/C video

capture pipeline

Capture/display

buffer

(2560 bytes)

Raw video

capture pipeline

BT.656 capture

pipeline

TSI capture

pipeline

Raw video

capture pipeline

VDIN[19−12]

8

VDIN[19−2]

16

DMA interface

64

Capture/display

buffer

(2560 bytes)

8

8

8

16

16

8

16

16

Timing and

control logic

VCTL2

VCTL3

VCLK1

VCTL1

VCLK2

DMA interface

8 8

64

32

VDOUT[19−12]

8

VDOUT[19−2]

16

BT.656 capture

pipeline

Video Port

This document describes the full feature set offered by the video port. See the device-specific datasheet

for details about I/O timing information.

Figure 1-1. Video Port Block Diagram

Overview 18 SPRUEM1 – May 2007

Submit Documentation Feedback

Page 19

www.ti.com

1.2 Video Port FIFO

The video port includes a FIFO to store data coming into or out from the video port. The video port

operates in conjunction with EDMA transfers to move data between the video port FIFO and external or

on-chip memory. You can program threshold settings so that EDMA events generate when the video port

FIFO reaches a certain fullness (for capture) or goes below a certain fullness (for display). You set up

EDMA Channels that are required to service the FIFO independently and are key to correct operation of

the video port. The FIFO size is relatively large to allow time for EDMA Channels to service the transfer

requests, since the device typically has many peripheral interfaces, including five video ports.

The following sections briefly describe the interaction with the EDMA and different FIFO configurations

that are used to support the various modes of the video port.

1.2.1 EDMA Interface

Video port data transfers take place using EDMA Channels. EDMA requests are based on buffer

thresholds. Since the video port does not directly source the transfer, it can not adjust the transfer size

based on buffer empty/full status. This means the EDMA transfer size is essentially fixed in the

user-programmed EDMA parameter table. The preferred transfer size is often one entire line of data

because this allows the most flexibility in terms of frame buffer line pitch (in RAM). Some modes of

operation for the highest display rates may require more frequent EDMA requests, such as on a half or

quarter line basis.

All requests are based on buffer thresholds. EDMA requests are made whenever the number of samples

in the buffer reaches the threshold value in video capture mode. In order to ensure that all data from a

capture field/frame gets emptied from the buffer, the transfer size must be equal to the threshold and the

total amount of field/frame data must be a multiple of the transfer size.

For video display operation, EDMA requests are made whenever there is at least the threshold number of

double words free in the FIFO. This means that the transfer size must be equal or smaller than the

threshold so that it fits into the available space. The field/frame size must still be a multiple of the transfer

size or there are pixels left in the buffer at the end of the field (which appear at the start of the next field).

Video Port FIFO

SPRUEM1 – May 2007 Overview 19

Submit Documentation Feedback

Page 20

www.ti.com

VDIN[9−2]

VDIN[19−12]

Capture FIFO A

Y Buffer A (1280 bytes)

Cb Buffer A (640 bytes)

8

8

64

64

Cb Buffer B (640 bytes)

Cr Buffer B (640 bytes)

CRSRCB

CBSRCB

8

8

8

8

CBSRCA

64

64

64

Capture FIFO B

Cr Buffer A (640 bytes)

YSRCB

CRSRCA

64

YSRCA

Y Buffer B (1280 bytes)

Video Port FIFO

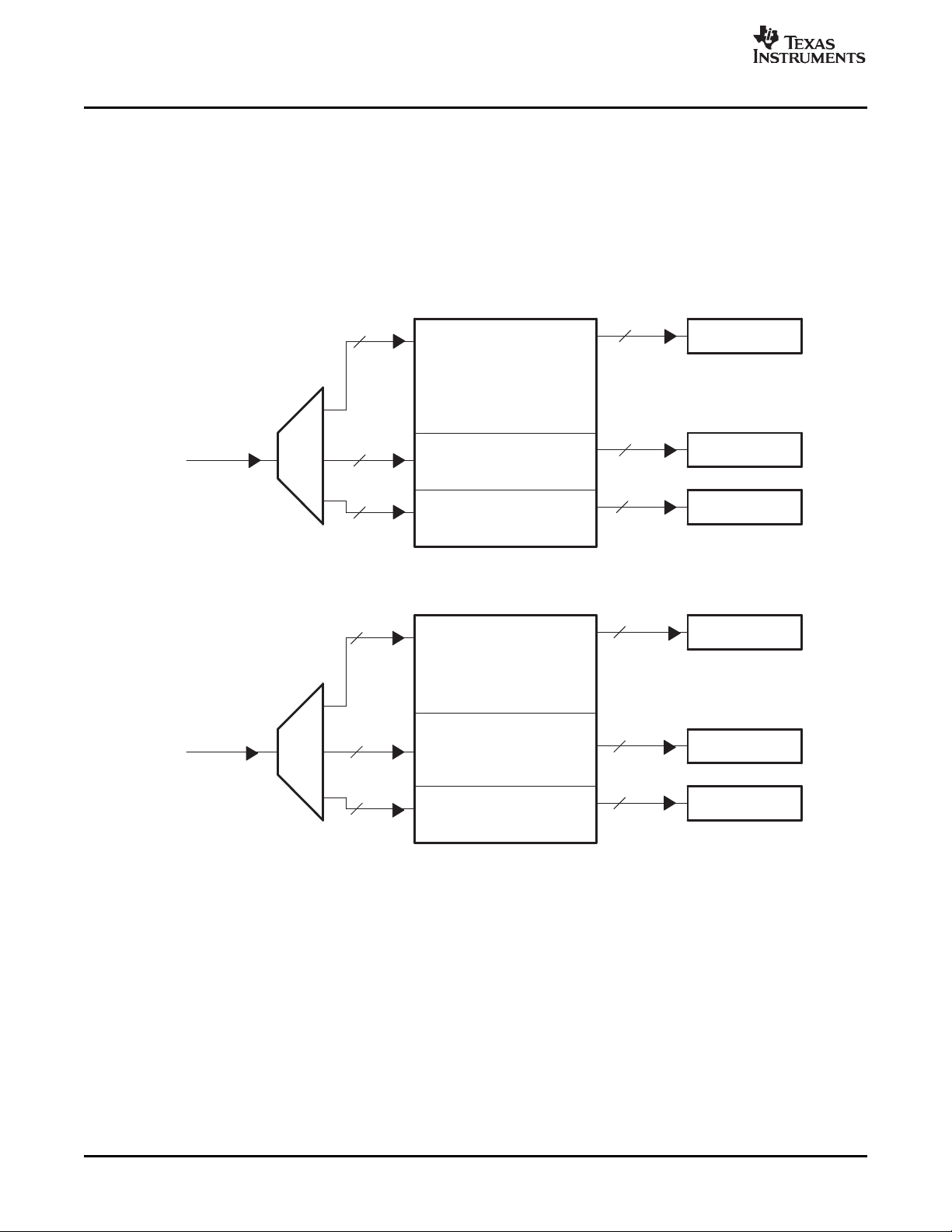

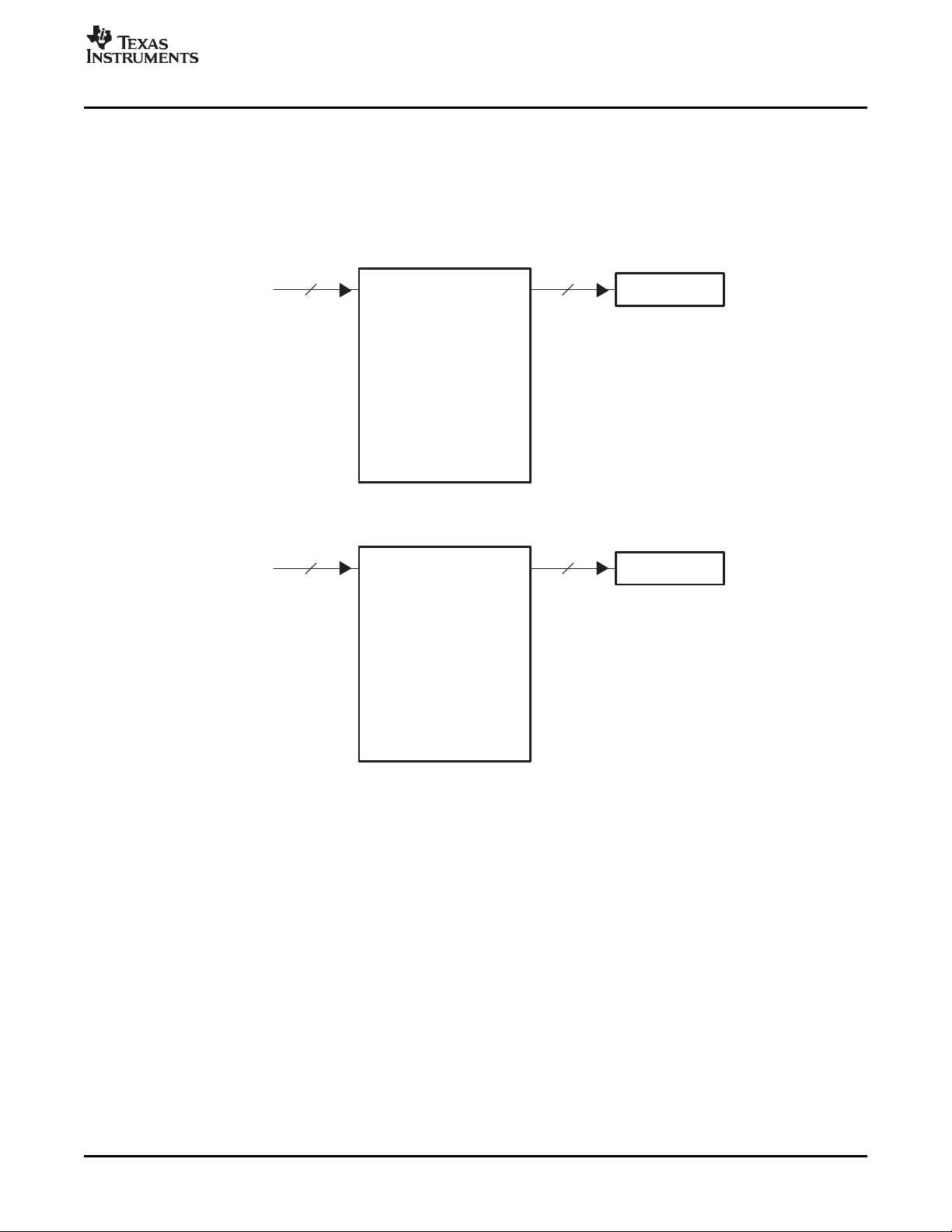

1.2.2 Video Capture FIFO Configurations

During video capture operation, the video port FIFO has one of four configurations depending on the

capture mode. For BT.656 operation, the FIFO is split into channel A and B, as shown in Figure 1-2 . Each

FIFO is clocked independently with the channel A FIFO receiving data from the VDIN[9-2] half of the bus

and the channel B FIFO receiving data from the VDIN[19-12] half of the bus. Each channel's FIFO is

further split into Y, Cb, and Cr buffers with separate write pointers and read registers (YSRC x, CBSRC x,

and CRSRC x).

Figure 1-2. BT.656 Video Capture FIFO Configuration

20 Overview SPRUEM1 – May 2007

Submit Documentation Feedback

Page 21

www.ti.com

VDIN[19−12]

8

Buffer B (2560 bytes)

Capture FIFO B

YSRCB

64

VDIN[9−2]

8

Buffer A (2560 bytes)

Capture FIFO A

YSRCA

64

Video Port FIFO

For 8-bit raw video, the FIFO is split into channel A and B, as shown in Figure 1-3 . Each FIFO is clocked

independently with the channel A FIFO receiving data from the VDIN[9-2] half of the bus and the channel

B FIFO receiving data from the VDIN[19-12] half of the bus. Each channel's FIFO has a separate write

pointer and read register (YSRC x). The FIFO configuration is identical for TCI capture, but channel B is

disabled.

Figure 1-3. 8-Bit Raw Video Capture and TCI Video Capture FIFO Configuration

SPRUEM1 – May 2007 Overview 21

Submit Documentation Feedback

Page 22

www.ti.com

VDIN[19−12]

Cr Buffer (1280 bytes)

Cb Buffer (1280 bytes)

8

8

64

64

CRSRCA

CBSRCA

Y Buffer (2560 bytes)

VDIN[9−2]

8

64

Capture FIFO

YSRCA

Video Port FIFO

For Y/C video capture, the FIFO is configured as a single channel split into separate Y, Cb, and Cr buffers

with separate write pointers and read registers (YSRCA, CBSRCA, and CRSRCA). Figure 1-4 shows how

Y data is received on the VDIN[9-2] half of the bus and Cb/Cr data is received on the VDIN[19-12] half of

the bus and de-multiplexed into the Cb and Cr buffers.

Figure 1-4. Y/C Video Capture FIFO Configuration

22 Overview SPRUEM1 – May 2007

Submit Documentation Feedback

Page 23

www.ti.com

Data Buffer

(5120 bytes)

VDIN[19−2]

16

Capture FIFO

YSRCA

64

Y Buffer

(2560 bytes)

Cb Buffer

(1280 bytes)

Cr Buffer

(1280 bytes)

YDSTA

CBDST

CRDST

VDOUT[9−2]

Display FIFO

8

8

8

64

64

64

Data Buffer

(5120 bytes)

YDSTA

VDOUT[9−2]

64

8

Display FIFO

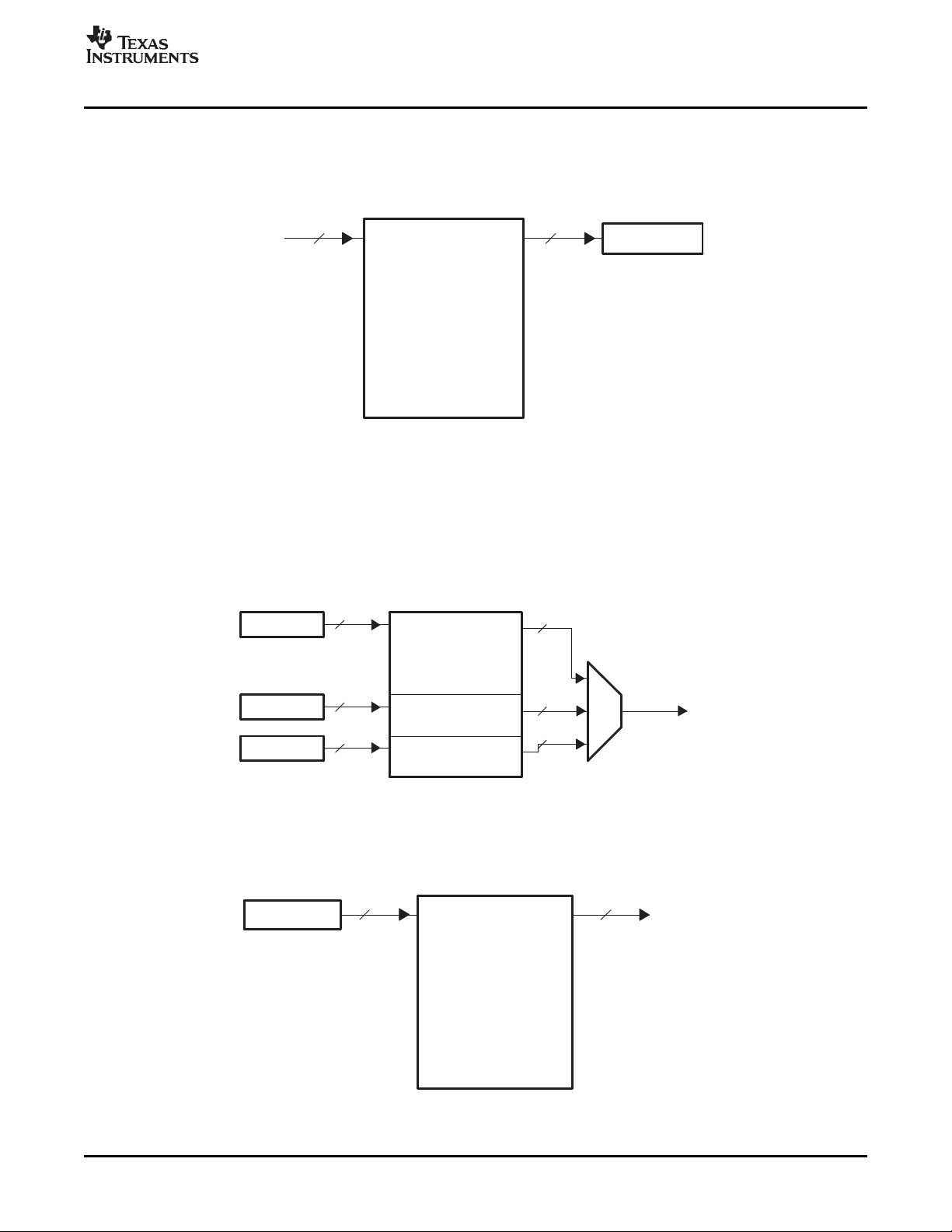

For 16-bit raw video, the FIFO is configured as a single buffer, as shown in Figure 1-5 . The FIFO receives

16-bit data from the VDIN[19-2] bus. The FIFO has a single write pointer and read register (YSRCA).

1.2.3 Video Display FIFO Configurations

During video display operation, the video port FIFO has one of five configurations depending on the

display mode. For BT.656 operation, a single output is provided on channel A, as shown in Figure 1-6 ,

with data output on VDOUT[9-2]. The channel's FIFO is split into Y, Cb, and Cr buffers with separate read

pointers and write registers (YDSTA, CBDST, and CRDST).

Video Port FIFO

Figure 1-5. 16-Bit Raw Video Capture FIFO Configuration

Figure 1-6. BT.656 Video Display FIFO Configuration

For 8-bit raw video, the FIFO is configured as a single buffer as shown in Figure 1-7 . The FIFO outputs

data on the VDOUT[9-2] half of the bus. The FIFO has a single read pointer and write register (YDSTA).

Figure 1-7. 8-Bit Raw Video Display FIFO Configuration

SPRUEM1 – May 2007 Overview 23

Submit Documentation Feedback

Page 24

www.ti.com

Buffer A (2560 bytes)

YDSTA

VDOUT[9−2]

64

8

Display FIFO A

Buffer B (2560 bytes)

YDSTB

VDOUT[19−12]

64

8

Display FIFO B

Data Buffer (5120 bytes)

YDSTA

VDOUT[19−2]

64

16

Display FIFO

Video Port FIFO

For locked raw video, the FIFO is split into channel A and B. The channels are locked together and use

the same clock and control signals. Each channel uses a single buffer and write register (YDST x) as

shown in Figure 1-8 .

For 16-bit raw video, the FIFO is configured as a single buffer, as shown in Figure 1-9 . The FIFO outputs

data on VDOUT[19-2]. The FIFO has a single read pointer and write register (YDSTA).

Figure 1-8. 8-Bit Locked Raw Video Display FIFO Configuration

Figure 1-9. 16-Bit Raw Video Display FIFO Configuration

24 Overview SPRUEM1 – May 2007

Submit Documentation Feedback

Page 25

www.ti.com

Cr Buffer (1280

bytes)

Cb Buffer

(1280 bytes)

CRDST

CBDST

64

64

VDOUT[19−12]

8

8

Y Buffer

(2560 bytes)

YDSTA

64

VDOUT[9−2]

Display FIFO

8

Video Port Registers

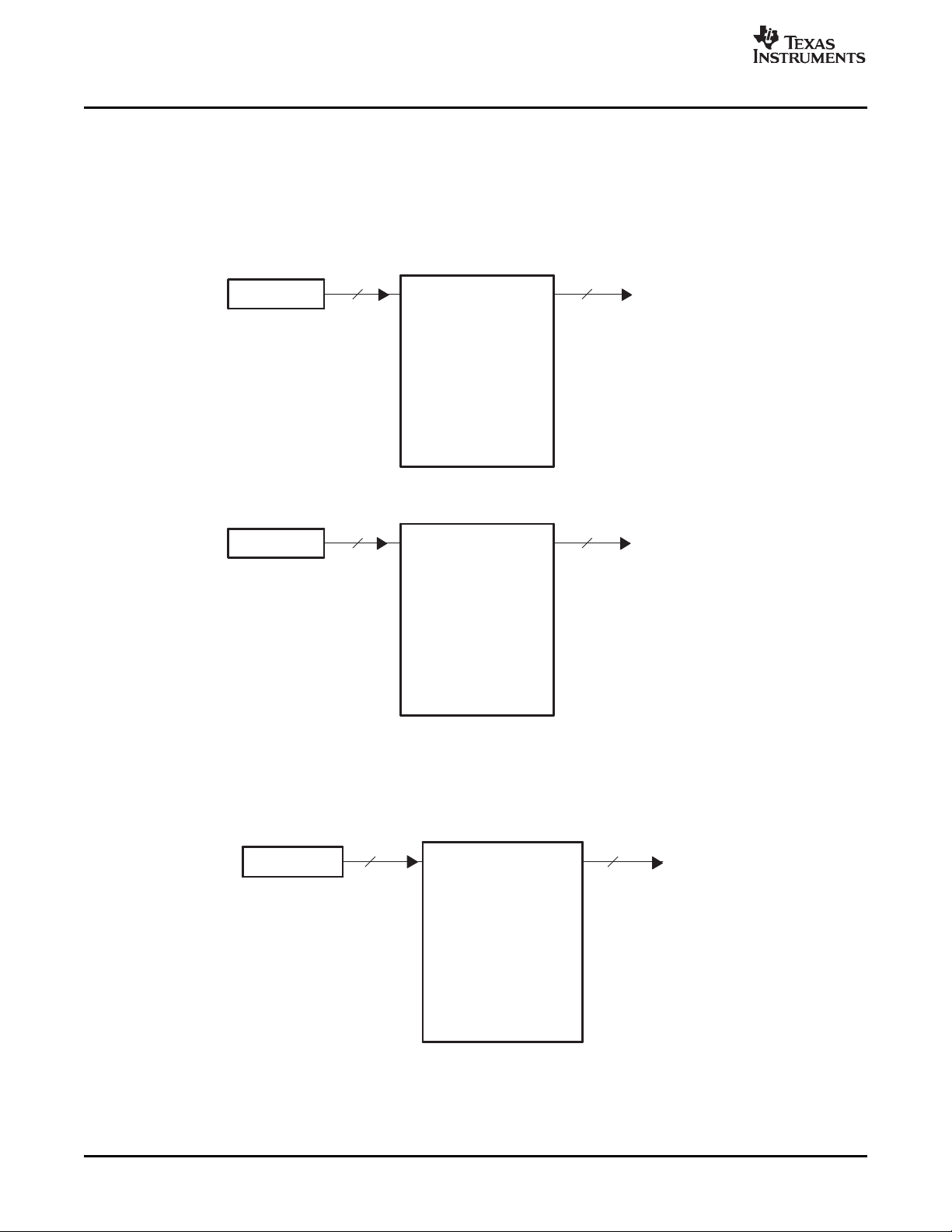

For Y/C video display, the FIFO is configured as a single channel split into separate Y, Cb, and Cr buffers

with separate read pointers and write registers (YDSTA, CBDST, and CRDST). Figure 1-10 shows how Y

data is output on the VDOUT[9-2] half of the bus and Cb/Cr data is multiplexed and output on the

VDOUT[19-12] half of the bus.

Figure 1-10. Y/C Video Display FIFO Configuration

1.3 Video Port Registers

The video port configuration register space is divided into several different sections with registers grouped

by function including top-level video port control, video capture control, video display control, and GPIO.

The registers for controlling the video port are in Section 2.4 .

The registers for controlling the video capture mode of operation are shown in Section 3.13 . An additional

space is dedicated for FIFO read pseudo-registers as shown in Section 3.14 . This space requires

high-speed access and is not mapped to the register access bus.

The registers for controlling the video display mode of operation are shown in Section 4.12 . An additional

space is dedicated for FIFO write pseudo-registers as shown in Section 4.14 . This space requires

high-speed access and is not mapped to the register access bus.

The registers for controlling the general-purpose input/output (GPIO) are shown in Section 5.1 .

SPRUEM1 – May 2007 Overview 25

Submit Documentation Feedback

Page 26

www.ti.com

Video Port Pin Mapping

1.4 Video Port Pin Mapping

The video port requires 21 external signal pins for full functionality. Pin usage and direction changes

depend on the selected operating mode. Pin functionality detail for video capture mode is listed in

Table 1-1 . Pin functionality detail for video display mode is listed in Table 1-2 . All unused port signals

(except VCLK1 and VCLK1) can be configured as general-purpose I/O (GPIO) pins.

Table 1-1. Video Capture Signal Mapping

Usage