Page 1

TMS320DM6467

www.ti.com

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

TMS320DM6467

Digital Media System-on-Chip

Check for Samples: TMS320DM6467

1 Digital Media System-on-Chip (DMSoC)

1.1 Features

12

• High-Performance Digital Media SoC • C64x+ L1/L2 Memory Architecture

– 594-, 729-MHz C64x+™ Clock Rate – 32K-Byte L1P Program RAM/Cache (Direct

– 297-, 364.5-MHz ARM926EJ-S™ Clock Rate

– Eight 32-Bit C64x+ Instructions/Cycle

– 4752, 5832 C64x+ MIPS

– Fully Software-Compatible With

C64x/ARM9™

– Supports SmartReflex™ [-594 only]

• Class 0

• 1.05-V and 1.2-V Adaptive Core Voltage

– Extended Temp Available [-594 only]

– Industrial Temp Available [-729 only]

• Advanced Very-Long-Instruction-Word (VLIW)

TMS320C64x+™ DSP Core

– Eight Highly Independent Functional Units

• Six ALUs (32-/40-Bit), Each Supports

Single 32-Bit, Dual 16-Bit, or Quad 8-Bit

Arithmetic per Clock Cycle

• Two Multipliers Support Four 16 x 16-Bit

Multiplies (32-Bit Results) per Clock

Cycle or Eight 8 x 8-Bit Multiplies (16-Bit • Embedded Trace Buffer™ (ETB11™) With 4KB

Results) per Clock Cycle Memory for ARM9 Debug

– Load-Store Architecture With Non-Aligned • Endianness: Little Endian for ARM and DSP

Support

– 64 32-Bit General-Purpose Registers Image Co-Processor (HDVICP) Engines

– Instruction Packing Reduces Code Size – Supports a Range of Encode, Decode, and

– All Instructions Conditional

– Additional C64x+™ Enhancements

• Protected Mode Operation

• Exceptions Support for Error Detection

and Program Redirection

• Hardware Support for Modulo Loop

Operation

• C64x+ Instruction Set Features

– Byte-Addressable (8-/16-/32-/64-Bit Data)

– 8-Bit Overflow Protection

– Bit-Field Extract, Set, Clear

– Normalization, Saturation, Bit-Counting

– Compact 16-Bit Instructions

– Additional Instructions to Support Complex

Multiplies

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testingof all parameters.

Mapped)

– 32K-Byte L1D Data RAM/Cache (2-Way

Set-Associative)

– 128K-Byte L2 Unified Mapped RAM/Cache

(Flexible RAM/Cache Allocation)

• ARM926EJ-S Core

– Support for 32-Bit and 16-Bit (Thumb®

Mode) Instruction Sets

– DSP Instruction Extensions and Single Cycle

MAC

– ARM® Jazelle® Technology

– EmbeddedICE-RT™ Logic for Real-Time

Debug

• ARM9 Memory Architecture

– 16K-Byte Instruction Cache

– 8K-Byte Data Cache

– 32K-Byte RAM

– 8K-Byte ROM

• Dual Programmable High-Definition Video

Transcode Operations

• H.264, MPEG2, VC1, MPEG4 SP/ASP

• 99-/108-MHz Video Port Interface (VPIF)

– Two 8-Bit SD (BT.656), Single 16-Bit HD

(BT.1120), or Single Raw (8-/10-/12-Bit) Video

Capture Channels

– Two 8-Bit SD (BT.656) or Single 16-Bit HD

(BT.1120) Video Display Channels

• Video Data Conversion Engine (VDCE)

– Horizontal and Vertical Downscaling

– Chroma Conversion (4:2:2↔4:2:0)

• Two Transport Stream Interface (TSIF) Modules

(One Parallel/Serial and One Serial Only)

– TSIF for MPEG Transport Stream

– Simultaneous Synchronous or

Copyright © 2007–2010, Texas Instruments Incorporated

Page 2

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

www.ti.com

Asynchronous Input/Output Streams • Three Configurable UART/IrDA/CIR Modules

– Absolute Time Stamp Detection

– PID Filter With 7 PID Filter Tables

– Corresponding Clock Reference Generator

(One With Modem Control Signals)

– Supports up to 1.8432 Mbps UART

– SIR and MIR (0.576 MBAUD)

(CRGEN) Modules for System Time-Clock – CIR With Programmable Data Encoding

Recovery

• One Serial Peripheral Interface (SPI) With Two

• External Memory Interfaces (EMIFs) Chip-Selects

– 297-/310.5-MHz 32-Bit DDR2 SDRAM Memory • Master/Slave Inter-Integrated Circuit (I2C Bus™)

Controller With 512M-Byte Address Space

(1.8-V I/O)

– Asynchronous16-Bit-Wide EMIF (EMIFA)

With 128M-Byte Address Reach

• Flash Memory Interfaces

– NOR (8-/16-Bit-Wide Data)

– NAND (8-/16-Bit-Wide Data)

• Enhanced Direct-Memory-Access (EDMA)

Controller (64 Independent Channels)

– Programmable Default Burst Size

• 10/100/1000 Mb/s Ethernet MAC (EMAC)

– IEEE 802.3 Compliant (3.3-V I/O Only)

– Supports MII and GMII Media Independent

Interfaces

– Management Data I/O (MDIO) Module

• USB Port With Integrated 2.0 PHY

– USB 2.0 High-/Full-Speed Client

– USB 2.0 High-/Full-/Low-Speed Host

(Mini-Host, Supporting One External

Device)

• 32-Bit, 33-MHz, 3.3-V Peripheral Component

Interconnect (PCI) Master/Slave Interface

– Conforms to PCI Specification 2.3

• Two 64-Bit General-Purpose Timers (Each

Configurable as Two 32-Bit Timers)

• One 64-Bit Watchdog Timer

• Two Multichannel Audio Serial Ports (McASPs)

– One Four-Serializer Transmit/Receive Port

– One Single DIT Transmit Port for S/PDIF

• 32-Bit Host Port Interface (HPI)

• VLYNQ™ Interface (FPGA Interface)

• Two Pulse Width Modulator (PWM) Outputs

• ATA/ATAPI I/F (ATA/ATAPI-6 Specification)

• Up to 33 General-Purpose I/O (GPIO) Pins

(Multiplexed With Other Device Functions)

• On-Chip ARM ROM Bootloader (RBL)

• Individual Power-Saving Modes for ARM/DSP

• Flexible PLL Clock Generators

• IEEE-1149.1 (JTAG) BoundaryScan-Compatible

• 529-Pin Pb-Free BGA Package

(ZUT Suffix), 0.8-mm Ball Pitch

• 0.09-mm/7-Level Cu Metal Process (CMOS)

• 3.3-V and 1.8-V I/O, 1.2-/1.05-V Internal

• Applications:

– Video Encode/Decode/Transcode/Transrate

– Digital Media

– Networked Media Encode/Decode

– Video Imaging

– Video Infrastructure

– Video Conferencing

2 Digital Media System-on-Chip (DMSoC) Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 3

TMS320DM6467

www.ti.com

1.2 Description

The TMS320DM6467 (also referenced as DM6467) leverages TI’s DaVinci™ technology to meet the

networked media encode and decode digital media processing needs of next-generation embedded

devices.

The DM6467 enables OEMs and ODMs to quickly bring to market devices featuring robust operating

systems support, rich user interfaces, high processing performance, and long battery life through the

maximum flexibility of a fully integrated mixed processor solution.

The dual-core architecture of the DM6467 provides benefits of both DSP and Reduced Instruction Set

Computer (RISC) technologies, incorporating a high-performance TMS320C64x+ DSP core and an

ARM926EJ-S core.

The ARM926EJ-S is a 32-bit RISC processor core that performs 32-bit or 16-bit instructions and

processes 32-bit, 16-bit, or 8-bit data. The core uses pipelining so that all parts of the processor and

memory system can operate continuously.

The ARM core incorporates:

• A coprocessor 15 (CP15) and protection module

• Data and program Memory Management Units (MMUs) with table look-aside buffers.

• Separate 16K-byte instruction and 8K-byte data caches. Both are four-way associative with virtual

index virtual tag (VIVT).

The TMS320C64x+™ DSPs are the highest-performance fixed-point DSP generation in the

TMS320C6000™ DSP platform. It is based on an enhanced version of the second-generation

high-performance, advanced very-long-instruction-word (VLIW) architecture developed by Texas

Instruments (TI), making these DSP cores an excellent choice for digital media applications. The C64x is a

code-compatible member of the C6000™ DSP platform. The TMS320C64x+ DSP is an enhancement of

the C64x+ DSP with added functionality and an expanded instruction set.

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and

C64x+ CPU, respectively.

With performance of up to 5832 million instructions per second (MIPS) at a clock rate of 729 MHz, the

C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses

the operational flexibility of high-speed controllers and the numerical capability of array processors. The

C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly

independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The

eight functional units include instructions to accelerate the performance in video and imaging applications.

The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2376 million

MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4752 MMACS. For more details

on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide

(literature number SPRU732).

The DM6467 also has application-specific hardware logic, on-chip memory, and additional on-chip

peripherals similar to the other C6000 DSP platform devices. The DM6467 core uses a two-level

cache-based architecture. The Level 1 program cache (L1P) is a 256K-bit direct mapped cache and the

Level 1 data cache (L1D) is a 640K-bit 2-way set-associative cache. The Level 2 memory/cache (L2)

consists of an 512K-bit memory space that is shared between program and data space. L2 memory can

be configured as mapped memory, cache, or combinations of the two.

The peripheral set includes: a configurable video port; a 10/100/1000 Mb/s Ethernet MAC (EMAC) with a

Management Data Input/Output (MDIO) module; a 4-bit transfer/4-bit receive VLYNQ interface; an

inter-integrated circuit (I2C) Bus interface; a multichannel audio serial port (McASP0) with 4 serializers; a

secondary multichannel audio serial port (McASP1) with a single transmit serializer; 2 64-bit

general-purpose timers each configurable as 2 independent 32-bit timers; 1 64-bit watchdog timer; a

configurable 32-bit host port interface (HPI); up to 33-pins of general-purpose input/output (GPIO) with

Copyright © 2007–2010, Texas Instruments Incorporated Digital Media System-on-Chip (DMSoC) 3

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 4

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

programmable interrupt/event generation modes, multiplexed with other peripherals; 3 UART/IrDA/CIR

interfaces with modem interface signals on UART0; 2 pulse width modulator (PWM) peripherals; an

ATA/ATAPI-6 interface; a 33-MHz peripheral component interface (PCI); and 2 external memory

interfaces: an asynchronous external memory interface (EMIFA) for slower memories/peripherals, and a

higher speed synchronous memory interface for DDR2.

The Ethernet Media Access Controller (EMAC) provides an efficient interface between the DM6467 and

the network. The DM6467 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps)

and 100 Mbps in either half- or full-duplex mode; and 1000Base-TX (1 Gbps) in full-duplex mode with

hardware flow control and quality of service (QOS) support.

The Management Data Input/Output (MDIO) module continuously polls all 32 MDIO addresses in order to

enumerate all PHY devices in the system. Once a PHY candidate has been selected by the ARM, the

MDIO module transparently monitors its link state by reading the PHY status register. Link change events

are stored in the MDIO module and can optionally interrupt the ARM, allowing the ARM to poll the link

status of the device without continuously performing costly MDIO accesses.

The PCI, HPI, I2C, SPI, USB2.0, and VLYNQ ports allow the DM6467 to easily control peripheral devices

and/or communicate with host processors.

The DM6467 also includes a High-Definition Video/Imaging Co-processor (HDVICP) and Video Data

Conversion Engine (VDCE) to offload many video and imaging processing tasks from the DSP core,

making more DSP MIPS available for common video and imaging algorithms. For more information on the

HDVICP enhanced codecs, such as H.264 and MPEG4, please contact your nearest TI sales

representative.

www.ti.com

The rich peripheral set provides the ability to control external peripheral devices and communicate with

external processors. For details on each of the peripherals, see the related sections later in this document

and the associated peripheral reference guides.

The DM6467 has a complete set of development tools for both the ARM and DSP. These include C

compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Windows™

debugger interface for visibility into source code execution.

4 Digital Media System-on-Chip (DMSoC) Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 5

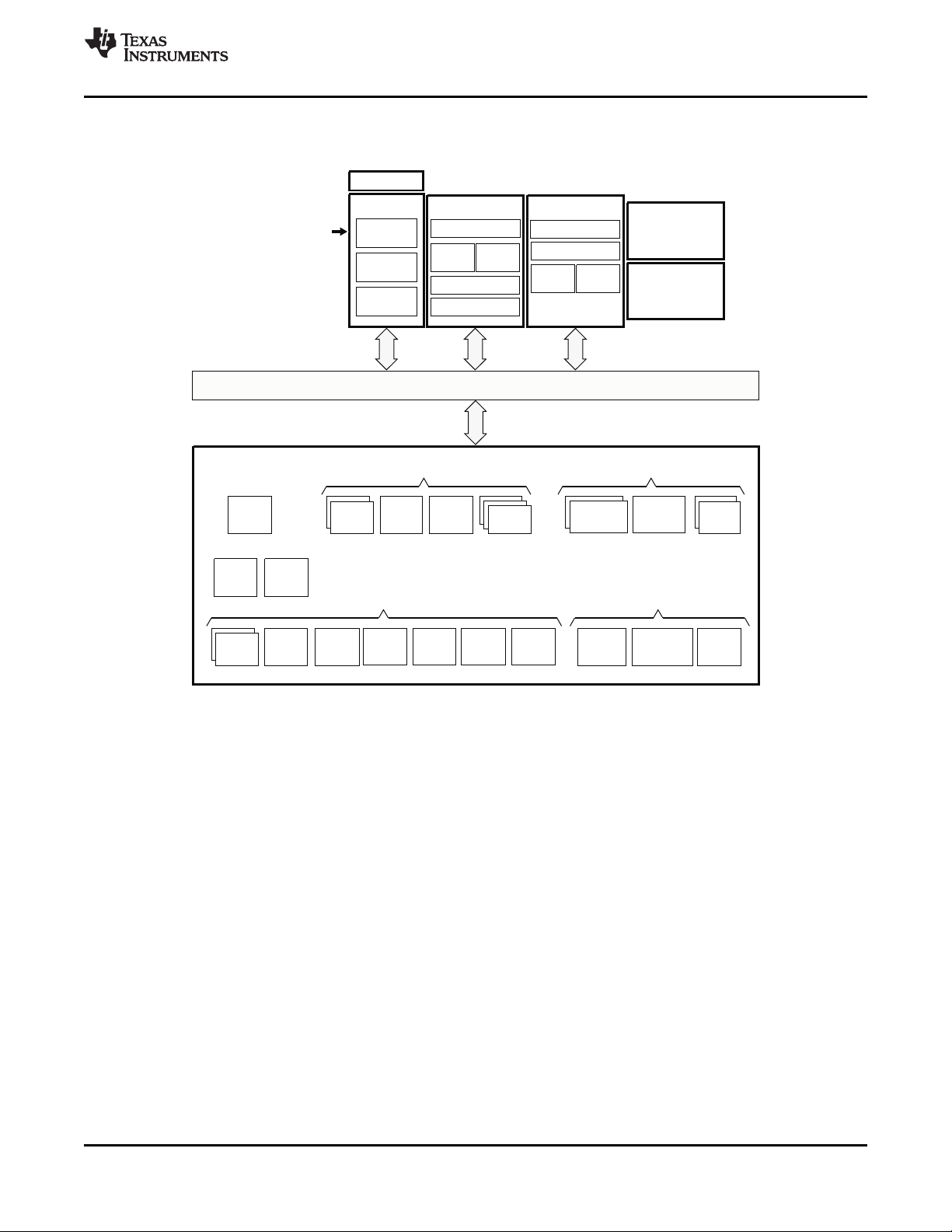

Switched Central Resource (SCR)

JTAG Interface

System Control

PLLs/Clock

Generator

Power/Sleep

Controller

Pin

Multiplexing

ARM Subsystem

ARM926EJ-S CPU

16KB

I-Cache

32KB RAM

8KB

D-Cache

8KB ROM

DSP Subsystem

C64x+ DSP CPU

TM

32KB

L1 Pgm

128KB L2 RAM

32KB

L1 Data

High-Definition

Video-Imaging

Coprocessor

(HDVICP0)

Input

Clock(s)

High-Definition

Video-Imaging

Coprocessor

(HDVICP1)

Peripherals

EDMA

I2C

SPI

UART

Serial Interfaces

DDR2

Mem Ctlr

(16b/32b)

Async EMIF/

NAND/

SmartMedia

ATA

Program/Data Storage

Watchdog

Timer

PWM

System

GeneralPurpose

Timer

USB 2.0

PHY

VLYNQ

EMAC

With

MDIO

Connectivity

HPI

McASP

Video

Port I/F

PCI

(33 MHz)

TSIF

CRGEN VDCE

TMS320DM6467

www.ti.com

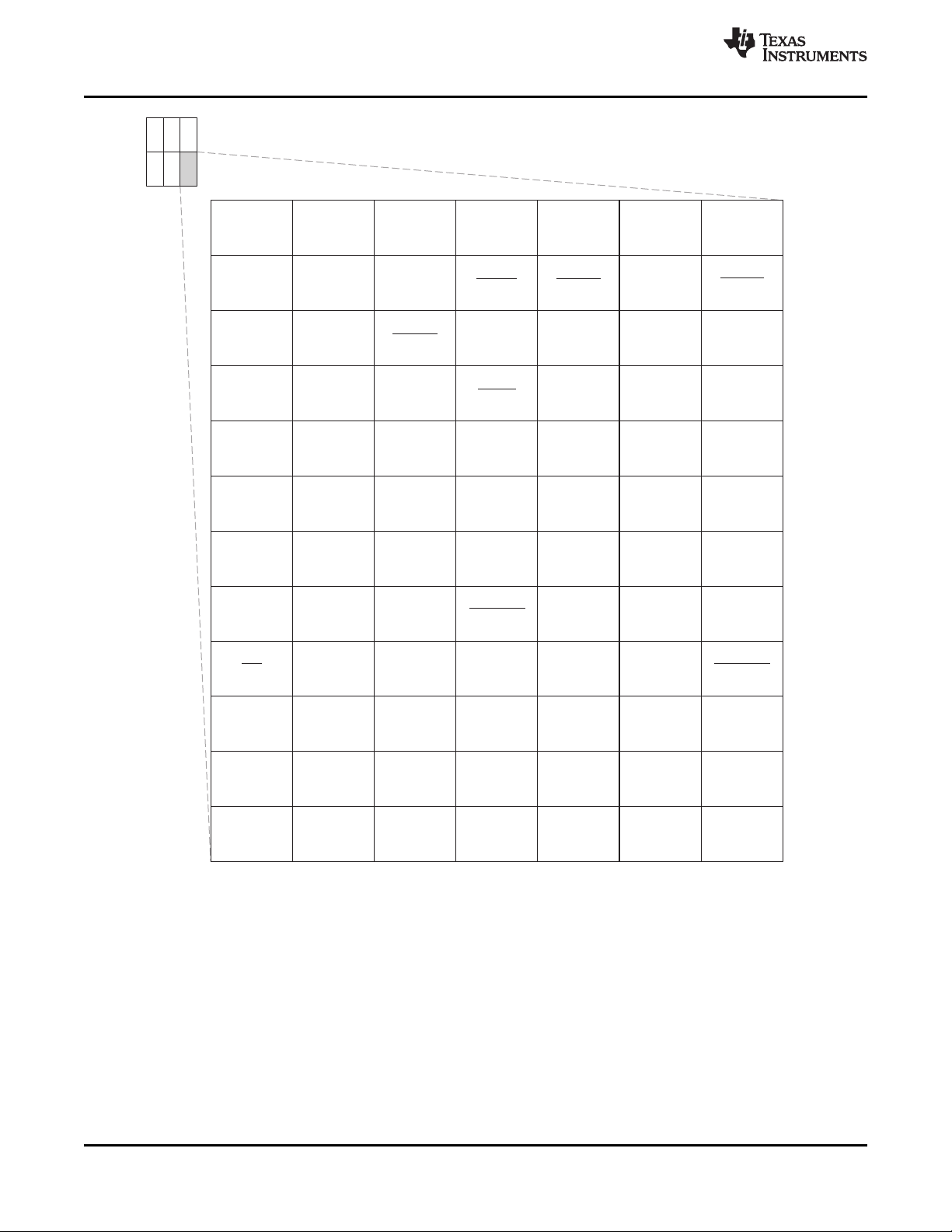

1.3 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the device.

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Copyright © 2007–2010, Texas Instruments Incorporated Digital Media System-on-Chip (DMSoC) 5

Figure 1-1. TMS320DM6467 Functional Block Diagram

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 6

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

www.ti.com

1 Digital Media System-on-Chip (DMSoC) ............ 1 7.1 Parameter Information ............................ 143

1.1 Features .............................................. 1

1.2 Description ........................................... 3

1.3 Functional Block Diagram ............................ 5

2 Revision History ......................................... 7

3 Device Overview ........................................ 8

3.1 Device Characteristics ............................... 8

3.2 Device Compatibility ................................ 11

3.3 ARM Subsystem .................................... 11

3.4 DSP Subsystem .................................... 15

3.5 Memory Map Summary ............................. 20

3.6 Pin Assignments .................................... 24

3.7 Terminal Functions ................................. 30

3.8 Device Support ..................................... 81

3.9 Documentation Support ............................ 83

3.10 Community Resources ............................. 83

4 Device Configurations ................................ 85

4.1 System Module Registers .......................... 85

4.2 Power Considerations .............................. 87

4.3 Clock Considerations ............................... 90

4.4 Boot Sequence ..................................... 97

4.5 Configurations At Reset ........................... 103

4.6 Configurations After Reset ........................ 106

4.7 Multiplexed Pin Configurations .................... 114

4.8 Debugging Considerations ........................ 137

5 System Interconnect ................................ 139

6 Device Operating Conditions ...................... 140

6.1 Absolute Maximum Ratings Over Operating Case

Temperature Range (Unless Otherwise Noted)

..................................................... 140

6.2 Recommended Operating Conditions ............. 141

6.3 Electrical Characteristics Over Recommended

Ranges of Supply Voltage and Operating

Temperature (Unless Otherwise Noted) .......... 142

7 Peripheral Information and Electrical

Specifications ......................................... 143

7.2 Recommended Clock and Control Signal Transition

Behavior ........................................... 144

7.3 Power Supplies .................................... 145

7.4 External Clock Input From DEV_MXI/DEV_CLKIN

and AUX_MXI/AUX_CLKIN Pins .................. 154

7.5 Clock PLLs ........................................ 157

7.6 Enhanced Direct Memory Access (EDMA3)

Controller .......................................... 165

7.7 Reset .............................................. 185

7.8 Interrupts .......................................... 196

7.9 External Memory Interface (EMIF) ................ 202

7.10 DDR2 Memory Controller ......................... 209

7.11 Video Port Interface (VPIF) ....................... 222

7.12 Transport Stream Interface (TSIF) ................ 230

7.13 Clock Recovery Generator (CRGEN) ............. 240

7.14 Video Data Conversion Engine (VDCE) .......... 243

7.15 Peripheral Component Interconnect (PCI) ........ 246

7.16 Ethernet MAC (EMAC) ............................ 252

7.17 Management Data Input/Output (MDIO) .......... 262

7.18 Host-Port Interface (HPI) Peripheral .............. 264

7.19 USB 2.0 ........................................... 272

7.20 ATA Controller ..................................... 282

7.21 VLYNQ ............................................ 297

7.22 Multichannel Audio Serial Port (McASP0/1)

Peripherals ........................................ 302

7.23 Serial Peripheral Interface (SPI) .................. 314

7.24 Universal Asynchronouse Receiver/Transmitter

(UART) ............................................ 329

7.25 Inter-Integrated Circuit (I2C) ...................... 336

7.26 Pulse Width Modulator (PWM) .................... 340

7.27 Timers ............................................. 342

7.28 General-Purpose Input/Output (GPIO) ............ 345

7.29 IEEE 1149.1 JTAG ................................ 348

8 Mechanical Packaging and Orderable

Information ............................................ 351

8.1 Thermal Data for ZUT ............................. 351

8.2 Packaging Information ............................ 351

6 Contents Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 7

TMS320DM6467

www.ti.com

2 Revision History

This data manual revision history highlights the technical changes made to the SPRS403F device-specific

data manual to make it an SPRS403G revision.

Scope: Applicable updates to the DM646x DMSoC device family, specifically relating to the

TMS320DM6467 device (all Silicon Revisions 3.0, 1.1, and 1.0) which is now in the production data (PD)

stage of development have been incorporated.

• Added, for clarification, the device-specific DDR2 Memory Controller speeds: 297-MHz (-594) and

310.5-MHz (-729).

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Global

Section 1.2

Description

Section 3.5 Table 3-3, Memory Map Summary:

Memory Map Summary

• Added, for clarification, the device-specific DDR2 Memory Controller speeds: 297-MHz (-594) and

310.5-MHz (-729)

• First paragraph:

– Updated/Changed "... to meet the networked media encode and decode application processing

needs ..." to "... to meet the networked media encode and decode digital media processing needs

..."

• Deleted C64x+ PCI Data access to address range 0x3000 0000 to 0x3FFF FFFF

Table 3-4, Configuration Memory Map Summary:

• Deleted C64x+ Timer2 access at address range 0x01C2 1C00 to 0x01C2 1FFF

• Deleted C64x+ PLL Controller1 access at address range 0x01C4 0800 to 0x01C4 0BFF

• Deleted C64x+ PLL Controller2 access at address range 0x01C4 0C00 to 0x01C4 0FFF

• Deleted HPI, PCI, and VLYNQ Master Peripheral Accessibility for address range 0x01D0 2000 to 0x01DF

FFFF

• Deleted HPI, PCI, and VLYNQ Master Peripheral Accessibility for address range 0x01E0 0000 to 0x01FF

FFFF

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Section 3.7 Table 3-6, Oscillator/PLL Terminal Functions:

Terminal Functions

Section 3.8.2 Figure 3-8, Device Nomenclature:

Device and

Development-Support Tool

Nomenclature

Section 6 Section 6.2, Recommended Operating Conditions:

Device Operating

Conditions

Section 7 Section 7.1.3, Timing Parameters and Board Routing Analysis:

Peripheral Information and

Electrical Specifications

• Updated/Changed DEV_CVDDdescription

• Updated/Changed AUX_CVDDdescription

Table 3-10, DDR2 Memory Controller Terminal Functions:

• Updated/Changed the ± resistor tolerance value to "5%" for the DDR_ZN [M19] and DDR_ZP [L19]

signals

• Updated figure

• Added associated "For actual device part numbers (P/Ns) and ordering information, ..." footnote

• Updated/Changed DDR_ZP tolerance from "±0.5%" to "±5%"

• Updated/ Changed DDR_ZN tolerance from "±0.5%" to "±5%"

• Updated/Changed second paragraph ("For the DDR2 memory controller interface, it is not ...")

Copyright © 2007–2010, Texas Instruments Incorporated Revision History 7

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 8

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Section 7.4.1 Figure 7-8, 27-MHz System Oscillator:

Clock Input Option 1—Cr

ystal

Section 7.4.2 Figure 7-10, 1.8-V LVCMOS-Compatible Clock Input:

Clock Input Option

2—1.8-V

LVCMOS-Compatible Clock

Input

Section 7.10.1 Table 7-32, Switching Characteristics Over Recommended Operating Conditions for DDR2 Memory

DDR2 Memory Controller Controller:

Electrical Data/Timing

Section 7.15.3 Deleted PCI Configuration Register table (was Table 7-63)

PCI Peripheral Register

Description(s)

Section 7.17.2 Table 7-80, Timing Requirements for MDIO Input:

Management Data

Input/Output (MDIO)

Electrical Data/Timing

Section 7.29

IEEE 1149.1 JTAG

• Added associated "The DEV_CVDDcore voltage value is device dependent (e.g., ..." footnote for

clarification

Figure 7-9, 24-MHz Auxiliary Oscillator:

• Added associated "The AUX_CVDDcore voltage value is device dependent (e.g., ..." footnote for

clarification

• Added associated "The DEV_CVDDcore voltage value is device dependent (e.g., ..." footnote for

clarification

Figure 7-11, 1.8-V LVCMOS-Compatible Clock Input:

• Added associated "The AUX_CVDDcore voltage value is device dependent (e.g., ..." footnote for

clarification

• Added frequency parameter with MIN/MAX values for clarification

• Updated/Changed the MIN value for t

from "10" to "0" ns.

• Deleted "For maximum reliability," from the "... DM6467 includes an internal pulldown (IPD) on the TRST

pin ..." paragraph [Cleared Documentation Feedback Issue]

h(MDCLKH-MDIO)

, Hold time, MDIO data input valid after MDCLK high

www.ti.com

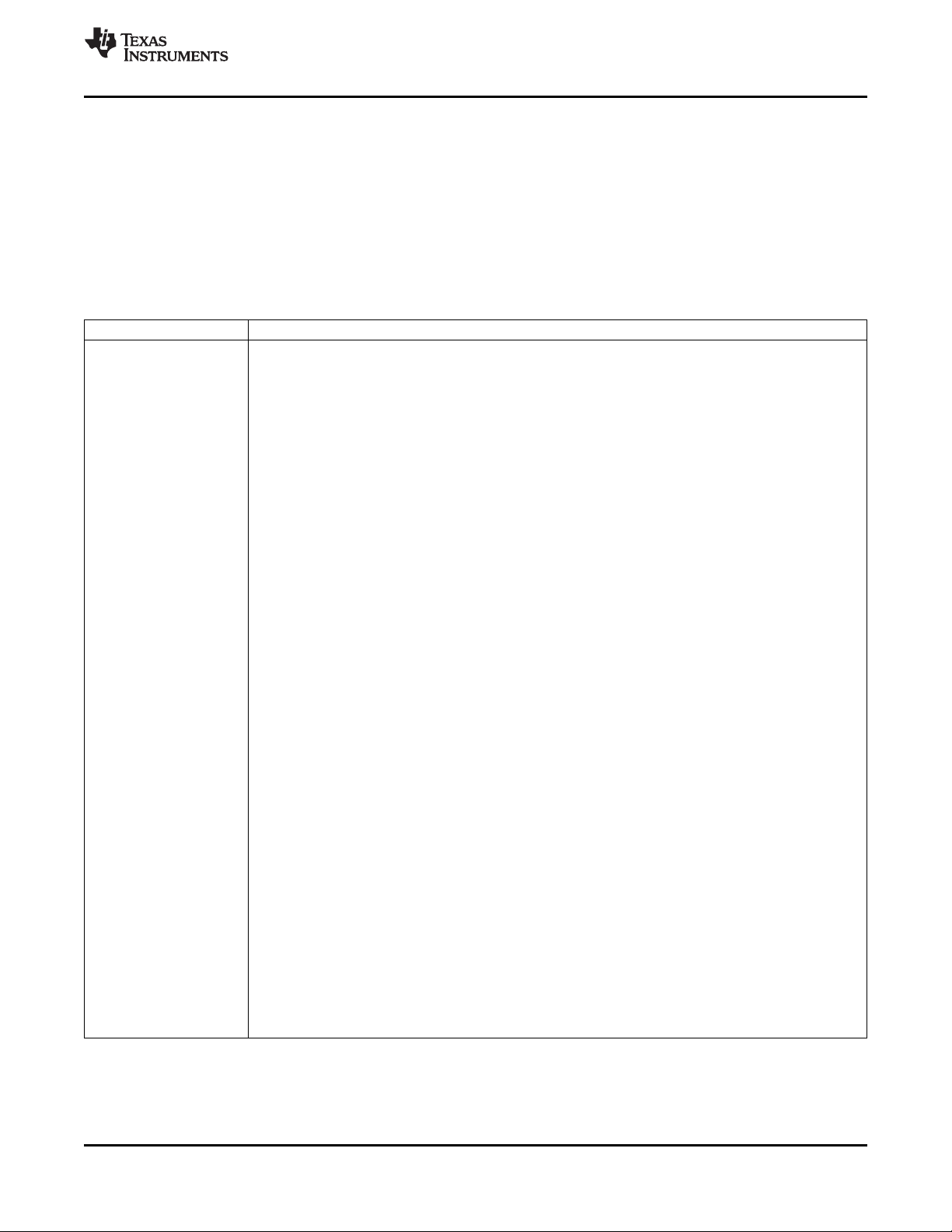

3 Device Overview

3.1 Device Characteristics

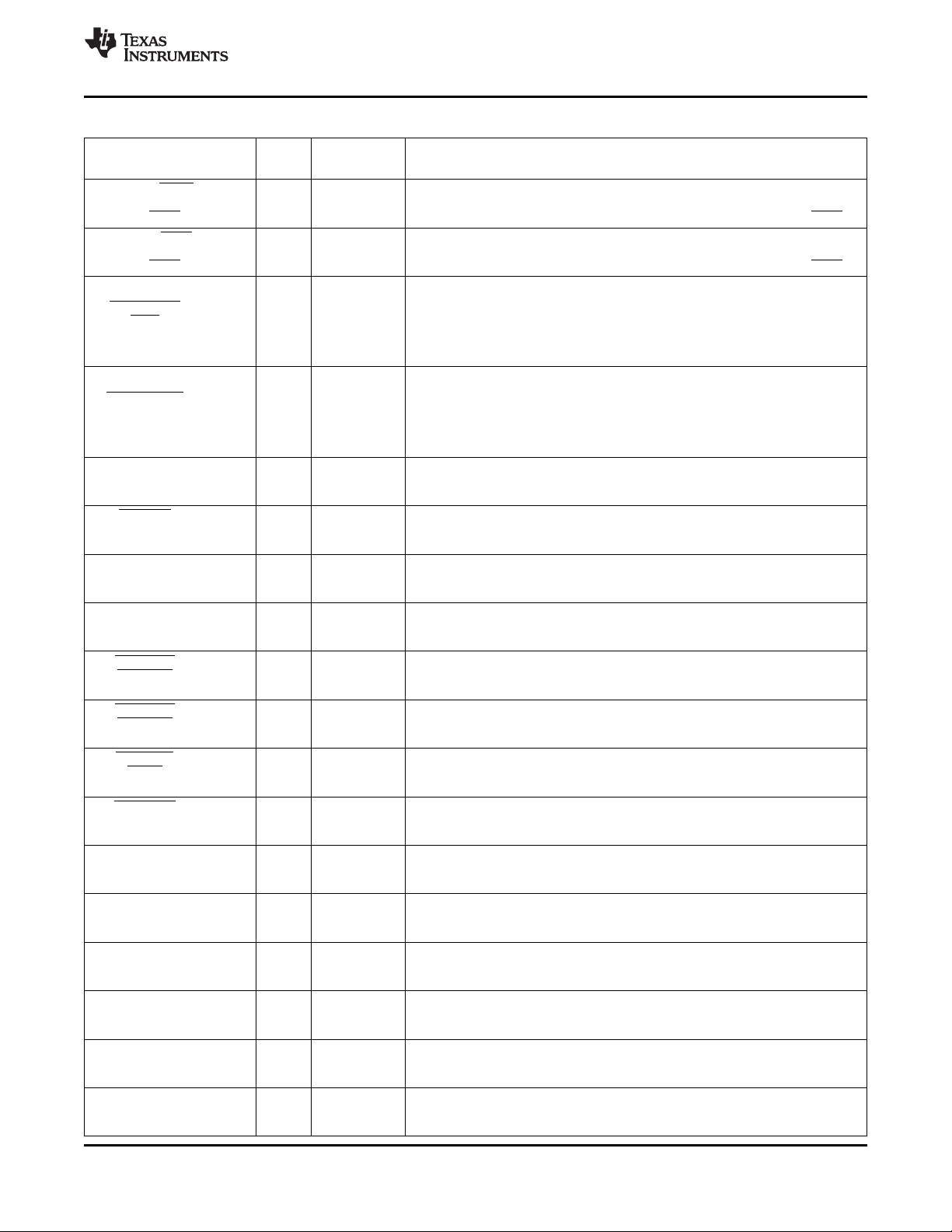

Table 3-1 provides an overview of the TMS320DM6467 SoC. The table shows significant features of the

device, including the capacity of on-chip RAM, peripherals, internal peripheral bus frequency relative to the

C64x+ DSP, and the package type with pin count.

8 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 9

TMS320DM6467

www.ti.com

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

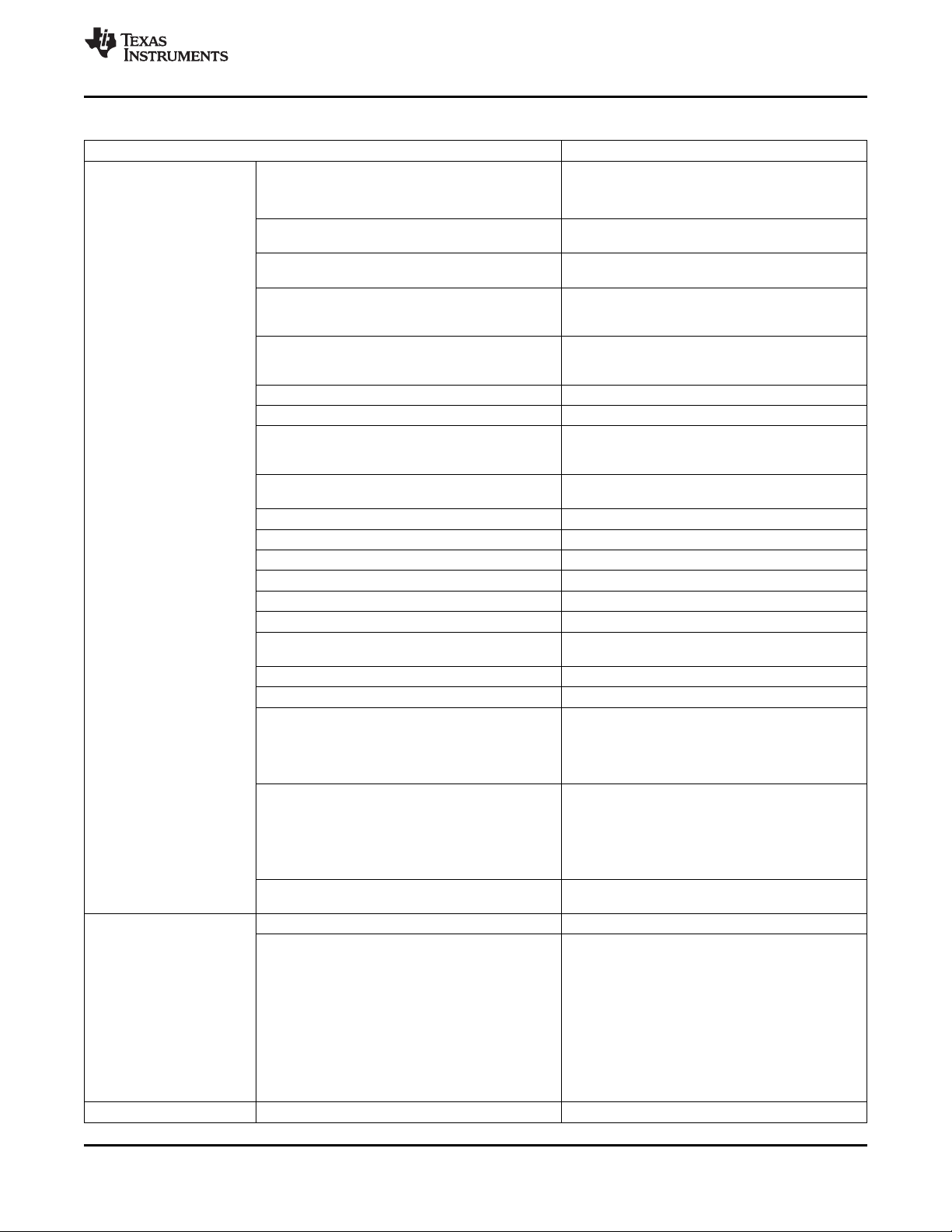

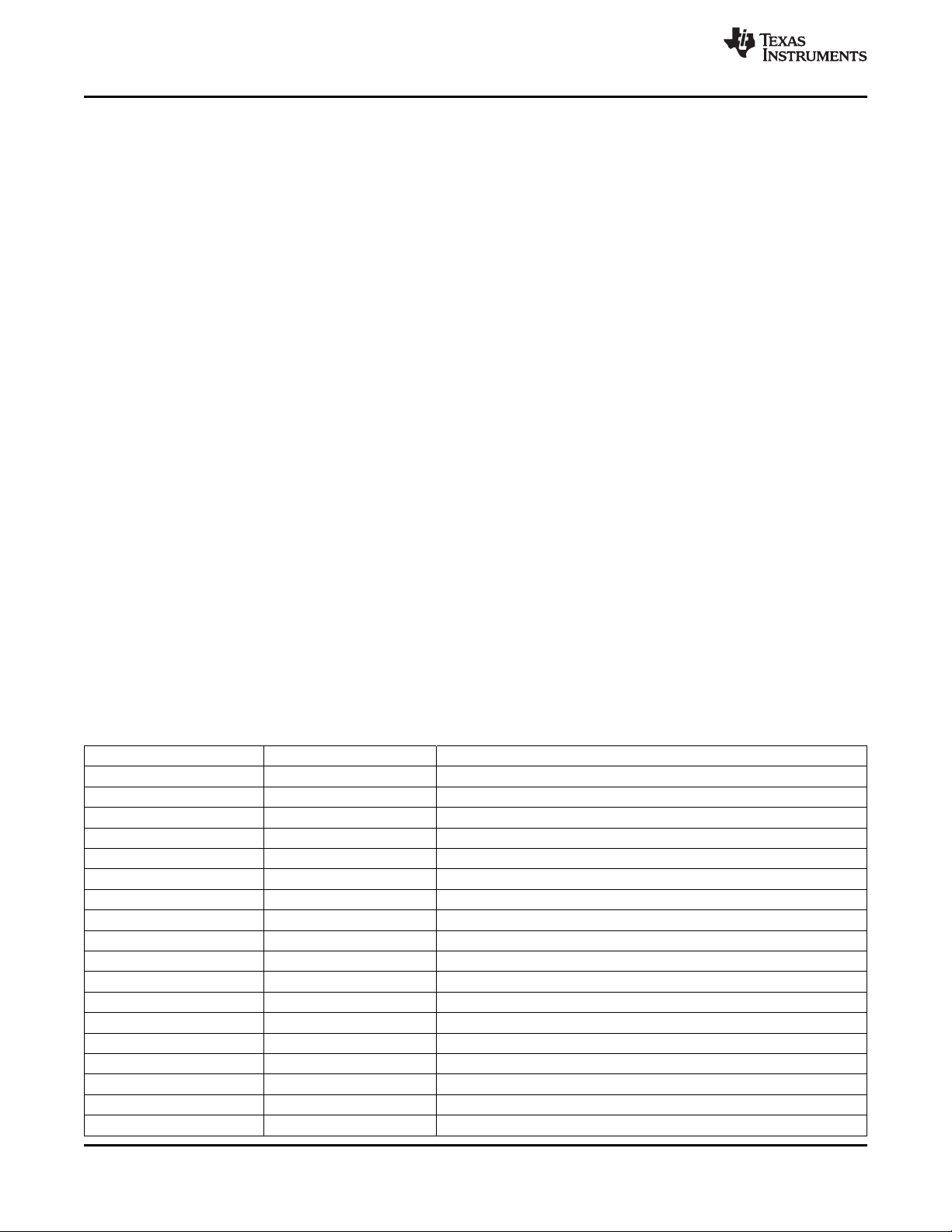

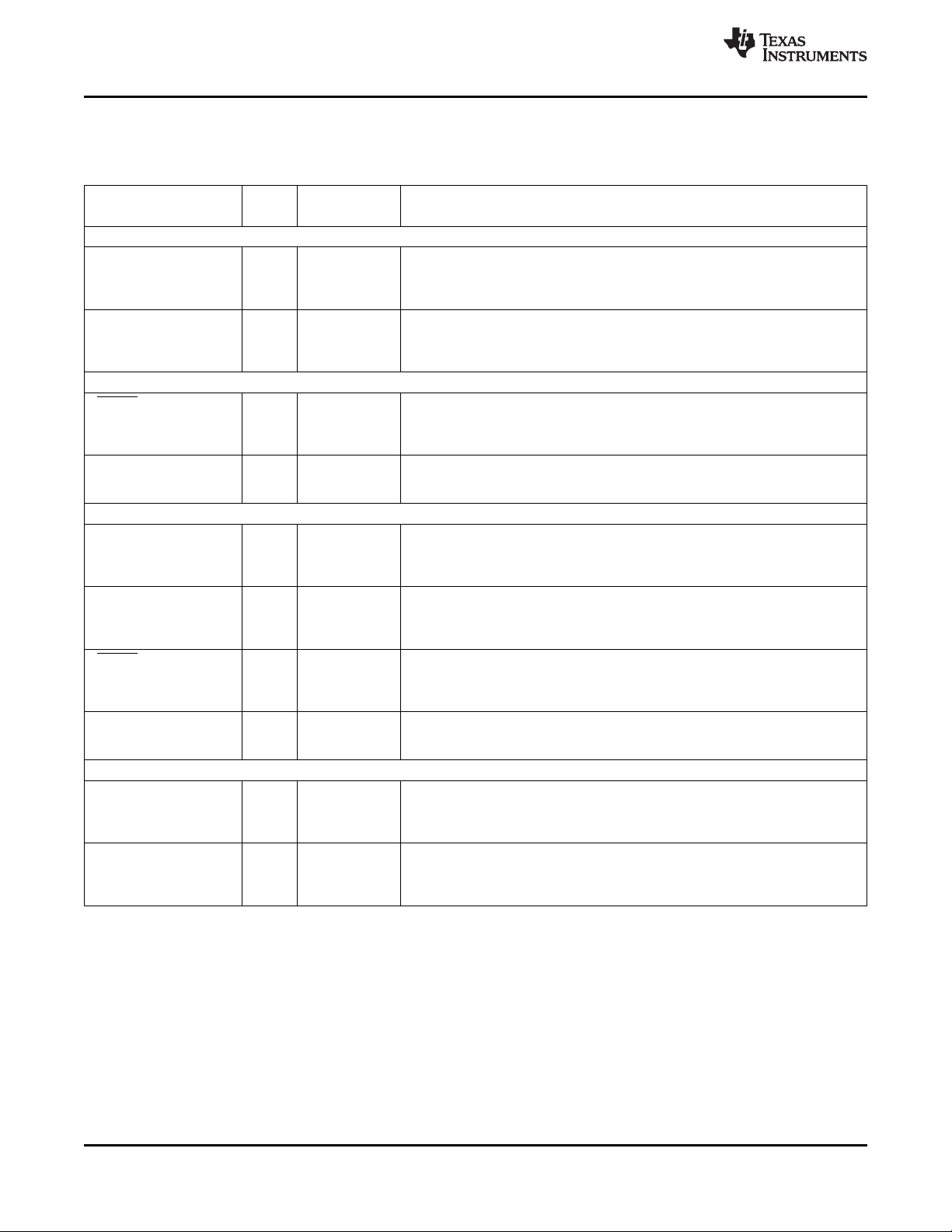

Table 3-1. Characteristics of the DM6467 Processor

HARDWARE FEATURES DM6467

DDR2 Memory Controller

297-MHz (-594)

310.5-MHz (-729)

Asynchronous EMIF (EMIFA)

EDMA

Timers separate 32-bit timers)

UART control)

SPI 1 (supports 2 slave devices)

I2C 1 (Master/Slave)

Multichannel Audio Serial Port (McASP) one DIT transmit only with 1 serializer for S/PDIF

Peripherals

Not all peripherals pins are

available at the same time

(for more detail, see the

Device Configurations

section).

On-Chip Memory

CPU ID + CPU Rev ID Control Status Register (CSR.[31:16]) 0x1000

10/100/1000 Ethernet MAC with Management Data

Input/Output (MDIO)

VLYNQ 1

General-Purpose Input/Output Port (GPIO) Up to 33 pins

PWM 2 outputs

ATA 1 (ATA/ATAPI-6)

PCI 1 (32-bit, 33 MHz)

HPI 1 (16-/32-bit multiplexed address/data)

VDCE

Clock Recovery Generator (CRGEN) 1

Power Sleep Controller (PSC) 1 (peripheral/module clock gating)

Configurable Video Port Interface (VPIF) 1 16-bit Y/C capture channel or

99-MHz (-594) 1 8-/10-/12-bit raw video capture channel and

108-MHz (-729) 2 8-bit BT.656 display channels or

Transport Stream Interface (TSIF) 1 with serial-only input and output

USB 2.0

Size (Bytes) 248KB RAM, 8KB ROM

Organization

Asynchronous (8/16-bit bus width) RAM, Flash

2 64-Bit General Purpose (each configurable as 2

3 (with SIR, MIR, CIR support and RTS/CTS flow

1 with 8-bit parallel or serial input and output

Each with corresponding clock recovery generator

DSP

• 32KB L1 Program (L1P)/Cache (up to 32KB)

• 32KB L1 Data (L1D)/Cache (up to 32KB)

• 128KB Unified Mapped RAM/Cache (L2)

ARM

• 16KB I-cache

• 8KB D-cache

• 32KB RAM

• 8KB ROM

DDR2 (16/32-bit bus width)

(NOR, NAND)

64 independent channels

8 QDMA channels

1 64-Bit Watchdog

(UART0 Supports Modem Interface)

2 (one transmit/receive with 4 serializers,

output)

1 (with MII/GMII Interface)

1 [horizontal and vertical downscaling,

chroma conversion (4:2:2↔4:2:0)]

2 8-bit BT.656 capture channels or

1 16-bit Y/C display channel

MPEG transport stream interface

(CRGEN) for external VCXO control.

High- and Full-Speed Device

High-, Full-, and Low-Speed Host

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 9

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 10

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

www.ti.com

Table 3-1. Characteristics of the DM6467 Processor (continued)

HARDWARE FEATURES DM6467

C64x+ Megamodule Revision ID Register (MM_REVID[15:0])

Revision (address location: 0x0181 2000)

JTAG BSDL_ID

CPU Frequency MHz

Cycle Time ns

Voltage Core (V) 1.2 V (-594V, -594AV)

PLL Options DEV_CLKIN frequency multiplier (PLLC2) x1 (Bypass), x14 to x22 (-594)

BGA Package 19 x 19 mm 529-Pin BGA (ZUT)

Process Technology mm 0.09 mm

Product Status

(1) PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

(1)

JTAGID Register See Section 7.29.1, JTAG ID (JTAGID) Register

(address location: 0x01C4 0028) Description(s)

ARM926 297 MHz(-594)

ARM926 364.5 MHz(-729)

Normal 1.2 V (-594, -594A, -729, -729D)

SmartReflex

(see Table 4-39)

I/O (V) 1.8 V, 3.3 V (-594, -729)

DEV_CLKIN frequency multiplier (PLLC1) x1 (Bypass), x14 to x22 (-594)

(27-MHz reference) x1 (Bypass), x14 to x27 (-729)

(27-MHz reference) x1 (Bypass), x14 to x23 (-729)

AUX_CLKIN frequency 24/48-MHz reference

Product Preview (PP),

Advance Information (AI), PD

or Production Data (PD)

0x0000

DSP 594 MHz (-594)

DSP 729 MHz (-729)

DSP 1.68 ns (-594)

DSP 1.37 ns (-729)

ARM926 3.37 ns (-594)

ARM926 2.74 ns (-729)

1.05 V (-594V, -594AV)

10 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 11

TMS320DM6467

www.ti.com

3.2 Device Compatibility

The ARM926EJ-S RISC CPU is compatible with other ARM9 CPUs from ARM Holdings plc.

The C64x+ DSP core is code-compatible with the C6000™ DSP platform and supports features of the

C64x DSP family.

3.3 ARM Subsystem

The ARM Subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In

general, the ARM is responsible for configuration and control of the device; including the DSP Subsystem,

the VPSS Subsystem, and a majority of the peripherals and external memories.

The ARM Subsystem includes the following features:

• ARM926EJ-S RISC processor

• ARMv5TEJ (32/16-bit) instruction set

• Little endian operation

• Co-Processor 15 (CP15)

• MMU

• 16KB Instruction cache

• 8KB Data cache

• Write Buffer

• 32KB Internal Tightly-Coupled Memory (TCM) RAM (32-bit wide access)

• 8KB Internal ROM (ARM bootloader for non-EMIFA boot options)

• Embedded Trace Module and Embedded Trace Buffer (ETM/ETB)

• ARM Interrupt Controller

• PLL Controller

• Power and Sleep Controller (PSC)

• System Module

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

3.3.1 ARM926EJ-S RISC CPU

The ARM Subsystem integrates the ARM926EJ-S processor. The ARM926EJ-S processor is a member of

ARM9 family of general-purpose microprocessors. This processor is targeted at multi-tasking applications

where full memory management, high performance, low die size, and low power are all important. The

ARM926EJ-S processor supports the 32-bit ARM and 16 bit THUMB instruction sets, enabling the user to

trade off between high performance and high code density. Specifically, the ARM926EJ-S processor

supports the ARMv5TEJ instruction set, which includes features for efficient execution of Java byte codes,

providing Java performance similar to Just in Time (JIT) Java interpreter, but without associated code

overhead.

The ARM926EJ-S processor supports the ARM debug architecture and includes logic to assist in both

hardware and software debug. The ARM926EJ-S processor has a Harvard architecture and provides a

complete high performance subsystem, including:

• ARM926EJ -S integer core

• CP15 system control coprocessor

• Memory Management Unit (MMU)

• Separate instruction and data Caches

• Write buffer

• Separate instruction and data Tightly-Coupled Memories (TCMs) [internal RAM] interfaces

• Separate instruction and data AHB bus interfaces

• Embedded Trace Module and Embedded Trace Buffer (ETM/ETB)

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 11

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 12

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

For more complete details on the ARM9, refer to the ARM926EJ-S Technical Reference Manual, available

at http://www.arm.com

3.3.2 CP15

The ARM926EJ-S system control coprocessor (CP15) is used to configure and control instruction and

data caches, Tightly-Coupled Memories (TCMs), Memory Management Unit (MMU), and other ARM

subsystem functions. The CP15 registers are programmed using the MRC and MCR ARM instructions,

when the ARM in a privileged mode such as supervisor or system mode.

3.3.3 MMU

The ARM926EJ-S MMU provides virtual memory features required by operating systems such as Linux®,

Windows® CE, Ultron®, ThreadX®, etc. A single set of two level page tables stored in main memory is

used to control the address translation, permission checks and memory region attributes for both data and

instruction accesses. The MMU uses a single unified Translation Lookaside Buffer (TLB) to cache the

information held in the page tables. The MMU features are:

• Standard ARM architecture v4 and v5 MMU mapping sizes, domains and access protection scheme.

• Mapping sizes are:

– 1MB (sections)

– 64KB (large pages)

– 4KB (small pages)

– 1KB (tiny pages)

• Access permissions for large pages and small pages can be specified separately for each quarter of

the page (subpage permissions)

• Hardware page table walks

• Invalidate entire TLB, using CP15 register 8

• Invalidate TLB entry, selected by MVA, using CP15 register 8

• Lockdown of TLB entries, using CP15 register 10

www.ti.com

3.3.4 Caches and Write Buffer

The size of the Instruction Cache is 16KB, Data cache is 8KB. Additionally, the Caches have the following

features:

• Virtual index, virtual tag, and addressed using the Modified Virtual Address (MVA)

• Four-way set associative, with a cache line length of eight words per line (32-bytes per line) and with

two dirty bits in the Dcache

• Dcache supports write-through and write-back (or copy back) cache operation, selected by memory

region using the C and B bits in the MMU translation tables.

• Critical-word first cache refilling

• Cache lockdown registers enable control over which cache ways are used for allocation on a line fill,

providing a mechanism for both lockdown, and controlling cache corruption

• Dcache stores the Physical Address TAG (PA TAG) corresponding to each Dcache entry in the TAG

RAM for use during the cache line write-backs, in addition to the Virtual Address TAG stored in the

TAG RAM. This means that the MMU is not involved in Dcache write-back operations, removing the

possibility of TLB misses related to the write-back address.

• Cache maintenance operations provide efficient invalidation of, the entire Dcache or Icache, regions of

the Dcache or Icache, and regions of virtual memory.

The write buffer is used for all writes to a noncachable bufferable region, write-through region and write

misses to a write-back region. A separate buffer is incorporated in the Dcache for holding write-back for

cache line evictions or cleaning of dirty cache lines. The main write buffer has 16-word data buffer and a

four-address buffer. The Dcache write-back has eight data word entries and a single address entry.

12 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 13

TMS320DM6467

www.ti.com

3.3.5 Tightly Coupled Memory (TCM)

ARM internal RAM is provided for storing real-time and performance-critical code/data and the Interrupt

Vector table. ARM internal ROM enables non-EMIFA boot options, such as NAND and UART. The RAM

and ROM memories interfaced to the ARM926EJ-S via the tightly coupled memory interface that provides

for separate instruction and data bus connections. Since the ARM TCM does not allow instructions on the

D-TCM bus or data on the I-TCM bus, an arbiter is included so that both data and instructions can be

stored in the internal RAM/ROM. The arbiter also allows accesses to the RAM/ROM from extra-ARM

sources (e.g., EDMA or other masters). The ARM926EJ-S has built-in DMA support for direct accesses to

the ARM internal memory from a non-ARM master. Because of the time-critical nature of the TCM link to

the ARM internal memory, all accesses from non-ARM devices are treated as DMA transfers.

Instruction and Data accesses are differentiated via accessing different memory map regions, with the

instruction region from 0x0000 through 0x7FFF and data from 0x10000 through 0x17FFF. The instruction

region at 0x0000 and data region at 0x10000 map to the same physical 32-KB TCM RAM. Placing the

instruction region at 0x0000 is necessary to allow the ARM Interrupt Vector table to be placed at 0x0000,

as required by the ARM architecture. The internal 32-KB RAM is split into two physical banks of 16KB

each, which allows simultaneous instruction and data accesses to be accomplished if the code and data

are in separate banks.

3.3.6 Advanced High-Performance Bus (AHB)

The ARM Subsystem uses the AHB port of the ARM926EJ-S to connect the ARM to the Config bus and

the external memories. Arbiters are employed to arbitrate access to the separate D-AHB and I-AHB by the

Config Bus and the external memories bus.

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

3.3.7 Embedded Trace Macrocell (ETM) and Embedded Trace Buffer (ETB)

To support real-time trace, the ARM926EJ-S processor provides an interface to enable connection of an

Embedded Trace Macrocell (ETM). The ARM926ES-J Subsystem in the DM6467 also includes the

Embedded Trace Buffer (ETB). The ETM consists of two parts:

• Trace Port provides real-time trace capability for the ARM9.

• Triggering facilities provide trigger resources, which include address and data comparators, counter,

and sequencers.

The DM6467 trace port is not pinned out and is instead only connected to the Embedded Trace Buffer.

The ETB has a 4KB buffer memory. ETB enabled debug tools are required to read/interpret the captured

trace data.

3.3.8 ARM Memory Mapping

The ARM memory map is shown in Section 3.5, Memory Map Summary of this document. The ARM has

access to memories shown in the following sections.

3.3.8.1 ARM Internal Memories

The ARM has access to the following ARM internal memories:

• 32KB ARM Internal RAM on TCM interface, logically separated into two 16KB pages to allow

simultaneous access on any given cycle if there are separate accesses for code (I-TCM bus) and data

(D-TCM) to the different memory regions.

• 8KB ARM Internal ROM

3.3.8.2 External Memories

The ARM has access to the following external memories:

• DDR2 Synchronous DRAM

• Asynchronous EMIF / NOR Flash / NAND Flash

• ATA

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 13

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 14

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

3.3.8.3 DSP Memories

The ARM has access to the following DSP memories:

• L2 RAM

• L1P RAM

• L1D RAM

3.3.8.4 ARM-DSP Integration

DM6467 ARM and DSP integration features are as follows:

• DSP visibility from ARM’s memory map, see Section 3.5, Memory Map Summary, for details

• Boot Modes for DSP - see Device Configurations section, Section 4.4.1, DSP Boot, for details

• ARM control of DSP boot / reset - see Device Configurations section, Section 4.4.2.4, ARM Boot, for

details

• ARM control of DSP isolation and powerdown / powerup - see Section 4, Device Configurations, for

details

• ARM & DSP Interrupts - see Section 7.8.1, ARM CPU Interrupts, and Section 7.8.2, DSP Interrupts, for

details

3.3.9 Peripherals

The ARM9 has access to all of the peripherals on the DM6467 device.

www.ti.com

3.3.10 PLL Controller (PLLC)

The ARM Subsystem includes the PLL Controller. The PLL Controller contains a set of registers for

configuring DM6467’s two internal PLLs (PLL1 and PLL2). The PLL Controller provides the following

configuration and control:

• PLL Bypass Mode

• Set PLL multiplier parameters

• Set PLL divider parameters

• PLL power down

• Oscillator power down

The PLLs are briefly described in this document in the Clocking section. For more detailed information on

the PLLs and PLL Controller register descriptions, see the TMS320DM646x DMSoC ARM Subsystem

Reference Guide (literature number SPRUEP9).

3.3.11 Power and Sleep Controller (PSC)

The ARM Subsystem includes the Power and Sleep Controller (PSC). Through register settings

accessible by the ARM9, the PSC provides two levels of power savings: peripheral/module clock gating

and power domain shut-off. Brief details on the PSC are given in Section 7.3, Power Supplies. For more

detailed information and complete register descriptions for the PSC, see the TMS320DM646x DMSoC

ARM Subsystem Reference Guide (literature number SPRUEP9).

3.3.12 ARM Interrupt Controller (AINTC)

The ARM Interrupt Controller (AINTC) accepts device interrupts and maps them to either the ARM’s IRQ

(interrupt request) or FIQ (fast interrupt request). The ARM Interrupt Controller is briefly described in this

document in the Interrupts section. For detailed information on the ARM Interrupt Controller, see the

TMS320DM646x DMSoC ARM Subsystem Reference Guide (literature number SPRUEP9).

14 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 15

TMS320DM6467

www.ti.com

3.3.13 System Module

The ARM Subsystem includes the System module. The System module consists of a set of registers for

configuring and controlling a variety of system functions. For details and register descriptions for the

System module, see Section 4, Device Configurations and see the TMS320DM646x DMSoC ARM

Subsystem Reference Guide (literature number SPRUEP9).

3.3.14 Power Management

DM6467 has several means of managing power consumption. There is extensive use of clock gating,

which reduces the power used by global device clocks and individual peripheral clocks. Clock

management can be utilized to reduce clock frequencies in order to reduce switching power. For more

details on power management techniques, see Section 4, Device Configurations, Section 7, Peripheral

and Electrical Specifications, and see the TMS320DM646x DMSoC ARM Subsystem Reference Guide

(literature number SPRUEP9).

DM6467 gives the programmer full flexibility to use any and all of the previously mentioned capabilities to

customize an optimal power management strategy. Several typical power management scenarios are

described in the following sections.

3.4 DSP Subsystem

The DSP Subsystem includes the following features:

• C64x+ DSP CPU

• 32KB L1 Program (L1P)/Cache (up to 32KB)

• 32KB L1 Data (L1D)/Cache (up to 32KB)

• 128KB Unified Mapped RAM/Cache (L2)

• Little endian

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

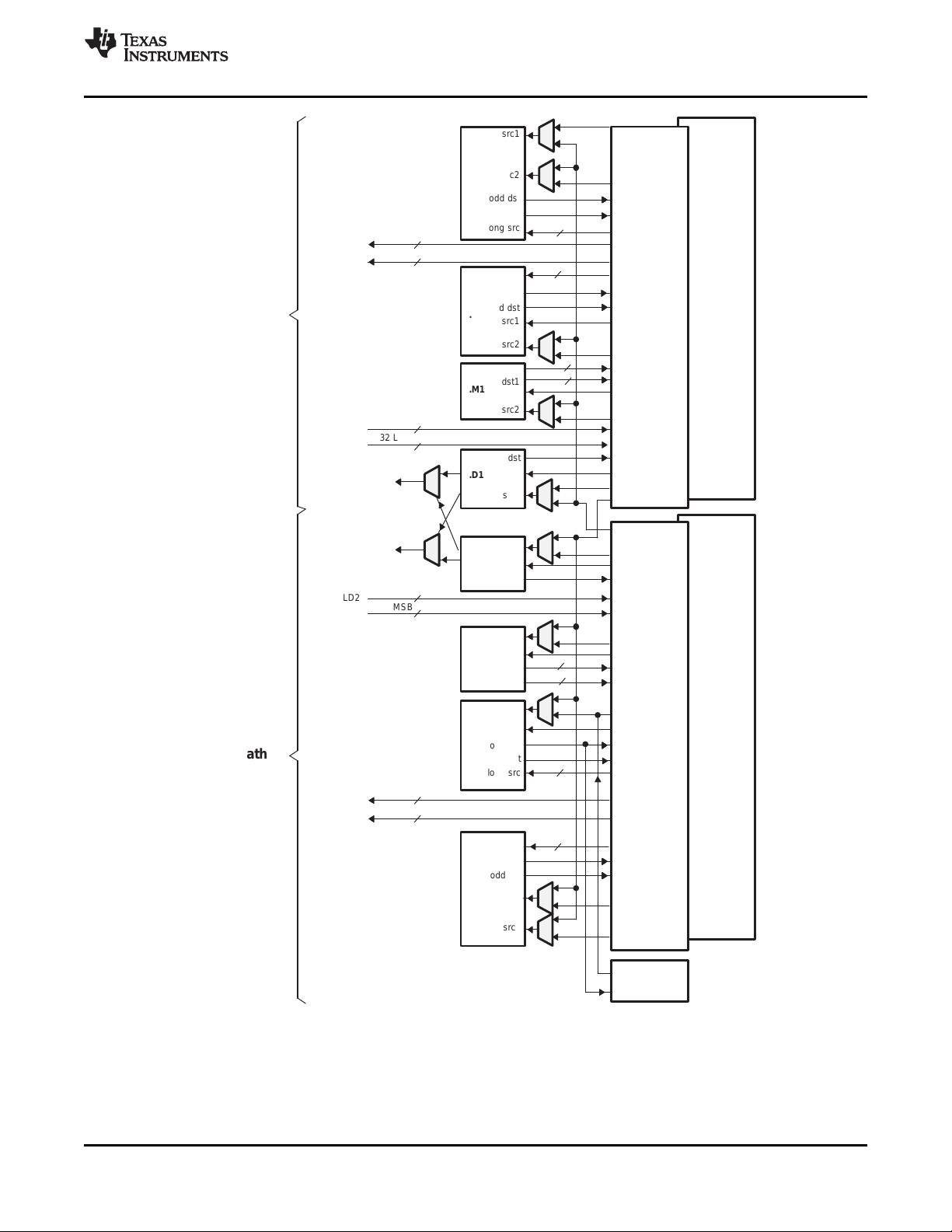

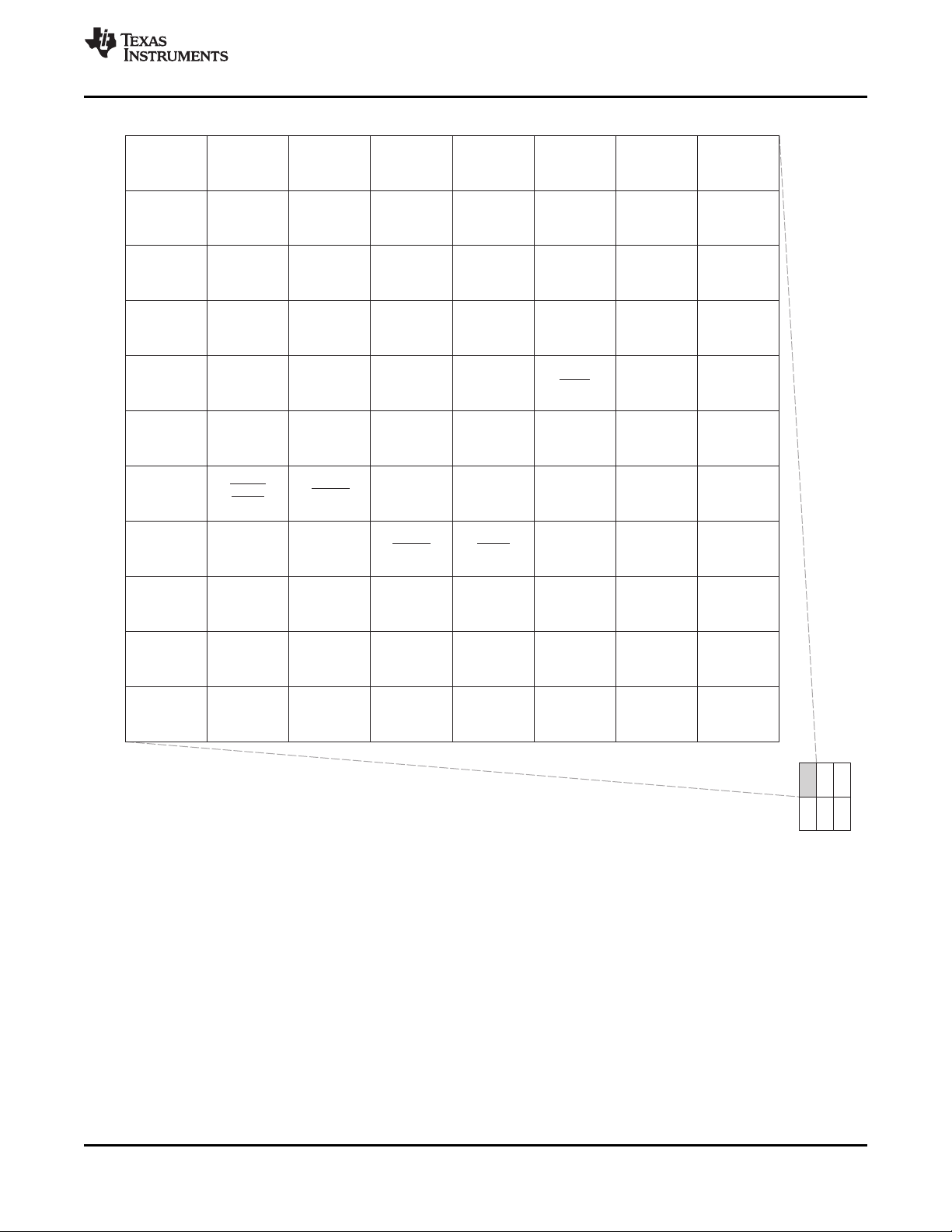

3.4.1 C64x+ DSP CPU Description

The C64x+ Central Processing Unit (CPU) consists of eight functional units, two register files, and two

data paths as shown in Figure 3-1. The two general-purpose register files (A and B) each contain

32 32-bit registers for a total of 64 registers. The general-purpose registers can be used for data or can be

data address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit

data, 40-bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are

stored in register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or

32 MSBs in the next upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one

instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units

perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from

memory to the register file and store results from the register file into memory.

The C64x+ CPU extends the performance of the C64x core through enhancements and new features.

Each C64x+ .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, one 16 x

32 bit multiply, two 16 x 16 bit multiplies, two 16 x 32 bit multiplies, two 16 x 16 bit multiplies with

add/subtract capabilities, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add operations, and four

16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There is also support for

Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms such as FFTs and

modems require complex multiplication. The complex multiply (CMPY) instruction takes for 16-bit inputs

and produces a 32-bit real and a 32-bit imaginary output. There are also complex multiplies with rounding

capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values. The

32 x 32 bit multiply instructions provide the extended precision necessary for audio and other

high-precision algorithms on a variety of signed and unsigned 32-bit data types.

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 15

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 16

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

The .L or (Arithmetic Logic Unit) now incorporates the ability to do parallel add/subtract operations on a

pair of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data

performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C64x+ core enhances the .S unit in several ways. In the C64x core, dual 16-bit MIN2 and MAX2

comparisons were only available on the .L units. On the C64x+ core they are also available on the .S unit

which increases the performance of algorithms that do searching and sorting. Finally, to increase data

packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit

and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack

instructions return parallel results to output precision including saturation support.

Other new features include:

• SPLOOP - A small instruction buffer in the CPU that aids in creation of software pipelining loops where

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

• Compact Instructions - The native instruction size for the C6000 devices is 32 bits. Many common

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C64x+

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

• Instruction Set Enhancement - As noted above, there are new instructions such as 32-bit

multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field

multiplication.

• Exceptions Handling - Intended to aid the programmer in isolating bugs. The C64x+ CPU is able to

detect and respond to exceptions, both from internally detected sources (such as illegal op-codes) and

from system events (such as a watchdog time expiration).

• Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

• Time-Stamp Counter - Primarily targeted for Real-Time Operating System (RTOS) robustness, a

free-running time-stamp counter is implemented in the CPU which is not sensitive to system stalls.

www.ti.com

For more details on the C64x+ CPU and its enhancements over the C64x architecture, see the following

documents:

• TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732)

• TMS320C64x Technical Overview (literature number SPRU395)

16 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 17

src2

src2

.D1

.M1

.S1

.L1

long src

odd dst

src2

src1

src1

src1

src1

even dst

even dst

odd dst

dst1

dst

src2

src2

src2

long src

DA1

ST1b

LD1b

LD1a

ST1a

Data path A

Odd

register

file A

(A1, A3,

A5...A31)

Odd

register

file B

(B1, B3,

B5...B31)

.D2

src1

dst

src2

DA2

LD2a

LD2b

src2

.M2

src1

dst1

.S2

src1

even dst

long src

odd dst

ST2a

ST2b

long src

.L2

even dst

odd dst

src1

Data path B

Control Register

32 MSB

32 LSB

dst2

(A)

32 MSB

32 LSB

2x

1x

32 LSB

32 MSB

32 LSB

32 MSB

dst2

(B)

(B)

(A)

8

8

8

8

32

32

32

32

(C)

(C)

Even

register

file A

(A0, A2,

A4...A30)

Even

register

file B

(B0, B2,

B4...B30)

(D)

(D)

(D)

(D)

A. On .M unit, dst2 is 32 MSB.

B. On .M unit, dst1 is 32 LSB.

C. On C64x CPU .M unit, src2 is 32 bits; on C64x+ CPU .M unit, src2 is 64 bits.

D. On .L and .S units, odd dst connects to odd register files and even dst connects to even register files.

TMS320DM6467

www.ti.com

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Figure 3-1. TMS320C64x+™ CPU (DSP Core) Data Paths

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 17

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 18

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

3.4.2 DSP Memory Mapping

The DSP memory map is shown in Section 3.5, Memory Map Summary. Configuration of the control

registers for DDR2, EMIFA, and ARM Internal RAM is supported by the ARM. The DSP has access to

memories shown in the following sections.

3.4.2.1 ARM Internal Memories

The DSP has access to the 32KB ARM Internal RAM on the ARM D-TCM interface (i.e., data only).

3.4.2.2 External Memories

The DSP has access to the following External memories:

• DDR2 Synchronous DRAM

• Asynchronous EMIF / NOR Flash

• ATA

3.4.2.3 DSP Internal Memories

The DSP has access to the following DSP memories:

• L2 RAM

• L1P RAM

• L1D RAM

www.ti.com

3.4.2.4 C64x+ CPU

The C64x+ core uses a two-level cache-based architecture. The Level 1 Program memory/cache (L1P)

consists of 32 KB memory space that can be configured as mapped memory or direct mapped cache. The

Level 1 Data memory/cache (L1D) consists of 32 KB that can be configured as mapped memory or 2-way

set associated cache. The Level 2 memory/cache (L2) consists of a 128 KB RAM memory space that is

shared between program and data space. L2 memory can be configured as mapped memory, cache, or a

combination of both.

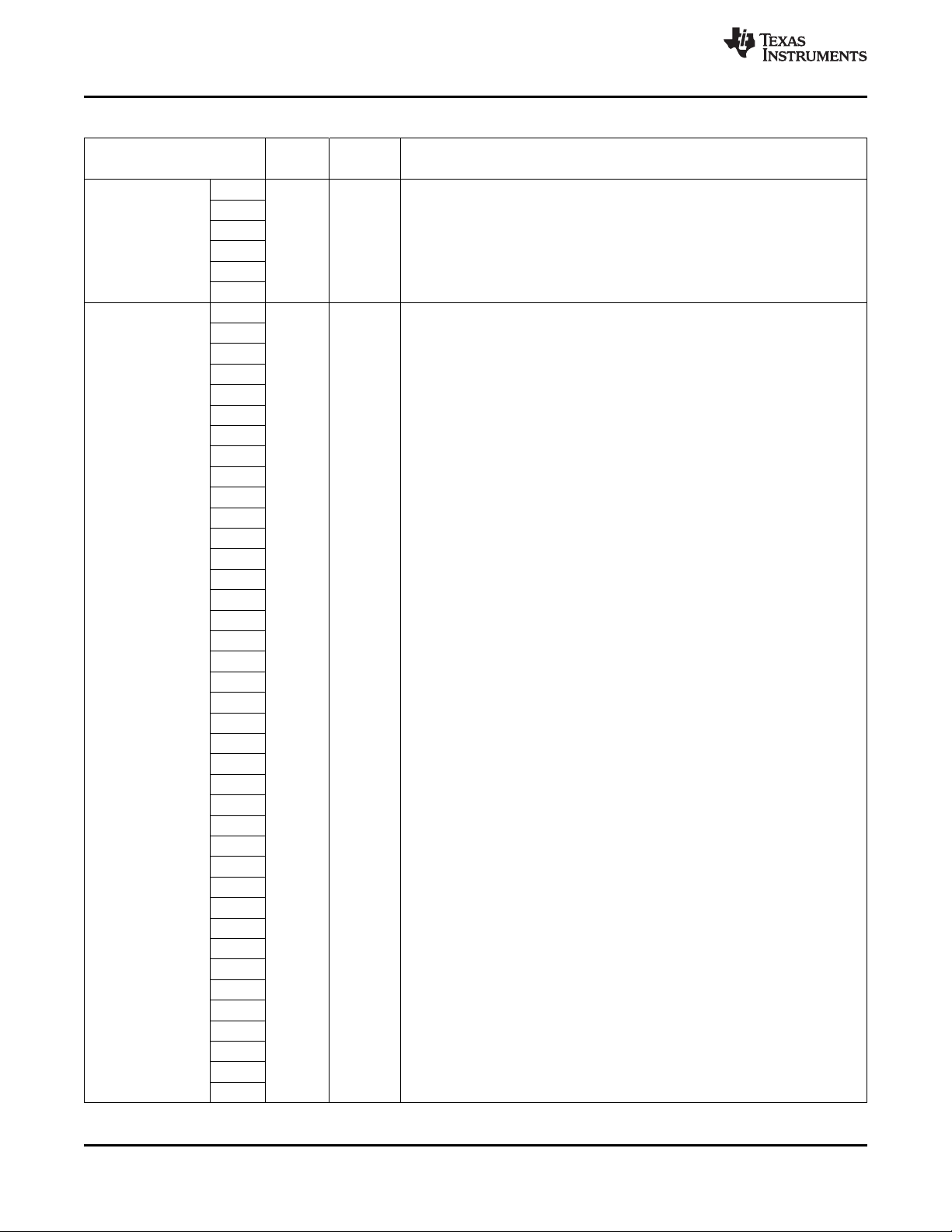

Table 3-2 shows a memory map of the C64x+ CPU cache registers for the device.

Table 3-2. C64x+ Cache Registers

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 0000 L2CFG L2 Cache configuration register

0x0184 0020 L1PCFG L1P Size Cache configuration register

0x0184 0024 L1PCC L1P Freeze Mode Cache configuration register

0x0184 0040 L1DCFG L1D Size Cache configuration register

0x0184 0044 L1DCC L1D Freeze Mode Cache configuration register

0x0184 0048 - 0x0184 0FFC - Reserved

0x0184 1000 EDMAWEIGHT L2 EDMA access control register

0x0184 1004 - 0x0184 1FFC - Reserved

0x0184 2000 L2ALLOC0 L2 allocation register 0

0x0184 2004 L2ALLOC1 L2 allocation register 1

0x0184 2008 L2ALLOC2 L2 allocation register 2

0x0184 200C L2ALLOC3 L2 allocation register 3

0x0184 2010 - 0x0184 3FFF - Reserved

0x0184 4000 L2WBAR L2 writeback base address register

0x0184 4004 L2WWC L2 writeback word count register

0x0184 4010 L2WIBAR L2 writeback invalidate base address register

0x0184 4014 L2WIWC L2 writeback invalidate word count register

0x0184 4018 L2IBAR L2 invalidate base address register

18 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 19

TMS320DM6467

www.ti.com

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Table 3-2. C64x+ Cache Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 401C L2IWC L2 invalidate word count register

0x0184 4020 L1PIBAR L1P invalidate base address register

0x0184 4024 L1PIWC L1P invalidate word count register

0x0184 4030 L1DWIBAR L1D writeback invalidate base address register

0x0184 4034 L1DWIWC L1D writeback invalidate word count register

0x0184 4038 - Reserved

0x0184 4040 L1DWBAR L1D Block Writeback

0x0184 4044 L1DWWC L1D Block Writeback

0x0184 4048 L1DIBAR L1D invalidate base address register

0x0184 404C L1DIWC L1D invalidate word count register

0x0184 4050 - 0x0184 4FFF - Reserved

0x0184 5000 L2WB L2 writeback all register

0x0184 5004 L2WBINV L2 writeback invalidate all register

0x0184 5008 L2INV L2 Global Invalidate without writeback

0x0184 500C - 0x0184 5027 - Reserved

0x0184 5028 L1PINV L1P Global Invalidate

0x0184 502C - 0x0184 5039 - Reserved

0x0184 5040 L1DWB L1D Global Writeback

0x0184 5044 L1DWBINV L1D Global Writeback with Invalidate

0x0184 5048 L1DINV L1D Global Invalidate without writeback

0x0184 8000 - 0x0184 803C MAR0 - MAR15 Reserved (corresponds to byte address 0x0000 0000 - 0x0FFF FFFF)

0x0184 8040 MAR16

0x0184 8044 - 0x0184 80FC MAR17 - MAR63 Reserved (corresponds to byte address 0x1100 0000 - 0x3FFF FFFF)

0x0184 8100 MAR64 Reserved (corresponds to byte address 0x4000 0000 - 0x40FF FFFF)

0x0184 8104 MAR65 Reserved (corresponds to byte address 0x4100 0000 - 0x41FF FFFF)

0x0184 8108 - 0x0184 8124 MAR66 - MAR73

0x0184 8128 - 0x0184 812C MAR74 - MAR75 Reserved (corresponds to byte address 0x4A00 0000 - 0x4BFF FFFF)

0x0184 8130 - 0x0184 813C MAR76 - MAR79

0x0184 8140 - 0x0184 81FC MAR80 - MAR127 Reserved (corresponds to byte address 0x5000 0000 - 0x7FFF FFFF)

0x0184 8200 - 0x0184 82FC MAR128 - MAR191

0x0184 8300 - 0x0184 83FC MAR192 - MAR255 Reserved (corresponds to byte address 0xC000 0000 - 0xFFFF FFFF)

Memory Attribute Registers for ARM TCM (corresponds to byte address

0x1000 0000 - 0x10FF FFFF)

Memory Attribute Registers for EMIFA (corresponds to byte address 0x4200

0000 - 0x49FF FFFF)

Memory Attribute Registers for VLYNQ (corresponds to byte address

0x4C00 0000 - 0x4FFF FFFF)

Memory Attribute Registers for DDR2 (corresponds to byte address 0x8000

0000 - 0xBFFF FFFF)

3.4.3 Peripherals

The DSP has access/controllability of the following peripherals:

• HDVICP0/1

• EDMA

• McASP0/1

• 2 Timers (Timer0 and Timer1) that can each be configured as 1 64-bit or 2 32-bit timers

3.4.4 DSP Interrupt Controller

The DSP Interrupt Controller accepts device interrupts and appropriately maps them to the DSP’s

available interrupts. The DSP Interrupt Controller is briefly described in this document in the Interrupts

section. For more detailed on the DSP Interrupt Controller, see the TMS320C64x+ DSP Megamodule

Reference Guide (literature number SPRU871).

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 19

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 20

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

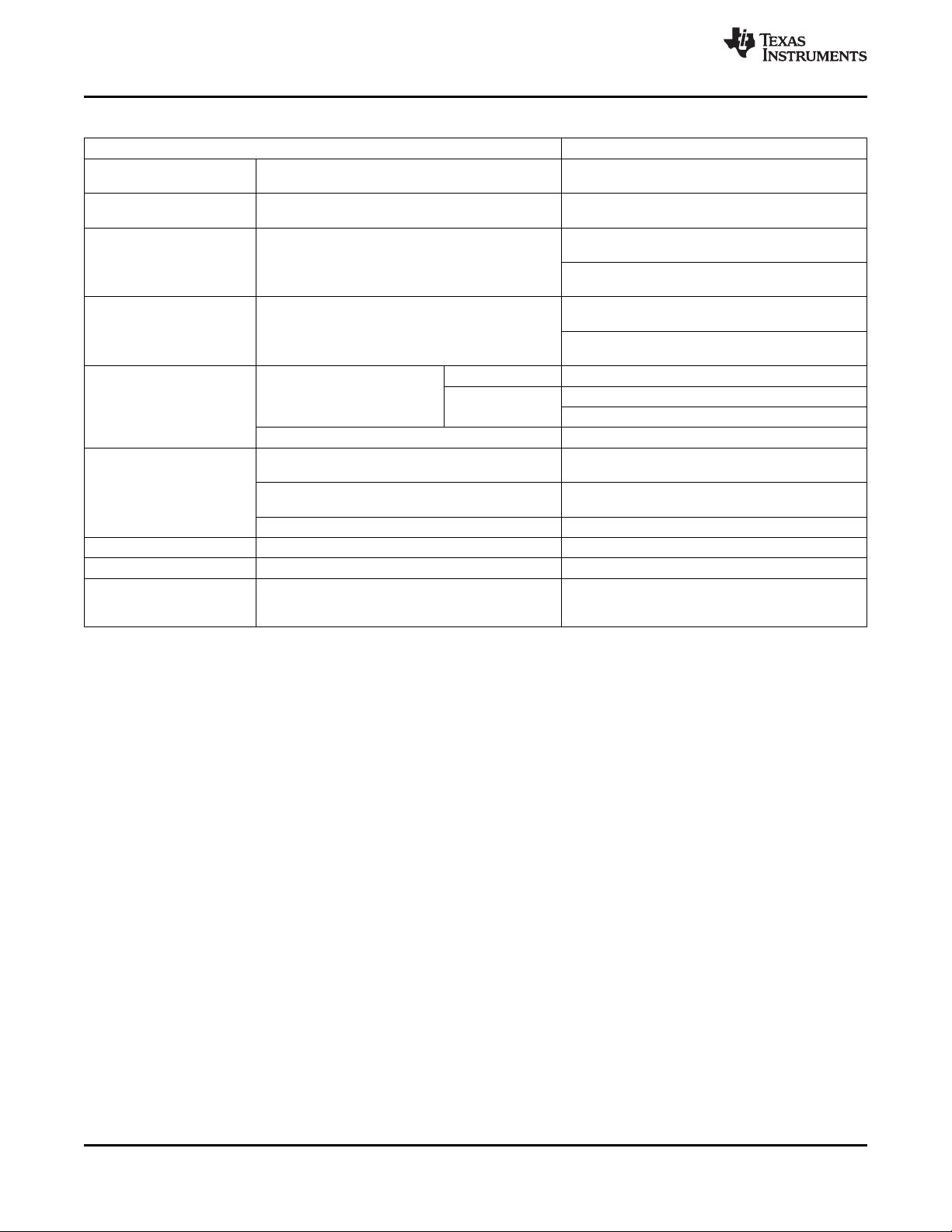

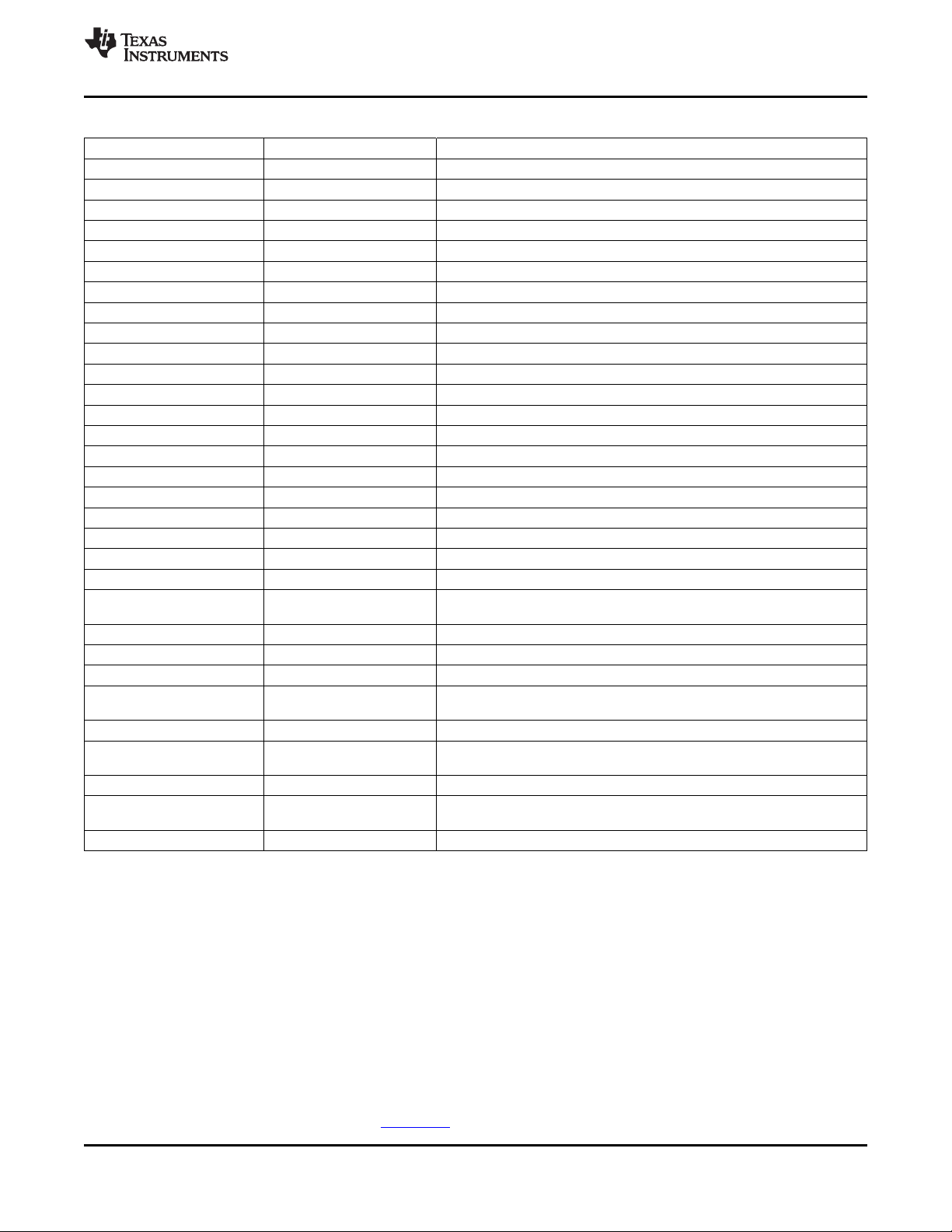

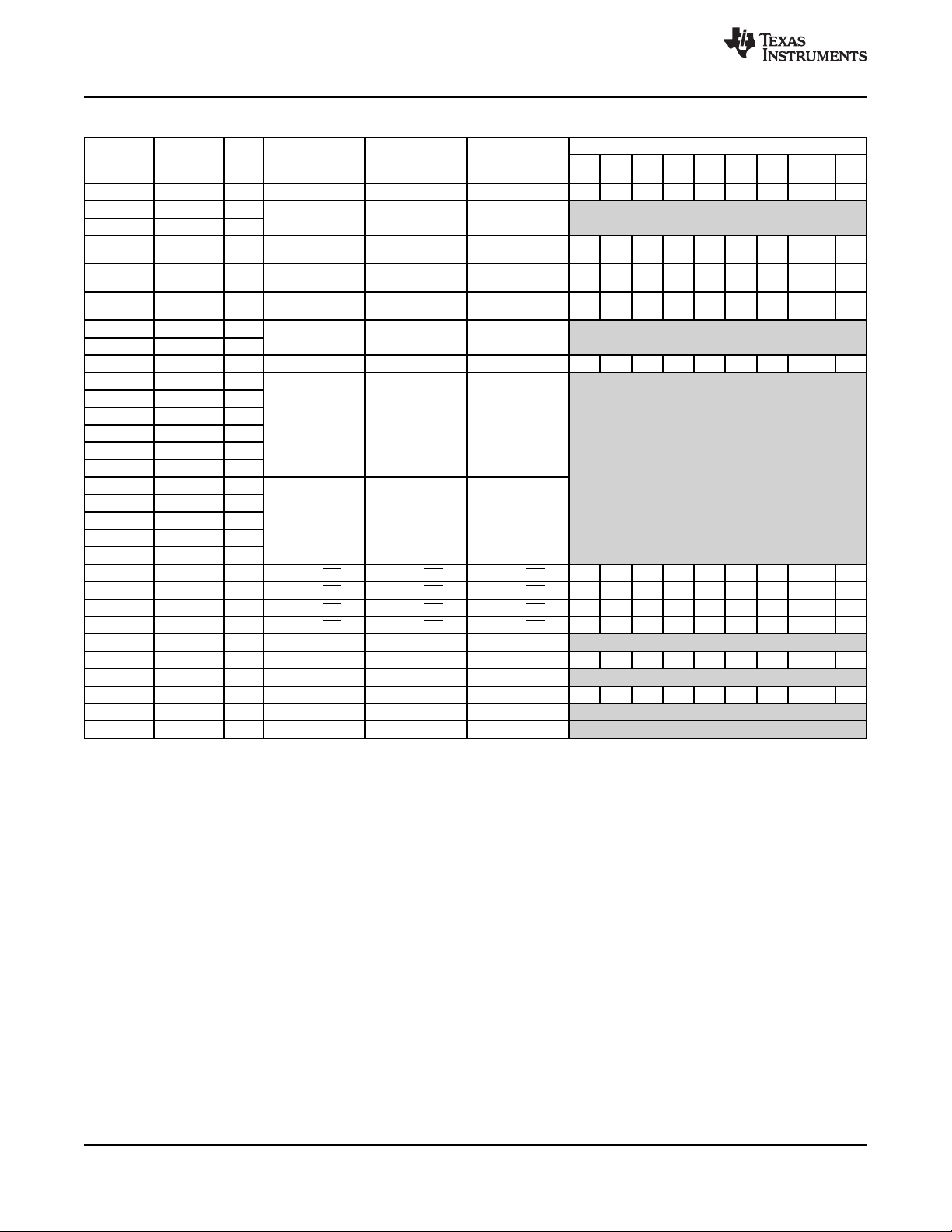

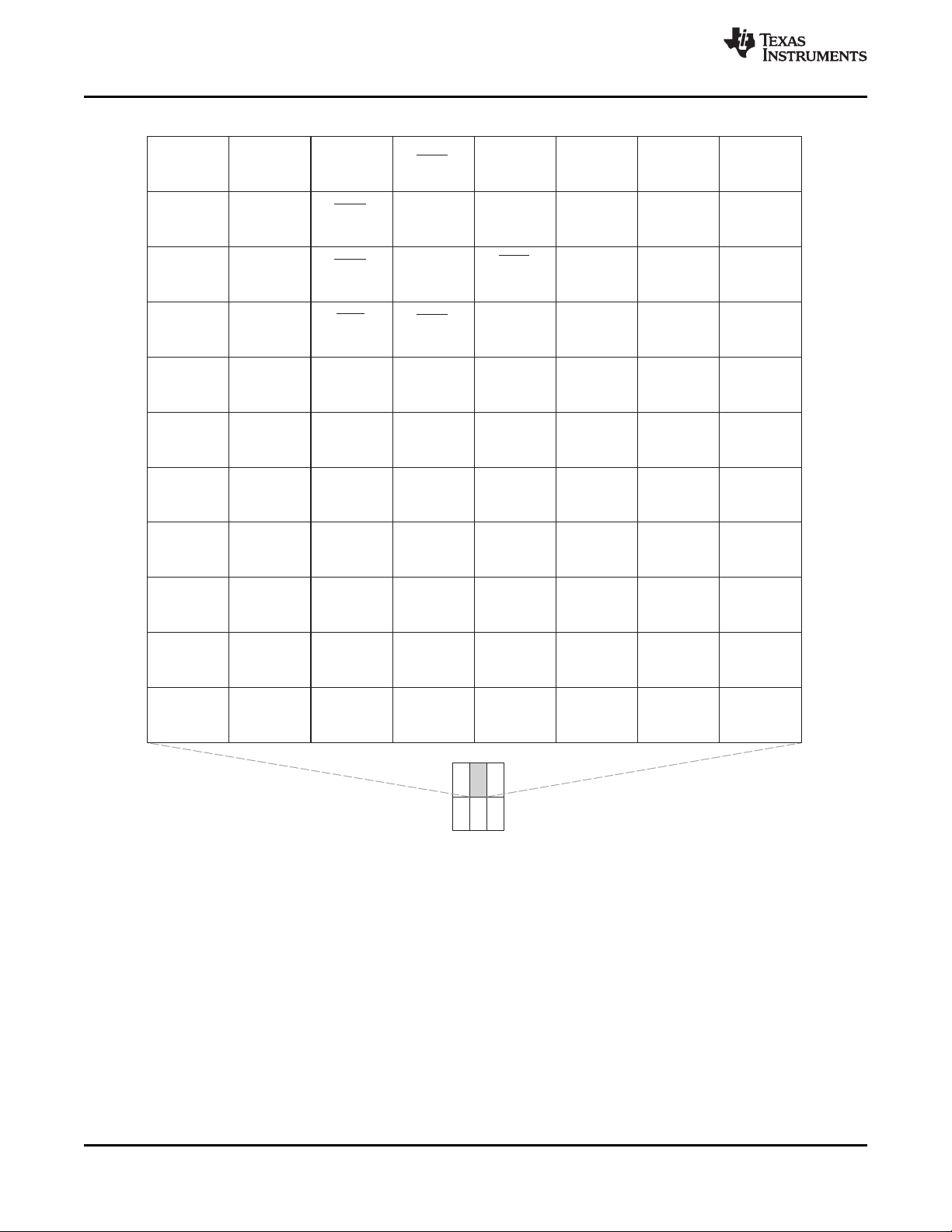

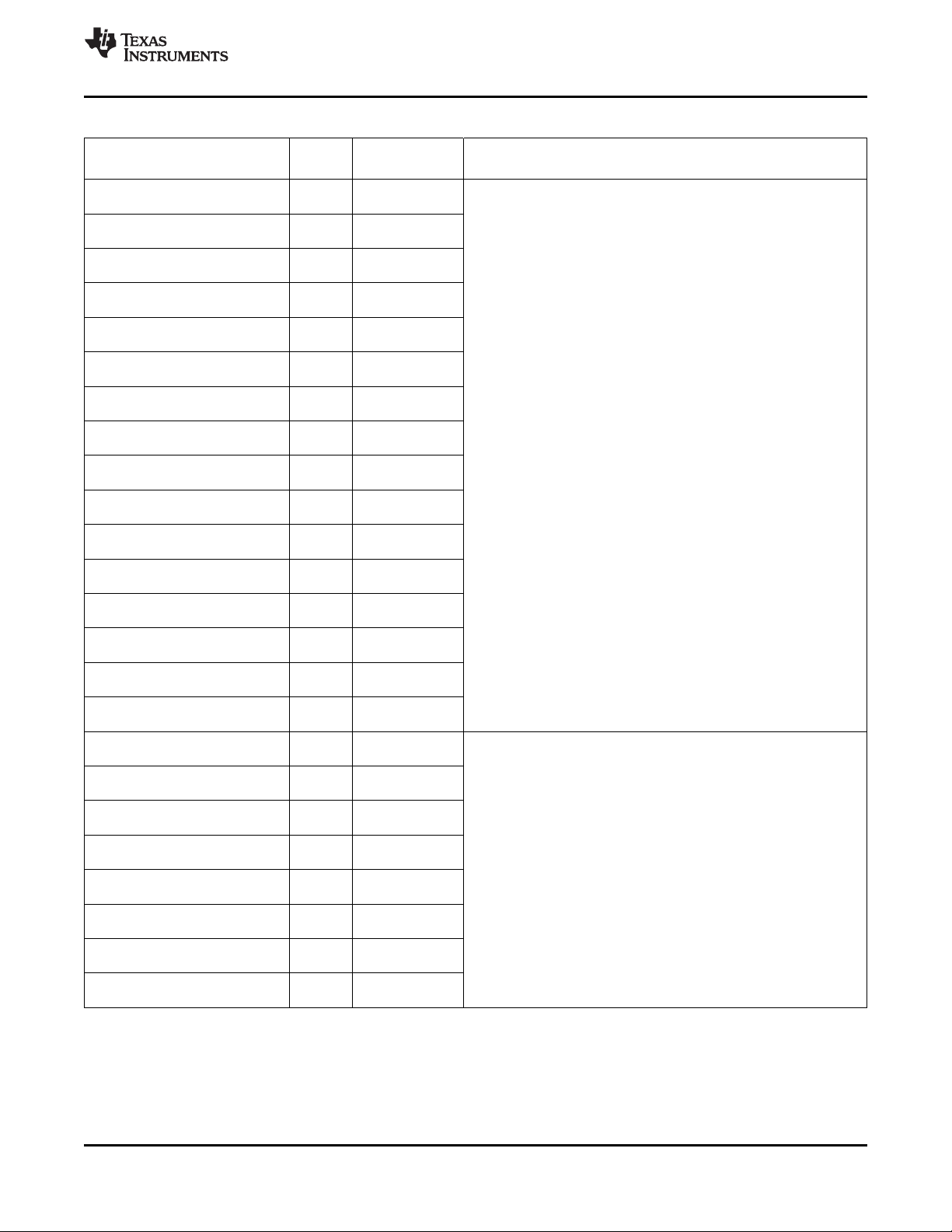

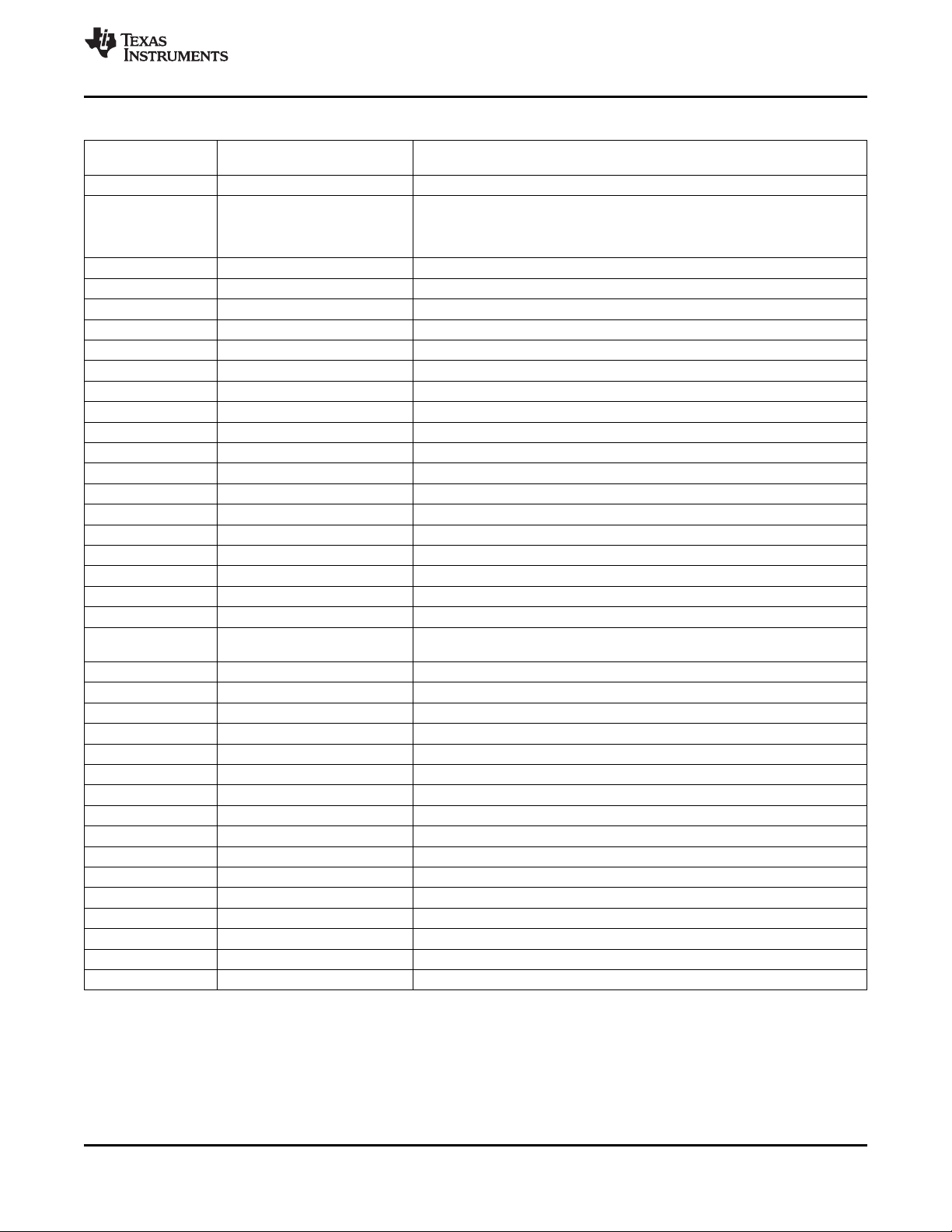

3.5 Memory Map Summary

Table 3-3 shows the memory map address ranges of the device. Table 3-4 depicts the expanded map of

the Configuration Space (0x0180 0000 through 0x0FFF FFFF). The device has multiple on-chip memories

associated with its two processors and various subsystems. To help simplify software development a

unified memory map is used where possible to maintain a consistent view of device resources across all

bus masters.

www.ti.com

20 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 21

TMS320DM6467

www.ti.com

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Table 3-3. Memory Map Summary

START END SIZE EDMA/

ADDRESS ADDRESS (Bytes) PERIPHERAL

0x0000 0000 0x0000 3FFF 16K ARM RAM0

0x0000 4000 0x0000 7FFF 16K ARM RAM1

0x0000 8000 0x0000 FFFF 32K ARM ROM (Instruction)

0x0001 0000 0x0001 3FFF 16K ARM RAM0 (Data)

0x0001 4000 0x0001 7FFF 16K ARM RAM1 (Data)

0x0001 8000 0x0001 FFFF 32K ARM ROM (Data)

0x0002 0000 0x000F FFFF 896K

0x0010 0000 0x003F FFFF 3M

0x0040 0000 0x004F FFFF 1M

0x0050 0000 0x005F FFFF 1M Reserved

0x0060 0000 0x006F FFFF 1M

0x0070 0000 0x007F FFFF 1M

0x0080 0000 0x0080 FFFF 64K

0x0081 0000 0x0081 7FFF 32K Reserved Hole (MPPA Disable)

0x0081 8000 0x0083 7FFF 128K L2 RAM/Cache

0x0083 8000 0x008F FFFF 800K Reserved

0x0090 0000 0x0092 FFFF 192K

0x0093 0000 0x009F FFFF 832K

0x00A0 0000 0x00DF FFFF 4M

0x00E0 0000 0x00E0 7FFF 32K L1P RAM/Cache

0x00E0 8000 0x00EF FFFF 992K Reserved

0x00F0 0000 0x00F0 7FFF 32K L1D RAM/Cache Reserved

0x00F0 8000 0x017F FFFF 9184K Reserved

0x0180 0000 0x01BB FFFF 3840K

0x01BC 0000 0x01BC 0FFF 4K ARM ETB Memory

0x01BC 1000 0x01BC 17FF 2K ARM ETB Registers

0x01BC 1800 0x01BC 18FF 256 ARM IceCrusher

0x01BC 1900 0x01BC 1BFF 768 Reserved

0x01BC 1C00 0x01BF FFFF 249K

0x01C0 0000 0x0FFF FFFF 228M CFG Bus Peripherals CFG Bus Peripherals CFG Bus Peripherals ✓

0x1000 0000 0x1000 FFFF 64K Reserved

0x1001 0000 0x1001 3FFF 16K ARM RAM0 (Data) ARM RAM0 (Data) ✓ ✓ ✓ ✓ ✓ ✓ ✓

0x1001 4000 0x1001 7FFF 16K ARM RAM1 (Data) ARM RAM1 (Data) ✓ ✓ ✓ ✓ ✓ ✓ ✓

0x1001 8000 0x1001 FFFF 32K ARM ROM (Data) ARM ROM (Data) ✓ ✓ ✓ ✓ ✓ ✓ ✓

0x1002 0000 0x10FF FFFF 16256K

0x1100 0000 0x113F FFFF 4M Reserved

0x1140 0000 0x114F FFFF 1M

0x1150 0000 0x115F FFFF 1M Reserved Reserved

0x1160 0000 0x116F FFFF 1M

0x1170 0000 0x117F FFFF 1M

0x1180 0000 0x1180 FFFF 64K

0x1181 0000 0x1181 7FFF 32K Reserved Hole (MPPA Disable)

0x1181 8000 0x1183 7FFF 128K L2 RAM/Cache L2 RAM/Cache L2 RAM/Cache ✓ ✓ ✓ ✓ ✓ ✓

0x1183 8000 0x118F FFFF 800K Reserved Reserved Reserved

0x1190 0000 0x11DF FFFF 5M

0x11E0 0000 0x11E0 7FFF 32K L1P RAM/Cache L1P RAM/Cache L1P RAM/Cache ✓ ✓ ✓ ✓ ✓

0x11E0 8000 0x11EF FFFF 992K Reserved Reserved Reserved

ARM C64x+

(Instruction)

(Instruction)

Reserved

Reserved Reserved

(2)

Reserved

CFG Space

(2)

Reserved

Video TSIF

Port (0/1)

MASTER PERIPHERAL ACCESSIBILITY

VDCE EMAC HPI PCI USB VLYNQ ATA

(3)✓(3)

(1)

(3)

✓

(1) These peripherals have their own DMA engine or master port interface to the DMSoC system bus and do not use the EDMA for data

transfers. The ✓ symbol indicates that the peripheral has a valid connection through the device switch fabric to the memory region

identified in the EDMA access column.

(2) MPPA should be used to disable the hole. For more information on MPPA, see the TMS320C64x+ DSP Megamodule Reference Guide

(SPRU871).

(3) The HPI's, PCI's, and VLYNQ's access to the configuration bus peripherals is limited, see Table 3-4, Configuration Memory Map

Summary for the details.

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 21

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 22

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

www.ti.com

Table 3-3. Memory Map Summary (continued)

START END SIZE EDMA/

ADDRESS ADDRESS (Bytes) PERIPHERAL

ARM C64x+

Video TSIF

Port (0/1)

MASTER PERIPHERAL ACCESSIBILITY

VDCE EMAC HPI PCI USB VLYNQ ATA

0x11F0 0000 0x11F0 7FFF 32K L1D RAM/Cache L1D RAM/Cache L1D RAM/Cache ✓ ✓ ✓ ✓ ✓

0x11F0 8000 0x11FF FFFF 992K Reserved Reserved Reserved

0x1200 0000 0x1FFF FFFF 224M

0x2000 0000 0x2000 7FFF 32K DDR2 Control DDR2 Control DDR2 Control

0x2000 8000 0x2000 FFFF 32K EMIFA Control EMIFA Registers EMIFARegisters

0x2001 0000 0x2001 7FFF 32K VLYNQ Control VLYNQ Registers VLYNQ Registers

Registers Registers Registers

Registers

Registers

✓

0x2001 8000 0x200F FFFF 928K Reserved Reserved Reserved

0x2010 0000 0x2FFF FFFF 255M

0x3000 0000 0x3FFF FFFF 256M PCI Data PCI Data

0x4000 0000 0x403F FFFF 4M Reserved Reserved Reserved

0x4040 0000 0x4043 FFFF 256K

0x4044 0000 0x4047 FFFF 256K

0x4048 0000 0x404B FFFF 256K

0x404C 0000 0x404F FFFF 256K

0x4050 0000 0x405F FFFF 1M

0x4060 0000 0x4063 FFFF 256K Reserved Reserved Reserved

0x4064 0000 0x4067 FFFF 256K

0x4068 0000 0x406B FFFF 256K

0x406C 0000 0x406F FFFF 256K

0x4070 0000 0x41FF FFFF 25M

0x4200 0000 0x43FF FFFF 32M EMIFA Data (CS2)

0x4400 0000 0x45FF FFFF 32M EMIFA Data (CS3)

0x4600 0000 0x47FF FFFF 32M EMIFA Data (CS4)

0x4800 0000 0x49FF FFFF 32M EMIFA Data (CS5)

(4)

EMIFA Data (CS2)

(4)

EMIFA Data (CS3)

(4)

EMIFA Data (CS4)

(4)

EMIFA Data (CS5)

(4)

EMIFA Data (CS2)

(4)

EMIFA Data (CS3)

(4)

EMIFA Data (CS4)

(4)

EMIFA Data (CS5)

(4)

(4)

(4)

(4)

✓ ✓ ✓ ✓

✓ ✓ ✓ ✓

✓ ✓ ✓ ✓

✓ ✓ ✓ ✓

0x4A00 0000 0x4BFF FFFF 32M Reserved Reserved Reserved

0x4C00 0000 0x4FFF FFFF 64M VLYNQ (Remote Data) VLYNQ (Remote Data) VLYNQ (RemoteData) ✓ ✓ ✓ ✓ ✓ ✓ ✓

0x5000 0000 0x7FFF FFFF 768M Reserved Reserved Reserved

0x8000 0000 0x9FFF FFFF 512M DDR2 Memory DDR2 Memory DDR2 Memory ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓ ✓

0xA000 0000 0xBFFF FFFF 512M Reserved Reserved Reserved

0xC000 0000 0xFFFF FFFF 1G Reserved Reserved Reserved

(4) EMIFA CS0 and CS1 are not functionally supported on the DM6467, and therefore, are not pinned out.

(1)

22 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 23

TMS320DM6467

www.ti.com

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

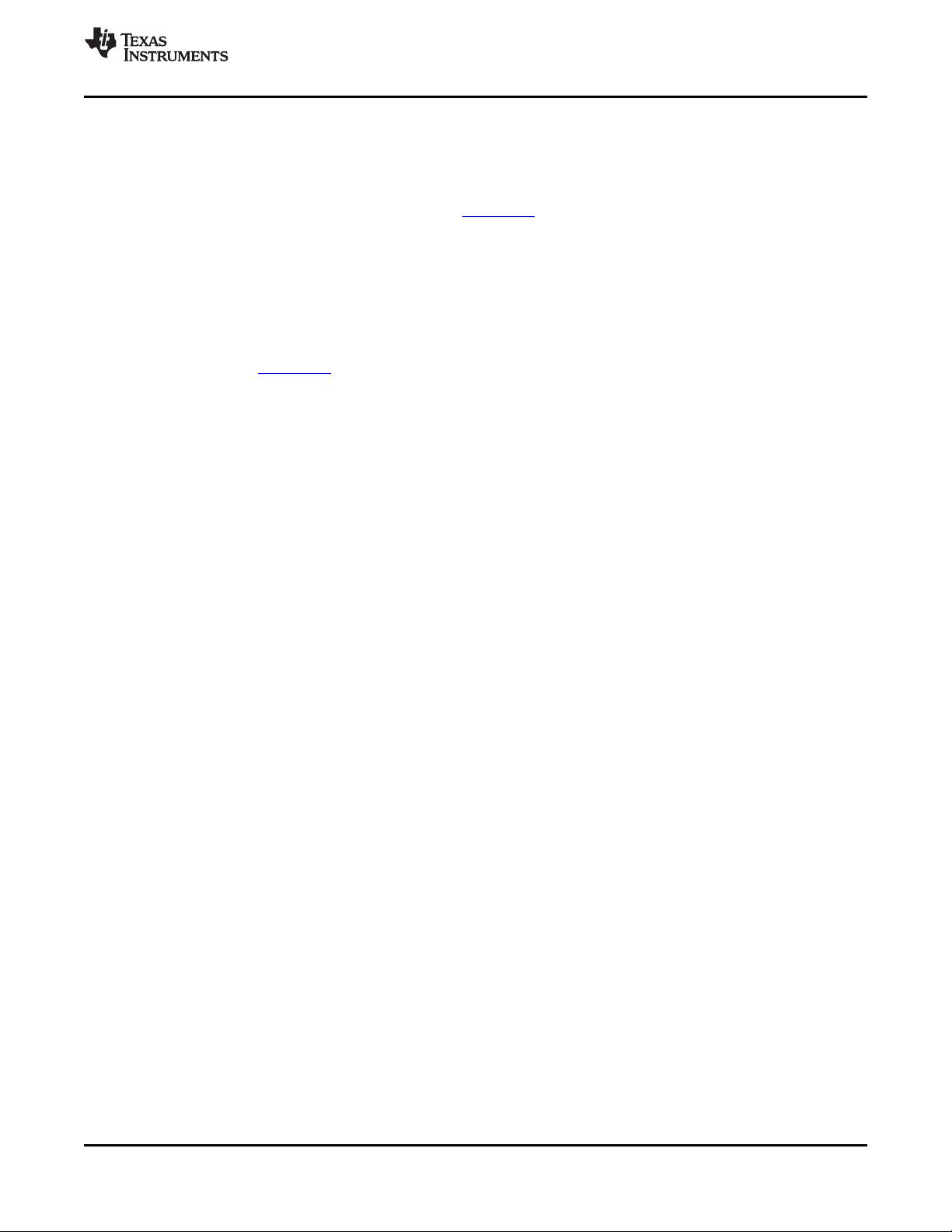

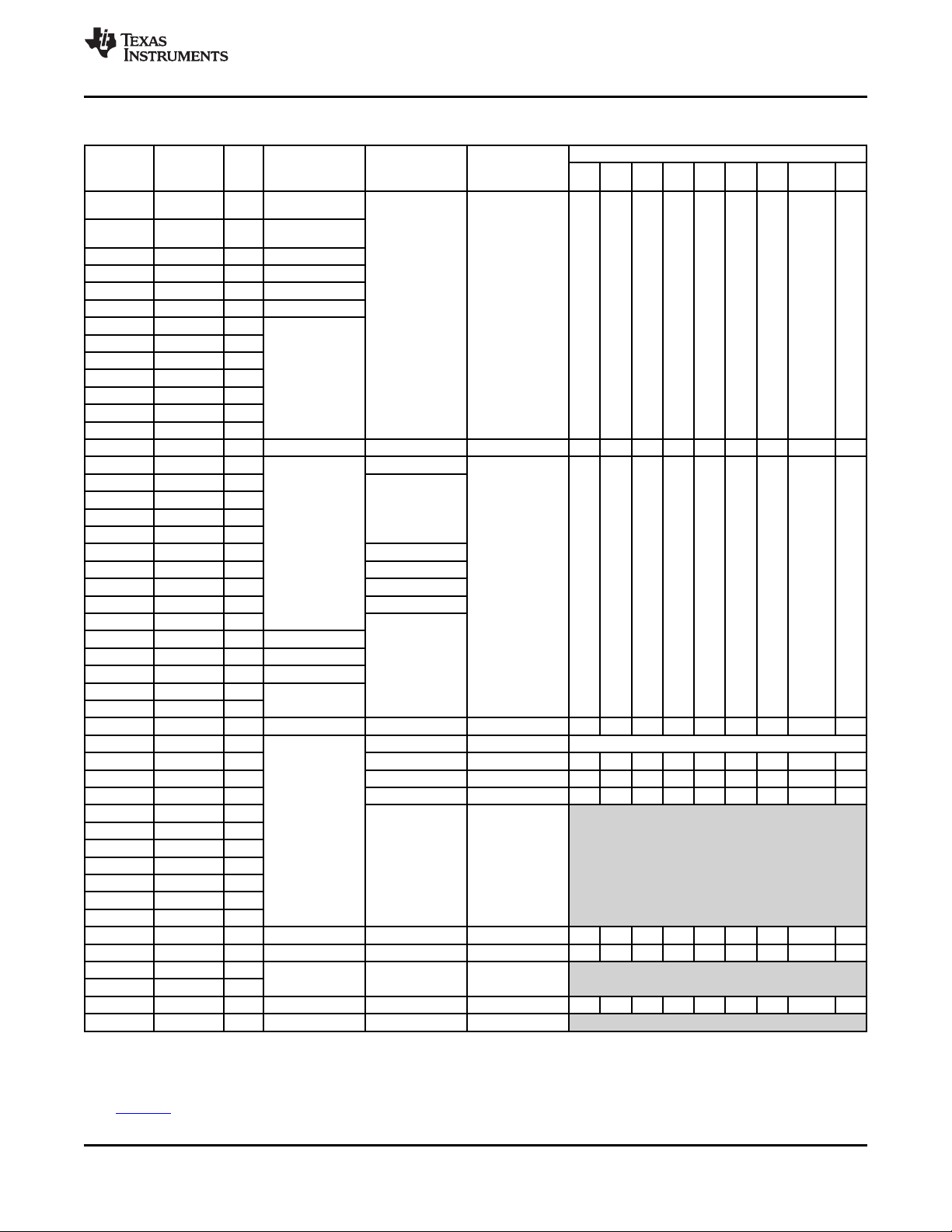

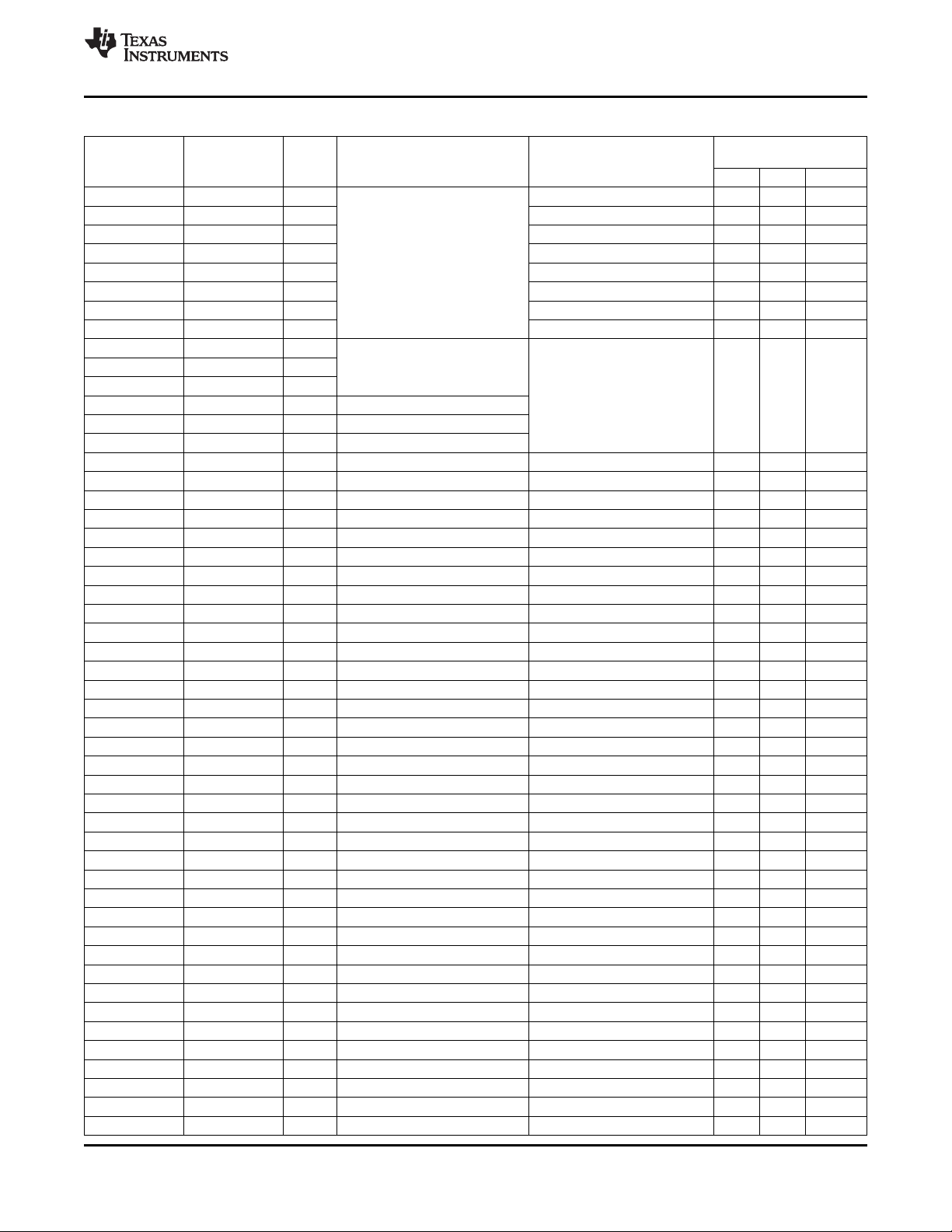

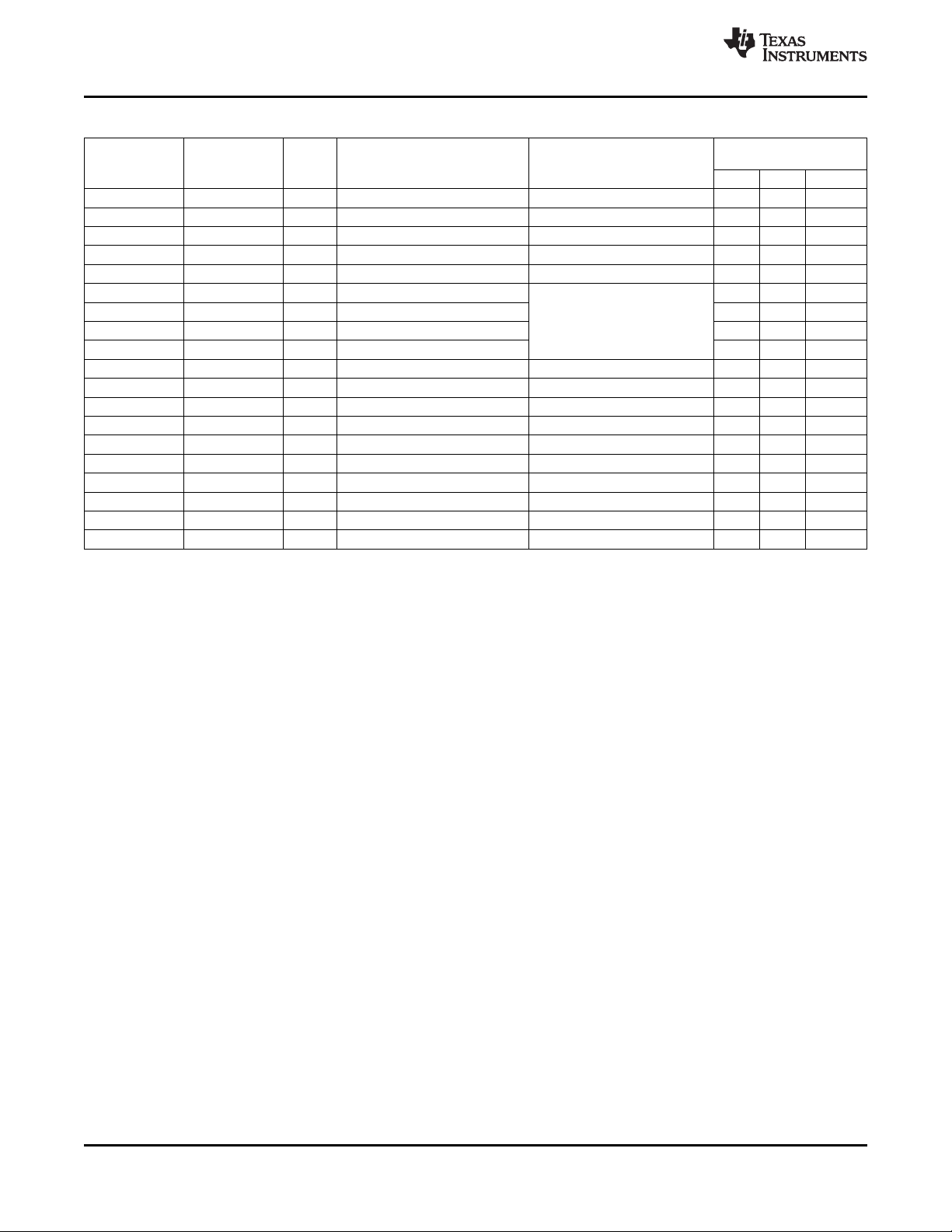

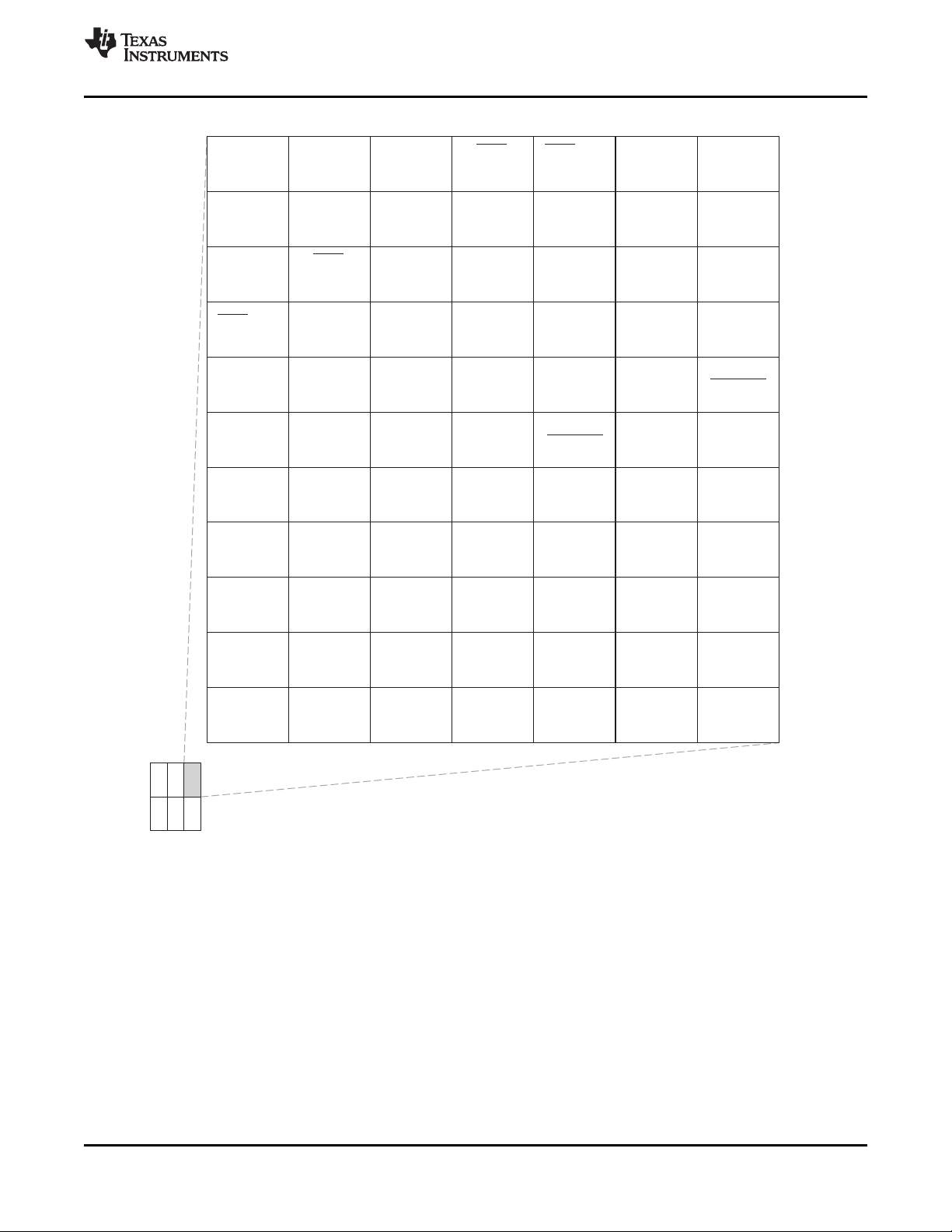

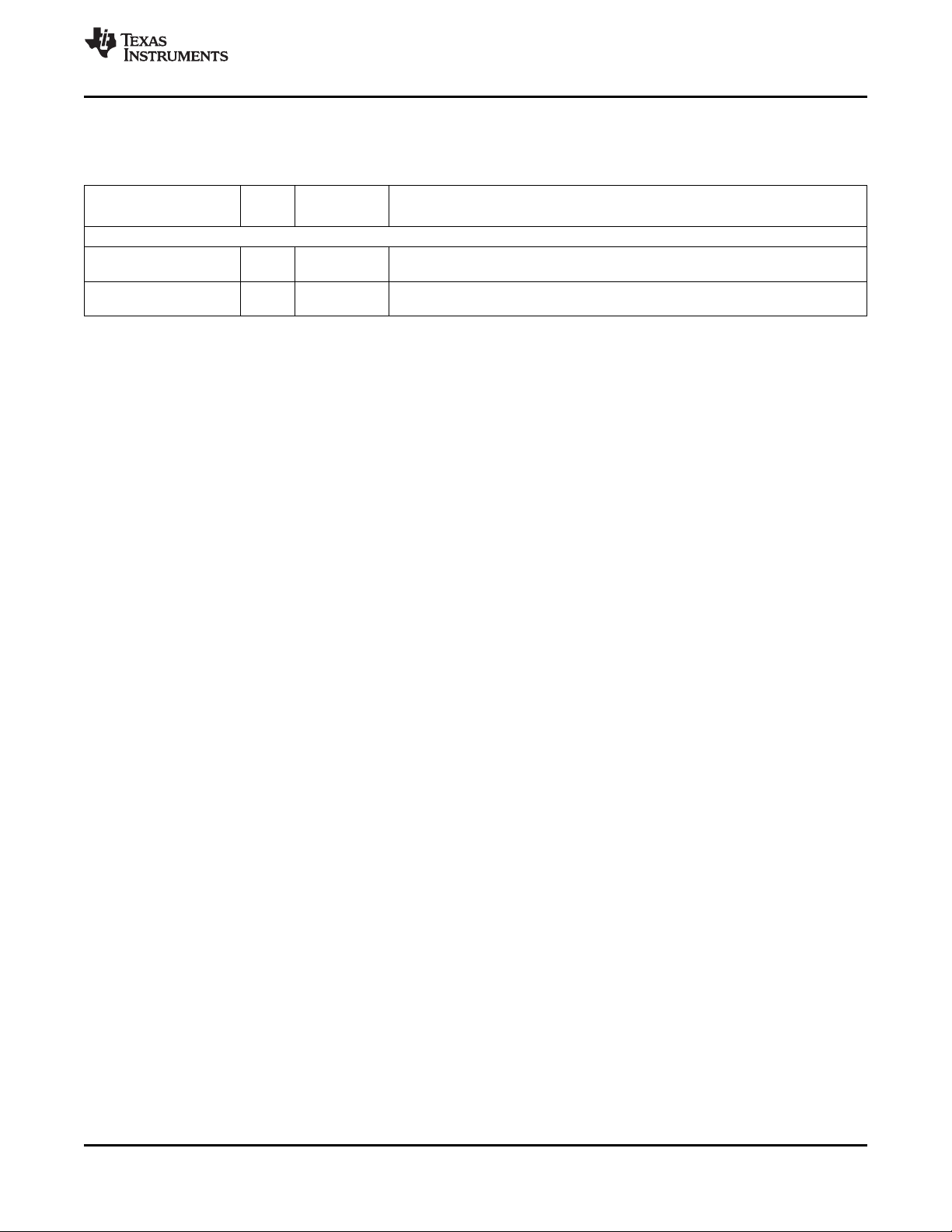

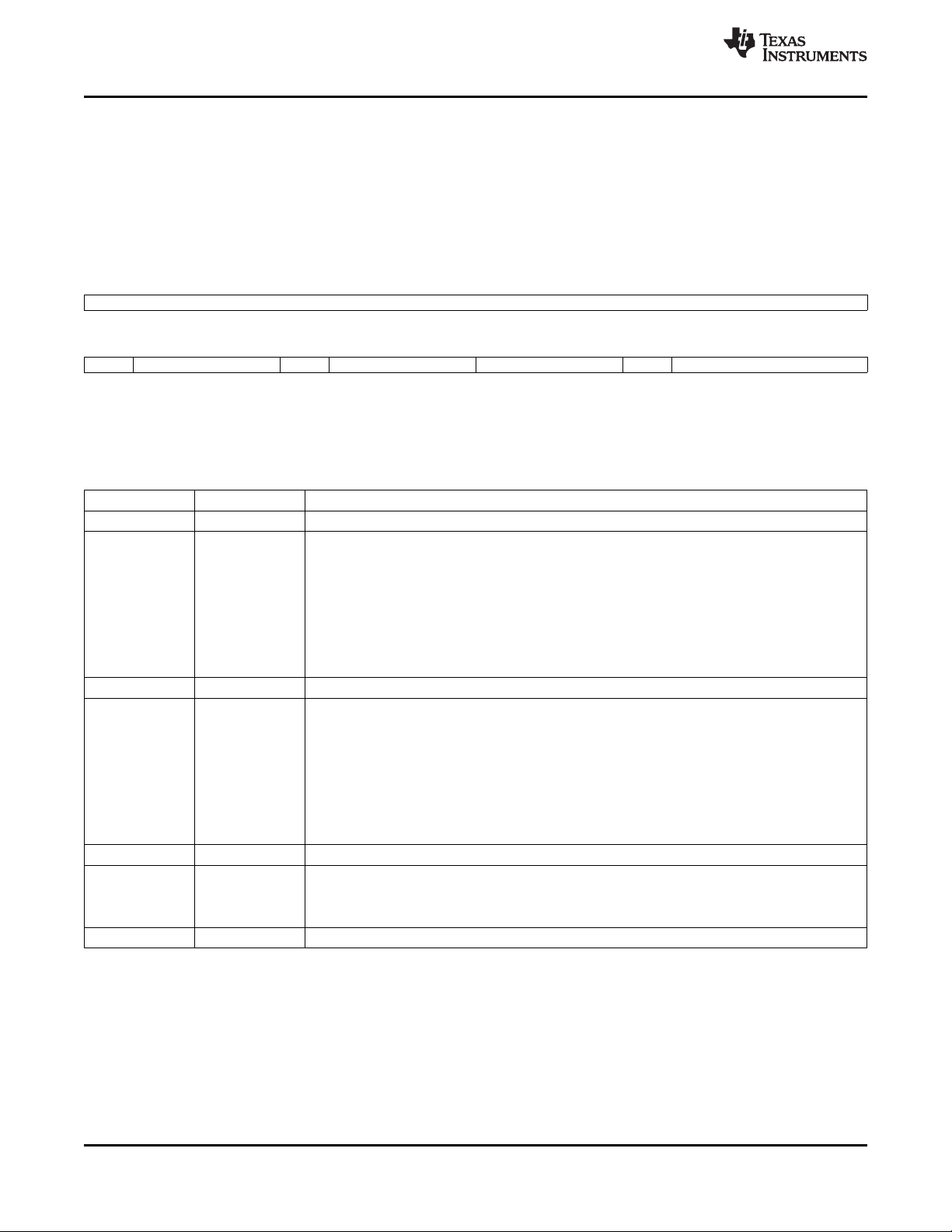

Table 3-4. Configuration Memory Map Summary

START END SIZE

ADDRESS ADDRESS (Bytes)

0x0180 0000 0x0180 FFFF 64K C64x+ Interrupt Controller

0x0181 0000 0x0181 0FFF 4K C64x+ Powerdown Controller

0x0181 1000 0x0181 1FFF 4K C64x+ Security ID

0x0181 2000 0x0181 2FFF 4K C64x+ Revision ID

0x0182 0000 0x0182 FFFF 64K C64x+ EMC

0x0183 0000 0x0183 FFFF 64K Reserved

0x0184 0000 0x0184 FFFF 64K C64x+ Memory System

0x0185 0000 0x01BB FFFF 3520K Reserved

0x01BC 0000 0x01BC 00FF 256

0x01BC 0100 0x01BC 01FF 256 ARM ETB Memory

0x01BC 0200 0x01BC 0FFF 3.5K

0x01BC 1000 0x01BC 17FF 2K ARM ETB Registers

0x01BC 1800 0x01BC 18FF 256 ARM Ice Crusher

0x01BC 1900 0x01BF FFFF 255744 Reserved

0x01C0 0000 0x01C0 FFFF 64K EDMA CC EDMA CC

0x01C1 0000 0x01C1 03FF 1K EDMA TC0 EDMA TC0

0x01C1 0400 0x01C1 07FF 1K EDMA TC1 EDMA TC1

0x01C1 0800 0x01C1 0BFF 1K EDMA TC2 EDMA TC2

0x01C1 0C00 0x01C1 0FFF 1K EDMA TC3 EDMA TC3

0x01C1 1000 0x01C1 1FFF 4K Reserved Reserved

0x01C1 2000 0x01C1 23FF 1K Video Port

0x01C1 2400 0x01C1 27FF 1K Reserved Reserved

0x01C1 2800 0x01C1 2FFF 2K VDCE

0x01C1 3000 0x01C1 33FF 1K TSIF0

0x01C1 3400 0x01C1 37FF 1K TSIF1

0x01C1 3800 0x01C1 9FFF 26K Reserved Reserved

0x01C1 A000 0x01C1 A7FF 2K PCI Control Registers

0x01C1 A800 0x01C1 FFFF 22K Reserved Reserved

0x01C2 0000 0x01C2 03FF 1K UART0 ✓ ✓ ✓

0x01C2 0400 0x01C2 07FF 1K UART1 ✓ ✓ ✓

0x01C2 0800 0x01C2 0BFF 1K UART2 ✓ ✓ ✓

0x01C2 0C00 0x01C2 0FFF 1K Reserved Reserved ✓ ✓ ✓

0x01C2 1000 0x01C2 13FF 1K I2C ✓ ✓ ✓

0x01C2 1400 0x01C2 17FF 1K Timer0 Timer0 ✓ ✓ ✓

0x01C2 1800 0x01C2 1BFF 1K Timer1 Timer1 ✓ ✓ ✓

0x01C2 1C00 0x01C2 1FFF 1K Timer2 (Watchdog) ✓ ✓ ✓

0x01C2 2000 0x01C2 23FF 1K PWM0 ✓ ✓ ✓

0x01C2 2400 0x01C2 27FF 1K PWM1 ✓ ✓ ✓

0x01C2 2800 0x01C2 5FFF 14K Reserved Reserved ✓ ✓ ✓

0x01C2 6000 0x01C2 63FF 1K CRGEN0 ✓ ✓ ✓

0x01C2 6400 0x01C2 67FF 1K CRGEN1 ✓ ✓ ✓

0x01C2 6800 0x01C3 FFFF 102K Reserved Reserved ✓ ✓ ✓

0x01C4 0000 0x01C4 07FF 2K System Module System Module ✓ ✓ ✓

0x01C4 0800 0x01C4 0BFF 1K PLL Controller 1 ✓ ✓ ✓

0x01C4 0C00 0x01C4 0FFF 1K PLL Controller 2 ✓ ✓ ✓

0x01C4 1000 0x01C4 1FFF 4K Power and Sleep Controller Power and Sleep Controller ✓ ✓ ✓

0x01C4 2000 0x01C4 7FFF 24K Reserved Reserved ✓ ✓ ✓

0x01C4 8000 0x01C4 83FF 1K ARM Interrupt Controller Reserved ✓ ✓ ✓

0x01C4 8400 0x01C6 3FFF 111K Reserved Reserved ✓ ✓ ✓

0x01C6 4000 0x01C6 5FFF 8K USB2.0 Registers / RAM ✓ ✓ ✓

Reserved

ARM/EDMA C64x+

Reserved

MASTER PERIPHERAL

ACCESSIBILITY

HPI PCI VLYNQ

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 23

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 24

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Table 3-4. Configuration Memory Map Summary (continued)

START END SIZE

ADDRESS ADDRESS (Bytes)

0x01C6 6000 0x01C6 67FF 2K ATA ✓ ✓ ✓

0x01C6 6800 0x01C6 6FFF 2K SPI ✓ ✓ ✓

0x01C6 7000 0x01C6 77FF 2K GPIO ✓ ✓ ✓

0x01C6 7800 0x01C6 7FFF 2K HPI HPI ✓ ✓ ✓

0x01C6 8000 0x01C7 FFFF 96K Reserved Reserved ✓ ✓ ✓

0x01C8 0000 0x01C8 0FFF 4K EMAC Control Registers ✓ ✓ ✓

0x01C8 1000 0x01C8 1FFF 4K EMAC Control Module Registers ✓ ✓ ✓

0x01C8 2000 0x01C8 3FFF 8K EMAC Control Module RAM ✓ ✓ ✓

0x01C8 4000 0x01C8 47FF 2K MDIO Control Registers ✓ ✓ ✓

0x01C8 4800 0x01D0 0FFF 498K Reserved Reserved ✓ ✓ ✓

0x01D0 1000 0x01D0 13FF 1K McASP0 Registers McASP0 Registers ✓ ✓ ✓

0x01D0 1400 0x01D0 17FF 1K McASP0 Data Port McASP0 Data Port ✓ ✓ ✓

0x01D0 1800 0x01D0 1BFF 1K McASP1 Registers McASP1 Registers ✓ ✓ ✓

0x01D0 1C00 0x01D0 1FFF 1K McASP1 Data Port McASP1 Data Port ✓ ✓ ✓

0x01D0 2000 0x01DF FFFF 1016K Reserved Reserved

0x01E0 0000 0x01FF FFFF 2M Reserved Reserved

0x0200 0000 0x021F FFFF 2M Reserved Reserved

0x0220 0000 0x023F FFFF 2M Reserved Reserved

0x0240 0000 0x0FFF FFFF 220M Reserved Reserved

ARM/EDMA C64x+

Reserved

MASTER PERIPHERAL

ACCESSIBILITY

HPI PCI VLYNQ

www.ti.com

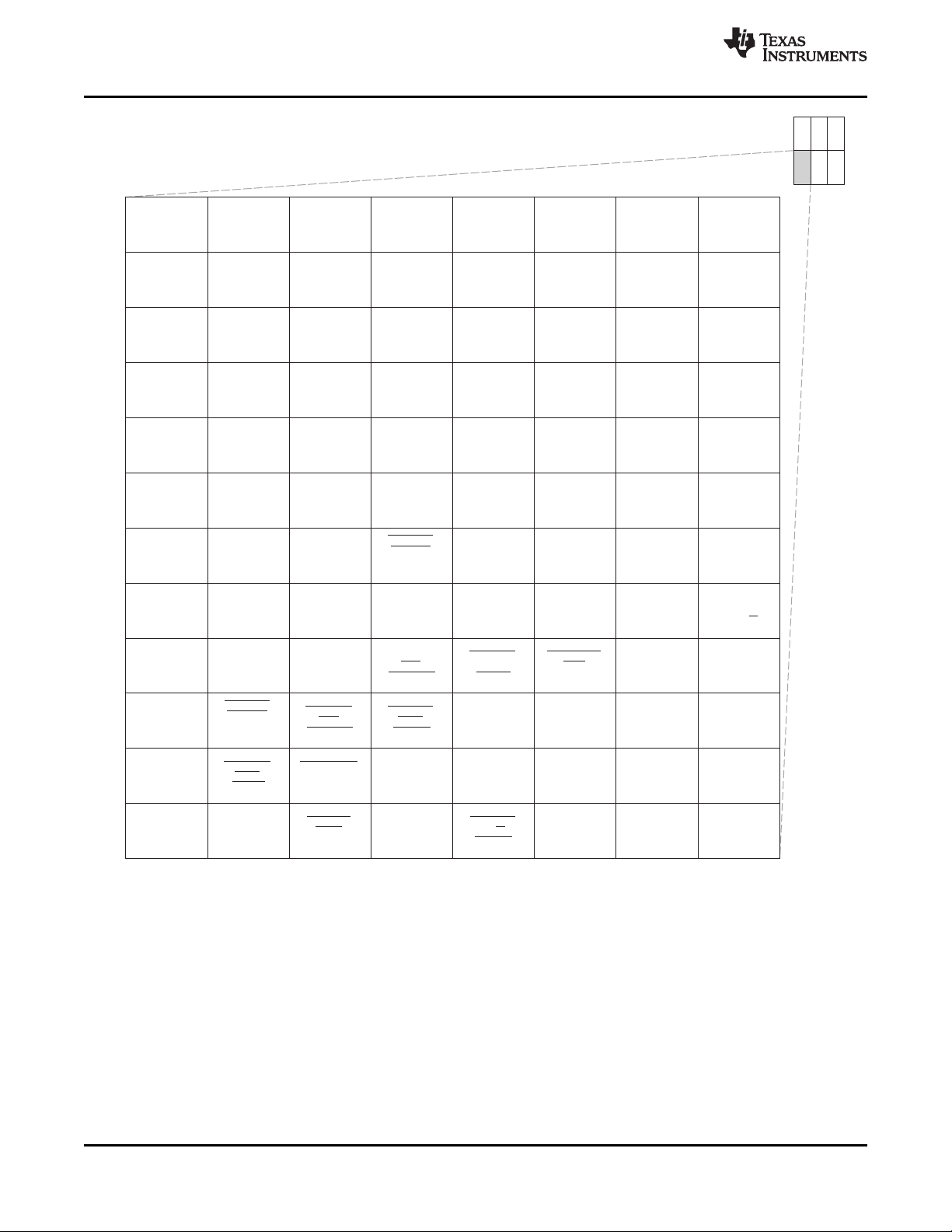

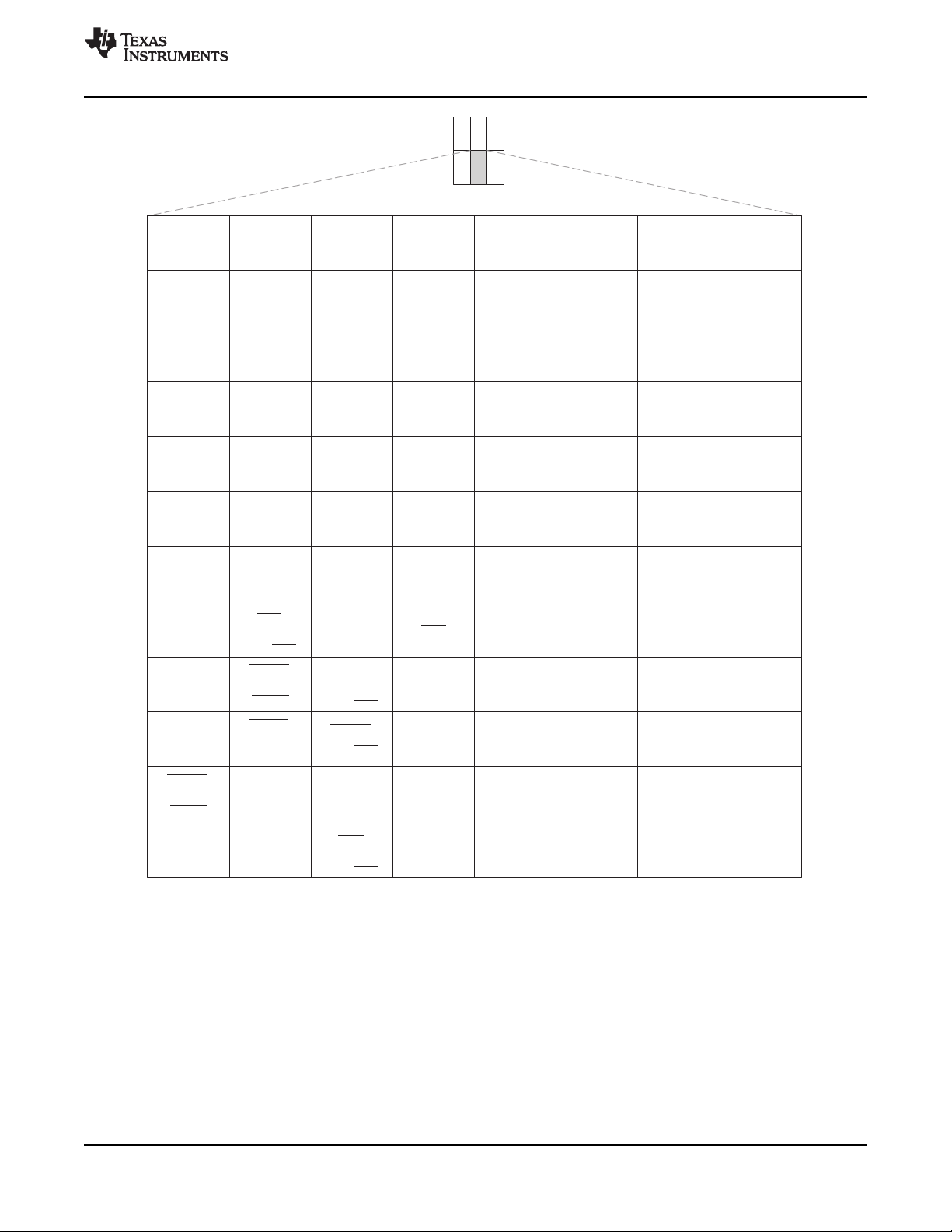

3.6 Pin Assignments

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in

the smallest possible package. Pin multiplexing is controlled using a combination of hardware

configuration at device reset and software programmable register settings. For more information on pin

muxing, see Section 4.7, Multiplexed Pin Configurations, of this document.

3.6.1 Pin Map (Bottom View)

Figure 3-2 through Figure 3-7 show the bottom view of the package pin assignments in six quadrants (A,

B, C, D, E, and F).

24 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 25

V

SS

V

SS

GP[4]/

STC_CLKIN

VP_DOUT1/

BTMODE1

VP_DOUT6/

DSPBOOT

VP_DOUT5/

PCIEN

VP_DOUT14/

TS1_PSTIN

VP_DOUT9/

TS1_ENAO

V

SS

AHCLKR0

GP[3]/

AUDIO_CLK0

TOUT1U

VP_DOUT0/

BTMODE0

VP_DOUT3/

BTMODE3

VP_DOUT7/

VADJEN

VP_DOUT15/

TS1_DIN

ACLKX0 ACLKR0

AMUTEIN0

GP[2]/

AUDIO_CLK1

TOUT1L

TINP0U

VP_DOUT4/

CS2BW

VP_DOUT12/

TS1_WAITO

AHCLKX0

AMUTE0

AFSR0 AFSX0

TOUT2

TINP1L

TINP0L

VP_DOUT2/

BTMODE2

ACLKX1 AHCLKX1

AXR0[3] AXR0[2]

GP[0]

RESET

TOUT0U TOUT0L

SPI_CLK

AXR1[0]

AXR0[0] AXR0[1]

GP[1]

V

SS

DV

DD33

DV

DD33

VLYNQ_

CLOCK

VLYNQ_

SCRUN

SPI_CS1

SDA SCL

DV

DD33

CV

DD

VLYNQ_TXD1 VLYNQ_TXD2 VLYNQ_TXD3

SPI_CS0

SPI_EN

1 2

AC

AB

AA

Y

W

V

U

T

MTCLK

VLYNQ_RXD2 VLYNQ_RXD3 VLYNQ_TXD0 SPI_SOMI

MTXD7 GMTCLK

VLYNQ_RXD1 VLYNQ_RXD0 SPI_SIMO

MTXD3 MTXD4

MTXD5

MTXD6

R

P

N

3 4 5 6 7 8

1 2 3 4 5 6 7 8

AC

AB

AA

Y

W

V

U

T

R

P

N

V

SS

V

SS

DV

DD33

CV

DD

CV

DD

DV

DD33

V

SS

V

SS

CV

DD

CV

DD

V

SS

V

SS

V

SS

V

SS

A B C

D E F

TMS320DM6467

www.ti.com

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Figure 3-2. Pin Map [Section A]

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 25

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 26

A B C

D E F

VP_CLKIN3/

TS1_CLKO

VP_CLKO3/

TS0_CLKO

TS1_CLKIN

UCTS0/

USD0

VP_CLKIN0

VP_DIN4/

TS0_DOUT4/

TS1_WAITO

VP_DIN0/

TS0_DOUT0

VP_DIN8/

TS0_DIN0

VP_DOUT8/

TS1_WAITIN

VP_DOUT11/

TS1_DOUT

UDSR0/

TS0_PSTO/

GP[37]

V

SS

URXD0/

TS1_DIN

VP_DIN5/

TS0_DOUT5/

TS1_EN_WAITO

VP_DIN1/

TS0_DOUT1

VP_DIN9/

TS0_DIN1

VP_CLKO2

VP_DOUT10/

TS1_PSTO

UDCD0/

TS0_WAITIN/

GP[38]

DV

DD33

URTS0/

UIRTX0/

TS1_EN_WAITO

VP_DIN6/

TS0_DOUT6/

TS1_PSTIN

VP_DIN2/

TS0_DOUT2

VP_DIN10/

TS0_DIN2

VP_DOUT13/

TS1_EN_WAITO

VP_CLKIN2

URIN0/

GP[8]/

TS1_WAITIN

UDTR0/

TS0_ENAO/

GP[36]

UTXD0/

URCTX0/

TS1_PSTIN

VP_DIN7/

TS0_DOUT7/

TS1_DIN

VP_DIN3/

TS0_DOUT3

VP_DIN11/

TS0_DIN3

DV

DD33

CV

DD

9 10

AC

AB

AA

Y

W

V

U

T

R

P

N

11 12 13 14 15 16

9 10 11 12 13 14 15 16

AC

AB

AA

Y

W

V

U

T

R

P

N

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DD33

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

V

SS

V

SS

V

SS

V

SS

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

V

SS

CV

DD

CV

DD

CV

DD

V

SS

V

SS

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

V

SS

V

SS

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

CV

DD

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

TMS320DM6467

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

www.ti.com

Figure 3-3. Pin Map [Section B]

26 Device Overview Copyright © 2007–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 27

VP_DIN12/

TS0_DIN4

VP_DIN15_

VP_VSYNC/

TS0_DIN7

TS0_CLKIN

URTS2/

UIRTX2/

TS0_PSTIN/

GP[41]

UCTS2/USD2/

CRG0_VCXI/

GP[42]/

TS1_PSTO

V

SS

VP_DIN13_

FIELD/

TS0_DIN5

VP_CLKIN1

UTXD1/

URCTX1/

TS0_DOUT7/

GP[24]

V

SS

DDR_D[23]

VP_DIN14_

VP_HSYNC/

TS0_DIN6

URTS1/

UIRTX1/

TS0_WAITO/

GP[25]

UTXD2/URCTX2/

CRG1_PO/

GP[40]/

CRG0_PO

DV

DDR2

DDR_D[28] DDR_D[21] DDR_D[20]

UCTS1/USD1/

TS0_EN_WAITO/

GP[26]

URXD1/

TS0_DIN7/

GP[23]

DDR_D[31] DDR_D[29] DDR_D[22]

DDR_DQM[2]

PWM0/

CRG0_PO/

TS1_ENAO

17 18

AC

AB

AA

Y

W

V

U

T

R

P

N

19 20 21 22 23

17 18 19 20 21 22 23

AC

AB

AA

Y

W

V

U

T

R

P

N

A B C

D E F

PWM1/

TS1_DOUT

V

SS

DDR_D[30] DV

DDR2

V

SS

DDR_DQS[2]

DDR_D[19]DDR_DQS[2]DDR_DQS[3]DDR_DQM[3]V

SS

V

SS

DDR_DQS[3] DDR_D[27]DV

DDR2

DDR_D[24]

DDR_D[18]DDR_D[16]V

SS

V

SS

DV

DDR2

V

SS

DV

DDR2

DDR_A[10]DDR_D[17]DDR_D[26]

DDR_D[25]

DV

DDR2

DDR_DQGATE2 DDR_A[1]DDR_A[3]DDR_DQGATE3

DDR_A[12]

DDR_BA[2] DDR_VREFV

SS

DV

DDR2

DDR_A[14]DDR_A[9]DDR_A[5]DDR_A[7]DDR_BA[0]V

SS

V

SS

V

SS

V

SS

DV

DD33

DV

DDR2

V

SS

URXD2/

CRG1_VCXI/

GP[39]/

CRG0_VCXI

V

SS

V

SS

TMS320DM6467

www.ti.com

SPRS403G–DECEMBER 2007–REVISED OCTOBER 2010

Figure 3-4. Pin Map [Section C]

Copyright © 2007–2010, Texas Instruments Incorporated Device Overview 27

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6467

Page 28

MTXD0

MTXEN

MCRS

MCOL

MRCLK MRXD7

MRXD6

V

SS

MRXD4

MRXD3

MRXD2

MRXDV

RFTCLK

MRXD1

MRXER

MDIO

MDCLK

DV

DD33

1 2

L

K

J

H

G

F

E

D

C

B

A

3 4 5 6 7 8

1 2 3 4 5 6 7 8

L

K

J

H

G

F

E

D

C

B

A

A B C

D E F

DV

DD33

PCI_AD0/

HD0/

EM_D0

PCI_AD2/

HD2/

EM_D2

PCI_AD4/

HD4/

EM_D4

V

SS

DV

DD33

CV

DD

V

SS

V

SS

PCI_AD9/

HD9/

EM_D9

PCI_CBE0

ATA_CS0//

GP[33]/

EM_A[18]

PCI_AD6/

HD6/

EM_D6

PCI_AD3/

HD3/

EM_D3

PCI_AD1/

HD1/

EM_D1

PCI_AD13/