Page 1

TMS320DM6443

www.ti.com

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

TMS320DM6443

Digital Media System-on-Chip

Check for Samples: TMS320DM6443

1 Digital Media System-on-Chip (DMSoC)

1.1 Features

12

• High-Performance Digital Media SoC • C64x+ L1/L2 Memory Architecture

– 594-MHz C64x+™ Clock Rate – 32K-Byte L1P Program RAM/Cache (Direct

– 297-MHz ARM926EJ-S™ Clock Rate

– Eight 32-Bit C64x+ Instructions/Cycle

– 4752 C64x+ MIPS

– Fully Software-Compatible With C64x /

ARM9™

• Advanced Very-Long-Instruction-Word (VLIW)

TMS320C64x+™ DSP Core

– Eight Highly Independent Functional Units

• Six ALUs (32-/40-Bit), Each Supports

Single 32-Bit, Dual 16-Bit, or Quad 8-Bit

Arithmetic per Clock Cycle

• Two Multipliers Support Four 16 x 16-Bit

Multiplies (32-Bit Results) per Clock

Cycle or Eight 8 x 8-Bit Multiplies (16-Bit • ARM9 Memory Architecture

Results) per Clock Cycle

– Load-Store Architecture With Non-Aligned

Support

– 64 32-Bit General-Purpose Registers

– Instruction Packing Reduces Code Size

– All Instructions Conditional

– Additional C64x+™ Enhancements

• Protected Mode Operation

• Exceptions Support for Error Detection

and Program Redirection

• Hardware Support for Modulo Loop

Operation

• C64x+ Instruction Set Features

– Byte-Addressable (8-/16-/32-/64-Bit Data)

– 8-Bit Overflow Protection

– Bit-Field Extract, Set, Clear

– Normalization, Saturation, Bit-Counting

– Compact 16-Bit Instructions

– Additional Instructions to Support Complex

Multiplies

Mapped)

– 80K-Byte L1D Data RAM/Cache (2-Way

Set-Associative)

– 64K-Byte L2 Unified Mapped RAM/Cache

(Flexible RAM/Cache Allocation)

• ARM926EJ-S Core

– Support for 32-Bit and 16-Bit (Thumb®

Mode) Instruction Sets

– DSP Instruction Extensions and Single Cycle

MAC

– ARM® Jazelle® Technology

– EmbeddedICE-RT™ Logic for Real-Time

Debug

– 16K-Byte Instruction Cache

– 8K-Byte Data Cache

– 16K-Byte RAM

– 8K-Byte ROM

• Emulation Trace Buffer™ (ETB11™) With 4-KB

Memory for ARM9 Debug

• Endianness: Little Endian for ARM and DSP

• Video Processing Subsystem

– Resize Engine Provides:

• Resize Images From 1/4x to 4x

• Separate Horizontal and Vertical Control

– Back End Provides:

• Hardware On-Screen Display (OSD)

• 4 - 54 MHz DACs for a Combination of

– Composite NTSC/PAL Video

– Luma/Chroma Separate Video

(S-video)

– Component (YPbPr or RGB) Video

(Progressive)

• Digital Output

– 8-/16-Bit YUV or up to 24-Bit RGB

– HD Resolution

– Up to 2 Video Windows

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testingof all parameters.

Copyright © 2005–2010, Texas Instruments Incorporated

Page 2

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

www.ti.com

• External Memory Interfaces (EMIFs) • 10/100 Mb/s Ethernet MAC (EMAC)

– 32-Bit DDR2 SDRAM Memory Controller With – IEEE 802.3 Compliant

256M-Byte Address Space (1.8-V I/O)

– Asynchronous16-Bit-Wide EMIF (EMIFA)

With 128M-Byte Address Reach

• Flash Memory Interfaces

– NOR (8-/16-Bit-Wide Data)

– NAND (8-/16-Bit-Wide Data)

• Flash Card Interfaces

– Media Independent Interface (MII)

• VLYNQ™ Interface (FPGA Interface)

• Host-Port Interface (HPI) with 16-Bit

Multiplexed Address/Data

• USB Port With Integrated 2.0 PHY

– USB 2.0 High-/Full-Speed (480 Mbps) Client

– USB 2.0 High-/Full-/Low-Speed Host

– Multimedia Card (MMC)/Secure Digital (SD) (Mini-Host, Supporting One External

with Secure Data I/O (SDIO) Device)

– Compact Flash Controller With True IDE • Three Pulse Width Modulator (PWM) Outputs

Mode

• On-Chip ARM ROM Bootloader (RBL) to Boot

– SmartMedia From NAND Flash or UART

• Enhanced Direct-Memory-Access (EDMA3) • ATA/ATAPI I/F (ATA/ATAPI-6 Specification)

Controller (64 Independent Channels)

• Two 64-Bit General-Purpose Timers (Each

Configurable as Two 32-Bit Timers)

• One 64-Bit Watch Dog Timer

• Three UARTs (One with RTS and CTS Flow

Control)

• One Serial Peripheral Interface (SPI) with Two

Chip-Selects

• Master/Slave Inter-Integrated Circuit (I2C Bus™)

• Audio Serial Port (ASP)

– I2S

– AC97 Audio Codec Interface

– Standard Voice Codec Interface (AIC12)

• Individual Power-Saving Modes for ARM/DSP

• Flexible PLL Clock Generators

• IEEE-1149.1 (JTAG) BoundaryScan-Compatible

• Up to 71 General-Purpose I/O (GPIO) Pins

(Multiplexed With Other Device Functions)

• 361-Pin Pb-Free BGA Package

(ZWT Suffix), 0.8-mm Ball Pitch

• 0.09-mm/6-Level Cu Metal Process (CMOS)

• 3.3-V and 1.8-V I/O, 1.2-V Internal

• Applications:

– Digital Media

– Networked Media Encode/Decode

– Video Imaging

2 Digital Media System-on-Chip (DMSoC) Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 3

TMS320DM6443

www.ti.com

1.2 Description

The TMS320DM6443 (also referenced as DM6443) leverages TI’s DaVinci™ technology to meet the

networked media encode and decode application processing needs of next-generation embedded devices.

The DM6443 enables OEMs and ODMs to quickly bring to market devices featuring robust operating

systems support, rich user interfaces, high processing performance, and long battery life through the

maximum flexibility of a fully integrated mixed processor solution.

The dual-core architecture of the DM6443 provides benefits of both DSP and Reduced Instruction Set

Computer (RISC) technologies, incorporating a high-performance TMS320C64x+™ DSP core and an

ARM926EJ-S core.

The ARM926EJ-S is a 32-bit RISC processor core that performs 32-bit or 16-bit instructions and

processes 32-bit, 16-bit, or 8-bit data. The core uses pipelining so that all parts of the processor and

memory system can operate continuously.

The ARM core incorporates:

• A coprocessor 15 (CP15) and protection module

• Data and program Memory Management Units (MMUs) with table look-aside buffers.

• Separate 16K-byte instruction and 8K-byte data caches. Both are four-way associative with virtual

index virtual tag (VIVT).

The TMS320C64x+™ DSPs are the highest-performance fixed-point DSP generation in the

TMS320C6000™ DSP platform. It is based on an enhanced version of the second-generation

high-performance, advanced very-long-instruction-word (VLIW) architecture developed by Texas

Instruments (TI), making these DSP cores an excellent choice for digital media applications. The C64x is a

code-compatible member of the C6000™ DSP platform. The TMS320C64x+ DSP is an enhancement of

the C64x+™ DSP with added functionality and an expanded instruction set.

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

Any reference to the C64x™ DSP or C64x™ CPU also applies, unless otherwise noted, to the C64x+™

DSP and C64x+™ CPU, respectively.

With performance of up to 4752 million instructions per second (MIPS) at a clock rate of 594 MHz, the

C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses

the operational flexibility of high-speed controllers and the numerical capability of array processors. The

C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly

independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The

eight functional units include instructions to accelerate the performance in video and imaging applications.

The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2376 million

MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 4752 MMACS. For more details

on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide

(literature number SPRU732).

The DM6443 also has application-specific hardware logic, on-chip memory, and additional on-chip

peripherals similar to the other C6000 DSP platform devices. The DM6443 core uses a two-level

cache-based architecture. The Level 1 program cache (L1P) is a 256K-bit direct mapped cache and the

Level 1 data cache (L1D) is a 640K-bit 2-way set-associative cache. The Level 2 memory/cache (L2)

consists of an 512K-bit memory space that is shared between program and data space. L2 memory can

be configured as mapped memory, cache, or combinations of the two.

The peripheral set includes: 1 configurable video port; a 10/100 Mb/s Ethernet MAC (EMAC) with a

Management Data Input/Output (MDIO) module; an inter-integrated circuit (I2C) Bus interface; one audio

serial port (ASP); 2 64-bit general-purpose timers each configurable as 2 independent 32-bit timers;

1 64-bit watchdog timer; up to 71-pins of general-purpose input/output (GPIO) with programmable

interrupt/event generation modes, multiplexed with other peripherals; 3 UARTs with hardware

handshaking support on 1 UART; 3 pulse width modulator (PWM) peripherals; and 2 external memory

interfaces: an asynchronous external memory interface (EMIFA) for slower memories/peripherals, and a

higher speed synchronous memory interface for DDR2.

Copyright © 2005–2010, Texas Instruments Incorporated Digital Media System-on-Chip (DMSoC) 3

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 4

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

The DM6443 includes a Video Processing Sub-System (VPSS) that has a configurable Resizer and Video

Processing Back-End (VPBE) output used for display.

The Resizer accepts image data for separate horizontal and vertical resizing from 1/4x to 4x in increments

of 256/N, where N is between 64 and 1024.

The Video Processing Back-End (VPBE) is comprised of an On-Screen Display Engine (OSD) and a

Video Encoder (VENC). The OSD engine is capable of handling 2 separate video windows and 2 separate

OSD windows. Other configurations include 2 video windows, 1 OSD window, and 1 attribute window

allowing up to 8 levels of alpha blending. The VENC provides four analog DACs that run at 54 MHz,

providing a means for composite NTSC/PAL video, S-Video, and/or Component video output. The VENC

also provides up to 24 bits of digital output to interface to RGB888 devices. The digital output is capable of

8/16-bit BT.656 output and/or CCIR.601 with separate horizontal and vertical syncs.

The Ethernet Media Access Controller (EMAC) provides an efficient interface between the DM644x and

the network. The DM6443 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps)

and 100 Mbps in either half- or full-duplex mode, with hardware flow control and quality of service (QOS)

support.

The Management Data Input/Output (MDIO) module continuously polls all 32 MDIO addresses in order to

enumerate all PHY devices in the system. Once a PHY candidate has been selected by the ARM, the

MDIO module transparently monitors its link state by reading the PHY status register. Link change events

are stored in the MDIO module and can optionally interrupt the ARM, allowing the ARM to poll the link

status of the device without continuously performing costly MDIO accesses.

www.ti.com

The HPI, I2C, SPI, USB2.0, and VLYNQ ports allow DM6443 to easily control peripheral devices and/or

communicate with host processors. The DM6443 also provides multimedia card support, MMC/SD, with

SDIO support.

The rich peripheral set provides the ability to control external peripheral devices and communicate with

external processors. For details on each of the peripherals, see the related sections later in this document

and the associated peripheral reference guides listed in Section 2.8.3.1, Related Documentation From

Texas Instruments.

The DM6443 has a complete set of development tools for both the ARM and DSP. These include

C compilers, a DSP assembly optimizer to simplify programming and scheduling, and a Windows™

debugger interface for visibility into source code execution.

4 Digital Media System-on-Chip (DMSoC) Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 5

JTAG Interface

System Control

PLLs/Clock

Generator

Input

Clock(s)

Power/Sleep

Controller

Pin

Multiplexing

ARM Subsystem

ARM926EJ-S CPU

16 KB

I-Cache

16 KB RAM

8 KB

D-Cache

8 KB ROM

DSP Subsystem

C64x+t DSP CPU

32 KB

L1 Pgm

64 KB L2 RAM

80 KB

L1 Data

Video Processing Subsystem (VPSS)

Front End

Resizer

10b DAC

On-Screen

Display

(OSD)

Video

Encoder

(VENC)

10b DAC

10b DAC

10b DAC

Back End 8b BT.656,

Y/C,

24b RGB

NTSC/

PAL,

S-Video,

RGB,

YPbPr

Switched Central Resource (SCR)

Peripherals

EDMA3

Audio

Serial

Port

I2C SPI

UART

Serial Interfaces

DDR2

Mem Ctlr

(16b/32b)

Async EMIF/

NAND/

SmartMedia

ATA/

Compact

Flash

MMC/

SD/

SDIO

Program/Data Storage

Watchdog

Timer

PWM

System

GeneralPurpose

Timer

USB 2.0

PHY

VLYNQ

EMAC

With

MDIO

Connectivity

HPI

TMS320DM6443

www.ti.com

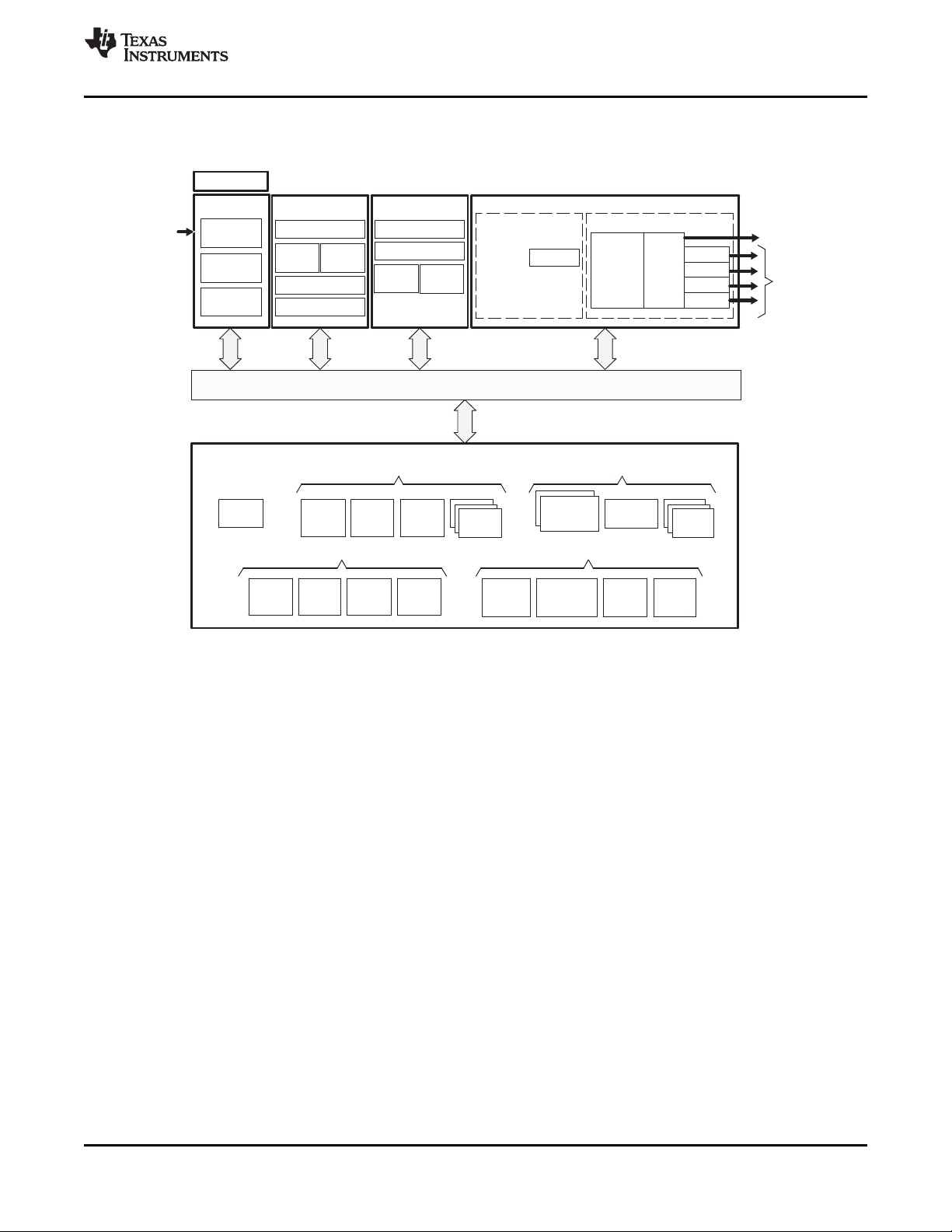

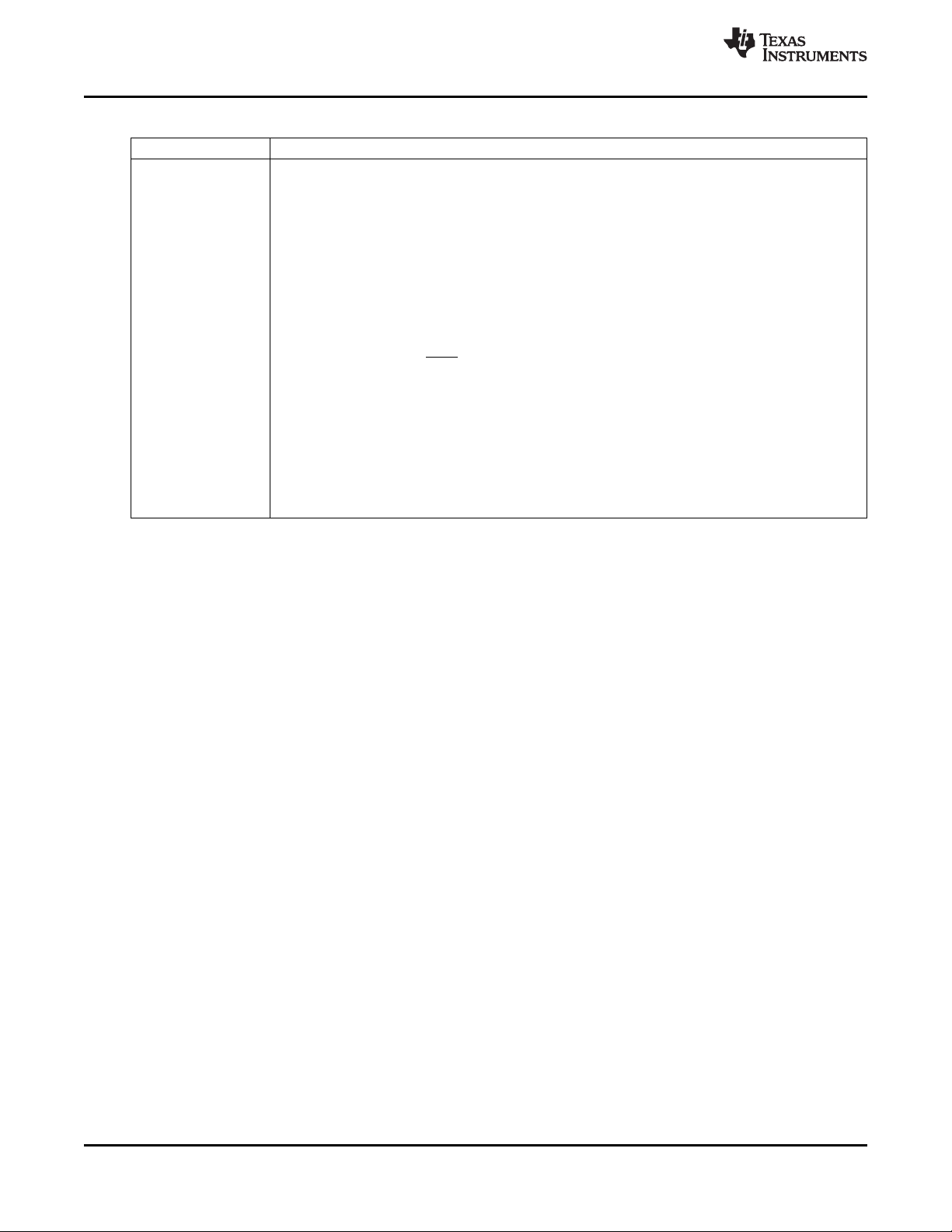

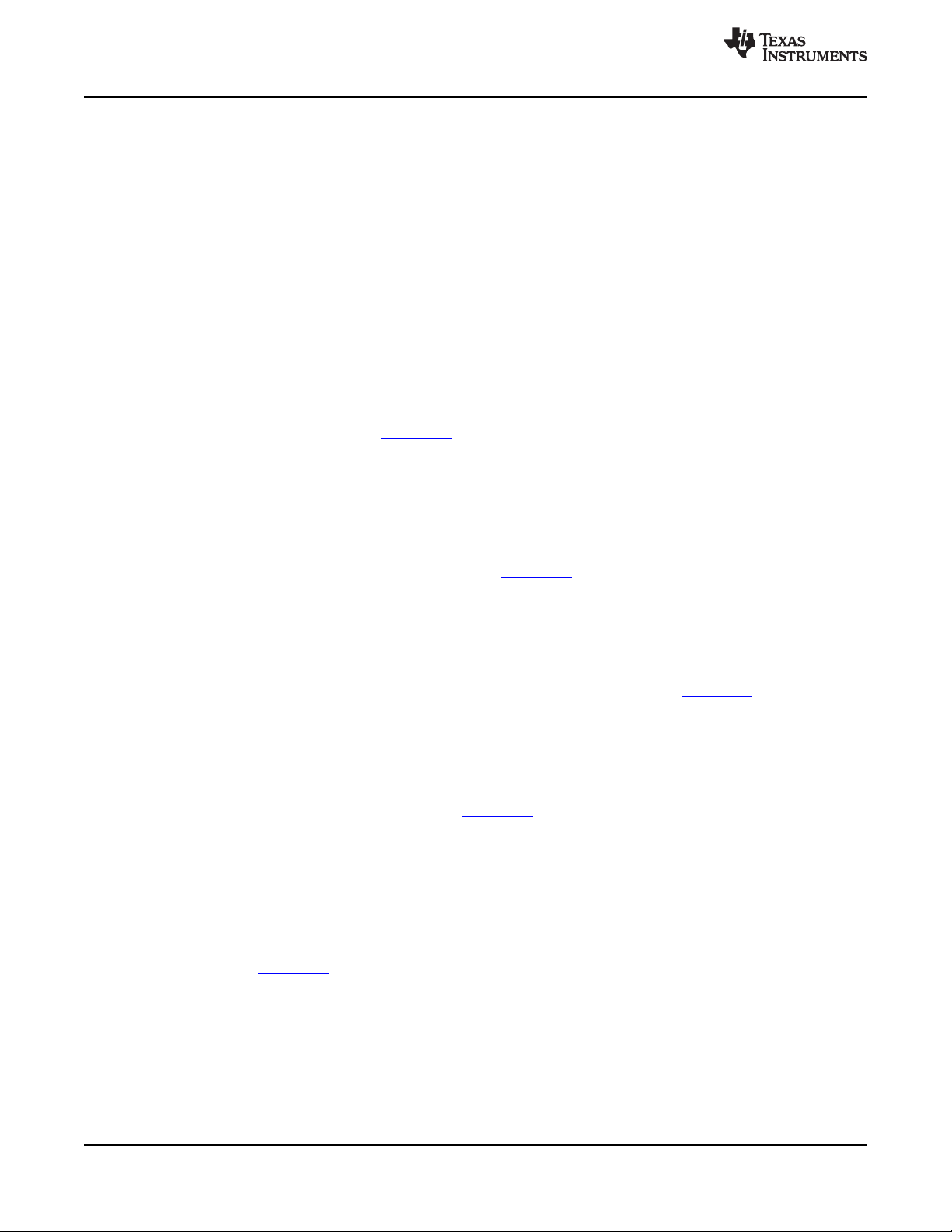

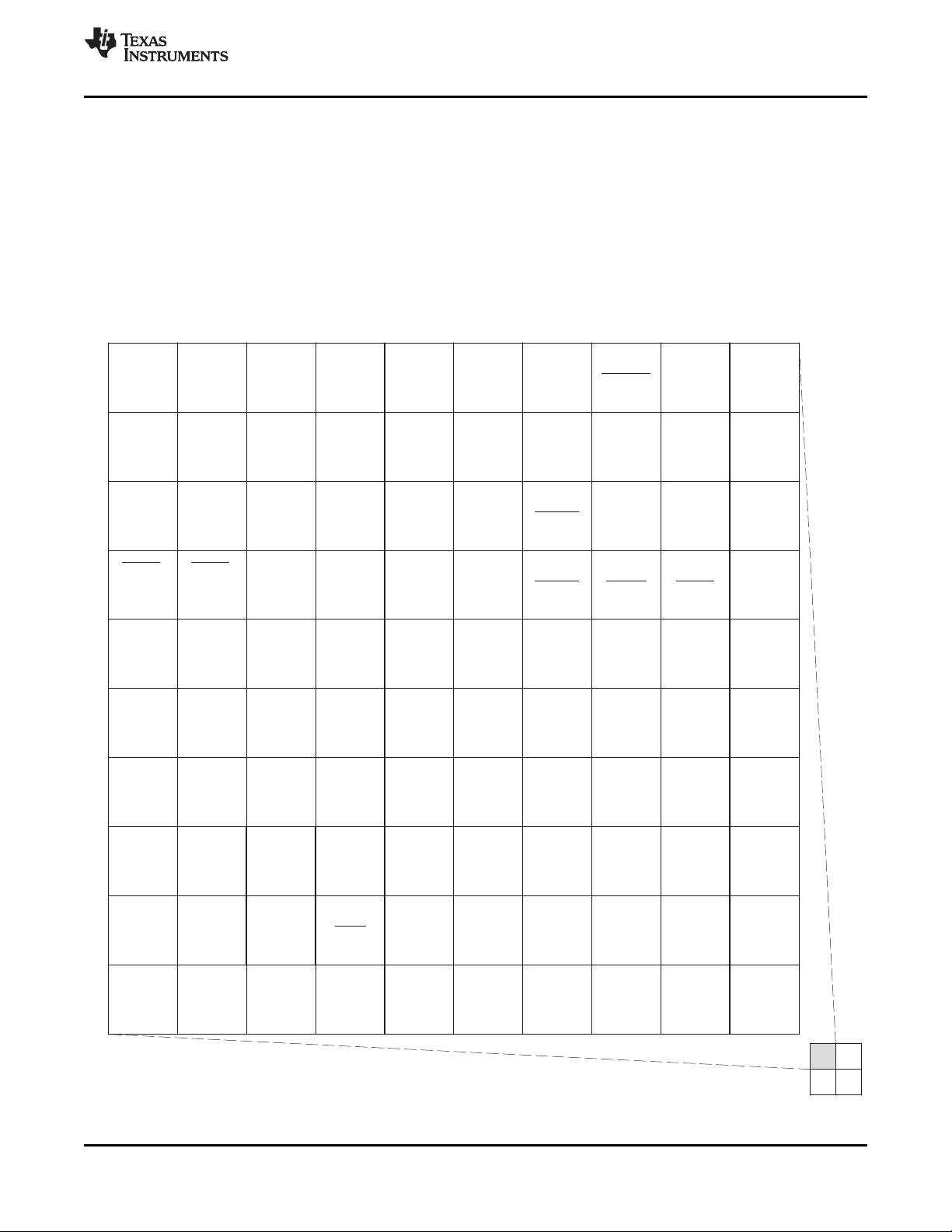

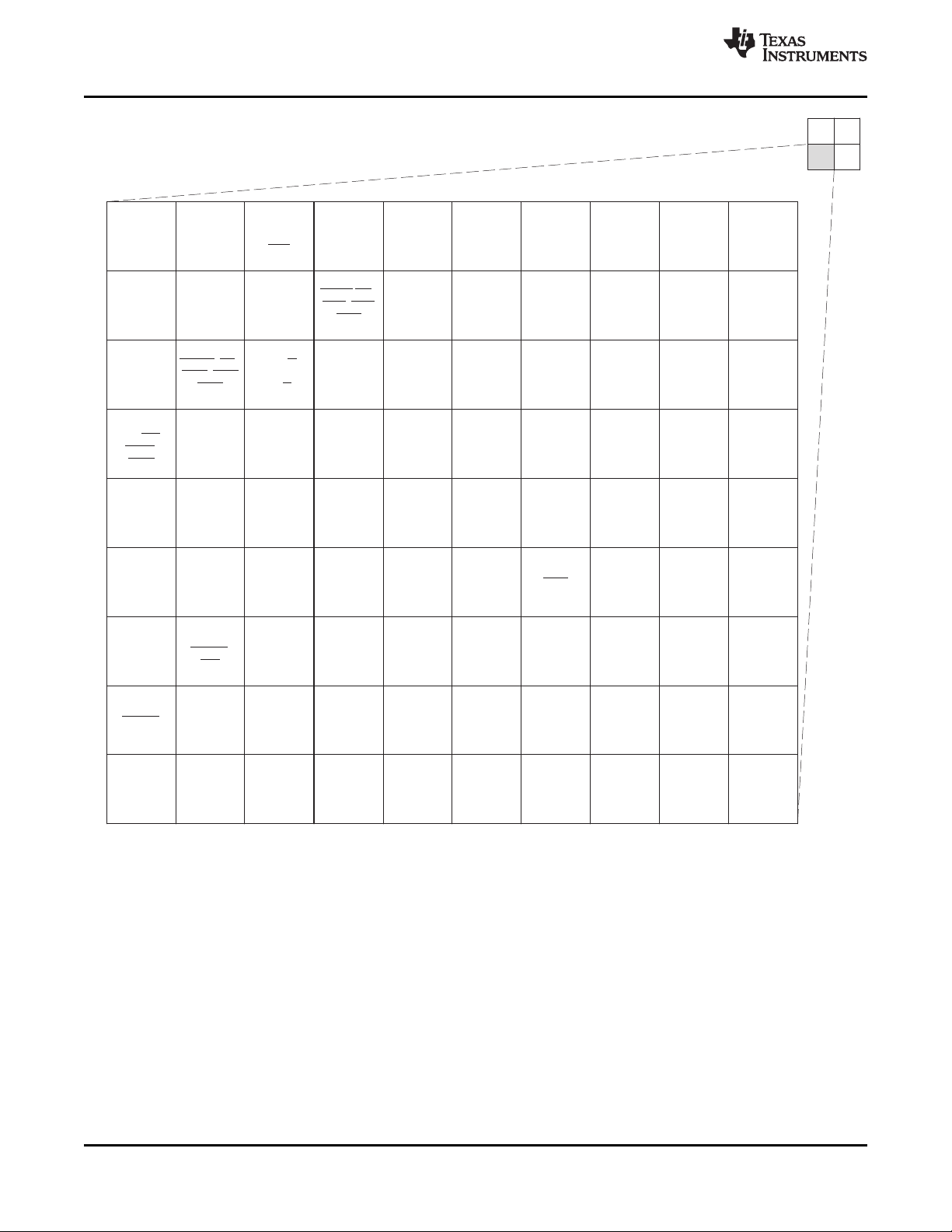

1.3 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the device.

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

Figure 1-1. TMS320DM6443 Functional Block Diagram

Copyright © 2005–2010, Texas Instruments Incorporated Digital Media System-on-Chip (DMSoC) 5

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 6

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

www.ti.com

1 Digital Media System-on-Chip (DMSoC) ............ 1 6 Peripheral and Electrical Specifications .......... 89

1.1 Features .............................................. 1

1.2 Description ........................................... 3

1.3 Functional Block Diagram ............................ 5

Revision History .............................................. 7

2 Device Overview ....................................... 11

2.1 Device Characteristics .............................. 11

2.2 Device Compatibility ................................ 12

2.3 ARM Subsystem .................................... 12

2.4 DSP Subsystem .................................... 17

2.5 Memory Map Summary ............................. 21

2.6 Pin Assignments .................................... 25

2.7 Terminal Functions ................................. 29

2.8 Device Support ..................................... 56

3 Device Configurations ................................ 61

3.1 System Module Registers .......................... 61

3.2 Power Considerations .............................. 62

3.3 Bootmode ........................................... 63

3.4 Configurations at Reset ............................ 66

3.5 Configurations After Reset ......................... 70

3.6 Emulation Control ................................... 82

4 System Interconnect .................................. 84

4.1 System Interconnect Block Diagram ............... 85

5 Device Operating Conditions ....................... 86

5.1 Absolute Maximum Ratings Over Operating Case

Temperature Range

(Unless Otherwise Noted) ................................. 86

5.2 Recommended Operating Conditions .............. 87

5.3 Electrical Characteristics Over Recommended

Ranges of Supply Voltage and Operating Case

Temperature (Unless Otherwise Noted) ............ 88

6.1 Parameter Information .............................. 89

6.2 Recommended Clock and Control Signal Transition

Behavior ............................................ 90

6.3 Power Supplies ..................................... 90

6.4 Reset ............................................... 99

6.5 External Clock Input From MXI/CLKIN Pin ........ 102

6.6 Clock PLLs ........................................ 105

6.7 Interrupts .......................................... 111

6.8 General-Purpose Input/Output (GPIO) ............ 118

6.9 Enhanced Direct Memory Access (EDMA3)

Controller .......................................... 121

6.10 External Memory Interface (EMIF) ................ 133

6.11 ATA/CF ............................................ 142

6.12 MMC/SD/SDIO .................................... 155

6.13 Video Processing Sub-System (VPSS) Overview

..................................................... 158

6.14 Host-Port Interface (HPI) .......................... 171

6.15 USB 2.0 ........................................... 174

6.16 Universal Asynchronous Receiver/Transmitter

(UART) ............................................ 183

6.17 Serial Peripheral Interface (SPI) .................. 186

6.18 Inter-Integrated Circuit (I2C) ...................... 190

6.19 Audio Serial Port (ASP) ........................... 193

6.20 Ethernet Media Access Controller (EMAC) ....... 197

6.21 Management Data Input/Output (MDIO) .......... 203

6.22 Timer .............................................. 205

6.23 Pulse Width Modulator (PWM) .................... 207

6.24 VLYNQ ............................................ 209

6.25 IEEE 1149.1 JTAG ................................ 213

7 Mechanical Packaging and Orderable

Information ............................................ 215

7.1 Thermal Data for ZWT ............................ 215

7.2 Packaging Information ............................ 215

6 Contents Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 7

TMS320DM6443

www.ti.com

This data manual revision history highlights the technical changes made to the SPRS282F device-specific

data manual to make it an SPRS282G revision.

Scope: Added information/data on silicon revision 2.3.

Applicable updates to the DM64x device family, specifically relating to the TMS320DM6443 device, have

been incorporated.

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

TMS320DM6443 Revision History

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Global

Section 1.3 Figure 1-1, TMS320DM6443 Functional Block Diagram:

Functional Block

Diagram

Section 2.1 Table 2-1, Characteristics of the Processor:

Device Characteristics

• Added information/data on silicon revision 2.3

• Updated/changed all applicable EDMA instances to "EDMA3" [Cleared Documentation Feedback

Issue]

• Updated the document to reflect the following:

– "ARM can boot from internal ROM SPI".

• Removed PCLK

• Video Processing Subsystem (VPSS):

– Removed CCD Controller Video Interface, Histogram/3A, and Preview from Front End block

• Updated/changed "C64x+ Megamodule Revision" for silicon revision 2.3

• Updated/changed "JTAG BSDL_ID" for silicon revision 2.3

• Added "ball finish SnAgCu" to the BGA Package HARDWARE FEATURES row [Cleared

Documentation Feedback Issue]

Section 2.4

DSP Subsystem

Section 2.8.2 Figure 2-6, Device Nomenclature:

Device and

Development-Support

Tool Nomenclature

Section 2.8.3.1

Related Documentation

From Texas

Instruments

Section 3.3.1.1

BOOTCFG Register

Description

Section 3.5.1 Table 3-12, DM6443 Default Bus Master Priorities:

Switched Central

Resource (SCR) Bus

Priorities

Section 3.5.2 "A summary of the pin multiplexing is ..." paragraph:

Multiplexed Pin

Configurations

• Added DSP Subsystem features list

• Added "B = Silicon 2.3" under SILICON REVISION

• Updated/changed list of reference documents

• Updated/changed the location of the BOOTCFG register from "0x01C4 000A" to "0x01C4 0014"

[Cleared Documentation Feedback Issue]

• Added, for clarity, ", DMA_PRI bit field" to the VPSSP DEFAULT PRIORITY LEVEL description

[Cleared Documentation Feedback Issue]

• Added "[For more detailed information ..." statement to the VPSSP, EDMATC0P, EDMATC1P, and

C64X+_DMAP rows

• Added "(MSTPRI1 Register)" to the HPIP DEFAULT PRIORITY LEVEL description

Figure 3-6, MSTPRI1 Register:

• Updated/changed bits 22:20 from Reserved to HPIP

• Added "these are multiplexed with GPIOs" to "The VPBE function of the VPSS requires ..." sentence

Copyright © 2005–2010, Texas Instruments Incorporated Contents 7

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 8

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

TMS320DM6443 Revision History (continued)

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Section 3.5.2 Table 3-13, DM6443 Multiplexed Peripheral Pins and Multiplexing Controls:

Multiplexed Pin

Configurations

Section 3.5.4 Figure 3-7, PINMUX0 Register:

PINMUX0 Register

Description

Section 6.3.1.3 Figure 6-6, PLL1 and PLL2 Clock Domain Block Diagram:

DM6443 Power and

Clock Domains

• "VPFE CCD, VPBE RGB888, GPIO" row:

– MULTIPLEXED PERIPHERALS column: Removed "VPFE CCD" from "VPFE CCD, VPBE

RGB888, GPIO"

– TERTIARY FUNCTION column: Removed "VPFE: CCD_FIELD"

– TERTIARY REGISTER/PIN CONTROL column: Removed "PinMux0:CFLDEN"

• "UART2, VPFE" row:

– MULTIPLEXED PERIPHERALS column: Removed "VPFE" from "UART2, VPFE"

– PRIMARY (DEFAULT) FUNCTION column: Updated/changed "VPFE:

CI[7:6]/CCD_DATA[15:14]" to "N/A"

• "UART2, VPFE" row:

– MULTIPLEXED PERIPHERALS column: Removed "VPFE" from "UART2, VPFE"

– PRIMARY (DEFAULT) FUNCTION column: Updated/changed "VPFE:

CI[5:4]/CCD_DATA[13:12]" to "N/A"

• Bits 28–26: Updated/changed "R/W-0" to "R/W-000"

• Bits 4–0: Updated/changed "R/W-LLLL" to "R/W-LLLLL"

• Updated/changed footnote—removed bit 29 from footnote

Table 3-14, PINMUX0 Register Description:

• Updated/changed the description of HPIEN [Cleared Documentation Feedback Issue]

• Added "HPI" block

• Updated/changed "EDMA" to "EDMA3"

• Removed PCLK

www.ti.com

Section 6.3.1.4 Table 6-6, PSC Register Memory Map [Cleared Documentation Feedback Issue]:

Power and Sleep

Controller (PSC)

Module

Section 6.4.1 Figure 6-9, Reset Timing:

Reset Electrical

Data/Timing

Section 6.6.3 Table 6-19, Switching Characteristics Over Recommended Operating Conditions for CLK_OUT1:

Clock PLL Electrical

Data/Timing (Input and

Output Clocks)

Section 6.9

Enhanced Direct

Memory Access

(EDMA3) Controller

Section 6.10.1.2 Table 6-35, Switching Characteristics Over Recommended Operating Conditions for Asynchronous

EMIFA Electrical Memory Cycles for EMIFA Module:

Data/Timing

Section 6.12.1 Table 6-43, MMC/SD/SDIO Register Descriptions:

MMC/SD/SDIO

Peripheral

Description(s)

Section 6.13

Video Processing

Sub-System (VPSS)

Overview

• Updated/changed address range "0x01C4 1004 through 0x01C4 1014 to "Reserved"

• Updated/changed address range "0x01C4 107C through 0x01C4 111F to "Reserved"

• Updated/changed address range "0x01C4 1308 through 0x01C4 17FF to "Reserved"

• Updated/changed the pins specified in the Z Group [Cleared Documentation Feedback Issue]

• Parameter 1 (tC): Added "ns" in UNIT column

• Added "The EDMA3 controller supports two addressing modes ..." paragraph

• Parameter 24 [t

• Updated/changed 0x01E1 0064 from "SDIO" to "SDIOCTL (SDIO Control Register)"

• Updated/changed 0x01E1 0068 from "SDIO" to "SDIOST0 (SDIO Status Register 0)"

• Updated/changed 0x01E1 006C from "SDIO" to "SDIOIEN (SDIO Interrupt Enable Register)"

• Updated/changed 0x01E1 0070 from "Reserved" to "SDIOIST (SDIO Interrupt Status Register)"

• Updated/changed "The DM6443 Video Processing Sub-System (VPSS) provides a Video Processing

Front End (VPFE) input interface ..." paragraph

• Updated/changed Note

w(EMWEL)

]: Added "ns" in UNIT column

8 Contents Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 9

TMS320DM6443

www.ti.com

TMS320DM6443 Revision History (continued)

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Section 6.13.1.2

VPFE Electrical

Data/Timing

Section 6.13.2.3 Table 6-52, Timing Requirements for VPBE CLK Inputs:

VPBE Electrical

Data/Timing

• Removed "VPFE Electrical Data/Timing" section

• Removed Parameter 1 [t

• Removed Parameter 2 [t

• Removed Parameter 3 [t

• Removed Parameter 4 [t

], Cycle time, PCLK

c(PCLK)

], Pulse duration, PCLK high

w(PCLKH)

], Pulse duration, PCLK low

w(PCLKL)

], Transition time, PCLK

t(PCLK)

Figure 6-46, VPBECLK Timing:

• Updated/changed figure title from "VPBE PCLK and VPBECLK Timing" to "VPBECLK Timing"

• Removed PCLK waveform

Table 6-53, Timing Requirements for VPBE Control Input With Respect to VPBECLK:

• Updated/changed table title from "Timing Requirements for VPBE Control Input With Respect to

PCLK and VPBECLK" to "Timing Requirements for VPBE Control Input With Respect to VPBECLK"

• Removed Parameter 9 [t

• Removed Parameter 10 [t

su(VCTLV-PCLK)

h(PCLK-VCTLV)

• Renumbered Parameter 27 as Parameter 9 [t

VPBECLK rising edge

• Renumbered Parameter 28 as Parameter 10 [t

VPBECLK rising edge

• Removed Parameter 33 [t

• Removed Parameter 34 [t

su(FIELD-PCLK)

h(PCLK-FIELD)

• Renumbered Parameter 35 as Parameter 33 [t

VPBECLK edge

• Renumbered Parameter 36 as Parameter 34 [t

VPBECLK edge

], Setup time, VCTL valid before PCLK edge

], Hold time, VCTL valid after PCLK edge

su(VCTLV-VPBECLK)

h(VPBECLK-VCTLV)

], Setup time, LCD_FIELD valid before PCLK edge

], Hold time, LCD_FIELD valid after PCLK edge

su(FIELD-VPBECLK)

h(VPBECLK-FIELD)

• Removed "PCLK may be configured ..." footnote

• Updated/changed "P = 1/(VCLKIN clock frequency) in ns ..." footnote

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

], Setup time, VCTL valid before

], Hold time, VCTL valid after

], Setup time, LCD_FIELD valid before

], Hold time, LCD_FIELD valid after

Figure 6-47, VPBE Input Timing With Respect to VPBECLK:

• Updated/changed figure title from "VPBE Input Timing With Respect to PCLK and VPBECLK" to

"VPBE Input Timing With Respect to VPBECLK"

• Removed VPBECLK waveform

• Renamed PCLK (Positive Edge Clocking) waveform as VPBECLK waveform

• Removed PCLK (Negative Edge Clocking) waveform

• Removed Parameters 27, 28, 35, and 36

Table 6-54, Switching Characteristics Over Recommended Operating Conditions for VPBE Control and

Data Output With Respect to VPBECLK:

• Updated/changed table title from "Switching Characteristics Over Recommended Operating

Conditions for VPBE Control and Data Output With Respect to PCLK and VPBECLK" to "Switching

Characteristics Over Recommended Operating Conditions for VPBE Control and Data Output With

Respect to VPBECLK"

• Removed Parameter 11 [t

• Removed Parameter 12 [t

• Removed Parameter 13 [t

• Removed Parameter 14 [t

d(PCLK-VCTLV)

d(PCLK-VCTLIV)

d(PCLK-VDATAV)

d(PCLK-VDATAIV)

], Delay time, PCLK edge to VCTL valid

], Delay time, PCLK edge to VCTL invalid

], Delay time, PCLK edge to VDATA valid

], Delay time, PCLK edge to VDATA invalid

• Removed "PCLK may be configured ..." footnote

Figure 6-48, VPBE Output Timing With Respect to VPBECLK:

• Updated/changed figure title from "VPBE Output Timing With Respect to PCLK and VPBECLK" to

"VPBE Output Timing With Respect to VPBECLK"

• Removed PCLK (Positive Edge Clocking) waveform

• Removed PCLK (Negative Edge Clocking) waveform

• Removed Parameters 11, 12, 13, and 14

Copyright © 2005–2010, Texas Instruments Incorporated Contents 9

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 10

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

TMS320DM6443 Revision History (continued)

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Table 6-55, Switching Characteristics Over Recommended Operating Conditions for VPBE Control and

Data Output With Respect to VCLK:

• Updated/changed PARAMETER NO. 22 to "Delay time, VCLKIN low to VCLK low". [Cleared

Documentation Feedback Issue]

• Updated/changed "VCLKIN = PCLK or VPBECLK" footnote to "VCLKIN = VPBECLK"

Figure 6-49, VPBE Control and Data Output Timing With Respect to VCLK:

• Updated/changed "VCLKIN = PCLK or VPBECLK" footnote to "VCLKIN = VPBECLK"

Section 6.13.2.4

DAC Electrical

Data/Timing

Section 6.25

IEEE 1149.1 JTAG

Section 6.25.1

JTAG Peripheral

Register Description(s)

– JTAG ID Register

• Updated/changed "The DM6443's analog video DAC outputs ..." paragraph. [Cleared Documentation

Feedback Issue]

• Updated/changed the "TRST only needs to be released when it is necessary to use ..." paragraph.

[Cleared Documentation Feedback Issue]

• Added "Note:" to the end of Section 6.25

• Updated/changed "The JTAG ID register is a read-only register ..." paragraph

Figure 6-74, JTAG ID Register Description - DM6443 Register Value - 0xXB70 002F:

• Updated/changed footnote

Table 6-106, JTAG ID Register Selection Bit Descriptions:

• Updated/changed DESCRIPTION of Bits 31:28 (VARIANT)

www.ti.com

10 Contents Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 11

TMS320DM6443

www.ti.com

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

2 Device Overview

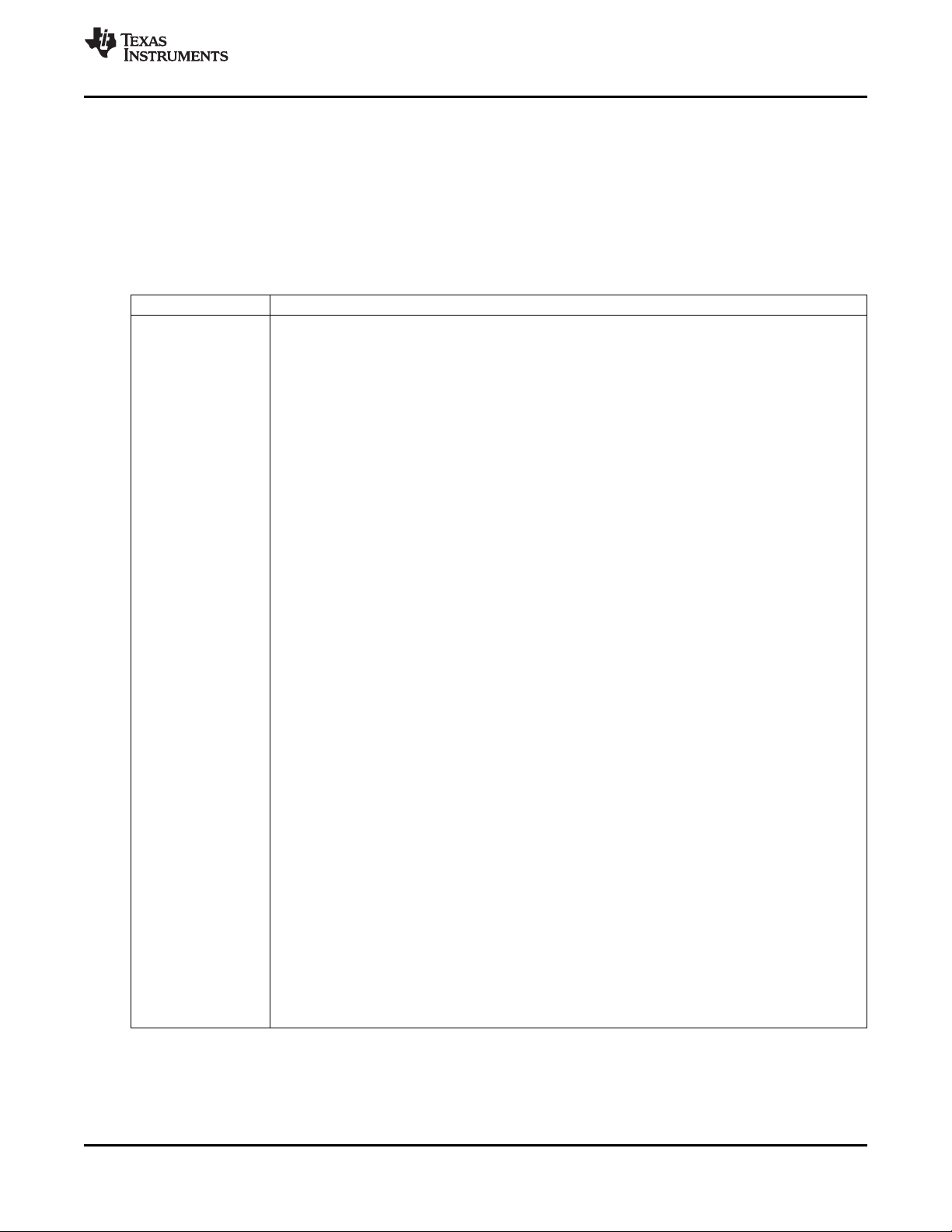

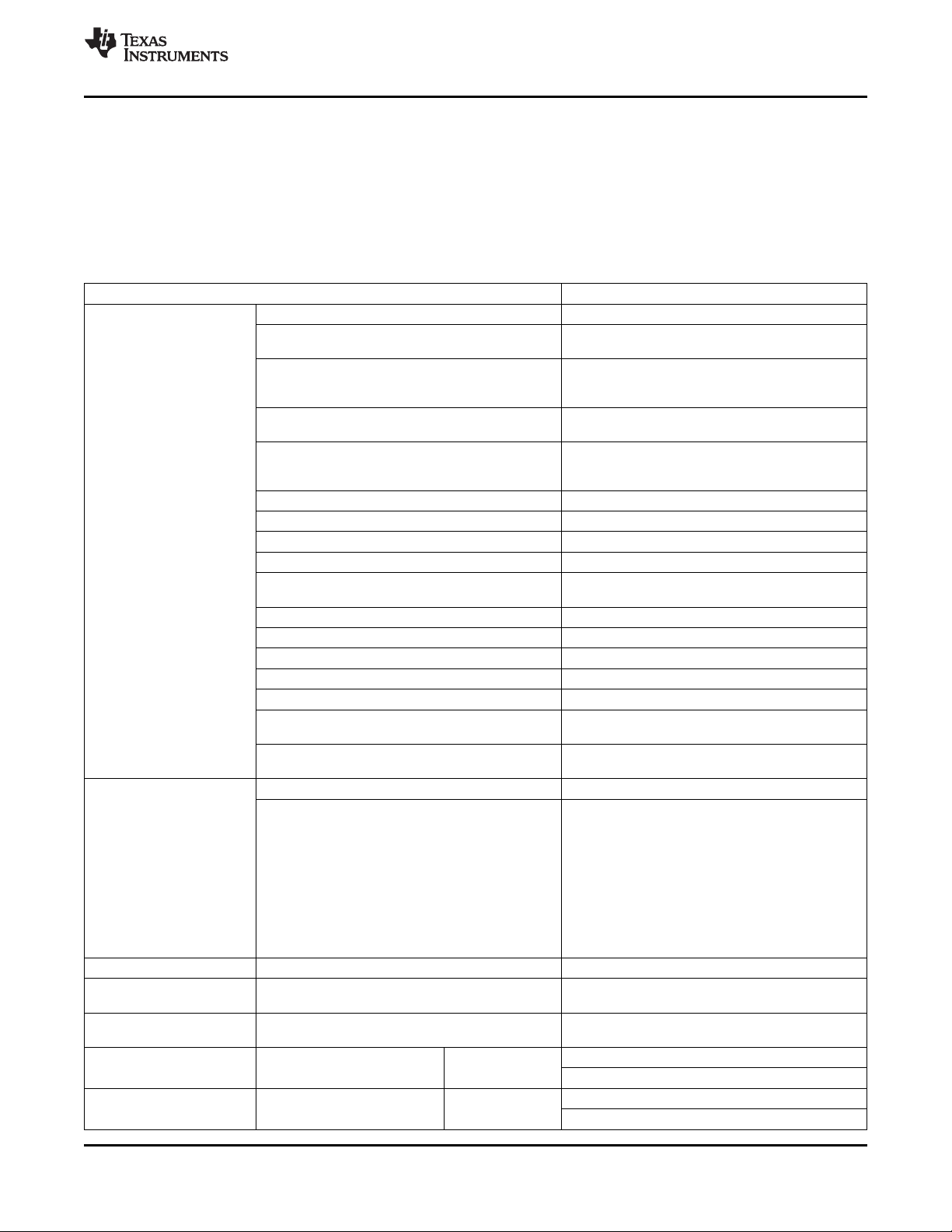

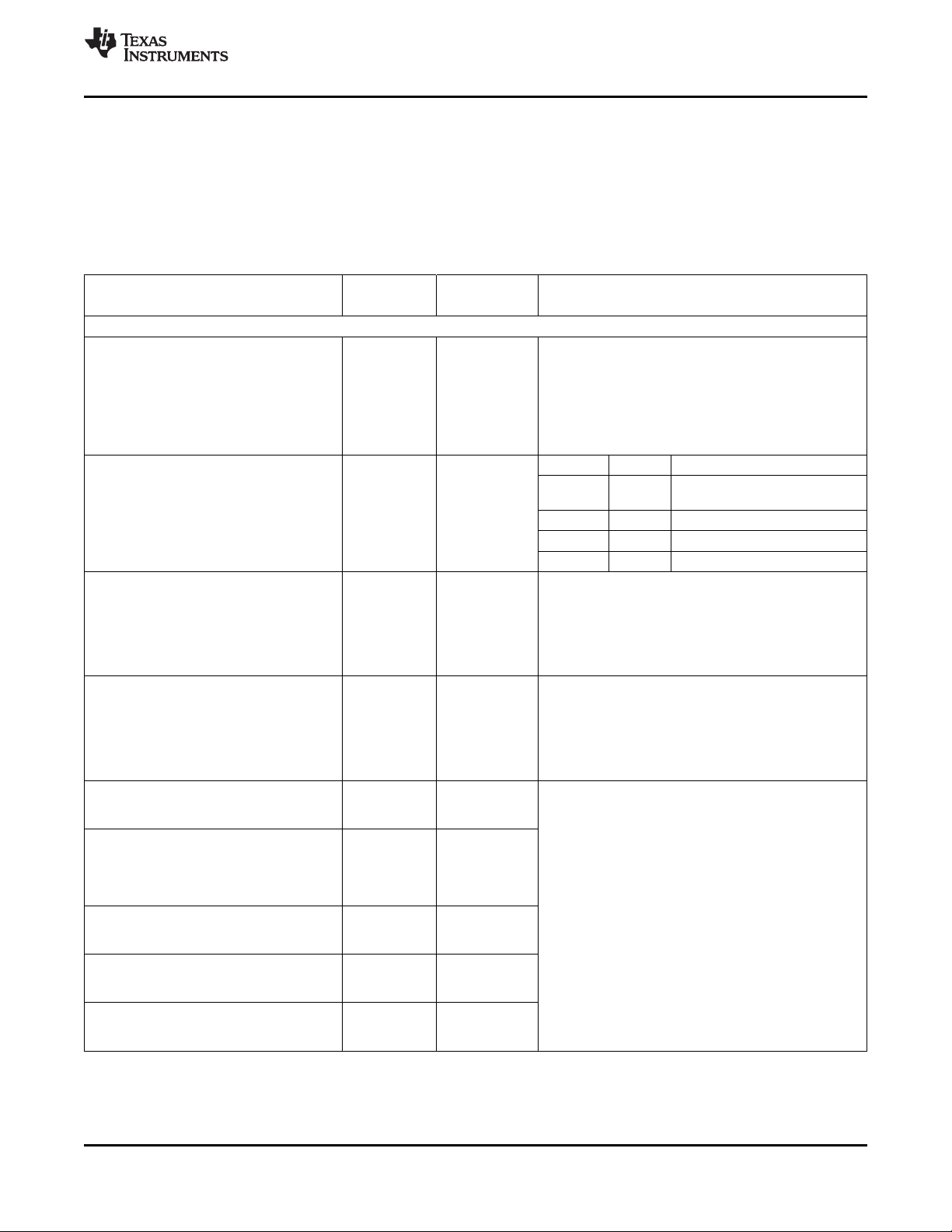

2.1 Device Characteristics

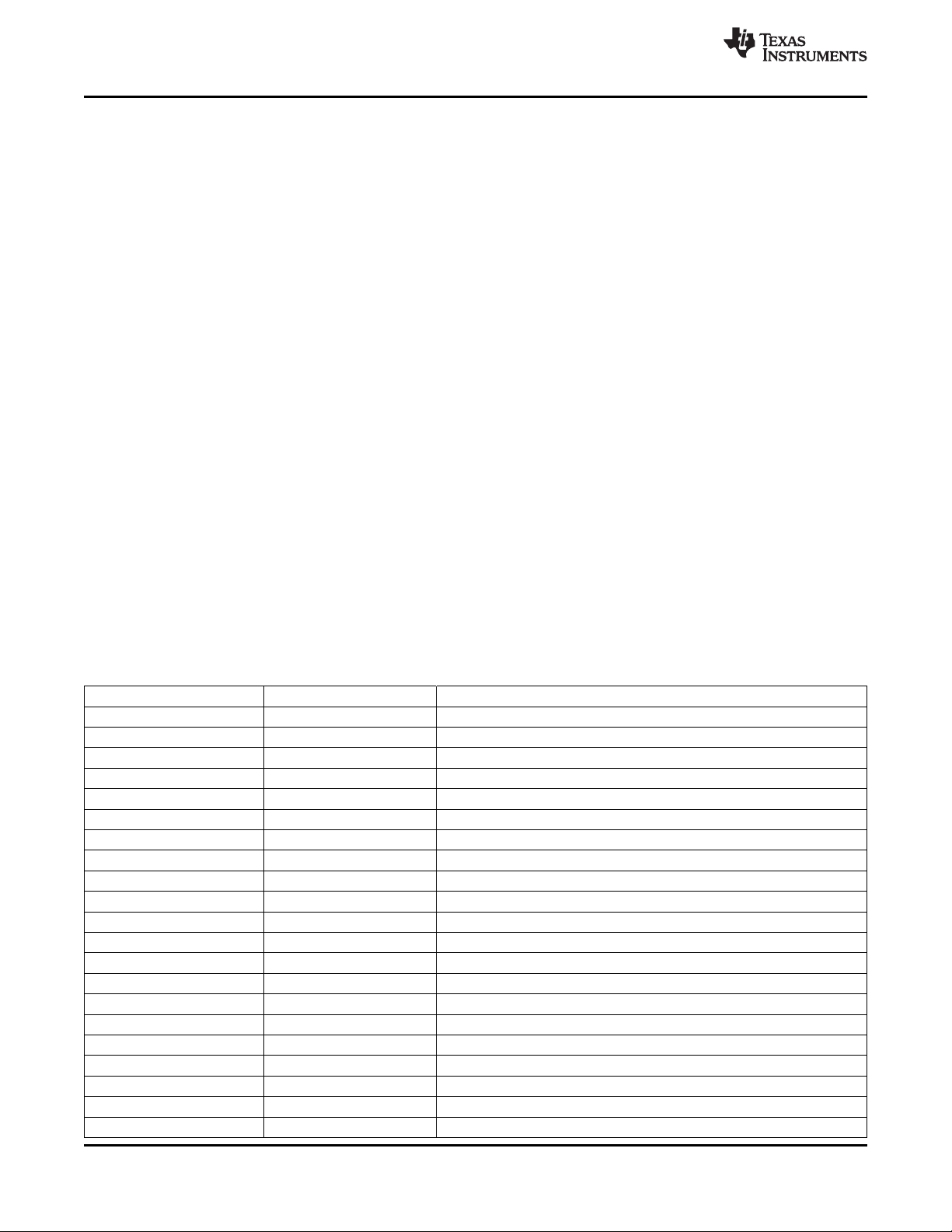

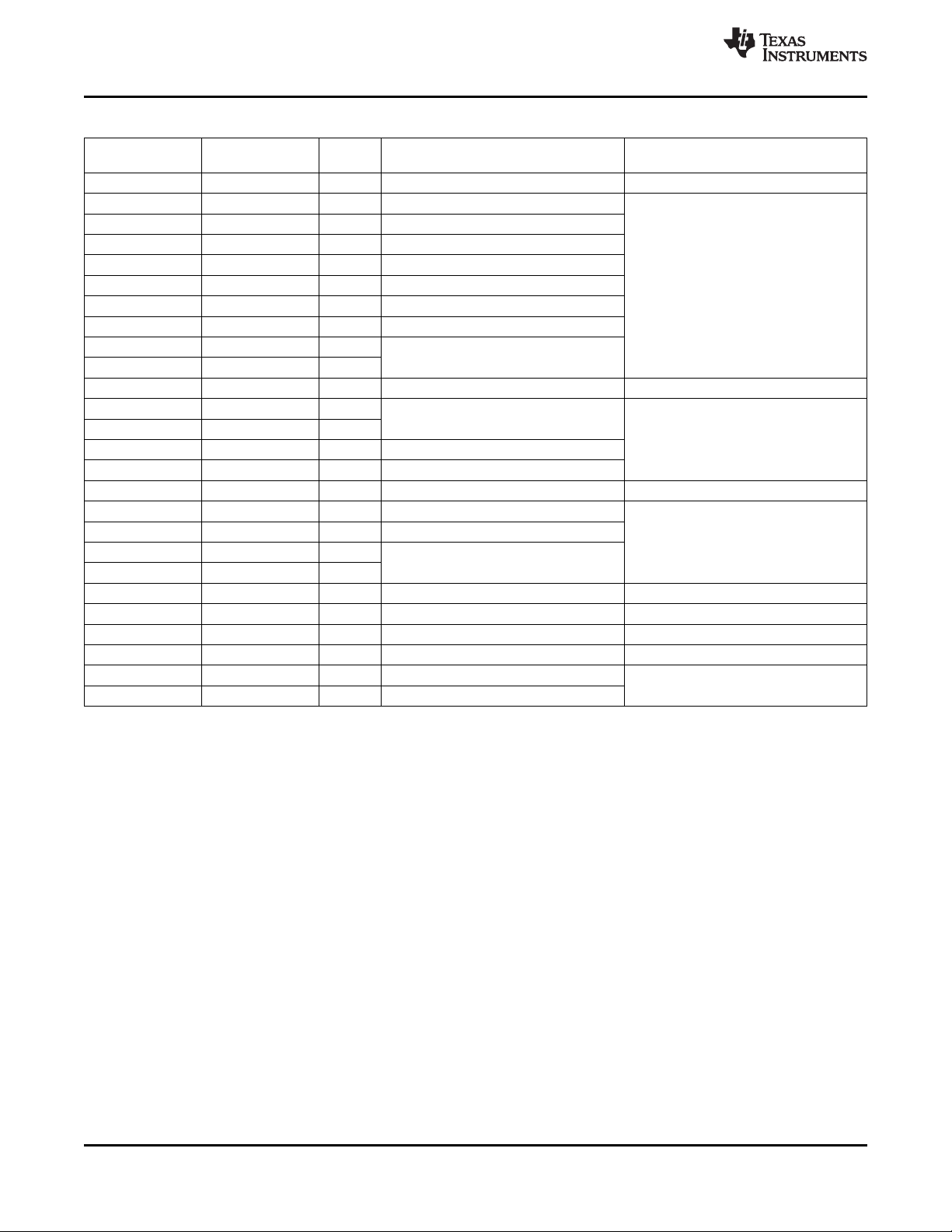

Table 2-1 provides an overview of the TMS320DM6443 SoC. The table shows significant features of the

device, including the capacity of on-chip RAM, peripherals, internal peripheral bus frequency relative to the

C64x+ DSP, and the package type with pin count.

Table 2-1. Characteristics of the Processor

HARDWARE FEATURES DM6443

DDR2 Memory Controller DDR2 (16/32-bit bus width)

Asynchronous EMIF (EMIFA)

Flash Cards MMC/SD with secure data input/output (SDIO)

EDMA3

Timers separate 32-bit timers)

Peripherals

Not all peripherals pins are

available at the same time.

(For more details, see

Section 3, Device

Configurations.)

On-Chip Memory

CPU ID + CPU Rev ID Control Status Register (CSR.[31:16]) 0x1000

C64x+ Megamodule Revision ID Register (MM_REVID[15:0]) 0x0000 (Silicon Revision 1.3 and earlier)

Revision (address location: 0x0181 2000) 0x0003 (Silicon Revision 2.1 and later)

JTAG BSDL_ID

CPU Frequency (Maximum) MHz DM6443 -594

Cycle Time (Minimum) ns DM6443 -594

UART 3 (one with RTS and CTS flow control)

SPI 1 (supports 2 slave devices)

I2C 1 (Master/Slave)

Audio Serial Port [ASP] 1

10/100 Ethernet MAC with Management Data

Input/Output

VLYNQ 1

HPI 1 (16-bit multiplexed address/data)

General-Purpose Input/Output Port Up to 71

PWM 3 outputs

ATA/CF 1 (ATA/ATAPI-6)

Configurable Video Port

USB 2.0

Size (Bytes) 160KB RAM, 8KB ROM

Organization

JTAGID Register 0x0B70 002F (Silicon Revision 1.3 and earlier)

(address location: 0x01C4 0028) 0x1B70 002F (Silicon Revision 2.1 and later)

Asynchronous (8/16-bit bus width) RAM, Flash

(NOR,NAND)

Compact Flash

SmartMedia/xD

64 independent channels

8 QDMA channels

2 64-Bit General Purpose (each configurable as 2

1 64-Bit Watch Dog

1

Resizer

1 Output (VPBE)

High Speed Device

High Speed Host

DSP

• 32KB L1 Program (L1P)/Cache (up to 32KB)

• 80KB L1 Data (L1D)/Cache (up to 32KB)

• 64KB Unified Mapped RAM/Cache (L2)

ARM

• 16KB I-cache

• 8KB D-cache

• 16KB RAM

• 8KB ROM

DSP 594 MHz

ARM 297 MHz

DSP 1.68 ns

ARM 3.37 ns

Copyright © 2005–2010, Texas Instruments Incorporated Device Overview 11

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 12

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

Table 2-1. Characteristics of the Processor (continued)

HARDWARE FEATURES DM6443

Voltage

PLL Options x1 (Bypass), x22 (-594)

BGA Package 357-Pin BGA (ZWT)

Process Technology µm 0.09 µm

Product Status

(1) PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas

Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

(1)

Core (V) 1.2 V (-594)

I/O (V) 1.8 V, 3.3 V

CLKIN frequency multiplier

(27 MHz reference)

16 x 16 mm

ball finish SnAgCu

Product Preview (PP),

Advance Information (AI), PD

or Production Data (PD)

2.2 Device Compatibility

The ARM926EJ-S RISC CPU is compatible with other ARM9 CPUs from ARM Holdings plc.

The C64x+ DSP core is code-compatible with the C6000™ DSP platform and supports features of the

C64x DSP family.

2.3 ARM Subsystem

The ARM Subsystem is designed to give the ARM926EJ-S (ARM9) master control of the device. In

general, the ARM is responsible for configuration and control of the device; including the DSP Subsystem,

the VPSS Subsystem, and a majority of the peripherals and external memories.

www.ti.com

The ARM Subsystem includes the following features:

• ARM926EJ-S RISC processor

• ARMv5TEJ (32/16-bit) instruction set

• Little endian

• Co-Processor 15 (CP15)

• MMU

• 16KB Instruction cache

• 8KB Data cache

• Write Buffer

• 16KB Internal RAM (32-bit-wide access)

• 8KB Internal ROM (ARM bootloader for non-EMIFA boot options)

• Embedded Trace Module and Embedded Trace Buffer (ETM/ETB)

• ARM Interrupt controller

• PLL Controller

• Power and Sleep Controller (PSC)

• System Module

12 Device Overview Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 13

TMS320DM6443

www.ti.com

2.3.1 ARM926EJ-S RISC CPU

The ARM Subsystem integrates the ARM926EJ-S processor. The ARM926EJ-S processor is a member of

ARM9 family of general-purpose microprocessors. This processor is targeted at multi-tasking applications

where full memory management, high performance, low die size, and low power are all important. The

ARM926EJ-S processor supports the 32-bit ARM and 16 bit THUMB instruction sets, enabling the user to

trade off between high performance and high code density. Specifically, the ARM926EJ-S processor

supports the ARMv5TEJ instruction set, which includes features for efficient execution of Java byte codes,

providing Java performance similar to Just in Time (JIT) Java interpreter, but without associated code

overhead.

The ARM926EJ-S processor supports the ARM debug architecture and includes logic to assist in both

hardware and software debug. The ARM926EJ-S processor has a Harvard architecture and provides a

complete high performance subsystem, including:

• ARM926EJ -S integer core

• CP15 system control coprocessor

• Memory Management Unit (MMU)

• Separate instruction and data Caches

• Write buffer

• Separate instruction and data Tightly-Coupled Memories (TCMs) [internal RAM] interfaces

• Separate instruction and data AHB bus interfaces

• Embedded Trace Module and Embedded Trace Buffer (ETM/ETB)

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

For more complete details on the ARM9, refer to the ARM926EJ-S Technical Reference Manual, available

at http://www.arm.com.

2.3.2 CP15

The ARM926EJ-S system control coprocessor (CP15) is used to configure and control instruction and

data caches, Tightly-Coupled Memories (TCMs), Memory Management Unit (MMU), and other ARM

subsystem functions. The CP15 registers are programmed using the MRC and MCR ARM instructions,

when the ARM in a privileged mode such as supervisor or system mode.

2.3.3 MMU

The ARM926EJ-S MMU provides virtual memory features required by operating systems such as Linux®,

Windows® CE, Ultron®, ThreadX®, etc. A single set of two level page tables stored in main memory is

used to control the address translation, permission checks and memory region attributes for both data and

instruction accesses. The MMU uses a single unified Translation Lookaside Buffer (TLB) to cache the

information held in the page tables. The MMU features are:

• Standard ARM architecture v4 and v5 MMU mapping sizes, domains and access protection scheme.

• Mapping sizes are:

– 1MB (sections)

– 64KB (large pages)

– 4KB (small pages)

– 1KB (tiny pages)

• Access permissions for large pages and small pages can be specified separately for each quarter of

the page (subpage permissions)

• Hardware page table walks

• Invalidate entire TLB, using CP15 register 8

• Invalidate TLB entry, selected by MVA, using CP15 register 8

• Lockdown of TLB entries, using CP15 register 10

Copyright © 2005–2010, Texas Instruments Incorporated Device Overview 13

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 14

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

2.3.4 Caches and Write Buffer

The size of the Instruction Cache is 16KB, Data cache is 8KB. Additionally, the Caches have the following

features:

• Virtual index, virtual tag, and addressed using the Modified Virtual Address (MVA)

• Four-way set associative, with a cache line length of eight words per line (32-bytes per line) and with

two dirty bits in the Dcache

• Dcache supports write-through and write-back (or copy back) cache operation, selected by memory

region using the C and B bits in the MMU translation tables.

• Critical-word first cache refilling

• Cache lockdown registers enable control over which cache ways are used for allocation on a line fill,

providing a mechanism for both lockdown, and controlling cache corruption

• Dcache stores the Physical Address TAG (PA TAG) corresponding to each Dcache entry in the TAG

RAM for use during the cache line write-backs, in addition to the Virtual Address TAG stored in the

TAG RAM. This means that the MMU is not involved in Dcache write-back operations, removing the

possibility of TLB misses related to the write-back address.

• Cache maintenance operations provide efficient invalidation of, the entire Dcache or Icache, regions of

the Dcache or Icache, and regions of virtual memory.

The write buffer is used for all writes to a noncachable bufferable region, write-through region and write

misses to a write-back region. A separate buffer is incorporated in the Dcache for holding write-back for

cache line evictions or cleaning of dirty cache lines. The main write buffer has 16-word data buffer and a

four-address buffer. The Dcache write-back has eight data word entries and a single address entry.

www.ti.com

2.3.5 Tightly Coupled Memory (TCM)

ARM internal RAM is provided for storing real-time and performance-critical code/data and the Interrupt

Vector table. ARM internal ROM enables non-EMIFA boot options, such as NAND and UART. The RAM

and ROM memories interfaced to the ARM926EJ-S via the tightly coupled memory interface that provides

for separate instruction and data bus connections. Since the ARM TCM does not allow instructions on the

D-TCM bus or data on the I-TCM bus, an arbiter is included so that both data and instructions can be

stored in the internal RAM/ROM. The arbiter also allows accesses to the RAM/ROM from extra-ARM

sources (e.g., EDMA3 or other masters). The ARM926EJ-S has built-in DMA support for direct accesses

to the ARM internal memory from a non-ARM master. Because of the time-critical nature of the TCM link

to the ARM internal memory, all accesses from non-ARM devices are treated as DMA transfers.

Instruction and Data accesses are differentiated via accessing different memory map regions, with the

instruction region from 0x0000 through 0x7FFF and data from 0x8000 through 0xFFFF. The instruction

region at 0x0000 and data region at 0x8000 map to the same physical 16KB TCM RAM. Placing the

instruction region at 0x0000 is necessary to allow the ARM Interrupt Vector table to be placed at 0x0000,

as required by the ARM architecture. The internal 16-KB RAM is split into two physical banks of 8KB

each, which allows simultaneous instruction and data accesses to be accomplished if the code and data

are in separate banks.

The ARM926EJ-S has built in DMA support for direct accesses to the ARM internal memory from a nonARM device. Furthermore, because of the time critical nature of the TCM link to the ARM internal memory,

all accesses from non-ARM devices are treated as DMA transfers.

2.3.6 Advanced High-Performance Bus (AHB)

The ARM Subsystem uses the AHB port of the ARM926EJ-S to connect the ARM to the Config bus and

the external memories. Arbiters are employed to arbitrate access to the separate D-AHB and I-AHB by the

Config Bus and the external memories bus.

14 Device Overview Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 15

TMS320DM6443

www.ti.com

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

2.3.7 Embedded Trace Macrocell (ETM) and Embedded Trace Buffer (ETB)

To support real-time trace, the ARM926EJ-S processor provides an interface to enable connection of an

Embedded Trace Macrocell (ETM). The ARM926ES-J Subsystem in the DM6443 also includes the

Embedded Trace Buffer (ETB). The ETM consists of two parts:

• Trace Port provides real-time trace capability for the ARM9.

• Triggering facilities provide trigger resources, which include address and data comparators, counter,

and sequencers.

The DM6443 trace port is not pinned out and is instead only connected to the Embedded Trace Buffer.

The ETB has a 4KB buffer memory. ETB enabled debug tools are required to read/interpret the captured

trace data.

2.3.8 ARM Memory Mapping

The ARM memory map is shown in Section 2.5, Memory Map Summary, of this document. The ARM has

access to memories shown in the following sections.

2.3.8.1 ARM Internal Memories

The ARM has access to the following ARM internal memories:

• 16KB ARM Internal RAM on TCM interface, logically separated into two 8KB pages to allow

simultaneous access on any given cycle if there are separate accesses for code (I-TCM bus) and data

(D-TCM) to the different memory regions.

• 8KB ARM Internal ROM

2.3.8.2 External Memories

The ARM has access to the following external memories:

• DDR2 Synchronous DRAM

• Asynchronous EMIF / NOR Flash / NAND Flash

• ATA/CF

• Flash card devices:

– MMC/SD with SDIO

– xD

– SmartMedia

2.3.8.3 DSP Memories

The ARM has access to the following DSP memories:

• L2 RAM

• L1P RAM

• L1D RAM

2.3.8.4 ARM-DSP Integration

DM6443 ARM and DSP integration features are as follows:

• DSP visibility from ARM’s memory map, see Section 2.5, Memory Map Summary, for details

• Boot Modes for DSP - see Device Configurations section, Section 3.3.3, DSP Boot, for details

• ARM control of DSP boot / reset - see Device Configurations section, Section 3.3.2, ARM Boot, for

details

• ARM control of DSP isolation and powerdown / powerup - see Section 3, Device Configurations, for

details

• ARM & DSP Interrupts - see Section 6.7.1, ARM CPU Interrupts, and Section 6.7.2, DSP Interrupts, for

details

Copyright © 2005–2010, Texas Instruments Incorporated Device Overview 15

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 16

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

2.3.9 Peripherals

The ARM9 has access to all of the peripherals on the DM6443 device.

2.3.10 PLL Controller (PLLC)

The ARM Subsystem includes the PLL Controller. The PLL Controller contains a set of registers for

configuring DM6443’s two internal PLLs (PLL1 and PLL2). The PLL Controller provides the following

configuration and control:

• PLL Bypass Mode

• Set PLL multiplier parameters

• Set PLL divider parameters

• PLL power down

• Oscillator power down

The PLLs are briefly described in this document in Section 6.6, Clock PLLs. For more detailed information

on the PLLs and PLL Controller register descriptions, see the TMS320DM644x DMSoC ARM Subsystem

Reference Guide (literature number SPRUE14).

2.3.11 Power and Sleep Controller (PSC)

The ARM Subsystem includes the Power and Sleep Controller (PSC). Through register settings

accessible by the ARM9, the PSC provides two levels of power savings: peripheral/module clock gating

and power domain shut-off. Brief details on the PSC are given in Section 6.3, Power Supplies. For more

detailed information and complete register descriptions for the PSC, see the TMS320DM644x DMSoC

ARM Subsystem Reference Guide (literature number SPRUE14).

www.ti.com

2.3.12 ARM Interrupt Controller (AINTC)

The ARM Interrupt Controller (AINTC) accepts device interrupts and maps them to either the ARM’s IRQ

(interrupt request) or FIQ (fast interrupt request). The ARM Interrupt Controller is briefly described in this

document in the Interrupts section. For detailed information on the ARM Interrupt Controller, see the

TMS320DM644x DMSoC ARM Subsystem Reference Guide (literature number SPRUE14)

2.3.13 System Module

The ARM Subsystem includes the System module. The System module consists of a set of registers for

configuring and controlling a variety of system functions. For details and register descriptions for the

System module, see Section 3, Device Configurations, and see the TMS320DM644x DMSoC ARM

Subsystem Reference Guide (literature number SPRUE14).

2.3.14 Power Management

DM6443 has several means of managing power consumption. There is extensive use of clock gating,

which reduces the power used by global device clocks and individual peripheral clocks. Clock

management can be utilized to reduce clock frequencies in order to reduce switching power. For more

details on power management techniques, see Section 3, Device Configurations, Section 6, Peripheral

and Electrical Specifications, and see the TMS320DM644x DMSoC ARM Subsystem Reference Guide

(literature number SPRUE14).

DM6443 gives the programmer full flexibility to use any and all of the previously mentioned capabilities to

customize an optimal power management strategy. Several typical power management scenarios are

described in the following sections.

16 Device Overview Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 17

TMS320DM6443

www.ti.com

2.4 DSP Subsystem

The DSP Subsystem includes the following features:

• C64x+ DSP CPU

• 32KB L1 Program (L1P)/Cache (up to 32KB)

• 80KB L1 Data (L1D)/Cache (up to 32KB)

• 64KB Unified Mapped RAM/Cache (L2)

• Little endian

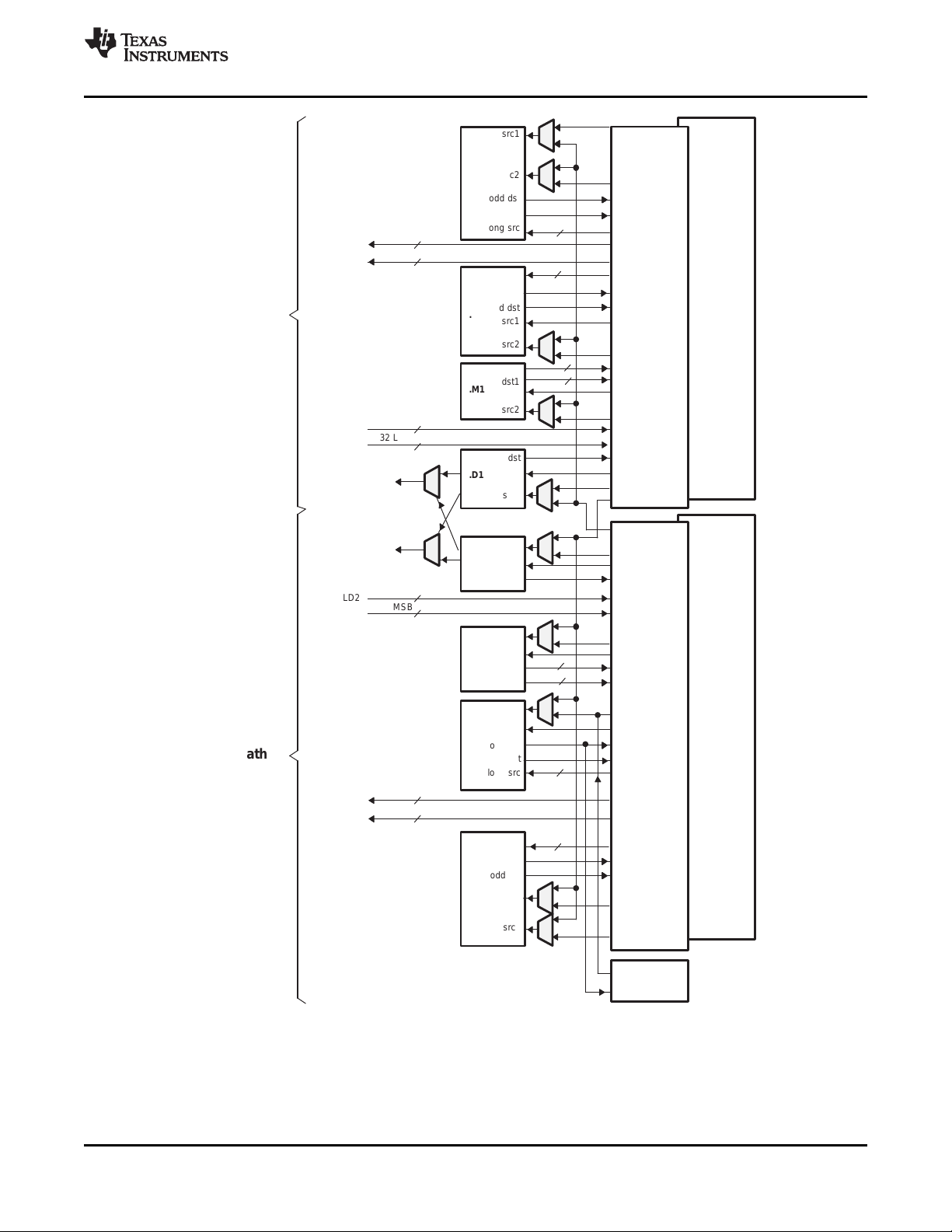

2.4.1 C64x+ DSP CPU Description

The C64x+ Central Processing Unit (CPU) consists of eight functional units, two register files, and two

data paths as shown in Figure 2-1. The two general-purpose register files (A and B) each contain

32 32-bit registers for a total of 64 registers. The general-purpose registers can be used for data or can be

data address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit

data, 40-bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are

stored in register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or

32 MSBs in the next upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one

instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units

perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from

memory to the register file and store results from the register file into memory.

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

The C64x+ CPU extends the performance of the C64x core through enhancements and new features.

Each C64x+ .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, one 16 x

32 bit multiply, two 16 x 16 bit multiplies, two 16 x 32 bit multiplies, two 16 x 16 bit multiplies with

add/subtract capabilities, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add operations, and four

16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There is also support for

Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms such as FFTs and

modems require complex multiplication. The complex multiply (CMPY) instruction takes for 16-bit inputs

and produces a 32-bit real and a 32-bit imaginary output. There are also complex multiplies with rounding

capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values. The

32 x 32 bit multiply instructions provide the extended precision necessary for audio and other

high-precision algorithms on a variety of signed and unsigned 32-bit data types.

The .L or (Arithmetic Logic Unit) now incorporates the ability to do parallel add/subtract operations on a

pair of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data

performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C64x+ core enhances the .S unit in several ways. In the C64x core, dual 16-bit MIN2 and MAX2

comparisons were only available on the .L units. On the C64x+ core they are also available on the .S unit

which increases the performance of algorithms that do searching and sorting. Finally, to increase data

packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit

and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack

instructions return parallel results to output precision including saturation support.

Copyright © 2005–2010, Texas Instruments Incorporated Device Overview 17

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 18

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

Other new features include:

• SPLOOP - A small instruction buffer in the CPU that aids in creation of software pipelining loops where

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

• Compact Instructions - The native instruction size for the C6000 devices is 32 bits. Many common

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C64x+

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

• Instruction Set Enhancement - As noted above, there are new instructions such as 32-bit

multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field

multiplication.

• Exceptions Handling - Intended to aid the programmer in isolating bugs. The C64x+ CPU is able to

detect and respond to exceptions, both from internally detected sources (such as illegal op-codes) and

from system events (such as a watchdog time expiration).

• Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

• Time-Stamp Counter - Primarily targeted for Real-Time Operating System (RTOS) robustness, a

free-running time-stamp counter is implemented in the CPU which is not sensitive to system stalls.

For more details on the C64x+ CPU and its enhancements over the C64x architecture, see the following

documents:

• TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732)

• TMS320C64x Technical Overview (literature number SPRU395)

www.ti.com

18 Device Overview Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 19

src2

src2

.D1

.M1

.S1

.L1

long src

odd dst

src2

src1

src1

src1

src1

even dst

even dst

odd dst

dst1

dst

src2

src2

src2

long src

DA1

ST1b

LD1b

LD1a

ST1a

Data path A

Odd

register

file A

(A1, A3,

A5...A31)

Odd

register

file B

(B1, B3,

B5...B31)

.D2

src1

dst

src2

DA2

LD2a

LD2b

src2

.M2

src1

dst1

.S2

src1

even dst

long src

odd dst

ST2a

ST2b

long src

.L2

even dst

odd dst

src1

Data path B

Control Register

32 MSB

32 LSB

dst2

(A)

32 MSB

32 LSB

2x

1x

32 LSB

32 MSB

32 LSB

32 MSB

dst2

(B)

(B)

(A)

8

8

8

8

32

32

32

32

(C)

(C)

Even

register

file A

(A0, A2,

A4...A30)

Even

register

file B

(B0, B2,

B4...B30)

(D)

(D)

(D)

(D)

A. On .M unit, dst2 is 32 MSB.

B. On .M unit, dst1 is 32 LSB.

C. On C64x CPU .M unit, src2 is 32 bits; on C64x+ CPU .M unit, src2 is 64 bits.

D. On .L and .S units, odd dst connects to odd register files and even dst connects to even register files.

TMS320DM6443

www.ti.com

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

Figure 2-1. TMS320C64x+™ CPU (DSP Core) Data Paths

Copyright © 2005–2010, Texas Instruments Incorporated Device Overview 19

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 20

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

2.4.2 DSP Memory Mapping

The DSP memory map is shown in Section 2.5, Memory Map Summary. Configuration of the control

registers for DDR2, EMIFA, and ARM Internal RAM is supported by the ARM. The DSP has access to

memories shown in the following sections.

2.4.2.1 ARM Internal Memories

The DSP has access to the 16KB ARM Internal RAM on the ARM D-TCM interface (i.e., data only).

2.4.2.2 External Memories

The DSP has access to the following External memories:

• DDR2 Synchronous DRAM

• Asynchronous EMIF / NOR Flash

2.4.2.3 DSP Internal Memories

The DSP has access to the following DSP memories:

• L2 RAM

• L1P RAM

• L1D RAM

2.4.2.4 C64x+ CPU

www.ti.com

The C64x+ core uses a two-level cache-based architecture. The Level 1 Program cache (L1P) is 32 KB

direct mapped cache and the Level 1 Data cache (L1D) is 80 KB 2-way set associated cache. The Level 2

memory/cache (L2) consists of a 64 KB memory space that is shared between program and data space.

L2 memory can be configured as mapped memory, cache, or a combination of both.

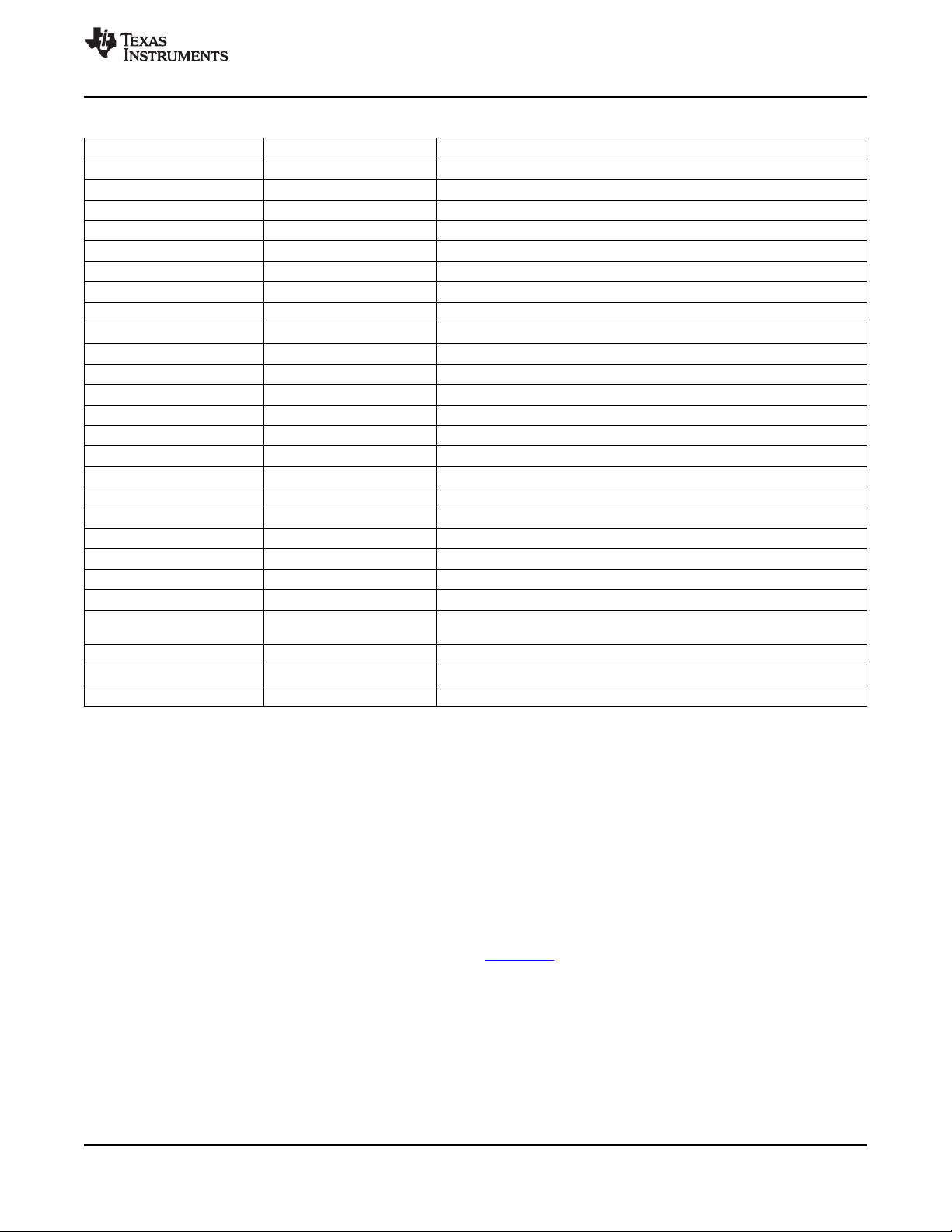

Table 2-2 shows a memory map of the C64x+ CPU cache registers for the device.

Table 2-2. C64x+ Cache Registers

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 0000 L2CFG L2 Cache configuration register

0x0184 0020 L1PCFG L1P Size Cache configuration register

0x0184 0024 L1PCC L1P Freeze Mode Cache configuration register

0x0184 0040 L1DCFG L1D Size Cache configuration register

0x0184 0044 L1DCC L1D Freeze Mode Cache configuration register

0x0184 0048 - 0x0184 0FFC - Reserved

0x0184 1000 EDMAWEIGHT L2 EDMA3 access control register

0x0184 1004 - 0x0184 1FFC - Reserved

0x0184 2000 L2ALLOC0 L2 allocation register 0

0x0184 2004 L2ALLOC1 L2 allocation register 1

0x0184 2008 L2ALLOC2 L2 allocation register 2

0x0184 200C L2ALLOC3 L2 allocation register 3

0x0184 2010 - 0x0184 3FFF - Reserved

0x0184 4000 L2WBAR L2 writeback base address register

0x0184 4004 L2WWC L2 writeback word count register

0x0184 4010 L2WIBAR L2 writeback invalidate base address register

0x0184 4014 L2WIWC L2 writeback invalidate word count register

0x0184 4018 L2IBAR L2 invalidate base address register

0x0184 401C L2IWC L2 invalidate word count register

0x0184 4020 L1PIBAR L1P invalidate base address register

0x0184 4024 L1PIWC L1P invalidate word count register

20 Device Overview Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 21

TMS320DM6443

www.ti.com

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

Table 2-2. C64x+ Cache Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 4030 L1DWIBAR L1D writeback invalidate base address register

0x0184 4034 L1DWIWC L1D writeback invalidate word count register

0x0184 4038 - Reserved

0x0184 4040 L1DWBAR L1D Block Writeback

0x0184 4044 L1DWWC L1D Block Writeback

0x0184 4048 L1DIBAR L1D invalidate base address register

0x0184 404C L1DIWC L1D invalidate word count register

0x0184 4050 - 0x0184 4FFF - Reserved

0x0184 5000 L2WB L2 writeback all register

0x0184 5004 L2WBINV L2 writeback invalidate all register

0x0184 5008 L2INV L2 Global Invalidate without writeback

0x0184 500C - 0x0184 5027 - Reserved

0x0184 5028 L1PINV L1P Global Invalidate

0x0184 502C - 0x0184 5039 - Reserved

0x0184 5040 L1DWB L1D Global Writeback

0x0184 5044 L1DWBINV L1D Global Writeback with Invalidate

0x0184 5048 L1DINV L1D Global Invalidate without writeback

0x0184 8000 - 0x0184 8004 MAR0 - MAR1 Reserved 0x0000 0000 - 0x01FF FFFF

0x0184 8008 - 0x0184 8024 MAR2 - MAR9 Memory Attribute Registers for EMIFA 0x0200 0000 - 0x09FF FFFF

0x0184 8028 - 0x0184 802C MAR10 - MAR11 Reserved 0x0A00 0000 - 0x0BFF FFFF

0x0184 8030 - 0x0184 803C MAR12 - MAR15 Memory Attribute Registers for VLYNQ 0x0C00 0000 - 0x0FFF FFFF

0x0184 8040 - 0x0184 8104 MAR16 - MAR65 Reserved 0x1000 0000 - 0x41FF FFFF

0x0184 8108 - 0x0184 813C MAR66 - MAR79

0x0184 8140- 0x0184 81FC MAR80 - MAR127 Reserved 0x5000 0000 - 0x7FFF FFFF

0x0184 8200 - 0x0184 823C MAR128 - MAR143 Memory Attribute Registers for DDR2 0x8000 0000 - 0x8FFF FFFF

0x0184 8240 - 0x0184 83FC MAR144 - MAR255 Reserved 0x9000 0000 - 0xFFFF FFFF

Memory Attribute Registers for EMIFA/VLYNQ Shadow 0x4200 0000 0x4FFF FFFF

2.4.3 Peripherals

The DSP has controllability for the following peripherals:

• EDMA3

• ASP

• 2 Timers (Timer0 and Timer1) that can each be configured as 1 64-bit or 2 32-bit timers

2.4.4 DSP Interrupt Controller

The DSP Interrupt Controller accepts device interrupts and appropriately maps them to the DSP’s

available interrupts. The DSP Interrupt Controller is briefly described in this document in Section 6.7,

Interrupts. For more detailed on the DSP Interrupt Controller, see the TMS320C64x/C64x+ DSP CPU and

Instruction Set Reference Guide (literature number SPRU732).

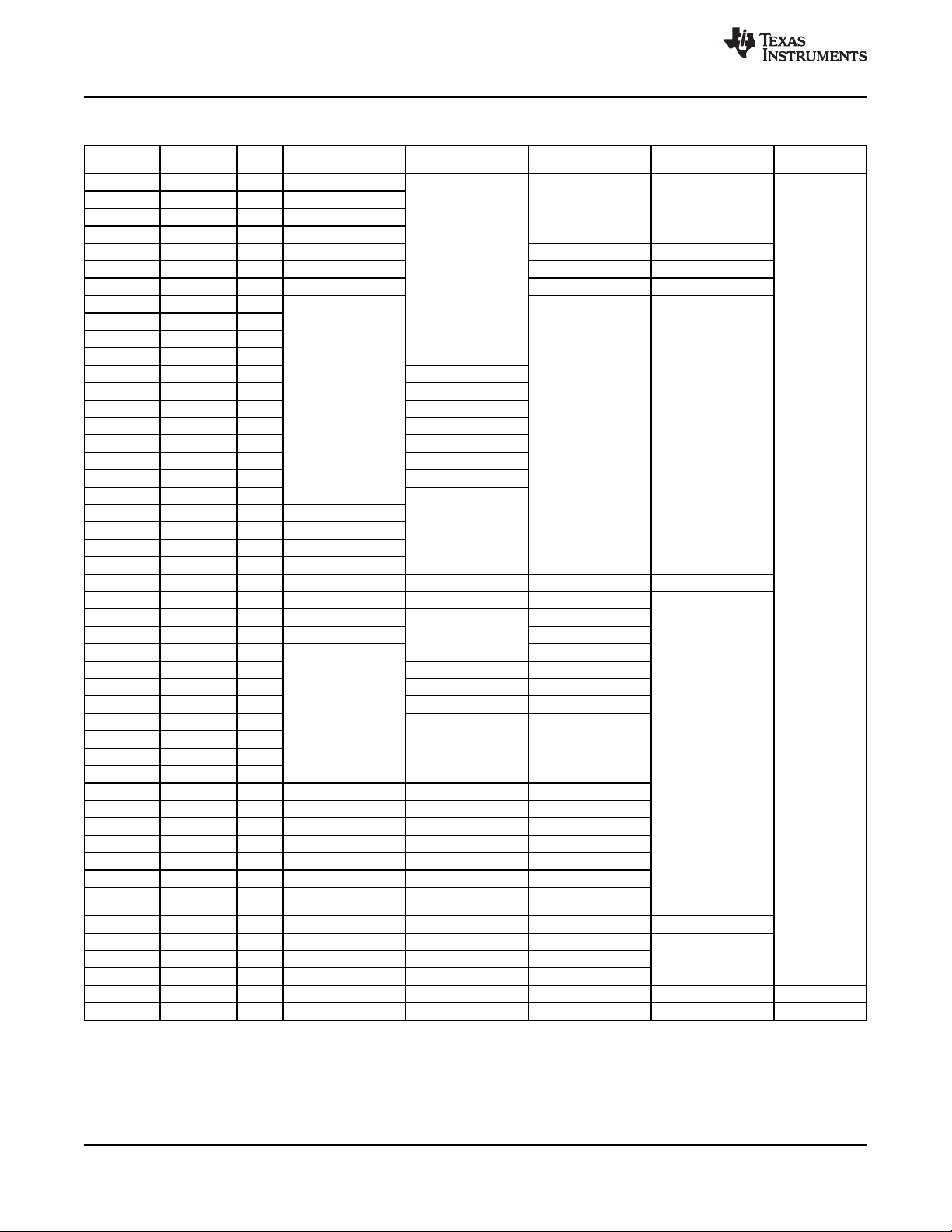

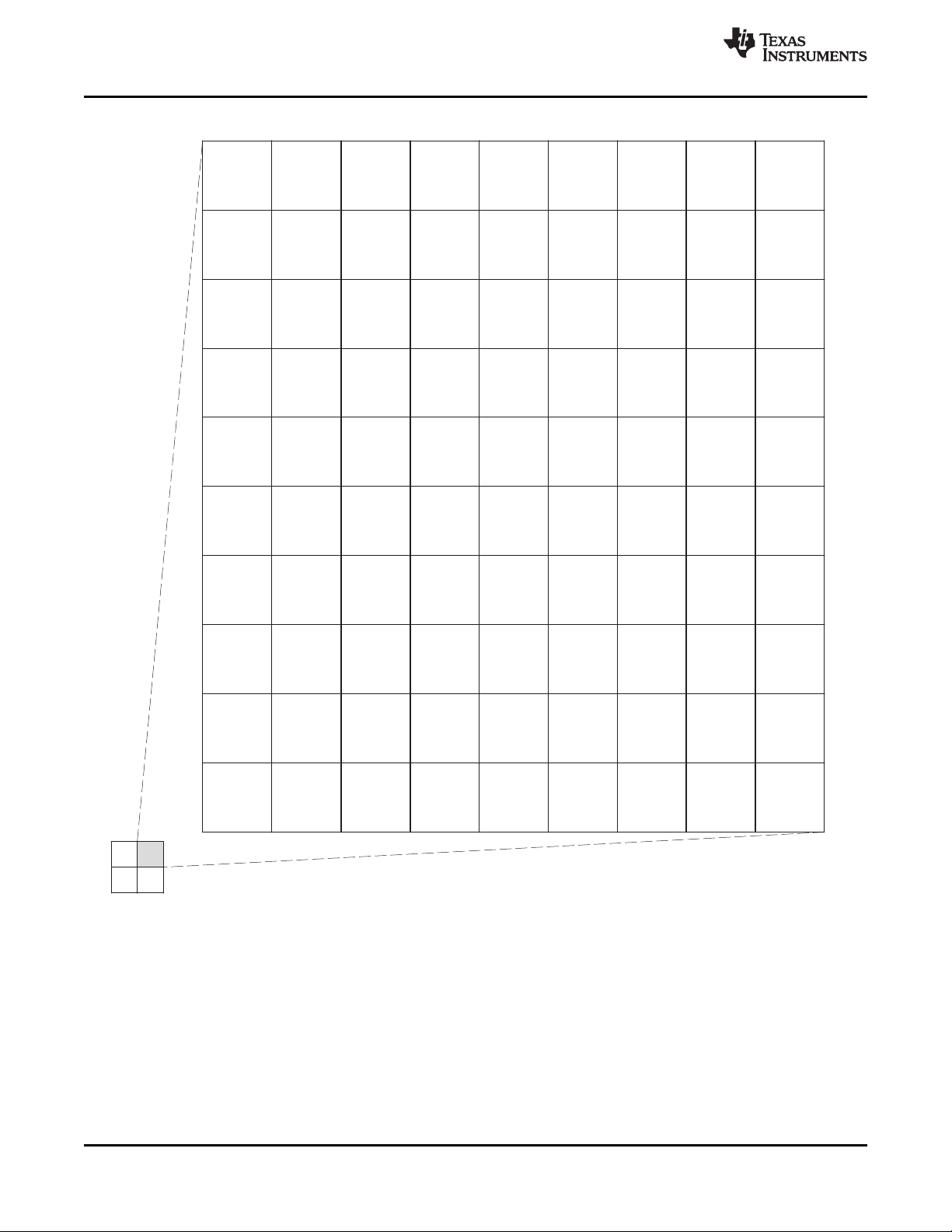

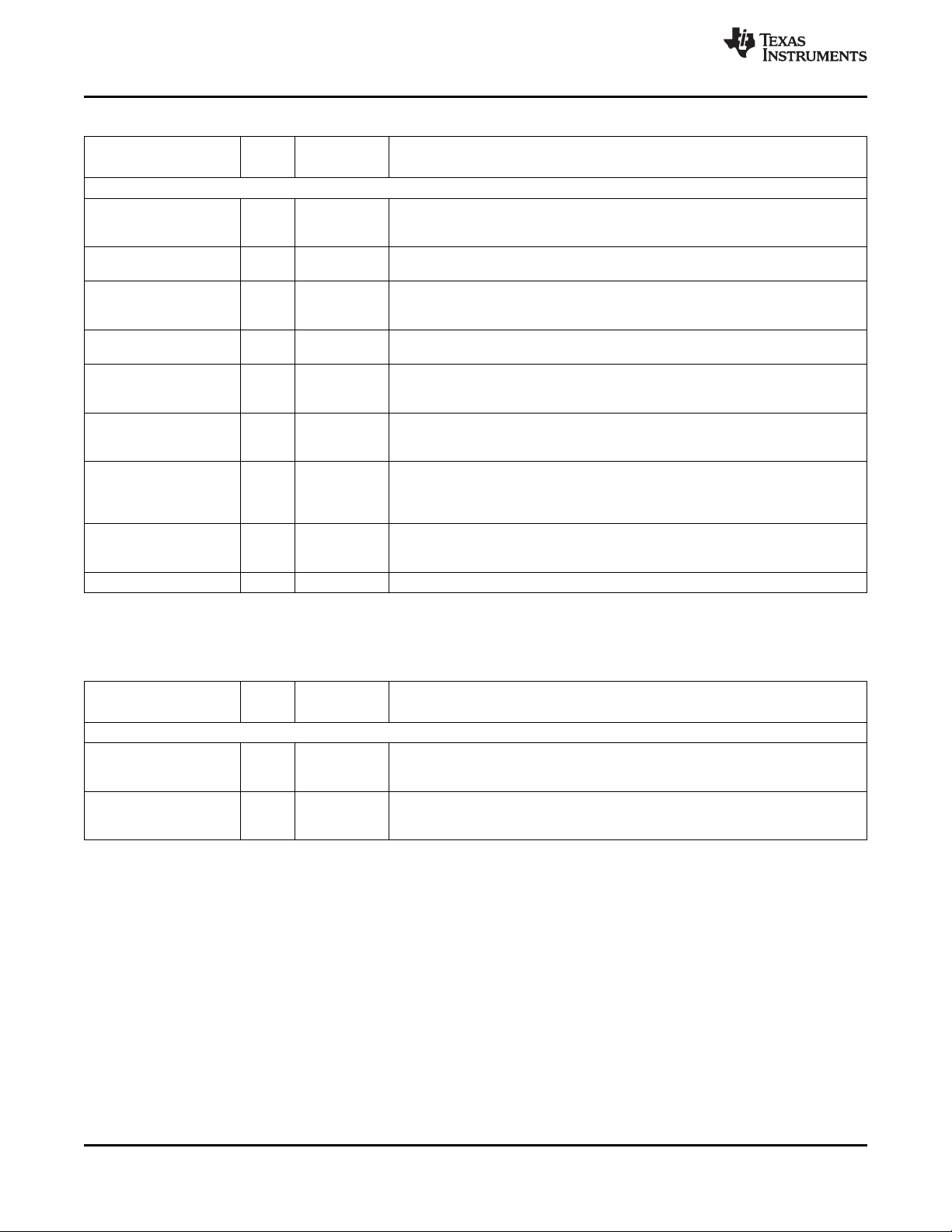

2.5 Memory Map Summary

Table 2-3 shows the memory map address ranges of the device. Table 2-4 depicts the expanded map of

the Configuration Space (0x0180 0000 through 0x0FFF FFFF). The device has multiple on-chip memories

associated with its two processors and various subsystems. To help simplify software development a

unified memory map is used where possible to maintain a consistent view of device resources across all

bus masters.

Copyright © 2005–2010, Texas Instruments Incorporated Device Overview 21

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 22

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

www.ti.com

Table 2-3. Memory Map Summary

START END SIZE EDMA3/

ADDRESS ADDRESS (Bytes) PERIPHERAL

0x0000 0000 0x0000 1FFF 8K ARM RAM0 (Instruction)

0x0000 2000 0x0000 3FFF 8K ARM RAM1 (Instruction)

0x0000 4000 0x0000 5FFF 8K ARM ROM (Instruction)

0x0000 6000 0x0000 7FFF 8K Reserved

0x0000 8000 0x0000 9FFF 8K ARM RAM0 (Data) ARM RAM0 ARM RAM0

0x0000 A000 0x0000 BFFF 8K ARM RAM1 (Data) Reserved ARM RAM1 ARM RAM1

0x0000 C000 0x0000 DFFF 8K ARM ROM (Data) ARM ROM ARM ROM

0x0000 E000 0x0000 FFFF 8K

0x0001 0000 0x000F FFFF 960K

0x0010 0000 0x001F FFFF 1M

0x0020 0000 0x007F FFFF 6M

0x0080 0000 0x0080 FFFF 64K L2 RAM/Cache

0x0081 0000 0x00E0 7FFF 6112K Reserved

0x00E0 8000 0x00E0 FFFF 32K L1P Cache

0x00E1 0000 0x00F0 3FFF 976K Reserved

0x00F0 4000 0x00F0 FFFF 48K L1D RAM

0x00F1 0000 0x00F1 7FFF 32K L1D Cache

0x00F1 8000 0x017F FFFF 9120K Reserved

0x0180 0000 0x01BB FFFF 3840K

0x01BC 0000 0x01BC 0FFF 4K ARM ETB Memory

0x01BC 1000 0x01BC 17FF 2K ARM ETB Registers CFG Space

0x01BC 1800 0x01BC 18FF 256 ARM IceCrusher

0x01BC 1900 0x01BF FFFF 255744 Reserved

0x01C0 0000 0x01FF FFFF 4M CFG Bus Peripherals CFG Bus Peripherals CFG BusPeripherals CFG Bus Peripherals

0x0200 0000 0x09FF FFFF 128M EMIFA (Code andData) EMIFA (Data) EMIFA (Data)

0x0A00 0000 0x0BFF FFFF 32M Reserved Reserved

0x0C00 0000 0x0FFF FFFF 64M VLYNQ (Remote) Reserved VLYNQ (Remote)

0x1000 0000 0x1000 7FFF 32K Reserved

0x1000 8000 0x1000 9FFF 8K ARM RAM0 ARM RAM0

0x1000 A000 0x1000 BFFF 8K ARM RAM1 ARM RAM1

0x1000 C000 0x1000 DFFF 8K ARM ROM ARM ROM

0x1000 E000 0x1000 FFFF 8K

0x1001 0000 0x110F FFFF 17344K

0x1110 0000 0x111F FFFF 1M

0x1120 0000 0x117F FFFF 6M

0x1180 0000 0x1180 FFFF 64K L2 RAM/Cache L2 RAM/Cache L2 RAM/Cache

0x1181 0000 0x11E0 7FFF 6112K Reserved Reserved Reserved

0x11E0 8000 0x11E0 FFFF 32K L1P Cache L1P Cache L1P Cache

0x11E1 0000 0x11F0 3FFF 976K Reserved Reserved Reserved

0x11F0 4000 0x11F0 FFFF 48K L1D RAM L1D RAM L1D RAM

0x11F1 0000 0x11F1 7FFF 32K L1D RAM/Cache L1D RAM/Cache L1D RAM/Cache

0x11F1 8000 0x1FFF FFFF 241M- Reserved Reserved Reserved

0x2000 0000 0x2000 7FFF 32K DDR2 Control Registers DDR2 Control Registers DDR2 Control Registers DDR2 Control Registers

0x2000 8000 0x41FF FFFF 544M-32k Reserved Reserved Reserved

0x4200 0000

0x5000 0000 0x7FFF FFFF 768M Reserved Reserved Reserved

0x8000 0000 0x8FFF FFFF 256M DDR2 DDR2 DDR2 DDR2 DDR2

0x9000 0000 0xFFFF FFFF 1792M Reserved Reserved Reserved Reserved Reserved

(2)

0x4FFF FFFF 224M Reserved EMIFA/VLYNQ Shadow EMIFA/VLYNQ Shadow Reserved

Reserved

Reserved

32K

(1) HPI's access to the configuration bus peripherals is limited to the power and sleep controller registers, PLL1 and PLL2 registers, and

HPI configuration registers.

(2) EMIFA shadow memory started a 0x4200 0000 is physically the same memory as location 0x0200 0000. Memory range 0x200 0000

through 0x09FF FFFF should only be used by C64x+ for data accesses. Memory range 0x4200 0000 through 0x4FFF FFFF can be

used by C64x+ for both code execution and data accesses.

ARM C64x+ HPI VPSS

Reserved Reserved

Reserved Reserved

(1)

Reserved

Reserved Reserved

Reserved

22 Device Overview Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 23

TMS320DM6443

www.ti.com

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

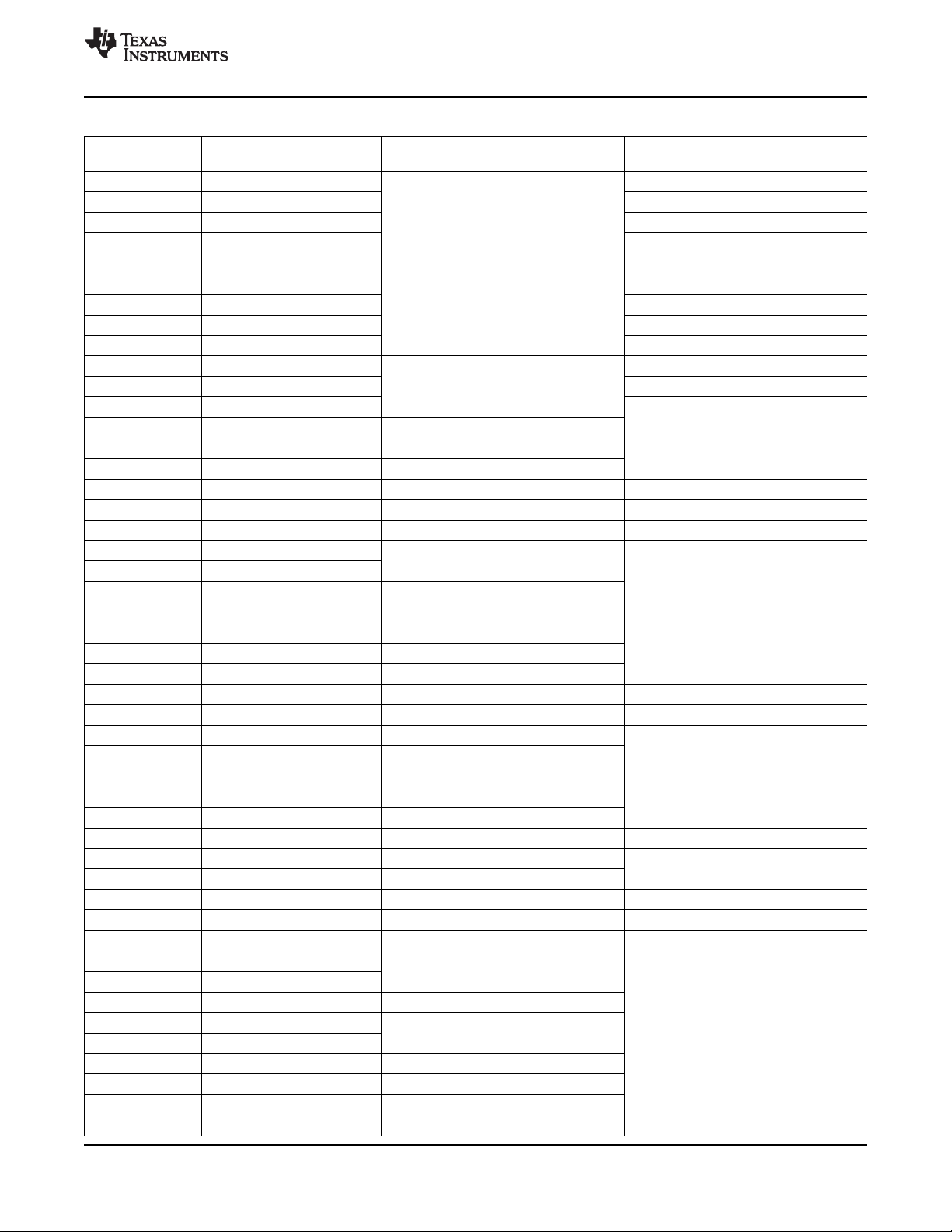

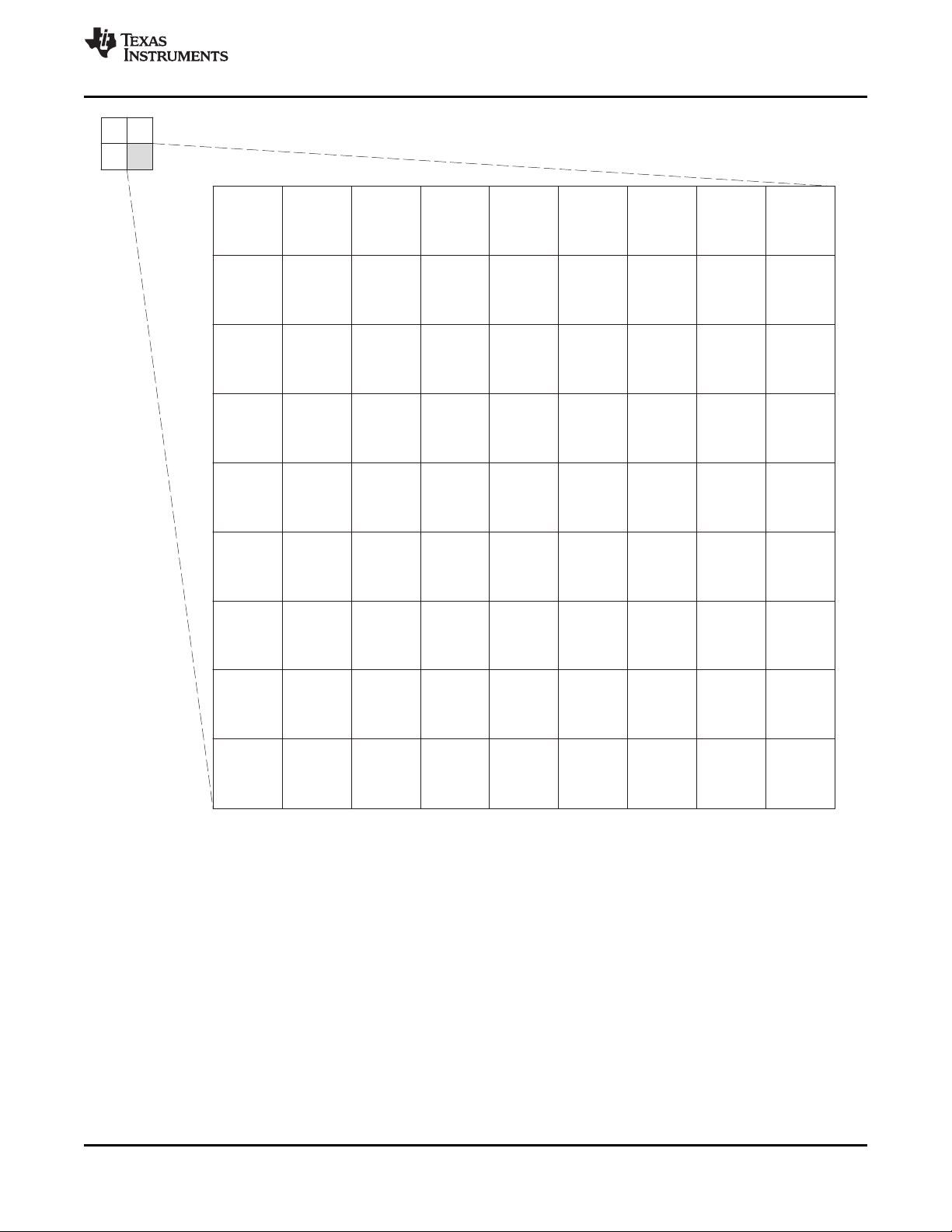

Table 2-4. Configuration Memory Map Summary

START END SIZE ARM/EDMA3 C64x+

ADDRESS ADDRESS (Bytes)

0x0180 0000 0x0180 FFFF 64K C64x+ Interrupt Controller

0x0181 0000 0x0181 0FFF 4K C64x+ Powerdown Controller

0x0181 1000 0x0181 1FFF 4K C64x+ Security ID

0x0181 2000 0x0181 2FFF 4K C64x+ Revision ID

0x0182 0000 0x0182 FFFF 64K Reserved C64x+ EMC

0x0183 0000 0x0183 FFFF 64K Reserved

0x0184 0000 0x0184 FFFF 64K C64x+ Memory System

0x0185 0000 0x0187 FFFF 192K Reserved

0x0188 0000 0x01BB FFFF 3328K Reserved

0x01BC 0000 0x01BC 00FF 256 Reserved

0x01BC 0100 0x01BC 01FF 256 ARM ETB Memory Pin Manager and Trace

0x01BC 0200 0x01BC 0FFF 3.5K

0x01BC 1000 0x01BC 17FF 2K ARM ETB Registers

0x01BC 1800 0x01BC 18FF 256 ARM Ice Crusher

0x01BC 1900 0x01BF FFFF 255744 Reserved

0x01C0 0000 0x01C0 FFFF 64K EDMA3 CC EDMA3 CC

0x01C1 0000 0x01C1 03FF 1K EDMA3 TC0 EDMA3 TC0

0x01C1 0400 0x01C1 07FF 1K EDMA3 TC1 EDMA3 TC1

0x01C1 8800 0x01C1 9FFF 6K

0x01C1 A000 0x01C1 FFFF 24K

0x01C2 0000 0x01C2 03FF 1K UART0

0x01C2 0400 0x01C2 07FF 1K UART1 Reserved

0x01C2 0800 0x01C2 0BFF 1K UART2

0x01C2 0C00 0x01C2 0FFF 1K Reserved

0x01C2 1000 0x01C2 13FF 1K I2C

0x01C2 1400 0x01C2 17FF 1K Timer0 Timer0

0x01C2 1800 0x01C2 1BFF 1K Timer1 Timer1

0x01C2 1C00 0x01C2 1FFF 1K Timer2 (Watchdog)

0x01C2 2000 0x01C2 23FF 1K PWM0

0x01C2 2400 0x01C2 27FF 1K PWM1 Reserved

0x01C2 2800 0x01C2 2BFF 1K PWM2

0x01C2 2C00 0x01C3 FFFF 117K Reserved

0x01C4 0000 0x01C4 07FF 2K System Module System Module

0x01C4 0800 0x01C4 0BFF 1K PLL Controller 1

0x01C4 0C00 0x01C4 0FFF 1K PLL Controller 2

0x01C4 1000 0x01C4 1FFF 4K Power and Sleep Controller Power and Sleep Controller

0x01C4 2000 0x01C4 202F 48 Reserved Reserved

0x01C4 2030 0x01C4 2033 4 DDR2 VTP Reg DDR2 VTP Reg

0x01C4 2034 0x01C4 23FF 1K - 52

0x01C4 2400 0x01C4 7FFF 23K

0x01C4 8000 0x01C4 83FF 1K ARM Interrupt Controller

0x01C4 8400 0x01C5 FFFF 95K

0x01C6 0000 0x01C6 3FFF 16K Reserved

0x01C6 4000 0x01C6 5FFF 8K USB2.0 Registers / RAM

0x01C6 6000 0x01C6 67FF 2K ATA/CF

0x01C6 6800 0x01C6 6FFF 2K SPI

0x01C6 7000 0x01C6 77FF 2K GPIO

Reserved

Reserved

Reserved

Reserved

Reserved

Copyright © 2005–2010, Texas Instruments Incorporated Device Overview 23

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 24

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

Table 2-4. Configuration Memory Map Summary (continued)

START END SIZE ARM/EDMA3 C64x+

ADDRESS ADDRESS (Bytes)

0x01C6 7800 0x01C6 7FFF 2K HPI HPI

0x01C6 8000 0x01C6 FFFF 32K Reserved

0x01C7 0000 0x01C7 3FFF 16K VPSS Registers

0x01C7 4000 0x01C7 FFFF 48K Reserved

0x01C8 0000 0x01C8 0FFF 4K EMAC Control Registers

0x01C8 1000 0x01C8 1FFF 4K EMAC Control Module Registers Reserved

0x01C8 2000 0x01C8 3FFF 8K EMAC Control Module RAM

0x01C8 4000 0x01C8 47FF 2K MDIO Control Registers

0x01C8 4800 0x01C8 4FFF 2K

0x01C8 5000 0x01CB FFFF 236K

0x01CC 0000 0x01CD FFFF 128K

0x01CE 0000 0x01CF FFFF 128K

0x01D0 0000 0x01DF FFFF 1M

0x01E0 0000 0x01E0 0FFF 4K EMIFA Control

0x01E0 1000 0x01E0 1FFF 4K VLYNQ Control Registers

0x01E0 2000 0x01E0 3FFF 8K ASP ASP

0x01E0 4000 0x01E0 FFFF 48K Reserved

0x01E1 0000 0x01E1 FFFF 64K MMC/SD/SDIO

0x01E2 0000 0x01E3 FFFF 128K

0x01E4 0000 0x01FF FFFF 1792K

0x0200 0000 0x03FF FFFF 32M EMIFA Data/Code (CS2) EMIFA Data (CS2)

0x0400 0000 0x05FF FFFF 32M EMIFA Data/Code (CS3) EMIFA Data (CS3)

0x0600 0000 0x07FF FFFF 32M EMIFA Data/Code (CS4) EMIFA Data (CS4)

0x0800 0000 0x09FF FFFF 32M EMIFA Data/Code (CS5) EMIFA Data (CS5)

0x0A00 0000 0x0BFF FFFF 32M Reserved

0x0C00 0000 0x0FFF FFFF 64M VLYNQ (Remote)

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

www.ti.com

24 Device Overview Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 25

W

V

U

T

R

P

N

M

L

K

10987654321

10987654321

DDR_D[1]

DV

DDR2

EM_A[4]/

GPIO27

CLK_OUT0/

GPIO48

MXI/CLKIN

EM_A[5]/

GPIO26

MXV

SS

PLLV

DD18

RSV24

EM_A[6]/

GPIO25

EM_A[8]/

GPIO23

EM_A[7]/

GPIO24

EM_A[13]/

GPIO18

EM_A[10]/

GPIO21

EM_A[15]/

GPIO16/

VLYNQ_TXD3

EM_A[11]/

GPIO20

EM_A[17]/

GPIO14/

VLYNQ_TXD2

EM_A[19]/

GPIO12/

VLYNQ_TXD1

EM_A[20]/

GPIO11/

VLYNQ_RXD0

EM_CS4

/

GPIO9/

VLYNQ_

SCRUN

DDR_

DQM[0]

DDR_D[0]

EM_A[21]/

GPIO10/

VLYNQ_TXD0

EM_A[14]/

GPIO17/

VLYNQ_RXD3

EM_A[9]/

GPIO22

MXV

DD

RESET

V

SS

RSV3

V

SS

CV

DD

DV

DDR2

DV

DDR2

V

SS

V

SS

DDR_A[11]DDR_A[12]DDR_CLK0

DDR_CLK0DDR_D[14]

DV

DDR2

V

SS

V

SS

DDR_D[5]

DDR_D[6]

DDR_D[9]

DV

DD18

EM_A[16]/

GPIO15/

VLYNQ_RXD2

DV

DDR2

DDR_BS[2]

CV

DD

DDR_D[11] DDR_D[15] DDR_CKE DDR_A[8]

V

SS

DV

DDR2

V

SS

V

SS

DV

DDR2

DDR_

DQM[1]

DDR_CAS

DDR_WE DDR_VDDDLL

CV

DDDSP

CV

DD

DDR_DQS[1] DDR_RAS DDR_A[10]

CV

DD

CV

DD

DDR_D[2] DDR_D[3] DDR_D[8] DDR_D[13] DDR_BS[1]

DDR_D[4] DDR_D[12]

V

SS

EM_A[3]/

GPIO28

DV

DD18

CV

DD

DV

DD18

RSV7

MXO V

SS

DV

DD18

V

SS

EM_A[18]/

GPIO13/

VLYNQ_RXD1

V

SS

EM_A[12]/

GPIO19

V

SS

DDR_CS

CV

DDDSP

DDR_DQS[0] DDR_D[10] DDR_BS[0]

EM_CS5

/

GPIO8/

VLYNQ_

CLOCK

RSV6

DDR_D[7]

W

V

U

T

R

P

N

M

L

K

TMS320DM6443

www.ti.com

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

2.6 Pin Assignments

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in

the smallest possible package. Pin multiplexing is controlled using a combination of hardware

configuration at device reset and software programmable register settings. For more information on pin

muxing, see Section 3.5.2, Multiplexed Pin Configurations, of this document.

2.6.1 Pin Map (Bottom View)

Figure 2-2 through Figure 2-5 show the bottom view of the package pin assignments in four quadrants (A,

B, C, and D).

Figure 2-2. Pin Map [Quadrant A]

Copyright © 2005–2010, Texas Instruments Incorporated Device Overview 25

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 26

W

V

U

T

R

P

N

M

L

K

191817161514131211

191817161514131211

DDR_A[9]

V

SS

V

SS

CV

DD

CV

DD

V

SS

CV

DD

V

SS

DV

DDR2

DV

DDR2

DV

DDR2

V

SS

DV

DDR2

DV

DDR2

V

SS

DDR_

VSSDLL

DDR_ZPDDR_ZN

V

SS

V

SS

V

SS

DV

DD18

DV

DD18

RSV11 RSV9

V

DDA_1P8V

UART_TXD2 UART_RXD2

DAC_IOUT_B

RSV4DDR_D[29]DDR_D[27]DDR_D[21]DDR_D[18]

DAC_IOUT_A

RSV19

DAC_RBIAS

DDR_A[3]

DDR_A[4]

DDR_A[0]

V

SS

V

SS

DDR_DQM[2]

DDR_D[26]

RSV16

DDR_D[17] DDR_D[22] DDR_D[24] DDR_D[30]

RSV23

V

SSA_1P8V

UART_CTS2

RSV14

UART_RTS2

DDR_VREF DDR_DQM[3] DDR_D[23] DAC_IOUT_D

RSV22 RSV20

DDR_D[20] DDR_DQS[3] DDR_D[31]

RSV17 RSV10

DDR_A[7] DDR_A[2] DDR_D[19] DDR_D[28]

DDR_A[6] DDR_D[16]

DAC_IOUT_C

CV

DDDSP

V

SS

RSV13

RSV18

DAC_V

REF

DV

DD18

RSV15

RSV12

DV

DDR2

V

DDA_1P1V

DV

DDR2

V

SSA_1P1V

RSV21

DDR_A[1] DDR_DQS[2] DDR_D[25]

V

SS

DDR_A[5]

W

V

U

T

R

P

N

M

L

K

TMS320DM6443

SPRS282G–DECEMBER 2005–REVISED AUGUST 2010

www.ti.com

Figure 2-3. Pin Map [Quadrant B]

26 Device Overview Copyright © 2005–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320DM6443

Page 27

H

G

F

E

D

C

B

A

191817161514131211

191817161514131211

CV

DDDSP

YOUT4/R4/

AEAW4

GPIOV33_1/

TXCLK

GPIOV33_2/

COL

GPIOV33_9/

RXD2

GPIOV33_8/

RXD1

GPIOV33_6/

TXD3

GPIOV33_4/

TXD1

GPIOV33_12/

RXDV

GPIO2/G0

GPIOV33_7/

RXD0

GPIOV33_10/

RXD3

DV

DD33

DV

DD33

DV

DD33

V

SS

V

SS

V

SS

GPIO1

GPIO0/

LCD_OE

GPIO4/R0

GPIOV33_0/

TXEN

GPIO6/B1

VSYNC VPBECLK

M24XI

YOUT3/R3/

AEAW3

VCLK

YOUT7/R7

CLK_OUT1/

TIM_IN/

GPIO49

PWM1/R2/

GPIO46

M24V

DD

CV

DDDSP

GPIO38/R1

DV

DD18

V

SS

USB_R1

COUT5/G2

COUT0/B3/

BTSEL0

YOUT6/R6

YOUT2/G7/

AEAW2

COUT7/G4

YOUT1/G6/

AEAW1

DV

DD18

USB_

V

SSREF

USB_

V

SSA1P2LD0

USB_DP

COUT2/B5/

EM_WIDTH

RSV2

V

SS

USB_V

SS1P8

USB_DM

COUT3/B6/

DSP_BT

COUT6/G3

M24XO

GPIOV33_5/

TXD2

PWM2/

B2/GPIO47

HSYNC

COUT1/B4/