Texas Instruments TMS320C6201, TMS320C6701, TMS320C6711, TMS320C6211, TMS320C6202 Reference Manual

Page 1

TMS320C6000 Peripherals

Reference Guide

Literature Number: SPRU190C

April 1999

Printed on Recycled Paper

Page 2

IMPORTANT NOTICE

T exas Instruments (TI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to obtain the latest

version of relevant information to verify , before placing orders, that the information being relied

on is current.

TI warrants performance of its semiconductor products and related software to the specifications

applicable at the time of sale in accordance with TI’s standard warranty . T esting and other quality

control techniques are utilized to the extent TI deems necessary to support this warranty.

Specific testing of all parameters of each device is not necessarily performed, except those

mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death,

personal injury , or severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES

OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer.

Use of TI products in such applications requires the written approval of an appropriate TI officer .

Questions concerning potential risk applications should be directed to TI through a local SC

sales office.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards should be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein. Nor does TI warrant or

represent that any license, either express or implied, is granted under any patent right, copyright,

mask work right, or other intellectual property right of TI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

Copyright 1999, Texas Instruments Incorporated

Page 3

About This Manual

Preface

Read This First

This reference guide describes the on-chip peripherals of the TMS320C6000

digital signal processors (DSPs). Main topics are the program memory, the data

memory , the direct memory access (DMA) controller, the enhanced DMA controller (EDMA), the host-port interface (HPI), the exansion bus, the external memory

interface (EMIF), the boot configuration, the multichannel buffered serial ports

(McBSPs), the timers, the interrupt selector and external interrupts, and the power-down modes.

The TMS320C62x (’C62x) and the TMS320C67x (’C67x) generations of digital signal processors make up the TMS320C6000 platform of the TMS320

family of digital signal processors. The ’C62x devices are fixed-point DSPs,

and the ’C67x devices are floating-point DSPs. The TMS320C6000 (’C6000)

is the first DSP to use the VelociTI architecture, a high-performance,

advanced VLIW (very long instruction word) architecture. The VelocTI architechure makes the ’C6x an excellent choice for multichannel, multifunction, and

high data rate applications.

Notational Conventions

This document uses the following conventions:

- Program listings, program examples, names are shown in a special

-

. Here is a sample program listing:

font

LDW .D1 *A0,A1

ADD .L1 A1,A2,A3

NOP 3

MPY .M1 A1,A4,A5

Throughout this book MSB means

least significant bit

.

most significant bit,

Contents

and LSB means

iii

Page 4

Notational Conventions / Related Documentation From Texas Instruments

Registers are described throughout this book in register diagrams. Each

diagram shows a rectangle divided into fields that represent the fields of the

register. Each field is labeled with its name inside, its beginning and ending bit

numbers above, and its properties below. A legend explains the notation used

for the properties. For example:

31 25 24 23 22 21 20 18 17 16

FIELDA FIELDB FIELDC R, +1 RW, +0

RW, +0 RC, +x R, +0 R, +1 HRW, +0

Note: R = Readable by the CPU, W = Writeable by the CPU, +x = V alue undefined after reset, +0 = Value is 0 after reset,

+1 = Value is 1 after reset, C = Clearable by the CPU, H = reads/writes performed by the host

Related Documentation From Texas Instruments

The following documents describe the TMS320C6x family and related support

tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please

identify the book by its title and literature number.

TMS320C6000 Technical Brief

introduction to the ’C6000 platform of digital signal processors, development tools, and third-party support.

TMS320C6000 CPU and Instruction Set Reference Guide

number SPRU189) describes the ’C6000 CPU architecture, instruction

set, pipeline, and interrupts for these digital signal processors.

TMS320C6000 Programmer’s Guide

describes ways to optimize C and assembly code for the TMS320C6000

DSPs and includes application program examples.

TMS320C6000 Assembly Language Tools User’s Guide

SPRU186) describes the assembly language tools (assembler, linker,

and other tools used to develop assembly language code), assembler

directives, macros, common object file format, and symbolic debugging

directives for the ’C6000 generation of devices.

TMS320C6000 Optimizing C Compiler User’s Guide

SPRU187) describes the ’C6000 C compiler and the assembly optimizer .

This C compiler accepts ANSI standard C source code and produces assembly language source code for the ’C6000 generation of devices. The

assembly optimizer helps you optimize your assembly code.

TMS320C6x C Source Debugger User’s Guide

SPRU188) tells you how to invoke the ’C6x simulator and emulator

versions of the C source debugger interface. This book discusses

various aspects of the debugger, including command entry, code

execution, data management, breakpoints, profiling, and analysis.

(literature number SPRU197) gives an

(literature

(literature number SPRU198)

(literature number

(literature number

(literature number

iv

Page 5

Related Documents / Trademarks

TMS320C6201, TMS320C6201B Digital Signal Processors Data Sheet

(literature number SPRS051) describes the features of the

TMS320C6201 and TMS320C6201B fixed-point DSPs and provides

pinouts, electrical specifications, and timings for the devices.

Trademarks

TMS320C6202 Digital Signal Processor Data Sheet

(literature number

SPRS072) describes the features of the TMS320C6202 fixed-point DSP

and provides pinouts, electrical specifications, and timings for the device.

TMS320C6701 Digital Signal Processor Data Sheet

(literature number

SPRS067) describes the features of the TMS320C6701 floating-point

DSP and provides pinouts, electrical specifications, and timings for the

device.

TMS320C6211 Digital Signal Processor Data Sheet

(literature number

SPRS073) describes the features of the TMS320C621 1 fixed-point DSP

and provides pinouts, electrical specifications, and timings for the device.

TMS320C6711 Digital Signal Processor Data Sheet

(literature number

SPRS088) describes the features of the TMS320C671 1 fixed-point DSP

and provides pinouts, electrical specifications, and timings for the device.

320 Hotline On-line, VelociTI, and XDS510 are trademarks of Texas

Instruments Incorporated.

PC is a trademark of International Business Machines Corporation.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

SPI is a trademark of Motorola, Inc.

ST-BUS is a trademark of Mitel.

Windows and Windows NT are registered trademarks of Microsoft Corporation.

Read This First

v

Page 6

If You Need Assistance

If You Need Assistance . . .

- World-Wide Web Sites

TI Online http://www.ti.com

Semiconductor Product Information Center (PIC) http://www.ti.com/sc/docs/pic/home.htm

DSP Solutions http://www.ti.com/dsps

320 Hotline On-linet http://www.ti.com/sc/docs/dsps/support.htm

- North America, South America, Central America

Product Information Center (PIC) (972) 644-5580

TI Literature Response Center U.S.A. (800) 477-8924

Software Registration/Upgrades (214) 638-0333 Fax: (214) 638-7742

U.S.A. Factory Repair/Hardware Upgrades (281) 274-2285

U.S. T echnical T raining Organization (972) 644-5580

DSP Hotline Email: dsph@ti.com

DSP Internet BBS via anonymous ftp to ftp://ftp.ti.com/pub/tms320bbs

- Europe, Middle East, Africa

European Product Information Center (EPIC) Hotlines:

Multi-Language Support +33 1 30 70 11 69 Fax: +33 1 30 70 10 32

Email: epic@ti.com

Deutsch +49 8161 80 33 11 or +33 1 30 70 11 68

English +33 1 30 70 11 65

Francais +33 1 30 70 11 64

Italiano +33 1 30 70 11 67

EPIC Modem BBS +33 1 30 70 11 99

European Factory Repair +33 4 93 22 25 40

Europe Customer Training Helpline Fax: +49 81 61 80 40 10

- Asia-Pacific

Literature Response Center +852 2 956 7288 Fax: +852 2 956 2200

Hong Kong DSP Hotline +852 2 956 7268 Fax: +852 2 956 1002

Korea DSP Hotline +82 2 551 2804 Fax: +82 2 551 2828

Korea DSP Modem BBS +82 2 551 2914

Singapore DSP Hotline Fax: +65 390 7179

Taiwan DSP Hotline +886 2 377 1450 Fax: +886 2 377 2718

Taiwan DSP Modem BBS +886 2 376 2592

Taiwan DSP Internet BBS via anonymous ftp to ftp://dsp.ee.tit.edu.tw/pub/TI/

- Japan

Product Information Center +0120-81-0026 (in Japan) Fax: +0120-81-0036 (in Japan)

DSP Hotline +03-3769-8735 or (INTL) 813-3769-8735 Fax: +03-3457-7071 or (INTL) 813-3457-7071

DSP BBS via Nifty-Serve Type “Go TIASP”

- Documentation

When making suggestions or reporting errors in documentation, please include the following information that is on the title

page: the full title of the book, the publication date, and the literature number.

Mail: Texas Instruments Incorporated Email: dsph@ti.com

Technical Documentation Services, MS 702

P.O. Box 1443

Houston, Texas 77251-1443

Note: When calling a Literature Response Center to order documentation, please specify the literature number of the

vi

book.

+03-3457-0972 or (INTL) 813-3457-0972 Fax: +03-3457-1259 or (INTL) 813-3457-1259

Page 7

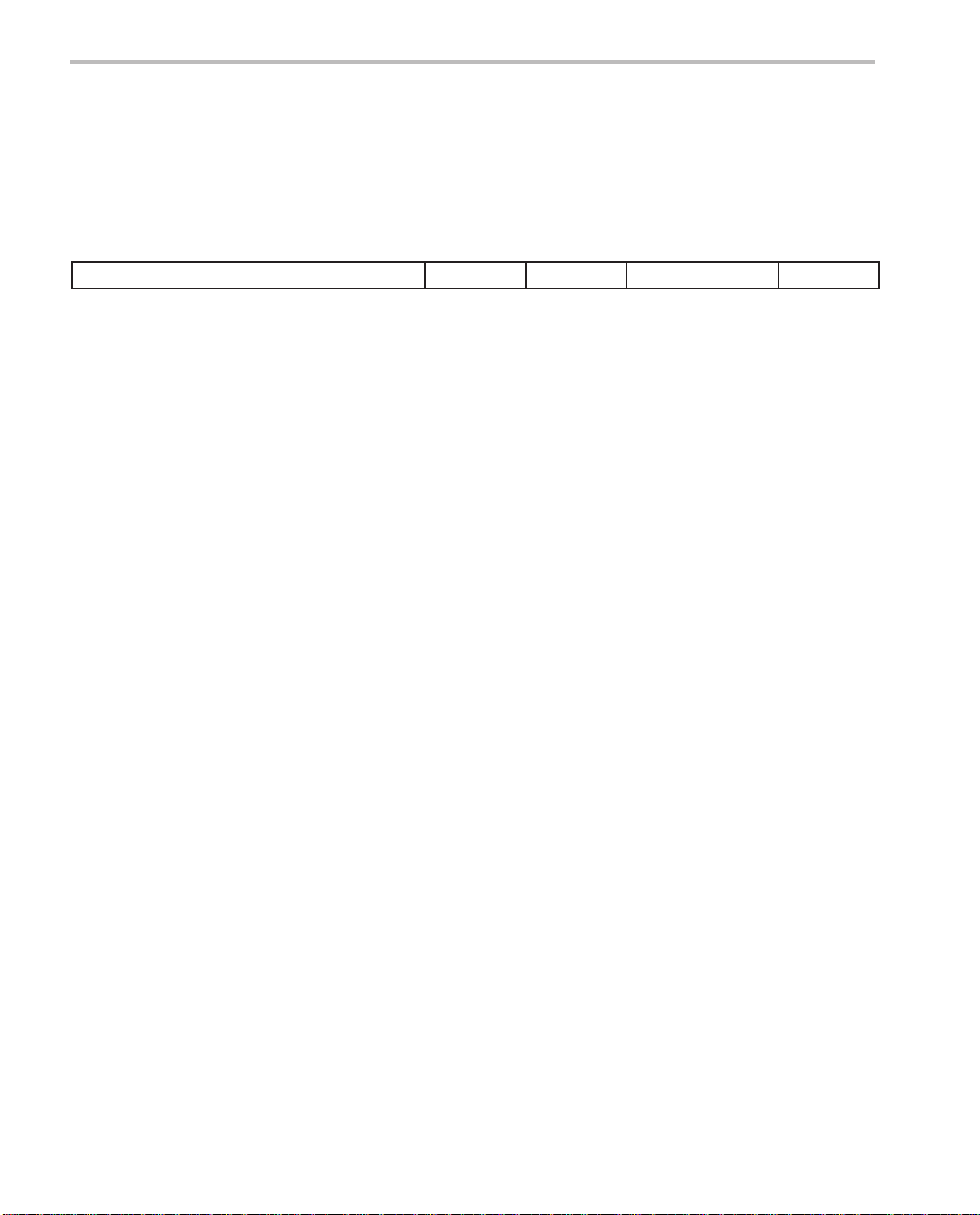

Contents

Contents

1 Introduction 1Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TMS320C6201 and TMS320C6701 DSPs and lists their key features.

1.1 TMS320 Family Overview 1Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.1 History of TMS320 DSPs 1Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.2 Typical Applications for the TMS320 Family 1Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Overview of the TMS320C6000 Platform of DSPs 1Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Features and Options of the TMS320C6000 Devices 1Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Overview of TMS320C6000 Memory 1Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Overview of TMS320C6000 Peripherals 1Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 TMS320C6201/C6701 Program and Data Memory 2Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the program and data memory system for the TMS320C6201/C6701. This includes

program memory organization,cache modes, DMA and peripheral bus operation.

2.1 Program Memory Controller 2Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Internal Program Memory 2Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Internal Program Memory Modes 2Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Cache Architecture 2Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 DMA Controller Access to Program Memory 2Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Data Memory Controller 2Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Data Memory Access 2Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Internal Data Memory Organization 2Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.1 TMS320C6201 Revision 2 2Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2 TMS320C6201 Revision 3 2Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.3 TMS320C6701 2Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.4 Data Alignment 2Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.5 Dual CPU Accesses to Internal Memory 2Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.6 DMA Accesses to Internal Memory 2Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.7 Data Endianness 2Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 Peripheral Bus 2Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.1 Byte and Halfword Access 2 Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.2 CPU Wait States 2Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.3 Arbitration Between the CPU and the DMA Controller 2Ć22. . . . . . . . . . . . . . . . . . .

vii

Page 8

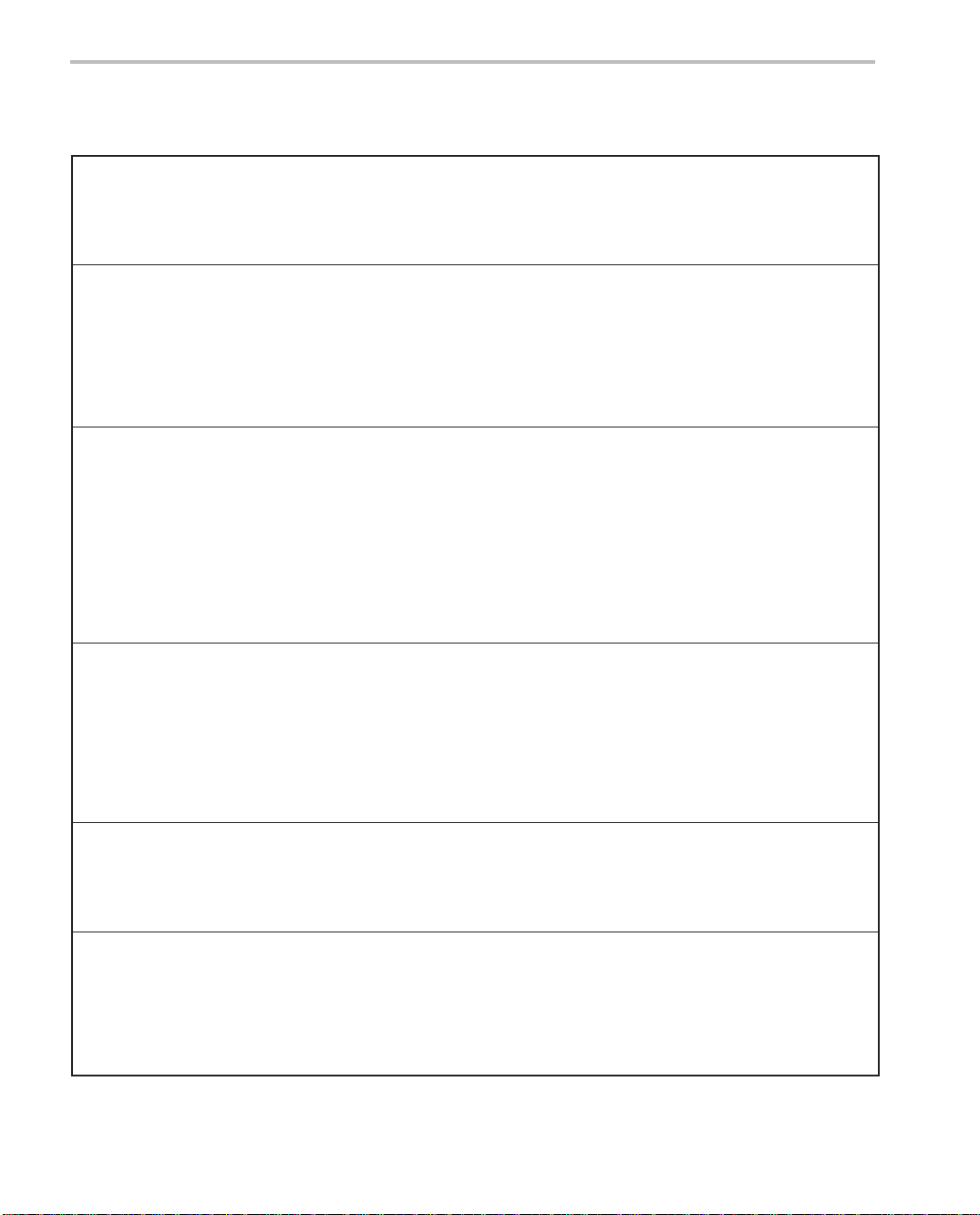

Contents

3 TMS320C6202 Program and Data Memory 3Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the 6202 program memory controller.

3.1 TMS320C6202 Program Memory Controller 3Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Memory Mapped Operation 3Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Cache Operation 3Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Bootload Operation 3Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 TMS320C6202 Data Memory Controller 3Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 TMS320C6211/C671 1

Two-Level Internal Memory 4Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the program and data memory for the TMS320C6211/C6711.

4.1 Overview 4Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Internal Memory Control Registers 4Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 L1P Description 4Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 L1D Description 4Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 L2 Description 4Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.1 L2 Interfaces 4Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.2 L2 Operation 4Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.3 L2 EDMA Service 4Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.4 L2 Invalidation 4Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Direct Memory Access (DMA) Controller 5Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the direct memory access controller operation.

5.1 Overview 5Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 DMA Registers 5Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 DMA Channel Control Registers 5Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Memory Map 5Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Initiating a Block Transfer 5Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.1 DMA Autoinitialization 5Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Transfer Counting 5Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Synchronization: Triggering DMA Transfers 5Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.1 Latching of DMA Channel Event Flags 5Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.2 Automated Event Clearing 5Ć19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.3 Synchronization Control 5Ć19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7 Address Generation 5Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.1 Basic Address Adjustment 5Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.2 Address Adjustment With the Global Index Registers 5Ć23. . . . . . . . . . . . . . . . . . . .

5.7.3 Element Size, Alignment, and Endianness 5Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.4 Using a Frame Index to Reload Addresses 5Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.5 Transferring a Large Single Block 5Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.6 Sorting 5Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 Split-Channel Operation 5Ć28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.1 Split DMA Operation 5Ć28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.2 Split Address Generation 5Ć29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

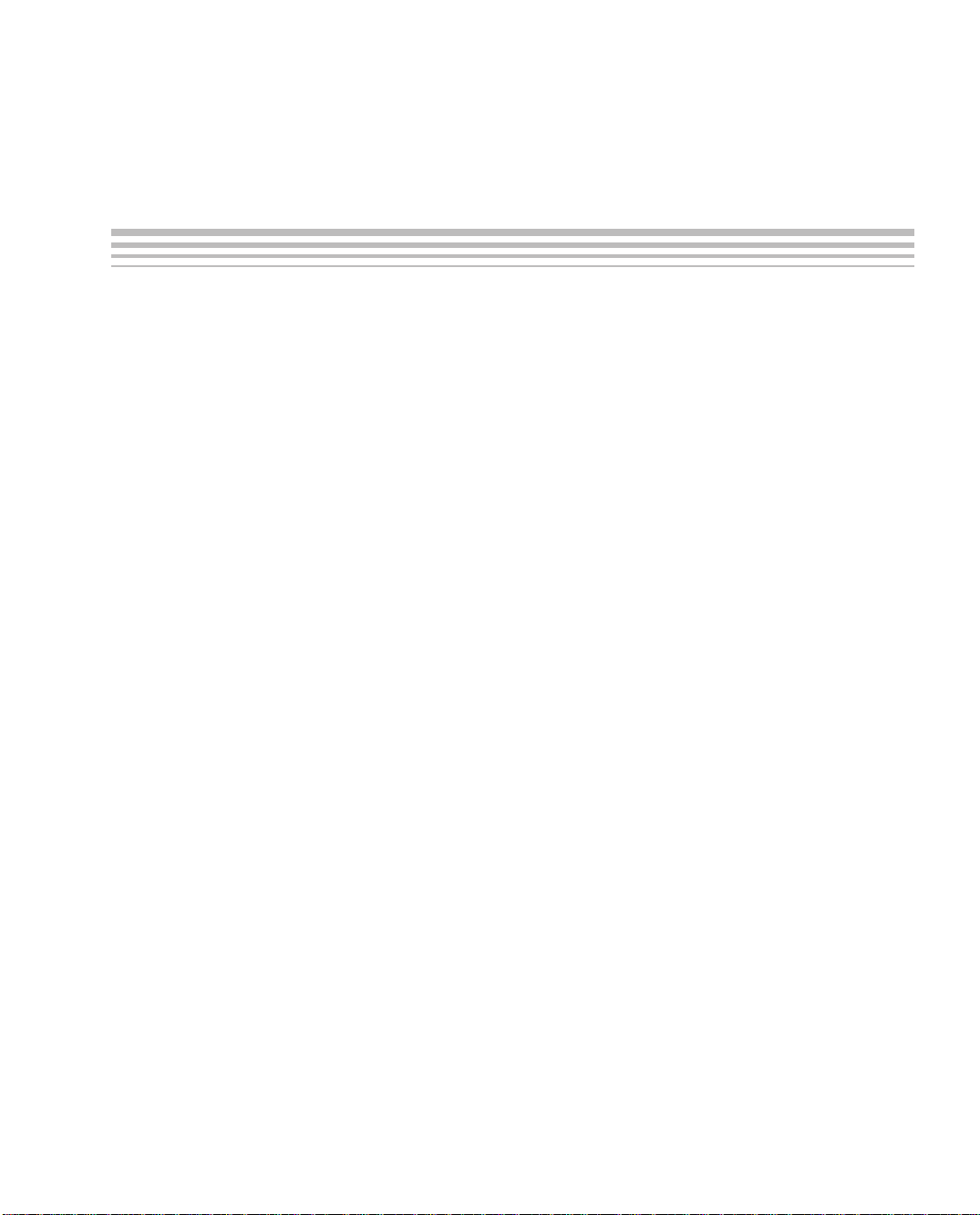

Page 9

Contents

5.9 Resource Arbitration and Priority Configuration 5Ć30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9.1 DMA Auxiliary Control Register and Priority Between Channels 5Ć30. . . . . . . . . . .

5.9.2 Switching Channels 5Ć32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10 DMA Channel Condition Determination 5Ć33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.10.1 Definition of Channel Conditions 5Ć34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.11 DMA Controller Structure 5Ć35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.11.1 Read and Write Buses 5Ć35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.11.2 DMA FIFO 5Ć36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.11.3 Internal Holding Registers 5Ć37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.11.4 DMA Performance 5Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.12 DMA Action Complete Pins 5Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.13 Emulation 5Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 EDMA Controller 6

This chapter describes the new enhanced DMA for the TMS320C6211/6711.

6.1 Overview 6Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 EDMA Terminology 6Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Event Processing and EDMA Control Registers 6Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Event Encoder 6Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5 Parameter RAM (PaRAM) 6Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5.1 EDMA Transfer Parameter Entry 6Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6 EDMA Transfer Parameters 6Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6.1 Options Parameter 6Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6.2 SRC/DST Address 6Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6.3 Element Count 6Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6.4 Frame/Array Count 6Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6.5 Element/(Frame/Array) Index 6Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6.6 Element Count Reload 6Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6.7 Link Address 6Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.7 Initiating an EDMA Transfer 6Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.7.1 Synchronization of EDMA Transfers 6Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.8 Types of EDMA Transfers 6Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.8.1 Non-2Dimensional Transfers 6Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.8.2 2-Dimensional Transfers 6Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.9 Linking EDMA Transfers 6Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.10 Element Size and Alignment 6Ć27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.11 Element and Frame/Array Count Updates 6Ć28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.11.1 Element Count Reload (ECRLD) 6Ć28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.12 Src/Dst Address Updates 6Ć29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.13 EDMA Interrupt Generation 6Ć32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.13.1 EDMA Interrupt Servicing by the CPU 6Ć34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.13.2 Chaining EDMA Channels by an Event 6Ć34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.14 Resource Arbitration and Priority Processing 6Ć36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.15 EDMA Performance 6Ć37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

ix

Page 10

Contents

6.16 Quick DMA (QDMA) 6Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.16.1 QDMA Registers 6Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.16.2 QDMA Register Access 6Ć40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.16.3 Pseudo Mappings 6 Ć40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.16.4 QDMA Performance 6Ć40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.16.5 QDMA Stalls and Priority 6Ć41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

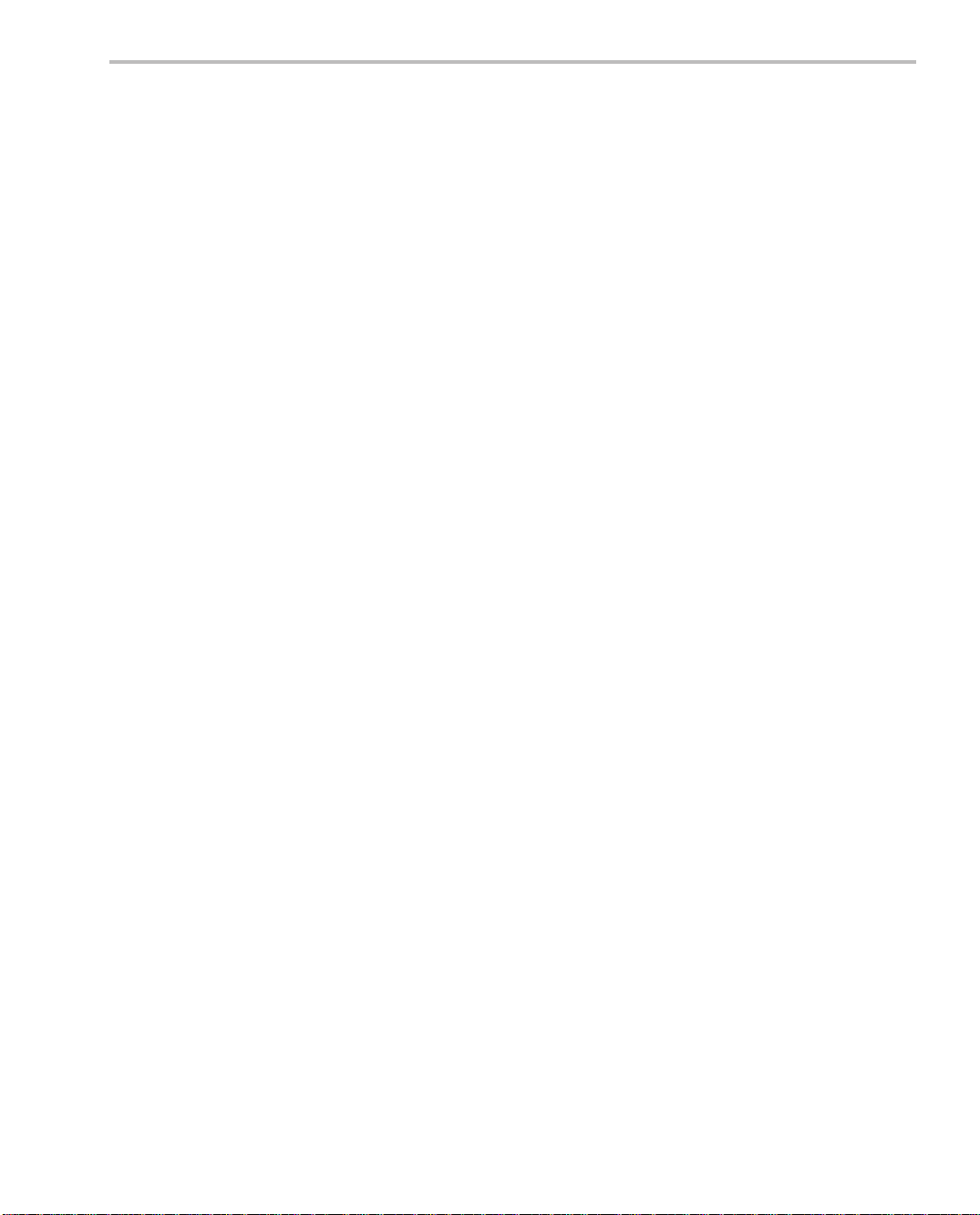

7 Host-Port Interface 7Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the host-port interface (HPI) used to access ’C6201 and ’C6701 memory-map space

by external processors.

7.1 Overview 7Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 HPI Signal Descriptions 7Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.1 Data Bus: HD[15:0] 7Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.2 Access Control Select: HCNTL[1:0] 7Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.3 Halfword Identification Select: HHWIL 7Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.4 Byte Enables: HBE[1:0] 7Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.5 Read/Write Select: HR/W 7Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.6 Ready: HRDY

7.2.7 Strobes: HCS

, HDS1, HDS2 7Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.8 Address Strobe Input: HAS

7.2.9 Interrupt to Host: HINT 7Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.10 HPI Bus Access 7Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 HPI Registers 7Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3.1 HPI Control Register (HPIC) 7Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3.2 Software Handshaking Using HRDY and FETCH 7Ć17. . . . . . . . . . . . . . . . . . . . . . .

7.3.3 Host Device Using DSPINT to Interrupt the CPU 7Ć18. . . . . . . . . . . . . . . . . . . . . . .

7.3.4 CPU Using HINT to Interrupt the Host 7Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 Host Access Sequences 7Ć19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.1 Host Initialization of HPIC and HPIA 7Ć19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.2 HPID Read Access Without Autoincrement 7Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.3 HPID Read Access With Autoincrement 7Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.4 Host Data Write Access Without Autoincrement 7Ć23. . . . . . . . . . . . . . . . . . . . . . . .

7.4.5 HPID Write Access With Autoincrement 7Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.6 Single Halfword Cycles 7Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5 Memory Access Through the HPI During Reset 7Ć27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 Expansion Bus 8Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the expansion bus used by CPU to access off-chip peripherals, FIFOs and PCI

interface chips.

8.1 Overview 8Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2 Expansion Bus Signals 8Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3 Expansion Bus Registers 8Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3.1 Expansion Bus Host Port Registers 8Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3.2 Expansion Bus Global Control Register 8Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

x

Page 11

Contents

8.3.3 XCE Space Control Registers 8Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4 Expansion Bus I/O Port Operation 8Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4.1 Asynchronous Mode 8Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4.2 Synch FIFO Modes 8Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4.3 DMA Transfer Examples 8Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5 Expansion Bus Host Port Operation 8Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5.1 Expansion Bus Host Port Registers Description 8Ć23. . . . . . . . . . . . . . . . . . . . . . . .

8.5.2 Synchronous Host Port Mode 8Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5.3 Asynchronous Host Port Mode 8Ć41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.6 Expansion Bus Arbitration 8Ć44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.6.1 Internal Bus Arbiter Enabled 8Ć44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.6.2 Internal Bus Arbiter Disabled 8Ć45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.6.3 Expansion Bus Requestor Priority 8Ć48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.7 Boot Configuration Control via Expansion Bus 8Ć49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9 External Memory Interface 9

Describes the external memory interface (EMIF) that the CPU uses to access off-chip memory .

9.1 Overview 9Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2 Resetting the EMIF 9Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3 EMIF Registers 9Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.1 Global Control Register 9Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.2 EMIF CE Space Control Registers 9Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.3 EMIF SDRAM Control Register 9Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.4 EMIF SDRAM Timing Register 9Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.5 TMS320C6211/C6711 SDRAM Extension Register 9Ć18. . . . . . . . . . . . . . . . . . . . .

9.4 SDRAM Interface 9Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.1 SDRAM Initialization 9Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.2 Monitoring Page Boundaries 9Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.3 SDRAM Refresh 9Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.4 Mode Register Set 9Ć28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.5 Address Shift 9Ć32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.6 Timing Requirements 9Ć34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.7 SDRAM Deactivation 9Ć35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.8 SDRAM Read 9Ć37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.9 SDRAM Write 9Ć39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.4.10 TMS320C6211/C6711 Seamless Data Access 9Ć41. . . . . . . . . . . . . . . . . . . . . . . . .

9.5 SBSRAM Interface 9Ć43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5.1 SBSRAM Reads 9Ć45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5.2 SBSRAM Writes 9 Ć47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6 Asynchronous Interface 9Ć49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.1 TMS320C6201/C6202/C6701 ROM Modes 9Ć52. . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.2 Programmable ASRAM Parameters 9Ć53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.3 Asynchronous Reads 9Ć54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.4 Asynchronous Writes 9Ć56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xi

Page 12

Contents

9.6.5 Ready Input 9Ć57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.7 Hold Interface 9 Ć60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.8 Memory Request Priority 9Ć61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.8.1 TMS320C6201/C6202/C6701 Memory Request Priority 9Ć61. . . . . . . . . . . . . . . . .

9.8.2 TMS320C6211/C6711 Memory Request Priority 9Ć62. . . . . . . . . . . . . . . . . . . . . . . .

9.9 Boundary Conditions When Writing to EMIF Registers 9Ć63. . . . . . . . . . . . . . . . . . . . . . . . . .

9.10 Clock Output Enabling 9Ć64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.11 Emulation Halt Operation 9Ć64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.12 Power Down 9Ć64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 Boot Modes and Configuration 10

Describes the boot modes and associated memory maps.

10.1 Overview 10Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2 Device Reset 10Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3 Boot Configuration 10Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.1 Memory Map 10Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.2 Memory at Reset Address 10Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.3 Boot Processes 10Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4 Device Configuration 10Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.1 Input Clock Mode 10Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.2 Endian Mode 10Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4.3 TMS320C6202 Expansion Bus 10Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11 Multichannel Buffered Serial Ports 11

Describes the features and operation of the two multichannel buffered serial ports.

11.1 Features 11Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2 McBSP Interface Signals and Registers 1 1 Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.1 Serial Port Configuration 11Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.2 Receive and Transmit Control Registers: RCR and XCR 11Ć14. . . . . . . . . . . . . . . .

11.3 Data Transmission and Reception 11Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.1 Resetting the Serial Port: (R/X

11.3.2 Determining Ready Status 11Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.3 CPU Interrupts: (R/X)INT 11Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.4 Frame and Clock Configuration 11Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.5 McBSP Standard Operation 11Ć33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.6 Frame Synchronization Ignore 11Ć36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.7 Serial Port Exception Conditions 11Ć41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.8 Receive Data Justification and Sign Extension: RJUST 11Ć49. . . . . . . . . . . . . . . . .

1 1.3.9 32-Bit Bit Reversal: (R/X)WDREVRS 11Ć49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1.4 µ-LAW/A-LAW Companding Hardware Operation 11Ć50. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.4.1 Companding Internal Data 11Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5 Programmable Clock and Framing 11Ć53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.5.1 Sample Rate Generator Clocking and Framing 11Ć54. . . . . . . . . . . . . . . . . . . . . . . .

11.5.2 Data Clock Generation 11Ć57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

)RST, GRST , and RESET 11Ć18. . . . . . . . . . . . . . . .

Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xii

Page 13

Contents

11.5.3 Frame Sync Signal Generation 11Ć61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1.5.4 Clocking Examples 11Ć65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6 Multichannel Selection Operation 11Ć68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.1 Multichannel Operation Control Registers 11Ć68. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.2 Enabling Multichannel Selection 1 1Ć71. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.3 Enabling and Masking of Channels 1 1 Ć71. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1.6.4 DX Enabler: DXENA 1 1Ć78. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1.7 SPI Protocol: CLKSTP 11Ć80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.7.1 McBSP Operation as the SPI Master 11Ć84. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.7.2 McBSP Operation as the SPI Slave 11Ć85. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.7.3 McBSP Initialization for SPI Mode 11Ć86. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.8 McBSP Pins as General-Purpose I/O 11Ć87. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12 Timers 12

Describes the 32-bit timers.

12.1 Overview 12Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2 Timer Registers 12Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.1 T imer Control Register 12Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.2 T imer Period Register 12Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.3 T imer Counter Register 12Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3 Resetting the T imers and Enabling Counting: GO and HLD

12.4 Timer Counting 12Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.5 Timer Clock Source Selection: CLKSRC 12Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.6 Timer Pulse Generation 12Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.7 Boundary Conditions in the Control Registers 12Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.8 Timer Interrupts 12Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.9 Emulation Operation 12Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13 Interrupt Selector and External Interrupts 13

12Ć7. . . . . . . . . . . . . . . . . . . . .

Describes the interrupt selector external interrupt operation.

13.1 Available Interrupt Sources 13Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2 External Interrupt Signal Timing 13Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3 Interrupt Selector Registers 13Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3.1 External Interrupt Polarity Register 13Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3.2 Interrupt Multiplexer Register 13Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.4 Configuring the Interrupt Selector 13Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14 Power-Down Logic 14

Describes the power-down modes.

14.1 Overview 14Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2 Triggering, Wake-Up, and Effects 14Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.3 Additional Power-Saving Modes for the TMS320C6202 14Ć6. . . . . . . . . . . . . . . . . . . . . . . . .

Contents

Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiii

Page 14

Contents

15 Designing for JTAG Emulation 15Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the JTAG emulator cable. Tells you how to construct a 14-pin connector on your

target system and how to connect the target sysem to the emulator.

15.1 Designing Your Target System’s Emulator Connector (14-Pin Header) 15Ć2. . . . . . . . . . . .

15.2 Bus Protocol 15Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.3 IEEE 1149.1 Standard 15Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.4 JTAG Emulator Cable Pod Logic 15Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.5 JTAG Emulator Cable Pod Signal Timing 15Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.6 Emulation Timing Calculations 15Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7 Connections Between the Emulator and the Target System 15Ć8. . . . . . . . . . . . . . . . . . . . .

15.7.1 Buffering Signals 15Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7.2 Using a Target-System Clock 15Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.7.3 Configuring Multiple Processors 15Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.8 Mechanical Dimensions for the 14-Pin Emulator Connector 15Ć12. . . . . . . . . . . . . . . . . . . .

15.9 Emulation Design Considerations 15Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.9.1 Using Scan Path Linkers 15Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.9.2 Emulation T iming Calculations for SPL 15Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.9.3 Using Emulation Pins 15Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.9.4 Performing Diagnostic Applications 15Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiv

Page 15

Figures

Figures

1–1 TMS320C6201/C6202/C6701 Block Diagram 1Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 TMS320C6211/C6711 Block Diagram 1

2–1 TMS320C6201/C6701 Program Memory Controller in the Block Diagram 2Ć2. . . . . . . . . . . . .

2–2 Logical Mapping of Cache Address 2Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 TMS320C6x Block Diagram 2

2–4 Data Memory Controller Interconnect to Other Banks

(TMS320C6201 Revision 2) 2Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Data Memory Controller Interconnect to Other Banks

(TMS320C6201 Revision 3) 2Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Data Memory Controller Interconnect to Other Blocks (TMS320C6701) 2

2–7 Conflicting Internal Memory Accesses to the Same Block

(TMS320C6201 Revisions 2 and 3) 2Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Conflicting Internal Memory Accesses to the Same Block (TMS320C6701) 2Ć17. . . . . . . . . .

3–1 TMS320C6202 Program Memory Controller Block Diagram 3

3–2 TMS320C6202 Data Memory Controller Block Diagram 3Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 TMS320C6211/C6711 Block Diagram 4

4–2 TMS320C6211 Internal Memory Block Diagram 4Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 TMS320C6711 Internal Memory Block Diagram 4Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 L1P Address Allocation 4

4–5 L1P Direct Mapped Cache Diagram 4Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 L1P Flush Base Address Register Fields (L1PFBAR) 4Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 L1P Flush Word Count Register Fields (L1PFWC) 4

4–8 L1D Address Allocation 4Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–9 L1D 2–Way Set Associative Cache Diagram 4

4–10 L1D Flush Base Address Register Fields (L1DFBAR) 4Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–11 L1D Flush Word Count Register Fields (L1DFWC) 4Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 Cache Configuration Register Fields (CCFG) 4

4–13 L2 Memory Configuration 4Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–14 L2 Cache Data Request Flow Chart 4Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–15 L2 CE Space Allocation Register Fields 4

4–16 L2 Flush Register Fields (L2FLUSH) 4Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–17 L2 Clean Register Fields (L2CLEAN) 4Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–18 L2 Flush Base Address Register Fields (L2FBAR) 4

4–19 L2 Flush Word Count Register Fields (L2FWC) 4Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–20 L2 Clean Base Address Register Fields (L2CBAR) 4

4–21 L2 Clean Word Count Register Fields (L2CWC) 4Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć14. . . . . . . . . . . . .

Ć3. . . . . . . . . . . . . . . . . . . . . . . .

Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xv

Page 16

Figures

5–1 DMA Controller Interconnect to TMS320C6201/C6202/C6701

Memory-Mapped Modules 5Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 DMA Channel Primary Control Register 5Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 DMA Channel Secondary Control Register 5Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 TMS320C6202 Secondary Control Register 5Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 DMA Channel Transfer Counter Register 5Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 DMA Global Count Reload Register Used As Transfer Counter Reload 5Ć16. . . . . . . . . . . . . .

5–7 Synchronization Flags 5Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 DMA Channel Source Address Register 5Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 DMA Channel Destination Address Register 5Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 DMA Global Index Register 5Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 DMA Global Address Register Used for Split Address 5Ć29. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 DMA Auxiliary Control Register 5Ć31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–13 Generation of DMA Interrupt for Channel x From Conditions 5Ć33. . . . . . . . . . . . . . . . . . . . . . .

5–14 DMA Controller Data Bus Block Diagram 5 Ć35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 TMS320C6211/C6711 Block Diagram 6Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 EDMA Controller 6Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 Event Register (ER) 6 Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Event Enable Register (EER) 6Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 Event Clear Register (ECR) 6Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 Event Set Register (ESR) 6Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–7 Parameter Storage for an EDMA Event 6Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–8 Options Bit-Fields 6Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–9 Non-2D R/W Sync EDMA Transfer Without Frame Sync 6Ć21. . . . . . . . . . . . . . . . . . . . . . . . . .

6–10 Non-2D EDMA Transfer With Frame Sync 6 Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–11 Read/Write Synchronized 2-D Transfer (No Frame Sync) 6Ć23. . . . . . . . . . . . . . . . . . . . . . . . . .

6–12 Frame Synchronized 2-D Transfer 6Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–13 Linked EDMA Transfer 6Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–14 Channel Interrupt Pending Register (CIPR) 6Ć32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–15 Channel Interrupt Enable Register (CIER) 6Ć32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–16 Channel Chain Enable Register (CCER) 6Ć35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–17 Priority Queue Status Register(PQSR) 6Ć37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–18 QDMA Memory-Mapped Registers 6Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–19 QDMA Pseudo Registers 6Ć39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–20 QDMA Options Register (QDMA_OPT, QDMA_S_OPT) 6Ć39. . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 TMS320C6201/C6701 Block Diagram 7Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 TMS320C6211/C6711 Block Diagram 7Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 HPI Block Diagram 7Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 HPI Block Diagram of TMS320C6211/C6711 7Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 Select Input Logic 7Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–6 HPI Read Timing (HAS Not Used, Tied High) 7Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–7 HPI Read Timing (HAS Used) 7Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–8 HPI Write Timing (HAS Not Used, Tied High) 7Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–9 HPI Write Timing (HAS Used) 7Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xvi

Page 17

Figures

7–10 HPIC Register 7Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–1 Expansion Bus Block Diagram 8Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–2 The Expansion Bus Interface in the TMS320C6202 Block Diagram 8

8–3 Expansion Bus Global Control Register 8Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–4 Expansion Bus XCE(0/1/2/3) Space Control Register Diagram 8Ć9. . . . . . . . . . . . . . . . . . . . . .

8–5 Example of the Expansion Bus Interface to Four 8-Bit FIFOs 8Ć11. . . . . . . . . . . . . . . . . . . . . .

8–6 Example of the Expansion Bus Interface to Two 16-Bit FIFOs 8

8–7 Glueless Write FIFO Interface 8Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–8 Read and Write FIFO Interface With Glue 8Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–9 FIFO Write Cycles 8Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–10 Glueless Read FIFO Interface 8Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–11 FIFO Read Mode – Read Timing (glueless case) 8

8–12 FIFO Read Mode – With Glue 8Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–13 Expansion Bus Host Port Interface Block Diagram 8Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–14 Expansion Bus Data Register 8Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–15 Expansion Bus Internal Slave Address Register (XBISA) 8Ć23. . . . . . . . . . . . . . . . . . . . . . . . . .

8–16 Expansion Bus Internal Master Address Register 8

8–17 Expansion Bus External Address Register 8 Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–18 Expansion Bus Host Port Interface Control (XBHC) Register 8

8–19 Read Transfer Initiated by the TMS320C6202 and Throttled by

8–20 Write Transfer Initiated by the TMS320C6202 and Throttled by

8–21 External Device Requests the Bus From the TMS320C6202 Using XBOFF 8Ć33. . . . . . . . . .

8–22 The Expansion Bus Master Writes a Burst of Data to the TMS320C6202 8Ć37. . . . . . . . . . . .

8–23 The Bus Master Reads a Burst of Data From the TMS320C6202 8Ć39. . . . . . . . . . . . . . . . . . .

8–24 Timing Diagrams for Asynchronous Host Port Mode of the Expansion Bus 8

8–25 Timing Diagrams for Bus Arbitration–XHOLD/XHOLDA

8–26 Timing Diagrams for Bus Arbitration XHOLD/XHOLDA

8–27 XHOLD Timing When the External Host Starts a Transfer to DSP Instead of

8–28 Expansion Bus Boot Configuration via Pull Up/Pull Down Resistors on XD[31:0] 8

9–1 External Memory Interface in the TMS320C6201/C6202/C6701BlockDiagram 9Ć3. . . . . . . .

9–2 External Memory Interface in the TMS320C6211/C6711BlockDiagram 9Ć3. . . . . . . . . . . . . . .

9–3 TMS320C6201/C6701 External Memory Interface 9Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–4 TMS320C6202 External Memory Interface 9Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–5 TMS320C6211/C6711 External Memory Interface 9

9–6 EMIF Global Control Register Diagram 9Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–7 TMS320C6201/C6202/C6701 EMIF CE Space Control Register Diagram 9Ć12. . . . . . . . . . .

9–8 TMS320C6211/C6711 EMIF CE Space Control Register 9Ć12. . . . . . . . . . . . . . . . . . . . . . . . . .

9–9 TMS320C6211/C6711 Byte Alignment by Endianness 9Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–10 TMS320C6201/C6202/C6701 EMIF SDRAM Control Register 9

9–11 TMS320C6211/C6711 EMIF SDRAM Control Register 9Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . .

XWAIT

XWAIT and XRDY (Internal Bus Arbiter Disabled) 8Ć31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(Internal Bus Arbiter Enabled) 8Ć45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(Internal Bus Arbiter Disabled) 8Ć45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Granting the DSP Access to the Expansion Bus(Internal Bus Arbiter Disabled) 8Ć46. . . . . . .

and XRDY (Internal Bus Arbiter Disabled) 8Ć29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć4. . . . . . . . . . . . . . . . . .

Ć12. . . . . . . . . . . . . . . . . . . . . .

Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć25. . . . . . . . . . . . . . . . . . . . . . .

Ć43. . . . . . . . . . .

Ć49. . . . . .

Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć15. . . . . . . . . . . . . . . . . . . . .

Contents

xvii

Page 18

Figures

9–12 EMIF SDRAM Timing Register 9Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–13 TMS320C6211/C6711 SDRAM Extension Register 9Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–14 TMS320C6201/C6202/C6701 EMIF to 16M-Bit SDRAM Interface 9Ć21. . . . . . . . . . . . . . . . . .

9–15 TMS320C6211/C6711 EMIF to 16M-Bit SDRAM Interface 9Ć21. . . . . . . . . . . . . . . . . . . . . . . . .

9–16 TMS320C6201/C6202/C6701 EMIF to 64M-Bit SDRAM Interface 9

9–17 SDRAM Refresh 9Ć28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–18 TMS320C6201/C6202/C6701 Mode Register Value 9

9–19 TMS320C6211/C6711 Mode Register Value (0032h) 9

9–20 TMS320C6211/C6711 Mode Register Value (0022h) 9Ć30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–21 SDRAM Mode Register Set: MRS Command 9

9–22 SDRAM DCAB — Deactivate all Banks 9

9–23 TMS320C6211/C6711 SDRAM DEAC — Deactivate Single Bank 9

9–24 TMS3206201/C6202/C6701 SDRAM Read 9Ć37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–25 TMS320C6211 SDRAM Read 9

9–26 TMS320C6201/C6202/C6701 SDRAM Three Word Write 9

9–27 TMS320C6211/C6711 SDRAM Three Word Write 9Ć40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–28 Burst Reads to 2 Pages of SDRAM 9Ć41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–29 Seamless SDRAM Write 9Ć42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–30 TMS320C6201/C6202/C6701 SBSRAM Interface 9Ć44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–31 TMS320C6211/C6711 SBSRAM interface 9Ć44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–32 SBSRAM Four-Word Read 9Ć45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–33 TMS320C6211/C6711 SBSRAM Six-Word Read 9

9–34 TMS320C6201/C6202/C6701 SBSRAM Four Word Write 9

9–35 TMS320C6211/C6711 SBSRAM Write 9

9–36 TMS6201/C6202/C6701 EMIF to 32-bit SRAM Interface 9Ć50. . . . . . . . . . . . . . . . . . . . . . . . . .

9–37 TMS320C6211/C6711 EMIF to 16-bit SRAM (Big Endian) 9

9–38 EMIF to 8-Bit ROM Interface 9Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–39 EMIF to 16-Bit ROM Interface 9Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–40 EMIF to 32-Bit ROM Interface 9

9–41 Asynchronous Read Timing Example 9Ć55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–42 Asynchronous Write Timing Example 9Ć57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–43 TMS320C6201/C6202/C6701 Ready Operation 9Ć58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–44 TMS320C6211/C6711 Ready Operation 9Ć59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–1 McBSP Block Diagram 11

11–2 Serial Port Control Register (SPCR) 11 Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–3 Pin Control Register (PCR) 11Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–4 Receive Control Register (RCR) 11

11–5 Transmit Control Register (XCR) 11Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–6 Frame and Clock Operation 11Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–7 Receive Data Clocking 11Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–8 Dual-Phase Frame Example 11

11–9 Inter-IC Sound (IIS) Timing 11Ć27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–10 Single-Phase Frame of Four 8-Bit Elements 11Ć29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–11 Single-Phase Frame of One 32-Bit Element 11

Ć22. . . . . . . . . . . . . . . . . .

Ć29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć36. . . . . . . . . . . . . . . . . .

Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć39. . . . . . . . . . . . . . . . . . . . . . . . .

Ć46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć48. . . . . . . . . . . . . . . . . . . . . . . . .

Ć48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć50. . . . . . . . . . . . . . . . . . . . . . . . .

Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xviii

Page 19

Figures

11–12 Data Delay 11Ć30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–13 2-Bit Data Delay Used to Discard Framing Bit 11Ć31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–14 AC97 Dual-Phase Frame Format 11

11–15 AC97 Bit Timing Near Frame Synchronization 11Ć33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–16 McBSP Standard Operation 11Ć34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–17 Receive Operation 11Ć34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–18 Transmit Operation 11

11–19 Maximum Frame Frequency Transmit and Receive 11Ć36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–20 Unexpected Frame Synchronization With (R/X)FIG = 0 11

11–21 Unexpected Frame Synchronization With (R/X)FIG = 1 11Ć38. . . . . . . . . . . . . . . . . . . . . . . . . .

11–22 Maximum Frame Frequency Operation With 8-Bit Data 11Ć39. . . . . . . . . . . . . . . . . . . . . . . . . .

11–23 Data Packing at Maximum Frame Frequency With (R/X)FIG = 1 11

11–24 Serial Port Receive Overrun 11Ć42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–25 Serial Port Receive Overrun Avoided 11

11–26 Decision Tree Response to Receive Frame Synchronization Pulse 11Ć44. . . . . . . . . . . . . . . .

1 1–27 Unexpected Receive Synchronization Pulse 11Ć44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–28 Transmit With Data Overwrite 11

11–29 Transmit Empty 11Ć46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–30 Transmit Empty Avoided 11Ć46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–31 Response to Transmit Frame Synchronization 11

11–32 Unexpected Transmit Frame Synchronization Pulse 11Ć48. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–33 Companding Flow 11

11–34 Companding Data Formats 11Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–35 Transmit Data Companding Format in DXR 11Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–36 Companding of Internal Data 11

11–37 Clock and Frame Generation 11Ć53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–38 Sample Rate Generator 11

11–39 Sample Rate Generator Register (SRGR) 11Ć55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–40 CLKG Synchronization and FSG Generation When GSYNC = 1

and CLKGDV = 1 11Ć59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–41 CLKG Synchronization and FSG Generation When GSYNC = 1

and CLKGDV = 3 11

11–42 Programmable Frame Period and Width 11Ć62. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–43 ST-BUS and MVIP Example 11Ć65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–44 Single-Rate Clock Example 11

11–45 Double-Rate Clock Example 1 1Ć67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–46 Multichannel Control Register 11

11–47 Element Enabling by Subframes in Partitions A and B 11Ć72. . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–48 XMCM Operation 11Ć74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–49 Receive Channel Enable Register (RCER) 11

11–50 Transmit Channel Enable Register (XCER) 11Ć76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–51 DX Timing for Multichannel Operation 11Ć78. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–52 SPI Configuration: McBSP as the Master 11

11–53 SPI Configuration: McBSP as the Slave 11Ć81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć37. . . . . . . . . . . . . . . . . . . . . . . . . .

Ć40. . . . . . . . . . . . . . . . . . .

Ć42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć66. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć69. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ć80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xix

Page 20

Figures

11–54 SPI Transfer with CLKSTP = 10b 11Ć82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–55 SPI Transfer with CLKSTP = 11b 1 1Ć82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–1 Timer Block Diagram 12Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–2 Timer Control Register 12Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–3 Timer Period Register 12Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–4 Timer Counter Register 12Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–5 Timer Operation in Pulse Mode (C/P = 0) 12Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12–6 Timer Operation in Clock Mode (C/P = 1) 12Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–1 Timing of External Interrupt Related Signals 13Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–2 External Interrupt Polarity Register 13Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–3 Interrupt Multiplexer Low Register Diagram 13Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13–4 Interrupt Multiplexer High Register Diagram 13Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–1 Power-Down Mode Logic 14Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–2 PWRD Field of the CSR Register 14Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14–3 Peripheral Power-Down Control Fields for the TMS320C6202 14Ć6. . . . . . . . . . . . . . . . . . . . .