Page 1

TMS320C64x DSP

Video Port/VCXO Interpolated Control (VIC) Port

Reference Guide

Literature Number: SPRU629

April 2003

Page 2

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections,

modifications, enhancements, improvements, and other changes to its products and services at

any time and to discontinue any product or service without notice. Customers should obtain the

latest relevant information before placing orders and should verify that such information is current

and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the

time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of

sale in accordance with TI’s standard warranty . Testing and other quality control techniques are

used to the extent TI deems necessary to support this warranty. Except where mandated by

government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are

responsible for their products and applications using TI components. To minimize the risks

associated with customer products and applications, customers should provide adequate design

and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any

TI patent right, copyright, mask work right, or other TI intellectual property right relating to any

combination, machine, or process in which TI products or services are used. Information

published by TI regarding third party products or services does not constitute a license from TI

to use such products or services or a warranty or endorsement thereof. Use of such information

may require a license from a third party under the patents or other intellectual property of that third

party , or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction

is without alteration and is accompanied by all associated warranties, conditions, limitations, and

notices. Reproduction of this information with alteration is an unfair and deceptive business

practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated

by TI for that product or service voids all express and any implied warranties for the associated

TI product or service and is an unfair and deceptive business practice. TI is not responsible or

liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright 2003, Texas Instruments Incorporated

Page 3

About This Manual

This document describes the video port and VCXO interpolated control (VIC) port

in the digital signal processors (DSPs) of the TMS320C6000 DSP family.

Notational Conventions

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the

following number is 40 hexadecimal (decimal 64): 40h.

Related Documentation From Texas Instruments

The following documents describe the C6000 devices and related support

tools. Copies of these documents are available on the Internet at www.ti.com.

Tip: Enter the literature number in the search box provided at www .ti.com.

Preface

Read This First

TMS320C6000 CPU and Instruction Set Reference Guide (literature

number SPRU189) describes the TMS320C6000 CPU architecture,

instruction set, pipeline, and interrupts for these digital signal processors.

TMS320C6000 Peripherals Reference Guide (literature number SPRU190)

describes the peripherals available on the TMS320C6000 DSPs.

TMS320C6000 Technical Brief (literature number SPRU197) gives an

introduction to the TMS320C62x and TMS320C67x DSPs, develop-

ment tools, and third-party support.

TMS320C64x Technical Overview (SPRU395) gives an introduction to the

TMS320C64x DSP and discusses the application areas that are

enhanced by the TMS320C64x VelociTI.

TMS320C6000 Programmer’s Guide (literature number SPRU198)

describes ways to optimize C and assembly code for the

TMS320C6000 DSPs and includes application program examples.

TMS320C6000 Code Composer Studio Tutorial (literature number

SPRU301) introduces the Code Composer Studio integrated development environment and software tools.

iiiContentsSPRU629

Page 4

Trademarks

Related Documentation From Texas Instruments / T rademarks

Code Composer Studio Application Programming Interface Reference

Guide (literature number SPRU321) describes the Code Composer

Studio application programming interface (API), which allows you to

program custom plug-ins for Code Composer.

TMS320C6x Peripheral Support Library Programmer’s Reference

(literature number SPRU273) describes the contents of the

TMS320C6000 peripheral support library of functions and macros. It

lists functions and macros both by header file and alphabetically,

provides a complete description of each, and gives code examples to

show how they are used.

TMS320C6000 Chip Support Library API Reference Guide (literature

number SPRU401) describes a set of application programming interfaces

(APIs) used to configure and control the on-chip peripherals.

Trademarks

Code Composer Studio, C6000, C62x, C64x, C67x, TMS320C6000,

TMS320C62x, TMS320C64x, TMS320C67x, and VelociTI are trademarks of

Texas Instruments.

iv SPRU629

Page 5

Contents

Contents

1 Overview 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Provides an overview of the video port peripheral in the digital signal processors (DSPs) of the

TMS320C6000 DSP family. Included are an overview of the video port functions, FIFO configurations, and signal mapping.

1.1 Video Port 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Video Port FIFO 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.1 DMA Interface 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.2 Video Capture FIFO Configurations 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2.3 Video Display FIFO Configurations 1-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Video Port Registers 1-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Video Port Pin Mapping 1-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.1 VDIN Bus Usage for Capture Modes 1-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.2 VDOUT Data Bus Usage for Display Modes 1-16. . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Video Port 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Discusses the basic operation of the video port. Included is a discussion of the sources and

types of resets, interrupt operation, DMA operation, external clock inputs, video port throughput

and latency, and the video port control registers.

2.1 Reset Operation 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 Power-On Reset 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Peripheral Bus Reset 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.3 Software Port Reset 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.4 Capture Channel Reset 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.5 Display Channel Reset 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Interrupt Operation 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 DMA Operation 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Capture DMA Event Generation 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.2 Display DMA Event Generation 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.3 DMA Size and Threshold Restrictions 2-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.4 DMA Interface Operation 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Clocks 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Video Port Functionality Subsets 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.1 Data Bus Width 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.2 FIFO Size 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vContentsSPRU629

Page 6

Contents

2.6 Video Port Throughput and Latency 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.1 Video Capture Throughput 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2 Video Display Throughput 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 Video Port Control Registers 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.1 Video Port Control Register (VPCTL) 2-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.2 Video Port Status Register (VPSTAT) 2-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.3 Video Port Interrupt Enable Register (VPIE) 2-21. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.4 Video Port Interrupt Status Register (VPIS) 2-24. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Video Capture Port 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Discusses operation of the video capture port.

3.1 Video Capture Mode Selection 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 BT.656 Video Capture Mode 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 BT.656 Capture Channels 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 BT.656 Timing Reference Codes 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.3 BT.656 Image Window and Capture 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.4 BT.656 Data Sampling 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.5 BT.656 FIFO Packing 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Y/C Video Capture Mode 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Y/C Capture Channels 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Y/C Timing Reference Codes 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 Y/C Image Window and Capture 3-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.4 Y/C FIFO Packing 3-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 BT.656 and Y/C Mode Field and Frame Operation 3-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Capture Determination and Notification 3-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.2 Vertical Synchronization 3-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.3 Horizontal Synchronization 3-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.4 Field Identification 3-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.5 Short and Long Field Detect 3-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Video Input Filtering 3-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Input Filter Modes 3-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2 Chrominance Resampling Operation 3-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.3 Scaling Operation 3-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.4 Edge Pixel Replication 3-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 Ancillary Data Capture 3-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1 Horizontal Ancillary (HANC) Data Capture 3-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2 Vertical Ancillary (VANC) Data Capture 3-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7 Raw Data Capture Mode 3-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.1 Raw Data Capture Notification 3-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.2 Raw Data FIFO Packing 3-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi SPRU629

Page 7

Contents

3.8 TSI Capture Mode 3-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.1 TSI Capture Features 3-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.2 TSI Data Capture 3-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.3 TSI Capture Error Detection 3-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.4 Synchronizing the System Clock 3-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.5 TSI Data Capture Notification 3-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.6 Writing to the FIFO 3-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.7 Reading from the FIFO 3-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9 Capture Line Boundary Conditions 3-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10 Capturing Video in BT.656 or Y/C Mode 3-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10.1 Handling FIFO Overrun in BT.656 or Y/C Mode 3-45. . . . . . . . . . . . . . . . . . . . . . . . .

3.11 Capturing Video in Raw Data Mode 3-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.11.1 Handling FIFO Overrun Condition in Raw Data Mode 3-47. . . . . . . . . . . . . . . . . . .

3.12 Capturing Data in TSI Capture Mode 3-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.1 Handling FIFO Overrun Condition in TSI Capture Mode 3-48. . . . . . . . . . . . . . . . .

3.13 Video Capture Registers 3-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.1 Video Capture Channel x Status Register (VCASTAT, VCBSTAT) 3-50. . . . . . . . .

3.13.2 Video Capture Channel A Control Register (VCACTL) 3-53. . . . . . . . . . . . . . . . . . .

3.13.3 Video Capture Channel x Field 1 Start Register

(VCASTRT1, VCBSTRT1) 3-58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.4 Video Capture Channel x Field 1 Stop Register

(VCASTOP1, VCBSTOP1) 3-60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.5 Video Capture Channel x Field 2 Start Register

(VCASTRT2, VCBSTRT2) 3-61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.6 Video Capture Channel x Field 2 Stop Register

(VCASTOP2, VCBSTOP2) 3-62. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.7 Video Capture Channel x Vertical Interrupt Register

(VCAVINT, VCBVINT) 3-63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.8 Video Capture Channel x Threshold Register

(VCA THRLD, VCBTHRLD) 3-65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.9 Video Capture Channel x Event Count Register

(VCAEVTCT, VCBEVTCT) 3-67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.10 Video Capture Channel B Control Register (VCBCTL) 3-68. . . . . . . . . . . . . . . . . .

3.13.11 TSI Capture Control Register (TSICTL) 3-72. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.12 TSI Clock Initialization LSB Register (TSICLKINITL) 3-74. . . . . . . . . . . . . . . . . . . .

3.13.13 TSI Clock Initialization MSB Register (TSICLKINITM) 3-75. . . . . . . . . . . . . . . . . . .

3.13.14 TSI System Time Clock LSB Register (TSISTCLKL) 3-76. . . . . . . . . . . . . . . . . . . .

3.13.15 TSI System Time Clock MSB Register (TSISTCLKM) 3-77. . . . . . . . . . . . . . . . . . .

3.13.16 TSI System Time Clock Compare LSB Register (TSISTCMPL) 3-78. . . . . . . . . . .

3.13.17 TSI System Time Clock Compare MSB Register (TSISTCMPM) 3-79. . . . . . . . .

3.13.18 TSI System Time Clock Compare Mask LSB Register (TSISTMSKL) 3-80. . . . .

3.13.19 TSI System Time Clock Compare Mask MSB Register (TSISTMSKM) 3-81. . . .

3.13.20 TSI System Time Clock Ticks Interrupt Register (TSITICKS) 3-82. . . . . . . . . . . . .

3.14 Video Capture FIFO Registers 3-83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viiContentsSPRU629

Page 8

Contents

4 Video Display Port 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Discusses the video display port.

4.1 Video Display Mode Selection 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.1 Image Timing 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.2 Video Display Counters 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.3 Sync Signal Generation 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.4 External Sync Operation 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.5 Port Sync Operation 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 BT.656 Video Display Mode 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 Display Timing Reference Codes 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.2 Blanking Codes 4-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.3 BT.656 Image Display 4-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.4 BT.656 FIFO Unpacking 4-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Y/C Video Display Mode 4-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.1 Y/C Display Timing Reference Codes 4-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Y/C Blanking Codes 4-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.3 Y/C Image Display 4-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.4 Y/C FIFO Unpacking 4-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Video Output Filtering 4-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 Output Filter Modes 4-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 Chrominance Resampling Operation 4-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.3 Scaling Operation 4-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.4 Edge Pixel Replication 4-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Ancillary Data Display 4-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.1 Horizontal Ancillary (HANC) Data Display 4-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.2 Vertical Ancillary (VANC) Data Display 4-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Raw Data Display Mode 4-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.1 Raw Mode RGB Output Support 4-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.2 Raw Data FIFO Unpacking 4-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 Video Display Field and Frame Operation 4-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7.1 Display Determination and Notification 4-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7.2 Video Display Event Generation 4-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8 Display Line Boundary Conditions 4-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9 Display Timing Examples 4-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9.1 Interlaced BT.656 Timing Example 4-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9.2 Interlaced Raw Display Example 4-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9.3 Y/C Progressive Display Example 4-43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.10 Displaying Video in BT.656 or Y/C Mode 4-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11 Displaying Video in Raw Data Mode 4-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.11.1 Handling Underrun Condition of the Display FIFO 4-51. . . . . . . . . . . . . . . . . . . . . . .

4.12 Video Display Registers 4-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.1 Video Display Status Register (VDSTAT) 4-53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.2 Video Display Control Register (VDCTL) 4-55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.3 Video Display Frame Size Register (VDFRMSZ) 4-60. . . . . . . . . . . . . . . . . . . . . . . .

4.12.4 Video Display Horizontal Blanking Register (VDHBLNK) 4-61. . . . . . . . . . . . . . . . .

4.12.5 Video Display Field 1 Vertical Blanking Start Register (VDVBLKS1) 4-62. . . . . . .

viii SPRU629

Page 9

Contents

4.12.6 Video Display Field 1 Vertical Blanking End Register (VDVBLKE1) 4-64. . . . . . . .

4.12.7 Video Display Field 2 Vertical Blanking Start Register (VDVBLKS2) 4-65. . . . . . .

4.12.8 Video Display Field 2 Vertical Blanking End Register (VDVBLKE2) 4-67. . . . . . . .

4.12.9 Video Display Field 1 Image Of fset Register (VDIMGOFF1) 4-68. . . . . . . . . . . . . .

4.12.10 Video Display Field 1 Image Size Register (VDIMGSZ1) 4-70. . . . . . . . . . . . . . . .

4.12.11 Video Display Field 2 Image Offset Register (VDIMGOFF2) 4-71. . . . . . . . . . . . . .

4.12.12 Video Display Field 2 Image Size Register (VDIMGSZ2) 4-73. . . . . . . . . . . . . . . .

4.12.13 Video Display Field 1 Timing Register (VDFLDT1) 4-74. . . . . . . . . . . . . . . . . . . . . .

4.12.14 Video Display Field 2 Timing Register (VDFLDT2) 4-75. . . . . . . . . . . . . . . . . . . . . .

4.12.15 Video Display Threshold Register (VDTHRLD) 4-76. . . . . . . . . . . . . . . . . . . . . . . . .

4.12.16 Video Display Horizontal Synchronization Register (VDHSYNC) 4-78. . . . . . . . .

4.12.17 Video Display Field 1 Vertical Synchronization Start Register

(VDVSYNS1) 4-79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.18 Video Display Field 1 Vertical Synchronization End Register

(VDVSYNE1) 4-80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.19 Video Display Field 2 Vertical Synchronization Start Register

(VDVSYNS2) 4-81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.20 Video Display Field 2 Vertical Synchronization End Register

(VDVSYNE2) 4-82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.21 Video Display Counter Reload Register (VDRELOAD) 4-83. . . . . . . . . . . . . . . . . .

4.12.22 Video Display Display Event Register (VDDISPEVT) 4-84. . . . . . . . . . . . . . . . . . .

4.12.23 Video Display Clipping Register (VDCLIP) 4-85. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.24 Video Display Default Display Value Register (VDDEFVAL) 4-86. . . . . . . . . . . . . .

4.12.25 Video Display Vertical Interrupt Register (VDVINT) 4-88. . . . . . . . . . . . . . . . . . . . .

4.12.26 Video Display Field Bit Register (VDFBIT) 4-89. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.12.27 Video Display Field 1 Vertical Blanking Bit Register (VDVBIT1) 4-90. . . . . . . . . .

4.12.28 Video Display Field 2 Vertical Blanking Bit Register (VDVBIT2) 4-92. . . . . . . . . .

4.13 Video Display Registers Recommended Values 4-94. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.14 Video Display FIFO Registers 4-96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 General Purpose I/O Operation 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signals not used for video display or video capture can be used as general-purpose I/O signals.

5.1 GPIO Registers 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 Video Port Peripheral Identification Register (VPPID) 5-3. . . . . . . . . . . . . . . . . . . . .

5.1.2 Video Port Peripheral Control Register (PCR) 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.3 Video Port Pin Function Register (PFUNC) 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.4 Video Port Pin Direction Register (PDIR) 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.5 Video Port Pin Data Input Register (PDIN) 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.6 Video Port Pin Data Output Register (PDOUT) 5-13. . . . . . . . . . . . . . . . . . . . . . . . .

5.1.7 Video Port Pin Data Set Register (PDSET) 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.8 Video Port Pin Data Clear Register (PDCLR) 5-17. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.9 Video Port Pin Interrupt Enable Register (PIEN) 5-19. . . . . . . . . . . . . . . . . . . . . . . .

5.1.10 Video Port Pin Interrupt Polarity Register (PIPOL) 5-21. . . . . . . . . . . . . . . . . . . . . .

5.1.11 Video Port Pin Interrupt Status Register (PISTAT) 5-23. . . . . . . . . . . . . . . . . . . . . . .

5.1.12 Video Port Pin Interrupt Clear Register (PICLR) 5-25. . . . . . . . . . . . . . . . . . . . . . . .

ixContentsSPRU629

Page 10

Contents

6 VCXO Interpolated Control Port 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Provides an overview of the VCXO interpolated control (VIC) port.

6.1 Overview 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Interface 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Operational Details 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Enabling VIC Port 6-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5 VIC Port Registers 6-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5.1 VIC Control Register (VICCTL) 6-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5.2 VIC Input Register (VICIN) 6-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5.3 VIC Clock Divider Register (VICDIV) 6-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Video Port Configuration Examples A-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes how to configure the video port in different modes with the help of examples. All

examples in this appendix use the video port Chip Support Library (CSL).

A.1 Example 1: Noncontinuous Frame Capture for 525/60 Format A-2. . . . . . . . . . . . . . . . . . . .

A.2 Example 2: Noncontinuous Frame Display for 525/60 Format A-10. . . . . . . . . . . . . . . . . . . .

x SPRU629

Page 11

Figures

Figures

1–1 Video Port Block Diagram 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 BT.656 Video Capture FIFO Configuration 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–3 8/10-Bit Raw Video Capture and TSI Video Capture FIFO Configuration 1-7. . . . . . . . . . . . . .

1–4 Y/C Video Capture FIFO Configuration 1-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–5 16/20-Bit Raw Video Capture FIFO Configuration 1-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–6 BT.656 Video Display FIFO Configuration 1-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–7 8/10-Bit Raw Video Display FIFO Configuration 1-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–8 8/10 Bit Locked Raw Video Display FIFO Configuration 1-11. . . . . . . . . . . . . . . . . . . . . . . . . . .

1–9 16/20-Bit Raw Video Display FIFO Configuration 1-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–10 Y/C Video Display FIFO Configuration 1-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

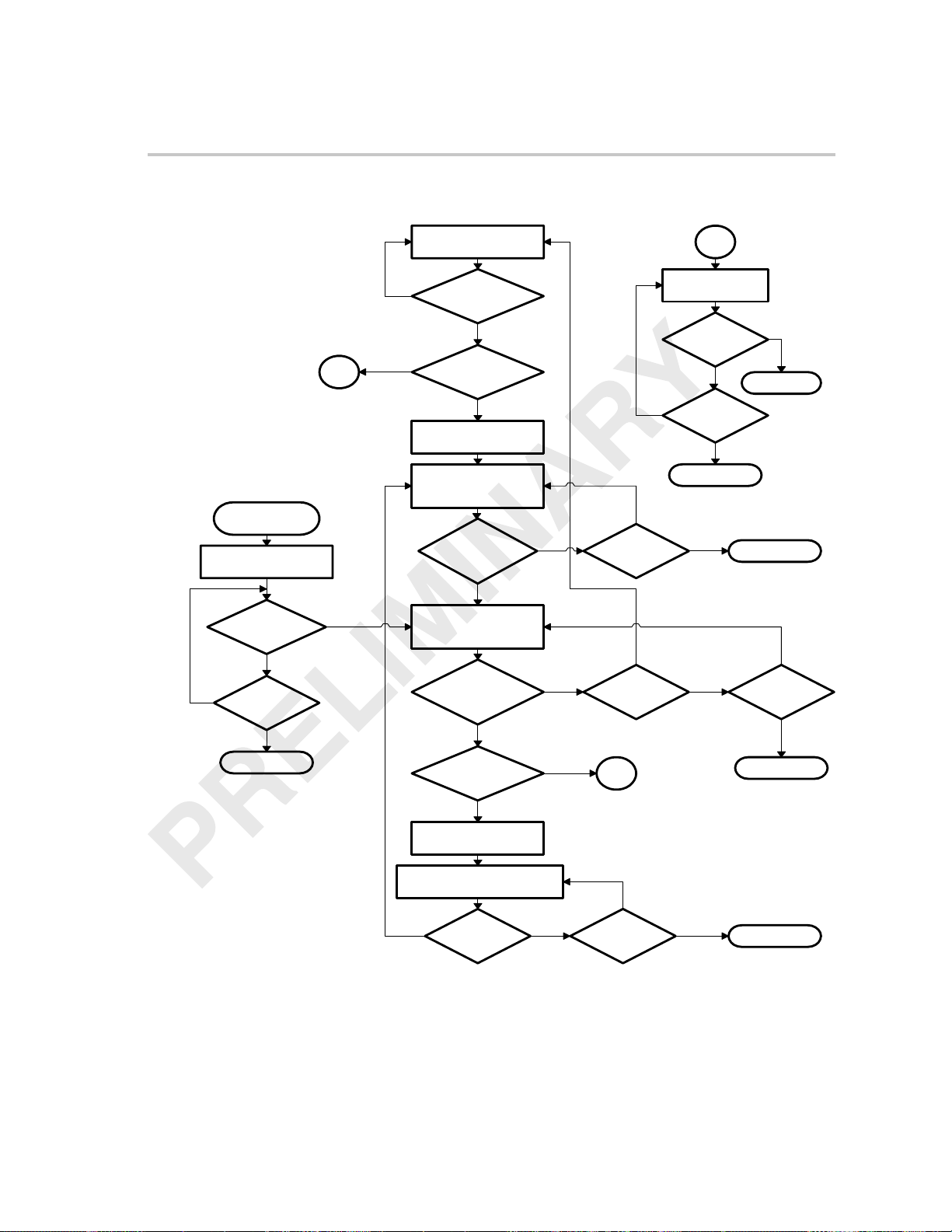

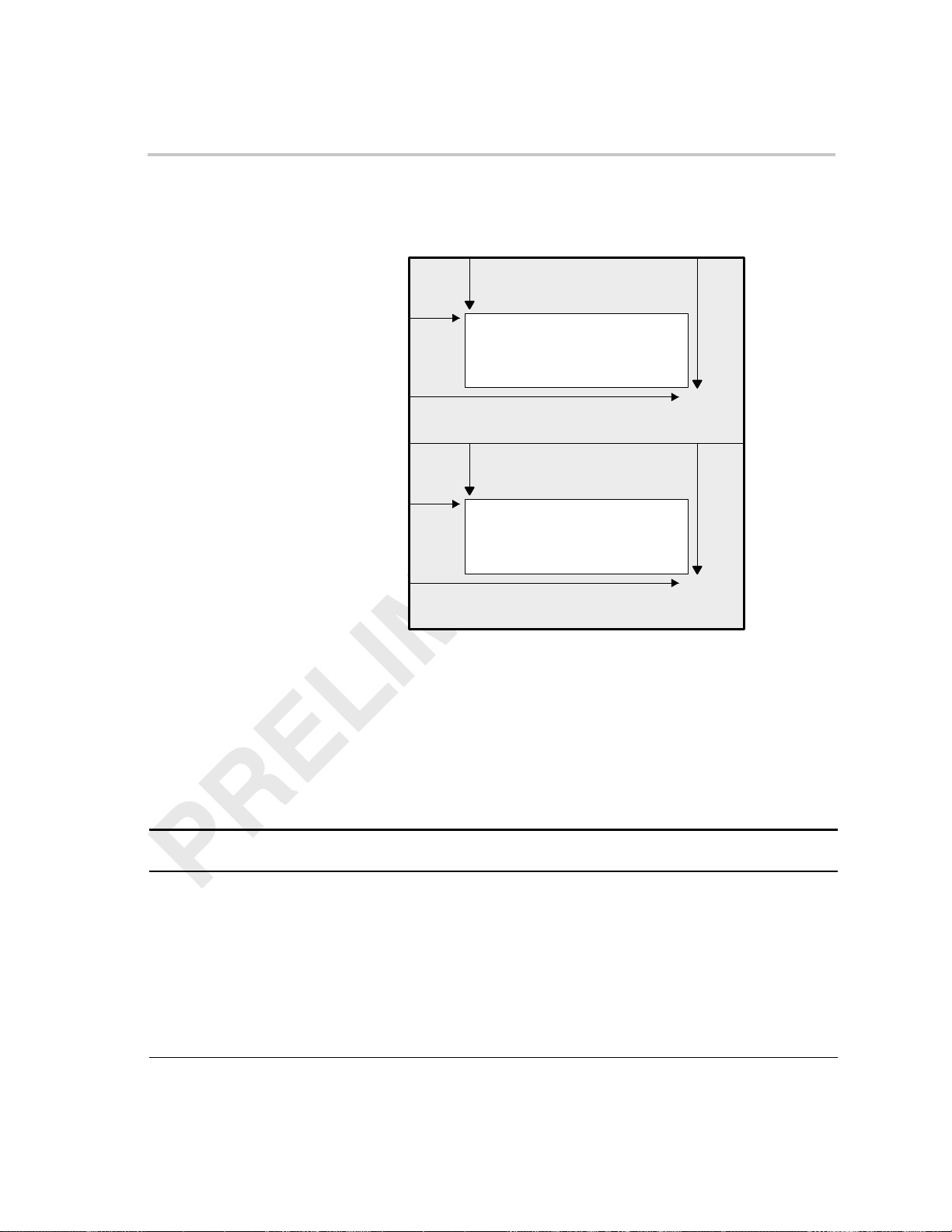

2–1 Capture DMA Event Generation Flow Diagram 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Display DMA Event Generation Flow Diagram 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Video Port Control Register (VPCTL) 2-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Video Port Status Register (VPSTAT) 2-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Video Port Interrupt Enable Register (VPIE) 2-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Video Port Interrupt Status Register (VPIS) 2-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Video Capture Parameters 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 8-Bit BT.656 FIFO Packing 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 10-Bit BT.656 FIFO Packing 3-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 10-Bit BT.656 Dense FIFO Packing 3-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 8-Bit Y/C FIFO Packing 3-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 10-Bit Y/C FIFO Packing 3-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 10-Bit Y/C Dense FIFO Packing 3-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 VCOUNT Operation Example (EXC = 0) 3-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 HCOUNT Operation Example (EXC = 0) 3-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 HCOUNT Operation Example (EXC = 1) 3-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 Field 1 Detection Timing 3-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 Chrominance Resampling 3-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 1/2 Scaled Co-Sited Filtering 3-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 1/2 Scaled Chrominance Resampled Filtering 3-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–15 Edge Pixel Replication 3-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–16 Capture Window Not Requiring Edge Pixel Replication 3-30. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–17 8-Bit Raw Data FIFO Packing 3-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–18 10-Bit Raw Data FIFO Packing 3-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–19 10-Bit Dense Raw Data FIFO Packing 3-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–20 16-Bit Raw Data FIFO Packing 3-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiFiguresSPRU629

Page 12

Figures

3–21 20-Bit Raw Data FIFO Packing 3-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–22 Parallel TSI Capture 3-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–23 Program Clock Reference (PCR) Header Format 3-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–24 System Time Clock Counter Operation 3-39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–25 TSI FIFO Packing 3-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–26 TSI Timestamp Format (Little Endian) 3-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–27 TSI Timestamp Format (Big Endian) 3-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–28 Capture Line Boundary Example 3-43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–29 Video Capture Channel x Status Register (VCASTAT, VCBSTAT) 3-50. . . . . . . . . . . . . . . . . . .

3–30 Video Capture Channel A Control Register (VCACTL) 3-53. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–31 Video Capture Channel x Field 1 Start Register (VCASTRT1, VCBSTRT1) 3-58. . . . . . . . . .

3–32 Video Capture Channel x Field 1 Stop Register (VCASTOP1, VCBST OP1) 3-60. . . . . . . . . .

3–33 Video Capture Channel x Field 2 Start Register (VCASTRT2, VCBSTRT2) 3-61. . . . . . . . . .

3–34 Video Capture Channel x Field 2 Stop Register (VCASTOP2, VCBST OP2) 3-62. . . . . . . . . .

3–35 Video Capture Channel x Vertical Interrupt Register (VCAVINT, VCBVINT) 3-63. . . . . . . . . .

3–36 Video Capture Channel x Threshold Register (VCATHRLD, VCBTHRLD) 3-66. . . . . . . . . . . .

3–37 Video Capture Channel x Event Count Register (VCAEVTCT, VCBEVTCT) 3-67. . . . . . . . . .

3–38 Video Capture Channel B Control Register (VCBCTL) 3-68. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–39 TSI Capture Control Register (TSICTL) 3-72. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–40 TSI Clock Initialization LSB Register (TSICLKINITL) 3-74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–41 TSI Clock Initialization MSB Register (TSICLKINITM) 3-75. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–42 TSI System Time Clock LSB Register (TSISTCLKL) 3-76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–43 TSI System Time Clock MSB Register (TSISTCLKM) 3-77. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–44 TSI System Time Clock Compare LSB Register (TSISTCMPL) 3-78. . . . . . . . . . . . . . . . . . . . .

3–45 TSI System Time Clock Compare MSB Register (TSISTCMPM) 3-79. . . . . . . . . . . . . . . . . . . .

3–46 TSI System Time Clock Compare Mask LSB Register (TSISTMSKL) 3-80. . . . . . . . . . . . . . .

3–47 TSI System Time Clock Compare Mask MSB Register (TSISTMSKM) 3-81. . . . . . . . . . . . . .

3–48 TSI System Time Clock Ticks Interrupt Register (TSITICKS) 3-82. . . . . . . . . . . . . . . . . . . . . . .

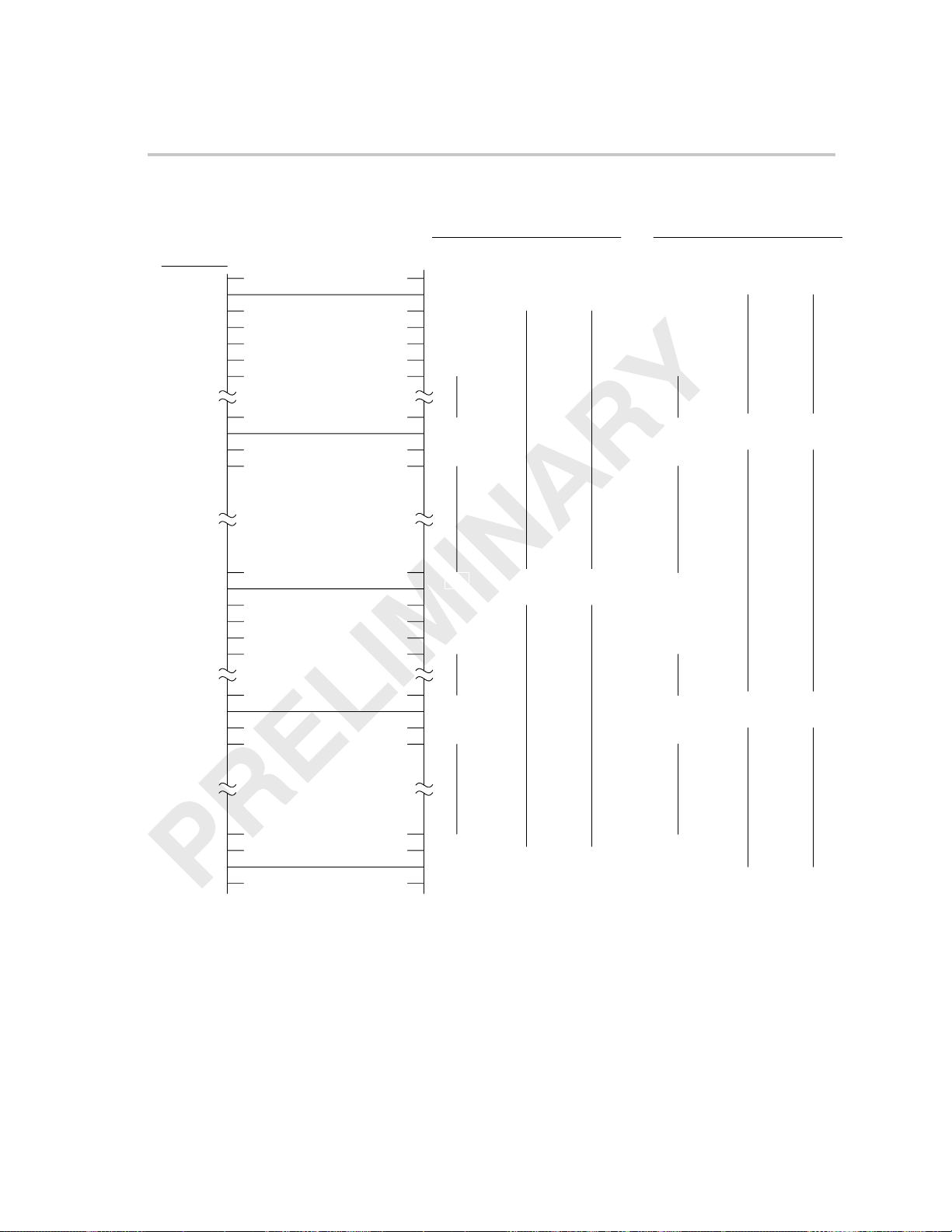

4–1 NTSC Compatible Interlaced Display 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 SMPTE 296M Compatible Progressive Scan Display 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Interlaced Blanking Intervals and Video Areas 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Progressive Blanking Intervals and Video Area 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Horizontal Blanking and Horizontal Sync Timing 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Vertical Blanking, Sync and Even/Odd Frame Signal Timing 4-7. . . . . . . . . . . . . . . . . . . . . . . .

4–7 Video Display Module Synchronization Chain 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 BT.656 Output Sequence 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–9 525/60 BT.656 Horizontal Blanking Timing 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–10 625/50 BT.656 Horizontal Blanking Timing 4-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–11 Digital Vertical F and V Transitions 4-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 8-Bit BT.656 FIFO Unpacking 4-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–13 10-Bit BT.656 FIFO Unpacking 4-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–14 BT.656 Dense FIFO Unpacking 4-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–15 Y/C Horizontal Blanking Timing (BT.1120 60I) 4-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–16 8-Bit Y/C FIFO Unpacking 4-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xii SPRU629

Page 13

4–17 10-Bit Y/C FIFO Unpacking 4-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–18 10-Bit Y/C Dense FIFO Unpacking 4-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–19 Chrominance Resampling 4-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–20 2x Co-Sited Scaling 4-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–21 2x Interspersed Scaling 4-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–22 Output Edge Pixel Replication 4-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–23 Luma Edge Replication 4-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–24 Interspersed Chroma Edge Replication 4-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–25 8-Bit Raw FIFO Unpacking 4-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–26 10-Bit Raw FIFO Unpacking 4-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–27 10-Bit Raw Dense FIFO Unpacking 4-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–28 16-Bit Raw FIFO Unpacking 4-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–29 20-Bit Raw FIFO Unpacking 4-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–30 8-Bit Raw 3/4 FIFO Unpacking 4-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–31 10-Bit Raw 3/4 FIFO Unpacking 4-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–32 Display Line Boundary Example 4-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–33 BT.656 Interlaced Display Horizontal Timing Example 4-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–34 BT.656 Interlaced Display Vertical Timing Example 4-38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–35 Raw Interlaced Display Horizontal Timing Example 4-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–36 Raw Interlaced Display Vertical Timing Example 4-42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–37 Y/C Progressive Display Horizontal Timing Example 4-44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–38 Y/C Progressive Display Vertical Timing Example 4-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–39 Video Display Status Register (VDSTAT) 4-53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–40 Video Display Control Register (VDCTL) 4-55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–41 Video Display Frame Size Register (VDFRMSZ) 4-60. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–42 Video Display Horizontal Blanking Register (VDHBLNK) 4-61. . . . . . . . . . . . . . . . . . . . . . . . . .

4–43 Video Display Field 1 Vertical Blanking Start Register (VDVBLKS1) 4-63. . . . . . . . . . . . . . . . .

4–44 Video Display Field 1 Vertical Blanking End Register (VDVBLKE1) 4-64. . . . . . . . . . . . . . . . .

4–45 Video Display Field 2 Vertical Blanking Start Register (VDVBLKS2) 4-66. . . . . . . . . . . . . . . . .

4–46 Video Display Field 2 Vertical Blanking End Register (VDVBLKE2) 4-67. . . . . . . . . . . . . . . . .

4–47 Video Display Field 1 Image Offset Register (VDIMGOFF1) 4-69. . . . . . . . . . . . . . . . . . . . . . .

4–48 Video Display Field 1 Image Size Register (VDIMGSZ1) 4-70. . . . . . . . . . . . . . . . . . . . . . . . . .

4–49 Video Display Field 2 Image Offset Register (VDIMGOFF2) 4-71. . . . . . . . . . . . . . . . . . . . . . .

4–50 Video Display Field 2 Image Size Register (VDIMGSZ2) 4-73. . . . . . . . . . . . . . . . . . . . . . . . . .

4–51 Video Display Field 1 Timing Register (VDFLDT1) 4-74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–52 Video Display Field 2 Timing Register (VDFLDT2) 4-75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–53 Video Display Threshold Register (VDTHRLD) 4-76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–54 Video Display Horizontal Synchronization Register (VDHSYNC) 4-78. . . . . . . . . . . . . . . . . . . .

4–55 Video Display Field 1 Vertical Synchronization Start Register (VDVSYNS1) 4-79. . . . . . . . . .

4–56 Video Display Field 1 Vertical Synchronization End Register (VDVSYNE1) 4-80. . . . . . . . . .

4–57 Video Display Field 2 Vertical Synchronization Start Register (VDVSYNS2) 4-81. . . . . . . . . .

4–58 Video Display Field 2 Vertical Synchronization End Register (VDVSYNE2) 4-82. . . . . . . . . .

4–59 Video Display Counter Reload Register (VDRELOAD) 4-83. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–60 Video Display Display Event Register (VDDISPEVT) 4-84. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figures

xiiiFiguresSPRU629

Page 14

Figures

4–61 Video Display Clipping Register (VDCLIP) 4-85. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–62 Video Display Default Display Value Register (VDDEFVAL) 4-86. . . . . . . . . . . . . . . . . . . . . . . .

4–63 Video Display Default Display Value Register (VDDEFVAL)—Raw Data Mode 4-87. . . . . . .

4–64 Video Display Vertical Interrupt Register (VDVINT) 4-88. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–65 Video Display Field Bit Register (VDFBIT) 4-89. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–66 Video Display Field 1 Vertical Blanking Bit Register (VDVBIT1) 4-90. . . . . . . . . . . . . . . . . . . . .

4–67 Video Display Field 2 Vertical Blanking Bit Register (VDVBIT2) 4-92. . . . . . . . . . . . . . . . . . . . .

5–1 Video Port Peripheral Identification Register (VPPID) 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Video Port Peripheral Control Register (PCR) 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Video Port Pin Function Register (PFUNC) 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Video Port Pin Direction Register (PDIR) 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Video Port Pin Data Input Register (PDIN) 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Video Port Pin Data Output Register (PDOUT) 5-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 Video Port Pin Data Set Register (PDSET) 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 Video Port Pin Data Clear Register (PDCLR) 5-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 Video Port Pin Interrupt Enable Register (PIEN) 5-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Video Port Pin Interrupt Polarity Register (PIPOL) 5-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 Video Port Pin Interrupt Status Register (PISTAT) 5-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 Video Port Pin Interrupt Clear Register (PICLR) 5-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 TSI System Block Diagram 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Program Clock Reference (PCR) Header Format 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 VIC Control Register (VICCTL) 6-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 VIC Input Register (VICIN) 6-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 VIC Clock Divider Register (VICDIV) 6-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiv SPRU629

Page 15

Tables

Tables

1–1 Video Capture Signal Mapping 1-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 Video Display Signal Mapping 1-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–3 VDIN Data Bus Usage for Capture Modes 1-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–4 VDOUT Data Bus Usage for Display Modes 1-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 Video Port Functional Clocks 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Y/C Video Capture FIFO Capacity 2-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Raw Video Display FIFO Capacity 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Video Port Control Registers 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Video Port Control Register (VPCTL) Field Descriptions 2-17. . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Video Port Operating Mode Selection 2-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Video Port Status Register (VPSTAT) Field Descriptions 2-20. . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Video Port Interrupt Enable Register (VPIE) Field Descriptions 2-21. . . . . . . . . . . . . . . . . . . . .

2–9 Video Port Interrupt Status Register (VPIS) Field Descriptions 2-24. . . . . . . . . . . . . . . . . . . . .

3–1 Video Capture Mode Selection 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 BT.656 Video Timing Reference Codes 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 BT.656 Protection Bits 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Error Correction by Protection Bits 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Common Video Source Parameters 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 BT.656 and Y/C Mode Capture Operation 3-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 Vertical Synchronization Programming 3-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 Horizontal Synchronization Programming 3-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 Field Identification Programming 3-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 Input Filter Mode Selection 3-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 Raw Data Mode Capture Operation 3-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 TSI Capture Mode Operation 3-40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 Video Capture Control Registers 3-49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 Video Capture Channel x Status Register (VCxSTAT) Field Descriptions 3-51. . . . . . . . . . . .

3–15 Video Capture Channel A Control Register (VCACTL) Field Descriptions 3-53. . . . . . . . . . . .

3–16 Video Capture Channel x Field 1 Start Register (VCxSTRT1) Field Descriptions 3-59. . . . . .

3–17 Video Capture Channel x Field 1 Stop Register (VCxSTOP1) Field Descriptions 3-60. . . . . .

3–18 Video Capture Channel x Field 2 Start Register (VCxSTRT2) Field Descriptions 3-61. . . . . .

3–19 Video Capture Channel x Field 2 Stop Register (VCxSTOP2) Field Descriptions 3-62. . . . . .

3–20 Video Capture Channel x Vertical Interrupt Register (VCxVINT) Field Descriptions 3-64. . . .

3–21 Video Capture Channel x Threshold Register (VCxTHRLD) Field Descriptions 3-66. . . . . . .

3–22 Video Capture Channel x Event Count Register (VCxEVTCT) Field Descriptions 3-67. . . . .

3–23 Video Capture Channel B Control Register (VCBCTL) Field Descriptions 3-68. . . . . . . . . . . .

xvTablesSPRU629

Page 16

Tables

3–24 TSI Capture Control Register (TSICTL) Field Descriptions 3-73. . . . . . . . . . . . . . . . . . . . . . . . .

3–25 TSI Clock Initialization LSB Register (TSICLKINITL) Field Descriptions 3-74. . . . . . . . . . . . .

3–26 TSI Clock Initialization MSB Register (TSICLKINITM) Field Descriptions 3-75. . . . . . . . . . . .

3–27 TSI System Time Clock LSB Register (TSISTCLKL) Field Descriptions 3-76. . . . . . . . . . . . . .

3–28 TSI System Time Clock MSB Register (TSISTCLKM) Field Descriptions 3-77. . . . . . . . . . . .

3–29 TSI System Time Clock Compare LSB Register (TSISTCMPL) Field Descriptions 3-78. . . .

3–30 TSI System Time Clock Compare MSB Register (TSISTCMPM) Field Descriptions 3-79. . .

3–31 TSI System Time Clock Compare Mask LSB Register (TSISTMSKL)

Field Descriptions 3-80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–32 TSI System Time Clock Compare Mask MSB Register (TSISTMSKM)

Field Descriptions 3-81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–33 TSI System Time Clock Ticks Interrupt Register (TSITICKS) Field Descriptions 3-82. . . . . .

3–34 Video Capture FIFO Registers 3-83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–35 Video Capture FIFO Registers Function 3-83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Video Display Mode Selection 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 BT.656 Frame Timing 4-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Output Filter Mode Selection 4-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Display Operation 4-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Video Display Control Registers 4-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Video Display Status Register (VDSTAT) Field Descriptions 4-54. . . . . . . . . . . . . . . . . . . . . . .

4–7 Video Display Control Register (VDCTL) Field Descriptions 4-55. . . . . . . . . . . . . . . . . . . . . . . .

4–8 Video Display Frame Size Register (VDFRMSZ) Field Descriptions 4-60. . . . . . . . . . . . . . . . .

4–9 Video Display Horizontal Blanking Register (VDHBLNK) Field Descriptions 4-62. . . . . . . . . .

4–10 Video Display Field 1 Vertical Blanking Start Register (VDVBLKS1)

Field Descriptions 4-63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–11 Video Display Field 1 Vertical Blanking End Register (VDVBLKE1)

Field Descriptions 4-65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 Video Display Field 2 Vertical Blanking Start Register (VDVBLKS2)

Field Descriptions 4-66. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–13 Video Display Field 2 Vertical Blanking End Register (VDVBLKE2)

Field Descriptions 4-68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–14 Video Display Field 1 Image Offset Register (VDIMGOFF1) Field Descriptions 4-69. . . . . . .

4–15 Video Display Field 1 Image Size Register (VDIMGSZ1) Field Descriptions 4-70. . . . . . . . . .

4–16 Video Display Field 2 Image Offset Register (VDIMGOFF2) Field Descriptions 4-72. . . . . . .

4–17 Video Display Field 2 Image Size Register (VDIMGSZ2) Field Descriptions 4-73. . . . . . . . . .

4–18 Video Display Field 1 Timing Register (VDFLDT1) Field Descriptions 4-74. . . . . . . . . . . . . . .

4–19 Video Display Field 2 Timing Register (VDFLDT2) Field Descriptions 4-75. . . . . . . . . . . . . . .

4–20 Video Display Threshold Register (VDTHRLD) Field Descriptions 4-77. . . . . . . . . . . . . . . . . .

4–21 Video Display Horizontal Synchronization Register (VDHSYNC) Field Descriptions 4-78. . .

4–22 Video Display Field 1 Vertical Synchronization Start Register (VDVSYNS1)

Field Descriptions 4-79. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–23 Video Display Field 1 Vertical Synchronization End Register (VDVSYNE1)

Field Descriptions 4-80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–24 Video Display Field 2 Vertical Synchronization Start Register (VDVSYNS2)

Field Descriptions 4-81. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–25 Video Display Field 2 Vertical Synchronization End Register (VDVSYNE2)

Field Descriptions 4-82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xvi SPRU629

Page 17

Tables

4–26 Video Display Counter Reload Register (VDRELOAD) Field Descriptions 4-83. . . . . . . . . . . .

4–27 Video Display Display Event Register (VDDISPEVT) Field Descriptions 4-84. . . . . . . . . . . . .

4–28 Video Display Clipping Register (VDCLIP) Field Descriptions 4-85. . . . . . . . . . . . . . . . . . . . . .

4–29 Video Display Default Display Value Register (VDDEFVAL) Field Descriptions 4-87. . . . . . .

4–30 Video Display Vertical Interrupt Register (VDVINT) Field Descriptions 4-88. . . . . . . . . . . . . . .

4–31 Video Display Field Bit Register (VDFBIT) Field Descriptions 4-89. . . . . . . . . . . . . . . . . . . . . .

4–32 Video Display Field 1 Vertical Blanking Bit Register (VDVBIT1) Field Descriptions 4-91. . . .

4–33 Video Display Field 2 Vertical Blanking Bit Register (VDVBIT2) Field Descriptions 4-93. . . .

4–34 Video Display Register Recommended Values 4-94. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–35 Video Display FIFO Registers 4-96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–36 Video Display FIFO Registers Function 4-96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Video Port Registers 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Video Port Peripheral Identification Register (VPPID) Field Descriptions 5-3. . . . . . . . . . . . . .

5–3 Video Port Peripheral Control Register (PCR) Field Descriptions 5-5. . . . . . . . . . . . . . . . . . . .

5–4 Video Port Pin Function Register (PFUNC) Field Descriptions 5-6. . . . . . . . . . . . . . . . . . . . . . .

5–5 Video Port Pin Direction Register (PDIR) Field Descriptions 5-8. . . . . . . . . . . . . . . . . . . . . . . .

5–6 Video Port Pin Data Input Register (PDIN) Field Descriptions 5-12. . . . . . . . . . . . . . . . . . . . . .

5–7 Video Port Pin Data Out Register (PDOUT) Field Descriptions 5-14. . . . . . . . . . . . . . . . . . . . .

5–8 Video Port Pin Data Set Register (PDSET) Field Descriptions 5-16. . . . . . . . . . . . . . . . . . . . . .

5–9 Video Port Pin Data Clear Register (PDCLR) Field Descriptions 5-18. . . . . . . . . . . . . . . . . . . .

5–10 Video Port Pin Interrupt Enable Register (PIEN) Field Descriptions 5-20. . . . . . . . . . . . . . . . .

5–11 Video Port Pin Interrupt Polarity Register (PIPOL) Field Descriptions 5-22. . . . . . . . . . . . . . . .

5–12 Video Port Pin Interrupt Status Register (PISTAT) Field Descriptions 5-24. . . . . . . . . . . . . . . .

5–13 Video Port Pin Interrupt Clear Register (PICLR) Field Descriptions 5-26. . . . . . . . . . . . . . . . .

6–1 VIC Port Interface Signals 6-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Example Values for Interpolation Rate 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 VIC Port Registers 6-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 VIC Control Register (VICCTL) Field Descriptions 6-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 VIC Input Register (VICIN) Field Descriptions 6-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 VIC Clock Divider Register (VICDIV) Field Descriptions 6-9. . . . . . . . . . . . . . . . . . . . . . . . . . . .

xviiTablesSPRU629

Page 18

Chapter 1

Overview

This chapter provides an overview of the video port peripheral in the digital

signal processors (DSPs) of the TMS320C6000 DSP family. Included are an

overview of the video port functions, FIFO configurations, and signal mapping.

Topic Page

1.1 Video Port 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Video Port FIFO 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Video Port Registers 1-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Video Port Pin Mapping 1-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-1

Page 19

Video Port

1.1 Video Port

The video port peripheral can operate as a video capture port, video display

port, or transport stream interface (TSI) capture port. It provides the following

functions:

- Video capture mode:

J Capture rate up to 80 MHz.

J Two channels of 8/10-bit digital video input from a digital camera or

analog camera (using a video decoder). Digital video input is in YCbCr

4:2:2 format with 8-bit or 10-bit resolution multiplexed in ITU-R BT .656

format.

J One channel of Y/C 16/20-bit digital video input in YCbCr 4:2:2 format

on separate Y and Cb/Cr inputs. Supports SMPTE 260M,

SMPTE 274M, SMPTE 296M, ITU-BT.1120, etc., as well as older

CCIR601 interfaces.

J YCbCr 4:2:2 to YCbCr 4:2:0 horizontal conversion and ½ scaling in

8-bit 4:2:2 modes.

J Direct interface for two channels of up to 10-bit or one channel of up to

20-bit raw video from A/D converters.

- Video display mode:

J Display rate up to 110 MHz.

J One channel of continuous digital video output. Digital video output is

YCbCr 4:2:2 co-sited pixel data with 8/10-bit resolution multiplexed in

ITU-R BT.656 format.

J One channel of Y/C 16/20-bit digital video output in YCbCr 4:2:2 format

on separate Y and Cb/Cr outputs. (Supports SMPTE 260M,

SMPTE 274M, SMPTE 296M, ITU-BT.1120, etc.)

J YCbCr 4:2:0 to YCbCr 4:2:2 horizontal conversion and 2× scaling of

output in 8-bit 4:2:2 modes.

J Programmable clipping of BT.656 and Y/C mode output values.

J One channel of raw data output up to 20-bits for interface to RAM-

DACs. Two channel synchronized raw data output.

J Synchronizes to external video controller or another video display port.

J Using the external clock, the frame timing generator provides

programmable image timing including horizontal and vertical blanking, start of active video (SAV) and end of active video (EAV) code

insertion, and horizontal and frame timing pulses.

J Generates horizontal and vertical synchronization and blanking

signals and a frame synchronization signal.

Overview1-2 SPRU629

Page 20

Video Port

TSI capture mode: Transport stream interface (TSI) from a front-end

-

device such as demodulator or forward error correction device in 8-bit

parallel format at up to 30 Mbytes/sec.

- The port generates up to three events per channel and one interrupt to the

DSP.

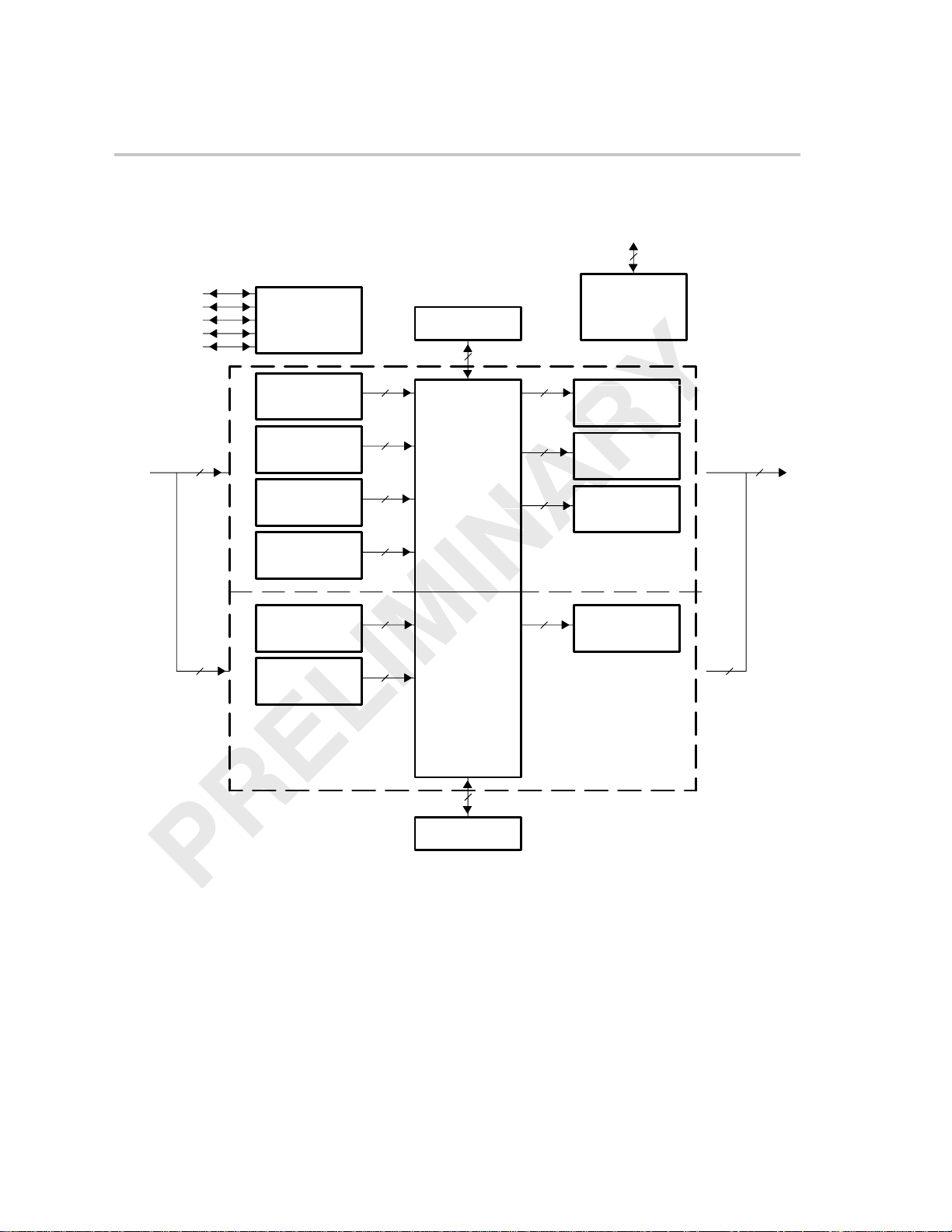

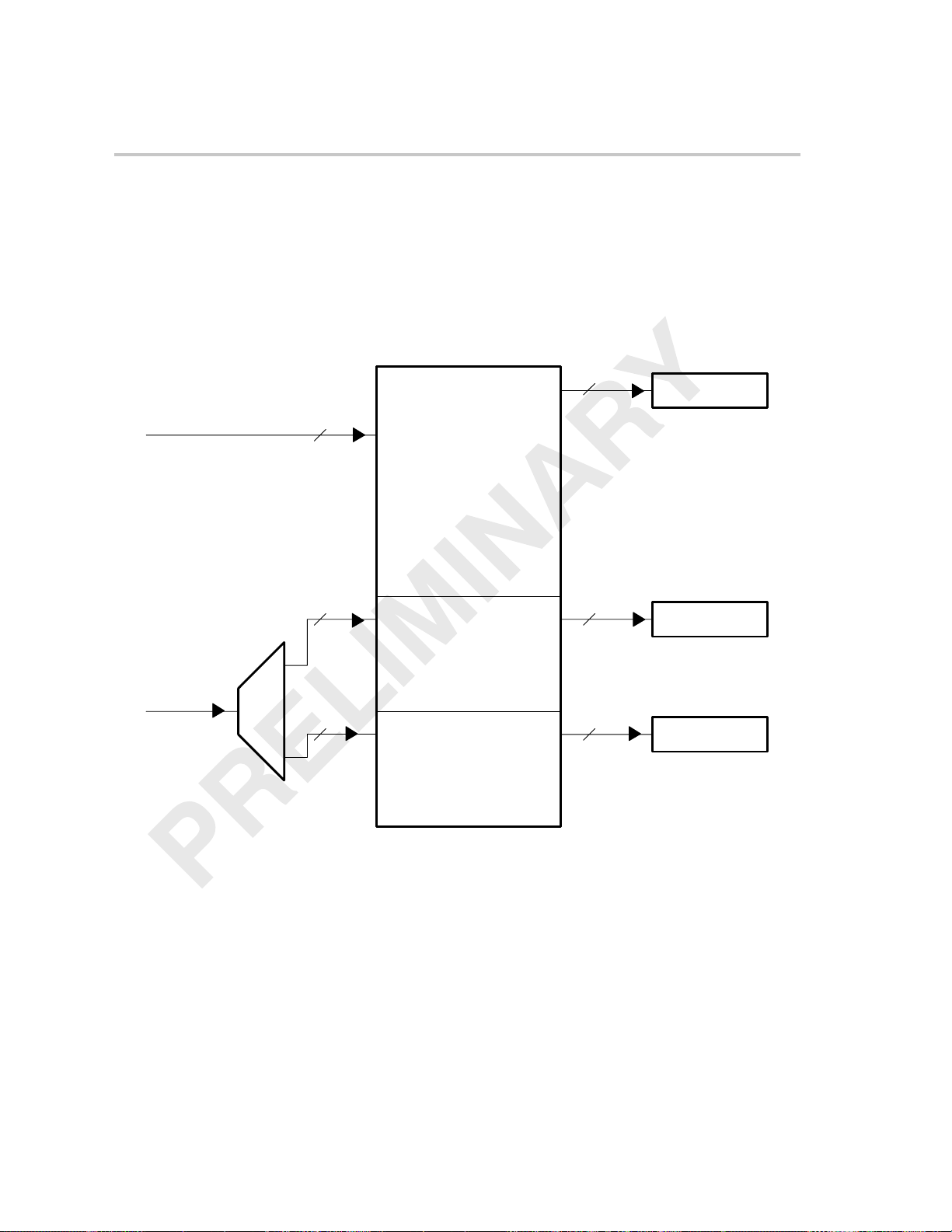

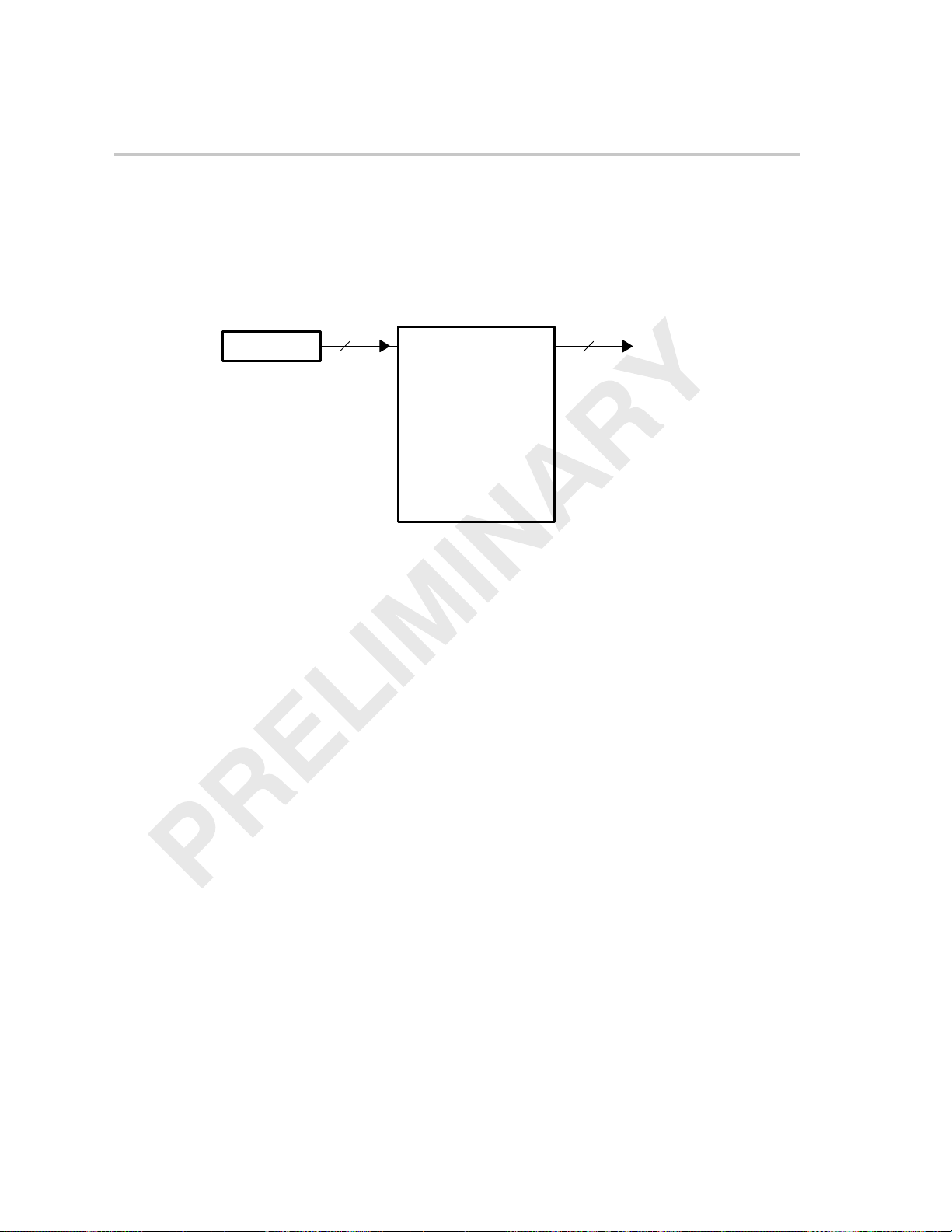

A high-level block diagram of the video port is shown in Figure 1–1. The port

consists of two channels: A and B. A 5120-byte capture/display buffer is splittable between the two channels. The entire port (both channels) is always

configured for either video capture or display only. Separate data pipelines

control the parsing and formatting of video capture or display data for each of

the BT.656, Y/C, raw video, and TSI modes.

For video capture operation, the video port may operate as two 8/10-bit channels of BT .656 or raw video capture; or as a single channel of 8/10-bit BT.656,

8/10-bit raw video, 16/20-bit Y/C video, 16/20-bit raw video, or 8-bit TSI.

For video display operation, the video port may operate as a single channel

of 8/10-bit BT.656, 8/10-bit raw video, 16/20 bit Y/C video, or 16/20-bit raw

video. It may also operate in a two channel 8/10-bit raw mode in which the two

channels are locked to the same timing. Channel B is not used during single

channel operation.

This document describes the full feature set offered by a 20-bit video port

implementation. Some devices may offer a subset of features such as video

capture only or video display only . Also, some devices may limit the video port

width to 8 or 10 bits. In this case, modes requiring wider video port widths such

as 16-bit raw, 20-bit raw, and Y/C are not supported. See the device-specific

datasheet for details and for I/O timing information.

1-3OverviewSPRU629

Page 21

Video Port

Figure 1–1. Video Port Block Diagram

VCLK1

VCLK2

VCTL1

VCTL2

VCTL3

Timing and

control logic

DMA interface

64

Internal peripheral bus

32

Memory

mapped

registers

VDIN[19–0]

20

10

VDIN[19–10]

BT.656 capture

pipeline

Y/C video

capture pipeline

Raw video

capture pipeline

TSI capture

pipeline

BT.656 capture

pipeline

Raw video

capture pipeline

10 10

20

Capture/display

(2560 bytes)

20

8

10

Capture/display

10

(2560 bytes)

DMA interface

buffer

buffer

64

20

20

10

BT.656 display

pipeline

Y/C video

display pipeline

Raw video

display pipeline

Channel A

Raw video

display pipeline

Channel B

VDOUT[19–0]

20

10

VDOUT[19–10]

Overview1-4 SPRU629

Page 22

1.2 Video Port FIFO

The video port includes a FIFO to store data coming into or out from the video

port. The video port operates in conjunction with DMA transfers to move data

between the video port FIFO and external or on-chip memory. You can program threshold settings so DMA events are generated when the video port

FIFO reaches a certain fullness (for capture) or goes below a certain fullness

(for display). DMAs required to service the FIFO are set up independently by

you and are key to correct operation of the video port. The FIFO size is relatively large to allow time for DMAs to service the transfer requests, since devices

typically have many peripheral interfaces often including multiple video ports.

The following sections briefly describe the interaction with the DMA and different FIFO configurations used to support the various modes of the video port.

1.2.1 DMA Interface

Video port data transfers take place using DMAs. DMA requests are based on

buffer thresholds. Since the video port does not directly source the transfer , it

can not adjust the transfer size based on buffer empty/full status. This means

the DMA transfer size is essentially fixed in the user-programmed DMA

parameter table. The preferred transfer size is often one entire line of data,

because this allows the most flexibility in terms of frame buffer line pitch (in

RAM). Some modes of operation for the highest display rates may require

more frequent DMA requests such as on a half or quarter line basis.

Video Port FIFO

All requests are based on buffer thresholds. In video capture mode, DMA

requests are made whenever the number of samples in the buffer reaches the

threshold value. In order to ensure that all data from a capture field/frame gets

emptied from the buffer , the transfer size must be equal to the threshold and

the total amount of field/frame data must be a multiple of the transfer size.

For video display operation, DMA requests are made whenever there is at

least the threshold number of doublewords free in the FIFO. This means that

the transfer size must be equal to or smaller than the threshold so that it fits

into the available space. The field/frame size must still be a multiple of the

transfer size or there are pixels left in the buffer at the end of the field (which

appear at the start of the next field).

1-5OverviewSPRU629

Page 23

Video Port FIFO

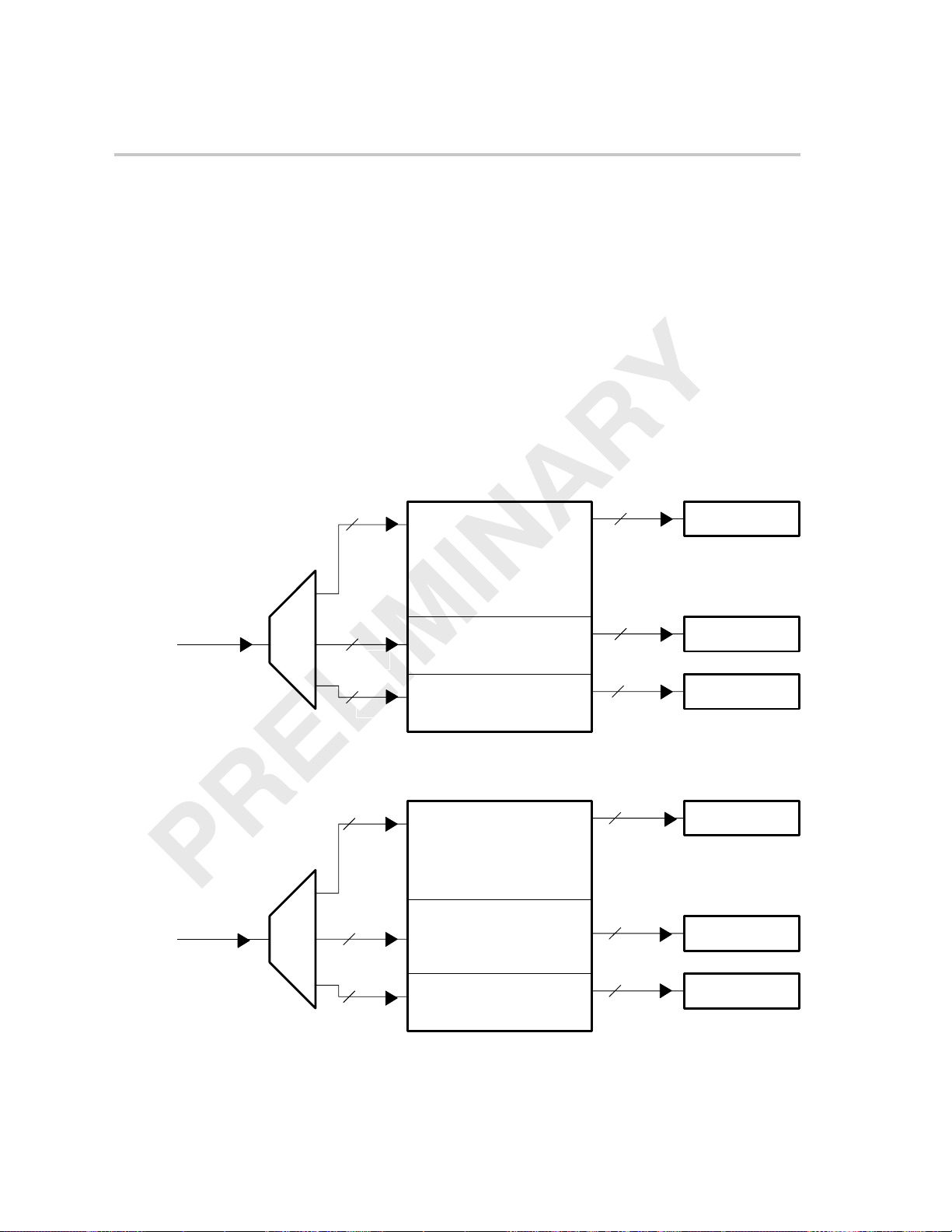

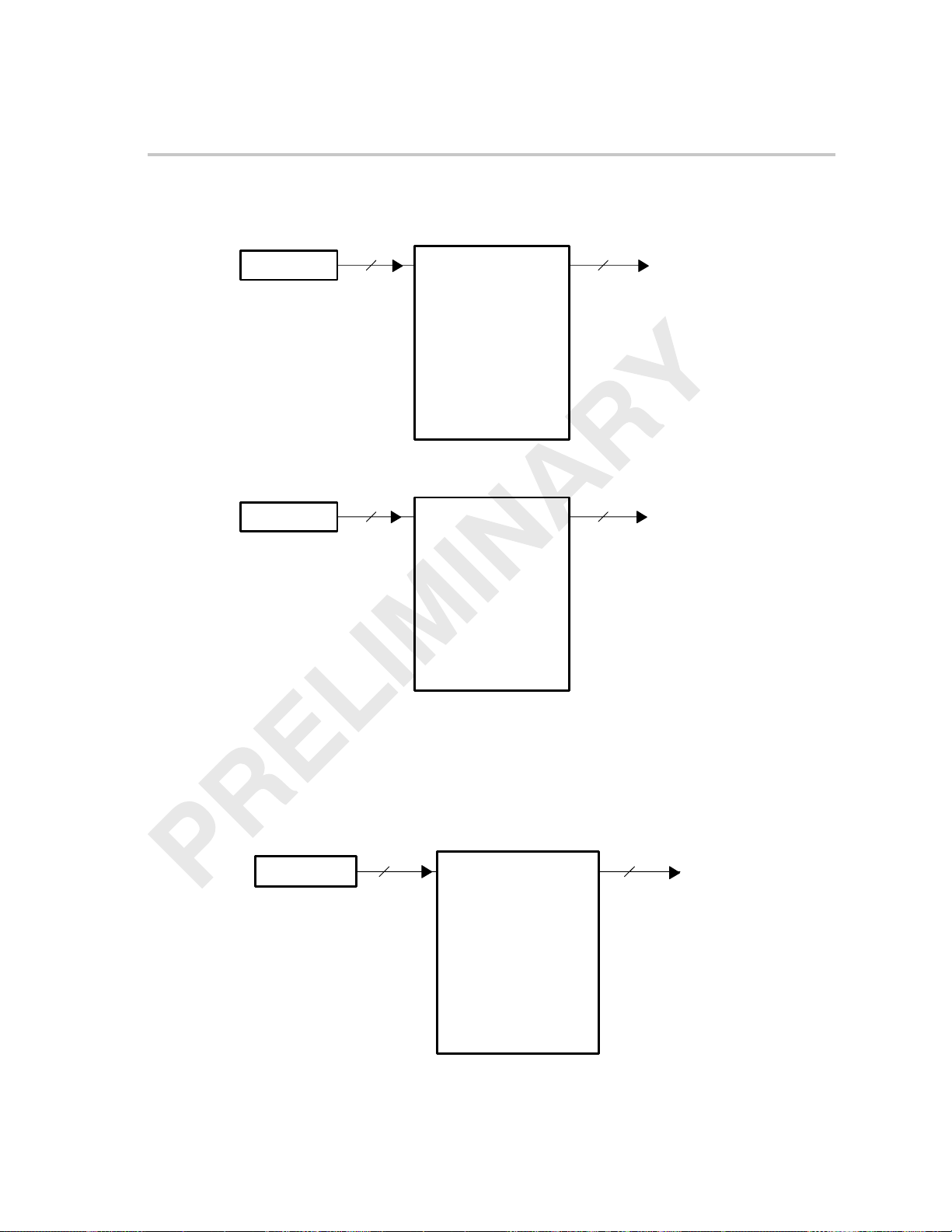

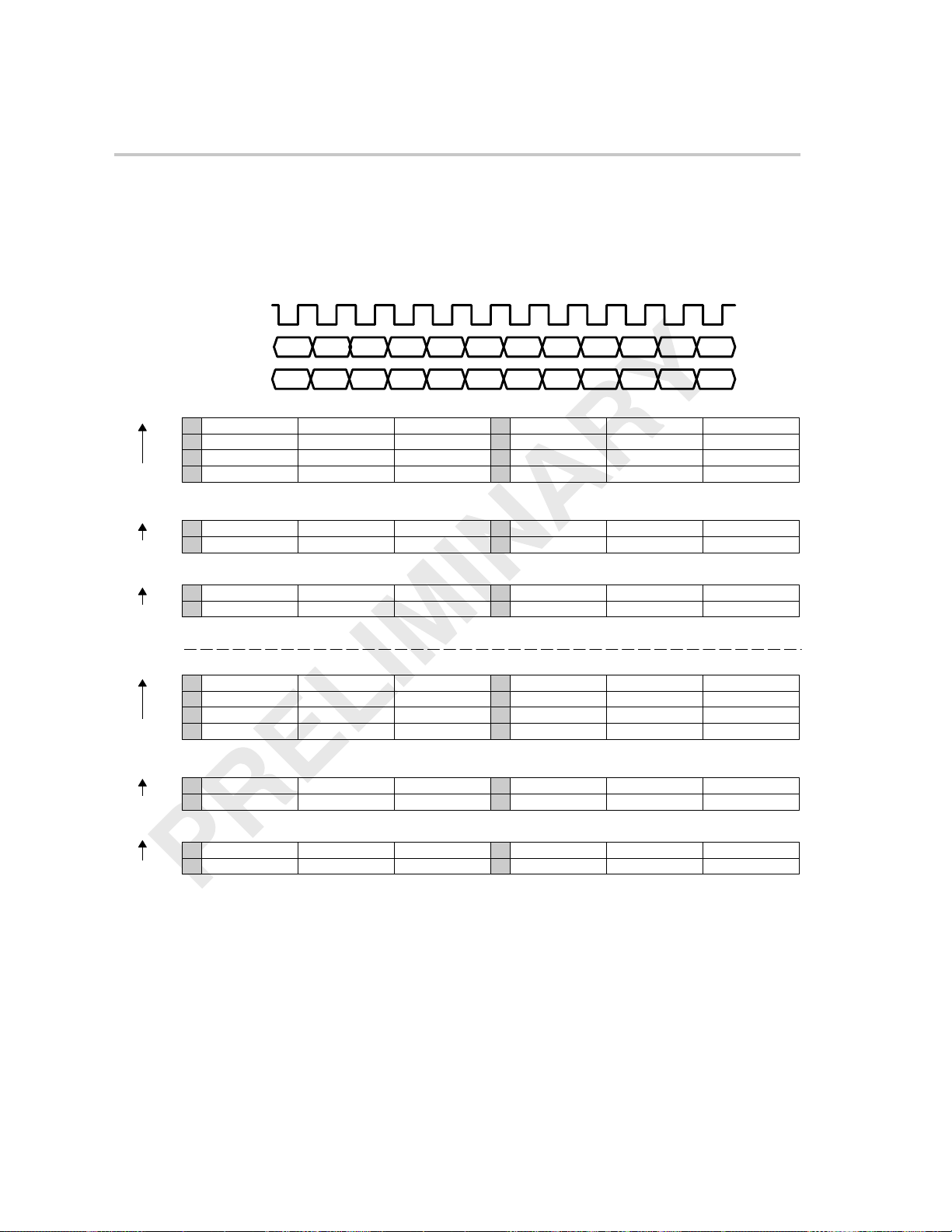

1.2.2 Video Capture FIFO Configurations

During video capture operation, the video port FIFO has one of four configurations depending on the capture mode. For BT.656 operation, the FIFO is split

into channel A and B, as shown in Figure 1–2. Each FIFO is clocked independently with the channel A FIFO receiving data from the VDIN[9–0] half of the

bus and the channel B FIFO receiving data from the VDIN[19–10] half of the

bus. Each channel’s FIFO is further split into Y, Cb, and Cr buffers with separate write pointers and read registers (YSRCx, CBSRCx, and CRSRCx).

Figure 1–2. BT.656 Video Capture FIFO Configuration

Capture FIFO A

VDIN[9–0]

VDIN[19–10]

8/10

8/10

8/10

8/10

8/10

Y Buffer A (1280 bytes)

Cb Buffer A (640 bytes)

Cr Buffer A (640 bytes)

Capture FIFO B

Y Buffer B (1280 bytes)

Cb Buffer B (640 bytes)

64

64

64

64

64

YSRCA

CBSRCA

CRSRCA

YSRCB

CBSRCB

8/10

Overview1-6 SPRU629

Cr Buffer B (640 bytes)

64

CRSRCB

Page 24

Video Port FIFO

For 8/10-bit raw video, the FIFO is split into channel A and B, as shown in

Figure 1–3. Each FIFO is clocked independently with the channel A FIFO

receiving data from the VDIN[9–0] half of the bus and the channel B FIFO

receiving data from the VDIN[19–10] half of the bus. Each channel’s FIFO has

a separate write pointer and read register (YSRCx). The FIFO configuration

is identical for TSI capture, but channel B is disabled.

Figure 1–3. 8/10-Bit Raw Video Capture and TSI Video Capture FIFO Configuration

Capture FIFO A

VDIN[9–0]

8/10

64

Buffer A (2560 bytes)

YSRCA

VDIN[19–10]

8/10

Capture FIFO B

Buffer B (2560 bytes)

64

YSRCB

1-7OverviewSPRU629

Page 25

Video Port FIFO

For Y/C video capture, the FIFO is configured as a single channel split into separate Y, Cb, and Cr buffers with separate write pointers and read registers

(YSRCA, CBSRCA, and CRSRCA). Figure 1–4 shows how Y data is received

on the VDIN[9–0] half of the bus and Cb/Cr data is received on the

VDIN[19–10] half of the bus and demultiplexed into the Cb and Cr buffers.

Figure 1–4. Y/C Video Capture FIFO Configuration

Capture FIFO

VDIN[9–0]

VDIN[19–10]

8/10

8/10

8/10

Y Buffer (2560 bytes)

Cb Buffer (1280 bytes)

Cr Buffer (1280 bytes)

64

64

64

YSRCA

CBSRCA

CRSRCA

Overview1-8 SPRU629

Page 26

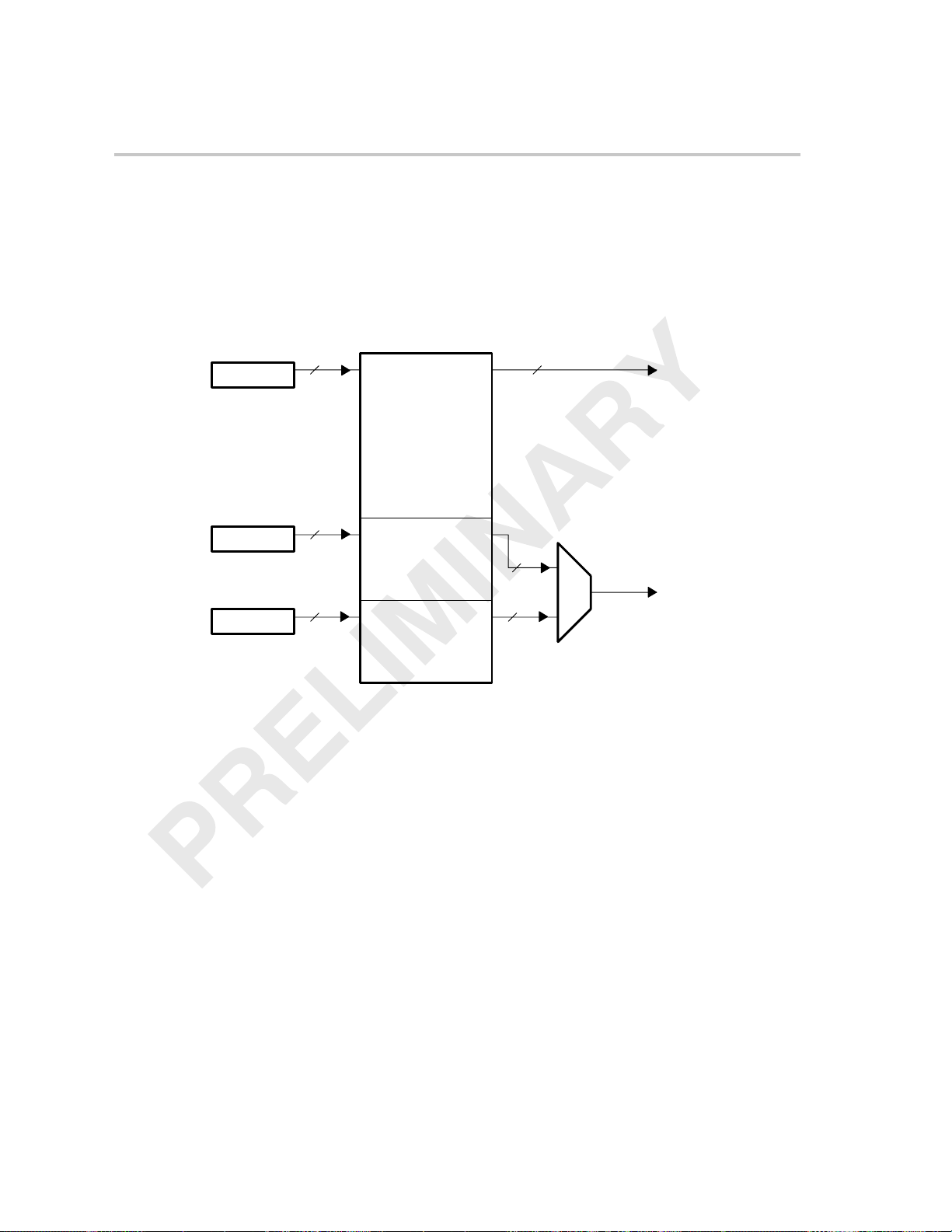

For 16/20-bit raw video, the FIFO is configured as a single buffer, as shown

in Figure 1–5. The FIFO receives 16/20-bit data from the VDIN[19–0] bus. The

FIFO has a single write pointer and read register (YSRCA).

Figure 1–5. 16/20-Bit Raw Video Capture FIFO Configuration

Capture FIFO

VDIN[19–0]

16/20

Data Buffer

(5120 bytes)

64

Video Port FIFO

YSRCA

1.2.3 Video Display FIFO Configurations

During video display operation, the video port FIFO has one of five configurations depending on the display mode. For BT.656 operation, a single output

is provided on channel A, as shown in Figure 1–6, with data output on

VDOUT[9–0]. The channel’s FIFO is split into Y, Cb, and Cr buffers with

separate read pointers and write registers (YDSTA, CBDST, and CRDST).

Figure 1–6. BT.656 Video Display FIFO Configuration

Display FIFO

YDSTA

CBDST

CRDST

64

64

64

Y Buffer

(2560 bytes)

Cb Buffer

(1280 bytes)

Cr Buffer

(1280 bytes)

8/10

VDOUT[9–0]

8/10

8/10

1-9OverviewSPRU629

Page 27

Video Port FIFO

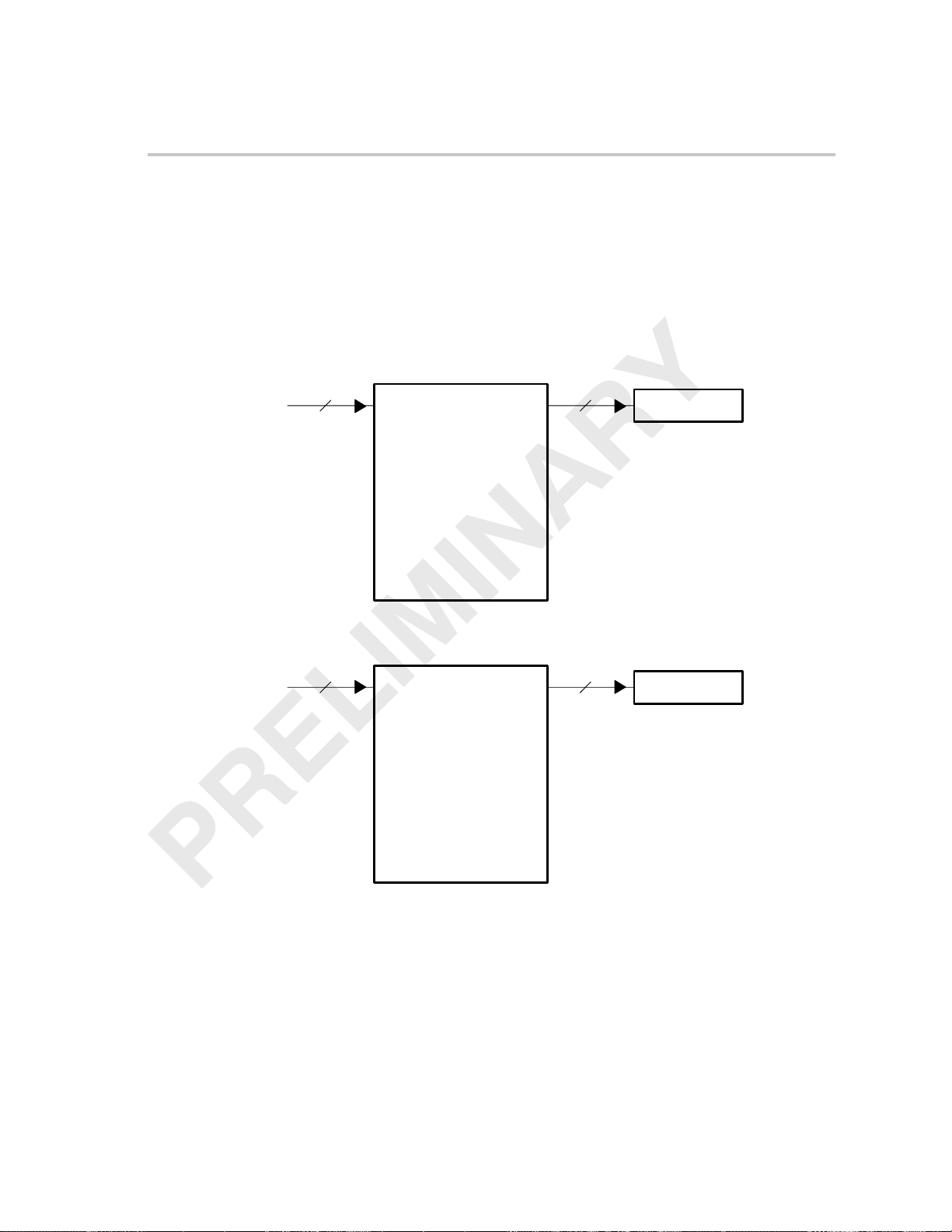

For 8/10-bit raw video, the FIFO is configured as a single buffer as shown in

Figure 1–7. The FIFO outputs data on the VDOUT[9–0] half of the bus. The

FIFO has a single read pointer and write register (YDSTA).

Figure 1–7. 8/10-Bit Raw Video Display FIFO Configuration

Display FIFO

YDSTA

64

Data Buffer

(5120 bytes)

For locked raw video, the FIFO is split into channel A and B. The channels are

locked together and use the same clock and control signals. Each channel

uses a single buffer and write register (YDSTx) as shown in Figure 1–8.

VDOUT[9–0]

8/10

Overview1-10 SPRU629

Page 28

Figure 1–8. 8/10 Bit Locked Raw Video Display FIFO Configuration

Display FIFO A

YDSTA

YDSTB

64 8/10

Buffer A (2560 bytes)

Display FIFO B

64 8/10

Buffer B (2560 bytes)

VDOUT[9–0]

VDOUT[19–10]

Video Port FIFO

For 16/20-bit raw video, the FIFO is configured as a single buffer, as shown

in Figure 1–9. The FIFO outputs data on VDOUT[19–0]. The FIFO has a single

read pointer and write register (YDSTA).

Figure 1–9. 16/20-Bit Raw Video Display FIFO Configuration

Display FIFO

YDSTA

64 16/20

Data Buffer (5120 bytes)

VDOUT[19–0]

1-11OverviewSPRU629

Page 29

Video Port Registers

Video Port FIFO / Video Port Registers

For Y/C video display , the FIFO is configured as a single channel split into separate Y, Cb, and Cr buffers with separate read pointers and write registers

(YDSTA, CBDST, and CRDST). Figure 1–10 shows how Y data is output on