Page 1

PRODUCTPREVIEW

www.ti.com

TMS320C6472 Fixed-Point Digital Signal Processor

1 Features

1

• Six On-Chip TMS320C64x+ Megamodules

• Endianess: Little Endian, Big Endian

• C64x+ Megamodule Main Features:

– High-Performance, Fixed-Point

TMS320C64x+ DSP • 8/16-Bit Transmit and Receive

– 500/625/700 MHz

– Eight 32-Bit Instructions/Cycle

– 4000 MIPS/MMACS (16-Bits) at 500 MHz

– Dedicated SPLOOP Instruction

– Compact Instructions (16-Bit)

– Instruction Set Enhancements

– Exception Handling

– L1/L2 Memory Architecture:

• 256K-Bit (32K-Byte) L1P Program

RAM/Cache [Direct Mapped, Flexible

Allocation]

• 256K-Bit (32K-Byte) L1D RAM/Cache

[2-Way Set-Associative, Flexible

Allocation] – 8 Independent Transmit (TX)

• 4.75M-Bit (608K-Byte) L2 Unified Mapped

RAM/Cache [4-Way Set-Associative, – 8 Independent Receive (RX)

Flexible Allocation] Channels

• L1P Memory Controller • Both EMACs (EMAC0 and EMAC1) Share

• L1D Memory Controller

• L2 Memory Controller

– Time Stamp Counter

– One 64-Bit General-Purpose/Watchdog Timer

• Shared Peripherals and Interfaces

– EDMA Controller

(64 Independent Channels)

– Shared Memory Architecture

• Shared L2 Memory Controller

• 768K-Byte of RAM

• Boot ROM

– Three Telecom Serial Interface Ports (TSIPs)

• Each TSIP is 8 Links of 8 Mbps per

Direction

– 32-Bit DDR2 Memory Controller (DDR2-533

SDRAM)

• 256 M-Byte x 2 Addressable Memory

Space

– Two 1x Serial RapidIO®Links,

v1.2 Compliant

• 1.25-, 2.5-, 3.125-Gbps Link Rates

• Message Passing, DirectIO Support,

Error Management Extensions, and

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCT PREVIEW information concernsproducts in the formative

or design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right

to change ordiscontinue these products withoutnotice.

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Congestion Control

• IEEE 1149.6 Compliant I/Os

– UTOPIA

• UTOPIA Level 2 Slave ATM Controller

Operations up to 50 MHz per Direction

• User-Defined Cell Format up to 64 Bytes

– Two 10/100/1000 Mb/s Ethernet MACs

(EMACs)

• Both EMACs are IEEE 802.3 Compliant

• EMAC0 Supports:

– MII, RMII, SS-SMII, GMII, and RGMII

– 8 Independent Transmit (TX)

Channels

– 8 Independent Receive (RX)

Channels

• EMAC1 Supports:

– RMII, SS-SMII and RGMII

Channels

MDIO Interface

– 16-Bit Host-Port Interface (HPI)

– One Inter-Integrated Circuit (I2C) Bus

– Six Shared 64-Bit General-Purpose Timers

• System PLL and PLL Controller

• Secondary PLL and PLL Controller, Dedicated

to EMAC

• Third PLL and PLL Controller Dedicated to

DDR2 Memory Controller

• 16 General-Purpose I/O (GPIO) Pins

• IEEE-1149.1 (JTAG™)

Boundary-Scan-Compatible

• 737-Pin Ball Grid Array (BGA) Package

(ZTZ Suffix), 0.8-mm Ball Pitch

• 0.09-mm/7-Level Cu Metal Process (CMOS)

• 3.3-, 1.8-, 1.5-, 1.2-V I/O Supplies

• 1.0-/1.1-, 1.2-V Core Supplies

• Commercial Temperature [0°C to 85°C]

• Extended Temperature [-40°C to 100°C]

Copyright © 2009–2010, Texas Instruments Incorporated

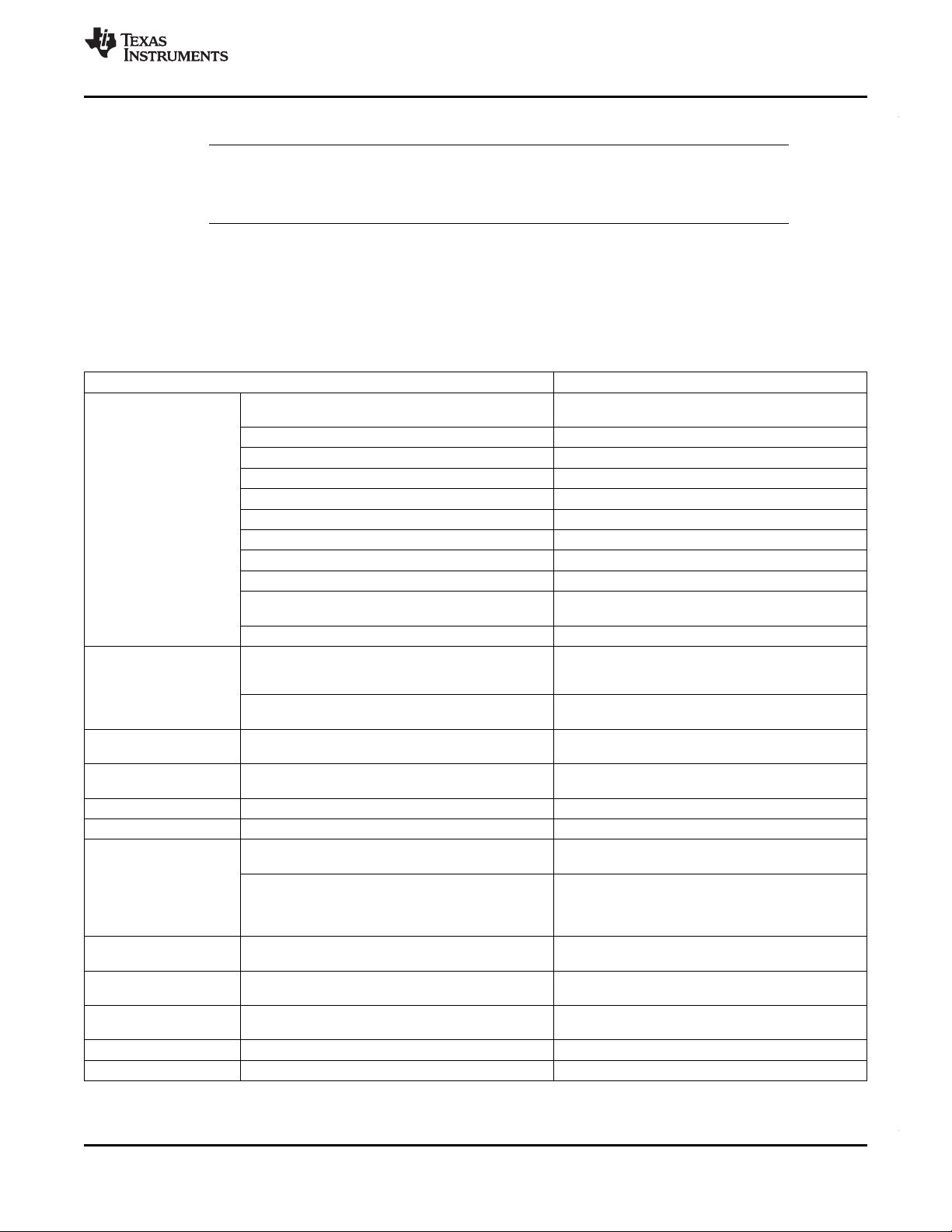

Page 2

PRODUCTPREVIEW

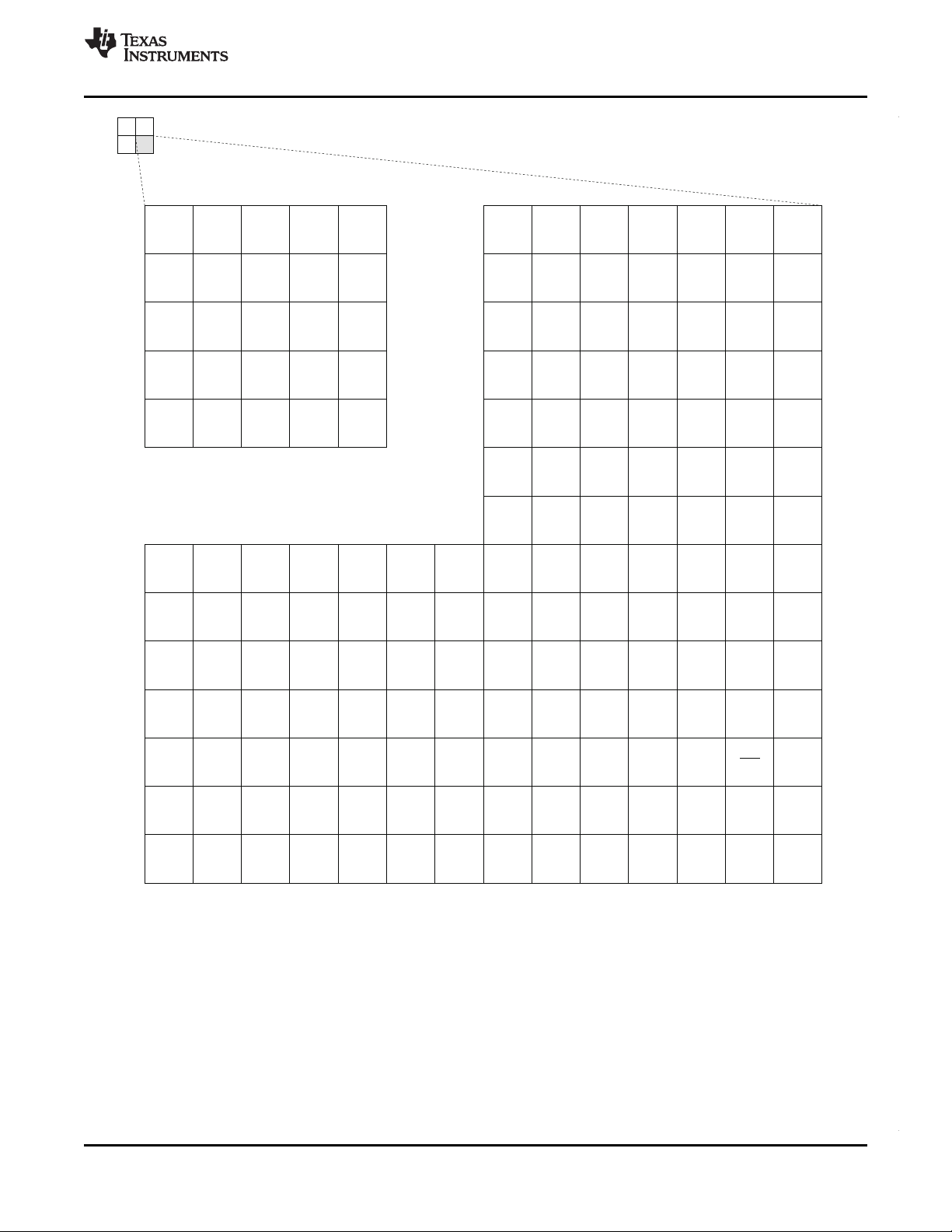

A

2

B

1 345678910111213141516171819202122232425

26

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

272829

AG

AH

AJ

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

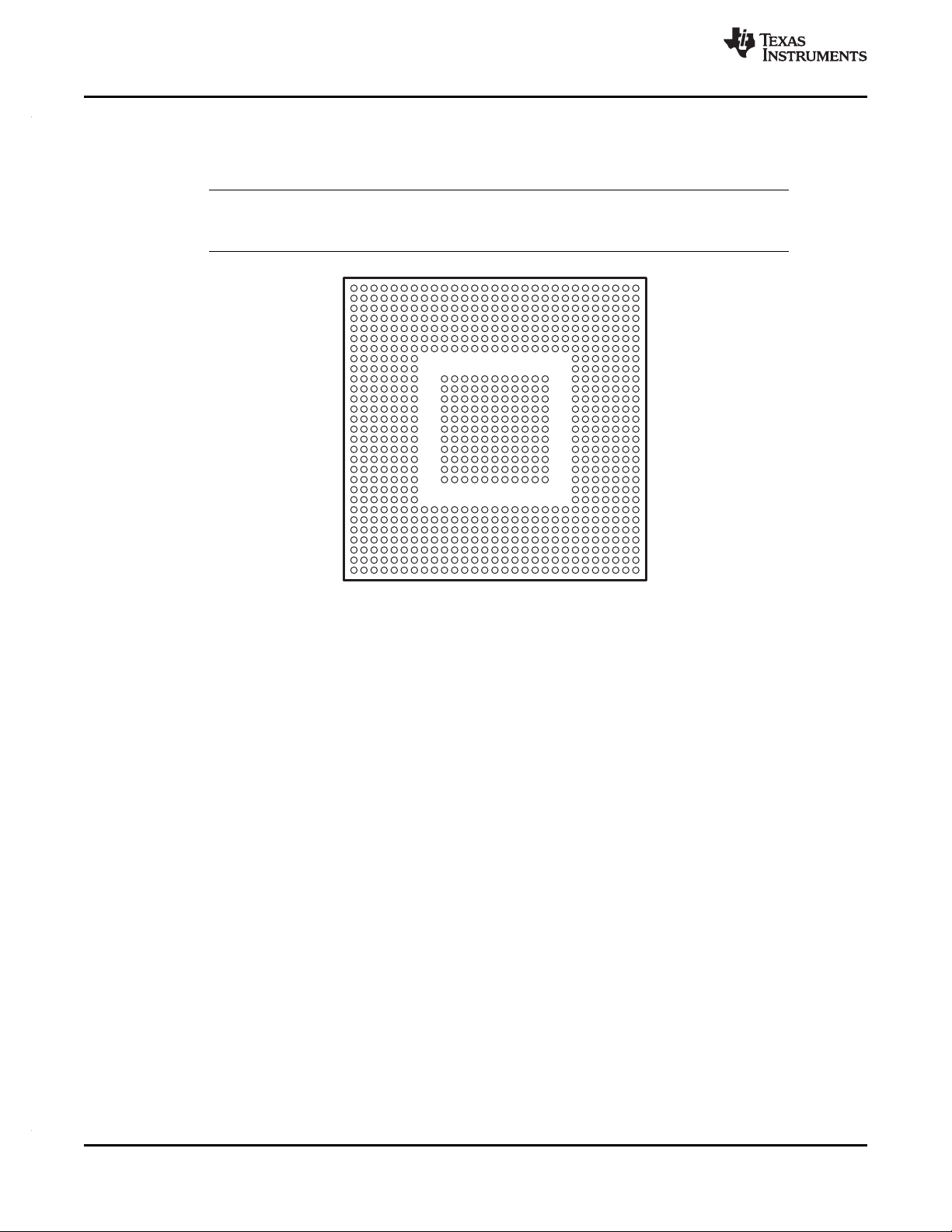

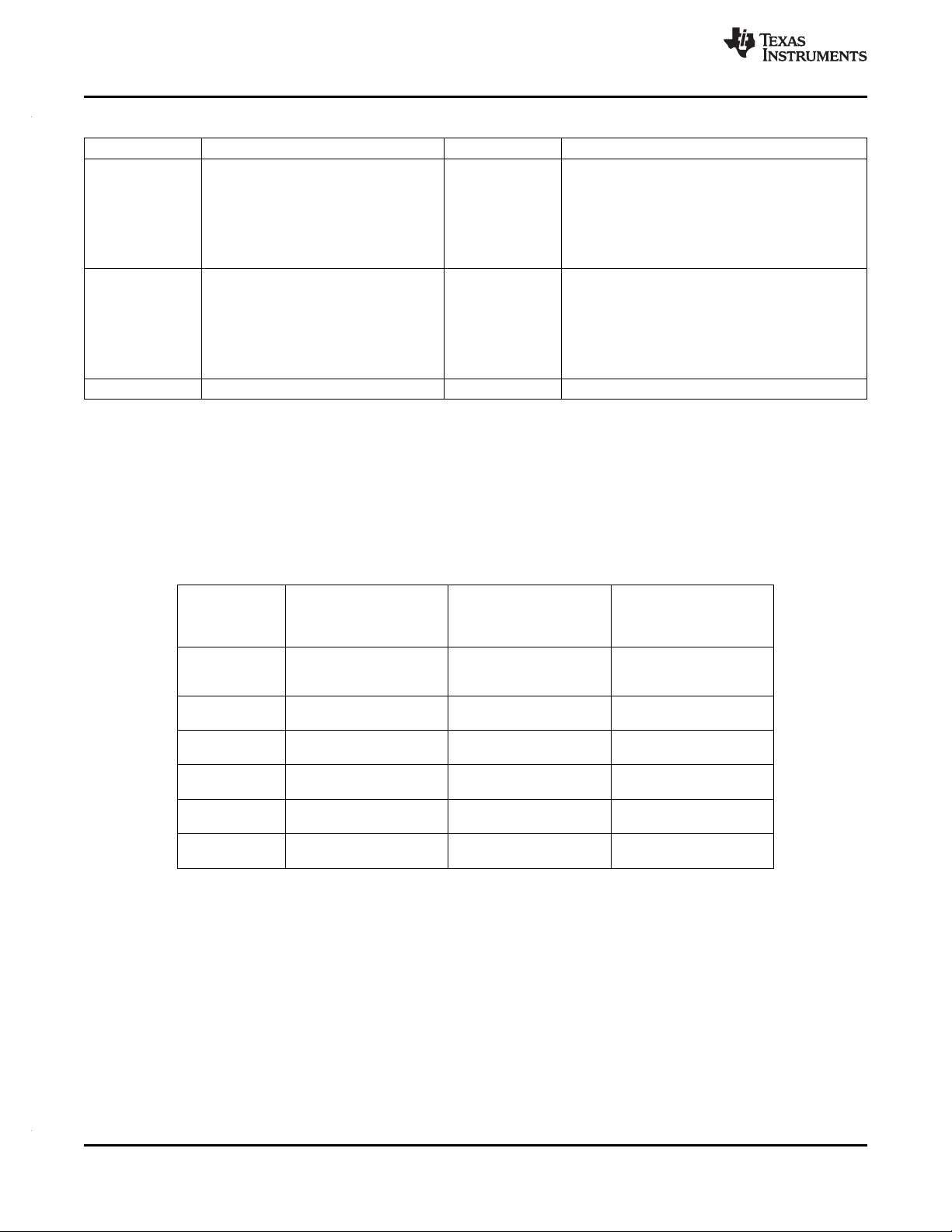

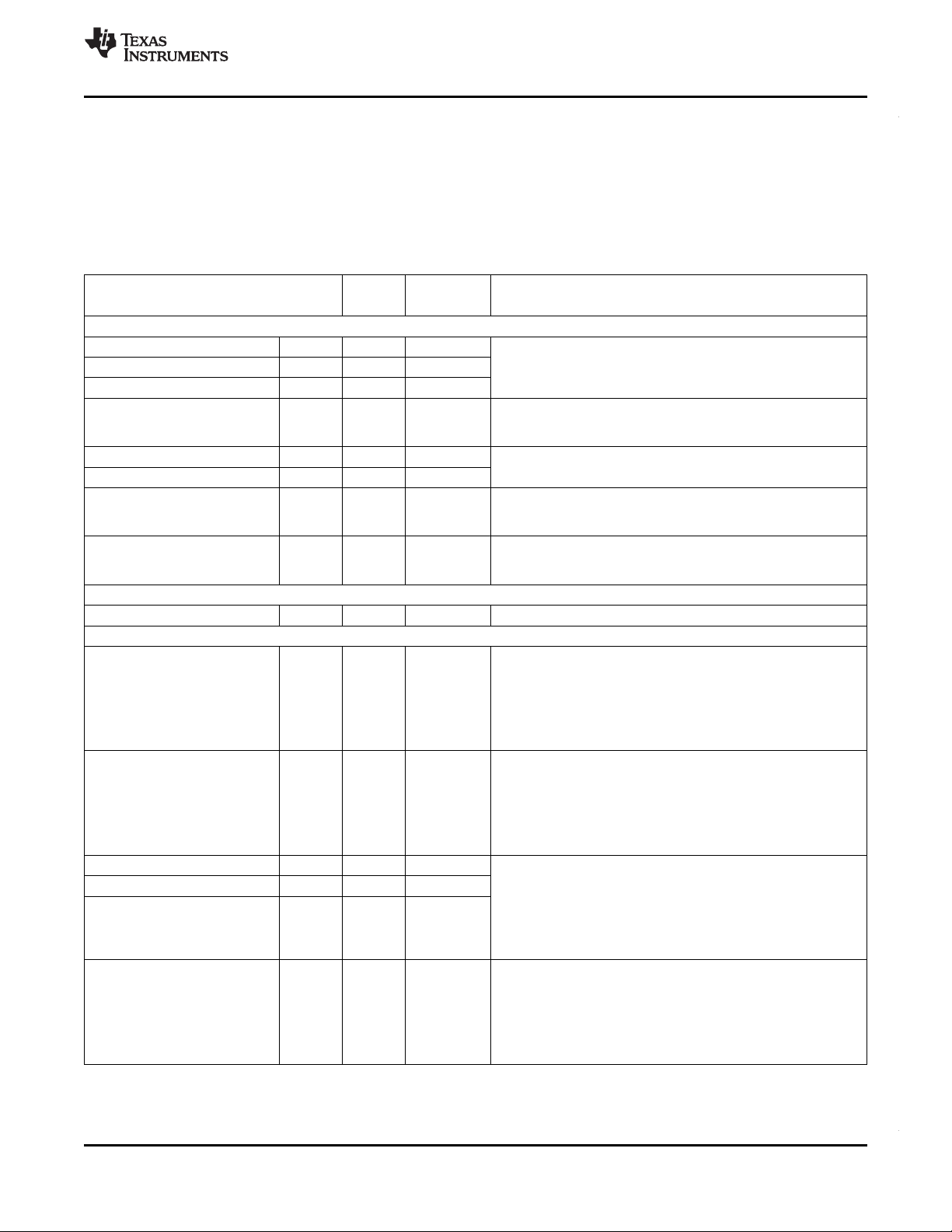

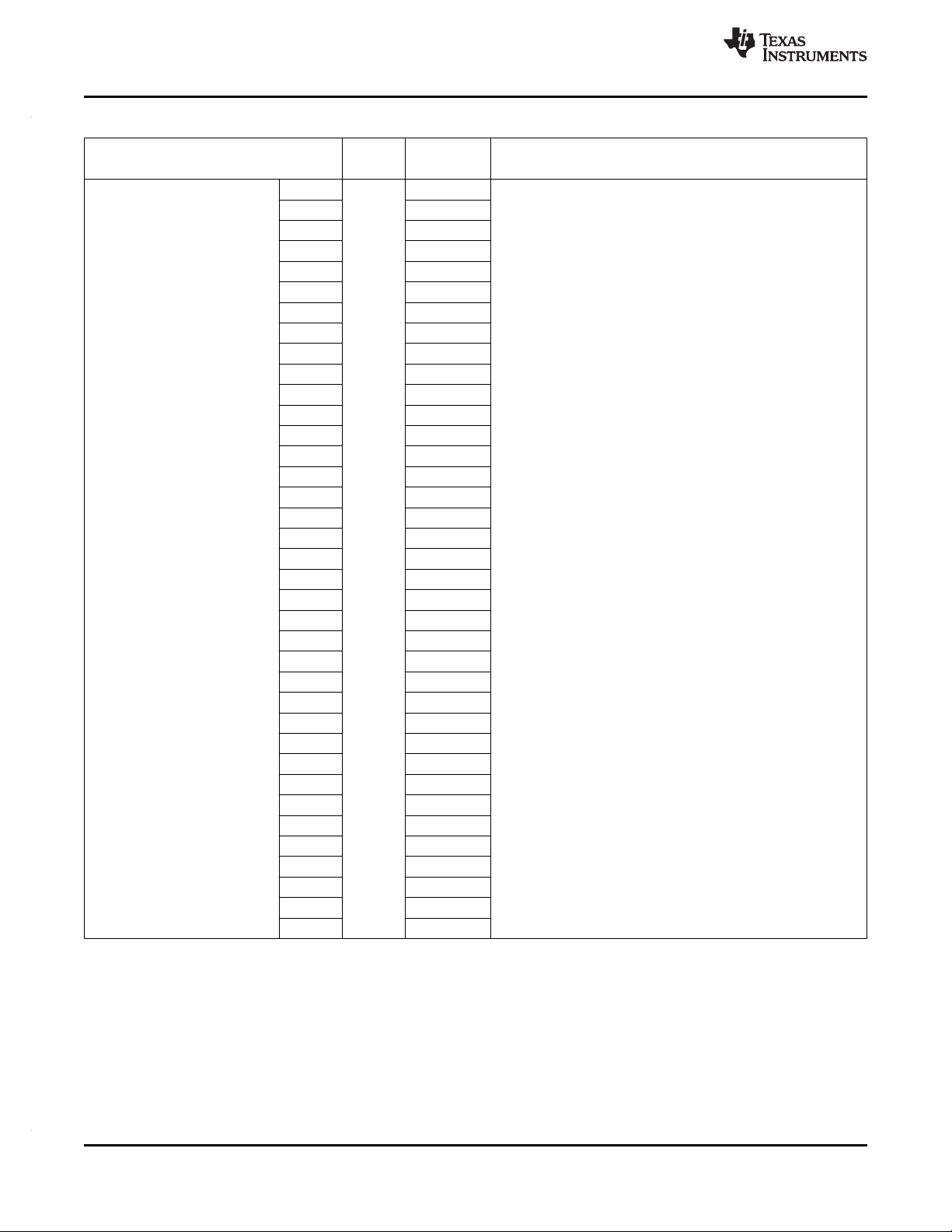

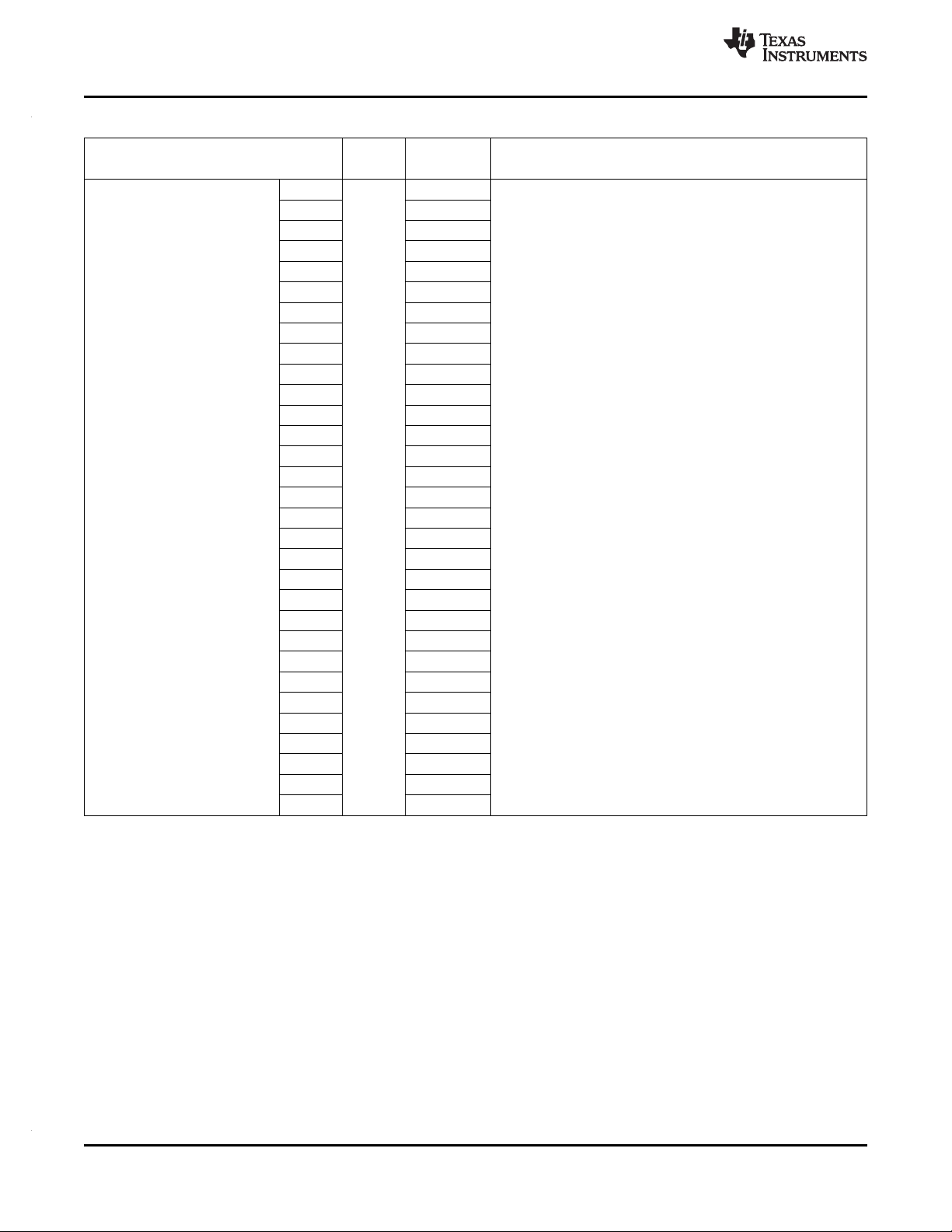

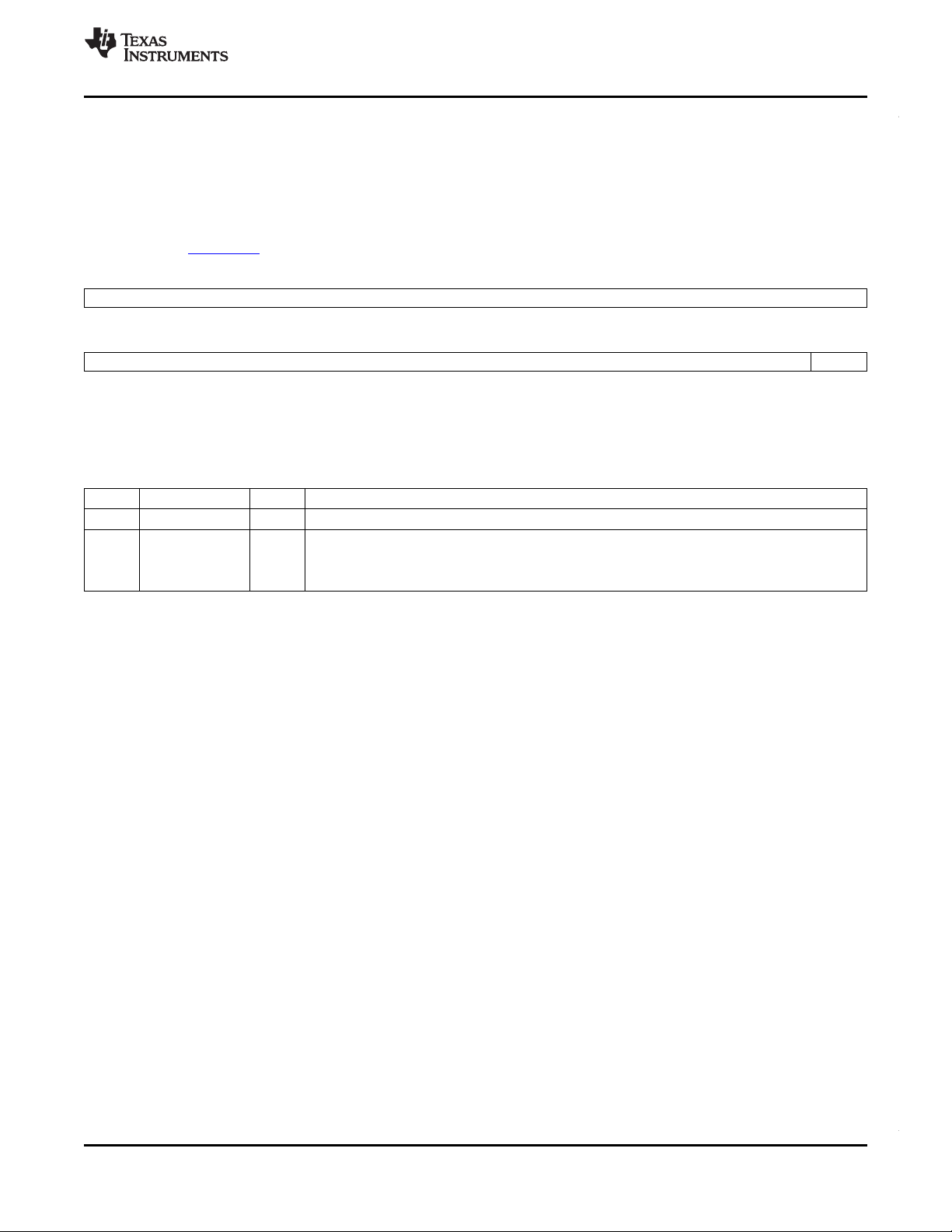

1.1 ZTZ BGA Package (Bottom View)

The TMS320C6472 devices are designed for a package temperature range of 0°C to 85°C (commercial

temperature range) or -40°C to 100°C (extended temperature range).

Extended temperature (A) range is available only on 500-MHz and 625-MHz devices.

www.ti.com

NOTE

Figure 1-1. ZTZ 737-Pin Ball Grid Array (BGA) Package (Bottom View)

2 Features Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 3

PRODUCTPREVIEW

www.ti.com

1.2 Description

The TMS320C6472 device is a Texas Instruments next-generation fixed-point digital signal processor

(DSP) targeting high-performance computing applications, including high-end industrial, mission-critical,

high-end image and video, communication, media gateways, and remote access servers. This device was

designed with these applications in mind. A common key requirement of these applications is the

availability of large on-chip memories to handle vast amounts of data during processing. With 768K-Byte

of shared RAM and 608K-Byte local L2 RAM per C64x+ Megamodule, the TMS320C6472 device can

eliminate the need for external memory, thereby reducing system power dissipation and system cost and

optimizing board density.

The TMS320C6472 device has six optimized TMS320C64x+™ megamodules, which combine high

performance with the lowest power dissipation per port. The TMS320C6472 device includes three different

speeds: 500 MHz, 625 MHz, and 700 MHz. The C64x+ megamodules are the highest-performance

fixed-point DSP generation in the TMS320C6000™ DSP platform. The C64x+ megamodule is based on

the third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture

developed by Texas Instruments (TI), making devices like TMS320C6472 an excellent choice for

applications including video and telecom infrastructure, imaging/medical, and wireless infrastructure (WI).

The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™

DSP platform.

The C64x+ megamodule core employs eight functional units, two register files, and two data paths. Like

the earlier C6000 devices, two of these eight functional units are multipliers or .M units. Each C64x+

megamodule core .M unit doubles the multiply throughput versus the C64x core by performing four

16-bit x 16-bit multiply-accumulates (MACs) every clock cycle. Thus, eight 16-bit x 16-bit MACs can be

executed every cycle on the C64x+ core. At a 500-MHz clock rate, this means 4000 16-bit MMACs can

occur every second. Moreover, each multiplier on the C64x+ megamodule core can compute one

32-bit x 32-bit MAC or four 8-bit x 8-bit MACs every clock cycle.

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

The C64x+ megamodule integrates a large amount of on-chip memory organized as a two-level memory

system. The level-1 (L1) program and data memories on this C64x+ megamodule are 32KB each. This

memory can be configured as mapped RAM, cache, or some combination of the two. When configured as

cache, L1 program (L1P) is a direct mapped cache where as L1 data (L1D) is a two-way set associative

cache. The level 2 (L2) memory is shared between program and data space and is 608K-Byte in size. L2

memory can also be configured as mapped RAM, cache, or some combination of the two. The C64x+

megamodule also has a 32-bit peripheral configuration (CFG) port, an internal DMA (IDMA) controller, a

system component with reset/boot control, interrupt/exception control, a power-down control, and a

free-running 32-bit timer for time stamp.

The peripheral set includes: three Telecom Serial Interface Port (TSIPs); an 16/8 bit Universal Test and

Operations PHY Interface for Asynchronous Transfer Mode (ATM) Slave [UTOPIA Slave] port; two

10/100/1000 Ethernet media access controllers (EMACs), which provide an efficient interface between the

C6472 DSP core processor and the network; a management data input/output (MDIO) module (shared by

both EMACs) that continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the

system; a Serial RapidIO®with two 1x lanes and support for packet forwarding; a 32-bit DDR2 SDRAM

interface; 12 64-bit general-purpose timers; an inter-integrated circuit bus module (I2C); 16

general-purpose input/output ports (GPIO) with programmable interrupt/event generation modes; and a

16-bit multiplexed host-port interface (HPI16).

The C6472 device has a complete set of development tools which includes: a C compiler, an assembly

optimizer to simplify programming and scheduling, and a Windows®debugger interface for visibility into

source code execution.

Copyright © 2009–2010, Texas Instruments Incorporated Features 3

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 4

PRODUCTPREVIEW

imerx[6thru11](A)

DSP Subsystem5

imerx[6thru11](A)

DSP Subsystem4

imerx[6thru11](A)

DSP Subsystem3

imerx[6thru11](A)

DSP Subsystem2

Timerx[6thru11](A)

DSP Subsystem1

Timerx[0-5]

(B)

EMAC1

SS-SMII

RGMII

Serial

RapidIO

DDR2

Memory

Controller

Power-Down

Logic

DSP Subsystem0

PLL1and

PLL1Controller

BootConfiguration

UTOPIA (16/8)

I2C

GPIO16

16

TSIP0

SharedL2Controller

TSIP1

HPI(16-bit)

DDR2

SDRAM

32

Timerx[6-11]

(Shared)

(A)(B)

PLL3and

PLL3

Controller

EDMA 3.0

System

©

)

PowerControl

C64x+DSP Core

DataPathB

BRegisterFile

InstructionFetch

DataPath A

A RegisterFile

.L1 .S1

.M1

xx

xx

.D1 .D2 .S2 .L2

InternalDMA

(IDMA)

L1P MemoryController (Memory Protect/BandwidthMgmt)

Instruction

Decode

16-/32-bit

InstructionDispatch

ControlRegisters

In-CircuitEmulation

SPLOOP Buffer

L1D MemoryController(MemoryProtect/BandwidthMgmt)

InterruptandExceptionController

EMAC0

32KBytes

L1P SRAM/Cache

Direct-Mapped

TSIP2

PLL2and

PLL2Controller

L2 SRAM/Cache

608KBytes

4-WaySet Assoc.

A31-A16

A15-A0

B31-B16

B15-B0

SS-SMII

GMII

MII

RGMII

RMII

32K-Bytes Total

L1DSRAM/Cache2-Way

Set-Associative

M

e

g

a

m

o

d

u

l

e

.M2

xx

xx

SL2RAM768K-Bytes

BootROM

L2MemoryController

(MemoryProtect/

BandwidthMgmt)

SwitchedCentralResource(SCR)

MDIO

RMII

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

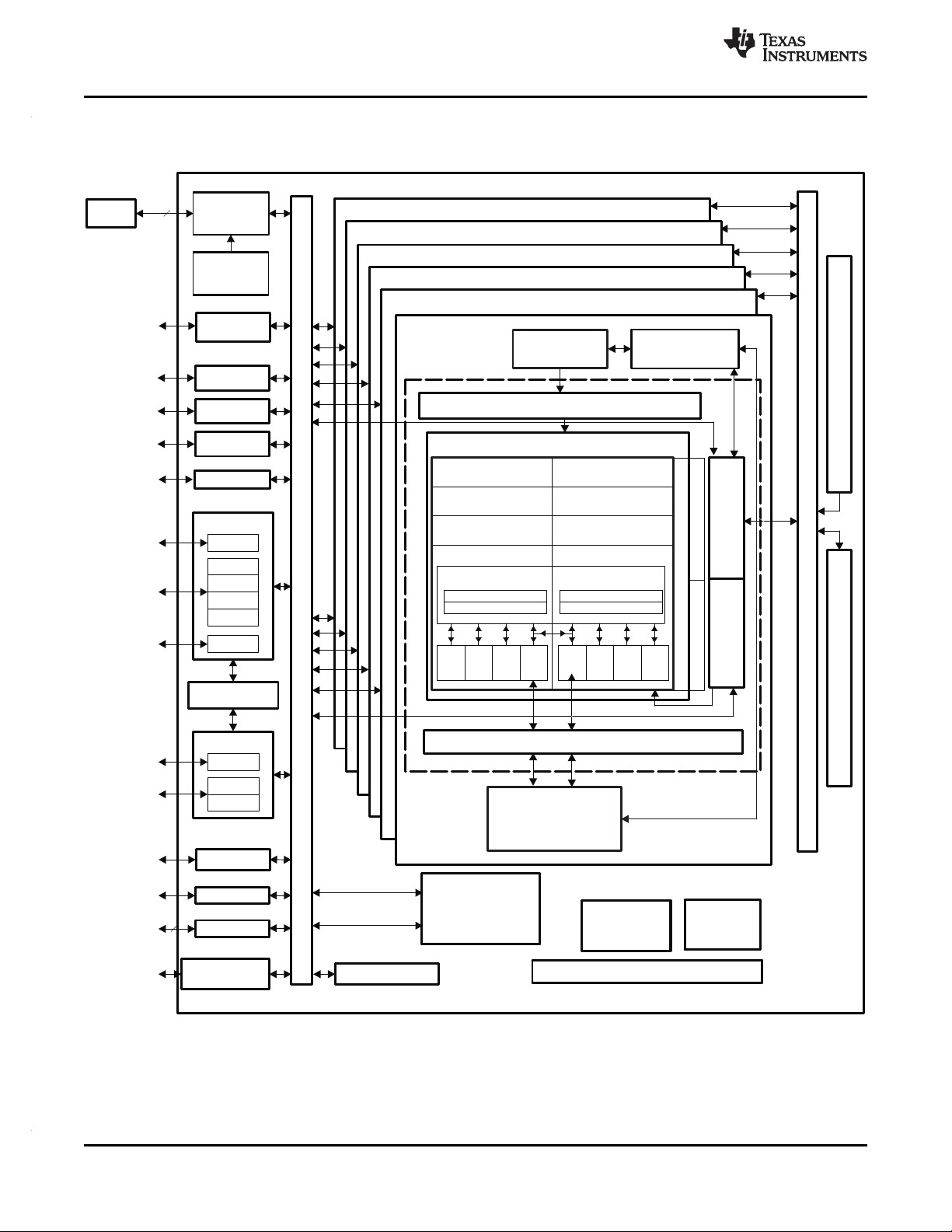

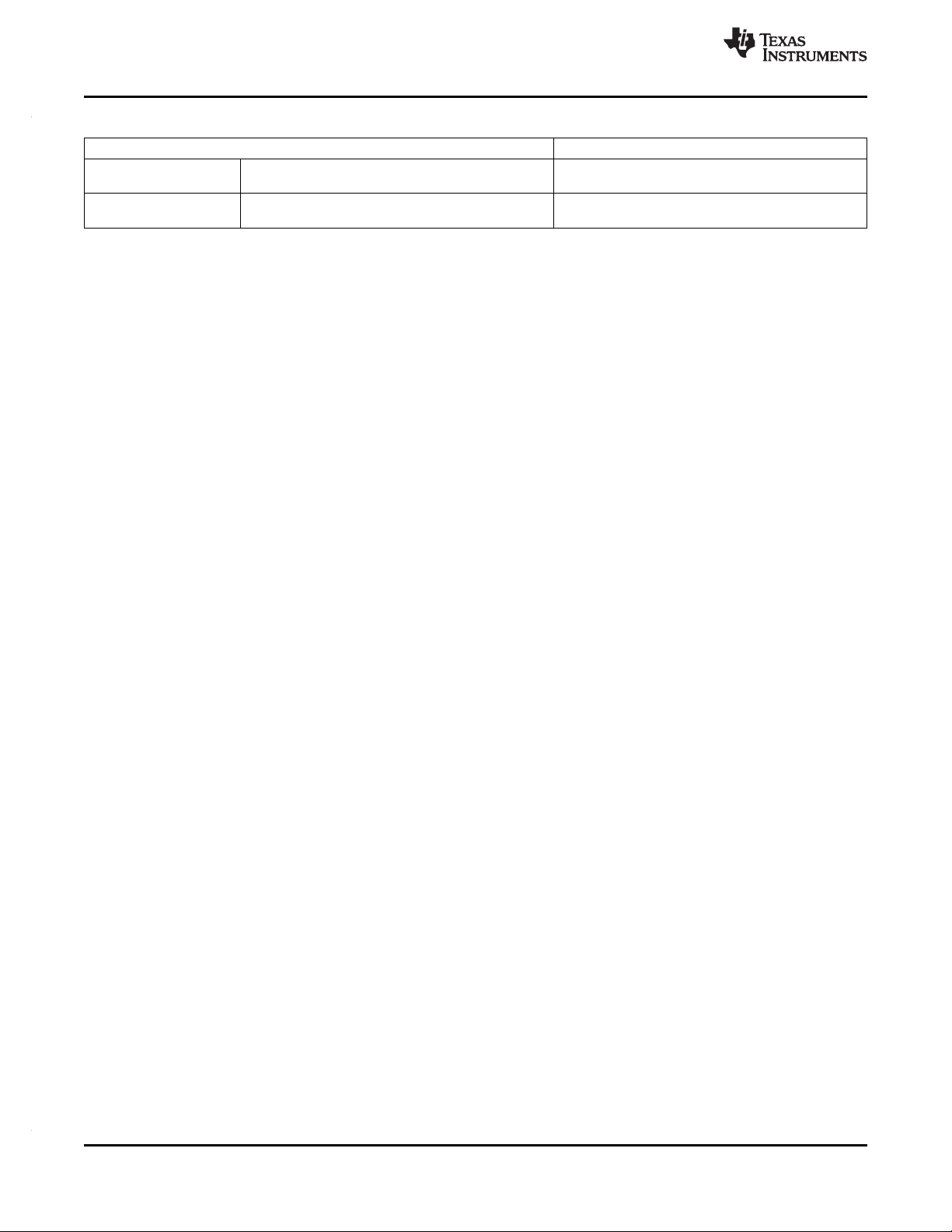

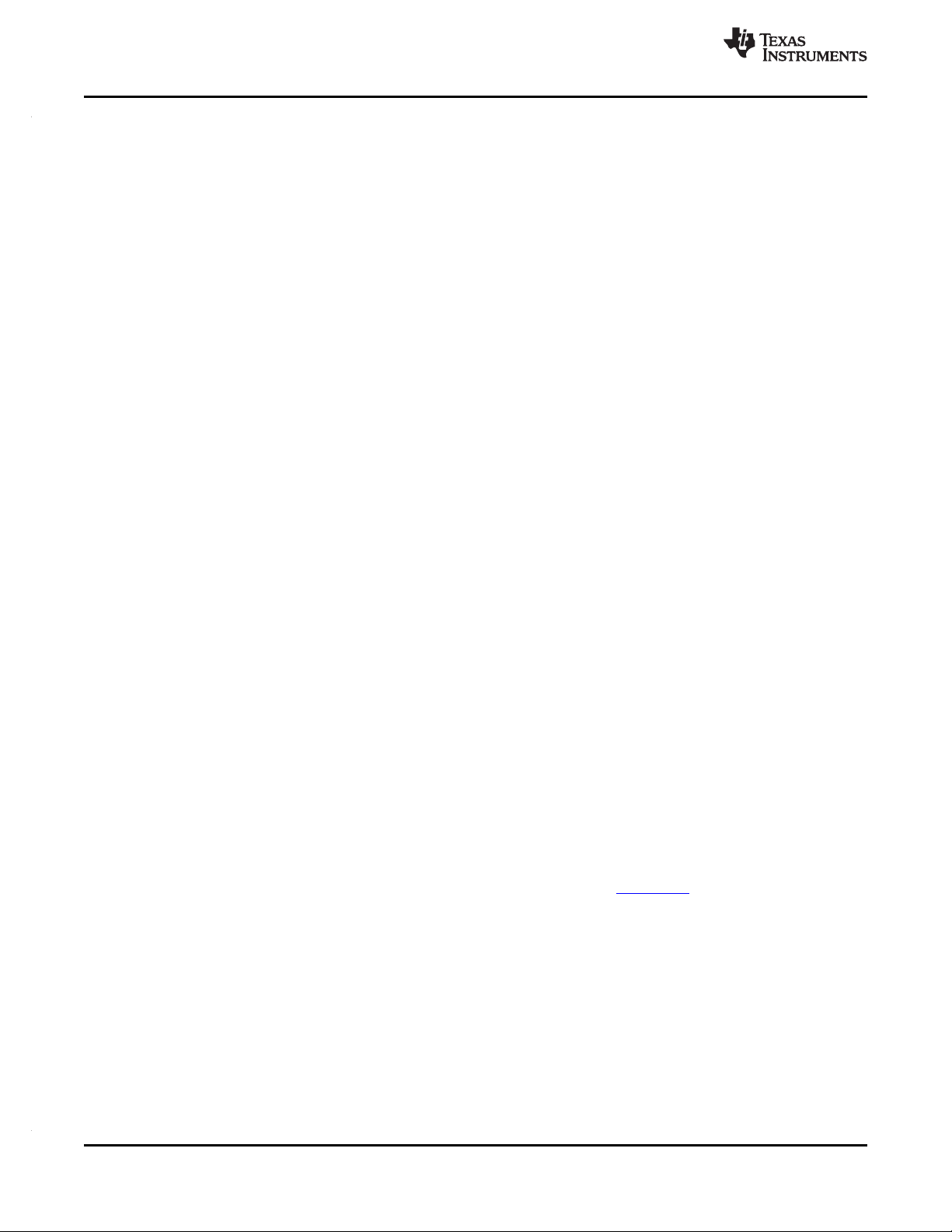

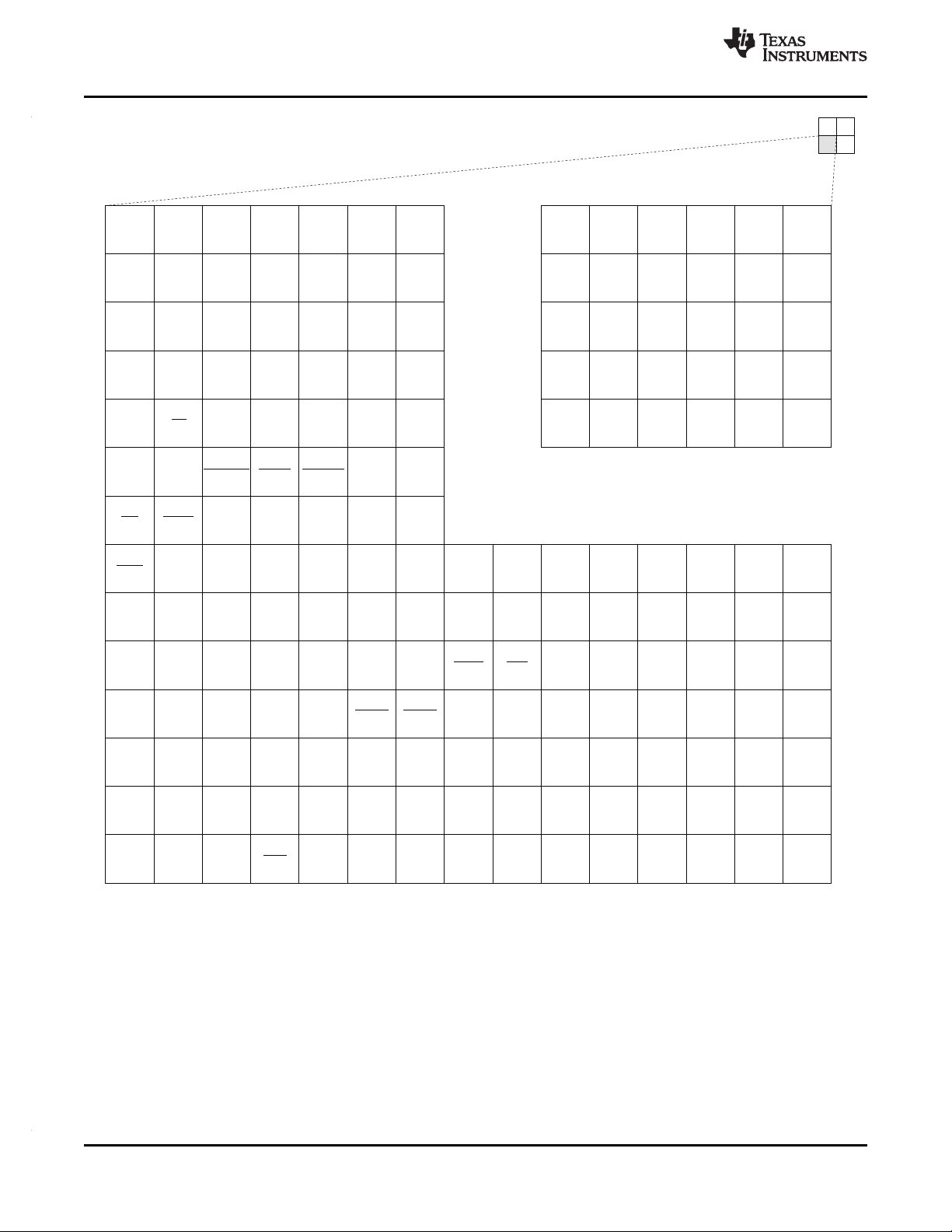

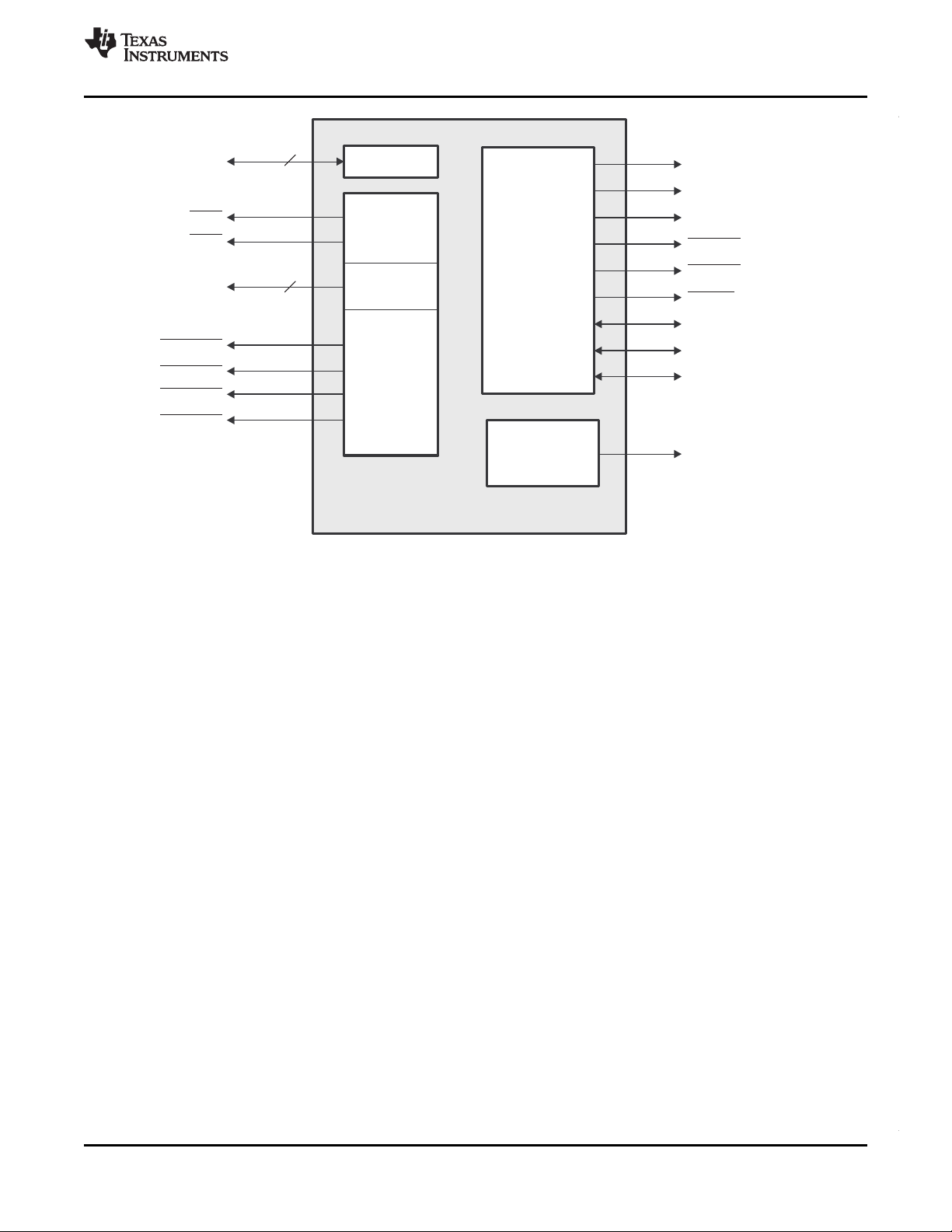

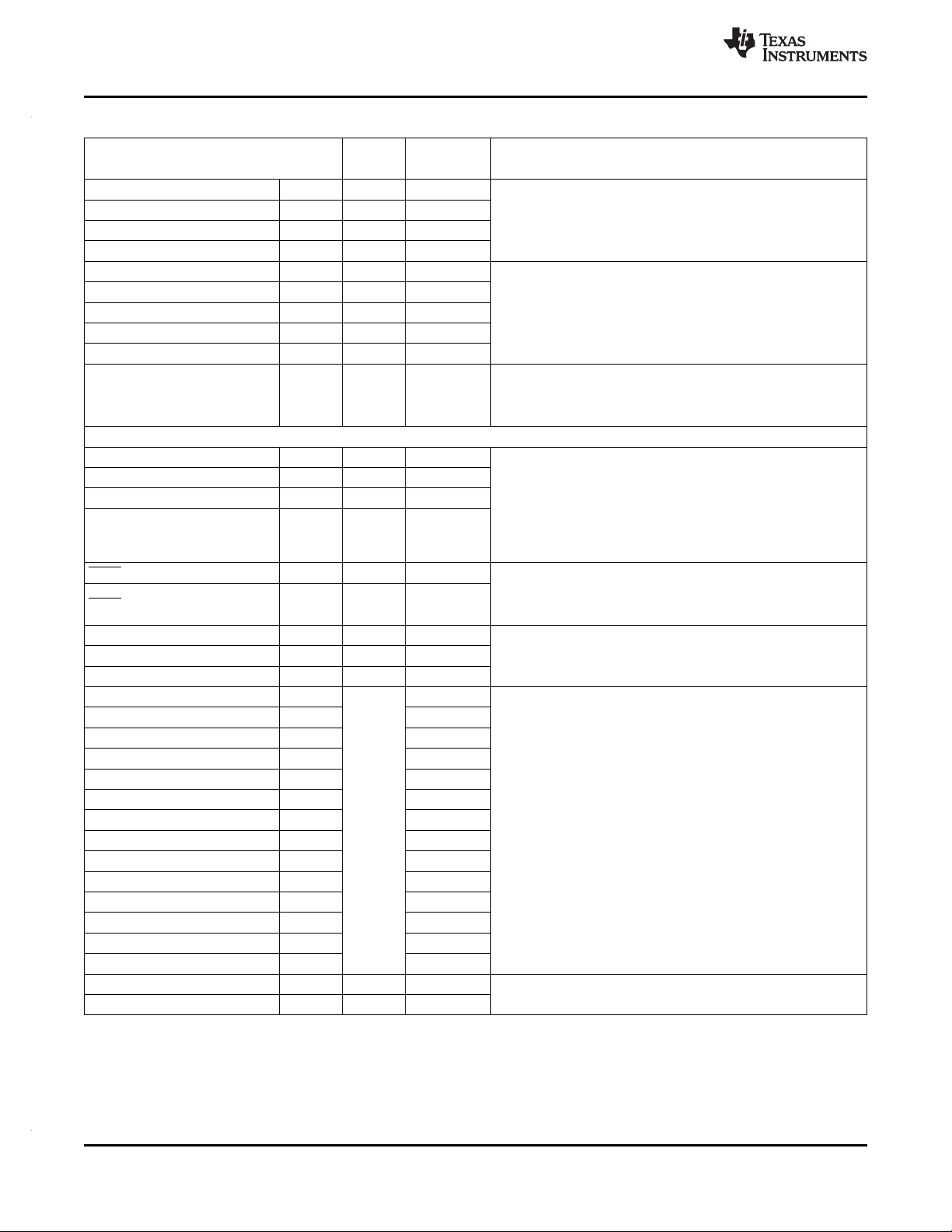

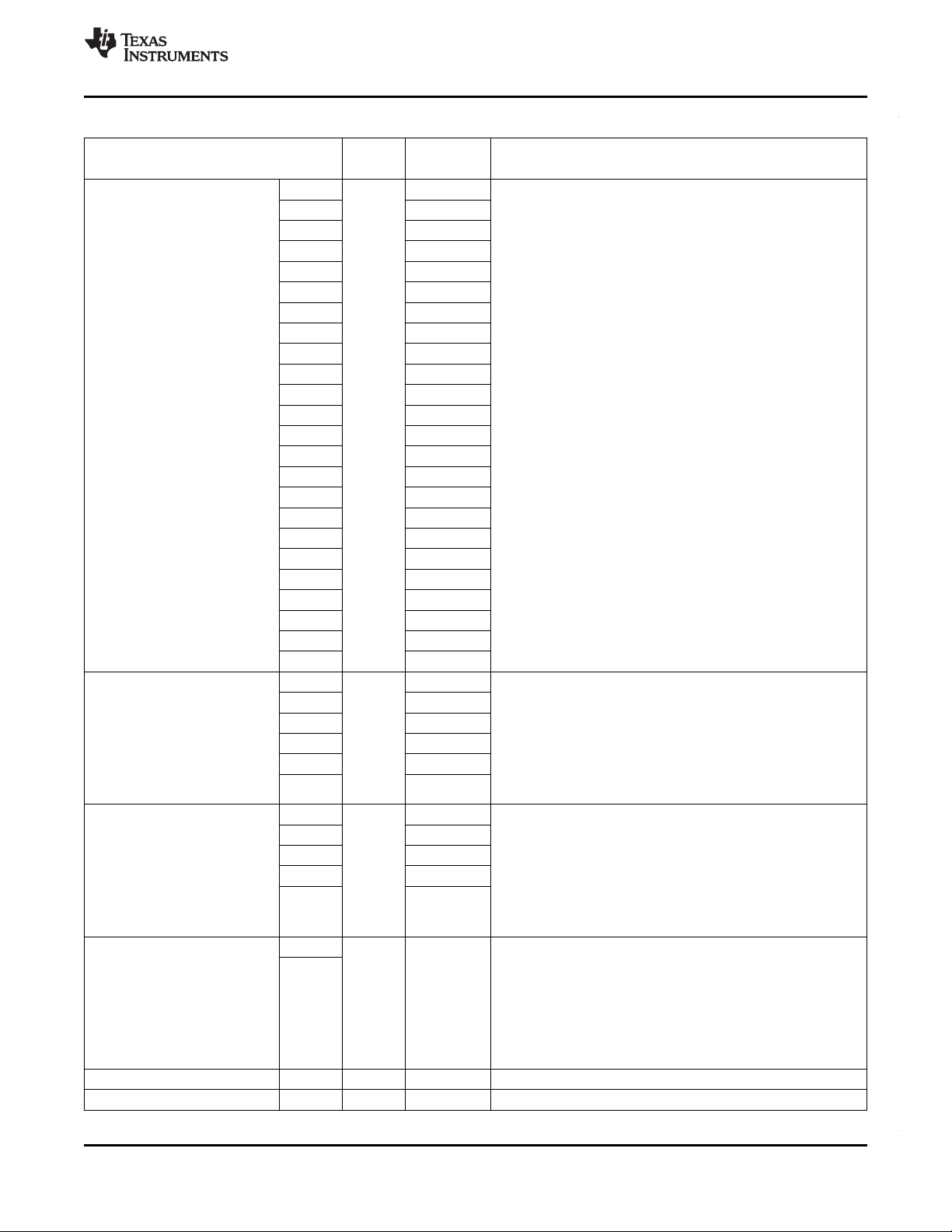

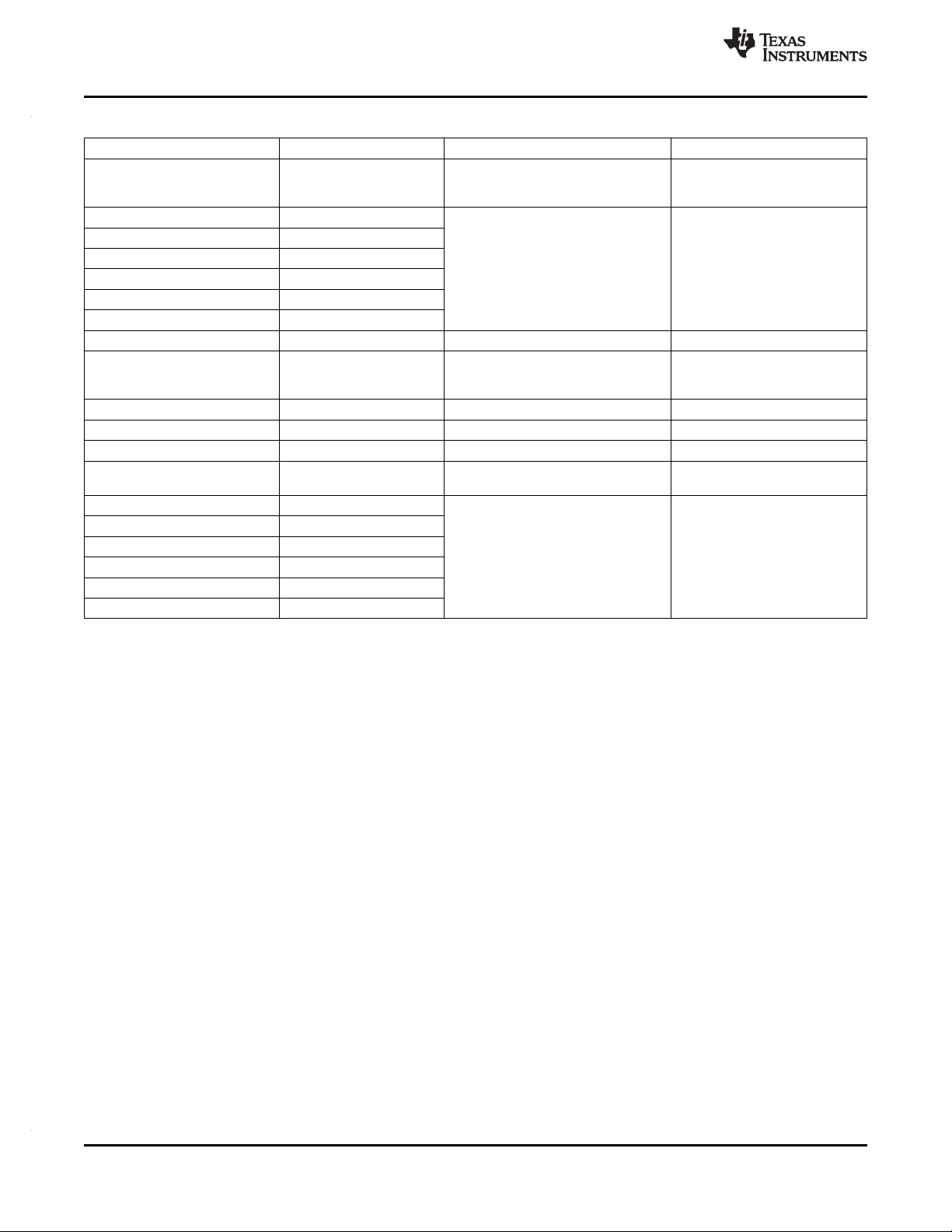

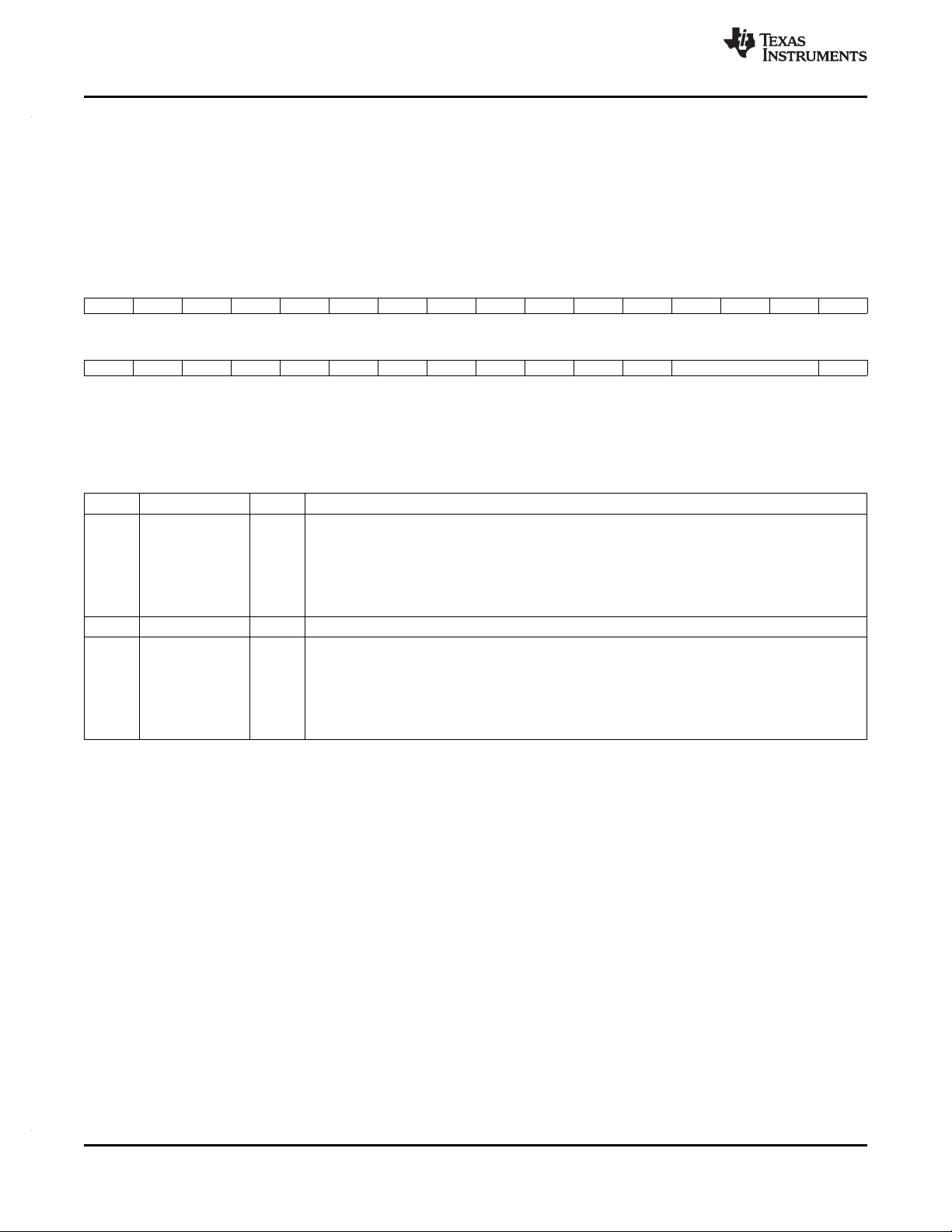

1.3 Functional Block Diagram

Figure 1-2 shows the functional block diagram of the C6472 device.

www.ti.com

A. Timers 6-11 are shared.

B. Each of the Timer peripherals are configurable as either one 64-bit general-purpose timer or two 32-bit

general-purpose timers or a watchdog timer.

C. System consists of Test, Emulation, Power Down, and Interrupt Controller.

4 Features Copyright © 2009–2010, Texas Instruments Incorporated

Figure 1-2. C6472 Functional Block Diagram

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 5

PRODUCTPREVIEW

www.ti.com

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

1 Features ................................................... 1

1.1 ZTZ BGA Package (Bottom View) ................... 2

1.2 Description ........................................... 3

1.3 Functional Block Diagram ............................ 4

Revision History .............................................. 6

2 Device Overview ........................................ 7

2.1 Device Characteristics ............................... 7

2.2 CPU (DSP Core) Description ........................ 8

2.3 Memory Map Summary ............................. 11

2.4 Boot Mode Sequence .............................. 14

2.5 Pin Assignments .................................... 19

2.6 Signal Groups Description .......................... 23

2.7 Terminal Functions ................................. 29

2.8 Development ........................................ 53

3 Device Configuration ................................. 58

3.1 Device Configuration at Device Reset .............. 58

3.2 Device Configuration Register Descriptions ........ 59

3.3 Peripheral Selection After Device Reset ........... 62

3.4 Device Status Register (DEVSTAT) ................ 72

3.5 RMIIn Reset Registers (RMIIRESET0 and

RMIIRESET1) ...................................... 73

3.6 Memory Privilege Registers ........................ 74

3.7 Host and Inter-DSP Interrupt Registers ............ 77

3.8 Timer Event Manager Registers .................... 82

3.9 Reset and Boot Registers .......................... 84

3.10 JTAG ID Register Description ...................... 88

3.11 Silicon Revision ID Register Description ........... 88

4 System Interconnect .................................. 89

4.1 Internal Buses, Bridges, and Switch Fabrics ....... 89

4.2 Data Switch Fabric Connections ................... 90

4.3 Priority Allocation ................................... 93

4.4 Configuration Switch Fabric ........................ 93

5 C64x+ Megamodule ................................... 95

5.1 Memory Architecture ............................... 95

5.2 Memory Protection Support ........................ 99

5.3 Bandwidth Management .......................... 100

5.4 Power-Down Control .............................. 101

5.5 Megamodule Resets .............................. 101

5.6 Megamodule Revision ............................. 102

5.7 C64x+ Megamodule Register Descriptions ....... 103

5.8 CPU Revision ID .................................. 111

6 Device Operating Conditions ...................... 112

6.1 Absolute Maximum Ratings Over Operating Case

Temperature Range (Unless Otherwise Noted)

..................................................... 112

6.2 Recommended Operating Conditions ............. 113

6.3 Electrical Characteristics Over Recommended

Ranges of Supply Voltage and Operating Case

Temperature (Unless Otherwise Noted) .......... 115

7 C64x+ Peripheral Information and Electrical

Specifications ......................................... 117

7.1 Parameter Information ............................ 117

7.2 Recommended Clock and Control Signal Transition

Behavior ........................................... 118

7.3 Power Supplies .................................... 118

7.4 Power and Sleep Controller (PSC) ................ 120

7.5 Enhanced Direct Memory Access (EDMA3)

Controller .......................................... 123

7.6 Interrupts .......................................... 136

7.7 Reset Controller ................................... 140

7.8 PLL1 and PLL1 Controller ......................... 148

7.9 PLL2 and PLL2 Controller ......................... 160

7.10 PLL3 and PLL3 Controller ......................... 171

7.11 DDR2 Memory Controller ......................... 175

7.12 I2C Peripheral ..................................... 177

7.13 Host-Port Interface (HPI) Peripheral .............. 182

7.14 TSIP ............................................... 189

7.15 Ethernet MAC (EMAC) ............................ 215

7.16 Timers ............................................. 236

7.17 UTOPIA ........................................... 242

7.18 Serial RapidIO (SRIO) Port ....................... 247

7.19 General-Purpose Input/Output (GPIO) ............ 258

7.20 Emulation Features and Capability ............... 260

8 Mechanical Data ...................................... 263

8.1 Thermal Data ...................................... 263

8.2 Packaging Information ............................ 263

Copyright © 2009–2010, Texas Instruments Incorporated Contents 5

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 6

PRODUCTPREVIEW

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

This revision history highlights the technical changes made to the document in this revision.

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Section 5.1 Modified L2 memory Port 1 configuration

Added Table 5-1, SL2 Prefetch Enabled Memory Regions

Section 5.2 Modified fourth paragraph on privilege ID assignment

Modified Table 5-3, Available Memory Page Protection Scheme with Privilege ID

www.ti.com

Revision History

C6472 Revisions

6 Contents Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 7

PRODUCTPREVIEW

www.ti.com

2 Device Overview

Unless otherwise noted, all address locations in this document are stated in hexidecimal

numbers.

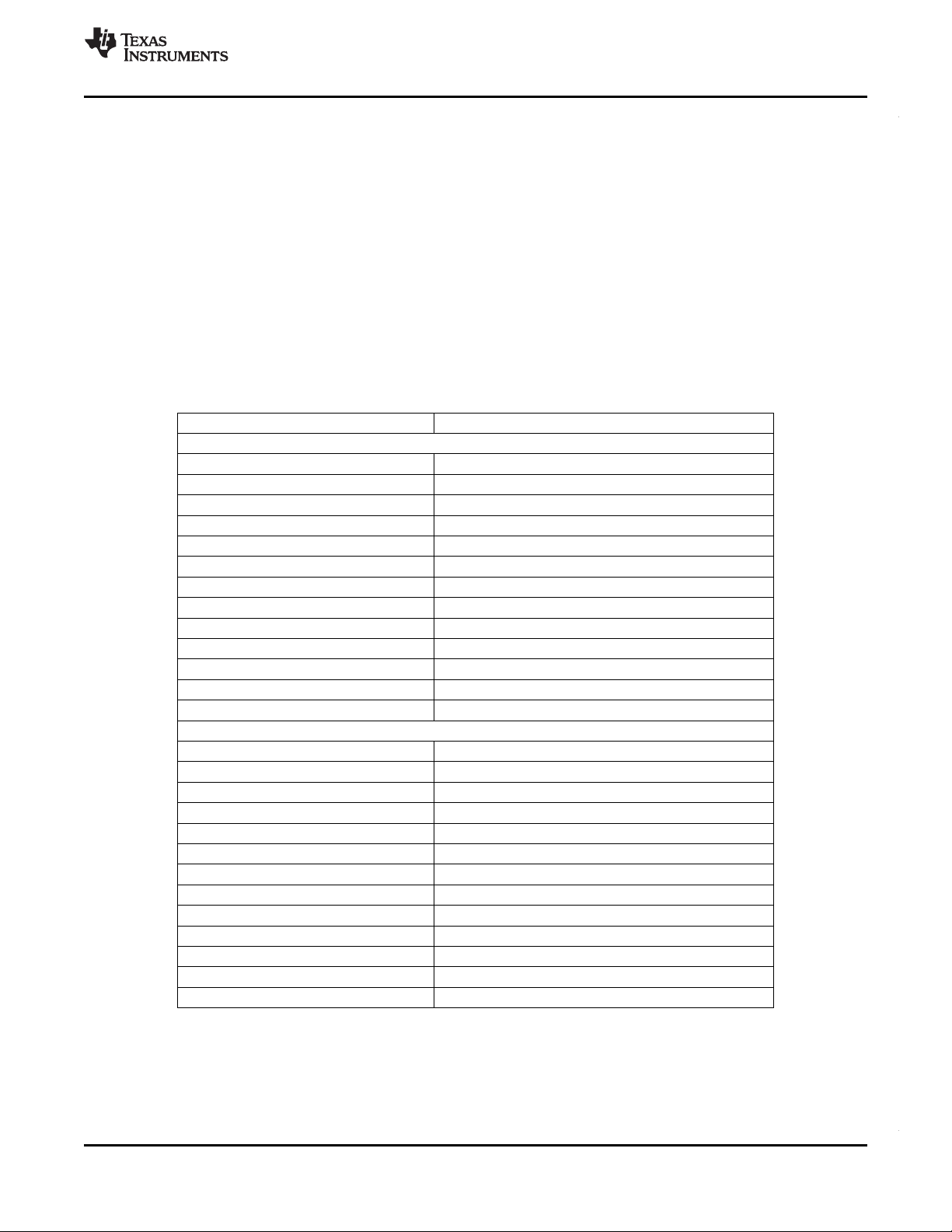

2.1 Device Characteristics

Table 2-1, provides an overview of the C6472 DSP. The table shows significant features of the C6472

device, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the package type

with pin count.

HARDWARE FEATURES C6472

DDR2 Memory Controller (32-bit bus width) [1.8 V I/O]

(clock source = CLKIN3)

EDMA (64 independent channels) 1

High-speed Serial RapidIO Port 2

Peripherals

Not all peripheral pins are

available at the same time

(for more detail, see

Section 3).

On-Chip Memory

CPU MegaModule Revision ID Register (MM_REVID.[15:0])

Revision ID Address 0181 2000

JTAG ID 0009 102Fh

Frequency MHz 500/625/700 MHz

Cycle Time ns 2 ns/1.6 ns

Voltage

PLL1 and

PLL1 Controller Options

PLL2 and CLKIN frequency multiplier

PLL2 Controller Options [EMAC support]

PLL3 and CLKIN frequency multiplier

PLL3 Controller Options [DDR2 Memory Controller support only]

BGA Package 24 x 24 mm 737-Pin Flip-Chip Plastic BGA (ZTZ)

Process Technology mm 0.09 mm

I2C 1

HPI (16 bit) 1

Telecom Serial Interface Port (TSIP) 3

UTOPIA (16/8-bit mode, 50-MHz, slave-only) 1

10/100/1000 Mb/s Ethernet MAC (EMAC) 2

Management Data Input/Output (MDIO) 1

64-bit Timers (Configurable)

General-Purpose Input/Output Port (GPIO) 16

Organization per C64x+ Megamodule 32K-Byte L1 Data Memory [SRAM/Cache]

Shared by all 6 C64x+ Megamodules

JTAG ID register

Address 02A8 0008

Core (V)

I/O (V)

CLKIN frequency multiplier Bypass (x1), x10-x32

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

NOTE

Table 2-1. Characteristics of the C6472 Processor

1

12 (6 dedicated [0-5], 1 per core; 6 shared [6-11])

1 64-bit or 2 32-bit or WD each

32K-Byte L1 Program Memory [SRAM/Cache]

608K-Byte L2 Unified Memory [SRAM/Cache]

768K-byte SL2 Unified SRAM

768K-byte SL2 ROM

0003h

1.2 V (DDR2 EMIF)

1.0 V (500 MHz) / 1.1 V (625 MHz) / 1.2 V (700 MHz)

1.2 V [RapidIO],

1.5 V/1.8 V [EMAC RGMII],

1.8 V [DDR2 EMIF I/O], and

1.8 V and 3.3 V [I/O Supply Voltage]

x20

x20

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 7

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 8

PRODUCTPREVIEW

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Table 2-1. Characteristics of the C6472 Processor (continued)

HARDWARE FEATURES C6472

Product Status

Device Part Numbers TMX320C6472

(1) PRODUCT PREVIEW information concerns products in the formative or design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right to change or discontinue these products without notice.

(1)

Product Preview (PP), Advance Information (AI),

or Production Data (PD)

(For more details on the C64x+™ DSP part

numbering, see Figure 2-13)

PP

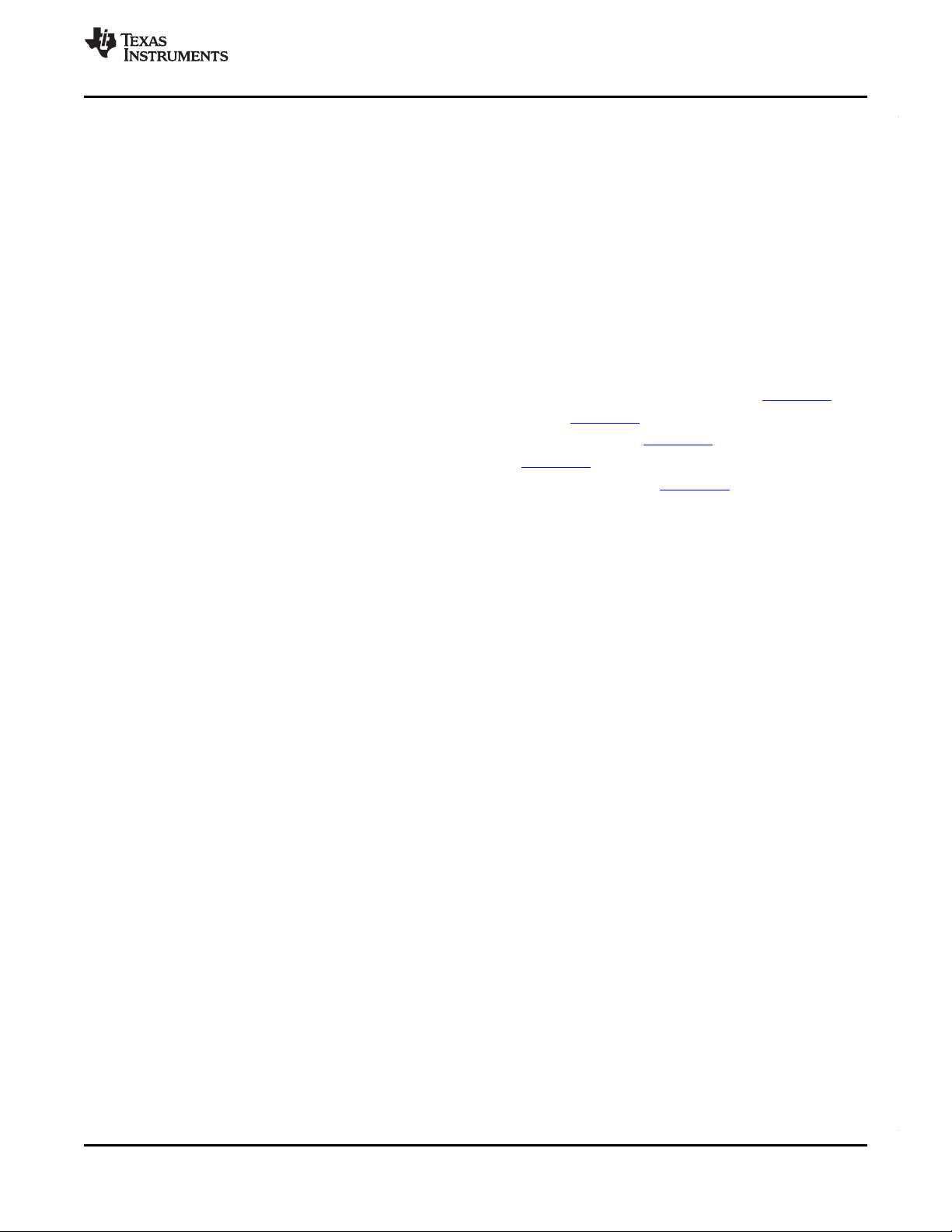

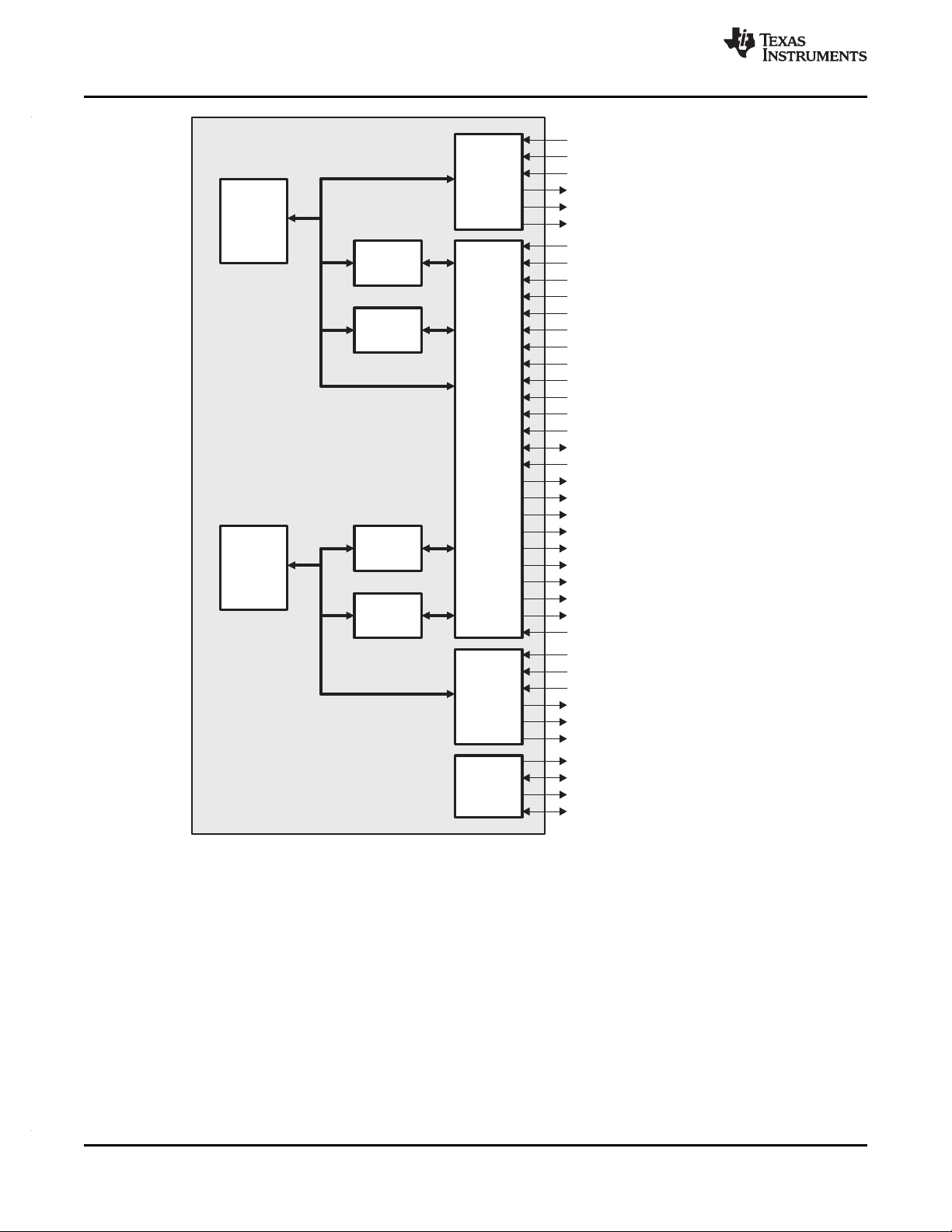

2.2 CPU (DSP Core) Description

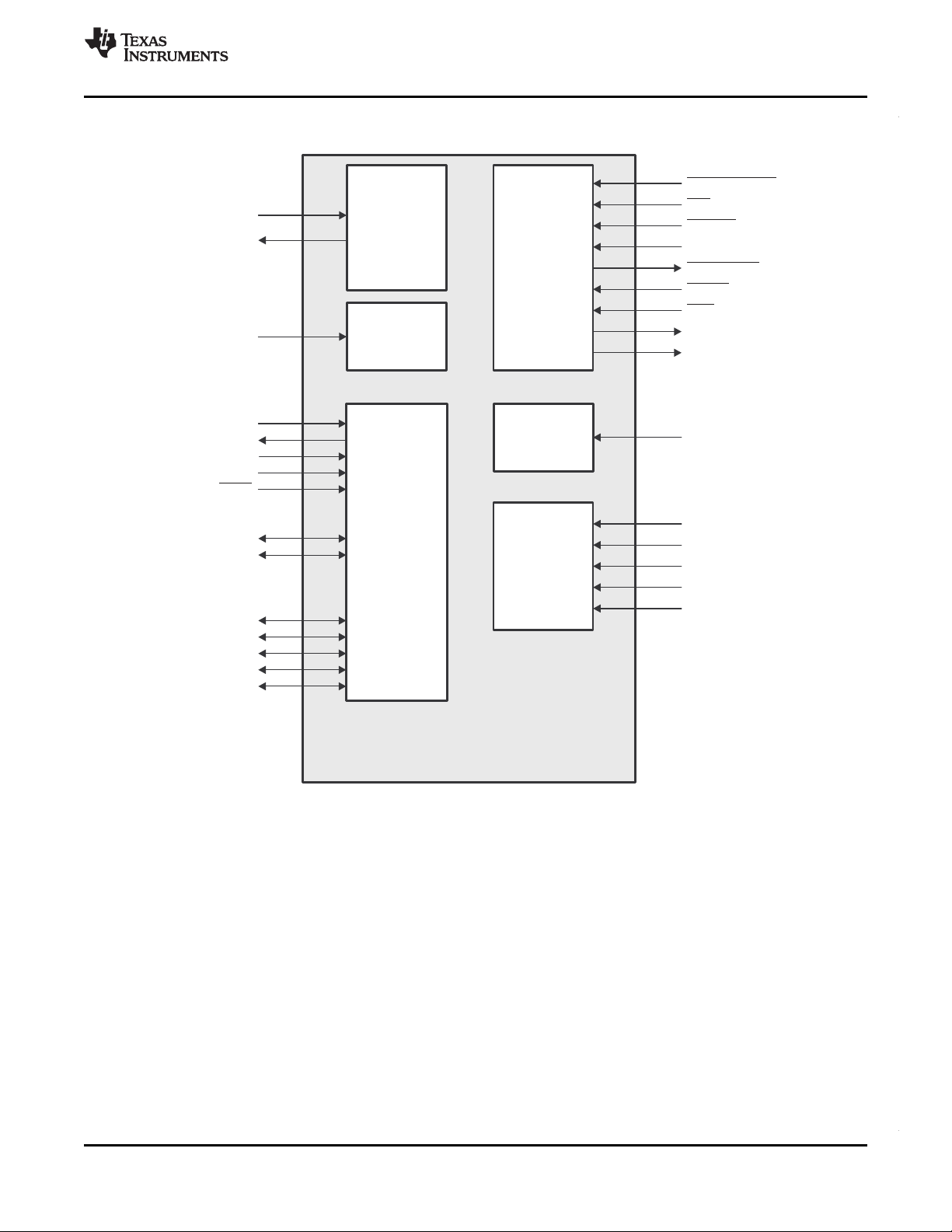

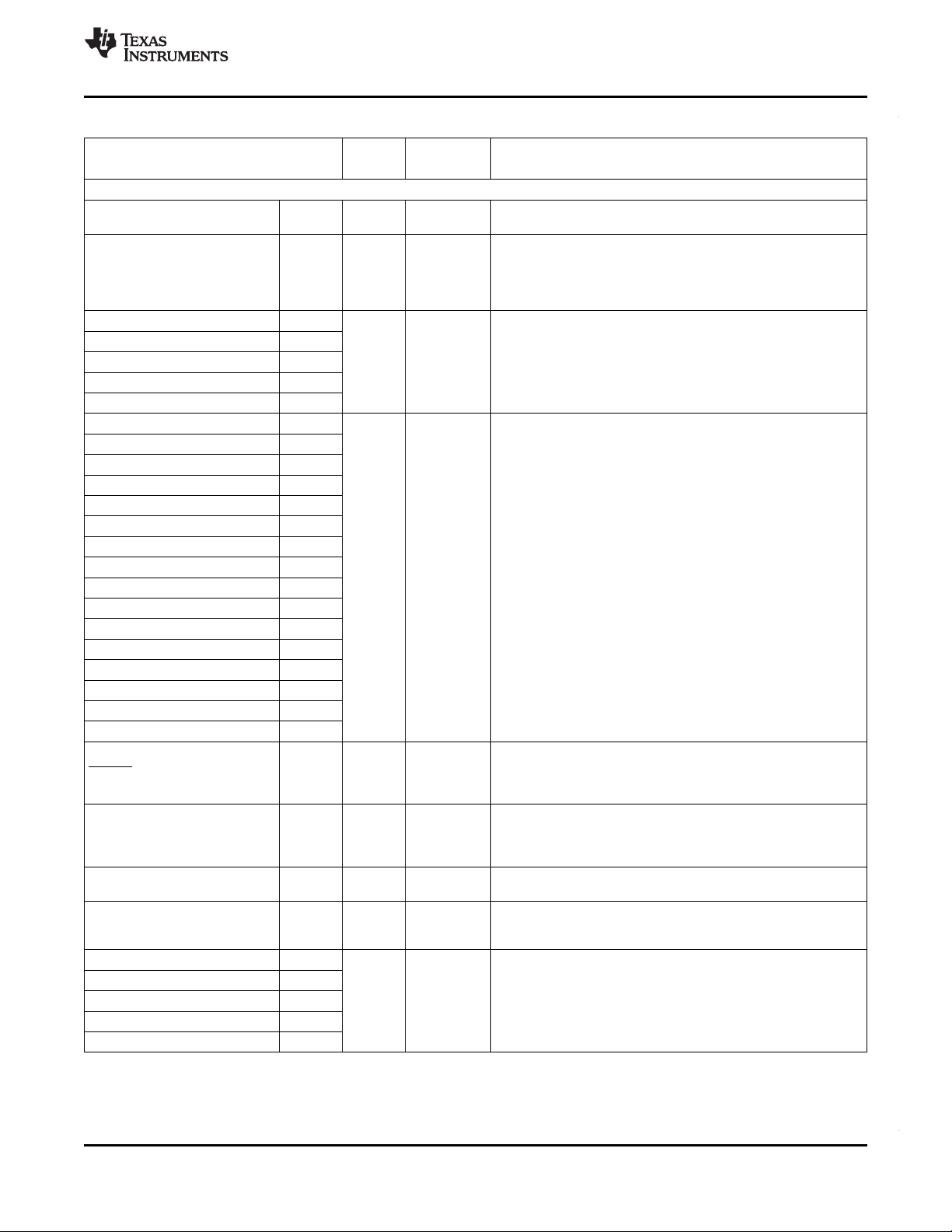

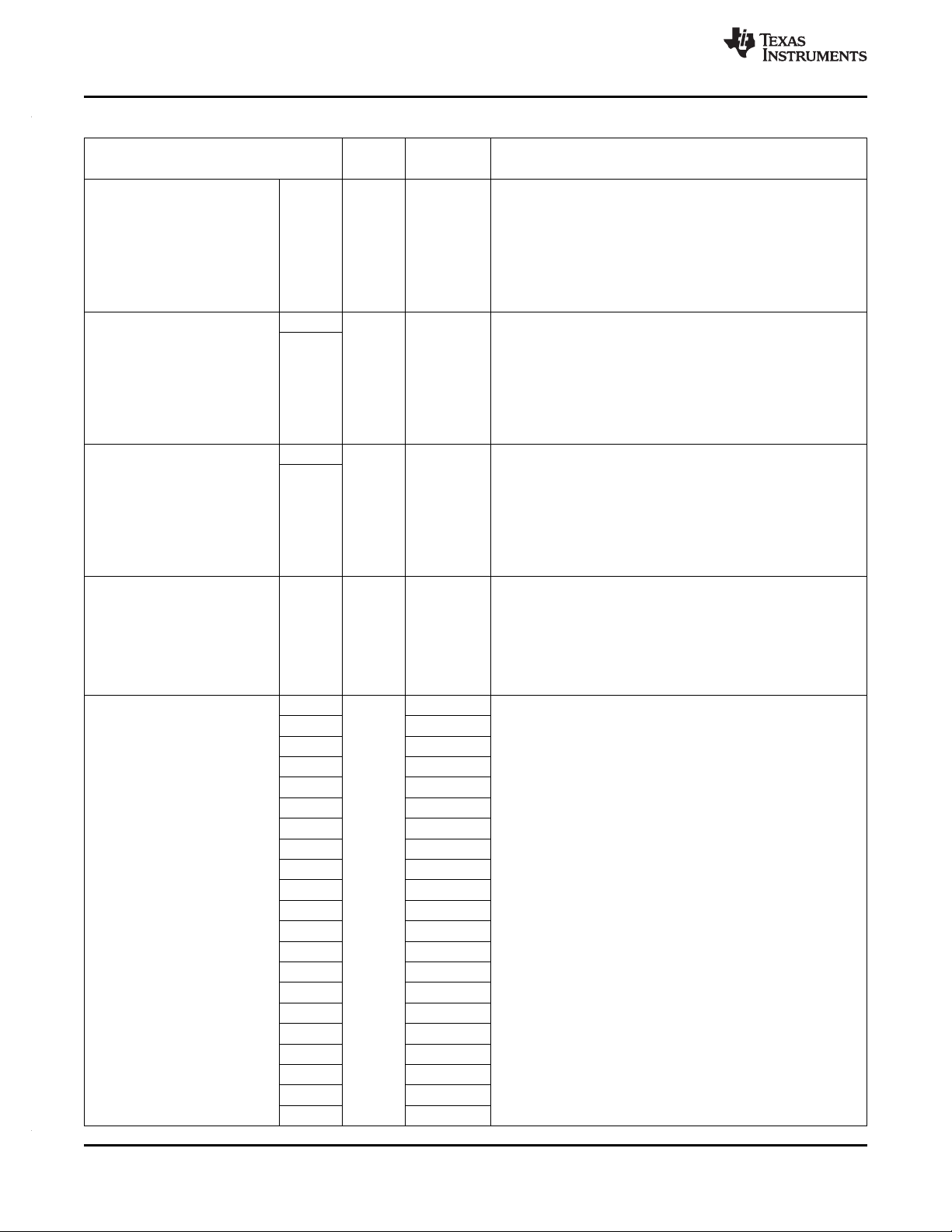

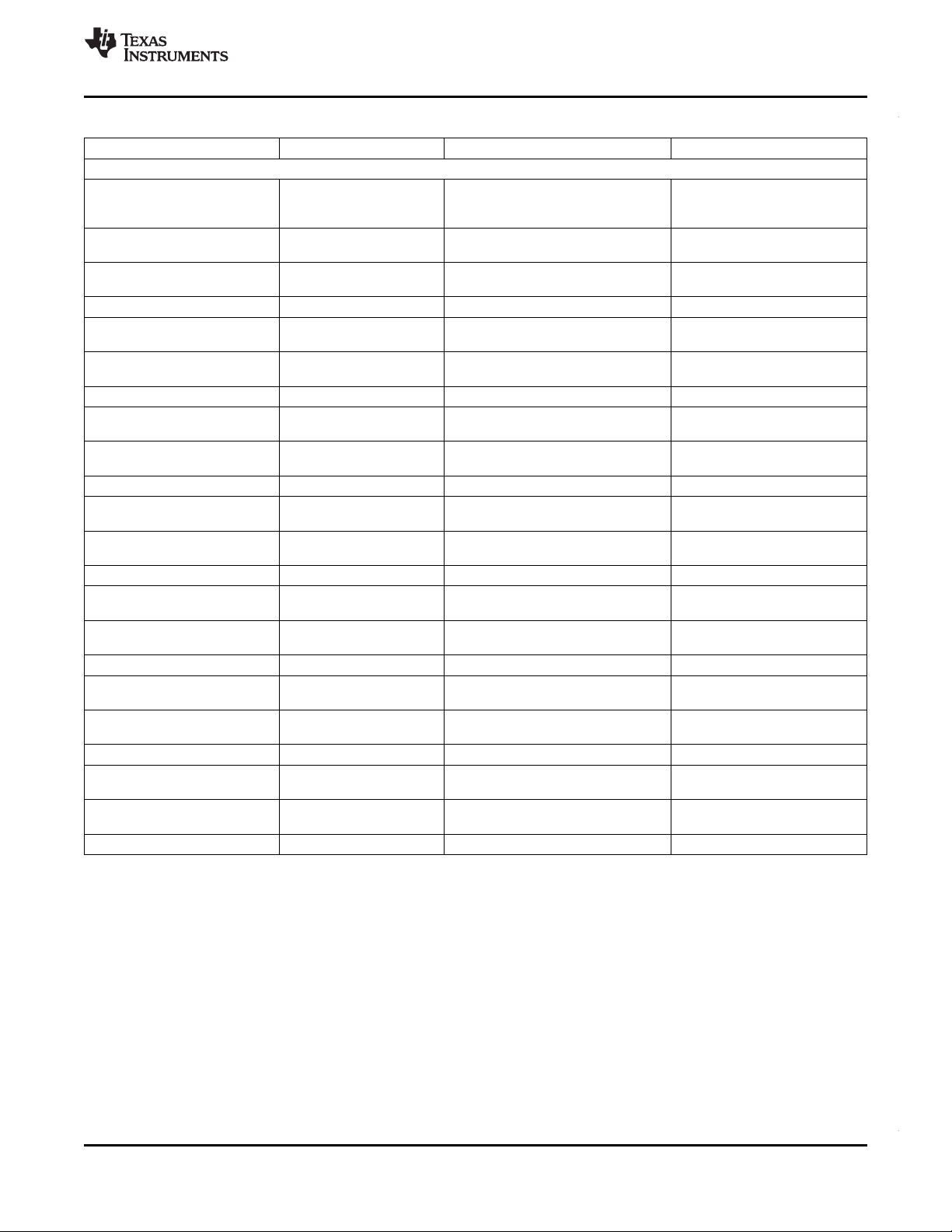

The C64x+ Central Processing Unit (CPU) consists of eight functional units, two register files, and two

data paths as shown in Figure 2-1. The two general-purpose register files (A and B) each contain

32 32-bit registers for a total of 64 registers. The general-purpose registers can be used for data or can be

data address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit

data, 40-bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are

stored in register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or

32 MSBs in the next upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one

instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units

perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from

memory to the register file and store results from the register file into memory.

www.ti.com

The C64x+ CPU extends the performance of the C64x core through enhancements and new features.

Each C64x+ .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, two

16 x 16 bit multiplies, two 16 x 32 bit multiplies, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add

operations, and four 16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There

is also support for Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms

such as FFTs and modems require complex multiplication. The complex multiply (CMPY) instruction takes

four 16-bit inputs and produces a 32-bit real and a 32-bit imaginary output. There are also complex

multiplies with rounding capability that produce one 32-bit packed output that contains 16-bit real and

16-bit imaginary values. The 32 x 32 bit multiply instructions provide the extended precision necessary for

audio and other high-precision algorithms on a variety of signed and unsigned 32-bit data types.

The .L or Arithmetic Logic Unit now incorporates the ability to do parallel add/subtract operations on a pair

of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data

performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C64x+ core enhances the .S unit in several ways. In the C64x core, dual 16-bit MIN2 and MAX2

comparisons were only available on the .L units. On the C64x+ core they are also available on the .S unit

which increases the performance of algorithms that do searching and sorting. Finally, to increase data

packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit

and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack

instructions return parallel results to output precision including saturation support.

Other new features include:

• SPLOOP - A small instruction buffer in the CPU that aids in creation of software pipelining loops where

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

• Compact Instructions - The native instruction size for the C6000 devices is 32 bits. Many common

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C64x+

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

8 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 9

PRODUCTPREVIEW

www.ti.com

• Instruction Set Enhancements - As noted above, there are new instructions such as 32-bit

• Exception Handling - Intended to aid the programmer in isolating bugs. The C64x+ CPU is able to

• Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a

• Time-Stamp Counter - Primarily targeted for Real-Time Operating System (RTOS) robustness, a

For more details on the C64x+ CPU and its enhancements over the C64x architecture, see the following

documents:

• TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732)

• TMS320C64x+ DSP Cache User's Guide (literature number SPRU862)

• TMS320C64x+ DSP Megamodule Reference Guide (literature number SPRU871)

• TMS320C64x Technical Overview (literature number SPRU395)

• TMS320C64x to TMS320C64x+ CPU Migration Guide (literature number SPRAA84)

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field

multiplication.

detect and respond to exceptions, both from internally detected sources (such as illegal op-codes) and

from system events (such as a watchdog time expiration).

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

free-running time-stamp counter is implemented in the CPU which is not sensitive to system stalls.

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 9

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 10

PRODUCTPREVIEW

src2

src2

.D1

.M1

.S1

.L1

longsrc

odddst

src2

src1

src1

src1

src1

evendst

evendst

odddst

dst1

dst

src2

src2

src2

longsrc

DA1

ST1b

LD1b

LD1a

ST1a

Data path A

Odd

register

file A

(A1, A3,

A5...A31)

Odd

register

fileB

(B1,B3,

B5...B31)

.D2

src1

dst

src2

DA2

LD2a

LD2b

src2

.M2

src1

dst1

.S2

src1

evendst

longsrc

odddst

ST2a

ST2b

longsrc

.L2

evendst

odddst

src1

Data pathB

Control Register

32MSB

32LSB

dst2

(A)

32MSB

32LSB

2x

1x

32LSB

32MSB

32LSB

32MSB

dst2

(B)

(B)

(A)

8

8

8

8

32

32

32

32

(C)

(C)

Even

register

file A

(A0, A2,

A4...A30)

Even

register

fileB

(B0,B2,

B4...B30)

(D)

(D)

(D)

(D)

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

www.ti.com

A. On .M unit, dst2 is 32 MSB.

B. On .M unit, dst1 is 32 LSB.

C. On C64x CPU .M unit, src2 is 32 bits; on C64x+ CPU .M unit, src2 is 64 bits.

D. On .L and .S units, odd dst connects to odd register files and even dst connects to even register files.

10 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Figure 2-1. TMS320C64x+™ CPU (DSP Core) Data Paths

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 11

PRODUCTPREVIEW

www.ti.com

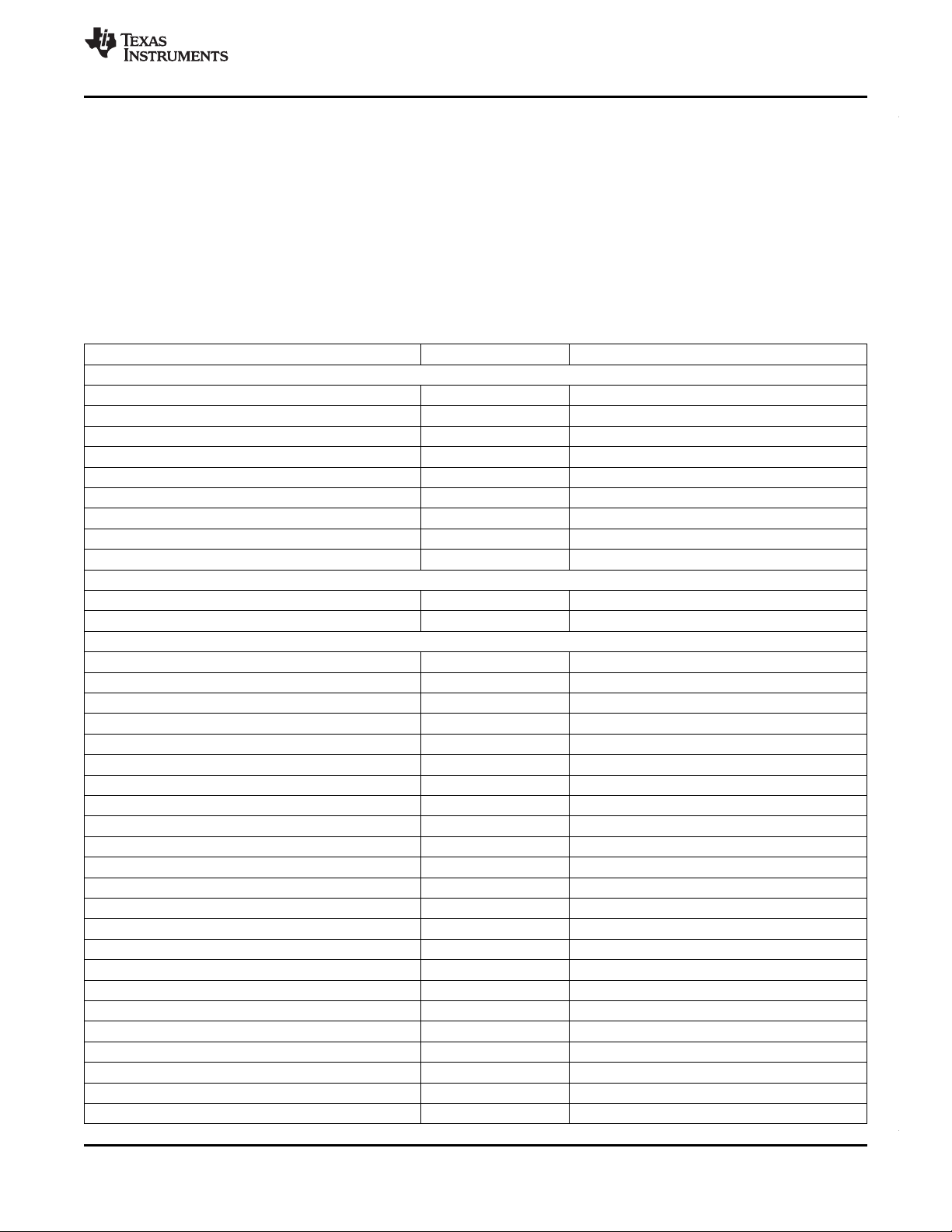

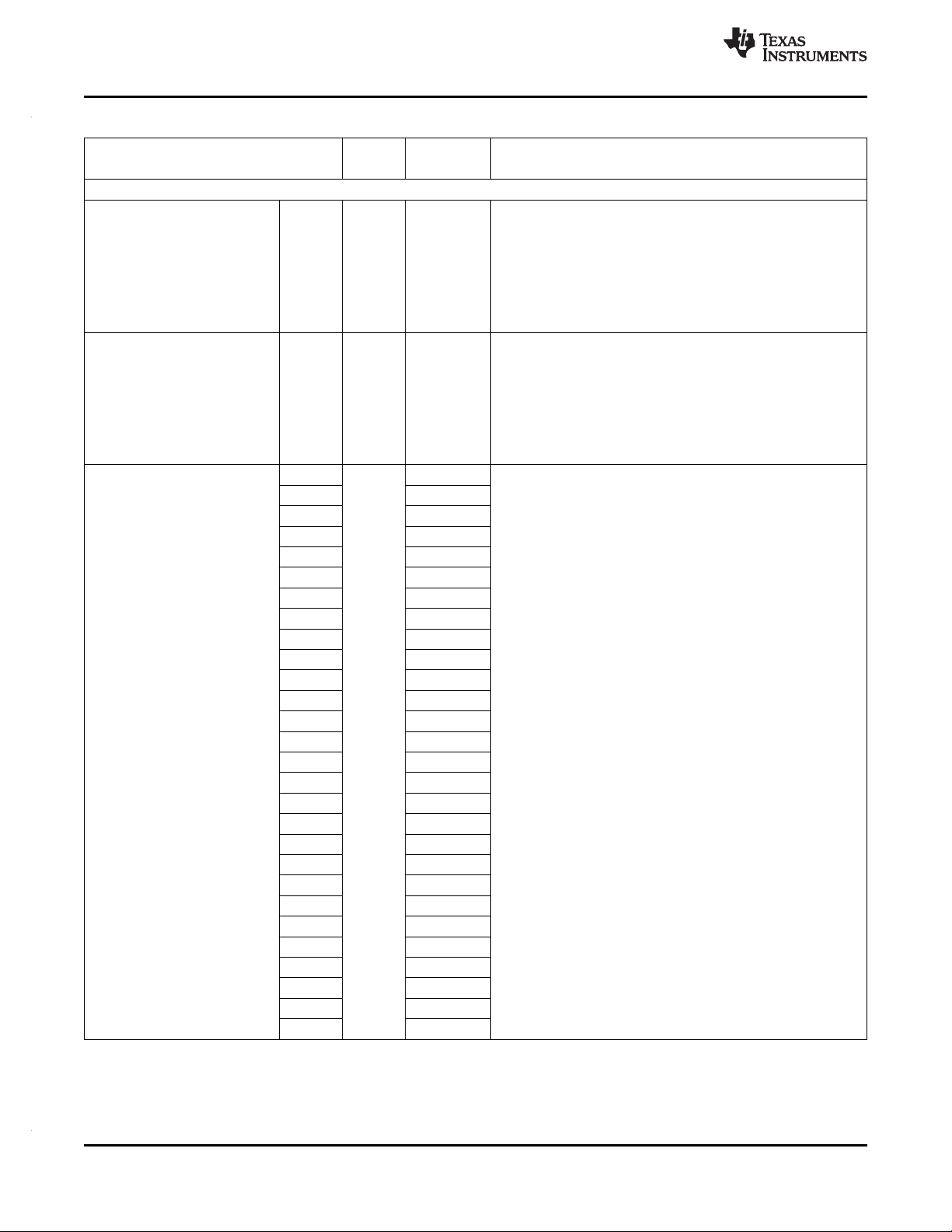

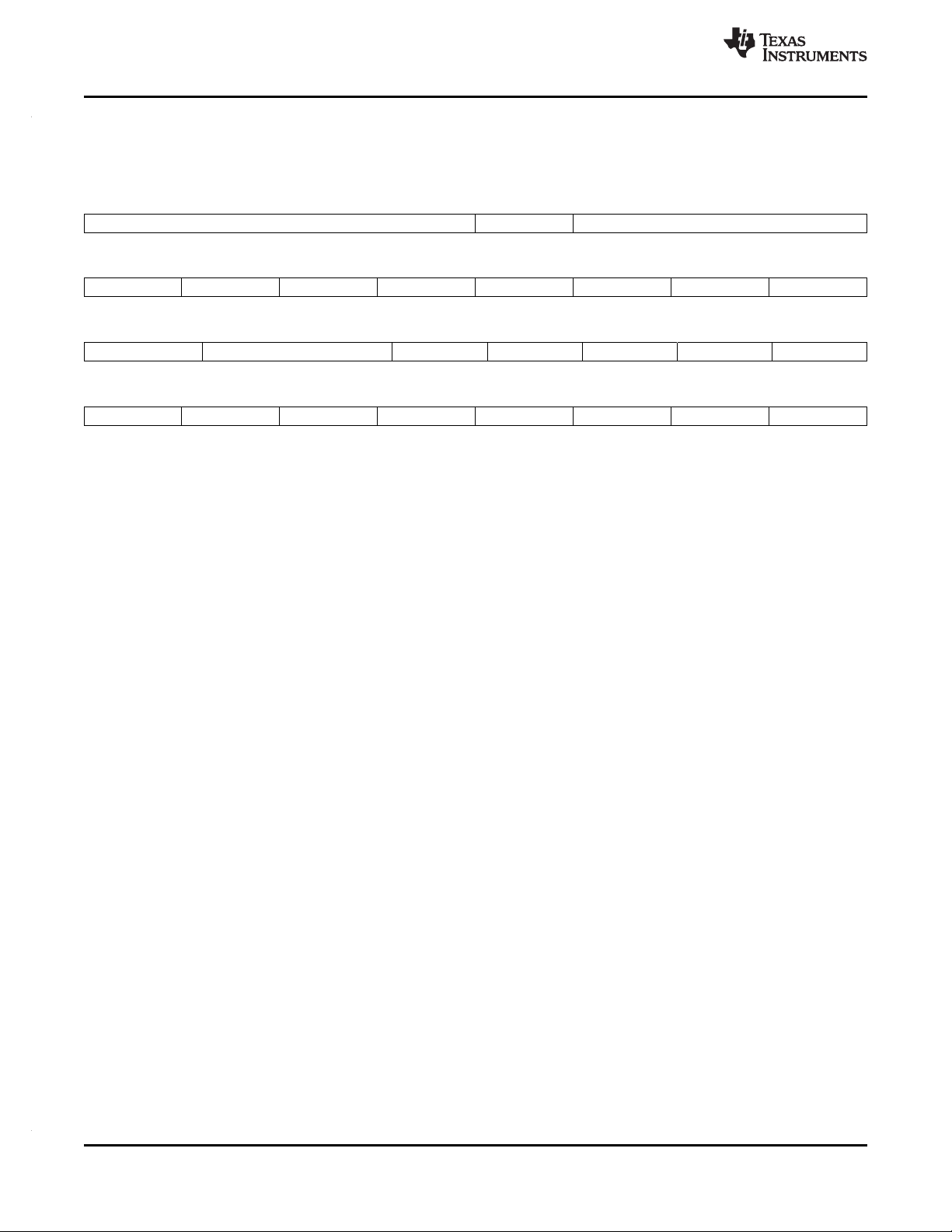

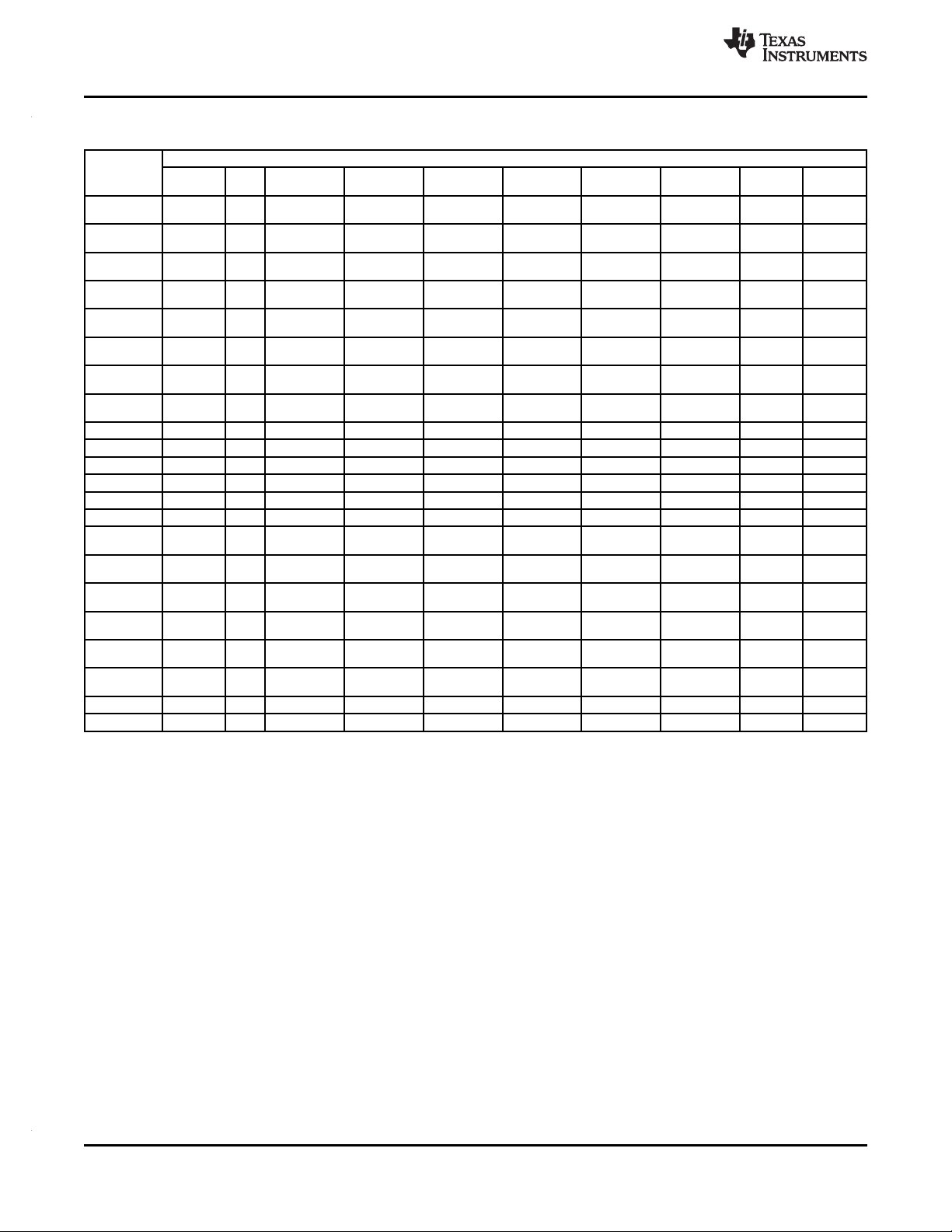

2.3 Memory Map Summary

Table 2-2 shows the memory map address ranges of the C6472 device. This table provides a combined

view of both local and global addresses. The C64x+ megamodule local memories have both local and

global addresses. The megamodule registers only have local addresses. Local addresses can only be

resolved within the megamodule. They cannot be accessed from outside the megamodule. All of the other

addresses listed in this table are global addresses. Global addresses can be accessed from any bus

master including all six C64x+ megamodules, the transfer controllers within the EDMA3 block, and any

peripheral that can master the bus.

Note: 1K = 1024, 1M = 1024K.

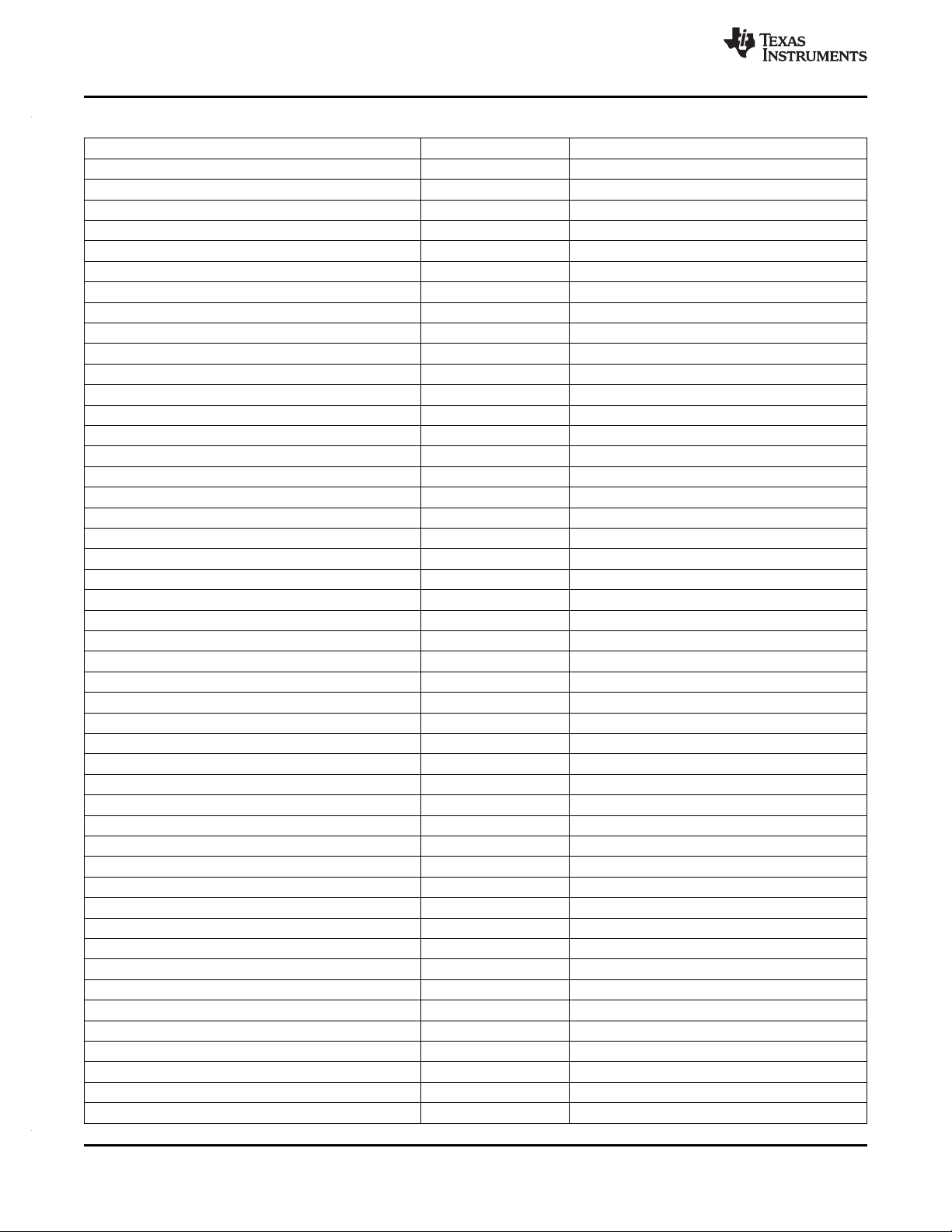

MEMORY BLOCK DESCRIPTION BLOCK SIZE (BYTES) HEX ADDRESS RANGE

Reserved 2M 00000000 - 001FFFFF

SL2 RAM (Local address map) 768K 00200000 - 002BFFFF

Reserved 5.25M 002C0000 - 007FFFFF

Local L2 SRAM 608K 00800000 - 00897FFF

Reserved 5M + 416K 00898000 - 00DFFFFF

Local L1P SRAM 32K 00E00000 - 00E07FFF

Reserved 992K 00E08000 - 00EFFFFF

Local L1D SRAM 32K 00F00000 - 00F07FFF

Reserved 992K 00F08000 - 00FFFFFF

Reserved 8M 01000000 - 017FFFFF

C64x+ Megamodule Registers 4M 01800000 - 01BFFFFF

Reserved 9M 01C00000 - 024FFFFF

TSIP0 256K 02500000 - 0253FFFF

TSIP1 256K 02540000 - 0257FFFF

TSIP2 256K 02580000 - 025BFFFF

Reserved 128K 025C0000 - 025DFFFF

Timer0 64K 025E0000 - 025EFFFF

Timer1 64K 025F0000 - 025FFFFF

Timer2 64K 02600000 - 0260FFFF

Timer3 64K 02610000 - 0261FFFF

Timer4 64K 02620000 - 0262FFFF

Timer5 64K 02630000 - 0263FFFF

Timer6 64K 02640000 - 0264FFFF

Timer7 64K 02650000 - 0265FFFF

Timer8 64K 02660000 - 0266FFFF

Timer9 64K 02670000 - 0267FFFF

Timer10 64K 02680000 - 0268FFFF

Timer11 64K 02690000 - 0269FFFF

Reserved 1.875M 026A0000 - 0287FFFF

HPI Control 128K 02880000 - 0289FFFF

Reserved 1M 028A0000 - 0299FFFF

PLL Controller 1 1K 029A0000 - 029A03FF

Reserved 127K 029A0400 - 029BFFFF

PLL Controller 2 1K 029C0000 - 029C03FF

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Table 2-2. C6472 Memory Map Summary

INTERNAL RAM AND ROM

C64x+ MEGAMODULE REGISTERS

CONTROL REGISTERS ON CONFIG SCR

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 11

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 12

PRODUCTPREVIEW

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

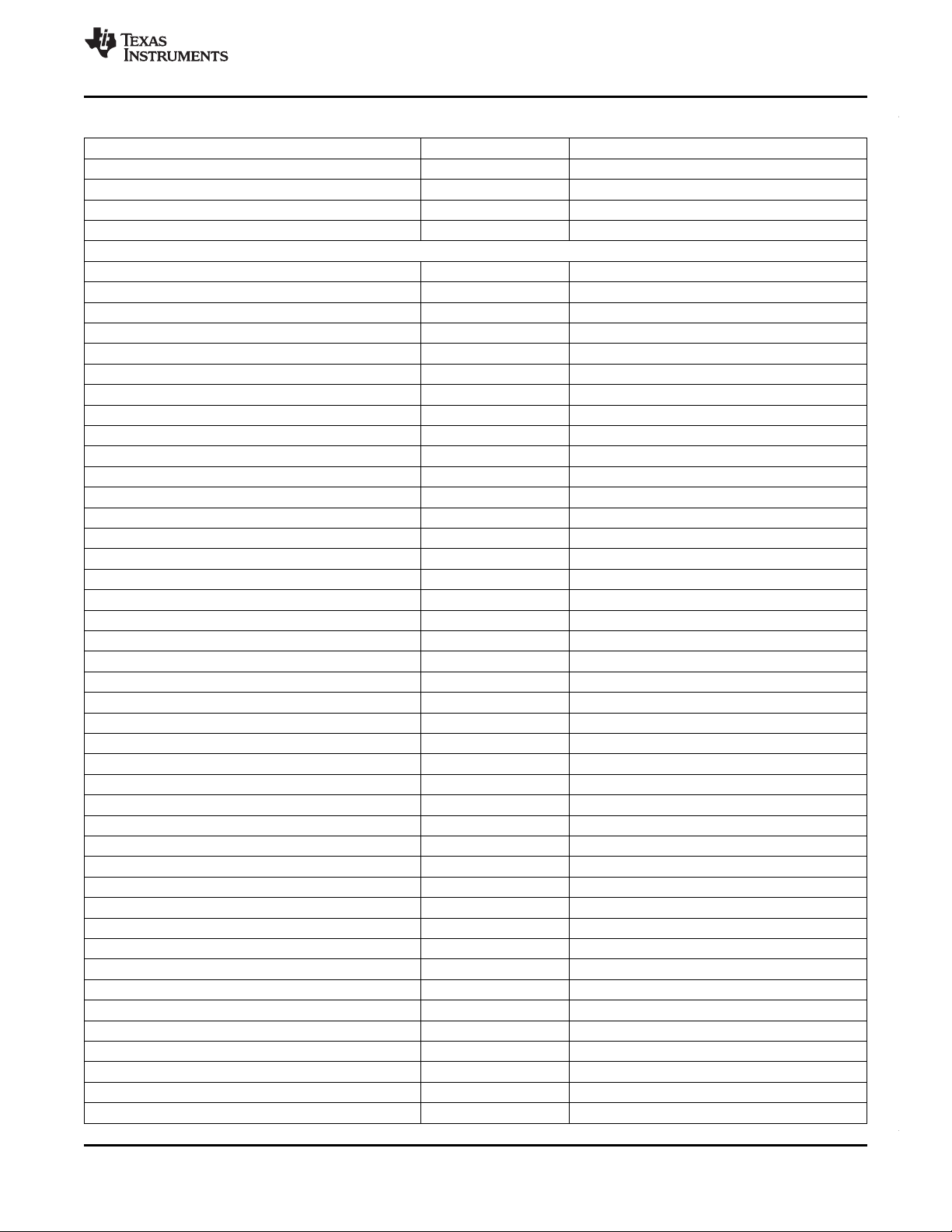

MEMORY BLOCK DESCRIPTION BLOCK SIZE (BYTES) HEX ADDRESS RANGE

PLL Controller 3 1K 029C0400 - 029C07FF

Reserved 254K 029C0800 - 029FFFFF

EDMA3 - EDMA3CC 32K 02A00000 - 02A07FFF

Reserved 96K 02A08000 - 02A1FFFF

EDMA3 - EDMA3TC0 32K 02A20000 - 02A27FFF

EDMA3 - EDMA3TC1 32K 02A28000 - 02A2FFFF

EDMA3 - EDMA3TC2 32K 02A30000 - 02A37FFF

EDMA3 - EDMA3TC3 32K 02A38000 - 02A3FFFF

Reserved 256K 02A40000 - 02A7FFFF

Chip-Level Registers 128K 02A80000 - 02A9FFFF

Reserved 32K 02AA0000 - 02AA7FFF

Shared Memory Controller 32K 02AA8000 - 02AAFFFF

Boot Controller 32K 02AB0000 - 02AB7FFF

Reserved 160K 02AB8000 - 02ADFFFF

PSC 128K 02AE0000 - 02AFFFFF

GPIO 16K 02B00000 - 02B03FFF

I2C Data and Control 16K 02B04000 - 02B07FFF

Reserved 224K 02B08000 - 02B3FFFF

UTOPIA 256K 02B40000 - 02B7FFFF

Reserved 256K 02B80000 - 02BBFFFF

UTOPIA-PDMA (PIM) Configuration 256K 02BC0000 - 02BFFFFF

Reserved 128K 02C00000 - 02C1FFFF

SMCP0 16K 02C20000 - 02C23FFF

SMCP1 16K 02C24000 - 02C27FFF

SMCP2 16K 02C28000 - 02C2BFFF

SMCP3 16K 02C2C000 - 02C2FFFF

SMCP4 16K 02C30000 - 02C33FFF

SMCP5 16K 02C34000 - 02C37FFF

Reserved 32K 02C38000 - 02C3FFFF

ETB0 4K 02C40000 - 02C40FFF

ETB1 4K 02C41000 - 02C41FFF

ETB2 4K 02C42000 - 02C42FFF

ETB3 4K 02C43000 - 02C43FFF

ETB4 4K 02C44000 - 02C44FFF

ETB5 4K 02C45000 - 02C45FFF

Reserved 232K 02C46000 - 02C7FFFF

EMAC0 Control 4K 02C80000 - 02C80FFF

EMAC0 Control Module Registers 2K 02C81000 - 02C817FF

MDIO Control Registers 2K 02C81800 - 02C81FFF

EMAC0 Descriptor Memory 8K 02C82000 - 02C83FFF

Reserved 240K 02C84000 - 02CBFFFF

EMAC1 Control 4K 02CC0000 - 02CC0FFF

EMAC1 Control Module Registers 2K 02CC1000 - 02CC17FF

EMIC0 1K 02CC1800 - 02CC1BFF

EMIC1 1K 02CC1C00 - 02CC1FFF

EMAC1 Descriptor Memory 8K 02CC2000 - 02CC3FFF

Reserved 240K 02CC4000 - 02CFFFFF

www.ti.com

Table 2-2. C6472 Memory Map Summary (continued)

12 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 13

PRODUCTPREVIEW

www.ti.com

Table 2-2. C6472 Memory Map Summary (continued)

MEMORY BLOCK DESCRIPTION BLOCK SIZE (BYTES) HEX ADDRESS RANGE

RapidIO Control Registers 256K 02D00000 - 02D3FFFF

Reserved 768K 02D40000 - 02DFFFFF

RapidIO Descriptor Memory 16K 02E00000 - 02E03FFF

Reserved 209M + 1008K 02E04000 - 0FFFFFFF

Reserved 2M 10000000 - 101FFFFF

SL2 RAM (through DSP0) 768K 10200000 - 102BFFFF

Reserved 5.25M 102C0000 - 107FFFFF

DSP0 L2 SRAM 608K 10800000 - 10897FFF

Reserved 5M + 416K 10898000 - 10DFFFFF

DSP0 L1P SRAM 32K 10E00000 - 10E07FFF

Reserved 992K 10E08000 - 10EFFFFF

DSP0 L1D SRAM 32K 10F00000 - 10F07FFF

Reserved 2M + 992K 10F08000 - 111FFFFF

SL2 RAM (through DSP1) 768K 11200000 - 112BFFFF

Reserved 5.25M 112C0000 - 117FFFFF

DSP1 L2 SRAM 608K 11800000 - 11897FFF

Reserved 5M + 416K 11898000 - 11DFFFFF

DSP1 L1P SRAM 32K 11E00000 - 11E07FFF

Reserved 992K 11E08000 - 11EFFFFF

DSP1 L1D SRAM 32K 11F00000 - 11F07FFF

Reserved 2M + 992K 11F08000 - 121FFFFF

SL2 RAM (through DSP2) 768K 12200000 - 122BFFFF

Reserved 5.25M 122C0000 - 127FFFFF

DSP2 L2 SRAM 608K 12800000 - 12897FFF

Reserved 5M + 416K 12898000 - 12DFFFFF

DSP2 L1P SRAM 32K 12E00000 - 12E07FFF

Reserved 992K 12E08000 - 12EFFFFF

DSP2 L1D SRAM 32K 12F00000 - 12F07FFF

Reserved 2M + 992K 12F08000 - 131FFFFF

SL2 RAM (through DSP3) 768K 13200000 - 132BFFFF

Reserved 5.25M 132C0000 - 137FFFFF

DSP3 L2 SRAM 608K 13800000 - 13897FFF

Reserved 5M + 416K 13898000 - 13DFFFFF

DSP3 L1P SRAM 32K 13E00000 - 13E07FFF

Reserved 992K 13E08000 - 13EFFFFF

DSP3 L1D SRAM 32K 13F00000 - 13F07FFF

Reserved 2M + 992K 13F08000 - 141FFFFF

SL2 RAM (through DSP4) 768K 14200000 - 142BFFFF

Reserved 5.25M 142C0000 - 147FFFFF

DSP4 L2 SRAM 608K 14800000 - 14897FFF

Reserved 5M + 416K 14898000 - 14DFFFFF

DSP4 L1P SRAM 32K 14E00000 - 14E07FFF

Reserved 992K 14E08000 - 14EFFFFF

DSP4 L1D SRAM 32K 14F00000 - 14F07FFF

Reserved 2M + 992K 14F08000 - 151FFFFF

SL2 RAM (through DSP5) 768K 15200000 - 152BFFFF

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

INTERNAL RAM (GLOBAL MEMORY MAP)

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 13

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 14

PRODUCTPREVIEW

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Table 2-2. C6472 Memory Map Summary (continued)

MEMORY BLOCK DESCRIPTION BLOCK SIZE (BYTES) HEX ADDRESS RANGE

Reserved 5.25M 152C0000 - 157FFFFF

DSP5 L2 SRAM 608K 15800000 - 15897FFF

Reserved 5M + 416K 15898000 - 15DFFFF

DSP5 L1P SRAM 32K 15E00000 - 15E07FFF

Reserved 992K 15E08000 - 15EFFFFF

DSP5 L1D SRAM 32K 15F00000 - 15F07FFF

Reserved 161M + 992K 15F08000 - 1FFFFFFF

DATA SPACE ON DMA

Reserved 1408M 20000000 - 77FFFFFF

DDR2 EMIF Config 128M 78000000 - 7FFFFFFF

Reserved 1536M 80000000 - DFFFFFFF

CE0-CE1 DDR2 SDRAM 512M E0000000 - FFFFFFFF

2.4 Boot Mode Sequence

The boot sequence is a process by which the DSP's internal memory is loaded with program and data

sections and the DSP's internal registers are programmed with predetermined values. The boot sequence

is started automatically after each power-on, warm, and system reset. For more details on the initiators of

these resets, see Section 7.7, Reset Controller.

www.ti.com

There are several methods by which the memory and register initialization can take place. Each of these

methods is referred to as a boot mode. The boot mode to be used is selected at reset through the

BOOTMODE[3:0] pins.

2.4.1 Boot Modes Supported

The TMS320C6472 has a dedicated Boot Controller, which is responsible for managing the boot process

for single and multiple C64x+ megamodule core boots. There are two types of resets on the C6472

device:

1. Device-level Resets (Global Resets)

– Power-on Reset; initiated by POR

– Chip-level Warm Reset (or Device Reset); initiated by RESET

– System Reset; initiated by a watchdog timeout or emulation

2. C64x+ megamodule-level Resets (Local Resets)

– External C64x+ megamodule selectable LRESET

– Local reset of the C64x+ megamodule initiated by on-chip Reset Controller

– Power Sleep Controller initiated by local C64x+ megamodule reset

After POR and RESET asserted resets, the boot controller selects the boot mode based on the status of

BOOTMODE[3:0] pins. When a system reset occurs, the boot mode used is determined by the

BOOTMODE field in the DEVSTAT register. All possible bootmodes are listed in Table 2-3. For a detailed

explanation of this operation, see the TMS320C645x/C647x Bootloader User's Guide (literature number

SPRUEC6).

Following a device-level reset, each C64x+ megamodule core can set its boot mode choice for

subsequent local resets using the registers BOOTMODE0 through BOOTMODE5 to either immediate boot

mode or host boot mode. The default values of these registers are set to immediate boot mode.

14 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 15

PRODUCTPREVIEW

www.ti.com

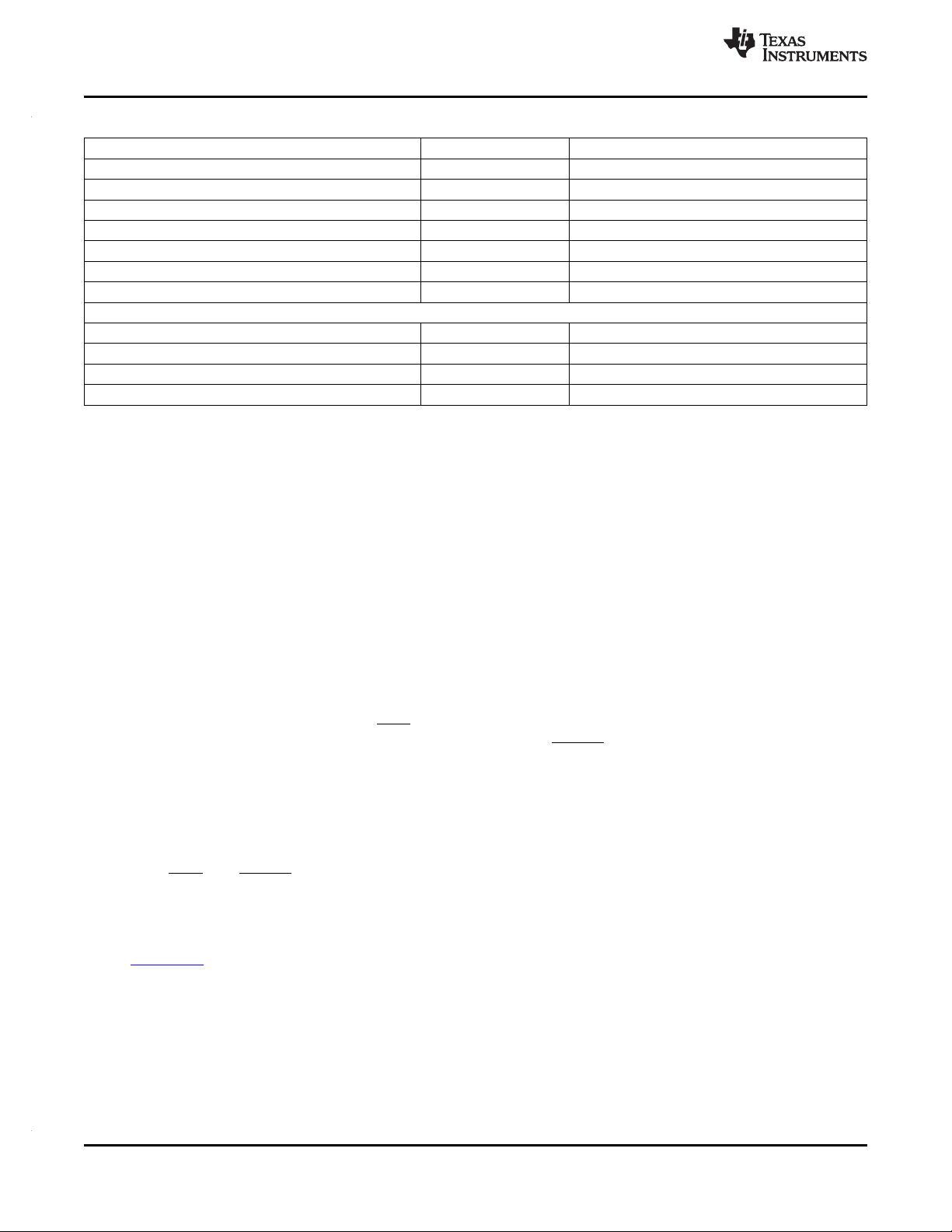

BOOTMODE[3:0] DESCRIPTION TYPE CFGGP[4:0]

0 (0000) Immediate boot Immediate Boot Don’t Care

1 (0001) Host boot (HPI) Host Don’t Care

2 (0010) Master I2C boot for I2C address 50h ROM

3 (0011) Master I2C boot for I2C address 51h ROM

4 (0100) Slave I2C boot ROM

5 (0101) ROM

6 (0110) ROM

7 (0111) ROM

8 (1000) ROM

9 (1001) (mode and speed determined by ROM

10 (1010) (mode and speed determined by ROM

11 (1011) RIO1 ROM

12 (1100) RIO2 ROM

UTOPIA boot 8-bit PLLx10 of main PHY ID

PLLCTL

UTOPIA boot 8-bit PLLx20 of main PHY ID

PLLCTL

UTOPIA boot 16-bit PLLx10 of main PHY ID

PLLCTL

UTOPIA boot 16-bit PLLx20 of main PHY ID

PLLCTL

Ethernet MAC Port 0 boot

MACSEL0 pins)

Ethernet MAC Port 1 boot

MACSEL1 pins)

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Table 2-3. Boot Mode Operation

CFGGP[4] =

0 PLLx9 mode of main PLLCTL is selected

1 PLLx19 mode of main PLLCTL is

selected

CFGGP[3:0] = Boot PARAM index

CFGGP[4] =

0 PLLx9 mode of main PLLCTL is selected

1 PLLx19 mode of main PLLCTL is

selected

CFGGP[3:0] = Boot PARAM index

CFGGP[4] =

0 PLLx9 mode of main PLLCTL is selected

1 PLLx19 mode of main PLLCTL is

selected

CFGGP[3:0] = Don’t Care

CFGGP[4] =

0 PLLx10 mode of main PLLCTL is

selected

1 PLLx20 mode of main PLLCTL is

selected

CFGGP[3:0]: Device ID (when RMII is selected,

CFGGP[3] controls speed - 1 for 100 Mbs, 0 for 10

Mbps - and Device ID[3] is 0)

CFGGP[4] =

0 PLLx10 mode of main PLLCTL is

selected

1 PLLx20 mode of main PLLCTL is

selected

CFGGP[3:0]: Device ID (when RMII is selected,

CFGGP[3] controls speed - 1 for 100 Mbs, 0 for 10

Mbps - and Device ID[3] is 0)

CFGGP[4] =

0 PLLx10 mode of main PLLCTL is

selected

1 PLLx20 mode of main PLLCTL is

selected

CFGGP [3:0]: Node (1111b for default)

CFGGP[4] =

0 PLLx10 mode of main PLLCTL is

selected

1 PLLx20 mode of main PLLCTL is

selected

CFGGP [3:0]: Node (1111b for default)

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 15

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 16

PRODUCTPREVIEW

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Table 2-3. Boot Mode Operation (continued)

BOOTMODE[3:0] DESCRIPTION TYPE CFGGP[4:0]

CFGGP[4] =

0 PLLx10 mode of main PLLCTL is

13 (1101) RIO3 ROM

CFGGP [3:0]: Node (1111b for default)

CFGGP[4] =

14 (1110) RIO4 ROM

CFGGP [3:0]: Node (1111b for default)

15 (1111) Reserved ROM Reserved

• Immediate boot

When immediate boot is selected after global reset, the C64x+ megamodule core executes directly

from the internal L2 SRAM address programmed in the DSP_BOOT_ADDRx register. Note: device

operation is undefined if invalid code is address programmed in the DSP_BOOT_ADDRx register.

Executing invalid code may prevent connection by an emulator.

The default start addresses for megamodule core 0-5 boot are listed in Table 2-4.

selected

1 PLLx20 mode of main PLLCTL is

selected

0 PLLx10 mode of main PLLCTL is

selected

1 PLLx20 mode of main PLLCTL is

selected

www.ti.com

MEGAMODULE ADDRESSES FOR ADDRESSES FOR

CORE NAME DEVICE RESET/ DEVICE RESET/

Megamodule 0x0080_0000 0x0010_0000 0x0010_0000, if the device

Core 0 reset was boot mode 2-15;

Megamodule 0x0080_0000 0x0080_0000 0x0080_0000

Core 1

Megamodule 0x0080_0000 0x0080_0000 0x0080_0000

Core 2

Megamodule 0x0080_0000 0x0080_0000 0x0080_0000

Core 3

Megamodule 0x0080_0000 0x0080_0000 0x0080_0000

Core 4

Megamodule 0x0080_0000 0x0080_0000 0x0080_0000

Core 5

For boot mode 1, these addresses can be modifed by the host before it releases each megamodule

core from reset; for details, see Section 3.9.5. For boot mode 2-15, it is possible to have megamodule

core 0 modify the default address of megamodule core 1-5 before it releases each megamodule core

from reset; for details, see Section 2.4.1. For local reset, if all cores are required to begin from a

particular address, the default addresses have to be modified. One example is that only the

megamodule core 0's default address is modified to match megamodule core 1-5.

• Host boot

If host boot is selected after global reset, all C64x+ megamodule cores are internally "held in reset"

while the remainder of the device (including all memory subsystems of the C64x+ megamodule) is

released from reset. During this period, an external host can initialize the C6472 device memory space

(shared memory as well as the C64x+ megamodule memory), as necessary through an HPI interface,

including internal configuration registers such as those that control the DDR2 or other peripherals.

Once the host is finished with all necessary initialization, it must write a 1 to bit fields BC0 through BC5

of the BOOT_COMPLETE_STAT register (inside the Boot Controller) indicating boot complete of the

16 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Table 2-4. Megamodule Core 0-5 Boot Start Addresses

DEFAULT START DEFAULT START

BOOT MODE 0-1 BOOT MODE 2-15

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

DEFAULT START

ADDRESSES FOR

LOCAL RESET

otherwise 0x0080_0000

Page 17

PRODUCTPREVIEW

www.ti.com

corresponding C64x+ megamodule. This transition causes the Boot Controller to bring the C64x+

megamodule core out of the "held-in-reset" state. The CPU then begins execution from the internal L2

SRAM address programmed in the DSP_BOOT_ADDRx register. All memory may be written to and

read by the host. This allows for the host to verify what it sends to the DSP, if required.

For the C6472 device, only the Host Port Interface (HPI) peripheral can be used for host boot. PLL1,

which provides CPU/6 clock to the HPI module, will initially be running in bypass mode. Therefore, the

HPI interface will be very slow and HRDY must be observed. Initial HPI accesses can configure PLL1

for full-speed operation to make HPI accesses shorter.

• Master I2C boot

After global reset, the C64x+ megamodule core 0 comes out of RESET and starts executing the

shared ROM code from the address provided by the Boot Controller based on the I2C boot mode

selection. Then C64x+ megamodule core 0 configures I2C and acts as a master to the I2C bus and

copies data from an I2C EPROM or a device acting as an I2C slave to the DSP using a predefined

boot table format. The destination address and length are contained within the boot table. After

initializing the on-chip memory to the known state and initializing the start address of the other C64x+

megamodule cores, C64x+ megamodule core 0 brings the other cores out of reset by writing a 1 to bit

fields BC1 through BC5 of the BOOT_COMPLETE_STAT register. After this, C64x+ megamodule

cores 1 through 5 start executing from the start address provided by C64x+ megamodule core 0.

• Slave I2C boot

A Slave I2C boot is also implemented, which programs the DSP as an I2C slave. A DSP in I2C slave

mode will never transmit on the I2C bus. The slave DSP must first receive a three-word transmission

from the master. This transmission includes a 16-bit length field (length is in bytes, should be 6 for this

block), a 16-bit checksum field for which a value of zero means ignore the checksum, and the 16-bit

options field described in the boot parameter table for standard I2C boot. This option field informs the

slave what information is contained in the next data blocks. Typically, the option field is set to 1 to

indicate boot tables will be received next. Only core 0 is active during the boot process. Using the

slave I2C boot, a single DSP or device acting as an I2C master can simultaneously boot multiple slave

DSPs connected to the same I2C bus. Note that the master DSP may require booting via an I2C

EEPROM before acting as a master and booting other DSPs.

• Ethernet MAC boot

When BOOTMODE [3:0] = 1001 is selected, Ethernet MAC boot is initiated on EMAC0 with the mode

specified by the MACSEL0[2:0] pins. Alternately, when BOOTMODE [3:0] = 1010 is selected, Ethernet

MAC boot is initiated on EMAC1 with the mode specified by the MACSEL1[1:0] pins.

After reset, the C64x+ megamodule core 0 comes out of RESET and starts executing the shared ROM

code from the address provided by the Boot Controller based on the Ethernet boot mode selection

(1001b or 1010b). The C64x+ megamodule core 0 configures the appropriate Ethernet MAC and

brings the code image into the on-chip memory via the protocol defined. After initializing the on-chip

memory to the known state and initializing the start address of the other C64x+ megamodule cores (1

through 5), C64x+ megamodule core 0 brings the other cores out of reset by writing a 1 to bit fields

BC1 through BC5 of the BOOT_COMPLETE_STAT register. After this, C64x+ megamodule cores 1

through 5 start executing from the start address provided by C64x+ megamodule core 0.

• Serial RapidIO boot

After reset, the C64x+ megamodule core 0 comes out of RESET and starts executing the shared ROM

code from the address provided by the Boot Controller based on the Serial RapidIO boot mode

selection (1011b, 1100b, 1101b, or 1110b). The C64x+ megamodule core 0 configures Serial RapidIO

and EDMA, if required, and brings the code image into the on-chip memory via the protocol defined by

the boot method (SRIO bootloader). After initializing the on-chip memory to the known state and

initializing the start address of the other C64x+ megamodule cores (1 through 5), C64x+ megamodule

core 0 brings the other cores out of reset by writing a 1 to bit fields BC1 through BC5 of the

BOOT_COMPLETE_STAT register. After this, the C64x+ megamodule cores 1 through 5 start

executing from the start address provided by C64x+ megamodule core 0.

• UTOPIA boot

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 17

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 18

PRODUCTPREVIEW

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

After reset, the C64x+ megamodule core 0 comes out of RESET and starts executing the shared ROM

code from the address provided by the Boot Controller based on the UTOPIA boot mode selection

(0101b, 0110b, 0111b, 1000b). The C64x+ megamodule core 0 configures the UTOPIA and brings the

code image into the on-chip memory via the protocol defined. After initializing the on-chip memory to

the known state and initializing the start address of the other C64x+ megamodule cores (1 through 5),

C64x+ megamodule core 0 brings the other cores out of reset by writing a 1 to bit fields ofBC1 through

BC5 the BOOT_COMPLETE_STAT register. After this, C64x+ megamodule cores 1 through 5 start

executing from the start address provided by C64x+ megamodule core 0.

After local resets, the C6472 device supports two boot modes via BOOTMODE0-BOOTMODE5

device-level registers:

• Immediate boot

When immediate boot is selected after global reset, the C64x+ megamodule core (x) executes directly

from the internal L2 SRAM address programmed in the DSP_BOOT_ADDRx register upon being given

a local reset. Note: device operation is undefined if invalid code is address programmed in the

DSP_BOOT_ADDRx register. Executing invalid code may prevent connection by an emulator.

• Host boot

If host boot is selected after global reset, the C64x+ megamodule core (x) is internally "held in reset"

while the remainder of the C64x+ megamodule is released from reset upon being given a local reset.

During this period, an external host can initialize the C64x+ megamodule (x) memory space, as

necessary, through an HPI interface. Once the host is finished with all necessary initialization, it must

write a 1 to the corresponding bit field BCx of the BOOT_COMPLETE_STAT register (inside the Boot

Controller) indicating boot complete of the corresponding C64x+ megamodule. This transition causes

the Boot Controller to bring the C64x+ megamodule core out of the "held-in-reset" state. The core (x)

then begins execution from the internal L2 SRAM programmed in the DSP_BOOT_ADDRx register. All

memory may be written to and read by the host. This allows for the host to verify what it sends to the

DSP, if required.

www.ti.com

2.4.2 BOOTACTIVE

The output pin, BOOTACTIVE, is asserted upon reset and de-asserted on boot complete. In the case of

BOOTMODE 0, all cores are released from reset immediately. BOOTACTIVE also goes low within a small

number of cycles, as all cores are out of reset and running. In the case of BOOTMODE 1, the host needs

to write to the boot complete bit in the BOOT_COMPLETE_STAT register corresponding to each C64x+

megamodule that is to be taken out of reset. BOOTACTIVE will be high if any cores are held in reset. In

the case of any other boot, core 0 comes out of RESET immediately, but all other cores are still in

RESET, so BOOTACTIVE will be high. The ROM code will not write to either the

BOOT_COMPLETE_STAT or the BOOT_ADDRESS register unless explicitly directed to do so by the data

provided in the boot process. Any active core can set bits in BOOT_COMPLETE_STAT at any time to

begin code execution on inactive cores. BOOTACTIVE will go low after the boot complete bit (BCx) in the

BOOT_COMPLETE_STAT register is set for all six cores. For a detailed explanation of this operation, see

the TMS320C645x/C647x Bootloader User's Guide (literature number SPRUEC6).

18 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 19

PRODUCTPREVIEW

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

13121110987654321

13121110987654321

AH

RSV11

14 15

14 15

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

AH

AJ

DV

DD33

V

SS

AJ

MRXD07

DV

DD33

V

SS

MTXD05/

RMTXD11

V

SS

MTCLK0/

REFCLK0/

SREFCLK0

MRXD03/

SRXSYNC1

MRXD02/

SRXD1

DV

DD33

MRXD06/

RMRXER1

V

SS

RGRD13

DV

DD15

RGRD12

V

SS

CLKIN2

MTXD01/

RMTXD01/

STXSYNC0

GMDIO

MRXD04/

RMRXD10

DV

DD33

MRXD00/

RMRXD00/

SRXD0

RSV10

MACSEL11

LENDIANTR21

TX14

V

SS

TR17 TR16 TX27 RSV12

MACSEL01

GMTCLK0/

REFCLK1/

SREFCLK1

MRXD05/

RMRXD11

MTXD02/

STXD1

GMDCLK

MRCLK0/

SRXCLK1

MRXD01/

RMRXD01/

SRXSYNC0

MTXD07/

STXCLK0

DV

DD15MON

AV

DDA2

RGRXC1

FSA1

TX11 TR22

TX20

MACSEL10

MACSEL02

RSV09

MTXD00/

RMTXD00/

STXD0

MTXD03/

STXSYNC1

MCRS0/

RMCRSDV0

MTXEN0/

RMRTXEN0

MRXER0/

RMRXER0/

SRXCLK0

HHV15EN

PTV15P RGRD11

RGRD10

PTV15NRSV14

MTDX06/

RMTXEN1

MRXDV0/

RMCRSDV1

CV

DD

CV

DDMON

MCOL0

MTDX04/

RMTXD10/

STXCLK1

MACSEL00

TX26

TR24

TR23

DV

DD33

V

SS

TX16

TX15 TX13

TR26

TX22

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD15

V

SS

DV

DD15

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

CLKB1 TR15

TR10

TX24

TX23

V

SS

DV

DD33

TR11

TR27

TR20

V

SS

DV

DD33

DV

DD33

V

SS

TR02 CLKB2

TX10

TR25

TX21

FSB0

TX17

TR12 TX12

TX25

V

SS

DV

DD33

FSA2

TR14

TR13

DV

DD33

V

SS

V

SS

DV

DD33

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

TR03

FSA0 CLKA1

CLKA2

DV

DD33MON

V

SS

DV

DD33

TR07

TX00 CLKA0 TR01 FSB2

DV

DD33

V

SS

V

SS

DV

DD33

DV

DD33

V

SS

V

SS

DV

DD33

TR00

TX02

FSB1

TX05 TR05

TR06

CLKB0

TX01

www.ti.com

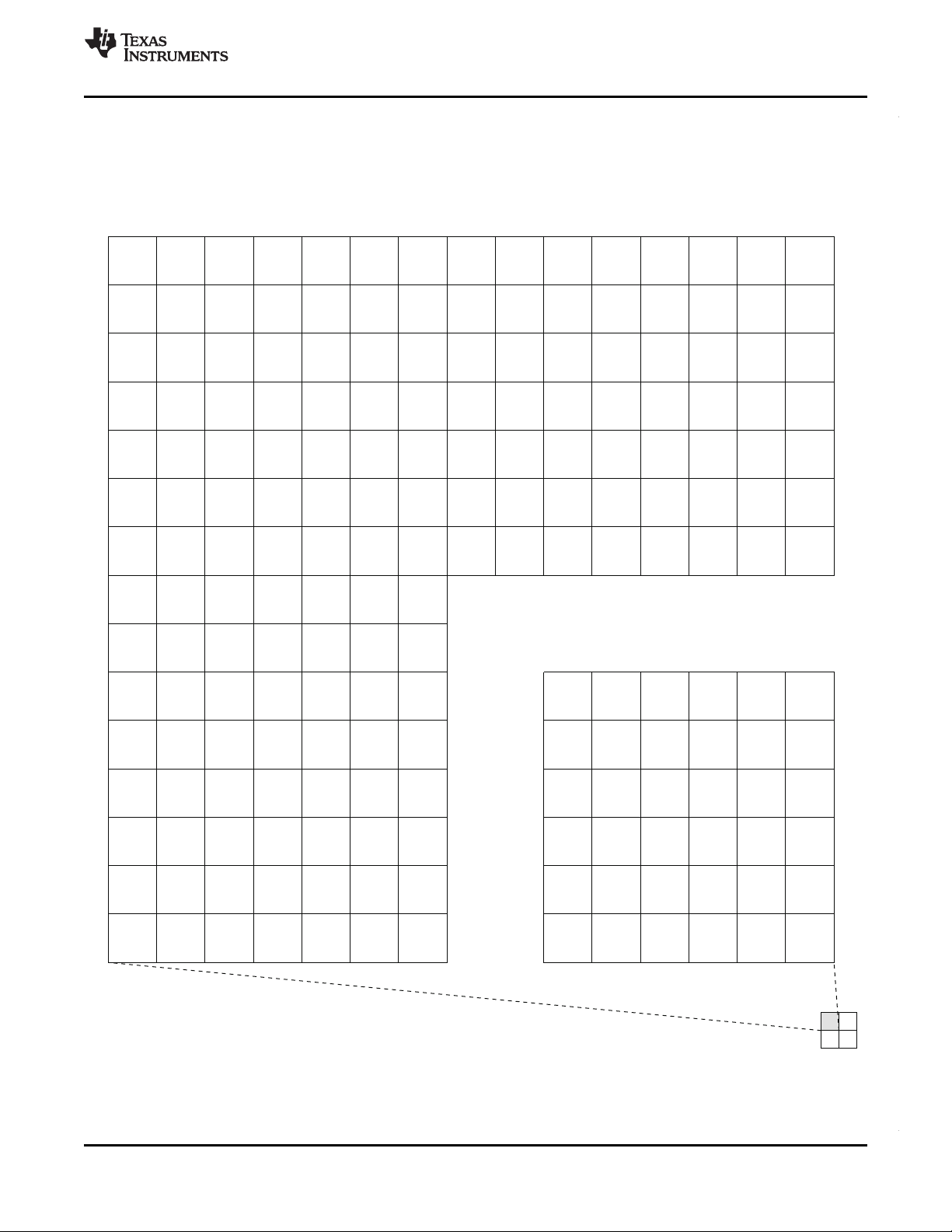

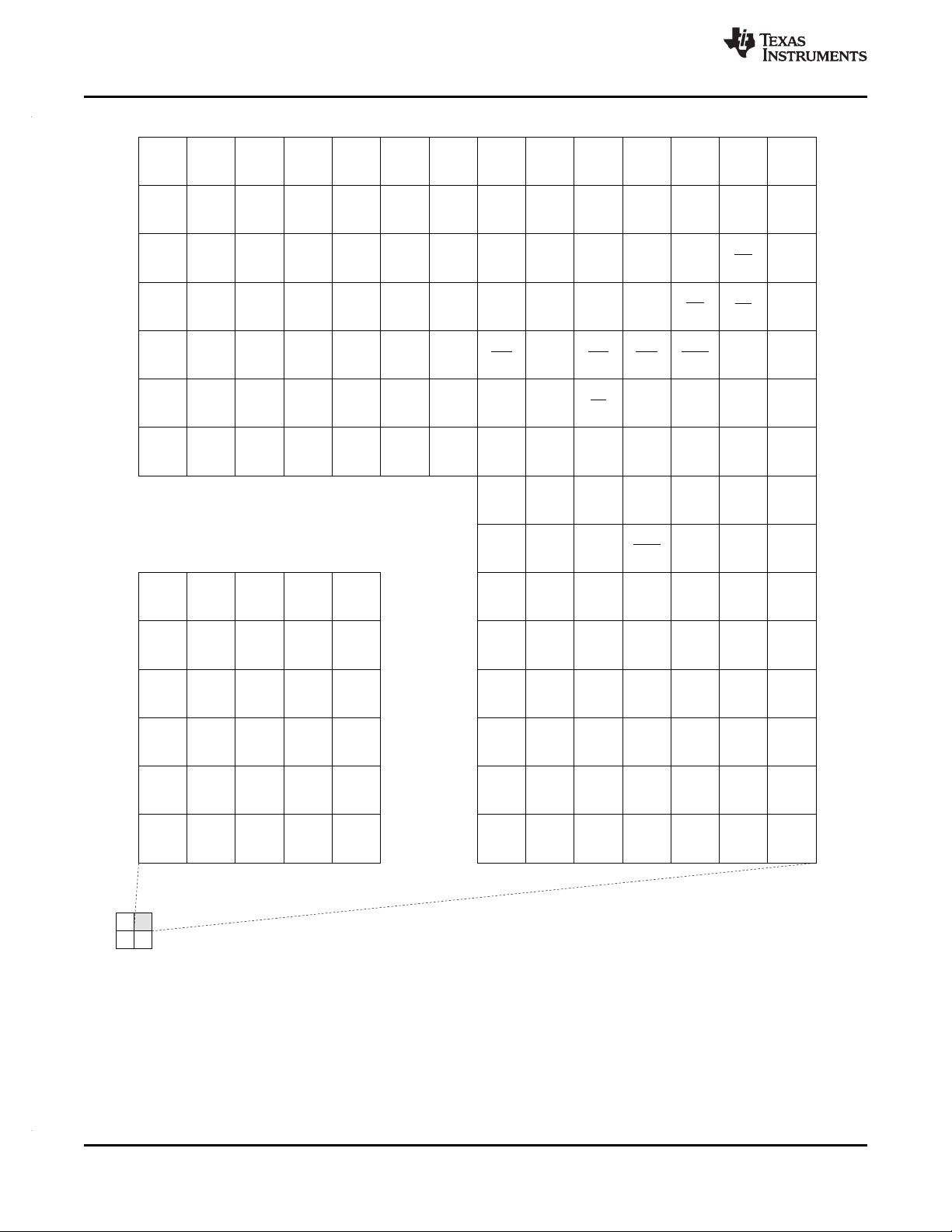

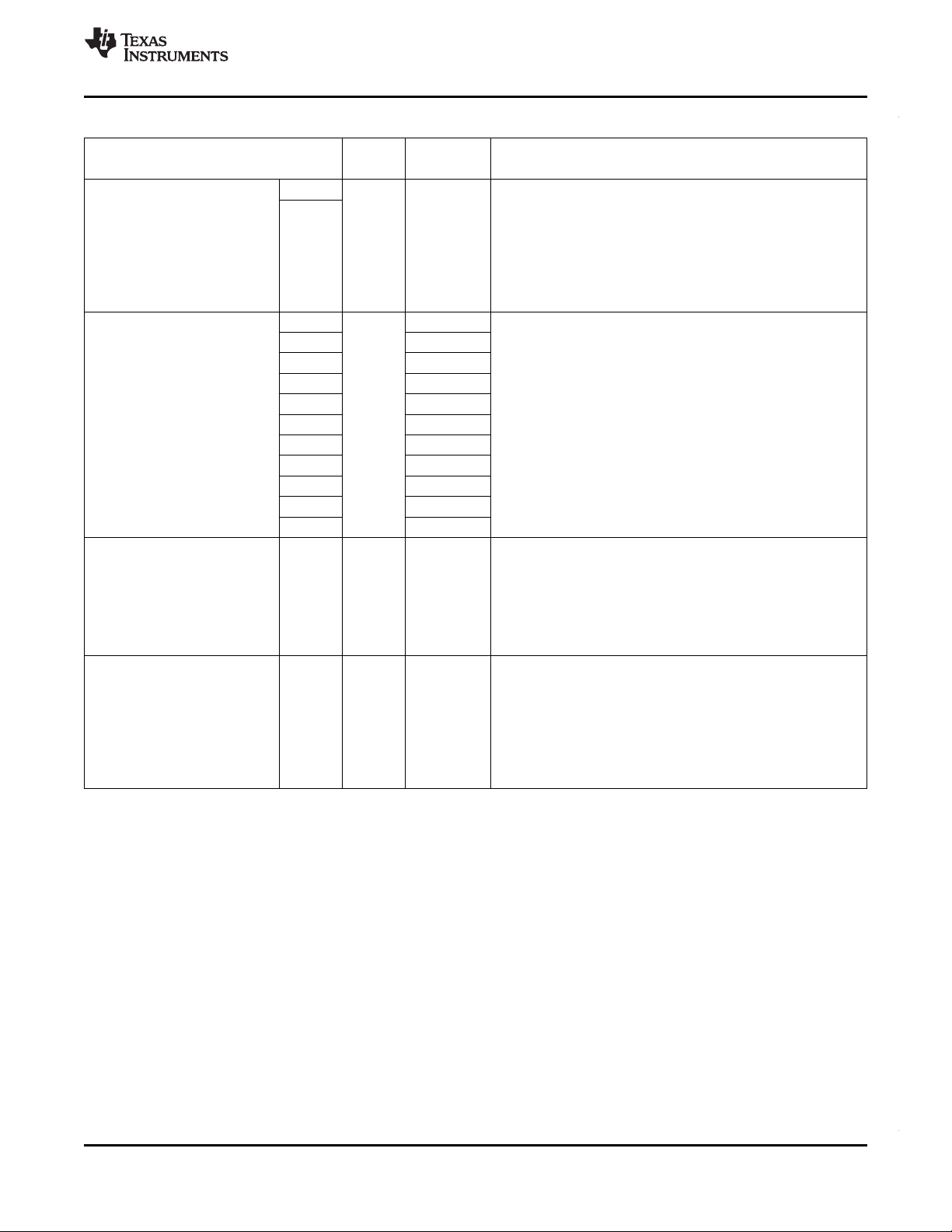

2.5 Pin Assignments

2.5.1 Pin Map

Figure 2-2 through Figure 2-5 show the C6472 pin assigments in four quadrants (A, B, C, and D).

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 19

Figure 2-2. C6472 Pin Map (Bottom View) [Quadrant A]

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 20

PRODUCTPREVIEW

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

28272625242322212019181716

28272625242322212019181716

AH

AJ

29

29

AG

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

AH

AJ

V

SS

CV

DD

V

SS

CV

DD

V

SS

DV

DD33

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD2

V

SS

DV

DDD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD2

V

SS

CV

DD

V

SS

CV

DD

V

SS

DV

DDD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD2

DV

DD33

V

SS

V

SS

DV

DD33

V

SS

DV

DD15

V

SS

DV

DD15

V

SS

DV

DD15

V

SS

DV

DD15

V

SS

DV

DD15

V

SS

DV

DD15

V

SS

DV

DD33

DV

DD33

V

SS

AV

DDA

AV

DDA

V

SS

DV

DD33

V

SS

V

SS

DV

DD33

V

SS

AV

DDT

V

SS

V

SS

V

SS

DV

DDR

RSV20

V

SS

RIOCLKN RIOTXN1 RIORXP1

V

SS

RIOCLKP RIOTXP1 RIORXN1RIOEN

CV

DD

V

SS

TIM02 TIMI1TIMIO

UXADDR4

UXADDR2 UXADDR0UXADDR1

UXADDR3

URADDR4

URADDR2 URADDR0URADDR1URADDR3

URSOC

URDATA2 URDATA0URDATA1UXENB

URDATA5

URDATA3URDATA4

DV

DD33

V

SS

URDATA10

URDATA8URDATA9

URDATA6URDATA7

HAS

URDATA13URDATA15 URDATA11URDATA12

V

SS

V

SS

RGTD12

RGTD13

RGCLK1

V

REFHSTL

RGTD00 RGRD03 HD08

HDS2

HD02

HDS1

HRDY URENB

DV

DD33

V

SS

RGTD02 RGMDCLK RGTXCTL0

HRW

HCS

URDATA14

RGRD02 RGRD00 HD15 HD09 HCNTL1 HD03 HCNTL0

HINT

HHWIL

HD00RGTD11 RGMDIO RGTD01 RGCLK0 RGRD01

RSV08

HD13

HD10

HD06

HD04

V

SS

V

SS

DV

DD33

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD15

V

SS

RGTXCTL1

RGRXCTL1

RGTXC1 RGTD10 RGTXC0

RGTD03

DV

DD15

RGRXC0

RGRXCTL0

HOUT

V

SS

HD12

HD14

HD07

HD11

HD01

HD05

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

www.ti.com

20 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Figure 2-3. C6472 Pin Map (Bottom View) [Quadrant B]

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 21

PRODUCTPREVIEW

M

L

K

J

H

G

F

E

D

C

B

A

28272625242322212019181716

28272625242322212019181716

N

P

29

29

M

L

K

J

H

G

F

E

D

C

B

A

N

P

V

SS

CV

DD

V

SS

CV

DD2

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD2

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

RIORXP0 RIOTXN0

V

SS

AV

DDT

V

SS

V

SS

V

SS

RIORXN0 RIOTXP0

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

DV

DD33

V

SS

V

SS

V

SS

V

SS

AV

DDA1

RSV13

SCL

V

SS

V

SS

RSV17 RSV16

DV

DD33

V

SS

SDA SYSCLKOUT CLKIN1

UXDATA8 UXCLK UXDATA14 URCLAV URCLK

UXDATA3

UXDATA9

UXCLAV

UXDATA13 UXDATA15

V

SS

UXDATA0 UXDATA4

UXDATA10

UXDATA12

V

SS

DV

DD33

CV

DD

CV

DD

V

SS

DV

DD18

DV

DD18

V

SS

DV

DD18

V

SS

DV

DD18

V

SS

V

SS

DV

DD33

DV

DD33

UXDATA1 UXDATA5 UXDATA11 UXSOC

DV

DD18

V

SS

RSV19 RSV18 DDREN RSV07

EMU10 EMU6 EMU17 EMU11

RSV21

UXDATA2 UXDATA6 UXDATA7

BED27

BED29

V

SS

V

SS

HHV18EN V

SS

EMU7 EMU3 EMU13 EMU2

EMUI6

TDI EMU8 EMU1

CV

DD

BSDDQM3

BSDDQS3P

BED30

PTV18N

PTV18P

DV

DD33

DV

DD33

EMU4 EMU14 EMU5

TCLK

TRST

TDO

V

SS

DV

DD33

V

SS

RSV23

RSV22

DV

DD33

EMU9

TMS

EMU15

CLKIN3 EMU12

DV

DD33

V

SS

DV

DD33

EMU18

EMU0

AV

DDA3

AV

DDA4

V

SS

DV

DD18

RSV15

RSV02

BSDDQS3N

BSDDQGATE2

BED28 BED31

BED26BED22

www.ti.com

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Figure 2-4. C6472 Pin Map (Bottom View) [Quadrant C]

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 21

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 22

PRODUCTPREVIEW

M

L

K

J

H

G

F

E

D

C

B

A

13121110987654321

13121110987654321

N

P

14 15

14 15

M

L

K

J

H

G

F

E

D

C

B

A

N

P

V

SS

CV

DD1

CV

DD1

CV

DD

TX07 TX04 TX06 TX03 TR04

V

SS

DV

DD33

DV

DD33

V

SS

V

SS

DV

DD33

DV

DD33

V

SS

V

SS

DV

DD33

DV

DD18

V

SS

V

SS

DV

DD18

DV

DD18

V

SS

V

SS

DV

DD33

GP11/

CFGGP1

GP05/

EMAC1_EN

GP01/

UTOPIA_EN

GP00/

HPI_EN

GP10/

CFGGP0

GP02/

TSIP0_EN

GP12/

CFGGP2

GP04/

TSIP2_EN

GP13/

CFGGP3

GP14/

CFGGP4

GP15/

SYSVLKOUTEN

GP07/

BOOTMODE1

GP06/

BOOTMODE0

BOOTACTIVE

NMI

GP08/

BOOTMODE2

GP09/

BOOTMODE3

GP03/

TSIP1_EN

LRESETNMIEN

LRESET

V

SS

DV

DD33

RESETSTAT

POR WDOUT

AV

DDA4

CORESEL0

RSV01

BED14

RESET

BSDDQM1

CORESEL1CORESEL2

DV

DD18

V

SS

DV

DD18

V

SS

DV

DD18

V

SS

DV

DD18

V

SS

V

SS

CV

DD1

V

SS

CV

DD1

V

SS

CV

DD1

V

SS

DV

DD18

V

SS

CV

DD1

DV

DD18

V

SS

V

SS

DV

DD18

BED15

BSDDQS1N

BED11 BED10

BED12

BSDDQS1P

BED09

BED07

BSDWE BCS1

V

REFSSTL

V

SS

DV

DD18

V

SS

BED20

BSDDQGATE3

BED25

BED23

BSDDQS2P

DV

DD18MON

BEA05

BEA08

BED24

BED21

DV

DD18

V

SS

BSDDQM2

BED18

V

SS

DV

DD18

BED13

BED08

BEA13

BECLKOUTN

BSDCAS BSDRAS

BSDDQGATE1

BED06

BSDDQS0P

BED03

DV

DD18

V

SS

BSDDQS0N

BED00

BED01

V

SS

BSDDQM0

BCSO

BED05 BED02

BSDDQGATE0

BED04 BBA0

BECLKOUTP

BSDCKE

BBA1

BBA2

BEA12

BEA11

BEA09 BEA07 BEA04

BED17

BSDDQS2N

BEA10

RSV24

RSV25

BEA06

DV

DD18

V

SS

BEA03

BEA02

BEA00

BEA01

BED19

BED16

V

SS

V

SS

CV

DD

V

SS

CV

DD

V

SS

V

SS

CV

DD

V

SS

CV

DD

V

SS

V

SS

CV

DD

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

www.ti.com

Figure 2-5. C6472 Pin Map (Bottom View) [Quadrant D]

22 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 23

PRODUCTPREVIEW

TRST

IEEEStandard

1149.1

(JTAG)

Emulation

Resetand

Interrupts

Control/Status

TDI

TDO

TMS

TCLK

Clock/PLL1

and

PLL Controller

EMU0

EMU1

CLKIN1

SYSCLKOUT

EMU14

EMU15

EMU16

EMU17

EMU18

·

·

·

CLKIN2

Clock/PLL2

(EMAC)

Clock/PLL3

(DDR2)

CLKIN3

RESET

RESETSTAT

POR

LRESETNMIEN

CORSEL[2:0]

LRESET

NMI

HOUT

DDREN

RIOEN

MACSEL0[2:0]

MACSEL1[1:0]

LENDIAN

Peripheral

Enable/Disable

BOOTACTIVE

www.ti.com

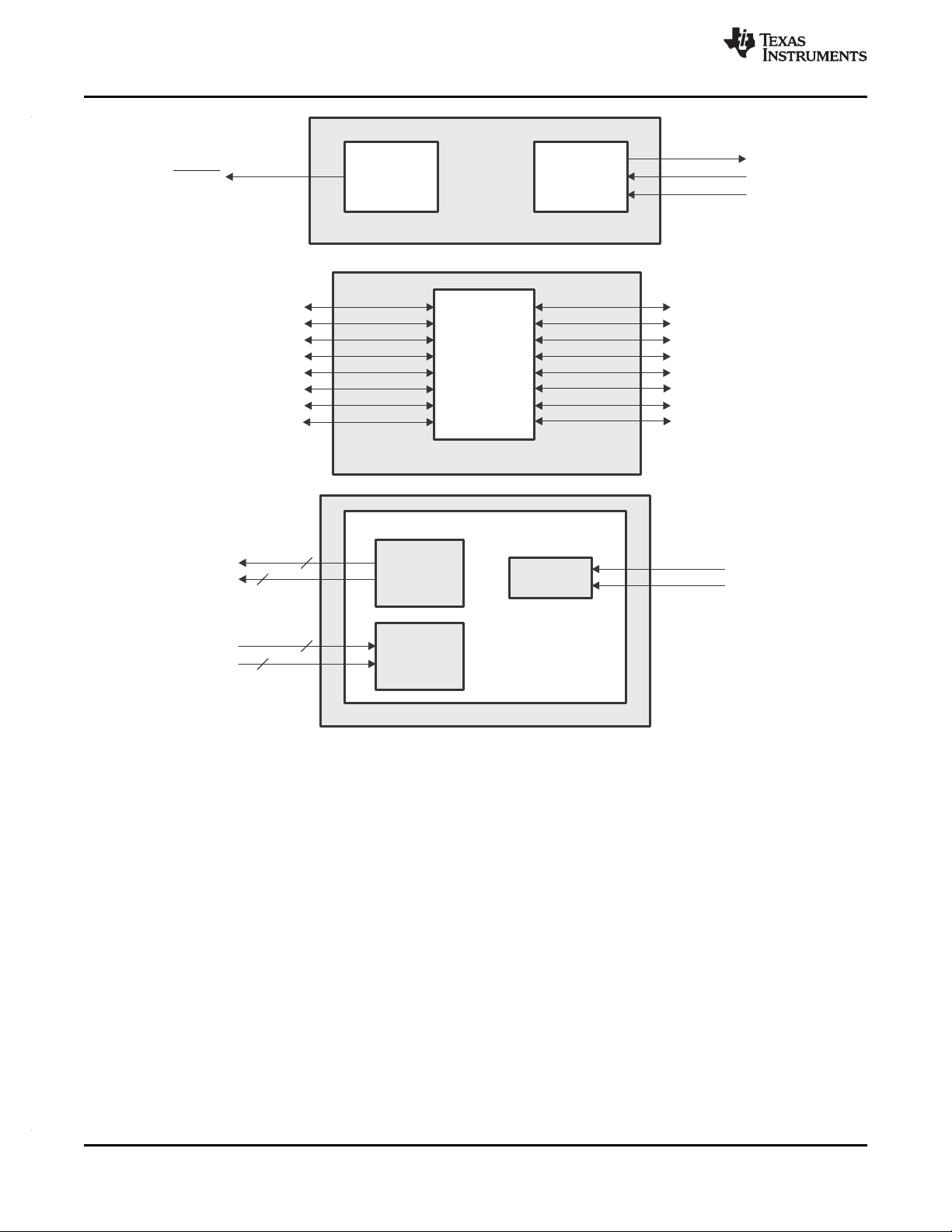

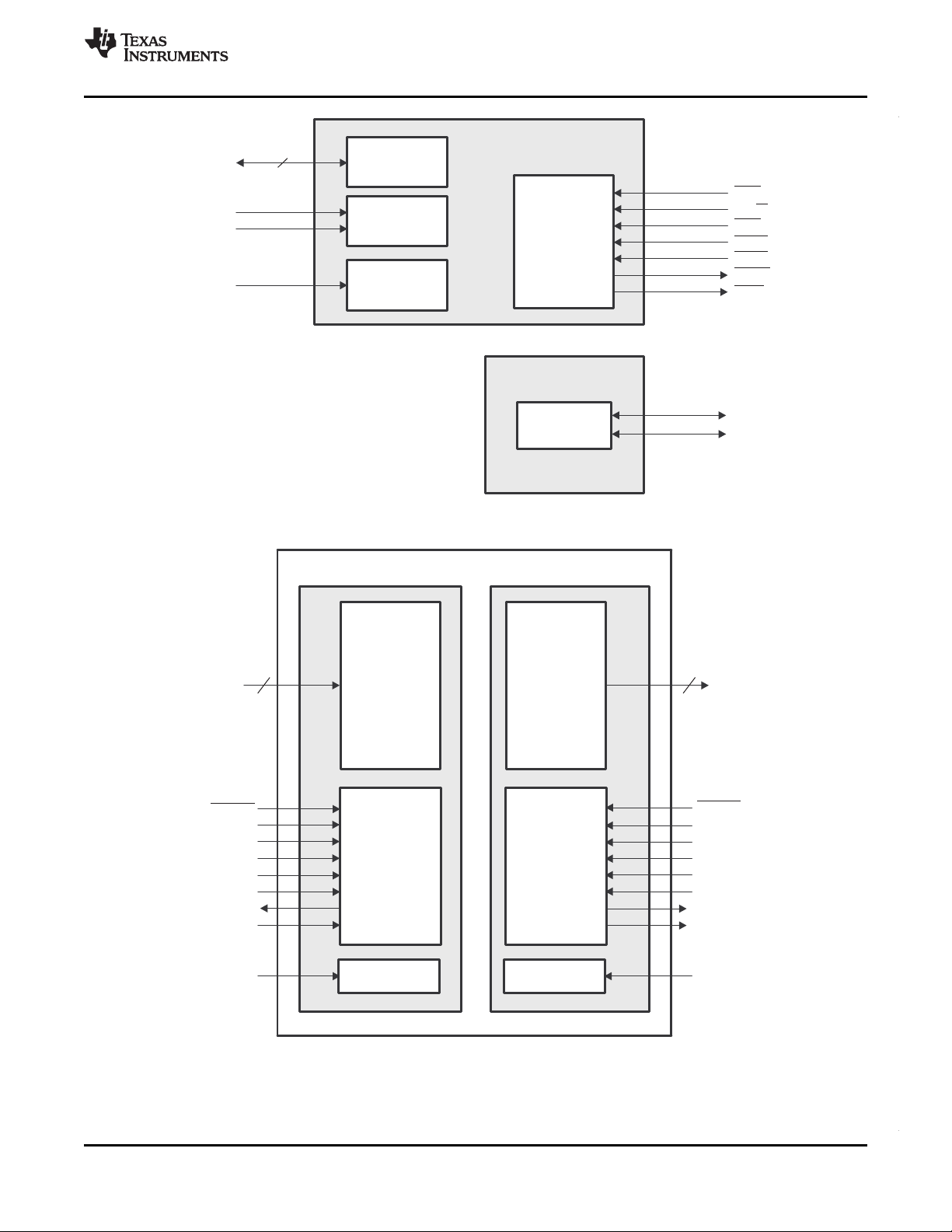

2.6 Signal Groups Description

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 23

Figure 2-6. CPU and Peripheral Signals

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 24

PRODUCTPREVIEW

GPIO

General-PurposeInput/Output0(GPIO)Port

GP[3]/TSIP1_EN

(D)

GP[2]/TSIP0_EN

(D)

GP[1]/UTOPIA_EN

(D)

GP[15]/SYSCLKOUTEN

(A)

GP[14]/CFGGP4

(B)

GP[13]/CFGGP3

(B)

GP[11]/CFGGP1

(B)

GP[10]/CFGGP0

(B)

GP[9]/BOOTMODE3

(C)

GP[8]/BOOTMODE2

(C)

GP[7]/BOOTMODE1

(C)

GP[6]/BOOTMODE0

(C)

GP[5]/EMAC1_EN

(D)

GP[4]/TSIP2_EN

(D)

GP[0]/HPI_EN

(D)

Timers(64-Bit)

Timers

0-5

Timers

6-11

RIOCLKP

Clock

RIOTXN[1:0]

RapidIO

Transmit

Receive

RIOCLKN

2

2

2

2

RIOTXP[1:0]

RIORXP[1:0]

RIORXN[1:0]

GP[12]/CFGGP2

(B)

TIMI1

TIMO2

TIMI0

WDOUT

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

www.ti.com

A. The SYSCLKOUTEN pin is muxed with GP[15]. For more details, see Section 3.

B. These CONFIG pins are muxed with the GPIO peripheral pins. For more details, see Section 3.

C. These BOOTMODE pins are muxed with the GPIO peripheral pins. For more details, see Section 3.

D. These pins are muxed with GPIO peripheral pins. For more details, see Section 3.

Figure 2-7. Timers/GPIO/RapidIO Peripheral Signals

24 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 25

PRODUCTPREVIEW

BECLKOUTP

BED[31:0]

BCS0

BEA[13:0]

Data

MemoryMap

SpaceSelect

Address

ByteEnables

32

14

External

MemoryI/F

Control

DDR2MemoryController(32-bitDataBus)

BSDCAS

BSDCKE

BECLKOUTN

BSDDQSP[3:0]

BSDRAS

BSDWE

BSDDQSN[3:0]

Bank Address

BBA[2:0]

BSDDQGATE[3:0]

BSDDQM3

BSDDQM2

BSDDQM1

BSDDQM0

BCS1

www.ti.com

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Figure 2-8. DDR2 Memory Controller Peripheral Signals

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 25

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 26

PRODUCTPREVIEW

RGRXC0

RGRD0[3:0]

RGRXCTL0

RGTXC0

RGTD0[3:0]

RGTXCTL0

RGMII0

Interface

MRXD00/RMRXD00/SRXD0

MRXD01/RMRXD01/SRXSYNC0

MRXD02/SRXD1

MRXD03/SRXSYNC1

MRXD04/RMRXD10

MRXD05/RMRXD11

MRXD06/RMRXER1

MRXD07

MRCLK0/SRXCLK1

MRXDV0/RMCRSDV1

MRXER0/RMRXER0/SRXCLK0

MCRS0/RMCRSDV0

GMTCLK0/REFCLK1/SREFCLK1

MTCLK0/REFCLK0/SREFCLK0

MTXD01/RMTXD01/STXSYNC0

MTXD02/STXD1

MTXD03/STXSYNC1

MTXD04/RMTXD10/STXCLK1

MTXD05/RMTXD11

MTXD06/RMTXEN1

MTXD07/STXCLK0

MTXEN0/RMTXEN0

MCOL0

Pin

Mux

RGRXC1

RGRD1[3:0]

RGRXCTL1

RGTXC1

RGTD1[3:0]

RGTXCTL1

RGMII1

Interface

GMDCLK

GMDIO

RGMDCLK

RGMDIO

MDIO

Controller

RMII0

Interface

S3MII0

Interface

Ethernet

MAC0

S3MII1

Interface

RMII1

Interface

Ethernet

MAC1

GMII0/MII0

MTXD00/RMTXD00/STXD0

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

www.ti.com

Figure 2-9. EMAC[1:0]/MDIO (RGMII[1:0], S3MII[1:0], MII0, RMII[1:0], and GMII0)

26 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Peripheral Signals

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 27

PRODUCTPREVIEW

HHWIL

(HPI16)

HCNTL0

HCNTL1

Data

RegisterSelect

Half-Word

Select

Control

HPI

16

HAS

HR/W

HCS

HDS1

HDS2

HRDY

HINT

HD[15:0]

SCL

I2C

SDA

URADDR2

Control/Status

URADDR4

URADDR3

URADDR1

URADDR0

ReceiveURDATA[15:0]

URCLAV

URSOC

URCLK

Clock

Control/Status

Clock

UXADDR2

UXADDR4

UXADDR3

UXADDR1

UXADDR0

UXDATA[15:0]

UXCLAV

UXENB

UXSOC

UXCLK

UTOPIA (SLAVE)

Transmit

URENB

16 16

www.ti.com

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

Figure 2-10. HPI/I2C Peripheral Signals

Copyright © 2009–2010, Texas Instruments Incorporated Device Overview 27

Figure 2-11. UTOPIA Peripheral Signals

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 28

PRODUCTPREVIEW

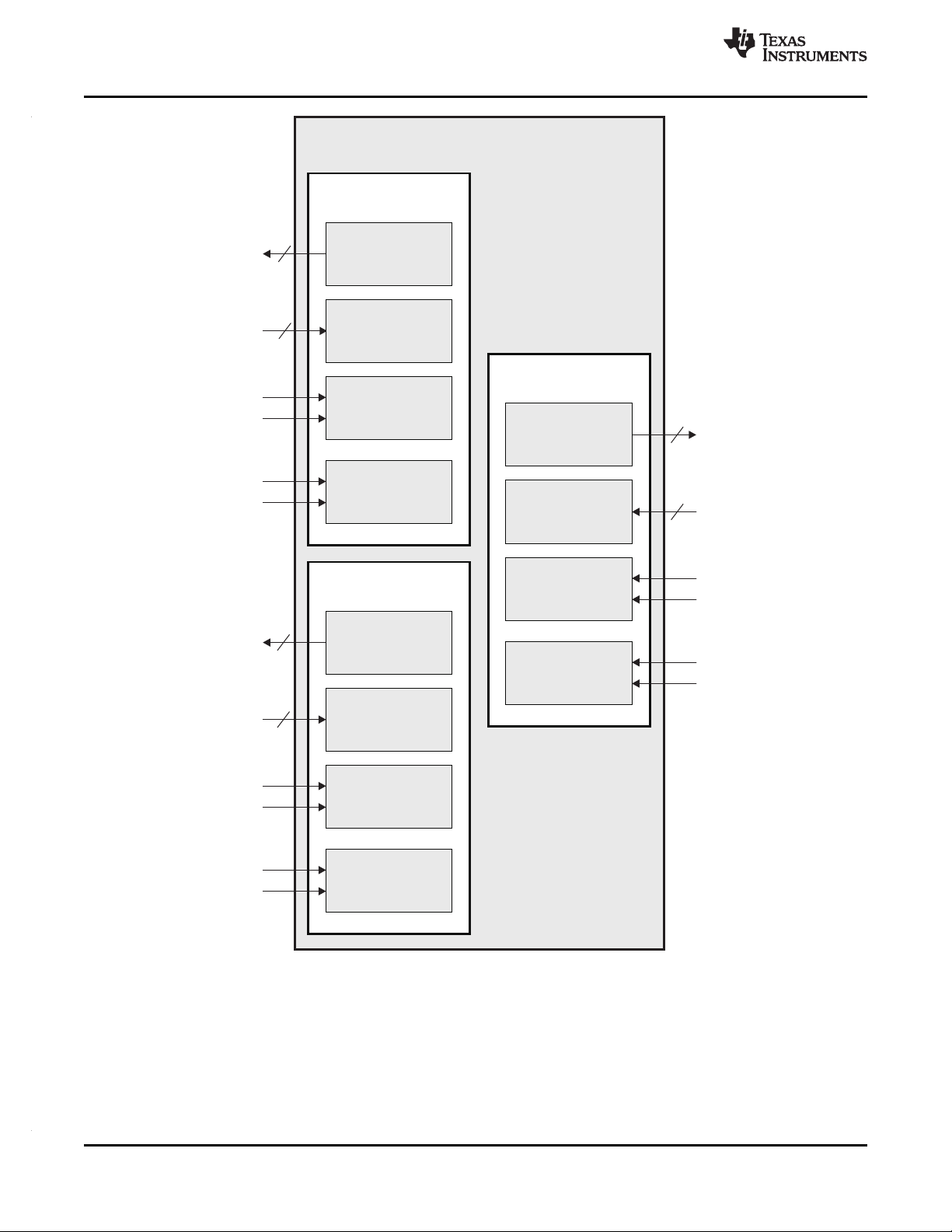

TelecomSerialInterfacePort

TX0[7:0]

TR0[7:0]

TSIP2

TX2[7:0]

TR2[7:0]

TX1[7:0]

TR1[7:0]

TSIP0

TSIP1

Transmit

Receive

Control

Clock

Transmit

Receive

Control

Clock

Transmit

Receive

Control

Clock

8

8

8

8

FSA0

FSB0

CLKA0

CLKB0

FSA2

FSB2

8

8

FSA1

FSB1

CLKA1

CLKB1

CLKA2

CLKB2

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

www.ti.com

Figure 2-12. TSIP[2:0] Peripheral Signals

28 Device Overview Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6472

Page 29

PRODUCTPREVIEW

www.ti.com

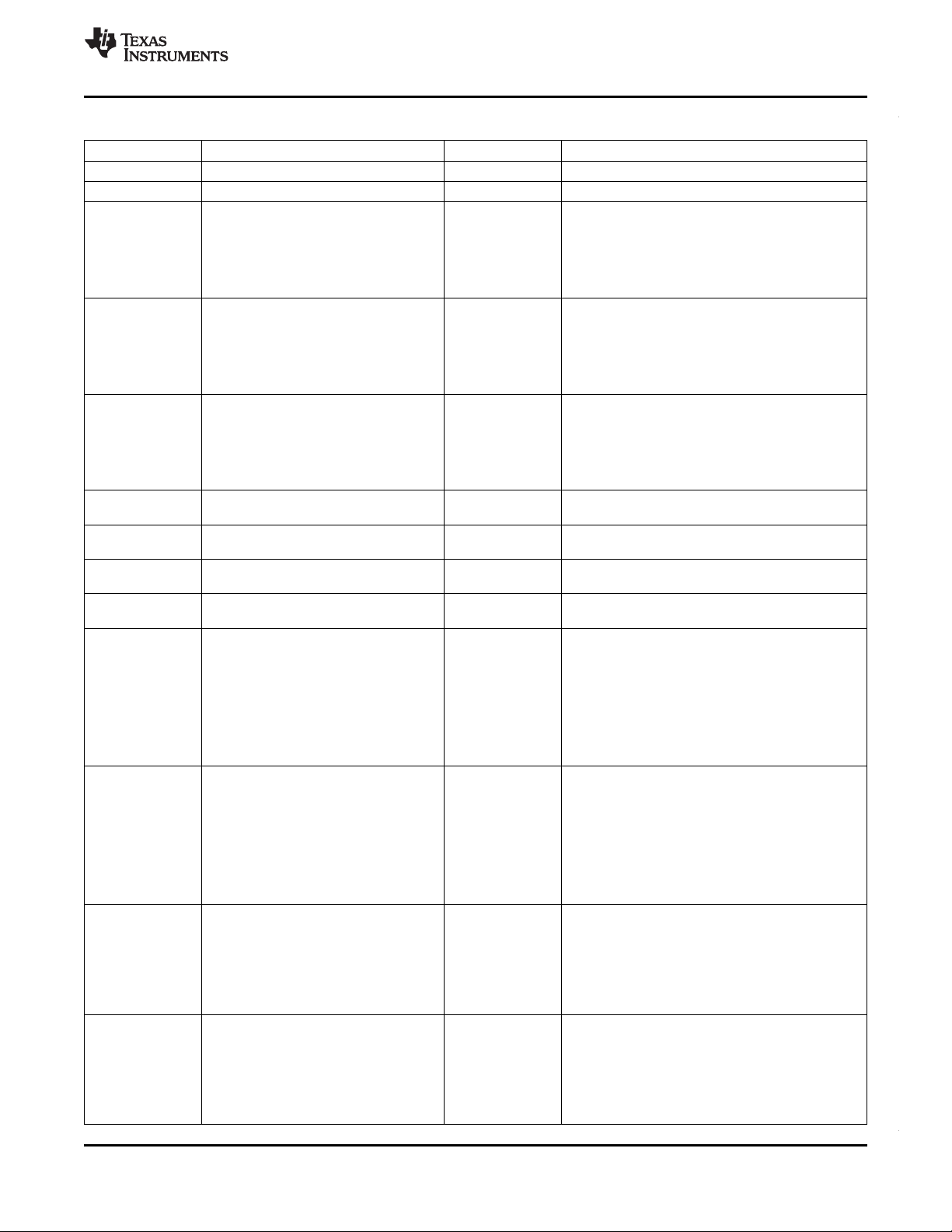

2.7 Terminal Functions

The terminal functions table (Table 2-5) identifies the external signal names, the associated pin (ball)

numbers along with the mechanical package designator, the pin type (I, O/Z, or I/O/Z), whether the pin

has any internal pullup/pulldown resistors and a functional pin description. For more detailed information

on device configuration, peripheral selection, multiplexed/shared pins, and debugging considerations, see

Section 3.

SIGNAL

NAME NO.

MACSEL0[0] AE6 I IPD

MACSEL0[1] AG5 I IPD EMAC0 configuration select pin (for details, see Table 3-1).

MACSEL0[2] AF6 I IPD

LENDIAN AH4 I IPU 0 = System operates in Big-Endian mode

MACSEL1[0] AF5 I IPD

MACSEL1[1] AH5 I IPD

DDREN E20 I IPD 0 = disabled (only use this mode if DDR is not powered)

RIOEN U26 I IPD 0 = disabled (only use this mode if RapidIO is not powered)

HOUT AH23 O/Z IPU Host event output.

GP00/HPI_EN M1 I/O/Z IPD off.

GP01/UTOPIA_EN N5 I/O/Z IPD turned off.

GP02/TSIP0_EN M3 I/O/Z IPD General-purpose input/output pin [4:2] multiplexed with TSIP[2:0]

GP03/TSIP1_EN K5 I/O/Z IPD

GP04/TSIP2_EN M5 I/O/Z IPD

GP05/EMAC1_EN N4 I/O/Z IPD turned off.

Table 2-5. Terminal Functions

(1)

TYPE

GENERAL-PURPOSE INPUT/OUTPUT PINS

IPD/IPU

CONFIGURATION PINS

(2) (3)

Device Endian pin.

1 = System operates in Little-Endian mode (default)

EMAC1 configuration select pin (for details, see Table 3-1).

DDR2 Memory Controller enable

1 = enabled

RapidIO enable

1 = enabled

HOST EVENT PINS

General-purpose input/output pin 0 multiplexed with HPI internal

pulls enable/disable

0 = Internal pulls on HPI IO are enabled and buffers are turned

1 = Internal pulls on most HPI IO are disabled and all buffers are

turned on.

For more detail about internal pull options, see Section 3.3.1.

General-purpose input/output pin 1 multiplexed with UTOPIA

internal pulls enable/disable

0 = Internal pulls on UTOPIA IO are enabled and buffers are

1 = Internal pulls on UTOPIA IO are disabled and buffers are

turned on.

For more detail about internal pull options, see Section 3.3.1.

internal pulls enable/disable

0 = Internal pulls on TSIPx IO are enabled and buffers are turned

off.

1 = Internal pulls on TSIPx IO are disabled and buffers are turned

on.

For more detail about internal pull options, see Section 3.3.1.

General-purpose input/output pin 5 multiplexed with EMAC1

internal pulls enable/disable

0 = Internal pulls on EMAC1 IO are enabled and buffers are

1 = Internal pulls on EMAC1 IO are disabled and buffers are

turned on.

For more detail about internal pull options, see Section 3.3.1.

TMS320C6472

SPRS612E–JUNE 2009–REVISED OCTOBER 2010

DESCRIPTION