Page 1

TMS320C6000

CPU and Instruction Set

Reference Guide

Literature Number: SPRU189D

March 1999

Printed on Recycled Paper

Page 2

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products

or to discontinue any product or service without notice, and advise customers to obtain the latest

version of relevant information to verify , before placing orders, that information being relied on

is current and complete. All products are sold subject to the terms and conditions of sale supplied

at the time of order acknowledgement, including those pertaining to warranty, patent

infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the

time of sale in accordance with TI’s standard warranty. Testing and other quality control

techniques are utilized to the extent TI deems necessary to support this warranty . Specific testing

of all parameters of each device is not necessarily performed, except those mandated by

government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE

POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR

ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR

PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUIT ABLE FOR

USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY

AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards must be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance or customer product design. TI does not

warrant or represent that any license, either express or implied, is granted under any patent right,

copyright, mask work right, or other intellectual property right of TI covering or relating to any

combination, machine, or process in which such semiconductor products or services might be

or are used. TI’s publication of information regarding any third party’s products or services does

not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1999, Texas Instruments Incorporated

Page 3

About This Manual

This reference guide describes the CPU architecture, pipeline, instruction set,

and interrupts for the TMS320C6000 digital signal processors (DSPs). Unless

otherwise specified, all references to the ’C6000 refer to the TMS320C6000

platform of DSPs, ’C62x refers to the TMS320C62x fixed-point DSPs in the

’C6000 platform, and ’C67x refers to the TMS320C67x floating-point DSPs in

the ’C6000 platform.

How to Use This Manual

Use this manual as a reference for the architecture of the TMS320C6000 CPU.

First-time readers should read Chapter 1 for general information about TI

DSPs, the features of the ’C6000, and the applications for which the ’C6000

is best suited.

Preface

Read This First

Read chapters 2, 5, 6, and 7 to grasp the concepts of the architecture. Chapter 3 and Chapter 4 contain detailed information about each instruction and is

best used as reference material; however, you may want to read sections 3.1

through 3.9 and sections 4.1 through 4.6 for general information about the

instruction set and to understand the instruction descriptions, then browse

through Chapter 3 and Chapter 4 to familiarize yourself with the instructions.

Contents

iii

Page 4

Read This First

The following table gives chapter references for specific information:

If you are looking for information about:

T urn to these chapters:

Addressing modes Chapter 3,

Instruction Set

Chapter 4,

Instruction Set

Conditional operations Chapter 3,

Instruction Set

Chapter 4,

Instruction Set

Control registers Chapter 2,

CPU architecture and data

paths

Delay slots Chapter 3,

General-purpose register files Chapter 2,

Instruction set Chapter 3,

Chapter 2,

Instruction Set

Chapter 4,

Instruction Set

Chapter 5,

Chapter 6,

Instruction Set

Chapter 4,

Instruction Set

TMS320C62x/C67x Fixed-Point

TMS320C67x Floating-Point

TMS320C62x/C67x Fixed-Point

TMS320C67x Floating-Point

CPU Data Paths and Control

CPU Data Paths and Control

TMS320C62x/C67x Fixed-Point

TMS320C67x Floating-Point

TMS320C62x Pipeline

TMS320C67x Pipeline

CPU Data Paths and Control

TMS320C62x/C67x Fixed-Point

TMS320C67x Floating-Point

Interrupts and control registers Chapter 7,

Parallel operations Chapter 3,

Instruction Set

Chapter 4,

Instruction Set

Pipeline phases and operation Chapter 5,

Chapter 6,

Reset Chapter 7,

If you are interested in topics that are not listed here, check

tation From Texas Instruments

, on page vi, for brief descriptions of other

Interrupts

TMS320C62x/C67x Fixed-Point

TMS320C67x Floating-Point

TMS320C62x Pipeline

TMS320C67x Pipeline

Interrupts

Related Documen-

’C6x-related books that are available.

iv

Page 5

Notational Conventions

This document uses the following conventions:

- Program listings and program examples are shown in a special font.

-

- In instruction syntaxes, portions of a syntax that are in bold should be en-

Notational Conventions

Here is a sample program listing:

LDW .D1 *A0,A1

ADD .L1 A1,A2,A3

NOP 3

MPY .M1 A1,A4,A5

To help you easily recognize instructions and parameters throughout the

book, instructions are in bold face and parameters are in

italics

(except

in program listings).

tered as shown; portions of a syntax that are in

italics

describe the

type

of

information that should be entered. Here is an example of an instruction:

MPY

src1,src2,dst

MPY is the instruction mnemonic. When you use MPY, you must supply

two source operands (

appropriate types as defined in Chapter 3,

Point Instruction Set

.

src1

and

src2

) and a destination operand (

TMS320C62x/C67x Fixed-

dst

) of

Although the instruction mnemonic (MPY in this example) is in capital letters, the ’C6x assembler

is not case sensitive

— it can assemble mnemon-

ics entered in either upper or lower case.

- Square brackets, [ and ], and parentheses, ( and ), are used to identify op-

tional items. If you use an optional item, you must specify the information

within brackets or parentheses; however, you do not enter the brackets or

parentheses themselves. Here is an example of an instruction that has optional items.

[

label

] EXTU (

.unit) src2, csta, cstb, dst

The EXTU instruction is shown with a label and several parameters. The

[

label

] and the parameter (

cstb,

and

dst

are not optional.

- Throughout this book MSB means

least significant bit

- A special icon is used to indicate material that applies only to the floating-

.

.unit

) are optional. The parameters

most significant bit

src2, csta,

and LSB means

point (’C67x) DSP:

Read This First

v

Page 6

Related Documentation From Texas Instruments

Related Documentation From Texas Instruments

The following books describe the TMS320C6x generation and related support

tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please

identify the book by its title and literature number.

TMS320C62x/C67x Technical Brief

introduction to the ’C62x/C67x digital signal processors, development

tools, and third-party support.

TMS320C6201 Digital Signal Processor Data Sheet

SPRS051) describes the features of the TMS320C6201 and provides

pinouts, electrical specifications, and timings for the device.

TMs320C6202 Digital Signal Processor Data Sheet

SPRS072) describes the features of the TMS320C6202 fixed-point DSP

and provides pinouts, electrical specifications, and timings for the device.

TMS320C6211 Digital Signal Processor Data Sheet

SPRS073) describes the features of the TMS320C621 1 fixed-point DSP

and provides pinouts, electrical specifications, and timings for the device.

TMS320C6701 Digital Signal Processor Data Sheet

SPRS067) describes the features of the TMS320C6701 floating-point

DSP and provides pinouts, electrical specifications, and timings for the

device.

TMS320C6000 Peripherals Reference Guide

describes common peripherals available on the TMS320C6000 digital

signal processors. This book includes information on the internal data

and program memories, the external memory interface (EMIF), the host

port, serial ports, direct memory access (DMA), clocking and phaselocked loop (PLL), and the power-down modes.

(literature number SPRU197) gives an

(literature number

(literature number

(literature number

(literature number

(literature number SPRU190)

TMS320C62x/C67x Programmer’s Guide

describes ways to optimize C and assembly code for the

TMS320C62x/C67x DSPs and includes application program examples.

TMS320C6000 Assembly Language Tools User’s Guide

SPRU186) describes the assembly language tools (assembler, linker,

and other tools used to develop assembly language code), assembler

directives, macros, common object file format, and symbolic debugging

directives for the ’C6000 generation of devices.

vi

(literature number SPRU198)

(literature number

Page 7

Related Documentation From Texas Instruments / Trademarks

Trademarks

TMS320C6000 Optimizing C Compiler User’s Guide

(literature number

SPRU187) describes the ’C6000 C compiler and the assembly optimizer .

This C compiler accepts ANSI standard C source code and produces assembly language source code for the ’C6000 generation of devices. The

assembly optimizer helps you optimize your assembly code.

TMS320 Third-Party Support Reference Guide

(literature number

SPRU052) alphabetically lists over 100 third parties that provide various

products that serve the family of TMS320 digital signal processors. A

myriad of products and applications are offered—software and hardware

development tools, speech recognition, image processing, noise cancellation, modems, etc.

TI, XDS510, V elociTI, and 320 Hotline On-line are trademarks of T exas Instruments Incorporated.

Windows and Windows NT are registered trademarks of Microsoft Corporation.

Read This First

vii

Page 8

If You Need Assistance

If You Need Assistance . . .

- World-Wide Web Sites

TI Online http://www.ti.com

Semiconductor Product Information Center (PIC) http://www.ti.com/sc/docs/pic/home.htm

DSP Solutions http://www.ti.com/dsps

320 Hotline On-linet http://www.ti.com/sc/docs/dsps/support.htm

- North America, South America, Central America

Product Information Center (PIC) (972) 644-5580

TI Literature Response Center U.S.A. (800) 477-8924

Software Registration/Upgrades (214) 638-0333 Fax: (214) 638-7742

U.S.A. Factory Repair/Hardware Upgrades (281) 274-2285

U.S. Technical Training Organization (972) 644-5580

DSP Hotline (281) 274-2320 Fax: (281) 274-2324 Email: dsph@ti.com

DSP Modem BBS (281) 274-2323

DSP Internet BBS via anonymous ftp to ftp://ftp.ti.com/pub/tms320bbs

- Europe, Middle East, Africa

European Product Information Center (EPIC) Hotlines:

Multi-Language Support +33 1 30 70 11 69 Fax: +33 1 30 70 10 32

Email: epic@ti.com

Deutsch +49 8161 80 33 11 or +33 1 30 70 11 68

English +33 1 30 70 11 65

Francais +33 1 30 70 11 64

Italiano +33 1 30 70 11 67

EPIC Modem BBS +33 1 30 70 11 99

European Factory Repair +33 4 93 22 25 40

Europe Customer Training Helpline Fax: +49 81 61 80 40 10

- Asia-Pacific

Literature Response Center +852 2 956 7288 Fax: +852 2 956 2200

Hong Kong DSP Hotline +852 2 956 7268 Fax: +852 2 956 1002

Korea DSP Hotline +82 2 551 2804 Fax: +82 2 551 2828

Korea DSP Modem BBS +82 2 551 2914

Singapore DSP Hotline Fax: +65 390 7179

Taiwan DSP Hotline +886 2 377 1450 Fax: +886 2 377 2718

Taiwan DSP Modem BBS +886 2 376 2592

Taiwan DSP Internet BBS via anonymous ftp to ftp://dsp.ee.tit.edu.tw/pub/TI/

- Japan

Product Information Center +0120-81-0026 (in Japan) Fax: +0120-81-0036 (in Japan)

DSP Hotline +03-3769-8735 or (INTL) 813-3769-8735 Fax: +03-3457-7071 or (INTL) 813-3457-7071

DSP BBS via Nifty-Serve Type “Go TIASP”

- Documentation

When making suggestions or reporting errors in documentation, please include the following information that is on the title

page: the full title of the book, the publication date, and the literature number.

Mail: Texas Instruments Incorporated Email: dsph@ti.com

Technical Documentation Services, MS 702

P.O. Box 1443

Houston, Texas 77251-1443

Note: When calling a Literature Response Center to order documentation, please specify the literature number of the

viii

book.

+03-3457-0972 or (INTL) 813-3457-0972 Fax: +03-3457-1259 or (INTL) 813-3457-1259

Page 9

Contents

Contents

Summarizes the features of the TMS320 family of products and presents typical applications.

Describes the TMS320C62x/C67x DSPs and lists their key features.

1 Introduction 1Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Summarizes the features of the TMS320 family of products and presents typical applications.

Describes the TMS320C62xx DSP and lists its key features.

1.1 TMS320 Family Overview 1Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.1 History of TMS320 DSPs 1Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.2 Typical Applications for the TMS320 Family 1Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Overview of the TMS320C6x Generation of Digital Signal Processors 1Ć4. . . . . . . . . . . . .

1.3 Features and Options of the TMS320C62x/C67x 1Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 TMS320C62x/C67x Architecture 1Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.1 Central Processing Unit (CPU) 1Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.2 Internal Memory 1Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.3 Peripherals 1Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 CPU Data Paths and Control 2Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Summarizes the TMS320C62x/C67x architecture and describes the primary components of

the CPU.

2.1 General-Purpose Register Files 2Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Functional Units 2Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Register File Cross Paths 2Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Memory, Load, and Store Paths 2Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Data Address Paths 2Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 TMS320C62x/C67x Control Register File 2Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.1 Addressing Mode Register (AMR) 2Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2 Control Status Register (CSR) 2Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.3 E1 Phase Program Counter (PCE1) 2Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 TMS320C67x Extensions to the Control Register File 2Ć13. . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.1 Floating-Point Adder Configuration Register (FADCR) 2Ć14. . . . . . . . . . . . . . . . . . .

2.7.2 Floating-Point Auxiliary Configuration Register (FAUCR) 2Ć16. . . . . . . . . . . . . . . . .

2.7.3 Floating-Point Multiplier Configuration Register (FMCR) 2Ć18. . . . . . . . . . . . . . . . .

ix

Page 10

Contents

3 TMS320C62x/C67x Fixed-Point Instruction Set 3Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the assembly language instructions that are common to both the TMS320C62x and

TMS320C67x, including examples of each instruction. Provides information about addressing

modes, resource constraints, parallel operations, and conditional operations.

3.1 Instruction Operation and Execution Notations 3Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Mapping Between Instructions and Functional Units 3Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 TMS320C62x/C67x Opcode Map 3Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Delay Slots 3Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Parallel Operations 3Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Example Parallel Code 3Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2 Branching Into the Middle of an Execute Packet 3Ć15. . . . . . . . . . . . . . . . . . . . . . . .

3.6 Conditional Operations 3Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7 Resource Constraints 3Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.1 Constraints on Instructions Using the Same Functional Unit 3Ć17. . . . . . . . . . . . . .

3.7.2 Constraints on Cross Paths (1X and 2X) 3Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.3 Constraints on Loads and Stores 3Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.4 Constraints on Long (40-Bit) Data 3Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.5 Constraints on Register Reads 3Ć19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.6 Constraints on Register Writes 3Ć19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 Addressing Modes 3Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.1 Linear Addressing Mode 3Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.2 Circular Addressing Mode 3Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.3 Syntax for Load/Store Address Generation 3Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9 Individual Instruction Descriptions 3Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 TMS320C67x Floating-Point Instruction Set 4Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the TMS320C67x floating-point instruction set, including examples of each

instruction. Provides information about addressing modes and resource constraints.

4.1 Instruction Operation and Execution Notations 4Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Mapping Between Instructions and Functional Units 4Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Overview of IEEE Standard Single- and Double-Precision Formats 4Ć6. . . . . . . . . . . . . . . .

4.4 Delay Slots 4Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 TMS320C67x Instruction Constraints 4Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Individual Instruction Descriptions 4Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 TMS320C62x Pipeline 5Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes phases, operation, and discontinuities for the TMS320C62x CPU pipeline.

5.1 Pipeline Operation Overview 5Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 Fetch 5Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2 Decode 5Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.3 Execute 5Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.4 Summary of Pipeline Operation 5Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Pipeline Execution of Instruction Types 5Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 Single-Cycle Instructions 5Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

x

Page 11

Contents

5.2.2 Multiply Instructions 5Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.3 Store Instructions 5Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.4 Load Instructions 5Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.5 Branch Instructions 5Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Performance Considerations 5Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Pipeline Operation With Multiple Execute Packets in a Fetch Packet 5Ć18. . . . . .

5.3.2 Multicycle NOPs 5Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.3 Memory Considerations 5Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 TMS320C67x Pipeline 6Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes phases, operation, and discontinuities for the TMS320C67x CPU pipeline.

6.1 Pipeline Operation Overview 6Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.1 Fetch 6Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.2 Decode 6Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.3 Execute 6Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.4 Summary of Pipeline Operation 6Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Pipeline Execution of Instruction Types 6Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Functional Unit Hazards 6Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.1 .S-Unit Hazards 6Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.2 .M-Unit Hazards 6Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.3 .L-Unit Hazards 6Ć30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.4 D-Unit Instruction Hazards 6Ć34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.5 Single-Cycle Instructions 6Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.6 16 × 16-Bit Multiply Instructions 6Ć39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.7 Store Instructions 6Ć40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.8 Load Instructions 6Ć42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.9 Branch Instructions 6Ć44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.10 2-Cycle DP Instructions 6Ć46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.11 4-Cycle Instructions 6Ć47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.12 INTDP Instruction 6Ć47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.13 DP Compare Instructions 6Ć48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.14 ADDDP/SUBDP Instructions 6Ć49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.15 MPYI Instructions 6Ć50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.16 MPYID Instructions 6Ć50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.17 MPYDP Instructions 6Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Performance Considerations 6Ć52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4.1 Pipeline Operation With Multiple Execute Packets in a Fetch Packet 6Ć52. . . . . .

6.4.2 Multicycle NOPs 6Ć54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4.3 Memory Considerations 6Ć56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xi

Page 12

Contents

7 Interrupts 7Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the TMS320C62x/C67x interrupts, including reset and nonmaskable interrupts

(NMI), and explains interrupt control, detection, and processing.

7.1 Overview of Interrupts 7Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.1 Types of Interrupts and Signals Used 7Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.2 Interrupt Service Table (IST) 7Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.3 Summary of Interrupt Control Registers 7Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 Globally Enabling and Disabling Interrupts

(Control Status Register–CSR) 7Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Individual Interrupt Control 7Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3.1 Enabling and Disabling Interrupts (Interrupt Enable Register–IER) 7Ć13. . . . . . . .

7.3.2 Status of, Setting, and Clearing Interrupts

(Interrupt Flag, Set, and Clear Registers–IFR, ISR, ICR) 7Ć14. . . . . . . . . . . . . . . . .

7.3.3 Returning From Interrupt Servicing 7Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 Interrupt Detection and Processing 7Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.1 Setting the Nonreset Interrupt Flag 7Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4.2 Conditions for Processing a Nonreset Interrupt 7Ć18. . . . . . . . . . . . . . . . . . . . . . . . .

7.4.3 Actions Taken During Nonreset Interrupt Processing 7Ć21. . . . . . . . . . . . . . . . . . . .

7.4.4 Setting the RESET Interrupt Flag for the TMS320C62x/C67x 7Ć22. . . . . . . . . . . . .

7.4.5 Actions Taken During RESET

Interrupt Processing 7Ć23. . . . . . . . . . . . . . . . . . . . . .

7.5 Performance Considerations 7Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.1 General Performance 7Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.2 Pipeline Interaction 7Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6 Programming Considerations 7Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.1 Single Assignment Programming 7Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.2 Nested Interrupts 7Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.3 Manual Interrupt Processing 7Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6.4 Traps 7Ć27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Glossary AĆ1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Defines terms and abbreviations used throughout this book.

xii

Page 13

Figures

Figures

1–1 TMS320C62x/C67x Block Diagram 1Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 TMS320C62x CPU Data Paths 2Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 TMS320C67x CPU Data Paths 2Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Storage Scheme for 40-Bit Data in a Register Pair 2Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Addressing Mode Register (AMR) 2Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 Control Status Register (CSR) 2Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 E1 Phase Program Counter (PCE1) 2Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Floating-Point Adder Configuration Register (FADCR) 2Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Floating-Point Auxiliary Configuration Register (FAUCR) 2Ć16. . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 Floating-Point Multiplier Configuration Register (FMCR) 2Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 TMS320C62x/C67x Opcode Map 3Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Basic Format of a Fetch Packet 3Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Examples of the Detectability of Write Conflicts by the Assembler 3Ć20. . . . . . . . . . . . . . . . . .

4–1 Single-Precision Floating-Point Fields 4Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Double-Precision Floating-Point Fields 4Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Fixed-Point Pipeline Stages 5Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Fetch Phases of the Pipeline 5Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Decode Phases of the Pipeline 5Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Execute Phases of the Pipeline and Functional Block Diagram

5–5 Fixed-Point Pipeline Phases 5Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Pipeline Operation: One Execute Packet per Fetch Packet 5Ć6. . . . . . . . . . . . . . . . . . . . . . . . .

5–7 Functional Block Diagram of TMS320C62x Based on Pipeline Phases 5Ć8. . . . . . . . . . . . . . .

5–8 Single-Cycle Instruction Phases 5Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 Single-Cycle Execution Block Diagram 5Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Multiply Instruction Phases 5Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 Multiply Execution Block Diagram 5Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 Store Instruction Phases 5Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–13 Store Execution Block Diagram 5Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–14 Load Instruction Phases 5Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–15 Load Execution Block Diagram 5Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–16 Branch Instruction Phases 5Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–17 Branch Execution Block Diagram 5Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–18 Pipeline Operation: Fetch Packets With Different Numbers of Execute Packets 5Ć19. . . . . . .

5–19 Multicycle NOP in an Execute Packet 5Ć20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–20 Branching and Multicycle NOPs 5Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

of the TMS320C62x 5Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xiii

Page 14

Figures

5–21 Pipeline Phases Used During Memory Accesses 5Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–22 Program and Data Memory Stalls 5Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–23 4-Bank Interleaved Memory 5Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–24 4-Bank Interleaved Memory With Two Memory Spaces 5Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Floating-Point Pipeline Stages 6Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Fetch Phases of the Pipeline 6Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 Decode Phases of the Pipeline 6Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Execute Phases of the Pipeline and Functional Block Diagram

of the TMS320C67x 6Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 Floating-Point Pipeline Phases 6Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 Pipeline Operation: One Execute Packet per Fetch Packet 6Ć6. . . . . . . . . . . . . . . . . . . . . . . . .

6–7 Functional Block Diagram of TMS320C67x Based on Pipeline Phases 6Ć10. . . . . . . . . . . . . .

6–8 Single-Cycle Instruction Phases 6Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–9 Single-Cycle Execution Block Diagram 6Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–10 Multiply Instruction Phases 6Ć39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–11 Multiply Execution Block Diagram 6Ć39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–12 Store Instruction Phases 6Ć40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–13 Store Execution Block Diagram 6Ć41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–14 Load Instruction Phases 6Ć42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–15 Load Execution Block Diagram 6Ć43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–16 Branch Instruction Phases 6Ć44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–17 Branch Execution Block Diagram 6Ć45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–18 2-Cycle DP Instruction Phases 6Ć46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–19 4-Cycle Instruction Phases 6Ć47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–20 INTDP Instruction Phases 6Ć48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–21 DP Compare Instruction Phases 6Ć48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–22 ADDDP/SUBDP Instruction Phases 6Ć49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–23 MPYI Instruction Phases 6Ć50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–24 MPYID Instruction Phases 6Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–25 MPYDP Instruction Phases 6Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–26 Pipeline Operation: Fetch Packets With Different Numbers of Execute Packets 6Ć53. . . . . . .

6–27 Multicycle NOP in an Execute Packet 6Ć54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–28 Branching and Multicycle NOPs 6Ć55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–29 Pipeline Phases Used During Memory Accesses 6Ć56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–30 Program and Data Memory Stalls 6Ć57. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–31 8-Bank Interleaved Memory 6Ć58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–32 8-Bank Interleaved Memory With Two Memory Spaces 6Ć59. . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 Interrupt Service Table 7Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 Interrupt Service Fetch Packet 7Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 IST With Branch to Additional Interrupt Service Code Located Outside the IST 7Ć7. . . . . . . .

7–4 Interrupt Service Table Pointer (ISTP) 7Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 Control Status Register (CSR) 7Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–6 Interrupt Enable Register (IER) 7Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–7 Interrupt Flag Register (IFR) 7Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiv

Page 15

7–8 Interrupt Set Register (ISR) 7Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–9 Interrupt Clear Register (ICR) 7Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–10 NMI Return Pointer (NRP) 7Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–11 Interrupt Return Pointer (IRP) 7Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–12 TMS320C62x Nonreset Interrupt Detection and Processing: Pipeline Operation 7Ć19. . . . . .

7–13 TMS320C67x Nonreset Interrupt Detection and Processing: Pipeline Operation 7Ć20. . . . . .

7–14 RESET Interrupt Detection and Processing: Pipeline Operation 7Ć22. . . . . . . . . . . . . . . . . . . .

Figures

Contents

xv

Page 16

Tables

Tables

1–1 Typical Applications for the TMS320 DSPs 1Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 40-Bit/64-Bit Register Pairs 2Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Functional Units and Operations Performed 2Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Control Registers 2Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Addressing Mode Register (AMR) Mode Select Field Encoding 2Ć9. . . . . . . . . . . . . . . . . . . . .

2–5 Block Size Calculations 2Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Control Status Register Field Descriptions 2Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–7 Control Register File Extensions 2Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Floating-Point Adder Configuration Register Field Descriptions 2Ć15. . . . . . . . . . . . . . . . . . . . .

2–9 Floating-Point Auxiliary Configuration Register Field Descriptions 2Ć17. . . . . . . . . . . . . . . . . .

2–10 Floating-Point Multiplier Configuration Register Field Descriptions 2Ć19. . . . . . . . . . . . . . . . . .

3–1 Fixed-Point Instruction Operation and Execution Notations 3Ć2. . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Instruction to Functional Unit Mapping 3Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Functional Unit to Instruction Mapping 3Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 TMS320C62x/C67x Opcode Map Symbol Definitions 3Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Delay Slot and Functional Unit Latency Summary 3Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 Registers That Can Be Tested by Conditional Operations 3Ć16. . . . . . . . . . . . . . . . . . . . . . . . .

3–7 Indirect Address Generation for Load/Store 3Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 Relationships Between Operands, Operand Size, Signed/Unsigned, Functional

3–9 Program Counter Values for Example Branch Using a Displacement 3Ć41. . . . . . . . . . . . . . . .

3–10 Program Counter Values for Example Branch Using a Register 3Ć43. . . . . . . . . . . . . . . . . . . .

3–11 Program Counter Values for B IRP 3Ć45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 Program Counter Values for B NRP 3Ć47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 Data Types Supported by Loads 3Ć67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 Address Generator Options 3Ć67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–15 Data Types Supported by Loads 3Ć72. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–16 Register Addresses for Accessing the Control Registers 3Ć87. . . . . . . . . . . . . . . . . . . . . . . . . .

3–17 Data Types Supported by Stores 3Ć123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–18 Address Generator Options 3Ć123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–19 Data Types Supported by Stores 3Ć127. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Floating-Point Instruction Operation and Execution Notations 4Ć2. . . . . . . . . . . . . . . . . . . . . . .

4–2 Instruction to Functional Unit Mapping 4Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Functional Unit to Instruction Mapping 4Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 IEEE Floating-Point Notations 4Ć7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Special Single-Precision Values 4Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Units, and Opfields for Example Instruction (ADD) 3Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xvi

Page 17

Tables

4–6 Hex and Decimal Representation for Selected Single-Precision Values 4Ć9. . . . . . . . . . . . . . .

4–7 Special Double-Precision Values 4Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Hex and Decimal Representation for Selected Double-Precision Values 4Ć10. . . . . . . . . . . . .

4–9 Delay Slot and Functional Unit Latency Summary 4Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–10 Address Generator Options 4Ć52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Operations Occurring During Fixed-Point Pipeline Phases 5Ć7. . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Execution Stage Length Description for Each Instruction Type 5Ć11. . . . . . . . . . . . . . . . . . . . .

5–3 Program Memory Accesses Versus Data Load Accesses 5Ć22. . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Loads in Pipeline From Example 5–2 5Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Operations Occurring During Floating-Point Pipeline Phases 6Ć7. . . . . . . . . . . . . . . . . . . . . . .

6–2 Execution Stage Length Description for Each Instruction Type 6Ć13. . . . . . . . . . . . . . . . . . . . .

6–3 Single-Cycle .S-Unit Instruction Hazards 6Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 DP Compare .S-Unit Instruction Hazards 6Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 2-Cycle DP .S-Unit Instruction Hazards 6Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 Branch .S-Unit Instruction Hazards 6Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–7 16 × 16 Multiply .M-Unit Instruction Hazards 6Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–8 4-Cycle .M-Unit Instruction Hazards 6Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–9 MPYI .M-Unit Instruction Hazards 6Ć27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–10 MPYID .M-Unit Instruction Hazards 6Ć28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–11 MPYDP .M-Unit Instruction Hazards 6Ć29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–12 Single-Cycle .L-Unit Instruction Hazards 6Ć30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–13 4-Cycle .L-Unit Instruction Hazards 6Ć31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–14 INTDP .L-Unit Instruction Hazards 6Ć32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–15 ADDDP/SUBDP .L-Unit Instruction Hazards 6Ć33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–16 Load .D-Unit Instruction Hazards 6Ć34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–17 Store .D-Unit Instruction Hazards 6Ć35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–18 Single-Cycle .D-Unit Instruction Hazards 6Ć36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–19 LDDW Instruction With Long Write Instruction Hazards 6Ć37. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–20 Single-Cycle Execution 6Ć38. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–21 16 × 16-Bit Multiply Execution 6Ć39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–22 Store Execution 6Ć40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–23 Load Execution 6Ć42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–24 Branch Execution 6Ć44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–25 2-Cycle DP Execution 6Ć46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–26 4-Cycle Execution 6Ć47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–27 INTDP Execution 6Ć48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–28 DP Compare Execution 6Ć48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–29 ADDDP/SUBDP Execution 6Ć49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–30 MPYI Execution 6Ć50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–31 MPYID Execution 6Ć50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–32 MPYDP Execution 6Ć51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–33 Program Memory Accesses Versus Data Load Accesses 6Ć56. . . . . . . . . . . . . . . . . . . . . . . . . .

6–34 Loads in Pipeline From Example 6–2 6Ć59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xvii

Page 18

Tables

7–1 Interrupt Priorities 7Ć3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 Interrupt Service Table Pointer (ISTP) Field Descriptions 7Ć8. . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 Interrupt Control Registers 7Ć10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Control Status Register (CSR) Interrupt Control Field Descriptions 7Ć11. . . . . . . . . . . . . . . . .

xviii

Page 19

Examples

Examples

3–1 Fully Serial p-Bit Pattern in a Fetch Packet 3Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Fully Parallel p-Bit Pattern in a Fetch Packet 3Ć14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Partially Serial p-Bit Pattern in a Fetch Packet 3Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 LDW in Circular Mode 3Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 ADDAH in Circular Mode 3Ć22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Execute Packet in Figure 5–7 5Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Load From Memory Banks 5Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Execute Packet in Figure 6–7 6Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Load From Memory Banks 6Ć58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 Relocation of Interrupt Service Table 7Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 Code Sequence to Disable Maskable Interrupts Globally 7Ć12. . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 Code Sequence to Enable Maskable Interrupts Globally 7Ć12. . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Code Sequence to Enable an Individual Interrupt (INT9) 7Ć14. . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 Code Sequence to Disable an Individual Interrupt (INT9) 7Ć14. . . . . . . . . . . . . . . . . . . . . . . . . .

7–6 Code to Set an Individual Interrupt (INT6) and Read the Flag Register 7Ć15. . . . . . . . . . . . . .

7–7 Code to Clear an Individual Interrupt (INT6) and Read the Flag Register 7Ć15. . . . . . . . . . . .

7–8 Code to Return From NMI 7Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–9 Code to Return from a Maskable Interrupt 7Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–10 Code Without Single Assignment: Multiple Assignment of A1 7Ć25. . . . . . . . . . . . . . . . . . . . . .

7–11 Code Using Single Assignment 7Ć25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–12 Manual Interrupt Processing 7Ć26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–13 Code Sequence to Invoke a Trap 7Ć27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–14 Code Sequence for Trap Return 7Ć27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xix

Page 20

Chapter 1

a

Introduction

The TMS320C6x generation of digital signal processors is part of the TMS320

family of digital signal processors (DSPs). The TMS320C62x devices are

fixed-point DSPs in the TMS320C6x generation, and the TMS320C67x

devices are floating-point DSPs in the TMS320C6x generation. The

TMS320C62x and TMS320C67x are code compatible and both use the

VelociTI architecture, a high-performance, advanced VLIW (very long

instruction word) architecture, making these DSPs excellent choices for multichannel and multifunction applications.

The VelociTI architecture of the ’C62x and ’C67x make them the first of f-theshelf DSPs to use advanced VLIW to achieve high performance through

increased instruction-level parallelism. A traditional VLIW architecture

consists of multiple execution units running in parallel, performing multiple

instructions during a single clock cycle. Parallelism is the key to extremely high

performance, taking these DSPs well beyond the performance capabilities of

traditional superscalar designs. VelociTI is a highly deterministic architecture,

having few restrictions on how or when instructions are fetched, executed, or

stored. It is this architectural flexibility that is key to the breakthrough efficiency

levels of the ’C6x compiler. VelociTI’s advanced features include:

- Instruction packing: reduced code size

- All instructions can operate conditionally: flexibility of code

- Variable-width instructions: flexibility of data types

- Fully pipelined branches: zero-overhead branching

Topic Page

1.1 TMS320 Family Overview 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Overview of the TMS320C6x Generation of

Digital Signal Processors 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Features and Options of the TMS320C62x/C67x 1-5. . . . . . . . . . . . . . . . .

1.4 TMS320C62x/C67x Architecture 1-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-1

Page 21

TMS320 Family Overview

1.1 TMS320 Family Overview

The TMS320 family consists of fixed-point, floating-point, and multiprocessor

digital signal processors (DSPs). TMS320 DSPs have an architecture designed specifically for real-time signal processing.

1.1.1 History of TMS320 DSPs

In 1982, Texas Instruments introduced the TMS32010—the first fixed-point

DSP in the TMS320 family. Before the end of the year,

magazine awarded the TMS32010 the title “Product of the Year”. Today, the

TMS320 family consists of many generations: ’C1x, ’C2x, ’C2xx, ’C5x, and

’C54x fixed-point DSPs; ’C3x and ’C4x floating-point DSPs, and ’C8x multiprocessor DSPs. Now there is a new generation of DSPs, the TMS320C6x generation, with performance and features that are reflective of T exas Instruments

commitment to lead the world in DSP solutions.

1.1.2 Typical Applications for the TMS320 Family

T able 1–1 lists some typical applications for the TMS320 family of DSPs. The

TMS320 DSPs offer adaptable approaches to traditional signal-processing

problems. They also support complex applications that often require multiple

operations to be performed simultaneously.

Electronic Products

1-2

Page 22

Table 1–1. Typical Applications for the TMS320 DSPs

Automotive Consumer Control

TMS320 Family Overview

Adaptive ride control

Antiskid brakes

Cellular telephones

Digital radios

Engine control

Global positioning

Navigation

Vibration analysis

Voice commands

General Purpose Graphics/Imaging Industrial

Adaptive filtering

Convolution

Correlation

Digital filtering

Fast Fourier transforms

Hilbert transforms

Waveform generation

Windowing

Instrumentation Medical Military

Digital filtering

Function generation

Pattern matching

Phase-locked loops

Seismic processing

Spectrum analysis

Transient analysis

Digital radios/TVs

Educational toys

Music synthesizers

Pagers

Power tools

Radar detectors

Solid-state answering machines

3-D transformations

Animation/digital maps

Homomorphic processing

Image compression/transmission

Image enhancement

Pattern recognition

Robot vision

Workstations

Diagnostic equipment

Fetal monitoring

Hearing aids

Patient monitoring

Prosthetics

Ultrasound equipment

Disk drive control

Engine control

Laser printer control

Motor control

Robotics control

Servo control

Numeric control

Power-line monitoring

Robotics

Security access

Image processing

Missile guidance

Navigation

Radar processing

Radio frequency modems

Secure communications

Sonar processing

Telecommunications Voice/Speech

1200- to 56Ă600-bps modems

Adaptive equalizers

ADPCM transcoders

Base stations

Cellular telephones

Channel multiplexing

Data encryption

Digital PBXs

Digital speech interpolation (DSI)

DTMF encoding/decoding

Echo cancellation

Faxing

Future terminals

Line repeaters

Personal communications

systems (PCS)

Personal digital assistants (PDA)

Speaker phones

Spread spectrum communications

Digital subscriber loop (xDSL)

Video conferencing

X.25 packet switching

Speaker verification

Speech enhancement

Speech recognition

Speech synthesis

Speech vocoding

Text-to-speech

Voice mail

Introduction

1-3

Page 23

Overview of the TMS320C6x Generation of Digital Signal Processors

1.2 Overview of the TMS320C6x Generation of Digital Signal Processors

With a performance of up to 1600 million instructions per second (MIPS) and

an efficient C compiler , the TMS320C6x DSPs give system architects unlimited possibilities to differentiate their products. High performance, ease of use,

and affordable pricing make the TMS320C6x generation the ideal solution for

multichannel, multifunction applications, such as:

- Pooled modems

- Wireless local loop base stations

- Beam-forming base stations

- Remote access servers (RAS)

- Digital subscriber loop (DSL) systems

- Cable modems

- Multichannel telephony systems

- Virtual reality 3-D graphics

- Speech recognition

- Audio

- Radar

- Atmospheric modeling

- Finite element analysis

- Imaging (examples: fingerprint recognition, ultrasound, and MRI)

The TMS320C6x generation is also an ideal solution for exciting new applications; for example:

- Personalized home security with face and hand/fingerprint recognition

- Advanced cruise control with global positioning systems (GPS) navigation

and accident avoidance

- Remote medical diagnostics

1-4

Page 24

Features and Options of the TMS320C62x/C67x

1.3 Features and Options of the TMS320C62x/C67x

The ’C62x devices operate at 200 MHz (5-ns cycle time). The ’C67x devices

operate at 167 MHz (6-ns cycle time). Both DSPs execute up to eight 32-bit

instructions every cycle. The device’s core CPU consists of 32 generalpurpose registers of 32-bit word length and eight functional units:

- Two multipliers

- Six ALUs

The ’C62x/C67x have a complete set of optimized development tools, including an efficient C compiler, an assembly optimizer for simplified assemblylanguage programming and scheduling, and a Windows based debugger

interface for visibility into source code execution characteristics. A hardware

emulation board, compatible with the TI XDS510 emulator interface, is also

available. This tool complies with IEEE Standard 1149.1–1990, IEEE Standard Test Access Port and Boundary-Scan Architecture.

Features of the ’C62x/C67x include:

- Advanced VLIW CPU with eight functional units, including two multipliers

and six arithmetic units

J Executes up to eight instructions per cycle for up to ten times the

performance of typical DSPs

J Allows designers to develop highly effective RISC-like code for fast

development time

- Instruction packing

J Gives code size equivalence for eight instructions executed serially or

in parallel

J Reduces code size, program fetches, and power consumption.

- All instructions execute conditionally .

J Reduces costly branching

J Increases parallelism for higher sustained performance

- Code executes as programmed on independent functional units.

J Industry’s most efficient C compiler on DSP benchmark suite

J Industry’s first assembly optimizer for fast development and improved

parallelization

- 8/16/32-bit data support, providing efficient memory support for a variety

of applications

- 40-bit arithmetic options add extra precision for vocoders and other com-

putationally intensive applications

Introduction

1-5

Page 25

Features and Options of the TMS320C62x/C67x

- Saturation and normalization provide support for key arithmetic opera-

tions.

- Field manipulation and instruction extract, set, clear, and bit counting

support common operation found in control and data manipulation

applications.

The ’C67x has these additional features:

- Peak 1336 MIPS at 167 MHz

- Peak 1G FLOPS at 167 MHz for single-precision operations

- Peak 250M FLOPS at 167 MHz for double-precision operations

- Peak 688M FLOPS at 167 MHz for multiply and accumulate operations

- Hardware support for single-precision (32-bit) and double-precision

(64-bit) IEEE floating-point operations

- 32 32-bit integer multiply with 32- or 64-bit result

A variety of memory and peripheral options are available for the ’C62x/C67x:

- Large on-chip RAM for fast algorithm execution

- 32-bit external memory interface supports SDRAM, SBSRAM, SRAM,

and other asynchronous memories for a broad range of external memory

requirements and maximum system performance

- 16-bit host port for access to ’C62x/C67x memory and peripherals

- Multichannel DMA controller

- Multichannel serial port(s)

- 32-bit timer(s)

1-6

Page 26

1.4 TMS320C62x/C67x Architecture

Á

Á

Á

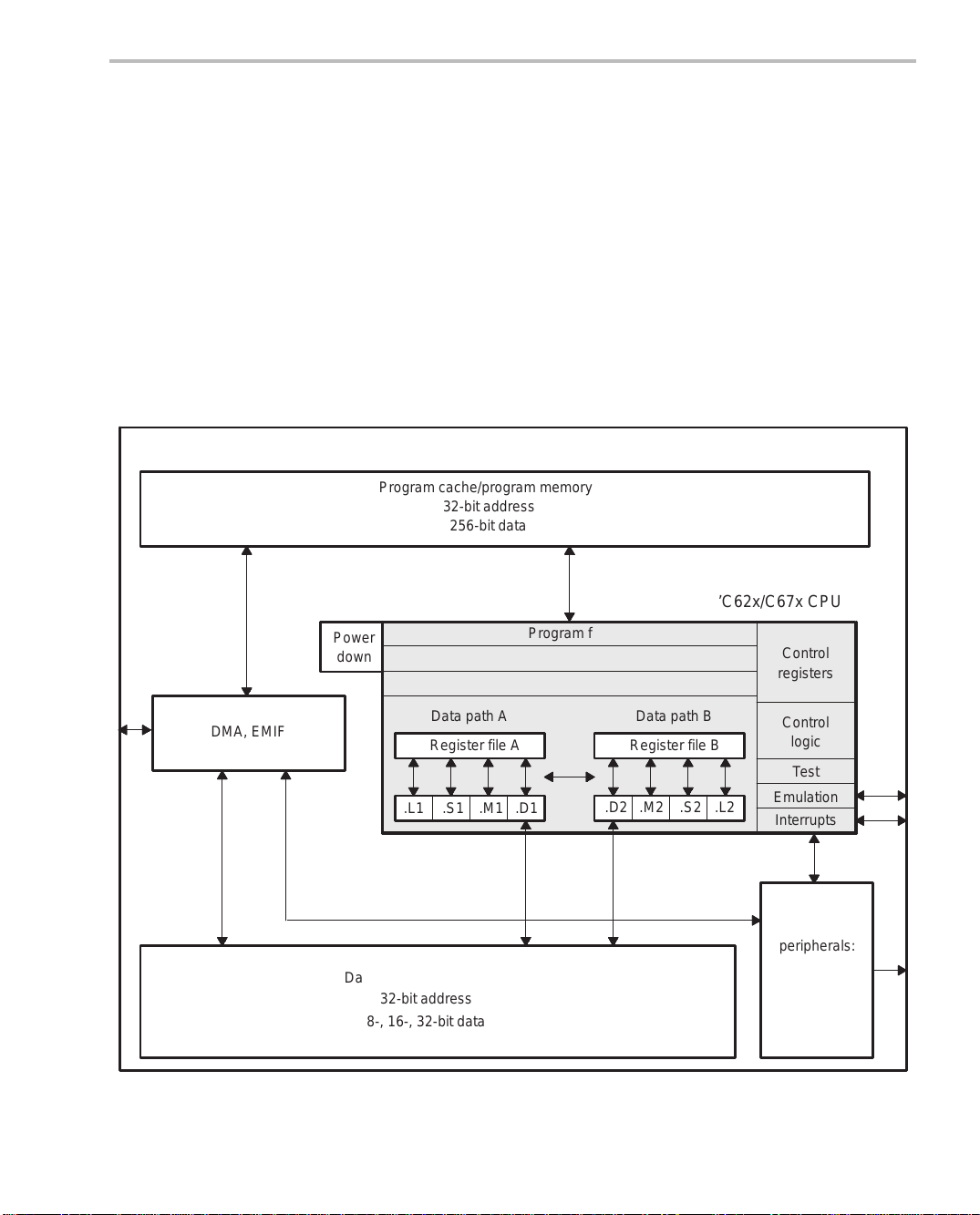

Figure 1–1 is the block diagram for the TMS320C62x/C67x DSPs. The

’C62x/C67x devices come with program memory, which, on some devices,

can be used as a program cache. The devices also have varying sizes of data

memory. Peripherals such as a direct memory access (DMA) controller,

power-down logic, and external memory interface (EMIF) usually come with

the CPU, while peripherals such as serial ports and host ports are on only

certain devices. Check the data sheet for your device to determine the specific

peripheral configurations you have.

Figure 1–1. TMS320C62x/C67x Block Diagram

’C62x/’C67x device

Program cache/program memory

32-bit address

256-bit data

TMS320C62x/C67x Architecture

DMA, EMIF

Power

down

Data path A Data path B

Data cache/data memory

32-bit address

8-, 16-, 32-bit data

Program fetch

Instruction dispatch

Instruction decode

.D1.M1.S1.L1

.D2 .M2 .S2 .L2

’C62x/C67x CPU

Control

registers

Control

Register file BRegister file A

logic

Test

Emulation

Interrupts

Additional

peripherals:

Timers,

serial ports,

etc.

Introduction

1-7

Page 27

TMS320C62x/C67x Architecture

1.4.1 Central Processing Unit (CPU)

The ’C62x/C67x CPU, shaded in Figure 1–1, is common to all the ’C62x/C67x

devices. The CPU contains:

- Program fetch unit

- Instruction dispatch unit

- Instruction decode unit

- Two data paths, each with four functional units

- 32 32-bit registers

- Control registers

- Control logic

- Test, emulation, and interrupt logic

The program fetch, instruction dispatch, and instruction decode units can

deliver up to eight 32-bit instructions to the functional units every CPU clock

cycle. The processing of instructions occurs in each of the two data paths (A

and B), each of which contains four functional units (.L, .S, .M, and .D) and 16

32-bit general-purpose registers. The data paths are described in more detail

in Chapter 2,

means to configure and control various processor operations. To understand

how instructions are fetched, dispatched, decoded, and executed in the data

path, see Chapter 5,

Pipeline

CPU Data Paths and Control

.

. A control register file provides the

TMS320C62x Pipeline

, and Chapter 6,

TMS320C67x

1.4.2 Internal Memory

The ’C62x/C67x have a 32-bit, byte-addressable address space. Internal (onchip) memory is organized in separate data and program spaces. When offchip memory is used, these spaces are unified on most devices to a single

memory space via the external memory interface (EMIF).

The ’C62x/C67x have two 32-bit internal ports to access internal data memory .

The ’C62x/C67x have a single internal port to access internal program

memory, with an instruction-fetch width of 256 bits.

1-8

Page 28

1.4.3 Peripherals

TMS320C62x/C67x Architecture

The following peripheral modules can complement the CPU on the

’C62x/C67x DSPs. Some devices have a subset of these peripherals but may

not have all of them.

- Serial ports

- Timers

- External memory interface (EMIF) that supports synchronous and

asynchronous SRAM and synchronous DRAM

- DMA controller

- Host-port interface

- Power-down logic that can halt CPU activity, peripheral activity, and

phased-locked loop (PLL) activity to reduce power consumption

Introduction

1-9

Page 29

Chapter 2

CPU Data Paths and Control

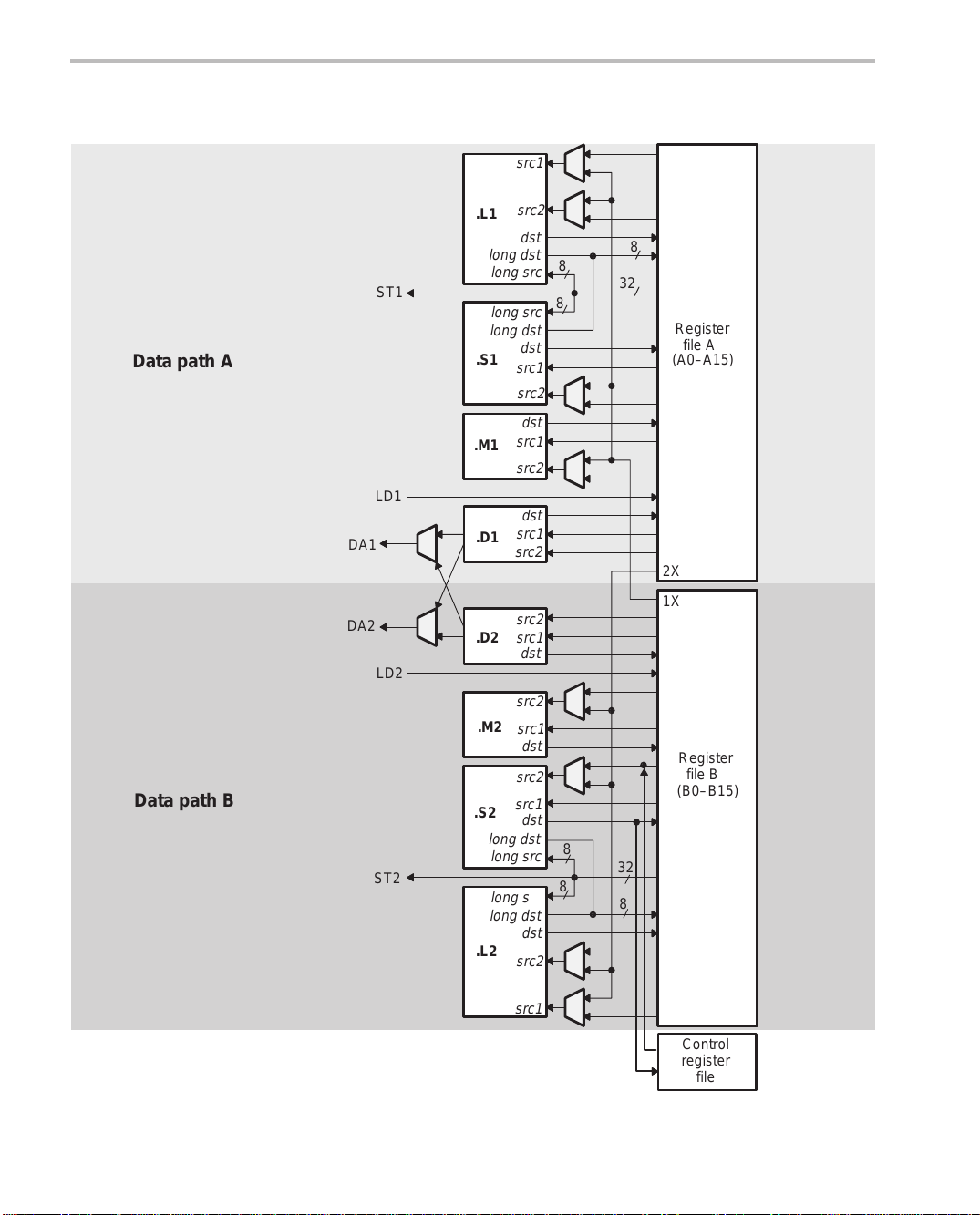

This chapter focuses on the CPU, providing information about the data paths

and control registers. The two register files and the data crosspaths are

described.

Figure 2–1 and Figure 2–2 show the components of the data paths the ’C62x

and C67x, repectively. These components consist of:

- Two general-purpose register files (A and B)

- Eight functional units (.L1, .L2, .S1, .S2, .M1, .M2, .D1, and .D2)

- Two load-from-memory paths (LD1 and LD2)

- Two store-to-memory paths (ST1 and ST2)

- Two register file cross paths (1X and 2X)

Topic Page

2.1 General-Purpose Register Files 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Functional Units 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Register File Cross Paths 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Memory, Load, and Store Paths 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Data Address Paths 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 TMS320C62x/C67x Control Register File 2-8. . . . . . . . . . . . . . . . . . . . . . . .

2.7 TMS320C67x Extensions to the Control Register File 2-13. . . . . . . . . . .

2-1 August 1996

Page 30

CPU Data Paths and Control

Figure 2–1. TMS320C62x CPU Data Paths

ST1

Data path A

LD1

DA1

DA2

LD2

Data path B

ST2

.L1

long dst

long src

long src

long dst

.S1

.M1

.D1

.D2

.M2

.S2

long dst

long src

long src

long dst

.L2

src1

src2

dst

dst

src1

src2

dst

src1

src2

dst

src1

src2

src2

src1

dst

src2

src1

dst

src2

src1

dst

dst

src2

8

8

32

8

Register

file A

(A0–A15)

2X

1X

Register

file B

(B0–B15)

8

32

8

8

2-2

src1

Control

register

file

Page 31

Figure 2–2. TMS320C67x CPU Data Paths

Á

Á

Á

LD1 32 MSB

ST1

Data path A

LD1 32 LSB

DA1

.L1

long dst

long src

long src

long dst

.S1

.M1

.D1

src1

src2

dst

dst

src1

src2

dst

src1

src2

dst

src1

src2

CPU Data Paths and Control

8

8

8

32

32

8

Register

file A

(A0–A15)

2X

Data path B

DA2

LD2 32 LSB

LD2 32 MSB

ST2

.D2

.M2

.S2

long dst

long src

long src

long dst

.L2

src2

src1

dst

src2

src1

dst

src2

src1

dst

dst

src2

src1

1X

Register

file B

(B0–B15)

8

8

32

8

32

8

Control

register

file

CPU Data Paths and Control

2-3

Page 32

General-Purpose Register Files

2.1 General-Purpose Register Files

There are two general-purpose register files (A and B) in the ’C62x/C67x data

paths. Each of these files contains 16 32-bit registers (A0–A15 for file A and

B0–B15 for file B). The general-purpose registers can be used for data, data

address pointers, or condition registers.

The general-purpose register files support 32- and 40-bit fixed-point data. The

32-bit data can be contained in any general-purpose register. The ’C67x also

supports 32-bit single-precision and 64-bit double-precision data. The 40-bit

data is contained across two registers; the 32 LSBs of the data are placed in

an even register and the remaining eight MSBs are placed in the eight LSBs

of the next upper register (which is always an odd register). There are 16 valid

register pairs for 40-bit data, as shown in Table 2–1. In assembly language

syntax, the register pairs are denoted by a colon between the register names

and the odd register is specified first. The ’C67x also uses these register pairs

to hold 64-bit double-precision floating-point values. See Chapter 4 for more

information on double-precision floating-point values.

Table 2–1. 40-Bit/64-Bit Register Pairs

Register Files

A B

A1:A0 B1:B0

A3:A2 B3:B2

A5:A4 B5:B4

A7:A6 B7:B6

A9:A8 B9:B8

A11:A10 B11:B10

A13:A12 B13:B12

A15:A14

B15:B14

2-4

Page 33

Figure 2–3 illustrates the register storage scheme for 40-bit long data. Operations requiring a long input ignore the 24 MSBs of the odd register. Operations

producing a long result zero-fill the 24 MSBs of the odd register. The even

register is encoded in the opcode.

Figure 2–3. Storage Scheme for 40-Bit Data in a Register Pair

31 0 31 0

Odd register Even register

Ignored

Odd register Even register

Zero-filled

78

Read from registers

39 32 31 0

Write to registers

39 32 31 0

General-Purpose Register Files

40-bit data

40-bit data

CPU Data Paths and Control

2-5

Page 34

Functional Units

2.2 Functional Units

The eight functional units in the ’C62x/C67x data paths can be divided into two

groups of four; each functional unit in one data path is almost identical to the

corresponding unit in the other data path. The functional units are described

in Table 2–2.

Table 2–2. Functional Units and Operations Performed

Functional Unit Fixed-Point Operations Floating-Point Operations

.L unit (.L1,.L2) 32/40-bit arithmetic and compare operations

Leftmost 1 or 0 bit counting for 32 bits

Normalization count for 32 and 40 bits

32-bit logical operations

.S unit (.S1, .S2) 32-bit arithmetic operations

32/40-bit shifts and 32-bit bit-field operations

32-bit logical operations

Branches

Constant generation

Register transfers to/from the control register file

(.S2 only)

.M unit (.M1, .M2) 16 16 bit multiply operations 32 32 bit fixed-point multiply

.D unit (.D1, .D2)

Note: Fixed-point operations are available on both the ’C62x and the ’C67x. Floating-point operations and 32-bit fixed-point

multiply are available only on the ’C67x.

32-bit add, subtract, linear and circular address

calculation

Loads and stores with a 5-bit constant offset

Loads and stores with 15-bit constant offset

(.D2 only)

Arithmetic operations

DP → SP, INT → DP, INT → SP

conversion operations

Compare

Reciprocal and reciprocal squareroot operations

Absolute value operations

SP → DP conversion operations

operations

Floating-point multiply operations