Page 1

TMS320C2xx

User’s Guide

Manufacturing Part Number: D412008-9761 revision A

Literature Number: SPRU127B

January 1997

Printed on Recycled Paper

Page 2

IMPORTANT NOTICE

T exas Instruments (TI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to obtain the latest

version of relevant information to verify , before placing orders, that the information being relied

on is current.

TI warrants performance of its semiconductor products and related software to the specifications

applicable at the time of sale in accordance with TI’s standard warranty . T esting and other quality

control techniques are utilized to the extent TI deems necessary to support this warranty.

Specific testing of all parameters of each device is not necessarily performed, except those

mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death,

personal injury , or severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES

OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer.

Use of TI products in such applications requires the written approval of an appropriate TI officer .

Questions concerning potential risk applications should be directed to TI through a local SC

sales office.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards should be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein. Nor does TI warrant or

represent that any license, either express or implied, is granted under any patent right, copyright,

mask work right, or other intellectual property right of TI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

Copyright 1996, Texas Instruments Incorporated

Page 3

About This Manual

How to Use This Manual

Preface

Read This First

This user’s guide describes the architecture, hardware, assembly language

instructions, and general operation of the TMS320C2xx digital signal

processors (DSPs). This manual can also be used as a reference guide for

developing hardware and/or software applications. In this document, ’C2xx

refers to any of the TMS320C2xx devices, except where device-specific

information is explicitly stated. When device-specific information is given, the

device name may be abbreviated; for example, TMS320C203 will be

abbreviated as ’C203.

How to Use This Manual

Chapter 1,

introduces the key features of the TMS320C2xx generation of that family.

Chapter 2,

providing information about the CPU, bus structure, memory, on-chip

peripherals, and scanning logic.

If you are reading this manual to learn about the ’C209, Chapter 1 1 is important

for you. There are some notable differences between the ’C209 and other

’C2xx devices, and Chapter 1 1 explains these differences. In addition, it shows

how to use this manual to get a complete picture of the ’C209.

The following table points you to major topics.

Introduction

Architectural Overview

, summarizes the TMS320 family of products and then

, summarizes the ’C2xx architecture,

iii

Page 4

How to Use This Manual

For this information: Look here:

Addressing modes (for addressing data

memory)

Assembly language instructions Chapter 7,

Chapter 6,

Instructions

Assembly language instructions of

TMS320C1x, ’C2x, ’C2xx, and ’C5x

compared

Boot loader Chapter 4,

Clock generator Chapter 8,

CPU Chapter 3,

Custom ROM from TI Appendix D,

Appendix B,

TMS320C1x/C2x/C2xx/C5x

Instruction Set Comparison

to TI

Emulator Appendix E,

Using XDS510 Emulator

Features Chapter 1,

Chapter 2,

Input/output ports Chapter 4,

Interrupts Chapter 5,

Memory configuration Chapter 4,

Memory interfacing Chapter 4,

On-chip peripherals Chapter 8,

Pipeline Chapter 5,

Program control Chapter 5,

Program examples Appendix C,

Program-memory address generation Chapter 5,

Registers summarized Appendix A,

Serial ports Chapter 9,

Chapter 10,

Stack Chapter 5,

Status registers Chapter 5,

Timer Chapter 8,

TMS320C209 differences and

similarities

Wait-state generator Chapter 8,

Chapter 1 1,

Addressing Modes

Assembly Language

Memory and I/O Spaces

On-Chip Peripherals

Central Processing Unit

Submitting ROM Codes

Design Considerations for

Introduction

Architectural Overview

Memory and I/O Spaces

Program Control

Memory and I/O Spaces

Memory and I/O Spaces

On-Chip Peripherals

Program Control

Program Control

Program Examples

Program Control

Register Summary

Synchronous Serial Port

Asynchronous Serial Port

Program Control

Program Control

On-Chip Peripherals

TMS320C209

On-Chip Peripherals

iv

Page 5

Notational Conventions

This document uses the following conventions:

-

-

Notational Conventions/Information About Cautions

Program listings and program examples are shown in a special

typeface.

Here is a segment of a program listing:

OUTPUT LDP #6 ;select data page 6

BLDD #300, 20h ;move data at address 300h to 320h

RET

In syntax descriptions, bold portions of a syntax should be entered as

shown;

italic

portions of a syntax identify information that you specify . Here

is an example of an instruction syntax:

BLDD

BLDD is the instruction mnemonic, which must be typed as shown. You

specify the two parameters,

-

Square brackets ( [ and ] ) identify an optional parameter. If you use an

optional parameter, you specify the information within the brackets; you

do not type the brackets themselves. Y ou separate each optional operand

from required operands with a comma and a space. Here is a sample

syntax:

BLDD

BLDD is the instruction. The two required operands are

destination

you choose to use AR

a chosen value for

BLDD *, #310h, AR3

Information About Cautions

This book contains cautions.

This is an example of a caution statement.

A caution statement describes a situation that could potentially

damage your software or equipment.

source, destination

source

and

source, destination

destination

[, ARn]

.

source

, and the optional operand is ARn. AR is bold and n is italic; if

n

, you must type the letters A and R and then supply

n

(in this case, a value from 0 to 7). Here is an example:

and

The information in a caution is provided for your protection. Please read each

caution carefully.

Read This First

v

Page 6

Related Documentation From Texas Instruments

Related Documentation From Texas Instruments

This subsection describes related TI documents that can be ordered by

calling the T exas Instruments Literature Response Center at (800) 477–8924.

When ordering, please identify the document by its title and literature number.

The following data sheets contain the electrical and timing specifications for

the TMS320C2xx devices, as well as signal descriptions and pinouts for all of

the available packages:

-

TMS320C2xx data sheet (literature number SPRS025)

-

TMS320F2xx data sheet (literature number SPRS050). This data sheet

covers the TMS320C2xx devices that have on-chip flash memory.

The books listed below provide additional information about using the

TMS320C2xx devices and related support tools, as well as more general

information about using the TMS320 family of DSPs.

TMS320C1x/C2x/C2xx/C5x Code Generation Tools Getting Started

Guide

TMS320C1x, TMS320C2x, TMS320C2xx, and TMS320C5x assembly

language tools and the C compiler for the ’C1x, ’C2x, ’C2xx, and ’C5x

devices. The installation for MS-DOS, OS/2, SunOS, and Solaris

systems is covered.

TMS320C1x/C2x/C2xx/C5x Assembly Language Tools User’s Guide

(literature number SPRU018) describes the assembly language tools

(assembler, linker, and other tools used to develop assembly language

code), assembler directives, macros, common object file format, and

symbolic debugging directives for the ’C1x, ’C2x, ’C2xx, and ’C5x

generations of devices.

TMS320C2x/C2xx/C5x Optimizing C Compiler User’s Guide

number SPRU024) describes the ’C2x/C2xx/C5x C compiler. This C

compiler accepts ANSI standard C source code and produces TMS320

assembly language source code for the ’C2x, ’C2xx, and ’C5x

generations of devices.

(literature number SPRU121) describes how to install the

(literature

TMS320C2xx C Source Debugger User’s Guide

(literature number

SPRU151) tells you how to invoke the ’C2xx emulator and simulator

versions of the C source debugger interface. This book discusses

various aspects of the debugger interface, including window

management, command entry , code execution, data management, and

breakpoints. It also includes a tutorial that introduces basic debugger

functionality.

vi

Page 7

Related Documentation From Texas Instruments

TMS320C2xx Simulator Getting Started

(literature number SPRU137)

describes how to install the TMS320C2xx simulator and the C source

debugger for the ’C2xx. The installation for MS-DOS, PC-DOS,

SunOS, Solaris, and HP-UX systems is covered.

TMS320C2xx Emulator Getting Started Guide

(literature number

SPRU209) tells you how to install the Windows 3.1 and Windows 95

versions of the ’C2xx emulator and C source debugger interface.

XDS51x Emulator Installation Guide

(literature number SPNU070)

describes the installation of the XDS510, XDS510PP, and

XDS510WS emulator controllers. The installation of the XDS511

emulator is also described.

JT AG/MPSD Emulation Technical Reference

(literature number SPDU079)

provides the design requirements of the XDS510 emulator controller.

Discusses JTAG designs (based on the IEEE 1149.1 standard) and

modular port scan device (MPSD) designs.

TMS320 DSP Development Support Reference Guide

(literature number

SPRU011) describes the TMS320 family of digital signal processors and

the tools that support these devices. Included are code-generation tools

(compilers, assemblers, linkers, etc.) and system integration and debug

tools (simulators, emulators, evaluation modules, etc.). Also covered are

available documentation, seminars, the university program, and factory

repair and exchange.

Digital Signal Processing Applications with the TMS320 Family,

Volumes 1, 2, and 3

(literature numbers SPRA012, SPRA016,

SPRA017) Volumes 1 and 2 cover applications using the ’C10 and ’C20

families of fixed-point processors. Volume 3 documents applications

using both fixed-point processors as well as the ’C30 floating-point

processor.

TMS320 DSP Designer’s Notebook: Volume 1

.

SPRT125)

’C3x, ’C4x, ’C5x, and other TI DSPs

Presents solutions to common design problems using ’C2x,

.

TMS320 Third-Party Support Reference Guide

(literature number

(literature number

SPRU052) alphabetically lists over 100 third parties that provide various

products that serve the family of ’320 digital signal processors. A myriad

of products and applications are offered—software and hardware

development tools, speech recognition, image processing, noise

cancellation, modems, etc.

Read This First

vii

Page 8

Related Articles

Related Articles

“A Greener World Through DSP Controllers”, Panos Papamichalis,

Multimedia Technology

“A Single-Chip Multiprocessor DSP for Image Processing—TMS320C80”,

Dr. Ing. Dung Tu,

“Application Guide with DSP Leading-Edge Technology”, Y. Nishikori, M.

Hattori, T. Fukuhara, R.Tanaka, M. Shimoda, I. Kudo, A.Yanagitani, H.

Miyaguchi, et al.,

“Approaching the No-Power Barrier”, Jon Bradley and Gene Frantz,

Design

“Beware of BAT: DSPs Add Brilliance to New Weapons Systems”, Panos

Papamichalis,

“Choose DSPs for PC Signal Processing”, Panos Papamichalis,

, January 9, 1995.

DSP & Multimedia Technology

Multimedia Technology

“Developing Nations Take Shine to Wireless”, Russell MacDonald, Kara

Schmidt and Kim Higden,

“Digital Signal Processing Solutions T arget V ertical Application Markets”, Ron

ECN

Wages,

“Digital Signal Processors Boost Drive Performance”, Tim Adcock,

Storage

, September 1995.

, September/October 1995.

, September 1994.

Industrie Elektronik

, Germany, March 1995.

Electronics Engineering

, January/February 1995.

EE Times

, October 2, 1995.

, November 1995.

, October 1994.

DSP &

Electronic

DSP &

Data

viii

“DSP and Speech Recognition, An Origin of the Species”, Panos

Papamichalis,

“DSP Design Takes Top-Down Approach”, Andy Fritsch and Kim Asal,

Series Part III

“DSPs Advance Low-Cost ‘Green’ Control”, Gregg Bennett,

II

,

EE Times

“DSPs Do Best on Multimedia Applications”, Doug Rasor,

World

, October 9–16, 1995.

“DSPs: Speech Recognition Technology Enablers”, Gene Frantz and Gregg

Bennett,

“Easing JTAG Testing of Parallel-Processor Projects”, Tony Coomes, Andy

Fritsch, and Reid Tatge,

November 1995.

DSP & Multimedia Technology

,

EE Times

, April 17, 1995.

I&CS

, May 1995.

, July 17, 1995.

Asian Electronics Engineer

, July 1994.

DSP

DSP Series Part

Asian Computer

, Manila, Philippines,

Page 9

Related Articles

“Fixed or Floating? A Pointed Question in DSPs”, Jim Larimer and Daniel

EDN

Chen,

“Function-Focused Chipsets: Up the DSP Integration Core”, Panos

Papamichalis,

, August 3, 1995.

DSP & Multimedia Technology

, March/April 1995.

“GSM: Standard, Strategien und Systemchips”, Edgar Auslander,

Praxis

, Germany, October 6, 1995.

“High T ech Copiers to Improve Images and Reduce Paperwork”, Karl Guttag,

Document Management

“Host-Enabled Multimedia: Brought to You by DSP Solutions”, Panos

Papamichalis,

“Integration Shrinks Digital Cellular Telephone Designs”, Fred Cohen and

Mike McMahan,

“On-Chip Multiprocessing Melds DSPs”, Karl Guttag and Doug Deao,

Series Part III

“Real-Time Control”, Gregg Bennett,

“Speech Recognition”, P.K. Rajasekaran and Mike McMahan,

DSP & Multimedia Technology

Wireless System Design

,

EE Times

Design & Development

“Telecom Future Driven by Reduced Milliwatts per DSP Function”, Panos

Papamichalis,

“The Digital Signal Processor Development Environment”, Greg Peake,

DSP & Multimedia Technology

Embedded System Engineering

, July/August 1995.

, September/October 1995.

, November 1994.

, July 18, 1994.

Appliance Manufacturer

, May 1995.

, May/June 1995.

, United Kingdom, February 1995.

Elektronik

DSP

, May 1995.

Wireless

“The Growing Spectrum of Custom DSPs”, Gene Frantz and Kun Lin,

,

Series Part II

“The Wide World of DSPs, ” Jim Larimer,

“Third-Party Support Drives DSP Development for Uninitiated and Experts

Alike”, Panos Papamichalis,

1994/January 1995.

“Toward an Era of Economical DSPs”, John Cooper,

Times

, Jan. 23, 1995.

EE Times

, April 18, 1994.

DSP & Multimedia Technology

Design News

Read This First

, June 27, 1994.

, December

DSP Series Part I, EE

DSP

ix

Page 10

Trademarks

Trademarks

TI, 320 Hotline On-line, XDS510, XDS510PP, XDS510WS, and XDS511 are

trademarks of Texas Instruments Incorporated.

HP-UX is a trademark of Hewlett-Packard Company.

Intel is a trademark of Intel Corporation.

MS-DOS and Windows are registered trademarks of Microsoft Corporation.

PAL

is a registered trademark of Advanced Micro Devices, Inc.

OS/2, PC, and PC-DOS are trademarks of International Business Machines

Corporation.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

x

Page 11

If Y ou Need Assistance

If You Need Assistance. . .

-

World-Wide Web Sites

TI Online http://www.ti.com

Semiconductor Product Information Center (PIC) http://www.ti.com/sc/docs/pic/home.htm

DSP Solutions http://www.ti.com/dsps

320 Hotline On-line

-

North America, South America, Central America

Product Information Center (PIC) (972) 644-5580

TI Literature Response Center U.S.A. (800) 477-8924

Software Registration/Upgrades (214) 638-0333 Fax: (214) 638-7742

U.S.A. Factory Repair/Hardware Upgrades (281) 274-2285

U.S. T echnical T raining Organization (972) 644-5580

DSP Hotline (281) 274-2320 Fax: (281) 274-2324 Email: dsph@ti.com

DSP Modem BBS (281) 274-2323

DSP Internet BBS via anonymous ftp to ftp://ftp.ti.com/mirrors/tms320bbs

-

Europe, Middle East, Africa

European Product Information Center (EPIC) Hotlines:

Multi-Language Support +33 1 30 70 11 69 Fax: +33 1 30 70 10 32 Email: epic@ti.com

Deutsch +49 8161 80 33 11 or +33 1 30 70 11 68

English +33 1 30 70 11 65

Francais +33 1 30 70 11 64

Italiano +33 1 30 70 11 67

EPIC Modem BBS +33 1 30 70 11 99

European Factory Repair +33 4 93 22 25 40

Europe Customer Training Helpline Fax: +49 81 61 80 40 10

t

http://www.ti.com/sc/docs/dsps/support.html

-

Asia-Pacific

Literature Response Center +852 2 956 7288 Fax: +852 2 956 2200

Hong Kong DSP Hotline +852 2 956 7268 Fax: +852 2 956 1002

Korea DSP Hotline +82 2 551 2804 Fax: +82 2 551 2828

Korea DSP Modem BBS +82 2 551 2914

Singapore DSP Hotline Fax: +65 390 7179

Taiwan DSP Hotline +886 2 377 1450 Fax: +886 2 377 2718

Taiwan DSP Modem BBS +886 2 376 2592

Taiwan DSP Internet BBS via anonymous ftp to ftp://dsp.ee.tit.edu.tw/pub/TI/

-

Japan

Product Information Center +0120-81-0026 (in Japan) Fax: +0120-81-0036 (in Japan)

DSP Hotline +03-3769-8735 or

DSP BBS via Nifty-Serve Type “Go TIASP”

-

Documentation

When making suggestions or reporting errors in documentation, please include the following information that is on the title

page: the full title of the book, the publication date, and the literature number.

Mail: Texas Instruments Incorporated Email: comments@books.sc.ti.com

Technical Documentation Services, MS 702

P.O. Box 1443

Houston, Texas 77251-1443

Note: When calling a Literature Response Center to order documentation, please specify the literature number of the

book.

+03-3457-0972 or (INTL) 813-3457-0972 Fax: +03-3457-1259 or (INTL) 813-3457-1259

(INTL) 813-3769-8735 Fax: +03-3457-7071 or (INTL) 813-3457-7071

Read This First

xi

Page 12

Contents

Contents

1 Introduction 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Summarizes the features of the TMS320 family of products and presents typical applications.

Describes the TMS320C2xx DSP and lists its key features.

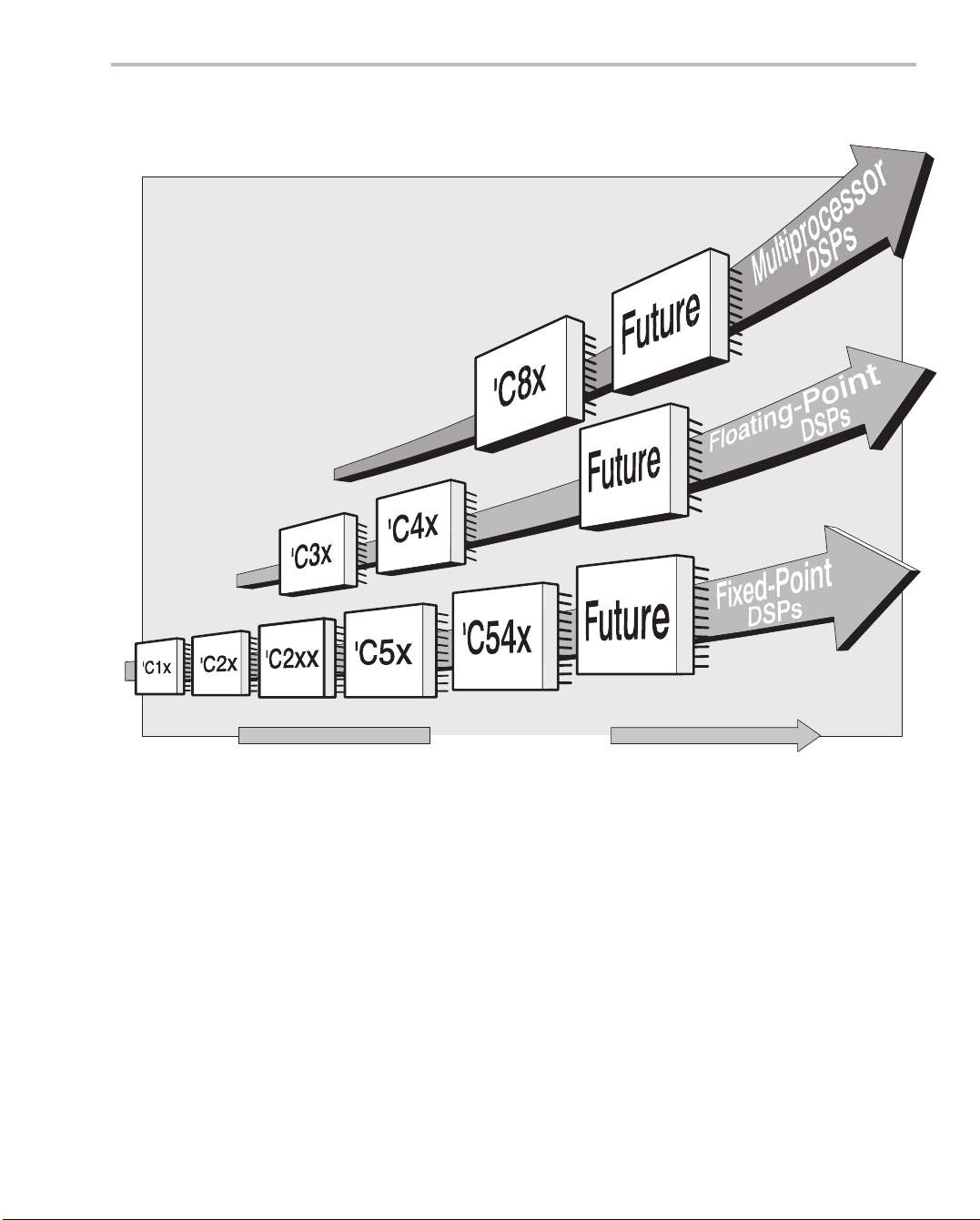

1.1 TMS320 Family 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.1 History, Development, and Advantages of TMS320 DSPs 1-2. . . . . . . . . . . . . . . . .

1.1.2 Typical Applications for the TMS320 Family 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 TMS320C2xx Generation 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Key Features of the TMS320C2xx 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Architectural Overview 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Summarizes the TMS320C2xx architecture. Provides information about the CPU, bus

structure, memory, on-chip peripherals, and scanning logic.

2.1 ’C2xx Bus Structure 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Central Processing Unit 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Central Arithmetic Logic Unit (CALU) and Accumulator 2-5. . . . . . . . . . . . . . . . . . .

2.2.2 Scaling Shifters 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.3 Multiplier 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.4 Auxiliary Register Arithmetic Unit (ARAU) and Auxiliary Registers 2-6. . . . . . . . . .

2.3 Memory and I/O Spaces 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Dual-Access On-Chip RAM 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.2 Single-Access On-Chip Program/Data RAM 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.3 Factory-Masked On-Chip ROM 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.4 Flash Memory 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Program Control 2-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 On-Chip Peripherals 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.1 Clock Generator 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.2 CLKOUT1-Pin Control (CLK) Register 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.3 Hardware Timer 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.4 Software-Programmable Wait-State Generator 2-11. . . . . . . . . . . . . . . . . . . . . . . . .

2.5.5 General-Purpose I/O Pins 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5.6 Serial Ports 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Scanning-Logic Circuitry 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiii

Page 13

Contents

3 Central Processing Unit 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the TMS320C2xx CPU. Includes information about the central arithmetic logic unit,

the accumulator, the shifters, the multiplier , and the auxiliary register arithmetic unit. Concludes

with a description of the status register bits.

3.1 Input Scaling Section 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Multiplication Section 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Multiplier 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Product-Scaling Shifter 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Central Arithmetic Logic Section 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Central Arithmetic Logic Unit (CALU) 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Accumulator 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 Output Data-Scaling Shifter 3-1 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Auxiliary Register Arithmetic Unit (ARAU) 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 ARAU and Auxiliary Register Functions 3-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Status Registers ST0 and ST1 3-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Memory and I/O Spaces 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the configuration and use of the TMS320C2xx memory and I/O spaces. Includes

memory/address maps and descriptions of the HOLD (direct memory access) operation and

the on-chip boot loader.

4.1 Overview of the Memory and I/O Spaces 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.1 Pins for Interfacing to External Memory and I/O Spaces 4-3. . . . . . . . . . . . . . . . . .

4.2 Program Memory 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 Interfacing With External Program Memory 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Local Data Memory 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.1 Data Page 0 Address Map 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Interfacing With External Local Data Memory 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Global Data Memory 4-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 Interfacing With External Global Data Memory 4-12. . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Boot Loader 4-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.1 Choosing an EPROM 4-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.2 Connecting the EPROM to the Processor 4-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.3 Programming the EPROM 4-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.4 Enabling the Boot Loader 4-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.5 Boot Loader Execution 4-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.6 Boot Loader Program 4-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 I/O Space 4-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.1 Accessing I/O Space 4-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7 Direct Memory Access Using the HOLD Operation 4-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7.1 HOLD

During Reset 4-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8 Device-Specific Information 4-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8.1 TMS320C203 Address Maps and Memory Configuration 4-31. . . . . . . . . . . . . . . .

4.8.2 TMS320C204 Address Maps and Memory Configuration 4-34. . . . . . . . . . . . . . . .

xiv

Page 14

Contents

5 Program Control 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the TMS320C2xx hardware and software features used in controlling program flow,

including program-address generation logic and interrupts. Also describes the reset operation

and power-down mode.

5.1 Program-Address Generation 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 Program Counter (PC) 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2 Stack 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.3 Micro Stack (MSTACK) 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Pipeline Operation 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Branches, Calls, and Returns 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Unconditional Branches 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 Unconditional Calls 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.3 Unconditional Returns 5-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Conditional Branches, Calls, and Returns 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.1 Using Multiple Conditions 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.2 Stabilization of Conditions 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.3 Conditional Branches 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.4 Conditional Calls 5-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.5 Conditional Returns 5-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 Repeating a Single Instruction 5-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Interrupts 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.1 Interrupt Operation: Three Phases 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.2 Interrupt Table 5-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.3 Maskable Interrupts 5-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.4 Interrupt Flag Register (IFR) 5-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.5 Interrupt Mask Register (IMR) 5-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.6 Interrupt Control Register (ICR) 5-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.7 Nonmaskable Interrupts 5-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.8 Interrupt Service Routines (ISRs) 5-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.9 Interrupt Latency 5-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7 Reset Operation 5-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8 Power-Down Mode 5-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.1 Normal Termination of Power-Down Mode 5-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.2 Termination of Power-Down During a HOLD Operation 5-37. . . . . . . . . . . . . . . . . .

6 Addressing Modes 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the operation and use of the TMS320C2xx data-memory addressing modes.

6.1 Immediate Addressing Mode 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1.1 Examples of Immediate Addressing 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Direct Addressing Mode 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.1 Using Direct Addressing Mode 6-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.2 Examples of Direct Addressing 6-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xv

Page 15

Contents

6.3 Indirect Addressing Mode 6-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.1 Current Auxiliary Register 6-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.2 Indirect Addressing Options 6-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.3 Next Auxiliary Register 6-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.4 Indirect Addressing Opcode Format 6-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.5 Examples of Indirect Addressing 6-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.6 Modifying Auxiliary Register Content 6-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7 Assembly Language Instructions 7-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the TMS320C2xx assembly language instructions in alphabetical order. Begins with

a summary of the TMS320C2xx instructions.

7.1 Instruction Set Summary 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 How To Use the Instruction Descriptions 7-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.1 Syntax 7-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.2 Operands 7-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.3 Opcode 7-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.4 Execution 7-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.5 Status Bits 7-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.6 Description 7-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.7 Words 7-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.8 Cycles 7-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.9 Examples 7-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Instruction Descriptions 7-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 On-Chip Peripherals 8-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduces the TMS320C2xx on-chip peripherals. Describes the clock generator, the

CLKOUT1-pin control register, the timer , the wait-state generator , and the general-purpose I/O

pins.

8.1 Control of On-Chip Peripherals 8-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2 Clock Generator 8-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1 Clock Generator Options 8-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3 CLKOUT1-Pin Control (CLK) Register 8-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4 Timer 8-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4.1 Timer Operation 8-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4.2 Timer Control Register (TCR) 8-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4.3 Timer Counter Register (TIM) and Timer Period Register (PRD) 8-12. . . . . . . . . .

8.4.4 Setting the Timer Interrupt Rate 8-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.4.5 The Timer at Hardware Reset 8-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5 Wait-State Generator 8-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.5.1 Generating Wait States With the READY Signal 8-14. . . . . . . . . . . . . . . . . . . . . . . .

8.5.2 Generating Wait States With the ’C2xx Wait-State Generator 8-14. . . . . . . . . . . . .

8.6 General-Purpose I/O Pins 8-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.6.1 Input Pin BIO

8.6.2 Output Pin XF 8-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.6.3 Input/Output Pins IO0, IO1, IO2, and IO3 8-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xvi

8-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page 16

Contents

9 Synchronous Serial Port 9-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the operation and control of the TMS320C2xx on-chip synchronous serial port.

9.1 Overview of the Synchronous Serial Port 9-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2 Components and Basic Operation 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.1 Signals 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.2 FIFO Buffers and Registers 9-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.3 Interrupts 9-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.4 Basic Operation 9-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3 Controlling and Resetting the Port 9-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.1 Selecting a Mode of Operation (Bit 1 of the SSPCR) 9-12. . . . . . . . . . . . . . . . . . . .

9.3.2 Selecting Transmit Clock Source and Transmit Frame Sync Source

(Bits 2 and 3 of the SSPCR) 9-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3.3 Resetting the Synchronous Serial Port (Bits 4 and 5 of the SSPCR) 9-13. . . . . . .

9.3.4 Using Transmit and Receive Interrupts (Bits 8–11 of the SSPCR) 9-13. . . . . . . . .

9.4 Managing the Contents of the FIFO Buffers 9-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5 Transmitter Operation 9-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5.1 Burst Mode Transmission With Internal Frame Sync

(FSM = 1, TXM = 1) 9-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5.2 Burst Mode Transmission With External Frame Sync

(FSM = 1, TXM = 0) 9-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5.3 Continuous Mode Transmission With Internal Frame Sync

(FSM = 0, TXM = 1) 9-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.5.4 Continuous Mode Transmission with External Frame Sync

(FSM=0, TXM=0) 9-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6 Receiver Operation 9-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.1 Burst Mode Reception 9-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.6.2 Continuous Mode Reception 9-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.7 Troubleshooting 9-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.7.1 Test Bits 9-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.7.2 Burst Mode Error Conditions 9-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.7.3 Continuous Mode Error Conditions 9-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 Asynchronous Serial Port 10-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the operation and control of the TMS320C2xx on-chip asynchronous serial port.

10.1 Overview of the Asynchronous Serial Port 10-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2 Components and Basic Operation 10-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.1 Signals 10-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.2 Baud-Rate Generator 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.3 Registers 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.4 Interrupts 10-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.5 Basic Operation 10-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xvii

Page 17

Contents

10.3 Controlling and Resetting the Port 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.1 Asynchronous Serial Port Control Register (ASPCR) 10-7. . . . . . . . . . . . . . . . . . . .

10.3.2 I/O Status Register (IOSR) 10-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.3 Baud-Rate Divisor Register (BRD) 10-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.4 Using Automatic Baud-Rate Detection 10-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

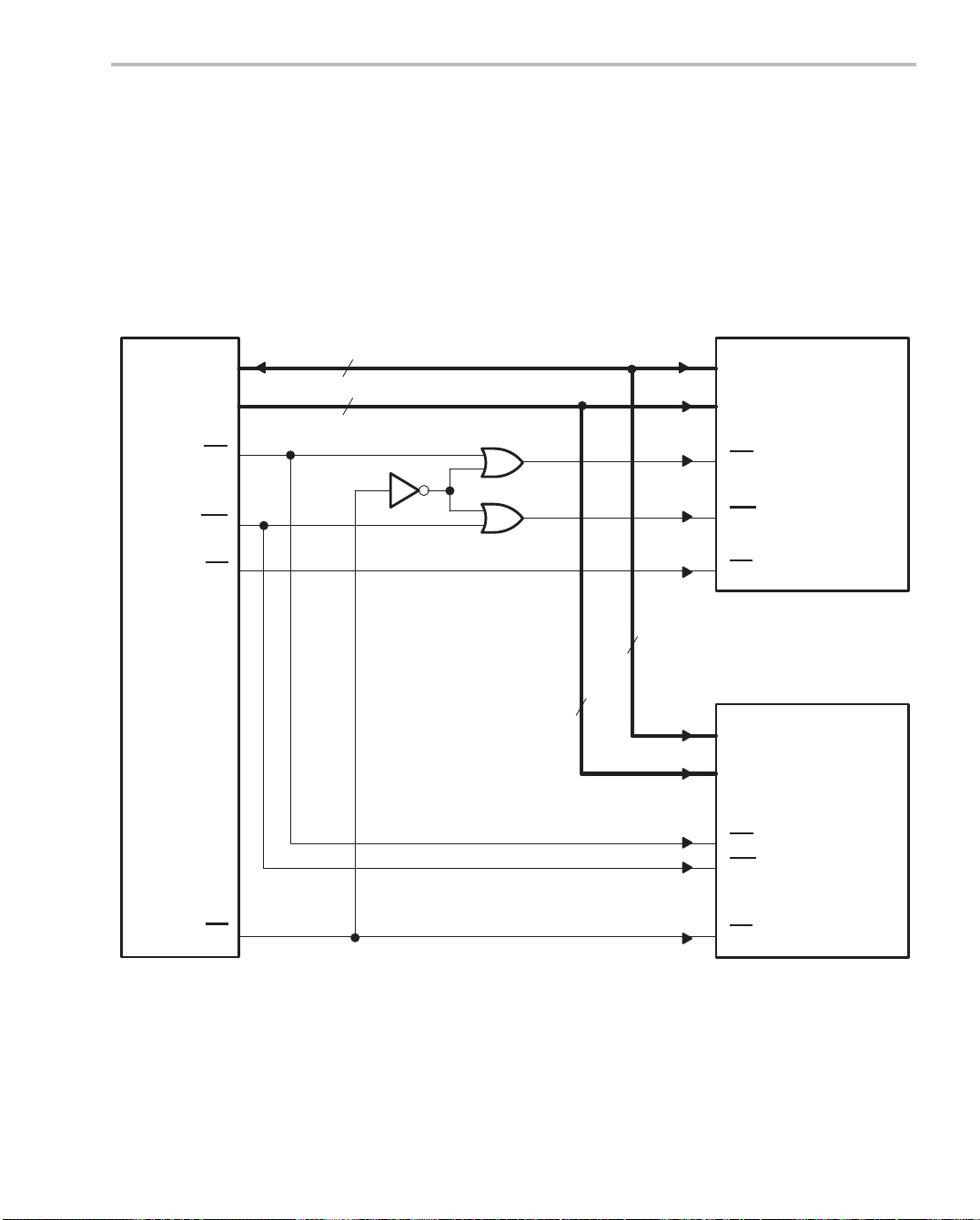

10.3.5 Using I/O Pins IO3, IO2, IO1, and IO0 10-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3.6 Using Interrupts 10-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.4 Transmitter Operation 10-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.5 Receiver Operation 10-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11 TMS320C209 11-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes how the TMS320C209 differs from other TMS320C2xx devices and is a central

resource for all the TMS320C209-specific control registers and configuration information.

11.1 ’C209 Versus Other ’C2xx Devices 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.1 What Is the Same 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.2 What Is Different 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1.3 Where to Find the Information You Need About the TMS320C209 11-3. . . . . . . .

11.2 ’C209 Memory and I/O Spaces 11-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3 ’C209 Interrupts 11-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3.1 ’C209 Interrupt Registers 11-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1 1.3.2 IACK

Pin 11-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.4 ’C209 On-Chip Peripherals 11-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.4.1 ’C209 Clock Generator Options 11-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.4.2 ’C209 Timer Control Register (TCR) 11-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.4.3 ’C209 Wait-State Generator 11-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A Register Summary A-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Is a concise, central resource for information about the TMS320C2xx on-chip registers.

Includes addresses, reset values, and descriptive illustrations for the registers.

A.1 Addresses and Reset Values A-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2 Register Descriptions A-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B TMS320C1x/C2x/C2xx/C5x Instruction Set Comparison B-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Discusses the compatibility of program code among the following devices: TMS320C1x,

TMS320C2x, TMS320C2xx, and TMS320C5x.

B.1 Using the Instruction Set Comparison Table B-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.1 An Example of a Table Entry B-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.1.2 Symbols and Acronyms Used in the Table B-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.2 Enhanced Instructions B-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B.3 Instruction Set Comparison Table B-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C Program Examples C-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Presents examples of assembly language programs for the TMS320C2xx, primarily examples

for the on-chip peripherals.

C.1 About These Program Examples C-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.2 Shared Program Code C-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.3 Task-Specific Program Code C-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C.4 Introduction to Generating Boot Loader Code C-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xviii

Page 18

Contents

D Submitting ROM Codes to TI D-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Explains the process for submitting custom program code to TI for designing masks for the

on-chip ROM on a TMS320 DSP.

E Design Considerations for Using XDS510 Emulator E-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the JTAG emulator cable and how to construct a 14-pin connector on your target

system and how to connect the target system to the emulator.

E.1 Designing Your Target System’s Emulator Connector (14-Pin Header) E-2. . . . . . . . . . . . .

E.2 Bus Protocol E-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.3 Emulator Cable Pod E-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.4 Emulator Cable Pod Signal Timing E-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.5 Emulation Timing Calculations E-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.6 Connections Between the Emulator and the Target System E-10. . . . . . . . . . . . . . . . . . . . .

E.6.1 Buffering Signals E-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.6.2 Using a Target-System Clock E-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.6.3 Configuring Multiple Processors E-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.7 Physical Dimensions for the 14-Pin Emulator Connector E-14. . . . . . . . . . . . . . . . . . . . . . . .

E.8 Emulation Design Considerations E-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.8.1 Using Scan Path Linkers E-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.8.2 Emulation Timing Calculations for a Scan Path Linker (SPL) E-18. . . . . . . . . . . . .

E.8.3 Using Emulation Pins E-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E.8.4 Performing Diagnostic Applications E-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

F Glossary F-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Explains terms, abbreviations, and acronyms used throughout this book.

Contents

xix

Page 19

Figures

Figures

1–1 TMS320 Family 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 Overall Block Diagram of the ’C2xx 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Bus Structure Block Diagram 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Block Diagram of the Input Scaling, Central Arithmetic Logic, and

3–2 Block Diagram of the Input Scaling Section 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Operation of the Input Shifter for SXM = 0 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Operation of the Input Shifter for SXM = 1 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–5 Block Diagram of the Multiplication Section 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 Block Diagram of the Central Arithmetic Logic Section 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 Shifting and Storing the High Word of the Accumulator 3-11. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 Shifting and Storing the Low Word of the Accumulator 3-11. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 ARAU and Related Logic 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 Status Register ST0 3-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 Status Register ST1 3-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Interface With External Program Memory 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Pages of Data Memory 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Interface With External Local Data Memory 4-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 GREG Register Set to Configure 8K for Global Data Memory 4-12. . . . . . . . . . . . . . . . . . . . . .

4–5 Global and Local Data Memory for GREG = 11100000 4-12. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 Using 8000h–FFFFh for Local and Global External Memory 4-13. . . . . . . . . . . . . . . . . . . . . . .

4–7 Simplified Block Diagram of Boot Loader Operation 4-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 Connecting the EPROM to the Processor 4-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–9 Storing the Program in the EPROM 4-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–10 Program Code Transferred From 8-Bit EPROM to 16-Bit RAM 4-19. . . . . . . . . . . . . . . . . . . . .

4–11 Interrupt Vectors Transferred First During Boot Load 4-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–12 I/O Address Map for the ’C2xx 4-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–13 I/O Port Interface Circuitry 4-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–14 HOLD

4–15 Reset Deasserted Before HOLD Deasserted 4-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–16 ’C203 Address Map 4-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–17 ’C204 Address Map 4-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Program-Address Generation Block Diagram 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 A Push Operation 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 A Pop Operation 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 4-Level Pipeline Operation 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Multiplication Sections of the CPU 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Deasserted Before Reset Deasserted 4-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xx

Page 20

Figures

5–5 INT2/INT3 Request Flow Chart 5-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Maskable Interrupt Operation Flow Chart 5-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 ’C2xx Interrupt Flag Register (IFR) — Data-Memory Address 0006h 5-21. . . . . . . . . . . . . . . .

5–8 ’C2xx Interrupt Mask Register (IMR) — Data-Memory Address 0004h 5-23. . . . . . . . . . . . . . .

5–9 ’C2xx Interrupt Control Register (ICR) — I/O-Space Address FFECh 5-26. . . . . . . . . . . . . . .

5–10 Nonmaskable Interrupt Operation Flow Chart 5-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Instruction Register Contents for Example 6–1 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Two Words Loaded Consecutively to the Instruction Register in Example 6–2 6-3. . . . . . . . .

6–3 Pages of Data Memory 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Instruction Register (IR) Contents in Direct Addressing Mode 6-5. . . . . . . . . . . . . . . . . . . . . . .

6–5 Generation of Data Addresses in Direct Addressing Mode 6-5. . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 Instruction Register Content in Indirect Addressing 6-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 Bit Numbers and Their Corresponding Bit Codes for BIT Instruction 7-45. . . . . . . . . . . . . . . .

7–2 Bit Numbers and Their Corresponding Bit Codes for BITT Instruction 7-47. . . . . . . . . . . . . . .

7–3 LST #0 Operation 7-87. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 LST #1 Operation 7-88. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–1 Using the Internal Oscillator 8-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–2 Using an External Oscillator 8-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–3 ’C2xx CLK Register — I/O-Space Address FFE8h 8-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–4 Timer Functional Block Diagram 8-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–5 ’C2xx Timer Control Register (TCR) — I/O-Space Address FFF8h 8-11. . . . . . . . . . . . . . . . . .

8–6 ’C2xx Wait-State Generator Control Register (WSGR)

— I/O-Space Address FFFCh 8-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–7 BIO

Timing Diagram Example 8-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–1 Synchronous Serial Port Block Diagram 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–2 2-Way Serial Port Transfer With External Frame Sync and External Clock 9-5. . . . . . . . . . . .

9–3 Synchronous Serial Port Control Register (SSPCR)

— I/O-Space Address FFF1h 9-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–4 Burst Mode Transmission With Internal Frame Sync and

Multiple Words in the Buffer 9-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–5 Burst Mode Transmission With External Frame Sync 9-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–6 Continuous Mode Transmission With Internal Frame Sync 9-21. . . . . . . . . . . . . . . . . . . . . . . . .

9–7 Continuous Mode Transmission With External Frame Sync 9-23. . . . . . . . . . . . . . . . . . . . . . . .

9–8 Burst Mode Reception 9-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–9 Continuous Mode Reception 9-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–10 Test Bits in the SSPCR 9-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–1 Asynchronous Serial Port Block Diagram 10-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

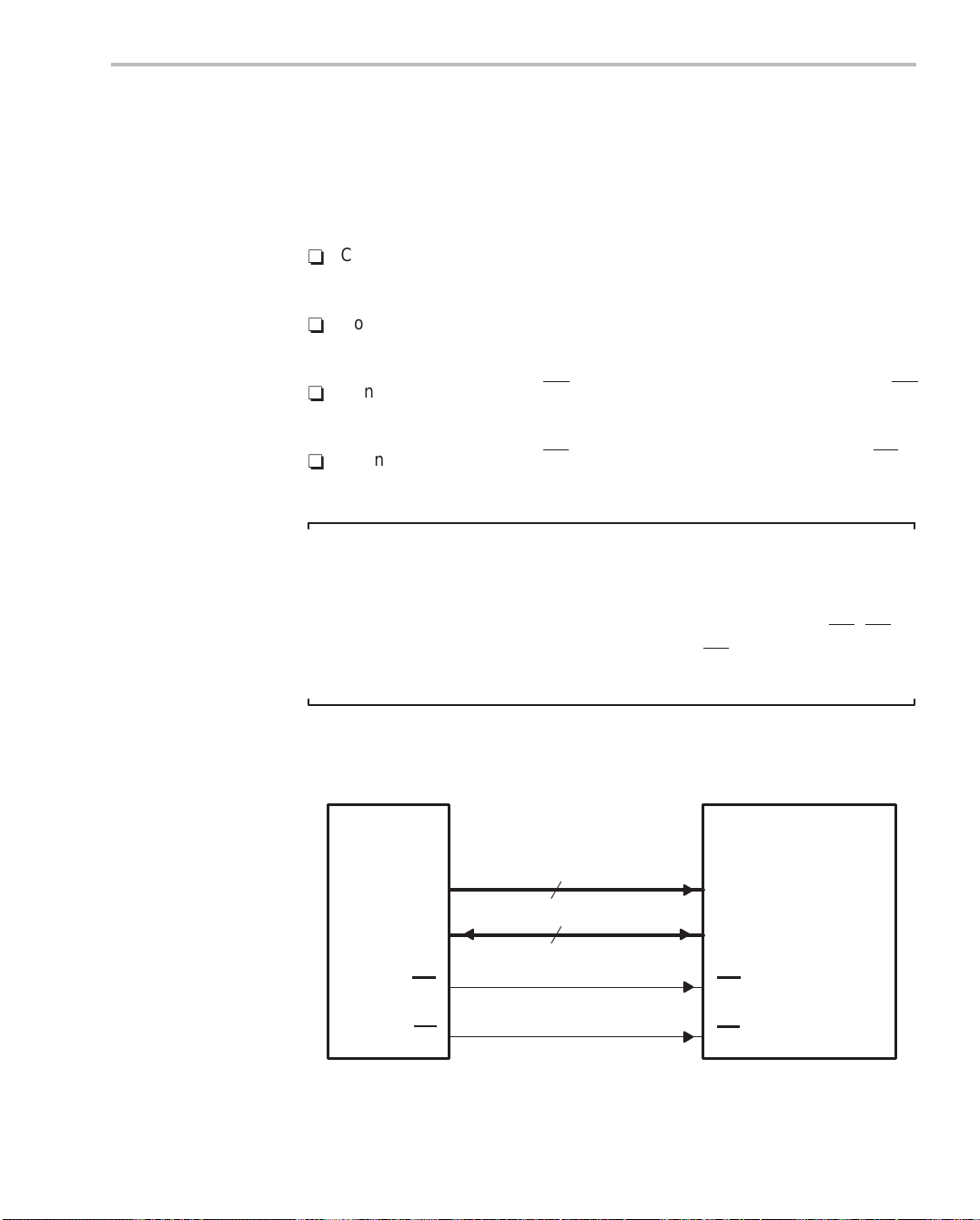

10–2 Typical Serial Link Between a ’C2xx Device and a Host CPU 10-6. . . . . . . . . . . . . . . . . . . . . .

10–3 Asynchronous Serial Port Control Register (ASPCR) — I/O-Space

Address FFF5h 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–4 I/O Status Register (IOSR) — I/O-Space Address FFF6h 10-10. . . . . . . . . . . . . . . . . . . . . . . . .

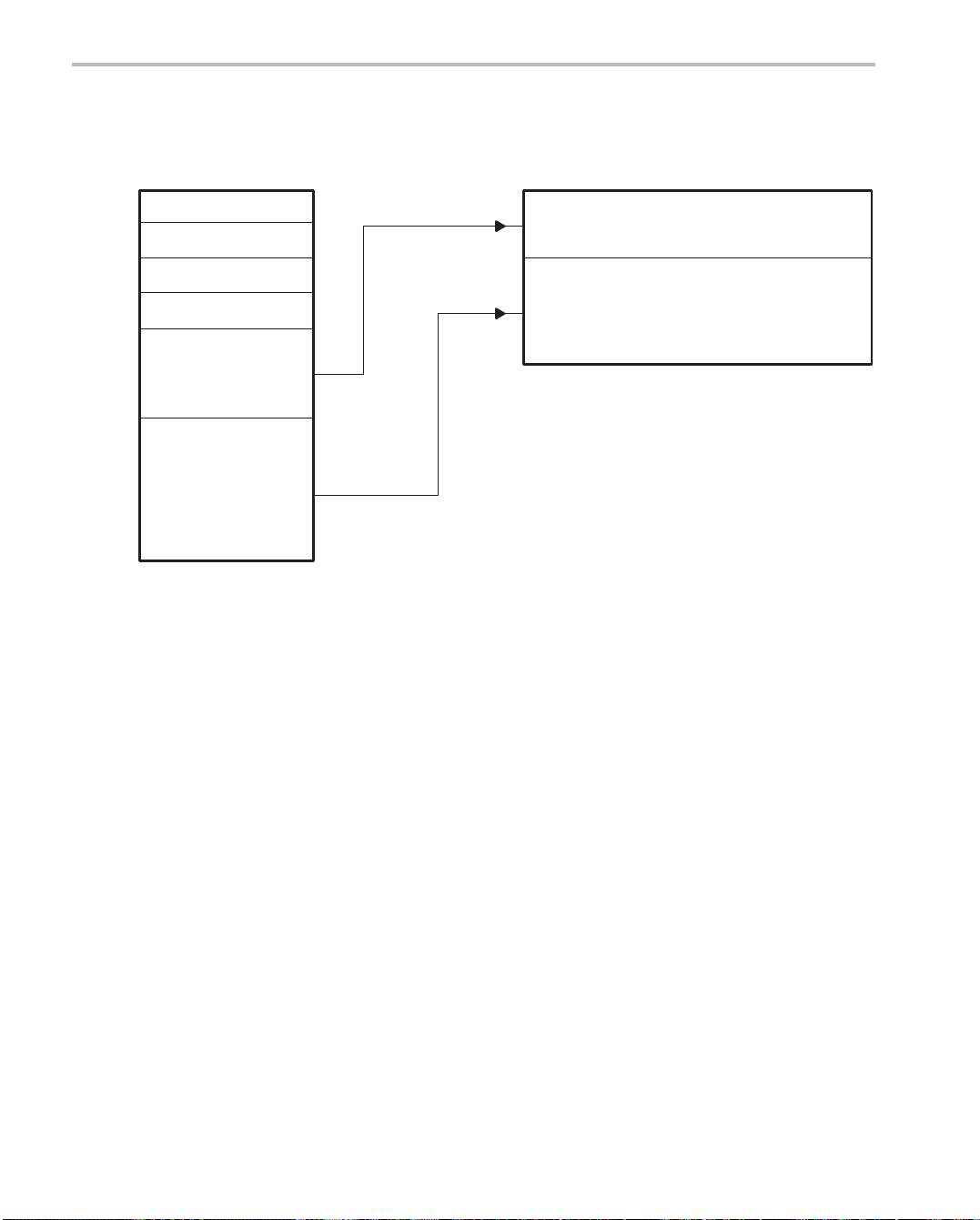

10–5 Example of the Logic for Pins IO0–IO3 10-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–6 Data Transmit 10-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–7 Data Receive 10-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–1 ’C209 Address Maps 11-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xxi

Page 21

Figures

11–2 ’C209 Interrupt Flag Register (IFR) — Data-Memory Address 0006h 11-12. . . . . . . . . . . . . . .

11–3 ’C209 Interrupt Mask Register (IMR) — Data-Memory Address 0004h 11-13. . . . . . . . . . . . .

11–4 ’C209 Timer Control Register (TCR) — I/O Address FFFCh 11-15. . . . . . . . . . . . . . . . . . . . . .

11–5 ’C209 Wait-State Generator Control Register (WSGR) — I/O Address FFFFh 11-17. . . . . . .

C–1 Procedure for Generating Executable Files C-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D–1 TMS320 ROM Code Submittal Flow Chart D-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–1 14-Pin Header Signals and Header Dimensions E-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–2 Emulator Cable Pod Interface E-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–3 Emulator Cable Pod Timings E-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–4 Emulator Connections Without Signal Buffering E-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–5 Emulator Connections With Signal Buffering E-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–6 Target-System-Generated Test Clock E-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–7 Multiprocessor Connections E-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–8 Pod/Connector Dimensions E-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–9 14-Pin Connector Dimensions E-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–10 Connecting a Secondary JTAG Scan Path to a Scan Path Linker E-17. . . . . . . . . . . . . . . . . . .

E–11 EMU0/1 Configuration to Meet Timing Requirements of Less Than 25 ns E-21. . . . . . . . . . . .

E–12 Suggested Timings for the EMU0 and EMU1 Signals E-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–13 EMU0/1 Configuration With Additional AND Gate to Meet

Timing Requirements of Greater Than 25 ns E-23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–14 EMU0/1 Configuration Without Global Stop E-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–15 TBC Emulation Connections for n JTAG Scan Paths E-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xxii

Page 22

Tables

Tables

1–1 Typical Applications for TMS320 DSPs 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 ’C2xx Generation Summary 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 Program and Data Memory on the TMS320C2xx Devices 2-7. . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Serial Ports on the ’C2xx Devices 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Product Shift Modes for the Product-Scaling Shifter 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Bit Fields of Status Registers ST0 and ST1 3-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 Pins for Interfacing With External Memory and I/O Spaces 4-3. . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Data Page 0 Address Map 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Global Data Memory Configurations 4-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 On-Chip Registers Mapped to I/O Space 4-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 ’C203 Program-Memory Configuration Options 4-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 ’C203 Data-Memory Configuration Options 4-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–7 ’C204 Program-Memory Configuration Options 4-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–8 ’C204 Data-Memory Configuration Options 4-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Program-Address Generation Summary 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Address Loading to the Program Counter 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Conditions for Conditional Calls and Returns 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Groupings of Conditions 5-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 ’C2xx Interrupt Locations and Priorities 5-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Reset Values of On-Chip Registers Mapped to Data Space 5-35. . . . . . . . . . . . . . . . . . . . . . . .

5–7 Reset Values of On-Chip Registers Mapped to I/O Space 5-35. . . . . . . . . . . . . . . . . . . . . . . . .

6–1 Indirect Addressing Operands 6-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Effects of the ARU Code on the Current Auxiliary Register 6-13. . . . . . . . . . . . . . . . . . . . . . . . .

6–3 Field Bits and Notation for Indirect Addressing 6-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–1 Accumulator, Arithmetic, and Logic Instructions 7-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–2 Auxiliary Register Instructions 7-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–3 TREG, PREG, and Multiply Instructions 7-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–4 Branch Instructions 7-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–5 Control Instructions 7-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–6 I/O and Memory Instructions 7-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–7 Product Shift Modes 7-37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7–8 Product Shift Modes 7-167. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–1 Peripheral Register Locations and Reset Conditions 8-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–2 ’C2xx Input Clock Modes 8-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–3 ’C2xx Timer Run/Emulation Modes 8-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8–4 Setting the Number of Wait States With the ’C2xx WSGR Bits 8-16. . . . . . . . . . . . . . . . . . . . .

Contents

xxiii

Page 23

Tables

9–1 SSP Interface Pins 9-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–2 Run and Emulation Modes 9-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–3 Controlling Transmit Interrupt Generation by Writing to Bits FT1 and FT0 9-9. . . . . . . . . . . . .

9–4 Controlling Receive Interrupt Generation by Writing to Bits FR1 and FR0 9-10. . . . . . . . . . . .

9–5 Selecting Transmit Clock and Frame Sync Sources 9-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9–6 Run and Emulation Modes 9-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–1 Asynchronous Serial Port Interface Pins 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10–2 Common Baud Rates and the Corresponding BRD Values 10-14. . . . . . . . . . . . . . . . . . . . . . .

10–3 Configuring Pins IO0–IO3 with ASPCR Bits CIO0–CIO3 10-15. . . . . . . . . . . . . . . . . . . . . . . . . .

10–4 Viewing the Status of Pins IO0–IO3 With IOSR Bits IO0–IO3 and DIO0–DIO3 10-16. . . . . . .

11–1 ’C209 Program-Memory Configuration Options 11-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–2 ’C209 Data-Memory Configuration Options 11-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–3 ’C209 On-Chip Registers Mapped to I/O Space 11-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–4 ’C209 Interrupt Locations and Priorities 11-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11–5 ’C209 Input Clock Modes 11-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–1 Reset Values of the Status Registers A-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A–2 Addresses and Reset Values of On-Chip Registers Mapped to Data Space A-2. . . . . . . . . . .

A–3 Addresses and Reset Values of On-Chip Registers Mapped to I/O Space A-2. . . . . . . . . . . .

B–1 Symbols and Acronyms Used in the Instruction Set Summary B-3. . . . . . . . . . . . . . . . . . . . . . .

B–2 Summary of Enhanced Instructions B-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–1 Shared Programs in This Appendix C-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–2 Task-Specific Programs in This Appendix C-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–1 14-Pin Header Signal Descriptions E-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–2 Emulator Cable Pod Timing Parameters E-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xxiv

Page 24

Examples

Examples

4–1 An Interrupt Service Routine Supporting INT1 and HOLD 4-28. . . . . . . . . . . . . . . . . . . . . . . . .

6–1 RPT Instruction Using Short-Immediate Addressing 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 ADD Instruction Using Long-Immediate Addressing 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 Using Direct Addressing with ADD (Shift of 0 to 15) 6-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 Using Direct Addressing with ADD (Shift of 16) 6-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 Using Direct Addressing with ADDC 6-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 Selecting a New Current Auxiliary Register 6-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–7 No Increment or Decrement 6-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–8 Increment by 1 6-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–9 Decrement by 1 6-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–10 Increment by Index Amount 6-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–11 Decrement by Index Amount 6-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–12 Increment by Index Amount With Reverse Carry Propagation 6-16. . . . . . . . . . . . . . . . . . . . . .

6–13 Decrement by Index Amount With Reverse Carry Propagation 6-16. . . . . . . . . . . . . . . . . . . . .

C–1 Generic Command File (c203.cmd) C-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–2 Header File With I/O Register Declarations (init.h) C-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–3 Header File With Interrupt Vector Declarations (vector.h) C-7. . . . . . . . . . . . . . . . . . . . . . . . . . .

C–4 Implementing Simple Delay Loops (delay.asm) C-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–5 Testing and Using the Timer (timer.asm) C-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–6 Testing and Using Interrupt INT1

C–7 Implementing a HOLD Operation (hold.asm) C-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–8 Testing and Using Interrupts INT2

C–9 Asynchronous Serial Port Transmission (uart.asm) C-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–10 Loopback to Verify Transmissions of Asynchronous Serial Port (echo.asm) C-14. . . . . . . . . .

C–11 Testing and Using Automatic Baud-Rate Detection on

Asynchronous Serial Port (autobaud.asm) C-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–12 Testing and Using Asynchronous Serial Port Delta Interrupts (bitio.asm) C-18. . . . . . . . . . . . .

C–13 Synchronous Serial Port Continuous Mode Transmission (ssp.asm) C-20. . . . . . . . . . . . . . . .

C–14 Using Synchronous Serial Port With Codec Device (ad55.asm) C-21. . . . . . . . . . . . . . . . . . . .

C–15 Linker Command File C-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

C–16 Hex Conversion Utility Command File C-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–1 Key Timing for a Single-Processor System Without Buffers E-8. . . . . . . . . . . . . . . . . . . . . . . . .

E–2 Key Timing for a Single- or Multiple-Processor System With

Buffered Input and Output E-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E–3 Key Timing for a Single-Processor System Without Buffering (SPL) E-19. . . . . . . . . . . . . . . . .

E–4 Key Timing for a Single- or Multiprocessor-System With

Buffered Input and Output (SPL) E-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(intr1.asm) C-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

and INT3 (intr23.asm) C-12. . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

xxv

Page 25

Notes, Cautions, and Warnings

Cautions

Obtain the Proper Timing Information 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Do Not Write to Test/Emulation Addresses 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .