Page 1

User's Guide

SLLU132–October 2010

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps,

Multi-Rate Transceiver Evaluation Module

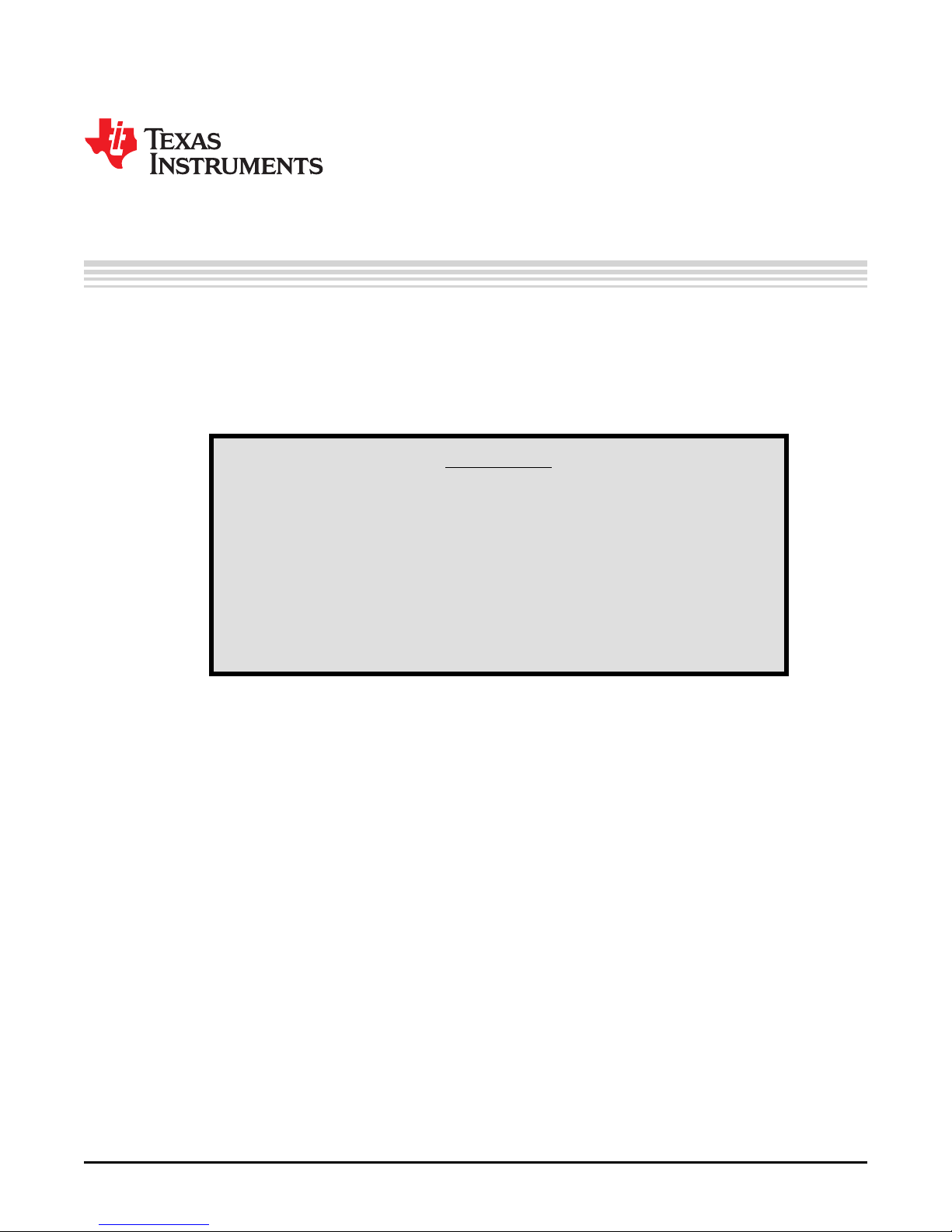

This user’s guide describes the usage and construction of the TLK6002 evaluation module (EVM). This

document provides guidance on proper use of the EVM by showing some device configurations and test

modes. In addition, design, layout, and schematic information is provided to the user. Users can use

information in this guide to choose the optimal design methods and materials when designing a complete

system.

WARNING

This equipment is intended for use in a laboratory test environment

only. It generates, uses, and can radiate radio frequency energy

and has not been tested for compliance with the limits of

computing devices pursuant to subpart J of part 15 of FCC rules,

which are designed to provide reasonable protection against radio

frequency interference. Operation of this equipment in other

environments may cause interference with radio communications,

in which case, users at their expense are required to take whatever

measures may be required to correct this interference.

Contents

1 Introduction .................................................................................................................. 4

2 EVM PCB and High-Speed Design Considerations .................................................................... 5

3 TLK6002 EVM Kit Contents ............................................................................................... 6

4 Power ......................................................................................................................... 6

5 Power Monitoring LEDs .................................................................................................... 9

6 Control and Output Status Signals ...................................................................................... 11

6.1 Control Signal and Status Pin Descriptions: .................................................................. 11

7 PRBS PASS Latch Circuits .............................................................................................. 16

8 MDIO ........................................................................................................................ 18

9 JTAG ........................................................................................................................ 19

10 Reset ........................................................................................................................ 20

11 Parallel Signals ............................................................................................................ 21

12 Peripheral Ports ............................................................................................................ 23

13 Test and Setup Configurations .......................................................................................... 24

14 TLK6002EVM Schematics ............................................................................................... 26

15 TLK6002EVM Bill of Materials ........................................................................................... 54

16 TLK6002EVM Board Layouts ............................................................................................ 60

List of Figures

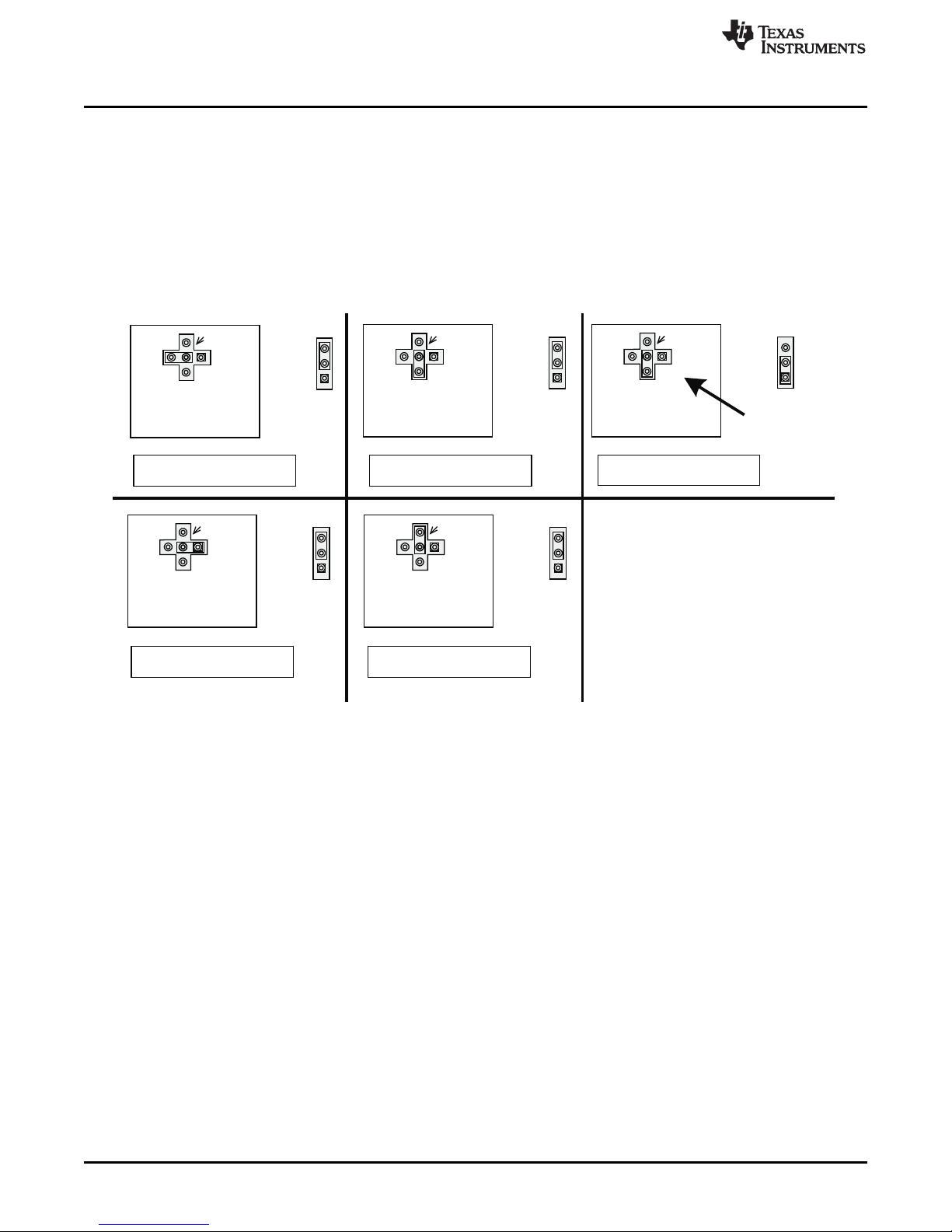

1 TLK6002 EVM Power Source Selection Example ..................................................................... 6

2 TLK6002 EVM 1p5/8V Voltage Source Selection ...................................................................... 7

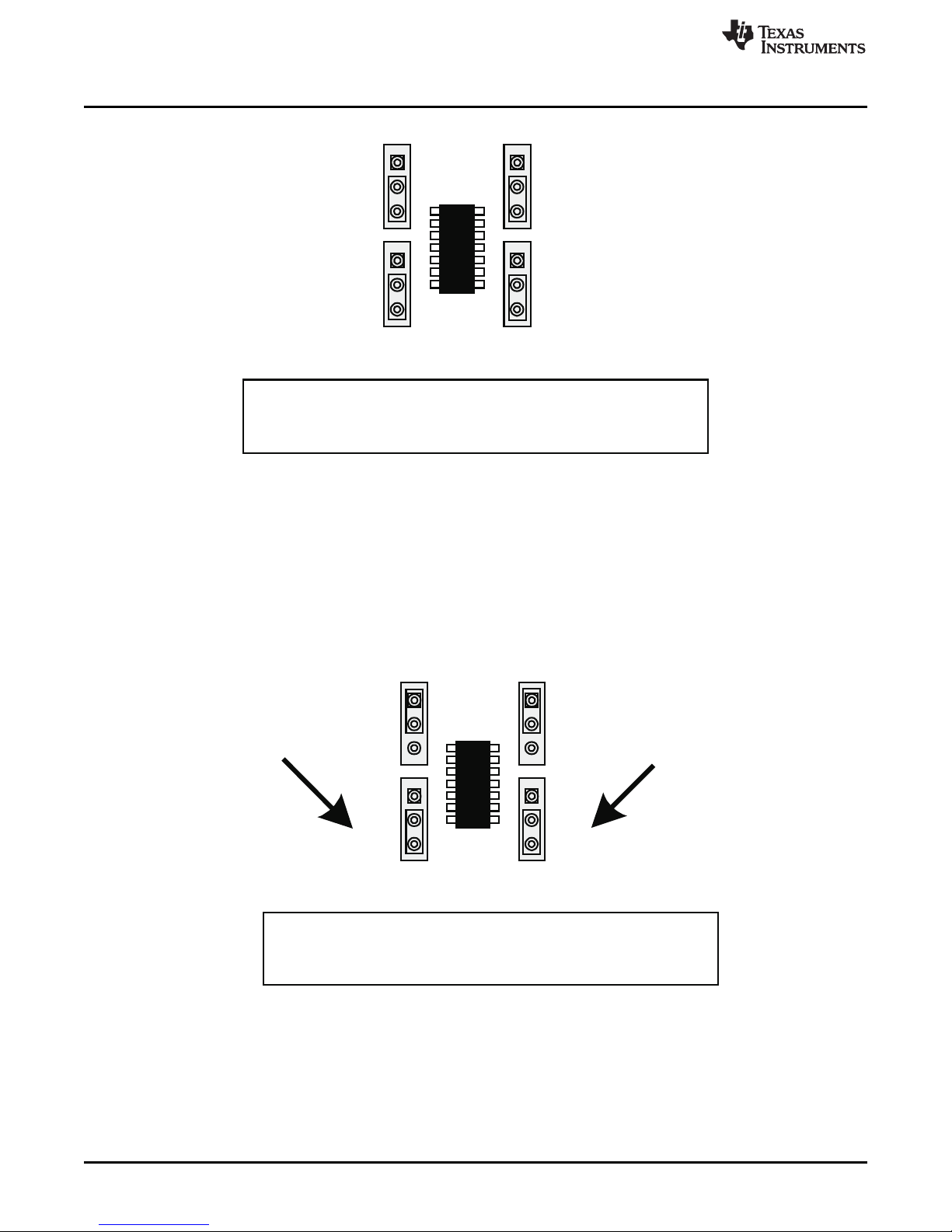

3 TLK6002 EVM Regulator Voltage Margin Selection ................................................................... 7

4 TLK6002 EVM Global Regulator Margin Selection..................................................................... 8

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Evaluation Module

1

Copyright © 2010, Texas Instruments Incorporated

Page 2

www.ti.com

5 TLK6002 EVM Voltage Monitor LED Enabled Example............................................................... 9

6 TLK6002 EVM Voltage Monitor LED Disabled Example............................................................. 10

7 TLK6002 EVM Voltage Monitor LED Connected Directly to Plane Example...................................... 10

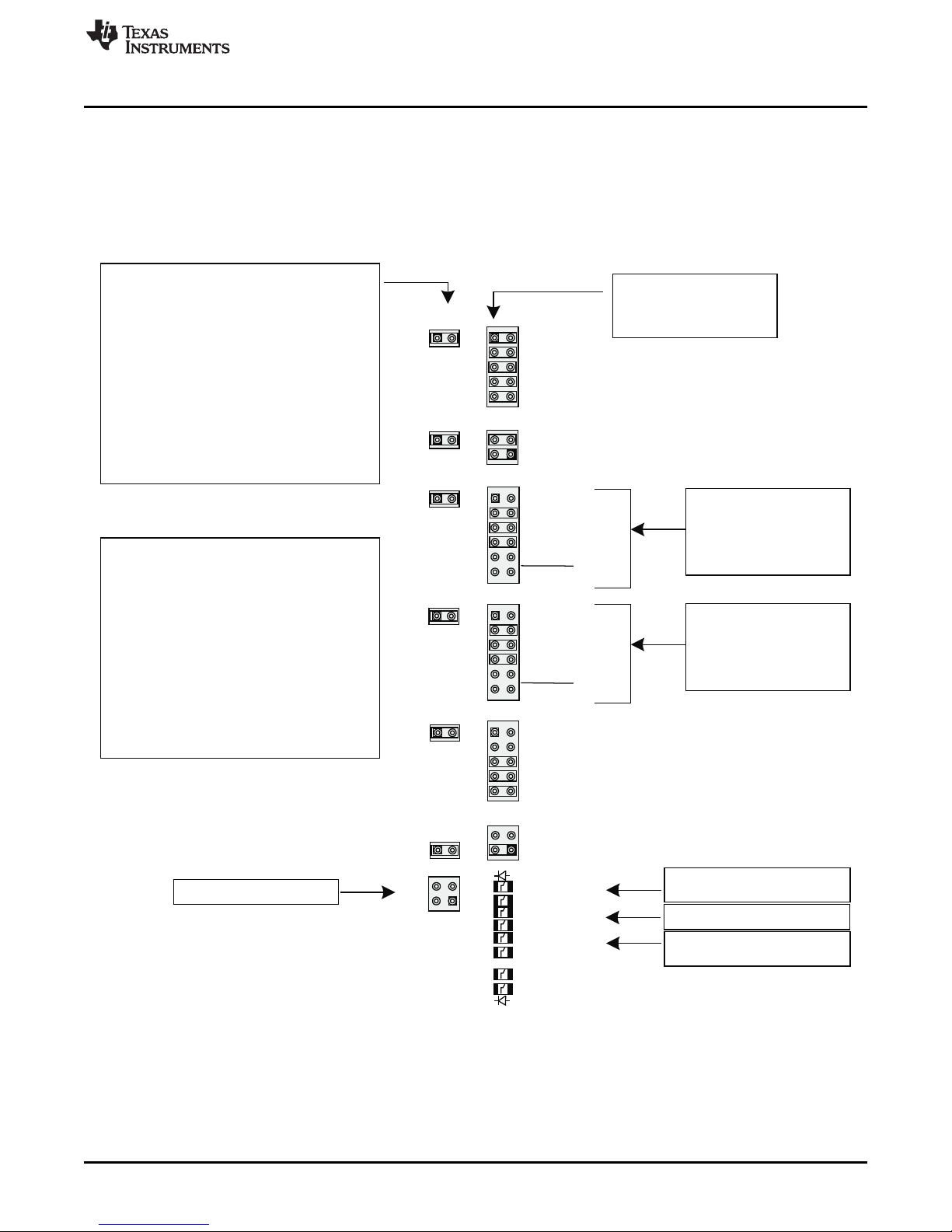

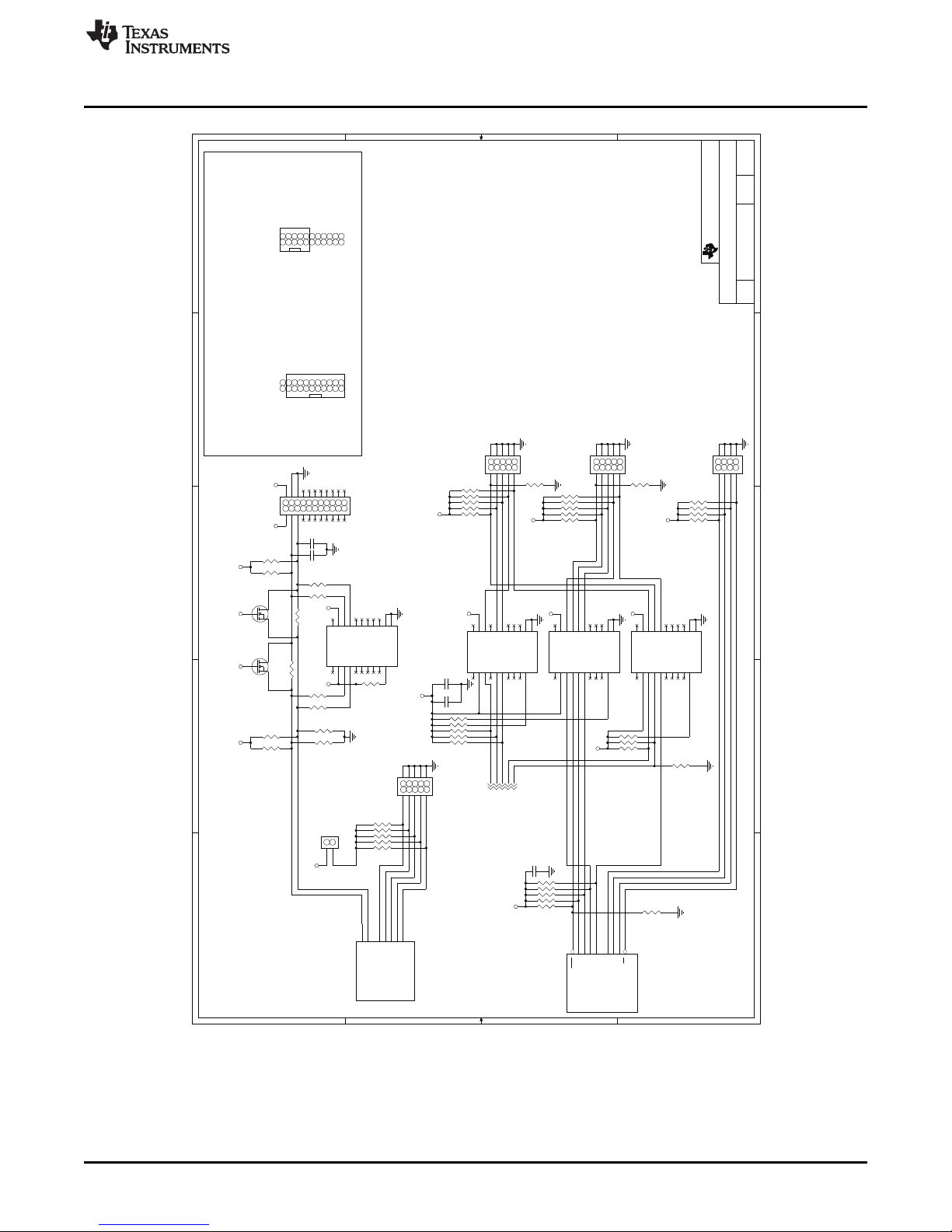

8 Control Connectors (JMP17, JMP23, JMP26, JMP27, JMP29, JMP33, JMP43) ................................ 11

9 TLK6002 EVM MDIO Connector (JMP30) ............................................................................. 17

10 TLK6002 EVM MDIO Connector (JMP30) ............................................................................. 18

11 TLK6002 EVM JTAG Connector (JMP35) ............................................................................. 19

12 RESET Switch – SW1, JMP14, or JMP15............................................................................. 20

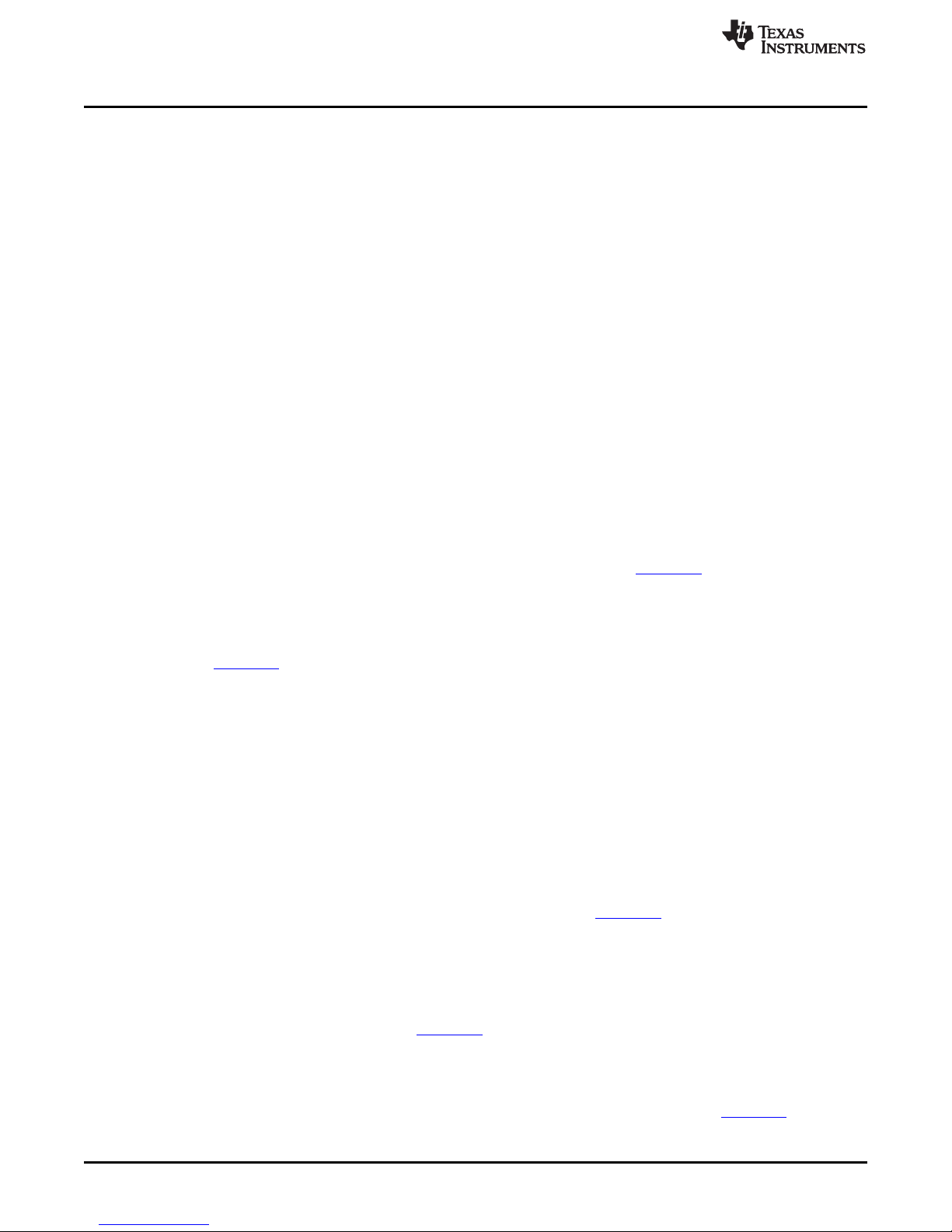

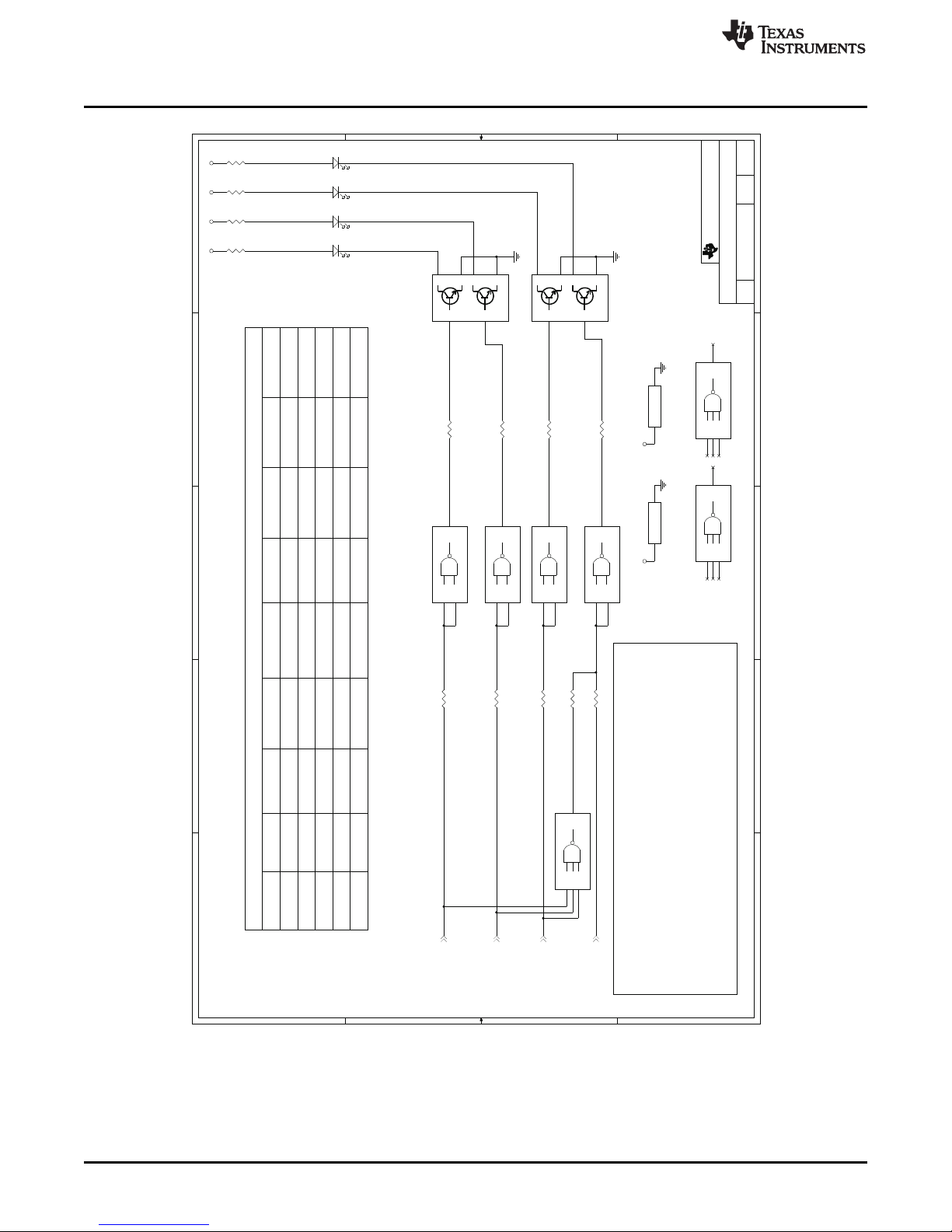

13 Parallel Signal Header Block Diagram.................................................................................. 21

14 Parallel Loopback Example .............................................................................................. 22

15 TDA[19:0] Static Clock Data Pattern Example ........................................................................ 23

16 Example TLK6002EVM Test Configuration – Serial Loopback ..................................................... 24

17 Example TLK6002 EVM Test Configuration – Parallel Loopback................................................... 25

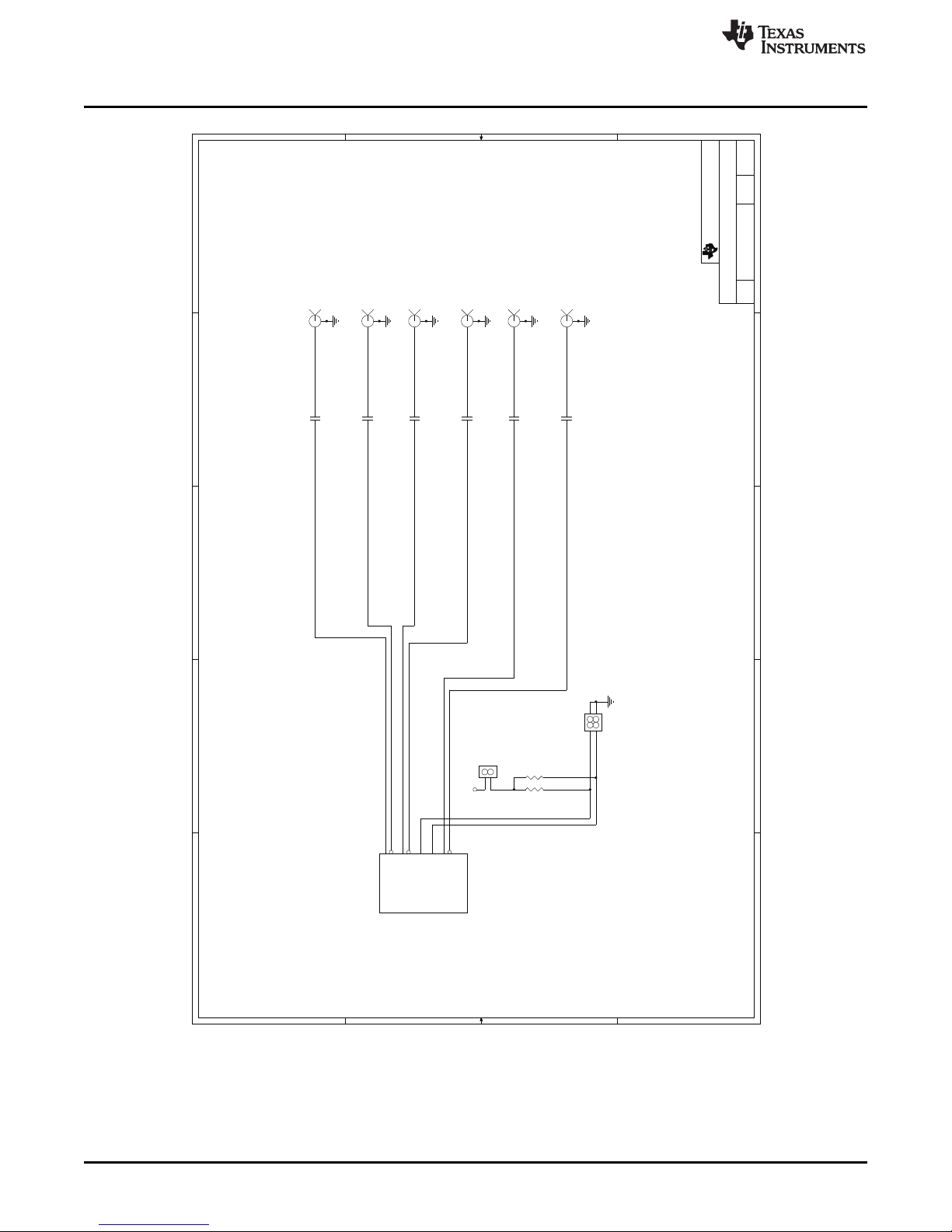

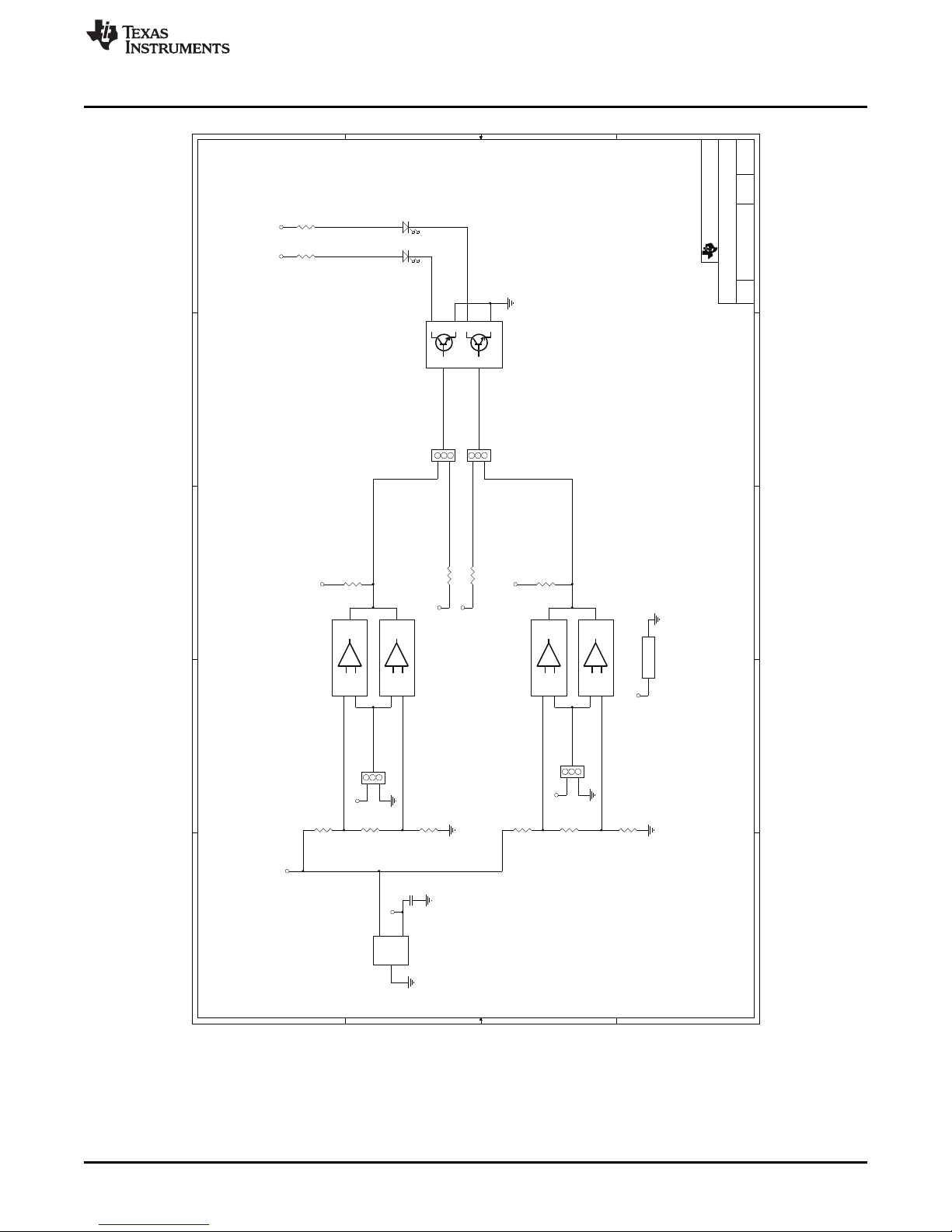

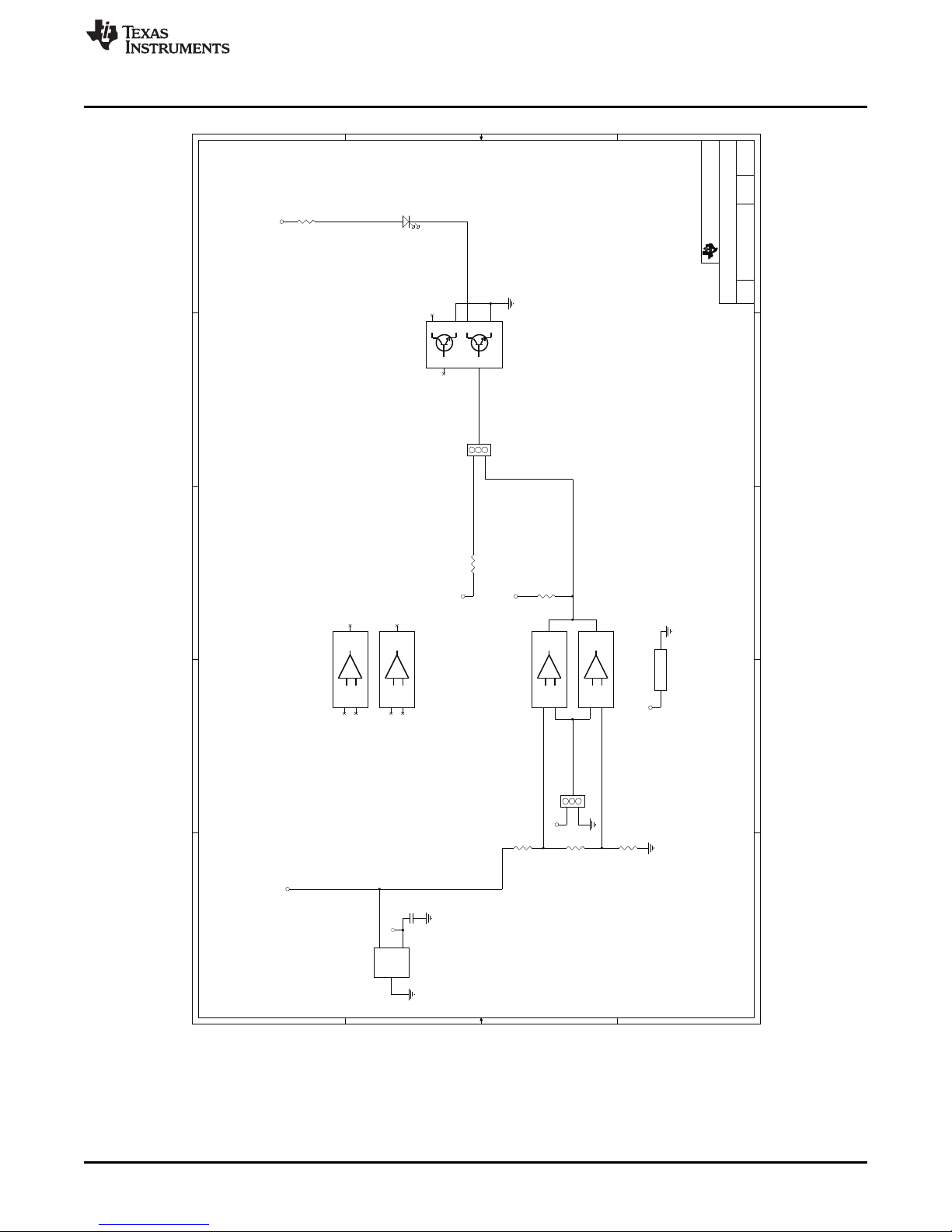

18 Cover Page and Index, Sheet 1 ........................................................................................ 26

19 Device Power and Ground, Sheet 2 .................................................................................... 27

20 Global Signals, Sheet 3................................................................................................... 28

21 High-Speed Differential, Sheet 4........................................................................................ 29

22 Reference and Output Clocks, Sheet 5 ................................................................................ 30

23 JTAG, SPI, I2C, STCI, and MDIO, Sheet 6............................................................................ 31

24 TD and RD Parallel Data Lines, Sheet 7............................................................................... 32

25 TX/RX Clocks and A and B Control, Sheet 8.......................................................................... 33

26 PRBS Pass/Fail LEDs, Sheet 9 ......................................................................................... 34

27 1p0V Power Regulator, Sheet 10 ....................................................................................... 35

28 1p2V Power Regulator, Sheet 11 ....................................................................................... 36

29 1p5V Power Regulator, Sheet 12 ....................................................................................... 37

30 1p8V Power Regulator, Sheet 13 ....................................................................................... 38

31 2p5V Power Regulator, Sheet 14 ....................................................................................... 39

32 3p3V Power Regulator, Sheet 15 ....................................................................................... 40

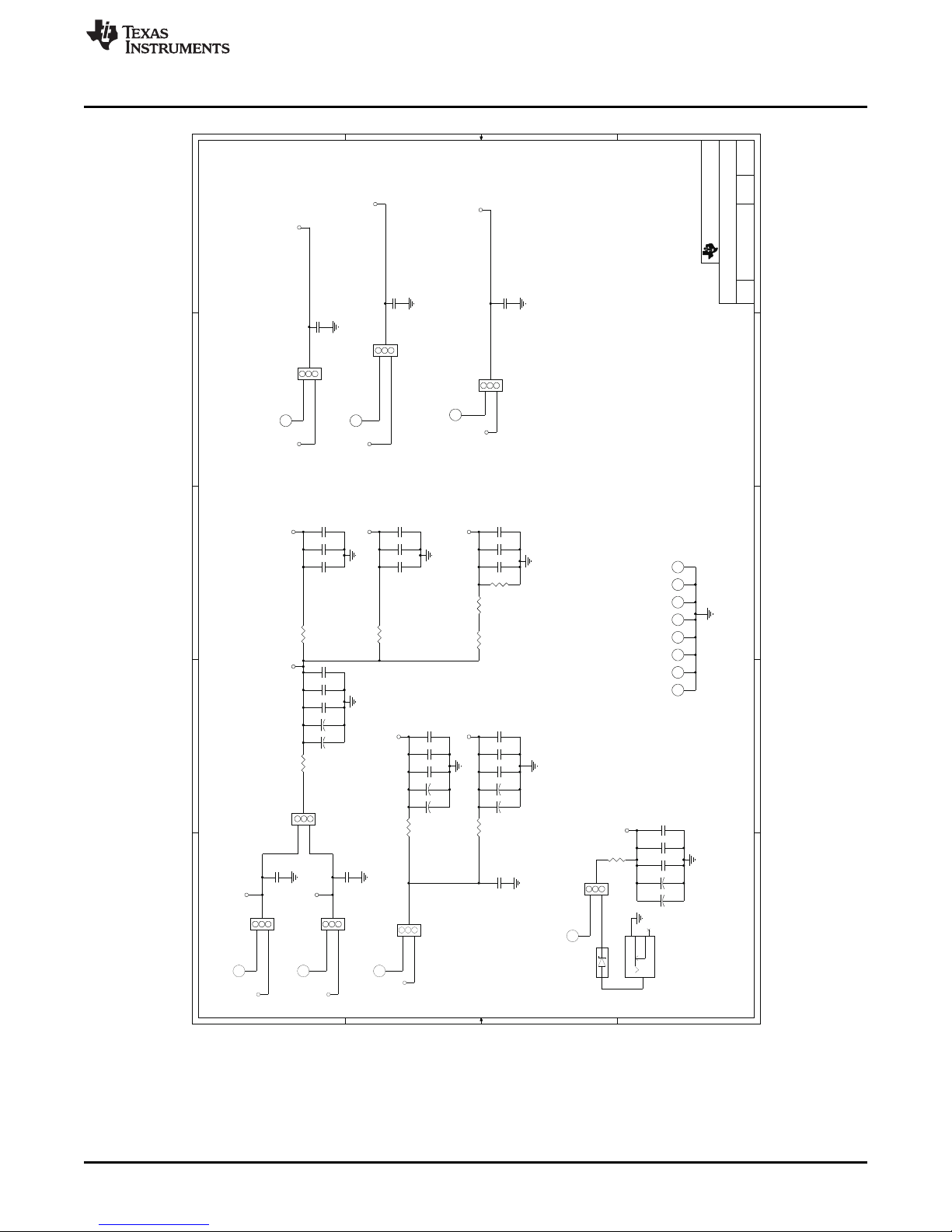

33 Power Regulator Min/Nom/Max Adjustment, Sheet 16............................................................... 41

34 Power Regulator Min/Nom/Max Adjustment LEDs, Sheet 17 ....................................................... 42

35 Power Distribution, Sheet 18............................................................................................. 43

36 1p0V and 1p2V Supply LEDs, Sheet 19 ............................................................................... 44

37 1p5V and 1p8V Supply LEDs, Sheet 20 ............................................................................... 45

38 2p5V, 3p3V, and 5V Supply LEDs, Sheet 21.......................................................................... 46

39 DVDD Supply LEDs, Sheet 22 .......................................................................................... 47

40 1p5/8V Supply LEDs, Sheet 23.......................................................................................... 48

41 VDDRA Supply LEDs, Sheet 24......................................................................................... 49

42 VDDRB Supply LEDs, Sheet 25......................................................................................... 50

43 VREFT Supply LEDs, Sheet 26 ......................................................................................... 51

44 No Connect Pins, Sheet 27 .............................................................................................. 52

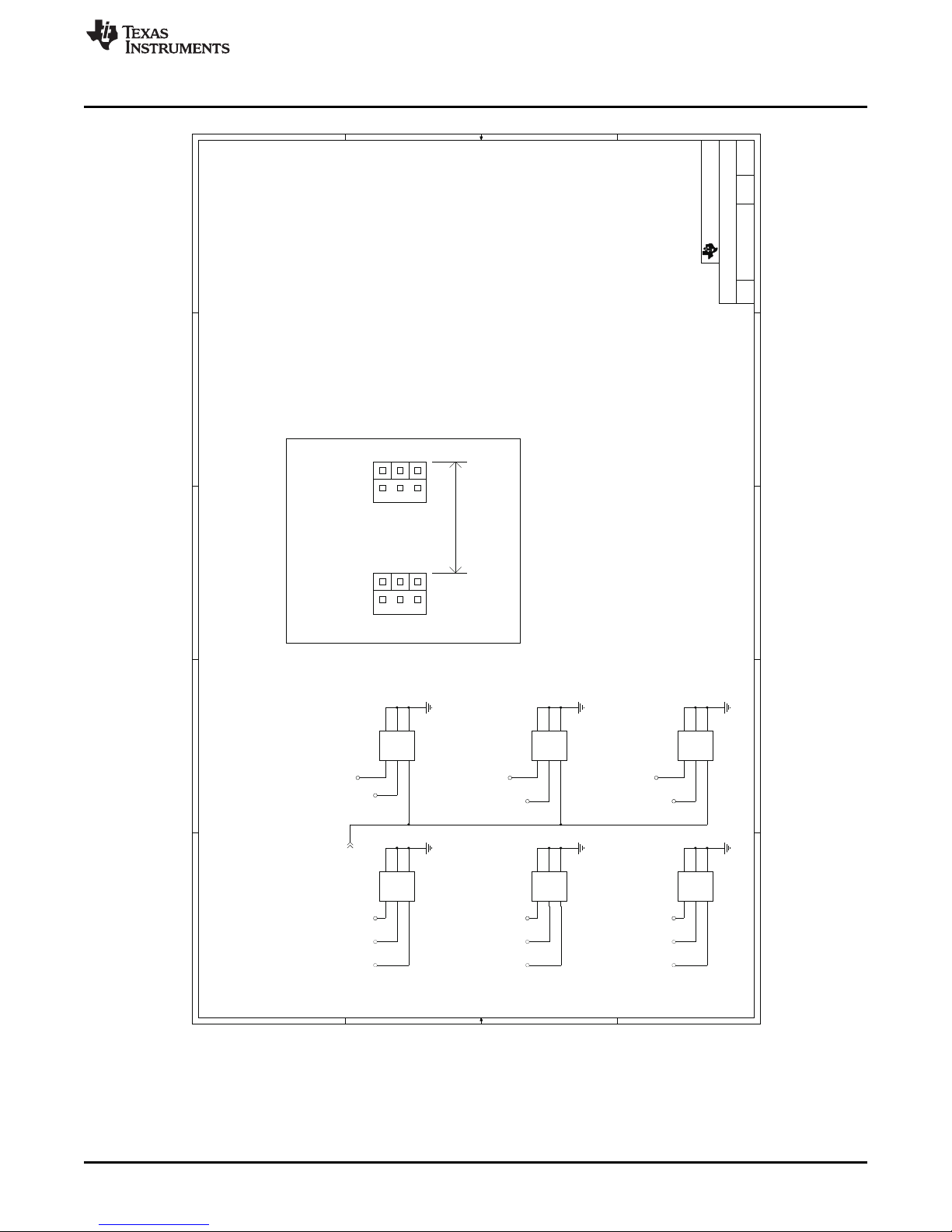

45 Peripheral Ports, Sheet 28 ............................................................................................... 53

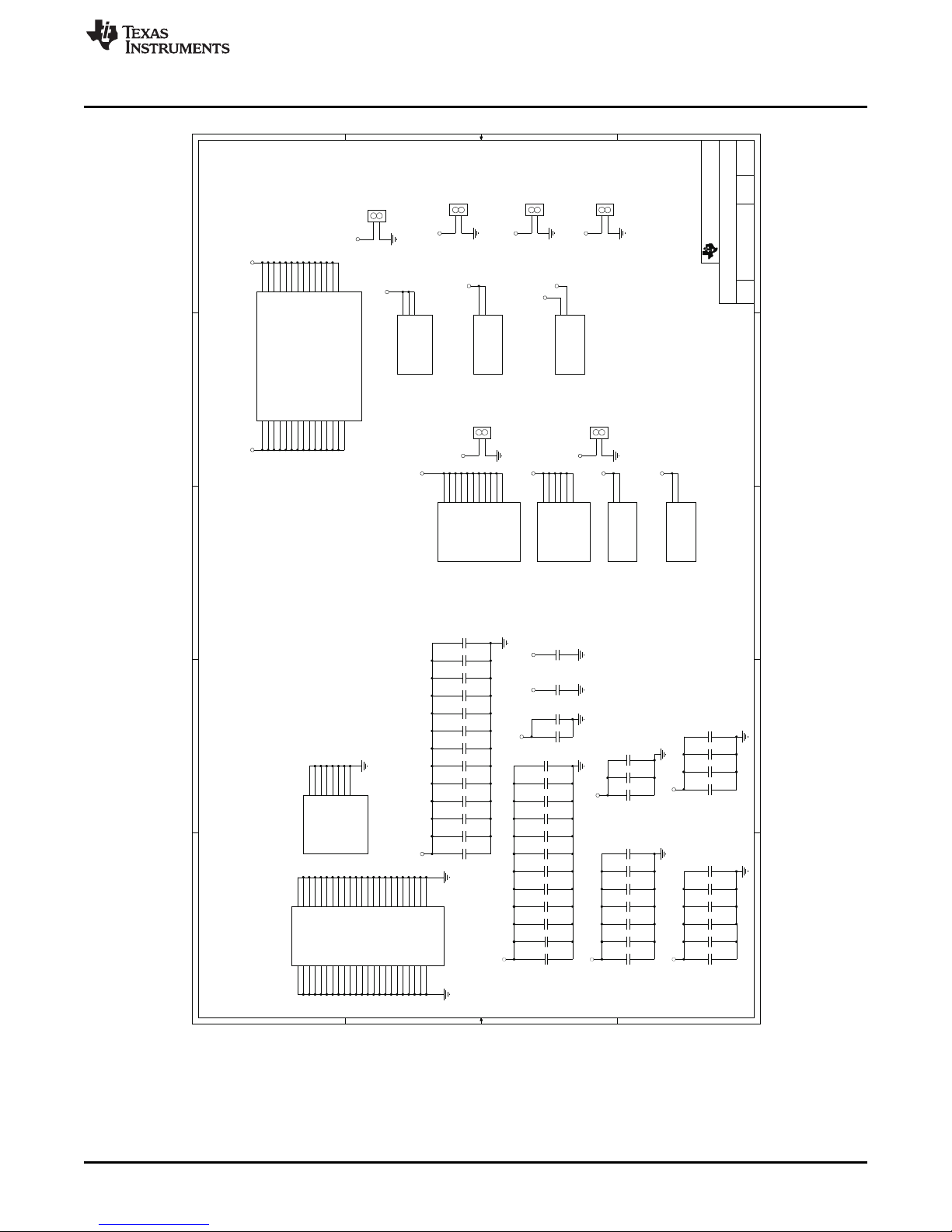

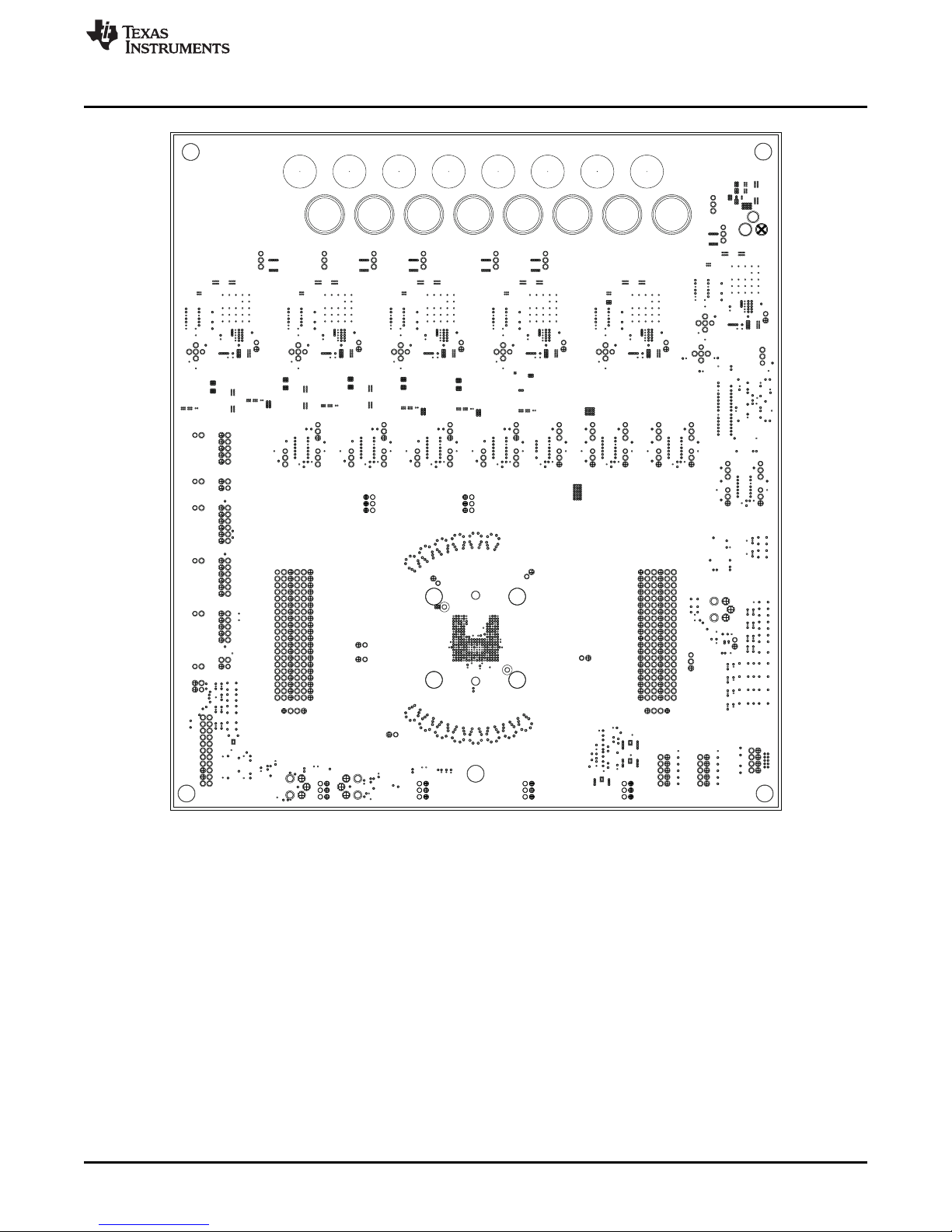

46 Top Signal, Layer 1 ....................................................................................................... 60

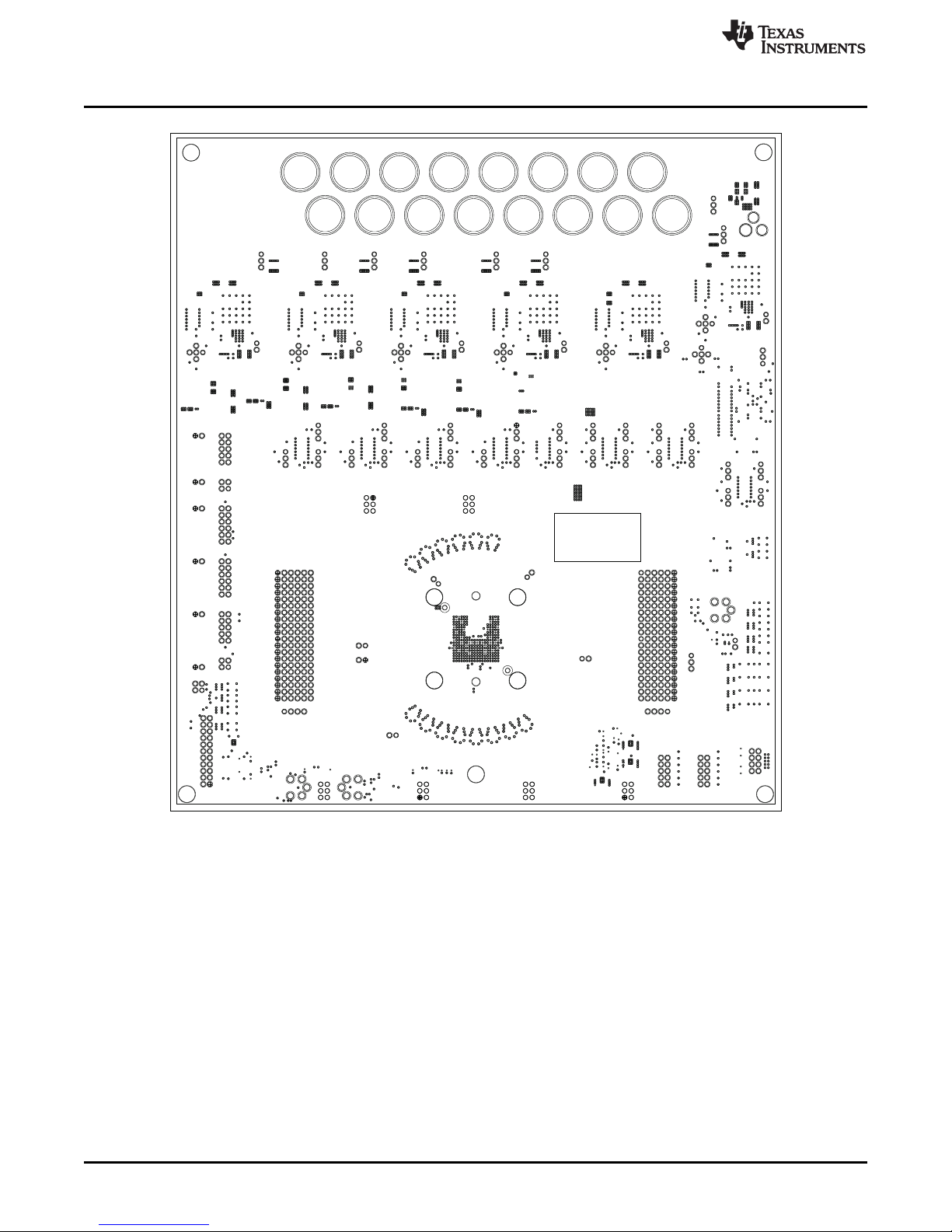

47 Internal Ground, Layers 2,4,6,8,10...................................................................................... 61

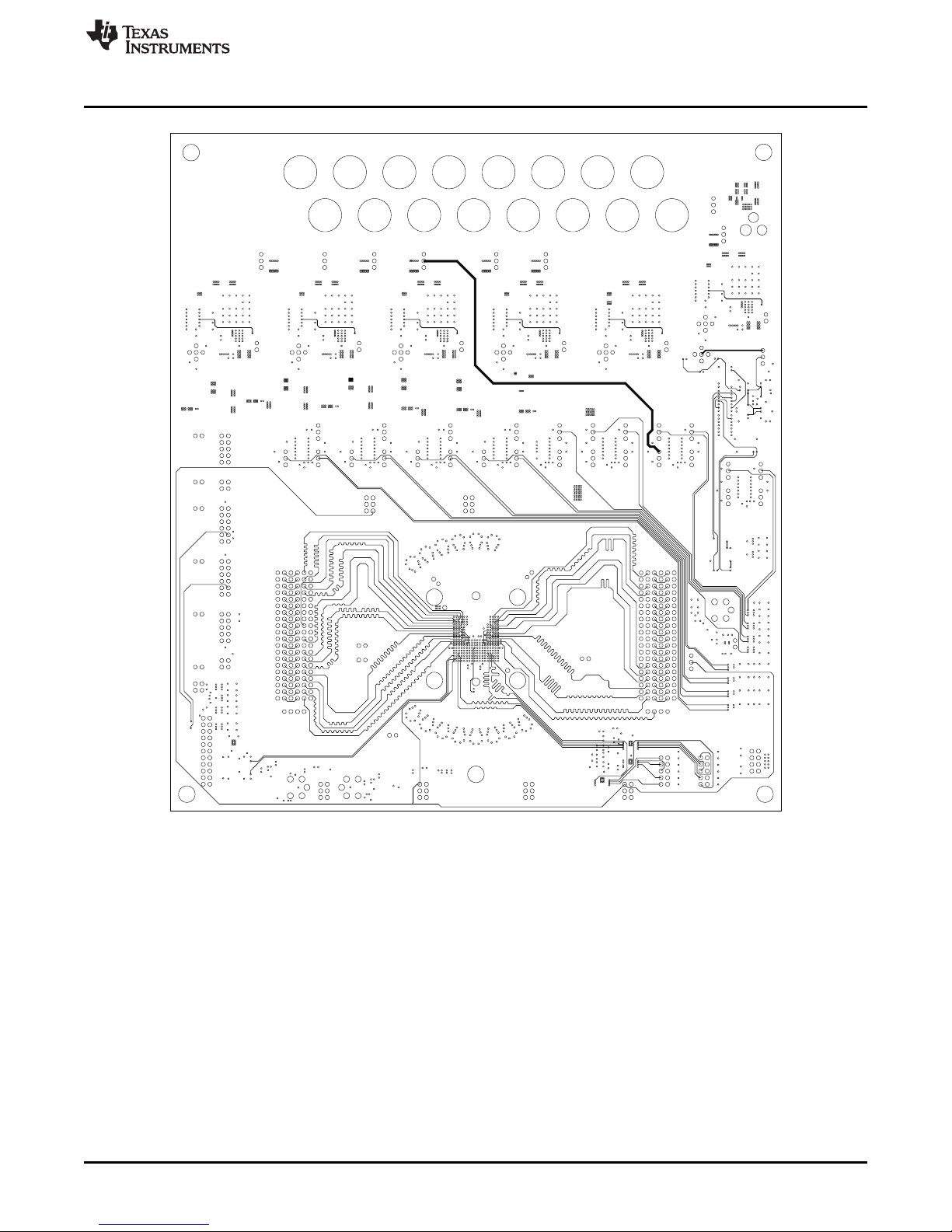

48 Internal Power, Layer 3................................................................................................... 62

49 Internal Signal, Layer 5................................................................................................... 63

50 Internal Signal, Layer 7................................................................................................... 64

51 Internal Power, Layer 9................................................................................................... 65

52 Internal Ground and Power, Layers 11,13,15,17...................................................................... 66

53 Internal Signal, Layer 12.................................................................................................. 67

2

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 3

www.ti.com

54 Internal Signal, Layer 14.................................................................................................. 68

55 Internal Power, Layer 16 ................................................................................................. 69

56 Bottom Signal, Layer 18.................................................................................................. 70

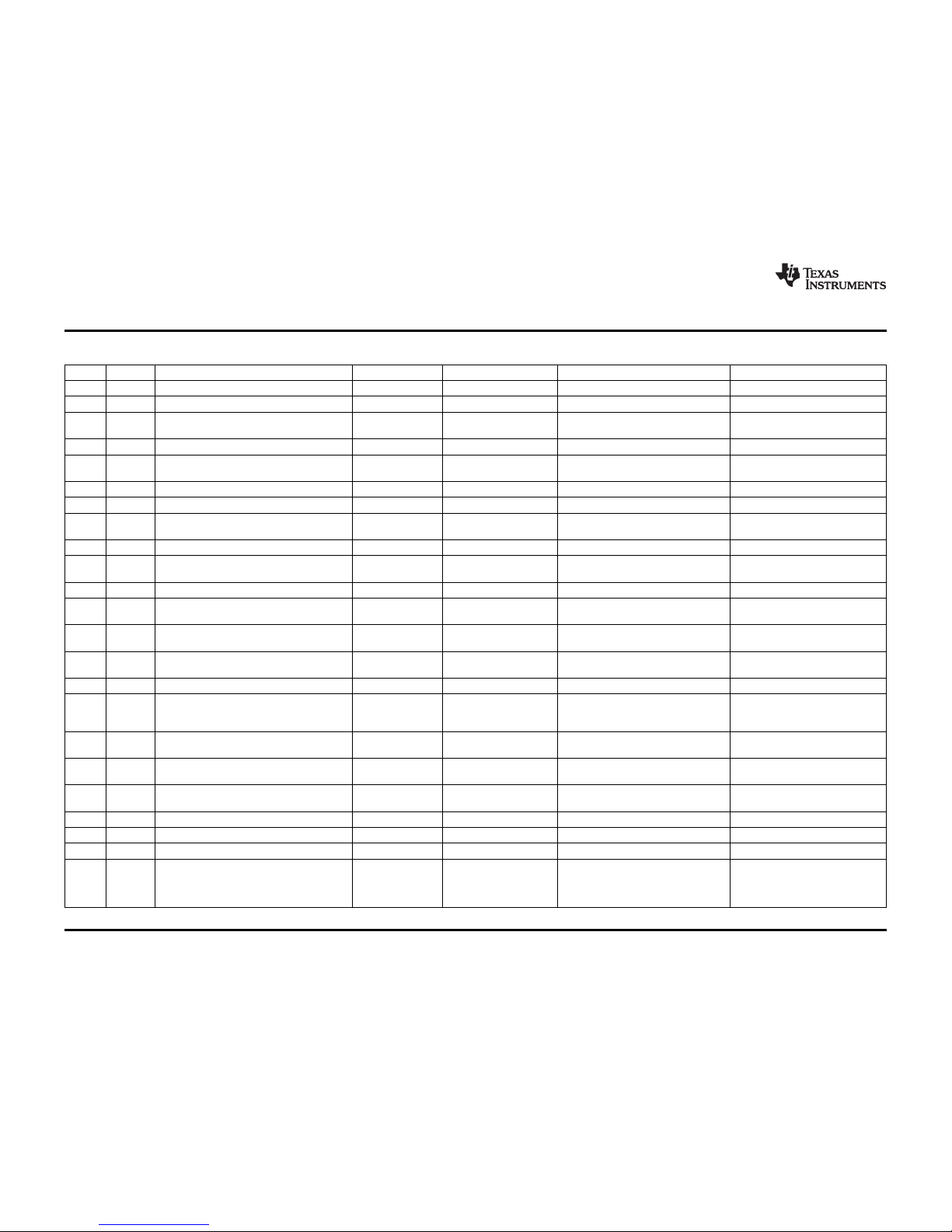

1 Bill of Materials............................................................................................................. 54

2 TLK6002EVM Layer Construction....................................................................................... 71

List of Tables

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Evaluation Module

3

Copyright © 2010, Texas Instruments Incorporated

Page 4

TLK6002

GND GND

GND GND GND GND GND GND

VADJ5V

1P2V

3P3V2P5V1P5V1P8V

1P0V

BANANA JACK BANANA JACKBANANA JACK BANANAJACK BANANA JACK

BJACK

BJACK

P2

P3

P16

P4

P5

P6 P7 P8 P9

P1

P20 P15 P29

P33

P30

P23

5V

PLUG

1P2V

1P2VREG

1P2V

REG

+5V

REG

REG

REG

REGREG

REG

REGREGREG

1P0V

1P0VREG

1P8V

1P5/8V

1P5V

1P8V

1P8VREG 1P5VREG

1P5V 2P5V

3P3V

2P5VREG

3P3VREG

1P0V

REG REG

1P8V 1P5V

2P5V

3P3V

REGEN

MIN

REGEN

REGEN

REGEN

REGEN

REGEN

GND

GND

GND

GND

GNDGND

NOM

MAX

AUTO

(VADJ)

ADJ

MIN

ADJ

NOM AUTO

(VADJ)

MAXMAX

NOM

MIN

ADJ

AUTO

(VADJ)

AUTO

(VADJ)

AUTO

(VADJ)

AUTO

(VADJ)

MAX

NOM

MIN

ADJ

MAX

NOM

MIN

ADJ

MAX

NOM

MIN

ADJ

MAX

(3V)

MIN

(1V)

NOM

(2V)

VADJBJ

ON

VADJ

OFF

(3.8V)

GLOBAL

VOLTAGE

ADJUST

RESISTOR

POWER

RESISTOR

POWER

RESISTOR

POWER

RESISTOR

POWER

RESISTOR

POWER

1P5/8V

1P5/8V

1P5/8V

1P5/8V

1P5/8V

1P5/8V

PRTAD0

PRTAD1

PRTAD2

PRTAD3

PRTAD4

REFCLK ASEL

REFCLKBSEL

RATEA 2

RATEA 1

RATEA 0

CODEA EN

LOSA

PD TRXA

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

RATEB2

RATEB1

RATEB0

CODEBEN

LOSB

PD TRXB

AMUXB

AMUXA

TESTEN

CLKOUTSEL

PRBSEN

GPI1

GPI0

PRBSBFAIL

PRBSBPASS

PRBSB

PRBSA

PRBSA FAIL

PRBSA PASS

A

B

LOSA

LOSB

MDC

MDIO

5V

1P5/8V

PRBSPASS

GND

GND

TXCLKA

RXCLKA

GND

GND

TXCLKB

RXCLKB

SCFG1

SOUT

SIN

SCFG0

SCLK

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

SCL

SDO

SDI

CS

TDI

TDO

TRST

TMS

TCK

GND

GND

GND

GND

GND

GND

1P0V

1P5/8V

DVDD

V

D

D

RA

V

R

E

FT

VDDRB

PLN

LED

MNT

0P75V

0P9V

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PLN

LED

MNT

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

PWR

EN

GND

VREFT

VDDRB

VDDRA

1P5/8V

3P3V2P5V

1P8V

1P5V1P0V1P2VDVDD

1P8V

1P5V

1P8V1P5V

1P5V

1P8V

LEDMONITOR LEDMONITOR

LEDMONITOR

LEDMONITOR

LEDMONITOR

LEDMONITOR

LEDMONITOR

LEDMONITOR

REGULATOR

ADJUST

OFF

MAX

NOM

MIN

MAINRST

RST

RST

MAIN

MANUAL RESET

GND

MAIN

RST BUTTON

RST

GND

5V

3P3V

2P5V

1P8V

1P5V

1P2V

1P0V

DVDD

1P5V

1P8V

1P5V

1P8V

1P5V 1P 8V

0P75V

0P9V

VREFT

VDDRB

VDDRA

1P5/8V

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

TLK6002

EVM

6519192

REVNA

1P5/8V

TDA0..19

TDA0..19

RDA0..19

GND

GND

1P5/8V

TDB0..19

TDB0..19

RDB0..19

GND

GND

MDIO

PRBSA

PRBSB

LATCH LATCH

RESET

RESET

STCI JTAG

SPI

JMP63

JMP59 JMP70 JMP58 JMP85 JMP149

JMP81

C187

C188

C189

P2

JMP89

U69

U12

JMP53

R106

C109

C108

R105

C107

JMP52

JMP56

R149

R150

R159

R152

R155

R162

U20

R158

R161

R139

R141

R142

R140

U16

R144

R143

R148

R145

R151

R153

JMP105

JMP104

JMP103

JMP102

U31

D5

D6

D7

D8

D16

D15

D14

D13

D12

D10

D11

D20

D22

D32

D34

D38

D37

D33

D31

D21

JMP15

SW1

D1

D2

JMP14

JMP39

JMP40

JMP146

JMP45

JMP35

JMP36

SW4

SW3

JMP145

JMP38

JMP37

V18V1

A18

A1A1

U1

JMP30

D41

D42

D4

D3

D52

D51

D50

D49

JMP43

JMP23

JMP21

JMP17

JMP16

JMP27

JMP25

JMP26

JMP24

JMP29

JMP28

JMP33

JMP31

C136

C139

C138

C135

C116

C115

C169

C170

C171

JMP57

C137

JMP55

U14

U13

R123

R122

C114

R124

JMP54

JMP51

R89

R88

C102

C101

C100

JMP50

R90

U10

JMP49

R72

R71

C93

C95

C94

JMP48

R73

U8

JMP47

R55

R54

C86

C87

C88

JMP46

R56

U6

U67

JMP148

R363

R362

C234

C236

C235

R364

JMP147

U70

U7

U9

U11

JMP138

U64

C168

JMP139

JMP140

C167

C141

C142

C145

C144

C143

JMP132

JMP134

U58

JMP133

C125

C126

C127

JMP129

U55

JMP130

JMP131

JMP114

C131

C132

C133

C158

C159

C160

JMP115

JMP116

U40

U37

JMP113

JMP112

JMP95

JMP94

U25

JMP96

JMP97

JMP98

JMP99

U28

JMP100

JMP101

R107

JMP7

JMP4

J

MP8

JMP6

JMP1

JMP3

T

X

A

N

TX

A

P

R

X

A

N

R

X

A

P

RXBP

R

X

B

N

T

X

B

P

T

X

B

N

C

L

K

1

N

R

E

F

C

L

K

1

P

R

E

F

C

L

K

0

N

R

E

F

C

L

K

0

P

R

E

F

O

U

T

N

C

L

O

C

K

O

U

T

P

C

L

O

C

K

J

1

0

J9

J

1

1

J

1

2

J

1

4

J

1

3

J

7

J

5

J

8

J6

J

2

J

4

J

1

J

3

Introduction

1 Introduction

www.ti.com

4

The Texas Instruments TLK6002 SERDES evaluation module (EVM) board is used to evaluate the

functionality and the performance of the TLK6002 Dual-Channel, Multi-Rate Transceiver device in a

324-ball PBGA package. The TLK6002 is a multi-gigabit transceiver intended for use in ultra-high-speed

bidirectional point-to-point data transmission systems such as base station RRH (Remote Radio Head)

applications as well as any other high-speed application. All CPRI and OBSAI data rates of 0.6144, 0.768,

1.2288, 1.536, 2.4576, 3.072, 4.9152, and 6.144 Gbps are supported using a single, fixed-reference clock

frequency of either 122.88 MHz or 153.6 MHz. Non-CPRI or OBSAI serial data rates between 0.470 Gbps

and 6.25 Gbps are also supported. Each channel of the TLK6002 can be operated from a single,

shared-reference clock or independently from separate reference clocks at different frequencies. A

CIPRI/OBSAI Automated Rate Sense (ARS) Function has been included to help facilitate the

determination of the incoming CPRI/OBSAI serial link rate per channel.

Other features of the TLK6002 include an integrated Latency Measurement function, PRBS (27-1), (223-1),

(231-1), and High, Low, and Mixed CRPAT Generation and Verification for self-test, system-level support.

Programmable Serial Side output swing and Serial Side Dual Tap Transmit De-emphasis as well as

Receive Adaptive Equalization allow extended backplane reach and transmission line optimization.

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 5

www.ti.com

EVM PCB and High-Speed Design Considerations

SERDES operation and 8B/10B Encoding and Decoding for 20-bit and 16-bit plus control bits are

supported allowing use of a lower cost FPGA solution compared to a FPGA with integrated high-speed

transceivers and built-in SERDES functionality. Latency/depth configurable transmit and receive FIFOs

and loss of signal (LOS) detection of ≤ 75 mVdfpp are just a few of the other features supported in this

device.

Configuration of the TLK6002 on a per-channel basis is available by way of accessing a register space of

control bits available through a two-wire access port called the Management Data Input/Output (MDIO)

interface as defined in Clause 22 of the IEEE 802.3 Ethernet Specification.

(1)

The TLK6002EVM board can be run from a single, 5-V power supply or 5-Vdc transformer. All voltages

needed are regulated down through onboard LDO regulators which can be adjusted to the appropriate

minimum, nominal, and maximum values through a single jumper location.

Voltage monitor circuits with LEDs are included on all voltage rails for easy debugging and identification of

valid power rails.

All data I/O signals are broken out to connectors for easy and rapid prototyping. All control signals are

easily controlled through shunts on header blocks.

PRBS latch circuits have been added to aid in PRBS BER tests.

The EVM board functionality can be easily expanded through the use of the three peripheral ports. Optical

modules, clock oscillator generators, and FPGAs are just a few possible uses for these ports.

2 EVM PCB and High-Speed Design Considerations

The board can be used to evaluate device parameters in addition to acting as a guide for high-speed

board layout. As the frequency of operation increases, the board designer must take special care to

ensure that the highest signal integrity is maintained. To achieve this, the board's impedance is controlled

to 50 Ω for both the high-speed differential serial and low-speed parallel data and clock connections. Vias

are minimized and, when necessary, are designed to minimize impedance discontinuities along the

transmission line. Because the board contains both serial and parallel transmission lines, care was taken

also to control trace length mismatch (board skew) to less than ±0.5 mil.

Overall, the board layout is designed and optimized to support high-speed operation. Thus, understanding

impedance control and transmission line effects are crucial when designing high-speed boards. Some of

the advanced features offered by this board include:

• PCB (printed-circuit board) is designed for optimal high-speed signal integrity.

• SMP and parallel header fixtures are easily connected to test equipment.

• All input/output signals are accessible for rapid prototyping.

• The entire board can be powered from a single, 5-V power supply where the power planes can be

supplied through onboard regulators or through separate banana jacks for isolation.

• Onboard capacitors provide ac coupling of high-speed transmit and receive signals.

• External parallel loop-back function can be achieved easily using simple 0.1-inch jumpers.

• Entire board can operate from a single 5-V power supply or from individual power supplies.

• Voltage monitoring LED circuits provide quick indication that the voltage is within specification.

(1)

The MDIO register map is located within the TLK6002, Dual-Channel 0.47Gbps to 6.25Gbps Multi-Rate Transceiver data sheet.

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Evaluation Module

5

Copyright © 2010, Texas Instruments Incorporated

Page 6

BANANA JACK BANANA JACKBANANA JACK

BANANA JACK BANANA JACK

BJACK

BJACK

5V

PLUG

1P2V

1P2VREG

1 P0V

1 P0VREG

1P8V

1P8VREG 1P5VREG

1P5V

2P5V

3P3V

2P5VREG

3P3VREG

JMP63

JMP70 JMP58

JMP85 JMP149

JMP81

JMP89

BANANA JACK

SELECTED

REGULATOR

SELECTED

REGULATOR

SELECTED

BANANA JACK

SELECTED

REGULATOR

SELECTED

REGULATOR

SELECTED

THESUPPLIED 5V

DC TRANSFORMER

TLK6002 EVM Kit Contents

3 TLK6002 EVM Kit Contents

The TLK6002 EVM kit contains the following:

• TLK6002 EVM board

• TLK6002 EVM User’s Guide (this document)

• TLK6002, Dual-Channel 0.47-Gbps to 6.25-Gbps Multi-Rate Transceiver data sheet

• MDIO Interface EVM

• MDIO Interface EVM documentation

• RS-232 cable

• 20-conductor MDIO ribbon cable

• CD-ROM containing MDIO Sonic Software and User Guides

• 14 3-foot SMA-to-SMP cables

• 4 1-foot SMP-to-SMP cables

• 5-Vdc transformer power supply

4 Power

The TLK6002EVM can be operated off of a single 5-V power supply using the onboard linear dropout

voltage regulators to generate the voltages required to correctly operate the TLK6002, 1-V, 1.5-V, and

1.8-V power rails. Additional 1.2-V, 2.5-V, and 3.3-V supplies have been added to support additional

circuitry on the EVM board and to provide voltage to the peripheral ports to minimize the amount of power

circuitry needed on those boards. Banana jacks and selection headers allow external laboratory power

supplies to be used instead of the onboard LDO regulators. The LDO regulators used on the EVM are TI’s

TPS74401 (or TPS74201 depending on available stock at the PCB assembly shop) and are adjustable

using a resistor divider between the output and a feedback pin. Each regulator has been set to provide the

appropriate minimum, nominal, or maximum voltage per the data sheet limits at its output when

appropriately set. However, no sense lines are connected to the plane near the DUT to compensate for

resistive loss through the board. This loss must be less than 5 mV to 10 mV and not affect the operation

of the TLK6002 device. If more information on the use of these regulators is desired, consult the regulator

data sheets found at www.ti.com.

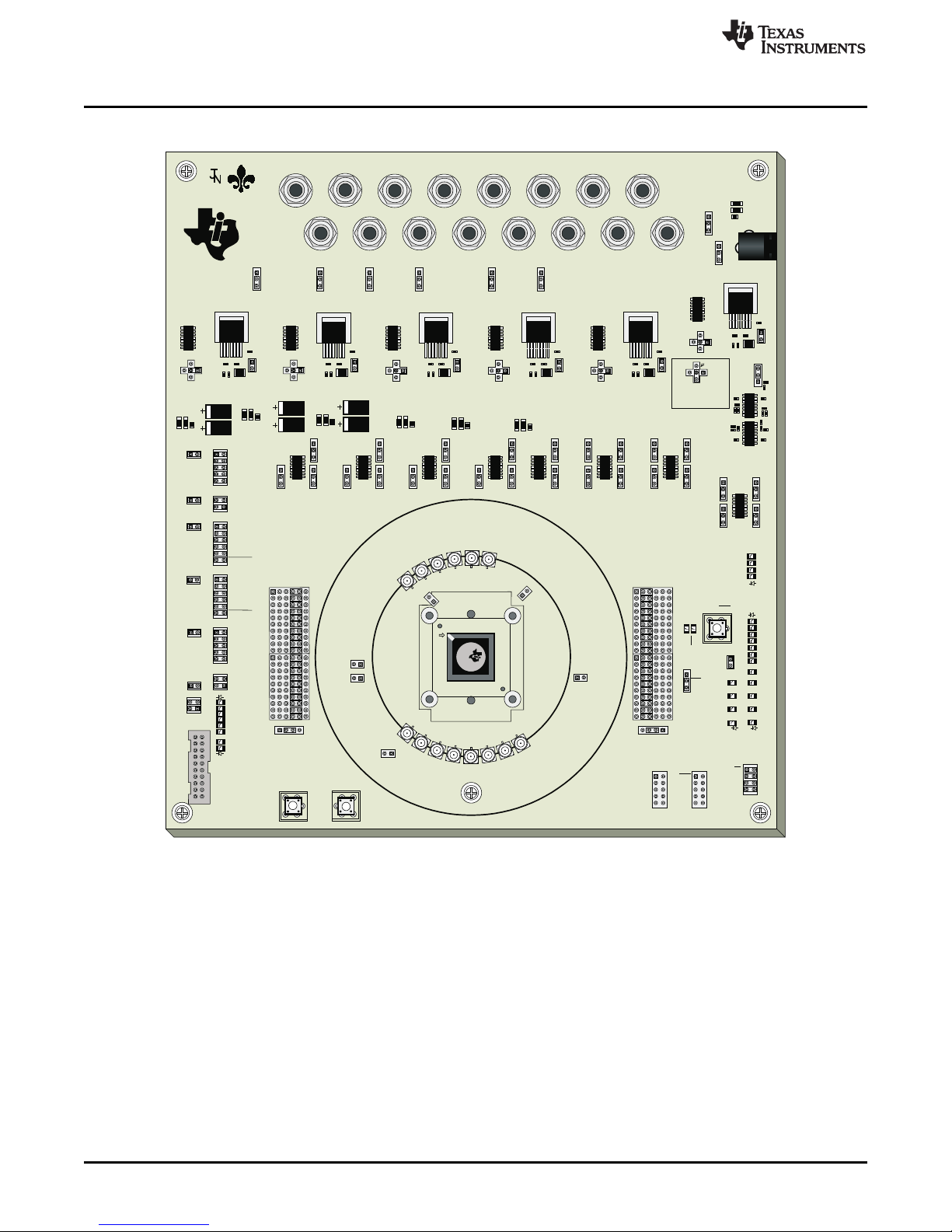

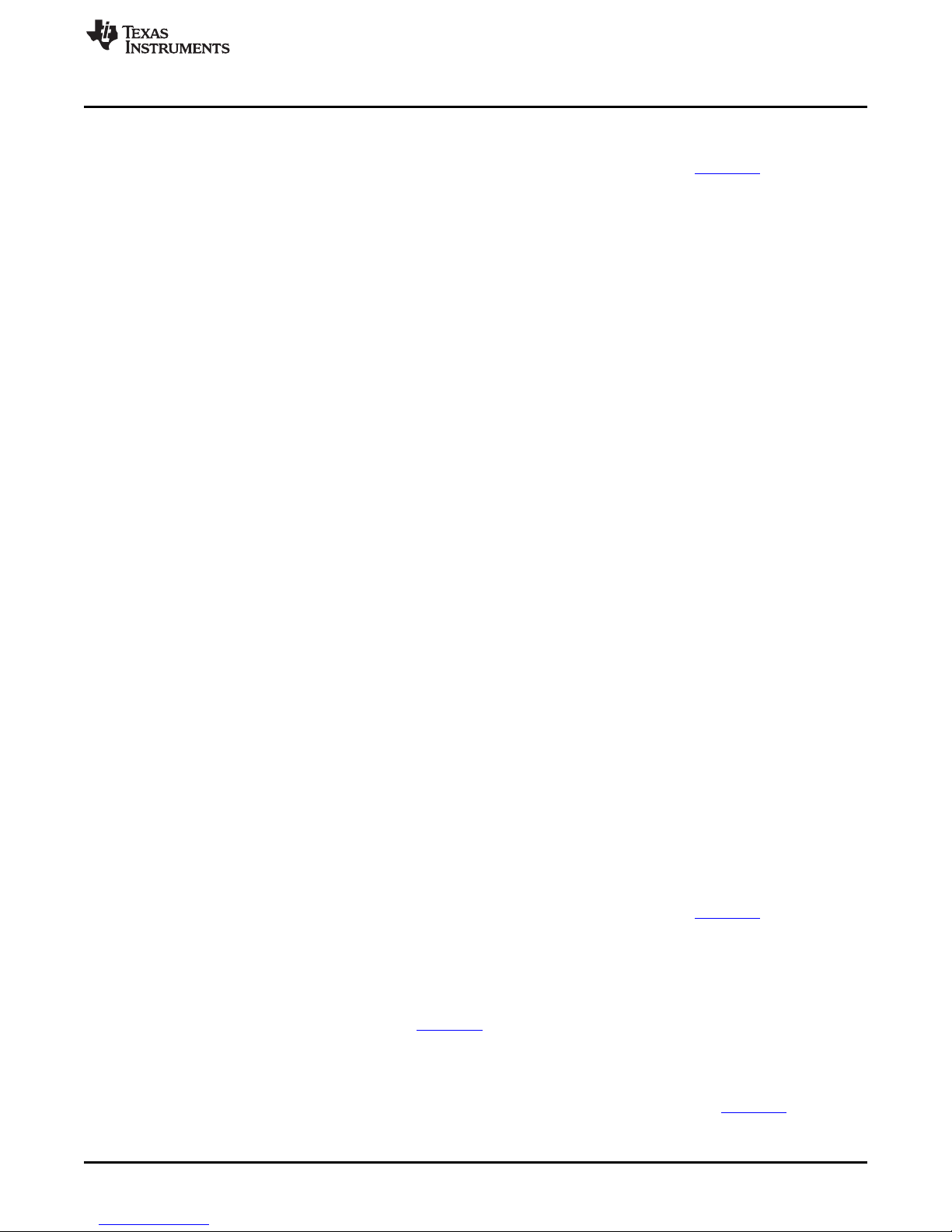

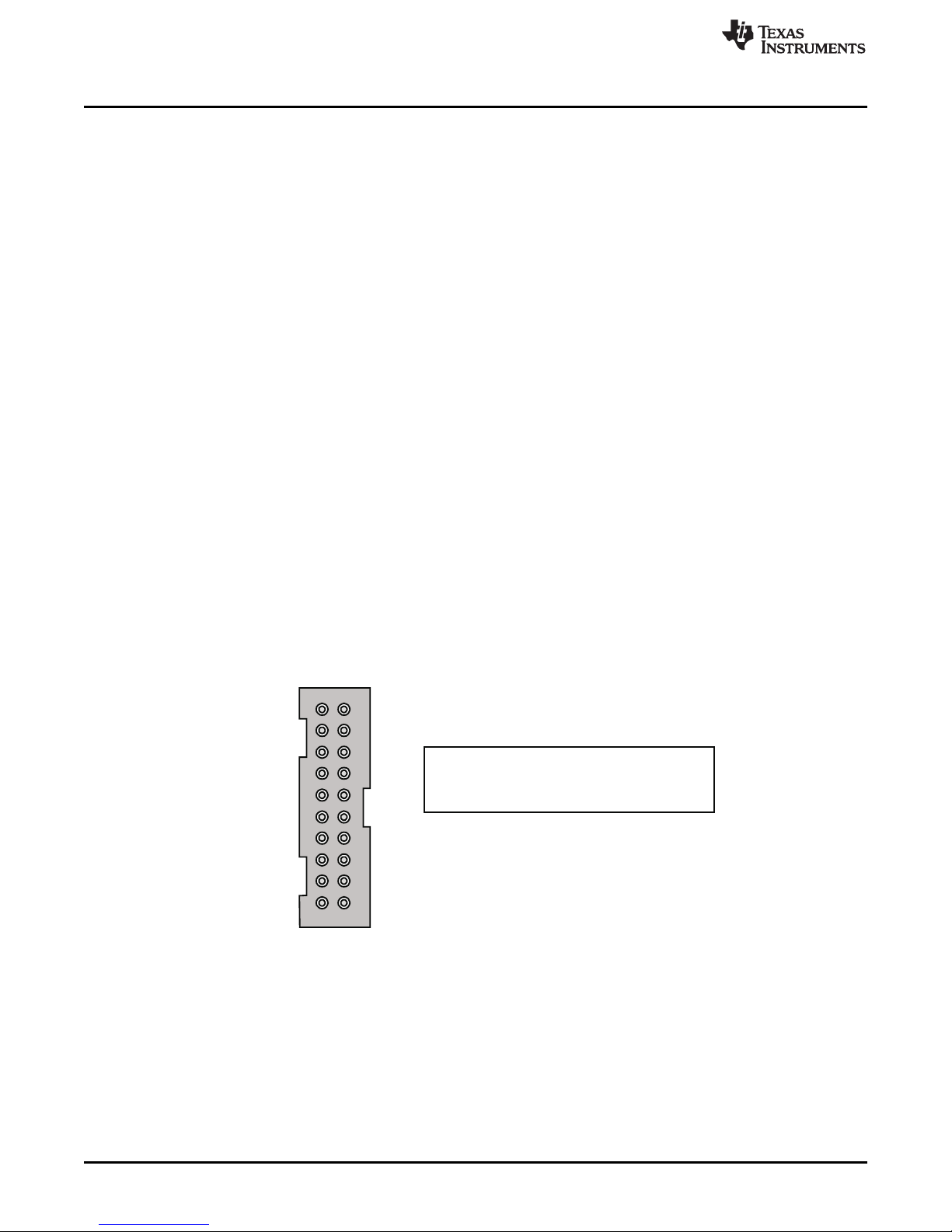

To modify your power supply configuration between either all individual supplies, all onboard regulators, or

a combination of both, simply change the jumper position on the appropriate power supply headers

(JMP58, JMP63, JMP70, JMP85, JMP89, and JMP149) selecting either the BANANA JACK or the REG

pin in combination with the center pin. The following figure shows how to use the onboard regulators for

the 1.2-V, 1.5-V, 1.8-V, 2.5-V, and 3.3-V supply rails, and an individual power supply connected to the 1-V

banana jack (P16) and 2.5-V banana jack (P29). The 5-V power supply is required for operation of the

LEDs on this board even if you are not using the onboard voltage regulators and can be provided from a

laboratory power supply through the banana jack (P1) or through the supplied 5-Vdc transformer. Moving

the jumper location on JMP81 changes the 5-V power supply source from the banana jack or supplied

5-Vdc transformer.

www.ti.com

6

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Figure 1. TLK6002 EVM Power Source Selection Example

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 7

1P8 V

1P5/8 V

1P5 V

JMP59

1.5 VSELECTED AS

THECOMMON

VOLTAGE

REG

AUTO

(VADJ)

MAX

NOM

MIN

ADJ

MINIMUMVOLTAGE

SELECTED

REG

AUTO

(VADJ)

MAX

NOM

MIN

ADJ

MAXIMUMVOLTAGE

SELECTED

REG

AUTO

(VADJ)

MAX

NOM

MIN

ADJ

NOMINAL VOLTAGE

SELECTED

REG

AUTO

(VADJ)

MAX

NOM

MIN

ADJ

COMMONVOLTAGE

CONTROL SELECTED

www.ti.com

Several power supplies such as VDDQA, VDDQB, VDDRA, VDDRB, VDDO1, VDDO2, and VDDO3 can

be operated off of either 1.5 V or 1.8 V depending on your specific setup. The EVM is designed to allow

either of these voltages to be selected for use with the previously mentioned TLK6002 supply rails, but

only allow either 1.5 V or 1.8 V to be selected at a time without some board modifications. Selection

between 1.5 V and 1.8 V is performed by moving the jumper between the center pin and the respective

1p5V and 1p8V pins of JMP59.

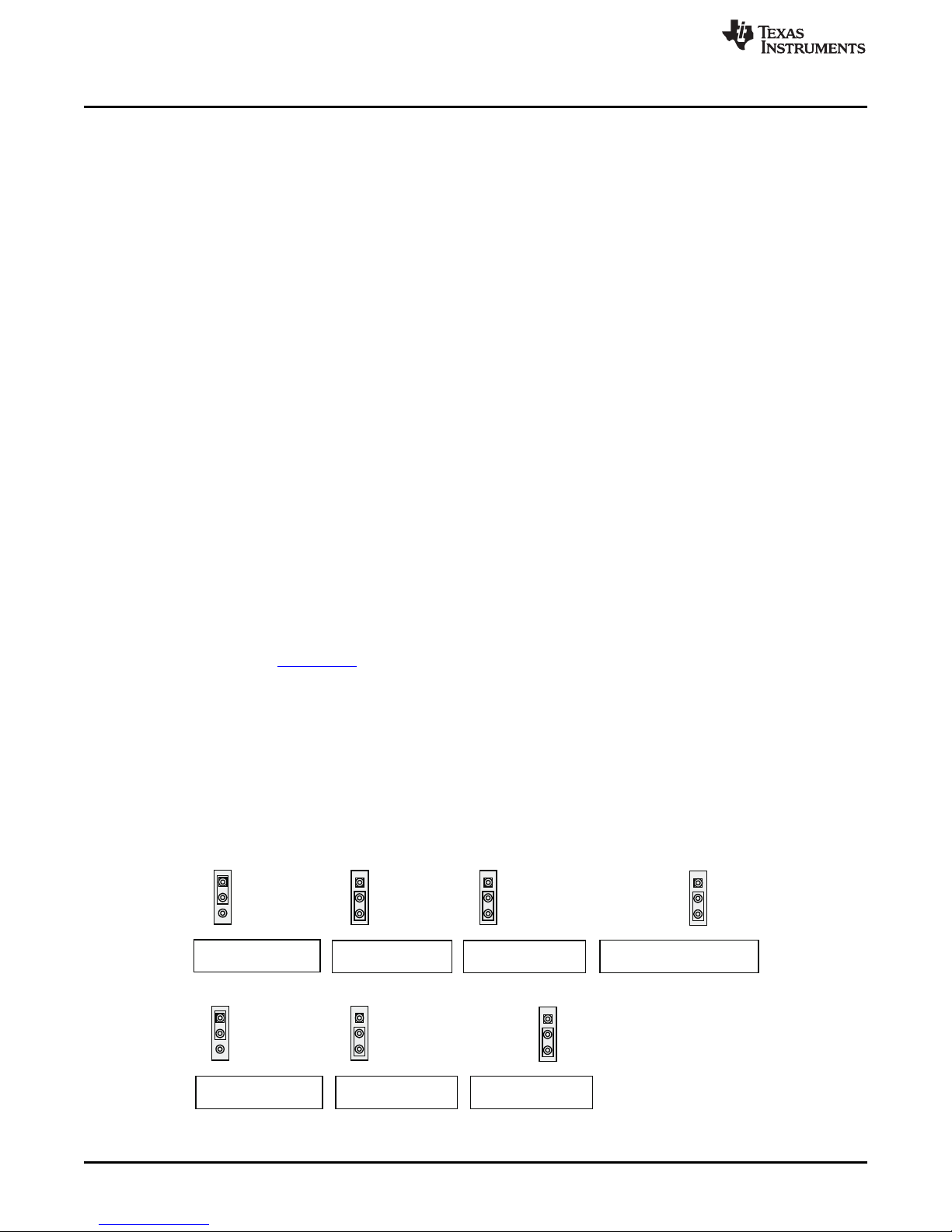

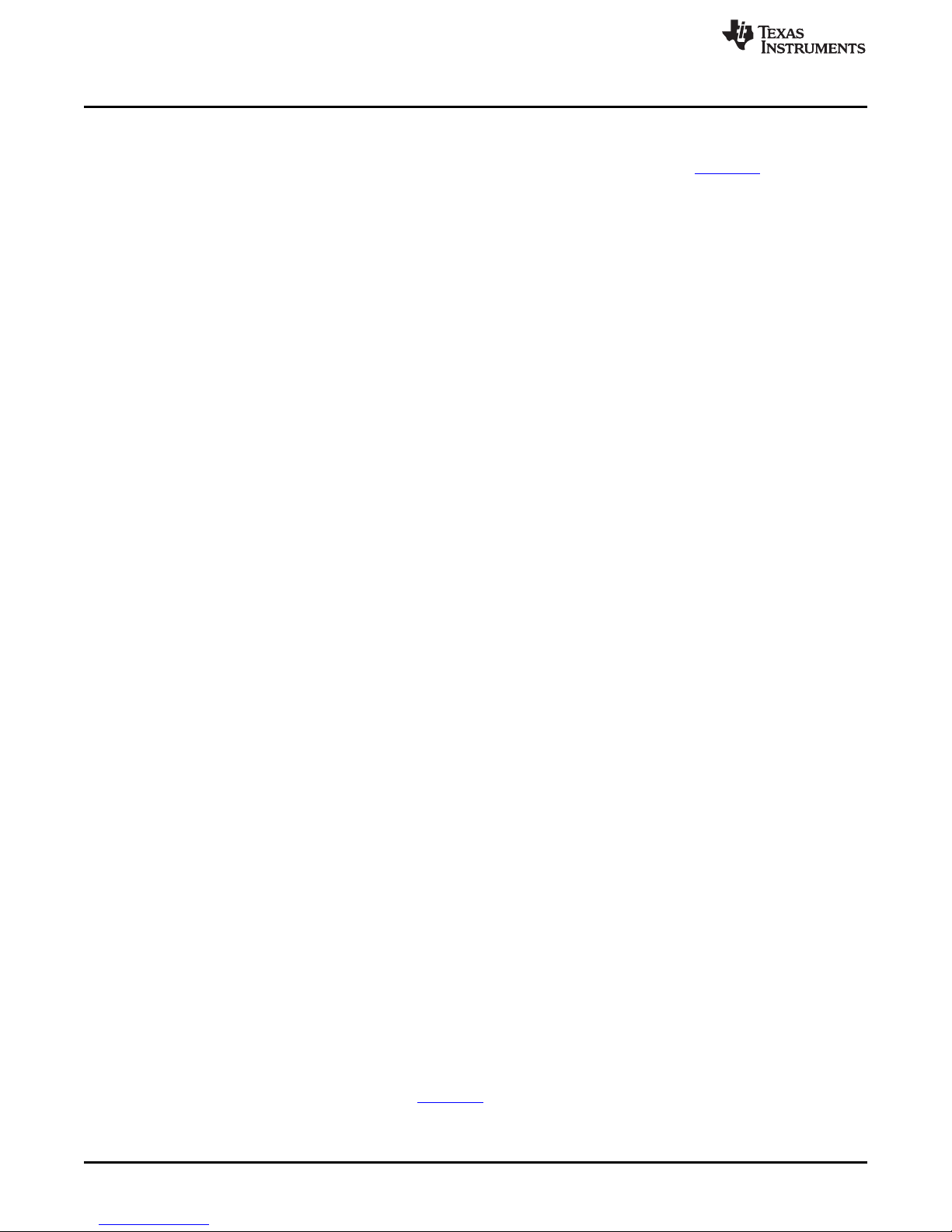

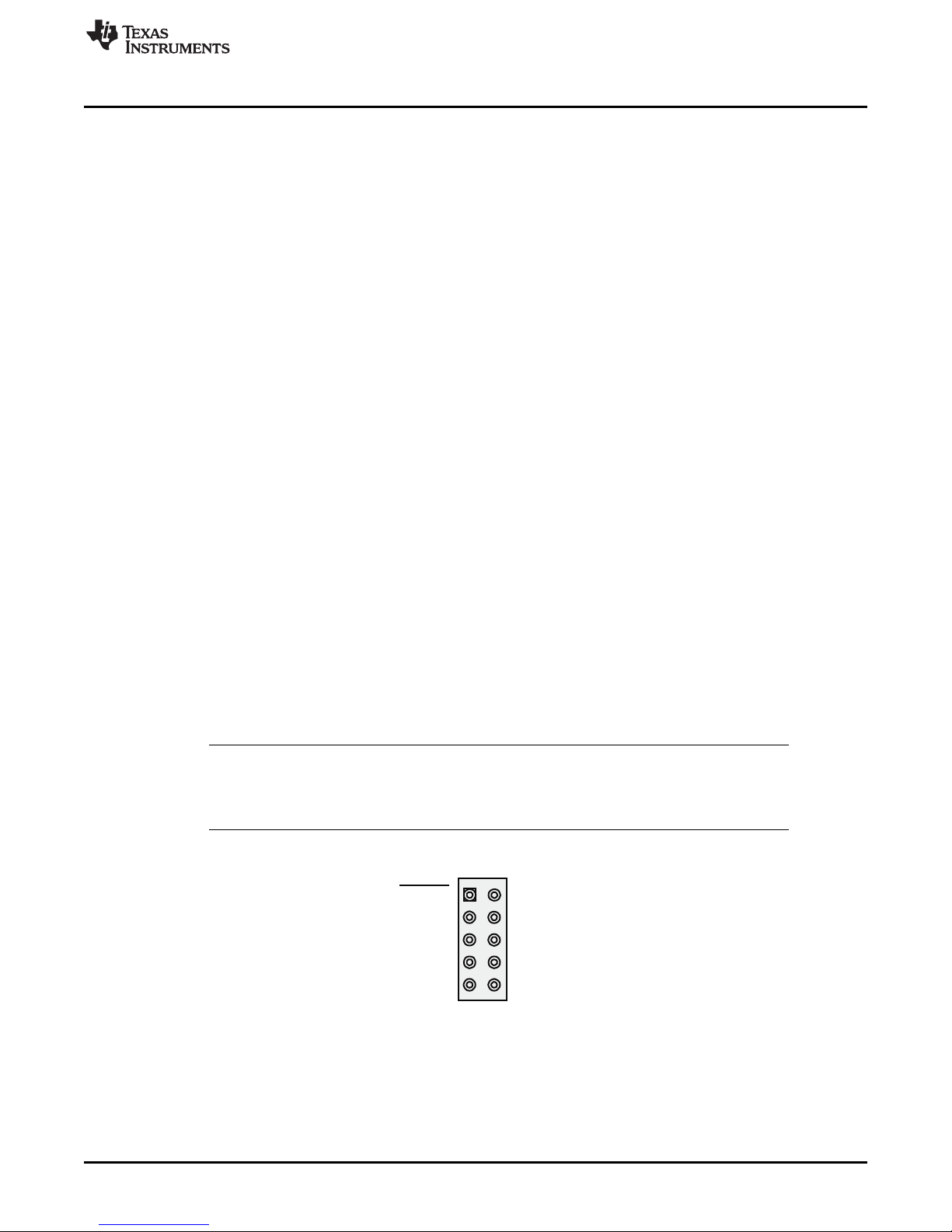

Each TPS74x01 LDO has a voltage margin adjust circuit connected to the voltage adjustment feedback

path to select among the minimum, nominal, and maximum output voltage for that particular voltage node.

To adjust the voltage margin, place the shunt between the center pin of the jumper shaped like a "+"

located next to the regulator and the desired MIN, NOM, or MAX value. A common voltage margin control

circuit is also added that adjusts all the regulators to their minimum, nominal, or maximum values through

a single jumper selection. In order to have the regulator respond to these common control signals, the

selection on the regulator’s margin control header needs to have the center pin and the AUTO pin

selected.

Power

Figure 2. TLK6002 EVM 1p5/8V Voltage Source Selection

Figure 3. TLK6002 EVM Regulator Voltage Margin Selection

The TLK6002EVM comes configured to allow for common voltage margin selection via JMP57, which is

set to a Nominal setting. To globally control the margin of all regulators, place the shunt between the

center pin and the appropriate MIN, NOM, or MAX pins. The adjustment circuit consists of a several

resistor dividers and some voltage window comparator circuits. When the minimum voltage is selected, 1

V is input to the comparator circuit. When the nominal voltage is selected, 2 V is input to the comparator

circuit. When the maximum voltage is selected, 3 V is input to the comparator circuit. The output of the

comparator circuits feeds some digital logic and engages the appropriate FETs located in each of the LDO

feedback adjustment circuits. This output places additional resistors in parallel with the defaulted minimum

value resistors creating the Thevenin equivalent resistance in the feedback voltage divider needed to

adjust the output voltage. Precision 0.1% resistors have been used in these circuits to provide accurate

output voltages, but due to manufacturing tolerances the actual output voltage may be less than 10 mV off

the theoretical and calculated value.

Using this voltage window approach eliminates the need for a programmable device such as a

microcontroller to adjust the LDO margins and allows for easy sweeps using a single shunt or an external

power supply.

A fourth selection on JMP57 labeled VADJ BJ has been added that places the voltage input to the window

comparator circuit that feeds the voltage supplied on the VADJ banana jack (P1) and allows for easy

automated testing sweeps to be performed by controlling this voltage to 1 V, 2 V, and 3 V. The voltage

window limits are set to ±0.25 V with respect to the mentioned control voltages. For example, the

minimum voltage window is 0.75 V to 1.25 V, the nominal voltage window is set to 1.75 V to 2.25 V, and

the maximum voltage window is set to 2.75 V to 3.25 V. If the voltage on the VADJ line does not fall

between one of these valid windows, no FETs is selected in the regulator’s feedback circuit and the

regulator defaults to the minimum output voltage.

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Evaluation Module

7

Page 8

MAX

(3V)

MIN

(1V)

NOM

(2V)

VADJBJ

ON

VADJ

OFF

(3.8V)

GLOBAL

VOLTAGE

ADJUST

JMP56

JMP57

MAX

(3V)

MIN

(1V)

NOM

(2V)

VADJBJ

ON

VADJ

OFF

(3.8V)

GLOBAL

VOLTAGE

ADJUST

JMP56

JMP57

MAX

(3V)

MIN

(1V)

NOM

(2V)

VADJBJ

ON

VADJ

OFF

(3.8V)

GLOBAL

VOLTAGE

ADJUST

JMP56

JMP57

MINIMUMVOLTAGE

SELECTED

NOMINAL VOLTAGE

SELECTED

MAXIMUMVOLTAGE

SELECTED

MAX

(3V)

MIN

(1V)

NOM

(2V)

VADJBJ

ON

VADJ

OFF

(3.8V)

GLOBAL

VOLTAGE

ADJUST

JMP56

JMP57

VADJBANANA JACK

SELECTED

MAX

(3V)

MIN

(1V)

NOM

(2V)

VADJBJ

ON

VADJ

OFF

(3.8V)

GLOBAL

VOLTAGE

ADJUST

JMP56

JMP57

REGULATORS

DISABLED

(JMP57 SHUNT

POSITIONIS A

DON’T CARE)

Power

www.ti.com

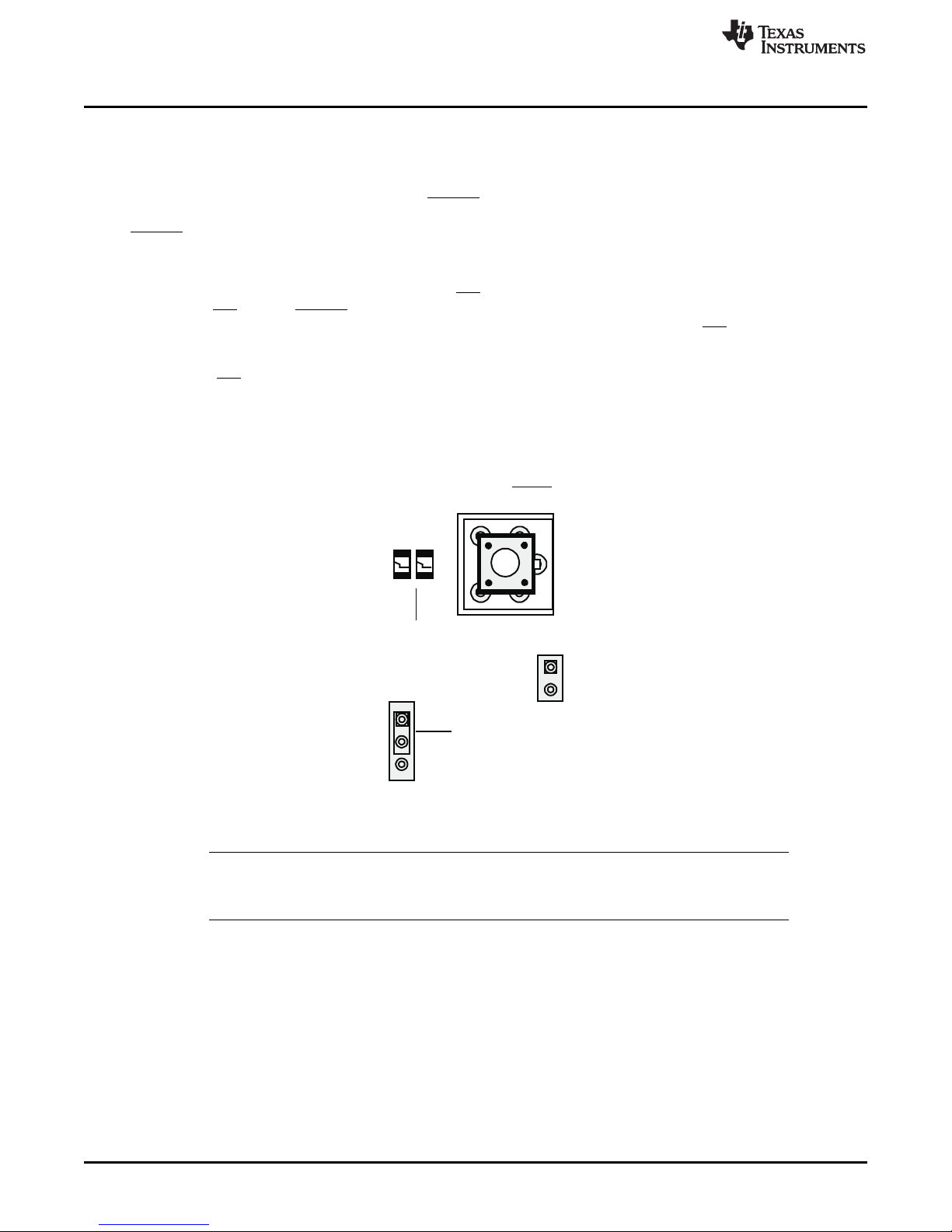

The regulators can also be disabled using this voltage window detect circuit by placing the shunt between

the center pin and the OFF pin of JMP56. This places 3.8 V on the input to the voltage window

comparator circuit which is set for 3.75 to 4.0V and turn on a FET connected to the Enable pin of the

regulators. 3.8V is used because it is within the window and the voltage reference chip used produces a

4.096-V voltage and 4 V may be too close to the high limits established by this reference chip. The

placement of the shunt on JMP57 is irrelevant if the OFF position on JMP56 is selected because it

overrides any min, nom, max setting. See the Power Regulator Min/Nom/Max Adjustment page 16 of the

TLK6002EVM schematics for more information on how this circuitry is connected.

Any combination of local regulator control, global regulator control, and external power supplies can be

implemented through the appropriate configuration of the various headers.

Figure 4. TLK6002 EVM Global Regulator Margin Selection

A large 1210 0-Ω resistor has been installed at the voltage entrance point of each power plane and can be

replaced with a ferrite bead of an appropriate value depending upon the desired data rate if desired. See

the Power Distribution page 18 of the TLK6002EVM schematics for more specific information on how all

the power planes are connected and sourced from either the banana jacks or regulators.

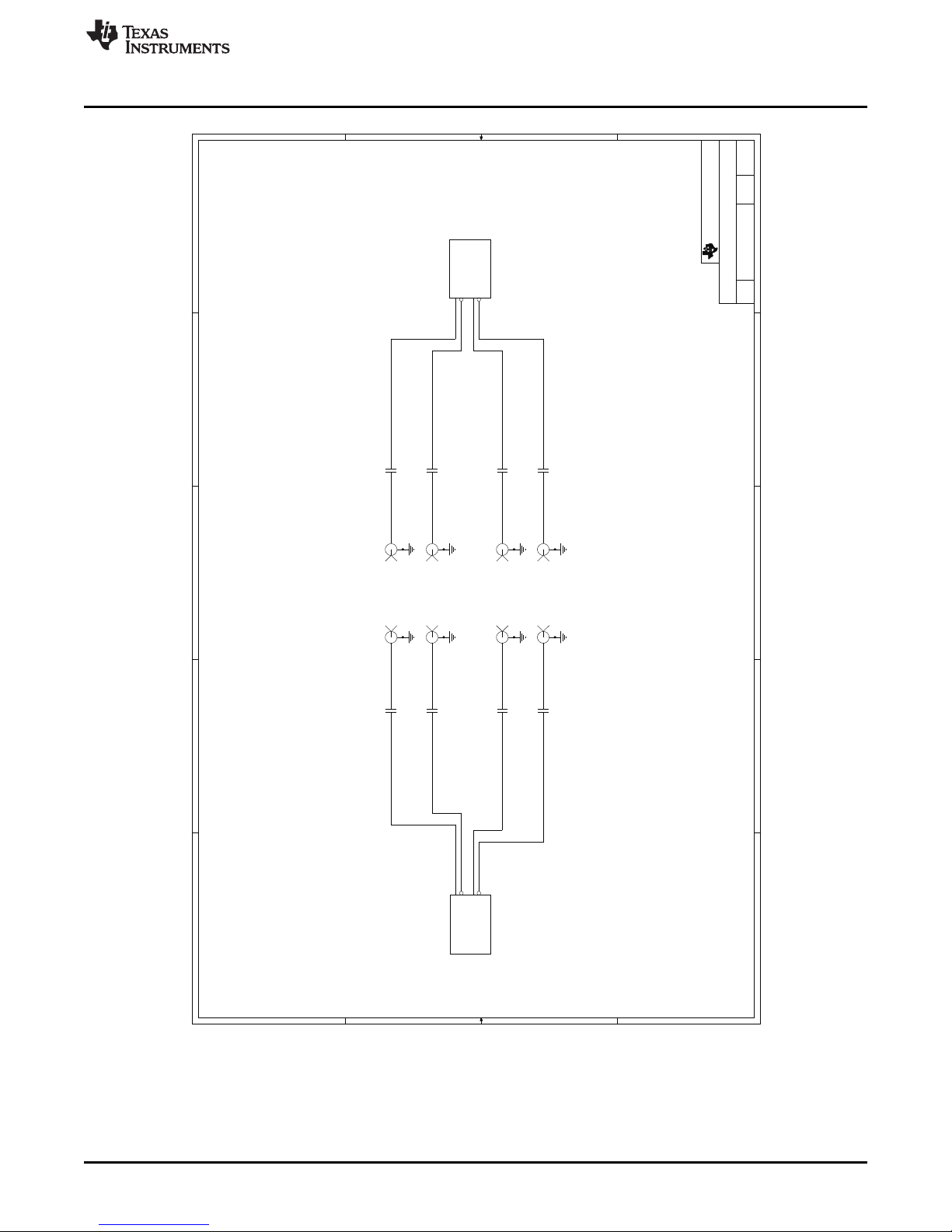

The VREFT plane is sourced through a voltage divider providing half of the voltage on the 1p5/8V plane.

The VDDQA/B, VDDRA/B, and VDDO1/2/3 power pins of the TLK6002 can be operated off of either 1.5 V

or 1.8 V with VREFTA/B being half of whatever voltage is on the VDDQA/B pins which is on the 1p5/8V

plane. The VREFT plane can be powered through the plane monitoring header (JMP4) and removing the

0-Ω resistor (R181), although this is not recommended. A separate VDDRA and VDDRB plane has been

added as no relationship exists between the VDDRA/B pin and the VDDQA/B pins; however, the

VDDRA/B planes are sourced through 0-Ω resistor (R176 and R177) from the voltage on the 1p5/8V plane

that provides power to the VDDQA/B and VDDO1/2/3 pins. These resistors can be replaced with a ferrite

bead or removed completely and an external supply can be connected to the VDDRA header (JMP8) and

VDDRB header (JMP7) in the case different voltages are desired on the two planes.

Furthermore, for more accurate current readings, the PULLUP_EN jumpers on all control pin headers can

be removed, quickly disconnecting the pullup resistors from the voltage plane. However, the removal of

the PULLUP_EN jumpers also requires manual high/low control of every control pins.

8

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 9

PLN

LED

MNT

PLN

LED

MNT

PWR

EN

GND

PWR

EN

GND

1P8V

1P5V

LEDMONITOR

JMP98

JMP

99

U28

JMP

100

JMP101

1P5V AND 1P8VLEDSCONNECTED TO

THEVOLTAGEMONITORINGCIRCUIT

www.ti.com

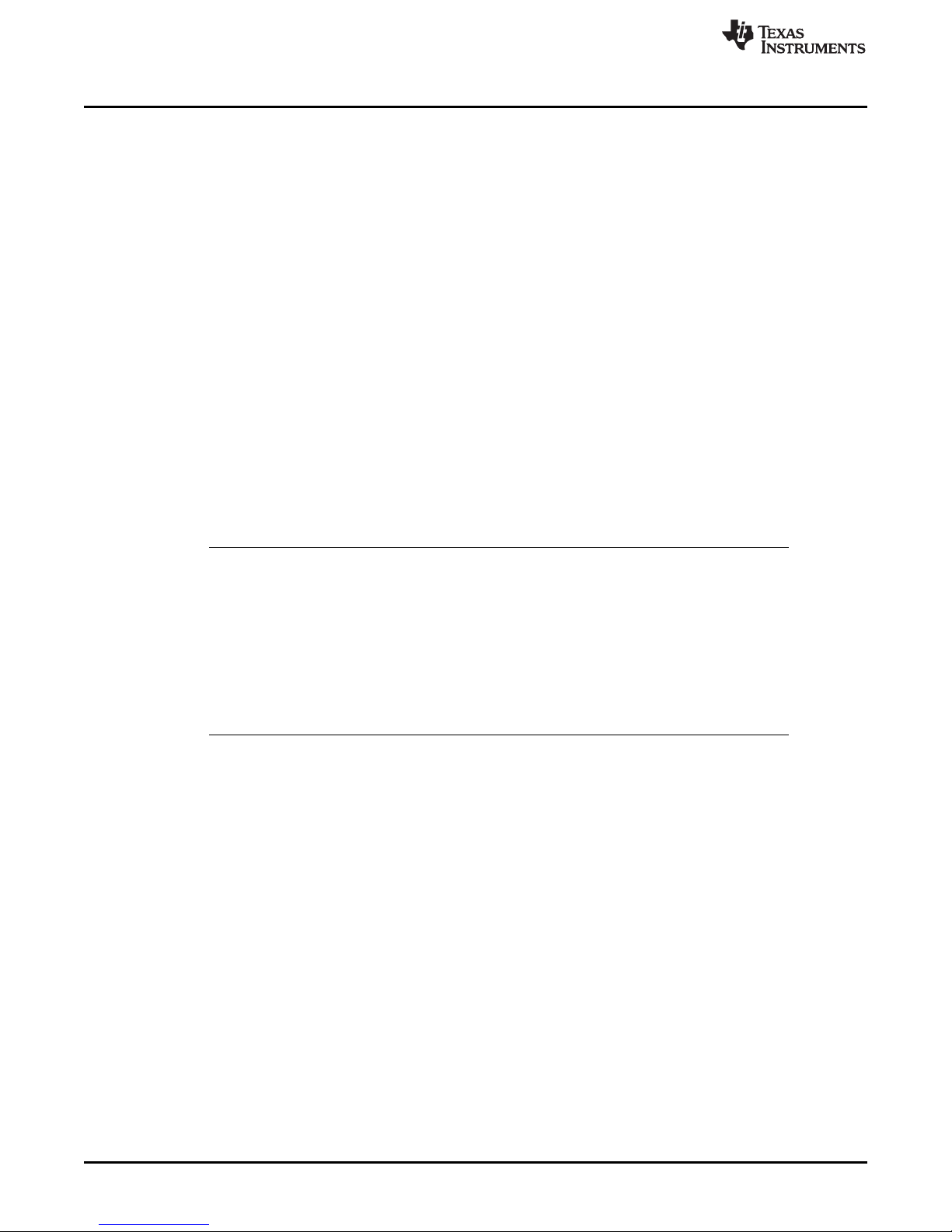

5 Power Monitoring LEDs

Each plane of the TLK6002EVM has been equipped with a voltage monitoring circuit that monitors the

voltage on the plane and lights the LEDs when the voltage is within the minimum/maximum data sheet

limits for that power supply. A precision TI voltage reference chip is used along with 0.1% precision

resistors setting minimum and maximum reference levels providing a detection circuit that is accurate to

approximately ±10 mV. The LEDs serve as a basic indication that the status of power on the board is

within the acceptable minimum/maximum limits given in the data sheet, and not as a precise

measurement tool as some LED circuits may turn off at slightly different voltages when approaching the

limits due to the manufacturing tolerances and available component values.

The voltage monitor circuits can also be bypassed, and the LEDs driven directly from the voltage on the

individual planes such as when performing voltage tolerance tests. Instead of being lit only when the

voltage on the plane is within the minimum/maximum range, the LED is lit when the voltage is greater than

the voltage needed to turn on the LED drive circuit’s NPN transistor, allowing current to flow, and the LED

to be lit from the 5-V source. In the Direct Connect mode, the base resistors have been given extra margin

to allow the LEDs to light when the voltage on the plane is a little below the minimum limit of that supply in

order to provide a LED indicator of power on the plane during voltage tolerance tests near the lower

supply limits.

Placing the jumper on the PWR side of the Voltage Monitor Enable/Disable header connects the power

plane to the input of the voltage monitoring circuit. This input is high impedance and does not load down

the power source providing the voltage to the plane.

Placing the header on the MNT side of the LED Monitor/Direct Connect selection header connects the

LED drive circuit to the output of the voltage monitor circuit causing the LED to be lit only when the

voltage is within the acceptable range.

Power Monitoring LEDs

Figure 5. TLK6002 EVM Voltage Monitor LED Enabled Example

Placing the jumper on the GND side of the Voltage Monitor Enable/Disable header disconnects the power

plane to the input of the voltage monitoring circuit and instead ties the input to GND. This prevents the

output of the voltage monitoring circuit from floating and possibly causing the LED to flicker during contact

with the board.

Placing the jumper on the MNT side of the LED Monitor/Direct Connect selection header connects the

LED drive circuit to the output of the voltage monitor circuit causing the LED to be off because the voltage

monitor circuit senses that the plane voltage is GND, which is less than the acceptable plane voltage.

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Evaluation Module

9

Copyright © 2010, Texas Instruments Incorporated

Page 10

PLN

LED

MNT

PLN

LED

MNT

PWR

EN

GND

PWR

EN

GND

1P8V

1P5V

LEDMONITOR

JMP98

JMP99

U28

JMP100

JMP101

1P5V AND 1P8VLEDSDISABLED

COMPLETELY

PLN

LED

MNT

PLN

LED

MNT

PWR

EN

GND

PWR

EN

GND

1P8V

1P5V

LEDMONITOR

JMP98

JMP99

U28

JMP100

JMP101

1P5V AND 1P8VLEDSDISABLED

COMPLETELY

(JMP57 SHUNT

POSITIONIS A

DON’T CARE)

(JMP57 SHUNT

POSITIONIS A

DON’T CARE)

Power Monitoring LEDs

Placing the jumper on the DIRECT side of the LED Monitor/Direct Connect selection header connects the

LED drive circuit to the power plane itself, causing the LED to be lit when the voltage is great enough to

cause current to flow through the LED drive circuit. This LED configuration has been designed to be used

when pushing the lower limits of the acceptable voltage range to continue to provide an indicator that

power is on the plane, however, without regards to what that voltage may actually be.

The jumper on the Voltage Monitor Enable/Disable header does not matter as this is only the input to the

voltage monitor circuit, which has been bypassed when the LED drive circuit is connected directly to the

power plane itself.

www.ti.com

Figure 6. TLK6002 EVM Voltage Monitor LED Disabled Example

Figure 7. TLK6002 EVM Voltage Monitor LED Connected Directly to Plane Example

10

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 11

RESISTOR

POWER

RESISTOR

POWER

RESISTOR

POWER

RESISTOR

POWER

RESISTOR

POWER

1P5/8V

1P5/8V

1P5/8V

1P5/8V

1P5/8V

1P5/8V

PRTAD 0

PRTAD 1

PRTAD 2

PRTAD 3

PRTAD 4

REFCLK A SEL

REFCLKBSEL

RATE A 2

RATE A 1

RATE A 0

CODEA EN

LOSA

PD TRXA

GND

GND

GND

GND

GND

GND

GND

GND

RATEB2

RATEB1

RATEB0

CODEBEN

LOSB

PD TRXB

AMUXB

AMUXA

TESTEN

CLKOUTSEL

PRBSEN

GPI1

GPI0

PRBSBFAIL

PRBSBPASS

PRBSB

PRBSA

PRBSA FAIL

PRBSA PASS

A

B

LOSA

LOSB

PRBSPASS

D41

D42

D4

D3

D52

D51

D50

D49

JMP43

JMP23

JMP21

JMP17

JMP16

JMP27

JMP25

JMP26

JMP24

JMP29

JMP28

JMP33

JMP31

PULLUP RESISTORS ARECONNECTED

TO ALL CONTROL INPUT LINES

THROUGH THESEHEADERS.

REMOVING THESHUNTSON THESE

HEADERSWILL DISCONNECT ALL THE

PULLUP RESISTORSFROM THE 1P5/8V

PLANEFORMORE ACCURATECURRENT

MEASUREMENTS.

LOGIC “HIGH” VOLTAGELEVELSWILL

HAVE TOBEMANUALLY DRIVEN .

THEPINSON THIS

SIDEOF ALL HEADER

BLOCKS AREGND

RESISTOR

POWER

CHANNEL A

CONTROL AND

STATUSPINS. THE

LOSA LEDIS

LOCATEDBELOW

CHANNEL B

CONTROL AND

STATUSPINS. THE

LOSBLEDIS

LOCATEDBELOW

PRBS_PASSSIGNALS

PRBS_PASSSIGNAL LEDS

PRBS_PASSBSIGNAL

LATCHLEDS

PRBS_PASSA SIGNAL

LATCHLEDS

PULLUP RESISTORS ARECONNECTED

TO ALL CONTROL INPUT LINES .

REMOVING THESHUNTSON THE

CONTROL BLOCKHEADERSWILL CAUSE

THEPULLUP RESISTOR TOPULL THE

LINE TO A LOGIC “HIGH” ANDPLACING A

SHUNT ON THELINEWILL SHORT THE

LINE TOGNDCREATING A LOGIC “LOW” .

www.ti.com

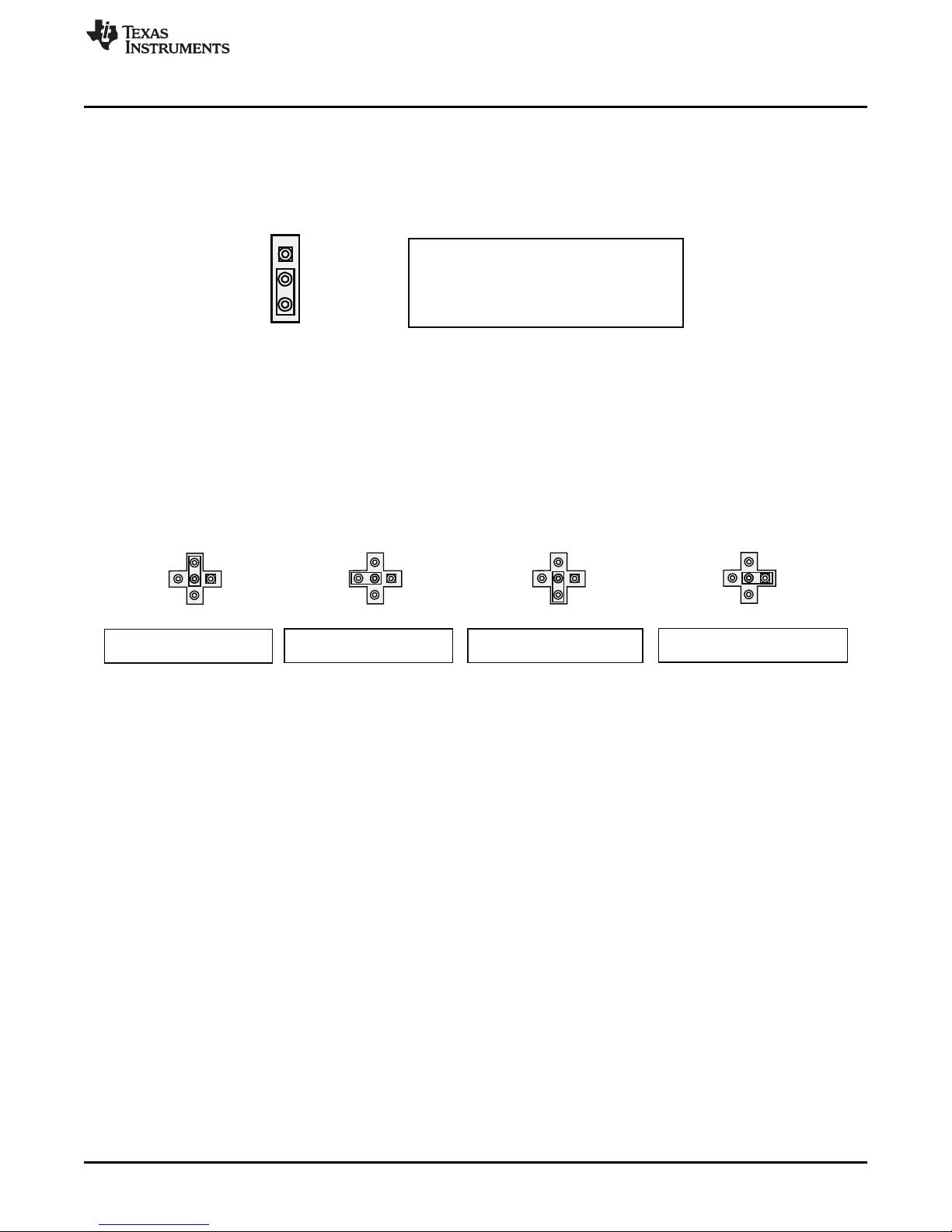

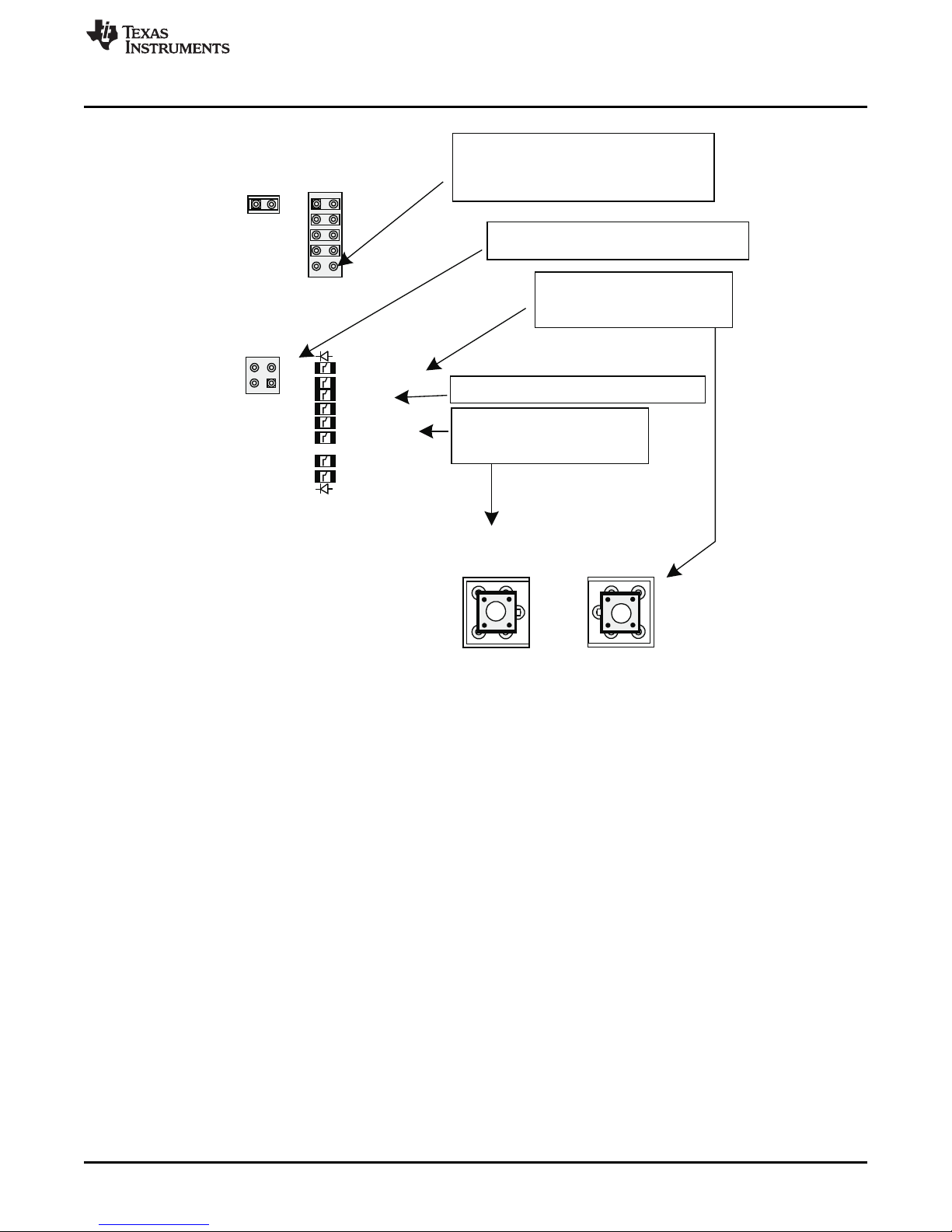

6 Control and Output Status Signals

All of the external control and status pins on the TLK6002EVM have been consolidated to a single location

on the board and broken out into several header blocks for easier reference. LEDs have been added to

the LOSA, LOSB, PRBS_PASSA, and PRBS_PASSB lines in addition to the headers for scope probes, to

allow easy monitoring of the High/Low value on the line. The LED is ON when the line is a Logic High, and

the LED is OFF when the line is a logic low. If the line is toggling, a dimming of the LED may be observed

as the LED is pulsing on and off relative to the activity on the line.

Control and Output Status Signals

Figure 8. Control Connectors (JMP17, JMP23, JMP26, JMP27, JMP29, JMP33, JMP43)

6.1 Control Signal and Status Pin Descriptions:

PRTAD[4:0]: Port Address. Used to select the Port ID.

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Evaluation Module

11

Page 12

Control and Output Status Signals

PRTAD[4:1] selects the device port address. TLK6002 has two different PHY addresses (ports).

Selecting a unique PRTAD[4:1] per TLK6002 device allows 16 TLK6002 devices per MDIO bus.

Each channel can be accessed by setting the appropriate port address field within the serial

interface protocol transaction.

TLK6002 responds if the four MSBs of the inband PHY address field on MDIO protocol (PA[4:1])

matches PRTAD[4:1]. The LSB of PHY address field (PA[0]) determines which channel/port

within TLK6002 to respond to.

PRTAD[0] is not used functionally, but is present for device testability and compatibility with other

devices in the family of products.

Channel A responds to port address 0 within the block of two port addresses.

Channel B responds to port address 1 within the block of two port addresses.

PRTAD[0] must be grounded on the application board.

The PRTAD[3] pin in application mode must be biased with a pullup or pulldown resistor (or allow

for an isolation mechanism from the onboard driver) and not connected directly to a power or

ground plane. The application board allows the flexibility of easily reworking the PRTAD[3] signal

to a high level if the device debug is necessary (by including an uninstalled resistor to VDDO1).

REFCLK_A_SEL: Reference Clock Select Channel A. This input, when low, selects REFCLK_0_P/N as

the clock reference to Channel A SERDES macro. When high, REFCLK_1_P/N is selected as the clock

reference to Channel A SERDES macro. If software control is desired (register bit 0.1), this input signal

must be tied low. See Figure 4, “TLK6002 Reference Clock/Output Clock Architecture” of the TLK6002,

Dual-Channel 0.47Gbps to 6.25Gbps Multi-Rate Transceiver data sheet (SLLSE34) for more detail.

REFCLK_B_SEL: Reference Clock Select Channel B. This input, when low, selects REFCLK_0_P/N as

the clock reference to Channel B SERDES macro. When high, REFCLK_1_P/N is selected as the clock

reference to Channel B SERDES macro. If software control is desired (register bit 0.1), this input signal

must be tied low. See Figure 4, “TLK6002 Reference Clock/Output Clock Architecture” of the TLK6002

data sheet (SLLSE34) for more detail.

RATE_A[2:0]: Channel A Rate select pins. These pins put channel A into one of the four supported

(full/half/quarter/eighth) channel operation rates, enable software control, or enable Auto Rate Sense

(ARS):

www.ti.com

000 – Full Rate mode

001 – Half Rate mode

010 – Quarter Rate mode

011 – Eighth Rate mode

100 – Software Selectable Rate

101 – Channel A Auto Rate Sense (ARS) Function Enabled.

Channel A SERDES settings are determined by Channel A ARS machine. CLK_OUT_P/N selected

by CLK_OUT_SEL. See Table 9 of the TLK6002 data sheet (SLLSE34) for additional details on

CLK_OUT_P/N.

110 – Channel A Auto Rate Sense (ARS) Function Enabled.

Channel A SERDES settings are determined by Channel A ARS machine. CLK_OUT_P/N is

not selected by CLK_OUT_SEL. Channel B may not be simultaneously configured with

RATE_B = 110 with respect to CLK_OUT_P/N, this setting has the highest priority. See Table

9 of the TLK6002 data sheet (SLLSE34) for additional details on CLK_OUT_P/N.

111 – Channel A Auto Rate Sense (ARS) Function Enabled – Slave Mode.

If Channel B ARS is enabled (Rate B = 101 or 110 only):

Channel A SERDES settings are determined by Channel B ARS machine. CLK_OUT_P/N is

not selected by CLK_OUT_SEL. See Table 9 of the TLK6002 data sheet (SLLSE34) for

additional details on CLK_OUT_P/N.

12

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 13

www.ti.com

Control and Output Status Signals

If Channel B ARS is not enabled (Rate B = 000/001/010/011/111):

Channel A SERDES settings are determined by Channel A MDIO registers. CLK_OUT_P/N is

selected by CLK_OUT_SEL. See Table 9 of the TLK6002 data sheet (SLLSE34) for additional

details on CLK_OUT_P/N.

Channel A and B must not be in slave mode simultaneously. Both directions of Channel A are

controlled by these input signals.

The RATE_A[2] pin must be routed to an uninstalled header so that it can be driven externally in

the event that device debug is required. In application mode, it must be biased with a pullup or

pulldown resistor and not connected directly to a power or ground plane.

CODEA_EN: Encoder/Decoder Channel A Enable: When this pin is asserted high, the internal 8b/10b

encoder/decoder is enabled. This signal is ORed with MDIO register bits and must be pulled low through

a resistor if software control is desired. This pin must be routed to an uninstalled header so that it can be

driven externally in the even that device debug is required. In application mode, it must be biased with a

pullup or pulldown resistor and not connected directly to a power or ground plane.

LOSA: Channel A Receive Loss Of Signal (LOS) Indicator.

LOSA = 0, signal detected.

LOSA = 1, loss of signal.

Loss of signal detection is based on the input signal level. When RXAP/N has an input signal

of ≤75mVdfpp, LOSA is asserted (if enabled). The input signal must be greater than or equal

to 150mVdfpp for this function to operate reliably.

Other functions can be observed on LOSA real time, configured via MDIO.

During device reset (RESET_N asserted low), this pin is driven low. During pin-based power

down (PD_TRXA_N asserted low), this pin is floating. During register-based power down (1.15

asserted high), this pin is floating.

It is highly recommended that LOSA be brought to an easily accessible point on the

application board (header) in the event that debug is required.

PD_TRXA_N: Transceiver Power Down. When this pin is held low (asserted), Channel A is placed in

power-down mode. When de-asserted, Channel A operated normally. After de-assertion, a software data

path reset must be issued through the MDIO interface.

RATE_B[2:0]: Channel B Rate select pins. These pins put channel B into one of the four supported

(full/half/quarter/eighth) channel operation rates, enable software control, or enable Auto Rate Sense

(ARS):

000 – Full Rate mode

001 – Half Rate mode

010 – Quarter Rate mode

011 – Eighth Rate mode

100 – Software Selectable Rate

101 – Channel A Auto Rate Sense (ARS) Function Enabled.

Channel B SERDES settings are determined by Channel B ARS machine. CLK_OUT_P/N is

selected by CLK_OUT_SEL. See Table 9 of the TLK6002 data sheet (SLLSE34) for additional

details on CLK_OUT_P/N.

110 – Channel B Auto Rate Sense (ARS) Function Enabled.

Channel B SERDES settings are determined by Channel B ARS machine. CLK_OUT_P/N is

not selected by CLK_OUT_SEL. Channel A may not be simultaneously configured with

RATE_A = 110 with respect to CLK_OUT_P/N; this setting has the highest priority. See Table

9 of the TLK6002 data sheet (SLLSE34) for additional details on CLK_OUT_P/N.

111 – Channel B Auto Rate Sense (ARS) Function Enabled – Slave Mode

If Channel B ARS is enabled (Rate B = 101 or 110 only):

Channel B SERDES settings are determined by Channel B ARS machine. CLK_OUT_P/N is

not selected by CLK_OUT_SEL. See Table 9 of the TLK6002 data sheet (SLLSE34) for

additional details on CLK_OUT_P/N.

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Evaluation Module

13

Copyright © 2010, Texas Instruments Incorporated

Page 14

Control and Output Status Signals

If Channel B ARS is not enabled (Rate B = 000/001/010/011/111):

Channel B SERDES settings are determined by Channel B MDIO registers. CLK_OUT_P/N is

selected by CLK_OUT_SEL. See Table 9 of the TLK6002 data sheet (SLLSE34) for additional

details on CLK_OUT_P/N.

Channel A and B must not be in slave mode simultaneously. Both directions of Channel A are

controlled by these input signals.

The RATE_B2 pin must be routed to an uninstalled header so that it can be driven externally

in the event that device debug is required. In application mode, it must be biased with a pullup

or pulldown resistor and not connected directly to a power or ground plane.

CODEB_EN: Encoder/Decoder Channel B Enable: When this pin is asserted high, the internal 8b/10b

encoder/decoder is enabled. This signal is ORed with MDIO register bits, and must be pulled low through

a resistor if software control is desired. This pin must be routed to an uninstalled header so that it can be

driven externally in the event that device debug is required. In application mode, it must be biased with a

pullup or pulldown resistor and not connected directly to a power or ground plane.

LOSB: Channel B Receive Loss Of Signal (LOS) Indicator.

LOSB = 0, signal detected.

LOSB = 1, loss of signal.

Loss of signal detection is based on the input signal level. When RXBP/N has an input signal

of ≤75 mVdfpp, LOSB is asserted (if enabled). The input signal must be greater than or equal

to 150mVdfpp for this function to operate reliably.

Other functions can be observed on LOSB real time, configured via MDIO.

During device reset (RESET_N asserted low), this pin is driven low. During pin-based power

down (PD_TRXB_N asserted low), this pin is floating. During register-based power down (1.15

asserted high), this pin is floating.

It is highly recommended that LOSB be brought to an easily accessible point on the

application board (header) in the event that debug is required.

www.ti.com

PD_TRXB_N: Transceiver Power Down. When this pin is held low (asserted), Channel B is placed in

power-down mode. When de-asserted, Channel B operated normally. After de-assertion, a software data

path reset must be issued through the MDIO interface.

AMUXB: SERDES Channel B Analog Testability I/O. This signal is used during the device manufacturing

process. It must be left unconnected in the device application.

AMUXA: SERDES Channel A Analog Testability I/O. This signal is used during the device manufacturing

process. It must be left unconnected in the device application.

TESTEN: Test Enable. This signal is used during the device manufacturing process. It must be grounded

through a resistor in the device application board. The application board must allow the flexibility of easily

reworking this signal to a high level if device debug is necessary (by including an uninstalled resistor to

VDDO2).

PRBS_EN: Enable PRBS: When this pin is asserted high, the internal PRBS generator and verifier

circuits are enabled on both transmit and receive data paths of both channels. This signal is logically

ORed with an MDIO register bit. PRBS 231-1 is selected by default, and can be changed in MDIO register

7.10:8. Note that PRBS is not possible in eighth rate mode.

The PRBS_EN pin must be routed to an uninstalled header so that it can be driven externally in the event

that device debug is required. In application mode, it must be biased with a pullup or pulldown resistor (or

allow for an isolation mechanism from the onboard driver) and not connected directly to a power or ground

plane.

CLK_OUT_SEL: Output Clock Selection. If ARS is not enabled and CLK_OUT_SEL is low, Channel A

recovered byte clock is output onto CLK_OUT_P/N. If ARS is not enabled and CLK_OUT_SEL is high,

Channel B recovered byte clock is output onto CLK_OUT_P/N. If software control is desired, (registered

bit 0.6), this input signal must be tied low. See Figure 4, “TLK6002 Reference Clock/Output Clock

Architecture” of the TLK6002 data sheet (SLLSE34) for more detail. If ARS is enabled, the function of

CLK_OUT_SEL is shown in Table 9 of the TLK6002 data sheet.

14

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 15

www.ti.com

GPI0: General Purpose Input Zero. This signal is used during the device manufacturing process. It must

be grounded through a resistor in the device application board. The application board must allow the

flexibility of easily reworking this signal to a high level if device debug is necessary (by including an

uninstalled resistor to VDDO2).

GPI1: General Purpose Input One. This signal can be used to logically combine an external status

condition with LOSA or LOSB if enabled in an MDIO register. Note that if GPI1 is low, LOSA/B is asserted

if a logical combination in enabled. Similarly, if GPI1 is high, LOSA/B is de-asserted. If unused, this input

must be grounded in the device application (not floating).

Control and Output Status Signals

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Evaluation Module

15

Copyright © 2010, Texas Instruments Incorporated

Page 16

PRBS PASS Latch Circuits

7 PRBS PASS Latch Circuits

The TLK6002EVM has a Pass/Fail Latch circuit to aid in PRBS testing. The PRBS_PASSA and

PRBS_PASSB status signals have been routed out to Header JMP43 for monitoring with an oscilloscope.

Additionally, these signals are routed to the base of an NPN transistor that drives an LED on or off

depending on whether the PRBS_PASSA/B signals are High or Low. The blue LEDs D51 and D52 are a

good indication of general passing or general failing depending on whether the LED is on or off. However,

it is not a good method to easily monitor individual bit failures. An error counter can be read through the

MDIO register interface that contains the actual error count should the counter not have overflowed;

however, it requires the counter to be read in order to determine whether an error has occurred. With

proper setup and operation, the PRBS_PASS Latch circuits can quickly indicate whether an error has

occurred or not.

To properly operate the PRBS_PASS latches, configure the TLK6002 for PRBS operation either by pulling

the PRBS_EN line high or through the appropriate MDIO register settings. PRBS data is generated and

output on the Serial Transmit and the Serial Receive monitors for valid PRBS data and counts the number

of errors received. In addition to counting the errors, the PRBS_PASS line is high if the line is error free,

and transitions low for the duration of time that an error, or errors, are detected. Once the PRBS link is

established and running error free, pushing the PRBS_PASS RESET button resets the latch circuit, which

consists of a J/K flip-flop and a red and green LED to indicate the state of the flip-flop. When the J/K

flip-flop is reset, the green LED is lit until a high-to-low transition on the PRBS_PASS signal is observed.

Because the PRBS_PASS signal is connected to the clock input of the J/K flip-flop, a high-to-low transition

causes the flip-flop to toggle to the next state which turns OFF the green LED and turns ON the red LED.

The circuit remains in this state until the RESET button is pushed again, which resets the flip-flop to its

initial state.

www.ti.com

NOTE: If the PRBS_PASS lines are low, indicating constant PRBS failure and the PRBS_PASS

RESET buttons are pushed, the green LEDs lights and remain lit, which might be falsely

interpreted as a passing result. This is incorrect as the line was not ever passing and as long

as it is failing the PRBS_PASS line will be low and never have the high-to-low transition

required to toggle the state and light the red LED. This is not the intended operation of the

circuit, and this latch circuit must ONLY be used on a passing and correctly established

channel with valid PRBS data. An easy indication of whether the PRBS Latch may be used

is whether the blue PRBSA/B LEDs are on as well, because they can only be on if the

PRBS_PASS signals are high indicating a passing status. If the blue LEDs are not on, then

the green and red PRBS_PASS/Fail LEDs are not a valid indication of the status of the test.

16

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 17

RESISTOR

POWER

1P5/8V

GND

GND

GND

AMUXB

AMUXA

TESTEN

CLKOUTSEL

PRBSEN

PRBSBFAIL

PRBSBPASS

PRBSB

PRBSA

PRBSA FAIL

PRBSA PASS

A

B

LOSA

LOSB

PRBSPASS

PRBSA

PRBSB

LATCH LATCH

RESET

RESET

SW4

SW3

D41

D42

D4

D3

D52

D51

D50

D49

JMP43

JMP23

JMP17

JMP16

JMP27

PRBS_PASSBSIGNAL

LATCHLEDSRESET BY

PRESSINGSW4

PRBS_PASSA SIGNAL

LATCHLEDSRESET BY

PRESSINGSW3

BLUEPRBS_PASSSIGNAL LEDS

PRBS_PASSSIGNALSCANBE

OBSERVEDWITH A SCOPEHERE

ENABLE THEPRBSGENERATOR/

ANALYZERFUNCTIONBY

REMOVING THISSHUNT AND

PULLING THELINEHIGH

www.ti.com

PRBS PASS Latch Circuits

Figure 9. TLK6002 EVM MDIO Connector (JMP30)

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Evaluation Module

17

Page 18

GND

GND

MDC

MDIO

MDIO

JMP30

ALL NON-LABELEDPINS

ARENO-CONNECTS

MDIO

8 MDIO

The TLK6002 supports the Management Data Input/Output (MDIO) Interface as defined in Clause 22 of

the IEEE 802.3 Ethernet Specification. The MDIO allows register-based management and control of the

serial links. Normal operation of the TLK6002 is possible without the use of this interface; however, some

additional features are accessible only through the MDIO interface.

The MDIO Management Interface consists of a bidirectional data path (MDIO) and a clock reference

(MDC). The port address is determined by control pins PRTAD[4:0

In Clause 22, the top four control pins PRTAD[4:1] determine the device port address. In this mode, the

two individual channels in TLK6002 are classified as two different ports. Therefore, any PRTAD[4:1] value

has two ports per TLK6002. The TLK6002 responds if the four MSBs of PHY address field on MDIO

protocol (PA[4:1]) matches PRTAD[4:1]. The LSB of PHY address field (PA[0]) determines which

channel/port within the TLK6002 to respond to.

If PA[0] = 1’b0, TLK6002’s Channel A responds.

If PA[0] = 1’b1, TLK6002’s Channel B responds.

Write transactions which address an invalid register or read-only registers are ignored. Read transactions

of invalid registers return a 0.

The bidirectional MDIO pin must be externally pulled up to 1.5 V or 1.8 V (VDDO) with an appropriate

resistor value as per the IEEE802.3 Clause 22/45 MDIO Standard.

The supplied MDIO EVM uses an FPGA with 2.5-V I/O signal levels whereas the TLK6002 requires either

1.5-V or 1.8-V I/O levels on these signals. Therefore, bidirectional level shifters have been provided on

board that level shift the 2.5-V MDIO and MDC signals to the appropriate 1p5/8V levels. If a different

MDIO controller id used that already has 1.5-V or 1.8-V signal levels, resistors R530, R531, R532, and

R533 can be removed; thus, disconnecting the level shifters and resistors R469 and R470 can be installed

which connects the TLK6002 MDIO and MDC signal pins directly to the pins of JMP30. A third option of

using NFETs as level shifters has also been provided, if this option is desired in the end application.

Removing resistors R530, R531, R532, and R533, as well R469 and R470 if they were installed, and

installing an appropriate NFET such as Fairchild’s FDV301N allows for this third option of level shifting to

be evaluated.

www.ti.com

Figure 10. TLK6002 EVM MDIO Connector (JMP30)

18

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 19

GND

GND

GND

GND

GND

TDI

TDO

TRST

TMS

TCK

JTAG

JMP35

www.ti.com

9 JTAG

The EVM also provides a separate connector to support the full five-pin JTAG interface of the TLK6002

with onboard level shifters to be compatible with most standard JTAG Control Interfaces to be used for

manufacturing tests. Pullup resistors on the 3.3-V (header) side of the level shifter are not installed by TI

but can be installed if an open-drain type of controller is used which requires the use of external pullup

resistors.

JTAG

TDI: JTAG Input Data. TDI is used to serially shift test data and test instructions into the device

during the operation of the test port. In system applications where JTAG is not implemented, this

input signal can be left floating. During pin-based power down (PD_TRXA_N and PD_TRXB_N

asserted low), this pin is not pulled up. During register-based power down (1.15 asserted high for

both channels), this pin is pulled up normally.

TDO: JTAG Output Data. TDO is used to serially shift test data and test instructions out of the

device during operation of the test port. When the JTAG port is not in use, TDO is in a

high-impedance state. During device reset (RESET_N asserted low), this pin is floating. During

pin-based power down (PD_TRXA_N and PD_TRXB_N asserted low), this pin is floating. During

register-based power down (1.15 asserted high on both channels), this pin is floating.

TMS: JTAG Mode Select. TMS is used to control the state of the internal test-port controller. In

system applications where JTAG is not implemented, this input signal can be left unconnected.

During pin-based power down (PD_TRXA_N and PD_TRXB_N asserted low), this pin is not

pulled up. During register-based power down (1.15 asserted high both channels), this pin is

pulled up normally.

TCK: JTAG Clock. TCK is used to clock state information and test data into and out of the device

during boundary scan operation. In system applications where JTAG is not implemented, this

input signal must be grounded.

TRST_N: JTAG Test Reset. TRST_N is used to reset the JTAG logic into system operational

mode. This input can be left unconnected in the application and is pulled down internally,

disabling the JTAG circuitry. If JTAG is implemented on the application board, this signal must be

de-asserted (high) during JTAG system testing, and otherwise asserted (low) during normal

operation mode. During pin-based power down (PD_TRXA_N and PD_TRXB_N asserted low),

this pin is not pulled down. During register-based power down (1.15 asserted high on both

channels), this pin is pulled down normally.

NOTE: TRST_N must be tied low when the JTAG port is not in use and during normal operation of

the port as shown in Figure 11 because an external pullup resistor is provided. If you have

no need to use the JTAG port, removing resistor R423 allows the internal pulldown to disable

the circuitry and installing resistor R426 provides an external pulldown on this pin.

Figure 11. TLK6002 EVM JTAG Connector (JMP35)

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Evaluation Module

19

Copyright © 2010, Texas Instruments Incorporated

Page 20

MAINRST

RST

RST

MAIN

MANUAL RESET

GND

MAIN

RST BUTTON

RST

GND

JMP15

SW1

D1

D2

JMP14

Reset

10 Reset

The TLK6002EVM comes configured for Manual Reset operations involving the Pushbutton Reset Switch

(SW1). When switch SW1 is pressed, the TLK6002 device RESET pin (RST_N) goes LOW and the entire

TLK6002 device is reinitialized. A TI TPS3125J18 Ultra Low Voltage Processor Supervisory Circuit is used

to control the Reset line. During power on, RESET pin of U2 is asserted when the supply voltage

becomes higher than 0.75 V. Thereafter, the supply voltage supervisor monitors the voltage and keeps

RESET output active as long as the voltage remains below the threshold voltage (VIT). An internal timer

delays the return of the output to the inactive state (high) to ensure proper system reset. The delay time, t

= 180 ms, starts after the voltage has risen above the threshold voltage (VIT).

A manual reset input to the supervisory circuit, MR, accepts the input from the pushbutton switch SW1. A

low level at MR causes RESET to become active, thus resetting the TLK6002 device whenever the

pushbutton RESET is pressed. By placing a jumper on JMP15, the Manual Reset (MR) is tied hard to

ground causing the TLK6002 to be held in a constant state of Reset without the need to continually hold

the Reset Pushbutton SW1. The Supervisory circuit released the Reset line to a HIGH 180 ms (td) from

the time the MR line becomes greater than the threshold voltage (VIT).

By removing the jumper from JMP14, the Supervised Reset Circuit is disconnected from the RST_N line.

Reset control from an external controller or piece of equipment can be connected directly to pin 2

(RST_N) of JMP14 and a ground pin GND has been added to the JMP14 header next to the RST_N pin

to allow easy access for the return current on that cable.

www.ti.com

d

Figure 12. RESET Switch – SW1, JMP14, or JMP15

NOTE: The Jumper on JMP14 connecting RESET SW to RST_N must be connected as shown in

order to cause the TLK6002 to be reset and reinitialized If switch SW1 is pressed, the device

RESET pin (RST_N) goes LOW, the entire TLK6002 device is reinitialized.

20

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 21

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

1P5/8V

TDA0..19

TDA0..19

RDA0..19

GND

GND

JMP145

JMP38

JMP37

GND

GND

TXCLKA

RXCLKA

PARALLEL SIGNAL

BIT NUMBER

PARALLEL SIGNAL

BIT NUMBER

PIN TYPEOFROW

PINNAMES

www.ti.com

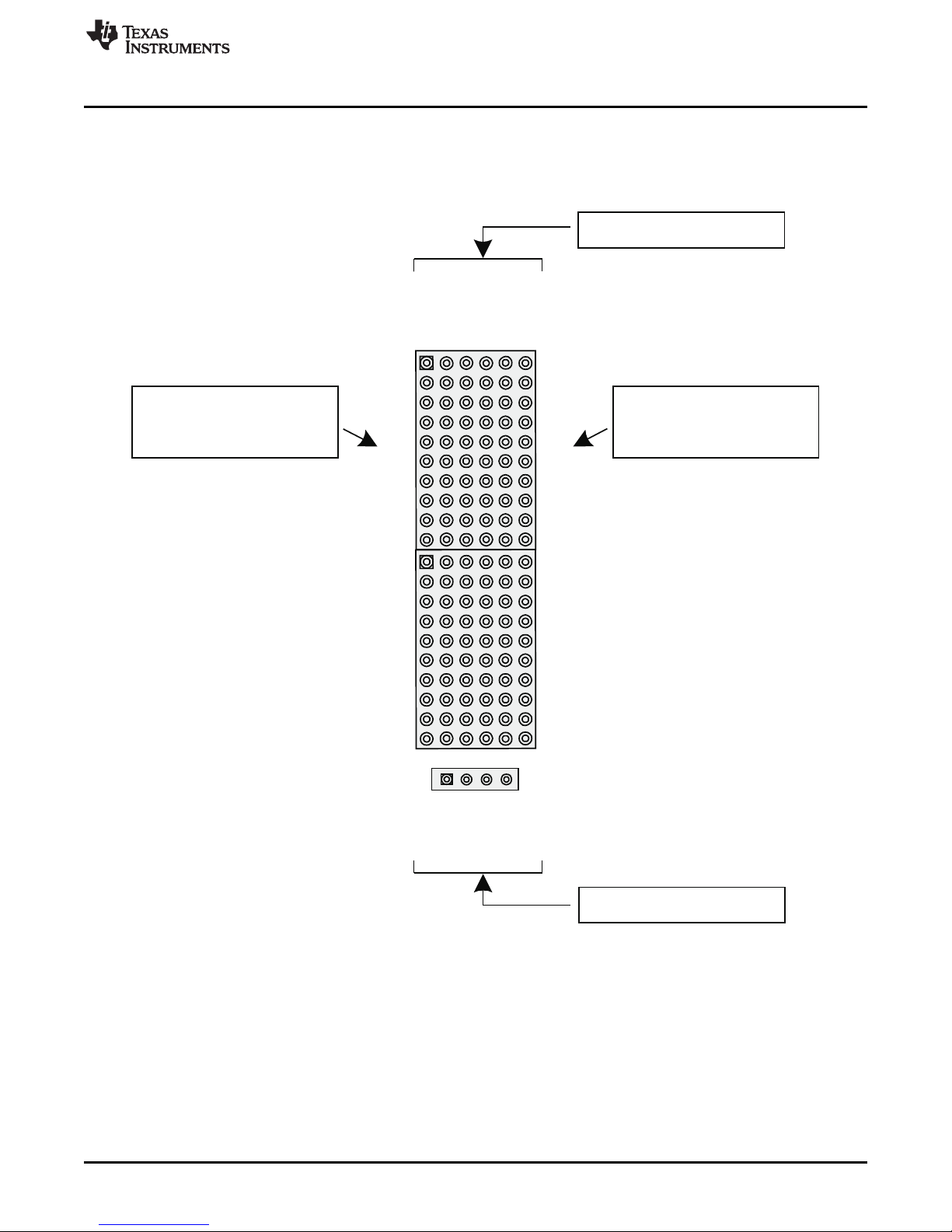

11 Parallel Signals

The parallel signals on the TLK6002EVM have been routed to a 0.1-in. header block that is configured like

Figure 13. All RD pins on header blocks RDA/B[7:0], RDA/B[15:8], as well as all TDA/B pins on header

blocks TDA/B[7:0], TDA/B[15:8], have matched trace lengths to themselves ±0.5 mil.

Parallel Signals

Parallel Loopback, shown in Figure 14, can be easily implemented by placing jumpers on the RDx/TDx

pins of the header. For example, placing a jumper on pins 4 and 5 of JMP37 loops back TDA19 to

RDA19.

The Transmit Data Clocks and Receive Data Clocks are located in header blocks JMP145 and JMP146

with the clock pins next to each other. These signals are the parallel side input and output clocks per

channel. During Parallel Loopback, the clocks can be shorted together as shown in Figure 14.

Figure 13. Parallel Signal Header Block Diagram

SLLU132–October 2010 TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Evaluation Module

21

Page 22

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

1P5/8V

TDA0..19

TDA0..19

RDA0..19

GND

GND

JMP145

JMP38

JMP37

GND

GND

TXCLKA

RXCLKA

PARALLEL

LOOPBACK

Parallel Signals

www.ti.com

Additional GND and VDD pins have been added into the header block for several reasons. The GND pins

next to the RDA/B and TDA/B pins provide a convenient ground reference for a scope probe or coaxial

cables. The additional TDA/B row and VDD pins allow a static pattern to be driven into the TDA/B bus by

placing jumpers across either the TDA and 1p5/8V pins for a HIGH, or TDA/B and GND pins for a LOW

eliminating the need for cables during quick tests. The extra row of TDA/B can also be used to monitor the

signals on the TDA/B pins. Figure 15 shows a clock pattern (01010101010101010101) on TDA[19:0].

Figure 14. Parallel Loopback Example

22

TLK6002 Dual-Channel, 0.47-Gbps to 6.25-Gbps, Multi-Rate Transceiver SLLU132–October 2010

Evaluation Module

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Page 23

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

GND

GND

JMP145

JMP38

JMP37

GND

GND

TXCLKA

RXCLKA

STATICCLOCK

DRIVENON TDA[19:0]

www.ti.com

Peripheral Ports

Figure 15. TDA[19:0] Static Clock Data Pattern Example

12 Peripheral Ports

The TLK6002EVM can support three small peripheral boards which can contain any sort of additional