Page 1

TM

Technology for Innovators

Interface Selection Guide

4Q 2006

Page 2

2

Interface Selection Guide

➔

Table of Contents

Introduction 3

LVDS, xECL, CML . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Multipoint-LVDS (M-LVDS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Digital Isolators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

RS-485/422 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

RS-232 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

UARTs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

FlatLink™3G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

SerDes (Serial Gigabit Transceivers and LVDS) . . . . . . . . . . . . . . . . . . . . . . . . . . .20

™

DVI/PanelBus

TMDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

USB Hub Controllers and Peripheral Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

USB Port Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

USB Power Managers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

PCI Express®. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

PCI Bridges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

CardBus Power Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

1394 (FireWire®) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

Check inter

face.ti.com

for the latest IBIS Models

and

evaluation modules

GTLP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

VME . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Clock Distribution Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Cross-Reference Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Device Index

Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

(EVMs).

Interface Selection Guide Texas Instruments 4Q 2006

Page 3

Interface Selection Guide

3

Introduction

Texas Instruments (TI) provides complete interface solutions that empower you to differentiate your products and accelerate time-to-market.

Our expertise in high-speed, mixed-signal circuits, system-on-a-chip integration and advanced product development processes ensures you will

eceive the silicon, support tools, software and technical documentation to create and deliver the best products on time and at competitive prices.

r

ncluded in this selection guide you will find design considerations, technical overviews, graphic representation of portfolios, parametric tables

I

nd resource information on the following families of devices:

a

LVDS: (p. 4) TIA/EIA-644A specification

d

esigned for differential transmission

delivering signaling rates into the Gbps range

and power in the mW range with low EMI to

the telecommunication and consumer markets.

xECL: (p. 4) Emitter coupled logic (xECL),

high-speed differential interface technology

designed for low jitter and skew.

CML: (p. 4) Current-mode logic (CML), high

speed differential interface technology.

M-LVDS: (p. 8) TIA/EIA-899 specification with

all the benefits of LVDS applicable to multipoint bus architecture in backplanes. Used

often for clock distribution, e.g. AdvancedTCA.

Digital Isolators: (p. 10) The new ISO72x

high-speed digital isolators use state-of-the-art

integrated capacitive coupling and silicondioxide isolation barrier to provide up to

150-Mbps signaling rate with only 1-ns jitter,

best-of-class noise immunity and high reliability.

RS-485/422: (p. 11) Robust TIA/EIA-485 and

TIA/ EIA-422 specifications specially designed

for harsh, industrial environments transmitting

a differential signal up to 50 Mbps or 1.2 km.

RS-232: (p. 13) TIA/EIA-232 specification

defining single-ended interface between data

terminal equipment (DTE) and data circuitterminating equipment (DCE).

UARTs: (p. 16) Universal Asynchronous

Receiver/T

nent of serial communication utilizing RS232,

RS485/422 or LVDS transceivers to transmit or

receive between remote devices performing

parallel

process and serial to parallel conversion in the

receive process.

CAN: (p. 18) Controller Area Network

(ISO11898) specification commonly used in

automotive and industrial applications describes

differential signaling at a rate up to 1 Mbps on

a 40-meter bus with multipoint topology.

ransmitters are the key logic compo

to serial conversion in the transmit

FlatLink™ 3G: (p. 19) A new family of serial-

i

zers and deserializers designed for mobile

phone displays.

SerDes: (p. 20) Serializers and deserializers

in the gigabit range designed to bridge large

numbers of data bits over a small number of

data lines in telecommunication applications.

DVI/PanelBus™: (p. 22) The Digital Visual

Interface Specification, DVI, is an industry

standard developed by the Digital Display

Working Group (DDWG) for high-speed digital

connection to digital displays. DVI uses

transition-minimized DC balanced (TMDS)

data signaling.

TMDS: (p. 24) Transition minimized differential

signaling is the electrical interface used by DVI

and HDMI.

USB Hub Controllers and Peripheral

Devices:

established to make connecting PCs, peripherals and consumer electronics flexible and easy.

The hub controller manages USB port connect/

disconnect activities and a peripheral controller

enables USB connectivity of a peripheral

device to either a host or hub.

USB Port Protection: (p. 26) Transient voltage

suppressor protects USB 1.1 devices from ESD

and electrical noise transients.

USB Power Managers: (p. 27)

like TPS204xA and TPS205xA, are designed to

-

meet all the USB 1.0 and 2.0 requirements for

current-limiting and power switching to reliably

control the power on the voltage bus.

PCI Express®: (p. 29)

flexible and cost-effective I/O interconnect.

PCI Bridges: (p. 33) A peripheral component

interconnect (PCI) bridge provides a highperformance connection path between either

two PCI buses or a PCI component and one or

more DSP devices.

(p. 25) The USB standard was

A robust, scalable,

TI products,

CardBus Power Switches: (p. 34) The

C

ardBus controller uses the card detect and

voltage sense pins to determine a PC card’s

voltage requirements and then directs the

PCMCIA power switch to enable the proper

voltages. Standard PC cards require that V

be switched between ground, 3.3 V, and 5 V,

while VPP is switched between ground, 3.3 V,

5 V, and 12 V. CardBay sockets have the standard requirements for VCC, but require ground,

3.3 V, and 5 V to VPP, and ground, 1.8 V, or 3.3

V to V

simply not need 12 V or VPP while still having

the standard requirements for V

consider the voltage requirements of the

application when selecting a PCMCIA

power switch.

1394: (p. 36) IEEE 1394 (FireWire®) high-speed

interconnection enables simple, low-cost,

high-bandwidth, real-time data connectivity

between computers, peripherals and consumer

electronics.

GTLP: (p. 39) Gunning transceiver logic plus

(GTLP) derived from the JEDEC JESD8-3 GTL

standard is a reduced-voltage-swing

technology designed for high-speed interface

between cards operating at LVTTL logic levels

and backplanes operating at GTLP signal levels.

VME: (p. 41)

64-bit, backplane architecture that is coordinated and controlled by VITA. VME is used

extensively in military

applications.

Clock Distribution Circuits: (p. 42)

TI offers both single-ended and differential

clock buffers that perform from below 200 MHz

up to 3.5 GHz in a variety of fan-out options. In

addition to simple option for customers needing

differential signals (LVPECL) and single-ended

signals (LVTTL/LVCMOS) from the same device.

. Other PC card applications may

CORE

The VMEbus™ is a standardized,

, industrial and aerospace

CC

CC

. Therefore,

➔

Texas Instruments 4Q 2006 Interface Selection Guide

Page 4

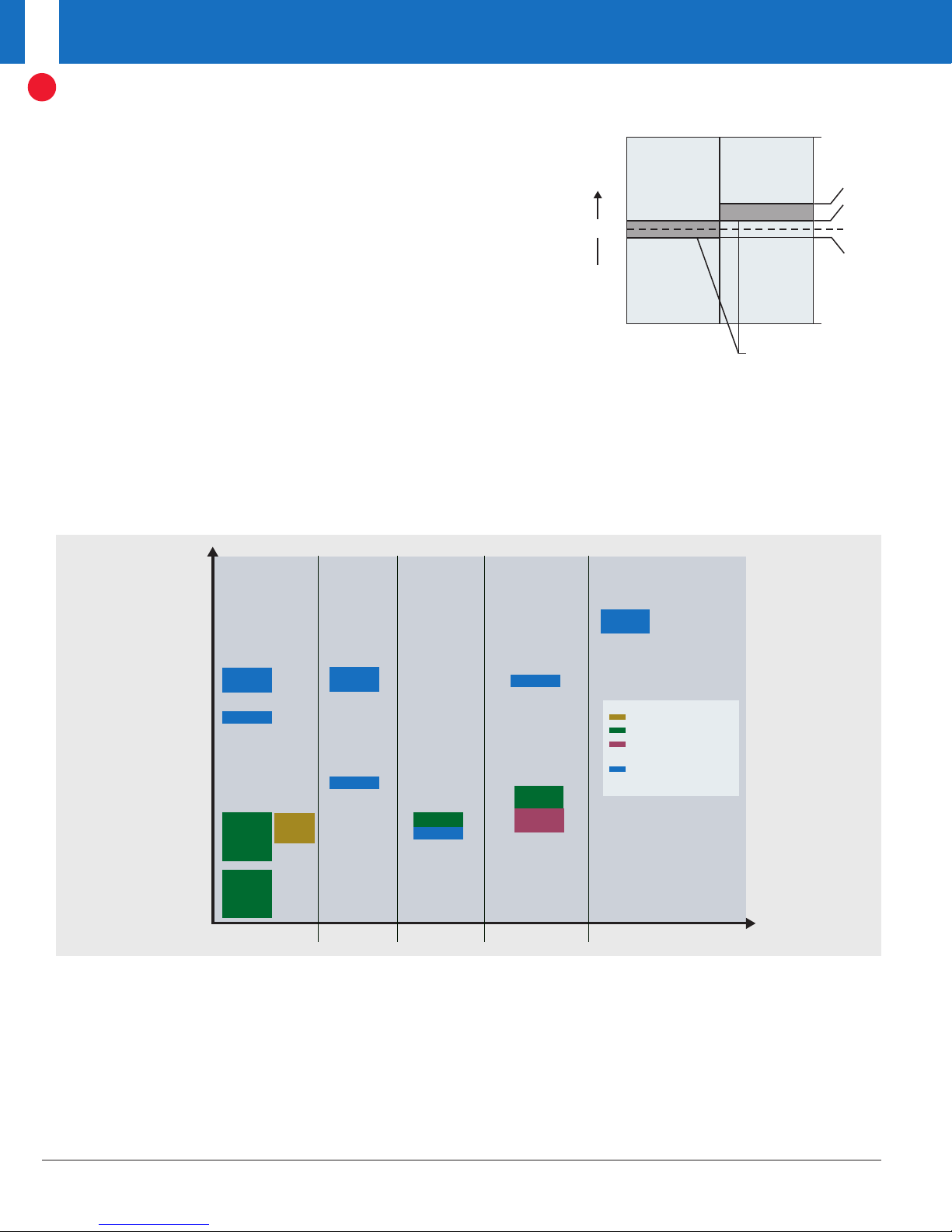

LVDS2

L

VDS9637

LVDS34

Singles

Transmitters Receivers Transceivers Repeaters/

Translators

Crosspoint

Switches

Up to 400 Mbps

Up to 630 Mbps

≥ 1 Gbps

Clock Distribution Devices

(See pg. 42 for table)

LVDS388A

LVDS386

C

DCLVD110

L

VDS108

LVDS104

L

VDS105

L

VDS117

LVDS116

L

VDS9638

LVDS179

LVDS180

L

VDS049

LVDS050

LVDS051

LVDS1050

CML100

LVDS100

LVDS101

LVDS16 LVP16

LVDS17 LVP17

LVDS18 LVP18

LVDS19 LVP19

LVDS20 LVP20

L

VDS22

LVCP22

LVCP23

LVDS122

L

VDS250

Duals

Quads

8 Channels

16 Channels

10 Channels

LVDS109

LVDS1

L

VDS389

LVDS387

LVDS047

LVDS31

LVDS3487

L

VDS391

LVDS048A/348

LVDS32/33

LVDS3486

L

VDS390

4

➔

LVDS, xECL, CML

Design Considerations

ignaling Rate—TI offers repeaters/transla-

S

tors and crosspoint switches with signaling

ates up to 4.0 Gbps.

r

Jitter — Reducing jitter, the deviation of a

signal timing event from its ideal position,

has become a priority for ensuring reliability

in high-speed data buses.

Skew — Excessive skew, the time delta

between the actual and expected arrival

LVDS Family of Products

time of a clock signal, can limit the maximum

bandwidth performance and lead to data

ampling errors. Low skew specifications

s

make high-speed interconnect devices

xcellent for signal buffering.

e

Power Consumption — Low-voltage

differential signaling (LVDS) offers a low-power

alternative to ECL and PECL devices. Currentmode drivers in LVDS produce a constant

current, which allows power consumption to

be relatively independent of frequency. The

constant current driver delivers about 3.5 mA

to a 100-W load.

Technical Information

• LVDS is based on the TIA/EIA-644A

standard conceived to provide a generalpurpose electrical-layer specification for

drivers and receivers connected in a

point-to-point or multidrop interface.

Resources For a complete list of resources (evaluation modules, data sheets and application notes), visit interface.ti.com

Literature

Number

Description

Application Notes

SLLA014A Low-Voltage Differential Signaling (LVDS) Design Notes (Rev. A)

SLLA030C Reducing Electromagnetic Interference with LVDS (Rev. C)

SLLA031A Using an LVDS Receiver with TIA/EIA-422 Data (Rev. A)

SLLA034A

SLLA038B

SLLA053B Performance of LVDS with Different Cables (Rev. B)

SLLA054A

SLLA065

SLLA082B Active Fail-Safe in TI's LVDS Receivers (Rev. B)

SLLA100 Increase Current Drive Using LVDS

SLLA101 Interfacing Different Logic with LVDS Receivers

Slew Rate Control of L

Interface Circuits for TIA/EIA-644 (LVDS) (Rev. B)

L

A Comparison of LinBiCMOS and CMOS Process T

VDS Multidrop Connections (Rev

VDS Circuits (Rev

. A)

. A)

echnologies in L

VDS ICs

SLLA103 LVPECL and LVDS Power Comparison

SLLA104 Suggestions for L

VDS Connections

SLLA105 DSP to DSP Link Using LVDS

SLLA107 Live Insertion with Differential Interface Products

SLLA147 Suitable LVDS Architectures

Interface Selection Guide Texas Instruments 4Q 2006

Literature

Number Description

Application Notes

VDS, HSTL, and CML

SCAA059

SCAA062

Part Number Description Price

Evaluation Modules (EVMs)

SN65LVDS31-32EVM Evaluation Module for LVDS31 and LVDS32 49.00

SN65LVDS31-32BEVM Evaluation Module for LVDS31 and LVDS32B 49.00

SN65LVDS31-33EVM Evaluation Module for LVDS31 and LVDS33 49.00

SN65LVDS386EVM SN65LVDS386 Evaluation Module 49.00

SN65L

SN65LVDS100EVM SN65LVDS100 Evaluation Module 99.00

SN65LVDS20EVM SN65LVDS20 Evaluation Module 49.00

SN65CML20EVM

SN65L

AC-Coupling Between Differential L

DC-Coupling Between Differential LVPECL, LVDS, HSTL, and CML

VDS387 Evaluation Module 49.00

SN65L

VDS387EVM

SN65CML20 Evaluation Module

VCP22 Evaluation Module

VCP22-23EVM

SN65L

VPECL, L

SN65LVDS122EVM SN65LVDS122 Evaluation Module 49.00

SN65LVDS250EVM SN65LVDS250 Evaluation Module 49.00

Note: IBIS models are available at interface.ti.com

*

Suggested resale price in U.S. dollars.

*

49.00

25.00

Page 5

LVDS, xECL, CML

L

VDS/LVPECL/CML Repeaters/Translators and Crosspoints Selection Guide

No. No. Signaling Jitter Part-to- Tx tpd Rx ESD

1

Device

Crosspoint Switch Family

SN65LVCP22 2X2 Crosspoint Switch: 2 2 LVPECL, LVDS 1000 105 100 0.65 0.65 85 5 16SOIC, 2.70

SN65LVCP23 2X2 Crosspoint Switch: 2 2 LVPECL, LVPECL 1300 100 100 0.65 0.65 65 5 16SOIC, 5.20

SN65LVCP40 Dual 1:2 Mux with Equalizer and 6 6 LVPECL, CML 4000 30 500 1 1 254 4 48QFN 17.40

SN65LVDS12222X2 Crosspoint Switch: 2 2 LVPECL, LVDS 1500 65 150 0.9 0.9 100 4 16SOIC, 4.75

SN65LVDS25024X4 Crosspoint Switch: 4 4 LVPECL, LVDS 2000 50 150 0.9 0.9 145 3 TSSOP 7.75

Repeaters/Translators

SN65CML100 LVDS/LVPECL/CML-to-CML 1 1 LVPECL, CML 1500 70 100 0.8 — 12 5 8SOIC, 2.55

VDS100

SN65L

SN65LVDS1012LVDS/LVPECL/CML-to-LVPECL 1 1 LVPECL, LVPECL 2000 65 100 0.9 — 90 5 8SOIC, 2.55

SN65LVDS16/17 2.5-V/3.3-V Oscillator Gain 1 1 LVPECL LVDS 2000 10 130 0.63 — 48 2 8QFN 2.55

SN65LVDS18/19 2.5-V/3.3-V Oscillator Gain 1 1 LVPECL LVDS 1000 10 130 0.63 — 36 2 8QFN 1.95

SN65LVDS20 2.5-V/3.3-V LVDS repeater with enable 1 1 LVPECL LVDS 4000 45 130

SN65LVP16/17 2.5-V/3.3-V Oscillator Gain Stage/Buffer 1 — LVPECL LVPECL 2000 10 130 0.63 — 30 2 8QFN 2.55

SN65LVP18/19

SN65LVP20 2.5-V/3.3-V LVPECL 1 1 LVPECL LVPECL 4000 10 130 0.63 — 45 3 8QFN 4.40

1

Supply voltage for all devices listed above is 3.3 V. 2Integrated termination available (100-Ω)-SN65LVDTxxx. New products are listed in bold red.

*Suggested resale price in U.S. dollars in quantities of 1,000.

Description Tx Rx Signal Signal (Mbps) (ps) Skew Max (ns) (ns) Max (mA) (kV) Package(s) Price*

LVDS Outputs LVDS, CML 16TSSOP

LVPECL Outputs LVDS, CML 16TSSOP

Pre-Emphasis LVDS, CML

LVDS Output LVDS, CML 16TSSOP

LVDS Output LVDS, CML

Repeater/Translator LVDS, CML 8VSSOP

2

VDS/LVPECL/CML 1 1 LVPECL, LVDS 2000 65 100 0.8 — 30 5 8SOIC, 2.55

L

to LVDS Repeater/Translator LVDS, CML 8VSSOP

Repeater/Translator LVDS, CML 8VSSOP

Stage/Buffer (single ended/diff inputs)

Stage/Buffer (single ended/diff inputs)

(single ended

2.5-V/3.3-V

(single ended

/diff inputs)

Oscillator Gain Stage/Buffer 1 — LVPECL LVPECL 1000 10 130 0.63 — 20 2 8QFN 1.95

/diff inputs)

of of Input Output Rate Max Part Typ tpd Typ I

0.63 —

LVDS, CML

LVDS, CML

HBM Pin/

CC

45 3 8QFN 3.30

5

➔

PECL Selection Guide

Device

TB5D1M

TB5D2H

TB5R1

TB5R2

TB5R3

TB3R1

TB3R2

TB5T1

VDS33

SN65L

SN65LVDS3481Receiver with –4 V to 5 V

SN65LVDS341Receiver with –4 V to 5 V

SN65LVDS3521Receiver with –4 V to 5 V

1

Integrated Termination Available (100-Ω)-SN65LVDTxxx.

*Suggested resale price in U.S. dollars in quantities of 1,000.

Description Tx Rx Signal Signal (Mbps) (ns) (ns) (mA) (kV) (V) Pin/Package(s) Price*

Replacement for Agere BDG1A & BPNGA, 4 — TTL PECL 400 1.2 — 40 3 3.3, 5 16SOIC gull-wing, 7.20

built-in surge protection

Replacement for Agere BDG1A & BDGLA,

power down open circuit o/p

Replacement for Agere BRF1A & BRF2A,

8KΩ Input Impedance

Replacement for Agere BRS2A & BRS2B

Replacement for Agere BRF1A

3.3-V supply alternative to Agere

BRF1A & BRF2A

3.3-V supply alternative to Agere

BRS2A & BRS2B

Dual differential transceiver

Receiver with –4 V to 5

Common-Mode Range, L

Common-Mode Range, L

Common-Mode Range

Common-Mode Range

V — 4 LVDS, LVPECL, LVTTL 400 — 4 23 15 3.3 16SOIC, 16TSSOP 1.60

VDS32 Footprint

VDS48 Footprint

Tx Rx

No. No. Signaling tpd tpd

of of Input Output Rate Typ Typ Max HBM Voltage

—

4

4

—

4

—

4 LVPECL TTL 400 — 2.6 50 3 5 16SOIC gull-wing, 8.65

—

4 LVPECL LVTTL 400 — — 32 3 3.3 16SOIC 8.65

—

4 LVPECL LVTTL 400 — — 32 3 3.3 16SOIC 8.65

—

2 LVPECL, LVPECL, 400 1.2 2.5 35 3 5 8SOIC gull-wing, 7.20

2

4

—

2 LVDS, LVPECL, LVTTL 400 — 4 12 15 3.3 8SOIC 1.15

—

4 LVDS, LVPECL, LVTTL 560 — 6 20 15 3.3 24TSSOP 1.80

—

TTL PECL 400 1.2 — 40 3 3.3, 5 16SOIC gull-wing, 7.20

PECL TTL 400 — 2.5 32 3 5 16SOIC gull-wing, 7.20

PECL TTL 400 — 2.5 32 3 5 16SOIC gull-wing, 7.20

VTTL 8SOIC

VTTL

L

VECL, ECL

PECL, L

LVDS, LVPECL, LVTTL 340 — 6 20 15 3.3 16SOIC, 16TSSOP 1.60

PECL, LVECL, ECL

VECL, ECL

PECL, L

VECL, ECL

PECL, L

L

I

CC

ESD Supply

16SOIC

16SOIC

16SOIC

16SOIC

16SOIC

Texas Instruments 4Q 2006 Interface Selection Guide

Page 6

6

LVDS, xECL, CML

➔

LVDS Selection Guide

Signaling Part-to-Part Tx tpd

No. of No. of Rate Skew Max Typ

Device Description Tx Rx Input Signal Output Signal (Mbps) (ps) (ns)

Single

SN65LVDS1 Driver 1 — LVTTL LVDS 630 — 1.7

SN65LVDS2

SN65LVDS179 Full-Duplex Transceiver, No Enables 1 1 LVDS, LVTTL LVTTL, LVDS 400 — 1.7

SN65LVDS180 Full-Duplex Transceiver, with Enables 1 1 LVDS, LVTTL LVTTL, LVDS 400 — 1.7

Dual

SN65LVDS9638 Driver 2 — LVTTL LVDS 400 800 1.7

SN65LVDS9637 Receiver — 2 LVDS LVTTL 400 1000 —

SN65LVDS049 Transceiver, Driver and Receiver Enable 2 2 LVDS, LVTTL LVTTL, LVDS 400 100 1.3

SN65LVDS050 Transceiver, Driver and Receiver Enable 2 2 LVDS, LVTTL LVDS, LVTTL 400 — 1.7

SN65LVDS051 Transceiver, Driver Enable Only 2 2 LVDS, LVTTL LVDS, LVTTL 400 — 1.7

SN65LVDS1050 Transceiver with 2.7-V Supply 2 2 LVDS, LVTTL LVTTL, LVDS 400 — 1.7

SN65LVDS22 Multiplexed LVDS Repeater 2 2 LVDS LVDS 250 — 4

Quad

SN65LVDS047 Driver with Flow-Through Pinout 4 — LVTTL LVDS 400 1000 1.8

SN65LVDS31 Driver, AM26LS31 Footprint 4 — LVTTL LVDS 400 800 1.7

SN65LVDS3487 Driver, MC34987 Footprint 4 — LVTTL LVDS 400 800 1.7

SN65LVDS391 Driver with Flow-Through Pinout 4 — LVTTL LVDS 630 1500 1.7

SN65LVDS048A Receiver with Flow-Through Pinout — 4 LVDS LVTTL 400 1000 —

SN65LVDS32 Receiver, AM26LS32 Footprint — 4 LVDS LVTTL 400 1000 —

SN65LVDS3486 Receiver, MC3486 Footprint — 4 LVDS LVTTL 400 1000 —

SN65LVDS390

8-Channel

SN65LVDS389 Driver 8 — LVTTL LVDS 630 1500 1.7

SN65LVDS388A

16-Channel

SN65LVDS387 Driver 16 — LVTTL LVDS 630 1500 1.7

SN65LVDS386

1

Integrated termination available (100-Ω) - SN65LVDTx.

1

1

1

1

Receiver — 1 LVDS LVTTL 400 — 1.7

Receiver with Flow-Through Pinout — 4 LVDS LVTTL 630 1000 —

Receiver — 8 LVDS LVTTL 630 1000

Receiver — 16 LVDS LVTTL 630 1000 —

Interface Selection Guide Texas Instruments 4Q 2006

Page 7

LVDS, xECL, CML

LVDS Selection Guide

x

R

tpd Typ Max HBM Voltage

Device (ns) (mA) (kV) (V) Pin/Package(s) Price

Single Family

SN65LVDS1 — 8 15 3.3 8SOIC, 5SOP 0.47

SN65LVDS2

SN65LVDS179 3.7 12 12 3.3 8SOIC, 8VSSOP 1.35

SN65LVDS180 3.7 12 12 3.3 14SOIC, 14TSSOP 1.35

Dual Family

SN65LVDS9638 — 13 8 3.3 8HTSSOP, 8SOIC, 8VSSOP 1.15

SN65LVDS9637 2.1 10 8 3.3 8HTSSOP, 8SOIC, 8VSSOP 1.15

SN65LVDS049 1.9 35 10 3.3 16TSSOP 1.00

SN65LVDS050 3.7 20 12 3.3 16SOIC, 16TSSOP 2.00

SN65LVDS051 3.7 20 12 3.3 16SOIC, 16TSSOP 2.00

SN65LVDS1050 3.7 20 12 2.7 16TSSOP 2.00

SN65LVDS22 4 20 12 3.3 16SOIC, 16TSSOP 2.80

Quad Family

SN65LVDS047 — 26 8 3.3 16SOIC, 16TSSOP 1.30

SN65LVDS31 — 35 8 3.3 16SOIC, 16TSSOP, 16SOP 1.50

SN65LVDS3487 — 35 8 3.3 16SOIC 1.50

SN65LVDS391 — 26 15 3.3 16SOIC, 16TSSOP 1.50

SN65LVDS048A 2.4 15 10 3.3 16SOIC, 16TSSOP 1.30

SN65LVDS32 2.1 18 8 3.3 16SOIC, 16TSSOP, 16SOP 1.50

SN65LVDS3486 2.1 18 8 3.3 16SOIC 1.50

SN65LVDS390

8-Channel Family

SN65LVDS389 — 70 15 3.3 38TSSOP 2.90

SN65LVDS388A

16-Channel Family

SN65LVDS387 — 95 15 3.3 64TSSOP 5.55

SN65LVDS386

1

Integrated termination available (100-Ω)-SN65LVDTx

*Suggested resale price in U.S. dollars in quantities of 1,000.

1

1

1

1

2.6 7 15 3.3 8SOIC, 5SOP 0.47

2.5 18 15 3.3 16SOIC, 16TSSOP 1.50

2.5 40 15 3.3 38TSSOP 2.90

2.5 70 15 3.3 64TSSOP 5.55

I

CC

SD Supply

E

7

➔

*

Texas Instruments 4Q 2006 Interface Selection Guide

Page 8

100 Mbps

200 Mbps

300 Mbps

400 Mbps

500 Mbps

600 Mbps

700 Mbps

Single Dual Quad 8-Channel 16-Channel

LVDM179

LVDM180

LVDM176

LVDM050

LVDM051

LVDM1676

LVDM1677

LVDM22

MLVD2

MLVD3

LVDM320

MLVD200A

MLVD202A

MLVD204A

MLVD205A

MLVD201

MLVD203

MLVD206

MLVD207

M-LVDS Transceivers

M-LVDS Clock Distribution

(see p.42 for table)

LVDM: a version of LVDS with

double the output current

M-LVDS Receivers

LVDM31

MLVD047

MLVD129

MLVD080

MLVD082

MLVD128

8

High

T

ype 1

Type 2

2.4 V

150 mV

50 mV

0 mV

–50 mV

High

Low

Transition Region

Low

V

I

D

2.4 V

➔

Multipoint-LVDS (M-LVDS)

M-LVDS Features

• TIA/EIA-899 standard

• Driver output current

11.3 mA vs. 3.5 mA (LVDS)

••

• Receiver thresholds

••

50 mV vs. 100 mV (LVDS)

• Driver edge rate control

••

1 ns min allows ease-of-stub design

• Contention provisions

Driver short circuit limited to 43 mA

••

••

Drivers, receivers and disabled devices

must limit their bus voltage from

0 to 2.4 V

••

Drivers are tested with 32 contending

nodes

Multipoint LVDS

M-LVDS Devices from TI

• TIA/EIA-899 standard compliant

guarantees true multipoint

• Type 1 receivers: 25-mV hysteresis

to prevent oscillation

Type 2 receivers: internal failsafe

•

(no external bias network)

• –1-V to 3.4-V common mode

• 3.3-V supply operation

M-LVDS for ATCA

• Synchronous ATCA clock signals

(8 kHz, 19.22 MHz and user defined

<100 MHz) use M-LVDS.

Receiver types.

Interface Selection Guide Texas Instruments 4Q 2006

Page 9

Multipoint-LVDS (M-LVDS)

M-LVDS Selection Guide

Tx

No. No. Half/ Signaling Part-to-

1

Device

SN65MLVD2 — 1 1 — M-LVDS LVTTL 200 — — — — — — ✔ Web

SN65MLVD3 — 1 2 — M-LVDS LVTTL 200 — — — — — — ✔ Web

SN65MLVD200A 1 1 1 Half LVTTL, M-LVDS LVTTL, M-LVDS 100 1000 2.5 3.6 24 8 8SOIC ✔ 1.55

SN65MLVD201 1 1 1 Half LVTTL, M-LVDS LVTTL, M-LVDS 200 1000 1.5 4 24 8 8SOIC ✔ 1.85

SN65MLVD202A 1 1 1 Full LVTTL, M-LVDS LVTTL, M-LVDS 100 1000 2.5 3.6 24 8 14SOIC ✔ 1.55

SN65MLVD203 1 1 1 Full LVTTL, M-LVDS LVTTL, M-LVDS 200 1000 1.5 4 24 8 14SOIC ✔ 1.85

SN65MLVD204A 1 1 2 Half LVTTL, M-LVDS LVTTL, M-LVDS 100 1000 2.5 3.6 24 8 8SOIC ✔ 1.55

SN65MLVD205A 1 1 2 Full LVTTL, M-LVDS LVTTL, M-LVDS 100 1000 2.5 3.6 24 8 14SOIC ✔ 1.55

SN65MLVD206 1 1 2 Half LVTTL, M-LVDS LVTTL, M-LVDS 200 1000 1.5 4 24 8 8SOIC ✔ 1.85

SN65MLVD207 1 1 2 Full LVTTL, M-LVDS LVTTL, M-LVDS 200 1000 1.5 4 24 8 14SOIC ✔ 1.85

SN65MLVD047 4 0 — Half LVTTL M-LVDS 200 1000 1.5 — 60 12 16SOIC, ✔ 1.45

SN65MLVD128 8 1 — — LVTTL M-LVDS 200 800 1.5 1.5 140 8 48TSSOP ✔ 3.80

SN65MLVD129 8 2 — — LVTTL M-LVDS 200 800 1.5 1.5 140 8 48TSSOP ✔ 3.80

SN65MLVD080 8 8 1 Half LVTTL, LVDS LVTTL, M-LVDS 250 1000 2.4 6 180 8 64TSSOP ✔ 4.75

SN65MLVD082 8 8 2 Half LVTTL, LVDS LVTTL, M-LVDS 250 1000 2.4 6 180 8 64TSSOP ✔ 4.75

SN65LVDM179 1 1 — Full LVTTL, LVDM LVTTL, LVDM 500 1000 1.7 3.7 15 12 8SOIC, — 1.70

SN65LVDM05022 2 — Full LVTTL, LVDM LVTTL, LVDM 500 1000 1.7 3.7 27 12 16SOIC, — 2.20

SN65LVDM22 2 2 — — LVDM LVDM 250 — 4 4 27 12 16SOIC, — 2.50

SN65LVDM31 4 0 — — LVCMOS LVDM 150 1000 2.3 — 40 12 16SOIC — 1.55

of of Rx Full Rate Part Skew Typ Typ Max HBM Pin/ Standard

Tx Rx Type Duplex Input Signal Output Signal (Mbps) Max (ps) (ns) (ns) (mA) (kV) Package(s) Compliance Price*

tpd

Rx

tpd

I

ESD TIA/EIA-899

CC

16TSSOP

8VSSOP

16TSSOP

16TSSOP

9

➔

SN65LVDM1676 16 16 — Half LVTTL, LVDM LVTTL, LVDM 630 1000 2.5 3 175 15 64TSSOP — 7.75

1

Supply voltage for all devices listed above is 3.3 V and temperature range is –40 to 85°C. New products are listed in bold red.

2

Automotive version available, temperature range of –40 to 125°C Preview products are listed in bold blue.

*Suggested resale price in U.S. dollars in quantities of 1,000.

Resources For a complete list of resources (evaluation modules, data sheets and application notes), visit interface.ti.com

Literature Number Description

Application Notes

SLLA106 TIA/EIA-485 and M-LVDS, Power and Speed Comparison

SLLA088A Transmission at 200 Mbps in VME Card Cage Using LVDM (Rev. A)

SLLA108 Introduction to M-LVDS (TIA/EIA-899)

SLLA121 Interoperability of M-LVDS and BusLVDS

SLLA119 Wired-Logic Signaling with M-LVDS

SLLA127 M-LVDS Signaling Rate Versus Distance

SLLA067A

Part Number Description Price

Evaluation Modules (EVMs)

MLVD20xEVM M-LVDS Evaluation Module 99.00

SN65LVDM31-32BEVM SN65LVDM31-32BEVM Evaluation Module 49.00

Note: IBIS models are available at interface.ti.com

*Suggested resale price in U.S. dollars.

Comparing Bus Solutions

*

Texas Instruments 4Q 2006 Interface Selection Guide

Page 10

10

Magnetic Flux Density vs. Frequency

100E-18

100E-12

100E-6

100E+0

100E+6

0.001 0.01 0.1 1 10 100

MHz

Wb/m

ISO721 Inductive IEC61000-4-9 IEC61000-4-8

2

ISO

721

Isol

ato

rs

➔

Digital Isolators

D

esign Considerations

Reliability — Best-in-class, high voltage

and functional reliability with > 25 years.

agnetic Immunity— Immunity from

M

external magnetic fields to prevent data

corruption is a critical consideration for

industrial applications. 1E6 times higher

magnetic immunity than inductive couplers.

Signaling rate — TI offers digital isolators

with the highest signaling rates of up to

150 Mbps.

Jitter — To ensure signal integrity,

jitter reduction is a priority. ISO72xx products

offer the lowest jitter with 1-ns jitter at

150-Mbps PRBS NRZ data input.

Key Features

• 4000-V

••

UL 1577, IEC 60747-5-2

peak

isolation

(VDE 0884, Rev. 2)

••

IEC 61010-1 and CSA approved

••

50-kV/µs transient immunity

• Signaling rate 0 Mbps to 150 Mbps

••

Low propagation delay

••

Low pulse skew

(pulse-width distortion)

• Low-power sleep mode

• High-electromagnetic immunity

• Low-input current requirement of 10 µA

• Fail-safe output

T

echnical Information

he ISO72xx is a family of digital isolators

T

sing the industry’s first application of digital

u

capacitive isolation technology. Digital buffers

apacitively couple data signals through a

c

silicone-dioxide (SiO2) insulation barrier which

provides galvanic isolation of up to 4000 V.

The device receives digital inputs and provides

clean digital outputs while preventing noise

currents and/or excessive voltages from

entering the local ground.

Recently introduced alternative isolation

techniques that use magnetic coupling may

still share the deficiencies of the older optocoupler solutions such as a restricted operating

temperature along with new concerns such as

he absence of a fail-safe output, an inability to

t

operate with DC-only signals and concerns

associated with susceptibility to external

magnetic fields and operating life under highvoltage conditions. TI isolation solutions are

designed to eliminate such problems.

Digital Isolators Selection Guide

Low-Power Transient

Device Description Rating (UL) Mode (Max) (Min) Voltage Price

ISO721 Single channel (TTL)

ISO721M Single channel (CMOS) 2500 V

ISO722 Single channel OUT EN (TTL) 2500 V

ISO722M Single channel OUT EN (CMOS)

ISO150 Dual channel bi-directional 1500 V

ISO7220A Dual channel uni-directional (TTL) 2500 V

ISO7220C Dual channel uni-directional (TTL)

ISO7220M Dual channel uni-directional (CMOS) 2500 V

ISO7221A Dual channel bi-directional (TTL) 2500 V

ISO7221C Dual channel bi-directional (TTL)

ISO7221M Dual channel bi-directional (CMOS) 2500 V

*Suggested resale price in U.S. dollars in quantities of 1,000.

Interface Selection Guide Texas Instruments 4Q 2006

Isolation Sleep Data Rate Immunity Supply

µs 3.3 V, 5 V 1.65

2500 V

2500 V

2500 V

2500 V

RMS

RMS

RMS

RMS

RMS

RMS

RMS

RMS

RMS

RMS

RMS

No

Yes 150 Mbps 25 kV/µs 3.3 V, 5 V 1.65

Yes 100 Mbps 25 kV/µs 3.3 V, 5 V 1.75

es

Y

No 80 Mbps 1.6 kV/µs 5 V 8.10

No 1 Mbps 25 kV/µs 3.3 V, 5 V 1.10

No

No 150 Mbps 25 kV/µs 3.3 V, 5 V 2.50

No 1 Mbps 25 kV/µs 3.3 V, 5 V 1.10

No

No 150 Mbps 25 kV/µs 3.3 V, 5 V 2.50

100 Mbps

150 Mbps 25 kV/µs 3.3 V, 5 V 1.75

25 Mbps

25 Mbps

25 kV/

25 kV/µs 3.3 V, 5 V 2.00

25 kV/µs 3.3 V, 5 V 2.00

New products are listed in

Preview products are listed in bold blue.

*

bold red.

Page 11

RS-485/422

11

➔

D

esign Considerations

Interoperability — In general, RS-485 is a

superset of RS-422. Compliance with the

TIA/EIA standard will ensure reliable data

communication in a variety of networks,

including Modbus, INTERBUS, PROFIBUS,

BACnet and a variety of proprietary protocols.

Robustness — RS-485 is a robust interface

standard for use in industrial environments.

It features a wide common mode range of

–7 V to 12 V. Parts from TI are available with

ESD protection up to 30 kV.

Reliability — Integrated fail-safe circuitry

protects the bus from interpreting noise as

valid data when short-circuit, open-circuit or

idle line fault conditions occur.

Speed and Distance — Low noise coupling

of differential signaling with twisted-pair

cabling and wide common-mode voltage

RS-485/422 Family of Products

range allows data exchange at signaling rates

of up to 50 Mbps or to distances of several

20 percent of the characteristic impedance

of the cable and can vary from 90 Ω to 120 Ω.

kilometers at lower rates.

Technical Information

Line Loading — RS-422 is capable of support-

ing one driver and up to 10 receivers on the bus

line. Standard RS-485 is capable of supporting

up to 32 unit loads or nodes on the bus line.

However, there are reduced unit load devices

available that can support up to 256 devices.

Termination — A multipoint bus architecture

requires termination at both ends of the bus

line. The termination resistors must be within

Resources F

Literature Number Description

Application Notes

SLLA036B Interface Circuits for TIA/EIA-485 (RS-485)

SLLA070C 422 and 485 Standards Overview and System Configurations

SLLA112 RS-485 for E-Meter Applications

SLLA177 PROFIBUS Electrical-Layer Solutions

SLLA169 Use Receiver Equalization to Extend RS-485 Data Communications

SLLA143 RS-485 for Digital Motor Control Applications

Note: IBIS models are available at interface.ti.com

or a complete list of resources (evaluation modules, data sheets and application notes), visit interface.ti.com

• The main difference between RS-422 and

RS-485 is the multidrop and multipoint

bus architecture—that is, one driver to

many receivers and many drivers to many

receivers, respectively.

• Typical signaling rates and distances for

these standards are up to 10 Mbps or up

to 1.2 km. TI offers devices capable of

reaching signaling rates of up to 50 Mbps.

Texas Instruments 4Q 2006 Interface Selection Guide

Page 12

12

RS-485/422

➔

RS-485/422 Selection Guide

S

No. of Supply Rate ESD Receiver

Dr/Rx (V) Enables Device1Features (Mbps) (kV) Fail-Safe Nodes Package(s) Price

DE, RE HVD12 3.3V Supply – Low-Speed Slew-Rate Control 1 15 Short, Open, Idle 256 8-PDIP, 8-SOIC 1.75

D

3.3

3 to 5

5 DE, RE HVD3082E Low Power Mode, Optimized for Low-Speed 0.2 15 Short, Open, Idle 256 8-PDIP, 8-SOIC, 8-MSOP 0.90

5

Half-Duplex

1/1

3.3

Full-Duplex

2/2

3/3 Separate DIR LBC170 FAST-20 SCSI, Skew: 3ns 30 12 Open 32 20-SOIC, 16-SSOP 4.10

3/3

4/0 Complementary LBC172 Low Power 10 2 — 32 16-PDIP, 20-SOIC 1.80

4/0

0/4 Complementary LBC173 Low Power 10 2 Open 32 16-PDIP, 16-SOIC 1.15

0/4

1

These devices use the temperature prefixes:

*Suggested resale price in U.S. dollars in quantities of 1,000.

5

Triple

Quad-Drivers

Quad-Receivers

E, RE HVD11 3.3V Supply – Low-Speed Slew-Rate Control 10 15 Short, Open, Idle 256 8-PDIP, 8-SOIC 1.80

DE, RE HVD10 3.3V Supply – High-Speed Signaling 25 15 Short, Open, Idle 64 8-PDIP, 8-SOIC 1.85

DE, RE HVD08 Wide Supply Range: 3 to 5.5V 10 15 Short, Open, Idle 256 8-PDIP, 8-SOIC 1.90

D

E, RE HVD3085E Low Power Mode, Optimized for Mid-Speed 1 15 Short, Open, Idle 256 8-PDIP, 8-SOIC, 8-MSOP 0.90

DE, RE HVD3088E Low Power Mode, Optimized for High-Speed 10 15 Short, Open, Idle 256 8-PDIP, 8-SOIC, 8-MSOP 1.00

DE, RE HVD485E Half Duplex Transceiver 10 15 Open 64 8-PDIP, 8-SOIC, 8-MSOP 0.70

DE, RE HVD1176 PROFIBUS Transceiver, EN 50170 40 10 Short, Open, Idle 160 8-SOIC 1.55

DE, RE HVD22 –20V to 25V Common Mode Operation 0.5 16 Short, Open, Idle 256 8-PDIP, 8-SOIC 1.65

DE, RE HVD21 –20V to 25V Common Mode, 5Mbps 5 16 Short, Open, Idle 256 8-PDIP, 8-SOIC 1.65

DE, RE HVD20 –20V to 25V Common Mode, 25Mbps 25 16 Short, Open, Idle 64 8-PDIP, 8-SOIC 1.65

DE, RE HVD23 Receiver Equalization, 160 Meters at 25 Mbps 25 16 Short, Open, Idle 64 8-PDIP, 8-SOIC 1.80

DE, RE HVD24 Receiver Equalization, 500 Meters at 3 Mbps 3 16 Short, Open, Idle 256 8-PDIP, 8-SOIC 1.80

DE, RE HVD07 Strong Driver Outputs – Low Signal Rate 1 16 Short, Open, Idle 256 8-PDIP, 8-SOIC 1.50

DE, RE HVD06 Strong Driver Outputs – Mid Signal Rate 10 16 Short, Open, Idle 256 8-PDIP, 8-SOIC 1.55

DE, RE HVD05 Strong Driver Outputs – Fast Signal Rate 40 16 Short, Open, Idle 64 8-PDIP, 8-SOIC 1.60

DE, RE LBC176 Low Power 10 2 Open 32 8-PDIP, 8-SOIC 0.90

DE, RE LBC176A Low Power, Fast Signaling, ESD Protection 30 12 Open 32 8-PDIP, 8-SOIC 1.20

DE, RE LBC184 Transient Protection, IEC Air, Contact, Surge 0.25 30 Open 128 8-PDIP, 8-SOIC 1.30

DE, RE LBC182 IEC ESD Protection, Air and Contact Tests

DE, RE ALS176 Fast Signaling, Skew: 15ns 35 2 Open 32 8-SOIC 1.26

DE, RE 176B Cost Effective 10 2 None 32 8-PDIP, 8-SOIC, 8-SOP 0.44

No HVD30 3.3V Supply, no Enables, 25Mbps 25 15 Short, Open, Idle 64 8-SOIC 1.80

No HVD31 3.3V Supply, no Enables, 5Mbps 5 15 Short, Open, Idle 256 8-SOIC 1.80

No HVD32 3.3V Supply, no Enables, 1Mbps 1 15 Short, Open, Idle 256 8-SOIC 1.80

No HVD379 Balanced Receivers, Ideal for Interbus 25

DE, RE HVD33 3.3V Supply, with Enables, 25Mbps 25 15 Short, Open, Idle 64 14-SOIC 1.85

DE, RE HVD34 3.3V Supply, with Enables, 5Mbps 5 15 Short, Open, Idle 256 14-SOIC 1.85

DE, RE HVD35 3.3V Supply, with Enables, 1Mbps 1 15

No HVD50 Strong Bus Outputs, no Enables, 25Mbps 25 15 Short, Open, Idle 64 8-SOIC 1.70

No HVD51 Strong Bus Outputs, no Enables, 5Mbps 5 15 Short, Open, Idle 256 8-SOIC 1.70

No HVD52 Strong Bus Outputs, no Enables, 1Mbps 1 15 Short, Open, Idle 256 8-SOIC 1.70

No HVD179 Balanced Receivers, Ideal for Interbus 25 15 None 256 8-SOIC 1.85

No LBC179 Low Power, without Enable 10 2 Open 32 8-PDIP, 8-SOIC 0.85

No

DE, RE HVD53 Strong Bus Outputs, with Enables, 25Mbps 25 15 Short, Open, Idle 64 14-SOIC 1.60

DE, RE HVD54 Strong Bus Outputs, with Enables, 5Mbps 5 15 Short, Open, Idle 256 14-SOIC 1.60

DE, RE HVD55 Strong Bus Outputs, with Enables, 1Mbps 1 15 Short, Open, Idle 256 14-SOIC 1.60

DE, RE

DE, RE ALS180 High Signaling Rate, with Enables 25 2 Open 32 14-SOIC 1.71

DE, RE ALS1177 Dual full-duplex drivers/receivers 10 2 Open 32 16-PDIP, 16-SOIC 3.24

1DE, 2DE

riple RE

DE, T

Complementary LBC172A High Signaling Rate, High ESD 30 13 — 32 16-PDIP, 16-SOIC, 20-SOIC 2.40

Pairwise LBC174 Low Power 10 2 — 32 16-PDIP, 20-SOIC 1.90

Pairwise

Complementary LBC173A High Signaling Rate, High ESD, Low Power 50 6 Short, Open, Idle 32 16-PDIP, 16-SOIC 1.50

Pairwise LBC175 Low Power 10 2 Open 32 16-PDIP, 16-SOIC 1.10

Pairwise LBC175A High Signaling Rate, High ESD, Low Power 50 6 Short, Open, Idle 32 16-PDIP, 16-SOIC 1.40

Pairwise

LBC179A

LBC180

ALS1178 Dual full-duplex drivers/receivers 10 2 Open 32 16-PDIP, 16-SOIC 3.24

LBC171 FAST-20 SCSI, Skew: 3ns 30 12 Open 32 20-SOIC, 20-SSOP 4.10

LBC174A

175 Standard 10 2 None 32 16-PDIP, 16-SOIC, 16-SOP 2.70

SN55 = military (–55

High Signaling Rate, High ESD w/o Enables

Low Power

High Signaling Rate, High ESD

, with Enables

C to 125° C); SN65 = industrial (–40° C to 85° C); SN75 = commercial (0° C to 70° C).

°

ignaling

0.25

30 10 Open 32 8-PDIP, 8-SOIC 1.10

10

30

15 Open 128 8-PDIP, 8-SOIC 1.05

15 None 256 8-SOIC 1.95

Short, Open, Idle 256 14-SOIC 1.85

2 Open 32 14-PDIP, 14-SOIC, 16-QFN 1.05

13 — 32 16-PDIP, 16-SOIC, 20-SOIC 2.50

*

Interface Selection Guide T

exas Instruments 4Q 2006

Page 13

IR

RS-232

Modem

USB

1394

802.11 1284

DV I

TMS320DM64x™

EMIF

Video

Out

Video

In

PCIJTA G

EMAC

SDRAM

TVP5146

TS5V330

TS3V330

Analog MUX

or 5150A

Flash

AMP

forTHS8135 only

Host CPU

Video DAC

THS8200

THS8135

Head-

TS5A23157

Analog

MUX

phone

Volume

Control

Audio DAC

TLV320DAC26

PCI

Bus

McASP

Speaker

ADSL

Cable

Modem

RS-232

13

➔

RS232: IEC6100-4-2 (Level 4)

ESD-Protected Devices

I offers new RS-232 devices with system-

T

level IEC61000-4-2 electrostatic discharge

(ESD) protection. This protection makes the

RS-232 interface immune to damage from

ESD strikes that may occur while the system

is up and running, such as when a connection

to the RS-232 cable is made. These devices

are drop-in replacements and are functionally

identical to the existing industry-standard

solutions, providing a seamless transition in

the qualification process. These devices meet

the requirements for low-power, high-speed

applications such as portable/consumer,

telecom and computing equipment.

TI offers these new devices in the NiPdAu

Pb-Free finish, which eliminates tin whiskers

that might compromise long-term system reliability. TI offers the space-saving QFN package on select devices in addition to its

already extensive RS-232 portfolio.

Key Features

• No external ESD device needed with

these system-level ESD ratings:

– ±15-kV human-body model (HBM)

– ±8-kV IEC61000-4-2, contact

discharge

– ±15-kV IEC61000-4-2, air-gap

discharge

• Improved drop-in replacement of

popular RS-232 devices

• Data rates meet or exceed today’s

high-speed-application requirements

• Flexible power-saving options enable

longer battery life

• Wide portfolio permits selection of the

right form, fit and functionality

• Industry-leading interface product

space with assured source of supply

• NiPdAu Pb-Free solution provides

whisker-free, reliable package options

• Space-saving QFN package options for

portable applications

pplications

A

• The three-driver, five-receiver MAX3243E

is most popular in applications like PCs,

notebooks and servers.

• The MAX3238E/37E offer

complementary five-driver, threereceiver solutions. These two devices

are popular in PC peripheral

applications like data cables, printers,

modems, industrial control, etc.

• The MAX3227E/23E/22E/21E are

popular in portable handheld

applications due to their reduced bit

count, package size and low power

consumption.

• Higher-speed versions like the

SNx5C3232E/23E/22E/21E meet today’s

higher throughput needs through the

serial interface.

• The MAX232E and MAX213 provide a

higher noise margin for more rugged

environments such as industrial control.

Texas Instruments 4Q 2006 Interface Selection Guide

Personal video recorder application block diagram.

Page 14

14

RS-232

➔

R

S232 Selection Guide

Data Rate ESD Supply I

Device (kbps) Drivers Receivers HBM (kV) Voltage(s) (V) (max) (mA) Pin/Package(s) Price

MAX3223E 500 2 2 IEC61000-4-2 3.3, 5 1 20SOIC, 20SSOP, 20TSSOP, 24QFN 0.84

MAX3222E 500 2 2 IEC61000-4-2 3.3, 5 1 20SOIC, 20SSOP, 20TSSOP, 24QFN 1.00

SN75C3222E 1000 2 2 IEC61000-4-2 3.3, 5 1 20SOIC, 20SSOP, 20TSSOP, 24QFN 2.50

SN65C3222E 1000 2 2 IEC61000-4-2 3.3, 5 1 20SOIC, 20SSOP, 20TSSOP, 24QFN 2.88

SN75C3223E 1000 2 2 IEC61000-4-2 3.3, 5 1 20SOIC, 20SSOP, 20TSSOP, 24QFN 2.11

SN65C3223E 1000 2 2 IEC61000-4-2 3.3, 5 1 20SOIC, 20SSOP, 20TSSOP, 24QFN 2.50

MAX3238E 400 5 3 IEC61000-4-2 3.3, 5 2 28SSOP, 28TSSOP, 32RHB 0.87

MAX3221E 250 1 1 IEC61000-4-2 3.3, 5 1 16SSOP, 16TSSOP 0.88

SN65C3221E 1000 1 1 IEC61000-4-2 3.3, 5 1 16SSOP, 16TSSOP 3.10

SN75C3221E 1000 1 1 IEC61000-4-2 3.3, 5 1 16SSOP, 16TSSOP 2.50

MAX3237E 1000 5 3 IEC61000-4-2 3.3, 5 2 28SSOP, 28TSSOP, 32RHB 0.87

ADM2209E 960 10 6 IEC61000-4-2 Dual 3.3V, 12V 5 38TSSOP TBD

MAX232E 120 2 2 IEC61000-4-2 5 10 38TSSOP, 16PDIP, 16SOIC, 16SSOP 0.39

AX202E

M

MAX207E 120 5 3 IEC61000-4-2 5 20 24SOIC, 24SSOP TBD

MAX208E 120 4 4 IEC61000-4-2 5 20 24PDIP, 24SOIC, 24SSOP TBD

MAX3386E 250 3 2 IEC61000-4-2 VL 1.65V to VCC, 1 20SOIC, 20TSSOP 1.92

SN65C3232E 1000 2 2 IEC61000-4-2 3.3, 5 1 16SOIC, 16SSOP, 16TSSOP 3.92

SN75C3232E 1000 2 2 IEC61000-4-2 3.3, 5 1 16SOIC, 16SSOP, 16TSSOP 3.22

MAX211E 120 4 5 IEC61000-4-2 5 20 20SOIC, 20SSOP, 28SOIC, 28SSOP TBD

MAX3227E 1000 1 1 IEC61000-4-2 3.3, 5 1 16SSOP 1.20

MAX3232E 250 2 2 IEC61000-4-2 3.3, 5 1 16SOIC, 16SSOP, 16TSSOP 0.68

MAX3243E 500 3 5 IEC61000-4-2 3.3, 5 1 28SOIC, 28SSOP, 28TSSOP, 32QFN 0.63

MAX3318E 460 2 2 IEC61000-4-2 2.25, 3 1 20SSOP, 20TSSOP 1.10

MAX213 120 4 5 15KV HBM 5 1 28SOIC, 28SSOP 1.08

MAX202 120 2 2 15KV HBM 5 15 16SOIC, 16TSSOP 0.51

MAX207 120 5 3 15KV HBM 5 20 24SOIC, 24SSOP 0.63

MAX208 120 4 4 15KV HBM 5 20 24PDIP, 24SOIC, 24SSOP 0.96

MAX211 120 4 5 15KV HBM 5 20 28SOIC, 28SSOP 0.63

MAX222 120 2 2 15KV HBM 5 10 18PDIP, 18SOIC 0.74

MAX3221 250 1 1 15KV HBM 3.3, 5 1 16SSOP, 16TSSOP 0.88

MAX3223 250 2 2 15KV HBM 3.3, 5 1 20SOIC, 20SSOP, 20TSSOP 1.12

MAX3232 250 2 2 15KV HBM 3.3, 5 1 16SOIC, 16SSOP, 16TSSOP 0.96

MAX3238 250 5 3 15KV HBM 3.3, 5 2 28SSOP, 28TSSOP 1.20

MAX3243 250 3 5 15KV HBM 3.3, 5 1 28SOIC, 28SSOP, 28TSSOP 0.88

MAX3318 460 2 2 15KV HBM 2.25, 3 2 20SSOP, 20TSSOP 1.58

SN65C23243 250 6 10 15KV HBM 3.3, 5 0.02 48SSOP, 48TSSOP 4.32

SN65C3221

SN65C3223 1000 2 2 15KV HBM 3.3 or 5 1 20SOIC, 20SSOP, 20TSSOP 2.50

SN65C3232 1000 2 2 15KV HBM 3.3 or 5 1 16SOIC, 16SSOP, 16TSSOP 3.02

SN65C3238 1000 5 3 15KV HBM 3.3 or 5 2 28SOIC, 28SSOP, 28TSSOP 3.24

SN65C3243 1000 3 5 15KV HBM 3.3 or 5 1 28SOIC, 28SSOP, 28TSSOP 3.46

SN75C23243 250 6 10 15KV HBM 3.3, 5 0.02 48SSOP, 48TSSOP 3.42

SN75C3221

SN75C3223

SN75C3232 1000 2 2 15KV HBM 3.3 or 5 1 16SOIC, 16SSOP, 16TSSOP 2.79

SN75C3238

SN75C3243 1000 3 5 15KV HBM 3.3 or 5 1 28SOIC, 28SSOP, 28TSSOP 1.51

SN75LP1185 256 3 5 15KV HBM 5, ±12 1 20PDIP, 20SOIC, 20SSOP 1.78

SN75LP196 256 5 3 15KV HBM 5, ±12 1 20PDIP, 20SOIC, 20SSOP, 20TSSOP 1.78

SN75LPE185 256 3 5 15KV HBM 5, ±12 1 24PDIP, 24SOIC, 24SSOP, 24TSSOP 1.89

SN75185 120 3 5 10KV HBM ±12, 5 30 20PDIP, 20SOIC, 20SSOP, 20TSSOP 0.45

SN75196

SN75LV4737A 128 3 5 4KV HBM 3 or 5 20.7 28SSOP 2.61

MAX232 120 2 2 2KV HBM 5 10 16PDIP, 16SO, 16SOIC 0.48

SN75150 120

SN75155 120

SN75188 120 4 2KV HBM –9 25 14PDIP, 14SO, 14SOIC 0.22

*Suggested resale price in U.S. dollars in quantities of 1,000. New products are listed in bold red.

20 2 2 IEC61000-4-2 5 15 16SOIC, 16TSSOP TBD

1

VCC3V to 5.5V

1000

1000

1000 2 2 15KV HBM 3.5 or 5 1 20SOIC, 20SSOP, 20TSSOP 2.38

1000

120

1

1

5

5

2

1

1

1

3

3 10KV HBM ±12, 5 20 20PDIP, 20SOIC 0.68

1

15KV HBM

15KV HBM 3.3 or 5 1 16SOIC, 16SSOP, 16TSSOP 1.94

15KV HBM

2KV HBM

2KV HBM –12 14 8PDIP, 8SOIC 0.72

3.3 or 5 1 16SOIC, 16SSOP, 16TSSOP 2.38

3.3 or 5

–12

C

C

2

22

28SOIC, 28SSOP, 28TSSOP 2.81

8PDIP, 8SOIC 0.72

Preview products are listed in bold blue.

*

Interface Selection Guide Texas Instruments 4Q 2006

Page 15

Smart Card

MMC SD

LAN

Port

Stereo Audio Line In

L

L

R

R

LED

Analog

Phone Line

Antenna

Plug

Satellite

Video Input

CATV

RF

FE

RF

FE

RF

FE

LCD

Display

USB Plug

Keypad

Camera

Video Processor

PCI

/

IF

EMAC

Video Port

Video Port

Video Port

EMIF

Bluetooth

®

Controller

ADSL

/

Cable MODEM

803.11

RS-232

1394 PHY

DVI

/

TMDS

Video

Decoder

3-Ch

DAC

3-Ch

DAC

Stereo Audio

CODEC

Voice

CODEX

ADC

ADC

ADC

3-Ch

Amp

3-Ch

Amp

Tuner

Tuner

Tuner

SDRAM

OFDM

QAM

QPSK

DEMOD

FLASH

CPU

PCI

Interface

IrDA

Video

Encoder

SDRAM FLASH

TV CH3-4 MOD

2-to-4 Wire

Interface

2-to-4 Wire

Interface

AC

Adapter

RS-232

RS-232 Selection Guide (Continued)

Device (kbps) Drivers Receivers HBM (kV) Voltage(s) (V) (max) (mA) Pin/Package Price

Data Rate ESD Supply I

SN75C1406 120 3 3 2KV HBM ± 12, 5 0.45 16PDIP, 16SO, 16SOIC 0.86

SN75C185 120 3 5 2KV HBM ± 12, 5 0.75 20PDIP, 20SOIC 1.08

SN75C188 120 4 — 2KV HBM –12 0.16 14PDIP, 14SO, 14SOIC, 14SSOP 0.31

TL145406 120 3 3 2KV HBM ± 12, 5 20 16PDIP, 16SOIC 0.94

GD65232 120 3 5 — ±9, 5 38 20PDIP, 20SOIC, 20SSOP, 20TSSOP 0.29

GD75232 120 3 5 — ±9, 5 30 20PDIP, 20SOIC, 20SSOP, 20TSSOP 0.27

GD75323 120 5 3 — ± 12, 5 32 20SOIC 0.41

LT1030 120 4 — — –5 1 14PDIP, 14SOIC 1.44

MAX3222 120 2 2 — 3.3, 5 1 20SOIC, 20SSOP, 20TSSOP 1.36

MC1488 120 4 — — –9 25 14PDIP 0.20

MC1489 120 — 4 — 5 26 14PDIP 0.25

MC1489A 120 — 4 — 5 26 14PDIP 0.29

SN65C1154 120 4 4 — — — 20PDIP 3.42

SN65C1406 120 3 3 — ± 12, 5 — 16SOIC 1.80

SN65C3222 120 2 2 — 3.3 or 5 1 20SOIC, 20SSOP, 20TSSOP 3.24

SN75154 120 4 4 — 5 or 12 35 16PDIP, 16SO, 16SOIC 0.72

SN751701 120 1 1 — ± 5, 9, 12 11.9 8SO 1.30

SN75186 120 1 1 — ± 12, 5 — 24SOIC 1.80

SN75189 120 — 4 — 5 26 14PDIP, 14SO, 14SOIC 0.22

SN75189A 120 — 4 — 5 26 14PDIP, 14SO, 14SOIC 0.22

SN752232 120 6 10 — 5 +/-50 48SSOP, 48TSSOP 0.90

SN75C1154 120 4 4 — ± 12, 5 — 20PDIP, 20SO, 20SOIC 0.76

SN75C189 120 — 4 — 5 0.7 14PDIP, 14SO, 14SOIC 0.31

SN75C189A 120 — 4 — 5 0.7 14PDIP, 14SO, 14SOIC, 14SSOP 0.31

SN75C198 120 4 — — –12 0.32 14PDIP, 14SOIC 2.25

SN75C3222 120 2 2 — 3.3 or 5 1 20SOIC, 20SSOP, 20TSSOP 2.81

SN75LBC187 120 3 5 — 5 30 28SSOP 3.60

SN75LBC241 120 4 5 — 5 8 28SOIC 2.16

UA9636A 120 2 — — –12 36 8PDIP, 8SOIC 0.36

UC5170C 120 — — — — — 28PLCC 3.15

UC5180C 120 — 8 — 4.75 to 5.25 35 28PLCC 3.00

UC5181C 120 — 8 — 4.75 to 5.25 35 28PLCC 3.15

*Suggested resale price in U.S. dollars in quantities of 1,000.

CC

15

➔

*

PDA interface application block diagram.

Texas Instruments 4Q 2006 Interface Selection Guide

Page 16

TL16C451

TL16C452

TL16C752B

TL16C2752

TL16C750

TL16PIR552A

TIR1000

TL16PC564B

TL16C754B

T

L16C554A

TL16C2550

TL16C2552

TL16C552A

TL16C550D

TL16C550C

TL16C450

1

2

4

No FIFO 16-Byte 64-Byte Special

Functions

FIFO Memory Size

Channels

16

➔

UARTs (Universal Asynchronous Receiver/Transmitters)

Design Considerations

The UART is a key component of an

asynchronous serial communications system.

For example, all internal modems have their

own UARTs. In this application, parallel data

within the computer is converted by the

UART to serial data before being transferred

to the modem. In addition to PC/peripheral

communication, UARTs can be used for

chip-to-chip communications.

As data transfer speeds have increased to

support applications such as telecommunication base stations, cell phones, PCs, fax

servers and rack modems, the transmission

rate of the UART has become critical to

Key Features

• Single-, dual- and quad-channel devices

• 16- and 64-byte FIFOs available

• 5-, 3.3-, 2.5- and 1.8-V supply

• Clock rates up to 24/20/16-MHz for

1.5/1.25/1.0-Mbps data transfer rates

• Hardware and software autoflow control

• Programmable sleep mode and

low-power mode

• Industrial temperature characterization

preventing system bottlenecks. When a fast

xternal modem is used, designers should be

e

ure the computer’s UART can handle the

s

odem’s maximum transmission rate. For

m

xample, the TL16C550D UART contains a

e

16-byte buffer, enabling it to support higher

sustained transmission rates than the older

8250 UART. To reduce software buffering

and data overruns, TI has added its patented

hardware autoflow control to all new

designs and most existing UARTs. Most

UARTs allow the divisor to be programmed

from 1 to 65,535 and sometimes with an

added predivisor factor of 1, 4, 16 or 64.

UART Family of Products

To accommodate the requirements of diverse

pplications, TI offers a wide portfolio of

a

arallel-to-serial and serial-to-parallel UARTs

p

n highly integrated, space-saving configura-

i

ions that allow designers to increase system

t

performance while decreasing space

requirements.

As one of the world’s leading high-volume

semiconductor manufacturers, TI offers

designers and OEMs the satisfaction of

knowing they are backed by a supplier with

the resources to meet their needs. These

include a dedicated marketing and technical

support team to assist with any issues.

Interface Selection Guide Texas Instruments 4Q 2006

Page 17

Functional block diagram ( for PT and PFB packages)

I

nternal

Data Bus

Autoflow

Control

(AFE)

8

7

S

IN

R

CLK

R

TS

B

AUDOUT

SOUT

CTS

INTRPT

OUT2

OUT1

RI

DCD

DSR

DTR

5

3

2

12

4

–2

47–43

28

A0

A

1

A

2

CS0

C

S1

CS2

ADS

MR

RD1

RD2

WR2

WR1

DDIS

TXRDY

XIN

XOUT

RXRDY

V

CC

V

SS

27

2

6

9

10

11

24

3

5

19

20

16

17

22

23

14

15

29

42

18

D

(7–0)

8

8

38

33

39

40

41

34

31

30

88

8

8

8

8

Power

Supply

S

elect

and

Control

Logic

Receiver

F

IFO

Receiver

S

hift

Register

Receiver

T

iming and

Control

Transmitter

T

iming and

Control

Transmitter

Shift

Register

R

eceiver

Buffer

R

egister

D

ata

Bus

B

uffer

S

e

l

e

c

t

S

e

l

e

c

t

Line

Control

R

egister

Line

S

tatus

Register

Transmitter

Holding

Register

Modem

Control

Register

Modem

Status

Register

Modem

Control

Logic

Interrupt

Enable

Register

Interrupt

Control

Logic

Interrupt

Identification

Register

FIFO

Control

Register

Divisor

L

atch (MS)

Divisor

L

atch (LS)

B

aud

Generator

Transmitter

FIFO

UARTs (Universal Asynchronous Receiver/Transmitters)

UART Selection Guide

Voltage Characterized

Device Channel(s) FIFOs (V) Temp. (°C) Package(s) Description Price

Universal Asynchronous Receiver/Transmitters (UARTs)

TL16C2550 2 16-Byte 1.8/2.5/3.3/5 –40 to 85 32 QFN, 44 PLCC, Dual UART with Programmable Auto-RTS and Auto-CTS 2.80

48 TQFP

TL16C2552 2 16-Byte 1.8/2.5/3.3/5 –40 to 85 32 QFN, 44 PLCC Dual UART with Programmable Auto-RTS and Auto-CTS 3.00

TL16C2752 2 64-Byte 1.8/2.5/3.3/5 — 44 PLCC Dual UART with Customizable Trigger Levels Call

TL16C450 1 None 5 0 to 70 40 DIP, 44 PLCC Single UART 1.50

TL16C451 1 None 5 0 to 70 68 PLCC Single UART with Parallel Port 2.50

TL16C452 2 None 5 0 to 70 68 PLCC Dual UART with Parallel Port 2.55

TL16C550C 1 16-Byte 3.3/5 –40 to 85 40 DIP, 44 PLCC, Single UART with Hardware Autoflow Control 1.75

48 LQFP, 48 TQFP

TL16C550D 1 16-Byte 2.5/3.3/5 –40 to 85 32 QFN Single UART with Hardware Autoflow Control 1.75

48 LQFP, 48 TQFP

TL16C552A 2 16-Byte 5 –40 to 85 68 PLCC, 80 TQFP Dual UART with Parallel Port 3.85

TL16C554A 4 16-Byte 5 –40 to 85 68 PLCC, 80 LQFP Quad UART with Hardware Autoflow Control 6.00

TL16C750 1 16/64-Byte 5 –40 to 85 44 PLCC, 64 LQFP Single UART with Hardware Autoflow Control, Low-Power Modes 3.70

TL16C752B 2 64-Byte 3.3 –40 to 85 48 LQFP, 48 TQFP Dual UART with Hardware Autoflow Control, Low-Power Modes 3.10

TL16C754B 4 64-Byte 3.3/5 –40 to 85 68 PLCC, 80 LQFP Dual UART with Hardware Autoflow Control, Low-Power Modes 8.35

TL16PC564B/BLV 1 16/64-Byte 3.3/5 0 to 70 100 BGA, 100 LQFP Single UART with PCMCIA Interface 5.90/6.10

TL16PIR552 2 16-Byte 5 0 to 70 80 QFP Dual UART with Selectable IR & 1284 Modes 6.10

*Suggested resale price in U.S. dollars in quantities of 1,000.

17

➔

*

TL16C550D Asynchronous Communications Element

Get samples, datasheets, EVMs and reports at: www.ti.com/sc/device/TL16C550D

Asynchronous Communications Element

with Autoflow Control

The TL16C550D is a performance-enhanced

version of TI’s industry-standard TL16C550C

single-channel UART with 16-byte FIFO. The

TL16C550D can support voltages of down to

2.5 V and data transfer rates of up to 1.5

Mbps. Combining these features with an

ultra-small 32-pin QFN package, the

TL16C550D is ideal for a variety of portable

applications.

Key Features

Expanded voltage and package options

•

ideal for small form factors

Lower voltage

•

TL16C550C

• Pin-for-pin replacement for TL16C550C

• Programmable auto-RTS and auto-CTS

(autoflow)

Texas Instruments 4Q 2006 Interface Selection Guide

and higher frequency than

• Up to 24/20/16-MHz clock rates for

up to 1.5/1.25/1-Mbps operation

• Programmable baud-rate generator

allows division to generate internal

16x clock

• Independent clock input receiver

Fully programmable serial interface

•

characteristics

• Available packages: DIP, PLCC,

TQFP and QFN

Applications

• PDAs

• MP3 players

• Gaming systems

• Modems

• Serial ports

elecom

T

•

Functional block diagram.

Page 18

18

➔

CAN (3.3-V and 5-V High-Speed CAN Transceivers)

D

esign Considerations

Bus Protection — Features such as

short-circuit protection, thermal shutdown

protection, glitch-free power-up and powerdown protection, high-ESD protection,

wide common-mode range that provides for

common-mode noise rejection, and currentlimiting circuitry to protect the transceivers

and system from damage during a fault

condition have been incorporated into

these devices.

Electromagnetic Compatibility — An

mportant requirement for products intended

i

for networking applications is that they

behave in a way that does not interfere with

the operation of other nearby components or

systems. TI offers specially designed and

tested transceivers for EM compatibility

without malfunction or degradation of

performance in rugged EM environments.

Compatibility in this definition means both

immunity to external EM fields, and the

limited strength of generated EM fields.

Supply Voltage — In addition to 5-V

transceivers, TI offers 3.3-V transceivers

that accomplish the same tasks with less

than half the power and save on the cost of

an additional voltage regulator in 3.3-V

powered applications.

Technical Information

• ISO11898 specifies the physical-layer

implementation of CAN.

• This specification describes a twisted

wire pair bus with 120-W characteristic

impedance (Zo) and differential signaling

rate of up to 1 Mbps on a 40-meter bus

with multi-drop topology.

CAN Transceiver Selection Guide

Supply I

Voltage Device Description Max (mA) (kV) Protection (V) Temp Range Price*

5.0 SN65HVD251 Improved Drop-In Replacement for the PCA82C250 and PCA82C251 65 ±14 ±36 –40 to 125° C 0.90

5.0

SN65HVD1050 Improved Drop-In Replacement for the TJA1050 with Better ESD 70 ±8 –27 to 40 –40 to 125° C 0.55

3.3 SN65HVD230 3.3-V CAN Bus Transceiver, Standby Mode 67 ±16 –4 to 16 –40 to 85° C 1.35

SN65HVD231 3.3-V CAN Bus Transceiver, Sleep Mode 67 ±16 –4 to 16 –40 to 85° C 1.35

SN65HVD232 3.3-V CAN Bus Transceiver, Cost Effective 67 ±16 –4 to 16 –40 to 85° C 1.30

3.3

SN65HVD233 3.3-V CAN Bus Transceiver, Standby Mode, Diagnostic Loop-back 56 ±16 ±36 –40 to 125° C 1.50

SN65HVD234 3.3-V CAN Bus Transceiver, Standby Mode, Sleep Mode 56 ±16 ±36 –40 to 125° C 1.45

SN65HVD235 3.3-V CAN Bus Transceiver, Standby Mode, Autobaud Loop-back 56 ±16 ±36 –40 to 125° C 1.50

All devices have a signaling rate of 1 Mbps. New products are listed in bold red.

*Suggested resale price in U.S. dollars in quantities of 1,000.

CC

ESD Bus Fault Operating

Selection Guide

Device

DSPs with CAN Controllers (3.3-V Supply Voltage)

TMS320LF2403A TMS320F2802-60 TMS320LC2403A TMS320F2806 TMS320LF2406A TMS320F2808 TMS320LC2406A TMS320F2809

TMS320LF2407A TMS320F2810 TMS320LF2407A TMS320C2810 TMS320F2801 TMS320F2811 TMS320F2801-100 TMS320R2811

TMS320F2801-60 TMS320C2811 TMS320F28016 TMS320F2812 TMS320C2802 TMS320C2812 TMS320F2802-100 TMS320R2812

ARM7 Microprocessors with CAN Controllers (3.3-V Supply Voltage)

TMS470R1A64 TMS470R1A384 TMS470R1A128 TMS470R1B512 TMS470R1A256 TMS470R1B768 TMS470R1A288 TMS470R1B1M

Standard Compliant Protocols

CAN is a serial communications bus for robust

real-time control applications that is rapidly

gaining the attention of industrial process,

test, measurement and control engineers

worldwide. It has excellent error detection

and confinement capabilities, and has the

flexibility to operate either as a primary

backbone data communications network, as a

secondary local embedded system, or as both.

The engineering community is just now

exploring the limits of what this bus can do

when coupled with newly developed intelligent

sensing technologies.

Besides CAN’s high reliability, another of the

main advantages of CAN when compared to

alternative networks, is the availability of

higher layer protocols (HLPs). There are many

CAN-related system development packages

prepared for these HLPs – hardware interface

cards and easy-to-use software packages that

provide system designers with a wide range of

design and diagnostic tools. These compo

nents provide for the rapid development of

complex control applications without building

each node of a system network from scratch.

The HLP relieves a developer from the burden

of dealing with CAN-specific details such as

bit-timing and implementation functions. It

provides standardized communication objects

for real-time data with Process Data Objects

(PDOs) and Service Data Objects (SDOs), and

provides special functions such as a time

stamp, a sync message, and emergency

shut-down procedures as well as network

management, boot-up commands, and error

management.

Among the most popular HLPs are CANopen,

CANkingdom and DeviceNet with applications

ranging from medical equipment to process

control and assembly line coordination.

Interface Selection Guide Texas Instruments 4Q 2006

Page 19

1

2

3

4

5

6

7

8

9

*

0

#

L

CD

Driver

L

VDS302

L

VDS301

CLK DATA

Application

P

rocessor

with

RGB

Video

Interface

Flatlink™ 3G

XGA

SVGA

VGA

HVGA

QVGA

Tx

LVDS301

Rx

LVDS302

Tx

LVDS303

Rx

LVDS304

Tx

LVDS305

Rx

LVDS306

QVGA 240 320

640 200

CIF+ 352 416

352 440

HVGA 320 480

800250

640 320

VGA 480 640

1024 320

WVGA 480 800

SVGA 800600

XGA 1024 768

Resolution (W x H)

XGA

SVGA

VGA

HVGA

QVGA

Tx

LVDS301

Rx

LVDS302

Tx

LVDS303

Rx

LVDS304

Tx

LVDS305

Rx

LVDS306

3-Ch 2-Ch 1-Ch

Flatlink

™

3G

19

➔

FlatLinkTM3G – Display SerDes

for Mobile Phones

FlatLink 3G uses low EMI subLVDS to carry

24-bit color RGB data from applications

processors, such as OMAP™ from TI, to the

LCD Driver. It caters to screen resolutions

from QVGA to XGA.

FPC cabling typically interconnects the

erializer-Transmitter with the display.

S

Compared to parallel signaling, FlatLink 3G

utputs significantly reducing the EMI of the

o

interconnect by over 20 dB. The electromag-

etic emission of the device itself is very low

n

and meets the SAE J1752/3 ‘M’-specification.

FlatLink™ 3G Selection Guide

Device

SN65LVDS301 QVGA-XGA Serializer Transmitter — 27 1755 4-65 — 3 2.10

SN65L

VDS302

SN65LVDS303 QVGA-VGA Serializer Transmitter — 27 810 4-30 — 2 Web

SN65LVDS304 QVGA-VGA Deserializer Receiver 27 — 810 4-30 2 — Web

SN65LVDS305 QVGA-HVGA Serializer Transmitter — 27 405 4-15 — 1 Web

SN65LVDS306 QVGA-HVGA Deserializer Receiver 27 — 405 4-15 1 — Web

*

Suggested resale price in U.S. dollars in quantities of 1,000. New products are listed in bold red.

Texas Instruments 4Q 2006 Interface Selection Guide

Description

QVGA-XGA Deserializer Receiver

Number of Number of Data Serial Data Serial Data

Parallel

Outputs Inputs (MB/s) (MHz) Channels Channels Price

Parallel

Throughout

PLL Frequency

Receiver

Transmitter

27 — 1755 4-65 3 — 2.10

Preview products are listed in bold blue.

*

Page 20

Line Module

Reference

Clock

DSP

Controller

Photo-

diode

Laser

Diode

TIA*

MAC

Framer/

Mapper

PLL Multiplier

NPU/

ASICs

Clock

Buffer

Backplane

SerDes

Frontplane

SerDes

Clock

Buffer

Memory

PA*

LD*

Power

Management

*TIA, PA and LD are in development and not currrently available.

L

VDS

SN65LVDS93/94

S

N65LVDS95/96

SN65LV1023A/1224B

S

N75

L

V

DT1422

S

N75LVDS82/83

10 Gigabit

E

thernet

S

erDes

P

ortfolio

Gigabit

E

thernet/FC

EPON

TLK3114SC

T

LK3104SA

T

LK3104SC

TLK3118

TLK10021

TLK1201AI

T

NETE2201

T

LK2208B

TLK2226

T

LK2201BI

TLK2201AJR

TLK1211

G

eneral

Purpose

TLK3101

T

LK2711

T

LK2701

TLK2501

T

LK1501

TLK4015

T

LK2521

TLK1521

TLK4120

T

LK4250

S

N75LVDS84A/86

20

SerDes (Serial Gigabit Transceivers and LVDS)

➔

The serial gigabit transceiver family of

devices from TI provides low power dissipation while enabling multigigabit transmission

over copper backplanes, cable and optical

links. The transceivers can be used in a

variety of applications, including Gigabit

Ethernet, 10-Gigabit Ethernet modules,

synchronous optical network (SONET) OC-48

and OC-192 based equipment, wireless

infrastructure backplanes and general-purpose

backplane applications.

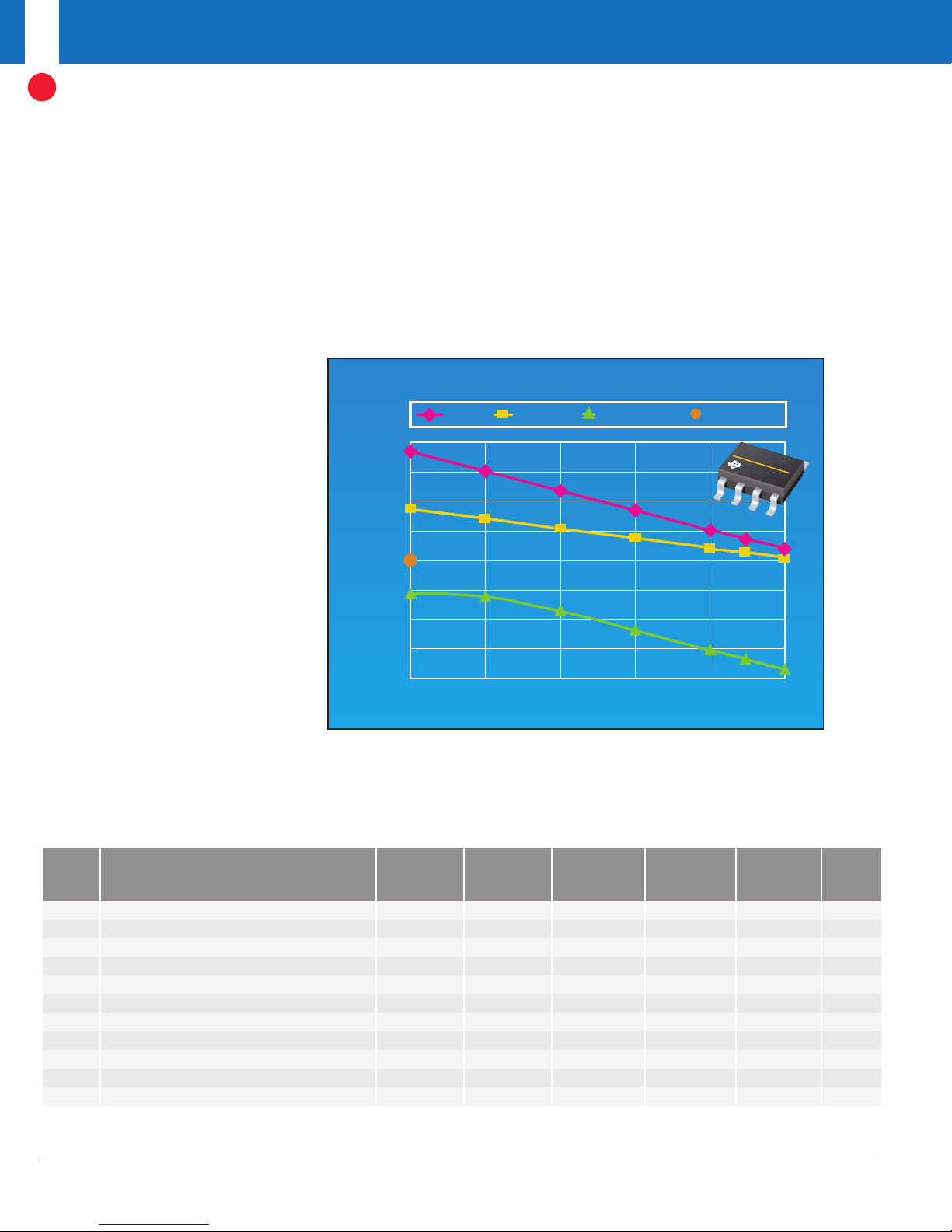

SerDes Solutions—Frontplane/Backplane

TLK1201AI/TLK2226/TLK2208B

Low-Power 1 GbE Transceiver

1 to 1.6 Gbps

(Backplane/Frontplane)

TLK3114SC

TLK2208B—8-Channel Gigabit Ethernet Xcvr (8 x 1-1.3-Gbps)

—10-Gigabit Ethernet Backplane Device XAUI (4 x 3.125 Gbps)

TLK2226—6-Channel Gigabit Ethernet Xcvr (6 x 1-1.3 Gbps)

TLK1201AI—1- to 1.6-Gbps Gigabit Ethernet-Compliant SerDes

TLK3101/TLK2501/TLK1501—600-Mbps to 3.2-Gbps General-Purpose Backplane SerDes

Interface Selection Guide Texas Instruments 4Q 2006

SN65LV1023A/1224B—100 to 660 Mbps—10:1 LVDS SerDes

Page 21

SerDes (Serial Gigabit Transceivers and LVDS)

SerDes (Serial Gigabit Transceivers) Selection Guide

Device Function Data Rate Serial I/F

General Purpose

TLK1501 Single-Ch. 16:1 SerDes 0.6-1.5 Gbps 1 CML 16 LVTTL 200 mW Built-In Testability 8.40

TLK2501 Single-Ch. 16:1 SerDes 1.6-2.5 Gbps 1 CML 16 LVTTL 300 mW Built-In Testability 12.60

TLK2701 Single-Ch. 1.6-2.5 Gbps 1 CML 16 LVTTL 300 mW Built-In Testability 12.60

16:1 SerDes and K Character Control

TLK2711 Single-Ch. 1.6-2.5 Gbps 1 VML 16 LVTTL 350 mW MicroStar Junior™BGA 10.50

TLK3101 Single-Ch. 16:1 SerDes 2.5-3.125 Gbps 1 VML 16 LVTTL 350 mW Built-In Testability 16.85

TLK2521 Single-Ch. 1.0-2.5 Gbps 1 VML 18 LVTTL <550 mW Low Power and 12.60

TLK1521 Single-Ch. 0.6-1.3 Gbps 1 VML 18 LVTTL <350 mW Low Power and 10.50

TLK4120 Four-Ch. 18:1 Serdes 0.5-1.3 Gbps 4 VML 18 LVTTL <350 mW

TLK4250 Four-Ch. 18:1 Serdes 1.0-2.5 Gbps 4 VML 18 LVTTL <550 mW

TLK4015 Four-Ch. of 16:1 Xcvr 0.6-1.5 Gbps/Ch. 4X CML 16 LVTTL/Ch. 1 W Four-Channel Version of TLK1501 29.40

EPON

TLK1211 Single-Ch. 10:1 Gigabit Ethernet 0.6-1.3 Gbps 1 LVPECL 10 LVTTL 200 mW Fast Relock for PON Web

Gigabit Ethernet/FibreChannel

TLK1201AI Single-Ch. 10:1 Gigabit 0.6-1.3 1 LVPECL 10 LVTTL 200 mW Industrial Temperature 4.85

TLK2201BI Single-Ch. 1.2-1.6 Gbps 1 LVPECL 10 LVTTL 200 mW JTAG; 5-Bit DDR Mode, 4.65

TLK2201AJR Single-Ch. 1.0-1.6 Gbps 1 LVPECL 10 LVTTL 200 mW MicroStar Junior 4.25

TLK2208B Eight-Ch. of 10:1 Gigabit 1.0-1.3 Gbps 8 VML 4/5-Bit/Ch. (Nibble 1 W JTAG, MDIO Supported 31.50

TLK2226 Six-Ch. 16:1 Gigabit 1.0-1.3 Gbps 6 VML 4/5-Bit RTBI or RGMII <1.5 W MDIO Supported 19.65

10 Gigabit (XAUI) Ethernet

TLK3104SA Four-Ch. of 2.5-3.125 Gbps 4X 3.125 Gbps 4X 10/8-Bit 700 mW/Ch. JTAG; Programmable 69.30

TLK3104SC Four-Ch. of 3.0-3.125 Gbps 4X 20X622 700 mW/Ch. JTAG, 8b/10b On/Off 126.00

TLK3114SC Four-Ch. of 2.5-3.125 Gbps 4X 3.125 Gbps 4X 10/8-Bit 600 mW/Ch. IEEE 802.3ae 57.75

TLK3118 Four-Ch. 10/8:1 Xcvr w/ 2.5-3.125 Gbps/Ch. 4X 3.125 8/10 HSTLx4 <2 W Full Redundancy for 80.00

TLK10021 Four XAUI to XFI 10 Gbps 1 XFI 4 XAUI 800 mW Built-In Testability Web

LVDS Serdes

SN65LVDS93/94 Four-Ch. 28:4 TX/RX 140-455 Mbps/Ch. 5 LVDS 28 LVTTL 250 mW/Chip Supports Up to 1.82 Gbps 3.45

SN65LVDS95/96 Three-Ch. 21:3 TX/RX 140-455 Mbps/Ch. 4 LVDS 28 LVTTL 250 mW/Chip Supports Up to 1.82 Gbps 3.45

SN65LV1023A/1224B Single-Ch. 10:1 TX/RX 100-660 Mbps 1 LVDS 10 LVTTL <400 mW Low Power Solution 4.60

VDT1422 14:1 Xcvr SerDes 140 Mbps-1.4 Gbps 1 LVDS 14-Bit LVTTL <300 mW Supports Spread Spectrum 3.70

SN75L

SN75LVDS82/83 Four-Ch. 28:4 TX/RX Chipset 0.651-1.428 Gbps 4 LVDS 28 LVTTL 250 mW/Chip Commercial Temp 2.25

VDS84A/86

SN75L

1

CML = Current Mode Logic; VML = Voltage Mode Logic. New products are listed in bold red.

*

Suggested resale price in U.S. dollars in quantities of 1,000. Preview products are listed in bold blue.

16:1 SerDes Packaging

18:1 SerDes Built-In Equalization

18:1 SerDes Built-In Equalization

Ethernet Xcvr Gbps

10:1 Gigabit Industrial Temperature

Ethernet Xcvr Qualified

10:1 Gigabit 5 mm x 5 mm LGA

Ethernet Xcvr

Ethernet Xcvr DDR Mode), 8/10-Bit/Ch.

Ethernet Xcvr 100-FX mode support

10/8:1 Xcvr LVPECL (XAUI) SSTL/HSTL Pre-Emphasis and XAUI I/F

4.1: Xcvr LVPECL LVDS Lines

10/8:1: Xcvr LVPECL (XAUI) SSTL/HSTL Backplane Transceiver

(XAUI) Full Redundancy LVPECL (XAUI) (XGMII) Four Channels (XAUI)

Chipset

Chipset Throughout

Chipset

Three-Ch. 21:3 TX/RX Chipset

0.42-1.428 Gbps

1

3 LVDS 21 LVTTL 250 mW/Chip Commercial Temp 2.10

Parallel I/F Power Special Features Price

Four-Channel Version of TLK1521

Four-Channel Version of TLK2521

(Multiplex Ch. Mode)

(XGMII) Compliant

Throughout

Clocking

24.00

32.00

21

➔

*

Texas Instruments 4Q 2006 Interface Selection Guide

Page 22

TX

Keys

TMDS

Decode

TMDS

Decode

DVI LinkContent

DVI TX

(PC’s D VI Output)

DVI RX

(Displays DVI Input)

Application

Program

S

W

Driver

EDID

PROM

Controller

I

2

C Master

Content

I

2

C

I

2

C

Slave IF

HDCP

Encrypt

HDCP

Encrypt

I

2

C

Slave IF

I

2

C

RX

Keys

22

DVI/PanelBus

™

➔

D

esign Considerations

The Digital Visual Interface (DVI)

Specification, is an industry standard developed by the Digital Display Working Group

DDWG) for high-speed digital connection to

(

digital displays. DVI uses Transition-minimized

DC balanced (TMDS) data signaling. Single

link supports up to 165Mpixels/s – UXGA

FPDs, SXGA DCRTs, 720p and 1080i HDTVs.

High Bandwidth Digital Content

Protection (HDCP)

• Content protection for video sent over DVI

• Implementation of HDCP requires a

license from the Digital Content

Protection Licensing, L.L.C.

(www.digital-cp.com)

HDCP Elements

• Authentication is a process for verifying

that a device is authorized (e.g. licensed)

DVI-HDCP implementation.

to handle protected content.

• Encryption prevents eavesdropping of

protected content.

• Renewability enables revocation of

compromised devices.

PanelBus™ (DVI) Transmitters and Receivers

Voltage Recvr./Trans. Parallel Data Speed I

Device (V) Channels Outputs (Mbps) (mA) Package Description Price

TFP401 3.3 3 48 495 400 100 HTQFP DVI receiver, 165 MHz 4.00

TFP401A

TFP403 3.3 3 48 495 400 100 HTQFP DVI receiver 5.45

TFP410 3.3 3 6 495 250 64 HTQFP DVI transmitter, 165 MHz 3.00

TFP501 3.3 3 48 495 400 100 HTQFP DVI receiver, 165 MHz plus HDCP Call

TFP503

TFP510

TFP513 3.3 3 6 495 250 64 HTQFP DVI transmitter, 165 MHz plus HDCP and embedded HDCP keys Call