Texas Instruments SN74ABT162244DGGR, SN74ABT162244DGVR, SN74ABT162244DL, SN74ABT162244DLR, SNJ54ABT162244WD Datasheet

SN54ABT162244, SN74ABT162244

16-BIT BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCBS238D – JUNE 1992 – REVISED MA Y 1997

D

Members of the Texas Instruments

Widebus

D

Output Ports Have Equivalent 25-Ω Series

Family

Resistors, So No External Resistors Are

Required

D

State-of-the-Art

EPIC-ΙΙB

BiCMOS Design

Significantly Reduces Power Dissipation

D

Latch-Up Performance Exceeds 500 mA Per

JEDEC Standard JESD-17

D

Typical V

(Output Ground Bounce)

OLP

< 1 V at VCC = 5 V, TA = 25°C

D

High-Impedance State During Power Up

and Power Down

D

Distributed VCC and GND Pin Configuration

Minimizes High-Speed Switching Noise

D

Flow-Through Architecture Optimizes PCB

Layout

D

Package Options Include Plastic 300-mil

Shrink Small-Outline (DL), Thin Shrink

Small-Outline (DGG), and Thin Very

Small-Outline (DGV) Packages and 380-mil

Fine-Pitch Ceramic Flat (WD) Package

Using 25-mil Center-to-Center Spacings

description

The ’ABT162244 are 16-bit buffers and line

drivers designed specifically to improve both the

performance and density of 3-state memory

address drivers, clock drivers, and bus-oriented

receivers and transmitters. These devices can be

used as four 4-bit buffers, two 8-bit buffers, or one

16-bit buffer . These devices provide noninverting

outputs and symmetrical active-low outputenable (OE

) inputs.

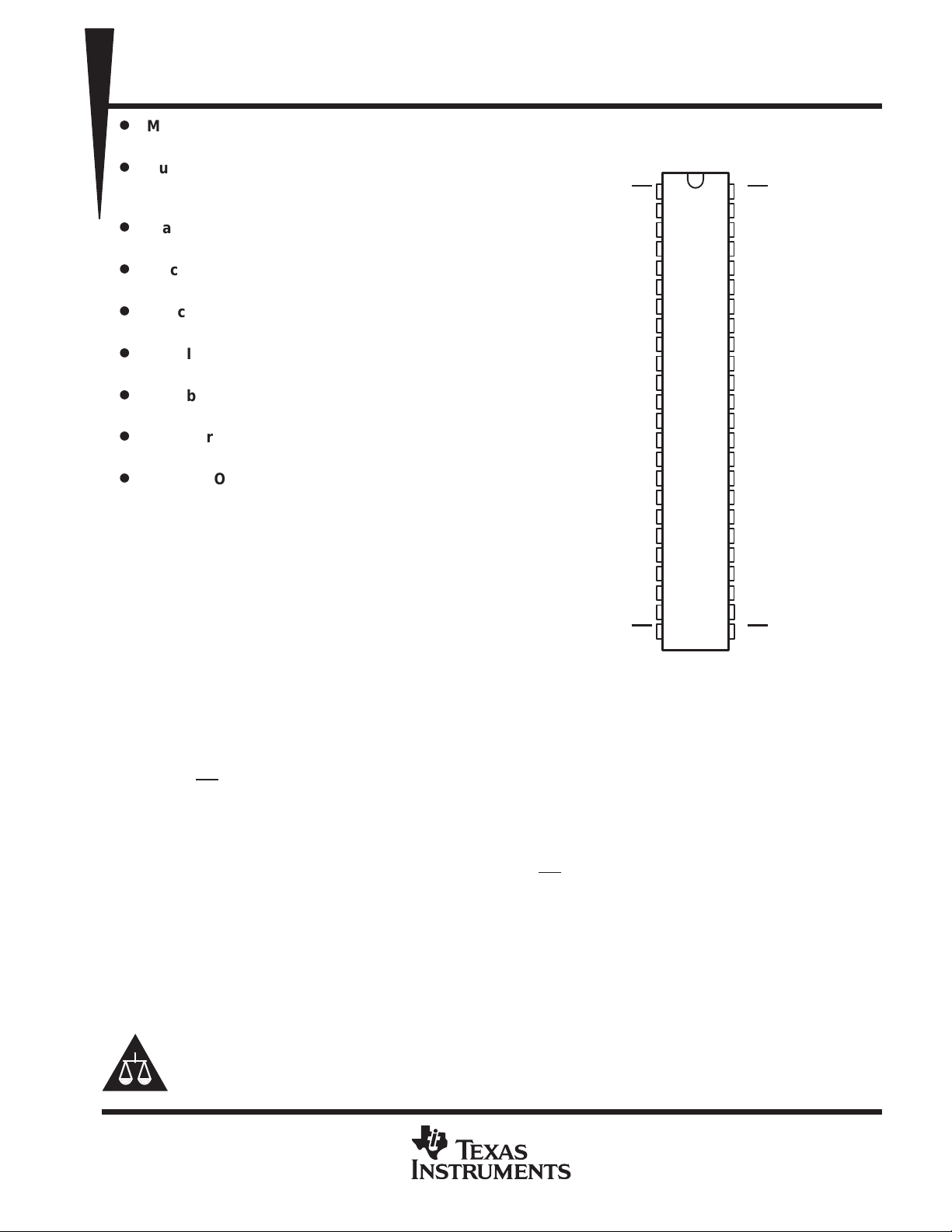

SN54ABT162244 . . . WD PACKAGE

SN74ABT162244 . . . DGG, DGV, OR DL PACKAGE

1OE

1Y1

1Y2

GND

1Y3

1Y4

V

CC

2Y1

2Y2

GND

2Y3

2Y4

3Y1

3Y2

GND

3Y3

3Y4

V

CC

4Y1

4Y2

GND

4Y3

4Y4

4OE

(TOP VIEW)

1

48

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

40

10

39

11

38

12

37

13

36

14

35

15

34

16

33

17

32

18

31

19

30

20

29

21

28

22

27

23

26

24

25

2OE

1A1

1A2

GND

1A3

1A4

V

CC

2A1

2A2

GND

2A3

2A4

3A1

3A2

GND

3A3

3A4

V

CC

4A1

4A2

GND

4A3

4A4

3OE

The outputs, which are designed to source or sink up to 12 mA, include equivalent 25-Ω series resistors to

reduce overshoot and undershoot.

When V

is between 0 and 2.1 V , the device is in the high-impedance state during power up or power down.

CC

However, to ensure the high-impedance state above 2.1 V, OE should be tied to VCC through a pullup resistor;

the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN54ABT162244 is characterized for operation over the full military temperature range of –55°C to 125°C.

The SN74ABT162244 is characterized for operation from –40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus and EPIC-ΙΙB are trademarks of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1997, Texas Instruments Incorporated

1

SN54ABT162244, SN74ABT162244

16-BIT BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCBS238D – JUNE 1992 – REVISED MA Y 1997

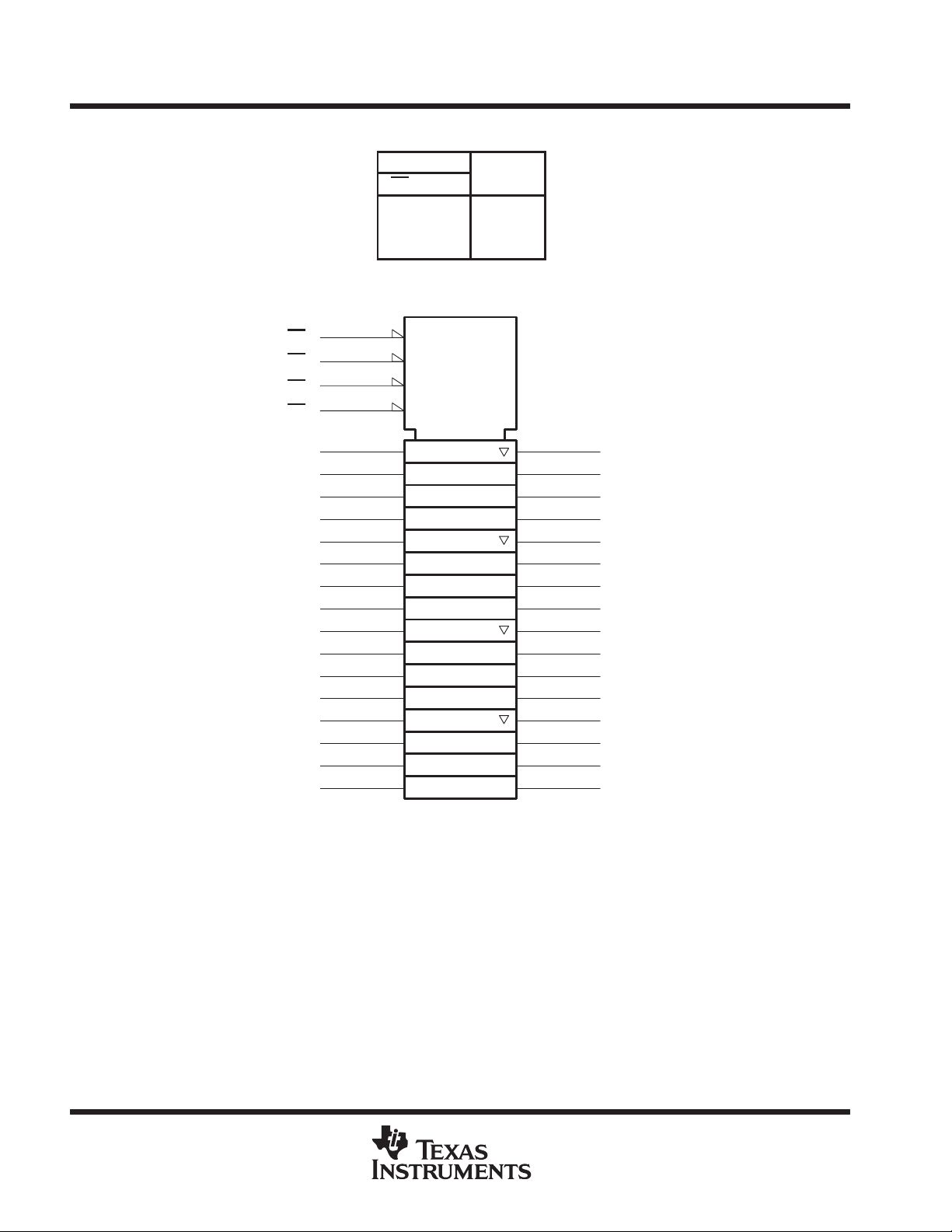

FUNCTION TABLE

(each 4-bit buffer)

INPUTS

OE

L H H

L LL

H X Z

OUTPUT

A

Y

logic symbol

†

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

3A1

3A2

3A3

3A4

4A1

4A2

4A3

4A4

1

48

25

24

47

46

44

43

41

40

38

37

36

35

33

32

30

29

27

26

EN1

EN2

EN3

EN4

11

12

13

14

16

17

19

20

22

23

2

1Y1

3

1Y2

5

1Y3

6

1Y4

8

2Y1

9

2Y2

2Y3

2Y4

3Y1

3Y2

3Y3

3Y4

4Y1

4Y2

4Y3

4Y4

1

1

1

2

1

3

1

4

1OE

2OE

3OE

4OE

†

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

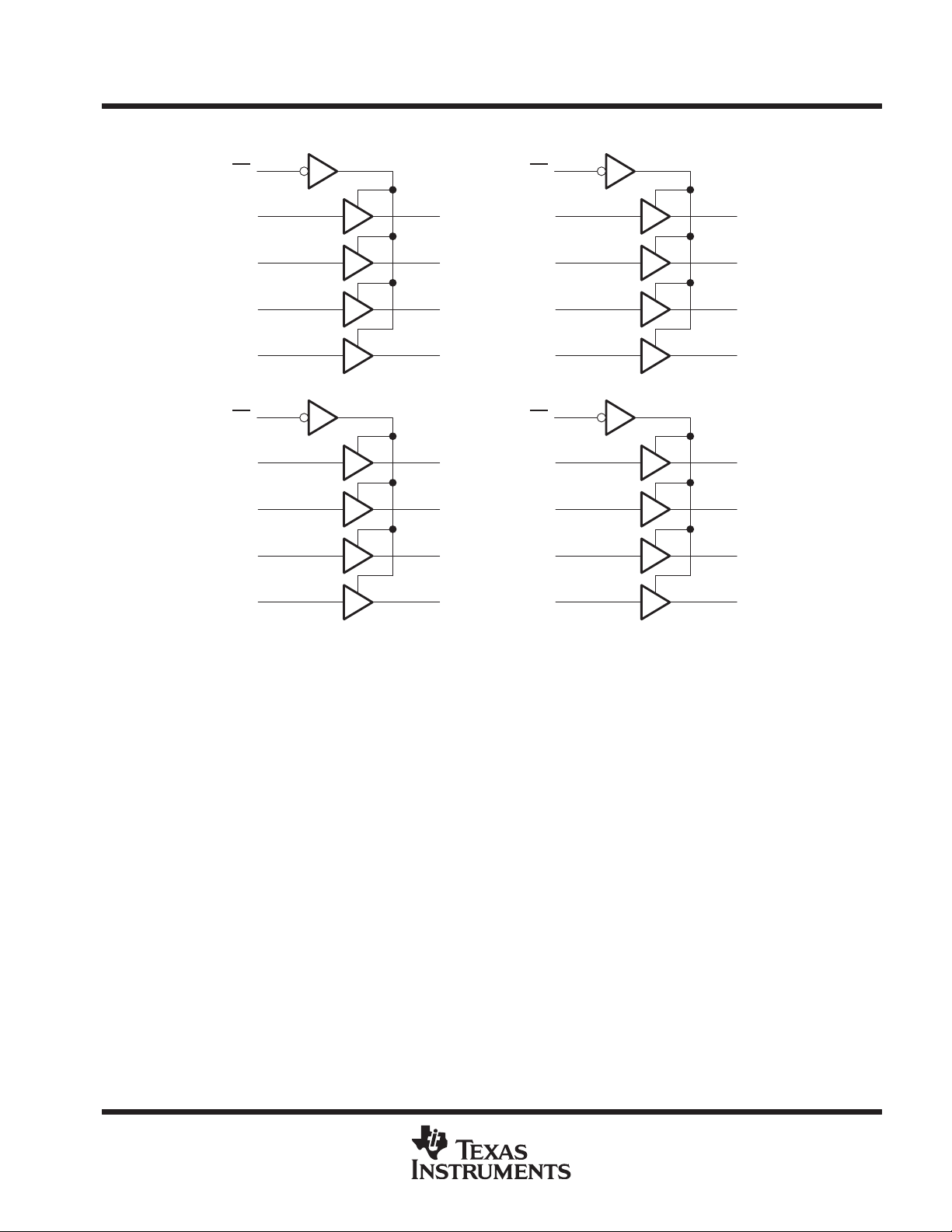

logic diagram (positive logic)

SN54ABT162244, SN74ABT162244

16-BIT BUFFERS/DRIVERS

WITH 3-STATE OUTPUTS

SCBS238D – JUNE 1992 – REVISED MA Y 1997

1OE

1A1

1A2

1A3

1A4

2OE

2A1

2A2

2A3

2A4

1

47

46

44

43

48

41

40

38

37

11

12

25

3OE

2

1Y1

3

1Y2

5

1Y3

6

1Y4

8

2Y1

9

2Y2

2Y3

2Y4

3A1

3A2

3A3

3A4

4OE

4A1

4A2

4A3

4A4

36

35

33

32

24

30

29

27

26

13

14

16

17

19

20

22

23

3Y1

3Y2

3Y3

3Y4

4Y1

4Y2

4Y3

4Y4

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, VCC –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, VI (see Note 1) –0.5 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range applied to any output in the high or power-off state, VO –0.5 V to 5.5 V. . . . . . . . . . . . . . . . . . .

Current into any output in the low state, I

Input clamp current, I

Output clamp current, I

(V

< 0) –18 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IK

I

(V

OK

< 0) –50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

O

Package thermal impedance, θJA (see Note 2): DGG package 89°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DGV package 93°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DL package 94°C/W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. The package thermal impedance is calculated in accordance with EIA/JEDEC Std JESD51.

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

30 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

Loading...

Loading...