Page 1

User’s G uide

2005 Mixed Signal Products

SLAU056E

Page 2

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI’s terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty . Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. To minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third-party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application

solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Interface interface.ti.com Digital Control www.ti.com/digitalcontrol

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

Telephony www.ti.com/telephony

Video & Imaging www.ti.com/video

Wireless www.ti.com/wireless

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright 2005, Texas Instruments Incorporated

Page 3

About This Manual

Related Documentation From Texas Instruments

Preface

Read This First

This manual discusses modules and peripherals of the MSP430x4xx family of

devices. Each discussion presents the module or peripheral in a general

sense. Not all features and functions of all modules or peripherals are present

on all devices. In addition, modules or peripherals may differ in their exact

implementation between device families, or may not be fully implemented on

an individual device or device family.

Pin functions, internal signal connections and operational paramenters differ

from device-to-device. The user should consult the device-specific datasheet

for these details.

Related Documentation From Texas Instruments

For related documentation see the web site http://www.ti.com/msp430.

FCC Warning

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested

for compliance with the limits of computing devices pursuant to subpart J of

part 15 of FCC rules, which are designed to provide reasonable protection

against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case

the user at his own expense will be required to take whatever measures may

be required to correct this interference.

Notational Conventions

Program examples, are shown in a special typeface.

iii

Page 4

Glossary

Glossary

ACLK Auxiliary Clock See Basic Clock Module

ADC Analog-to-Digital Converter

BOR Brown-Out Reset See System Resets, Interrupts, and Operating Modes

BSL Bootstrap Loader See www.ti.com/msp430 for application reports

CPU Central Processing Unit See RISC 16-Bit CPU

DAC Digital-to-Analog Converter

DCO Digitally Controlled Oscillator See FLL+ Module

dst Destination See RISC 16-Bit CPU

FLL Frequency Locked Loop See FLL+ Module

GIE General Interrupt Enable See System Resets Interrupts and Operating Modes

INT(N/2) Integer portion of N/2

I/O Input/Output See Digital I/O

ISR Interrupt Service Routine

LSB Least-Significant Bit

LSD Least-Significant Digit

LPM Low-Power Mode See System Resets Interrupts and Operating Modes

MAB Memory Address Bus

MCLK Master Clock See FLL+ Module

MDB Memory Data Bus

MSB Most-Significant Bit

MSD Most-Significant Digit

NMI (Non)-Maskable Interrupt See System Resets Interrupts and Operating Modes

PC Program Counter See RISC 16-Bit CPU

POR Power-On Reset See System Resets Interrupts and Operating Modes

PUC Power-Up Clear See System Resets Interrupts and Operating Modes

RAM Random Access Memory

SCG System Clock Generator See System Resets Interrupts and Operating Modes

SFR Special Function Register

SMCLK Sub-System Master Clock See FLL+ Module

SP Stack Pointer See RISC 16-Bit CPU

SR Status Register See RISC 16-Bit CPU

src Source See RISC 16-Bit CPU

TOS Top-of-Stack See RISC 16-Bit CPU

WDT Watchdog Timer See Watchdog Timer

iv

Page 5

Register Bit Conventions

Each register is shown with a key indicating the accessibility of the each

individual bit, and the initial condition:

Register Bit Accessibility and Initial Condition

Key Bit Accessibility

rw Read/write

r Read only

r0 Read as 0

r1 Read as 1

w Write only

w0 Write as 0

w1 Write as 1

(w) No register bit implemented; writing a 1 results in a pulse.

The register bit is always read as 0.

h0 Cleared by hardware

Register Bit Conventions

h1 Set by hardware

−0,−1 Condition after PUC

−(0),−(1) Condition after POR

v

Page 6

vi

Page 7

Contents

Contents

1 Introduction 1-1

1.1 Architecture 1-2

1.2 Flexible Clock System 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Embedded Emulation 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Address Space 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.1 Flash/ROM 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.2 RAM 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.3 Peripheral Modules 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.4 Special Function Registers (SFRs) 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.5 Memory Organization 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 System Resets, Interrupts, and Operating Modes 2-1

2.1 System Reset and Initialization 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 Brownout Reset (BOR) 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Device Initial Conditions After System Reset 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Interrupts 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 (Non)-Maskable Interrupts (NMI) 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Maskable Interrupts 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.3 Interrupt Processing 2-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.4 Interrupt Vectors 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.5 Special Function Registers (SFRs) 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Operating Modes 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Entering and Exiting Low-Power Modes 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Principles for Low-Power Applications 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Connection of Unused Pins 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 RISC 16-Bit CPU 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 CPU Introduction 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 CPU Registers 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Program Counter (PC) 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Stack Pointer (SP) 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.3 Status Register (SR) 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.4 Constant Generator Registers CG1 and CG2 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.5 General−Purpose Registers R4 - R15 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Addressing Modes 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1 Register Mode 3-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Indexed Mode 3-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3 Symbolic Mode 3-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.4 Absolute Mode 3-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

Page 8

Contents

3.3.5 Indirect Register Mode 3-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.6 Indirect Autoincrement Mode 3-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.7 Immediate Mode 3-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Instruction Set 3-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Double-Operand (Format I) Instructions 3-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.2 Single-Operand (Format II) Instructions 3-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.3 Jumps 3-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.4 Instruction Cycles and Lengths 3-72

3.4.5 Instruction Set Description 3-74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 FLL+ Clock Module 4-1

4.1 FLL+ Clock Module Introduction 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 FLL+ Clock Module Operation 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 FLL+ Clock features for Low-Power Applications 4-5. . . . . . . . . . . . . . . . . . . . . . . .

4.2.2 LFXT1 Oscillator 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.3 XT2 Oscillator 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.4 Digitally-Controlled Oscillator (DCO) 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.5 Frequency Locked Loop (FLL) 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.6 DCO Modulator 4-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.7 Disabling the FLL Hardware and Modulator 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.8 FLL Operation from Low-Power Modes- 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.9 Buffered Clock Output 4-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.10 FLL+ Fail-Safe Operation 4-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 FLL+ Clock Module Registers 4-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Flash Memory Controller 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 Flash Memory Introduction 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Flash Memory Segmentation 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Flash Memory Operation 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Flash Memory Timing Generator 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 Erasing Flash Memory 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.3 Writing Flash Memory 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.4 Flash Memory Access During Write or Erase 5-14. . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.5 Stopping a Write or Erase Cycle 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.6 Configuring and Accessing the Flash Memory Controller 5-15. . . . . . . . . . . . . . . .

5.3.7 Flash Memory Controller Interrupts 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.8 Programming Flash Memory Devices 5-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Flash Memory Registers 5-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Supply Voltage Supervisor 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 SVS Introduction 6-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 SVS Operation 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.1 Configuring the SVS 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.2 SVS Comparator Operation 6-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.3 Changing the VLDx Bits 6-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.4 SVS Operating Range 6-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 SVS Registers 6-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

Page 9

Contents

7 Hardware Multiplier 7-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1 Hardware Multiplier Introduction 7-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2 Hardware Multiplier Operation 7-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.1 Operand Registers 7-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.2 Result Registers 7-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.3 Software Examples 7-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.4 Indirect Addressing of RESLO 7-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.5 Using Interrupts 7-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3 Hardware Multiplier Registers 7-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8 DMA Controller 8-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.1 DMA Introduction 8-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2 DMA Operation 8-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.1 DMA Addressing Modes 8-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.2 DMA Transfer Modes 8-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.3 Initiating DMA Transfers 8-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.4 Stopping DMA Transfers 8-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.5 DMA Channel Priorities 8-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.6 DMA Transfer Cycle Time 8-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.7 Using DMA with System Interrupts 8-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.8 DMA Controller Interrupts 8-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.9 Using the I2C Module with the DMA Controller 8-17. . . . . . . . . . . . . . . . . . . . . . . . .

8.2.10 Using ADC12 with the DMA Controller 8-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.2.11 Using DAC12 With the DMA Controller 8-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8.3 DMA Registers 8-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9 Digital I/O 9-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.1 Digital I/O Introduction 9-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2 Digital I/O Operation 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.1 Input Register PxIN 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.2 Output Registers PxOUT 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.3 Direction Registers PxDIR 9-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.4 Function Select Registers PxSEL 9-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.5 P1 and P2 Interrupts 9-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.2.6 Configuring Unused Port Pins 9-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

9.3 Digital I/O Registers 9-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10 Watchdog Timer, Watchdog Timer+ 10-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.1 Watchdog Timer Introduction 10-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2 Watchdog Timer Operation 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.1 Watchdog Timer Counter 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.2 Watchdog Mode 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.3 Interval Timer Mode 10-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.4 Watchdog Timer Interrupts 10-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.5 WDT+ Enhancements 10-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.6 Operation in Low-Power Modes 10-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.2.7 Software Examples 10-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10.3 Watchdog Timer Registers 10-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ix

Page 10

Contents

11 Basic Timer1 11-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.1 Basic Timer1 Introduction 11-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2 Basic Timer1 Operation 11-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.1 Basic Timer1 Counter One 11-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.2 Basic Timer1 Counter Two 11-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.3 16-bit Counter Mode 11-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.4 Basic Timer1 Operation: Signal fLCD 11-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.2.5 Basic Timer1 Interrupts 11-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.3 Basic Timer1 Registers 11-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12 Timer_A 12-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.1 Timer_A Introduction 12-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2 Timer_A Operation 12-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.1 16-Bit Timer Counter 12-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.2 Starting the Timer 12-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.3 Timer Mode Control 12-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.4 Capture/Compare Blocks 12-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.5 Output Unit 12-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.2.6 Timer_A Interrupts 12-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12.3 Timer_A Registers 12-19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13 Timer_B 13-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1 Timer_B Introduction 13-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.1.1 Similarities and Differences From Timer_A 13-2. . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2 Timer_B Operation 13-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.1 16-Bit Timer Counter 13-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.2 Starting the Timer 13-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.3 Timer Mode Control 13-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.4 Capture/Compare Blocks 13-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.5 Output Unit 13-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.2.6 Timer_B Interrupts 13-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13.3 Timer_B Registers 13-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14 USART Peripheral Interface, UART Mode 14-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.1 USART Introduction: UART Mode 14-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2 USART Operation: UART Mode 14-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.1 USART Initialization and Reset 14-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.2 Character Format 14-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.3 Asynchronous Communication Formats 14-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.4 USART Receive Enable 14-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.5 USART Transmit Enable 14-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.6 UART Baud Rate Generation 14-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.2.7 USART Interrupts 14-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14.3 USART Registers: UART Mode 14-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

x

Page 11

Contents

15 USART Peripheral Interface, SPI Mode 15-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.1 USART Introduction: SPI Mode 15-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2 USART Operation: SPI Mode 15-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2.1 USART Initialization and Reset 15-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2.2 Master Mode 15-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2.3 Slave Mode 15-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2.4 SPI Enable 15-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2.5 Serial Clock Control 15-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.2.6 SPI Interrupts 15-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15.3 USART Registers: SPI Mode 15-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16 OA 16-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.1 OA Introduction 16-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.2 OA Operation 16-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.2.1 OA Amplifier 16-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.2.2 OA Input 16-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.2.3 OA Output 16-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.2.4 OA Configurations 16-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16.3 OA Registers 16-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17 Comparator_A 17-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.1 Comparator_A Introduction 17-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.2 Comparator_A Operation 17-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.2.1 Comparator 17-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.2.2 Input Analog Switches 17-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.2.3 Output Filter 17-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.2.4 Voltage Reference Generator 17-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.2.5 Comparator_A, Port Disable Register CAPD 17-6. . . . . . . . . . . . . . . . . . . . . . . . . .

17.2.6 Comparator_A Interrupts 17-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17.2.7 Comparator_A Used to Measure Resistive Elements 17-7. . . . . . . . . . . . . . . . . . .

17.3 Comparator_A Registers 17-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18 LCD Controller 18-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.1 LCD Controller Introduction 18-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2 LCD Controller Operation 18-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.1 LCD Memory 18-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.2 Blinking the LCD 18-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.3 LCD Timing Generation 18-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.4 LCD Voltage Generation 18-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.5 LCD Outputs 18-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.6 Static Mode 18-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.7 2-Mux Mode 18-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.8 3-Mux Mode 18-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.2.9 4-Mux Mode 18-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18.3 LCD Controller Registers 18-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xi

Page 12

Contents

19 LCD_A Controller 19-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.1 LCD_A Controller Introduction 19-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2 LCD_A Controller Operation 19-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.1 LCD Memory 19-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.2 Blinking the LCD 19-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.3 LCD_A Voltage And Bias Generation 19-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.4 LCD Timing Generation 19-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.5 LCD Outputs 19-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.6 Static Mode 19-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.7 2-Mux Mode 19-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.8 3-Mux Mode 19-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.2.9 4-Mux Mode 19-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19.3 LCD Controller Registers 19-21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20 ADC12 20-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.1 ADC12 Introduction 20-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2 ADC12 Operation 20-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.1 12-Bit ADC Core 20-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.2 ADC12 Inputs and Multiplexer 20-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.3 Voltage Reference Generator 20-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.4 Auto Power-Down 20-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.5 Sample and Conversion Timing 20-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.6 Conversion Memory 20-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.7 ADC12 Conversion Modes 20-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.8 Using the Integrated Temperature Sensor 20-16. . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.2.9 ADC12 Grounding and Noise Considerations 20-17. . . . . . . . . . . . . . . . . . . . . . . . .

20.2.10 ADC12 Interrupts 20-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

20.3 ADC12 Registers 20-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21 SD16 21-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.1 SD16 Introduction 21-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2 SD16 Operation 21-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.1 ADC Core 21-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.2 Analog Input Range and PGA 21-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.3 Voltage Reference Generator 21-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.4 Auto Power-Down 21-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.5 Channel Selection 21-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.6 Digital Filter 21-6

21.2.7 Conversion Memory Registers: SD16MEMx 21-9. . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.8 Conversion Modes 21-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.9 Conversion Operation Using Preload 21-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.10 Using the Integrated Temperature Sensor 21-15. . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.2.1 1 Interrupt Handling 21-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21.3 SD16 Registers 21-18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xii

Page 13

Contents

22 SD16_A 22-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.1 SD16_A Introduction 22-2

22.2 SD16_A Operation 22-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.1 ADC Core 22-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.2 Analog Input Range and PGA 22-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.3 Voltage Reference Generator 22-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.4 Auto Power-Down 22-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.5 Channel Selection 22-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.6 Analog Input Characteristics 22-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.7 Digital Filter 22-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.8 Conversion Memory Register: SD16MEM0 22-10. . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.9 Conversion Modes 22-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.10 Using the Integrated Temperature Sensor 22-12. . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.2.1 1 Interrupt Handling 22-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22.3 SD16_A Registers 22-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23 DAC12 23-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.1 DAC12 Introduction 23-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.2 DAC12 Operation 23-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.2.1 DAC12 Core 23-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.2.2 DAC12 Reference 23-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.2.3 Updating the DAC12 Voltage Output 23-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.2.4 DAC12_xDAT Data Format 23-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.2.5 DAC12 Output Amplifier Offset Calibration 23-8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.2.6 Grouping Multiple DAC12 Modules 23-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.2.7 DAC12 Interrupts 23-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23.3 DAC12 Registers 23-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24 Scan IF 24-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.1 Scan IF Introduction 24-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2 Scan IF Operation 24-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2.1 Scan IF Analog Front End 24-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2.2 Scan IF Timing State Machine 24-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2.3 Scan IF Processing State Machine 24-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2.4 Scan IF Debug Register 24-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2.5 Scan IF Interrupts 24-27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2.6 Using the Scan IF with LC Sensors 24-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2.7 Using the Scan IF With Resistive Sensors 24-32. . . . . . . . . . . . . . . . . . . . . . . . . . .

24.2.8 Quadrature Decoding 24-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

24.3 Scan IF Registers 24-35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

xiii

Page 14

Chapter 1

Introduction

This chapter describes the architecture of the MSP430.

Topic Page

1.1 Architecture 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Flexible Clock System 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Embedded Emulation 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Address Space 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-1Introduction

Page 15

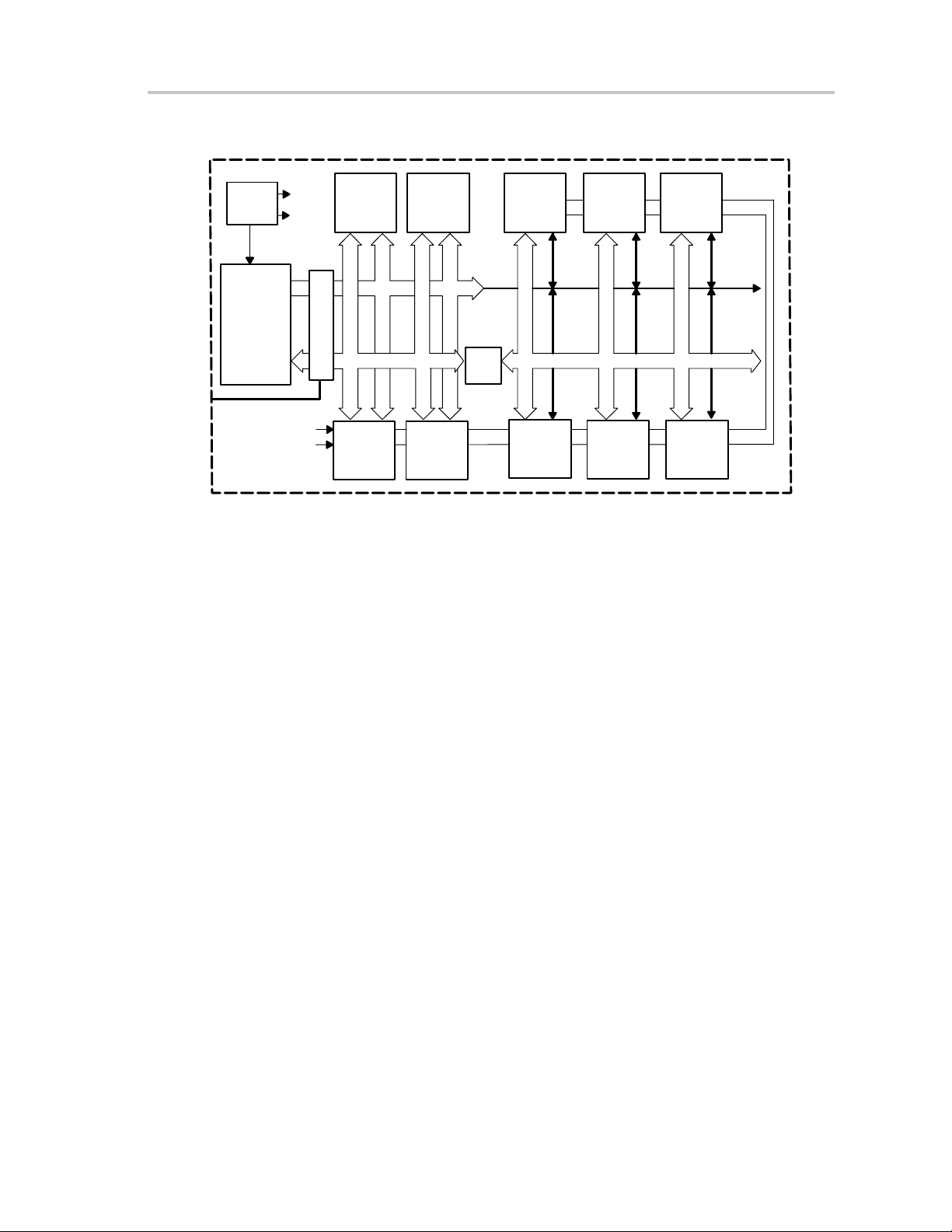

Architecture

1.1 Architecture

The MSP430 incorporates a 16-bit RISC CPU, peripherals, and a flexible clock

system that interconnect using a von-Neumann common memory address

bus (MAB) and memory data bus (MDB). Partnering a modern CPU with

modular memory-mapped analog and digital peripherals, the MSP430 offers

solutions for demanding mixed-signal applications.

Key features of the MSP430x4xx family include:

- Ultralow-power architecture extends battery life

J 0.1-µA RAM retention

J 0.8-µA real-time clock mode

J 250-µA / MIPS active

- High-performance analog ideal for precision measurement

J 12-bit or 10-bit ADC — 200 ksps, temperature sensor, V

J 12-bit dual-DAC

J Comparator-gated timers for measuring resistive elements

J Supply voltage supervisor

- 16-bit RISC CPU enables new applications at a fraction of the code size.

J Large register file eliminates working file bottleneck

J Compact core design reduces power consumption and cost

J Optimized for modern high-level programming

J Only 27 core instructions and seven addressing modes

J Extensive vectored-interrupt capability

- In-system programmable Flash permits flexible code changes, field

upgrades and data logging

1.2 Flexible Clock System

The clock system is designed specifically for battery-powered applications. A

low-frequency auxiliary clock (ACLK) is driven directly from a common 32-kHz

watch crystal. The ACLK can be used for a background real-time clock self

wake-up function. An integrated high-speed digitally controlled oscillator

(DCO) can source the master clock (MCLK) used by the CPU and high-speed

peripherals. By design, the DCO is active and stable in less than 6 µs.

MSP430-based solutions effectively use the high-performance 16-bit RISC

CPU in very short bursts.

Ref

1-2 Introduction

- Low-frequency auxiliary clock = Ultralow-power stand-by mode

- High-speed master clock = High performance signal processing

Page 16

Figure 1−1.MSP430 Architecture

Embedded Emulation

MCLK

ACLK

SMCLK

ACLK

SMCLK

Flash/

ROM

MAB 16-Bit

JTAG/Debug

MDB 16-Bit

Watchdog

Clock

System

RISC CPU

16-Bit

JTAG

1.3 Embedded Emulation

Dedicated embedded emulation logic resides on the device itself and is

accessed via JTAG using no additional system resources.

RAM

Peripheral

Peripheral Peripheral Peripheral

Bus

Conv.

Peripheral

MDB 8-Bit

Peripheral Peripheral

The benefits of embedded emulation include:

- Unobtrusive development and debug with full-speed execution,

breakpoints, and single-steps in an application are supported.

- Development is in-system subject to the same characteristics as the final

application.

- Mixed-signal integrity is preserved and not subject to cabling interference.

1-3Introduction

Page 17

Address Space

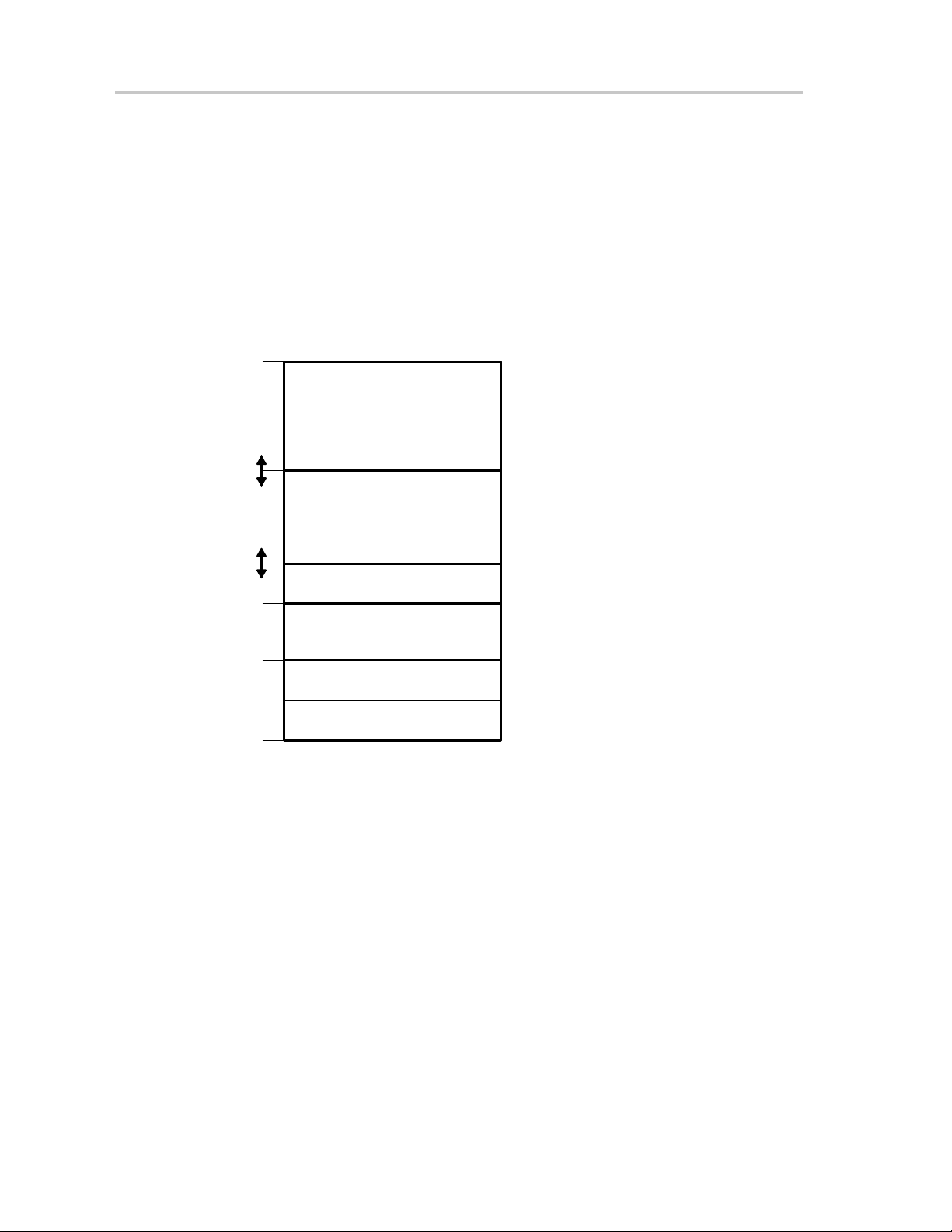

1.4 Address Space

The MSP430 von-Neumann architecture has one address space shared with

special function registers (SFRs), peripherals, RAM, and Flash/ROM memory

as shown in Figure 1−2. See the device-specific data sheets for specific

memory maps. Code access are always performed on even addresses. Data

can be accessed as bytes or words.

The addressable memory space is 64 KB with future expansion planned.

Figure 1−2.Memory Map

Access

0FFFFh

0FFE0h

0FFDFh

0200h

01FFh

0100h

0FFh

010h

1.4.1 Flash/ROM

Word/Byte

Word/Byte

Word/Byte

Word

Byte

Byte

0Fh

0h

Interrupt Vector Table

Flash/ROM

RAM

16-Bit Peripheral Modules

8-Bit Peripheral Modules

Special Function Registers

The start address of Flash/ROM depends on the amount of Flash/ROM

present and varies by device. The end address for Flash/ROM is 0FFFFh.

Flash can be used for both code and data. Word or byte tables can be stored

and used in Flash/ROM without the need to copy the tables to RAM before

using them.

1.4.2 RAM

1-4 Introduction

The interrupt vector table is mapped into the upper 16 words of Flash/ROM

address space, with the highest priority interrupt vector at the highest

Flash/ROM word address (0FFFEh).

RAM starts at 0200h. The end address of RAM depends on the amount of RAM

present and varies by device. RAM can be used for both code and data.

Page 18

1.4.3 Peripheral Modules

Peripheral modules are mapped into the address space. The address space

from 0100 to 01FFh is reserved for 16-bit peripheral modules. These modules

should be accessed with word instructions. If byte instructions are used, only

even addresses are permissible, and the high byte of the result is always 0.

The address space from 010h to 0FFh is reserved for 8-bit peripheral modules.

These modules should be accessed with byte instructions. Read access of

byte modules using word instructions results in unpredictable data in the high

byte. If word data is written to a byte module only the low byte is written into

the peripheral register , ignoring the high byte.

1.4.4 Special Function Registers (SFRs)

Some peripheral functions are configured in the SFRs. The SFRs are located

in the lower 16 bytes of the address space, and are organized by byte. SFRs

must be accessed using byte instructions only. See the device-specific data

sheets for applicable SFR bits.

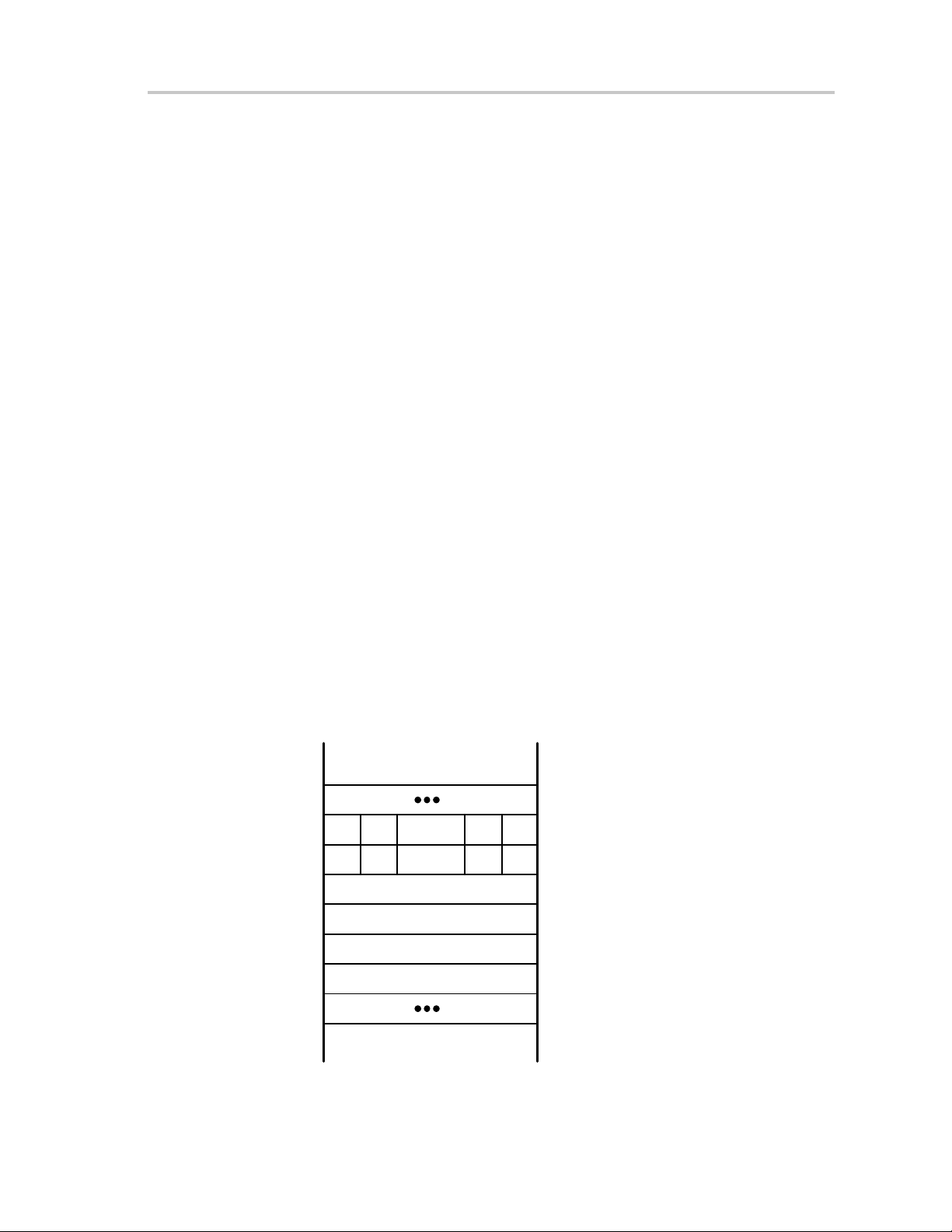

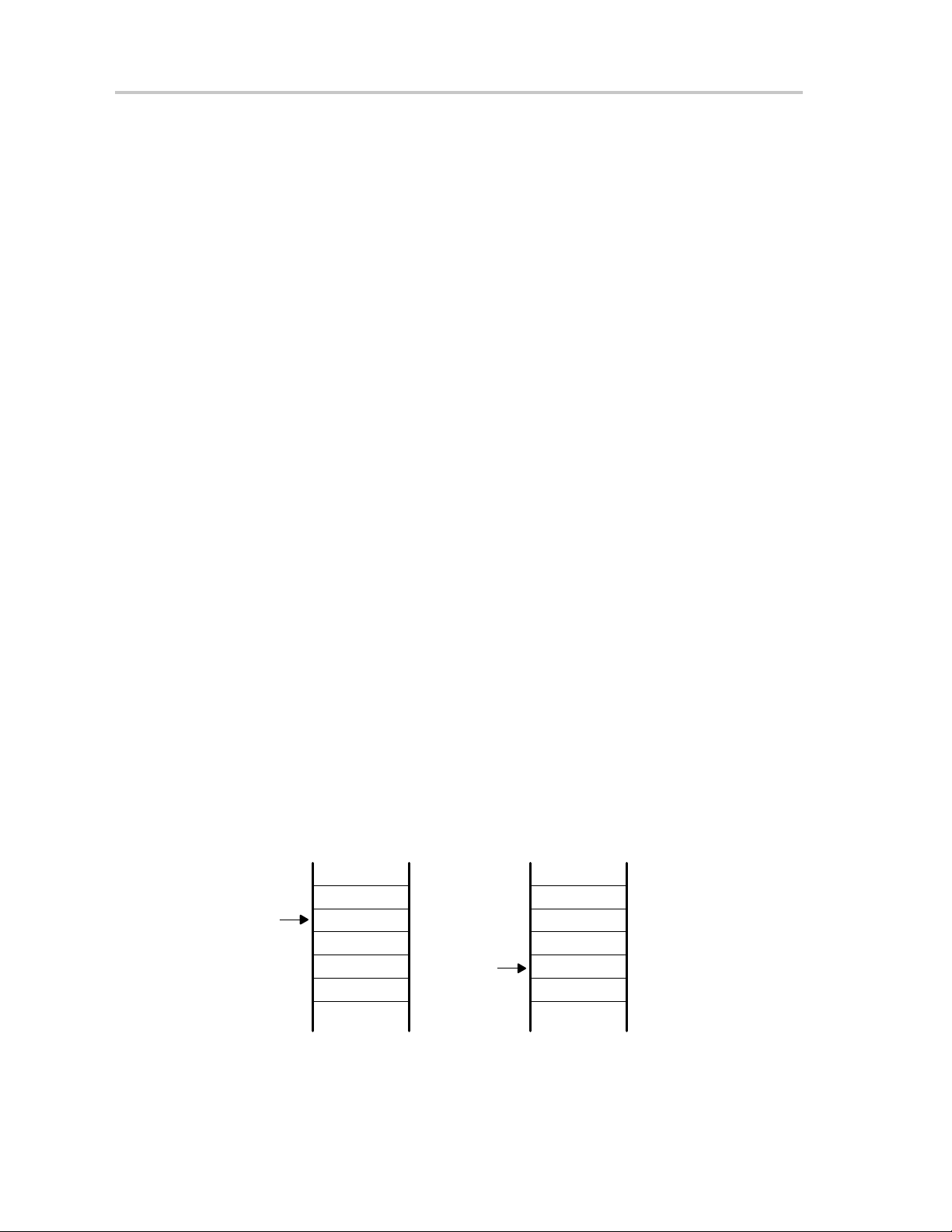

1.4.5 Memory Organization

Address Space

Bytes are located at even or odd addresses. Words are only located at even

addresses as shown in Figure 1−3. When using word instructions, only even

addresses may be used. The low byte of a word is always an even address.

The high byte is at the next odd address. For example, if a data word is located

at address xxx4h, then the low byte of that data word is located at address

xxx4h, and the high byte of that word is located at address xxx5h.

Figure 1−3.Bits, Bytes, and Words in a Byte-Organized Memory

xxxAh

157146. . Bits . .

. . Bits . .9180

Byte

Byte

Word (High Byte)

Word (Low Byte)

xxx9h

xxx8h

xxx7h

xxx6h

xxx5h

xxx4h

xxx3h

1-5Introduction

Page 19

Chapter 2

System Resets, Interrupts,

and Operating Modes

This chapter describes the MSP430x4xx system resets, interrupts, and

operating modes.

Topic Page

2.1 System Reset and Initialization 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Interrupts 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Operating Modes 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Principles for Low-Power Applications 2-16. . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Connection of Unused Pins 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-1System Resets, Interrupts, and Operating Modes

Page 20

System Reset and Initialization

2.1 System Reset and Initialization

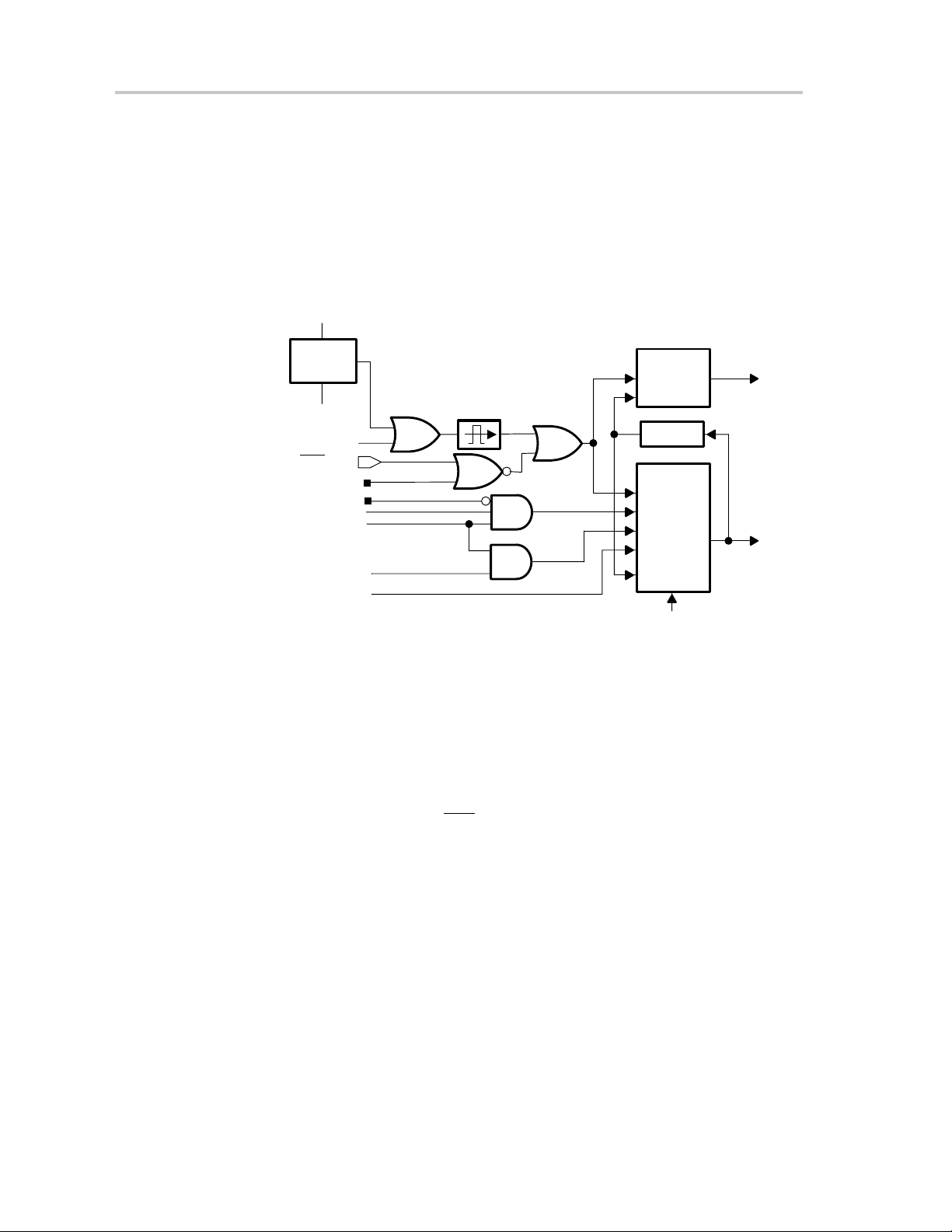

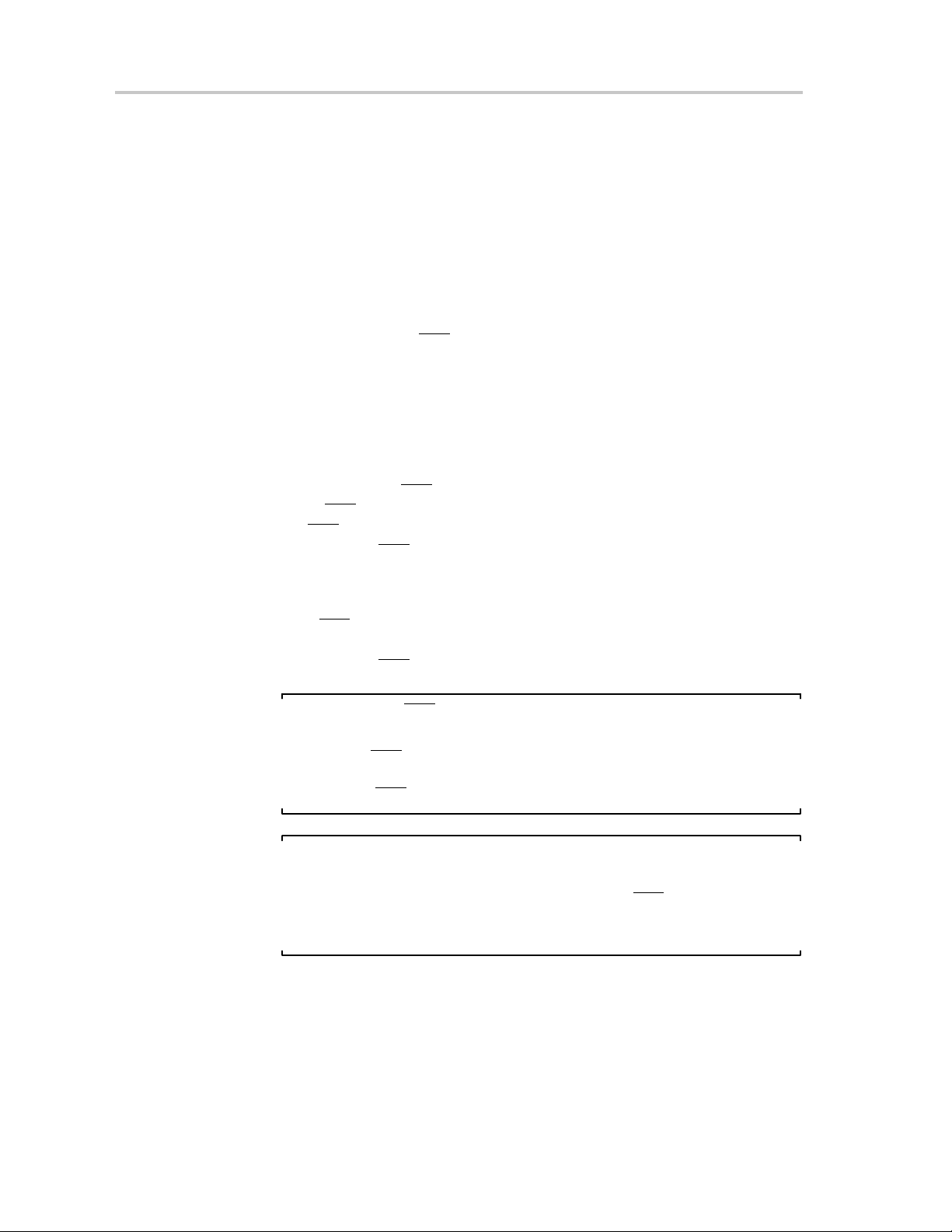

The system reset circuitry shown in Figure 2−1 sources both a power-on reset

(POR) and a power-up clear (PUC) signal. Different events trigger these reset

signals and different initial conditions exist depending on which signal was

generated.

Figure 2−1.Power-On Reset and Power-Up Clear Schematic

V

CC

Brownout

Reset

0 V

0 V

SVS_POR

RST/NMI

WDTNMI

WDTSSEL

WDTIFG

† From watchdog timer peripheral module

†

†

†

WDTQn

†

†

EQU

KEYV

(from flash module)

~ 50us

Resetwd1

Resetwd2

S

R

S

S

S

S

R

POR

Latch

Delay

PUC

Latch

MCLK

POR

PUC

A POR is a device reset. A POR is only generated by the following three

events:

- Powering up the device

- A low signal on the RST/NMI pin when configured in the reset mode

- An SVS low condition when PORON = 1.

A PUC is always generated when a POR is generated, but a POR is not

generated by a PUC. The following events trigger a PUC:

- A POR signal

- Watchdog timer expiration when in watchdog mode only

- Watchdog timer security key violation

- A Flash memory security key violation

2-2 System Resets, Interrupts, and Operating Modes

Page 21

2.1.1 Brownout Reset (BOR)

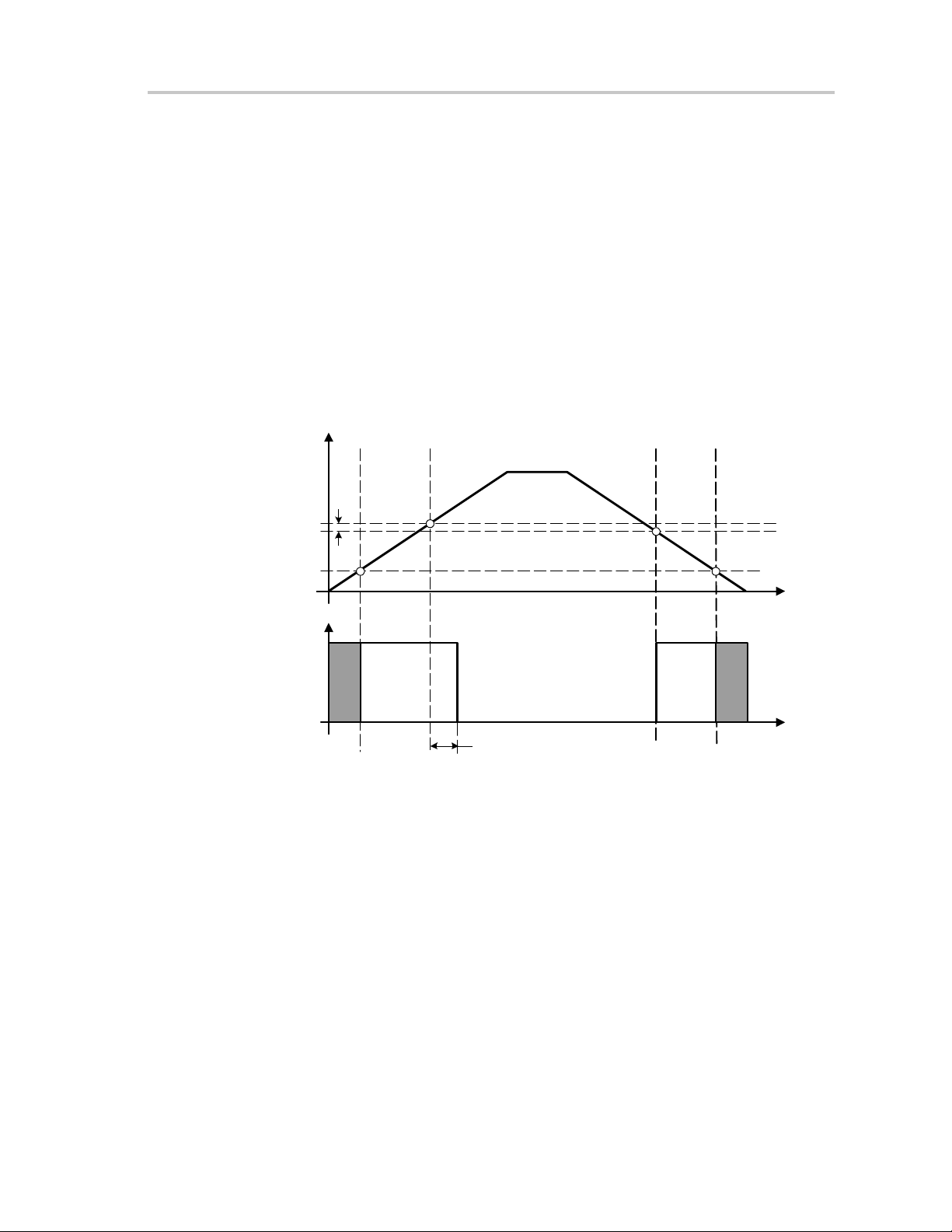

All MSP430x4xx devices have a brownout reset circuit. The brownout reset

circuit detects low supply voltages such as when a supply voltage is applied

to or removed from the VCC terminal. The brownout reset circuit resets the

device by triggering a POR signal when power is applied or removed. The

operating levels are shown in Figure 2−2.

System Reset and Initialization

The POR signal becomes active when VCC crosses the V

remains active until VCC crosses the V

elapses. The delay t

hysteresis V

V

(B_IT−)

Figure 2−2.Brownout Timing

V

V

(B_IT+)

V

(B_IT−)

V

CC(start)

Set Signal for

POR circuitry

hys(B_IT−)

level. It

(BOR)

CC.

(BOR)

hys(B_ IT−)

CC(start)

threshold and the delay t

(B_IT+)

is adaptive being longer for a slow ramping V

ensures that the supply voltage must drop below

to generate another POR signal from the brownout reset circuitry.

V

CC

The

t

(BOR)

As the V

level is significantly above the V

(B_IT−)

level of the POR circuit,

(MIN)

the BOR provides a reset for power failures where VCC does not fall below

V

See device-specific datasheet for parameters.

(MIN).

2-3System Resets, Interrupts, and Operating Modes

Page 22

System Reset and Initialization

2.1.2 Device Initial Conditions After System Reset

After a POR, the initial MSP430 conditions are:

- The RST/NMI pin is configured in the reset mode.

- I/O pins are switched to input mode as described in the Digital I/O chapter.

- Other peripheral modules and registers are initialized as described in their

respective chapters in this manual.

- Status register (SR) is reset.

- The watchdog timer powers up active in watchdog mode.

- Program counter (PC) is loaded with address contained at reset vector

location (0FFFEh). CPU execution begins at that address.

Software Initialization

After a system reset, user software must initialize the MSP430 for the

application requirements. The following must occur:

- Initialize the SP, typically to the top of RAM.

- Initialize the watchdog to the requirements of the application.

- Configure peripheral modules to the requirements of the application.

Additionally, the watchdog timer, oscillator fault, and flash memory flags can

be evaluated to determine the source of the reset.

2-4 System Resets, Interrupts, and Operating Modes

Page 23

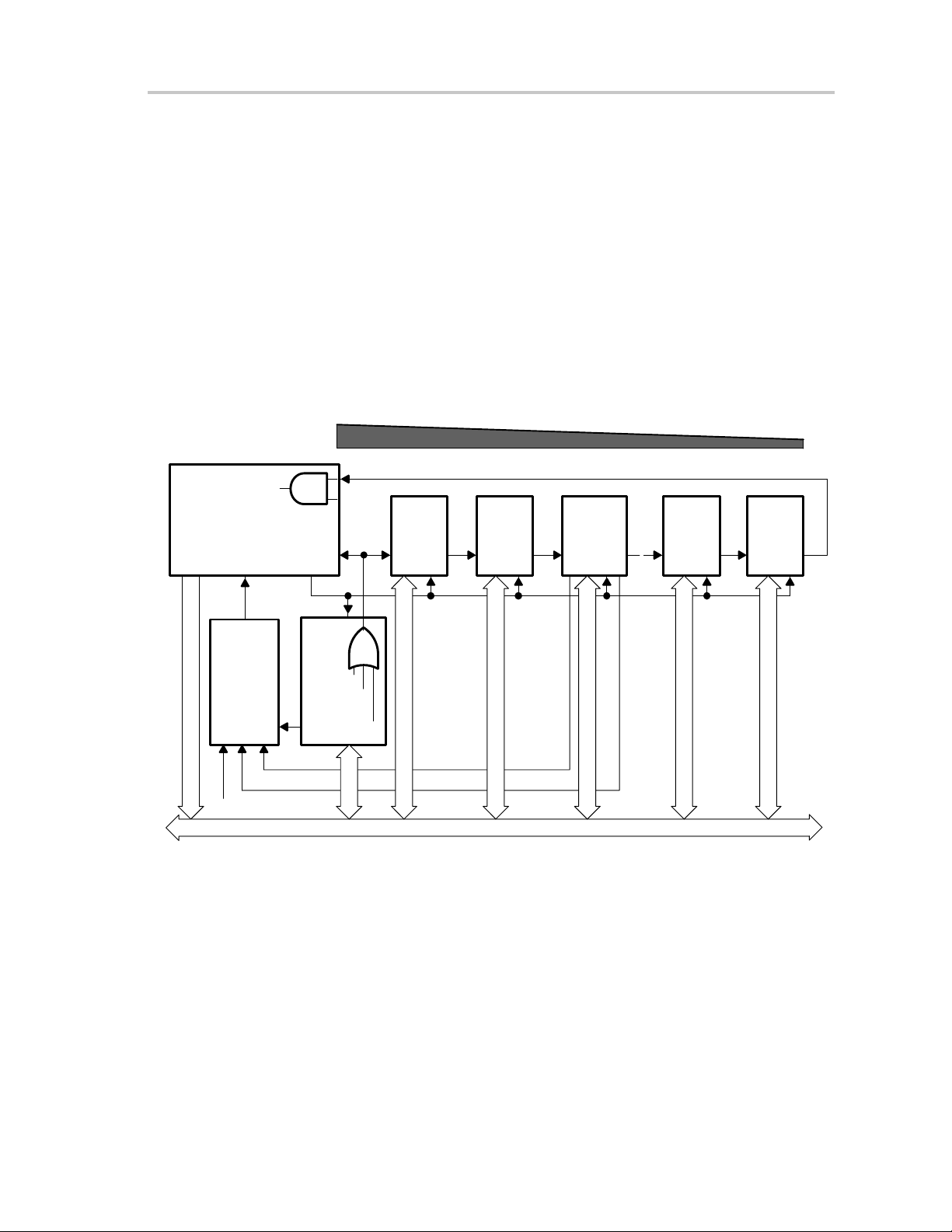

2.2 Interrupts

The interrupt priorities are fixed and defined by the arrangement of the

modules in the connection chain as shown in Figure 2−3. The nearer a module

is to the CPU/NMIRS, the higher the priority . Interrupt priorities determine what

interrupt is taken when more than one interrupt is pending simultaneously.

There are three types of interrupts:

- System reset

- (Non)-maskable NMI

- Maskable

Figure 2−3.Interrupt Priority

System Reset and Initialization

CPU

PUC

PUC

Circuit

WDT Security Key

Flash Security Key

Priority

GMIRS

GIE

NMIRS

OSCfault

Flash ACCV

Reset/NMI

MAB − 5LSBs

High

Module

1

Low

Module

2

12 12 12 12 1

Bus

Grant

WDT

Timer

Module

m

Module

n

2-5System Resets, Interrupts, and Operating Modes

Page 24

System Reset and Initialization

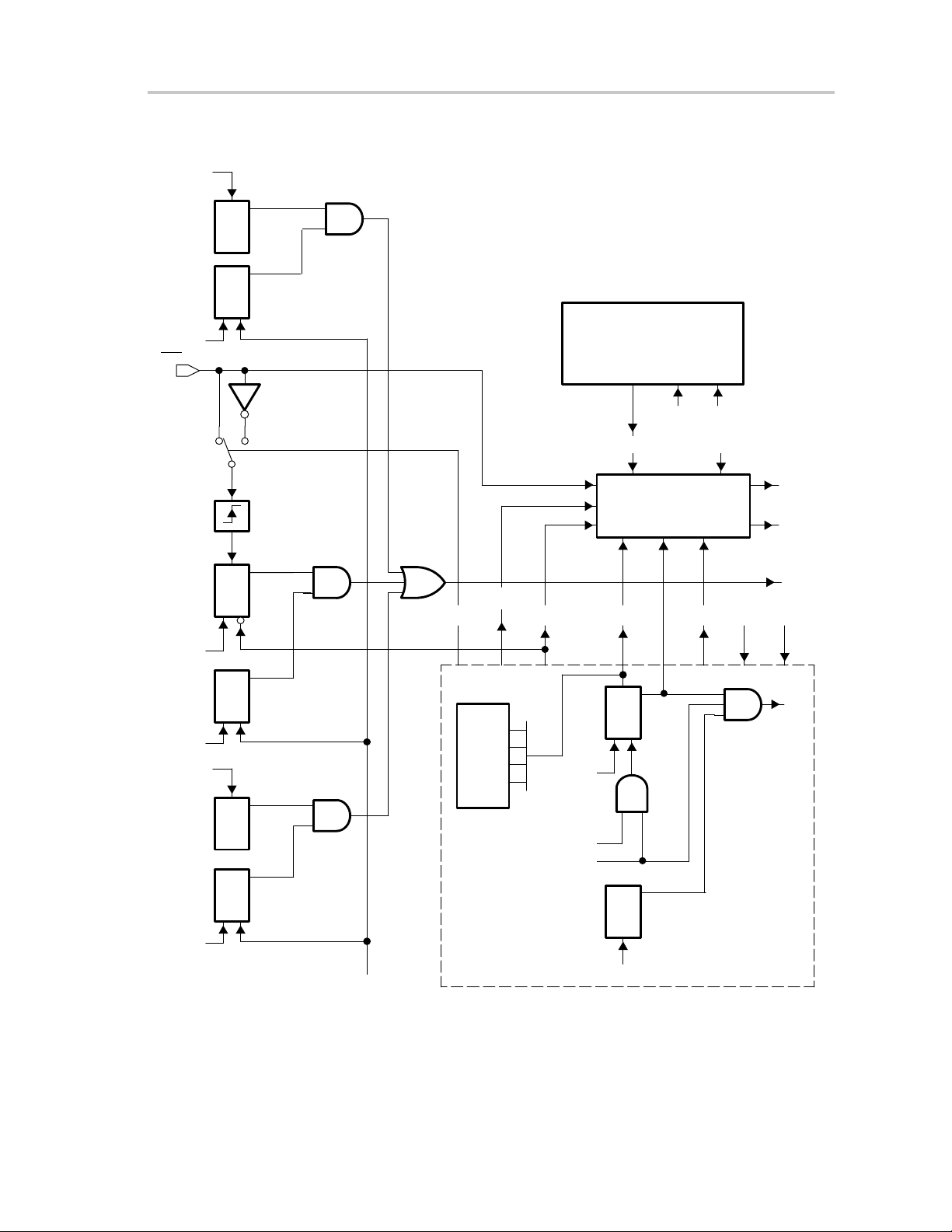

2.2.1 (Non)-Maskable Interrupts (NMI)

(Non)-maskable NMI interrupts are not masked by the general interrupt enable

bit (GIE), but are enabled by individual interrupt enable bits (ACCVIE, NMIIE,

OFIE). When a NMI interrupt is accepted, all NMI interrupt enable bits are

automatically reset. Program execution begins at the address stored in the

(non)-maskable interrupt vector, 0FFFCh. User software must set the required

NMI interrupt enable bits for the interrupt to be re-enabled. The block diagram

for NMI sources is shown in Figure 2−4.

A (non)-maskable NMI interrupt can be generated by three sources:

- An edge on the RST/NMI pin when configured in NMI mode

- An oscillator fault occurs

- An access violation to the flash memory

Reset/NMI Pin

At power-up, the RST/NMI pin is configured in the reset mode. The function

of the RST/NMI pins is selected in the watchdog control register WDTCTL. If

the RST/NMI pin is set to the reset function, the CPU is held in the reset state

as long as the RST/NMI pin is held low. After the input changes to a high state,

the CPU starts program execution at the word address stored in the reset

vector, 0FFFEh.

If the RST/NMI pin is configured by user software to the NMI function, a signal

edge selected by the WDTNMIES bit generates an NMI interrupt if the NMIIE

bit is set. The RST/NMI flag NMIIFG is also set.

Note: Holding RST/NMI Low

When configured in the NMI mode, a signal generating an NMI event should

not hold the RST/NMI pin low . If a PUC occurs from a different source while

the NMI signal is low, the device will be held in the reset state because a PUC

changes the RST/NMI pin to the reset function.

Note: Modifying WDTNMIES

When NMI mode is selected and the WDTNMIES bit is changed, an NMI can

be generated, depending on the actual level at the RST/NMI pin. When the

NMI edge select bit is changed before selecting the NMI mode, no NMI is

generated.

2-6 System Resets, Interrupts, and Operating Modes

Page 25

Figure 2−4.Block Diagram of (Non)-Maskable Interrupt Sources

ACCV

ACCVIFG

S

FCTL1.1

ACCVIE

IE1.5

Clear

System Reset and Initialization

PUC

RST/NMI

IFG1.4

PUC

IE1.4

PUC

OSCFault

IFG1.1

IE1.1

PUC

S

Clear

Clear

S

Clear

NMIIFG

NMIIE

OFIFG

OFIE

NMI_IRQA

WDTTMSEL

WDTNMIES

Counter

WDTNMI

WDT

WDTTMSEL

KEYV

WDTQn EQU

S

IFG1.0

Clear

POR

IRQA

IE1.0

Clear

Flash Module

POR PUC

System Reset

Generator

WDTIE

WDTIFG

V

CC

PUC POR

PUC

POR

NMIRS

IRQ

IRQA: Interrupt Request Accepted

Watchdog Timer Module

PUC

2-7System Resets, Interrupts, and Operating Modes

Page 26

System Reset and Initialization

Oscillator Fault

The oscillator fault signal warns of a possible error condition with the crystal

oscillator. The oscillator fault can be enabled to generate an NMI interrupt by

setting the OFIE bit. The OFIFG flag can then be tested by NMI the interrupt

service routine to determine if the NMI was caused by an oscillator fault.

A PUC signal can trigger an oscillator fault, because the PUC switches the

LFXT1 to LF mode, therefore switching of f the HF mode. The PUC signal also

switches off the XT2 oscillator.

Flash Access Violation

The flash ACCVIFG flag is set when a flash access violation occurs. The flash

access violation can be enabled to generate an NMI interrupt by setting the

ACCVIE bit. The ACCVIFG flag can then be tested by NMI the interrupt service

routine to determine if the NMI was caused by a flash access violation.

2-8 System Resets, Interrupts, and Operating Modes

Page 27

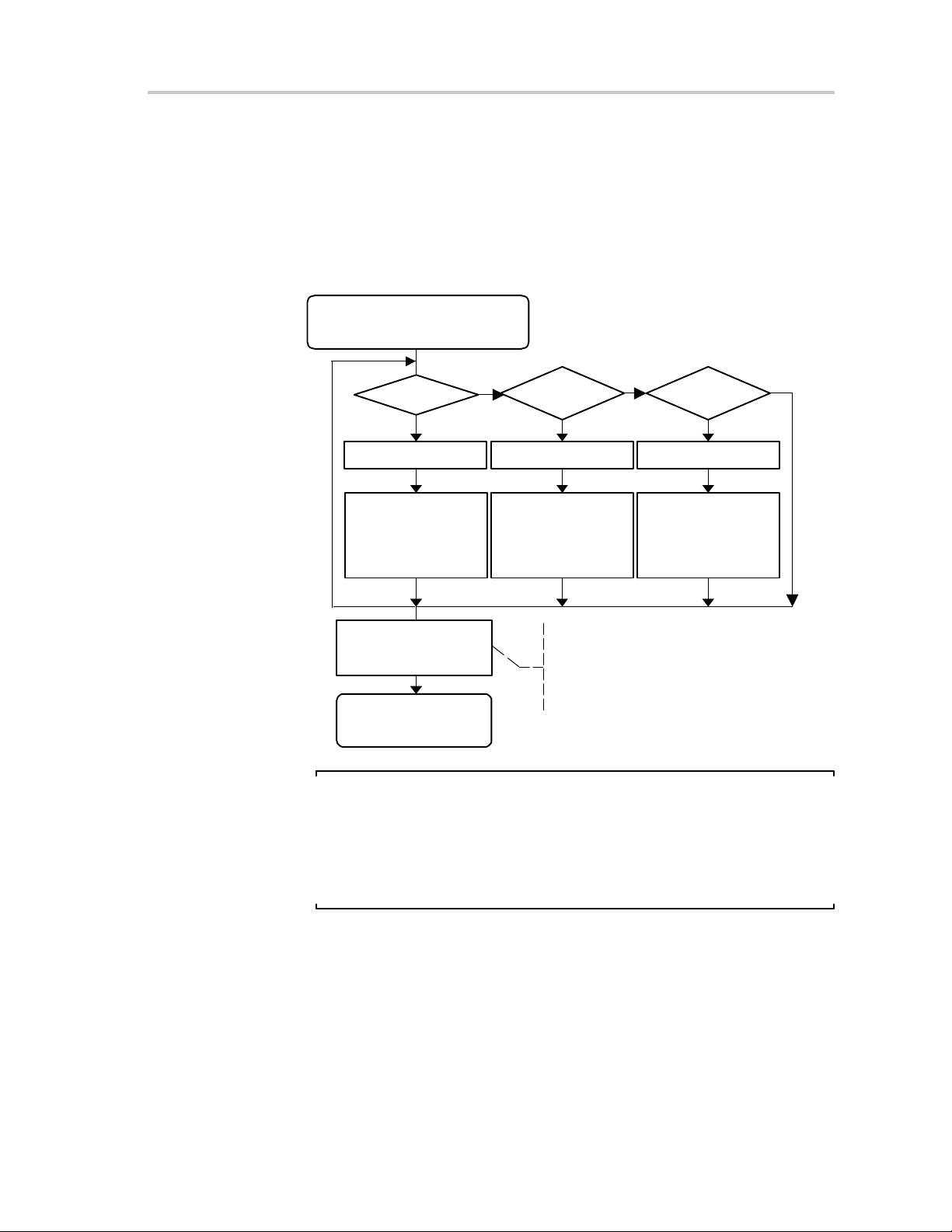

Example of an NMI Interrupt Handler

The NMI interrupt is a multiple-source interrupt. An NMI interrupt automatically

resets the NMIIE, OFIE and ACCVIE interrupt-enable bits. The user NMI

service routine resets the interrupt flags and re-enables the interrupt-enable

bits according to the application needs as shown in Figure 2−5.

Figure 2−5.NMI Interrupt Handler

Start of NMI Interrupt Handler

Reset by HW:

OFIE, NMIIE, ACCVIE

System Reset and Initialization

OFIFG=1

User’s Software,

Oscillator Fault

Handler

Optional

Set NMIIE, OFIE,

ACCVIE Within One

Instruction

RETI

End of NMI Interrupt

Handler

yes

no

ACCVIFG=1

yes

Reset ACCVIFG

User’s Software,

Flash Access

Violation Handler

Example 1:

BIS #(NMIIE+OFIE+ACCVIE), &IE1

Example 2:

BIS Mask,&IE1 ; Mask enables only

no

NMIIFG=1

yes

Reset NMIIFGReset OFIFG

User’s Software,

External NMI

Handler

; interrupt sources

no

Note: Enabling NMI Interrupts with ACCVIE, NMIIE, and OFIE

Care should be taken when the ACCVIE, NMIIE, and OFIE enable bits are

set inside of an NMI interrupt service routine. This re-enables the interrupt

and can cause stack overflow if the interrupt flag has become set, due to

nested interrupts. When set inside of an NMI service routine, they should be

set by the last instruction of the routine before the RETI instruction.

2.2.2 Maskable Interrupts

Maskable interrupts are caused by peripherals with interrupt capability

including the watchdog timer overflow in interval-timer mode. Each maskable

interrupt source can be disabled individually by an interrupt enable bit, or all

maskable interrupts can be disabled by the general interrupt enable (GIE) bit

in the status register (SR).

2-9System Resets, Interrupts, and Operating Modes

Page 28

System Reset and Initialization

Each individual peripheral interrupt is discussed in the associated peripheral

module chapter in this manual.

2.2.3 Interrupt Processing

When an interrupt is requested from a peripheral and the peripheral interrupt

enable bit and GIE bit are set, the interrupt service routine is requested. Only

the individual enable bit must be set for (non)-maskable interrupts to be

requested.

Interrupt Acceptance

The interrupt latency is 6 cycles, starting with the acceptance of an interrupt

request, and lasting until the start of execution of the first instruction of the

interrupt-service routine, as shown in Figure 2−6. The interrupt logic executes

the following:

1) Any currently executing instruction is completed.

2) The PC, which points to the next instruction, is pushed onto the stack.

3) The SR is pushed onto the stack.

4) The interrupt with the highest priority is selected if multiple interrupts

occurred during the last instruction and are pending for service.

5) The interrupt request flag resets automatically on single-source flags.

Multiple source flags remain set for servicing by software.

6) The SR is cleared with the exception of SCG0, which is left unchanged.

This terminates any low-power mode. Because the GIE bit is cleared,

further interrupts are disabled.

7) The content of the interrupt vector is loaded into the PC: the program

continues with the interrupt service routine at that address.

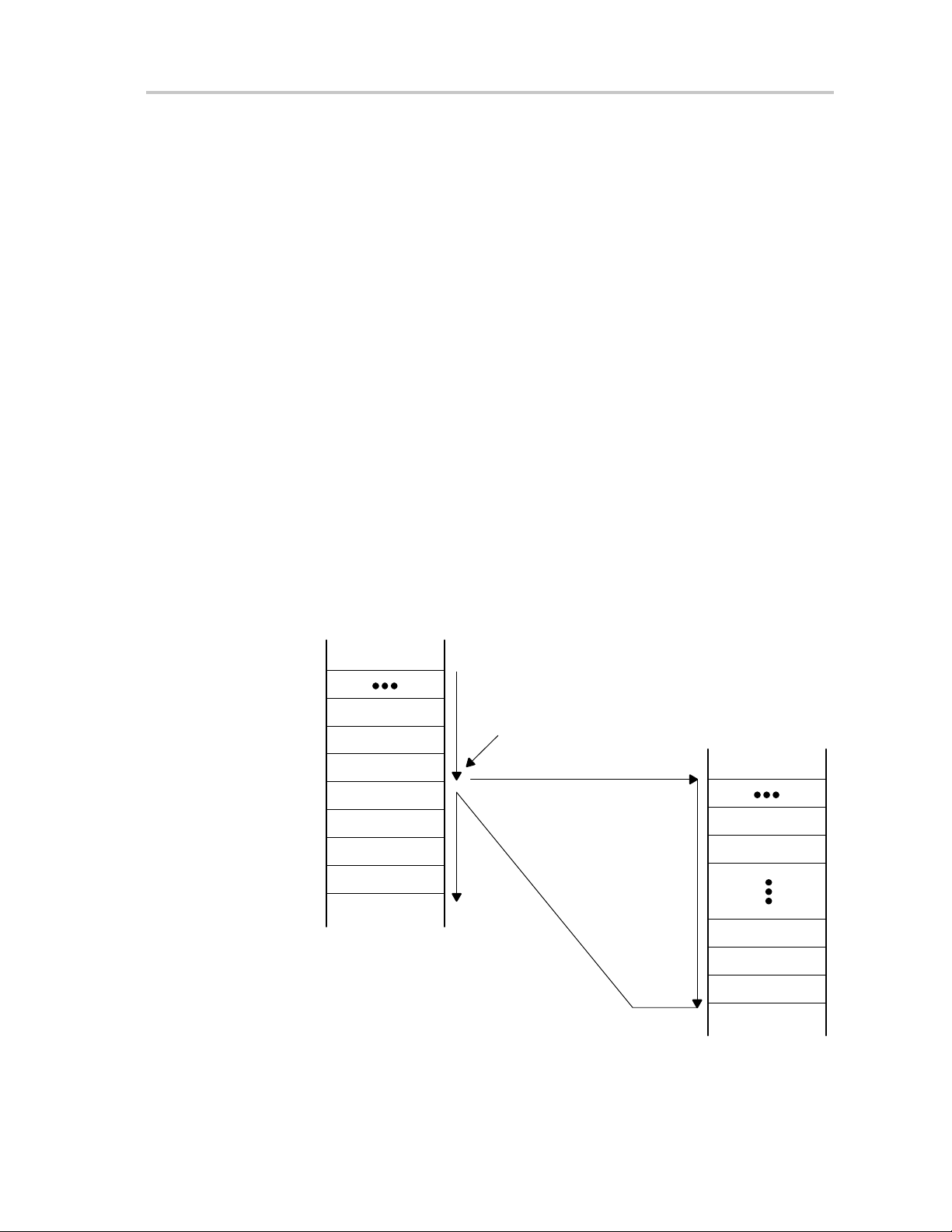

Figure 2−6.Interrupt Processing

Before

Interrupt

Item1

SP TOS

Item2

After

Interrupt

Item1

Item2

PC

SP TOS

SR

2-10 System Resets, Interrupts, and Operating Modes

Page 29

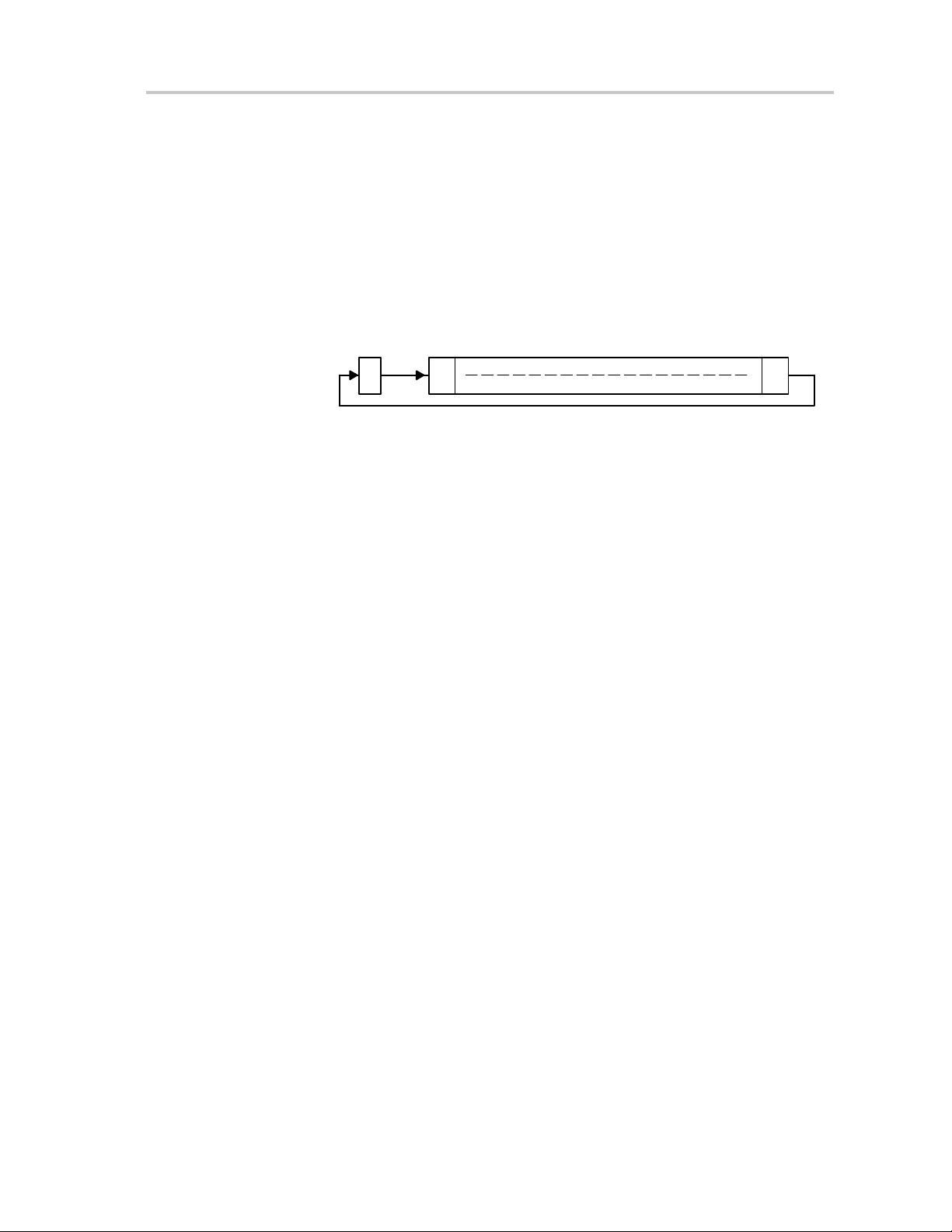

Return From Interrupt

The interrupt handling routine terminates with the instruction:

RETI (return from an interrupt service routine)

The return from the interrupt takes 5 cycles to execute the following actions

and is illustrated in Figure 2−7.

1) The SR with all previous settings pops from the stack. All previous settings

of GIE, CPUOFF, etc. are now in effect, regardless of the settings used

during the interrupt service routine.

2) The PC pops from the stack and begins execution at the point where it was

interrupted.

Figure 2−7.Return From Interrupt

Before After

System Reset and Initialization

Return From Interrupt

Item1

Item2

PC

SP TOS

SR

SP TOS

Item1

Item2

PC

SR

Interrupt nesting is enabled if the GIE bit is set inside an interrupt service

routine. When interrupt nesting is enabled, any interrupt occurring during an

interrupt service routine will interrupt the routine, regardless of the interrupt

priorities.

2-11System Resets, Interrupts, and Operating Modes

Page 30

System Reset and Initialization

2.2.4 Interrupt Vectors

The interrupt vectors and the power-up starting address are located in the

address range 0FFFFh − 0FFE0h as described in Table 2−1. A vector is

programmed by the user with the 16-bit address of the corresponding interrupt

service routine. See the device-specific data sheet for the complete interrupt

vector list.

Table 2−1.Interrupt Sources,Flags, and Vectors

INTERRUPT SOURCE

Power-up, external

reset, watchdog,

flash password

NMI, oscillator fault,

flash memory access

violation

device-specific 0FFFAh 13

device-specific 0FFF8h 12

device-specific 0FFF6h 11

Watchdog timer WDTIFG maskable 0FFF4h 10

device-specific 0FFF2h 9

device-specific 0FFF0h 8

device-specific 0FFEEh 7

device-specific 0FFECh 6

device-specific 0FFEAh 5

device-specific 0FFE8h 4

device-specific 0FFE6h 3

device-specific 0FFE4h 2

device-specific 0FFE2h 1

device-specific

INTERRUPT

FLAG

WDTIFG

KEYV

NMIIFG

OFIFG

ACCVIFG

SYSTEM

INTERRUPT

Reset 0FFFEh 15, highest

(non)-maskable

(non)-maskable

(non)-maskable

WORD

ADDRESS

0FFFCh 14

0FFE0h 0, lowest

PRIORITY

2.2.5 Special Function Registers (SFRs)

Some module enable bits, interrupt enable bits, and interrupt flags are located

in the SFRs. The SFRs are located in the lower address range and are

implemented in byte format. SFRs must be accessed using byte instructions.

See the device-specific datasheet for the SFR configuration.

2-12 System Resets, Interrupts, and Operating Modes

Page 31

2.3 Operating Modes

The MSP430 family is designed for ultralow-power applications and uses

different operating modes shown in Figure 2−9.

The operating modes take into account three different needs:

- Ultralow-power

- Speed and data throughput

- Minimization of individual peripheral current consumption

The MSP430 typical current consumption is shown in Figure 2−8.

Figure 2−8.Typical Current Consumption of 41x Devices vs Operating Modes

Operating Modes

90

45

300

200

55

32

17

0

AM

LPM0 LPM2 LPM3 LPM4

11

Operating Modes

0.9

0.7

VCC = 3 V

VCC = 2.2 V

0.1 0.1

A @ 1 MHzµ

ICC/

315

270

225

180

135

The low-power modes 0−4 are configured with the CPUOFF , OSCOFF, SCG0,

and SCG1 bits in the status register The advantage of including the CPUOFF,

OSCOFF, SCG0, and SCG1 mode-control bits in the status register is that the

present operating mode is saved onto the stack during an interrupt service

routine. Program flow returns to the previous operating mode if the saved SR

value is not altered during the interrupt service routine. Program flow can be

returned to a d i fferent operating mode by manipulating the saved SR value on

the stack inside of the interrupt service routine. The mode-control bits and the

stack can be accessed with any instruction.

When setting any of the mode-control bits, the selected operating mode takes

effect immediately. Peripherals operating with any disabled clock are disabled

until the clock becomes active. The peripherals may also be disabled with their

individual control register settings. All I/O port pins and RAM/registers are

unchanged. Wake up is possible through all enabled interrupts.

2-13System Resets, Interrupts, and Operating Modes

Page 32

Operating Modes

Figure 2−9.MSP430x4xx Operating Modes For Basic Clock System

WDT Active,

Time Expired, Overflow

WDT Active,

Security Key Violation

CPUOFF = 1

SCG0 = 0

SCG1 = 0

LPM0

CPU Off, FLL+ On,

MCLK On, ACLK On

CPUOFF = 1

SCG0 = 1

SCG1 = 0

LPM1

CPU Off, FLL+ Off,

MCLK On, ACLK On

RST/NMI

Reset Active

WDTIFG = 1

WDTIFG = 1

Active Mode

CPU Is Active

Peripheral Modules Are Active

CPUOFF = 1

SCG0 = 0

SCG1 = 1

LPM2

CPU Off, FLL+ Off,

MCLK Off, ACLK On

POR

WDTIFG = 0

PUC

CPUOFF = 1

VCC On

RST/NMI is Reset Pin

WDT is Active

CPUOFF = 1

OSCOFF = 1

SCG0 = 1

SCG1 = 1

CPU Off, FLL+ Off,

MCLK Off, ACLK On

DC Generator Off

RST/NMI

NMI Active

SCG0 = 1

SCG1 = 1

LPM4

CPU Off, FLL+ Off,

MCLK Off, ACLK Off

DC Generator Off

LPM3

SCG1 SCG0 OSCOFF CPUOFF Mode CPU and Clocks Status

0 0 0 0 Active CPU is active, all enabled clocks are active

0 0 0 1 LPM0 CPU, MCLK are disabled

SMCLK , ACLK are active

0 1 0 1 LPM1 CPU, MCLK, DCO osc. are disabled

DC generator is disabled if the DCO is not used for

MCLK or SMCLK in active mode

SMCLK , ACLK are active

1 0 0 1 LPM2 CPU, MCLK, SMCLK, DCO osc. are disabled

DC generator remains enabled

ACLK is active

1 1 0 1 LPM3 CPU, MCLK, SMCLK, DCO osc. are disabled

DC generator disabled

ACLK is active

1

1 1 1 LPM4 CPU and all clocks disabled

2-14 System Resets, Interrupts, and Operating Modes

Page 33

2.3.1 Entering and Exiting Low-Power Modes

An enabled interrupt event wakes the MSP430 from any of the low-power

operating modes. The program flow is:

- Enter interrupt service routine:

J The PC and SR are stored on the stack

J The CPUOFF, SCG1, and OSCOFF bits are automatically reset

- Options for returning from the interrupt service routine:

J The original SR is popped from the stack, restoring the previous

operating mode.

J The SR bits stored on the stack can be modified within the interrupt

service routine returning to a different operating mode when the RETI

instruction is executed.

; Enter LPM0 Example

BIS #GIE+CPUOFF,SR ; Enter LPM0

; ... ; Program stops here

;

; Exit LPM0 Interrupt Service Routine

BIC #CPUOFF,0(SP) ; Exit LPM0 on RETI

RETI

Operating Modes

; Enter LPM3 Example

BIS #GIE+CPUOFF+SCG1+SCG0,SR ; Enter LPM3

; ... ; Program stops here

;

; Exit LPM3 Interrupt Service Routine

BIC #CPUOFF+SCG1+SCG0,0(SP) ; Exit LPM3 on RETI

RETI

Extended Time in Low-Power Modes

The negative temperature coefficient of the DCO should be considered when

the DCO is disabled for extended low-power mode periods. If the temperature

changes significantly, the DCO frequency at wake-up may be significantly

different from when the low-power mode was entered and may be out of the

specified operating range. To avoid this, the DCO can be set to it lowest value

before entering the low-power mode for extended periods of time where

temperature can change.

; Enter LPM4 Example with lowest DCO Setting

BIC.B #FN_8+FN_4+FN_3+FN_2,&SCFI0 ; Lowest Range

MOV.B #010h,&SCFI1 ; Select Tap 2

BIS #GIE+CPUOFF+OSCOFF+SCG1+SCG0,SR ; Enter LPM4

; ... ; Program stops

; Interrupt Service Routine

BIC #CPUOFF+OSCOFF+SCG1+SCG0,0(SR); Exit LPM4 on RETI

RETI

2-15System Resets, Interrupts, and Operating Modes

Page 34

Principles for Low-Power Applications

2.4 Principles for Low-Power Applications

Often, the most important factor for reducing power consumption is using the

MSP430’s clock system to maximize the time in LPM3. LPM3 power

consumption is less than 2 µA typical with both a real-time clock function and

all interrupts active. A 32-kHz watch crystal is used for the ACLK and the CPU

is clocked from the DCO (normally off) which has a 6-µs wake-up.

- Use interrupts to wake the processor and control program flow.

- Peripherals should be switched on only when needed.

- Use low-power integrated peripheral modules in place of software driven

functions. For example Timer_A and Timer_B can automatically generate

PWM and capture external timing, with no CPU resources.

- Calculated branching and fast table look-ups should be used in place of

flag polling and long software calculations.

- Avoid frequent subroutine and function calls due to overhead.

- For longer software routines, single-cycle CPU registers should be used.

2.5 Connection of Unused Pins

The correct termination of all unused pins is listed in Table 2−2.

Table 2−2.Connection of Unused Pins

Pin Potential Comment

AV

CC

AV

SS

V

REF+

Ve

REF+

V

/Ve

REF−

XIN DV

XOUT Open

XT2IN DV

XT2OUT Open 43x and 44x devices

Px.0 to Px.7 Open Switched to port function, output direction

RST

/NMI DVCC or V

R03 DV

COM0 Open

TDO Open

TDI Open

TMS Open

TCK Open

Sxx

REF−

DV

DV

Open

DV

DV

Open

CC

SS

SS

SS

CC

SS

SS

43x and 44x devices

47 kΩ pullup with 10nF pull down

CC

2-16 System Resets, Interrupts, and Operating Modes

Page 35

Chapter 3

This chapter describes the MSP430 CPU, addressing modes, and instruction

set.

Topic Page

3.1 CPU Introduction 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 CPU Registers 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Addressing Modes 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Instruction Set 3-17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-1RISC 16-Bit CPU

Page 36

CPU Introduction

3.1 CPU Introduction

The CPU incorporates features specifically designed for modern

programming techniques such as calculated branching, table processing and

the use of high-level languages such as C. The CPU can address the complete

address range without paging.

The CPU features include:

- RISC architecture with 27 instructions and 7 addressing modes.

- Orthogonal architecture with every instruction usable with every

- Full register access including program counter, status registers, and stack

- Single-cycle register operations.

- Large 16-bit register file reduces fetches to memory.

- 16-bit address bus allows direct access and branching throughout entire

addressing mode.

pointer.

memory range.

- 16-bit data bus allows direct manipulation of word-wide arguments.

- Constant generator provides six most used immediate values and

reduces code size.