Page 1

LMK04906 Evaluation Board

User's Guide

January 2012

Literature Number SNAU126A

Revised – December 2013

Page 2

LMK04906 Family

Low-Noise Clock Jitter Cleaner with Dual Loop PLLs

Evaluation Board Instructions

2 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 3

Table of Contents

TABLE OF CONTENTS ..............................................................................................................................................................3

GENERAL DESCRIPTION ..........................................................................................................................................................5

Evaluation Board Kit Contents .................................................................................................................. 5

Available LMK04906 Evaluation Boards ................................................................................................. 5

Available LMK04906 Family Devices ...................................................................................................... 5

QUICK START ..........................................................................................................................................................................6

Default CodeLoader Modes for Evaluation Boards................................................................................... 7

EXAMPLE: USING CODELOADER TO PROGRAM THE LMK04906B ............................................................................................8

1. Start CodeLoader 4 Application ............................................................................................................ 8

2. Select Device ......................................................................................................................................... 8

3. Program/Load Device ............................................................................................................................ 9

4. Restoring a Default Mode ...................................................................................................................... 9

5. Visual Confirmation of Frequency Lock ............................................................................................. 10

6. Enable Clock Outputs .......................................................................................................................... 10

PLL LOOP FILTERS AND LOOP PARAMETERS ......................................................................................................................... 12

PLL 1 Loop Filter .................................................................................................................................... 12

25 MHz VCXO PLL ............................................................................................................................ 12

PLL2 Loop Filter ..................................................................................................................................... 13

EVALUATION BOARD INPUTS AND OUTPUTS ........................................................................................................................ 14

RECOMMENDED TEST EQUIPMENT ...................................................................................................................................... 21

APPENDIX A: CODELOADER USAGE....................................................................................................................................... 22

Port Setup Tab.......................................................................................................................................... 22

Clock Outputs Tab ................................................................................................................................... 23

PLL1 Tab ................................................................................................................................................. 26

Setting the PLL1 VCO Frequency and PLL2 Reference Frequency ................................................... 27

PLL2 Tab ................................................................................................................................................. 28

Bits/Pins Tab ............................................................................................................................................ 29

Registers Tab ........................................................................................................................................... 34

APPENDIX B: TYPICAL PHASE NOISE PERFORMANCE PLOTS .................................................................................................. 35

PLL1 ........................................................................................................................................................ 35

25 MHz VCXO Phase Noise ............................................................................................................... 35

Clock Output Measurement Technique ............................................................................................... 36

Clock Outputs (CLKout).......................................................................................................................... 37

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 3

Copyright © 2013, Texas Instruments Incorporated

Page 4

LMK04906B CLKout Phase Noise ..................................................................................................... 37

APPENDIX C: SCHEMATICS .................................................................................................................................................... 38

Power Supplies......................................................................................................................................... 38

LMK04906B Device with Loop Filter and Crystal Circuits ................................................................... 39

Reference Inputs (CLKin0, CLKin1 & CLKin2), External VCXO (OSCin) & VCO Circuits............... 40

Clock Outputs (OSCout0, CLKout0 to CLKout5) .................................................................................. 41

uWire Header, Logic I/O Ports and Status LEDs .................................................................................... 42

APPENDIX D: BILL OF MATERIALS ......................................................................................................................................... 43

APPENDIX E: PCB LAYERS STACKUP ..................................................................................................................................... 47

APPENDIX F: PCB LAYOUT ..................................................................................................................................................... 48

Layer #1 – Top ......................................................................................................................................... 48

Layer #2 – RF Ground Plane (Inverted) .................................................................................................. 49

Layer #3 – Vcc Planes ............................................................................................................................. 50

Layer #4 – Ground Plane (Inverted) ........................................................................................................ 51

Layer # 5 – Vcc Planes 2 ......................................................................................................................... 52

Layer #6 – Bottom ................................................................................................................................... 53

Layers #1 and 6 – Top and Bottom (Composite) ..................................................................................... 54

APPENDIX G: PROPERLY CONFIGURING LPT PORT ................................................................................................................ 55

LPT Driver Loading ................................................................................................................................. 55

Correct LPT Port/Address........................................................................................................................ 55

Correct LPT Mode ................................................................................................................................... 56

Legacy Board Port Setup ......................................................................................................................... 56

APPENDIX H: TROUBLESHOOTING INFORMATION ................................................................................................................ 57

1) Confirm Communications ................................................................................................................ 57

2) Confirm PLL1 operation/locking ..................................................................................................... 57

3) Confirm PLL2 operation/locking ..................................................................................................... 58

APPENDIX I: EVM SOFTWARE AND COMMUNICATION ......................................................................................................... 59

OPTION 1 ................................................................................................................................................ 59

OPTION 2 ................................................................................................................................................ 59

4 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 5

Evaluation Board ID

Device

PLL1 VCXO

25 MHz Epson VCXO

Model VG-4231CA 25.0000M-FGRC3

Buffered/

Outputs

Programmable

Outputs

LMK04906B

3 1 6

2370 to 2600 MHz

General Description

The LMK04906 Evaluation Board simplifies evaluation of the LMK04906B Low-Noise Clock

Jitter Cleaner with Dual Loop PLLs. Texas Instrument’s CodeLoader software can be used to

program the internal registers of the LMK04906B device through the USB2ANY-uWIRE

interface. The CodeLoader software will run on a Windows 2000/XP or Windows 7 PC and can

be downloaded from http://www.ti.com/tool/codeloader.

Evaluation Board Kit Contents

The evaluation board kit includes:

• (1) LMK04906 Evaluati on Boar d fr om Table 1

• (1) CodeLoader and USB2ANY-uWIRE Interface uWire header on EVM

A vailable LMK04906 Ev aluation Bo ards

The LMK04906 Evaluation Board supports any of the four devices offered in the LMK04906

Family. All evaluation boards use the same PCB layout and bill-of-materials, except for the

corresponding LMK04906B device affixed to the board. A commercial-quality VCXO is also

mounted to the board to provide a known reference point for evaluating device performance and

functionality.

Table 1: Available Evaluation Board Configurations

LMK04906BEVAL LMK04906B

A vailable LMK04906 F amily Devices

Table 2: LMK04906B Devices

Device

Reference

Inputs

Divided

OSCin

LVDS/LVPECL/

LVCMOS

VCO Frequency

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 5

Copyright © 2013, Texas Instruments Incorporated

Page 6

125 MHz

(Default)

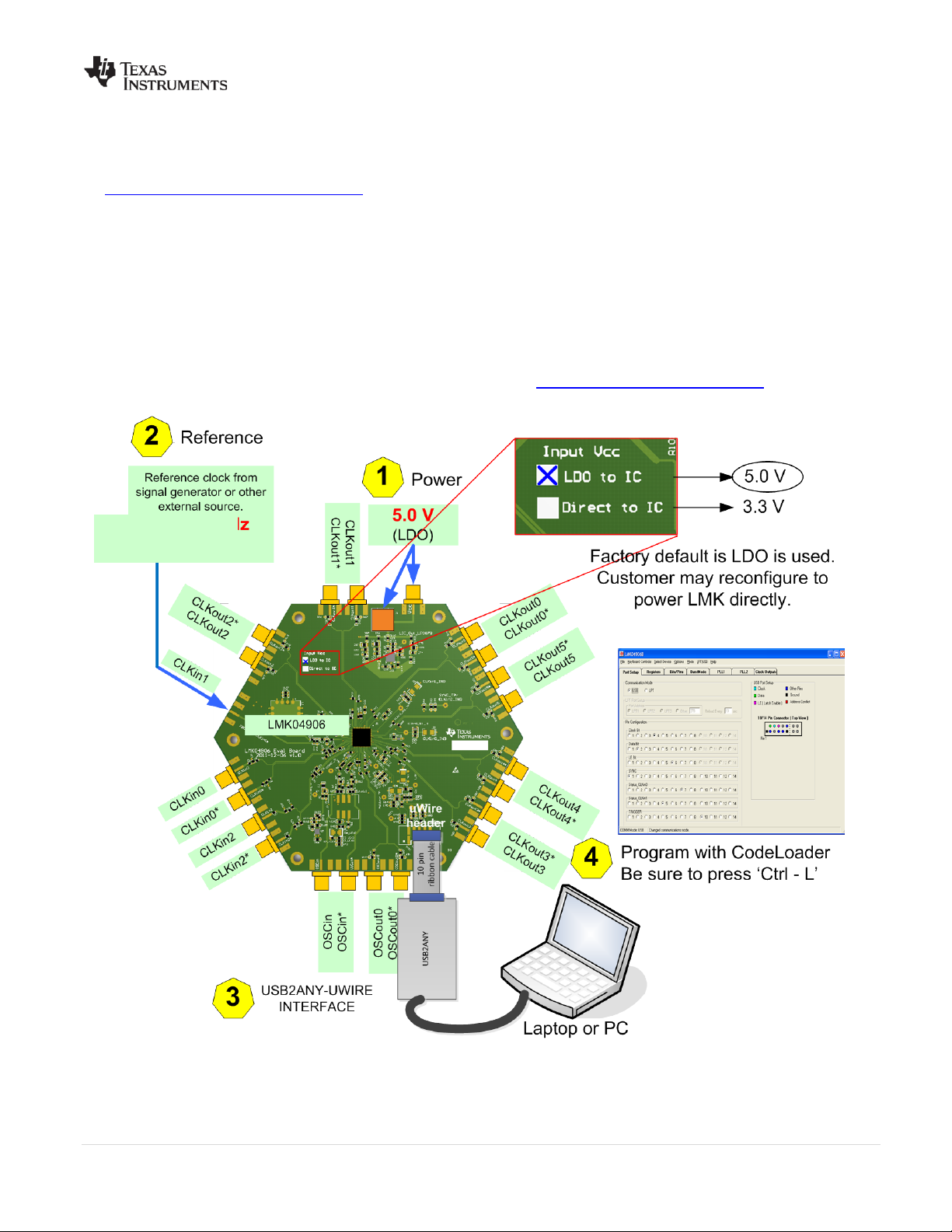

Quick Start

Full evaluation board instructions are downloadable from the LMK04906B device product folder

at www.ti.com/product/LMK04906.

1. Connect a power supply voltage of 5 V to the Vcc SMA connector. The onboard LP3878ADJ LDO regulator will output a low-noise 3.3 V supply to operate the device.

2. Connect a reference clock from a signal source to the CLKin1 SMA port. Use 125 MHz

for default. The reference frequency depends on the device programming.

3. Connect the uWire header to a PC USB port using the USB2ANY-uWIRE interface.

4. Program the device with a default mode using CodeLoader. Ctrl+L must be pressed at

least once to load all registers. Alternatively click menu “Keyboard Controls” “Load

Device”. CodeLoader can be downloaded from www.ti.com/tool/codeloader.

5. Measurements may be made on an active output clock port via its SMA connector.

Figure 1: Quick Start Diagram

6 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 7

CLKin

Frequency

OSCin

Frequency

122.88 MHz CLKin1, 122.88 MHz

VCXO

122.88

MHz

122.88

MHz

125 MHz CLKin1, 25 MHz VCXO

Dual PLL, Internal VCO

125 MHz

25 MHz

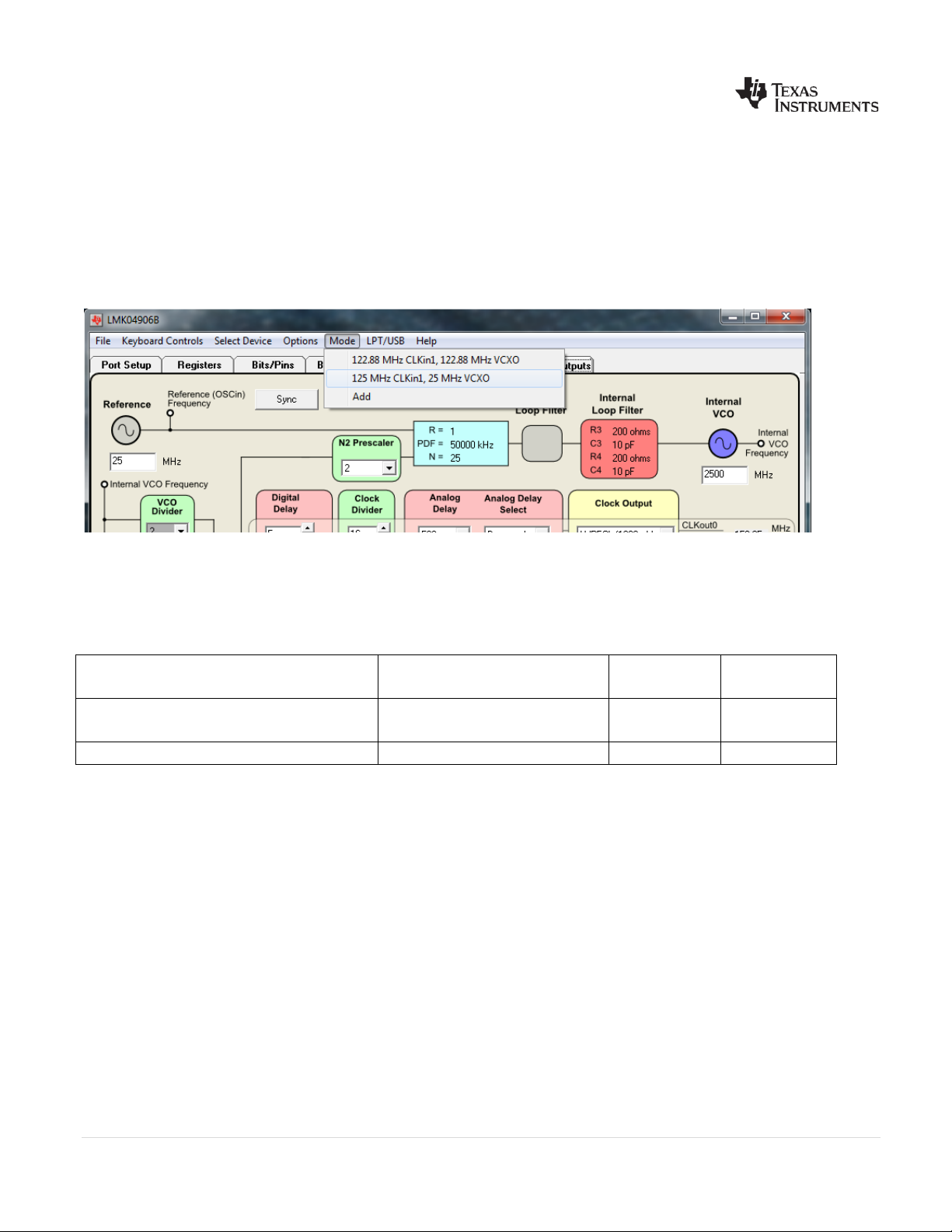

Default CodeLoader Modes for Evaluation Boards

CodeLoader saves the state of the selected LMK04906B device when exiting the software. To

ensure a common starting point, the following modes listed in Table 3 may be restored by

clicking “Mode” and selecting the appropriate device configuration, as shown in Figure 2 in the

case of the LMK04906B device. Similar default modes are available for each LMK04906B

device in CodeLoader. Choose a mode with CLKin0 or CLKin2 for differential clock signal or

CLKin1 for a single ended signal.

Figure 2: Selecting a Default Mode for the LMK04906 Device

After restoring a default mode, press Ctrl+L to program the device. The default modes also

disable certain outputs , so make sure t o enable the output under test to make measurements.

Table 3: Default CodeLoader Modes for LMK04906

Default CodeLoader Mode Device Mode

Dual PLL, Internal VCO

The next section outlines step-by-step procedures for using the evaluation board with the

LMK04906B. For boards with another part number, make sure to select the corresponding part

number under the “Device” menu.

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 7

Copyright © 2013, Texas Instruments Incorporated

Page 8

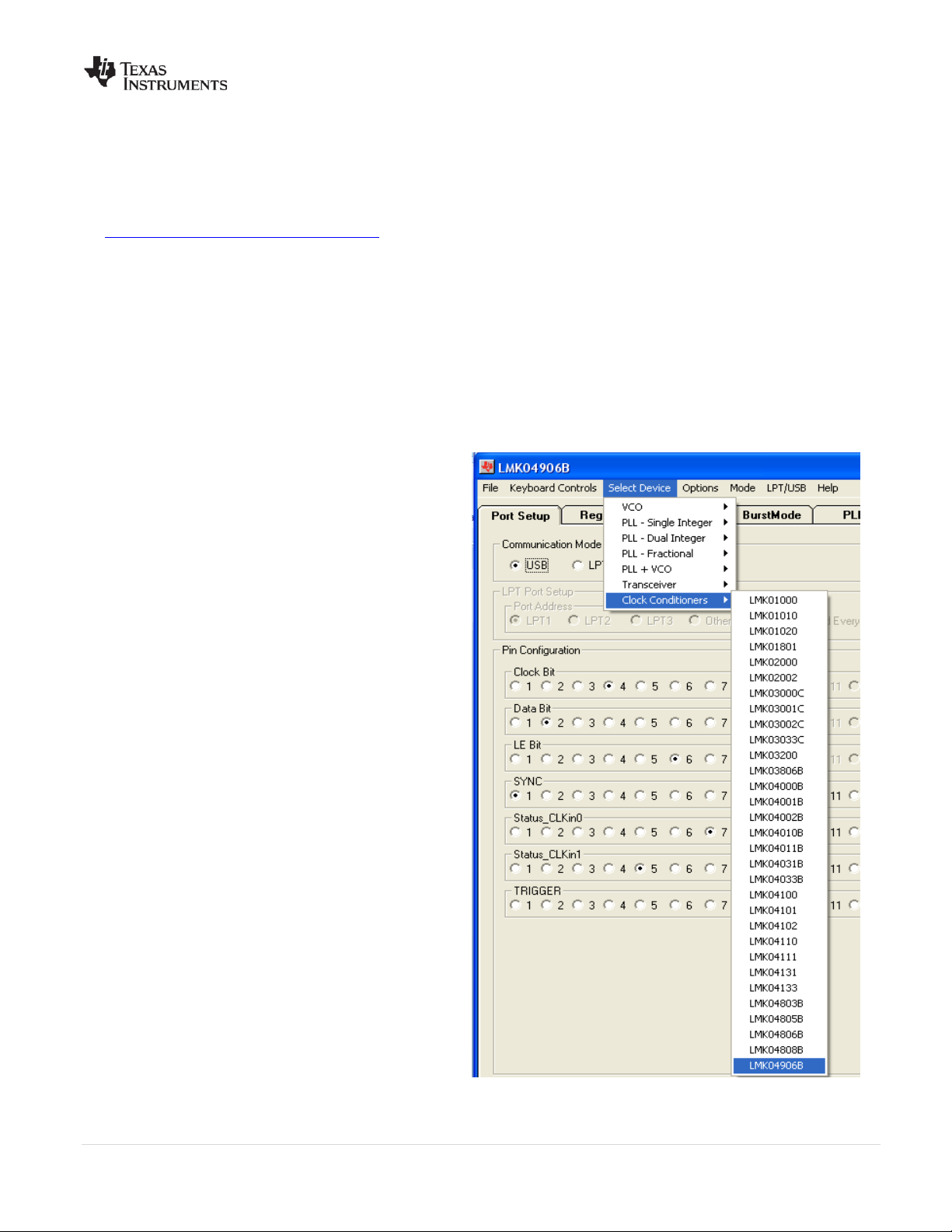

Figure 3 – Selecting the LMK04906B device

Example: Using CodeLoader to Program the LMK04906B

The purpose of this section is to walk the user through using CodeLoader 4 to make some

measurements with the LMK04906B device as an example. For more information on

CodeLoader refer to Appendix A: CodeLoader Usage or the CodeLoader 4 instructions located

at http://www.ti.com/tool/codeloader.

Before proceeding, be sur e to foll ow the Quick Start section above to ensure proper

connections.

1. Start CodeLoader 4 A pplication

Click “Start” “Programs” “CodeLoader 4” “CodeLoader 4”

The CodeLoader 4 program is installed by default to the CodeLoader 4 application group.

2. Select Device

Click “Select Device” “Clock Conditioners”

“LMK04906B”

Once started CodeLoader 4 will load the last

used device. To load a new device, click

“Select Device” from the menu bar. Then,

select the subgroup and finally device to

load. In this example, the LMK04906B is

chosen. Selecting the device does cause

the device to be programmed.

8 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 9

Figure 4 – Loading the Device

3. Program/Load Device

Assuming the Port Setup settings are

correct, press the “Ctrl+L” shortcut or click

“Keyboard Controls” “Load Device” from

the menu to program the device to the

current state of the newly loaded

LMK04906 file.

Once the device has been initially loaded,

CodeLoader will automatically program

changed registers so it is not necessary to re-load the device upon subsequent changes in the

device configuration. It is possible to disable this functionality by ensuring there is no

checkmark by the “Options” “AutoR el oa d with Changes.”

Because a default mode will be restored in the next step, this step is not really needed but is

included to emphasize the importance of pressing “Ctrl+L” to load the device at least once after

starting CodeLoader, restoring a mode, or restoring a saved setup using the File menu.

See Appendix A: CodeLoader Usage or the CodeLoader 4 instructions located at

http://www.ti.com/tool/codeloader for more informati on on Por t Setu p. Appendix H:

Troubleshooting Information contains information on troubleshooting communi cat ions.

4. Restoring a Default Mode

Click “Mode” “125 MHz CLKin1, 25 MHz VCXO”; then press Ctrl+L.

Figure 5: Setting the Default mode for L MK04906

For the purpose of this walkthrough, a default mode will be loaded to ensure a common starting

point. This is important because when CodeLoader is closed, it remembers the last settings

used for a particular device. Again, remember to press Ctrl+L as the first step after loading a

default mode.

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 9

Copyright © 2013, Texas Instruments Incorporated

Page 10

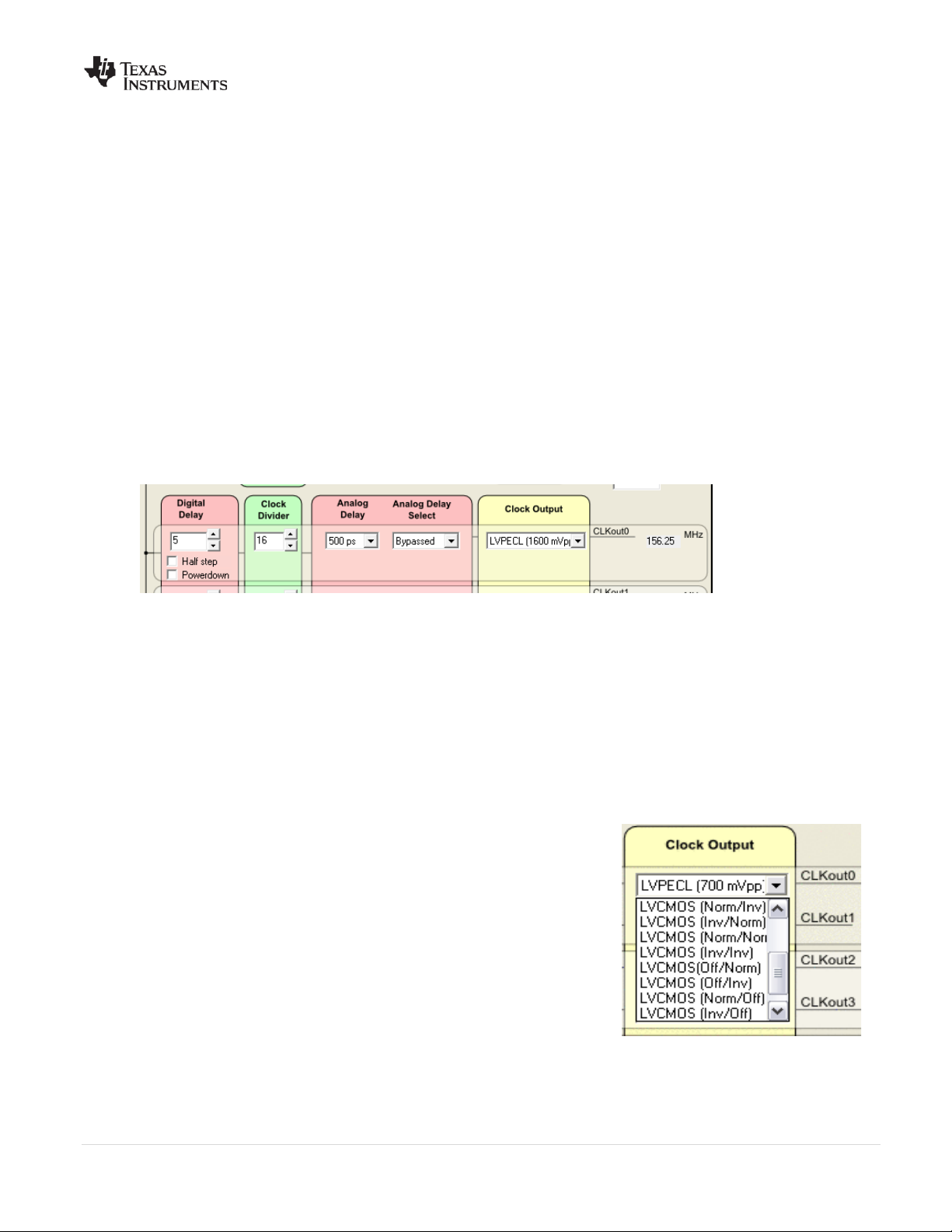

Figure 7: Setting LVCMOS modes

Figure 6: Setting Digital Delay, Clock Divider, Analog Delay, and Output Format for CLKout0

5. Visual Confirmation of Frequency Lock

After a default mode is restored and loaded, LED D5 should illuminate when PLL1 and PLL2 are

locked to the reference clock applied to CLKin1. This assumes LD_M U X = PLL1/2 DLD an d

LD_TYPE = Active High, which are the default settings.

6. Enable Clock Outputs

While the LMK04906B offers programmable clock output buffer formats, the evaluation board is shipped

with preconfigured output terminations to match the default buffer type for each output. Refer to the

CLKout port description in the Evaluation Board Inputs and Outputs section.

To measure phase noise at one of the clock outputs, for example, CLKout0:

1. Click on the Clock Outputs tab,

2. Uncheck “Powerdown” in the Digital Delay box to enable the channel,

3. Set the following settings as needed:

a. Digital Delay value

b. Clock Divider value

c. Analog Delay select and Analog Delay value (if not “Bypassed”)

d. Clock Output type.

4. Depending on the configured output type, the clock output SMAs can be interfaced to a test

instrument with a single-ended 50-ohm input as follows.

a. For LVDS:

i. A balun (like ADT2-1T) is recommended for differential-to-single-ended

conversion.

b. For LVPECL:

i. A balun can be used, or

ii. One side of the LVPECL signal can be terminated with a 50-ohm load and the

other side can be run single-ended to the instrument.

c. For LVCMOS:

i. There are two single-ended outputs, CLKoutX

and CLKoutX*, and each output can be set to

Normal, Inverted, or Off. There are nine (9)

combinations of LVCMOS modes in the Clock

Output list.

ii. One side of the LVCMOS signal can be

terminated with a 50-ohm load and the other

side can be run single-ended to the

instrument.

iii. A balun may also be used. Ensure CLKoutX

and CLKoutX* states are complementary to

each other. That is, Norm/Inv or Inv/Norm.

10 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 11

5. The phase noise may be measured with a spectrum analyzer or signal source analyzer.

See Appendix B: Typical Phase Noise Performance Plots for phase noise plots of the clock

outputs.

National’s Clock Design Tool can be used to calculate divider values to achieve desired clock

output frequencies. See: http://www.ti.com/tool/clockdesigntool.

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 11

Copyright © 2013, Texas Instruments Incorporated

Page 12

25 MHz VCXO PLL

PLL Loop Filters and Loop Parameters

In jitter cleaning applications that use a cascaded or dual PLL architecture, the first PLL’s

purpose is to substitute the phase noise of a low-noise oscillator (VCXO or crystal resonator) for

the phase noise of a “dirty” reference clock. The first PLL is typically configured with a narrow

loop bandwidth in order to minimize the impact of the reference clock phase noise. The

reference clock consequently serves only as a frequency reference rather than a phase

reference.

The loop filters on the LMK04906 ev al uati o n boar d ar e se tup using t he approach above. The

loop filter for PLL1 has been configured for a narrow loop bandwidth (< 100 Hz), while the loop

filter of PLL2 has been configured for a wide loop bandwidth (> 100 kHz). The specific loop

bandwidth values depend on the phase noise performance of the oscillator mounted on the

board. The following tables co ntai n the par am eter s for PLL 1 and PL L2 f or eac h oscil l at or opt ion.

National’s Clock Design Tool can be used to optimize PLL phase noise/jitter for given

specifications. See: http://www.ti.com/tool/clockdesigntool.

PLL 1 Loop Filter

Table 4: PLL1 Loop Filter Parameters for Epson 25 MHz VCXO

Phase Margin

49˚

Kφ (Charge Pump)

400 uA

Loop Bandwidth

Reference Clock

Frequency

Loop Filter

Components

21 Hz

125 MHz

C1_VCXO = 3300

nF

Phase Detector Freq

VCO Gain

Output Frequency

C2_VCXO = 10000 nF

C2A_VCXO = 10000 nF

2083.33 MHz

4.5 kHz/Volt

25 MHz (To PLL 2)

R2_VCXO = 1 kΩ

Note: PLL Loop Bandwidth is a function of Kφ, Kvco, N as well as loop components. Changing

Kφ and N will change the loop bandwidth.

12 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 13

LMK04906B

C1_VCO

0.082

nF

C2_VCO

5.6

nF

C3 (internal)

0.01

nF

C4 (internal)

0.01

nF

R2_VCO

0.68

kΩ

R3 (internal)

0.2

kΩ

R4 (internal)

0.2

kΩ

Charge Pump

Current, Kφ

Phase

Frequency

Frequency

2500

MHz

Kvco

18.5

MHz/V N 50

degree

s

Loop

Bandwidth

PLL2 Loop Filter

Table 5: PLL2 Loop Filter Parameters for LMK04906B

3.2 mA

Detector

50 MHz

Phase Margin 69

132 kHz

Note: PLL Loop Bandwidth is a function of Kφ, Kvco, N as well as loop components. Changing

Kφ and N will change the loop bandwidth.

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 13

Copyright © 2013, Texas Instruments Incorporated

Page 14

Signal Type,

Input/Output

Clock outputs with programmable output buffers.

Clock output pair

Default Board Termination

CLKout0

LVPECL*

CLKout1

LVPECL

CLKout2

LVDS* / LVCMOS

CLKout3

LVDS / LVCMOS

CLKout4

LVDS* / LVCMOS

CLKout5

LVPECL

state).

Evaluation Board Inputs and Outputs

The following table contains descriptions of the inputs and outputs for the evaluation board.

Unless otherwise noted, the connectors described can be assumed to be populated by default.

Additionally, some applicable CodeLoader programming controls are noted for convenience.

Refer to the LMK04906 Family Datasheet for complete register programming information.

Table 6: Evaluation Board Inputs and Outputs

Connector Name

Populated:

CLKout0, CLKout0*,

CLKout1, CLKout1*,

CLKout2, CLKout2*,

CLKout3, CLKout3*,

CLKout4, CLKout4*,

CLKout5, CLKout5*

Analog, Output

Description

The output terminations by default on the evaluation board

are shown below, and the output type selected by default in

CodeLoader is indicated by an asterisk (*):

Each CLKout pair has a programmable LVDS, LVPECL, or

LVCMOS buffer. The output buffer type can be selected in

CodeLoader in the Clock Outputs tab via the

CLKoutX_TYPE control.

All clock outputs are AC-coupled to allow safe testing with

RF test equipment.

All LVPECL clock outputs are source-terminated using 240ohm resistors.

If an output pair is programmed to LVCMOS, each output

can be independently configured (normal, inverted, or off/tri-

14 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 15

Signal Type,

Input/Output

Buffered outputs of OSCin port.

OSC output pair

Default Board Termination

OSCout0

LVDS* / LVCMOS

off/tri-state).

Main power supply input for the evaluation board.

r

schematics for more details.

Alternative power supply input for the evaluation board using

Apply power to either Vcc SMA or J1, but not both.

Optional Vcc input to power the VCO circuit if separated

power.

Connector Name

Populated:

OSCout0, OSCout0*,

Vcc

Analog,

Output

Power,

Input

Description

The output terminations on the evaluation board are shown

below, the output type selected by default in CodeLoader is

indicated by an asterisk (*):

OSCout0 has a programmable LVDS, LVPECL, or LVCMOS

output buffer. The OSCout0 buffer type can be selected in

CodeLoader on the Clock Outputs tab via the

OSCout0_TYPE control.

OSCout0 is AC-coupled to allow safe testing with RF test

equipment.

If OSCout0 is programmed as LVCMOS, each output can be

independently configured (normal, inverted, inverted, and

A 3.9 V DC power source applied to this SMA will, by

default, source the onboard LDO regulators that power the

inner layer planes that supply the LMK04906B and its

auxiliary circuits (e.g. VCXO).

The LMK04906B contains internal voltage regulators for the

VCO, PLL and other internal blocks. The clock outputs do

not have an internal regulator, so a clean power supply with

sufficient output current capability is required for optimal

performance.

On-board LDO regulators and 0

flexibility to supply and route power to various devices. See

Populated:

J1

Unpopulated:

VccVCO/Aux

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 15

Power,

Input

Power,

Input

Copyright © 2013, Texas Instruments Incorporated

two unshielded wires (Vcc and GND).

voltage rails are needed. The VccVCO/Aux input can power

these circuits directly or supply the on-board LDO

regulators. 0 Ω resistor options provide flexibility to route

Page 16

Signal Type,

Input/Output

Reference Clock Inputs for PLL1 (CLKin0, 1, 2).

selected in CodeLoader. The clock input selection

Input

Mode

Min

Max

Units

Differential

Bipolar or

0.5

3.1

Vpp

Single

Ended

0.25

2.4

Vpp

Ext VCO (Fin)

Connector Name

CLKin1 can alternatively be used as an External

Feedback Clock Input (FBCLKin) in 0-delay mode

or an RF Input (Fin) in External VCO mode.

Reference Clock Inputs for PLL1 (CLKin0, 1)

FBCLKin/CLKin1* is configured by default for a

single-ended reference clock input from a 50-ohm

source. The non-driven input pin

(FBCLKin/CLKin1) is connected to GND with a 0.1

uF. CLKin0/CLKin0* is configured by default for a

differential reference clock input from a 50-ohm

source.

CLKin1* is the default reference clock input

mode can be programmed on the Bits/Pins tab

via the CLKin_Select_MODE control . Re fer t o the

LMK04906 Family Datasheet secti on “I npu t C l ock

Populated:

CLKin0, CLKin0*,

FBCLKin*/CLKin1*

CLKin2, CLKin2*

Analog,

Input

Switching” for more information.

AC coupled Input Clock Swing Levels

Not Populated:

FBCLKin/CLKin1

External Feedback Input (FBCLKin) for 0-Delay

CLKin1 is shared for use with FBCLKin as an

external feedback clock input to PLL1 for 0-delay

mode. See section, Error! Reference source

not found. Error! Reference source not found.,

for more details on using 0-delay mode with the

evaluation board and the evaluation board

software.

RF Input (Fin) for External VCO

CLKin1 is also shared for use with Fin as an RF

input for external VCO mode usi ng the onboard

VCO footprint (U3) or add-on VCO board. To

enable Dual PLL mode with External VCO, the

following registers must be properly configured in

CodeLoader:

Description

CMOS

• MODE = (3) Dual PLL, Ext VCO (F i n), (5)

Dual PLL, Ext VCO, 0-Delay, (11) PLL2,

16 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 17

Signal Type,

Input/Output

Feedback VCXO clock input to PLL1 and

does not accommodate the desired VCXO device.

Input (OSCin) specifications.

Test point:

Tuning voltage output from the loop filter for PLL1.

Test point:

VTUNE2_TP

Analog,

Output

Tuning voltage output from the loop filter for PLL2.

10-pin header for uWire programming interface

dedicated SMAs and test poi nts .

Connector Name

Not populated:

OSCin, OSCin*

Analog,

Input

Description

Reference clock input to PLL2.

By default, these SMAs are not connected to the

traces going to the OSCin/OSCin* pins of the

LMK04906B. Instead, the single-ended output of

the onboard VCXO (U2) drives the OSCin* input

of the device and the OSCin input of the device is

connected to GND with 0.1 uF.

A VCXO add-on board may be optionally attached

via these SMA connectors with minor modification

to the components going to the OSCin/OSCin*

pins of device. This is useful if the VCXO footprint

A single-ended or differential signal may be used

to drive the OSCin/OSCin* pins and must be AC

coupled. If operated in single-ended mode, the

unused input must be connected to GND with 0.1

uF.

Refer to the LMK04906 Family Datasheet section

“Electrical Characteristics” for PLL2 Reference

VTUNE1_TP

Analog,

Output

and programmable logi c I/O pins for the

Populated:

uWire

Test points:

DATAuWire_TP

CLKuWIRE_TP

LEuWIRE_TP

CMOS,

Input/Output

LMK04906B.

The uWire interface includes CLKuWire,

DATAuWire, and LEuWire signals.

The programmable logic I/O signals accessible

through this header include: SYNC,

Status_Holdover , Status _LD, Status_CLKin0, and

Status_CLKin1. These logic I/O signals also have

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 17

Copyright © 2013, Texas Instruments Incorporated

Page 18

Signal Type,

Input/Output

Programmable status outp ut pi n. By defaul t, set

output.

Programmable status outp ut pi n. By defaul t, set

loading the output.

Connector Name

Test point:

LD_TP

Not populated:

Status_LD

Description

to output the digital lock detect status signal for

PLL1 and PLL2 combined.

In the default CodeLoader modes, LED D5 will

illuminate green when PLL lock is detected by the

LMK04906B (output is high) and turn off when

lock is lost (output is low).

The status output signal for the Status_LD pin can

CMOS,

Output

be selected on the Bits/Pins tab via the LD_MUX

control.

Refer to the LMK04906 Family Datasheet section

“Status Pins” and “Digital Lock Detect” for more

information.

Note: Before a high-frequency inter nal sig nal ( e.g .

PLL divider output signal) is selected by LD_MUX,

it is suggested to first remove the 270 ohm

resistor to prevent the LED from loading the

Test point:

Holdover_TP

CMOS,

Output

to the output holdover mode status signal.

In the default CodeLoader mode, LED D8 will

illuminate red when holdover mode is active

(output is high) and turn off when holdover mode

is not active (output is low).

Refer to the LMK04906 Family Datasheet section

“Status Pins” and “Holdover Mode” for more

information.

Note: Before a high-frequency internal signal (e.g.

PLL divider output signal) is selected by

HOLDOVER_MUX, it is suggested to first remove

the 270 ohm resistor to prevent the LED from

18 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 19

Signal Type,

Input/Output

Programmable status I/O pins. By default, set as input

Status_CLKin1

Status_CLKin0

Active Clock

0

0

CLKin0

0

1

CLKin1

1

0

CLKin2

1

1

Holdover

Active

Clock

X

0

CLKin0

1

0

CLKin1

0

0

Reserved

“Status Pins” for more information.

Connector Name

pins for controlling input clock switching of CLKin0 and

CLKin1.

These inputs will not be functional because

CLKin_Select_MODE is set to 0 (CLKin0 Manual) by

default in the Bits/Pins tab in CodeLoader. To enable

input clock switching, CLKin_Select_MODE must be 3

or 6 and Status_CLKinX_TYPE must be 0 to 3 (pin

enabled as an input).

Input Clock Switching – Pin Select Mode

When CLKin_SELECT_MODE is 3, the

Status_CLKinX pins select which clock input is active

as follows:

Test point:

CLKin0_SEL_TP

CLKin1_SEL_TP

CMOS,

Input/Output

Input Clock Switching – Auto with Pin Select

When CLKin_SELECT_MODE is 6, the active clock is

selected using the Status_CLKinX pins upon an input

clock switch event as follows:

Description

Status_CLKin1 Status_CLKin0

Refer to the LMK04906 Family Datasheet

section

“Input Clock Switching” for more information.

Status Outputs

When Status_CLKinX_TYPE is 3 to 6 (pin enabled as

an output), the status output signal for the

corresponding Status_CLKinX pin can be programmed

on the Bits/Pins tab via the Status_CLKinX_MUX

control.

Refer to the LMK04906 Family Datasheet

section

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 19

Copyright © 2013, Texas Instruments Incorporated

Page 20

Signal Type,

Input/Output

Programmable status I/O pin. By default, set as

control.

Connector Name

Test point:

SYNC_TP

CMOS,

Input/Output

Description

an input pin for synchronize the clock outputs with

a fixed and known phase relationship between

each clock output selected for SYNC. A SYNC

event also causes the digital delay values to take

effect.

In the default CodeLoader mode, SYNC will

asserted when the SYNC pin is low and the

outputs to be synchronized will be held in a logic

low state. When SYNC is unasserted, the clock

outputs to be synchronized are activated and will

be initially phase aligned with each other except

for outputs programmed with different digital delay

values.

A SYNC event can also be programmed by

toggling the SYNC_POL_INV bit in the Bits/Pins

tab in CodeLoader.

Refer to the LMK04906 Family Datasheet section

“Clock Output Synchronization” for more

information.

Status Output

When SYNC_MUX is 3 to 6 (pin enabled as

output), a status signal for the SYNC pin can be

selected on the Bits/Pins tab via the SYNC_MUX

20 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 21

Recommended Test Equipment

Power Supply

The Power Supply should be a low noise power supply, particularly when the devices on the

board are being directly powered (onboard LDO regulators bypassed).

Phase Noise / Spectrum Analyzer

To measure phase noise and RMS jitter, an Agilent E5052 Signal Source Analyzer is

recommended. An Agilent E4445A PSA Spectrum Analyzer with the Phase Noise option is also

usable although the architecture of the E5052 is superior for phase noise measurements. At

frequencies less than 100 MHz the local oscillator noise of the E4445A is too high and

measurements will reflect the E4445A’s internal local oscillator performance, not the device

under test.

Oscilloscope

To measure the output clocks for AC performance, such as rise time or fall time, propagation

delay, or skew, it is suggested to use a real-time oscilloscope with at least 1 GHz analog input

bandwidth (2.5+ GHz recommended) with 50 ohm inputs and 10+ Gsps sample rate. To

evaluate clock synchronization or phase alignment between multiple clock outputs, it’s

recommended to use phase-matched, 50-ohm cables to minimize external sources of skew or

other errors/distortion that may be introduced if using oscilloscope probes.

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 21

Copyright © 2013, Texas Instruments Incorporated

Page 22

Appendix A: CodeLoader Usage

Code Loader is used to program the evaluation board via USB using the USB2ANYuWIRE interface. .

Port Setup T ab

Figure 8: Port Setup tab

On the Port Setup tab, the user may select the type of communication port (LPT or

USB) that will be used to program the device on the evaluation board. If parallel port is

selected, the user should ensure that the correct port address is entered.

The Pin Configuration field is hardware dependent and needs to be configured for use

with the USB2ANY-uWIRE interface. Figure 8 shows the settings required for this

configuration. Legacy board or use with a LPT cable can be configured with the use of

Appendix G: Properly Configuring LPT Port.

22 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 23

Clock Outputs Tab

Figure 9: Clock Outputs Tab

The Clock Outputs tab allows the user to control the output channel blocks, including:

• Clock Group Source from either VCO or OSCin (via OSC Mux1 and OSC Mux2)

• Channel Powerdown (affects digital and analog delay, clock divider, and buffer

blocks)

• Digital Delay value and Half Step

• Clock Divide value

• Analog Delay value and Delay bypass/enable (per output)

• Clock Output format (per output)

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 23

Copyright © 2013, Texas Instruments Incorporated

Page 24

This tab also allows the user to select the VCO Divider value (2 to 8). Note that the total

PLL2 N divider value is the product of the VCO Divider value and the PLL N Prescaler

and N Counter values (shown in the PLL2 tab), and is given by:

PLL2 N Total = VCO Divider * PLL2 N Prescaler * PLL2 N Counter

Clicking on the cyan-colored PLL2 block that contains R, PDF and N values will bring

the PLL2 tab into focus where these values may be modified, if needed.

Clicking on the values in the box containing the Internal Loop Filter component (R3, C3,

R4, C4) allow one to step through the possible values. Left click to increase the

component value, and right click to decrease the value. These values can also be

changed in the Bits/Pins tab.

The Reference Oscillator value field may be changed in either the Clock Outputs tab or

the PLL2 tab. The PLL2 Reference frequency should match the frequency of the

onboard VCXO or Crystal (i.e., VCO frequency in the PLL1 tab); if not, a warning

message will appear to indicate that the PLL(s) may be out of lock, as highlighted by the

red box in Figure 10.

24 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 25

Figure 10: Warning me ss ag e indic ati ng mis m atch bet ween

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 25

Copyright © 2013, Texas Instruments Incorporated

Page 26

Control Name

Register Name

Description

Reference Oscillator

Frequency (MHz)

n/a

CLKin frequency of the selected

reference clock.

Phase Detector

n/a

PLL1 Phase Detector Frequency (PDF).

value of the selected input clock.

PLL1 VCO frequency (25 MHz) and PLL2 reference frequency (25 MHz)

PLL1 T ab

Figure 11: PLL1 tab

The PLL1 tab allows the user to change the following parameters in Table 7.

Table 7: Registers Controls and Descriptions in PLL1 tab

Frequency (MHz)

This value is calculated as:

PLL1 PDF = CLKin Frequency / (PLL1_R

* CLKinX_PreR_DIV), where

CLKinX_PreR_DIV is the predivider

26 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 27

VCO Frequency (MHz)

n/a

The VCO Frequency should be the

Frequency for details.

R Counter

PLL1_R

PLL1 R Counter value (1 to 16383).

N Counter

PLL1_N

PLL1 N Counter value (1 to 16383).

Phase Detector Polarity

PLL1_CP_POL

PLL1 Phase Detector Polarity.

polarity “+” or “–”.

Charge Pump Gain

PLL1_CP_GAIN

PLL1 Charge Pump Gain.

uA).

Charge Pump State

PLL1_CP_TRI

PLL1 Charge Pump State.

State.

OSCin frequency, except w hen operating

in Dual PLL with 0-delay feedback. This

value is calculated as:

VCO Freq (OSCin freq) = PLL1 PDF *

PLL1_N.

In Dual PLL mode with 0-delay feedbac k,

the VCO frequency should be set to the

feedback clock input frequency. See the

section Setting the PLL1 VCO

Frequency and PLL2 Reference

Click on the polarity sign to toggle

Setting the PLL1 VCO Frequency and PLL2 Reference Frequency

When operating in Dual PLL mode without 0-delay feedback , the VCO frequency value

on the PLL1 tab must match the Reference Osci ll ator (OSC i n) frequency value on the

PLL2 tab; otherwise, the one or both PLLs may be out of lock. Updating the Reference

Oscillator frequency on the PLL2 tab will automatically update the value of

OSCin_FREQ on the Bits/Pins tab.

Left-click/right-click to increase/decrease

charge pump gain (100, 200, 400, 1600

Click to toggle between Active and Tri-

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 27

Copyright © 2013, Texas Instruments Incorporated

Page 28

Control Name

Register Name

Description

Reference Oscillator

Frequency (MHz)

OSCin_FREQ

OSCin frequency from the Ext er n al

VCXO or Crystal.

Phase Detector

n/s

PLL2 Phase Detector Frequency (PDF).

*(2

) / PLL2_R.

VCO Frequency (MHz)

n/a

Internal VCO Frequency should be

* PLL2_P * VCO divider value).

Doubler

EN_PLL2_REF_2X

PLL2 Doubler.

1 = Enable Doubler

R Counter

PLL2_R

PLL2 R Counter value (1 to 4095).

N Counter

PLL2_N

PLL2 N Counter value (1 to 262143).

PLLN Prescaler

PLL2_P

PLL2 N Prescaler value (2 to 8).

PLL2 T ab

Figure 12: PLL2 tab

The PLL2 tab allows the user to change the following parameters in Table 8.

Table 8: Registers Controls and Descriptions in PLL2 tab

Frequency (MHz)

This value is calculated as:

PLL2 PDF = OSCin Frequency

EN_PLL2_REF_2X

within the allowable range of the

LMK04906B device.

This value is calculated as:

VCO Frequency = PLL2 PDF * (PLL2_N

0 = Bypass Doubler

28 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 29

Phase Detector Polarity

PLL2_CP_POL

PLL2 Phase Detector Polarity.

polarity “+” or “–”.

Charge Pump Gain

PLL2_CP_GAIN

PLL2 Charge Pump Gain.

uA).

Charge Pump State

PLL2_CP_TRI

PLL2 Charge Pump State.

State.

Click on the polarity sign to toggle

Left-click/right-click to increase/decrease

charge pump gain (100, 400, 1600, 3200

Click to toggle between Active and Tri-

Changes made on this tab will be reflected in the Clock Outputs tab. The VCO

Frequency should conform to the specified internal VCO frequency range for the

LMK04906B device (per Table 2).

Bits/Pins T ab

The Bits/Pins tab allows the user to program bits directly, many of which are not

available on other tabs. Brief descriptions for the controls on this tab are provided in

Table 9 to supplement the datasheet. Refer to the LMK04906 Family Datasheet for

more information.

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 29

Figure 13: Bits/Pins tab

Copyright © 2013, Texas Instruments Incorporated

Page 30

Group

Register Name

Description

RESET

Resets the device to default register values.

programmed.

POWERDOWN

Places the device in powerdown mode.

MODE

Selects the operating mode (topology) for the

LMK04906 device.

PD_OSCin

Powers down the OSCin buffer. For use in Clock

Distribution mode if OSCin path is not used.

FEEDBACK_MUX

Selects the feedback source for 0-delay mode.

OSCin_FREQ

Must be set to the OSCin frequency range for

proper frequency range.

VCO_MUX

Selects between VCO and VCO divider to drive the

valid if MODE is selecting the Internal VCO.

uWire_LOCK

When checked, no other uWire programming will

programming of regist ers R0 to R30.

CLKin_Select_MODE

Selects operational mode for how the device

selects the reference clock for PLL1.

EN_CLKin1

Enables CLKin1 as a usable reference input during

auto switching mode.

EN_CLKin0

Enables CLKin0 as a usable reference input during

CLKinX_BUF_TYPE

Selects the CLKinX input buffer to Bipolar (internal

0 mV offset) or MOS (internal 55 mV offset).

EN_LOS

Enable the Loss-Of-Signal (LOS) detect circuitry.

LOS_TIMEOUT

Sets the timeout value for the LOS detect circuitry

to assert a loss of signal state on a clock input.

EN_PLL2_XTAL

Enables Crystal Oscillator

XTAL_LVL

Sets peak amplitude on the tunable crystal.

Values listed are for a 20.48 MHz crystal.

LD_MUX

Sets the selected signal on the Status_LD pin.

LD_TYPE

Sets I/O pin type on the Status_LD pin.

HOLDOVER_MUX

Sets the selected signal on the

Status_HOLDOVER pin.

HOLDOVER_TYPE

Sets I/O pin type on the Status_Holdover pin.

TIP: Right-clicking any register name in the Bits/Pins tab will display a Help prompt

with the register address, data bit location/length, and a brief register description.

Table 9: Register Controls and Descriptions on Bits/Pins ta b

RESET must be cleared for normal operation to

prevent an unintended reset every time R0 is

PLL2. Used for proper operation of the internal

Mode Control

VCO calibration routine.

Entering a reference oscillator frequency on PLL2

tab will automatically update OSCin_FREQ to the

CLKin

Crystal

clock distribution path. The VCO divider is only

have effect. Must be unchecked to enable uWire

auto switching mode.

IO Control

30 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 31

Status_CLKin0 _MUX

Sets the selected signal on the Status_CLKin0

pin.

Status_CLKin0_TYPE

Sets I/O pin type on the Status_CLKin0 pin.

Status_CLKin1_MUX

Sets the selected signal on the Status_CLKin1

pin.

Status_CLKin1_TYPE

Sets I/O pin type on the Status_CLKin1 pin.

CLKin_Sel_INV

Inverts the Status_CL Kin0/ 1 pin polar i ty when

CLKin_SELECT_MODE is 3 or 6.

SYNC_MUX

Sets the selected signal on the SYNC pin.

SYNC_TYPE

Sets I/O pin type on the SYNC pin.

SYNC_POL_INV

Sets polarity on SYNC input to active low

SYNC event.

SYNC_PLL1_DLD

Engage SYNC mode until PLL1 DLD is true

SYNC_PLL2_DLD

Engage SYNC mode until PLL2 DLD is true

NO_SYNC_CLKoutX_Y

Synchronization will not affect selected clock

Y = odd-numbered output.

SYNC_QUAL

Sets the SYNC to qualify mode for dynamic

digital delay.

EN_SYNC

Must be set when using SYNC, but may be

proper SYNC occurs.

SYNC_EN_AUTO

Enable auto SYNC when R0 to R5 is written.

HOLDOVER_MODE

Sets holdover mode to be disabled or enabled.

FORCE_HOLDOVER

Engages holdover when checked reg ar dl ess of

on.

EN_TRACK

Enables DAC tracking. DAC tracks the PLL1

that DAC update rate is <= 100 kHz.

set to an input type. Significant when

when checked. Toggling this bit will initiate a

outputs, where X = even-numbered out put and

cleared after the SYNC event. When using

dynamic digital delay (SYNC_QUAL = 1),

IO Control – Sync

EN_SYNC must always be set.

Changing this value from 0 to 1 can cause a

SYNC event, so clocks which should not be

SYNCed when setting this bit should have the

NO_SYNC_CLKoutX_Y bit set.

NOTE: This bit is not a valid method of

generating a SYNC event. Use one of the

other SYNC generation methods to ensure a

HOLDOVER_MODE value. Turns the DAC

DAC/Holdover

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 31

Copyright © 2013, Texas Instruments Incorporated

Vtune to provide for an accurate HOLDOVER

mode. DAC_CLK_DIV should also be set so

Page 32

EN_VTUNE_RAIL_DET

Allows rail-to-rail operation of VCXO with default of

be 4 or 6 (auto mode) to use.

HOLD_DLD_CNT

In HOLDOVER mode, wait for this many clocks of

_SIZE before exiting holdover mode.

DAC_CLK_DIV

DAC update clock is the PLL1 phase detector

/ DAC_CLK_DIV

EN_MAN_DAC

Enables manual DAC mode and set DAC voltage

when in holdover.

MAN_DAC

Sets the value for the DAC when EN_MAN_DAC is

manual DAC mode or DAC tracking mode

DAC_LOW_TRIP

Value from GND in ~50mV steps at which a clock

for this to be valid.

DAC_HIGH_TRIP

Value from VCC (3.3V) in ~50mV steps at which

for this to be valid.

PLL1_WND_SIZE

If the phase error between the PLL1 reference and

PLL1_DLD_CNT value.

PLL1_DLD_CNT

The reference and feedback of PLL1 must be

PLL1 digital lock detect is asserted.

CLKinX_PreR_DIV

The PreR dividers divide the CLKinX reference

divider to keep the device in lock.

0. Allows use of DAC_LOW_TRIP,

DAC_HIGH_TRIP. Must be used with

EN_MAC_DAC = 1. CLKin_SELECT_MODE mus t

PLL1 PDF within the tolerances of PLL1_WND

divided by this divisor. For proper operation, DAC

update clock rate should be <= 100 kHz.

DAC update rate = PLL1 phase detector frequency

1 and holdover is engaged. Readback from this

register is the current DAC value whether in

switch event is generated. If Holdover mode is

enabled, it will be engaged upon the clock switch

event.

NOTE: EN_VTUNE_RAIL_DET must be enabled

clock switch event is generated. If Holdover mode

is enabled, it will be engaged upon the clock switch

event.

NOTE: EN_VTUNE_RAIL_DET must be enabled

feedback clocks is less than specified time, then

the PLL1 lock counter increments.

NOTE: Final lock detect valid signal is determined

when the PLL1 lock counter meets or exceeds the

within the window of phase error as specified by

PLL1

PLL1_WND_SIZE for this many cycles before

before the PLL1_R divider.

Unique divides on individual CLKinX signals allows

switchover from one clock input to another clock

input without needing to reprogram the PLL1_R

32 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 33

PLL1_N_DLY

N delay causes clock outputs to lead clock input

the input.

PLL1_R_DLY

R delay causes clock outputs to lag clock input

input.

PLL2_WND_SIZE

If the phase error between the PLL2 reference and

PLL2 lock counter increments.

PLL2_DLD_CNT

The reference and feedback of PLL2 must be

PLL2 digital lock detect is asserted.

EN_PLL2_REF_2X

Enables the doubler block to doubles the reference

at the phase detector of PLL2.

PLL2_N_CAL

The PLL2_N_CAL register contains the N value

PLL2_N_CAL registers will be exactly the same.

PLL2_R3_LF

Set the corresponding integrated PLL2 loop filter

the loop filter values on the Clock Outputs tab.

PLL2_R4_LF

PLL2_C3_LF

PLL2_C4_LF

PLL2_FAST_PDF

Enable this bit when using a PLL2 phase detector

frequency > 100 MHz.

SYNC

Sets these pins on the uWire header to logic high

Status_CLKin0

Status_CLKin1

when in a 0-delay mode. Increasing the N delay

value increases the output phase lead relative to

when in a 0-delay mode. Increasing the R delay

value increases the output phase lag relative to the

feedback clock is less than specified time, then the

within the window of phase error as specified by

PLL2_WND_SIZE for this many cycles before

frequency into the PLL2 R counter. This can allow

for frequency of 2/3, 2/5, etc. of OSCin to be used

PLL2

used for the VCO calibration routine. Except

during 0-delay modes, the PLL2_N and

Program Pins

values: R3, R4, C3, and C4.

It is also possible to set these values by clicking on

(checked) or logic low (unchecked).

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 33

Copyright © 2013, Texas Instruments Incorporated

Page 34

Registers Tab

Figure 14: Registers Tab

The Registers tab shows the value of each register. This is convenient for programming

the device to the desired settings, then exporting to a text file the register values in

hexadecimal for use in your own application.

By clicking in the “bit field” it is possible to manually change the value of registers by

typing ‘1’ and ‘0.’

34 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 35

Parameter

Value

PLL1 Reference clock input

CLKin1 single-ended input, CLKin1* AC-coupled to

GND

PLL1 Reference Clock

frequency

125 MHz

PLL1 Phase detector freq uenc y

2083.33 MHz

PLL1 Charge Pump Gain

400 uA

VCXO frequency

25 MHz

PLL2 phase detector freq uency

50 MHz

PLL2 Charge Pump Gain

3200 uA

PLL2 REF2X mode

Disabled

Appendix B: Typical Phase Noise Performance Plots

PLL1

The LMK04906B’s dual PLL architecture achieves ultra low jitter and phase noise by

allowing the external VCXO or Crystal’s phase noise to dominate the final output phase

noise at low offset frequencies and the internal VCO’s phase noise to dominate the final

output phase noise at high offset frequencies. This results in the best overall noise and

jitter performance.

Table 10 lists the test conditions used for output clock phase noise measurements with

the Epson 25 MHz VCXO.

Table 10: LMK04906B Test Conditions

25 MHz VCXO Phase Noise

The phase noise of the reference is masked by the phase noise of this VCXO by using

a narrow loop bandwidth for PLL1 while retaining the frequency accuracy of the

reference clock input. This VCXO sets the reference noise to PLL2. Figure 15 shows

the open loop typical phase noise performance of the Epson VG -4231CA 25.0000MFGRC3 VCXO.

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 35

Copyright © 2013, Texas Instruments Incorporated

Page 36

Table 11: VCXO Phase Noise

Phase

Noise

10 Hz

-73.6

100 Hz

-103.7

1 kHz

-130.8

10 kHz

-147.6

100 kHz

-155.42

1 MHz

-160.4

10 MHz

-168.1

40 MHz

-168.1

Table 12: VCXO RMS Jitter

Low

Offset

10 Hz

515.4

100 Hz

60.5

1 kHz

36.2

10 kHz

35.0

100 kHz

34.5

1 MHz

32.9

10 MHz

22.7

VCXO Phase Noise

-50

-60

-70

-80

-90

-100

-110

-120

-130

-140

Phase Noise (dBc/Hz)

-150

-160

-170

10 100 1000 10000 100000 1000000 10000000

Offset (Hz)

Figure 15: Epson VG-4231CA 25 MHz VCXO Phase Noise at 25 MHz

CVHD-930-25

at 25 MHz (dBc/Hz)

Offset

to high offset of 20 MHz

at 25 MHz (rms fs)

Jitter

Clock Output Measurement Technique

The same technique was used to measure phase noise for all three output types

available on the programmable OSCout and CLKout buffers. This was achieved by

connection the differential outputs to a Prodyn GXXX Balun and measuring the side

single-ended using an Agilent E5052B Source Signal Analyzer.

36 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 37

625 MHz LVPECL

1.6

156.25 MHz

LVPECL 1.6

125 MHz

LVPECL 1.6

100 Hz

-76.0

-88.0

-90.8

1 kHz

-103.2

-115.6

-117.1

10 kHz

-118.1

-130.2

-132.2

100 kHz

-121.5

-134.0

-136.0

800 kHz

-140.5

-152.5

-154.3

1 MHz

-142.7

-154.4

-156.1

10 MHz

-154.6

-161.1

-161.7

20 MHz

-154.8

-161.1

-161.8

RMS Jitter (fs)

12 kHz to 20 MHz

RMS Jitter (fs)

1 kHz to 5 MHz

Clock Outputs (CLKout)

The LMK04906 Family features programmable LVDS, LVPECL, and LVCMOS buffer modes for

the CLKoutX and OSCout0 output pairs. Included below are various phase noise

measurements for each output format. For the LMK04906B, the internal VCO frequency is 2500

MHz. The divide-by-4 CLKout frequency is 625 MHz, the divide-by-16 CLKout frequency is

156.25 MHz, and the divide-by-20 CLKout frequency is 125 MHz.

LMK04906B CLKout Phase Noise

LMK04906B CLKout Phase Noise

-70

-80

-90

-100

-110

-120

-130

Phase Noise (dBc/Hz)

-140

-150

-160

-170

100 1000 10000 100000 1000000 10000000

Frequency Offset (Hz)

Figure 16: LMK04906B CLKout Phase Noise

Table 13: LMK04906B Phase Noise (dBc/Hz) Phase Noise and RMS Jitter (fs)

Offset

156.25 MHz LVPECL16

125 MHz LVPECL16

625 MHz LVPECL16

146.0 147.4 149.5

166.4 160.6 159.8

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 37

Copyright © 2013, Texas Instruments Incorporated

Page 38

Appendix C: Schematics

Power Supplies

38 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 39

1

1

2

2

3

3

4

4

5

5

6

6

D D

C

C

B B

A

A

3 8Main

Sheet /

IC

8/1/

2013

LMK049xx_

PLL.SchDoc

She

et Title:

Size:

Schematic:

Mod. Date:

File:

Rev:

Shee

t: of

B

Texas Instr

uments

and/or its l

icensors

do not wa

rrant the

accuracy

or comple

teness o

f this

specific

ation o

r any informa

tion co

ntained there

in. Te

xas Instrumen

ts and

/or its licen

sors do

not

warra

nt that this

design w

ill meet the s

pecific

ations, will

be suitab

le for your

applicati

on or fit f

or

any particu

lar purpos

e, or will o

perate in a

n implementa

tion. Texas I

nstrument

s and/or its

l

icensors do

not warran

t that the de

sign is pro

duction worth

y. You sho

uld complet

ely validate

and

test your d

esign implemen

tation to c

onfirm the sy

stem function

ality for you

r application

.

http://www.t

i.com

Contact: ht

tp://www.nati

onal.com/suppo

rt

LMK0

49xx Evalu

ation Boa

rdProject

:

Designed

for:Eva

luation

Customer

8706

00738 1

Ass

embly Variant

:12-21-201

1

© Texas

Instruments Co

pyrightYear

1

00

pF

C

2p

_

VC

O

DNP

0

.1µ

F

C

38

DN

P

0.1µ

F

C30

10uF

C2_

VCXO

0

R

40

D

NP

2

pF

C36

DNP

22

00pF

C3

4

DN

P

2pF

C3

1

DNP

22

00pF

C

32

DNP

PL

L2

Lo

op F

ilt

er

P

LL1 Lo

op Fil

ter

O

SCin

Tun

eabl

e C

rys

tal

4.

7k

R

36

DNP

10

00pF

C33

DN

P

10

k

R38

DN

P

VCXO

Loop F

ilt

er

Y30

0

D

NP

D

NP

V

TU

N

E2

_T

P

0

R4

2

Designa

tors g

reater tha

n and equal

to 200

are plac

ed on bo

ttom of PCB

10

µF

C

37

0.1

µF

C3

9

C

LKo

ut0_

P

CL

Kou

t0_N

CL

Kout

1_P

C

LKo

ut1

_N

CLKout2_P

CLKout2_N

CLKin0_P

CLKin0_N

CLKin1_P

CLKin1_N

CLKin2_P

CLKin2_N

Status_Hold

S

tatu

s_L

D

Status_CLKin0

Status_CLKin1

CLKout5_N

CLKout5_P

CLKout4_N

CLKout4_P

CLKout3_N

CLKout3_P

SYN

C

0

R

35

DNP

uW

ire

_DA

T

A

uW

ire

_CLK

u

Wir

e_L

E

OS

Cou

t0_

N

OSCo

ut0

_P

Vc

c1_

VCO

Vcc

2_CLKout_C

G1

Vcc

3_CLKou

t_CG2

Vcc4

_Digita

l V

cc5_CLK

in

Vc

c6_PDCP1

Vcc

7_O

SC

Vcc

9_P

LL2

Vc

c12

_CL

Kou

t_

C

G5

V

cc

13

_

CL

Ko

u

t_

CG0

Vcc

8_P

DCP

2

O

SCi

n_N

O

SCin

_P

4.

7k

R39

DN

P

VT

UNE

1_TP

Vt

une

_VCX

O

S

tatus_H

old

SYN

C

S

tatus_LD

St

at

u

s_

CL

K

in

0

S

t

at

us

_

CL

Ki

n

1

uWir

e_L

E

u

Wi

re

_

DAT

A

u

Wir

e_C

LK

0.1

µF

C

35

D

NP

0

R4

3

V

CO

_V

t

un

e

0

R34

D

NP

0

.1µF

C

40

3.3µF

C1_VCXO

10u

F

C2A_VC

XO

1

k

R2

_VCX

O

6

20

R

2_V

CO

47pF

C1_

VC

O

39

00

p

F

C

2

_VCO

OS

Cin_

1_N

O

SCi

n_1

_P

1

3

2

SM

V12

49-0

74L

F

D1

DNP

CPo

ut1

Vcc

10_C

LKo

ut_

CG3

Vc

c

11

_C

L

Ko

ut

_

CG

4

OS

Cin

_1_

N

OS

Cin

_1_

P

5

1

R37

D

NP

V

cc

13

1

NC

2

CL

Kou

t0

4

CL

Kou

t0*

3

N

C

5

SY

NC/

Stat

us_

CLK

in2

6

NC

7

NC

8

NC

9

Vc

c1

1

0

LD

Oby

p1

1

1

L

DOb

yp2

12

NC

19

CLKout2*

20

NC

22

CLKout2

21

GND

23

Vcc4

24

FBCLKin/CLKin1

25

FBCLKin*/CLKin1*

26

Status_Holdover

27

CLKin0

28

CLKin0*

29

Vcc5

30

Vcc

6

35

O

SCi

n

36

O

SCin

*

37

Vc

c7

3

8

OSC

out0

39

OS

Cou

t0*

40

Vcc

8

41

CP

out

2

42

Vc

c9

43

LE

uWi

re

4

4

CLK

uWir

e

45

DA

TAu

Wir

e

46

NC

51

Vcc11

52

CLKout4

53

CLKout4*

54

NC

55

NC

56

Vcc12

57

CLKout5

58

CLKout5*

59

NC

60

NC

61

Status_CLKin0

62

LMK

049

06

DAP

PA

D

0

C

LKo

ut1

13

C

LKo

ut1

*

14

N

C

15

V

cc2

16

NC

17

Vcc3

18

CLKin2

31

CLKin2*

32

Sta

tus

_LD

3

3

C

Pou

t1

3

4

N

C

4

7

Vcc1

0

48

CLKout3

49

CLKout3*

50

Status_CLKin1

63

NC

64

U1

Us

e

d

in

BO

M

r

ep

or

t

Vt

une_

XTA

L

0

R41

DNP

Vt

une_

XTAL

100p

F

C3

_VC

XO

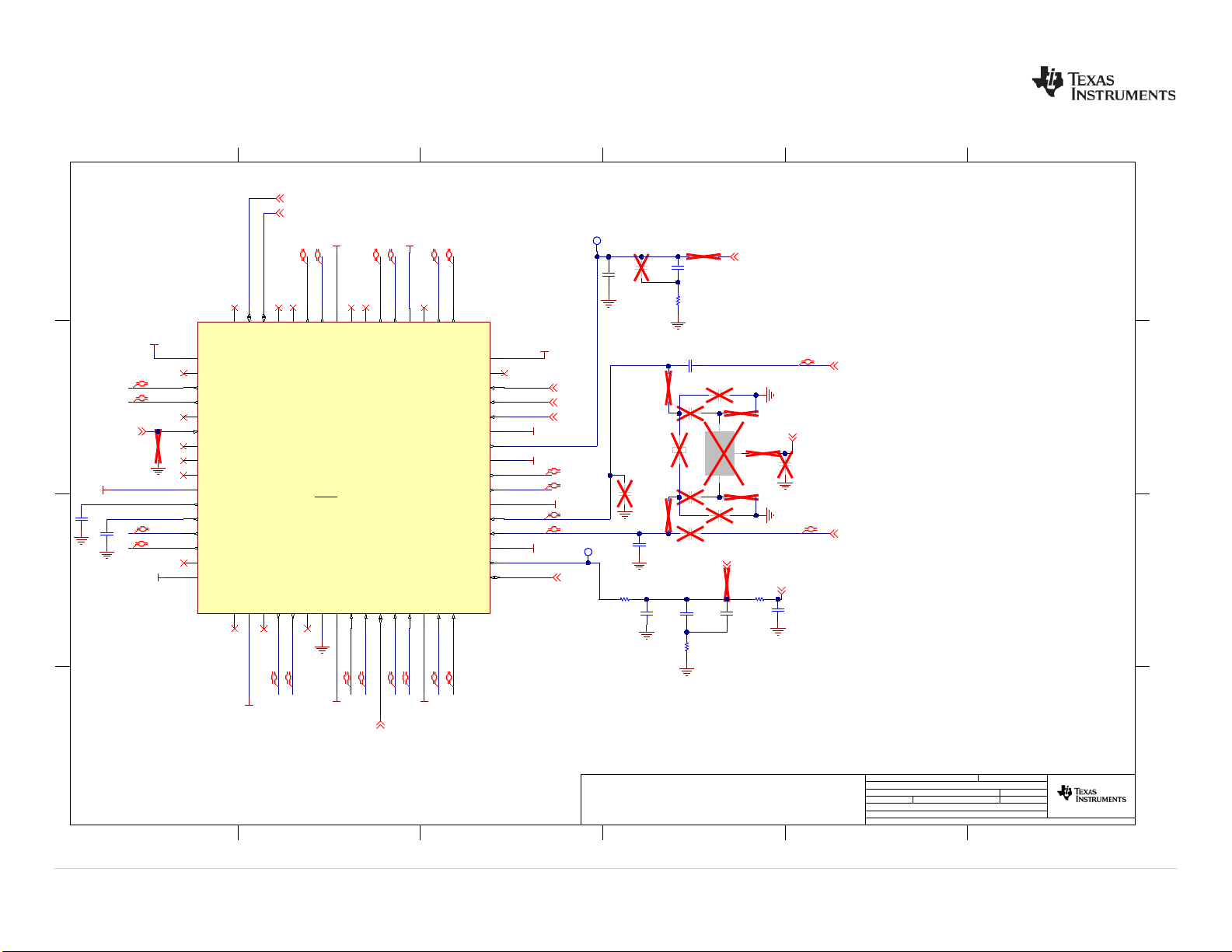

LMK04906B Device with Loop Filter and Crystal Circuits

Copyright © 2013, Texas Instruments Incorporated

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 39

Page 40

1

1

2

2

3

3

4

4

5

5

6

6

D D

C C

B B

A A

5 8Clock Inputs

8/1/2013

InClks.SchDoc

Sheet Title:

Size: Schematic:

Mod. Date:

File:

Rev:

Sheet: of

B

Texas Instruments and/or its licensors do not warrant the accuracy or completeness of this

specification or any information contained therein. Texas Instruments and/or its licensors do not

warrant that this design will meet the specifications, will be suitable for your application or fit for

any particular purpose, or will operate in an implementation. Texas Instruments and/or its

licensors do not war

rant that the design is production worthy. You should completely validate

and test your design implementation to confirm the system functionality for your application.

http://www.ti.com

Contact: http://www.national.com/support

LMK049xx Evaluation BoardProject:

Designed for:Evaluation Customer

870600738 1

Assembly Variant:12-21-2011

© Texas Instruments CopyrightYear

0.1µF

C15

18

R19

270

R20

0.1µF

C19

0.1µF

C14

DNP

100pF

C20

DNP

FBCLKin/CLKin1 Impedance Matching and Attenuation

CLKin1

0

R2

270

R4

DNP

0.1µF

C2

0.1µF

C10

0.1µF

C6

DNP

100

R5

0.1µF

C1

0

R8

0.1µF

C9

CLKin0 Impedance Matching and Attenuation

270

R11

DNP

0.1µF

C11

DNP

0.1µF

C25

0.1µF

C28

270

R29

DNP

270

R33

DNP

CLKin2 Impedance Matching and Attenuation

Vcc_VCO

100pF

C17

DNP

0.1µF

C16

0

R15

DNP

CLKin0_P

CLKin0_N

CLKin1_P

CLKin1_N

CLKin2_P

CLKin2_N

0.1µF

C27

0.1µF

C24

0

R27

0

R31

270

R28

DNP

270

R32

DNP

100

R30

GND

3

Vtune

2

GND

1

GND

7

Mo

d

6

GN

D

5

G

ND

8

GND

4

GND

9

Fout

10

GND

11

GND

12

GN

D

13

V

cc

14

GND

15

GND

16

U3

CRO2949A-LF

DNP

0.1µF

C21

DNP

0.1µF

C18

DNP

0

R24

DNP

10k

R25

DNP

10k

R26

DNP

Vcc_VCO_OpAmp

0

R23

DNP

Vcc_VCO_OpAmp

4

3

2

1

5

V+

V-

U4

LMP7731MF

DNP

VCO_Vtune

PLL2 External VCO Loop Filter

Vcc_VCO_LDO

0.1µF

C23

DNP

0

R22

DNP

270

R21

0.1µF

C22

DNP

CLKin0*

SMA

CLKin0

SMA

FBCLKin*/CLKin1*

SMA

CLKin2*

SMA

CLKin2

SMA

CLKin2_2_N

CLkin2_2_P

CLKin0_2_N

CLKin0_2_P

0.1uF

C29

DNP

270

R10

DNP

270

R3

DNP

Vtune

1

NC

2

GND

3

RF

4

RF*

5

Vs

6

U2

VG-4231CA 25.0000M-FGRC3

OSCin VCXO

8.2

R12

DNP

8.2

R9

DNP

140

R7

DNP

0

R14

0.1µF

C7

DNP

0.1µF

C13

DNP

0.1µF

C12

0.1µF

C8

DNP

120

R1

OSCin_1_N

OSCin_1_P

OSCin

SMA

DNP

OSCin*

SMA

DNP

10µF

C3

2200pF

C4

82pF

C5

Switch capacitor for signal

(shared pad)

Switch capacitor for signal

(shared pad)

0

R16

Vtune_VCXO

VCC_VCXO_TP

Vcc_VCXO

0.1uF

C26

DNP

CLKin2_1_P

CLKin2_1_N

0

R13

140

R6

DNP

120

R17

DNP

120

R18

DNP

Reference Inputs (CLKin0, CLKin1 & CLKin2), External VCXO (OSCin) & VCO Circuits

40 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 41

Clock Outputs (OSCout0, CLKout0 to CLKout5)

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 41

Copyright © 2013, Texas Instruments Incorporated

Page 42

uWire Header , Logic I/O Ports and Status LEDs

42 SNAU126A LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs Revised - December 2013

Copyright © 2013, Texas Instruments Incorporated

Page 43

Item

Designator

Description

Manufacturer

PartNumber

Qty

1

C1, C2, C9

CAP, CERM, 0.1uF, 16V, +/-10%, X7R, 0603

Kemet

C0603C104K4RACTU

3

2

C1_VCO

CAP, CERM, 82pF, 50V, +/-5%, C0G/NP0, 0603

MuRata

GRM1885C1H820JA01D

1

3

C1_VCXO

CAP, CERM, 3.3uF, 10V, +/-10%, X5R, 0805

Kemet

C0805C335K8PACTU

1

4

C2_VCO

CAP, CERM, 5600pF, 50V, +/-10%, X7R, 0603

MuRata

GRM188R71H562KA01D

1

5

C3

CAP, CERM, 10µF, 10V, +/-20%, X5R, 0805

Kemet

C0805C106M8PACTU

1

6

C3_VCXO

CAP, CERM, 100pF, 50V, +/-5%, C0G/NP0, 0603

Kemet

C0603C101J5GACTU

1

7

C4

CAP, CERM, 2200pF, 50V, +/-10%, X7R, 0603

Kemet

C0603C222K5RACTU

1

8

C5

CAP, CERM, 82pF, 50V, +/-10%, C0G/NP0, 0603

Kemet

C0603C820K5GACTU

1

9

C10, C15, C16,

C81

CAP, CERM, 0.1uF, 25V, + / -5%, X7R, 0603

Kemet

C0603C104J3RACTU

28

10

C12

CAP, CERM, 0.1µF, 25V, +/-10%, X7R, 0603

Kemet

C0603C104K3RACTU

1

11

C37, C61, C67,

C2A_VCXO

CAP, CERM, 10uF, 10V, +/-10%, X5R, 0805

Kemet

C0805C106K8PACTU

7

12

C56, C65, C72,

C75

CAP, CERM, 0.1uF, 25V, +/-10%, X7R, 0603

Kemet

C0603C104K3RACTU

4

13

C64, C71

CAP, CERM, 1uF, 10V, +/-10%, X5R, 0603

Kemet

C0603C105K8PACTU

2

14

C83

CAP, CERM, 4.7uF, 10V, +/-10%, X5R, 0603

Kemet

C0603C475K8PACTU

1

15

C84

CAP, CERM, 2200pF, 100V, +/-5%, X7R, 0603

AVX

06031C222JAT2A

1

16

C85

CAP, CERM, 1uF, 16V, +/-10%, X7R, 0603

TDK

C1608X7R1C105K

1

17

C88

CAP, CERM, 0.01uF, 25V, +/-5%, C0G/NP0, 0603

TDK

C1608C0G1E103J

1

18

C94, C96

CAP, CERM, 0.47uF, 25V, +/-10%, X7R, 0603

MuRata

GRM188R71E474KA12D

2

19

CLKin0, CLKin0*,

CLKout0,

Connector, SMT, End launch SMA 50 Ohm

Emerson Network

142-0701-851

20

Appendix D: Bill of Materials

Table 14: Bill of Materials for LMK04906 Evaluation Boards

C19, C24, C25,

C27, C28, C30,

C39, C40, C47,

C48, C49, C50,

C51, C52, C53,

C54, C55, C57,

C58, C59, C60,

C63, C69, C78,

C73, C86,

C2_VCXO,

CLKin2, CLKin2*,

Revised - December 2013 LMK04906 Family: Low-Noise Clock Jitter with Dual Loop PLLs SNAU126A 43

Power

Copyright © 2013, Texas Instruments Incorporated

Page 44