This device is not yet released to market. Volume shipments possible under waiver.

CC2430

A True System-on-Chip solution for 2.4 GHz IEEE 802.15.4 / ZigBee™

Applications

• 2.4 GHz IEEE 802.15.4 systems

• ZigBee™ systems

• Home/building automation

• Industrial Control and Monitoring

Product Description

The

CC2430

CC2430-F32/64/128, with 32/64/128 KB of

flash memory respectively. The

true System-on-Chip (SoC) solution

specifically tailored for IEEE 802.15.4 and

ZigBee™ applications. It enables ZigBee™

nodes to be built with very low total bill-ofmaterial costs. The

excellent performance of the leading

RF transceiver with an industry-standard

enhanced 8051 MCU, 32/64/128 KB flash

memory, 8 KB RAM and many other powerful

features. Combined with the industry leading

ZigBee™ protocol stack (Z-Stack) from Figure

8 Wireless / Chipcon, the

market’s most competitive ZigBee™ solution.

comes in three different versions:

CC2430

CC2430

combines the

is a

CC2420

CC2430

provides the

• Low power wireless sensor network s

• PC peripherals

• Set-top boxes and remote controls

• Consumer Electronics

The

CC2430

is highly suited for systems where

ultra low power consumption is required. This

is ensured by various operating modes. Short

transition times between operating modes

further ensure low power consumption.

Key Features

• High performance and low power 8051

microcontroller core.

• 2.4 GHz IEEE 802.15.4 compliant RF

transceiver (industry leading

core).

• Excellent receiver sensitivity and robustness to

interferers

• 32, 64 or 128 KB in-system programmable

flash

• 8 KB RAM, 4 KB with data retention in all

power modes

• Powerful DMA functionality

• Very few external components

• Only a single crystal needed for mesh network

systems

• Low current consumption (RX: 27mA, TX:

27mA, microcontroller running at 32 MHz)

• Only 0.5 µA current consumption in power-

down mode, where external interrupts or the

RTC can wake up the system

• 0.3 µA current consumption in stand-by mode,

where external interrupts can wake up the

system

• Very fast transition times from low-power

modes to active mode enables ultra low

CC2420

radio

average power consumption in low duty-cycle

systems

• CSMA/CA hardware support.

• Wide supply voltage range (2.0V – 3.6V)

• Digital RSSI / LQI support

• Battery monitor and temperature sensor

• ADC with up to eight inputs and configurable

resolution

• AES security coprocessor

• Two powerful USARTs with support for several

serial protocols

• Watchdog timer

• One IEEE 802.15.4 MAC Timer, one general

16-bit timer and two 8-bit timers

• Hardware debug support

• 21 general I/O pins, two with 20mA sink/source

capability

• Powerful and flexible development tools

available

• RoHS compliant 7x7mm QLP48 package

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 1 of 233

Table Of Contents

1

ABBREVIATIONS.....................................................................................................................5

2

REFERENCES...........................................................................................................................7

3

REGISTER CONVENTIONS...................................................................................................8

4

FEATURES (CONTINUED FROM FRONT PAGE).............................................................9

4.1

4.2

4.3

4.4

4.5

4.6

4.7

5

6

7

7.1

7.2

7.3

7.4

7.5

7.6

7.7

7.8

7.9

7.10

7.11

7.12

7.13

7.14

7.15

7.16

8

H

IGH-PERFORMANCE AND LOW-POWER

U

P TO

128 KB NON-

H

ARDWARE

P

ERIPHERAL FEATURES

L

OW POWER

802.15.4 MAC

I

NTEGRATED

ABSOLUTE MAXIMUM RATINGS.....................................................................................10

OPERATING CONDITIONS.................................................................................................10

ELECTRICAL SPECIFICATIONS.......................................................................................11

G

ENERAL CHARACTERISTICS

RF R

RF T

32 MHZ C

32.768 KHZ C

32 KHZ RC O

H

IGH FREQUENCY RC OSCILLATOR

F

REQUENCY SYNTHESIZER CHARACTERISTICS

A

NALOG TEMPERATURE SENSOR

ADC.......................................................................................................................................19

C

ONTROL AC CHARACTERISTICS

SPI AC C

D

EBUG INTERFACE AC CHARACTERISTICS

P

ORT OUTPUTS AC CHARACTERISTICS

T

IMER INPUTS AC CHARACTERISTICS

DC C

PIN AND I/O PORT CONFIGURATION.............................................................................24

AES E

.............................................................................................................................9

ECEIVE SECTION

RANSMIT SECTION

RYSTAL OSCILLATOR

HARACTERISTICS

HARACTERISTICS

This device is not yet released to market. Volume shipments possible under waiver.

8051-C

VOLATILE PROGRAM MEMORY AND 2 X 4 KB DATA MEMORY

NCRYPTION/DECRYPTION

............................................................................................................9

HARDWARE SUPPORT

2.4GHZ DSSS D

.................................................................................................12

.............................................................................................................13

..........................................................................................................15

RYSTAL OSCILLATOR

SCILLATOR

........................................................................................................16

.....................................................................................................21

...........................................................................................................23

.......................................................................................9

IGITAL RADIO

.............................................................................................15

.......................................................................................16

.......................................................................................17

...........................................................................................18

...........................................................................................20

..................................................................................22

....................................................................................23

OMPATIBLE MICROCONTROLLER

...........................................................................9

...........................................................................9

.......................................................................17

............................................................................22

CC2430

..................9

................9

9

9.1

9.2

10

11

11.1

11.2

11.3

11.4

11.5

11.6

12

12.1

12.2

12.3

12.4

12.5

12.6

12.7

CIRCUIT DESCRIPTION......................................................................................................26

CPU

AND PERIPHERALS

R

ADIO

....................................................................................................................................28

POWER MANAGEMENT......................................................................................................29

APPLICATION CIRCUIT......................................................................................................30

I

NPUT / OUTPUT MATCHING

B

IAS RESISTORS

C

RYSTAL

V

OLTAGE REGULATORS

D

EBUG INTERFACE

P

OWER SUPPLY DECOUPLING AND FILTERING

8051 CPU...................................................................................................................................33

8051 CPU I

R

ESET

.....................................................................................................................................33

M

EMORY

SFR R

EGISTERS

CPU R

EGISTERS

I

NSTRUCTION SET SUMMARY

I

NTERRUPTS

......................................................................................................................30

................................................................................................................................30

NTRODUCTION

................................................................................................................................33

......................................................................................................................44

...........................................................................................................................53

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 2 of 233

.........................................................................................................26

....................................................................................................30

..........................................................................................................30

.................................................................................................................30

.........................................................................30

.....................................................................................................33

.....................................................................................................................47

.................................................................................................49

12.8

12.9

12.10

12.11

12.12

13

13.1

13.2

13.3

13.4

13.5

13.6

13.7

13.8

13.9

13.10

13.11

13.12

13.13

13.14

14

14.1

14.2

14.3

14.4

14.5

14.6

14.7

14.8

14.9

14.10

14.11

14.12

14.13

14.14

14.15

14.16

14.17

14.18

14.19

14.20

14.21

14.22

14.23

14.24

14.25

14.26

14.27

14.28

14.29

14.30

14.31

14.32

14.33

14.34

14.35

15

This device is not yet released to market. Volume shipments possible under waiver.

O

SCILLATORS AND CLOCKS

D

EBUG INTERFACE

RAM......................................................................................................................................68

F

LASH MEMORY

M

EMORY ARBITER

PERIPHERALS........................................................................................................................71

I/O

PORTS

...............................................................................................................................71

DMA C

16MAC T

S

8-

ADC.....................................................................................................................................122

R

AES C

P

P

W

USART................................................................................................................................144

F

RADIO.....................................................................................................................................161

IEEE 802.15.4 M

C

RF R

I

FIFO

DMA....................................................................................................................................167

R

RXFIFO

T

G

D

F

S

L

MAC

F

RF D

A

A

R

MAC S

L

RSSI / E

L

C

F

VCO

O

I

T

S

PCB L

A

CSMA/CA S

R

RADIO TEST OUTPUT SIGNALS......................................................................................218

ONTROLLER

BIT TIMER, TIMER

IMER (TIMER

LEEP TIMER

BIT TIMER 3 AND TIMER

ANDOM NUMBER GENERATOR

OPROCESSOR

OWER MANAGEMENT

OWER ON RESET AND BROWN OUT DETECTOR

ATCHDOG TIMER

LASH CONTROLLER

OMMAND STROBES

EGISTERS

NTERRUPTS

ACCESS

ECEIVE MODE

OVERFLOW

RANSMIT MODE

ENERAL CONTROL AND STATUS

EMODULATOR, SYMBOL SYNCHRONIZER AND DATA DECISION

RAME FORMAT

YNCHRONIZATION HEADER

ENGTH FIELD

PROTOCOL DATA UNIT

RAME CHECK SEQUENCE

ATA BUFFERING

DDRESS RECOGNITION

CKNOWLEDGE FRAMES

ADIO CONTROL STATE MACHINE

ECURITY OPERATIONS (ENCRYPTION AND AUTHENTICATION

INEAR IF AND

NERGY DETECTION

INK QUALITY INDICATION

LEAR CHANNEL ASSESSMENT

REQUENCY AND CHANNEL PROGRAMMING

AND

PLL S

UTPUT POWER PROGRAMMING

NPUT / OUTPUT MATCHING

RANSMITTER TEST MODES

YSTEM CONSIDERATIONS AND GUIDELINES

AYOUT RECOMMENDATION

NTENNA CONSIDERATIONS

ADIO REGISTERS

.................................................................................................................64

.....................................................................................................................68

.................................................................................................................68

........................................................................................................................111

..............................................................................................................130

...............................................................................................................142

ODULATION FORMAT

......................................................................................................................163

.........................................................................................................................163

........................................................................................................................166

.....................................................................................................................167

..................................................................................................................168

...................................................................................................................170

......................................................................................................................171

AGC S

ELF-CALIBRATION

TROBE PROCESSOR

................................................................................................................198

....................................................................................................63

...............................................................................................................81

1 ...........................................................................................................92

2)........................................................................................................104

4.................................................................................................113

...........................................................................................128

.........................................................................................................135

..................................................................141

............................................................................................................154

................................................................................162

.............................................................................................................163

............................................................................................................167

.........................................................................................169

.........................................169

.................................................................................................170

................................................................................................171

.....................................................................................................172

...........................................................................................................173

.......................................................................................................174

......................................................................................................174

........................................................................................176

ETTINGS

...........................................................................................178

.................................................................................................178

..................................................................................................178

............................................................................................179

........................................................................179

.....................................................................................180

..........................................................................................180

.................................................................................................181

.................................................................................................181

.......................................................................183

.......................................................................................185

................................................................................................186

..........................................................................................186

CC2430

).................................177

16

VOLTAGE REGULATORS .................................................................................................219

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 3 of 233

16.1

17

18

19

19.1

19.2

19.3

19.4

19.5

20

21

21.1

21.2

22

23

This device is not yet released to market. Volume shipments possible under waiver.

V

OLTAGE REGULATORS POWER-ON

EVALUATION SOFTWARE...............................................................................................219

REGISTER OVERVIEW......................................................................................................220

PACKAGE DESCRIPTION (QLP 48).................................................................................223

R

ECOMMENDED

P

ACKAGE THERMAL PROPERTIES

S

OLDERING INFORMATION

T

RAY SPECIFICATION

C

ARRIER TAPE AND REEL SPECIFICATION

ORDERING INFORMATION..............................................................................................226

GENERAL INFORMATION................................................................................................227

D

OCUMENT HISTORY

P

RODUCT STATUS DEFINITIONS

ADDRESS INFORMATION.................................................................................................230

TI WORLDWIDE TECHNICAL SUPPORT......................................................................230

PCB

LAYOUT FOR PACKAGE

....................................................................................................224

............................................................................................................224

...........................................................................................................227

.....................................................................................219

(QLP 48).......................................................224

..........................................................................................224

.............................................................................225

...........................................................................................230

CC2430

IMPORTANT NOTICE.....................................................................................................................233

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 4 of 233

This device is not yet released to market. Volume shipments possible under waiver.

1 Abbreviations

CC2430

ADC Analog to Digital Converter

AES Advanced Encryption Standard

AGC Automatic Gain Control

ARIB Association of Radio Industries and

Businesses

BCD Binary Coded Decimal

BER Bit Error Rate

BOD Brown Out Detector

BOM Bill of Materials

CBC Cipher Block Chaining

CBC-MAC Cipher Block Chaining Message

Authentication Code

CCA Clear Channel Assessment

CCM Counter mode + CBC-MAC

CFB Cipher Feedback

CFR Code of Federal Regulations

CMOS Complementary Metal Oxide

Semiconductor

CPU Central Processing Unit

CRC Cyclic Redundancy Check

CSMA-CA Carrier Sense Multiple Access with

Collision Avoidance

CSP CSMA/CA Strobe Processor

CTR Counter mode (encryption)

CW Continuous Wave

DAC Digital to Analog Converter

DC Direct Current

DMA Direct Memory Access

DSM Delta Sigma Modulator

DSSS Direct Sequence Spread Spectrum

ECB Electronic Code Book (encryption)

EM Evaluation Module

ESD Electro Static Discharge

ESR Equivalent Series Resistance

ETSI European Telecommunications

Standards Institute

EVM Error Vector Magnitude

FCC Federal Communications Commission

FCF Frame Control Field

FCS Frame Check Sequence

FFCTRL FIFO and Frame Control

FIFO First In First Out

HF High Frequency

HSSD High Speed Serial Data

I/O Input / Output

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 5 of 233

I/Q In-phase / Quadrature-phase

IEEE Institute of Electrical and Electronics

Engineers

IF Intermediate Frequency

IOC I/O Controller

ISM Industrial, Scientific and Medical

ITU-T International Telecommunication Union

– Telecommunication Standardization

Sector

IV Initialization Vector

IRQ Interrupt Request

JEDEC Joint Electron Device Engineering

Council

KB 1024 bytes

kbps kilo bits per second

LC Inductor-capacitor

LFSR Linear Feedback Shift Register

LNA Low-Noise Amplifier

LO Local Oscillator

LQI Link Quality Indication

LSB Least Significant Bit / Byte

LSB Least Significant Byte

MAC Medium Access Control

MAC Message Authentication Code

MCU Microcontroller Unit

MFR MAC Footer

MHR MAC Header

MIC Message Integrity Code

MISO Master In Slave Out

MPDU MAC Protocol Data Unit

MOSI Master Out Slave In

MSB Most Significant Byte

MSDU MAC Service Data Unit

MUX Multiplexer

NA Not Available

NC Not Connected

OFB Output Feedback (encryption)

O-QPSK Offset - Quadrature Phase Shift Keying

PA Power Amplifier

PCB Printed Circuit Board

PER Packet Error Rate

PHR PHY Header

PHY Physical Layer

PLL Phase Locked Loop

This device is not yet released to market. Volume shipments possible under waiver.

PM{0-3} Power Mode 0-3

PMC Power Management Controller

POR Power On Reset

PSDU PHY Service Data Unit

PWM Pulse Width Modulator

QLP Quad Leadless Package

RAM Random Access Memory

RBW Resolution Bandwidth

RC Resistor-Capacitor

RCOSC RC Oscillator

RF Radio Frequency

RoHS Restriction on Hazardous Substances

RSSI Receive Signal Strength Indicator

RTC Real-Time Clock

RX Receive

SCK Serial Clock

SFD Start of Frame Delimiter

SFR Special Function Register

SHR Synchronization Header

SINAD Signal-to-noise and distortion ratio

SPI Serial Peripheral Interface

SRAM Static Random Access Memory

ST Sleep Timer

T/R Transmit / Receive

T/R Tape and reel

TBD To Be Decided / To Be Defined

THD Total Harmonic Distortion

TI Texas Instruments

TX Transmit

UART Universal Asynchronous

Receiver/Transmitter

USART Universal Synchronous/Asynchronous

Receiver/Transmitter

VCO Voltage Controlled Oscillator

VGA Variable Gain Amplifier

WDT Watchdog Timer

XOSC Crystal Oscillator

CC2430

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 6 of 233

This device is not yet released to market. Volume shipments possible under waiver.

2 References

[1] IEEE std. 802.15.4 - 2003: Wireless Medium Access Control (MAC) and Physical Layer

(PHY) specifications for Low Rate Wireless Personal Area Networks (LR-WPANs)

CC2430

http://standards.ieee.org/getieee802/download/802.15.4-2003.pdf

[2] NIST FIPS Pub 197: Advanced Encryption Standard (AES), Federal Information Processing

Standards Publication 197, US Department of Commerce/N.I.S.T., November 26, 2001.

Available from the NIST website.

http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 7 of 233

This device is not yet released to market. Volume shipments possible under waiver.

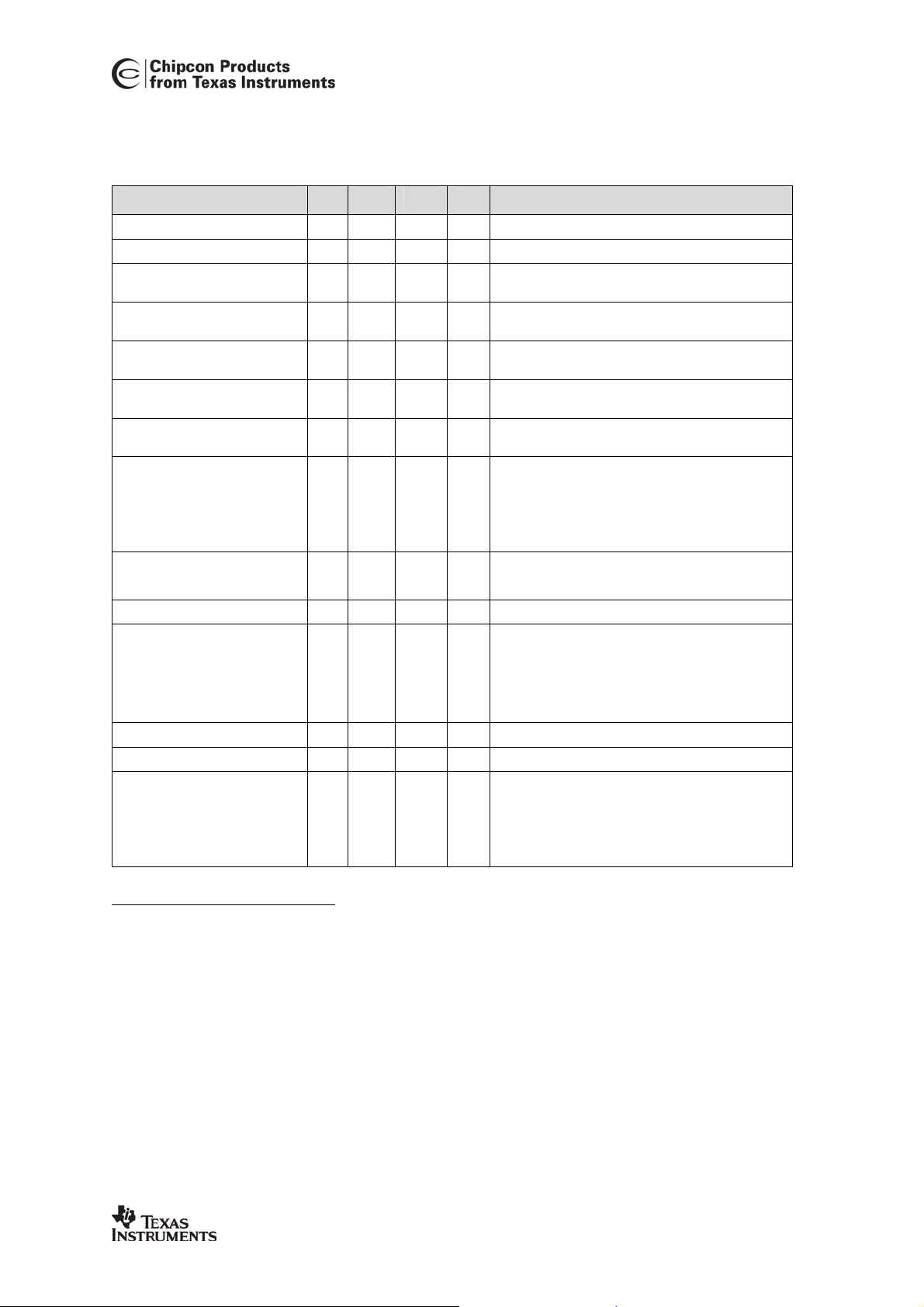

3 Register conventions

Each SFR register is described in a separate table. The table heading is given in the following format:

REGISTER NAME (SFR Address) - Register Description.

Each RF register is described in a separate table. The table heading is given in the following format:

REGISTER NAME (XDATA Address)

In the register descriptions, each register bit is shown with a symbol indicating the access mode of the

register bit. The register values are always given in binary notation unless prefixed by ‘0x’ which

indicates hexadecimal notation.

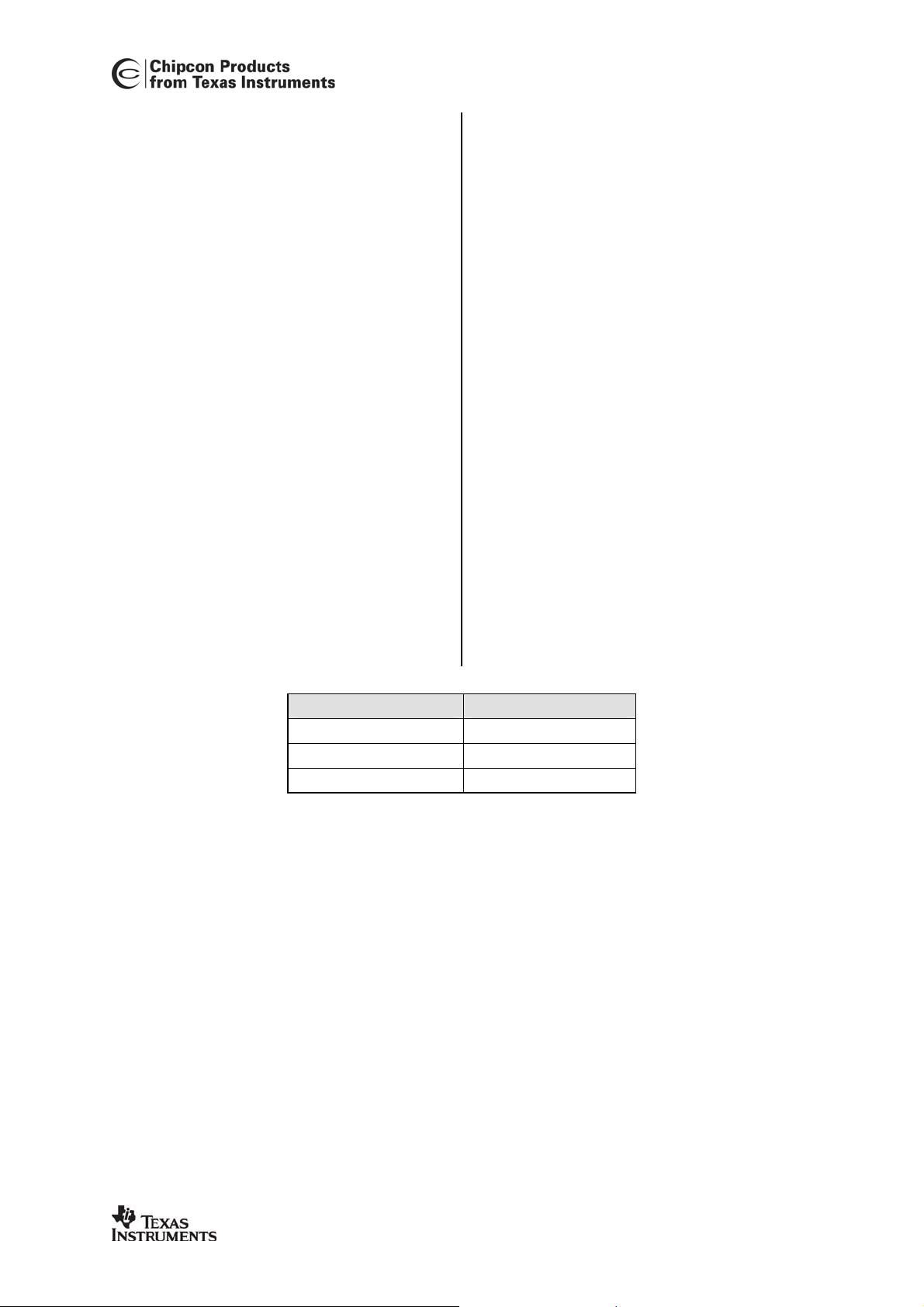

Symbol Access Mode

R/W Read/write

R Read only

R0 Read as 0

R1 Read as 1

W Write only

W0 Write as 0

W1 Write as 1

H0 Hardware clear

H1 Hardware set

CC2430

Table 1: Register bit conventions

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 8 of 233

This device is not yet released to market. Volume shipments possible under waiver.

4 Features (continued from front page)

4.1 High-Performance and Low-Power

8051-Compatible Microcontroller

• Optimized 8051 core, which typically gives

8x the performance of a standard 8051

• Dual data pointers

• In-circuit interactive debugging is supported

for the IAR Embedded Workbench through

a simple two-wire serial interface

4.2 Up to 128 KB Non-volatile Program

Memory and 2 x 4 KB Data Memory

• 32/64/128 KB of non-volatile flash memory

in-system programmable through a simple

two-wire interface or by the 8051 core

• Worst-case flash memory endurance:

1000 write/erase cycles.

CC2430

• True random number generator

4.5 Low Power

• Four flexible power modes for reduced

power consumption

• System can wake up on external interrupt

or real-time counter event

• Low-power fully static CMOS design

• System clock source can be 16 MHz RC

oscillator or 32 MHz crystal oscillator. The

32 MHz oscillator is used when radio is

active.

• Optional clock source for ultra-low power

operation can be either low-power RC

oscillator or an optional 32.768 kHz crystal

oscillator.

• Programmable read and write lock of

portions of Flash memory for software

security

• 4096 bytes of internal SRAM with data

retention in all power modes.

• Additional 4096 bytes of internal SRAM

with data retention in power modes 0 and

1.

4.3 Hardware AES Encryption/Decryption

• AES supported in hardware coprocessor

4.4 Peripheral Features

• Powerful DMA Controller

• Power On Reset/Brown-Out Detection

• Eight channel ADC with configurable

resolution

• Programmable watchdog timer

• Real time clock with 32.768 kHz crystal

oscillator

• Four timers: one general 16-bit timer, two

general 8-bit timers, one MAC timer

• Two programmable USARTs for

master/slave SPI or UART operation

4.6 802.15.4 MAC hardware support

• Automatic preamble generator

• Synchronization word insertion/detection

• CRC-16 computation and checking over

the MAC payload

• Clear Channel Assessment

• Energy detection / digital RSSI

• Link Quality Indication

• CSMA/CA Coprocessor

4.7 Integrated 2.4GHz DSSS Digital Radio

• 2.4 GHz IEEE 802.15.4 compliant RF

transceiver (based on industry leading

CC2420

• Excellent receiver sensitivity and

robustness to interferers

• 250 kbps data rate, 2 MChip/s chip rate

• Reference designs comply with worldwide

radio frequency regulations covered by

ETSI EN 300 328 and EN 300 440 class 2

(Europe), FCC CFR47 Part 15 (US) and

ARIB STD-T66 (Japan). Operation on

2480MHz under FCC is supported by

duty-cycling or by reducing output power.

radio core).

• 21 configurable general-purpose digital

I/O-pins

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 9 of 233

This device is not yet released to market. Volume shipments possible under waiver.

5 Absolute Maximum Ratings

Under no circumstances must the absolute maximum ratings given in Table 2 be violated. Stress

exceeding one or more of the limiting values may cause permanent damage to the device.

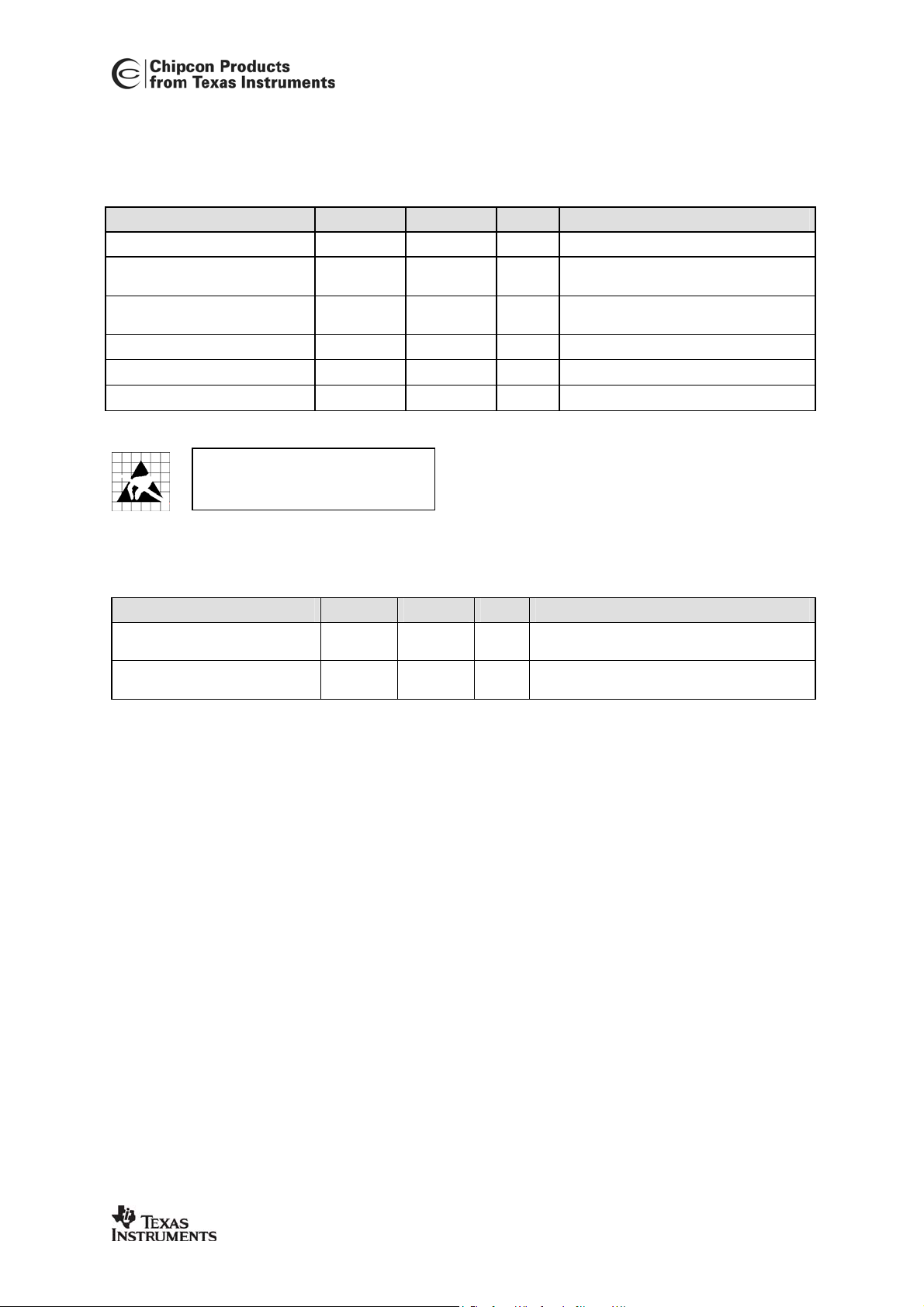

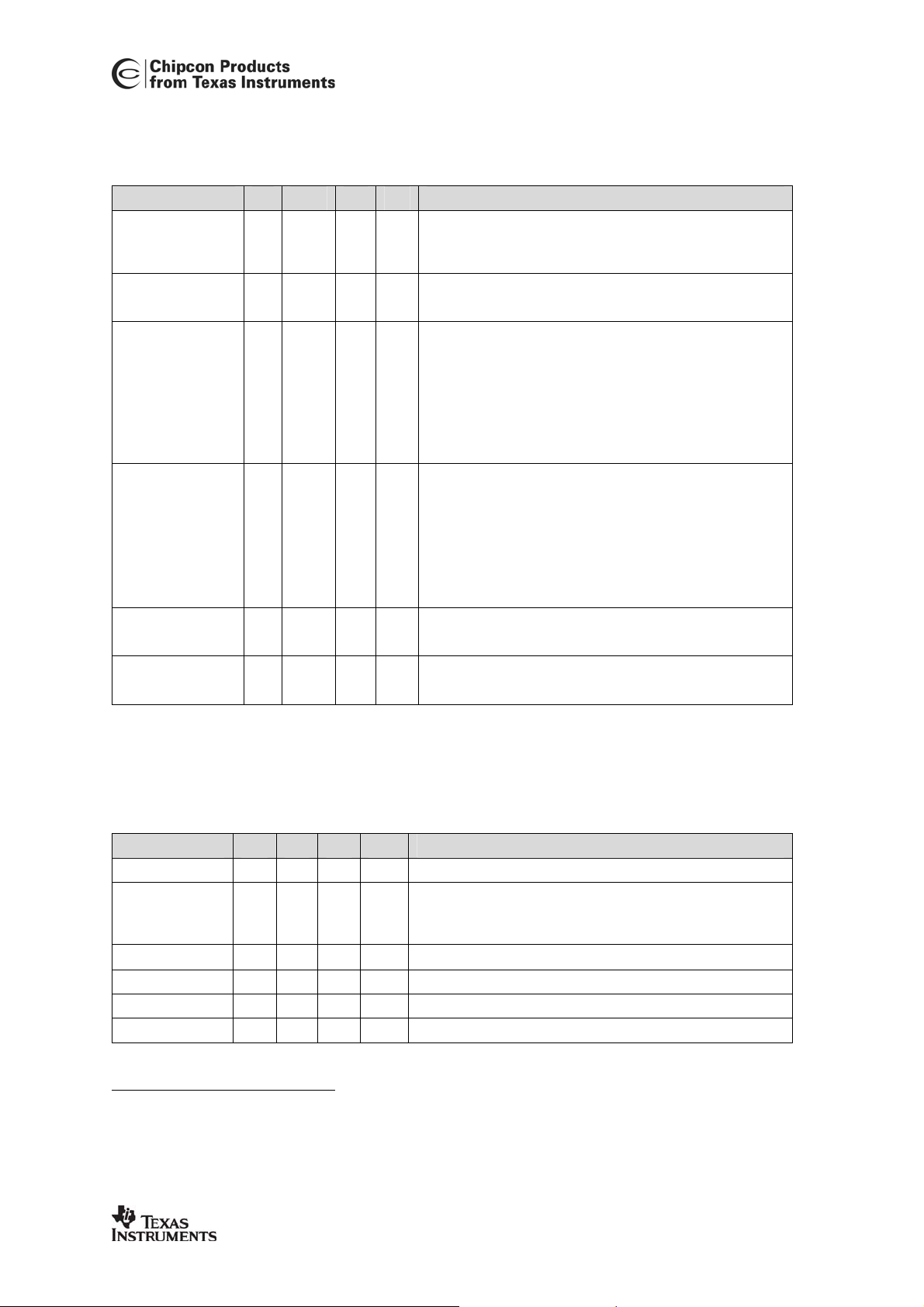

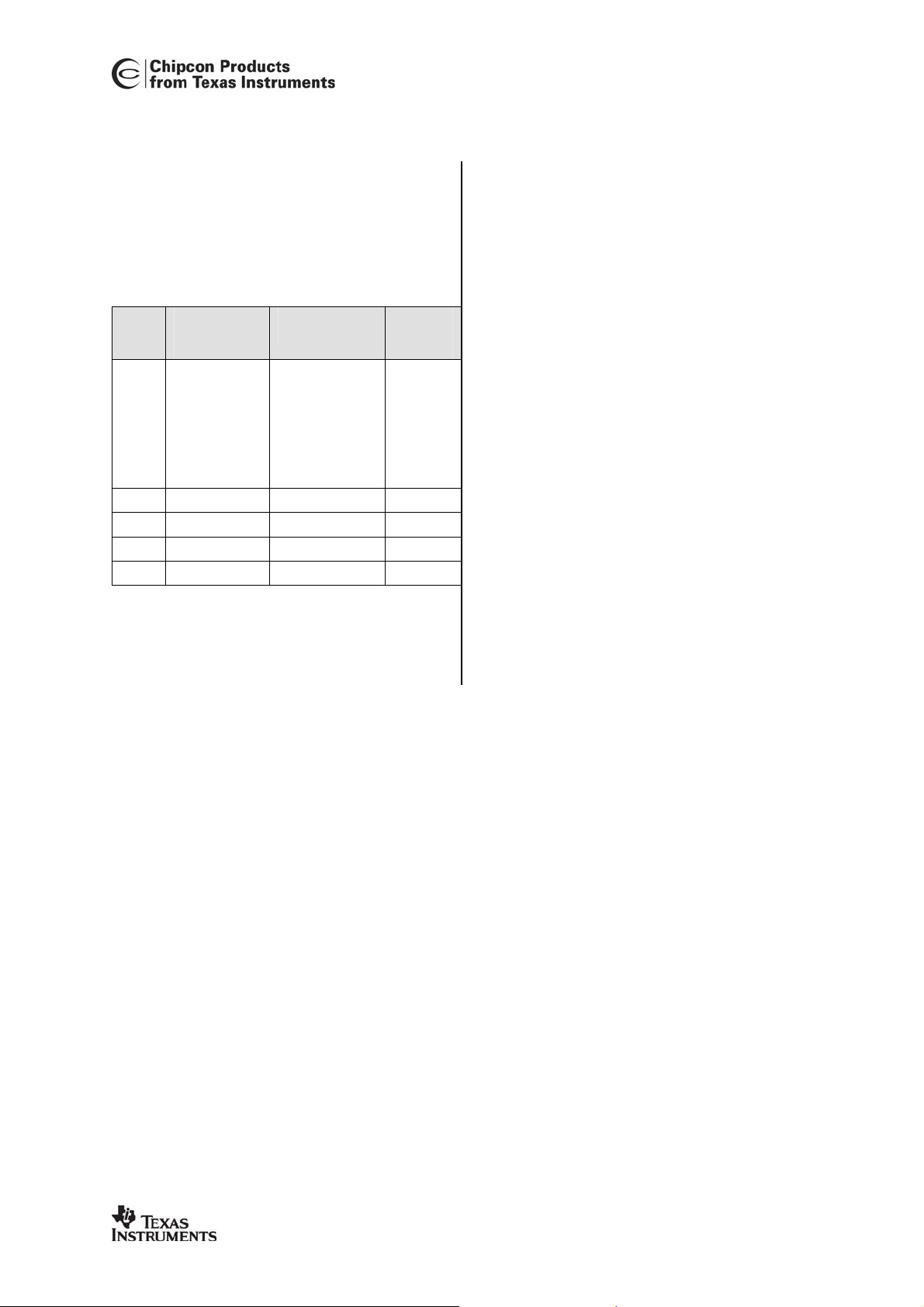

Parameter Min Max Units Condition

Supply voltage –0.3 3.6 V All supply pins must have the same voltage

Voltage on any digital pin –0.3 VDD+0.3,

Voltage on the 1.8V pins (pin no.

22, 25-40 and 42)

Input RF level 10 dBm

Storage temperature range –50 150

Reflow soldering temperature 260

–0.3 2.0 V

max 3.6

Table 2: Absolute Maximum Rati ngs

Caution! ESD sensitive device.

Precaution should be used when handling

the device in order to prevent permanent

damage.

V

Device not programmed

°C

According to IPC/JEDEC J-STD-020C

°C

CC2430

6 Operating Conditions

The operating conditions for

Parameter Min Max Unit Condition

Operating ambient temperature

range, T

Operating supply voltage 2.0 3.6 V The supply pins to the radio part must be driven

A

CC2430

are listed in Table 3 .

-40 85

Table 3: Operating Condi tions

°C

by the 1.8 V on-chip regulator

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 10 of 233

This device is not yet released to market. Volume shipments possible under waiver.

7 Electrical Specifications

CC2430

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

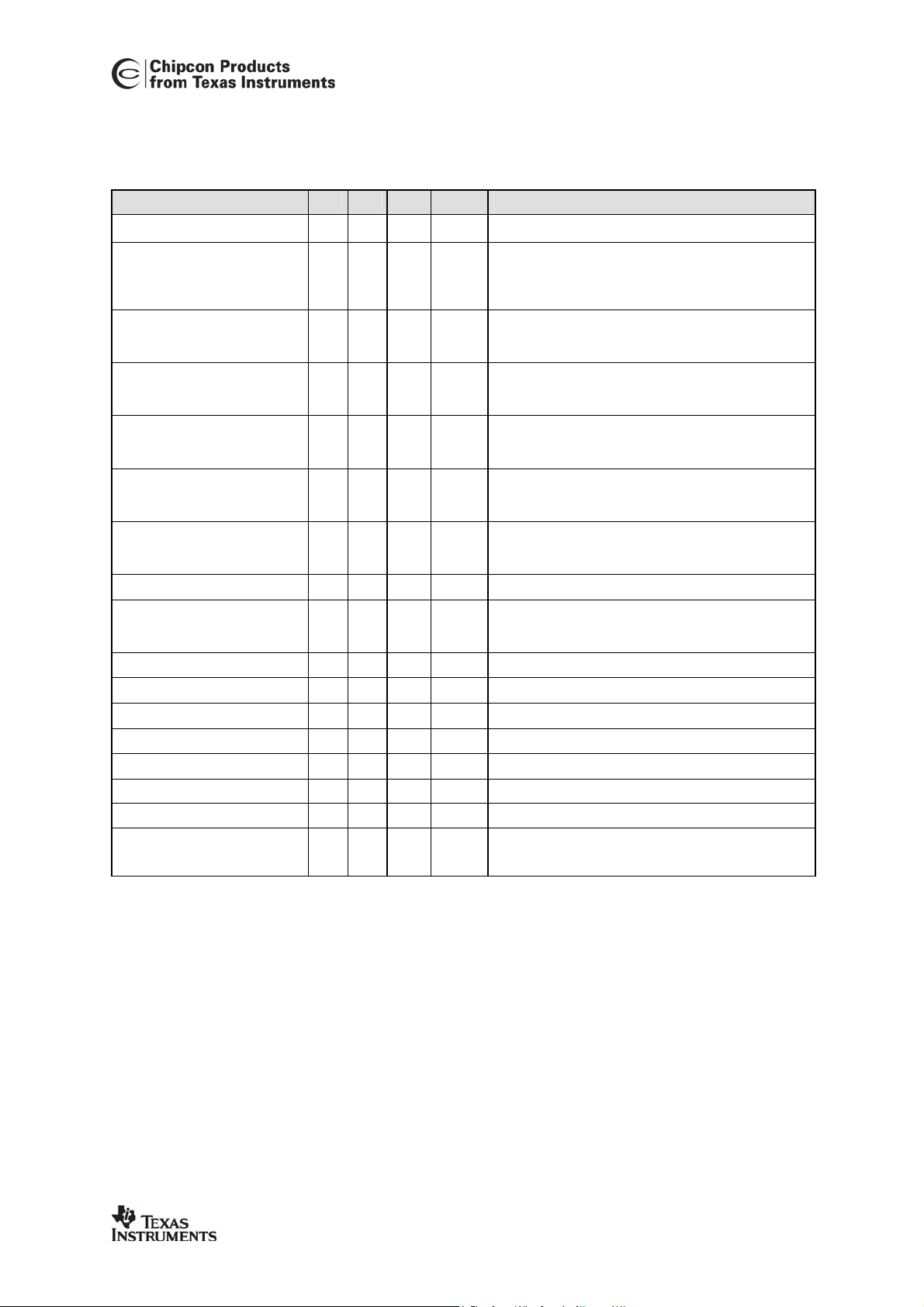

Parameter Min Typ Max Unit Condition

Current Consumption

MCU Active Mode, 16 MHz 4.3 mA

MCU Active Mode, 32 MHz 9.5 mA

MCU Active and RX Mode 26.7 mA

MCU Active and TX Mode, 0dBm 26.9 mA

Power mode 1 190

Power mode 2 0.5

Power mode 3 0.3

Peripheral Current

Consumption

Timer 1 150

Timer 2 230

Timer 3 50

Timer 4 50

Sleep Timer 0.2

ADC 1.2 mA When converting.

Flash write 3 mA Estimated value

Flash erase 3 mA Estimated value

Digital regulator on, High frequency (16 MHz) RCOSC

running.

No radio, crystals, or peripherals active. Code run with

Cache hit.

MCU running at full speed (32MHz), 32MHz XOSC

running. No radio or peripherals active. Code run with

Cache hit.

MCU running at full speed (32MHz), 32MHz XOSC

running, radio in RX mode, -50 dBm input power. No

peripherals active. Code run with Cache hit.

MCU running at full speed (32MHz), 32MHz XOSC

running, radio in TX mode, 0dBm output power. No

peripherals active. Code run with Cache hit.

Digital regulator on, High frequency RCOSC and crystal

oscillator off. 32.768 kHz XOSC, POR and ST active.

µA

RAM retention.

Digital regulator off, High frequency RCOSC and crystal

oscillator off. 32.768 kHz XOSC, POR and ST active.

µA

RAM retention.

No clocks. RAM retention. POR active.

µA

Adds to the figures above if the peripheral unit is

activated

Timer running, 32MHz XOSC used.

µA

Timer running, 32MHz XOSC used.

µA

Timer running, 32MHz XOSC used.

µA

Timer running, 32MHz XOSC used.

µA

Including 32 kHz RCOSC or 32.768 kHz XOSC

µA

Table 4: Electrical Specifications

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 11 of 233

This device is not yet released to market. Volume shipments possible under waiver.

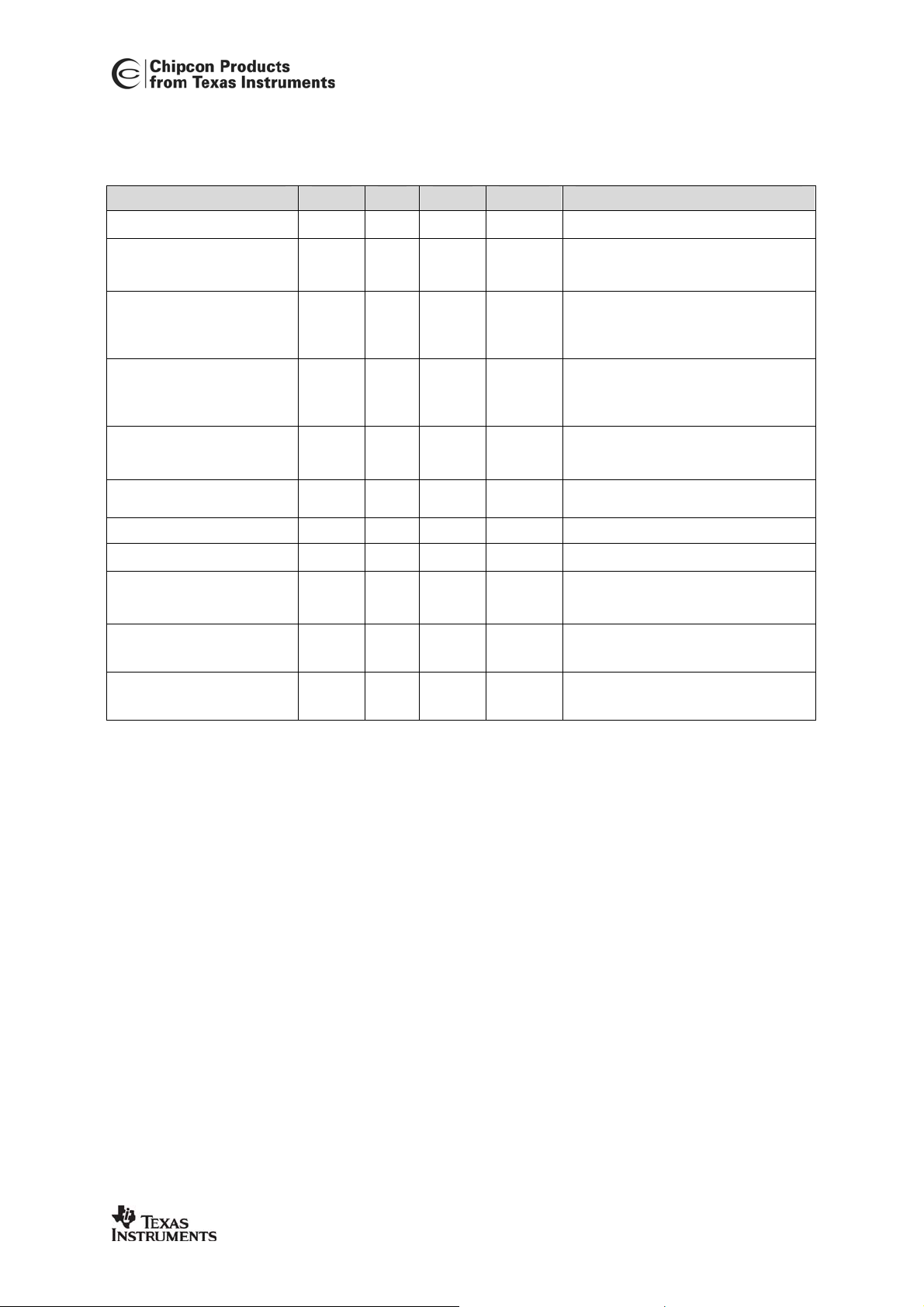

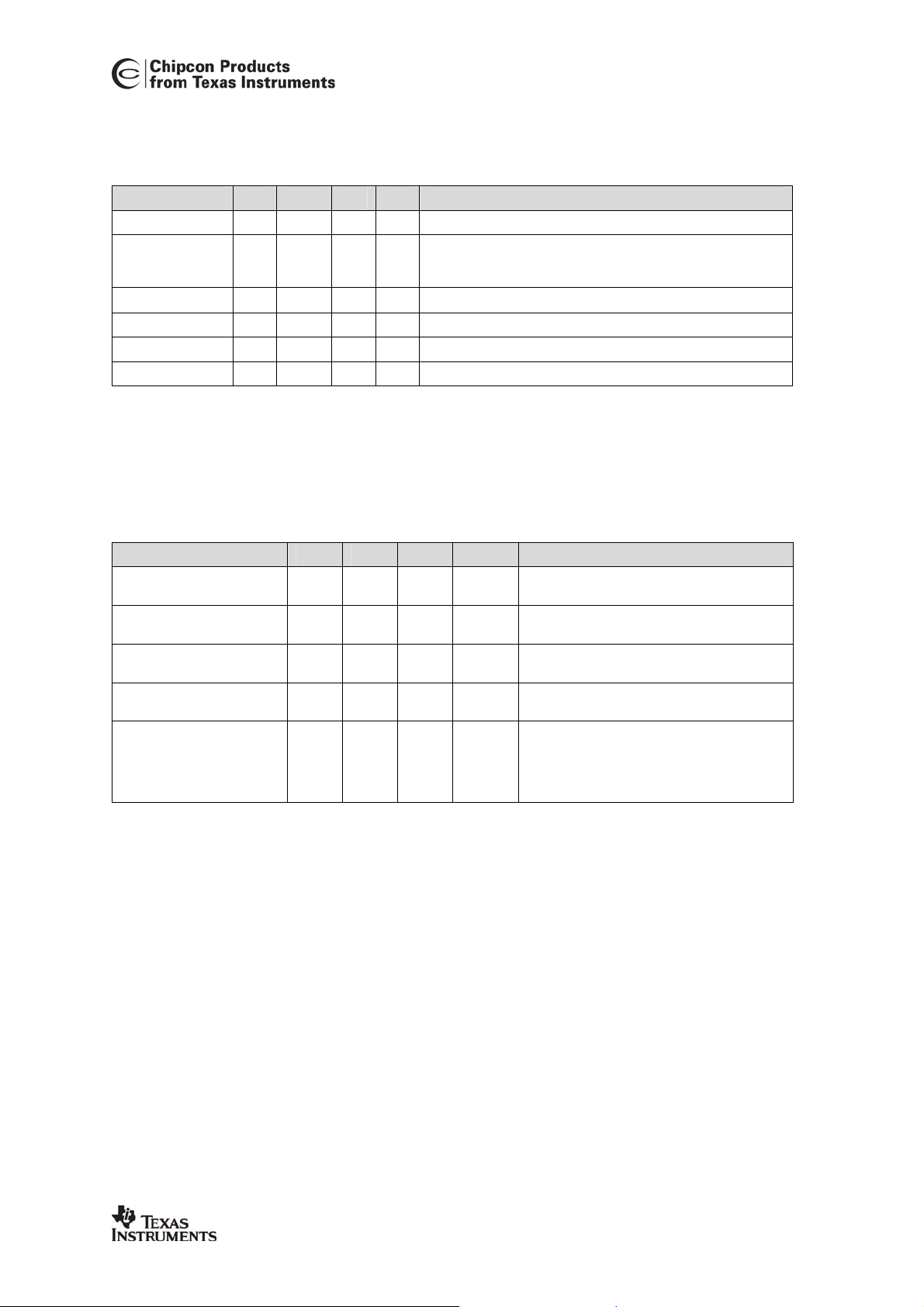

7.1 General Characteristics

CC2430

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Wake-Up and Timing

Power mode 1 Æ power

mode 0

Power mode 2 or 3 Æ power

mode 0

Active Æ TX or RX

32MHz XOSC initially OFF.

Voltage regulator initially OFF

Active Æ TX or RX

Voltage regulator initially OFF

Active Æ RX or TX 192

RX/TX turnaround 192

Radio part

RF Frequency Range 2400 2483.5 MHz Programmable in 1 MHz steps, 5 MHz

Radio bit rate 250 kbps As defined by [1]

4.1

89.2

525

320

µs

µs

µs

µs

µs

µs

Digital regulator on, High frequency

RCOSC and crystal oscillator off. Startup of High frequency RCOSC.

Digital regulator off, High frequency

RCOSC and crystal oscillator off. Startup of regulator and High frequency

RCOSC.

Time from enabling radio part in power

mode 0, until TX or RX starts. Includes

start-up of voltage regulator and crystal

oscillator in parallel. Crystal ESR=16Ω.

Time from enabling radio part in power

mode 0, until TX or RX starts. Includes

start-up of voltage regulator.

Radio part already enabled.

Time until RX or TX starts.

between channels for compliance with

[1]

Radio chip rate

2.0 MChip/s As defined by [1]

Table 5: General Characteristics

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 12 of 233

This device is not yet released to market. Volume shipments possible under waiver.

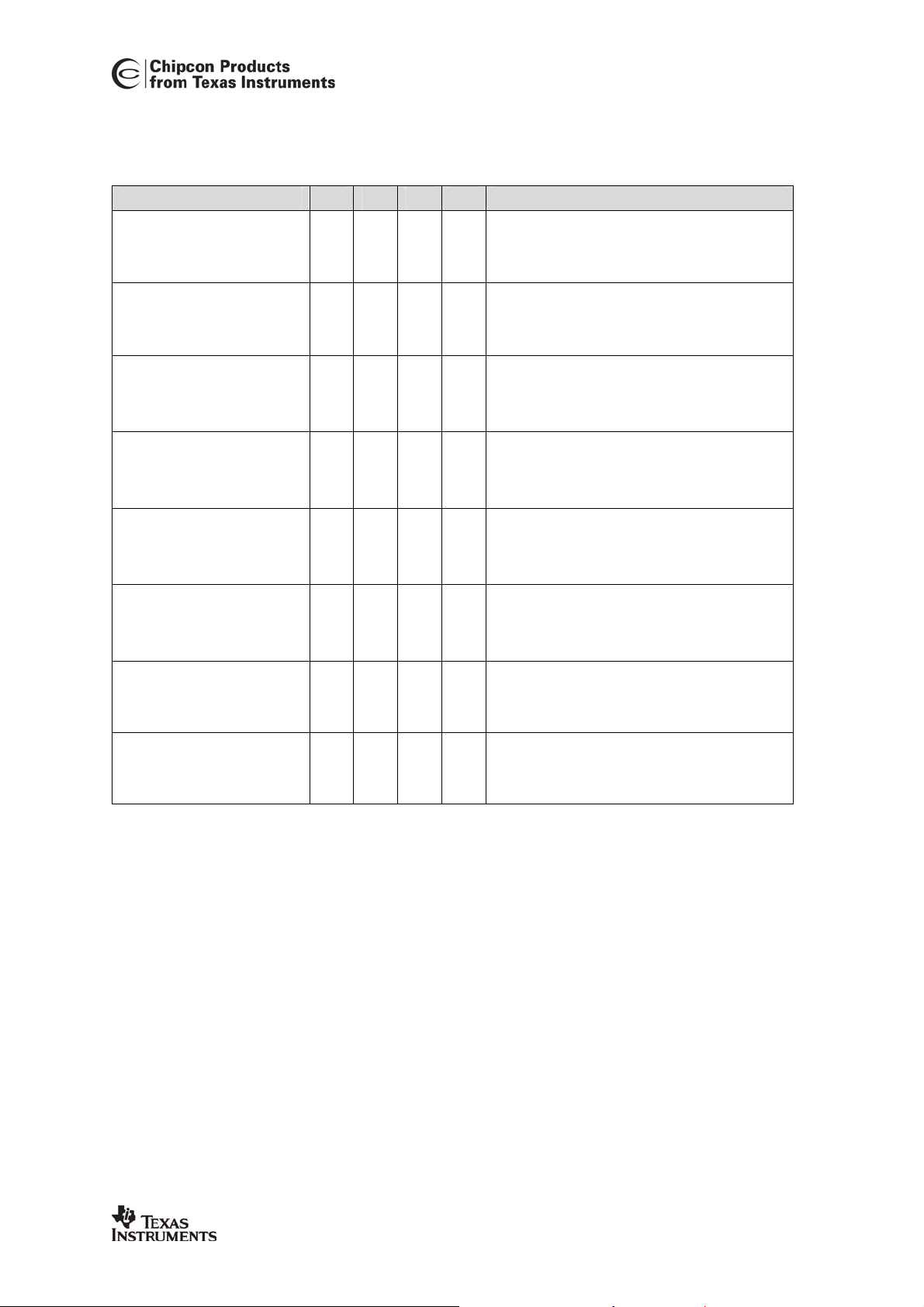

7.2 RF Receive Section

CC2430

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Receiver sensitivity

Saturation (maximum input

level)

Adjacent channel rejection

+ 5 MHz channel spacing

Adjacent channel rejection

- 5 MHz channel spacing

Alternate channel rejection

+ 10 MHz channel spacing

Alternate channel rejection

- 10 MHz channel spacing

Channel rejection

≥ + 15 MHz

≤ - 15 MHz

Co-channel rejection

-91 dBm PER = 1%, as specified by [1]

Measured in 50 Ω single endedly through a balun.

[1] requires –85 dBm

10 dBm PER = 1%, as specified by [1]

Measured in 50 Ω single endedly through a balun.

[1] requires –20 dBm

41

30

55

53

55

53

-6

Wanted signal -88dBm, adjacent modulated channel

at

dB

+5 MHz, PER = 1 %, as specified by [1].

[1] requires 0 dB

Wanted signal -88dBm, adjacent modulated channel

at

dB

-5 MHz, PER = 1 %, as specified by [1].

[1] requires 0 dB

Wanted signal -88dBm, adjacent modulated channel

at

dB

+10 MHz, PER = 1 %, as specified by [1]

[1] requires 30 dB

Wanted signal -88dBm, adjacent modulated channel

at

dB

-10 MHz, PER = 1 %, as specified by [1]

[1] requires 30 dB

Wanted signal @ -82 dBm. Undesired signal is an

802.15.4 modulated channel, stepped through all

dB

channels from 2405 to 2480 MHz. Signal level for

PER = 1%. Values are estimated.

dB

Wanted signal @ -82 dBm. Undesired signal is

802.15.4 modulated at the same frequency as the

dB

desired signal. Signal level for PER = 1%.

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 13 of 233

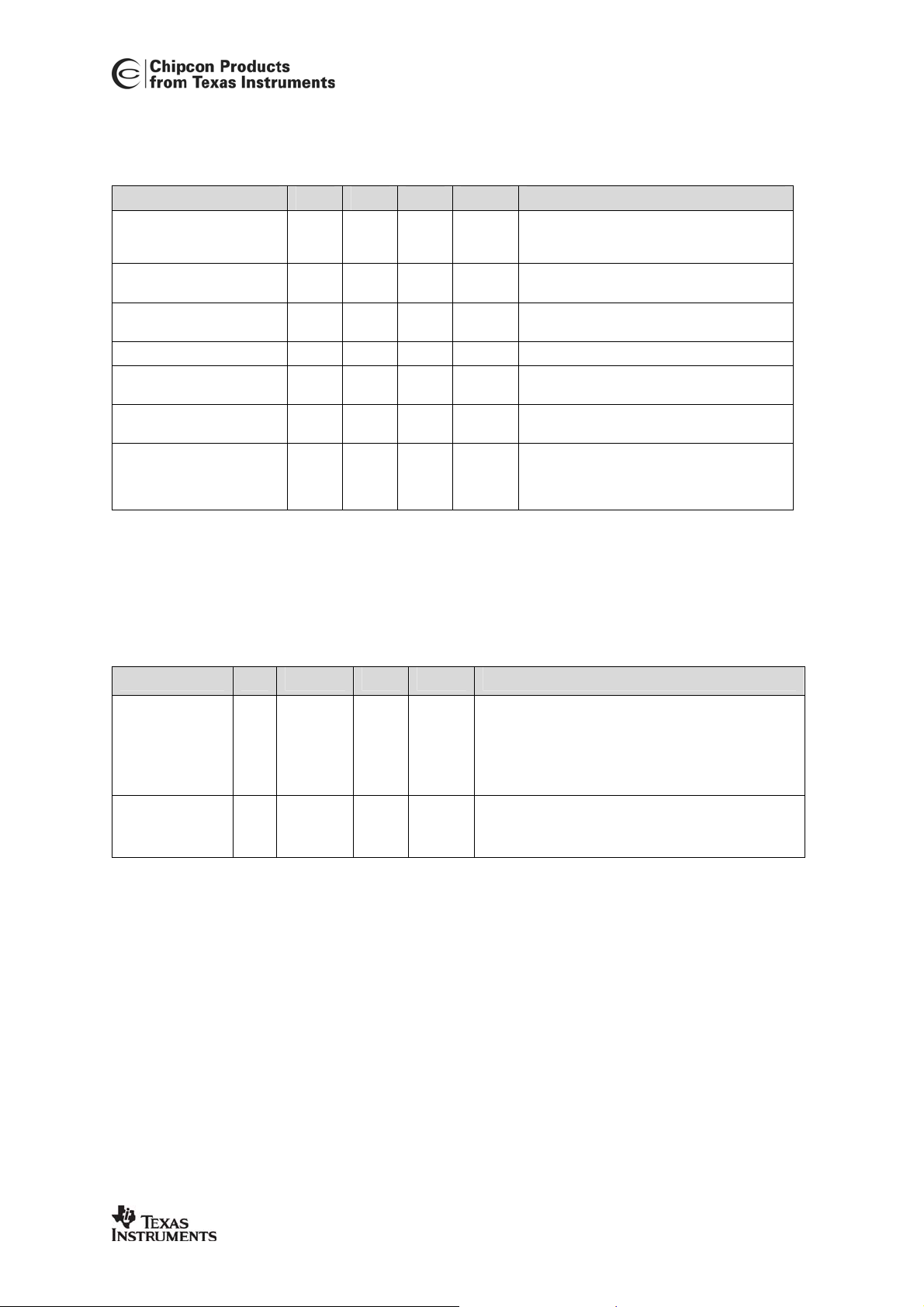

This device is not yet released to market. Volume shipments possible under waiver.

Parameter Min Typ Max Unit Condition/Note

Blocking / Desensitization

+ 5 MHz from band edge

+ 10 MHz from band edge

+ 20 MHz from band edge

+ 50 MHz from band edge

- 5 MHz from band edge

- 10 MHz from band edge

- 20 MHz from band edge

- 50 MHz from band edge

Spurious emission

30 – 1000 MHz

1 – 12.75 GHz

Frequency error tolerance ±140 ppm Difference between centre frequency of the received

Symbol rate error tolerance ±900 ppm Difference between incoming symbol rate and the

-42

-45

-26

-22

-31

-36

-24

-25

dBm

dBm

dBm

dBm

dBm

dBm

dBm

dBm

−64

dBm

−75

dBm

Wanted signal 3 dB above the sensitivity level, CW

jammer, PER = 1%. Measured according to EN 300

440 class 2.

Conducted measurement in a 50 Ω single ended

load. Complies with EN 300 328, EN 300 440 class

2, FCC CFR47, Part 15 and ARIB STD-T-66

RF signal and local oscillator frequency.

[1] requires minimum 80 ppm

internally generated symbol rate

[1] requires minimum 80 ppm

CC2430

Table 6: RF Receive Parameters

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 14 of 233

This device is not yet released to market. Volume shipments possible under waiver.

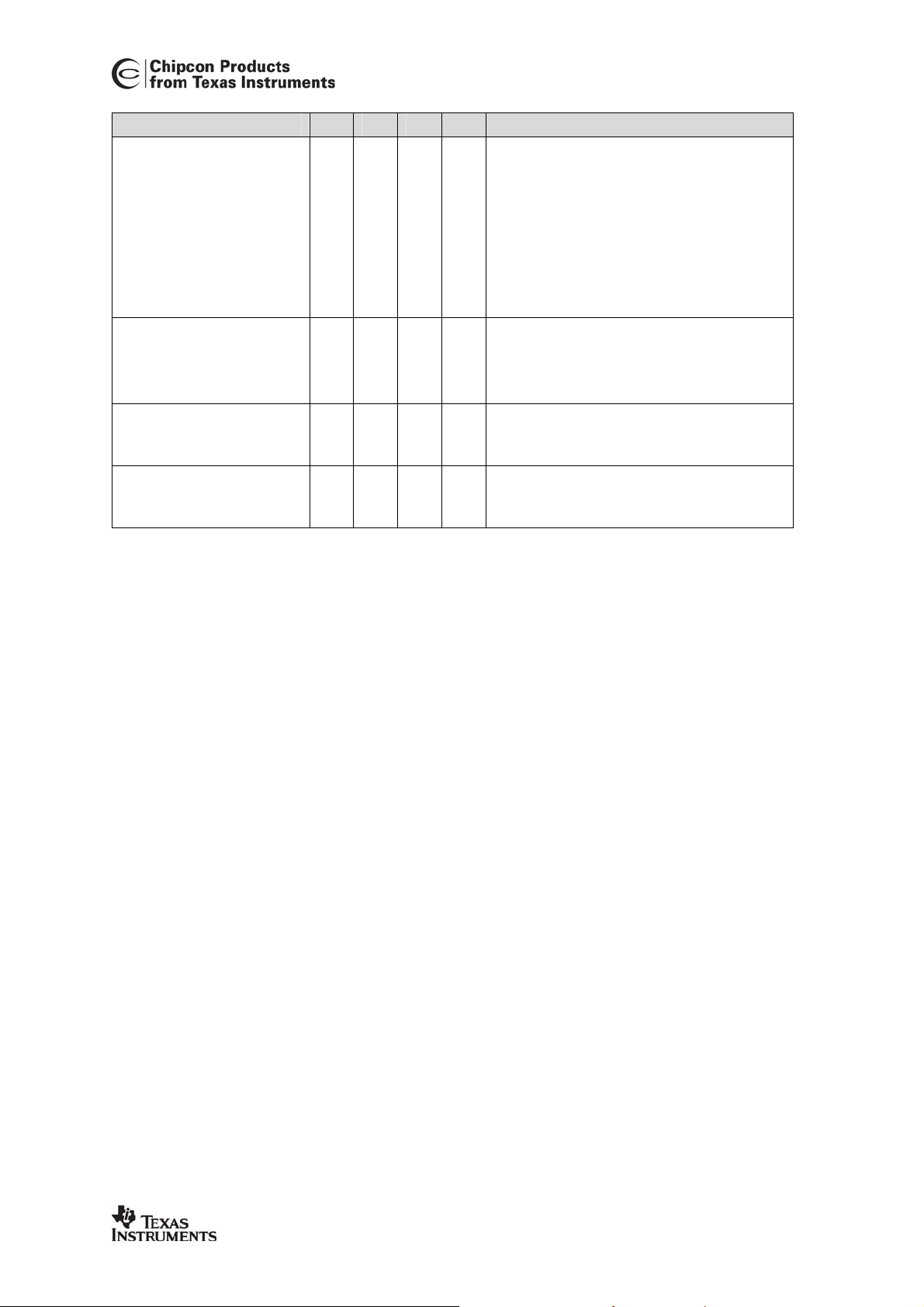

7.3 RF Transmit Section

CC2430

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Nominal output

power

Programmable

output power range

Harmonics

nd

harmonic

2

rd

harmonic

3

th

harmonic

4

th

harmonic

5

Spurious emission

30 - 1000 MHz

1– 12.75 GHz

1.8 – 1.9 GHz

5.15 – 5.3 GHz

Error Vector

Magnitude (EVM)

Optimum load

impedance

0 dBm

25.8 dB The output power is programmable in 16 steps from

-50.7

-55.8

-54.2

-53.4

-47

-43

-58

-56

11 % Measured as defined by [1]

115

+ j180

Delivered to a single ended 50 Ω load through a balun and

output power control set to 0x5F (TXCTRLL).

[1] requires minimum –3 dBm

approximately –25.2 to 0.6 dBm.

dBm

Measurement conducted with 100 kHz resolution bandwidth on

spectrum analyzer and output power control set to 0x5F

dBm

(TXCTRLL). Output Delivered to a single ended 50 Ω load

through a balun.

dBm

dBm

Maximum output power.

dBm

The peak conducted spurious emission is -47dBm@192MHz

which isin a EN300440 restricted band limited to -54dBm. All

dBm

radiated spurious emissions are within the limits of

ETSI/FCC/ARIB.

dBm

Texas Instruments

dBm

EN 300 328, EN 300 440, FCC CFR47 Part 15 and ARIB STDT-66

[1] requires max. 35 %

Ω

Differential impedance as seen from the RF-port (

RF_N

) towards the antenna.

CC2430

EM reference design complies with

RF_P

and

Table 7: RF Transmit Parameters

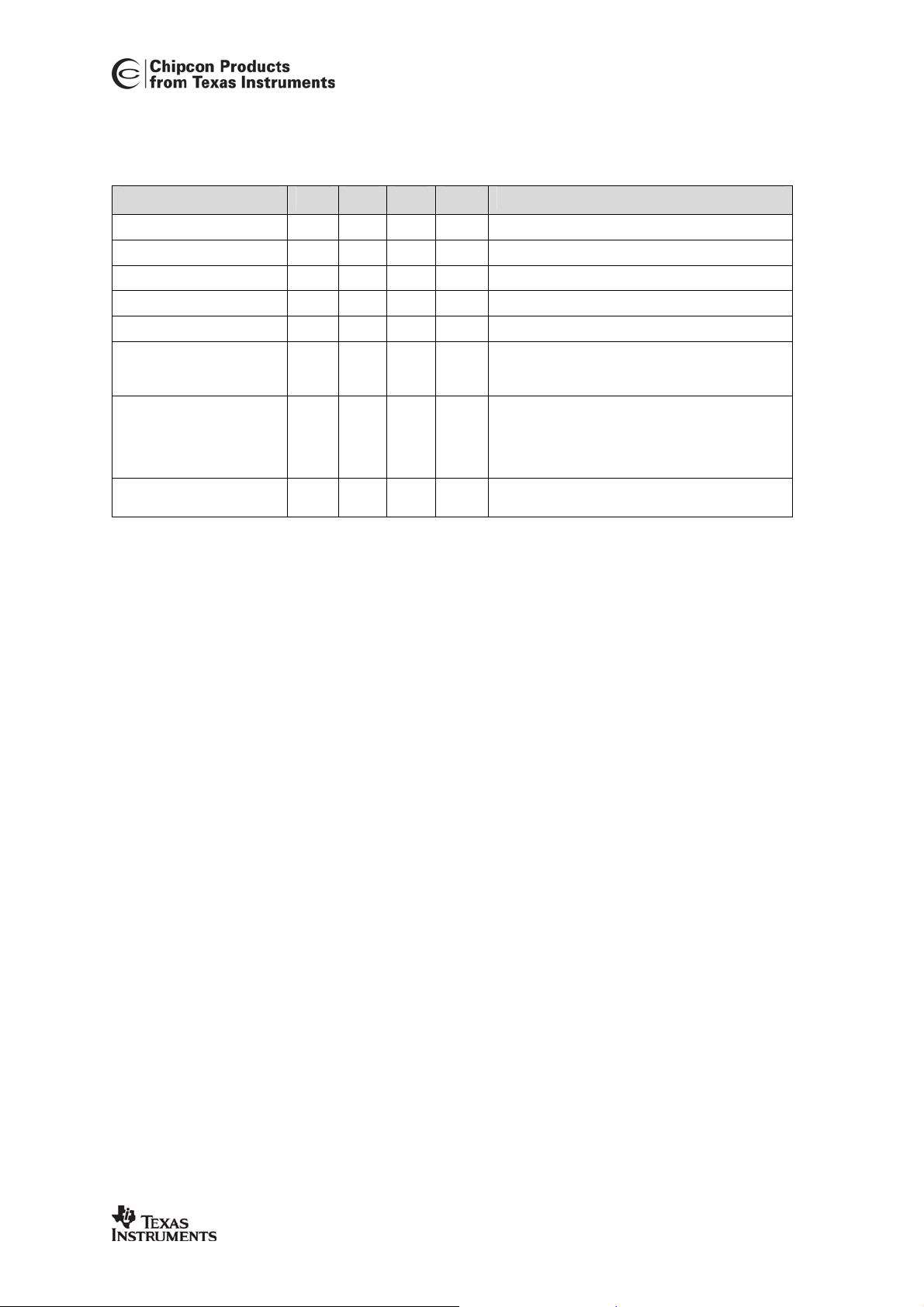

7.4 32 MHz Crystal Oscillator

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Crystal frequency 32 MHz

Crystal frequency

accuracy

requirement

ESR 6 16 60

C0 1 1.9 7 pF

CL 10 13 16 pF Load capacitance is optionally tunable through software

Start-up time 212 µs

- 40

40 ppm Including aging and temperature dependency, as specified by [1]

Accuracy requirements can be relaxed by optional built-in tuning of

load capacitance through software

Ω

1

Table 8: 32 MHz Crystal Oscillator Parameters

1

Only for devices with Chip Version register, CHVER.VERSION equal to 0x02 or greater

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 15 of 233

This device is not yet released to market. Volume shipments possible under waiver.

7.5 32.768 kHz Crystal Oscillator

CC2430

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Crystal frequency 32.768 kHz

Crystal frequency

accuracy

requirement

ESR 40 130

C0 0.9 2.0 pF

CL 12 16 pF

Start-up time 450 ms Value is estimated.

–40 40 ppm Including aging and temperature dependency, as specified by [1]

kΩ

Table 9: 32.768 kHz Crystal Oscillator Parameters

7.6 32 kHz RC Oscillator

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Calibrated frequency 32.753 kHz The calibrated 32 kHz RC Oscillator frequency

Frequency accuracy after

calibration

Temperature coefficient +0.4

Supply voltage coefficient +3 % / V Frequency drift when supply voltage changes

Initial calibration time 1.7 ms

±0.2 % Value is estimated.

% / °C

is the 32 MHz XTAL frequency divided by 977

Frequency drift when temperature changes

after calibration. Value is estimated.

after calibration. Value is estimated.

When the 32 kHz RC Oscillator is enabled,

calibration is continuously done in the

background as long as the 32 MHz crystal

oscillator is running and

SLEEP.OSC32K_CALDIS bit is cleared.

Table 10: 32 kHz RC Oscillator parameters

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 16 of 233

This device is not yet released to market. Volume shipments possible under waiver.

7.7 High Frequency RC Oscillator

CC2430

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Frequency 16 MHz The calibrated High Frequency RC Oscillator

Uncalibrated frequency

accuracy

Calibrated frequency

accuracy

Start-up time 10 µs

Temperature coefficient -325

Supply voltage coefficient 28

Initial calibration time 50 µs When the High Frequency RC Oscillator is

±18

±0.6 ±1

%

%

ppm / °C

ppm / mV

frequency is the 32 MHz XTAL frequency

multiplied by 1/2

CC2430

Measured on Texas Instruments

reference design.

Frequency drift when temperature changes

after calibration

Frequency drift when supply voltage changes

after calibration

enabled, calibration is continuously done in the

background as long as the crystal oscillator is

running.

EM

Table 11: High Frequency RC Oscillator parameters

7.8 Frequency Synthesizer Characteristics

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Phase noise

−116

−117

−118

PLL lock time

192

dBc/Hz

dBc/Hz

dBc/Hz

µs

Unmodulated carrier

At ±1.5 MHz offset from carrier

At ±3 MHz offset from carrier

At ±5 MHz offset from carrier

The startup time when the crystal oscillator is running

and RX / TX turnaround time

Table 12: Frequency Synthesizer Parameters

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 17 of 233

This device is not yet released to market. Volume shipments possible under waiver.

7.9 Analog Temperature Sensor

CC2430

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C and VDD=3.0V

unless stated otherwise.

Parameter Min Typ Max Unit Condition/Note

Output voltage at –40°C

Output voltage at 0°C

Output voltage at +40°C

Output voltage at +80°C

Temperature coefficient 2.45

Absolute error in calculated

temperature

Error in calculated

temperature, calibrated

Current consumption

increase when enabled

0.648 V Values are estimated

0.743 V Values are estimated

0.840 V Values are estimated

0.939 V Values are estimated

mV/°C Fitted from –20°C to +80°C on estimated values.

–8

-2 0 2

280 µA

°C From –20°C to +80°C when assuming best fit for

absolute accuracy on estimated values: 0.743V at

0°C and 2.45mV / °C.

°C From –20°C to +80°C when using 2.45mV / °C,

after 1-point calibration at room temperature.

Values are estimated. Indicated min/max with 1point calibration is based on simulated values for

typical process parameters

Table 13: Analog Temperature Sensor Parameters

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 18 of 233

7.10 ADC

This device is not yet released to market. Volume shipments possible under waiver.

CC2430

Measured on Texas Instruments

CC2430

EM reference design with TA=25°C, VDD=3.0V.

Preliminary characterized parameters.

Parameter Min Typ Max Unit Condition/Note

Input voltage 0 AVDD V AVDD is voltage on AVDD_SOC pin

External reference voltage 0 AVDD V AVDD is voltage on AVDD_SOC pin

External reference voltage

differential

Input resistance, ADC singleended input

Input resistance, ADC

differential input

Input resistance, single-ended

reference

Input resistance, differential

reference

Effective number of bits 5.5 bits 8-bits setting.

(ENOB)2 7.3 10-bits setting.

9.0 12-bits setting.

10.5 14-bits setting.

Effective number of bits (ENOB)

Differential input

Offset1 TBD LSB

Conversion time 20

36

68

132

Differential nonlinearity (DNL)3 ±0.14 1.0 LSB 8-bits setting.

Integral nonlinearity (INL) 2 ±0.5 3.4 LSB 8-bits setting.

SINAD2 34 dB 8-bits setting.

(sine input signal 46 dB 10-bits setting.

frequency 1 Hz and 1 kHz) 56 dB 12-bits setting.

65 dB 14-bits setting.

2

1

1

0 AVDD V AVDD is voltage on AVDD_SOC pin

167 kΩ AIN0 to AIN7 selected as ADC input

TBD

49 kΩ AIN7 selected as external reference input

TBD

TBD

8-bits setting.

µs

10-bits setting.

µs

12-bits setting.

µs

14-bits setting.

µs

Table 14: ADC Characteristics

2

Not characterized for this data sheet revision.

3

Single-ended input signal and AVDD used as reference. Sine input, tested at frequencies 1 Hz and 1 kHz

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 19 of 233

This device is not yet released to market. Volume shipments possible under waiver.

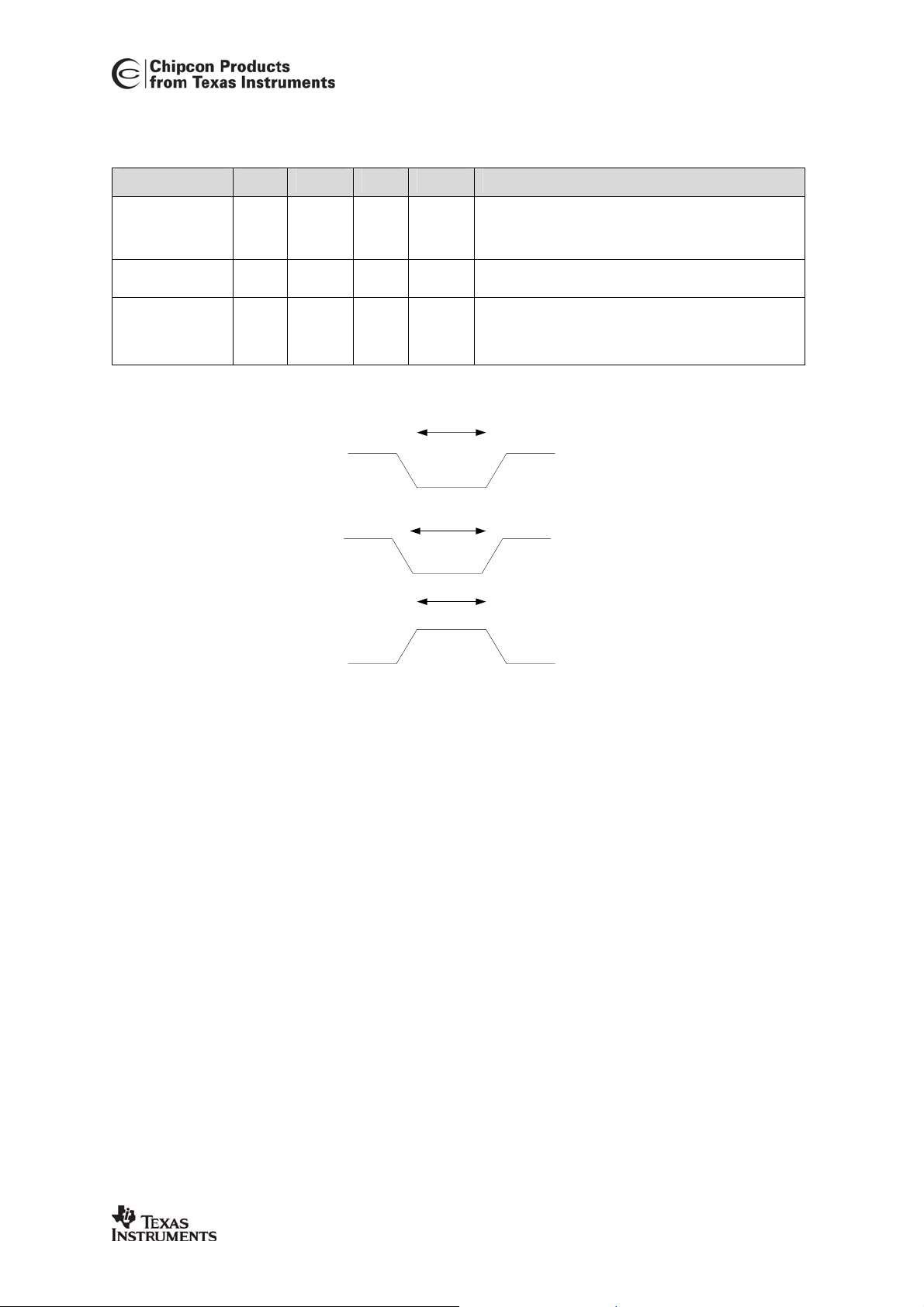

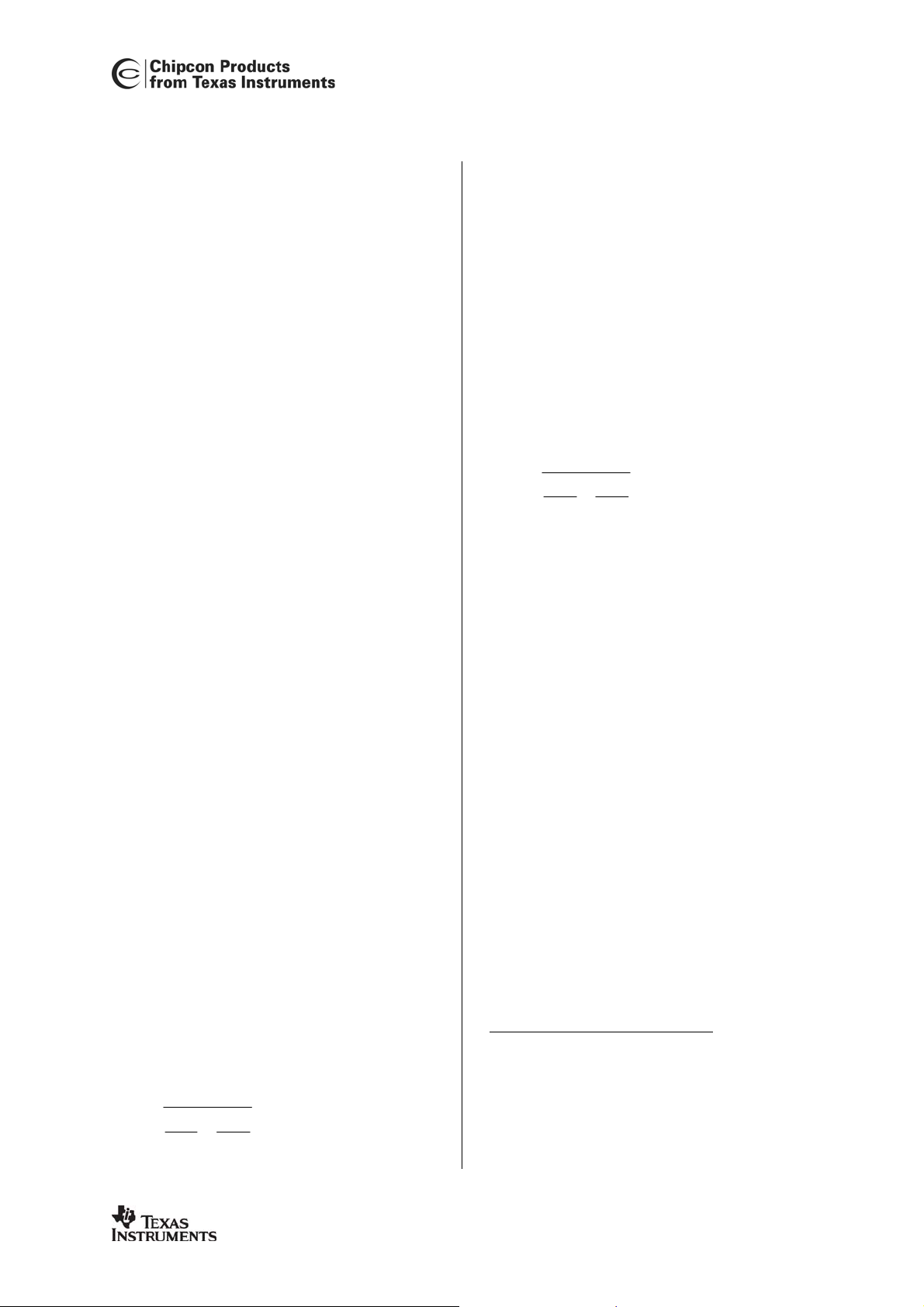

7.11 Control AC Characteristics

= -40°C to 85°C, VDD=3.0V if nothing else stated.

T

A

Parameter Min Typ Max Unit Condition/Note

CC2430

System clock,

f

SYSCLK

= 1/ f

t

SYSCLK

RESET_N low

width

Interrupt pulse

width

SYSCLK

16 32 MHz System clock is when 32 MHz crystal oscillator is used.

2.5 ns See item 1, Figure 1. This is the shortest pulse that is

t

ns See item 2, Figure 1.This is the shortest pulse that is

SYSCLK

System clock is 16 MHz when high frequency RC

oscillator is used.

guaranteed to be recognized as a reset pin request.

guaranteed to be recognized as an interrupt request. In

PM2/3 the internal synchronizers are bypassed so this

requirement does not apply in PM2/3.

Table 15: Control Inputs AC Characteristics

1

RESET_N

Px.n

Px.n

2

2

Figure 1: Control Inputs AC Characteristics

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 20 of 233

This device is not yet released to market. Volume shipments possible under waiver.

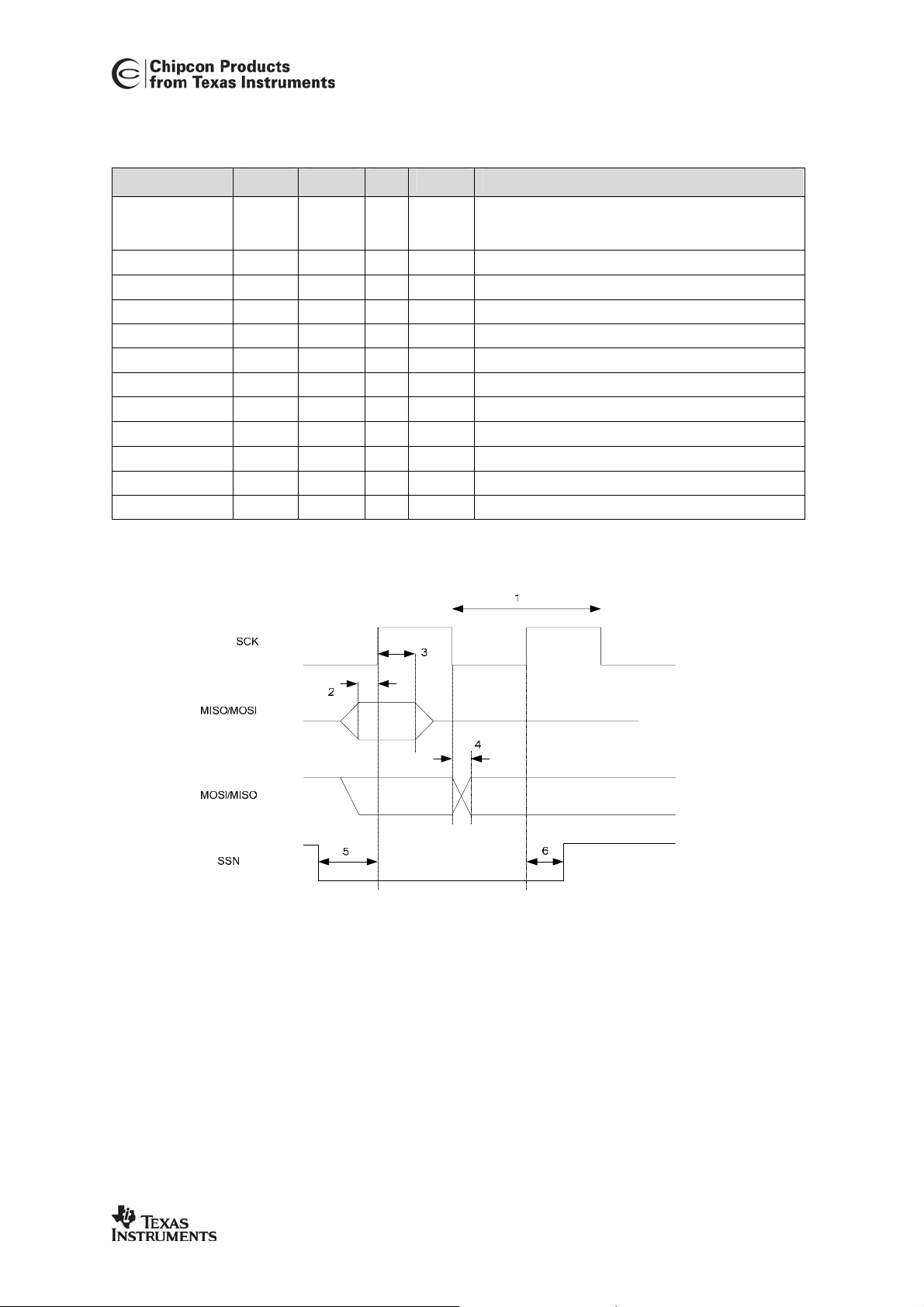

7.12 SPI AC Characteristics

= -40°C to 85°C, VDD=3.0V if nothing else stated.

T

A

Parameter Min Typ Max Unit Condition/Note

CC2430

SCK period See

SCK duty cycle 50%

SSN low to SCK 2*t

SCK to SSN high 30 ns See item 6 Figure 2

MISO setup 10 ns Master. See item 2 Figure 2

MISO hold 10 ns Master. See item 3 Figure 2

SCK to MOSI 25 ns Master. See item 4 Figure 2, load = 10 pF

SCK period 100 ns Slave. See item 1 Figure 2

SCK duty cycle 50%

MOSI setup 10 ns Slave. See item 2 Figure 2

MOSI hold 10 ns Slave. See item 3 Figure 2

SCK to MISO 25 ns Slave. See item 4 Figure 2, load = 10 pF

SYSCLK

section

13.13.3

See item 5 Figure 2

ns Master. See item 1 Figure 2

Master.

Slave.

Table 16: SPI AC Characteristics

Figure 2: SPI AC Characteristics

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 21 of 233

This device is not yet released to market. Volume shipments possible under waiver.

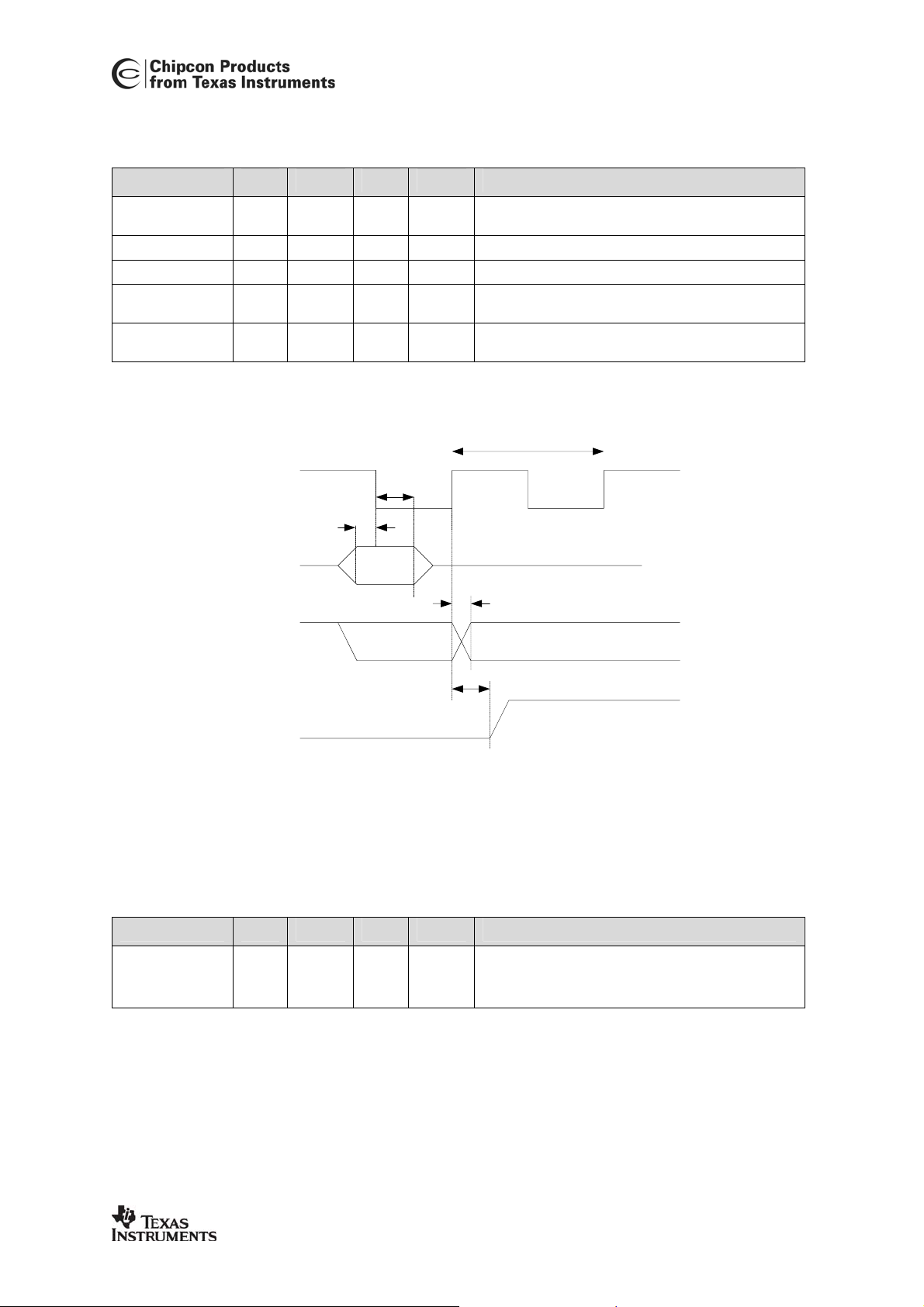

7.13 Debug Interface AC Characteristics

= -40°C to 85°C, VDD=3.0V if nothing else stated.

T

A

Parameter Min Typ Max Unit Condition/Note

CC2430

Debug clock

period

Debug data setup 5 ns See item 2 Figure 3

Debug data hold 5 ns See item 3 Figure 3

Clock to data

delay

RESET_N inactive

after P2_2 rising

128 ns See item 1 Figure 3

10 ns See item 4 Figure 3, load = 10 pF

10 ns See item 5 Figure 3

Table 17: Debug Interface AC Characteristics

1

DEBUG CLK

P2_2

2

DEBUG DATA

P2_1

DEBUG DATA

P2_1

3

4

RESET_N

5

Figure 3: Debug Interface AC Characteristics

7.14 Port Outputs AC Characteristics

T

= -40°C to 85°C, VDD=3.0V if nothing else stated.

A

Parameter Min Typ Max Unit Condition/Note

P0, P1, P2 Port

output pins, rise

and fall time

10 ns Load = 10 pF

Timing is with respect to 10% VDD and 90% VDD levels.

Value is estimated

Table 18: Port Outputs AC Characteristics

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 22 of 233

This device is not yet released to market. Volume shipments possible under waiver.

7.15 Timer Inputs AC Characteristics

= -40°C to 85°C, VDD=3.0V if nothing else stated.

T

A

Parameter Min Typ Max Unit Condition/Note

CC2430

Input capture

pulse width

t

ns Synchronizers determine the shortest input pulse that

SYSCLK

can be recognized. The synchronizers operate at the

current system clock rate (16 or 32 MHz)

Table 19: Timer Inputs AC Characteristics

7.16 DC Characteristics

The DC Characteristics of

=25°C, VDD=3.0V if nothing else stated.

T

A

Digital Inputs/Outputs Min Typ Max Unit Condition

Logic "0" input voltage 0 0.7 0.9 V

Logic "1" input voltage VDD-0.7 VDD VDD V

Logic "0" output voltage 0 0 0.25 V For up to 4mA output current on all pins except

Logic "1" output voltage VDD-0.25 VDD VDD V For up to 4mA output current on all pins except

Logic "0" input current NA –1 –1

Logic "1" input current NA 1 1

I/O pin pull-up and pull-down

resistor

CC2430

are listed in Table 20 below.

17 20 23 kΩ

P1_0 and P1_1 which are up to 20 mA

P1_0 and P1_1 which are up to 20 mA

Input equals 0V

µA

Input equals VDD

µA

Table 20: DC Characteristics

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 23 of 233

This device is not yet released to market. Volume shipments possible under waiver.

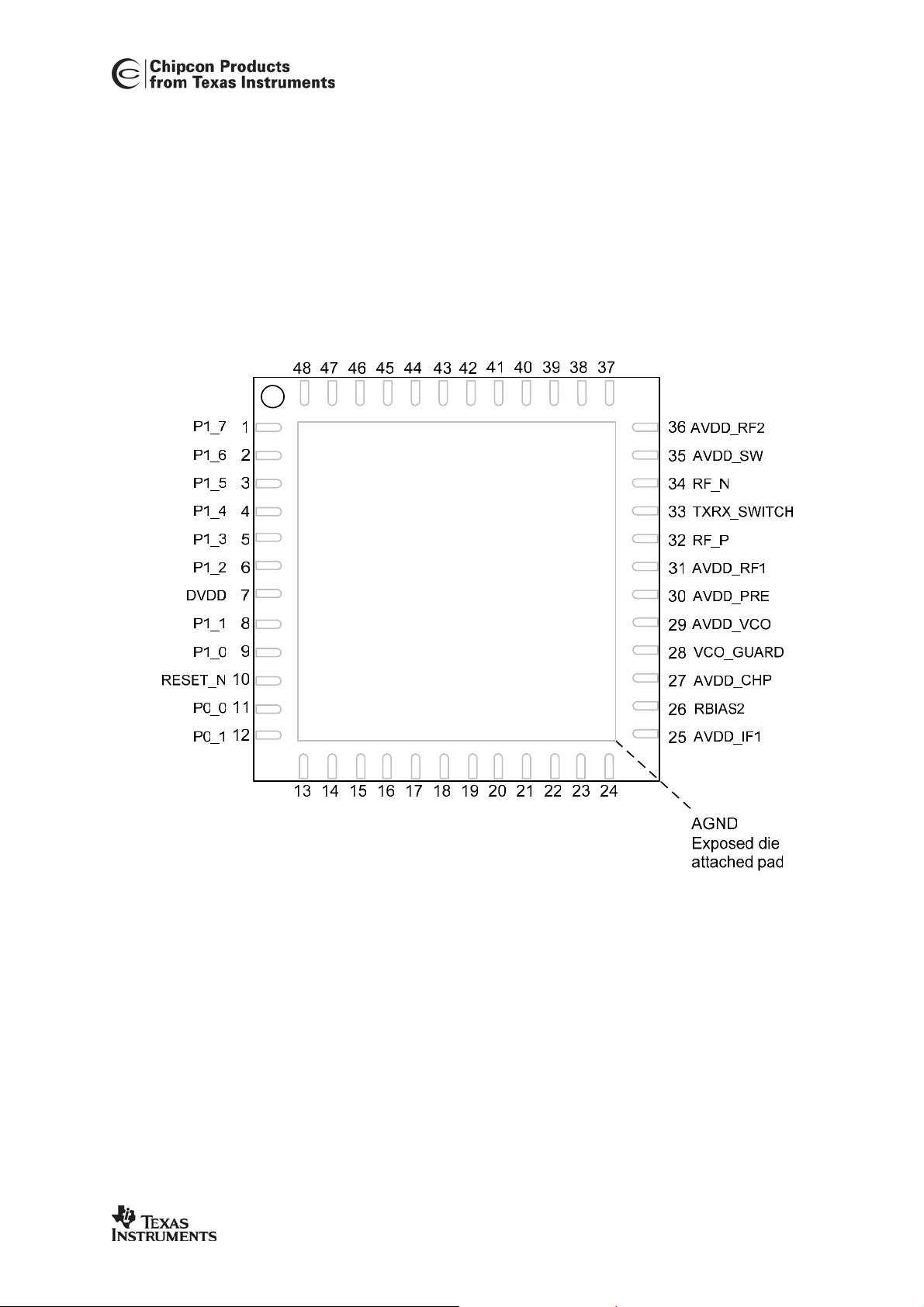

8 Pin and I/O Port Configuration

The

CC2430

configuration of digital I/O ports.

pinout is shown in Figure 4 and Table 21. See section 13.1 for details on the

CC2430

P0_2

P2_0

DVDD

P0_3

P0_4

P2_1

P0_5

P2_2

P2_3/XOSC_Q1

P0_6

P2_4/XOSC_Q2

P0_7

AVDD_DREG

DCOUPL

XOSC_Q2

AVDD_SOC

AVDD_DGUARD

DVDD_ADC

AVDD_ADC

AVDD_IF2

XOSC_Q1

RBIAS1

AVDD_RREG

RREG_OUT

Figure 4: Pinout top view

Note: The exposed die attach pad must be connected to a solid ground plane as this is the

ground connection for the chip.

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 24 of 233

This device is not yet released to market. Volume shipments possible under waiver.

Pin Pin name Pin type Description

- GND Ground The exposed die attach pad must be connected to a solid ground plane

1 P1_7 Digital I/O Port 1.7

2 P1_6 Digital I/O Port 1.6

3 P1_5 Digital I/O Port 1.5

4 P1_4 Digital I/O Port 1.4

5 P1_3 Digital I/O Port 1.3

6 P1_2 Digital I/O Port 1.2

7 DVDD Power (Digital) 2.0V-3.6V digital power supply for digital I/O

8 P1_1 Digital I/O Port 1.1 – 20 mA drive capability

9 P1_0 Digital I/O Port 1.0 – 20 mA drive capability

10 RESET_N Digital input Reset, active low

11 P0_0 Digital I/O Port 0.0

12 P0_1 Digital I/O Port 0.1

13 P0_2 Digital I/O Port 0.2

14 P0_3 Digital I/O Port 0.3

15 P0_4 Digital I/O Port 0.4

16 P0_5 Digital I/O Port 0.5

17 P0_6 Digital I/O Port 0.6

18 P0_7 Digital I/O Port 0.7

19 XOSC_Q2 Analog I/O 32 MHz crystal oscillator pin 2

20 AVDD_SOC Power (Analog) 2.0V-3.6V analog power supply connection

21 XOSC_Q1 Analog I/O 32 MHz crystal oscillator pin 1, or external clock input

22 RBIAS1 Analog I/O External precision bias resistor for reference current

23 AVDD_RREG Power (Analog) 2.0V-3.6V analog power supply connection

24 RREG_OUT Power output 1.8V Voltage regulator power supply output. Only intended for supplying the analog

25 AVDD_IF1 Power (Analog) 1.8V Power supply for the receiver band pass filter, analog test module, global bias

26 RBIAS2 Analog output

27 AVDD_CHP Power (Analog) 1.8V Power supply for phase detector, charge pump and first part of loop filter

28 VCO_GUARD Power (Analog) Connection of guard ring for VCO (to AVDD) shielding

29 AVDD_VCO Power (Analog) 1.8V Power supply for VCO and last part of PLL loop filter

30 AVDD_PRE Power (Analog) 1.8V Power supply for Prescaler, Div-2 and LO buffers

31 AVDD_RF1 Power (Analog) 1.8V Power supply for LNA, front-end bias and PA

32 RF_P RF I/O Positive RF input signal to LNA during RX. Positive RF output signal from PA during

33 TXRX_SWITCH Power (Analog) Regulated supply voltage for PA

34 RF_N RF I/O Negative RF input signal to LNA during RX

35 AVDD_SW Power (Analog) 1.8V Power supply for LNA / PA switch

36 AVDD_RF2 Power (Analog) 1.8V Power supply for receive and transmit mixers

37 AVDD_IF2 Power (Analog) 1.8V Power supply for transmit low pass filter and last stages of VGA

38 AVDD_ADC Power (Analog) 1.8V Power supply for analog parts of ADCs and DACs

39 DVDD_ADC Power (Digital) 1.8V Power supply for digital parts of ADCs

40 AVDD_DGUARD Power (Digital) Power supply connection for digital noise isolation

41 AVDD_DREG Power (Digital) 2.0V-3.6V digital power supply for digital core voltage regulator

42 DCOUPL Power (Digital) 1.8V digital power supply decoupling. Do not use for supplying external circuits.

43 P2_4/XOSC_Q2 Digital I/O Port 2.4/32.768 kHz XOSC

44 P2_3/XOSC_Q1 Digital I/O Port 2.3/32.768 kHz XOSC

45 P2_2 Digital I/O Port 2.2

46 P2_1 Digital I/O Port 2.1

47 DVDD Power (Digital) 2.0V-3.6V digital power supply for digital I/O

48 P2_0 Digital I/O Port 2.0

1.8V part (power supply for pins 25, 27-31, 35-40).

and first part of the VGA

External precision resistor, 43 kΩ, ±1 %

TX

Negative RF output signal from PA during TX

CC2430

Table 21: Pinout overview

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 25 of 233

This device is not yet released to market. Volume shipments possible under waiver.

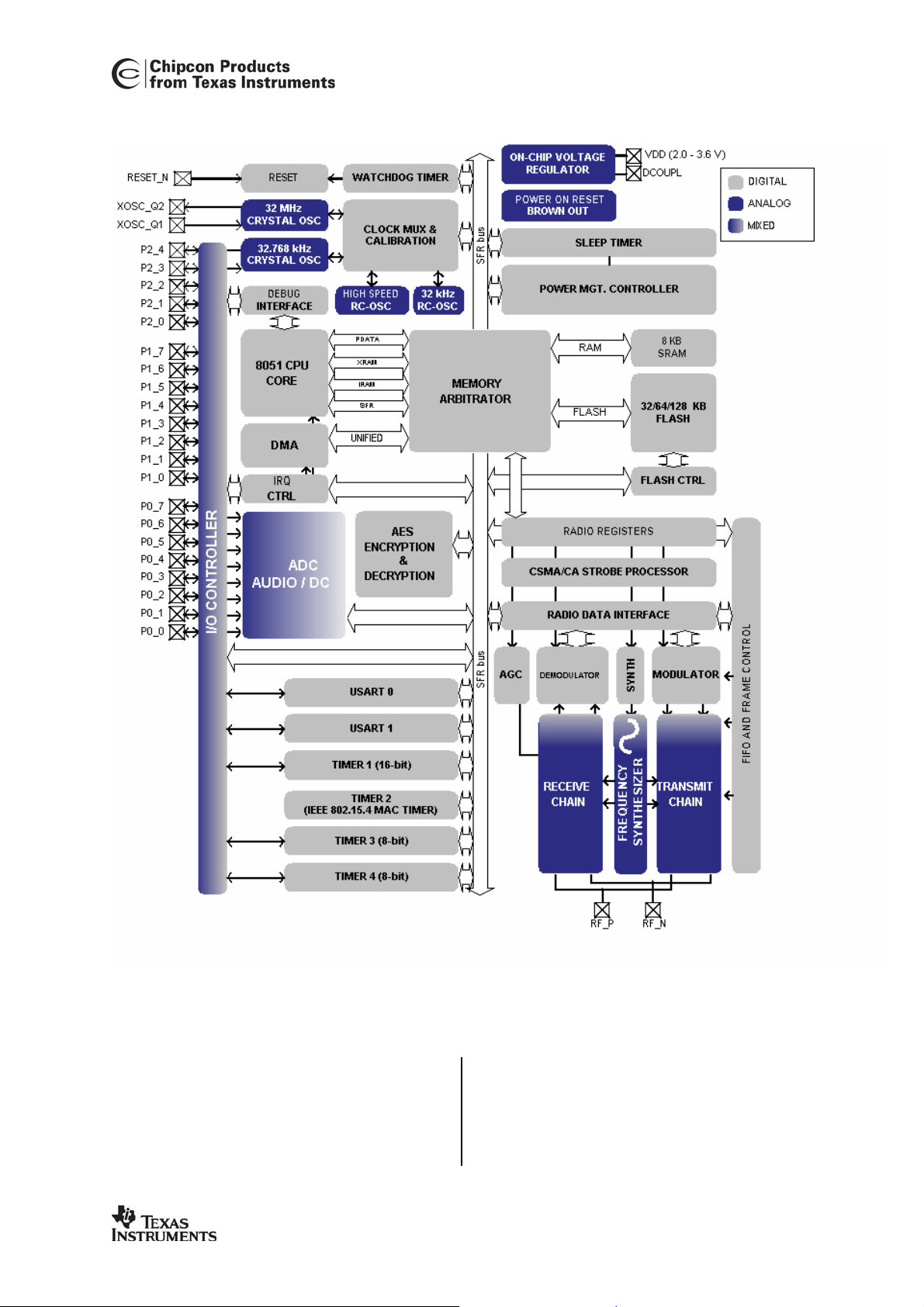

9 Circuit Description

CC2430

Figure 5:

A block diagram of

5. The modules can be roughly divided into

one of three categories: CPU-related modules,

radio-related modules and modules related to

power, test and clock distribution. In the

following subsections, a short description of

CC2430

is shown in Figure

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 26 of 233

CC2430

Block Diagram

each module that appears in Figure 5 is given.

9.1 CPU and Peripherals

The 8051 CPU core is a single-cycle 8051-

compatible core. It has three different memory

This device is not yet released to market. Volume shipments possible under waiver.

CC2430

access buses (SFR, DATA and

CODE/XDATA), a debug interface and an 18input extended interrupt unit. See section 12

for details on the CPU.

The memory crossbar/arbitrator is at the

heart of the system as it connects the CPU

and DMA controller with the physical

memories and all peripherals through the SFR

bus. The memory arbitrator has four memory

access points, access at which can map to

one of three physical memories: an 8 KB

SRAM, flash memory or RF and SFR

registers. The memory arbitrator is responsible

for performing arbitration and sequencing

between simultaneous memory accesses to

the same physical memory.

The SFR bus is drawn conceptually in the

block diagram as a common bus that connects

all hardware peripherals to the memory

arbitrator. The SFR bus in the block diagram

also provides access to the radio registers in

the radio register bank even though these are

indeed mapped into XDATA memory space.

The 8 KB SRAM maps to the DATA memory

space and to parts of the XDATA memory

spaces. 4 KB of the 8 KB SRAM is an ultralow-power SRAM that retains its contents even

when the digital part is powered off (power

modes 2 and 3). The rest of the SRAM loses

its contents when the digital part is powered

off.

The 32/64/128 KB flash block provides in-

circuit programmable non-volatile program

memory for the device and maps into the

CODE and XDATA memory spaces. Table 22

shows the available devices in the

family. The available devices differ only in

flash memory size. Writing to the flash block is

performed through a flash controller that

allows page-wise (2048 byte) erasure and 4

byte-wise programming. See section 13.14 for

details on the flash controller.

A versatile five-channel DMA controller is

available in the system and accesses memory

using a unified memory space (XDATA) and

thus has access to all physical memories.

Each channel is configured (trigger, priority,

transfer mode, addressing mode, source and

destination pointers, and transfer count) with

DMA descriptors anywhere in memory. Many

of the hardware peripherals rely on the DMA

controller for efficient operation (AES core,

flash write controller, USARTs, Timers, ADC

interface) by performing data transfers

between a single SFR address and

flash/SRAM. See section 13.2 for details.

CC2430

The interrupt controller services a total of 18

interrupt sources, divided into six interrupt

groups, each of which is associated with one

of four interrupt priorities. An interrupt request

is serviced even if the device is in a sleep

mode (power modes 1-3) by bringing the

CC2430

The debug interface implements a proprietary

two-wire serial interface that is used for incircuit debugging. Through this debug

interface it is possible to perform an erasure of

the entire flash memory, control which

oscillators are enabled, stop and start

execution of the user program, execute

supplied instructions on the 8051 core, set

code breakpoints, and single step through

instructions in the code. Using these

techniques it is possible to elegantly perform

in-circuit debugging and external flash

programming. See section 12.9 for details.

The I/O-controller is responsible for all

general-purpose I/O pins. The CPU can

configure whether peripheral modules control

certain pins or whether they are under

software control, and if so whether each pin is

configured as an input or output and if a pullup or pull-down resistor in the pad is

connected. Each peripheral that connects to

the I/O-pins can choose between two different

I/O pin locations to ensure flexibility in various

applications. See section 13.1 for details.

The sleep timer is an ultra-low power timer

that counts 32.768 kHz crystal oscillator or

32.768 kHz RC oscillator periods. The sleep

timer runs continuously in all operating modes

except power mode 3. Typical uses for it is as

a real-time counter that runs regardless of

operating mode (except power mode 3) or as a

wakeup timer to get out of power mode 1 or 2.

See section 13.5 for details.

A built-in watchdog timer allows the

to reset itself in case the firmware hangs.

When enabled by software, the watchdog

timer must be cleared periodically, otherwise it

will reset the device when it times out. See

section 13.12 for details.

Timer 1 is a 16-bit timer with

timer/counter/PWM functionality. It has a

programmable prescaler, a 16-bit period value

and three individually programmable

counter/capture channels each with a 16-bit

compare value. Each of the counter/capture

channels can be used as PWM outputs or to

capture the timing of edges on input signals.

See section 13.3 for details.

back to active mode (power mode 0).

CC2430

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 27 of 233

This device is not yet released to market. Volume shipments possible under waiver.

CC2430

Timer 2 (MAC timer) is specially designed for

supporting an IEEE 802.15.4 MAC or other

time-slotted protocols in software. The timer

has a configurable timer period and an 8-bit

overflow counter that can be used to keep

track of the number of periods that have

transpired. There is also a 16-bit capture

register used to record the exact time at which

a start of frame delimiter is

received/transmitted or the exact time of which

transmission ends, as well as a 16-bit output

compare register that can produce various

command strobes (start RX, start TX, etc) at

specific times to the radio modules. See

section 13.4 for details.

Timers 3 and 4 are 8-bit timers with

timer/counter/PWM functionality. They have a

programmable prescaler, an 8-bit period value

and one programmable counter channel with a

8-bit compare value. Each of the counter

channels can be used as PWM outputs. See

section 13.6 for details.

USART 0 and 1 are each configurable as

either an SPI master/slave or a UART. They

provide double buffering on both RX and TX

and hardware flow-control and are thus well

suited to high-throughput full-duplex

applications. Each has its own high-precision

baud-rate generator thus leaving the ordinary

timers free for other uses. When configured as

an SPI slave they sample the input signal

using SCK directly instead of some oversampling scheme and are thus well-suited to

high data rates. See section 13.13 for details.

The AES encryption/decryption core allows

the user to encrypt and decrypt data using the

AES algorithm with 128-bit keys. The core is

able to support the AES operations required

by IEEE 802.15.4 MAC security, the ZigBee™

network layer and the application layer. See

section 13.9 for details.

The ADC supports 8 to 14 bits of resolution in

a 30 kHz to 4 kHz bandwidth respectively. DC

and audio conversions with up to 8 input

channels (Port 0) are possible. The inputs can

be selected as single ended or differential.

The reference voltage can be internal, AVDD,

or a single ended or differential external signal.

The ADC also has a temperature sensor input

channel. The ADC can automate the process

of periodic sampling or conversion over a

sequence of channels. See Section 13.7 for

details.

9.2 Radio

CC2430

radio based on the leading

transceiver. See Section 14 for details.

features an IEEE 802.15.4 compliant

CC2420

Device Flash

CC2430-F32 32 KB

CC2430-F64 64 KB

CC2430-F128 128 KB

Table 22: CC2430 Flash Memory Options

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 28 of 233

This device is not yet released to market. Volume shipments possible under waiver.

10 Power Management

CC2430

The

CC2430

has four major power modes,

called PM0, PM1, PM2 and PM3. PM0 is the

active mode while PM3 has the lowest power

consumption. The power modes are shown in

Table 23 together with voltage regulator and

oscillator options.

Power

Mode

PM0 B, C, D B, C B

PM1 A B, C B

PM2 A B, C A

PM3 A A A

High

frequency

oscillator

A None

B 32 MHz

C HF

D Both

Configuration

XOSC

RCOSC

Low- frequency

oscillator

A None

B 32.768

kHz

RCOSC

C 32.768

kHz

XOSC

Voltage

regulator

(digital)

A Off

B On

Table 23: Power Modes

PM0 : The full functional mode. The voltage

regulator to the digital core is on and either the

High frequency RC oscillator or the 32 MHz

crystal oscillator or both are running. Either the

32.768 kHz RC oscillator or the 32.768 kHz

crystal oscillator is running.

PM1 : The voltage regulator to the digital part

is on. Neither the 32 MHz crystal oscillator nor

the High frequency RC oscillator are running.

Either the 32.768 kHz RC oscillator or the

32.768 kHz crystal oscillator is running. The

system will go to PM0 on reset or an external

interrupt or when the sleep timer expires.

PM2 : The voltage regulator to the digital core

is turned off. Neither the 32 MHz crystal

oscillator nor the High frequency RC oscillator

are running. Either the 32.768 kHz RC

oscillator or the 32.768 kHz crystal oscillator is

running. The system will go to PM0 on reset or

an external interrupt or when the sleep timer

expires.

PM3 : The voltage regulator to the digital core

is turned off. None of the oscillators are

running. The system will go to PM0 on reset or

an external interrupt.

Refer to section 13.10 on page 135 for a

detailed description of power management.

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 29 of 233

This device is not yet released to market. Volume shipments possible under waiver.

11 Application Circuit

CC2430

Few external components are required for the

operation of

circuit is shown in Figure 6. Typical values and

description of external components are shown

in Table 24

11.1 Input / output matching

The RF input/output is high impedance and

differential. The optimum differential load for

the RF port is 115+j180 Ω.

When using an unbalanced antenna such as a

monopole, a balun should be used in order to

optimize performance. The balun can be

implemented using low-cost discrete inductors

and capacitors. The recommended balun

shown, consists of C341, L341, L321 and

L331 together with a PCB microstrip

transmission line (λ/2-dipole), and will match

the RF input/output to 50 Ω. An internal T/R

switch circuit is used to switch between the

LNA and the PA. See Input/output matching

section on page 181 for more details.

If a balanced antenna such as a folded dipole

is used, the balun can be omitted. If the

antenna also provides a DC path from

TXRX_SWITCH pin to the RF pins, inductors

are not needed for DC bias.

CC2430

. A typical application

The load capacitance is optionally tunable

through software

accuracy. The tuning adds the capacitance,

C

shown in the equation above. Hence

tune

initial crystal inaccuracy may compensated for

by tuning. See page 63 for details about

tuning.

XTAL2 is an optional 32.768 kHz crystal, with

two loading capacitors (C441 and C431), used

for the 32.768 kHz crystal oscillator. The

32.768 kHz crystal oscillator is used in

applications where you need both very low

sleep current consumption and accurate wake

up times. The load capacitance seen by the

32.768 kHz crystal is given by:

C +

=

11.4 Voltage regulators

The on chip voltage regulators supply all 1.8 V

power supply pins and internal power supplies.

C241 and C421 are required for stability of the

regulators. A series resistor may be used to

comply with the ESR requirement.

4

to improve the frequency

1

+

CC

C

11

431441

parasiticL

Figure 6 shows a suggested application circuit

using a differential antenna. The antenna type

is a standard folded dipole. The dipole has a

virtual ground point; hence bias is provided

without degradation in antenna performance.

Also refer to the section Antenna

Considerations on page 186.

11.2 Bias resistors

The bias resistors are R221 and R261. The

bias resistor R221 is used to set an accurate

bias current for the 32 MHz crystal oscillator.

11.3 Crystal

An external 32 MHz crystal, XTAL1, with two

loading capacitors (C191 and C211) is used

for the 32 MHz crystal oscillator. See page 15

for details. The load capacitance seen by the

32 MHz crystal is given by:

C ++

=

1

11

+

CC

211191

CC

tuneparasiticL

11.5 Debug interface

The debug interface pin P2_2 is connected

through pull-up resistor R451 to the power

supply. See section 13.1.6 on page 74.

11.6 Power supply decoupling and

filtering

Proper power supply decoupling must be used

for optimum performance. The placement and

size of the decoupling capacitors and the

power supply filtering are very important to

achieve the best performance in an

application. TI provides a compact reference

design that should be followed very closely.

Refer to the section PCB Layout

Recommendation on page 185.

4

Only for devices with Chip Version register,

CHVER.VERSION equal to 0x02 or greater

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 30 of 233

This device is not yet released to market. Volume shipments possible under waiver.

CC2430

optional

1

P1_7

2

P1_6

3

P1_5

4

P1_4

5

P1_3

P1_2

6

7

DVDD

P1_1

8

9

P1_0

RESET_N

10

11

P0_0

P0_1

12

P0_2

13

C441

C431

XTAL2

R451

48

47

46

45

44

P2_0

P2_1

DVDD

P2_3

P2_2

QLP48

CC2430

7x7

P0_3

14

P0_4

15

16

P0_5

P0_6

17

P0_7

18

43

P2_4

C421

2.0 - 3.6V Power Supply

42

41

40

DCOUPL

AVDD_DREG

AVDD_DGUARD

AVDD_SOC

XOSC_Q2

XOSC_Q1

RBIAS1

20

21

19

XTAL1

22

39

38

AVDD_ADC

DVDD_ADC

TXRX_SWITCH

VCO_GUARD

AVDD_RREG

23

R221

C241

37

AVDD_IF2

AVDD_RF2

AVDD_SW

RF_N

RF_P

AVDD_RF1

AVDD_PRE

AVDD_VCO

AVDD_CHP

RBIAS2

RREG_OUT

AVDD_IF1

24

Antenna

36

35

34

33

32

31

30

29

28

27

26

25

L321

L331

λ/4

R261

L341

λ/4

(50 Ohm)

C341

or

Folded Dipole PCB

Antenna

L331

L321

C211C191

Figure 6: CC2430 Application Circuit. (Digital I/O and ADC interface not connected).

Decoupling capacitors not shown.

CC2430 PRELIMINARY Data Sheet (rev. 2.01) SWRS036E Page 31 of 233

This device is not yet released to market. Volume shipments possible under waiver.

CC2430

Component Description

C191, C211 32 MHz crystal load capacitor 22 pF, 5%, NP0, 0402 22 pF, 5%, NP0, 0402

C241, C421 Load capacitance for power supply

voltage regulators

C341 DC block to antenna and match 5.6 pF, +/- 0.25pF, NP0,

C431, C441 32.768 kHz crystal load capacitor (if low-

frequency crystal is needed in application)

L321 Discrete balun and match 6.8 nH5,, 5%,

L331 Discrete balun and match 22 nH, 5%,

L341 Discrete balun and match 1.8 nH, 5%,

R221 Precision resistor for current reference

generator to system-on-chip part

R261 Precision resistor for current reference

generator to RF part

R451 Pull-up resistor connected to 2.0V-3.6V

power supply.

XTAL1 32 MHz Crystal 32 MHz crystal,

XTAL2 Optional 32.768 kHz watch crystal (if low-

frequency crystal is needed in application)

Single Ended 50Ω Output

220 nF, 10%, 0402 220 nF, 10%, 0402

0402

15 pF, 5%, NP0, 0402 15 pF, 5%, NP0, 0402

Monolithic/multilayer, 0402

Monolithic/multilayer, 0402

Monolithic/multilayer, 0402

56 kΩ, 1%, 0402 56 kΩ, 1%, 0402

43 kΩ, 1%, 0402 43 kΩ, 1%, 0402

ESR < 60 Ω

32.768 kHz crystal,

Epson MC 306.

Differential Antenna

Not used

12 nH 5%,

Monolithic/multilayer, 0402

27 nH, 5%,

Monolithic/multilayer, 0402

Not used