Page 1

TI

C28x DSP Design Workshop

Student Guide

C28x

Revision 5.0

February 2004

Technical Training

Organization

Page 2

Important Notice

Important Notice

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to

discontinue any product or service without notice, and advise customers to obtain the latest version of

relevant information to verify, before placing orders, that information being relied on is current and

complete. All products are sold subject to the terms and conditions of sale supplied at the time of order

acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the

extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not

necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or

represent that any license, either express or implied, is granted under any patent right, copyright, mask

work right, or other intellectual property right of TI covering or relating to any combination, machine, or

process in which such semiconductor products or services might be or are used. TI’s publication of

information regarding any third party’s products or services does not constitute TI’s approval, warranty or

endorsement thereof.

Copyright 2001, 2002, 2003, 2004 Texas Instruments Incorporated

Revision History

October 2001 – Revision 1.0

January 2002 – Revision 2.0

May 2002 – Revision 3.0

June 2002 – Revision 3.1

October 2002 – Revision 4.0

December 2002 – Revision 4.1

July 2003 – Revision 4.2

August 2003 – Revision 4.21

February 2004 – Revision 5.0

Mailing Address

Texas Instruments

Training Technical Organization

7839 Churchill Way

M/S 3984

Dallas, Texas 75251-1903

ii C28x - Introduction

Page 3

C28x Workshop

C28x Workshop

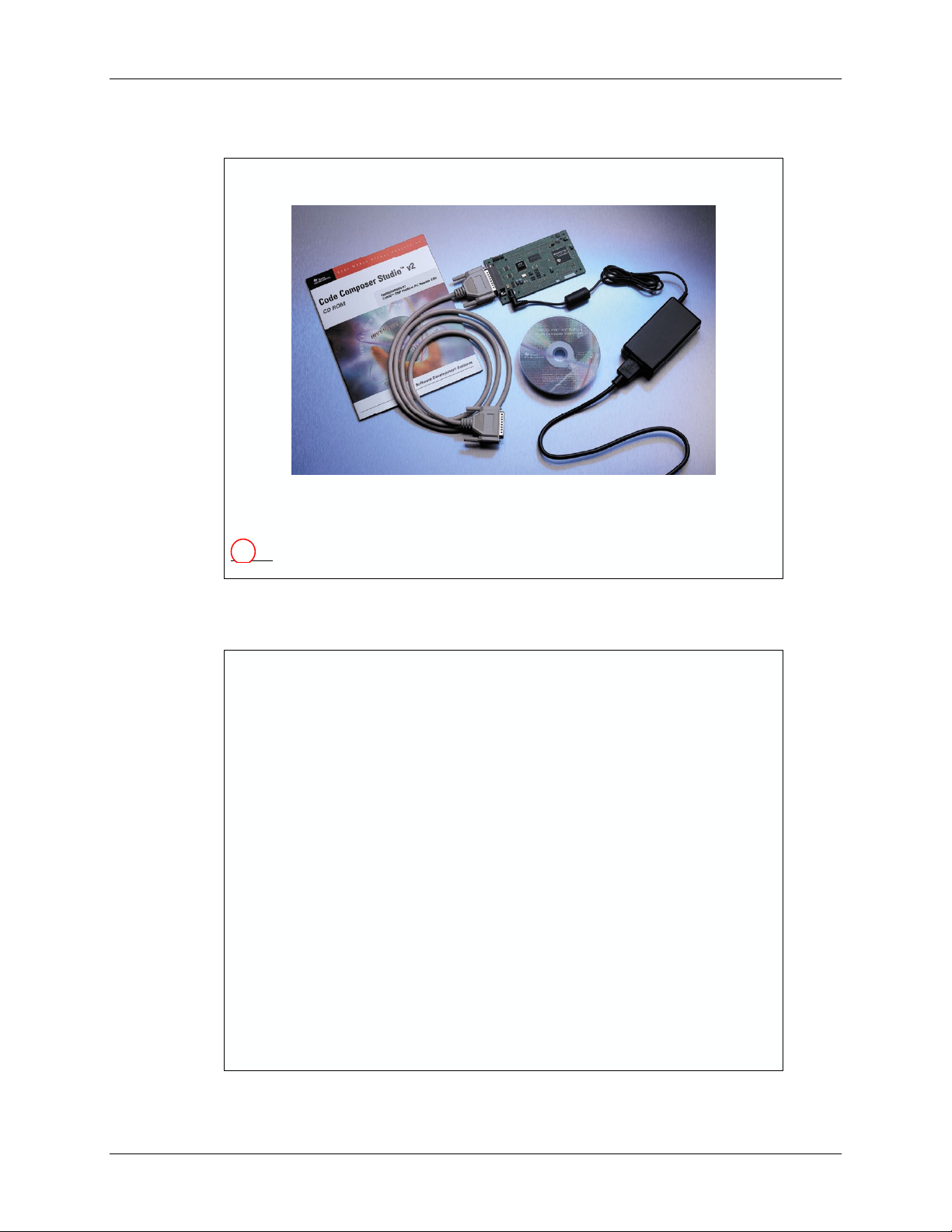

C28x DSP Design Workshop

C28x DSP Design Workshop

eZdsp™ F2812 Starter Kit

Texas Instruments

Texas Instruments

Technical Training

Technical Training

TO

TTTO

Technical Training

Technical Training

Organization

Organization

eZdsp

is a trademark of Spectrum Digital, Inc.

eZdsp

is a trademark of Spectrum Digital, Inc.

Introductions

Name

Name

Company

Company

Project Responsibilities

Project Responsibilities

DSP / Microcontroller Experience

DSP / Microcontroller Experience

TMS320 DSP Experience

TMS320 DSP Experience

Hardware / Software --

Hardware / Software

Interests

Interests

Copyright © 2004 Texas Instruments. All rights reserved.

Copyright © 2004 Texas Instruments. All rights reserved.

Introductions

Introductions

Assembly / C

Assembly / C

C28x - Introduction iii

Page 4

C28x Workshop

C28x Workshop Outline

C28x Workshop Outline

C28x Workshop Outline

Architecture Overview

1.1.Architecture Overview

Programming Development Environment

2.2.Programming Development Environment

Peripheral Register Header Files

3.3.Peripheral Register Header Files

Reset and Interrupts

4.4.Reset and Interrupts

System Initialization

5.5.System Initialization

Analog--toto--

6.6.Analog

Event Manager

7.7.Event Manager

Numerical Concepts and IQ Math

8.8.Numerical Concepts and IQ Math

Using DSP/BIOS

9.9.Using DSP/BIOS

10.

System Design

10.

System Design

11.

Communications

11.

Communications

12.

Support Resources

12.

Support Resources

Digital Converter

Digital Converter

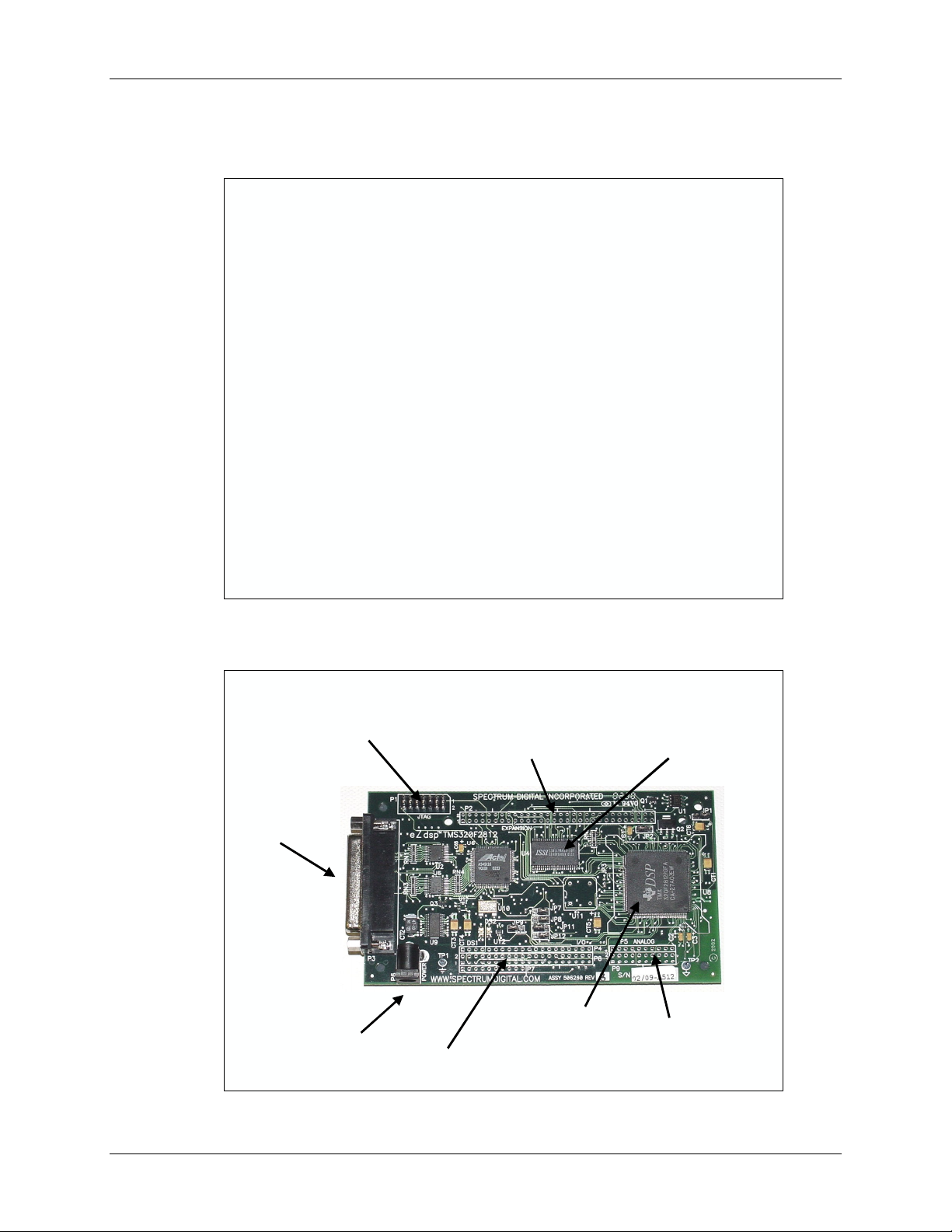

eZdsp™ F2812 Hardware

JTAG Interface (P1)

JTAG Interface (P1)

Parallel Port/

Parallel Port/

JTAG

JTAG

Controller

Controller

Interface (P3)

Interface (P3)

eZdsp

eZdsp

™ F2812 Hardware

™ F2812 Hardware

EXPANSION

EXPANSION

Data & Address (P2)

Data & Address (P2)

SRAM

SRAM

64K x 16

64K x 16

TMS320F2812 --

Power

Power

Connector (P6)

Connector (P6)

+5V

+5V

iv C28x - Introduction

I/O Interface (P4/P8/P7)

I/O Interface (P4/P8/P7)

TMS320F2812

DSP

DSP

ANALOG

ANALOG

Interface (P5/P9)

Interface (P5/P9)

Page 5

Introduction

This architecture overview introduces the basic architecture of the TMS320C28x (C28x) series of

Digital Signal Processors from Texas Instruments. The C28x series adds a new level of general

purpose processing ability unseen in any previous DSP chips. The C28x is ideal for applications

combining DSP, standard microcontroller processing, efficient C code execution, or operating

system tasks.

Learning Objectives

When this module is complete, you should have a basic understanding of the C28x architecture

and how all of its components work together to create a high-end, uniprocessor control system.

Learning Objectives

Learning Objectives

Identify the three main components

Identify the three main components

Architecture Overview

of the C28x

of the C28x

List the key features of the C28x

List the key features of the C28x

CPU

CPU

Identify the memory capabilities of

Identify the memory capabilities of

the C28x

the C28x

Identify the peripherals available on

Identify the peripherals available on

the C28x

the C28x

C28x - Architecture Overview 1 - 1

Page 6

Module Topics

Module Topics

Architecture Overview.............................................................................................................................. 1-1

Module Topics......................................................................................................................................... 1-2

What is the TMS320C28x?...................................................................................................................... 1-3

C28x CPU............................................................................................................................................... 1-4

Multiplier, ALU, and Shifters............................................................................................................. 1-5

TMS320C28x Internal Bussing .......................................................................................................... 1-6

Special Instructions............................................................................................................................. 1-7

Pipeline Advantage............................................................................................................................. 1-8

Memory ................................................................................................................................................... 1-9

Memory Map...................................................................................................................................... 1-9

Code Security Module (CSM)...........................................................................................................1-10

Peripherals .........................................................................................................................................1-10

Fast Interrupt Response.........................................................................................................................1-11

C28 Mode...............................................................................................................................................1-12

Reset.......................................................................................................................................................1-13

Summary ................................................................................................................................................1-14

1 - 2 C28x - Architecture Overview

Page 7

What is the TMS320C28x?

What is the TMS320C28x?

The TMS320C28x is a 32-bit fixed point DSP that specializes in high performance control

applications such as, robotics, industrial automation, mass storage devices, lighting, optical

networking, power supplies, and other control applications needing a single processor to solve a

high performance application.

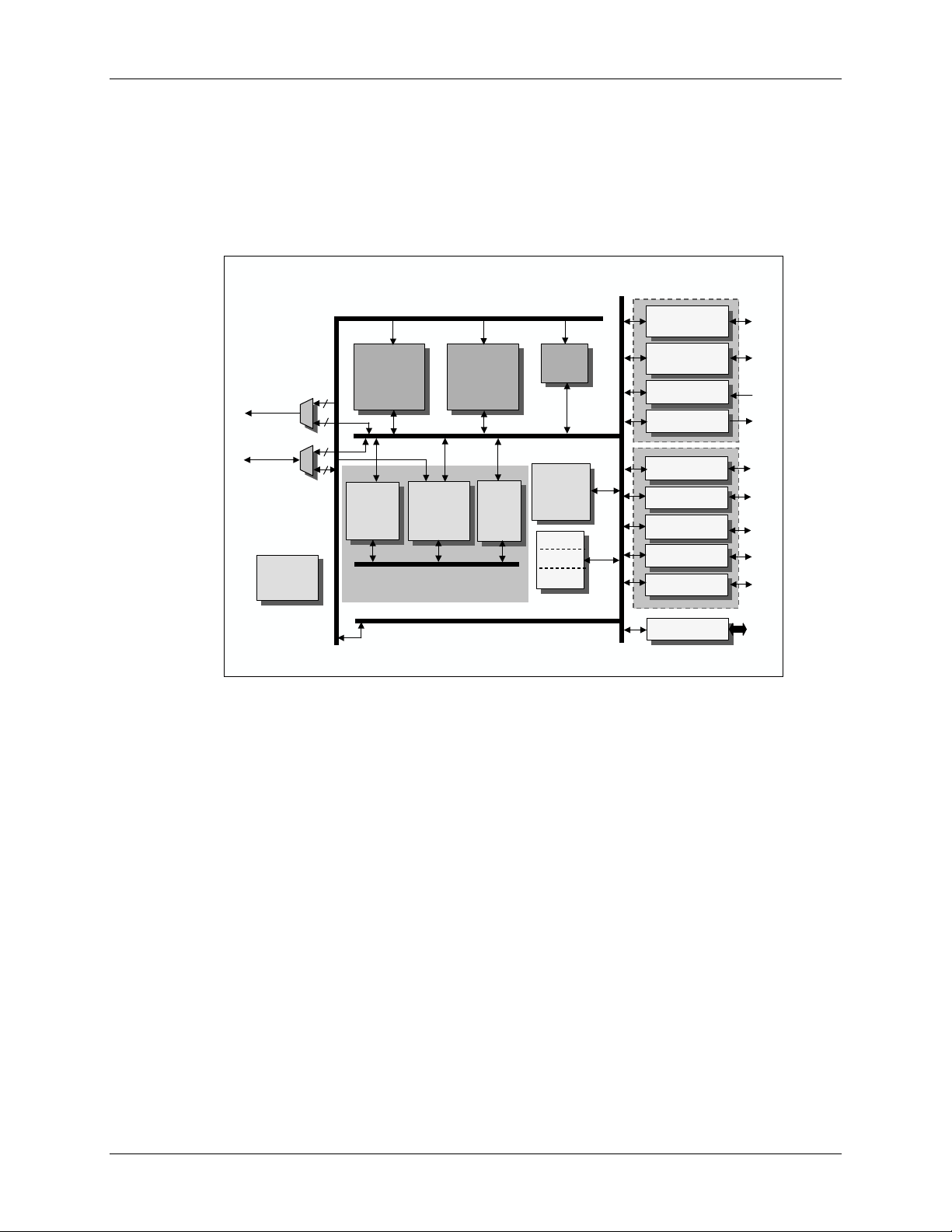

C28x Block Diagram

C28x Block Diagram

Program Bus

A(18--0)0)

A(18

D(15--0)0)

D(15

Realtime

Realtime

Realtime

JTAG

JTAG

JTAG

22

22

32

32

32

32

32

32

Sectored

Sectored

Sectored

Flash

Flash

Flash

bit

3232--bit

32-bit

Auxiliary

Auxiliary

Auxiliary

Registers

Registers

Registers

Program Bus

32x32 bit

32x32 bit

32x32 bit

Multiplier

Multiplier

Multiplier

Register Bus

Register Bus

CPU

CPU

RAM

RAM

RAM

RR--MM--W

R-M-W

Atomic

Atomic

Atomic

ALU

ALU

ALU

W

Boot

Boot

Boot

ROM

ROM

ROM

PIE

PIE

Interrupt

Interrupt

Manager

Manager

3

3

3

32 bit

32 bit

32 bit

Timers

Timers

Timers

Event

Event

Event

Manager A

Manager A

Manager A

Event

Event

Event

Manager B

Manager B

Manager B

bit ADC

1212--bit ADC

12-bit ADC

Watchdog

Watchdog

Watchdog

McBSP

McBSP

McBSP

CAN2.0B

CAN2.0B

CAN2.0B

SCI--AA

SCI

SCI-A

SCI--BB

SCI

SCI-B

SPI

SPI

SPI

Data Bus

Data Bus

The C28x architecture can be divided into 3 functional blocks:

• CPU and busing

• Memory

• Peripherals

GPIO

GPIO

GPIO

C28x - Architecture Overview 1 - 3

Page 8

C28x CPU

C28x CPU

The C28x is a highly integrated, high performance solution for demanding control applications.

The C28x is a cross between a general microcontroller and a digital signal processor, balancing

the code density of a RISC chip and the execution speed of a DSP with the architecture,

firmware, and development tools of a microcontroller.

The DSP features include a modified Harvard architecture and circular addressing. The RISC

features are single-cycle instruction execution, register-to-register operations, and modified

Harvard architecture. The microcontroller features include ease of use through an intuitive

instruction set, byte packing and unpacking, and bit manipulation.

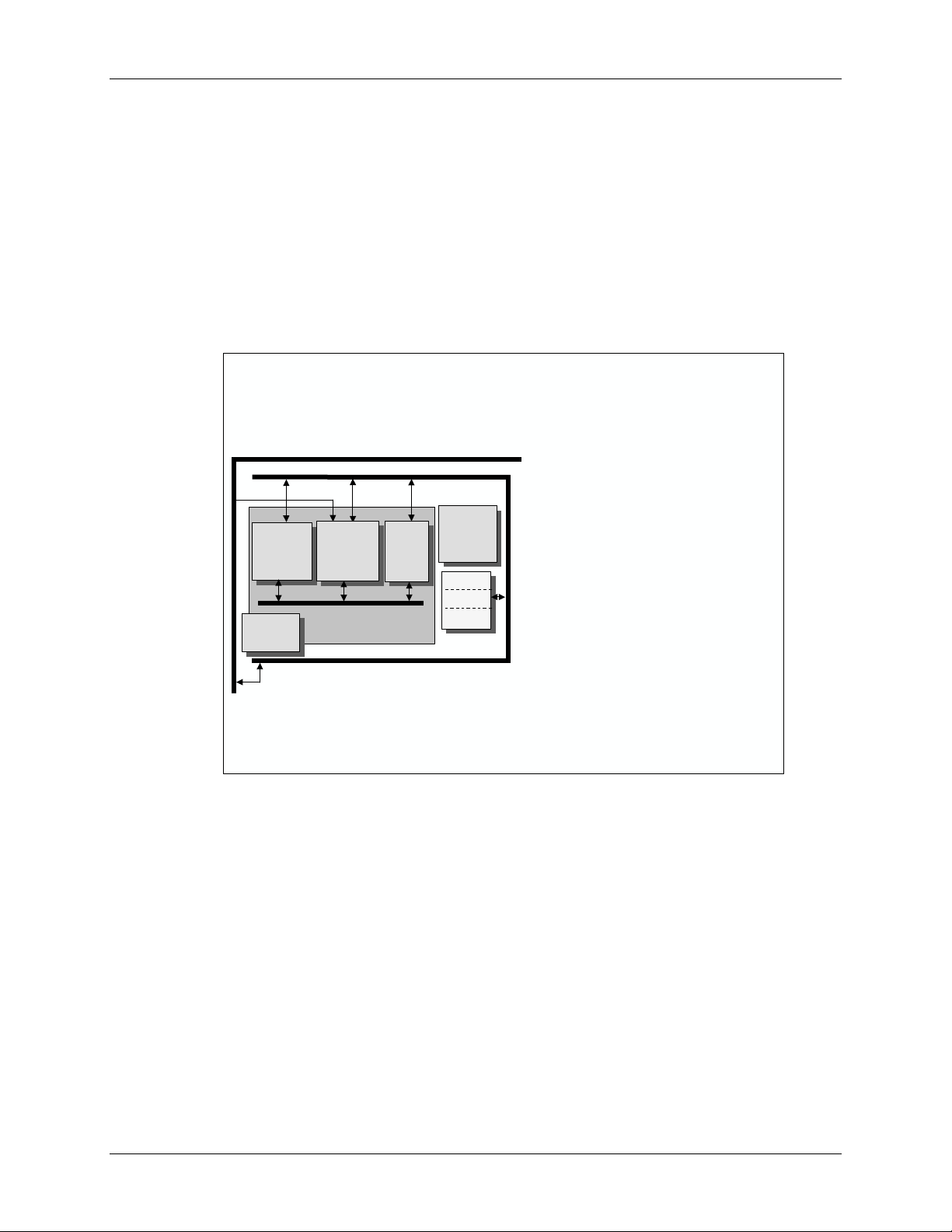

bit

3232--bit

32-bit

Auxiliary

Auxiliary

Auxiliary

Registers

Registers

Registers

Realtime

Realtime

Realtime

JTAG

JTAG

JTAG

Program Bus

Program Bus

32x32 bit

32x32 bit

32x32 bit

Multiplier

Multiplier

Multiplier

Register Bus

Register Bus

CPU

CPU

Data Bus

Data Bus

W

RR--MM--W

R-M-W

Atomic

Atomic

Atomic

ALU

ALU

ALU

C28x CPU

C28x CPU

MCU/DSP balancing code density

MCU/DSP balancing code density

& execution time.

& execution time.

PIE

PIE

Interrupt

Interrupt

Manager

Manager

3

3

3

32 bit

32 bit

32 bit

Timers

Timers

Timers

3232--bit fixed

32 x 32 bit fixed--

32 x 32 bit fixed

Dual 16 x 16 single--

Dual 16 x 16 single

point MAC (DMAC)

point MAC (DMAC)

3232--/64

64/32 and 32/32 modulus division

64/32 and 32/32 modulus division

Fast interrupt service time

Fast interrupt service time

Single cycle read--

Single cycle read

instructions

instructions

Unique real--

Unique real

capabilities

capabilities

Upward code compatibility

Upward code compatibility

Supports 32--

Supports 32

for improved execution time;

for improved execution time;

Supports 16--

Supports 16

for improved code efficiency

for improved code efficiency

bit fixed--

/64--

bit saturation

bit saturation

bit instructions

bit instructions

bit instructions

bit instructions

point DSP

point DSP

point MAC

point MAC

cycle fixed--

cycle fixed

modify--

modify

time debugging

time debugging

write

write

The C28x design supports an efficient C engine with hardware that allows the C compiler to

generate compact code. Multiple busses and an internal register bus allow an efficient and

flexible way to operate on the data. The architecture is also supported by powerful addressing

modes, which allow the compiler as well as the assembly programmer to generate compact code

that is almost one to one corresponded to the C code.

The C28x is as efficient in DSP math tasks as it is in system control tasks that typically are

handled by microcontroller devices. This efficiency removes the need for a second processor in

many systems.

The C28x is one of several members of the fixed-point generations of digital signal processors

(DSPs) in the TMS320 family. The C28x is source-code and object-code compatible with the

C27x. In addition, the C28x is source code compatible with the 24x/240x DSP and previously

written code can be reassembled to run on a C28x device. This allows for migration of existing

code onto the C28x.

1 - 4 C28x - Architecture Overview

Page 9

C28x CPU

Multiplier, ALU, and Shifters

C28x Multiplier and ALU / Shifters

C28x Multiplier and ALU / Shifters

Program Bus

Program Bus

Data Bus

Data Bus

Shift R/L (0--

Shift R/L (0

Data Bus

Data Bus

32

32

16/32

XT (32) or T/TL

16

16

16)

16)

32

32

32

32

32

32

AH (16)

AH (16)

AH.MSB AH.LSB

AH.MSB AH.LSB

Shift R/L (0--

Shift R/L (0

XT (32) or T/TL

MULTIPLIER

MULTIPLIER

32

32

Dual 16 x 16

Dual 16 x 16

P (32) or PH/PL

P (32) or PH/PL

Shift R/L (0--

Shift R/L (0

ALU (32)

ALU (32)

32

32

ACC (32)

ACC (32)

AL (16)

AL (16)

AL.MSB AL.LSB

AL.MSB AL.LSB

32

•

32

•

32

32

32 x 32 or

32 x 32 or

32

32

16)

16)

16)

16)

16/32

8/16

8/16

•

•

32

32

The 32 x 32-bit MAC capabilities of the C28x and its 64-bit processing capabilities, enable the

C28x to efficiently handle higher numerical resolution problems that would otherwise demand a

more expensive floating-point processor solution. Along with this is the capability to perform

two 16 x 16-bit multiply accumulate instructions simultaneously or Dual MACs (DMAC).

C28x

C28x

XARn

XARn

XARn →→3232--

XARn

ARn→→1616--

ARn

XAR0

XAR0

XAR1

XAR1

XAR2

XAR2

XAR3

XAR3

XAR4

XAR4

XAR5

XAR5

XAR6

XAR6

XAR7

XAR7

ARAU

ARAU

bits

bits

bits

bits

, DP and Memory

, DP and Memory

Data Bus

Data Bus

Program Bus

Program Bus

6 LSB

6 LSB

from IR

from IR

32

32

Data Memory

Data Memory

DP (16)

DP (16)

22

22

MUX

MUX

MUX

MUX

C28x - Architecture Overview 1 - 5

Page 10

C28x CPU

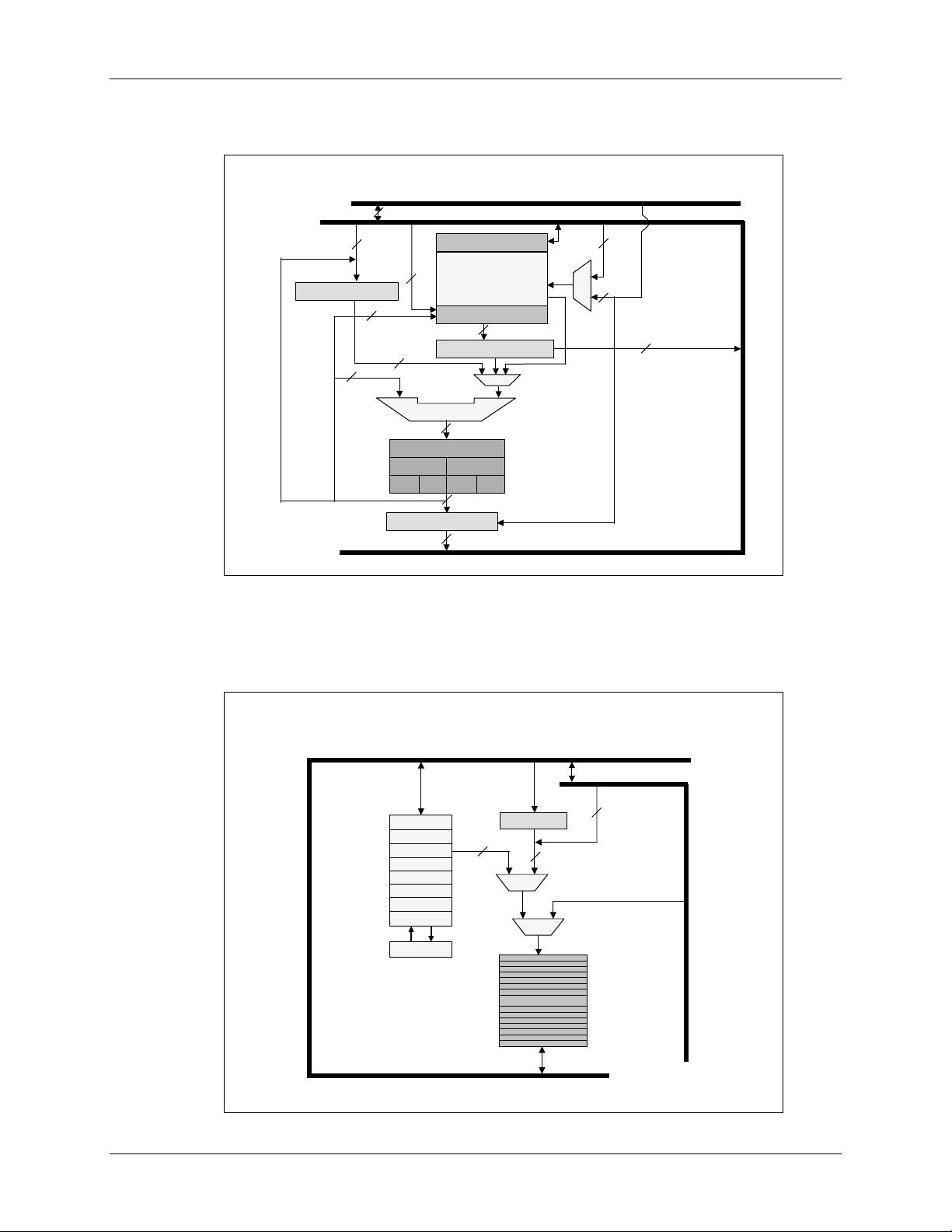

TMS320C28x Internal Bussing

As with many DSP type devices, multiple busses are used to move data between the memories

and peripherals and the CPU. The C28x memory bus architecture contains:

• A program read bus (22 bit address line and 32 bit data line)

• A data read bus (32 bit address line and 32 bit data line)

• A data write bus (32 bit address line and 32 bit data line)

C28x Internal Bus Structure

C28x Internal Bus Structure

Program

Program

PC

PC

Decoder

Decoder

Registers

Registers

ARAU

ARAU

SP

DPDP@X

XAR0

XAR0

to

to

XAR7

XAR7

SP

@X

Program Address Bus (22)

Program Address Bus (22)

Program--

Program

Data--

Data

Data--

Data

Execution

Execution

MPY32x32

MPY32x32

ALU

ALU

XT

XT

P

P

ACC

ACC

read Data Bus (32)

read Data Bus (32)

read Address Bus (32)

read Address Bus (32)

read Data Bus (32)

read Data Bus (32)

RR--MM--W

Atomic

Atomic

ALU

ALU

W

Debug

Debug

Real--

Time

Real

Time

Emulation

Emulation

&

&

Test

Test

Engine

Engine

JTAG

JTAG

Program

Program

(4M* 16)

(4M* 16)

Data

Data

(4G * 16)

(4G * 16)

Memory

Memory

Standard

Standard

Peripherals

Peripherals

External

Register Bus / Result Bus

Register Bus / Result Bus

Data/Program--

Data/Program

Data--

Data

write Data Bus (32)

write Data Bus (32)

write Address Bus (32)

write Address Bus (32)

External

Interfaces

Interfaces

The 32-bit-wide data busses enable single cycle 32-bit operations. This multiple bus architecture,

known as a Harvard Bus Architecture enables the C28x to fetch an instruction, read a data value

and write a data value in a single cycle. All peripherals and memories are attached to the memory

bus and will prioritize memory accesses.

1 - 6 C28x - Architecture Overview

Page 11

C28x CPU

Special Instructions

C28x Atomic Read/Modify/Write

C28x Atomic Read/Modify/Write

Atomic Instructions Benefits:

Atomic Instructions Benefits:

LOAD

Registers

Registers

CPU

CPU

LOAD

ALU / MPY

ALU / MPY

STORE

STORE

READ

READ

WRITE

WRITE

Mem

Mem

Simpler programming

¾

¾

Simpler programming

¾

Smaller, faster code

¾

Smaller, faster code

Uninterruptible (Atomic)

¾

¾

Uninterruptible (Atomic)

¾

More efficient compiler

¾

More efficient compiler

Standard Load/Store

Standard Load/Store

DINT

DINT

MOV

MOV

AND

AND

MOV

MOV

EINT

EINT

AL,*XAR2

AL,*XAR2

AL,#1234h

AL,#1234h

*XAR2,AL

*XAR2,AL

6 words / 6 cycles

6 words / 6 cycles

Atomic Read/Modify/Write

Atomic Read/Modify/Write

AND *XAR2,#1234h

AND *XAR2,#1234h

2 words / 1 cycles

2 words / 1 cycles

Atomics are small common instructions that are non-interuptable. The atomic ALU capability

supports instructions and code that manages tasks and processes. These instructions usually

execute several cycles faster than traditional coding.

C28x - Architecture Overview 1 - 7

Page 12

C28x CPU

Pipeline Advantage

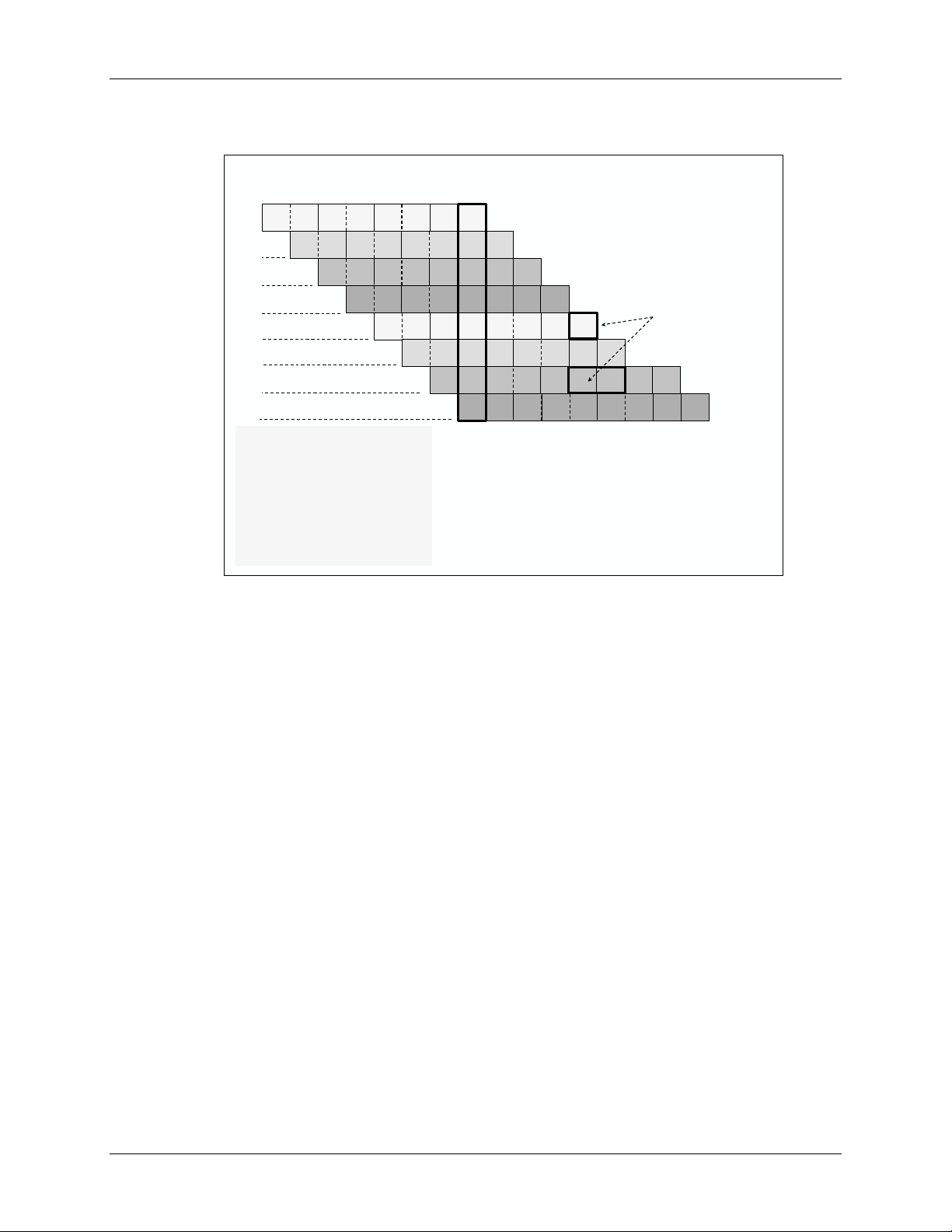

C28x Pipeline

C28x Pipeline

F

F

D

D

R

F

F

D

2

1

1

D

1

1

F

D

F

D

2

2

F

F

F

F

1

1

F

F

1

2

1

A

A

F

B

B

C

C

D

D

E

E

F

F

G

G

H

H

F1: Instruction Address

F1: Instruction Address

F2: Instruction Content

F2: Instruction Content

D1: Decode Instruction

D1: Decode Instruction

D2: Resolve Operand Addr

D2: Resolve Operand Addr

R1: Operand Address

R1: Operand Address

R2: Get Operand

R2: Get Operand

X: CPU doing “real” work

X: CPU doing “real” work

W: store content to memory

W: store content to memory

F

2

2

1

1

2

2

1

1

R

R

R

1

1

D

R

D

R

2

2

D

D

D

D

1

1

F

D

F

D

2

2

F

F

F

F

1

1

F

F

X

X

W

2

2

1

2

2

1

1

2

2

1

1

W

W

1

R

R

R

R

D

D

D

D

1

F

F

2

2

F

F

1

1

W

X

X

2

2

R

X

R

X

1

2

1

2

R

R

R

R

2

1

2

1

Protected Pipeline

Protected Pipeline

2

1

2

D

R

D

R

2

1

2

1

D

D

D

D

1

2

1

2

F

D

F

D

2

1

2

1

F

F

F

F

1

2

1

2

Order of results are as written in

¾

¾

Order of results are as written in

source code

source code

¾

Programmer need not worry about

¾

Programmer need not worry about

the pipeline

the pipeline

stage pipeline

88--stage pipeline

W

W

X

X

W

W

R

X

2

2

1

1

2

2

1

1

W

X

W

R

X

2

2

1

1

1

1

2

2

2

2

W

X

W

R

X

R

R

X

W

R

XXW

R

R

R

R

2

2

2

1

2

1

R

R

W

X

X

2

2

2

2

R

R

1

1

R

R

R

R

R

D

D

D

D

R

R

R

D

D

D

D

E & G Access

E & G Access

same address

same address

W

X W

W

X W

W

The C28x uses a special 8-stage protected pipeline to maximize the throughput. This protected

pipeline prevents a write to and a read from the same location from occurring out of order.

This pipelining also enables the C28x to execute at high speeds without resorting to expensive

high-speed memories. Special branch-look-ahead hardware minimizes the latency for conditional

discontinuities. Special store conditional operations further improve performance.

1 - 8 C28x - Architecture Overview

Page 13

Memory

Memory

The memory space on the C28x is divided into program and data space. There are several

different types of memory available that can be used as both program or data space. They include

the flash memory, single access RAM (SARAM), expanded SARAM, and Boot ROM which is

factory programmed with boot software routines or standard tables used in math related

algorithms.

Memory Map

The C28x CPU contains no memory, but can access memory both on and off the chip. The C28x

uses 32-bit data addresses and 22-bit program addresses. This allows for a total address reach of

4G words (1 word = 16 bits) in data space and 4M words in program space. Memory blocks on

all C28x designs are uniformly mapped to both program and data space.

This memory map shows the different blocks of memory available to the program and data space.

TMS320F2812 Memory Map

TMS320F2812 Memory Map

Data

0x00 0000

0x00 0000

0x00 0400

0x00 0400

0x00 0800

0x00 0800

0x00 0D00

0x00 0D00

0x00 1000

0x00 1000

0x00 6000

0x00 6000

0x00 7000

0x00 7000

0x00 8000

0x00 8000

0x00 9000

0x00 9000

0x00 A000

0x00 A000

0x3D 7800

0x3D 7800

0x3D 7C00

0x3D 7C00

0x3D 8000

0x3D 8000

0x3F 8000

0x3F 8000

0x3F A000

0x3F A000

0x3F F000

0x3F F000

0x3F FFC0

0x3F FFC0

| Program

Data

| Program

MO SARAM (1K)

MO SARAM (1K)

M1 SARAM (1K)

M1 SARAM (1K)

PF 0 (2K)

PF 0 (2K)

PIE vector

PIE vector

(256)

(256)

ENPIE=1

ENPIE=1

PF 2 (4K)

PF 2 (4K)

PF 1 (4K)

PF 1 (4K)

LO SARAM (4K)

LO SARAM (4K)

L1 SARAM (4K)

L1 SARAM (4K)

FLASH (128K)

FLASH (128K)

128--

128

HO SARAM (8K)

HO SARAM (8K)

Boot ROM (4K)

Boot ROM (4K)

BROM vector (32)

BROM vector (32)

MP/MC=0 ENPIE=0

MP/MC=0 ENPIE=0

reserved

reserved

reserved

reserved

reserved

reserved

OTP (1K)

OTP (1K)

reserved

Bit Password

Bit Password

reserved

MP/MC=0

MP/MC=0

Data

| Program

Data

| Program

reserved

XINT Zone 0 (8K)

XINT Zone 1 (8K)

reserved

XINT Zone 2 (0.5M)

XINT Zone 6 (0.5M)

reserved

XINT Zone 7 (16K)

MP/MC=1

XINT Vector-RAM (32)

MP/MC=1 ENPIE=0

0x00 2000

0x00 2000

0x00 4000

0x00 4000

0x08 0000

0x08 0000

0x10 0000

0x10 0000

0x18 0000

0x18 0000

0x3F C000

0x3F C000

CSM: LO, L1

CSM: LO, L1

OTP, FLASH

OTP, FLASH

C28x - Architecture Overview 1 - 9

Page 14

Memory

Code Security Module (CSM)

Code Security Module

Code Security Module

Prevents reverse engineering and

Prevents reverse engineering and

protects valuable intellectual property

protects valuable intellectual property

0x00 8000

0x00 8000

0x00 9000

0x00 9000

0x00 A000

0x00 A000

0x3D 7800

0x3D 7800

0x3D 7C00

0x3D 7C00

0x3D 8000

0x3D 8000

128--

bit user defined password is stored in Flash

128

bit user defined password is stored in Flash

128

128--

bits = 2

128

bits = 2

To try 1 password every 2 cycles at 150 MHz, it

To try 1 password every 2 cycles at 150 MHz, it

would take at least 1.4 x 10

would take at least 1.4 x 10

possible combinations!

possible combinations!

128

LO SARAM (4K)

LO SARAM (4K)

L1 SARAM (4K)

L1 SARAM (4K)

reserved

OTP (1K)

OTP (1K)

reserved

FLASH (128K)

FLASH (128K)

128--

Bit Password

128

Bit Password

= 3.4 x 10

= 3.4 x 10

38

38

possible passwords

possible passwords

23

23

years to try all

years to try all

Peripherals

The C28x comes with many built in peripherals optimized to support control applications. These

peripherals vary depending on which C28x device you choose.

• Event Manager

• Analog-to-Digital Converter

• Watchdog Timer

• SPI

• SCI

• CAN

• McBSP

• GPIO

1 - 10 C28x - Architecture Overview

Page 15

Fast Interrupt Response

Fast Interrupt Response

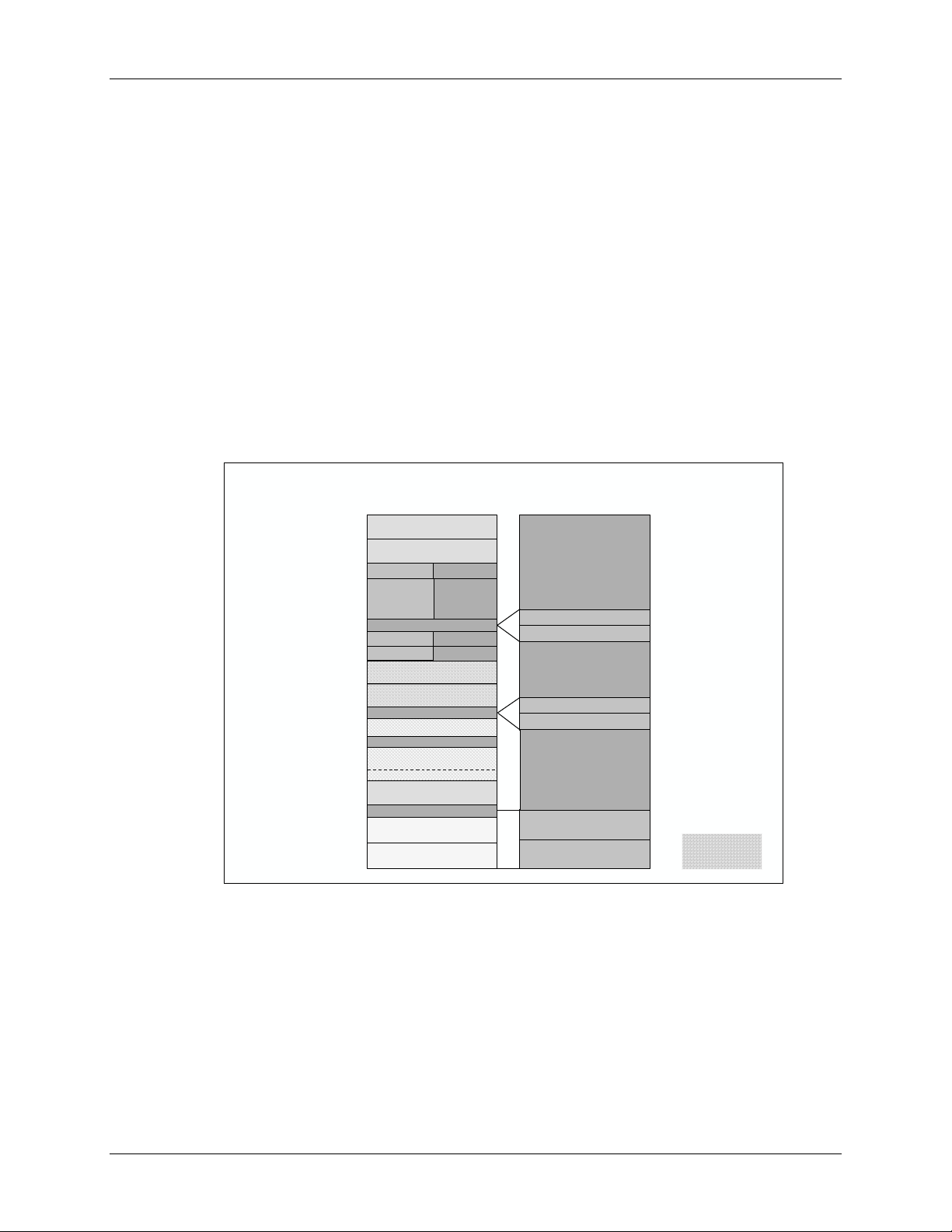

The fast interrupt response, with automatic context save of critical registers, resulting in a device

that is capable of servicing many asynchronous events with minimal latency. C28x implements a

zero cycle penalty to do 14 registers context saved and restored during an interrupt. This feature

helps reduces the interrupt service routine overheads.

C28x Fast Interrupt Response Manager

C28x Fast Interrupt Response Manager

96 dedicated PIE

¾

¾

96 dedicated PIE

vectors

vectors

No software decision

¾

¾

No software decision

96

96

PIE module

PIE module

For 96

For 96

interrupts

interrupts

PIE

PIE

Register

Register

Map

Map

INT1 to

INT1 to

INT12

INT12

12 interrupts

12 interrupts

28x CPU Interrupt logic

28x CPU Interrupt logic

IFR

IER

IFR

IER

INTM

INTM

28x

28x

CPU

CPU

making required

making required

Direct access to RAM

¾

¾

Direct access to RAM

vectors

vectors

Auto flags update

¾

¾

Auto flags update

Concurrent auto

¾

¾

Concurrent auto

context save

context save

Auto Context Save

Auto Context Save

T

T

AH

AH

PH

PH

AR1 (L)

AR1 (L)

DP

DP

DBSTAT

DBSTAT

PC(msw)

PC(msw)

ST0

ST0

AL

AL

PL

PL

AR0 (L)

AR0 (L)

ST1

ST1

IER

IER

PC(lsw)

PC(lsw)

Peripheral Interrupts 12x8 = 96

Peripheral Interrupts 12x8 = 96

C28x - Architecture Overview 1 - 11

Page 16

C28 Mode

C28 Mode

The C28x is one of several members of the fixed-point generations of digital signal processors

(DSPs) in the TMS320 family. The C28x is source-code and object-code compatible with the

C27x. In addition, the C28x is source code compatable with the 24x/240x DSP and previously

written code can be reassembled to run on a C28x device. This allows for migration of existing

code onto the C28x.

C28x / C24x Modes

C28x / C24x Modes

Mode Type

Mode Type

C24x Mode

C24x Mode

C28x Mode

C28x Mode

Test Mode (default)

Test Mode (default)

Reserved

Reserved

C24x source--

¾

¾

C24x source

Allows you to run C24x source code which has been reassembled

¾

¾

Allows you to run C24x source code which has been reassembled

using the C28x code generation tools (need new vectors)

using the C28x code generation tools (need new vectors)

C28x mode:

¾

¾

C28x mode:

Can take advantage of all the C28x native features

¾

¾

Can take advantage of all the C28x native features

compatible mode:

compatible mode:

Mode Bits

Mode Bits

OBJMODE AMODE

OBJMODE AMODE

1

1

1

1

0 00

0

0 11

0

1

1

0

0

Compiler

Compiler

Option

Option

v28 --

m20

--v28

m20

v28

--v28

v27

--v27

(workshop)

(workshop)

1 - 12 C28x - Architecture Overview

Page 17

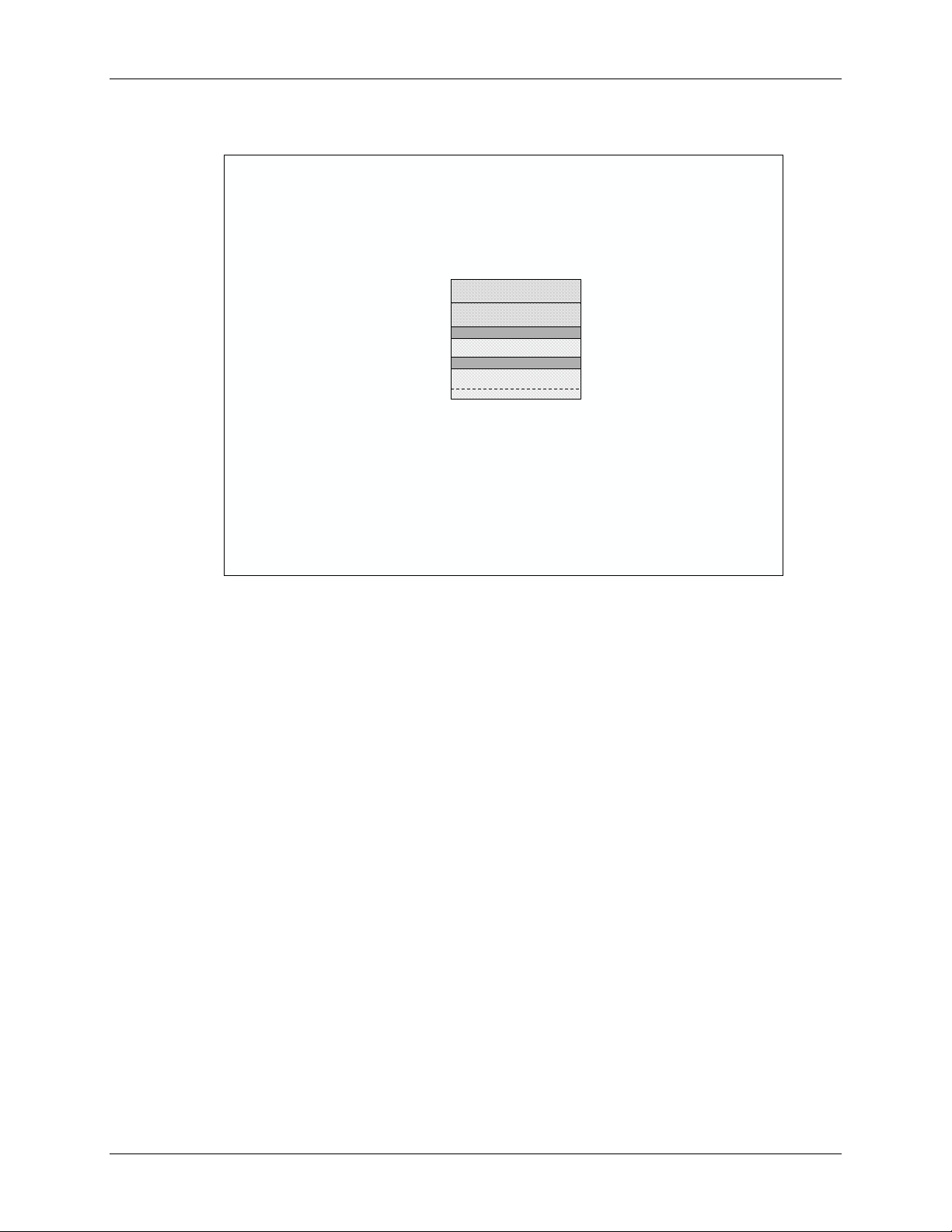

Reset

Reset

Reset ––

Reset

Reset

Reset

OBJMODE=0 AMODE=0

OBJMODE=0 AMODE=0

ENPIE=0 VMAP=1

ENPIE=0 VMAP=1

XMPNMC=0

XMPNMC=0

(microcomputer mode)

(microcomputer mode)

Reset vector fetched

Reset vector fetched

from boot ROM

from boot ROM

0x3F FFC0

0x3F FFC0

Note:

Note:

Details of the various boot options will be

Details of the various boot options will be

discussed in the Reset and Interrupts module

discussed in the Reset and Interrupts module

Bootloader

Bootloader

Bootloader

Bootloader

OBJMODE = 1

OBJMODE = 1

AMODE = 0

AMODE = 0

Boot determined by

Boot determined by

state of GPIO pins

state of GPIO pins

Execution

Execution

Entry Point

Entry Point

H0 SARAM

H0 SARAM

sets

sets

C28x - Architecture Overview 1 - 13

Page 18

Summary

Summary

Summary

Summary

High performance 32--

High performance 32

32 x 32 bit or dual 16 x 16 bit MAC

32 x 32 bit or dual 16 x 16 bit MAC

bit DSP

bit DSP

Atomic read--

Atomic read

stage fully protected pipeline

88--stage fully protected pipeline

Fast interrupt response manager

Fast interrupt response manager

128Kw on--

128Kw on

Code security module (CSM)

Code security module (CSM)

Two event managers

Two event managers

bit ADC module

1212--bit ADC module

56 shared GPIO pins

56 shared GPIO pins

Watchdog timer

Watchdog timer

Communications peripherals

Communications peripherals

modify--

modify

chip flash memory

chip flash memory

write instructions

write instructions

1 - 14 C28x - Architecture Overview

Page 19

Programming Development Environment

Introduction

This module will explain how to use Code Composer Studio (CCS) integrated development

environment (IDE) tools to develop a program. Creating projects and setting building options

will be covered. Use and the purpose of the linker command file will be described. Additionally,

the DSP/BIOS Configuration Tool will be used to handle system memory and system setup.

Learning Objectives

Learning Objectives

Learning Objectives

Use Code Composer Studio to:

Use Code Composer Studio to:

Create a

Create a

Set

Build Options

Set

Build Options

Project

Project

Create a

Create a

Describes a system’s available memory

Describes a system’s available memory

Indicates where sections will be placed

Indicates where sections will be placed

in memory

in memory

Use

Use

DSP/BIOS Configuration Tool

DSP/BIOS Configuration Tool

Handle system memory and system setup

Handle system memory and system setup

Create a .

Create a .

user

user

cdb

cdb

linker command file which:

linker command file which:

to:

to:

and .

and .

cmd

cmd

file

file

C28x - Programming Development Environment 2 - 1

Page 20

Module Topics

Module Topics

Programming Development Environment .............................................................................................. 2-1

Module Topics......................................................................................................................................... 2-2

Code Composer Studio ........................................................................................................................... 2-3

Software Development and COFF Concepts...................................................................................... 2-3

Projects ............................................................................................................................................... 2-5

Build Options...................................................................................................................................... 2-6

Creating a Linker Command File ........................................................................................................... 2-9

Sections .............................................................................................................................................. 2-9

Linker Command Files (.cmd).........................................................................................................2-12

Memory-Map Description .................................................................................................................2-12

Section Placement..............................................................................................................................2-14

Exercise 2a.............................................................................................................................................2-15

Summary: Linker Command File......................................................................................................2-16

Lab 2a: Linker Command File...............................................................................................................2-17

DSP/BIOS Configuration Tool...............................................................................................................2-21

Lab 2b: DSP/BIOS Configuration Tool .................................................................................................2-26

Solutions.................................................................................................................................................2-30

2 - 2 C28x - Programming Development Environment

Page 21

Code Composer Studio

Code Composer Studio

Software Development and COFF Concepts

In an effort to standardize the software development process, TI uses the Common Object File

Format (COFF). COFF has several features which make it a powerful software development

system. It is most useful when the development task is split between several programmers.

Each file of code, called a module, may be written independently, including the specification of

all resources necessary for the proper operation of the module. Modules can be written using

Code Composer Studio (CCS) or any text editor capable of providing a simple ASCII file output.

The expected extension of a source file is .ASM for assembly and .C for C programs.

Code Composer Studio

Code Composer Studio

Build

Compile

Compile

Build

lnk..

lnk

cmd

cmd

Probe In

Probe In

SIM

SIM

eZdsp™™

eZdsp

Asm

Asm

DSP/BIOS

Edit

Edit

Code Composer Studio includes:

Code Composer Studio includes:

DSP/BIOS

Config

Config

Tool

Tool

Integrated Edit/Debug GUI

Integrated Edit/Debug GUI

Code Generation Tools

Code Generation Tools

DSP/BIOS

DSP/BIOS

Link

Link

DSP/BIOS

DSP/BIOS

Libraries

Libraries

Debug

Debug

Probe Out

Probe Out

Graphs

Graphs

Profiling

Profiling

EVM

EVM

Third

Third

Party

Party

XDS

XDS

DSP

DSP

Board

Board

Code Composer Studio includes a built-in editor, compiler, assembler, linker, and an automatic

build process. Additionally, tools to connect file input and output, as well as built-in graph

displays for output are available. Other features can be added using the plug-ins capability

Numerous modules are joined to form a complete program by using the linker. The linker

efficiently allocates the resources available on the device to each module in the system. The

linker uses a command (.CMD) file to identify the memory resources and placement of where the

various sections within each module are to go. Outputs of the linking process includes the linked

object file (.OUT), which runs on the DSP, and can include a .MAP file which identifies where

each linked section is located.

The high level of modularity and portability resulting from this system simplifies the processes of

verification, debug and maintenance. The process of COFF development is presented in greater

detail in the following paragraphs.

C28x - Programming Development Environment 2 - 3

Page 22

Code Composer Studio

The concept of COFF tools is to allow modular development of software independent of

hardware concerns. An individual assembly language file is written to perform a single task and

may be linked with several other tasks to achieve a more complex total system.

Writing code in modular form permits code to be developed by several people working in parallel

so the development cycle is shortened. Debugging and upgrading code is faster, since

components of the system, rather than the entire system, is being operated upon. Also, new

systems may be developed more rapidly if previously developed modules can be used in them.

Code developed independently of hardware concerns increases the benefits of modularity by

allowing the programmer to focus on the code and not waste time managing memory and moving

code as other code components grow or shrink. A linker is invoked to allocate systems hardware

to the modules desired to build a system. Changes in any or all modules, when re-linked, create a

new hardware allocation, avoiding the possibility of memory resource conflicts.

Code Composer Studio: IDE

Code Composer Studio: IDE

Integrates

Integrates

and debug

and debug

Single--

Single

Powerful

Powerful

Automated tasks using

Automated tasks using

Built--

Built

Support TI or 3

Support TI or 3

: edit, code generation,

: edit, code generation,

click access

click access

graphing/profiling

graphing/profiling

in access to

in access to

using buttons

using buttons

BIOS

BIOS

rd

rd

party

party

tools

tools

GEL scripts

GEL scripts

functions

functions

plug--

ins

plug

ins

2 - 4 C28x - Programming Development Environment

Page 23

Code Composer Studio

Projects

Code Composer works with a project paradigm. Essentially, within CCS you create a project for

each executable program you wish to create. Projects store all the information required to build

the executable. For example, it lists things like: the source files, the header files, the target

system’s memory-map, and program build options.

The CCS Project

The CCS Project

Project (.

Project (.

Source files (by reference)

Source files (by reference)

Project settings:

Project settings:

pjt

) files contain:

pjt

) files contain:

Source (C, assembly)

Source (C, assembly)

Libraries

Libraries

DSP/BIOS configuration

DSP/BIOS configuration

Linker command files

Linker command files

Build Options (compiler and

Build Options (compiler and

assembler)

assembler)

Build configurations

Build configurations

DSP/BIOS

DSP/BIOS

Linker

Linker

The project information is stored in a .PJT file, which is created and maintained by CCS. To

create a new project, you need to select the

Project:New… menu item.

Along with the main Project menu, you can also manage open projects using the right-click

popup menu. Either of these menus allows you to Add Files… to a project. Of course, you can

also drag-n-drop files onto the project from Windows Explorer.

C28x - Programming Development Environment 2 - 5

Page 24

Code Composer Studio

Build Options

Project options direct the code generation tools (i.e. compiler, assembler, linker) to create code

according to your system’s needs. When you create a new project, CCS creates two sets of build

options – called Configurations: one called Debug, the other Release (you might think of as

Optimize).

To make it easier to choose build options, CCS provides a graphical user interface (GUI) for the

various compiler options. Here’s a sample of the Debug configuration options.

Build Options GUI --

Build Options GUI

GUI has 8 pages of categories for code

GUI has 8 pages of categories for code

generation tools

generation tools

Controls many aspects of the build process,

Controls many aspects of the build process,

such as:

such as:

Optimization level

Optimization level

Target device

Target device

Compiler/assembly/link options

Compiler/assembly/link options

Compiler

Compiler

There is a one-to-one relationship between the items in the text box and the GUI check and dropdown box selections. Once you have mastered the various options, you can probably find

yourself just typing in the options.

2 - 6 C28x - Programming Development Environment

Page 25

Code Composer Studio

Build Options GUI --

Build Options GUI

There are many linker options but these four handle all of the basic needs.

• -o <filename> specifies the output (executable) filename.

Linker

Linker

GUI has 2 categories

GUI has 2 categories

for linking

for linking

Specifies various link

Specifies various link

options

options

Debug\\

“.“.\\Debug

on subfolder level

on subfolder level

below project (.

below project (.

location

location

” indicates

” indicates

pjt) )

pjt

• -m <filename> creates a map file. This file reports the linker’s results.

• -c tells the compiler to autoinitialize your global and static variables.

• -x tells the compiler to exhaustively read the libraries. Without this option libraries are

searched only once, and therefore backwards references may not be resolved.

C28x - Programming Development Environment 2 - 7

Page 26

Code Composer Studio

Default Build Configurations

Default Build Configurations

For new projects, CCS automatically

For new projects, CCS automatically

creates two build configurations:

creates two build configurations:

Debug

Debug

Release

Release

Use the drop--

Use the drop

select the build configuration

select the build configuration

Add/Remove your own custom

Add/Remove your own custom

build configurations using

build configurations using

Project Configurations

Project Configurations

Edit a configuration:

Edit a configuration:

1.

Set it active

1.

Set it active

Modify build options

2.

2.

Modify build options

3.

Save project

3.

Save project

unoptimized))

((unoptimized

(optimized)

(optimized)

down menu to quickly

down menu to quickly

To help make sense of the many compiler options, TI provides two default sets of options

(configurations) in each new project you create. The Release (optimized) configuration invokes

the optimizer with –o3 and disables source-level, symbolic debugging by omitting –g (which

disables some optimizations to enable debug).

2 - 8 C28x - Programming Development Environment

Page 27

Creating a Linker Command File

Creating a Linker Command File

Sections

Looking at a C program, you'll notice it contains both code and different kinds of data (global,

local, etc.).

Sections

Sections

Global Vars (.

int

int

int

int

void main(void)

void main(void)

{

{

}

}

Local vars (

In the TI code-generation tools (as with any toolset based on the COFF – Common Object File

Format), these various parts of a program are called Sections. Breaking the program code and

data into various sections provides flexibility since it allows you to place code sections in ROM

and variables in RAM. The preceding diagram illustrated five sections:

• Global Variables

ebss)

ebss

x = 2;

x = 2;

y = 7;

y = 7;

long z;

long z;

z = x + y;

z = x + y;

.stack) Code (

.stack

Init vals (..

cinit)

cinit

.text)

.text

Every C program

Every C program

consists of different

consists of different

parts called

parts called

All default sections

All default sections

names begin with “.”

names begin with “.”

The compiler has

The compiler has

default sections

default sections

names for

names for

and

uninitialized

and

uninitialized

sections

sections

initialized

initialized

sections

sections

• Initial Values for global variables

• Local Variables (i.e. the stack)

• Code (the actual instructions)

C28x - Programming Development Environment 2 - 9

Page 28

Creating a Linker Command File

Following is a list of the sections that are created by the compiler. Along with their description,

we provide the Section Name defined by the compiler.

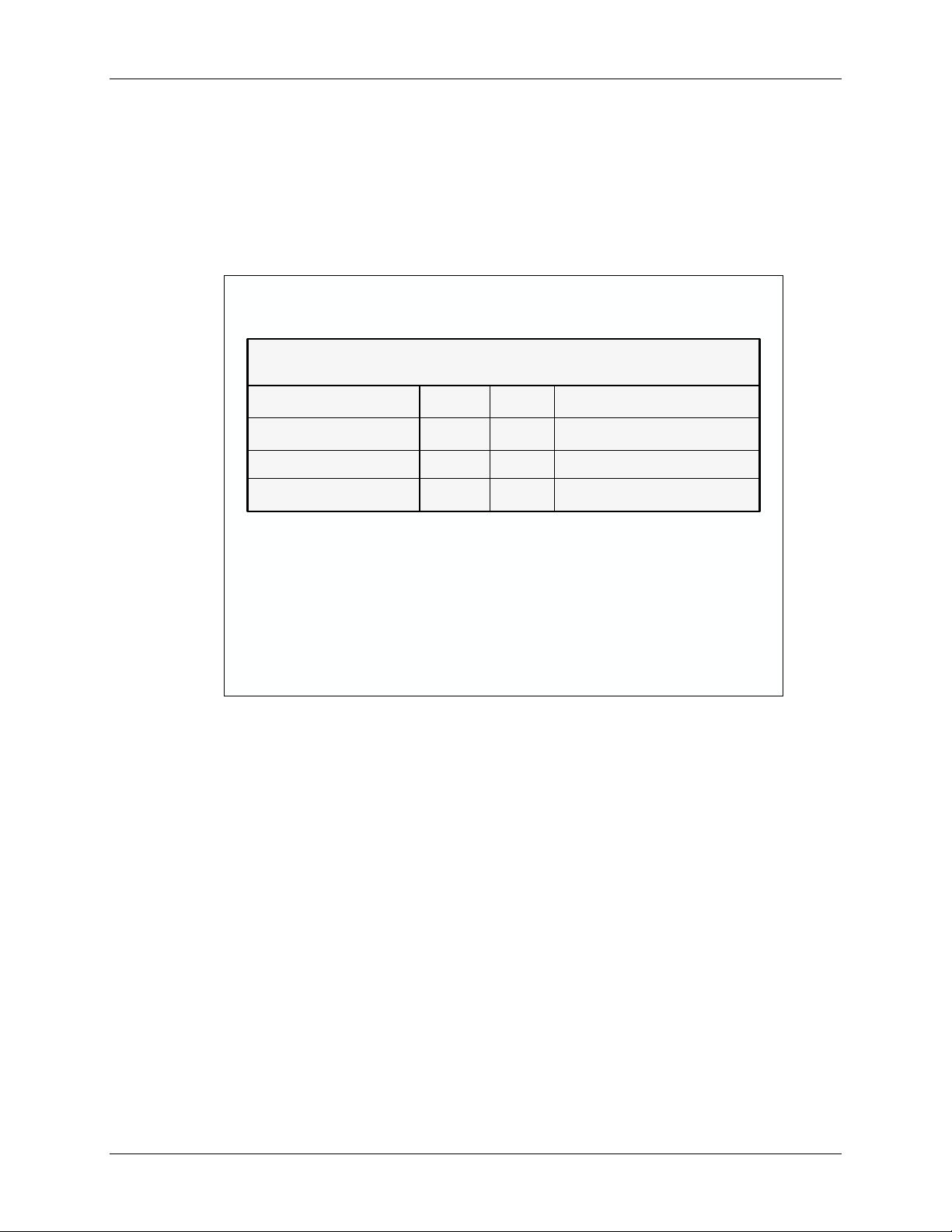

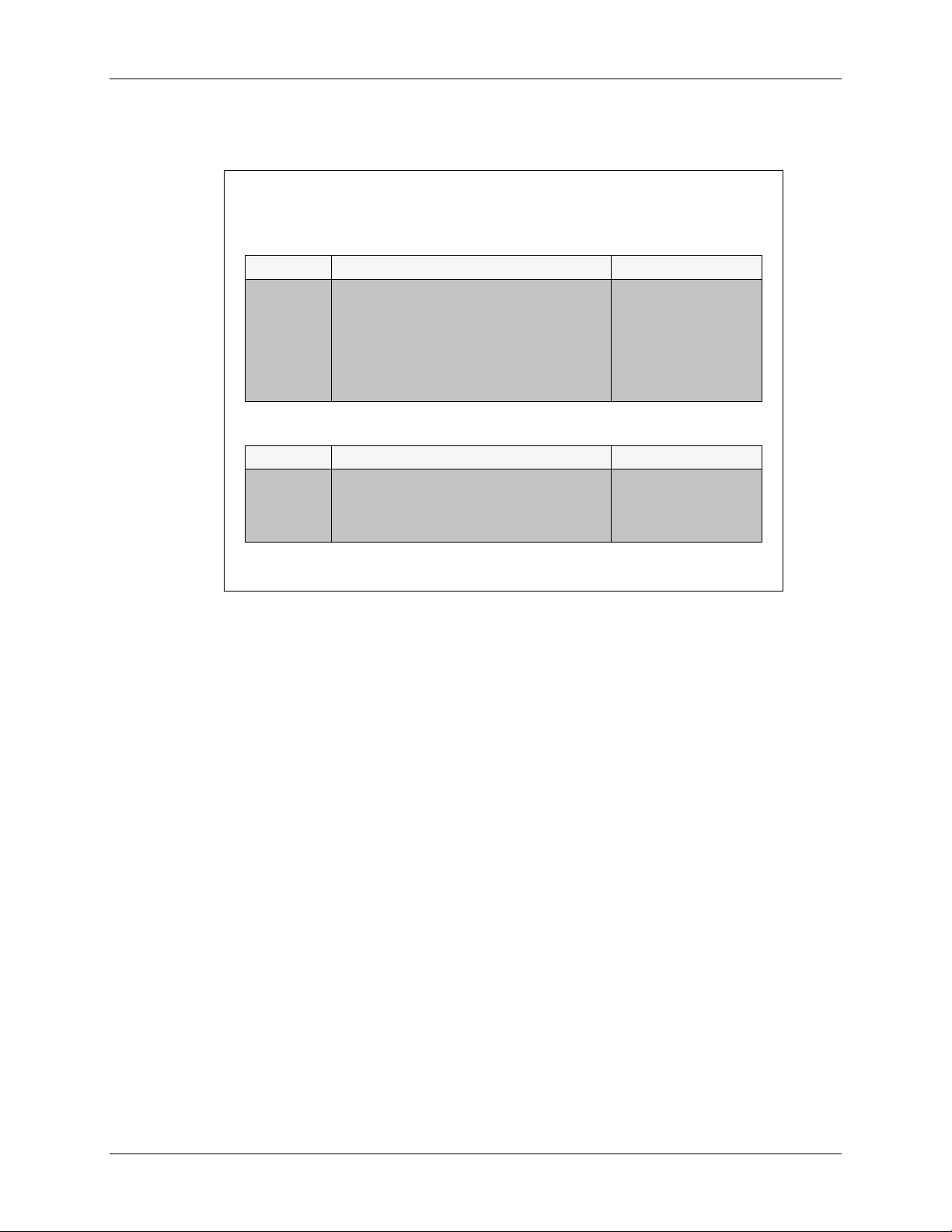

Initialized Sections

Initialized Sections

Name

Name

.text

.text

cinit

..cinit

econst

..econst

.switch

.switch

pinit

..pinit

Compiler Section Names

Compiler Section Names

Description

Description

code

code

initialized global and static variables program

initialized global and static variables program

constant data (e.g. const

constant data (e.g. const

tables for switch statements

tables for switch statements

tables for global constructors (C++)

tables for global constructors (C++)

int

k = 3;) data

int

k = 3;) data

Link Location

Link Location

program

program

prog

/low 64K data

prog

/low 64K data

program

program

Uninitialized

Uninitialized

Name

Name

ebss

..ebss

.stack stack space

.stack stack space

esysmem

..esysmem

Sections

Sections

Description

Description

global & static variables

global & static variables

memory for far

memory for far

malloc

malloc

functions

functions

Link Location

Link Location

data

data

low 64K data

low 64K data

data

data

Sections of a C program must be located in different memories in your target system. This is the

big advantage of creating the separate sections for code, constants, and variables. In this way,

they can all be linked (located) into their proper memory locations in your target embedded

system. Generally, they’re located as follows:

Program Code (.text)

Program code consists of the sequence of instructions used to manipulate data, initialize system

settings, etc. Program code must be defined upon system reset (power turn-on). Due to this basic

system constraint it is usually necessary to place program code into non-volatile memory, such as

FLASH or EPROM.

Constants (.cinit – initialized data)

Initialized data are those data memory locations defined at reset.It contains constants or initial

values for variables. Similar to program code, constant data is expected to be valid upon reset of

the system. It is often found in FLASH or EPROM (non-volatile memory).

Variables (.ebss – uninitialized data)

Uninitialized data memory locations can be changed and manipulated by the program code during

runtime execution. Unlike program code or constants, uninitialized data or variables must reside

in volatile memory, such as RAM. These memories can be modified and updated, supporting the

way variables are used in math formulas, high-level languages, etc. Each variable must be

declared with a directive to reserve memory to contain its value. By their nature, no value is

assigned, instead they are loaded at runtime by the program

2 - 10 C28x - Programming Development Environment

Page 29

Creating a Linker Command File

Placing Sections in Memory

Placing Sections in Memory

Memory

0x00 0000

0x00 0000

0x00 0400

0x00 0400

0x3D 8000

0x3D 8000

Memory

M0SARAM

M0SARAM

(0x400)

(0x400)

M1SARAM

M1SARAM

(0x400)

(0x400)

FLASH

FLASH

(0x20000)

(0x20000)

Sections

Sections

ebss

..ebss

.stack

.stack

cinit

..cinit

.text

.text

Linking code is a three step process:

1. Defining the various regions of memory (on-chip SARAM vs. FLASH vs. External Memory).

2. Describing what sections go into which memory regions

3. Running the linker with “build” or “rebuild”

C28x - Programming Development Environment 2 - 11

Page 30

Creating a Linker Command File

Linker Command Files (.cmd)

The linker concatenates each section from all input files, allocating memory to each section based

on its length and location as specified by the MEMORY and SECTIONS commands in the linker

command file.

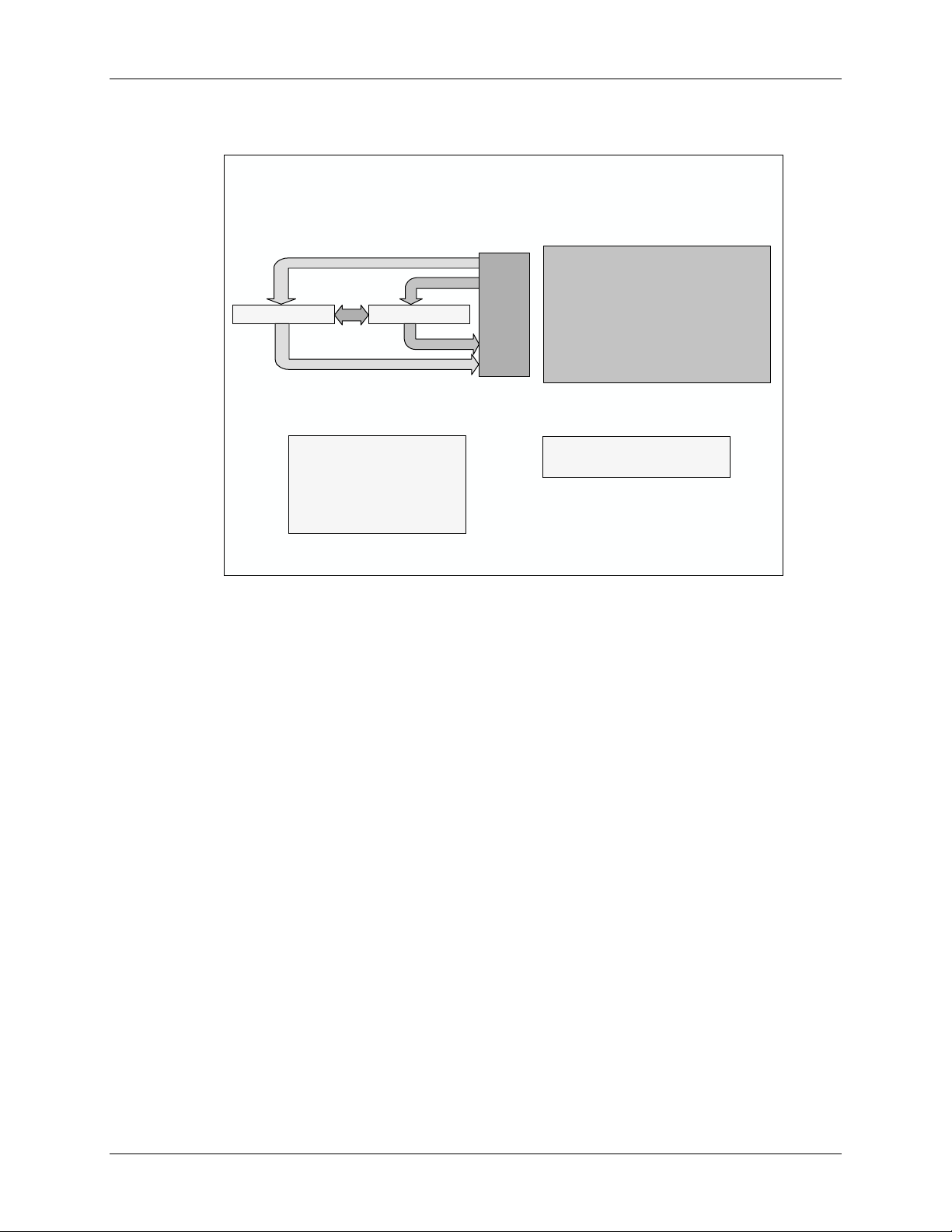

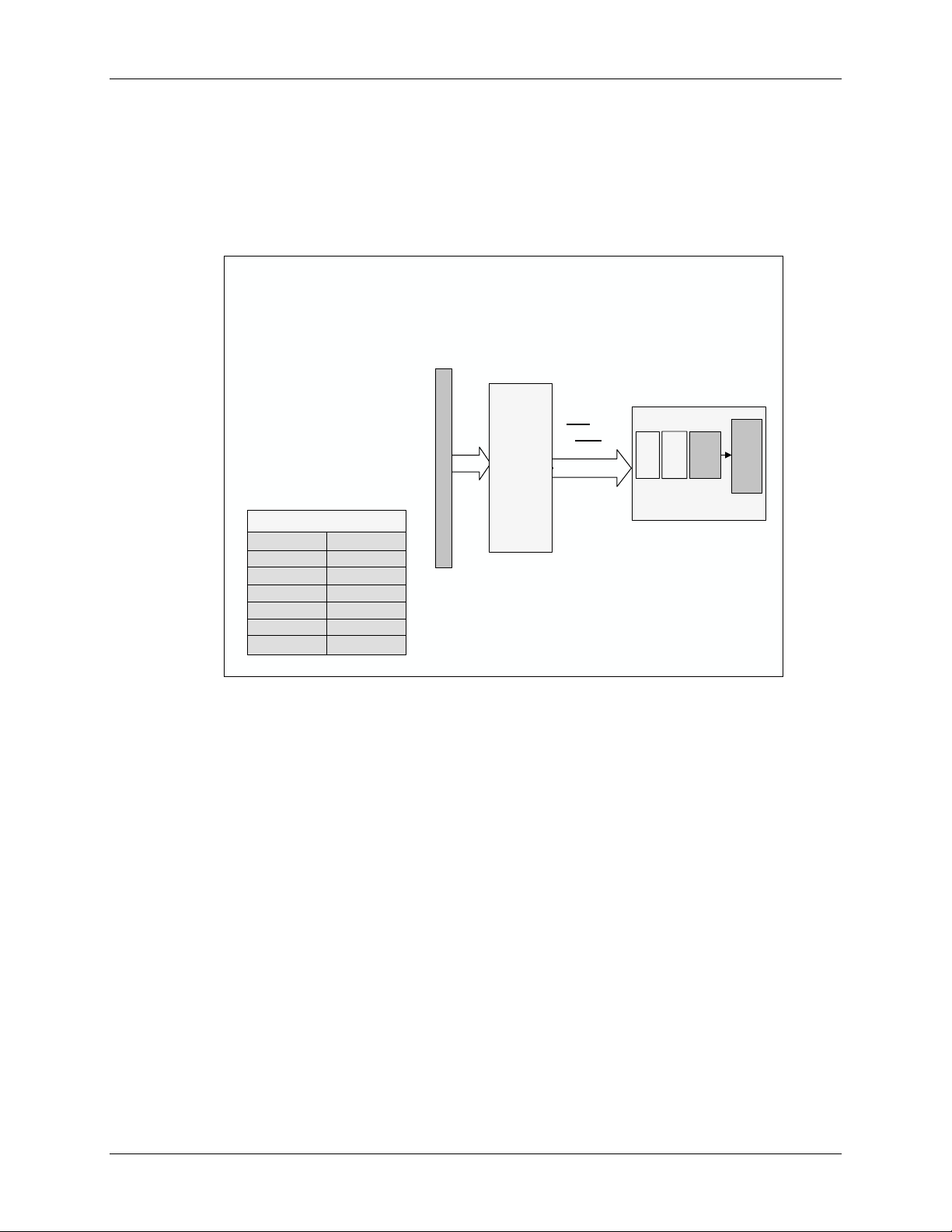

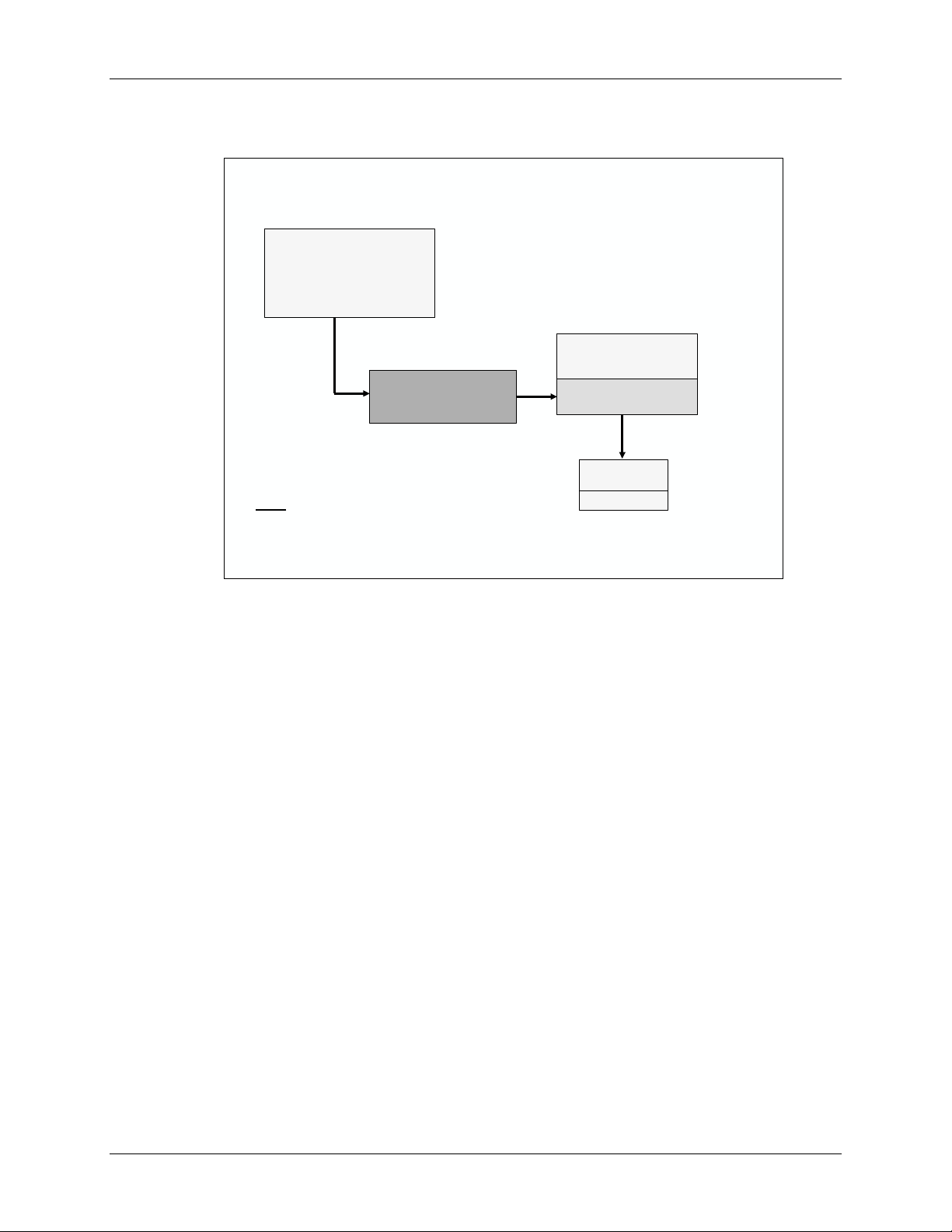

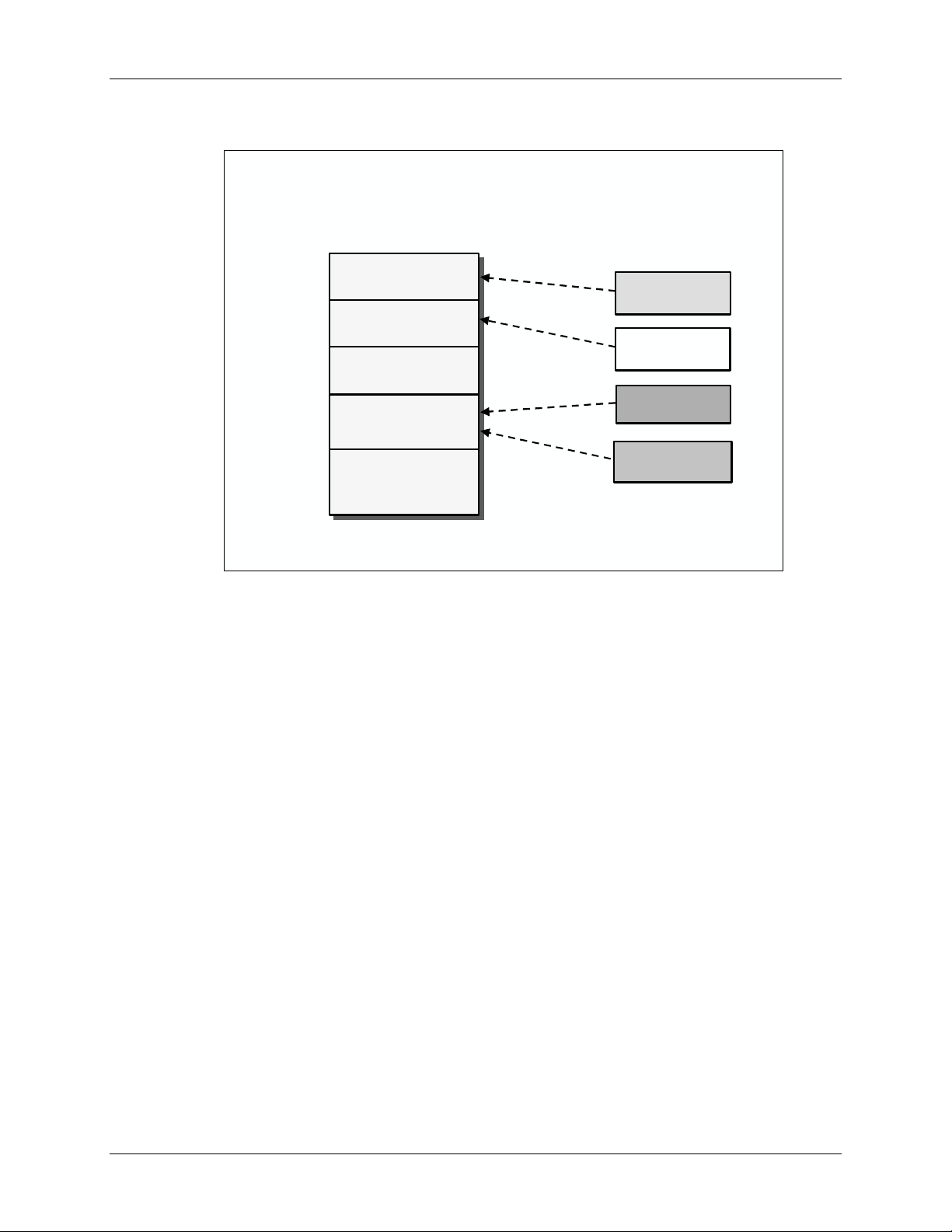

Linking

Linking

Memory description

Memory description

Memory description

How to place s/w into h/w

How to place s/w into h/w

How to place s/w into h/w

obj

..obj

Link.

Link.

Linker

Linker

.map

.map

cmd

cmd

.out

.out

Memory-Map Description

Describe the memory configuration of your target system to the linker. Without this specification,

the linker might place code or data into memory that doesn’t exist.

The format is: Name: origin = 0x????, length = 0x????

For example, if you placed a 2K EPROM starting at memory location zero, it would read:

MEMORY

{

EPROM: origin = 0x0000 , length = 0x0800

}

You define each memory segment using the above format. If you added a RAM and an ABT646

transceiver, it might look like:

MEMORY

{

EPROM: origin = 0x0000 , length = 0x0800

RAM: origin = 0x1000 , length = 0x02000

ABT646: origin = 0x8000 , length = 0x00001

}

2 - 12 C28x - Programming Development Environment

Page 31

Creating a Linker Command File

Remember that the DSP has two memory maps: Program, and Data. Therefore, the MEMORY

description must describe each of these separately. The loader uses the following syntax to

delineate each of these:

Linker Page TI Definition

Page 0 Program

Page 1 Data

Linker Command File

Linker Command File

MEMORY

MEMORY

{

{

PAGE 0: /* Program Space */

PAGE 0: /* Program Space */

FLASH: org = 0x3D8000,

FLASH: org = 0x3D8000,

PAGE 1: /* Data Space */

PAGE 1: /* Data Space */

M0SARAM: org = 0x000000,

M0SARAM: org = 0x000000,

M1SARAM: org = 0x000400,

M1SARAM: org = 0x000400,

}

}

len

len

len

len

len

len

= 0x20000

= 0x20000

= 0x400

= 0x400

= 0x400

= 0x400

C28x - Programming Development Environment 2 - 13

Page 32

Creating a Linker Command File

Section Placement

You can specify how you want the sections to be distributed through memory. You would use the

following code to link the sections into the memory specified in the previous example:

SECTIONS

{

.text:> FLASH PAGE 0

.ebss:> M0SARAM PAGE 1

.cinit:> FLASH PAGE 0

.stack:> M1SARAM PAGE 1

}

The linker will gather all the code sections from all the files being linked together. Similarly, it

will combine all ‘like’ sections.

Beginning with the first section listed, the linker will place it into the specified memory segment.

Linker Command File

Linker Command File

MEMORY

MEMORY

{

{

PAGE 0:

PAGE 0:

FLASH: org = 0x3D8000,

FLASH: org = 0x3D8000,

PAGE 1:

PAGE 1:

M0SARAM: org = 0x000000,

M0SARAM: org = 0x000000,

M1SARAM: org = 0x000400,

M1SARAM: org = 0x000400,

}

}

SECTIONS

SECTIONS

{

{

.text:> FLASH PAGE 0

.text:> FLASH PAGE 0

ebss

..ebss

..cinit

.stack:>

.stack:>

}

}

:> M0SARAM PAGE 1

:> M0SARAM PAGE 1

cinit

:> FLASH PAGE 0

:> FLASH PAGE 0

/* Program Space */

/* Program Space */

len

= 0x20000

len

= 0x20000

/* Data Space */

/* Data Space */

len

= 0x400

len

= 0x400

len

= 0x400

len

= 0x400

M1SARAM

M1SARAM

PAGE 1

PAGE 1

2 - 14 C28x - Programming Development Environment

Page 33

Exercise 2a

Exercise 2a

Looking at the following block diagram, and create a linker command file.

Exercise 2a

Exercise 2a

0x00 0000

0x00 0000

0x00 8000

0x00 8000

M0SARAM

M0SARAM

(0x400)

(0x400)

L0SARAM

L0SARAM

(0x1000)

(0x1000)

0x00 0400

0x00 0400

0x00 9000

0x00 9000

M1SARAM

M1SARAM

(0x400)

(0x400)

L1SARAM

L1SARAM

(0x1000)

(0x1000)

Create the linker command file for the given memory

Create the linker command file for the given memory

map by filling in the blanks on the following slide

map by filling in the blanks on the following slide

Fill in the blanks:

0x3D 8000

0x3D 8000

F2812

F2812

Exercise 2a --

Exercise 2a

Memory

Memory

{

{

PAGE__: /* Program Space */

PAGE__: /* Program Space */

_____: org = ____

_____: org = ____

______: /* Data Space */

______: /* Data Space */

_______: org = ___

_______: org = ___

_______:

_______:

_______:

_______:

_______: org = ___

_______: org = ___

_______: org = ___

_______: org = ___

}

}

SECTIONS

SECTIONS

{

{

.text: > FLASH PAGE 0

.text: > FLASH PAGE 0

ebss

: > M1SARAM PAGE 1

..ebss

: > M1SARAM PAGE 1

cinit

..cinit

.stack: > M0SARAM PAGE 1

.stack: > M0SARAM PAGE 1

}

}

FLASH

FLASH

(0x20000)

(0x20000)

org = ____

org = ____

org = ___

org = ___

: > FLASH PAGE 0

: > FLASH PAGE 0

0x3F 8000

0x3F 8000

Command File

Command File

____,

____,

____,

____,

____,

____,

____,

____,

H0SARAM

H0SARAM

(0x2000)

(0x2000)

___,

___,

___,

___,

len

len

len

len

len

len

len

len

len

len

len

len

= ___

= ___

= _____

= _____

= _____

= _____

= __

___

= __

= _

= _

= _

= _

___

____

____

____

____

___

___

C28x - Programming Development Environment 2 - 15

Page 34

Exercise 2a

Summary: Linker Command File

The linker command file (.cmd) contains the inputs — commands — for the linker. This

information is summarized below:

Linker Command File Summary

Linker Command File Summary

Memory Map Description

Memory Map Description

Name

Name

Location

Location

Size

Size

Sections Description

Sections Description

Directs software sections into named

Directs software sections into named

memory regions

memory regions

Allows per--

Allows per

Allows separate load/run locations

Allows separate load/run locations

file discrimination

file discrimination

2 - 16 C28x - Programming Development Environment

Page 35

Lab 2a: Linker Command File

Lab 2a: Linker Command File

Objective

Create a linker command file and link the C program file (LAB2.C) into the system described

below.

Lab 2a: Linker Command File

Lab 2a: Linker Command File

Memory

Memory

chip

onon--chip

on-chip

memory

memory

memory

F2812

F2812

System Description:

System Description:

TMS320F2812

••TMS320F2812

All internal RAM blocks allocated

••All internal RAM blocks allocated

Placement of Sections:

Placement of Sections:

.text into RAM Block H0SARAM on PAGE 0 (code space)

••.text into RAM Block H0SARAM on PAGE 0 (code space)

cinit

into RAM Block H0SARAM on PAGE 0 (code space)

••..cinit

into RAM Block H0SARAM on PAGE 0 (code space)

ebss

••..ebss

••.stack into RAM Block M0SARAM on PAGE 1 (data space)

into RAM Block M1SARAM on PAGE 1 (data space)

into RAM Block M1SARAM on PAGE 1 (data space)

.stack into RAM Block M0SARAM on PAGE 1 (data space)

System Description

• TMS320F2812

• All internal RAM blocks allocated

M0SARAM

M0SARAM

M0SARAM

(0x400)

(0x400)

(0x400)

M1SARAM

M1SARAM

M1SARAM

(0x400)

(0x400)

(0x400)

H0SARAM

H0SARAM

H0SARAM

(0x2000)

(0x2000)

(0x2000)

0x00 0000

0x00 0000

0x00 0400

0x00 0400

0x3F 8000

0x3F 8000

L0SARAM

L0SARAM

L0SARAM

(0x1000)

(0x1000)

(0x1000)

L1SARAM

L1SARAM

L1SARAM

(0x1000)

(0x1000)

(0x1000)

0x00 8000

0x00 8000

0x00 9000

0x00 9000

Placement of Sections:

• .text into RAM Block H0SARAM on PAGE 0 (code space)

• .cinit into RAM Block H0SARAM on PAGE 0 (code space)

• .ebss into RAM Block M1SARAM on PAGE 1 (data space)

• .stack into RAM Block M0SARAM on PAGE 1 (data space)

Procedure

Create a New Project

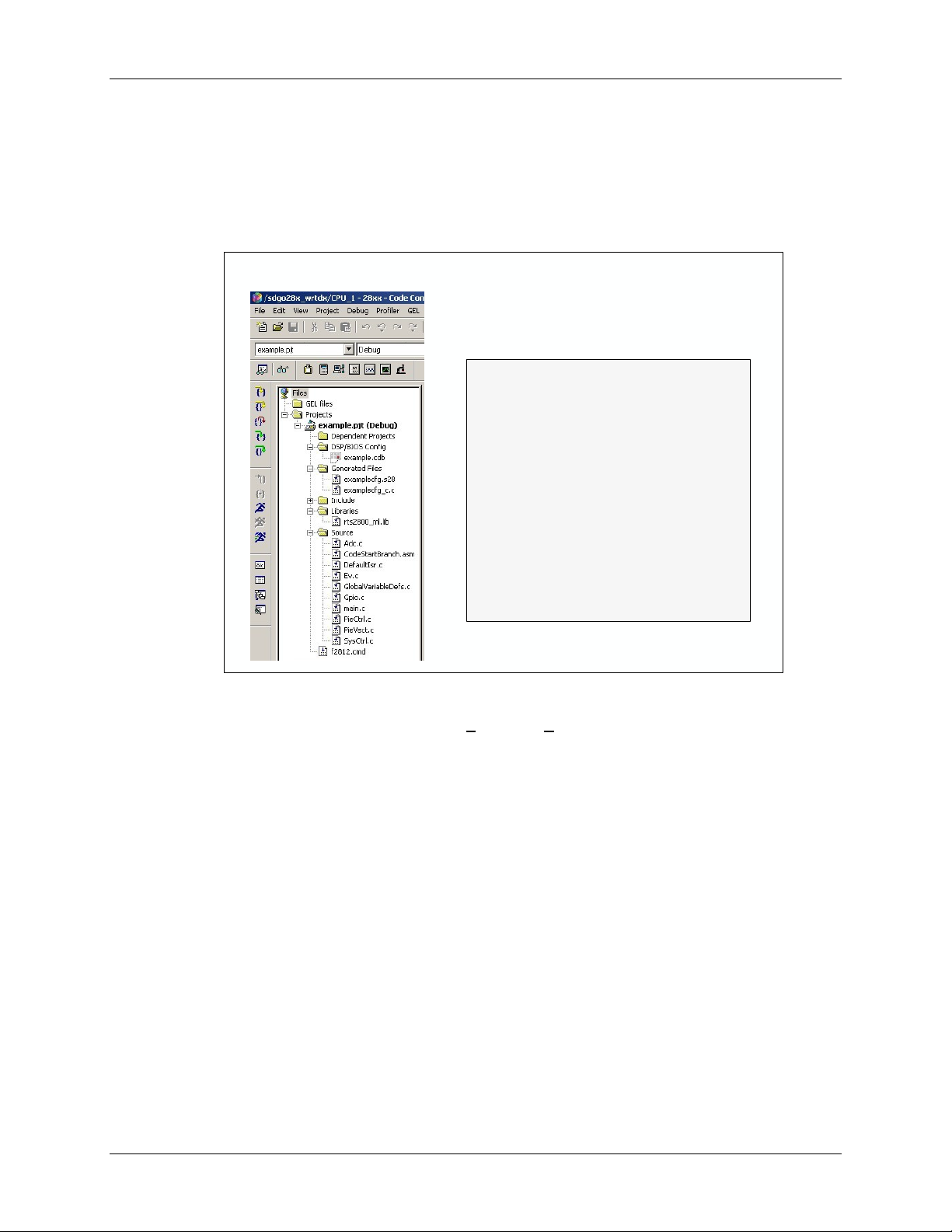

1. Double click on the Code Composer Studio icon on the desktop. Maximize Code

Composer Studio to fill your screen. The menu bar (at the top) lists File ... Help. Note

the horizontal tool bar below the menu bar and the vertical tool bar on the left-hand side.

C28x - Programming Development Environment 2 - 17

Page 36

Lab 2a: Linker Command File

The window on the left is the project window and the large right hand window is your

workspace.

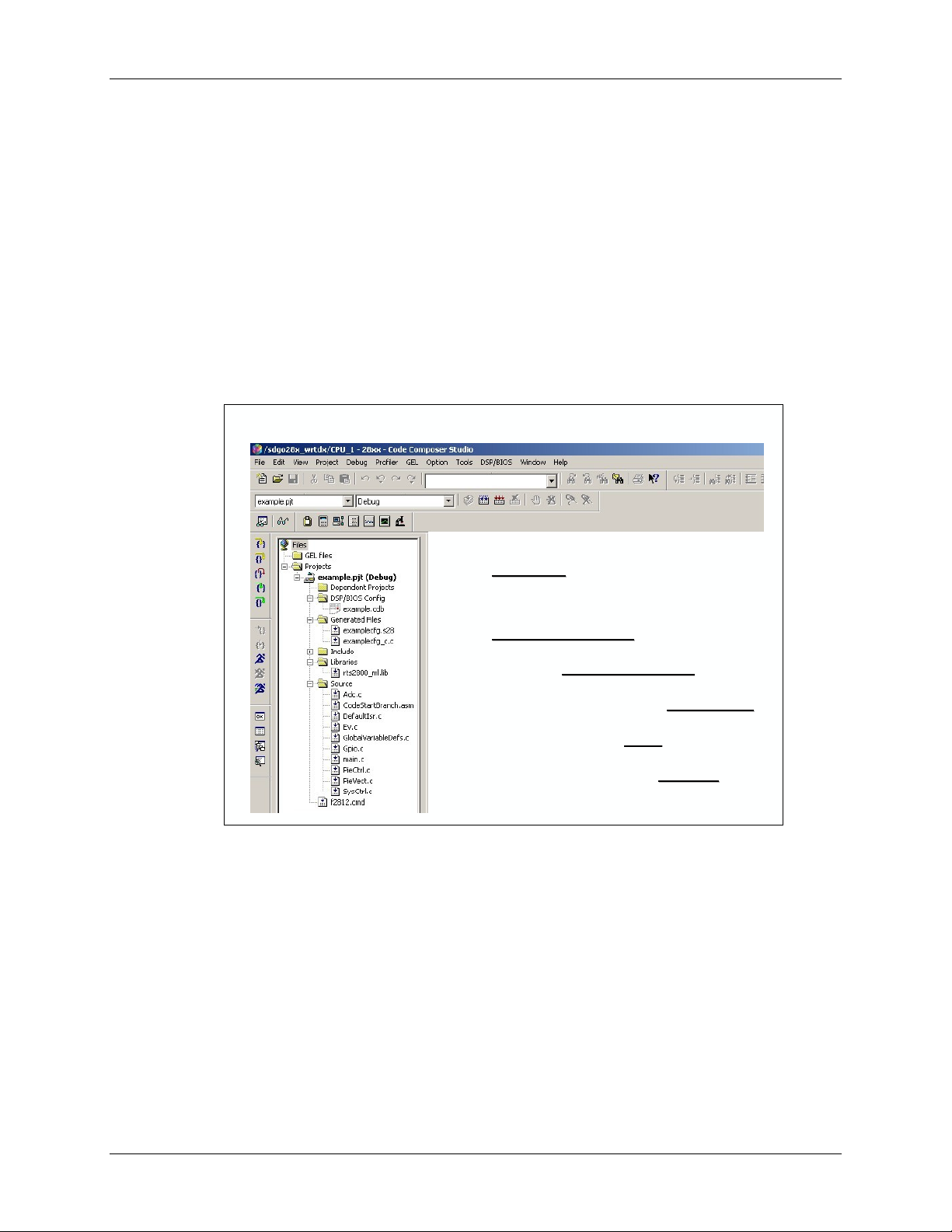

2. A project is all the files you will need to develop an executable output file (.out) which

can be run on the DSP hardware. Let’s create a new project for this lab. On the menu bar

click:

Project New

type Lab2 in the project name field and make sure the save in location is:

C:\C28x\LABS\LAB2. This will create a .pjt file which will invoke all the necessary

tools (compiler, assembler, linker) to build your project. It will also create a debug

folder that will hold immediate output files.

3. Add the C file to the new project. Click:

Project Add Files to Project…

and make sure you’re looking in C:\C28x\LABS\LAB2. Change the “files of type” to

view C source files (*.c) and select Lab2.c and click OPEN. This will add the file

Lab2.c to your newly created project.

4. Add Lab2a.cmd to the project using the same procedure. This file will be edited

during the lab exercise.

5. Next, add the compiler run-time support library to the project

(C:\ti\c2000\cgtools\lib\rts2800_ml.lib).

6. In the project window on the left click the plus sign (+) to the left of Project. Now,

click on the plus sign next to Lab2.pjt. Notice that the Lab2a.cmd file is listed.

Click on Source to see the current source file list (i.e. Lab2.c).

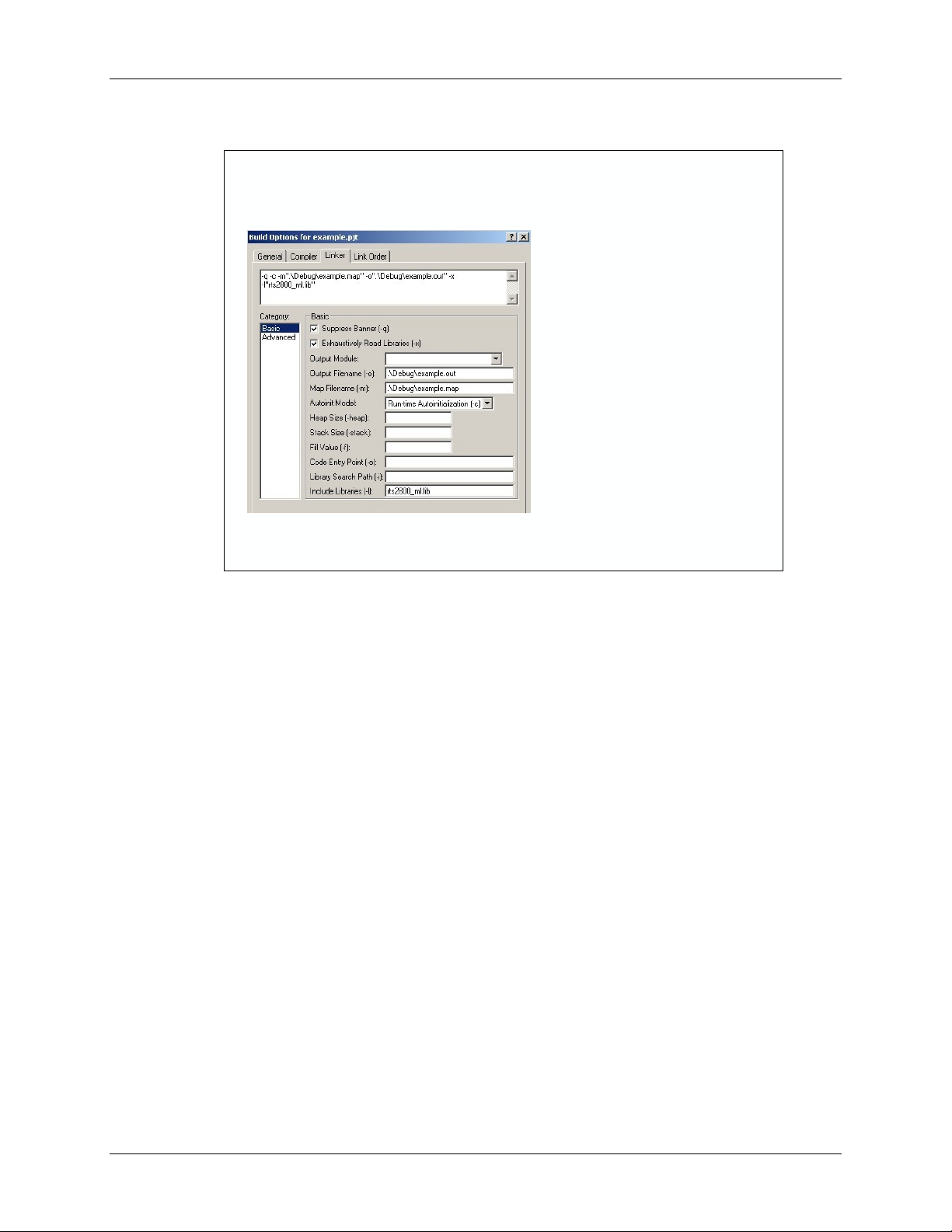

Project Build Options

7. There are numerous build options in the project. The default option settings are sufficient

for getting started. We will inspect a couple of the default linker options at this time.

Click: Project Build Options…

8. Select the Linker tab. Notice that .out and .map files are being created. The .out file is

the executable code that will be loaded into the DSP. The .map file will contain a linker

report showing memory useage and section addresses in memory.

9. Set the Stack Size to 0x200. Select OK and then close the Build Options window.

Edit the Linker Command File - Lab2a.cmd

10. To open and edit Lab2a.cmd, double click on the filename in the project window.

11. Edit the Memory{} declaration by describing the system memory shown on the “Lab2a:

Linker Command File” slide.

2 - 18 C28x - Programming Development Environment

Page 37

Lab 2a: Linker Command File

12. In the Sections{} area, notice that a section called .reset has already been allocated.

The .reset section is part of the rts2800_ml.lib, and is not needed. By putting the TYPE =

DSECT modifier after its allocation, the linker will ignor this section and not allocate it.

13. Place the sections defined on the slide into the appropriate memories via the

Sections{} area. Save your work.

Build and Load the Project

14. The top four buttons on the horizontal toolbar control code generation. Hover your

mouse over each button as you read the following descriptions:

Button Name Description

1 Compile File Compile, assemble the current open file

2 Incremental Build Compile, assemble only changed files, then link

3 Rebuild All Compile, assemble all files, then link

4 Stop Build Stop code generation

15. Code Composer Studio can automatically load the output file after a successful build. On

the menu bar click: Option Customize… and select the “Program Load

Options” tab, check “Load Program After Build”, then click OK.

16. Click the “Build” button and watch the tools run in the build window. Check for

errors (we have deliberately put an error in Lab2.c). When you get an error, scroll the

build window at the bottom of the Code Composer Studio screen until you see the error

message (in red), and simply double-click the error message. The editor will

automatically open the source file containing the error, and position the mouse cursor at

the correct code line.

17. Fix the error by adding a semicolon at the end of the "z = x + y" statement. For

future knowlege, realize that a single code error can sometimes generate multiple error

messages at build time. This was not the case here.

18. Rebuild the project (there should be no errors this time). The output file should

automatically load. The Program Counter should be pointing to _c_int00 in the

Disassembly Window.

19. Under Debug on the menu bar click “Go Main”. This will run through the C-

environment initialization routine in the rts2800_ml.lib and stop at main() in

Lab2.c.

Debug Enviroment Windows

It is standard debug practice to watch local and global variables while debugging code. There

are various methods for doing this in Code Composer Studio. We will examine two of them

here: memory windows, and watch windows.

20. Open a memory window to view the global variable “z”.

Click: View Memory on the menu bar.

C28x - Programming Development Environment 2 - 19

Page 38

Lab 2a: Linker Command File

Type “&z” into the address field. Note that you must use the ampersand (meaning

"address of") when using a symbol in a memory window address box. Also note that

Code Composer Studio is case sensitive.

Set the properties format to “Hex – TI style.” This will give you more viewable data in

the window.

Click OK to close the window property selection screen. The memory window will now

open. You can change the contents of any address in the memory window by doubleclicking on its value. This is useful during debug.

21. Open the watch window to view the local variables x and y.

Click: View Watch Window on the menu bar.

Click the “Watch Locals” tab and notice that the local variables x and y are already

present. The watch window will always contain the local variables for the code function

currently being executed.

(Note that local variables actually live on the stack. You can also view local variables in

a memory window by setting the address to “SP” after the code function has been

entered).

22. We can also add global variables to the watch window if desired. Let's add the global

variable “z”.

Click the “Watch 1" tab at the bottom of the watch window. In the empty box in the

"Name" column, type “z”. Note that you do not use an ampersand here. The watch

window knows you are specifying a symbol.

Check that the watch window and memory window both report the same value for “z”.

Trying changing the value in one window, and notice that the value also changes in the

other window.

Single-stepping the Code

23. Single-step through main() by using the <F8> key (or you can use the Single

Step button on the vertical toolbar). Check to see if the program is working as

expected. What is the value for “z” when you get to the end of the program?

End of Exercise

2 - 20 C28x - Programming Development Environment

Page 39

DSP/BIOS Configuration Tool

DSP/BIOS Configuration Tool

The DSP/BIOS Configuration Tool (often called Config Tool or GUI Tool or GUI) creates and

modifies a system file called the Configuration DataBase (.CDB). If we talk about using CDB

files, we’re also talking about using the Config Tool.

(file .

DSP/BIOS Configuration Tool

DSP/BIOS Configuration Tool

MEM handles system

MEM handles system

memory configuration

memory configuration

(builds .

(builds .

Configures BIOS

Configures BIOS

scheduling, RTA and

scheduling, RTA and

other BIOS functions

other BIOS functions

Automatically

Automatically

handles: run--

handles: run

support libraries,

support libraries,

interrupt vectors,

interrupt vectors,

system reset, etc.

system reset, etc.

cmd

cmd

(file .

file)

file)

time

time

cdb))

cdb

The GUI (graphical user interface) simplifies system design by:

• Automatically including the appropriate runtime support libraries

• Automatically handles interrupt vectors and system reset

• Handles system memory configuration (builds CMD file)

• When a CDB file is saved, the Config Tool generates 5 additional files:

Filename.cdb

Filenamecfg_c.c

Filenamecfg.s28

Filenamecfg.cmd

Filenamecfg.h

Filenamecfg.h28

When you add a CDB file to your project, CCS automatically adds the C and assembly

(.S28) files to the project under the Generated Files folder. (You must manually add the

CMD file, yourself.)

Configuration Database

C code created by Config Tool

ASM code created by Config Tool

Linker commands

header file for *cfg_c.c

header file for *cfg.s28

C28x - Programming Development Environment 2 - 21

Page 40

DSP/BIOS Configuration Tool

1. Creating a New Memory Region (Using MEM)

First, to create a specific memory area, open up the .CDB file, right-click on the Memory Section

Manager and select “Insert MEM”. Give this area a unique name and then specify its base and

length. Once created, you can place sections into it (shown in the next step).

Memory Section Manager

Memory Section Manager

Mem

manager allows

Mem

you to create

you to create

memory area and

memory area and

place sections

place sections

To create a new

To create a new

memory area:

memory area:

manager allows

Right--

click on MEM

Right

click on MEM

and select Insert

and select Insert

memory

memory

Fill in base, length,

Fill in base, length,

space

space

2 - 22 C28x - Programming Development Environment

Page 41

DSP/BIOS Configuration Tool

2. Placing Sections – MEM Manager Properties

The configuration tool makes it easy to place sections. The predefined compiler sections that

were described earlier each have their own drop-down menu to select one of the memory regions

you defined (in step 1).

Memory Section Manager Properties

Memory Section Manager Properties

To place a section

To place a section

into a memory area:

into a memory area:

Right--

click on MEM

Right

click on MEM

and select

and select

Properties

Properties

Select the

Select the

appropriate tab (e.g.

appropriate tab (e.g.

Compiler)

Compiler)

Select the memory

Select the memory

for each section

for each section

C28x - Programming Development Environment 2 - 23

Page 42

DSP/BIOS Configuration Tool

3. Running the Linker

Creating the Linker Command File (via .CDB)

When you have finished creating memory regions and allocating sections into these memory

areas (i.e. when you save the .CDB file), the CCS configuration tool creates five files. One of the

files is BIOS’s cfg.cmd file — a linker command file.

Files Created by

Files Created by

MEMORY{

MEMORY{

FLASH: org = 0x3D8000, len = 0x20000

FLASH: org = 0x3D8000, len = 0x20000

H0SARAM: org = 0x3F8000, len = 0x2000

H0SARAM: org = 0x3F8000, len = 0x2000

… }

… }

SECTIONS{

SECTIONS{

.text: > FLASH

.text: > FLASH

.bss: > M0SARAM

.bss: > M0SARAM

… }

… }

Config

Config

Config

Config

different files

different files

Notice, one of them is the

Notice, one of them is the

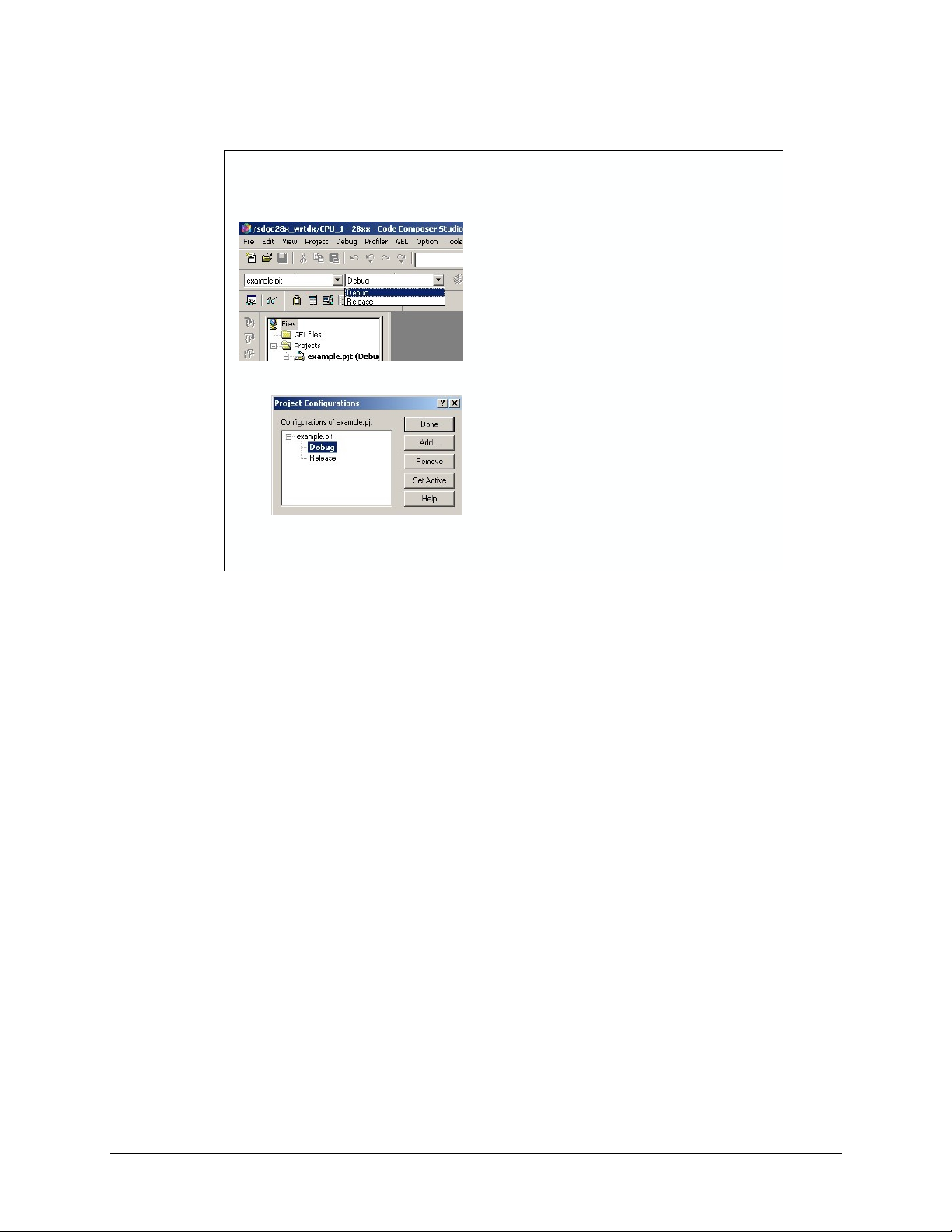

linker command file

linker command file

CMD file is generated from

CMD file is generated from

your MEM settings

your MEM settings

Tool

Tool

tool generates five

tool generates five

cfg_c.c

**cfg_c.c

cfg.s28

**cfg.s28

cfg.cmd

**cfg.cmd

cfg.h

**cfg.h

cfg.h28

**cfg.h28

This file contains two main parts, MEMORY and SECTIONS. (Though, if you open and

examine it, it’s not quite as nicely laid out as shown above.)

2 - 24 C28x - Programming Development Environment

Page 43

DSP/BIOS Configuration Tool

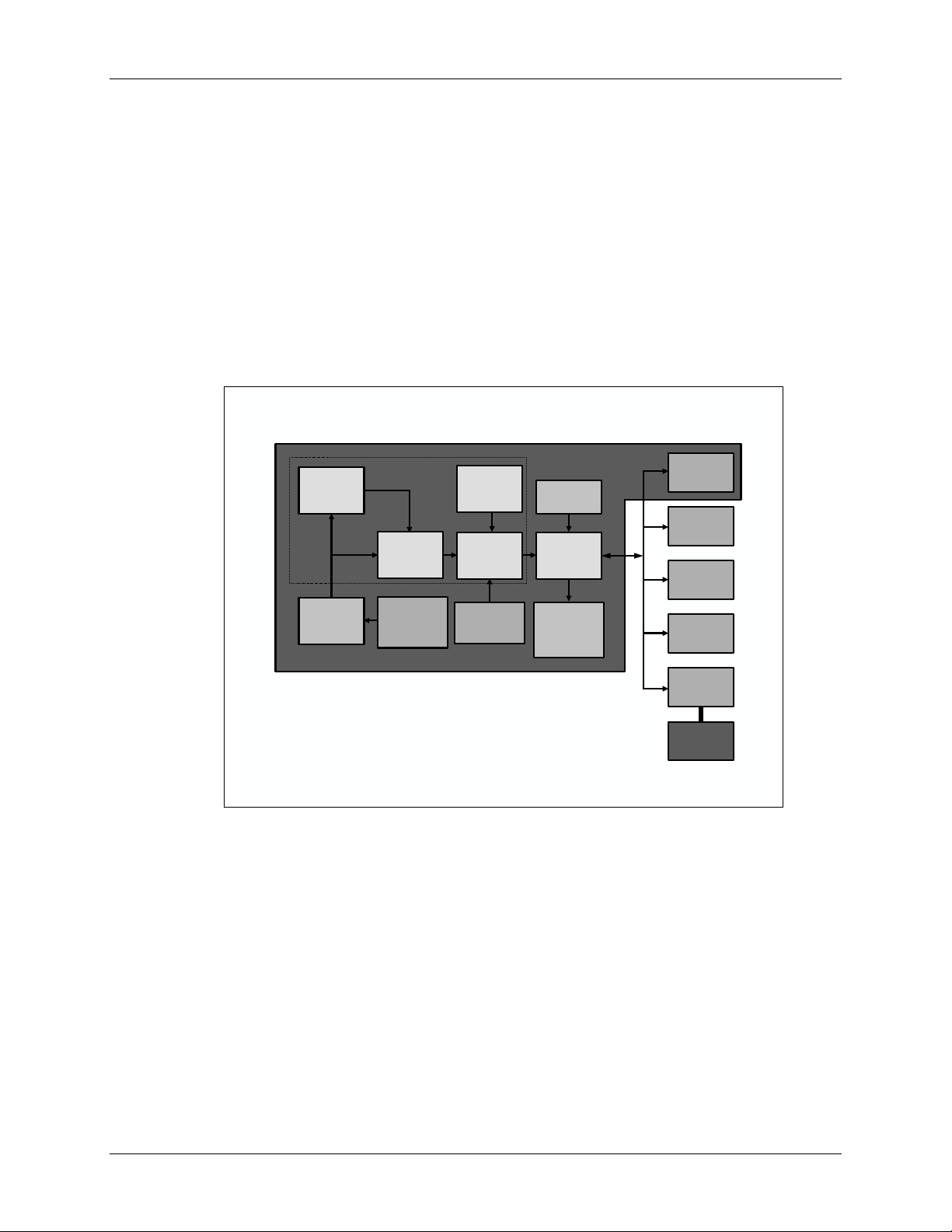

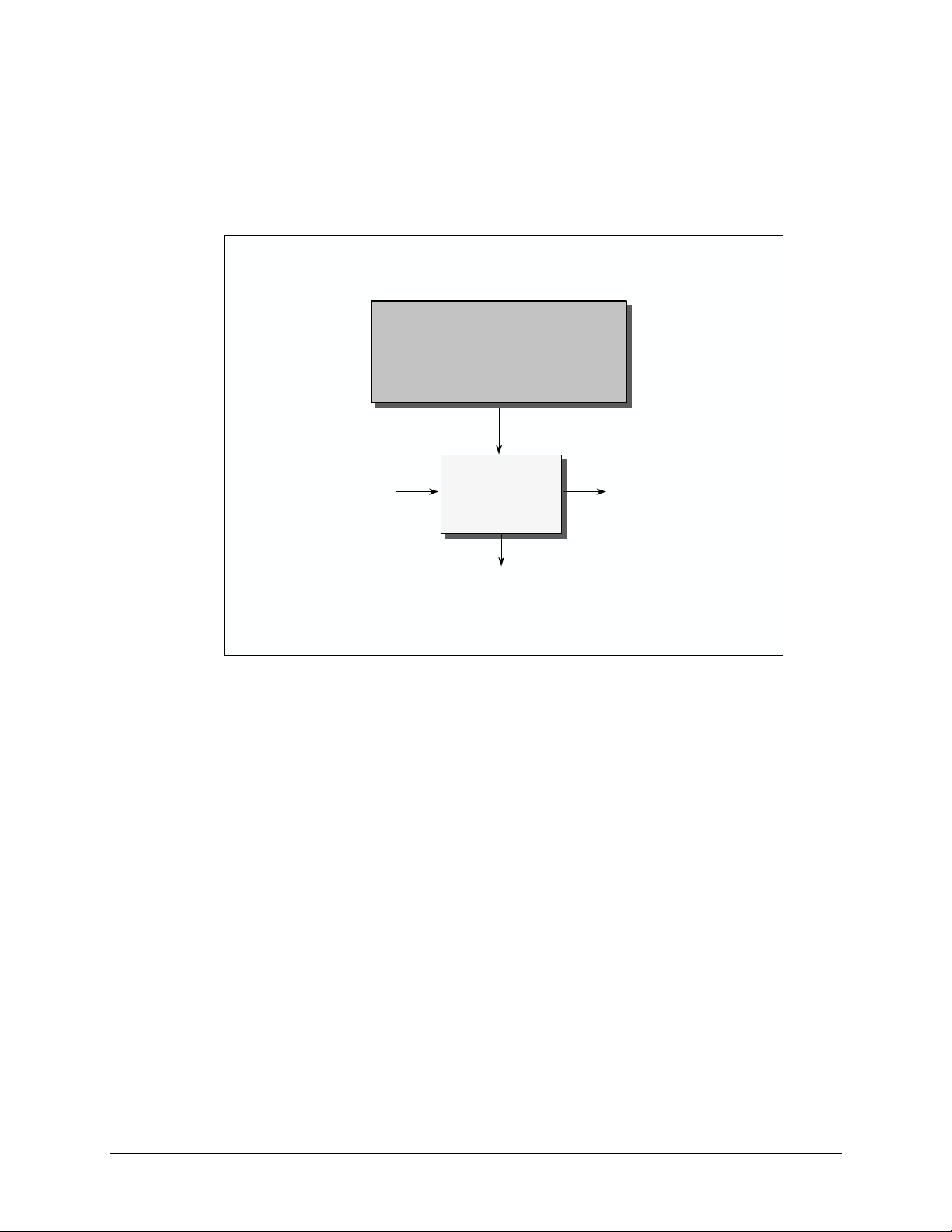

Running the Linker

The linker’s main purpose is to link together various object files. It combines like-named input

sections from the various object files and places each new output section at specific locations in

memory. In the process, it resolves (provides actual addresses for) all of the symbols described in

your code.

Config

Config

Tool Linker Command File

Tool Linker Command File

“Build”

app.cdb

Linker

appcfg.cmd

Linker

.obj files

libraries

(.lib)